## South Dakota State University

# Open PRAIRIE: Open Public Research Access Institutional Repository and Information Exchange

**Electronic Theses and Dissertations**

1986

## The Vector Processor

Ramachandra K. Manja

Follow this and additional works at: https://openprairie.sdstate.edu/etd

#### **Recommended Citation**

Manja, Ramachandra K., "The Vector Processor" (1986). *Electronic Theses and Dissertations*. 4407. https://openprairie.sdstate.edu/etd/4407

This Thesis - Open Access is brought to you for free and open access by Open PRAIRIE: Open Public Research Access Institutional Repository and Information Exchange. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of Open PRAIRIE: Open Public Research Access Institutional Repository and Information Exchange. For more information, please contact michael.biondo@sdstate.edu.

#### THE VECTOR PROCESSOR

bу

Ramachandra K. Manja

A thesis paper

in partial fulfillment of the requirements of the

Degree, Master of Science, Department of

Electrical Engineering

South Dakota State University

1986

THE VECTOR PROCESSOR

bу

Ramachandra K. Manja

This thesis paper is approved as a creditable and independent investigation by a candidate for the degree, Master of Science, and is acceptable for meeting the thesis paper requirements for this degree. Acceptance of this thesis paper does not imply that the conclusions reached by candidate are necessarily the conclusions of the major department.

Thesis Paper Advisor

Date

Head, Electrical Engineering Date

#### **ACKNOWLEDGEMENTS**

It is with immense pleasure that I acknowledge excellent guidance and suggestion of Dr. D. B. Associate Professor of Electrical Engineering. Ι my sincere appreciation to Dr. V. G. Ellerbruch, Professor and Head of Department of Electrical Engineering, for his valuable review and encouragement. I must also thank Mostad, Electrical Technician, Department Electrical Engineering, for his technical assistance. thankful to Mrs. Mary Lou Michalewicz, Secretary to Department of Electrical Engineering, for her skillfull and excellent typing of the manuscript.

Manja

# TABLE OF CONTENTS

| Chapte | er   | I                                                                           | Page |

|--------|------|-----------------------------------------------------------------------------|------|

| I      | INTI | RODUCTION                                                                   | 1    |

| II     | THE  | 8088 MICROPROCESSOR                                                         | 6    |

|        | Α.   | <pre>Internal Architecture of the 8088</pre>                                | 11   |

|        |      | 1. 8088 Registers                                                           | 11   |

|        |      | 2. Execution Unit and Bus Interface Unit                                    | 16   |

| III    | THE  | 8087 MATH COPROCESSOR                                                       | 17   |

|        | Α.   | Math Coprocessor Pin Description                                            | 19   |

|        | В.   | Internal Architecture of the 8087 Math                                      |      |

|        |      | <u>Coprocessor</u>                                                          | 22   |

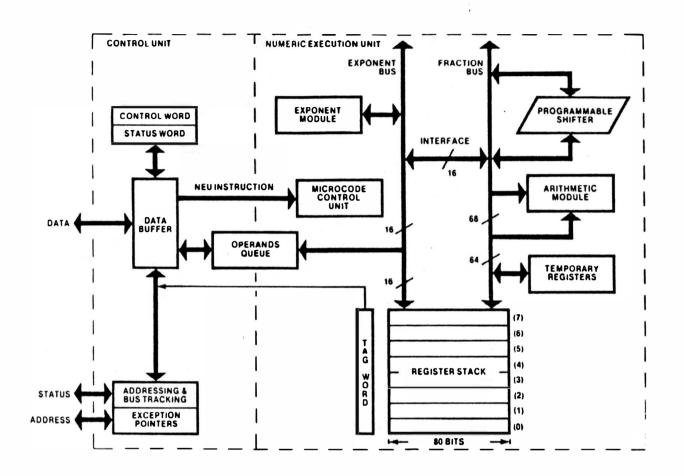

|        |      | 1. Control Unit                                                             | 22   |

|        |      | 2. Numeric Execution Unit                                                   | 24   |

|        |      | 3. Status Word and Control Word Registers                                   | 25   |

|        | С.   | Number System and Data Types                                                | 29   |

|        | D.   | <u>Instruction</u> <u>Decoding</u> <u>and</u> <u>Instruction</u> <u>Set</u> | 32   |

| IV     | SYS  | TEM CLOCK AND BUS CYCLES                                                    | 37   |

|        | Α.   | 8284 Clock Generator/Driver                                                 | 37   |

|        | В.   | T-Clock States                                                              | 41   |

|        | С.   | <u>Status Lines</u>                                                         | 42   |

|        | D.   | Read, Write and Instruction Fetch Cycles                                    | 45   |

|        | Ε.   | Ready and Queue Status Lines                                                | 48   |

| V    | VEC | TOR CONTROLLER                             | 53  |

|------|-----|--------------------------------------------|-----|

|      | Α.  | The Scalar Mode                            | 55  |

|      | В.  | The Vector Mode                            | 56  |

|      |     | 1. Serial Mode                             | 56  |

|      |     | 2. Parallel Mode                           | 57  |

|      | C.  | <u>Vector</u> <u>Instructions</u>          | 58  |

| VI   | VEC | TOR INSTRUCTIONS DECODER                   | 61  |

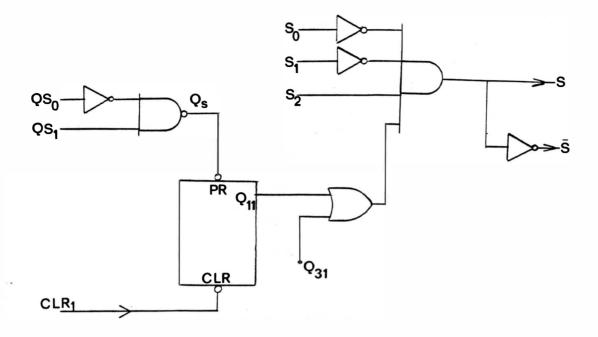

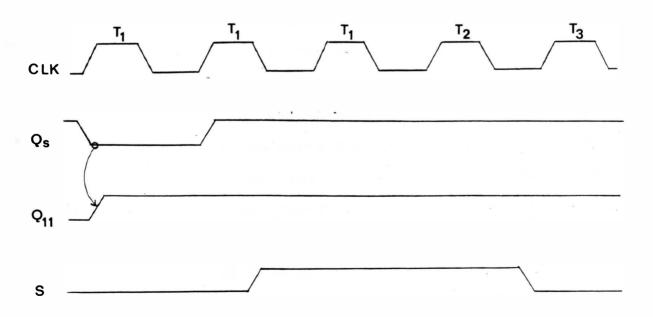

|      | Α.  | <u>Instruction Fetch Bus Cycle Monitor</u> | 63  |

|      | В.  | <pre>Data Enable Generator</pre>           | 66  |

|      | С.  | Data Line Monitor for "DF"                 | 70  |

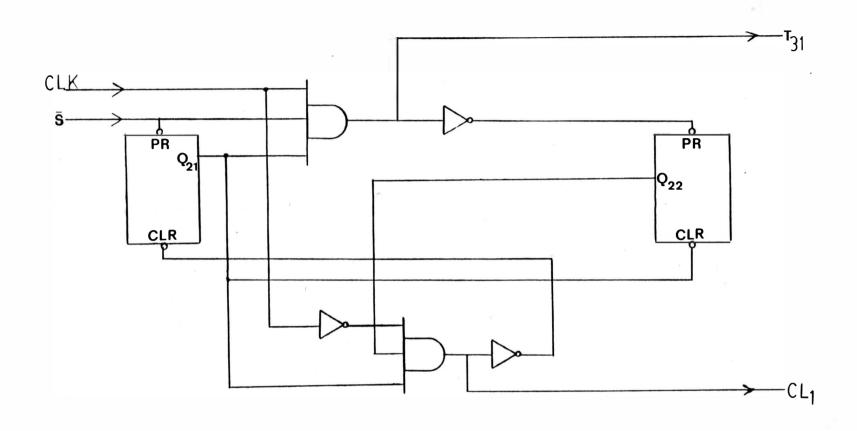

|      | D.  | Clearing and Control                       | 73  |

|      | Ε.  | Subsequent Byte Decoder                    | 76  |

| VII  | SEQ | UENTIAL LOAD/STORE CONTROL                 | 80  |

|      | A . | <pre>Main Controller</pre>                 | 84  |

|      |     | 1. The Control Block                       | 84  |

|      |     | 2. T22 Clock Generator                     | 85  |

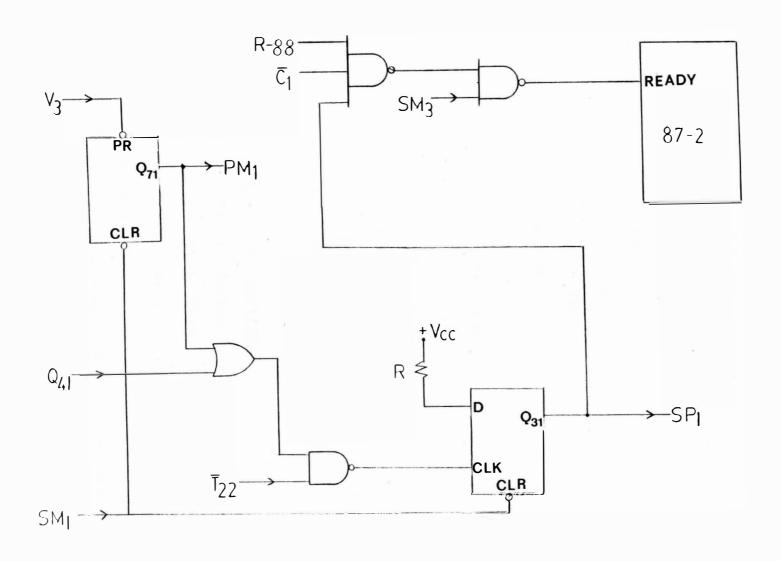

|      | В.  | <u>87-1</u> <u>Ready Control</u>           | 90  |

|      | С.  | 87-1 Queue Status Control                  | 92  |

|      | D.  | <u>87-2</u> <u>Ready</u> <u>Control</u>    | 94  |

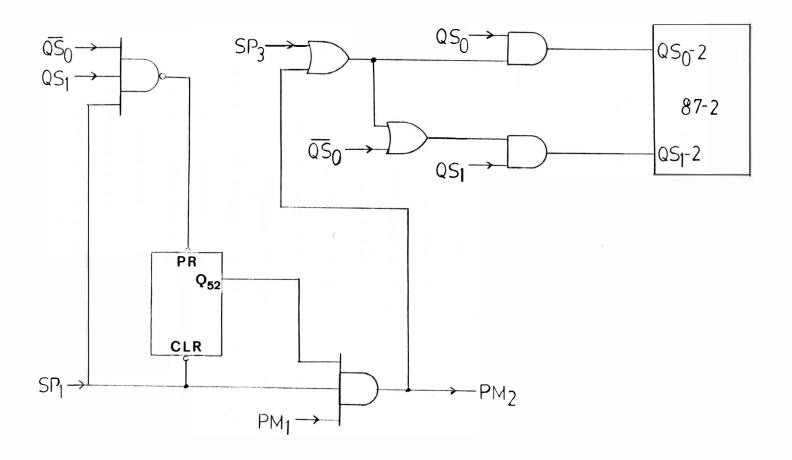

|      | Ε.  | 87-2 Queue Status Control                  | 97  |

| VIII | PAR | ALLEL EXECUTION CONTROL                    | 102 |

|      | A . | Parallel Ready Control                     | 103 |

|      | В.  | Parallel Queue Status Control              | 106 |

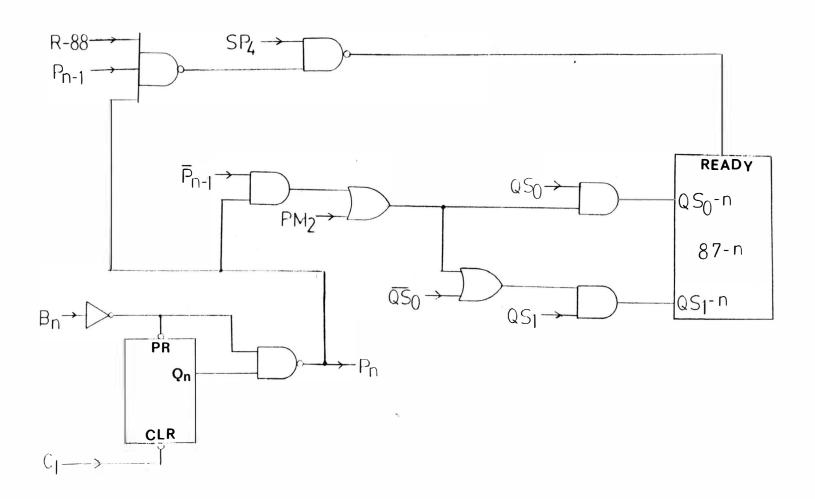

|      | С.  | A Generalized Control Circuit              | 110 |

|      |     | 1. Serial Mode Operation                   | 110 |

|      |     | 2. Parallel Mode Operation                 | 113 |

| IX     | ASS  | SEMBLY | LANGUA | GE P    | ROGRAM      | FORMAT      | FOR     | THE     | VECTOR                                  |     |

|--------|------|--------|--------|---------|-------------|-------------|---------|---------|-----------------------------------------|-----|

|        | PRO  | CESSO  | R      | • • • • | • • • • •   | • • • • • • | • • • • |         | • • • • • • • • •                       | 114 |

| X      | CON  | CLUSI  | ON     | • • • • | • • • • • • |             | • • • • | • • • • | • • • • • • • • • • • • • • • • • • • • | 123 |

| APPENI | XIC  | A      |        | • • • • | • • • • •   | • • • • • • | • • • • |         | • • • • • • • • • • • • • • • • • • • • | 127 |

| APPENI | XIC  | В      |        | • • • • | • • • • • • |             | • • • • | • • • • | •••••                                   | 128 |

| REFERE | ENCE | ES     |        |         |             |             |         |         |                                         | 133 |

.

## LIST OF FIGURES

| FIGURE | I                                         | PAGE |

|--------|-------------------------------------------|------|

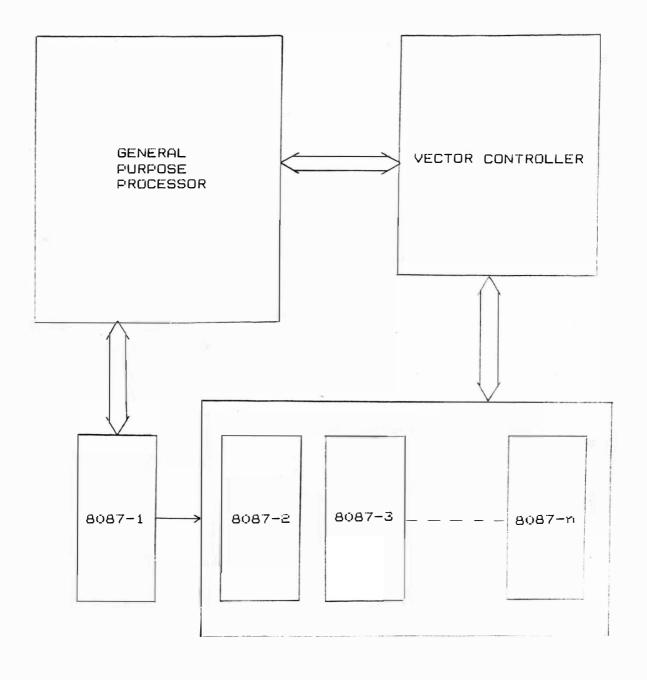

| 1.1    | The Vector Processor Block Diagram        | 2    |

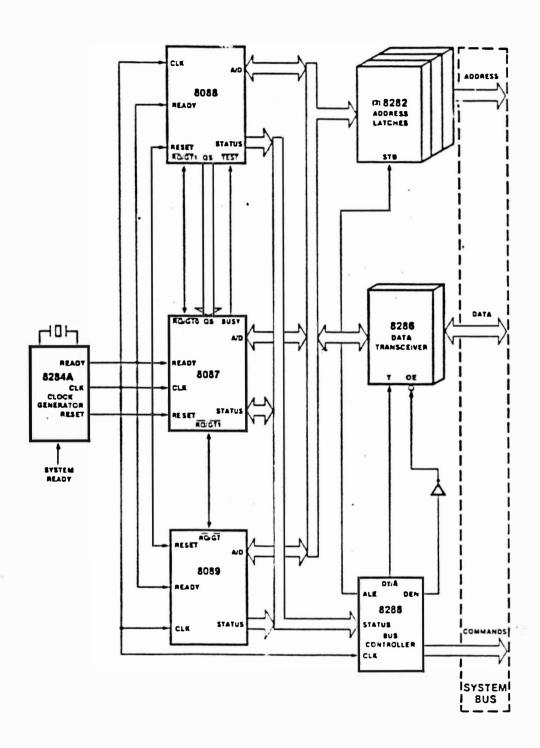

| 1.2    | General System Configuration              | 3    |

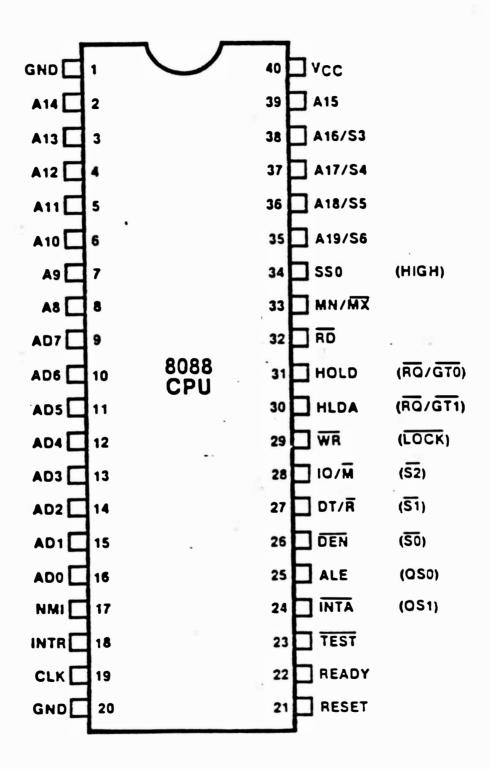

| 2.1    | 8088 CPU Pin Diagram                      | 7    |

| 2.2    | System Mode Signals                       | 9    |

| 2.3    | Bus Status Codes and Commoand Signals     | 10   |

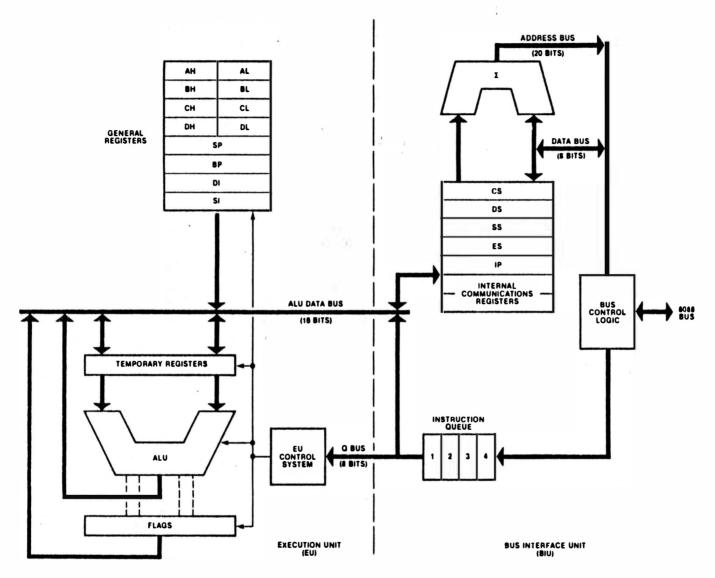

| 2.4    | 8088 Functional Block Diagram             | 12   |

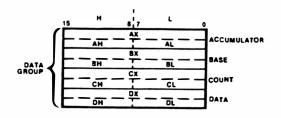

| 2.5    | 8088 Registers                            | 15   |

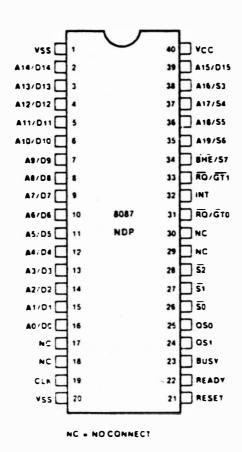

| 3.1    | 8087 Math Coprocessor Pin Diagram         | 18   |

| 3.2    | 8087 Functional Block Diagram             | 23   |

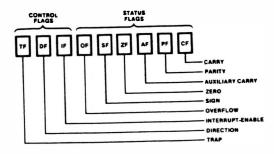

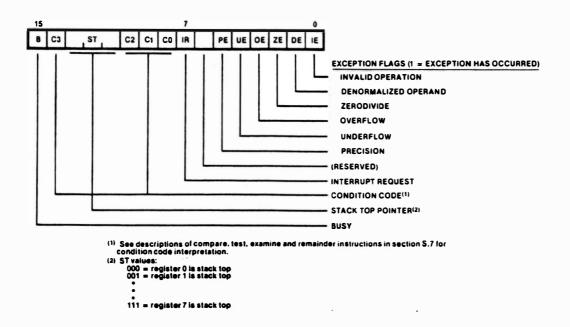

| 3.3    | Status Word Format                        | 26   |

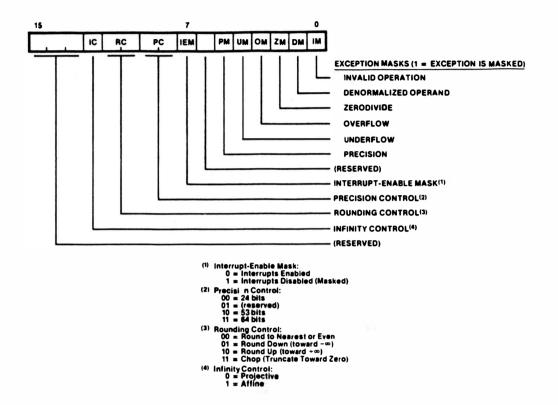

| 3.4    | Control Word Format                       | 28   |

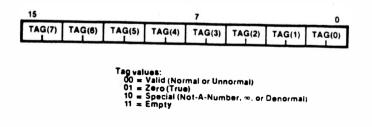

| 3.5    | Tag Word Format                           | 28   |

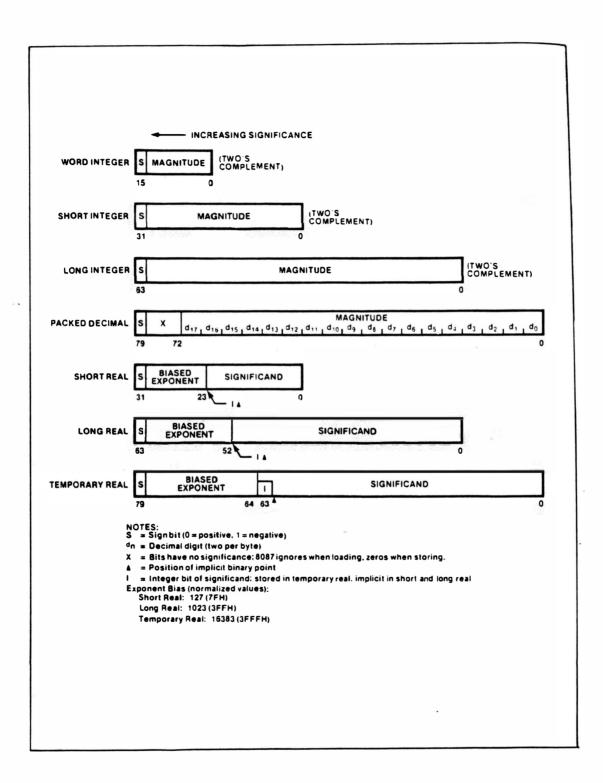

| 3.6    | Data Formats                              | 31   |

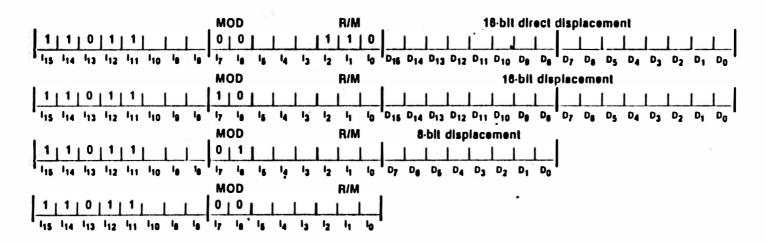

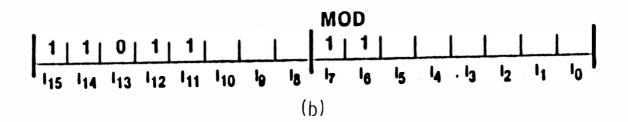

| 3.7    | Escape Instruction Forms                  | 33   |

|        | (a)Non-memory Reference                   | 33   |

|        | (b)Memory Reference                       | 33   |

| 3.8    | 8087 Coprocessor Instructions             | 35   |

|        | (a)Arithmetic Instructions                | 35   |

|        | (b)Constant Instructions                  | 35   |

|        | (c)Processor Control Instructions         | 35   |

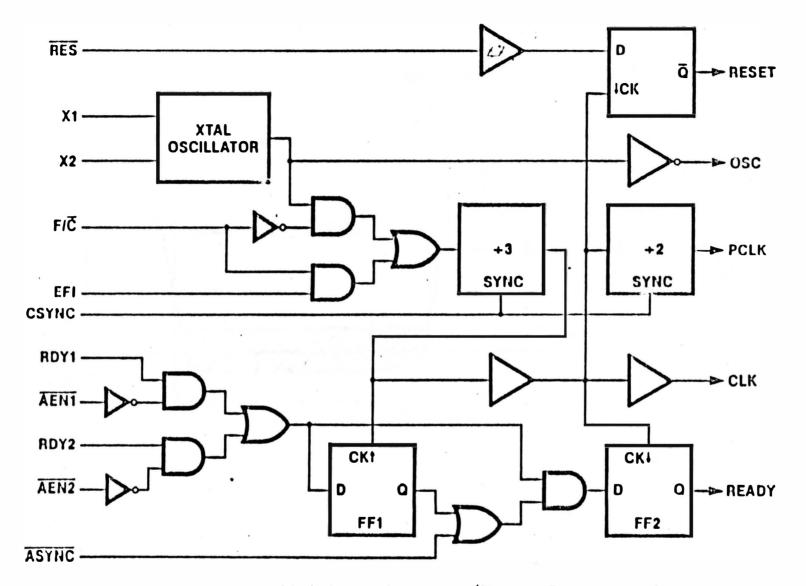

| 4.1    | 8284 Clock Generator/Driver Block Diagram | 38   |

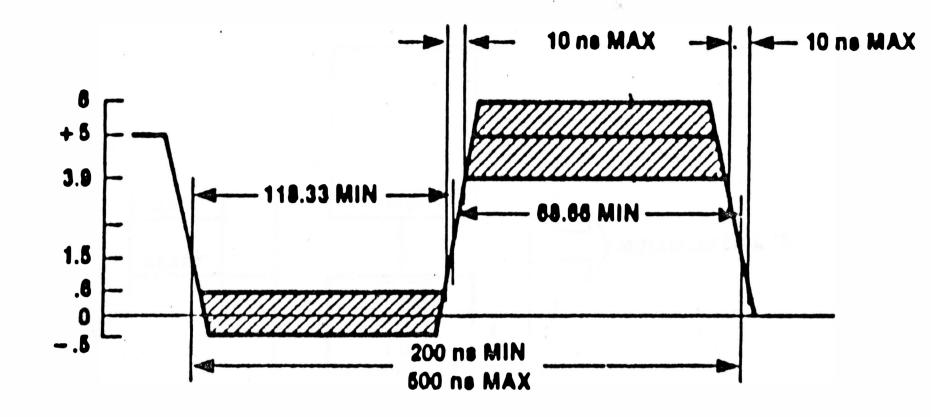

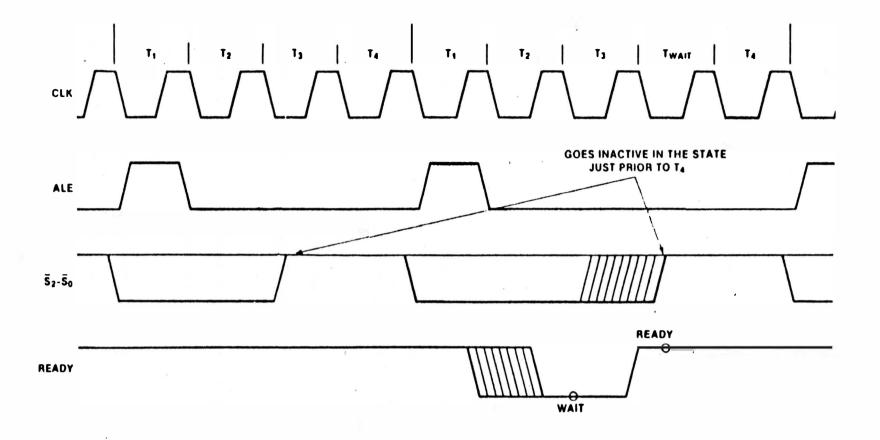

| 4 2    | 2022 Clack Wayafarm                       | 30   |

| 4.3  | 8088 and Coprocessor on the Local Bus Share |            |

|------|---------------------------------------------|------------|

|      | a Common 8284                               | 40         |

| 4.4  | Status Line Activation And Termination      | 42         |

| 4.5  | Status Codes                                | 44         |

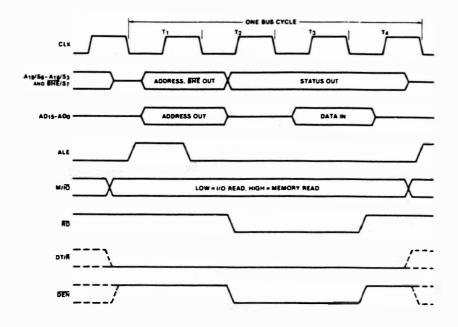

| 4.6  | Memory Read Bus Cycle                       | 47         |

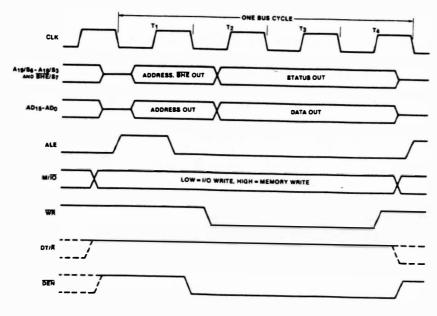

| 4.7  | Memory Write Bus Cycle                      | 47         |

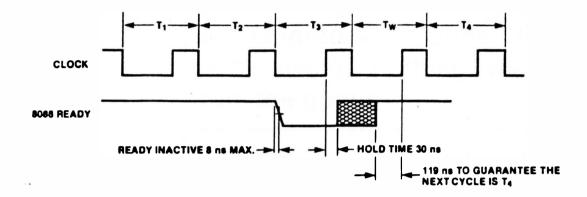

| 4.8  | (a)Normally Ready System                    | 50         |

|      | (b)Normally Not Ready System                | 50         |

| 4.9  | Queue Status Codes                          | 51         |

| 5.1  | Vector Controller                           | 54         |

| 5.2  | Available Escape Instructions               | 59         |

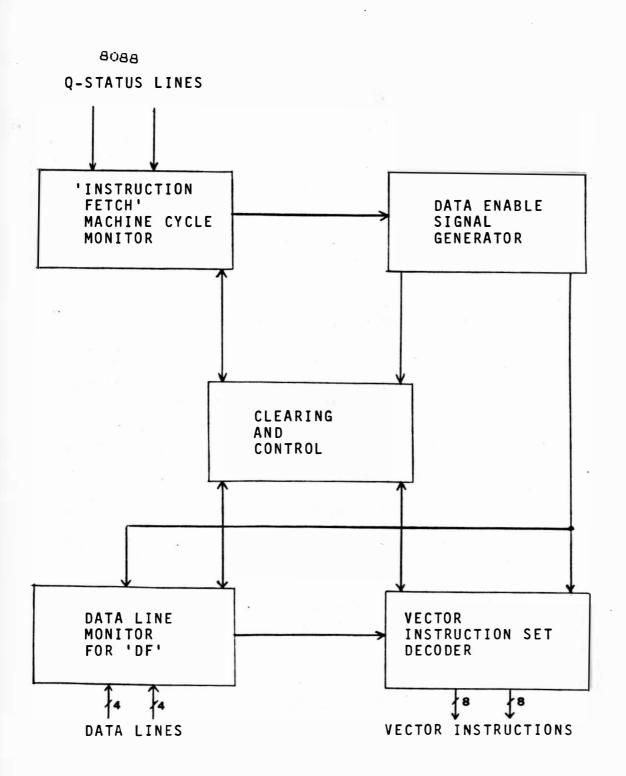

| 6.1  | Vector Instructions Monitor Block Diagram   | 62         |

| 6.2  | Machine Code for Vector Instructions        | 64         |

| 6.3  | Instruction Fetch Bus Cycle Monitor         | 65         |

| 6.4  | Timing Waveforms                            | 65         |

| 6.5  | Data Enable Generator                       | 68         |

| 6.6  | Timing Waveforms of DEG                     | 69         |

| 6.7  | Hexadecimal Code for Vector Instructions    | 71         |

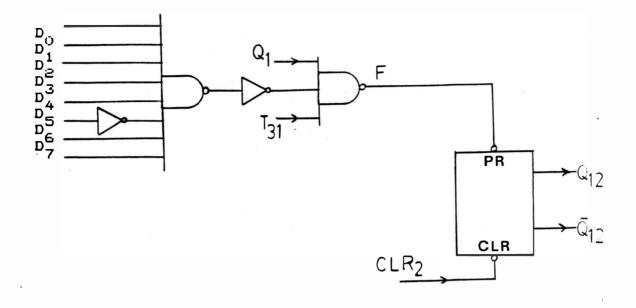

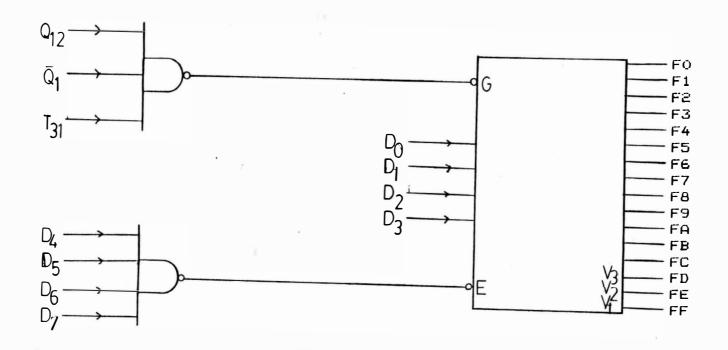

| 6.8  | Data Line Monitor for "DF"                  | 72         |

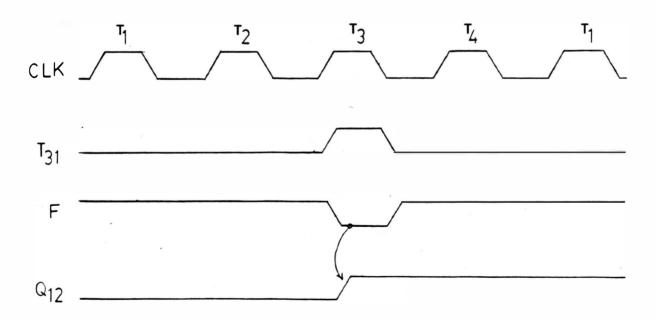

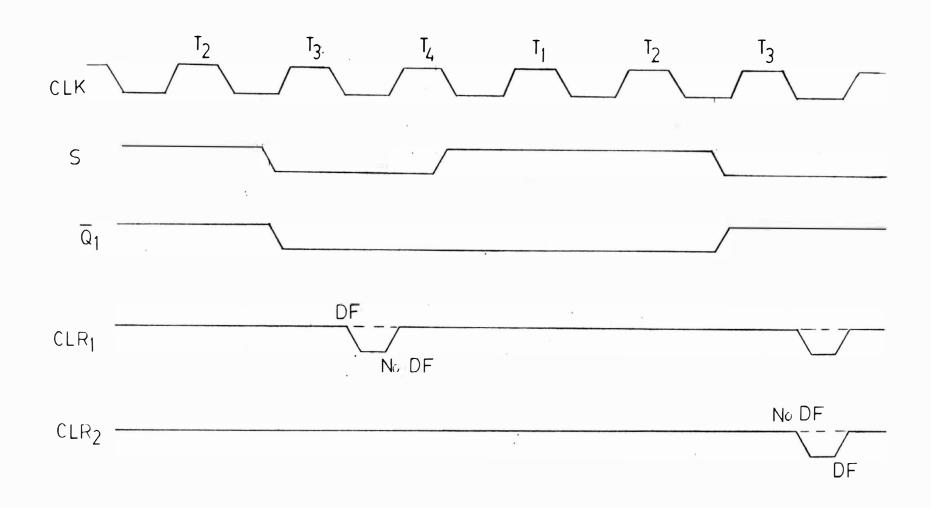

| 6.9  | Timing Waveforms                            | 72         |

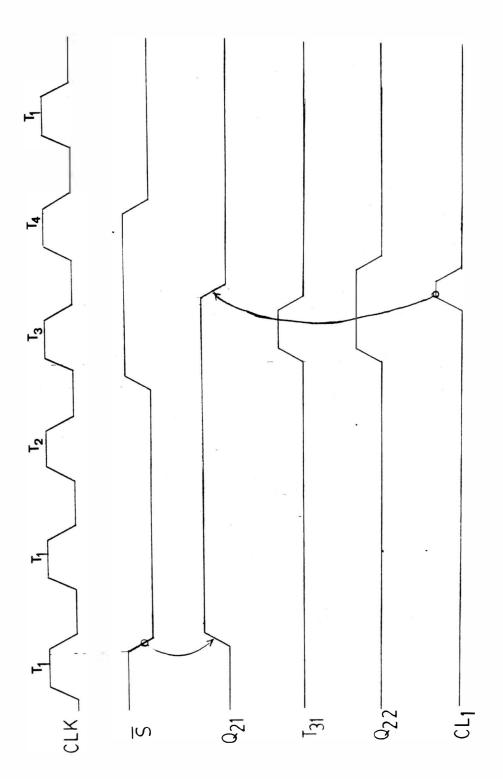

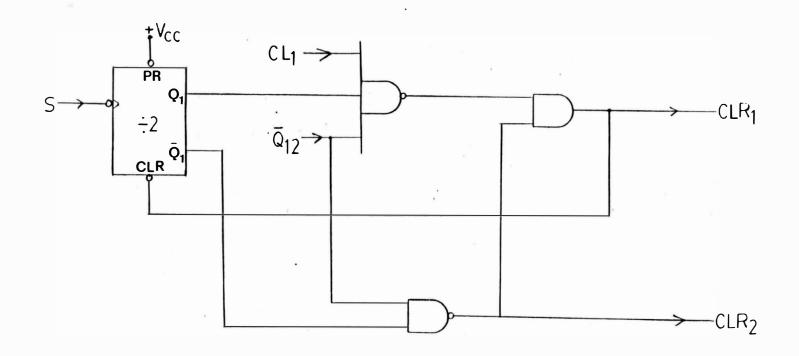

| 6.10 | Clearing and Control Circuit                | 74         |

| 6.11 | Clearing and Control Timing Waveforms       | <b>7</b> 5 |

| 6.12 | Subsequent Byte Decoder                     | 77         |

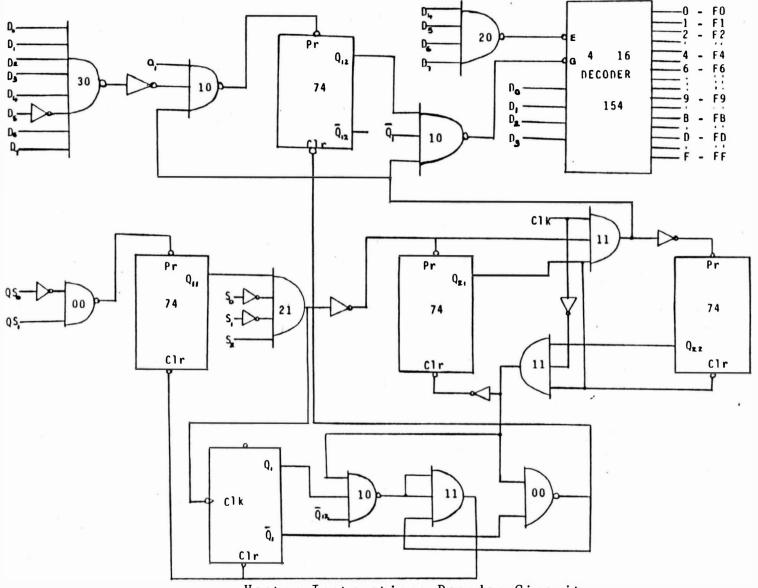

| 6.13 | Vector Instructions Decoder Circuit         | 79         |

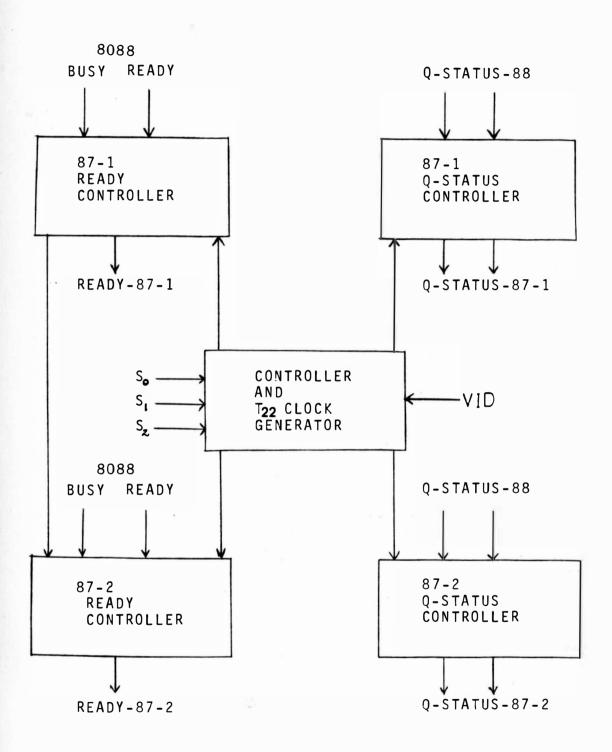

| 7.1  | Sequential LOAD/STORE Control Block Diagram | 81         |

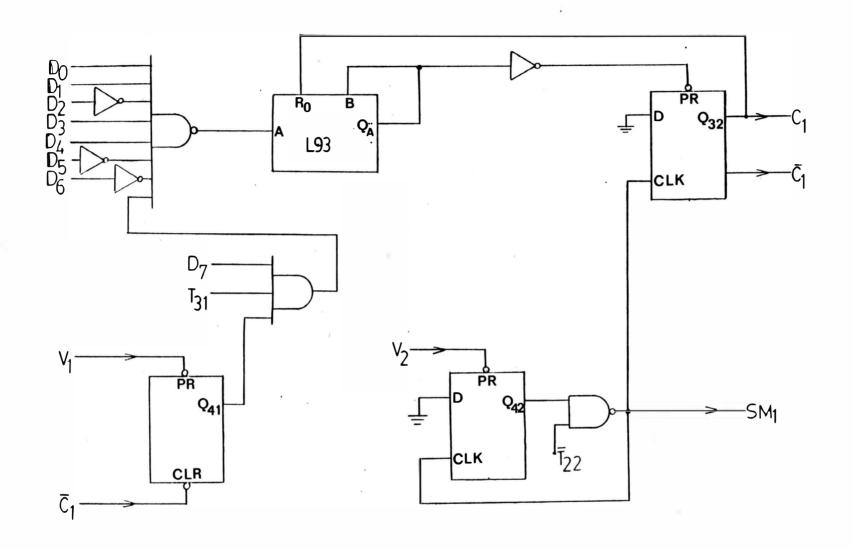

| 7.2  | Circuit of Control Block                   | 86  |

|------|--------------------------------------------|-----|

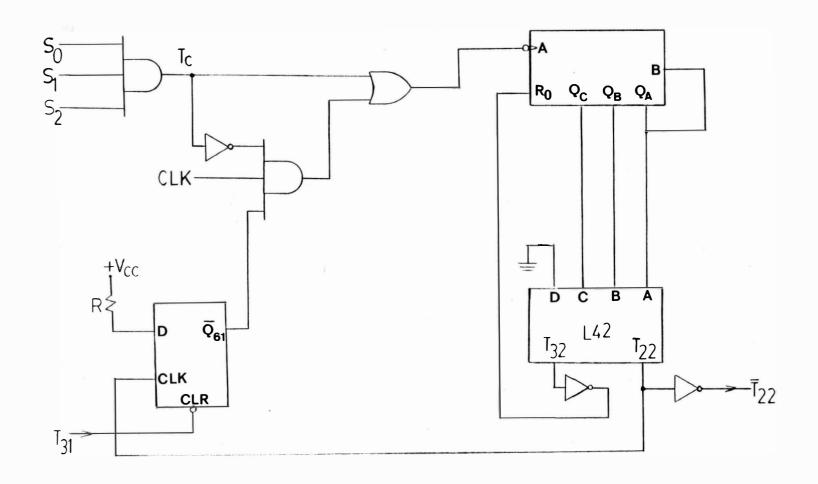

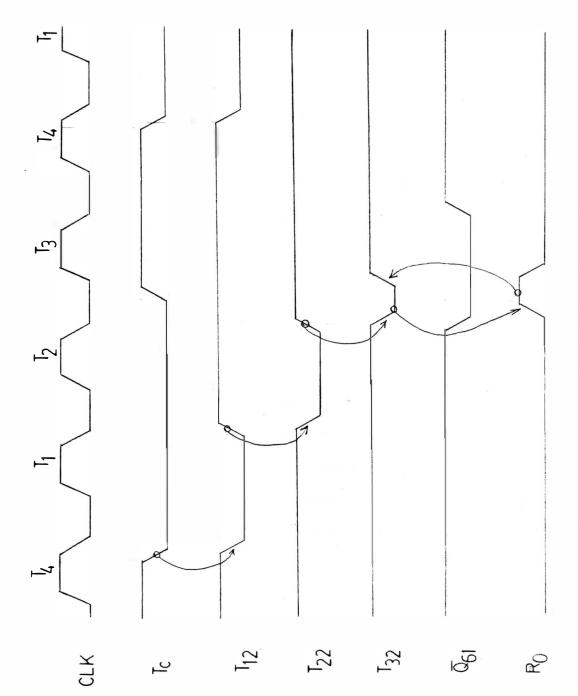

| 7.3  | T22 Clock Generator                        | 88  |

| 7.4  | T22 Clock Generator Waveforms              | 89  |

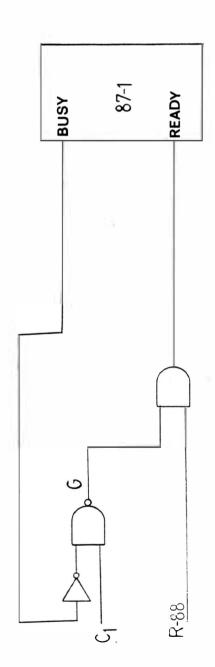

| 7.5  | 87-1 Ready Control                         | 91  |

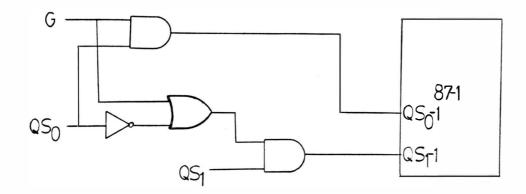

| 7.6  | 87-1 Queue Status Control                  | 93  |

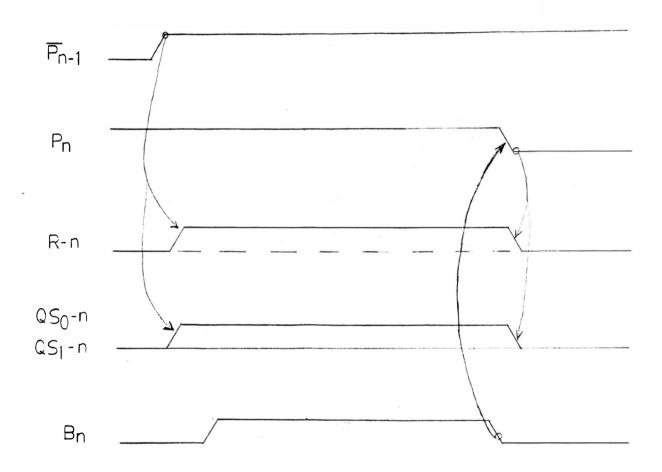

| 7.7  | Timing Waveforms                           | 93  |

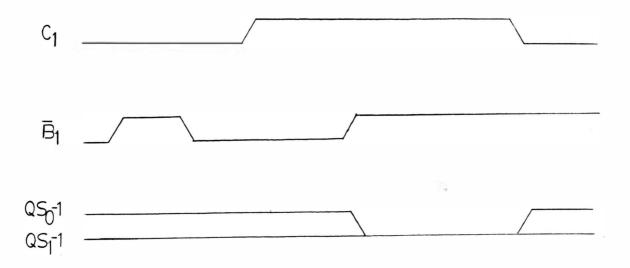

| 7.8  | 87-2 Ready Control                         | 95  |

| 7.9  | 87-2 Ready Control Timings                 | 96  |

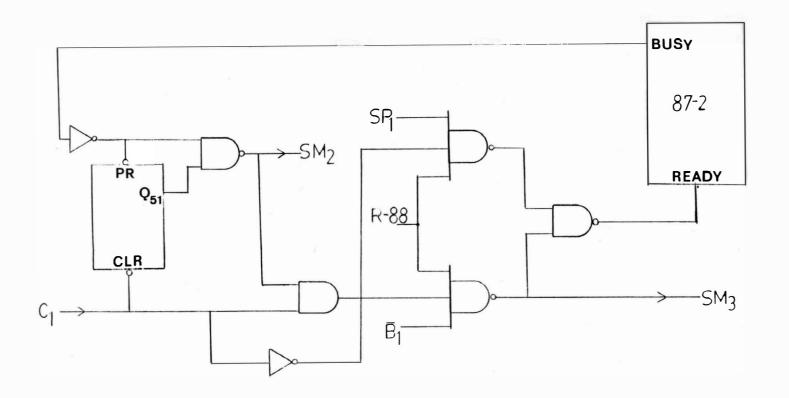

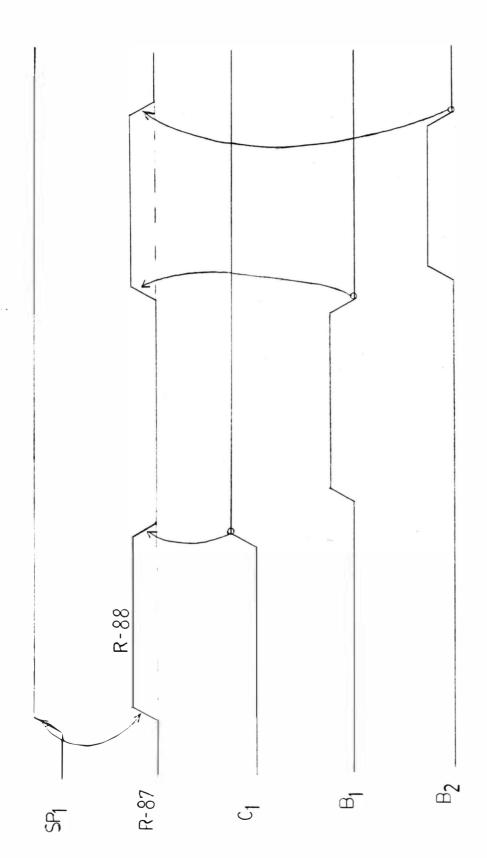

| 7.10 | 87-2 Queue Status Control                  | 99  |

| 7.11 | Timing Waveforms                           | 99  |

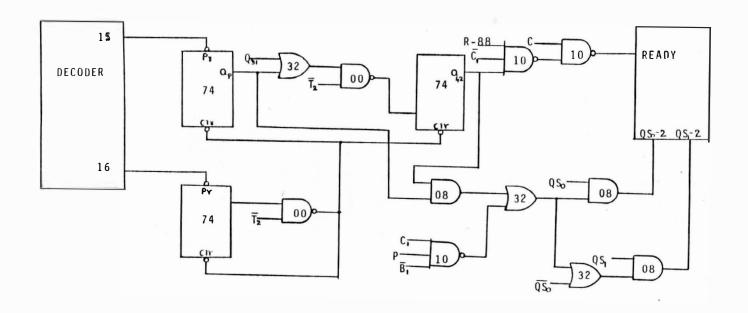

| 7.12 | Sequential LOAD/STORE Control Circuit 1    | .00 |

| 8.1  | Parallel Execution Control Block Diagram 1 | .04 |

| 8.2  | Parallel Ready Control 1                   | 05  |

| 8.3  | Parallel Queue Status Control 1            | .07 |

| 8.4  | Parallel Execution Control Circuit 1       | .09 |

| 8.5  | Generalized Control Circuit 1              | 11  |

| 8.6  | Generalized Control Timing Waveforms 1     | 12  |

| 9.1  | Assembly Language Program                  | 16  |

| 9.2  | Modified Assembly Language Program 1       | 18  |

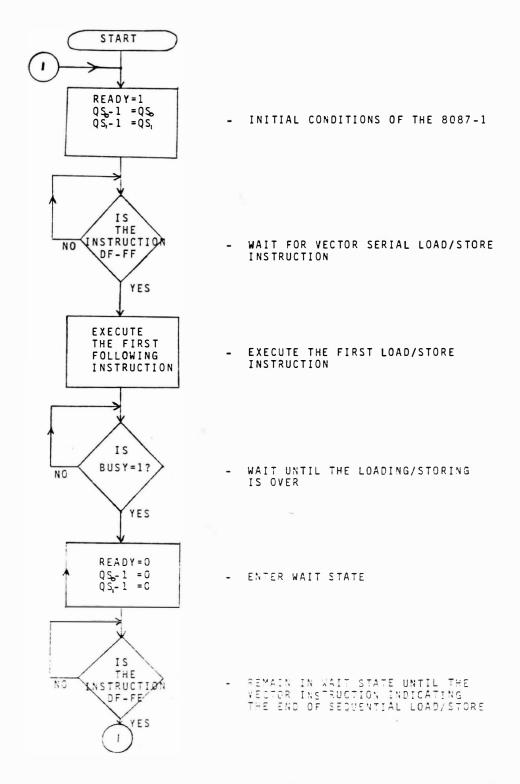

| 9.3  | 87-1 Ready and Queue Status Conditions     |     |

|      | Flow Chart 1                               | 20  |

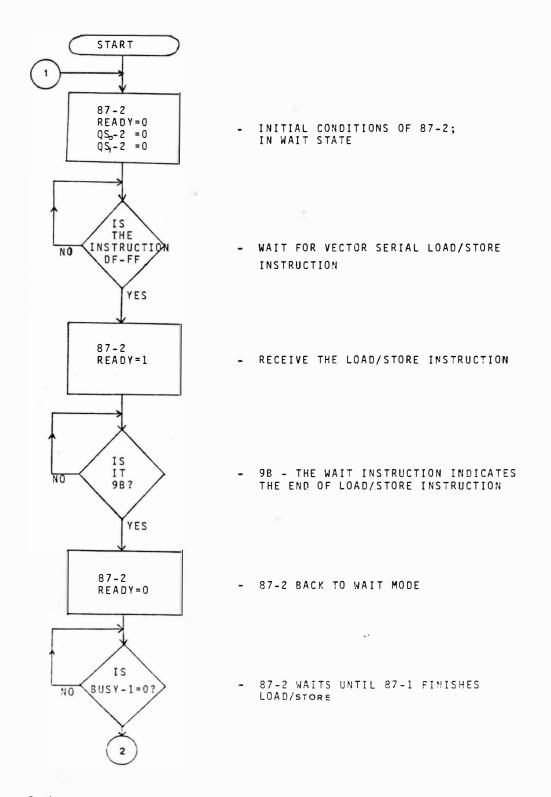

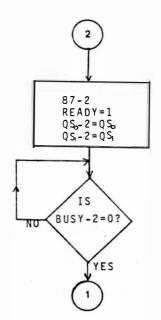

| 9.4  | 87-2 Ready and Queue Status Conditions     |     |

|      | Flow Chart                                 | 21  |

| 10.1 | 8087 Math Coprocessor Speed Comparison     | 25  |

#### CHAPTER I

#### INTRODUCTION

The Vector Processor is a device designed for the purpose of economically achieving maximum speed the computer execution of a group of common scientific and engineering calculations. In these operations, a variable name represents a group of data items which may be thought of as being arranged in a line. This is known as a vector. Each element of the vector, the individual data item, may be a number, a logical value, or a character. A vector's elements must be all of the same type. A vector may have meaning in its own right, or it may be part of an array, a row or a column of elements. Manipulations and operations with vectors have been used by mathematicians, scientists and engineers for centuries in procedures for analysis and design.

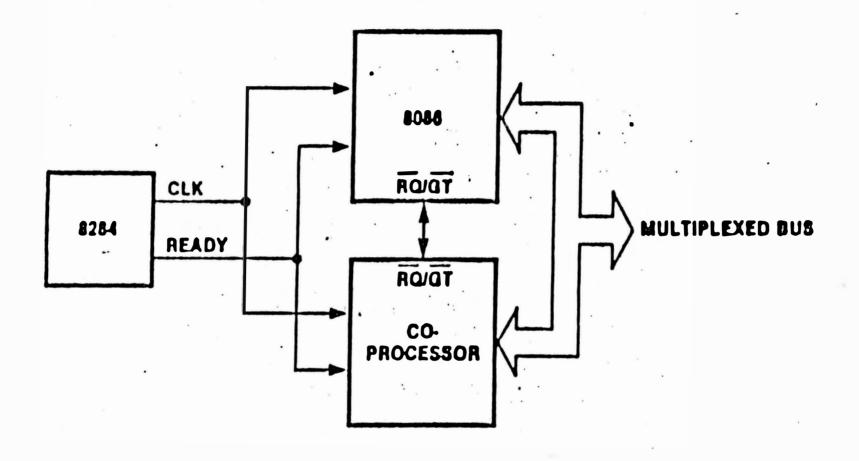

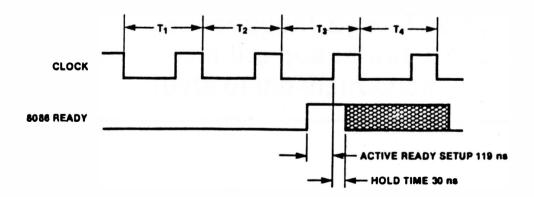

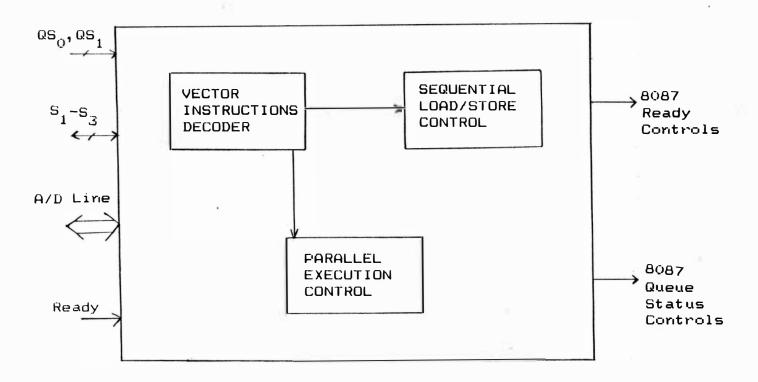

The general arrangement of the major elements of The Vector Processor are shown in Figure 1.1. The IBM PC is choosen as the General Purpose Processor and the Vector Controller is designed to coordinate the activities of a group of components called Math Coprocessors with that of the IBM PC. Figure 1.2 shows the conventional architecture containing the 8088 CPU and the 8087 Math Coprocessor. The

Figure 1.1 The Vector Processor Block Diagram

Figure 1.2 General System Configuration

two processors cooperate by sharing the buses and ignoring each others instructions. The bus sharing is managed by the interface signals.

operations are done in the Math The vector Coprocessors (Figure 1.1), by loading the data elements sequentially into the Math Coprocessors and executing instruction in parallel. The sequential and the parallel operations are controlled by the Vector Controller which recognizes the vector instructions. In the abscence instructions involving vector quantities, the Vector Controller has one of the Math Coprocessors connected the General Purpose Processor as in the conventional architecture of Figure 1.2. This allows for maximum in executing ordinary arithmetic operations.

When a vector instruction appears, it is decoded by the Vector Controller and appropriate action taken. The effect of these actions is to load the elements of the required vectors sequentially from Memory into the Math Coprocessors, do the required operations simultaneously, and then write the results out sequentially to Memory. This simultaneous operation on a number of data elements is the key to the speed of this processor.

The ensuing chapters describe the hardware and software requirements for the design. Understanding of the hardware design requires the knowledge of the architecture

of the 8088 and the 8087 processors. The next chapters, Chapter ΙI and Chapter III, explain the architecture of the 8088 CPU and the 8087 Math Coprocessor, in brief. Chapter IV describes System Clock and Cycles giving an idea about timing requirements of system. Chapter V and the subsequent Chapters explain detail the hardware implementation οf the Controller. Finally the software requirements are described in Chapter IX, with Conclusions in Chapter X.

#### CHAPTER II

#### THE 8088 MICROPROCESSOR

The heart of the IBM PC is its 8/16-bit 8088 microprocessor. A microprocessor is a general purpose processing unit built into a single integrated circuit. The 8088 was the first 8/16 -bit microprocessor introduced by Intel Corporation. The 8088 is enclosed in a 40-pin dual-in-line package as shown in Figure 2.1 and requires a +5V power supply.

The 8088 is called an 8/16-bit processor as it has an 8-bit external data path, whereas, its internal bit is 16-bits wide. The 20-bit wide address bus enables it to address up to one Mega byte of memory. It can also address up to 64K of byte-wide input/output ports. The pins ADO through AD7 serve as time multiplexed address and data bus.

The 8088 has two system modes of operation and can be configured to operate in either of these two modes, viz, the minimum system mode and the maximum system mode. By applying logic 1 or 0 to the MN/MX input lead (pin 33), one of the two required modes can be selected. The minimum mode systems are smaller and contain a single processor, whereas the maximum system mode feature lets the 8088 coordinate the activities of other processors in the system

Figure 2.1 8088 CPU Pin Diagram

like the 8087 Math Coprocessor, the 8089 Input/Output (I/0) processor, etc. Figure 2.2 gives the pin descriptions of the 8088 in both minimum and maximum mode system configuration.

As indicated in Figure 2.2, in the minimum system mode of operation, the 8088 provides all the control signals needed to implement the memory and the I/O interfaces. For the Vector Processor interface, the 8088 must be configured in maximum system mode and hence requires that the input lead (pin 33) be tied low. In this mode the 8088 produces signals for implementing a Coprocessor multiprocessor system environment. This mode also facilitates the passing of bus control to other Coprocessors through the RQ/GT lead. Looking at Fig it is shown that the 8088 does not directly provide all the signals that are required to control the memory, I/O interrupt interfaces. Instead, it generates three status signals SO, S1 and S2 prior to the beginning of each machine cycle or bus cycle. Each 3-bit status code represents the type of bus cycle that is to follow. The Vector Controller and the 8288 bus controller decode status information to identify the type of microprocessor bus cycle. Figure 2.3 shows the decoded status signal also the command signals generated by the 8288 bus controller.

|     |                                                           | Common Signals                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Name                                                      | Function                                                                                                                                                                                                                      | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | AD15-AD0                                                  | Address/Data Bus                                                                                                                                                                                                              | Bidirectional,<br>3-State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | A19/S6-<br>A16/S3                                         | Address/Status                                                                                                                                                                                                                | Output,<br>3-State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | BHE/S7                                                    | Bus High Enable/<br>Status                                                                                                                                                                                                    | Output,<br>3-State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | MN/MX                                                     | Minimum/Maximum<br>Mode Control                                                                                                                                                                                               | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (a) | RD                                                        | Read Control                                                                                                                                                                                                                  | Output,<br>3-State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | TEST                                                      | Wait On Test Control                                                                                                                                                                                                          | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | READY                                                     | Wait State Control                                                                                                                                                                                                            | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | RESET                                                     | System Reset                                                                                                                                                                                                                  | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | NMI                                                       | Non-Maskable<br>Interrupt Request                                                                                                                                                                                             | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | INTR                                                      | Interrupt Request                                                                                                                                                                                                             | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | CLK                                                       | System Clock                                                                                                                                                                                                                  | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | Vcc                                                       | +5V                                                                                                                                                                                                                           | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | GND                                                       | Ground                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | Minimu                                                    | m Mode Signals (MN/                                                                                                                                                                                                           | $MX = V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                           |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | Name                                                      | Function                                                                                                                                                                                                                      | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | Name<br>HOLD                                              | Function Hold Request                                                                                                                                                                                                         | Type<br>Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                                           |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     | HOLD                                                      | Hold Request                                                                                                                                                                                                                  | Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (b) | HOLD<br>HLDA                                              | Hold Request Hold Acknowledge Write Control Memory/IO Control                                                                                                                                                                 | Input<br>Output<br>Output,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (b) | HOLD<br>HLDA<br>WR                                        | Hold Request Hold Acknowledge Write Control                                                                                                                                                                                   | Input Output Output, 3-State Output,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (b) | HOLD<br>HLDA<br>WR<br>M/IO                                | Hold Request Hold Acknowledge Write Control Memory/IO Control Data Transmit/                                                                                                                                                  | Input Output Output, 3-State Output, 3-State Output,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

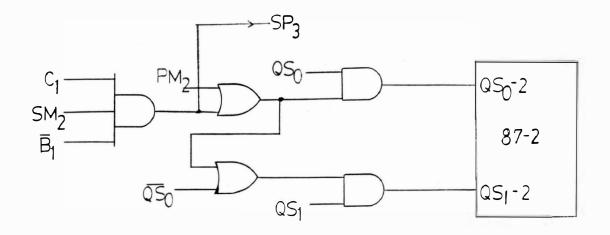

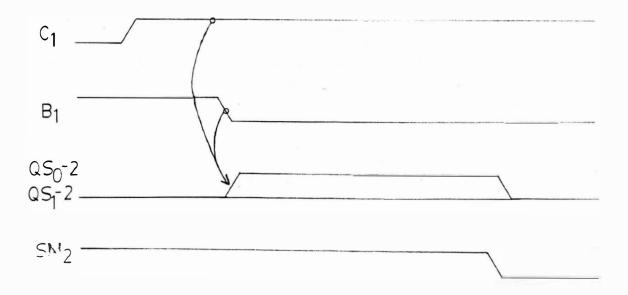

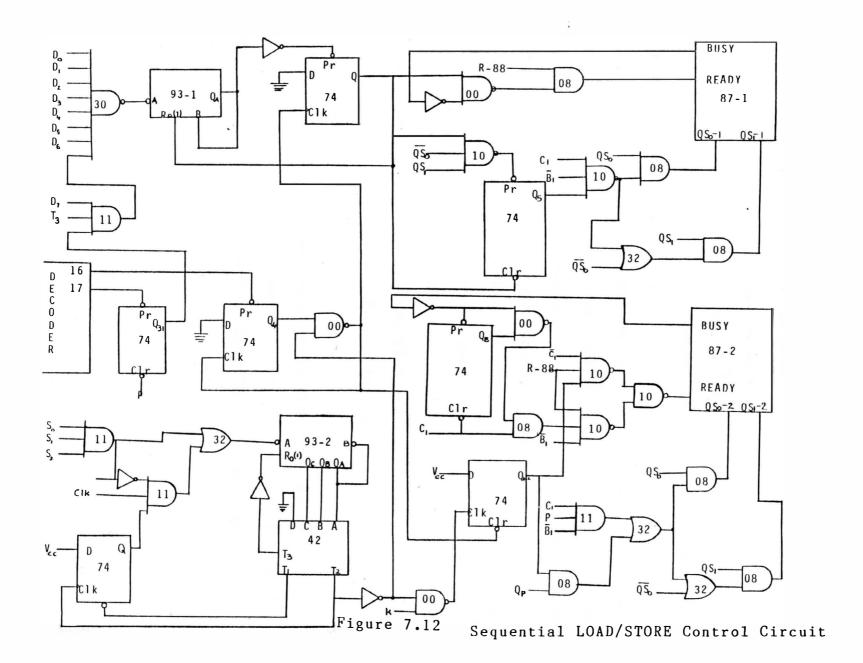

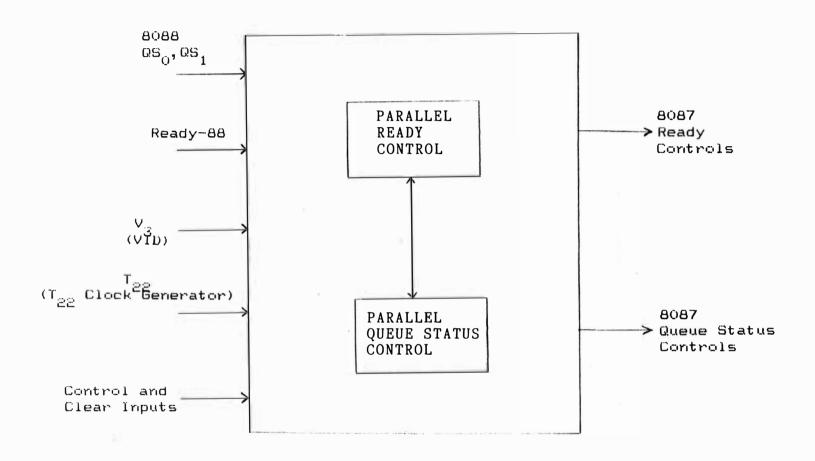

| (b) | HOLD<br>HLDA<br>WR<br>M/IO<br>DT/R<br>DEN<br>ALE          | Hold Request Hold Acknowledge Write Control Memory/IO Control Data Transmit/ Receive                                                                                                                                          | Input Output, 3-State Output, 3-State Output, 3-State Output, 0-tput,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |