# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

| Traçage et profilage | de systèmes | hétérogènes |

|----------------------|-------------|-------------|

|----------------------|-------------|-------------|

# ARNAUD FIORINI

Département de génie informatique et génie logiciel

Mémoire présenté en vue de l'obtention du diplôme de Maîtrise ès sciences appliquées Génie informatique

Août 2020

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Ce mémoire intitulé :

Traçage et profilage de systèmes hétérogènes

# présenté par Arnaud FIORINI

en vue de l'obtention du diplôme de Maîtrise ès sciences appliquées a été dûment accepté par le jury d'examen constitué de :

Gilles PESANT, président

Michel DAGENAIS, membre et directeur de recherche

Guillaume-Alexandre BILODEAU, membre

#### REMERCIEMENTS

Je tiens à exprimer toute ma reconnaissance pour mon directeur de recherche, Michel Dagenais, pour m'avoir donné l'opportunité de participer à ce projet de recherche au sein du laboratoire DORSAL. Son expérience m'a beaucoup guidé dans les différents problèmes rencontrés au cours de ma maitrise.

Je tiens aussi à remercier le soutien financier, technique et matériel des entreprises : Ericsson, Advance Micro Devices (AMD), EfficiOS ainsi que du Conseil de recherches en sciences naturelles et en génie du Canada (CRSNG).

Je remercie spécifiquement Geneviève Bastien, Matthew Khouzam, Guillaume Champagne et Evgeny Shcherbakov pour leurs conseils et leur aide tout au long de mon projet.

Par ailleurs, j'aimerais exprimer ma gratitude à tous mes collègues du laboratoire DORSAL qui m'ont souvent apporté des conseils ou de l'aide.

Enfin, j'aimerais remercier ma famille ainsi que mes amis pour leur soutien constant.

# RÉSUMÉ

Les systèmes hétérogènes sont de plus en plus présents dans tous les ordinateurs. En effet, de nombreuses tâches nécessitent l'utilisation de coprocesseurs spécialisés. Ces coprocesseurs ont permis des gains de performance très importants qui ont mené à des découvertes scientifiques, notamment l'apprentissage profond qui n'est réapparu qu'avec l'arrivée de la programmation multiusage des processeurs graphiques.

Ces coprocesseurs sont de plus en plus complexes. La collaboration et la cohabitation dans un même système de ces puces mènent à des comportements qui ne peuvent pas être prédits avec l'utilisation d'analyse statique. De plus, l'utilisation de systèmes parallèles qui possèdent des milliers de fils d'exécution, et de modèles de programmation spécialisés, rend la compréhension de tels systèmes très difficile. Ces problèmes de compréhension rendent non seulement la programmation plus lente, plus couteuse, mais empêchent aussi le diagnostic de problèmes de performance.

C'est pourquoi il est nécessaire d'avoir recours à des outils d'analyse dynamique qui permettent d'analyser l'état d'un système au cours du temps. Ces outils permettent d'étudier en détail le comportement d'un système après l'exécution de celui-ci. Idéalement, ces outils ont un impact minimal pour s'assurer de la précision des résultats obtenus. Il est aussi nécessaire que les résultats obtenus permettent d'avoir suffisamment d'information pour décrire complètement le système, sinon l'analyse est fortement biaisée.

Il est cependant de plus en plus difficile d'obtenir ces outils, car dans les systèmes hétérogènes de nombreux processeurs fonctionnent ensemble, tout en ayant des architectures, des gestionnaires de périphérique et des modèles de programmation différents. Cette diversité doit être prise en compte dans l'élaboration d'un outil de traçage. L'avènement de l'architecture HSA permet le fonctionnement dans un cadre commun, basé sur un modèle d'exécution générique, de ces différents coprocesseurs.

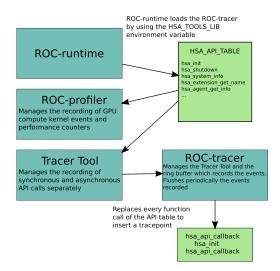

Cette architecture permet donc d'obtenir des outils suffisamment génériques pour s'adapter à la diversité des systèmes hétérogènes. Dans ce mémoire, nous présentons une approche en deux temps. En premier lieu, l'utilisation de ROC-profiler et de ROC-tracer qui permet de recueillir des traces qui peuvent être corrélées avec des moyens de traçage plus traditionnels pour obtenir une vue d'ensemble d'un système. Ensuite nous avons développé une analyse des données de traçage et de profilage. Cette analyse s'effectue en deux étapes, la lecture séquentielle des évènements qui permet de générer un historique des états et ensuite, l'affichage de ces états pour générer plusieurs visualisations. La génération de traces s'effectue

avec les outils ROC-profiler et ROC-tracer qui font partie de ROCm, une implémentation de la spécification HSA. Ensuite une analyse de cette trace et des compteurs de performance a été développée grâce à TraceCompass.

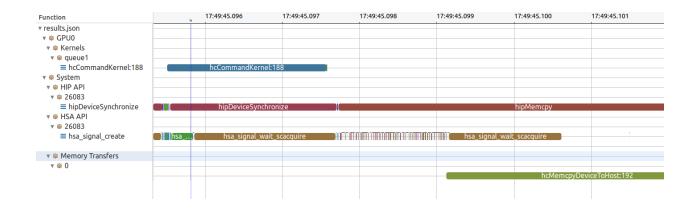

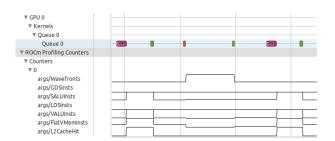

Cette analyse permet de visualiser les appels à l'interface de programmation HIP et HSA effectués par l'utilisateur, les transferts mémoires et les compteurs de performance. Ces informations sont affichées au sein d'une même vue. Cela permet à l'utilisateur de visualiser toutes les données pertinentes, synchronisées au niveau du temps. L'outil utilisé permet de corréler facilement ces données avec les données d'exécution du système d'exploitation, du CPU et d'autres systèmes communs à tous les systèmes hétérogènes. Cette approche est facilement adaptable à n'importe quel système respectant la spécification HSA, ce qui est le cas de nombreux coprocesseurs qui supportent cette spécification.

#### ABSTRACT

Heterogeneous systems are becoming increasingly relevant and important with the emergence of powerful specialized coprocessors. Because of the nature of certain problems, like graphics display, deep learning and physics simulation, these devices have become a necessity. The power derived from their highly parallel or very specialized architecture is essential to meet the demands of these problems. Because these use cases are common on everyday devices like cellphones and computers, highly parallel coprocessors are added to these devices and collaborate with standard CPUs.

The cooperation between these different coprocessors makes the system very difficult to analyze and understand. The highly parallel workload and specialized programming models make programming applications very difficult. Troubleshooting performance issues is even more complex. Since these systems communicate through many layers, the abstractions hide many performance defects.

Therefore, it is becoming essential to use diagnostic toolkits that record performance details. These performance details can be traces or performance counters. They are very useful in order to analyze the state of a system, with respect to time, and its behaviour. However, these tools should minimize the impact on the execution of the studied applications to be effective in finding performance defects. Also, to cover most use cases, it is necessary to have enough data to adapt and produce different kinds of analysis.

It is very difficult to obtain tools that are compatible with most coprocessors and that can be correlated with more traditional tracers and profilers. There are many different programming models and architectures, and most tools are closed source and do not provide access to the relevant information that would allow correlating with other sources. The HSA foundation enables many software improvements that would be generic enough to support different programming models.

In this thesis, we propose a novel approach that uses ROC-profiler, ROC-tracer and Trace-Compass to achieve offline analysis of heterogeneous program executions. The tracing and profiling data collection tools that record runtime information, ROC-tracer and ROC-profiler, are developed mainly by AMD and are open source. Therefore they can be easily modified to correlate their data with other tools. We use these tools to generate a trace and performance counters. Then, we developed an analysis with TraceCompass to process this trace and that produces two new views.

These two views show HIP and HSA API calls, memory transfers and compute kernels, all synchronized with respect to time. This enables the user to have an overview of the program execution on heterogeneous systems. This approach allows the user to simultaneously profile and trace the program, is compatible with different hardware, and would easily adapt to other modern processors that comply with the HSA requirements.

# TABLE DES MATIÈRES

| REME   | RCIEMENTS                                                   | iii  |

|--------|-------------------------------------------------------------|------|

| RÉSUM  | ſÉ                                                          | iv   |

| ABSTR  | ACT                                                         | vi   |

| TABLE  | DES MATIÈRES                                                | riii |

| LISTE  | DES TABLEAUX                                                | xi   |

| LISTE  | DES FIGURES                                                 | xii  |

| LISTE  | DES SIGLES ET ABRÉVIATIONS                                  | iii  |

| LISTE  | DES ANNEXES                                                 | iv   |

| CHAPI' | TRE 1 INTRODUCTION                                          | 1    |

| 1.1    | Définitions et concepts de base                             | 1    |

|        | 1.1.1 Système parallèle                                     | 1    |

|        | 1.1.2 Système hétérogène                                    | 2    |

|        | 1.1.3 Traçage logiciel                                      | 2    |

|        | 1.1.4 Analyse de trace                                      | 3    |

| 1.2    | Éléments de la problématique                                | 3    |

| 1.3    | Objectifs de recherche                                      | 4    |

| 1.4    | Plan du mémoire                                             | 5    |

| CHAPI' | TRE 2 REVUE CRITIQUE DE LA LITTÉRATURE                      | 6    |

| 2.1    | Calcul sur systèmes hétérogènes                             | 6    |

|        | 2.1.1 Mémoire partagée / Communication interprocesseurs     | 6    |

|        | 2.1.2 Ordonnancement des calculs et répartition des charges | 11   |

|        | 2.1.3 Gestion de la mémoire tampon                          | 16   |

| 2.2    | Traçage, profilage et débogage de systèmes hétérogènes      | 20   |

|        | 2.2.1 Traçage et analyse                                    | 20   |

|        | 2.2.2 Profilage sur processeurs distants                    | 26   |

|        | 2.2.3 Débogage sur processeurs distants                     | 32   |

| 2.3    | Conclusion de la revue de littérature                       | 35   |

| CHAPI     | TRE 3 MÉTHODOLOGIE                                  |

|-----------|-----------------------------------------------------|

| 3.1       | Environnement de travail                            |

|           | 3.1.1 ROCm                                          |

|           | 3.1.2 ROC-profiler                                  |

|           | 3.1.3 ROC-tracer                                    |

|           | 3.1.4 Trace Compass                                 |

| 3.2       | Travail réalisé                                     |

|           | 3.2.1 Analyse des informations de trace             |

|           | 3.2.2 Analyse des informations de profilage         |

|           | 3.2.3 Récupération de métadonnées                   |

|           | 3.2.4 Compatibilité avec Theia Compass              |

| 3.3       | Environnement de test                               |

| ~         |                                                     |

| CHAPI     |                                                     |

|           | J-GPU PROGRAMS                                      |

| 4.1       | Introduction                                        |

| 4.2       | Related Work                                        |

|           | 4.2.1 TAU                                           |

|           | 4.2.2 Vampir                                        |

|           | 4.2.3 CodeXL                                        |

|           | 4.2.4 Nvidia Nsight                                 |

|           | 4.2.5 LTTng-HSA                                     |

| 4.3       | Methodology                                         |

|           | 4.3.1 Tracing                                       |

|           | 4.3.2 Performance Counters                          |

|           | 4.3.3 Visualisation                                 |

| 4.4       | Results                                             |

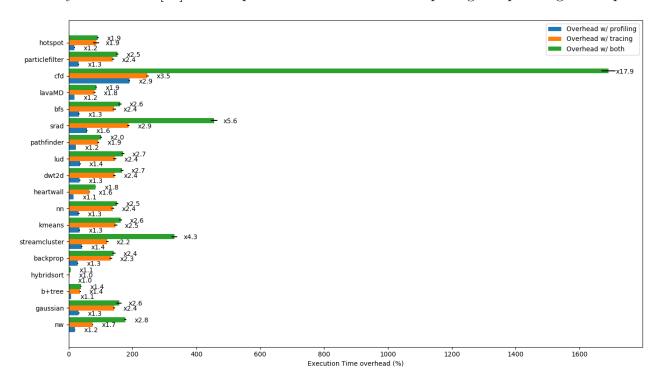

|           | 4.4.1 Overhead Analysis                             |

|           | 4.4.2 Use case analysis                             |

| 4.5       | Conclusion                                          |

| 4.6       | Acknowledgements                                    |

| CHAPI     | TRE 5 DISCUSSION GÉNÉRALE                           |

| 5.1       | Retour sur les résultats obtenus                    |

| 0.1       | 5.1.1 Évaluation du surcout de la solution proposée |

| 5.2       | Adaptabilité de la solution                         |

| 5.2 $5.3$ | •                                                   |

| 0.5       | Comparaison avec d'autres approches                 |

|       | 5.3.1  | CodeXL et LT Ing-HSA               | 59 |

|-------|--------|------------------------------------|----|

|       | 5.3.2  | Nsight et systèmes basés sur CUPTI | 60 |

|       | 5.3.3  | TAU                                | 60 |

| СНАРІ | TRE 6  | CONCLUSION                         | 61 |

| 6.1   | Synthè | èse des travaux                    | 61 |

| 6.2   | Limita | ations de la solution proposée     | 62 |

| 6.3   | Amélio | orations futures                   | 62 |

| RÉFÉR | RENCES | 5                                  | 64 |

| ANNEX | KES    |                                    | 80 |

# LISTE DES TABLEAUX

| Tableau 4.1 | Events and data accessible through ROC-profiler and ROC-tracer     | 50 |

|-------------|--------------------------------------------------------------------|----|

| Tableau 4.2 | Experimental results for Needleman Wunsch                          | 57 |

| Tableau A.1 | Temps d'exécution et écarts types des programmes du banc d'essai   |    |

|             | Rodinia                                                            | 80 |

| Tableau A.2 | Compteurs de performance moyens par kernel du banc d'essai Rodinia | 81 |

# LISTE DES FIGURES

| Figure 2.1 | Hiérarchie de mémoire pour un GPU                                     | Ĝ  |

|------------|-----------------------------------------------------------------------|----|

| Figure 2.2 | Relation des librairies dans l'environnement ROC<br>m ©2020, AMD. Re- |    |

|            | produit avec permission                                               | 11 |

| Figure 2.3 | Architecture d'une unité de calcul GCN [1] sur un GPU ©2012, AMD.     |    |

|            | Reproduit avec permission                                             | 13 |

| Figure 2.4 | Modèle roofline                                                       | 28 |

| Figure 4.1 | ROC-profiler tracepoint insertion mechanism                           | 49 |

| Figure 4.2 | ROCm Plugin System View in Trace Compass                              | 52 |

| Figure 4.3 | ROCm Performance counter view View in Trace Compass                   | 52 |

| Figure 4.4 | Overhead results from the Rodinia benchmark (%) $\dots \dots$         | 53 |

| Figure 4.5 | Correlation between overhead and performance metrics                  | 54 |

| Figure 4.6 | Trace Compass comparison between tracing only and tracing with pro-   |    |

|            | filing enabled                                                        | 56 |

|            |                                                                       |    |

# LISTE DES SIGLES ET ABRÉVIATIONS

GPU Graphic Processing Unit

UCT Unité Centrale de Traitement

FPGA Field Programmable Gate-Array

AMD Advanced Micro Devices

CUDA Compute Unified Device Architecture

ROCm Radeon Open Compute platforM

HIP Heterogeneous-Computing Interface for Portability

GDB GNU Debugger

DSP Digital Signal Processor

OTF Open Tracing Format

CTF Common Trace Format

VTF Vampir Trace Format

API Application Protocol Interface

TAU Tuning and Analysis Utilities

CUPTI CUDA Profiling Tools Interface

PAPI Performance API

PTX Parallel Thread Execution

LTTng Linux Trace Toolkit next generation

HSA Heterogeneous System Architecture

LRU Least Recently Used

PLRU Pseudo LRU

MRU Most Recently Used

GCN Graphics Core Next

TLP Thread Level Parallelism

SIMD Single Instruction Multiple Data

HPC High Performance Computing

PCIe Peripheral Component Interconnect express

DMA Direct Memory Access

# LISTE DES ANNEXES

| Annexe A | Résultats du banc d'essai Rodinia                  | 80 |

|----------|----------------------------------------------------|----|

| Annexe B | Instructions pour exécuter le banc d'essai Rodinia | 82 |

#### CHAPITRE 1 INTRODUCTION

Les systèmes hétérogènes sont de plus en plus présents pour répondre aux besoins des utilisateurs. En effet, de nombreuses tâches nécessitent des processeurs spécialisés pour être exécutées avec la rapidité voulue. Ces tâches ayant des demandes particulières en termes de performance, il est important d'avoir les outils nécessaires pour atteindre ces objectifs.

Les analyses statiques sont limitées et ne peuvent pas aider beaucoup pour l'analyse de performance d'applications complexes. Il est donc nécessaire d'avoir recours à des techniques d'analyse dynamique comme le traçage et le profilage. Ces techniques sont difficiles à appliquer dans des systèmes de calcul à haute performance, car le surcout est proportionnel au nombre d'évènements. Afin de ne pas modifier le comportement des applications étudiées, on cherche à minimiser le surcout des outils qui collectent les données de performance. Ceci impose des contraintes importantes pour développer des outils d'analyse de performance efficaces. De plus, les systèmes hétérogènes présentent de nombreuses architectures différentes qui collaborent au sein d'un même programme. Cette collaboration nécessite l'utilisation d'une multitude d'outils pour pouvoir enregistrer les données propres à chaque architecture. Ces outils doivent pouvoir être modifiés pour corréler les données entre elles, et les outils doivent avoir un surcout faible.

Développer de tels outils est difficile, et une grande partie des mécanismes internes pourrait être réutilisée sur d'autres architectures. Avec l'avènement d'architectures hétérogènes qui possèdent de nombreux coprocesseurs, la demande pour des outils génériques qui fonctionnent avec plusieurs types d'architecture est forte. De plus, des outils génériques permettront de corréler les données de différentes sources. C'est pourquoi nous nous intéressons à ce problème dans le présent travail de recherche.

#### 1.1 Définitions et concepts de base

Dans cette section, nous allons définir quelques concepts qui sont importants pour la bonne compréhension de la suite du mémoire.

### 1.1.1 Système parallèle

Un système parallèle est un système qui exécute plusieurs calculs simultanément sur plusieurs processeurs. Ces calculs sont divisés en instructions et ces instructions sont exécutées simultanément. Il est à différencier du système réparti qui comporte plusieurs ordinateurs qui

communiquent entre en eux à travers une interface réseau. Dans un système réparti, plusieurs ordinateurs se synchronisent sur un temps commun et utilisent une mémoire distincte.

Le processeur central (CPU) est aujourd'hui capable d'effectuer des calculs parallèles. Cependant, on aura souvent recours à des processeurs spécialisés dans le calcul parallèle comme les processeurs graphiques (GPU), les processeurs de signaux numériques (DSP) ou les circuits logiques programmables (FPGA). Ces processeurs spécialisés sont beaucoup plus efficaces pour les tâches nécessitant de nombreux calculs qui sont souvent sur des données ayant plusieurs dimensions, ce qui nécessite un nombre élevé de fils d'exécution.

# 1.1.2 Système hétérogène

Un système hétérogène est un système composé d'un processeur central et de plusieurs coprocesseurs qui généralement partagent une même mémoire. Ces coprocesseurs sont souvent spécialisés dans certaines tâches et permettent au processeur central de répartir les tâches pour une exécution plus efficace. Aujourd'hui, la mémoire partagée est virtuelle, car souvent les coprocesseurs possèdent leur propre mémoire et doivent maintenir une synchronisation avec la mémoire principale.

Nous avons vu précédemment que les GPU, DSP et FPGA étaient plus appropriés pour traiter des tâches nécessitant du calcul parallèle. C'est pourquoi ces coprocesseurs sont souvent utilisés en supplément du CPU pour des raisons de performance.

# 1.1.3 Traçage logiciel

Le traçage logiciel est l'enregistrement d'une suite d'évènements d'un programme ou d'un système. Ces évènements sont une représentation d'un état ou d'un changement d'état du système et permettent de traquer l'état du système par rapport à une échelle du temps. Ils comportent une étiquette de temps et des informations par rapport à l'état du programme. Une trace est donc une séquence de ces évènements et permet, en analysant cette séquence, de retracer l'évolution du programme dans le temps et de mieux comprendre le comportement de celui-ci.

Le traçage peut avoir lieu à différents niveaux : soit dans le contexte du système d'exploitation ou alors dans le contexte utilisateur. Si des points de trace sont déjà présents dans le système d'exploitation, on dit que le système est instrumenté. Ces points de trace sont des instructions spécifiques permettant d'enregistrer les informations liées à un évènement.

Le traçage peut être statique, c'est-à-dire utiliser les points de trace déjà présents dans le programme, ou dynamique, où l'on insère à l'exécution des points de trace.

# 1.1.4 Analyse de trace

L'analyse de trace est la lecture d'une séquence d'évènements qui permet, grâce à une machine à états ou à un algorithme particulier, de produire soit une visualisation de l'état du programme, soit des statistiques sur l'exécution. Le plus souvent, la production d'un graphique montrant l'exécution de différentes tâches, ou de l'état d'un fil d'exécution par rapport au temps, est effectuée.

# 1.2 Éléments de la problématique

Les systèmes hétérogènes nécessitent donc des outils spécialisés qui sont suffisamment génériques pour pouvoir s'adapter à différentes architectures. Des outils existent aujourd'hui qui permettent l'analyse de processeurs spécialisés. Cependant, ces outils sont presque tous uniquement compatibles avec un modèle de programmation et une architecture bien précise. De plus, il est souvent impossible d'adapter ces outils pour les rendre plus génériques ou les utiliser pour corréler leurs informations avec d'autres outils, car ils sont à source fermée. L'arrivée de spécifications qui définissent une architecture générique permet de développer une approche adaptable et qui permet de répondre à ce problème.

L'analyse d'un système hétérogène est très complexe, car de nombreux systèmes communiquent entre eux et chaque système a sa propre architecture. Il devient ainsi difficile d'avoir une vue d'ensemble du fonctionnement d'un programme. Il est donc nécessaire d'avoir une trousse d'outils qui permet d'obtenir toutes les visualisations nécessaires pour comprendre et détecter les problèmes de performance.

Ces difficultés sont causées par le manque d'un modèle générique de fonctionnement d'un système hétérogène et le manque d'interfaces communes de communication avec ces coprocesseurs. De plus, les outils existants ne permettent pas d'avoir assez d'information pour générer une vue d'ensemble du système. Il est aussi nécessaire d'étudier les avancées actuelles dans le domaine des coprocesseurs pour pouvoir mieux les analyser et instrumenter les librairies nécessaires.

La spécification HSA est un standard qui permet à un système hétérogène d'avoir une interface commune pour accéder aux différents coprocesseurs grâce à une API générique. Cette spécification a été conçue pour répondre aux besoins d'un système hétérogène. Ceci nous permet de développer une application pour ce standard en nous assurant d'être génériques pour pouvoir adapter l'approche à l'avenir. Nous choisirons ROCm comme implémentation du standard HSA. En effet, c'est la seule implémentation suffisamment complète qui permette de supporter les modèles de programmation parallèles les plus utilisés tels que OpenMP,

OpenCL, CUDA et HIP. De plus, des outils de traçage et de profilage associés à ROCm permettent de commencer à expérimenter plus rapidement. Enfin, ROCm est à source ouverte, ce qui permet d'instrumenter le code de façon efficace.

# 1.3 Objectifs de recherche

L'objectif principal de cette recherche est de produire une approche permettant d'obtenir une vue d'ensemble du fonctionnement d'un système hétérogène comprenant les évènements des coprocesseurs.

Pour atteindre cet objectif, il est nécessaire en premier lieu de comprendre les nouvelles technologies qui sont présentes dans les coprocesseurs, et ensuite d'évaluer la spécification HSA. Par la suite, il faut implémenter à l'aide de ROCm une approche pouvant profiler et tracer : le comportement du programme dans le contexte utilisateur, les communications avec le coprocesseur, et le programme s'exécutant sur le coprocesseur. ROCm est une collection de librairies qui implémente le standard HSA. Cette collection étant à source ouverte, nous pourrons l'utiliser facilement pour développer une approche qui sera adaptable à d'autres environnements.

Un système hétérogène fait intervenir de nombreux coprocesseurs ayant des architectures différentes. Nous avons vu précédemment que pour comprendre un tel système, il est nécessaire d'obtenir les données de tous les composants pour avoir une vue d'ensemble. Donc l'un des objectifs est d'avoir un outil capable de s'adapter à chaque coprocesseur. Il est ainsi nécessaire de fonctionner avec plusieurs architectures.

Comme nous développons une approche qui doit s'exécuter sur des programmes où la performance est primordiale, il sera important de garder un surcout relativement faible. Enfin, il sera nécessaire de développer plusieurs vues qui permettent d'offrir une vue d'ensemble de l'exécution du programme sur un outil de visualisation. Notre approche utilisera Trace Compass pour la visualisation, car cet outil est à source ouverte, est facilement adaptable, et possède tous les outils de corrélation nécessaires pour compléter notre visualisation.

### Questions de recherche

Nous pouvons donc poser les questions de recherche suivantes :

- 1. Quelles sont les données requises pour l'analyse d'un système hétérogène?

- 2. À partir de quels outils pouvons-nous produire ces données?

- 3. Quelles visualisations permettent de rendre les données plus accessibles et compréhen-

sibles?

# 1.4 Plan du mémoire

Suite à cette introduction, nous présenterons, dans le chapitre 2, l'état de l'art des processeurs graphiques, processeurs de signaux et autres coprocesseurs. Nous étudierons en détail les avancées dans le domaine du calcul sur système hétérogène et ensuite nous verrons les différentes techniques et outils de traçage, profilage et débogage.

Le chapitre 3 est consacré à la présentation d'un article scientifique qui détaille l'approche utilisée, son évaluation et les résultats de cette recherche.

Le chapitre 4 est une discussion supplémentaire, suite à cet article, qui complétera l'article avec quelques détails additionnels.

Nous conclurons dans le chapitre 5 en faisant une synthèse des travaux, en présentant ses limites et en proposant des améliorations futures.

# CHAPITRE 2 REVUE CRITIQUE DE LA LITTÉRATURE

Dans cette revue de littérature, nous allons d'abord aborder les problématiques liées aux calculs sur des systèmes hétérogènes. En effet, cette partie est primordiale pour bien comprendre quelles sont les causes des défauts de performance sur les systèmes hétérogènes et quels sont les défis qu'apportent ces systèmes. Cette première partie aura donc pour but d'analyser ces défis pour pouvoir produire ensuite des outils et des visualisations pertinentes qui permettront une analyse ciblée. Cette analyse nous permettra ensuite dans une deuxième partie d'étudier comment et avec quels outils, ces problèmes sont résolus. Ces outils nous permettront d'établir une base, pour adapter notre approche en fonction de ce qui existe déjà. De plus, ces outils peuvent être utilisés dans le futur pour recueillir certaines informations, ou corriger d'éventuelles lacunes de notre approche.

# 2.1 Calcul sur systèmes hétérogènes

Cette première partie se porte sur les trois domaines de recherche qui cherchent à optimiser et réduire le temps d'exécution pour des applications de calculs à haute performance sur des systèmes hétérogènes : le partage de la mémoire et la communication entre les différents composants du système, l'ordonnancement des calculs et comment est réparti la charge sur les accélérateurs et le CPU, enfin comment sont résolus les problèmes au niveau de la mémoire tampon qui est un enjeu majeur pour la performance. La majeure partie des recherches sur les systèmes hétérogènes se portent sur les GPUs. En effet, ce type de coprocesseur est le plus utilisé aujourd'hui dans les systèmes hétérogènes. Conséquemment, une grande partie des sujets exposés dans cette partie ne sont pas pertinents pour d'autres types de coprocesseurs.

De plus, même si les téléphones possèdent de nombreux coprocesseurs et sont une des cibles de cette recherche, les technologies utilisées ne sont pas encore disponibles sur cette plateforme.

# 2.1.1 Mémoire partagée / Communication interprocesseurs

Aujourd'hui, le principal ralentissement des programmes est dû aux lectures et écritures en mémoire. En effet, la différence de vitesse entre les processeurs et les mémoires a considérablement augmenté [2,3]. C'est pourquoi la communication interprocesseurs est très importante dans un système hétérogène, surtout dans le cas d'un très grand nombre de calculs parallèles.

#### Accès direct en mémoire

Dans un système hétérogène, des échanges d'information sont nécessaires entre le CPU et d'autres types de puces comme un processeur graphique (GPU), un processeur de traitement numérique des signaux (DSP) ou une matrice FPGA. Ces échanges utilisent un mécanisme d'accès direct en mémoire [4–7]. Celui-ci fonctionne à l'aide d'un circuit supplémentaire, le contrôleur DMA, qui effectue les traductions d'adresse, interrompt le CPU quand le transfert est terminé, et gère le trafic du bus vers le CPU.

Ce type de transfert de mémoire n'a pas été conçu pour communiquer avec des accélérateurs hautement parallèles. De nombreux défauts de ce système sont donc présents :

Ces transferts de mémoire doivent être faits explicitement à travers l'API fournie (CUDA, OpenCL). En général, ces échanges de données nécessaires introduisent de grandes inefficacités [6]: des accès non uniformes qui sont nécessaires dans de nombreuses tâches: algorithme de graphe, inférence par apprentissage automatique [4,8]. De plus, ces accélérateurs ont besoin de grandes quantités de mémoire, et cela pose différents problèmes soulignés par [5,6]. Les communications intensives dans un programme ont tendance à générer beaucoup de bulles ("pipeline stalls"). Ces bulles peuvent être masquées en changeant l'exécution vers un autre groupe de fils d'exécution [4,9]. Cependant, dans des programmes très intensifs au niveau de la mémoire, les fils d'exécution se concurrencent et cela peut avoir un impact important sur la performance. Même avec un débit entre 10 et 40 GB/s et en donnant des capacités en mémoire infinies, l'accélération due à ces changements n'est que de 10% [5]. Ces synchronisations imposent une lourde charge pour les programmeurs et les compilateurs [2]. Des propositions ont été faites pour tenter d'améliorer le mécanisme d'accès en mémoire [5,7]. Cependant les récentes recherches comme les récents GPUs utilisent plutôt une technologie de mémoire virtuelle unifiée [4,6,10–19].

#### Mémoire virtuelle unifiée

La mémoire virtuelle unifiée permet de simplifier grandement la programmation du point de vue de l'utilisateur. Elle permet d'avoir une mémoire virtuelle unifiée entre le CPU et les autres processeurs. Cette technologie a été introduite avec l'arrivée de "CUDA Unified Memory" avec CUDA 6.X, et OpenCL 2.0 "Shared Virtual Memory". Ce mécanisme introduit une facilité pour les utilisateurs qui ne manipulent plus qu'un seul espace de mémoire virtuelle. Cependant les premiers résultats de performance montrent un surcout par rapport à un programme qui définit les appels manuellement [10]. Les deux principaux problèmes de cette mémoire unifiée sont la surinscription de pages mémoire et la latence due aux défauts de

pages [10, 11, 14, 18–20]. En effet, dans les cas où la mémoire utilisée rentre complètement dans la mémoire GPU et que le problème de surinscription de pages n'est pas présent, alors la mémoire virtuelle partagée permet de gagner en performance [14].

La surinscription de pages est présente lorsque plus de mémoire est allouée au CPU qu'au GPU. Cela cause un grand nombre de défauts de pages, à cause d'une part de la politique de remplacement de pages, et d'autre part une stratégie de prélecture trop agressive [11,13,19]. Pour éviter ce problème, il est possible d'utiliser une politique de remplacement de pages plus optimale, pour limiter le nombre de défauts de page en analysant la localité des accès et faisant varier la taille des pages utilisées [11,21].

La latence due aux défauts de pages est un autre problème majeur, car les GPUs sont des processeurs qui ont une grande bande passante, mais aussi une grande latence. Donc chaque défaut de page a un gros impact sur la rapidité d'exécution d'un programme. Une technique qui tient compte de ce problème-là et du problème précédent est de choisir l'endroit où est allouée la mémoire en fonction de la sensibilité du programme. Si le programme est sensible à la latence alors on alloue directement sur le GPU pour éviter un défaut de pages sinon on alloue sur le CPU et on attend que le GPU fasse un défaut de pages [19].

Une autre technique a été développée par Wu et al. [8] pour résoudre les problèmes de performance des accès en mémoire non continue.

# Communication interprocesseurs

La communication interprocesseurs est très utile pour envoyer les informations de calculs à des circuits spécialisés. Cependant, ceux-ci peuvent utiliser des technologies très spécialisées pour s'assurer de la rapidité des communications. Ces technologies nécessitent souvent de passer vers des moyens logiciels spécialisés et des librairies propriétaires. En effet, pour les puces de l'entreprise NVidia, les pilotes logiciels sont propriétaires; pour AMD, la plupart des librairies constituant l'ensemble ROCm sont à code source ouvert, ce qui permet de mieux comprendre et de modifier ces pilotes logiciels. De plus en plus, les puces peuvent communiquer entre elles sans avoir à passer par la mémoire de l'UTC. Des technologies comme NVidia Collective Communication Library, PCIe v3, NVLink v1 et v2, permettent d'échanger des données nécessaires afin d'accélérer grandement les calculs.

D'après Young et al. [22], un système possédant quatre GPUs est ralenti de 50% en comparaison à un système idéal. Malheureusement, dû à la multiplication des périphériques dans un seul système, cette intercommunication doit pouvoir s'étendre sans mener à des goulots d'étranglement. Young et al. propose donc d'augmenter la taille du cache pour chaque GPU

afin de limiter les communications entre le CPU et les GPUs. Dans le nouveau système vendu par NVidia, DGX-1, une recherche a été faite pour mesurer l'impact d'une stratégie de communication en anneaux [23]. Cette stratégie [24] s'applique sur un réseau composé de 8 GPUs et utilise seulement la technologie NVLink pour communiquer, celle-ci offrant une latence moindre, et une meilleure bande passante. En utilisant cette technique, ils réussissent à doubler la performance de GPUs utilisant uniquement PCIe v3.

Une évaluation des diverses technologies de communication par A. Li et al. [25] montrent que l'intercommunication entre plusieurs GPUs est essentielle pour obtenir une meilleure performance sur des machines hétérogènes comme le DGX-1 ou DGX-2.

Il est aussi possible d'utiliser GPUDirect pour établir une communication entre FPGA et GPU [26]. La multiplication des cas d'utilisation qui nécessitent l'interopération entre GPUs, FPGAs et DSPs va nécessiter un standard pour établir une interface de communication où chaque processeur peut échanger des informations. Ce bus de communication commun est déjà présent dans le standard HSA [27]. De plus, de nombreuses applications aujourd'hui nécessitent l'utilisation de GPUs dans l'infonuagique. Ces cas d'utilisation ont aussi besoin de limiter les copies intermédiaires et d'accéder directement à la mémoire du GPU, par exemple en utilisant la technologie GPUDirect.

#### **CUDA**

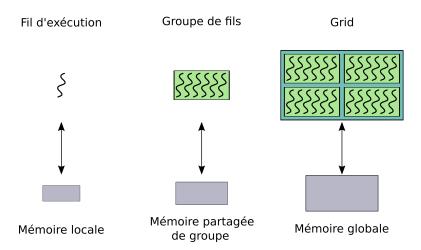

Figure 2.1 Hiérarchie de mémoire pour un GPU

CUDA est une des premières technologies à avoir existé pour effectuer du HPC sur GPU (GPGPU). Celle-ci permet de programmer directement les processeurs du GPU à travers des fonctions appelées kernels. Cette technologie utilise un mécanisme de transferts de mémoire entre UTC et GPU qui doit être explicite pour l'utilisateur. Depuis quelques années de

nouvelles technologies ont permis la création d'une mémoire unifiée qui permet une synchronisation beaucoup plus simple pour l'utilisateur. Cette mémoire unifiée utilise un mécanisme de défauts de pages pour synchroniser le CPU et les autres processeurs possédant la région de mémoire qui a été modifiée.

Pour exécuter des programmes sur un GPU, CUDA se repose sur la compilation de petites fonctions de code appelées "kernel". Il est aussi possible d'écrire du code directement avec l'utilisation de *Parallel Thread Execution (PTX)*, qui est l'architecture de jeux d'instructions de CUDA. CUDA utilise un modèle hiérarchique de mémoire qui ressemble à la hiérarchie dans la multiplication des fils d'exécution, comme on peut le voir dans la figure 2.1. En effet la mémoire partagée avec le groupe de fils d'exécution et au niveau des grids permet une plus rapide disponibilité et renforce le principe de localité [28].

### OpenCL

OpenCL est un standard de calcul parallèle sur divers types de matériel existant. L'un des principaux avantages est sa compatibilité avec plusieurs plateformes. Après le développement d'un kernel sous OpenCL, l'exécution peut être sur un CPU, un GPU, un FPGA ou même un DSP [29,30]. OpenCL n'est qu'une spécification abstraite, il permet donc une plus grande portabilité. Cependant, une évaluation de la portabilité d'OpenCL montre que des bogues subsistent dans l'implémentation de chaque vendeur. De plus, des comportements différents sont adoptés par les constructeurs quand la documentation n'est pas claire.

Cette spécification, avant la version 2.0, obligeait l'utilisateur à explicitement déclarer les transferts de mémoire. Avec la dernière version de OpenCL, une plus fine granularité est possible et il est possible d'utiliser une mémoire unifiée virtuelle pour faciliter la programmation avec cette spécification.

### **HSA**

HSA est un standard développé par la fondation HSA. Des entreprise notables ont contribué à créer cette fondation : ARM, AMD, Qualcomm et Samsung. Cependant, seulement AMD produit des coprocesseurs compatibles actuellement. Ce standard décrit comment les accélérateurs doivent communiquer avec le CPU et entre eux. Ce standard a pour but d'augmenter la programmabilité de ces accélérateurs et d'améliorer la performance des systèmes hétérogènes. Ce standard définit une mémoire virtuelle unifiée qui peut soit être de granularité grosse, ou de granularité fine, en fonction du déroulement optimal du programme. Pour envoyer des commandes aux accélérateurs, l'envoi de paquets en mode usager, AQL, est utilisé

pour permettre une certaine flexibilité, et aussi pour ne pas avoir à changer de contexte. Ceci permet un gain de performance qui a été mis en évidence par Sun et al. [31]. En comparant ROCm, l'implémentation de HSA par AMD, à l'ancien pilote graphique, ils ont montré que cette approche permettait de gagner de la performance grâce aux files d'attente utilisateur et une plus fine granularité. HSA permet aussi le *Device Side Enqueuing* qui permet à un accélérateur de lancer un kernel sans interagir avec le CPU, à la fin de l'exécution d'un autre kernel. Le support pour échanger des signaux entre le CPU et le GPU a été ajouté, permettant une communication rapide et évitant le *polling* qui est couteux en performance [32]. De plus, il permet un contrôle de l'exécution plus important, ce qui permet de nombreuses optimisations quant à l'ordonnancement [33].

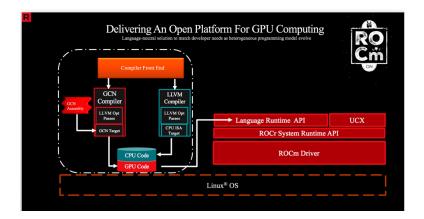

Figure 2.2 Relation des librairies dans l'environnement ROCm ©2020, AMD. Reproduit avec permission.

Ce standard est implémenté par AMD qui a développé ROCm, un ensemble de librairies dans le but d'être modulaire, décrit dans la figure 2.2. Cet ensemble permet d'utiliser des accélérateurs du vendeur AMD qui utilisent HSA. De plus cet ensemble est pour la majorité à source ouverte, ce qui permet une modification et une instrumentation des pilotes graphique plus aisée.

### 2.1.2 Ordonnancement des calculs et répartition des charges

Sur les systèmes hétérogènes, il est très important de tenir compte des capacités des différents coprocesseurs. En effet, ceux-ci ayant des architectures spécialisées, un programme peut avoir un temps d'exécution très différent selon le coprocesseur sur lequel il est exécuté. De plus, les communications entre le CPU et les différents coprocesseurs sont souvent la cause des principaux défauts de performance. Donc il est nécessaire d'ordonnancer correctement les charges de travail pour éviter de surcharger les transferts mémoires tout au long de l'exécution d'un

programme. Nous allons étudier les différents modèles de performance et les caractéristiques des charges de travail d'une part. D'autre part, nous allons voir comment il est possible de faire collaborer plusieurs coprocesseurs pour atteindre de meilleures performances.

# Modèles de performance et Ordonnancement

Pour comprendre comment un programme est inefficace pour une architecture donnée, il faut comprendre comment celle-ci fonctionne ou, du moins, avoir une abstraction qui est réaliste. Une architecture multi SIMD, telle que celle d'un GPU, nécessite une bonne compréhension de l'architecture pour pouvoir écrire un programme efficace. Cependant, pour des standards tels qu'OpenCL qui se veulent multi plateforme, l'utilisation d'une architecture type permet d'abstraire certains détails techniques. Cette abstraction est utile pour obtenir une performance raisonnable sur différentes architectures semblables, mais de vendeurs différents. De plus, l'utilisation d'un modèle de performance est utile dans les cas d'utilisation où l'on doit prédire la performance d'un kernel pour répartir une charge de travail. Nous avons vu précédemment qu'une charge de travail trop importante pouvait donner lieu à des pertes de performance à cause des synchronisations de mémoire entre GPU et CPU.

Pour évaluer automatiquement la performance d'un programme sur un GPU, une approche analytique est moins performante qu'un modèle statistique d'apprentissage machine [34]. En effet, le modèle statistique est plus robuste aux changements d'architecture. De plus, il est difficile d'estimer certains paramètres qui sont propres aux vendeurs comme la politique d'ordonnancement des warps dans un compute unit. L'utilisation de compteurs de performance et de données du compilateur permet donc de prédire, avec une certaine erreur, la performance de fonctions kernel qui s'exécutent sur un accélérateur. D'autres modèles [35] prédisent les performances du CPU pour pouvoir améliorer la performance des systèmes hétérogènes.

L'ordonnancement permet d'améliorer grandement la performance d'un système hétérogène. En effet le temps d'exécution d'un grand nombre d'applications dépend grandement de l'ordre dans lequel ces tâches sont exécutées. De plus l'utilisation de nouvelles technologies, comme la mémoire virtuelle unifiée, influe sur la performance obtenue et doit être prise en compte au niveau d'un modèle de prédiction [36].

La plupart des modèles de prédiction proposés sont linéaires [34,36–38] et comprennent pour la plupart majoritairement des compteurs de performance. Cependant, d'autres données statiques proviennent du compilateur, ce qui permet de prendre en compte d'autres paramètres. Ces modèles sont ensuite utilisés pour l'ordonnancement et permettent des gains entre 20 et 30% en temps d'exécution [34,37].

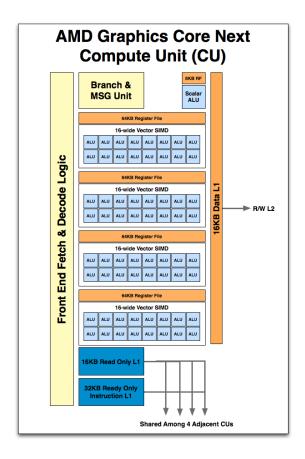

Figure 2.3 Architecture d'une unité de calcul GCN [1] sur un GPU c2012, AMD. Reproduit avec permission.

L'architecture d'un GPU est composée de multiples *Compute Units* (selon la terminologie d'OpenCL) qui permettent d'exécuter plusieurs kernels simultanément. Chaque *Compute Unit*, a une architecture semblable à celle illustrée dans la figure 2.3. Elle est composée de plusieurs processeurs SIMD qui exécutent chacun des groupes de fils d'exécution.

### Caractéristiques des charges de travail

Pour correctement évaluer les modèles de performance présentés, la plupart des recherches se basent sur des bancs d'essai qui présentent diverses charges de calculs suffisamment différentes les unes des autres pour représenter l'ensemble des programmes qui peuvent être exécutés sur un accélérateur. Une partie de ces bancs d'essai permettent d'évaluer certaines capacités matérielles de façon pratique comme la vitesse du bus, la bande passante, le nombre de calculs à virgule flottante, etc. [39, 40]. Sinon, ils utilisent des applications spécifiques de simulation physique, mathématique ou d'autres problèmes nécessitant une forte puissance de calculs [39, 41–43]. Ces bancs d'essai sont fortement utilisés dans les recherches pour évaluer

une politique d'ordonnancement, la prédiction d'un modèle, stratégie de préchargement, etc.

Ces bancs d'essai prennent en compte différentes caractéristiques de charges de travail. Sur un GPU, il est possible d'avoir un programme qui n'utilise pas toutes les ressources disponibles d'un compute unit. On mesure donc le taux d'occupation, qui est le pourcentage de SIMD utilisé par compute unit durant l'exécution d'un programme. De plus, à cause des branches conditionnelles, certaines instructions sont exécutées alors que la condition n'est pas valide, car tous les fils d'exécution sont synchronisés. Il y a donc une divergence. La performance d'un programme ayant une grande divergence dépend des autres kernels qui s'exécutent simultanément, à cause de l'utilisation intensive de la mémoire tampon. D'autre part, la mémoire dans un système hétérogène est très importante et a un impact non négligeable sur la performance. C'est pourquoi les bancs d'essai doivent avoir une bonne variation dans l'utilisation de la mémoire, pour s'assurer qu'une meilleure performance atteinte n'est pas due à un biais qui privilégie le résultat du banc d'essai.

Une évaluation de ces bancs d'essai [44], en les comparant entre eux, montre que certains ne couvrent qu'une faible variance dans l'espace des programmes existants. En revanche certains, comme [41], sont relativement efficaces, mais restent biaisés dans leur évaluation car la majorité des programmes ont une grande occupation. L'idéal est donc de combiner plusieurs bancs d'essai pour éviter de biaiser les résultats et d'avantager une caractéristique en particulier.

La prise en compte de ces diverses caractéristiques est essentielle pour obtenir un banc d'essai qui évalue objectivement la performance d'une technologie, d'une optimisation, ou d'une stratégie.

# Mesurer la charge de travail

Pour mesurer l'occupation, la divergence et l'utilisation de la mémoire, les logiciels de profilage ont recours aux compteurs de performance. Nous avons déjà vu précédemment que ceux-ci étaient très efficaces pour prédire le temps d'exécution d'un programme. En effet, ces compteurs sont obtenus de différentes manières. L'utilisation d'un simulateur de GPU permet de définir et d'obtenir n'importe quelle sorte de compteurs. L'utilisation de compteurs matériels est souvent limitée, on ne peut pas les obtenir tous simultanément. Souvent, seulement une partie de ces compteurs sont utilisables en même temps donc, nous sommes obligés d'activer seulement une partie des compteurs et d'exécuter plusieurs fois l'application pour obtenir l'ensemble des compteurs voulus.

Une des mesures les plus utilisées pour évaluer la performance de la mémoire est le taux de

fautes de caches. En effet, dans de nombreuses études [45–47], ce compteur de performance permet d'évaluer la capacité de l'accélérateur et des pilotes à utiliser efficacement la bande passante. De plus, ce compteur est souvent disponible à différents niveaux de caches. Cette mesure est donc utilisée pour comparer différents algorithmes de remplacement des lignes de cache ou pour diriger l'optimisation d'un programme qui est limité par la bande passante.

Pour mesurer l'occupation d'un GPU, on a souvent recours au parallélisme des fils d'exécution (TLP). Cette mesure indique si le programme exécuté occupe de façon optimale toutes les ressources disponibles de l'accélérateur. On utilise le nombre moyen de warps par cycle comme métrique pour mesurer ce paramètre [48, 49]. Le TLP est notamment utilisé pour réguler la charge de travail dans un système hétérogène, car un trop grand TLP peut surcharger la mémoire et ralentir drastiquement l'exécution.

Le nombre d'instructions exécutées par cycle (IPC) est aussi utilisé pour identifier la cause d'une amélioration d'un programme. Cependant, une amélioration de l'IPC ne mène pas toujours à un plus petit temps d'exécution. Des bulles qui bloquent des instructions mènent à une réexécution de ces instructions, ce qui explique un plus grand IPC associé à un plus grand temps d'exécution. D'après Jablin et al. [50], dans le cas où un plus grand IPC est associé à une exécution plus rapide, alors l'IPC peut remplacer la TLP.

Pour prédire le temps d'exécution d'un kernel, on peut utiliser le nombre d'instructions : vectorielles, scalaires, de branches, etc. En effet, ces informations fournies par le compilateur sont très corrélées avec le temps d'exécution [51]. Cependant, les programmes s'exécutant sur le même système hétérogène ont une grande influence sur la performance des kernels. Il est donc essentiel de tenir compte de ces programmes colocalisés [51].

# Répartition des charges

Nous avons vu comment les programmes sont évalués grâce à des caractéristiques de performance pour prédire leur temps d'exécution sur divers coprocesseurs. En effet, il est important de répartir les charges, dans un système hétérogène, pour s'assurer que le coprocesseur soit adapté aux tâches qu'on lui envoie. De plus, il est souvent nécessaire de fusionner ou de diviser des tâches pour mieux les répartir. Nous allons voir ici les différentes techniques qui permettent aux coprocesseurs de mieux collaborer.

Une approche classique pour faire collaborer plusieurs processeurs est de diviser les données en autant de processeurs, pour que chacun exécute une partie. Cette première approche n'est pas tout le temps applicable, mais reste une technique très performante et très utilisée dans les systèmes *MapReduce*. Cette technique a été évaluée dans le contexte d'un système

hétérogène composé d'un CPU et d'un FPGA [52]. L'étude a utilisé le banc d'essai Chai qui est composé d'algorithmes de traitement d'images. La meilleure performance a été atteinte en calculant une partie des images sur le CPU et l'autre partie sur le FPGA, et en utilisant un ordonnancement dynamique (contrôlé par un fil durant l'exécution).

Une autre stratégie est de séparer les tâches entre les différents coprocesseurs. Selon Huang et al. [52], les gains de cette stratégie sont similaires au gain du partitionnement de données. De plus, la séparation de tâches a un plus grand cout pour les transferts de mémoire. Cependant, les processeurs ont des périodes où ils sont à l'arrêt avec cette stratégie, donc une amélioration de performance est possible, et surement atteignable en évaluant le meilleur coprocesseur pour la tâche. Toutefois, ces approches ne permettent pas toujours de gagner en performance, comme l'ont souligné Zhang et al. [53]. Ils ont développé un modèle permettant de prédire si le programme peut bénéficier d'une stratégie de collaboration ou non. Il est donc important de toujours évaluer ces stratégies sur des programmes variés pour être certains des gains de performance qui ne sont pas toujours présents.

# 2.1.3 Gestion de la mémoire tampon

Nugteren et al. [54] montre que "comme les GPUs cachent la latence d'accès à la mémoire interne du GPU à travers l'utilisation de nombreux fils d'exécution, ils nécessitent une grande bande passante. L'utilité principale de la mémoire tampon n'est donc pas de réduire la latence d'accès à la mémoire interne du GPU, mais de réduire les transferts de mémoire entre le CPU et le GPU". Dublish et al. [55] montre en effet que la bande passante entre le CPU et le GPU limite la performance. Cependant, l'un des facteurs les plus limitants est la bande passante de la mémoire tampon L2. La latence n'est donc jamais un facteur limitant, car le nombre de fils d'exécutions permet de pallier les défauts de cache, sans impacter la performance, tant que l'application ne nécessite pas de grandes quantités de mémoire. Au cas où l'application nécessite beaucoup de mémoire, alors c'est la bande passante qui limite le temps d'exécution. Une utilisation efficace de la mémoire tampon devient alors essentielle pour améliorer le temps d'exécution.

### Le principe de localité

La localité des données est le paramètre exploité par la mémoire tampon pour améliorer la performance en réduisant la latence d'accès. Il existe deux types de localités, la localité temporelle et la localité spatiale. La localité temporelle est l'utilisation des mêmes ressources dans un temps proche. La localité spatiale est l'utilisation de ressources proches ou similaires à d'autres ressources accédées récemment. Il est donc primordial d'optimiser la localité des

données dans un programme. De nombreuses techniques d'exécution ont été développées dans ce but et le principe de localité dirige les analyses de performance sur les CPUs, qui ont ensuite été adaptées pour les accélérateurs [54,56]. Nous verrons ces techniques dans la partie concernant le profilage et le traçage.

Nous verrons comment l'ordonnancement, à plusieurs niveaux, est primordial. Ensuite, ralentir volontairement l'exécution peut limiter certaines interférences améliorant le temps d'exécution. Ne pas utiliser la mémoire tampon dans certains cas peut être bénéfique. Enfin, en raison de la spécificité des accélérateurs, les algorithmes de remplacement de ligne de cache utilisés traditionnellement sur les CPU peuvent être modifiés pour être plus optimaux sur les accélérateurs.

#### Ordonnancement des kernels

L'exécution de code sur un accélérateur se fait par fonction kernel. Ces kernels sont ordonnancés grâce à une file d'attente dans la plupart des cas. Cette file d'attente étant remplie par l'hôte. Il est souvent possible sur des accélérateurs d'exécuter simultanément plusieurs kernels. L'exécution peut aussi être répartie de façon à minimiser le temps d'exécution. On peut diviser chaque kernel en plusieurs sous-kernel. Un test [57] avec Rodinia [41] montre qu'en fonction du kernel, la performance varie grandement entre une exécution sérielle, une exécution simultanée, un découpage variable et un découpage statique. L'article conclut que le découpage pour améliorer la performance est nécessaire. L'ordonnancement et la division de kernels pour améliorer la performance est donc primordiale.

Pour ordonnancer correctement les kernels, l'état de l'art est de posséder une étape de profilage pour évaluer la performance et l'impact qu'ont chaque kernel [57,58]. Il est aussi possible de mesurer le nombre de certains types d'instruction pour estimer certains paramètres [59]. Suite à cette étape, grâce à l'utilisation d'un modèle de prédiction, on peut déterminer quelles combinaisons de kernels sont optimales. Après l'obtention des différentes combinaisons à exécuter simultanément, il faut déterminer comment diviser la charge de travail de manière à occuper toutes les unités de calcul de l'accélérateur [57]. Ces divisions tiennent compte des données de profilage, combinées aux données spécifiques à l'architecture utilisée.

# Ordonnancement des warps

Dans l'architecture du constructeur Nvidia un warp, ou wavefront dans l'architecture du constructeur AMD, est un ensemble de fils d'exécution sur un processeur graphique. Cet ensemble représente un certain nombre de calculs et donc de cycles d'exécution. Par exemple

un wavefront s'exécute en quatre cycles sur l'architecture GCN d'AMD.

Ces blocs de calculs sont ordonnancés au niveau des multiprocesseurs de flux. Ces warps sont ordonnancés en deux étapes : l'attente du chargement des instructions et des données, et la priorisation. À l'étape de la priorisation, plusieurs ordonnanceurs (dépendant de l'architecture) priorisent différents warps en utilisant un algorithme comme le round-robin [60]. Ensuite un seul warp est sélectionné et exécuté en quatre cycles, que ce soit sur l'architecture AMD ou Nvidia.

Les accès mémoire pour préparer l'exécution des warps peuvent mener à une saturation des MSHR, ce qui empêche les autres warps d'accéder à la mémoire tampon [60,61]. La méthode OAWS [60] effectue une prédiction du nombre de MSHRs utilisés par un warp et ordonne les warps de façon à maximiser l'utilisation de ces registres, sans les saturer, tout en estimant le nombre optimal de warps simultanés. La méthode Mascar [61] sélectionne un warp et lui donne la priorité pour ses requêtes mémoire de manière à garantir l'exécution complète de ce warp. Celui-ci pourra donc être exécuté sans ralentir grandement l'exécution, car tous les warps en cours d'exécution saturent les registres et donc attendent chacun leur requête mémoire. Le ralentissement de l'exécution est donc parfois bénéfique au temps d'exécution, du fait des interférences entre chaque warp au niveau de la mémoire tampon.

Une autre approche est de tirer profit de l'hétérogénéité des warps [62]. Le système Me-DiC classifie les warps en différents types. Ensuite, l'ordonnancement des requêtes mémoire pour préparer les warps à l'exécution, et l'utilisation du cache, dépendent du type. D'autres approches ne sont pas détaillées ici, mais ont fait l'objet d'un article : PRO [63], DAWS [64].

## Contournement de la mémoire tampon

Certains des warps n'utilisent pas efficacement la mémoire tampon. Pour ceux-ci, Ausavarungnirun et al. [62] proposent de contourner l'utilisation de la mémoire tampon. La mémoire tampon n'améliorant pas beaucoup l'exécution de ces warps, cela permettra de réduire les conflits au niveau du cache.

Dans d'autres cas, il est nécessaire d'ignorer la mémoire tampon et d'envoyer directement le résultat d'une seule requête mémoire. En effet, si l'on décide d'utiliser le cache, celui-ci devra libérer d'autres variables qui, à leur tour, vont entrainer un défaut de cache quand elles seront utilisées à nouveau. Ce cas arrive régulièrement dans les applications nécessitant beaucoup d'appels mémoire. Un des moyens pour éviter de surcharger la mémoire tampon, appelé prédiction de la distance de protection (PDP), est de protéger chaque ligne du cache avec un compteur. Ce compteur est décrémenté à chaque accès. Lorsque le compteur arrive

à zéro, alors la ligne peut être remplacée. Cette technique existe depuis longtemps, mais est toujours utilisée pour améliorer l'utilisation du cache dans des programmes et soulager l'emballement de la mémoire tampon [65–68].

# Indexation adaptative de la mémoire tampon

Une autre façon d'optimiser l'utilisation du cache est d'adapter la manière d'indexer différemment celui-ci. Cette approche étend de précédents travaux qui ont été effectués sur les CPUs [69]. Nous avions vu précédemment que le conflit est une des trois causes de défauts de cache. En modifiant l'indexation, il est possible de mieux répartir l'utilisation de la mémoire tampon sur les processeurs graphiques [66]. Cette technique a récemment été utilisée dans un contexte de calcul générique, mais Kim et al. [70] avait obtenu une réduction dans le nombre de défauts de cache pour une application utilisant des processeurs graphiques.

En effet cet article combine l'utilisation d'une indexation adaptative avec le contournement de la mémoire tampon et la limitation de warps pour fournir la meilleure performance possible. Une autre approche est d'utiliser un cache complètement associatif, ce qui permet de réduire dramatiquement les conflits [71]. Cette approche reste cependant étudiée grâce à un simulateur et n'est pas encore implémentée.

# Algorithme de remplacement de lignes de cache

Nous avons vu précédemment qu'une indexation avait un impact significatif sur la performance et le nombre de défauts de cache. L'utilisation d'un algorithme de remplacement de lignes de cache spécifique aux accélérateurs et à leur architecture est aussi une très bonne façon d'optimiser la performance.

Les CPUs Intel aujourd'hui utilisent un algorithme Pseudo-LRU (PLRU) pour les caches L1 et L2 [72], mais ce type d'algorithme n'est pas forcément applicable directement aux accélérateurs. En effet, dans certains cas, MRU est plus performant, et donc en fonction du type de warp, on privilégiera un algorithme plutôt qu'un autre [62]. Il a déjà été montré qu'en utilisant uniquement LRU, la performance était loin d'être optimale, et qu'en utilisant une stratégie qui maximise certains paramètres comme le nombre d'instructions par cycle, ou alors qui minimise le nombre de défauts par cycle, alors on obtenait des résultats bien plus proches de l'optimal [73].

# 2.2 Traçage, profilage et débogage de systèmes hétérogènes

On a vu précédemment des techniques pour améliorer différents aspects de la performance des systèmes hétérogènes. Le profilage de systèmes hétérogènes consiste à évaluer certains paramètres pour pouvoir mesurer la performance. On peut résumer ces problèmes en quatre catégories [74]: l'efficacité d'exécution du kernel sur un accélérateur, les interactions entre l'hôte et l'accélérateur, les interférences entre plusieurs exécutions sur un accélérateur et les communications entre accélérateurs. Il existe trois approches pour prendre des mesures: le traçage, le profilage et le débogage. Les trois approches nécessitent une analyse pour pouvoir être compréhensibles pour l'utilisateur. Nous allons donc étudier chacune de ces approches de façon détaillée dans cette partie.

# 2.2.1 Traçage et analyse

Le traçage est souvent très couteux et donc il est nécessaire de limiter le traçage horizontalement (quelle partie du programme est instrumentée) et verticalement (dans quelle fonction instrumente-t-on?) [75].

# LTTng

LTTng (Linux Trace Toolkit next-generation), est sorti initialement en 2005. Le projet a été créé par Mathieu Desnoyers pour permettre le traçage sur le système d'exploitation Linux. C'est une trousse d'outils permettant le traçage à travers l'utilisation de point de traçage, de kprobes et d'informations de profilage. En effet, les points de traçage sont des éléments de code permettant l'exécution de code à certains endroits précis. Le code s'exécutant est dénommé kprobe pour kernel probe. Il s'agit en effet de permettre à l'utilisateur de sonder quand est-ce que le kernel exécute certaines fonctionnalités et de pouvoir donc mieux comprendre son fonctionnement, étudier sa performance et comment il interagit avec les programmes utilisateurs.

LTTng se sert donc de ces points de traçage pour instrumenter le kernel Linux avec ses propres fonctions pour enregistrer les différents évènements. En effet, l'enregistrement des informations de trace peut être complexe dû à la fréquence avec laquelle ceux-ci sont produits. Des millions d'évènements ont lieu chaque seconde et il faut les enregistrer sans impacter fortement la performance, dans un format qui reste utilisable. D'autres librairies existent pour réaliser la même tâche : SystemTap [76], DTrace [77], ftrace [78]. Cependant, chaque librairie possède sa propre spécificité et ses propres fonctionnalités.

La particularité de LTTng est qu'il n'utilise aucun verrou pour supporter plusieurs fils d'exé-

cution simultanés. L'utilisation de verrous dans un système parallèle est souvent cause de nombreux problèmes de performance dus aux différents changements de contexte et au maintien de la cohérence de la mémoire tampon. Les algorithmes qui permettent l'exécution parallèle sans verrous sont donc très performants. Cela permet à LTTng d'être un outil de traçage qui possède un des surcouts les plus faibles [79] pour le traçage du noyau Linux.

LTTng possède aussi la capacité de tracer en mode utilisateur pour enregistrer des traces de programmes à l'aide de différents mécanismes. L'instrumentation est soit effectuée par l'utilisateur du programme, soit injectée automatiquement par le compilateur (typiquement aux débuts et fins de fonctions), soit déjà incluse dans une librairie utilisée. Les informations de trace sont envoyées à un daemon, qui les enregistre dans un fichier de trace.

Le format utilisé par LTTng est le format CTF (Common Trace Format). C'est un format de stockage binaire qui permet le stockage efficace d'une trace. En effet le format étant séquentiel et possédant plusieurs canaux, plusieurs fils d'exécution enregistrent simultanément les évènements. De plus, un fichier de méta données enregistre les informations nécessaires pour la lecture et l'analyse de la trace. Ce format est aussi utilisé pour de nombreuses analyses sur l'outil de visualisation Trace Compass.

#### **CLUST**

Couturier et Dagenais [80] ont présenté un outil appelé LTTng CLUST qui permet de tracer l'exécution d'un système hétérogène fonctionnant avec OpenCL. En effet, la librairie OpenCL a été instrumentée à l'aide de LTTng pour fournir cette fonctionnalité. De plus, comme LTTng a la capacité de tracer le noyau Linux, cet outil permet d'observer à la fois l'exécution dans le contexte du noyau et dans le contexte du processus exécutant l'application.

On peut donc observer les commandes asynchrones envoyées à travers l'interface d'OpenCL synchronisées avec le temps du CPU. Cet outil utilise Trace Compass pour visualiser le fonctionnement de l'application dans sa globalité. Le surcout de cette approche est significatif, mais augmente peu avec l'augmentation de la charge de travail. Une des limitations de cet outil est l'absence de données de profilage. En effet, la seule donnée existante est la durée d'exécution du kernel. L'outil ne permet pas donc facilement d'améliorer le temps d'exécution des kernels sur les accélérateurs, ce qui est un enjeu important du calcul de haute performance.

# LTTng-HSA

Margheritta et Dagenais [81] ont présenté un outil appelé LTTng-HSA. Cet outil permet de tracer l'exécution d'une application sur un système hétérogène sur la plateforme ROCm.

En effet, il se sert des capacités d'interfaçage de ROCm pour insérer des points de trace à l'aide de LTTng. De plus, il se sert de la librairie GPA pour collecter les compteurs de performance liés à l'exécution. Dû aux limites de registres sur le processeur graphique utilisé, il est possible de prendre plusieurs mesures pour pallier ce problème. De plus, les évènements étant asynchrones, il est nécessaire de trier la trace obtenue pour les réordonner.

Plusieurs vues ont ensuite été développées sur Trace Compass pour visualiser les différentes files d'attente créées, et leur état durant l'exécution du programme. Cet outil permet donc l'obtention de données de profilage, en plus des données de traçage, mais n'a pas de capacités d'analyse de ces données. De plus, les données de traçage ne sont pas synchronisées avec le traçage du noyau, ce qui aurait permis une analyse plus complète du système. Dû à l'évolution de ROCm, cet outil n'est plus à jour, car l'interface utilisée a évolué. Des tests avec des bancs d'essai connus comme Rodinia [41] ou Hetero-mark [42] auraient permis d'évaluer plus en détail les capacités de cet outil.

# **Dyninst**

Dyninst [82] est une librairie développée en C++ qui permet de manipuler un programme après sa compilation. En effet, cela permet à un utilisateur de cette librairie d'instrumenter dynamiquement son programme durant son exécution. L'utilisateur a à sa disposition une interface de protocole d'application. Grâce à cette librairie, il est donc possible d'instrumenter et de tracer, profiler ou déboguer une application à l'exécution. Cet outil n'est pas un outil de traçage, mais sert à créer des outils de traçage ou de profilage [83,84].

Pour insérer dynamiquement du code au niveau d'un programme en exécution, Dyninst se sert des mêmes mécanismes qu'un débogueur pour localiser et accéder au processus. Ensuite, pour générer le code, il transforme le code à insérer en langage machine et il utilise un trampoline pour exécuter ce code. Un trampoline est une technique permettant d'insérer une longue section de code à l'intérieur sans interagir avec l'état du programme. En effet, une instruction de saut est utilisée pour exécuter un "trampoline" qui va ensuite à son tour sauter vers un "mini-trampoline" qui va enregistrer l'état du programme et le restaurer après l'exécution du code à insérer. Ensuite ce "mini-trampoline" va aller exécuter le code à insérer. De cette façon, le code du programme est très peu modifié et, si l'on choisit le point d'insertion correctement, la logique n'est pas impactée.

#### Instrumentation du kernel

Le traçage d'une application au niveau de l'hôte permet d'obtenir une vue d'ensemble du fonctionnement de l'application. Il permet de diagnostiquer les problèmes de performance et d'étudier son comportement. Cependant, dans un système hétérogène, il est nécessaire, dans certains cas d'instrumenter le code au niveau de l'accélérateur.

Il existe deux approches : instrumenter à l'aide d'un simulateur et instrumenter le langage machine de l'accélérateur. Le premier permet une plus grande liberté et souplesse pour instrumenter, car le simulateur permet d'accéder à tous les composants du processeur. Cependant, la précision n'est pas toujours bonne et dépend du simulateur et de l'architecture utilisée. En outre, l'exécution peut être très longue et rendre l'expérimentation difficile. Le second peut perturber les mesures à cause des effets de bord de l'instrumentation. De plus, le surcout dû à l'instrumentation dépend beaucoup du kernel [85].

## Lynx

Le système Lynx, développé par Farooqui et al. [85], permet d'instrumenter dynamiquement un kernel en insérant des instructions au niveau du jeu d'instructions PTX. Ce système se base sur un outil précédent, Ocelot [86], qui permet de transformer un kernel en y ajoutant des instructions PTX. Ces instructions fonctionnent donc uniquement avec les accélérateurs graphiques Nvidia, car AMD utilise un jeu d'instruction différent. Cependant, il a été adapté plus récemment pour être compatible avec les accélérateurs d'AMD [87]. Ocelot modifie le code du programme après sa compilation pour l'instrumenter, ce qui permet d'avoir des capacités similaires à Dyninst pour un kernel qui s'exécute sur un accélérateur.

Lynx permet d'ajouter des instructions en langage C à l'intérieur du kernel compilé en PTX. De plus, les appels à cudaMalloc, cudaMemcpy, cudaFree ont été instrumentés pour permettre à l'accélérateur de copier les données de traçage vers l'hôte pour enregistrer une trace. Lynx offre la possibilité de tracer par fil d'exécution, par groupe de fils, warps et SM. Cela permet de configurer facilement la façon dont un programme est tracé ou profilé, et de réduire le surcout si celui est trop grand. Il supporte aussi l'instrumentation définie par l'utilisateur, alors que les outils donnés par Nvidia ne permettent que le choix d'un certain nombre de compteurs de performance à activer. Des outils ont été développés avec Lynx pour permettre d'optimiser des applications durant l'exécution, en utilisant les informations de profilage [88].

# Trace Compass

Trace Compass est un outil de visualisation de trace à source ouverte développé en Java et basé sur l'infrastructure Eclipse. Il permet d'effectuer un certain nombre d'analyses à partir des informations de trace. Ces évènements pour les traces noyaux comportent des informations spécifiques à propos du système. La plus importante est l'estampille de temps. Celle-ci permet de dériver l'état de chaque processus et chaque fil d'exécution grâce à leur numéro d'identification. D'autre part, des informations spécifiques à chaque point de trace permettent de définir un état pour le processus. Il est aussi possible de définir des dépendances entre chaque processus, d'une part en sachant sur quel processeur le processus est en train d'être exécuté. D'autre part, en analysant les causes de la mise en attente des processus, il est possible de construire le chemin critique de n'importe quel processus en exécution pendant l'enregistrement de la trace [89].

Trace Compass fonctionne grâce à une machine à états qui parcourt la trace en ordre chronologique et qui attribue à chaque fil d'exécution un état. Au fur et à mesure que les évènements sont traités, chaque fil d'exécution va changer d'état en fonction des évènements traités. Le résultat est présenté sous forme d'une frise avec pour chaque ligne un fil d'exécution ou un processus.

Trace Compass permet l'analyse de n'importe quelle trace, tant que l'on spécifie les objets dont on souhaite traquer l'état et comment l'état est modifié par les évènements. De nombreuses analyses existent aujourd'hui pour différentes applications : analyser la pile d'appels en fonction du temps, l'ouverture et la fermeture des fichiers par chaque processus en fonction du temps, le *flamegraph* d'une application, la consommation de mémoire en fonction du temps, etc.

Trace Compass étant construit avec Eclipse, il hérite de son interface utilisateur. Les interfaces utilisateur évoluant maintenant très rapidement, un nouveau projet a été créé par la fondation Eclipse: Theia. Ce projet a pour but d'avoir un éditeur de code avec un découplage entre l'interface et le coeur de l'application. TraceCompass a été modifié pour supporter ce découplage et il est possible d'exécuter un serveur TraceCompass et d'analyser des traces sur un serveur distant. Un module implémentant une interface pour Trace Compass sur Theia est donc en développement pour avoir une interface plus moderne, et plus facilement modifiable.

#### L'analyse de distance de réutilisation

L'analyse de distance de réutilisation (RDA) est un modèle populaire [47, 54, 56, 90, 91] qui permet de mesurer l'efficacité d'un programme à tirer profit de la mémoire tampon. Initiale-

ment pour une architecture de CPU, ce modèle a été adapté pour une architecture parallèle. Dans ce cas-ci, l'ordre d'exécution est difficile à connaitre, car de nombreux fils d'exécution s'exécutent de façon concurrente et l'algorithme d'ordonnancement des warps n'est pas toujours connu. De plus, l'algorithme de remplacement des lignes de cache n'est pas toujours le même pour les architectures parallèles.

Les défauts de cache ont trois causes : le conflit, la capacité et l'obligation [92]. Le conflit survient lorsque la place est suffisante en mémoire tampon, mais différentes régions de la mémoire utilisées sont alignées. Ces régions de mémoire seront alors en conflit à cause de l'utilisation des mêmes lignes de cache (*n-way set associative cache*). Un défaut de cache peut survenir à cause d'une capacité limitée et un défaut de cache initial est obligatoire pour charger une valeur dans la mémoire cache.

Nous avons vu précédemment que l'utilisation du cache est primordiale pour limiter les transferts entre l'accélérateur et le CPU. En effet, c'est la principale source de ralentissement et ces transferts limitent la performance sur les systèmes hétérogènes [46,47,90,93]. Dans l'analyse de distance de réutilisation, seulement les défauts de cache obligatoires et ceux dus à la limite de capacité sont pris en compte, car la méthode RDA est basée sur un cache complètement associatif. La distance de réutilisation correspond au nombre d'adresses différentes accédées entre deux accès à la même case mémoire. Cette distance est utile pour profiler un programme et obtenir une mesure de l'efficacité de l'utilisation de la mémoire tampon. Des approches différentes ont été prises pour prendre en compte divers paramètres : l'associativité du cache [47], les registres permettant de traquer les diverses requêtes en mémoire après un défaut de cache [47,54,94], et l'exécution simultanée de kernels [90]. Aucune approche cependant ne combine tous ces paramètres. De plus, certains de ces paramètres sont très dépendants de l'architecture, et donc d'un vendeur à un autre, d'une génération à une autre, ils sont susceptibles de changer.

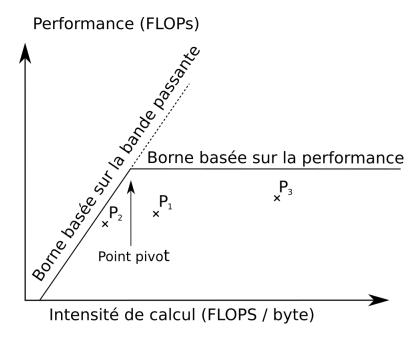

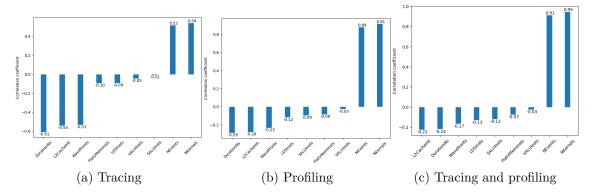

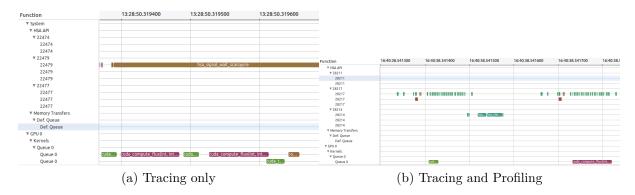

# Analyse de l'empreinte mémoire