# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

**PoET-BiN:** Power Efficient Tiny Binary Neurons

# SIVAKUMAR CHIDAMBARAM

Département de génie électrique

Mémoire présenté en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* Génie électrique

Décembre 2019

© Sivakumar Chidambaram, 2019.

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Ce mémoire intitulé :

# **PoET-BiN: Power Efficient Tiny Binary Neurons**

# présenté par **Sivakumar CHIDAMBARAM** en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* a été dûment accepté par le jury d'examen constitué de :

François LEDUC-PRIMEAU, président Jean-Pierre DAVID, membre et directeur de recherche Pierre LANGLOIS, membre et codirecteur de recherche Grabiela NICOLESCU, membre

# DEDICATION

To my parents This is just the beginning...

#### ACKNOWLEDGEMENTS

Three years ago, a knock on the door of Prof. Jean-Pierre David is something I will always remember. Since then he has been with me through thick and thin making me a better individual professionally and personally. Setting research directions, constructing a solution step by step, not losing courage in dire situations are some the things I learnt from him. He has been a great source of motivation and inspiration for me. There is no amount of words enough to express my gratitude.

I would extend my heartfelt gratitude to my co-Supervisor Prof. Pierre Langlois. Apart form research, his pragmatic approach to solve problems, fast context-switching and thinking in a clutter-free manner are some of the things I deeply admire and wish to emulate. Apart from my supervisors, Ahmed has always been my mainstay at Polytechnique to discuss any topic under the sun from research to philosophy. The weekly meetings with him was something I cherished and looked forward to.

I would like to thank Roberto and Federico for their support and guidance during the initial days of my stay in Montréal. The laboratory wouldn't have been the same without Alex and Hossein. It was great work alongside them.

I would like to thank my friends who were a second family in Montreal- Aryan, Ajin, Arna, Pratap, Komal and Irfan.

Last, but not the least, I would like to my parent for their sacrifices, their belief in me and also for being with me in every step and endeavour I take.

## RÉSUMÉ

Le succès des réseaux de neurones dans la classification des images a inspiré diverses implémentations matérielles sur des systèmes embarqués telles que des FPGAs, des processeurs embarqués et des unités de traitement graphiques. Ces systèmes sont souvent limités en termes de puissance. Toutefois, les réseaux de neurones consomment énormément à travers les opérations de multiplication/accumulation et des accès mémoire pour la récupération des poids. La quantification et l'élagage ont été proposés pour résoudre ce problème. Bien que efficaces, ces techniques ne prennent pas en compte l'architecture sous-jacente du matériel utilisé. Dans ce travail, nous proposons une implémentation économe en énergie, basée sur une table de vérité, d'un neurone binaire sur des systèmes embarqués à ressources limitées. Une approche d'arbre de décision modifiée constitue le fondement de la mise en œuvre proposée dans le domaine binaire. Un accès de LUT consomme beaucoup moins d'énergie que l'opération équivalente de multiplication/accumulation qu'il remplace. De plus, l'algorithme modifié de l'arbre de décision élimine le besoin d'accéder à la mémoire. Nous avons utilisé les neurones binaires proposés pour mettre en œuvre la couche de classification de réseaux utilisés pour la résolution des jeux de données MNIST, SVHN et CIFAR-10, avec des résultats presque à la pointe de la technologie. La réduction de puissance pour la couche de classification atteint trois ordres de grandeur pour l'ensemble de données MNIST et cinq ordres de grandeur pour les ensembles de données SVHN et CIFAR-10.

### ABSTRACT

The success of neural networks in image classification has inspired various hardware implementations on embedded platforms such as Field Programmable Gate Arrays, embedded processors and Graphical Processing Units. These embedded platforms are constrained in terms of power, which is mainly consumed by the Multiply Accumulate operations and the memory accesses for weight fetching. Quantization and pruning have been proposed to address this issue. Though effective, these techniques do not take into account the underlying architecture of the embedded hardware. In this work, we propose PoET-BiN, a Look-Up Table based power efficient implementation on resource constrained embedded devices. A modified Decision Tree approach forms the backbone of the proposed implementation in the binary domain. A LUT access consumes far less power than the equivalent Multiply Accumulate operation it replaces, and the modified Decision Tree algorithm eliminates the need for memory accesses. We applied the PoET-BiN architecture to implement the classification layers of networks trained on MNIST, SVHN and CIFAR-10 datasets, with near state-of-the art results. The energy reduction for the classifier portion reaches up to six orders of magnitude compared to a floating point implementations and up to three orders of magnitude when compared to recent binary quantized neural networks.

# TABLE OF CONTENTS

| DEDIC  | ATION                                                                                                                                                | ii         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| ACKNO  | DWLEDGEMENTS                                                                                                                                         | v          |

| RÉSUM  | ſÉ                                                                                                                                                   | v          |

| ABSTR  | ACT v                                                                                                                                                | <i>'</i> i |

| TABLE  | OF CONTENTS vi                                                                                                                                       | ii         |

| LIST O | F TABLES                                                                                                                                             | X          |

| LIST O | F FIGURES                                                                                                                                            | х          |

| LIST O | F SYMBOLS AND ACRONYMS                                                                                                                               | ci         |

| CHAPT  | TER 1 INTRODUCTION                                                                                                                                   | 1          |

| CHAPT  |                                                                                                                                                      | 5          |

| 2.1    |                                                                                                                                                      | 5          |

| 2.2    | Fully connected layer                                                                                                                                | 6          |

| 2.3    | Convolutional neural networks                                                                                                                        | 7          |

| 2.4    | Training neural networks                                                                                                                             | 8          |

| 2.5    | Inference of neural networks                                                                                                                         | 9          |

| CHAPT  |                                                                                                                                                      | 1          |

| 3.1    | Algorithm level modifications                                                                                                                        | 1          |

|        | 3.1.1 Quantization $\ldots \ldots 1$                      | 1          |

|        | 3.1.2 Pruning $\ldots \ldots \ldots$ | 4          |

|        | 3.1.3 Decision Trees                                                                                                                                 | 5          |

| 3.2    | Hardware implementation of neural networks                                                                                                           | 9          |

| CHAPT  |                                                                                                                                                      | 4          |

| 4.1    | Multi-level RINC architecture                                                                                                                        | 4          |

|        | 4.1.1 RINC-0 : Modified Decision Tree algorithm                                                                                                      | 4          |

|        | 4.1.2 RINC-1: Boosting the MAT units                                                                                                                 | 9          |

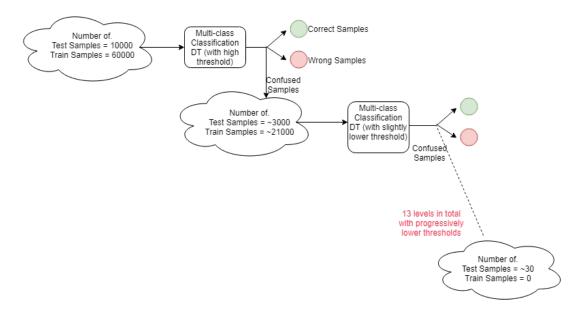

|       | 4.1.3  | RINC-L: Hierarchical Adaboost algorithm                                | 32 |

|-------|--------|------------------------------------------------------------------------|----|

| 4.2   | Binary | to multiclass classification                                           | 35 |

|       | 4.2.1  | Replacing the hidden layers                                            | 35 |

|       | 4.2.2  | Sparsely connected output layer                                        | 37 |

| 4.3   | Parser | to generate VHDL code                                                  | 37 |

| СНАРТ | ER 5   | EXPERIMENTAL SETUP, RESULTS AND DISCUSSIONS                            | 41 |

| 5.1   | Experi | mental setup                                                           | 41 |

|       | 5.1.1  | MNIST                                                                  | 42 |

|       | 5.1.2  | CIFAR-10                                                               | 42 |

|       | 5.1.3  | SVHN                                                                   | 43 |

| 5.2   | Result | s and Discussions                                                      | 43 |

|       | 5.2.1  | Classification accuracy                                                | 43 |

|       | 5.2.2  | Power                                                                  | 46 |

|       | 5.2.3  | Latency and Area                                                       | 49 |

|       | 5.2.4  | Simulation results                                                     | 51 |

| СНАРТ | ER 6   | CONCEPTION OF PoET-Bin                                                 | 54 |

| 6.1   | Attem  | pt 1: Accelerating the Inference Phase in Ternary Convolutional Neural |    |

|       | Netwo  | rks using Configurable Processors                                      | 54 |

| 6.2   | Attem  | pt 2: Decision Trees and Adaboost                                      | 54 |

| 6.3   | Attem  | pt 3: Conception of the PoET-BiN architecture                          | 55 |

| СНАРТ | ER 7   | CONCLUSION                                                             | 61 |

| 7.1   | Limita | tions                                                                  | 62 |

| 7.2   | Future | Research                                                               | 62 |

| REFER | ENCES  | 3                                                                      | 63 |

# LIST OF TABLES

| 3.1  | FPGA implementation comparisons                                                    | 23 |

|------|------------------------------------------------------------------------------------|----|

| 5.1  | Network architecture                                                               | 42 |

| 5.2  | Overall classification accuracy on MNIST, CIFAR-10 and SVHN dataset                | 43 |

| 5.3  | Comparison with other techniques                                                   | 44 |

| 5.4  | Comparison with other works in the literature $\ldots \ldots \ldots \ldots \ldots$ | 45 |

| 5.5  | RINC power results                                                                 | 46 |

| 5.6  | Single arithmetic operation power results                                          | 47 |

| 5.7  | Total arithmetic operations                                                        | 47 |

| 5.8  | Energy consumption                                                                 | 49 |

| 5.9  | Implementation results                                                             | 50 |

| 5.10 | Hardware implementation comparisons                                                | 53 |

| 6.1  | Accuracy on MNIST                                                                  | 56 |

| 6.2  | Comparisons of various MAC operation grouping technique in Adaboost                | 60 |

|      |                                                                                    |    |

# LIST OF FIGURES

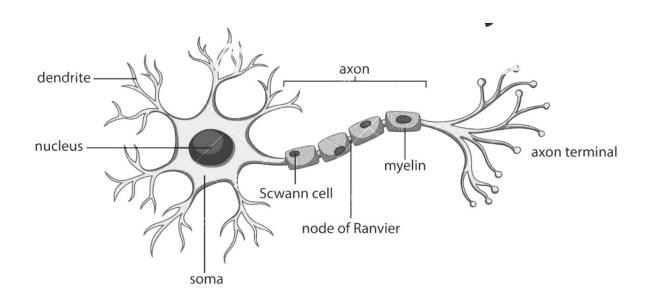

| 2.1 | Neuron structure in human brain [Image source]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

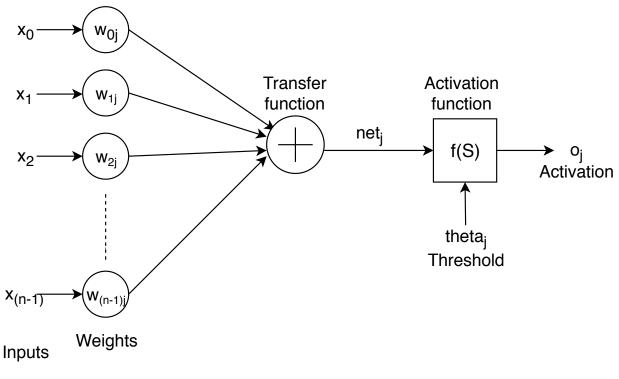

| 2.2 | Artificial neuron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6  |

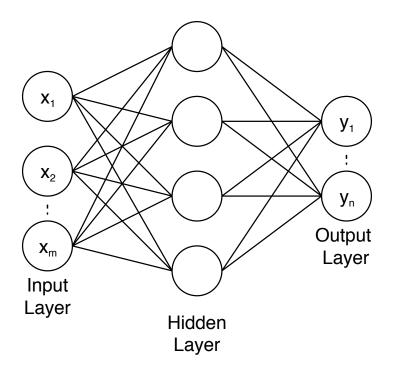

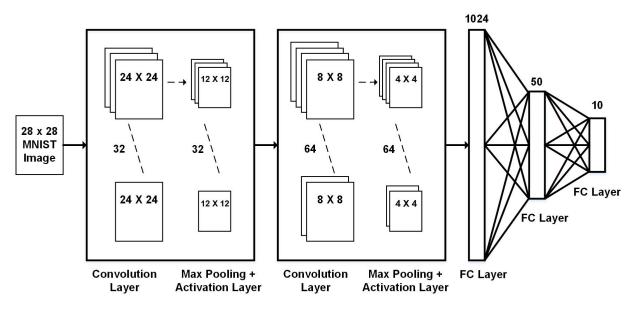

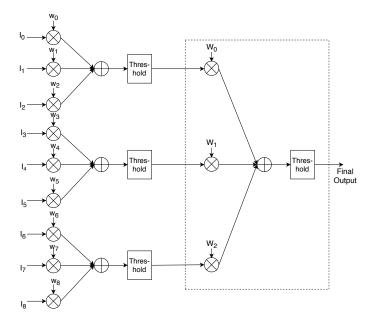

| 2.3 | Fully connected layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7  |

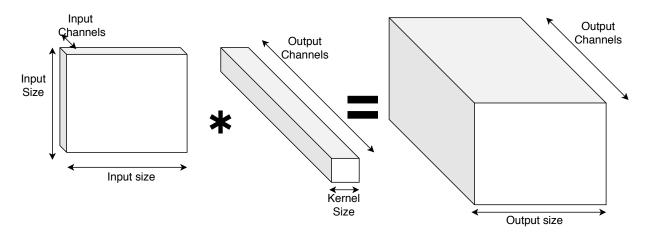

| 2.4 | Convolutional layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8  |

| 2.5 | LeNet CNN architecture (Chidambaram et al.,2018)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9  |

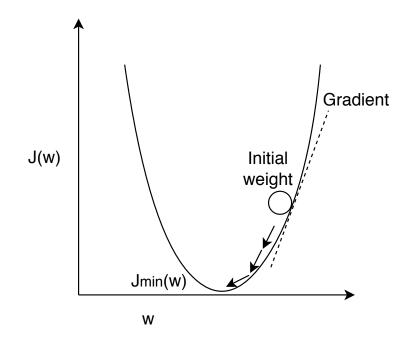

| 2.6 | Gradient descent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 |

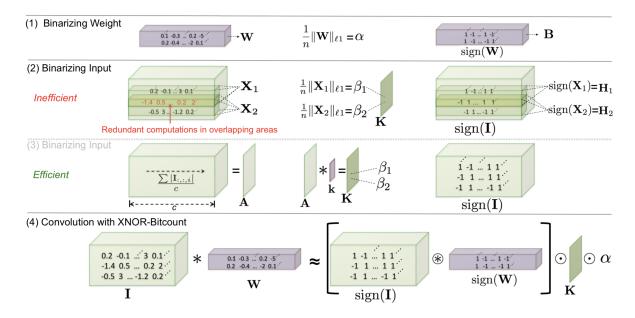

| 3.1 | XNORNet (Rastegari et al., 2016) [With Permission] $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13 |

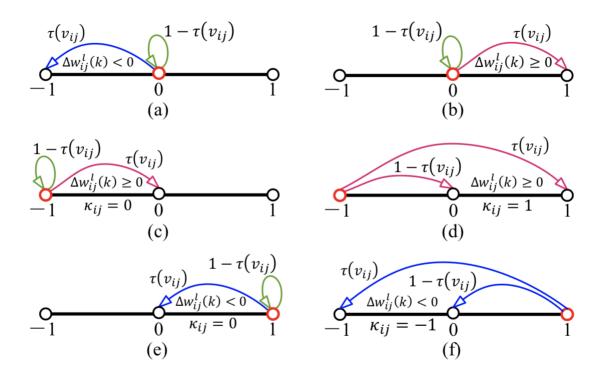

| 3.2 | Gated-XNOR Weight Update (Deng et al., 2018) [With Permission] $% \left[ \left( {{{\rm{A}}} \right)_{\rm{A}} \right] = \left[ {{{\rm{A}}} \right]_{\rm{A}} \left[ {{{\rm{A}}} \left[ {{{\rm{A}}} \right]_{\rm{A}} \left[ {{{\rm{A}}} \right]_{\rm{A}} \left[ {{{\rm{A}}} \left[ {{{\rm{A}}} \right]_{\rm{A}} \left[ {{{\rm{A}}} \right]_{\rm{A}} \left[ {{{\rm{A}}} \right]_{\rm{A}} \left[ {{{\rm{A}}} \left[ {{{\rm{A}}} \left[ {{{\rm{A}}} \left[ {{$ | 15 |

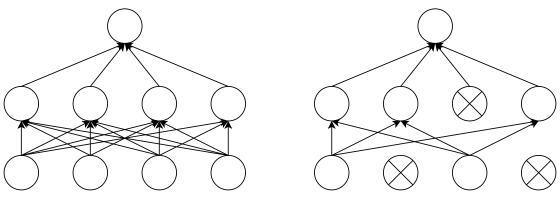

| 3.3 | Pruned neural networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15 |

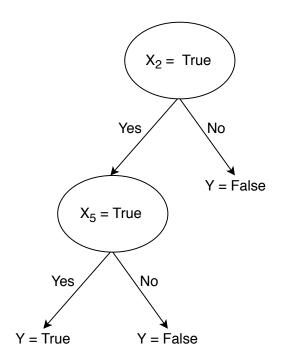

| 3.4 | Basic decision tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16 |

| 3.5 | POLYBiNN (Abdelsalam et al., 2018) [©, 2018 IEEE]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17 |

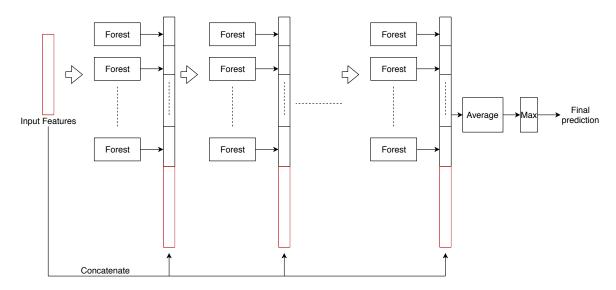

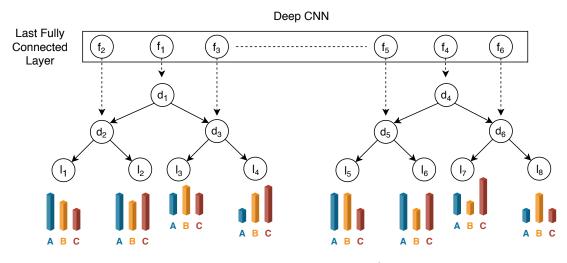

| 3.6 | Deep Forest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17 |

| 3.7 | Deep neural decision forest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

| 3.8 | FINN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20 |

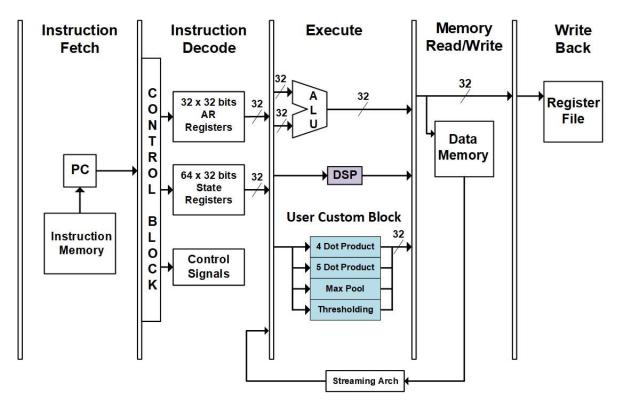

| 3.9 | Vector processor (Chidambaram et al., 2018)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21 |

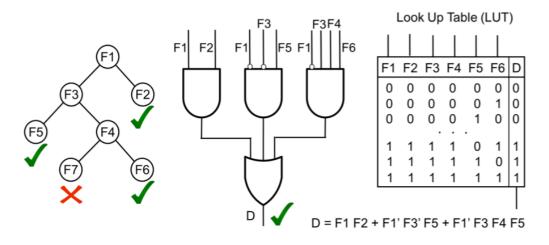

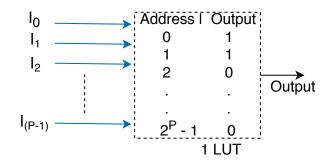

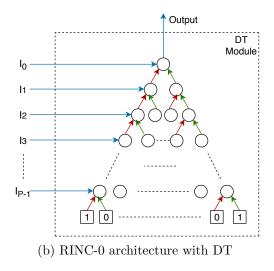

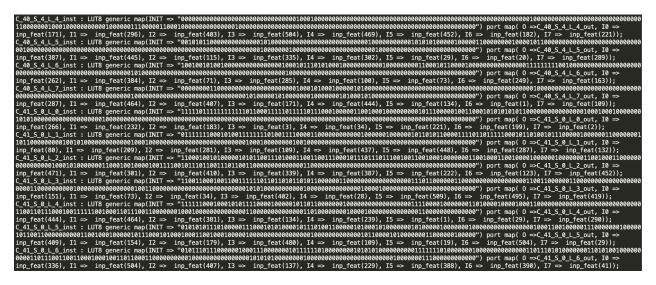

| 4.1 | LUT and its equivalent DT $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27 |

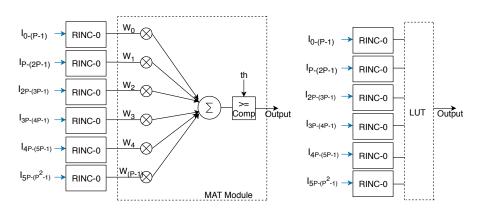

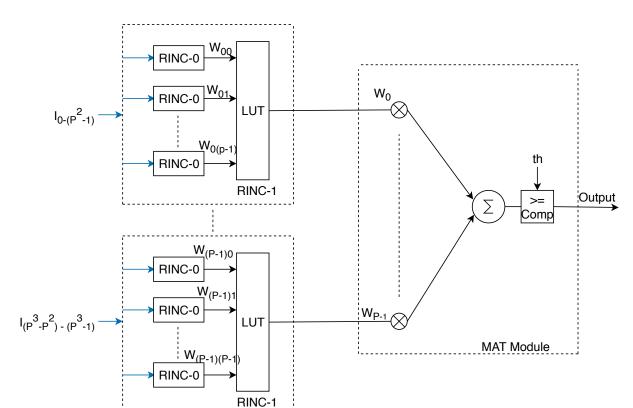

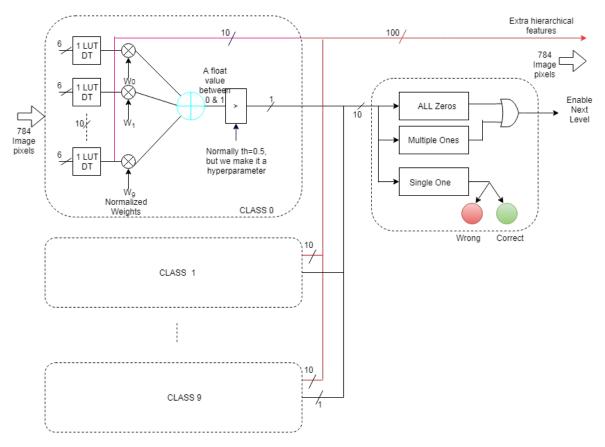

| 4.2 | RINC-1 architecture with $p=6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

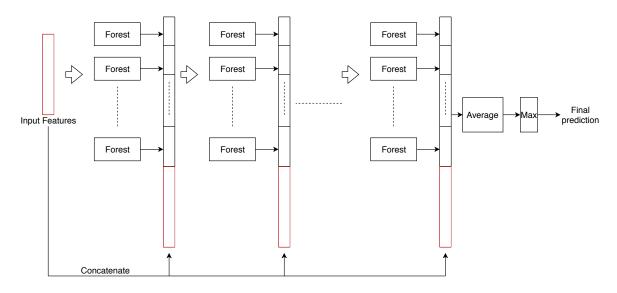

| 4.3 | RINC-2 architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32 |

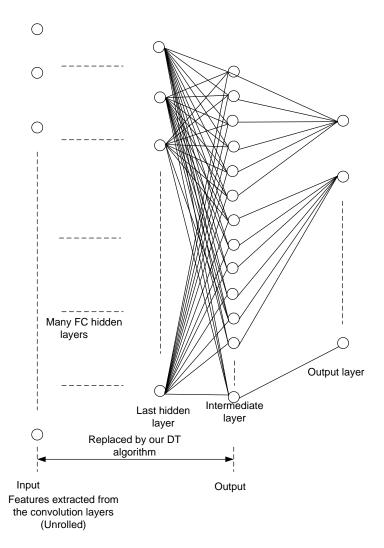

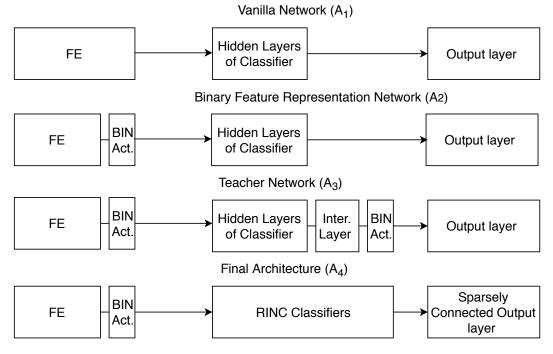

| 4.4 | Intermediate layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36 |

| 5.1 | Overall work flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41 |