## POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

## CPU utilization improvement of multiple-core processors through cache management and task scheduling

## MAHDI MORADMAND BADIE

Département de génie électrique

Mémoire présenté en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* Génie électrique

Août 2019

© Mahdi Moradmand Badie, 2019.

# POLYTECHNIQUE MONTRÉAL

affiliée à l'Université de Montréal

Ce mémoire intitulé :

CPU utilization improvement of multiple-core processors through cache management and task scheduling

présenté par **Mahdi MORADMAND BADIE** en vue de l'obtention du diplôme de *Maîtrise ès sciences appliquées* a été dûment accepté par le jury d'examen constitué de :

Guchuan ZHU, président Yvon SAVARIA, membre et directeur de recherche Jean-Pierre DAVID, membre et codirecteur de recherche François LEDUC-PRIMEAU, membre

### ACKNOWLEDGEMENTS

I would like to express my deep-felt gratitude to my supervisor, Prof. Yvon Savaria, and special thanks to my co-supervisor Prof. Jean-Pierre David, in the Department of Electrical Engineering at Polytechnique Montréal in Canada, for their advice, encouragement, enduring patience and support.

Additionally, I would like to express my appreciation to Professor Guchuan Zhu in the Department of Electrical Engineering as a leader of our project, for his support and encouragement. Also I want to say thanks a lot Professor François Leduc-Primeau for their time and effort putting on the evaluation of my thesis. Also I just wanted to say thanks to my team mates, Meng Li and Michel Gemieux, for their helps contributions and collaborations that providing me the means to complete my degree.

I would like to thanks Huawei Technologies Canada Co. Ltd and of the Natural Sciences and Engineering Research Council of Canada for their financial contributions in support of this project.

And finally, I wish to express my love and gratitude to my wife; for her understanding and endless love, through the duration of my studies.

### RÉSUMÉ

De nos jours, les architectures multicœurs et multiprocesseurs sont largement utilisées dans les centres de données. Une telle utilisation fournit les performances requises pour diverses tâches, telles que le C-RAN(accès radio par info-nuagique). Le traitement du signal sans fil en bande de base(wireless baseband) pour les normes 4G et 5G désigne un ensemble de tâches qui doivent être exécutées dans un intervalle de temps spécifique. Par exemple, la pile de liaison montante(up-link stack) pour une station de base 4G virtualisée a été décomposée en plus de 1000 tâches exécutables en 5 ms. Avec la 5G, la latence cible dans un scénario de bout en bout avec utilisation à latence très faible(ultra-low latency) est de 1 ms, tandis que la complexité de calcul est d'un à deux ordres de grandeur plus élevée que celle de la 4G. Le défi à surmonter c'est de répondre à ces objectifs en terme de complexité de traitement. Pour ce faire, il est crucial de caractériser la variabilité du temps de traitement par rapport aux caractéristiques du modèle de mémoire afin de garantir un temps de traitement donné dans les grappes d'ordinateurs classiques.

En outre, la planification des tâches sur les systèmes multicœurs reste un problème ouvert. Un tel problème doit être analysé afin d'utiliser pleinement la capacité de traitement d'un système multicoeur d'un système multicoeur et d'atteindre une faible latence. Afin de remédier à l'utilisation inefficace des cœurs de processeur, un schéma d'ordonnancement des tâches basé sur la mise en file d'attente, qui se focalise sur le calcul parallèle local, est proposé. Dans cette mémoire, on introduit la gestion multi-files pour la planification dynamique des tâches afin de cibler une utilisation complète à 100% des cœurs de CPU locaux pour des tâches d'entrée suffisantes. Plusieurs simulations sont faites pour vérifier le schéma de planification des tâches proposé. Les résultats rapportés confirment sa viabilité et son efficacité.

De plus, l'utilisation de la mémoire cache est l'une des principales sources de variabilité du temps d'exécution. En outre, une gestion inefficace de la mémoire cache s'avère problématique dans les systèmes avec WCET. Une approche efficace de gestion de la cache doit prendre en compte simultanément la planification des tâches et la gestion de la cache. L'approche optimale de gestion de la cache oblige de manière critique à prendre en compte les priorités associées à toutes les tâches; la connaissance de ces priorités est essentielle pour détecter et éviter les goulots d'étranglement dans le système. Cette approche affecte des ressources suffisantes à une tâche aussi critique pour faciliter une meilleure gestion. On commence par l'introduction d'une méthode de test simple, évolutive et configurable appelée un tableau de compteurs(Array of Counters), dont le but est de caractériser les variations de temps de traitement des architectures multicœurs. Cette technique aide à trouver les goulots d'étranglement. Un tel outil est utile pour l'élaboration d'un algorithme de gestion de la cache plus optimisé et amélioré.

L'objectif principal est d'améliorer l'utilisation des processeurs multicœurs en gérant mieux les ressources disponibles. De plus, les lacunes de l'approche dans la littérature sont brièvement décrites et étudiées. La puissance et l'efficacité de l'approche tableau de compteurs contribue à la recherche et à l'évaluation du WCET et à l'identification des goulots goulots d'étranglement.

#### ABSTRACT

Nowadays, modern multiprocessor and multicore architectures are widely used in data centers. Such usage provides the required performance for a variety of tasks, such as the C-RAN(Cloud-Radio-Access-Network). Wireless baseband signal processing for the 4G and 5G standards designates a range of tasks which must be executed in a specific time slot. For instance, the up-link stack of one 4G virtualized-base station was decomposed in more than 1000 tasks executable within 5ms. In 5G, the expected target latency for ultra-low latency use cases is 1ms in an end-to-end scenario; while the computational complexity is expected to be one to two orders of magnitude higher than that of 4G. It remains to be seen whether and how reaching such computational complexity is feasible. It is a crucial factor to characterize processing time variability besides features of memory model to guarantee a given processing time in mainstream computer clusters.

Besides, the task scheduling on multicore systems is still an open issue. Such a problem needs to be analyzed in order to fully utilize the processing capacity and to achieve low processing latency. In order to tackle the inefficient utilization of CPU cores, a queueing-based datadriven task scheduling scheme, which focuses on local parallel computing, is proposed in this thesis. This thesis introduces multi-queue management for dynamic task scheduling to target 100% utilization of local CPU cores for sufficient input tasks. Finally, the thesis entails several simulations to verify the proposed task scheduling scheme. The reported results confirm its viability and efficiency.

Moreover, cache memory usage is one of the primary sources of execution time variability. Besides, inefficient management of cache memory proves to be problematic in systems with which WCET(Worst-Case-Execution-Time) is of concern. An efficient cache managing approach needs to take both task scheduling and cache management into account simultaneously. Optimal cache-management imposes considering priorities associating with all tasks; the knowledge of such priorities is essential for detecting and avoiding system bottlenecks. Such approach proposes allocating adequate resources to such a critical task to facilitate better management. The work starts with the introduction of a simple, scalable, and configurable test method called an Array of Counters, the purpose of which is to characterize the processing time variations of multicore architectures. The technique helps to find system bottlenecks. Such help is conducive to a more optimized and enhanced cache-management algorithm.

The primary objective of this research is to enhance the utilization of multicore processors

by better managing the resources at hand. Also, the shortcomings of the state-of-the-art approaches are briefly discussed and investigated. The powerful and efficient method of Array of Counters contributes to finding and evaluating the WCET, aka bottlenecks.

## TABLE OF CONTENTS

| ACKNO  | OWLEDGEMENTS                                                                                                 | iii  |

|--------|--------------------------------------------------------------------------------------------------------------|------|

| RÉSUM  | ЛÉ                                                                                                           | iv   |

| ABSTR  | RACT                                                                                                         | vi   |

| TABLE  | C OF CONTENTS                                                                                                | viii |

| LIST O | DF TABLES                                                                                                    | х    |

| LIST O | PF FIGURES                                                                                                   | xi   |

| LIST O | PF SYMBOLS AND ABBREVIATIONS                                                                                 | xiii |

| LIST O | PF APPENDICES                                                                                                | xiv  |

| CHAPT  |                                                                                                              | 1    |

| 1.1    | Problem statement                                                                                            | 1    |

|        | 1.1.1 General definitions                                                                                    | 2    |

|        | 1.1.2 Data-centers and cloud computing                                                                       | 3    |

|        | 1.1.3 5G communication systems and C-RAN                                                                     | 5    |

| 1.2    | Research objectives and contributions                                                                        | 8    |

| 1.3    | Thesis outline                                                                                               | 9    |

| CHAPT  | FER 2    LITERATURE REVIEW                                                                                   | 10   |

| 2.1    | Introduction                                                                                                 | 10   |

| 2.2    | Processing time variability                                                                                  | 10   |

| 2.3    | Cache allocation technology                                                                                  | 11   |

|        | 2.3.1 Cache locking technique                                                                                | 11   |

|        | 2.3.2 Advantages and disadvantages of cache locking                                                          | 13   |

| 2.4    | Task scheduling                                                                                              | 15   |

| 2.5    | Conclusion                                                                                                   | 16   |

| CHAPT  |                                                                                                              | 18   |

| 3.1    | Array Of Counters(AOCs): A generic scalable micro-benchmark to character-<br>ize processing time variability | 18   |

|                                          | 3.1.1                                  | Best/Worst Case Execution Time(BCET/WCET) of a program                      | 20 |  |  |  |  |

|------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------|----|--|--|--|--|

|                                          | 3.1.2                                  | .2 AOCs as a micro-benchmark                                                |    |  |  |  |  |

| 3.2                                      | Multi-level dynamic cache management   |                                                                             |    |  |  |  |  |

| 3.3                                      | Experiments and results                |                                                                             |    |  |  |  |  |

| СНАРТ                                    | TER 4                                  | PRIORITY-QUEUE-BASED DATA-DRIVEN TASK SCHEDULING                            | 32 |  |  |  |  |

| 4.1                                      | Data-I                                 | Driven task scheduling                                                      | 32 |  |  |  |  |

|                                          | 4.1.1                                  | Queue-based data-driven task scheduling                                     | 32 |  |  |  |  |

|                                          | 4.1.2                                  | General definition                                                          | 35 |  |  |  |  |

|                                          | 4.1.3                                  | Task allocation based on DAG                                                | 35 |  |  |  |  |

|                                          | 4.1.4                                  | Optimized queue-based data-driven task scheduling                           | 38 |  |  |  |  |

|                                          | 4.1.5                                  | Software + Hardware task scheduling in data-driven concept                  | 43 |  |  |  |  |

| 4.2 Experiments and results              |                                        |                                                                             |    |  |  |  |  |

|                                          | 4.2.1                                  | The first implementation of data-driven task scheduling                     | 46 |  |  |  |  |

|                                          | 4.2.2                                  | The optimized version of data-driven task scheduling $\ldots \ldots \ldots$ | 47 |  |  |  |  |

| CHAPTER 5 CONCLUSION AND RECOMMENDATIONS |                                        | CONCLUSION AND RECOMMENDATIONS                                              | 68 |  |  |  |  |

| 5.1                                      | Advan                                  | cement of knowledge                                                         | 68 |  |  |  |  |

| 5.2                                      | Limits                                 | and constraints                                                             | 70 |  |  |  |  |

| 5.3                                      | 5.3 Future work and recommendations    |                                                                             |    |  |  |  |  |

|                                          | 5.3.1                                  | Multi-level dynamic cache locking                                           | 70 |  |  |  |  |

|                                          | 5.3.2                                  | Preemptive queuing-based data-driven task scheduling                        | 71 |  |  |  |  |

|                                          | 5.3.3                                  | Refine AOCs to improve its accuracy for processing time variations on       |    |  |  |  |  |

|                                          |                                        | multi-core processors                                                       | 71 |  |  |  |  |

| 5.4                                      | Perspective ideas for potential papers |                                                                             |    |  |  |  |  |

|                                          | 5.4.1                                  | Contention-free method to reduce processing time variations of cloud        |    |  |  |  |  |

|                                          |                                        | applications on multi-core processors                                       | 72 |  |  |  |  |

|                                          | 5.4.2                                  | Multi-level dynamic cache allocation to reduce worst case execution         |    |  |  |  |  |

|                                          |                                        | time in multi-core processors                                               | 72 |  |  |  |  |

|                                          | 5.4.3                                  | Local queuing-based data-driven task scheduling on multi-core system        | 72 |  |  |  |  |

| REFER                                    | ENCES                                  | 5                                                                           | 74 |  |  |  |  |

| APPEN                                    | DICES                                  |                                                                             | 78 |  |  |  |  |

## LIST OF TABLES

| Table 4.1 | Task Package Profile | 35 |

|-----------|----------------------|----|

| Table 4.2 | Data Package Profile | 35 |

| Table 4.3 | Task Grouping        | 36 |

## LIST OF FIGURES

| Figure 3.1  | CAT provides more cache space for high priorities applications                       | 22 |

|-------------|--------------------------------------------------------------------------------------|----|

| Figure 3.2  | Example of cache capacity bitmasks                                                   | 23 |

| Figure 3.3  | Multi-level dynamic cache locking.                                                   | 24 |

| Figure 3.4  | The general format of the gathered data, as processing time varies                   |    |

|             | according to different levels of cache and memory                                    | 27 |

| Figure 3.5  | Various results that characterize the impact of changing the size of the             |    |

|             | array for a variable number of active logical cores. For each curve, the             |    |

|             | dotted lines stand for best/worst processing time                                    | 28 |

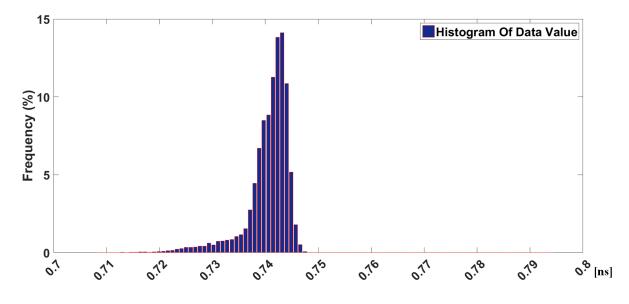

| Figure 3.6  | Representative histogram of the observed processing time<br>(1000 runs on            |    |

|             | 22 hyper-threaded cores for 1.35 MB memory block size                                | 29 |

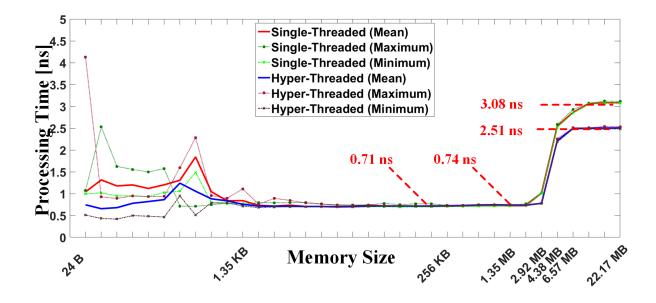

| Figure 3.7  | The mean, WCET and BCET in latency observed when executing in                        |    |

|             | hyper-threaded mode<br>(blue) vs. single-threaded mode<br>(red). $\ldots$ . $\ldots$ | 30 |

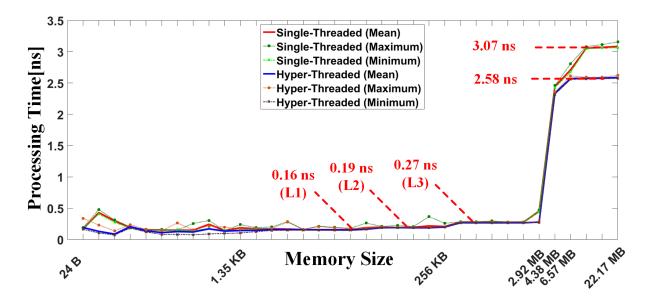

| Figure 3.8  | The latency of hyper-threaded core(blue) vs. single-threaded core(red)               |    |

|             | using AVX2 instructions                                                              | 31 |

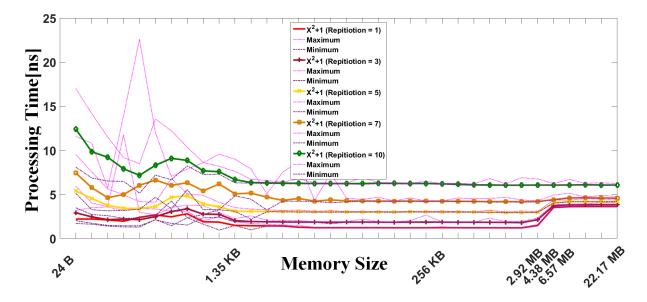

| Figure 3.9  | The latency of hyper-threaded core for the $x^2 + 1$ function with different         |    |

|             | repetition values                                                                    | 31 |

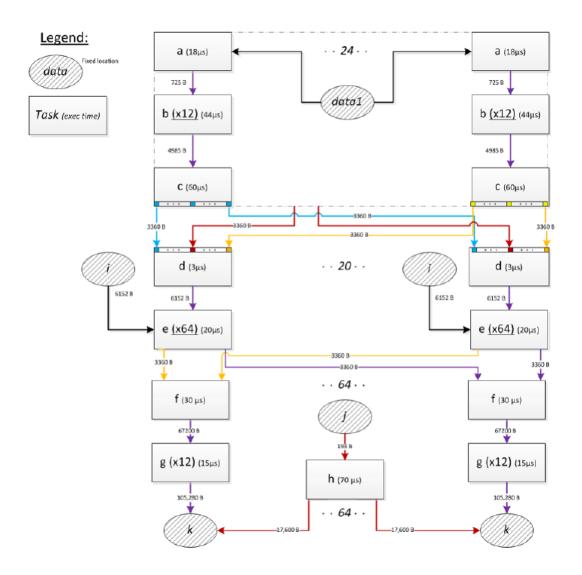

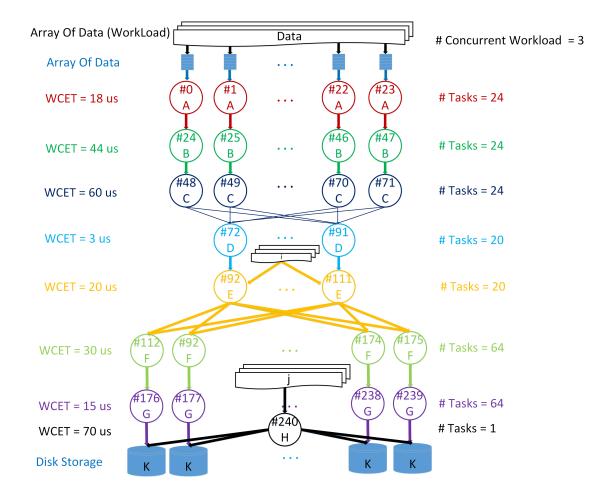

| Figure 4.1  | An example of real DAG from Huawei Co                                                | 33 |

| Figure 4.2  | Simplified DAG of Figure 4.1                                                         | 34 |

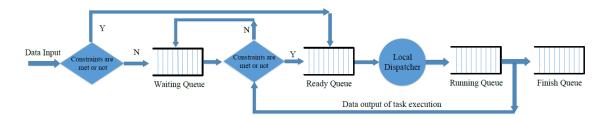

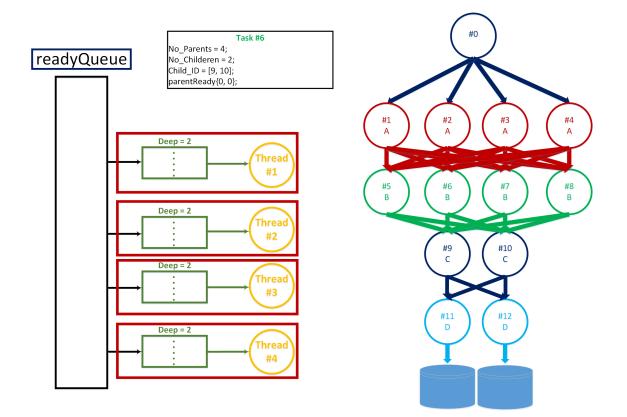

| Figure 4.3  | Queue-based data-driven task scheduling                                              | 37 |

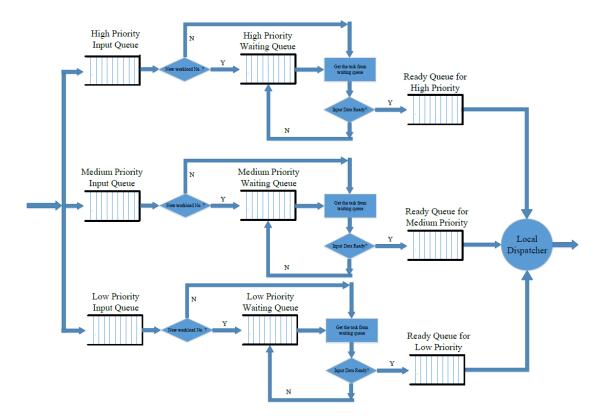

| Figure 4.4  | The structure of priority-based queue management in a local blade                    | 38 |

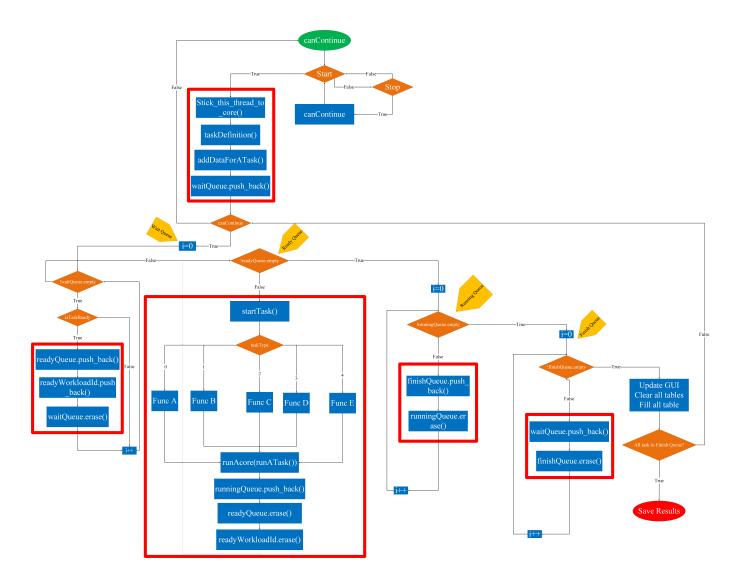

| Figure 4.5  | Flowchart of Quebe-based Data-Driven Task Scheduling                                 | 39 |

| Figure 4.6  | Example of optimized version for first version                                       | 40 |

| Figure 4.7  | addTask function parameters                                                          | 42 |

| Figure 4.8  | An example of initDag function with 13 tasks                                         | 43 |

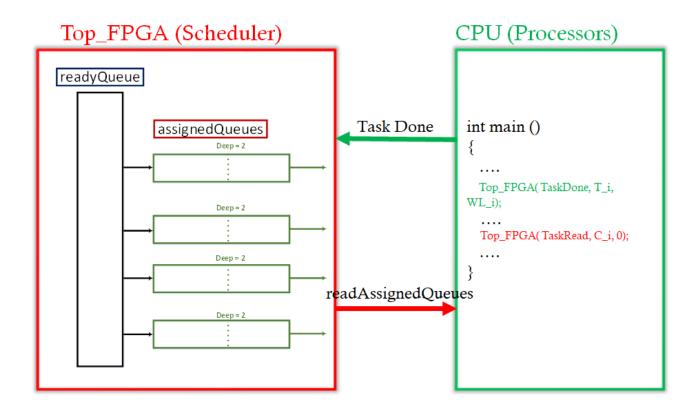

| Figure 4.9  | Software + Hardware Task Scheduling in the Data Driven Concept $% \mathcal{A}$ .     | 45 |

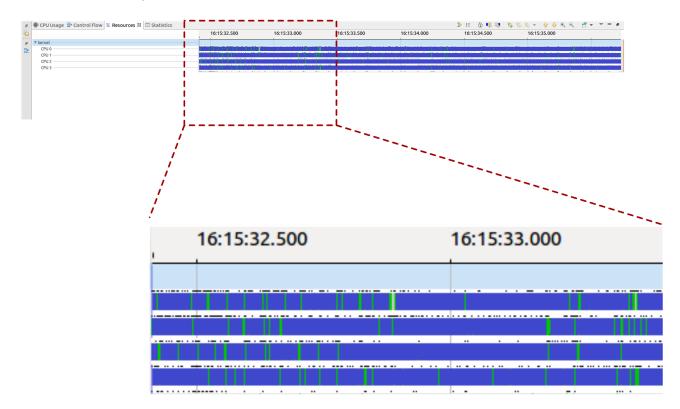

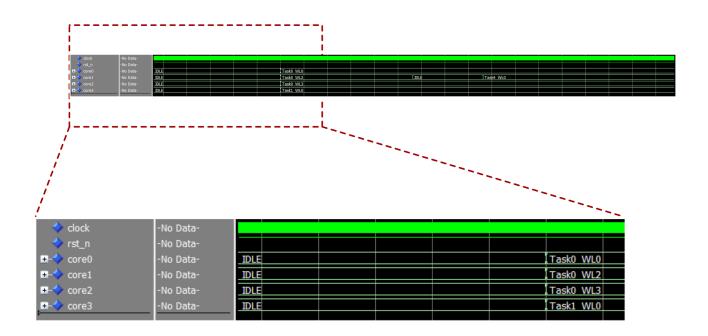

| Figure 4.10 | Core utilization as reported by LTTng, dark blue stands for busy state               |    |

|             | and green for wait/idle state. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 46 |

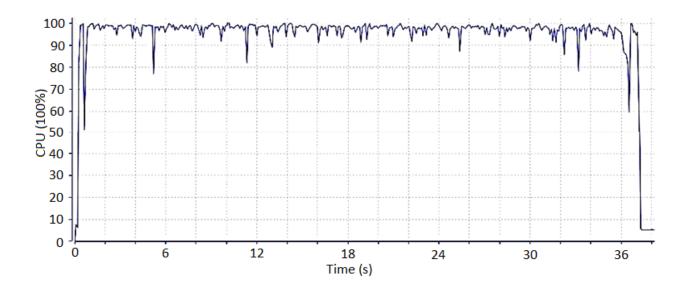

| Figure 4.11 | CPU usage of real DAG with total 24 workloads, 3 concurrent work-                    |    |

|             | loads, and 24 active cores                                                           | 47 |

| Figure 4.12 | Optimized version of Task Scheduling vs. The first version $\ . \ . \ .$             | 48 |

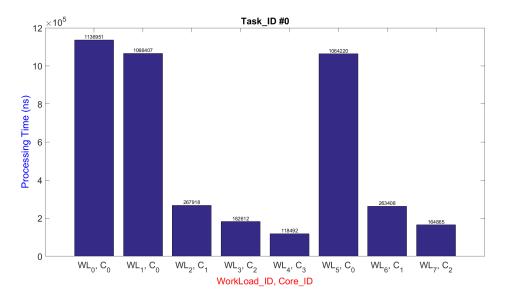

| Figure 4.13 | Results for Task #0                                                                  | 48 |

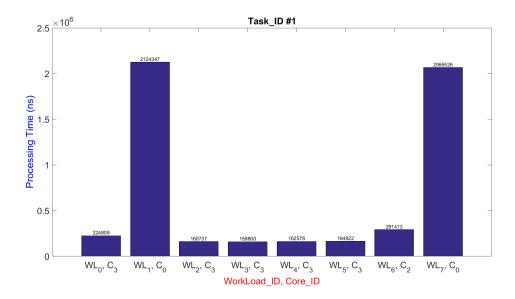

| Figure 4.14 | Results for Task #1                                                                  | 49 |

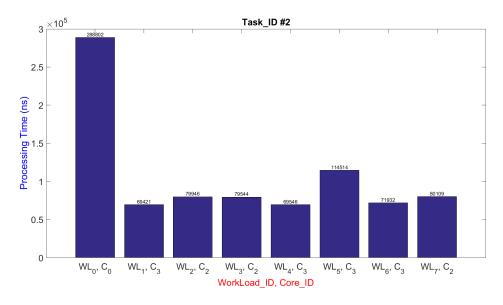

| Figure 4.15 | Results for Task #2                                                                  | 49 |

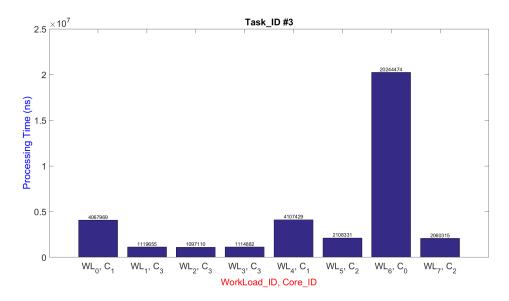

| Figure 4.16 | Results for Task #3                                                   | 50 |

|-------------|-----------------------------------------------------------------------|----|

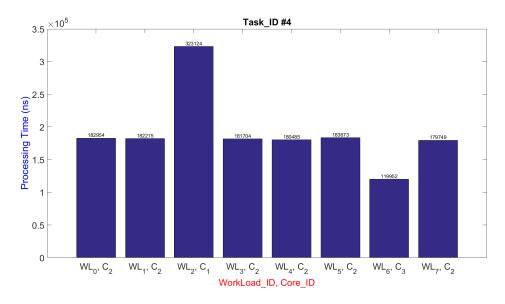

| Figure 4.17 | Results for Task #4                                                   | 50 |

| Figure 4.18 | Results for Task #5                                                   | 51 |

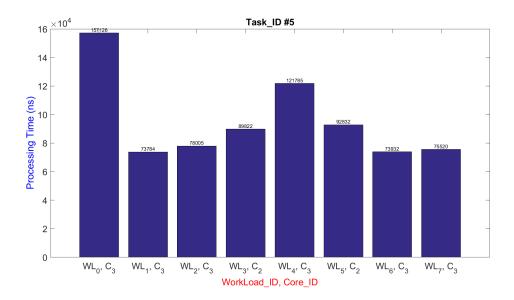

| Figure 4.19 | Results for Task $\#6.$                                               | 51 |

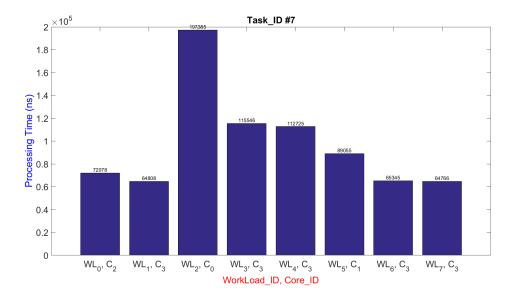

| Figure 4.20 | Results for Task $\#7$                                                | 52 |

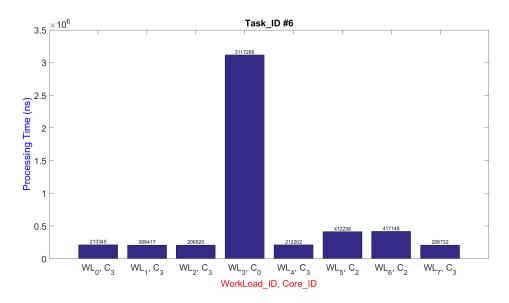

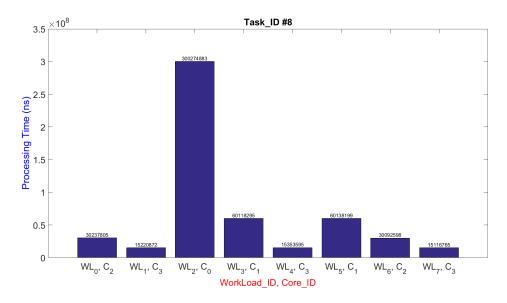

| Figure 4.21 | Results for Task #8                                                   | 52 |

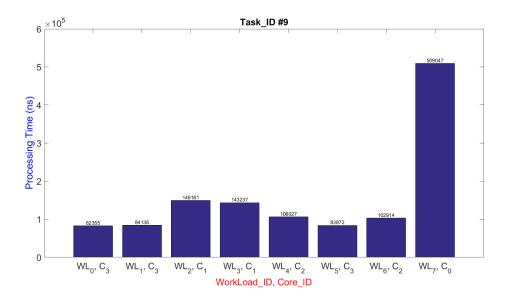

| Figure 4.22 | Results for Task #9                                                   | 53 |

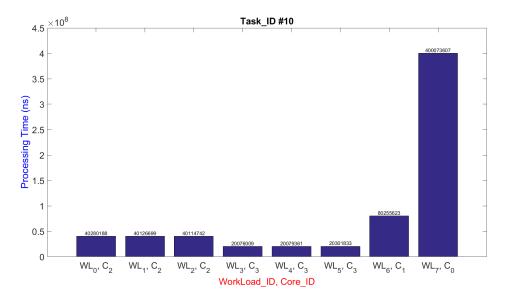

| Figure 4.23 | Results for Task #10                                                  | 53 |

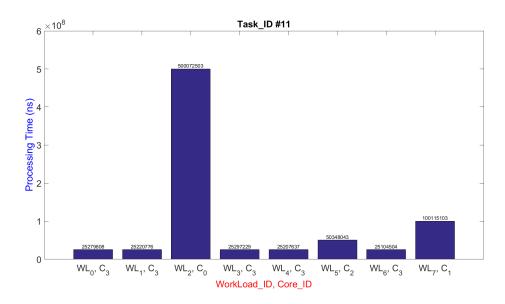

| Figure 4.24 | Results for Task #11                                                  | 54 |

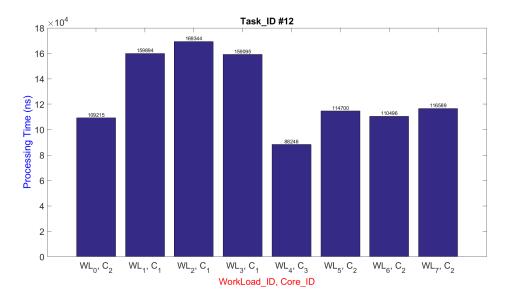

| Figure 4.25 | Results for Task #12                                                  | 54 |

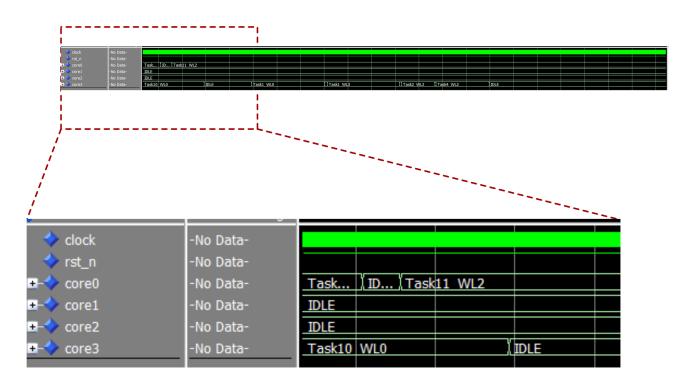

| Figure 4.26 | 1.Busy and Idle states, 4 workers and 4 workloads, from start to stop |    |

|             | $\operatorname{point.}$                                               | 59 |

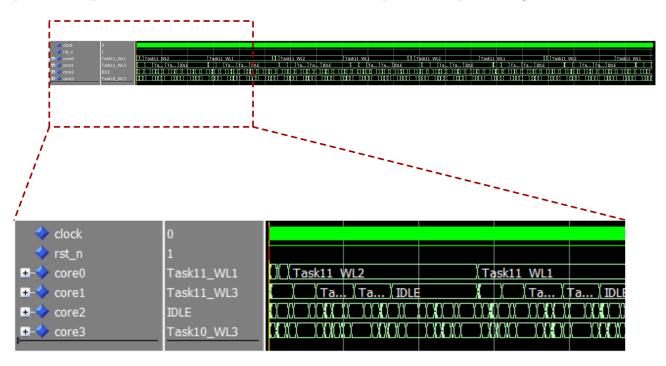

| Figure 4.27 | 2. Busy and Idle states, 4 workers and 4 workloads, start point       | 60 |

| Figure 4.28 | 3. Busy and idle states, 4 workers and 4 workloads, stop point        | 60 |

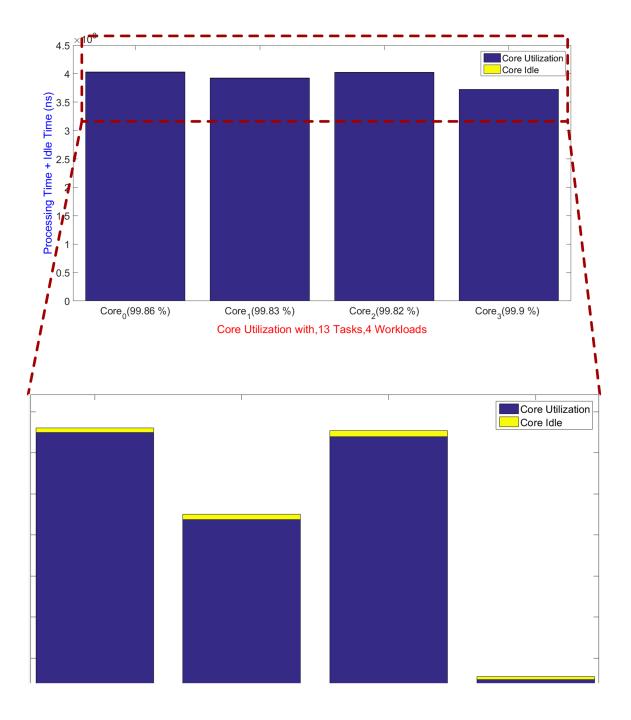

| Figure 4.29 | Core utilization with 13 Tasks, 4 workloads                           | 62 |

| Figure 4.30 | Core utilization with 13 Tasks, 4 workloads                           | 63 |

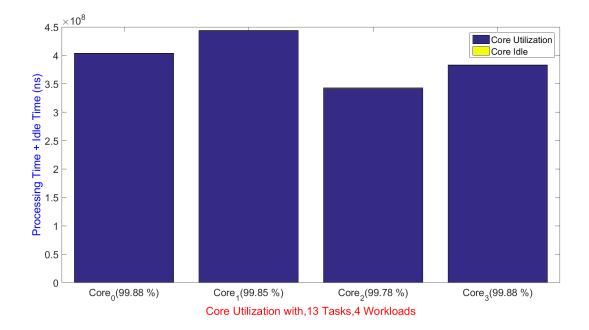

| Figure 4.31 | Core utilization with 13 Tasks, 7 workloads                           | 63 |

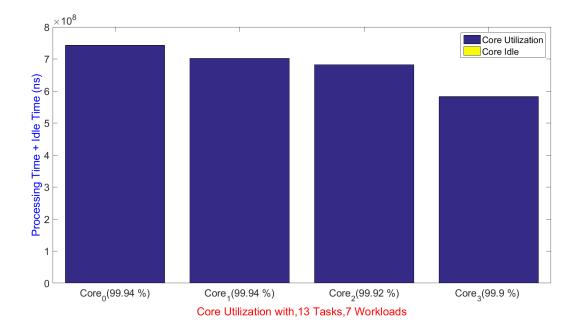

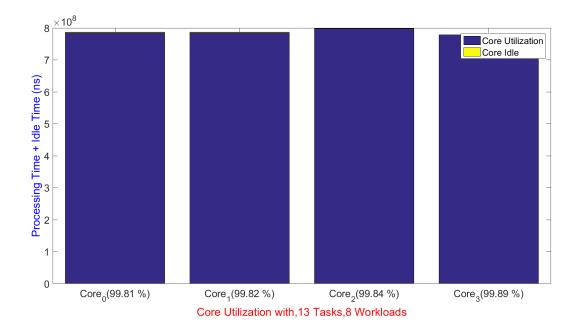

| Figure 4.32 | Core utilization with 13 Tasks, 8 workloads                           | 64 |

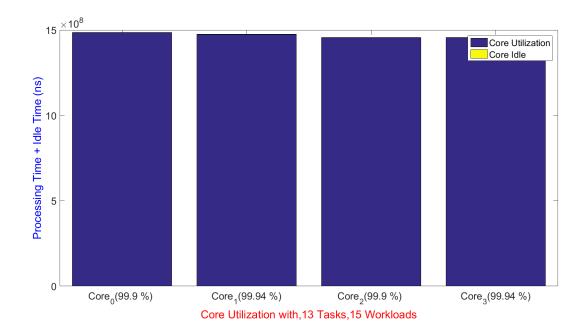

| Figure 4.33 | Core utilization with 13 Tasks, 15 workloads                          | 64 |

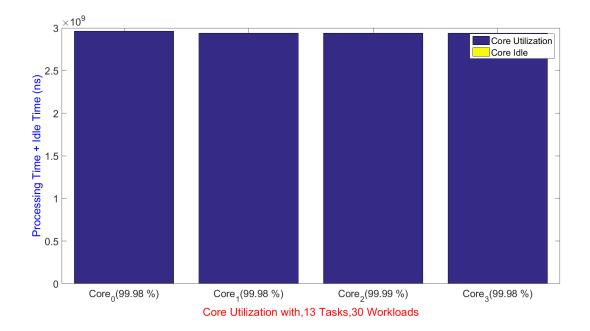

| Figure 4.34 | Core utilization with 13 Tasks, 30 workloads                          | 65 |

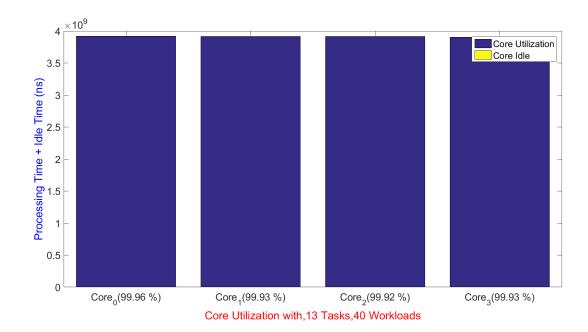

| Figure 4.35 | Core utilization with 13 Tasks, 40 workloads                          | 65 |

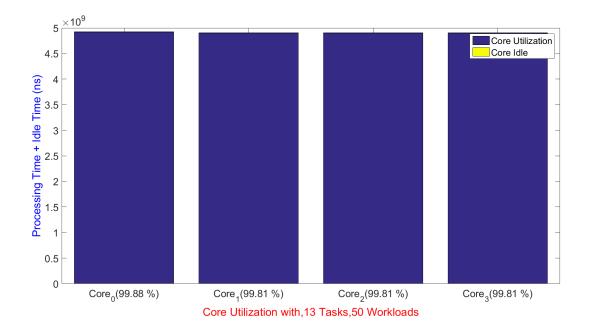

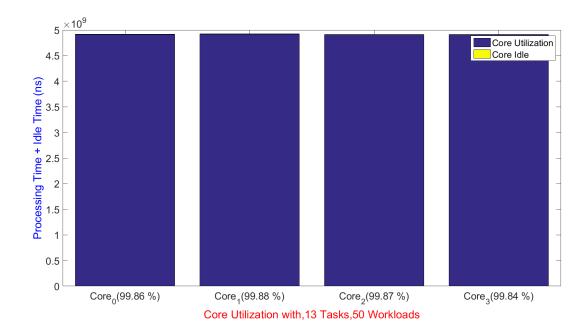

| Figure 4.36 | Core utilization with 13 Tasks, 50 workloads                          | 66 |

| Figure 4.37 | Core utilization with 13 Tasks, 50 workloads                          | 66 |

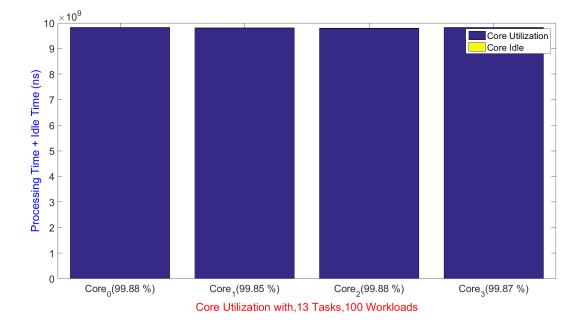

| Figure 4.38 | Core utilization with 13 Tasks, 100 workloads                         | 67 |

| Figure A.1  | Adding Directives.                                                    | 80 |

| Figure A.2  | Solution Configuration.                                               | 81 |

| Figure A.3  | Latency Constraints.                                                  | 82 |

| Figure A.4  | Loop Unrolling                                                        | 82 |

| Figure A.5  | Loop Flattening.                                                      | 83 |

| Figure A.6  | Loop Merging                                                          | 83 |

| Figure A.7  | Dataflow Optimization Command.                                        | 84 |

## LIST OF SYMBOLS AND ABBREVIATIONS

| C-RAN  | Cloud-Radio Access Network             |

|--------|----------------------------------------|

| GSM    | Global System for Mobile communication |

|        | •                                      |

| LTE    | Long-Term Evolution                    |

| FPGA   | Field Programmable Gate Array          |

| IT     | Information Technology                 |

| IoT    | Internet of Things                     |

| BTS    | Base Transceiver Station               |

| DAG    | Directed Acyclic Graph                 |

| OS     | Operating System                       |

| AOC's  | Array Of Counters                      |

| LIC    | Low-Interference Configuration         |

| HIC    | High-Interference Configuration        |

| WCET   | Worst-Case Execution Time              |

| BCET   | Best-Case Execution Time               |

| PTC    | Processing Time Characterization       |

| PTV    | Processing Time Variation              |

| CAT    | Cache Allocation Technology            |

| CAM    | Cache Allocation Management            |

| CL     | Cache Locking                          |

| SCL    | Static Cache Locking                   |

| DCL    | Dynamic Cache Locking                  |

| COS    | Class Of Services                      |

| SWCL   | Software-based Cache Locking           |

| HWCL   | Hardware-based Cache Locking           |

| MLDCA  | Multi-Level Dynamic Cache Allocation   |

| DPDK   | Data Plane Development Kit             |

| WL     | Work Load                              |

| IAOC's | Interference Array Of Counters         |

| LTTng  | Linux Trace Toolkit Next Generation    |

| HLS    | High-Level Synthesis                   |

| SOC    | System On the Chip                     |

| AVX    | Advanced Vector Extension              |

| SIMD   | Single-Instruction-Multiple-Data       |

|        |                                        |

## LIST OF APPENDICES

| Appendix A   | Introduction to        | Vivado and | Vivado HLS  | <br> | <br>78  |

|--------------|------------------------|------------|-------------|------|---------|

| rippondin ri | inter o a a contoir to | riraao ana | ritado iiio | <br> | <br>• • |

#### CHAPTER 1 INTRODUCTION

Nowadays, we are in a world surrounded by accessible information and technology. We need to constantly connect and want everyone of our move to be recorded, processed, analyzed and found in the "Cloud" [1]. Thus, this project is located in the cloud world, more precisely at the data-center level. We seek to improve the processing of tasks in a Cloud Radio Access Network(C-RAN) operating environment, focused on CPU utilization and timing deadline. To do this, we want to exploit the benefits of a data-driven task scheduling, characterizing processing time variability and cache management.

Better task scheduling as well as reducing the Worst-Case-Execution-Time(WCET) in the C-RAN context would allow a more efficient and adequate use of a computing clusters. This research aims to deploy systems that consume substantially less energy and for which the costs of installations are reduced, which can reduce negative impacts on the planet.

In this introduction we will first define the problem statement concepts associated with the research project documented by this thesis. Then, we will expose the general definition and the basic concepts such as data-center and cloud computing, 5G communication systems and C-RAN. Afterward, the different research objectives followed throughout this master's degree will be listed. Finally, the organization of the different chapters and the contents of this thesis will be summarized.

#### 1.1 Problem statement

Huawei's Radio Computing Architecture (RCA) team is actively working on various technologies related to C-RAN and it supports the research by providing the constraints of the LTE software stack and possibly other use cases. Huawei's research team (CRC, Canada Research Centre) is designing and developing a C-RAN prototype and Polytechnique worked closely with Huawei to characterize and improve the platform. This research is a joint Collaborative Research and Development(CRD) project financially supported by the Natural Sciences and Engineering Research Council of Canada. The main research goal of Huawei is to investigate new computing and communication architectures for C-RAN base station virtualization. In this regards, our problem statement consists of a two-step questioning. First, we want to study the impact of processing time variations not only to control them but also to reduce the WCET. Second, we ask ourselves which algorithm help us to increase the CPU utilization in order to get a maximum benefit of each active core. The research questions are:

- 1. What is the impact and source of resource utilization on the processing time variation and reducing the WCET?

- 2. Can we determine a scheduling algorithm to increase the CPU utilization for active cores?

### 1.1.1 General definitions

The number of cores on a chip increases significantly over time in modern real-time systems. Such increase translates into a corresponding increase in the complexity of the systems containing such chips. Besides, this increase results in a substantially-elevated number of tasks running on these cores. This mandates new management techniques to address the higher numbers of tasks and a higher complexity. On the one hand, the transition from uniprocessor to multiprocessors in real-time systems poses a challenge. Such a challenge, often, rises from synchronization limitation between different processors in the same or in different systems. It is evident that applying the same scheduling algorithms, similar to those used in uniprocessors, for multiprocessors undermines the performance. On the other hand, multicore processors dominate the commercial marketplace.

Applications and systems should use proper strategies concerning parallelism and functionality between cores to take maximum advantage of multicore processors technologies. In parallel computing, speed-up is generally achieved by running multiple more or less independent tasks simultaneously. Thus, a paradigm is required to represent the inter-task dependencies to utilize the computing resources efficiently.

In addition, the overall energy consumption of modern multiprocessors and multicores is considerable when they are idle. In many applications, the CPU's are idle much of the time, so power consumption when idle contributes significantly to overall system power usage. Task scheduling for multicore processors is one of the main factors determining the utilization of multicore processors. Modern task scheduling strategies in real-time systems mainly focus on uniprocessors, and some of these strategies cannot be generalized to multicore processors system efficiently. A task schedule model can often be described by a Directed Acyclic Graph(DAG). Because the DAG model is used to schedule tasks in multicore systems as well, DAGs play a central role in various proposed state-of-the-art algorithms. The DAG is a common model for task scheduling. It is a dominant model used in parallel computation. In general, a DAG model represents tasks as a graph with vertices representing dynamic functions, computation cost, edges between vertices representing dependencies, and communication cost. A critical path(the path in this study is a finite sequence of edges in a DAG that joins a sequence of distinct nodes) of a DAG represents the longest path concerning time consumption or computation cost.

### 1.1.2 Data-centers and cloud computing

Sometimes it is thought that data-centers and cloud are two terms that have exactly the same meaning, unless you are in a business that is related to these services. But these are two different words. the cloud is basically Internet based, but a data-center is based on physical location. In the following we briefly describe and discuss data-centers and cloud.

- Data-centers: The term data-center can be interpreted in several ways. First, the datacenter is housed in a company and IT professionals are hired to keep an eye on it and ensure its operation. Second, the data-center can be an offsite storage center where servers and other storage components are used to make the data stored physically and virtually available.

- Advantages: Organizations that have internal data-center access in their company have much less internet connectivity. As long as the local network is stable, data access is maintained. Remote storage also has its own advantages. If the primary location of the organization is affected by a fire, theft or flood, the company's second location remains completely intact and may be accessed.

- Disadvantages: Keeping your data in one place makes it easier for people who are not approved to access your data physically and virtually. Depending on your organization's budget, maintaining an organization-wide data-center can cost you a great deal.

- 2. Cloud-Computing: Before the advent of the Internet, there was no cloud computing and it could not exist. Today, as data speeds up in the world, some people predict that data-centers will decline in 2018 and cloud computing will grow. But what is Cloud? An online storage system that is used to parse and store your data in multiple locations. With Cloud, we always make sure there is a backup of our backups. The only way to eliminate the data that exists on the cloud is to destroy the Internet itself.

- Advantages: In today's world where communication is increasing day by day, Cloud is the ultimate solution. Services like Microsoft Office 365 and Google Drive have understood the importance of storing data online and moving to the full potential. Your organization can treat information the same way to make it always available. With online access, data will never be out of reach unless

you have internet access. The following are six common reasons organizations use cloud computing:

- (a) Cost: Cloud computing eliminates the cost of purchasing software, hardware, installing and deploying site data-centers or server racks (daily electricity to power and cool them) as well as the need for IT(Information Technology) experts to manage infrastructure, which speeds up work.

- (b) Speed: Most cloud computing services are self-service based on needs, so large amounts of computing resources can be provided in a matter of minutes and with just a few mouse clicks, a highly flexible business is possible and planning pressure is reduced.

- (c) World scale: One of the benefits of cloud computing services is the flexible scale. In the term cloud, this means that the exact amount of IT resources (such as more or less computing power, storage and bandwidth) are delivered right when needed and from a geographic location.

- (d) Productivity: Data-centers require a lot of racking, including hardware installation, software patching, and other day-to-day IT management tasks. Cloud computing eliminates the need for many of these tasks, so IT teams can spend a great deal of time on achieving important business goals.

- (e) Performance: The largest cloud computing services run on a global network of secure data-centers that are constantly upgraded to the latest, fast and efficient computing hardware version. This brings many advantages to a single data-center in a large company, which includes reducing network latency for apps and saving on a larger scale.

- (f) Reliability: Cloud computing makes data backup, data retrieval and business continuity easier and cheaper because it can reflect data elsewhere in the cloud provider's network.

- Disadvantages: Everything online is more vulnerable to cyber-attacks. It's very simple: a hacker tends to isolate a cloud storage rather than a data-center. Cloud is also less powerful than data-center because of its online nature. Compare Microsoft Office offline with Google Docs Online. Although Google Docs works well, it doesn't have the power of Microsoft Office that you can access offline.

In the areas of "Cloud Computing" and "High Performance Computing (HPC)", an efficient scheduling of the tasks of a process is essential in order to have the greatest possible performance. There are many literature on the subject of task scheduling, so what we can deduce, there is not a perfect solution that has the ability to solve all the problems. Thus, instead of trying to find the ultimate scheduling solution, designers rely on algorithms or strategies, which they choose based on the characteristics of the application.

#### 1.1.3 5G communication systems and C-RAN

Cloud-RAN or Centralized-RAN [2], is a new type of network architecture aimed at improving the systems currently used in mobile communications. C-RAN, is a mobile network architecture that is expected to be a cornerstone of 5G. C-RAN derives from traditional Radio Access Network (RAN), which was built with multiple BTS(Base Transceiver Station) across a region. A BTS, covers a small area at a time, and the system includes everything needed for wireless communications, from GSM(Global System for Mobile communication) 2G to 3G and afterwards from 3G to 4G LTE(Long-Term Evolution).

• What is the 5G?

The term 5G means "5<sup>th</sup> Generation"; this technology is the fifth generation of cellular communication. The design is so fast that it is much faster than 4G LTE technology(in 5G, the delay will be 4 milliseconds, which is much less than 20 milliseconds for 4G technology). The purpose of this new standard, however, is not merely to speed up the internet connection of smartphones. This standard will provide high-speed wireless internet everywhere and for everything including connected cars, smart homes and IoT(Internet of Things) tools.

- Why should we be eager for 5G?

- New Realities: The widespread release of 5G makes virtual reality and augmented reality more widely used. Augmented reality allows users to access a lot of information - for example, simply identify their route; identify price tags on products and bar-codes; Virtual reality, on the other hand, will provide a completely artificial perspective. An important point in using virtual reality and augmented reality is that both require very fast internet connection.

- 2. High Speed: Download speeds up to 150 Mbps at 4G, while 5G speed are 10 Gbps. It's so fast that you can download a full movie in just 4 seconds.

- 3. Quick Response: A few seconds delay is not so important when initializing online video, but this delay is unacceptable for a self-driving car(also known as an autonomous car, driver-less car, or robotic car), where milliseconds are important. Using 4G connectivity, a smart car takes approximately 15 to 20 milliseconds to notify the smart car behind it that it has compressed the brake; this amounts is 1 millisecond in a 5G con-

nection. Overall, as download speeds have increased dramatically, the initial delay in this type of communication has been eliminated as much as possible.

In the future, the smartphones and all devices with cellular connectivity will use the 5G standard instead of 4G LTE technology.

Modern multiprocessor and multi-core architectures are widely used providing needed performance for relative tasks, such as C-RAN. Wireless baseband signal processing for the 4G and 5G standards specifies many tasks that must be executed in a particular time slot, related to the duration of Radio Frames. In [3], the up-link stack of one 4G virtualized base station was decomposed in more than 1000 tasks, all of which are expected to end within 5 ms. In 5G, the considered target latency for ultra-low latency use cases is 1 ms in an end-to-end scenario, while the computational complexity is expected to be one to two orders of magnitude higher than that of 4G. The characterization of such systems is of particular concern because their characteristics are affected by variations of the access time to shared-resources in a way that can be detrimental to C-RAN. For instance, in multicore architectures with multi-task functions, the cores compete to access the memory resources and therefore could interfere with each other in doing so, resulting in sub-optimal performance.

Improving processor utilization in order to decrease the number of active cores is the main concern for modern multiprocessor and multi-core architectures in data-centers. We investigated a method that not only exploits the advantages of the existing algorithms, but, that also points out to new ideas for improving the task scheduling effects on multiprocessors. The original concept is proposed in [4],

and Professor David had a main role to finalize the optimized version. The author contributed to the validation of this method by implementing a prototype confirming its efficiency.

The concept of Directed Acyclic Graph(DAG) related to task scheduling approach, is used in this thesis to build a task model, such that task dependency, task priority, and task WCET can collectively form priority metrics. A priority-based task scheduling list can be set up from a comprehensive analysis and by calculating the priority for each task. Then queue-based and data-driven task allocation strategies are employed to map tasks to processors. Such strategies can improve processor utilization and timing predictability using cache management. Cache management leads to allocating a more significant part of a shared cache to high priority tasks.

The WCET is dramatically increased in modern multi-core processor due to interference caused by shared resources in software and in hardware. The obvious case in software is a preemptive OS(Operating System) scheduler that could interrupt task execution. On hardware side, shared cache, shared processing units or automatic power saving mode are hardware features that also impact the WCET. One of the most significant benefits of cache management(cache sharing) is enhancing core utilization. That is to say, when one core is not in a running state, the other core can access the whole or part of the shared cache. The benefit of cache sharing is more evident when hyper-threading used. In multicore processor cache sharing can increase efficiency and performance by reducing the number of cores needed to perform a task by improving the utilization of each core.

One of the main concerns of the Huawei team is having a framework that will target task execution in a reserved (locked) cache blocks and minimize cache misses in reserved cache memory area. The prototype computing platform uses Intel Xeon server processors. A hardware cache-locking mechanism is available in many multi-core processors but it is not yet available on the Intel server processor.

Cache locking is a useful strategy in real-time systems that improves timing predictability in cache management concept. Cache locking, if used properly, can enhance the performance of modern processors. Hence, cache locking is an essential technique not only as a means to mitigate execution time variation, but also as an a means to improve performance.

We propose a flexible priority-based multi-level dynamic cache locking approach in order to keep the balance between high and low priority tasks. Considering WCET and BCET, we reserve cache slots to given high-priority tasks. Obtaining near deterministic processing time of tasks executing on multicores processors with dynamic cache management, and reducing the WCET is the main goal of this approach.

Our strategy is a priority-based approach that incorporates a top view to decide on the number of locking slots at each entry-point and then selects the memory blocks to be locked for each level based on prioritized tasks. In effect, it is necessary to scheduled tasks to keep resource utilization balanced, which leads to shared resource management and dynamic cache locking. In effect, a task scheduling algorithm for multicore processors is critically needed in addition to an effective cache management strategy.

The relations between the two requirements of cache sharing and task scheduling is an important and challenging issue in improving utilization of multicore processors. The widespread adoption of multicore processors poses a few critical challenges both in research and in software development. Multicore CPUs will require a new generation of applications to fulfill and maximize their performance potential; applications that are specifically designed and implemented for multicore processors.

A significant challenge in cache management design is to limit the worst case processing

time and its variations. The main impact of cache misses in processing time is leading to processing time variability. If we could avoid provoking cache misses so we can control the processing time variability. Key resources that influence the processing time are the shared Last Level of Cache(LLC) and external memory. This sets a need to characterize the access time associated with each task that directly impacts processing time distribution and the WCET of relevant tasks.

We introduce a simple, scalable, and configurable test method called an Array of Counters(AOCs) to characterize the processing time variations of multicore architectures. The first idea of AOCs proposed by Professor David(thesis advisor) who had a significant role this method development and validation.

An AOCs is a tool to measure execution time variability. Besides, we should notice that AOCs have the potential of being extended to micro-benchmarks to measure and identify more memory parameters of CPUs in addition to those in the status quo version. We propose a novel procedure to characterize the impact of resource utilization and computation time of concurrent tasks on the processing time variation. The procedure leads to a better understanding of factors controlling processing time variations.

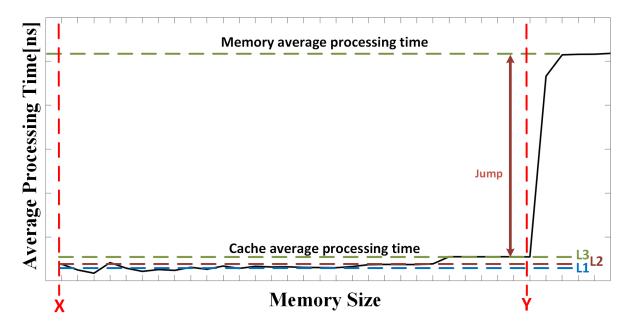

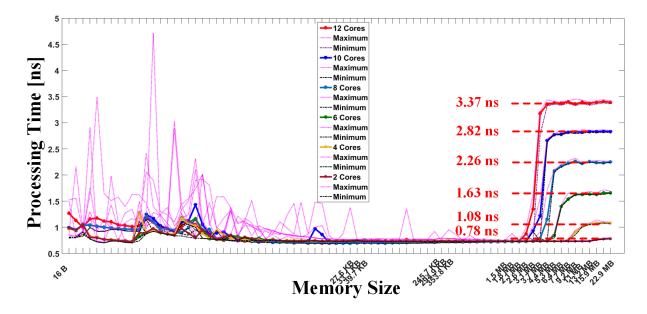

The proposed procedure consists of using AOCs where data and computation time can be set independently from each physical resource. The application is simple, scalable, and controllable, while producing measurable results concerning the average, maximum(WCET), and minimum(BCET) processing time obtained when using different levels of cache and memory. An AOCs is a set of 32-bit unsigned counters stored in various memory blocks. The array size is a parameter that can be changed to induce misses at every level of cache and memory. The simple atomic increment operation in the counters can also be replaced by a computing loop with no memory access to stretch the computation time or increase its complexity as desired.

#### **1.2** Research objectives and contributions

In this thesis, we introduce a method to improve the utilization of multicore processors considering two main objectives: cache management and task scheduling. This research focuses on these two objectives addressing the following three fundamental challenges:

• <u>Process-Time Variations</u>: By introducing a novel method, the Array Of Counters (AOCs), we can characterize the impact of resource utilization and computation time of concurrent tasks the processing time variations.

- <u>Resource Sharing</u>: Using dynamic cache management both the instruction and data cache are considered to keep a proper balance between high and low priority tasks.

- <u>Task Scheduling</u>: Validate a queue-based data-driven task scheduling algorithm to increase the utilization of cores in such a way to reduce the number of active cores in order to improve each core's utilization.

#### 1.3 Thesis outline

The outline of this thesis is as follows. In Chapter 2 the literature reviews will explain in more detail all the concepts used throughout this document while keeping a general view. In Chapter 3 will study the AOCs as a generic scalable micro-benchmark, and cache management strategy to enhance the WCET. In the Chapter 4 task scheduling will be studied. The main focus in this chapter is presenting the technique for designing task schedulers exploiting the data-driven concept. In addition, at the end of both Chapter 3 and Chapter 4, we will see the modalities of our proof of concept by presenting the plan, the test method and the experimental results obtained. Finally, we will summarize the work done throughout this thesis in Chapter 5, and discuss the results obtained. Several future works will be proposed at the end of this chapter.

#### CHAPTER 2 LITERATURE REVIEW

#### 2.1 Introduction

Here, we review factors that influence processing time variability, cache management, and the task scheduling problem. In each case, the opportunities, obstacles, and challenges are also briefly discussed. The primary objective of this research is to improve the utilization of multicore processors. Existing approaches are also prone to several shortcomings, which are briefly addressed in the study.

#### 2.2 Processing time variability

Processing Time Characterization(PTC) is a measurement method which can be used to identify the input/output behavior of systems with respect to their ability to meet some execution time targets. Via PTC, it is feasible to estimate the robustness of systems with respect to their ability to meet some timing. Also, PTC allows building models to describe the relationships between the parameters influencing processing time. Accurately measuring the effective process-time is the concern of a rich literature, [5]. Agarwal and Sharma [6] proposed a new method to compute effective process times from a data set. They estimated the mean, as well as the variance of given processing time for upcoming workloads. The results of this characterization process can be used to analyze and improve applications processing time [7,8].

There are different sources and types of variation for processing time. The two most important classes are controlled and uncontrolled variations. The conceptualization of controlled and uncontrolled sources of processing time variation is mandatory. The key difference between the two classes is whether or not the process of interest varies significantly over time or some other condition that itself may vary over time. A "steady stable" process is the one that runs in a consistent, robust, and predictable manner so that the processing time value is essentially constant, and therefore the variability is under control. On the contrary, If the process varies over time, it may lead to some unpredictable situation concerning the resources used by the process; thus a time-variant process falls into the uncontrolled variation category. Stable processes only exhibit controlled variations [5]. In order to compare the time variations of processes, we need a flexible and straightforward benchmark. The authors in [9] proposed an algorithm to characterize task memory access on multicore architectures which is hard to implement. To reduce the timing variation in [10], the authors propose a technique which uses some low-overhead instruction to measure cache and memory latency. Prior research such as store pre-fetching [11] have limited applicability and merely investigate several trivial sources of variations.

It is possible that some inter-cluster interference can be alleviated substantially. However, the potential risk for interference between cores on the same cluster running and using the shared resources still exists [12]. Using the Worst-Case-Execution-Time(WCET) approach that is independent of co-runner interference, which is used in [12], may affect the efficiency of the application. Besides, we should consider that real interference from co-runners depends on the scheduling technique at hand. Evaluating the WCET of the program may pose some challenges. Also, there is no guarantee to reproduce the maximum interference scenario even when we know everything about the setting of the system and of the application.

We propose a novel procedure, that can be considered as a type of microbenchmark, to characterize the impact of resource utilization and computation time of concurrent tasks on processing time variations. This procedure leads to better understanding of processing time variations particularly when a shared cache is involved. The proposed application is simple, scalable and controllable, while producing observable results with respect to the observed processing time obtained when using different levels of cache and memory. The main drawback of applications found in the current literature, is their complexity, lack of scalibility and controllability features.

#### 2.3 Cache allocation technology

Cache locking is a means to protect access to some or all instructions or data needed by multiprocessors sharing a cache. It can be useful to improve predictability in real-time systems so it can improve the performance of modern processors if implemented in a technically sound manner. Cache locking may improve the task execution performances, and as a result, it can help reduce task processing time variability. In this regards, non appropriate using of cache locking can cause processing time variations.

#### 2.3.1 Cache locking technique

Cache Allocation Technique(CAT) and Cache Locking(CL) are techniques that might be appropriate to all or a portion of the shared cache between processors. Many recent modern processors support cache locking, e.g., the one embedded in Intel Xeon E5-2650 V4. By choosing accurately the memory slots for locking, CAT can improve performance dramat-

ically. For instance, in the strategies proposed in [13, 14], the authors recommended two distinctive heuristic algorithms, line locking, and way locking, to improve the performance of the cache. They emphasize that CL is a an effective procedure for improving the processing time.

Cache locking methods can be grouped into two main classes, static and dynamic. In Static Cache Locking(SCL), the locked memory slots do not change during the execution time. So SCL is not a reasonable methodology when distinctive memory slots are fighting for a memory. Dynamic Cache Locking(DCL), as its name implies, can alleviate some restrictions observed with SCL. The DCL approach partitions a program into Classes of Service(COS) dynamically during processing time. DCL adjusts the locked contents at runtime, which improves the WCET in contrast with SCL. DCL gives better results as far as performance and flexibility yielded by SCL is concerned [15].

The classification of CL methods applies in both cases of software and hardware implementation. In which case they are called Software Cache Locking(SWCL) or Hardware Cache Locking(HWCL). SWCL focuses on theoretical algorithms and software coding implementation. By contrast, HWCL uses available features embedded on modern CPUs. Obviously, in HWCL, some software coding is needed, but the software complexity and implementation can reduce dramatically in comparison to SWCL.

Most existing CL strategies go for improving the WCET by utilizing SCL, as mentioned in [15]. A key issue is the simplicity of implementation of SCL versus DCL. SCL generally uses full CL, but full locking does not permit the unlocked cache slots to be shared. Not utilizing all the cache leads the under-exploited locality, which prompts a negative effect on the general WCET and can dramatically degrade performance [15]. Besides, with large programs, utilizing SCL on a small cache can lead to increased processing time.

Most of the proposed CL approaches concentrates on instruction caches rather than on data caches [16, 17], because usually during execution, the instructions remain fixed, yet the data may vary from one cycle to another [18, 19]. So applying CL for data is a more complicated problem; in the same way the majority of the work done does not address data cache, as mentioned in [15].

In the instruction cache, in order to reduce the WCET execution, Puaut and Arnaud [20] proposed a method which relies on partitioning the regions for the ordered tasks just for the instruction cache. In spite of the fact that their methodology decreased the WCET, it expanded the loading cost. In [21], Ding et al. proposed the space-share cache management approach, which assigns a part of the cache based on to task necessities and priority. Even though each running task just uses a segment of the cache, as this portion is fixed during

execution, such fixed part allocation may lead to cache line misses in DCL [15].

In order to have a good trade-off between predictability and performance, in [19], Vera et al. present a method with DCL. They used a procedure that depends on the compiler to distinguish dependencies between data segments in different code regions. They outline how to mix the cache analysis model and CL approach to ensure that all contention between running tasks can be predictable. Their results show that even though they accomplished some reduction in the WCET, they encountered some degradation in performance [15, 19]. Additionally, their methodology does not address instruction cache.

The authors of [22], Zheng and Wu, propose two methods to reduce the WCET of task. The first approach is based on picking the possible data cache. Their reported results show that data dependencies limit this methodology. The second methodology attempts to improve over the first by exploiting data structure expressed by a non-cyclic task graph. The result of the former methodology exhibits improvements in WCET but faces difficulties on data cache utilization [15, 22].

After reviewing some significant literature on cache locking method, we are going to discuss the advantages and disadvantages of cache locking, which will lead us to the proposed technique.

### 2.3.2 Advantages and disadvantages of cache locking

Cache locking has a few potential advantages. The first and potentially the most basic benefit that CL can bring is predictability. As referenced, SCL and DCL are utilized to anticipate task WCET and improve predictability. The second advantage of CL depends on tasks model. In such applications, when a task is in active state, the replaced cache lines should be fetched again into the cache. Such interaction causes a delay in the system which such delay causes the overhead associated with switching. CL can decrease this effect and, consequently, CL can be helpful for any system performing multiple tasks.

The last but not least benefit of cache locking is performance. There often is a tradeoff between performance and predictability. One of the main objectives of cache locking techniques is to develop energy-efficient and cost-effective solutions, or in a nutshell, to obtain better performance.

Despite all the advantages, CL can cause several issues. Balancing between throughput and latency very often causes a trade-off in real-time systems. It should be noted that kind of processors under study, can affect the efficiency of the CL approach.

Multicore processors and Graphics Processing Units(GPUs) are two classes of architectures

that can benefit from CL. The move from uni-processor to multi-processor systems poses critical challenge particularly with respect to power utilization. Along these lines, in multicore processors, in contrast with single-core ones, CL implementation is a more complex problem.

As referenced previously, SWCL and HWCL methodologies require programming support, but that can also benefit from hardware support in present processors. Since some hardware features are not accessible on all processors, this makes CL more complex to implement, which as a result, lead some designer to deal with CL by software only.

DCL and SCL both involve various degrees of implementation complexity. A flexible loopbased dynamic cache locking technique was proposed in [23]. It was shown that the proposed technique improves very significantly the WCET, while preserving predictability, in contrast with previous strategies. Their implementation is complex and takes into account instruction caches and does not address hardware locking techniques, which make implementation much more straightforward.

In [24], a proposed semi-partitioned technique addresses the task relocation between cores in multiple tasks applications utilizing CL to optimize cache performance and energy consumption. Their methodology demonstrates a few improvement in cache performance, but leads to communication overload, which is not promising in real-time systems. In contrast, in [14,21] the authors utilizes SCL without relocating tasks between cores; in any case, the locking pattern cannot change during processing. References [14,21] present how to wrap up instruction cache analysis, but not data cache. It is of interest that in [14], the authors show 10 percent improvement over previous techniques.

In [25], the authors propose a procedure for improving the performance of data caches and their energy consumption. To validate that procedure, they experimented different strategies with various benchmarks. These experiments showed 20 percent miss-rate decrease, which improved the energy efficiency by 20% [15,25]. Although performance has a main role in many real-time systems, predictability, which is one of the main advantages of CL, should not to be disregarded. Additionally, we should consider the instruction and data CL combined and employ the dynamic methodology as much as possible.

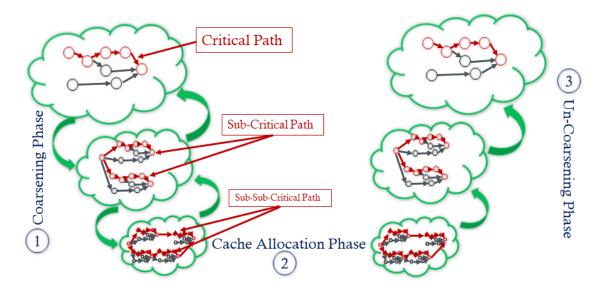

Ding et al., in [23], studied CL and showed that performance degradation can be as high as 100-150 extra cycles of latency. Hyperthreading leads to memory latency [26] that CL could reduce. These two aspects oppose each other. Subsequently, finding a fair trade-off is challenging in the current multicore systems. So finding the appropriate strategy reasonably and practically seem to rely more on objective-based rather than performance-based, or predictability-based techniques. Considering all the literature, we propose a Multi-Level Dynamic Cache Allocation (MLDCA) algorithm for shared caches to reduce the WCET. One of the most important goals of our approach is to reasonably allocate cache lines to each core(processor), under given constraints. Unlike all previous cache-locking approaches, like [27], that considers the longest path(the path in this study is a finite sequence of edges in DAG concept which joins a sequence of distinct nodes); our algorithm focuses on a sub-critical path. Besides, our method takes into account not only the instruction cache but also the data cache. Inclusion of data cache compounds the complexity of the problem significantly.

#### 2.4 Task scheduling

The increase in the number of cores on modern multi-core processors increases the structural complexity of such systems. Moreover, this increase in the number of cores in a processor has substantially increased the number of tasks that can be handled; therefore, making the task scheduling difficult in such systems. On the other hand, the transition from uniprocessor to multi-processor in real-time systems [28] poses significant challenges. The source of such challenges, is often associated with synchronizing the different processors. Applying scheduling algorithms specifically designed for uni-processors is not ideal for multi-processors. Research shows that this typically reduce the overall performance.

Task scheduling for multi-core processors plays an essential role in the performance of realtime systems. At this time, large data-centers are critical to the prosperity of many companies. The construction and maintenance of data-centers are very costly as they use a very large amount of power and energy. Also, managing data-centers efficiently is a technical as well as a financial challenge.

The authors of [29] propose a task scheduling model for multi-core systems which relies on the DAG approach. Minimizing scheduling length is the primary objective, not only in [29], but in most algorithms. On the other hand, load balancing between multiple cores is a second challenge. Regarding the comparison with related work, one sees that the model of algorithm and implementation has advantages in scheduling length; an example of which is discussed in this paper [30]. Furthermore, the authors propose an algorithm based on task duplication. The results show that they obtain nearly optimal solutions in very large time; however, the improvement performance is small compared with soutions obtained with a Genetic Algorithms(GA). The reported implementation is also quite complicated and it cannot meet timing deadlines.

The task scheduling algorithm can be divided into two categories, static task scheduling, and

dynamic task scheduling. The static scheduling algorithms are more straightforward and they have a lower overhead in comparison to dynamic scheduling. Random-based search and heuristics-based [6] are two kinds of basic static scheduling algorithm. The algorithm for random search includes GA [31], annealing algorithm, and local-search approach [32].

The primary focus of most recently published task scheduling strategies is on uni-core processor [29], which are not expendable to multi-core processors system. Optimal task scheduling of resources in real-time systems is a typical NP-hard problem [22]. So for this reason, task scheduling for minimizing the overall execution time of workflow application, and reducing the number of running cores have gained wide attention, [33].

In [34], the authors consider online-scheduling of multiple workflows submitted in a time period. Their approach is to maximize the utilization of resources. A limitation of that method is that it does not guarantee satisfaction of workflow deadlines. Task scheduling for multi-core systems has two requirements [35], load balancing and processor utilization. Most of the time, there is a conflict between the two requirements. Generally, tasks need to migrate from one processor to another to guarantee load balancing; on the contrary, due to the processor dependency, the load balancing may be violated with task migration. Finding a good trade-off between these two requirements is a big challenge in multi-core systems.

The heuristic algorithms proposed to solve that problem are generally classified into three categories: list-based task scheduling algorithm, cluster-based task scheduling algorithm, [36] and task-duplication-based algorithm [32].

List based scheduling algorithms, which are illustrated in [32, 37], investigates if a task fits into the gap period between scheduled tasks or not. Cluster-based scheduling algorithms break down into two steps the mapping and scheduling a task [32]. In the first step, the tasks are mapped into different groups, in the mapping stage, based on specified policy. In the second step, the same processor allocates to the same tasks. The mapping and scheduling steps are solved by complex algorithms without guarantee to meet the timing deadlines, which is our concern in this research.

In [38], the authors propose an algorithm for load balancing. The objective of this approach is reducing data locality, data-transferring overhead, as well as making some degree of balance between the two.

#### 2.5 Conclusion

With an increasing use of multi-core processors, an effective task scheduling strategy to solve the DAG-based problems has been a hot issue. Many researches have been conducted on task scheduling. However, the current task scheduling strategies still have some drawbacks. As mentioned, improving processor utilization and reducing the implementation complexity, are two main concerns of existing data-centers. The main concern for modern data-centers is more on power and energy rather than speed. However, we focus on both timing deadlines and increasing the number of unused processors.

The priority-queue-based data-driven task scheduling method is a unique approach explored in this research to reduce the number of active cores and improve each core utilization via the task scheduling concept. In addition, we investigate some aspects of processing time variability as well as of cache management, which can be used as part of future works.

## CHAPTER 3 CHARACTERIZING PROCESSING TIME VARIABILITY

As discussed in the previous chapter, task scheduling for multi-core processors while maintaining a high resource utilization alongside and meeting the specified timing deadline are critical requirements for achieving high performance. In brief, this work takes into account the effects of processing time variability on the multi-core processor.

## 3.1 Array Of Counters(AOCs): A generic scalable micro-benchmark to characterize processing time variability

The key idea behind the AOCs, proposed in this thesis, is to provide a micro-benchmark which can characterize the performance of multi-core and multi-processor systems. The benchmark and characterization method was designed to meet the following criteria: simplicity, scalability, and stretchability.

- 1. *Simplicity*: The basic algorithm is based on simple atomic operations such as one or more additions. Simplicity helps to predict the behavior of the processor in its interactions with memory. It is of interest that processing time of basic operations may have no impact if they execute faster than memory access time.

- 2. *Scalability*: The algorithm should be scalable such that the benchmark can spread over a multi-processor, a multi-core, or combinations of such systems. Management of the functions and data sent to the cores is facilitated by using the Intel Data Plane Development Kit(DPDK)cite50 library.

- 3. Controllability/Stretchability: Memory usage of the algorithm must be stretchable, so it can at will, and in a fully controllable way, exceed the capacity of every memory hierarchy level. In the beginning, the benchmark data would fit in the L1 cache, and it would migrate to L2, L3, and finally to the DDR4 external memory. The stretchability allows measuring the impact on the performance of each cache level and DDR4 memory. The stretchability allows to measure the impact on performance of each cache level and DDR4 memory.

In this research, a stretch factor (e.g., Scale = 1.5) is used to expand the AOCs data footprint gradually. In the beginning, the algorithm starts with an array of size 24 Bytes, and at each step, the dataset grows to 150% of its previous size in 34 steps (24 B, 36 B ...  $24 \times 1.5^{34} = 22$  MB).

```

1: procedure MAIN FUNCTION

```

- 2:  $N \leftarrow$  Number of counters;

- 3:  $cMax \leftarrow$  Maximum counting value;

- 4:  $iMax \leftarrow$  Maximum number of iterations;

- 5:  $bMax \leftarrow$  Maximum number of memory block size;

- 6:  $Scale \leftarrow$  stretch factor;

- 7: Processing Time  $\leftarrow 0$ ;

- 8:  $counter \leftarrow 0;$

- 9: for  $i = 1, i \leq bMax, i++$  do

```

10:

for j = 1, j \leq iMax, j++ do

Time Measurement: T_1

11:

for m = 1, m \leq cMax, m + + do

12:

for n = 1, n < N, n++ do

13:

counter/m/n = counter/m/n + 1;

14:

end for

15:

end for

16:

Time Measurement: T_2

17:

18:

Processing Time(j,i) = T_2 - T_1;

end for

19:

N \leftarrow N \times Scale;

20:

end for

21:

return Processing Time;

22:

23: end procedure

```

The details of the AOCs algorithm goes as follows (shown in Algorithm 1). The AOCs can run simultaneously on each core or thread of a many-core architecture. The inner loop increments a single counter on the array and goes on to the next one (for example in 24 B we have 6 counters, 32 bits = 4 bytes so 24/4 = 6). The second inner loop enforces the maximum counting value of each counter.

These two inner loops are surrounded by time measurement and the outer loop repeats this procedure for iMax times. In order to have a fair comparison when hyper-threading is used, we split the computation load into two different threads(one for each logical core), each thread processing N/2 counters. It is possible to execute AOCs single-threaded and hyper-threaded at the same time. In all cases, the average processing time we report is the total time divided by the total number of counter increments. As addressed in the following, AOCs, as a timing analysis method, is a useful tool to estimate worst/best/average processing time. This helps us ordering the tasks according to some constraints and priority, and then assigning them to cache slots with the proper cache locking strategy.

## 3.1.1 Best/Worst Case Execution Time(BCET/WCET) of a program

To exploit the BCET of an application, an AOCs was configured in a mode which we call a "controlled mode". The entire application, in this mode, is assigned to a core, assuming that all the other cores are in idle mode and all the software and hardware are always available for the running core. Such an arrangement leads to no interaction with the other parts of the system. To do so, we implemented a platform for the Intel Xeon E5-2650 V4 processor. Via this platform, we can do the following:

Via this platform, we can do the following;

- 1. Isolate the target core on which the program is running. An isolated system would suffer no interference from the rest of the system. Also, such implementation is feasible with the concept of atomic operation, which is a means through which no other instruction can interrupt the running operation

- 2. Handle all operations regarding the system with a master core in order to minimize the interference as much as possible.

- 3. Enforce some operations, which can be available for a user to configure based on which test is to be conducted; relevant operations include: activate/deactivate the data/instruction cache, invalidate the data/instruction cache, flush the data cache.

With these configuration methods, low interference and high interference options can be implemented. A Low-Interference Configuration(LIC) is defined when, the data cache is enabled, the shared cache is set in "interleaved" mode, and the instruction cache is enabled so it means assuming a minimum interference on all the shared resources(software and hardware services) happen for a given set of input data to produce its output. So this mode helps us to have an estimation for BCET. On the other hand, a High-Interference Configuration(HIC) happens when there is a maximum interference on all the shared resources. In this case, HIC is defined when the data cache is disabled, the shared cache is set in "sequential" mode, and the instruction cache is disabled. This mode gives a good understanding of WCET.

Using the LIC and HIC, we can illustrate the impact on variability of execution time for the application. These two configurations are useful to evaluate the performance in general on any system like, the Intel Xeon E5-2650 V4 processor to find the WCET and BCET, which is desirable in this research.

To exploit the WCET of each application, an AOCs is configured in "uncontrolled mode." This mode is built to create the WCET conditions for each application. So the execution time of all running programs can be suspended for a while because of interference between one program with another. Such mode can be useful to estimate an upper-bound of the WCET of a program.

Unlike the controlled mode, which shuts down all the CPUs, in uncontrolled mode, we enforce a small program of Interference Array Of Counters(IAOCs) to run onto all the other CPUs. IAOCs can be configured to saturate the shared resources. To obtain the maximum benefit of IAOCs, we strongly recommends running IAOCs before starting the analysis program and stopping the IAOCs upon finalization of the program.

Often, there is no guarantee to reproduce the maximum interference scenario throughout the experiments, even thought one knows adequate parameters about the setting of the system and application.

The importance of knowing the WCET using AOCs helps us to find the critical path, bottlenecks of the system, and the source of interference or variation. In all cases, a proper cache locking strategy the can be used to protect operations of high priority tasks.

## 3.1.2 AOCs as a micro-benchmark

A micro-benchmark is used to identify many CPUs memory parameters such as L1/L2/L3 cache size, L1/L2/L3 cache access time, page size, memory access time, etc. With the help of AOCs, we measure the access time required to access different cache layers and memory for different block-sizes and strides. AOCs provided a framework for time measurement that allows to characterize the impact of block-size, stride, and scale-factor. So AOCs allow computing the execution time for varying block sizes and strides. Also, this lets us compute cache miss-rate or hit-rates for each cache level and memory separately which is the objective of the micro-benchmark concept.

### 3.2 Multi-level dynamic cache management

Cache locking is a useful strategy in real-time systems to improve timing predictability. Cache locking can improve the performance of modern processors if used properly. Hence, cache locking is crucial as it is a source of processing time variation; however, it can also improve performance and reduce time variation. Generally, there are two categories of cache locking, static cache locking, and dynamic cache locking.

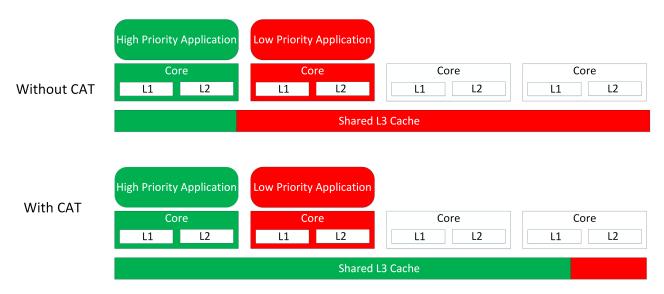

The Cache Allocation Technology(CAT) features provide more cache space which is available for high priority applications as shown in Figure 3.1. CAT allocate the cache to tasks with the help of the Dynamic Cache Locking(DCL) approach, during runtime to further optimize

the performance of the high priority applications versus the low priority applications.

Figure 3.1 CAT provides more cache space for high priorities applications