# University of Arkansas, Fayetteville

# ScholarWorks@UARK

Theses and Dissertations

7-2020

# Development of a Reference Design for a Cyber-Physical System

Nicholas Paul Blair University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Power and Energy Commons, and the Systems and Communications Commons

#### Citation

Blair, N. P. (2020). Development of a Reference Design for a Cyber-Physical System. *Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3821

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

# Development of a Reference Design for a Cyber-Physical System

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Nicholas Paul Blair University of Arkansas Bachelor of Science in Engineering, 2018

> July 2020 University of Arkansas

| This thesis is approved for recommen    | dation to the Graduate Council. |  |

|-----------------------------------------|---------------------------------|--|

| H. Alan Mantooth, Ph.D. Thesis Director | _                               |  |

| Roy A. McCann, Ph.D. Committee Member   | Jia Di, Ph.D. Committee Member  |  |

| Chris Farnell Committee Member          |                                 |  |

## **ABSTRACT**

The purpose of this thesis is to develop a reference design to assist in the selection of security practices in power electronics design. A prototype will be developed from this reference design for evaluation. This evaluation will include a brief cost/benefit analysis to gauge the efficacy of implementing each layer of security throughout the power electronics design process. This thesis will also describe the obstacles and effectiveness of integrating a Trusted Platform Module (TPM) into a cyber-hardened grid-connected device. The TPM device is a secured crypto processor that assists in generating, storing, and restricting the use of cryptographic keys. The emphasis of this research is to establish integrity, authenticity, and confidentiality within a system by providing a baseline of security concerns for segments of the system. This research considers communication, control, and hardware level securities. The scope of this thesis will review the necessary security methods as well as consider the effects these methods have on the embedded system, to assess the desired security to responsiveness trade off. Applying this approach to a design process will alleviate various unknowns of appending security to a power electronics design.

This thesis describes the specific vulnerabilities introduced within this grid-edge environment, and how the liabilities within the system can be mitigated. Initially, common security techniques will be considered to establish a guideline to benchmark performance and resource costs of the system. The foundation will be a non-hardened power electronic system platform with industry standard communication protocols. Several security techniques and attack vectors will then be evaluated to contribute to the base level platform. Other fail-safe features take place to gauge progress of the selected approach, non-inclusive to the TPM. Collectively, this investigation will determine a valid experiment by appraising and categorizing resource

allocation, performance overhead, and monetary cost analysis results into a reference design. The prototype will then demonstrate methods to relieve common threats that are purposefully implemented into the design.

©2020 by Nicholas Paul Blair All Rights Reserved

## **ACKNOLEDGMENTS**

My gratitude goes to my advisor, Dr. H. Alan Mantooth, who has been my guide through my graduate education providing a deeper understanding of cybersecurity as well as many other opportunities. I would also like to thank Dr. Jia Di, Dr. McCann, and Chris Farnell for being on my advising committee, directing me along the way. It has also been a pleasure to work with Joe Moquin, Ammar Khan, Estefano Soria, and many other students in the cyber security group who have helped me progress.

# TABLE OF CONTENTS

| Chapter 1                                      | 1  |

|------------------------------------------------|----|

| Introduction                                   | 1  |

| 1.1 Motivation                                 | 1  |

| 1.2 Security Principles                        | 2  |

| 1.3 Thesis Objectives                          | 7  |

| 1.4 Thesis Organization                        | 8  |

| 1.5 References                                 | 8  |

| Chapter 2                                      | 10 |

| Background                                     | 10 |

| 2.1 Introduction                               | 10 |

| 2.2 Cyber-Physical System                      | 10 |

| 2.3 Trusted Platform Module                    | 22 |

| 2.4 References                                 | 26 |

| Chapter 3                                      | 28 |

| Test Setup and Experimental Results            | 28 |

| 3.1 Introduction                               | 28 |

| 3.2 Communication Layer Assessment and Results | 28 |

| 3.3 Control Layer Assessment and Results       | 38 |

| 3.4 Hardware Layer Assessment and Results      | 41 |

| 3.5 References                                 | 45 |

| Chapter 4                                      | 47 |

| Cost/Benefit Analysis of Mitigation Strategies | 47 |

| 4.1 Introduction                               | 47 |

| 4.2 Overhead and Computation Costs             | 48 |

| 4.3 Economical Costs                           | 54 |

| 4.4 References                                 | 58 |

| Chapter 5                                      | 60 |

| Conclusions and Recommendations                | 60 |

| 5.1 Summary of Conclusions                     | 60 |

| 5.2 Recommendations and Future Work            | 61 |

| Appendicies                                    | 62 |

| Appendix A: Code                               | 62 |

| A-1 DSP C Code             | 2 |

|----------------------------|---|

| A-2 CPLD VHDL Code         | 3 |

| A-3 Web Server Python Code | 9 |

# LIST OF FIGURES

| Figure 1.1. U.S. annual installed DER power capacity additions by DER technology [4] 2 |

|----------------------------------------------------------------------------------------|

| Figure 2.1. Reference design architecture                                              |

| Figure 2.2. Physical device architecture recognition                                   |

| Figure 2.3. Communication layer topology                                               |

| Figure 2.4. Raspberry Pi 4 Model B Board Layout                                        |

| Figure 2.5. Lantronix XPort embedded ethernet module                                   |

| Figure 2.6. Optiga TPM SLI 9670 development board                                      |

| Figure 2.7. Control layer topology                                                     |

| Figure 2.8. Reference design controller board                                          |

| Figure 2.9. Hardware layer topology                                                    |

| Figure 2.10. PE-EVAL board                                                             |

| Figure 2.11.Components of the TPM [1]                                                  |

| Figure 3.1. Communication path diagram                                                 |

| Figure 3.2. CSPR web server user interface                                             |

| Figure 3.3. HTTP packet Wireshark monitor                                              |

| Figure 3.4. TPM 2.0 key wrapping [5]                                                   |

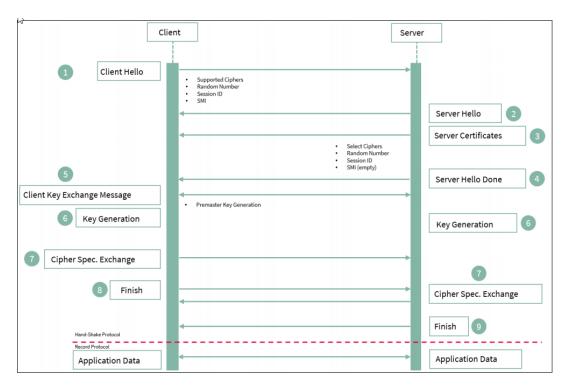

| Figure 3.5. OpenSSL client/server session flow [5]                                     |

| Figure 3.6. HTTPS packet Wireshark monitor                                             |

| Figure 3.7. Phase-A voltage cutoff                                                     |

| Figure 3.8. Phase-A low voltage output switching                                       |

| Figure 3.9. Basic 3-phase inverter topology                                            |

| Figure 3.10. Dead time effect                                                          |

| Figure 3.11. Accurate on/off delay wave forms         | 43 |

|-------------------------------------------------------|----|

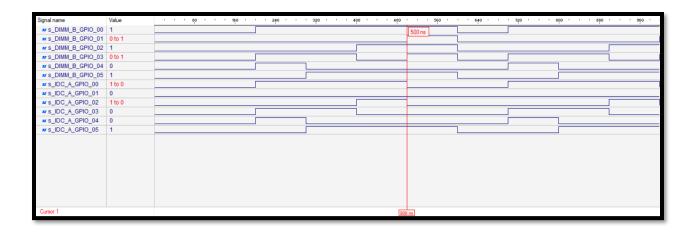

| Figure 3.12. CPLD shoot-through protection simulation | 45 |

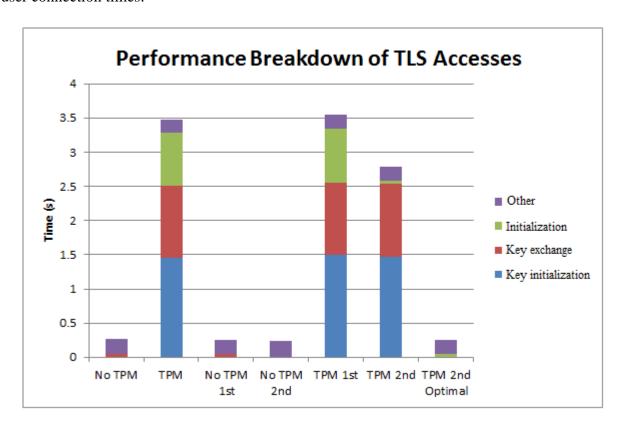

| Figure 4.1. Performance Breakdown of TLS Accesses [2] | 50 |

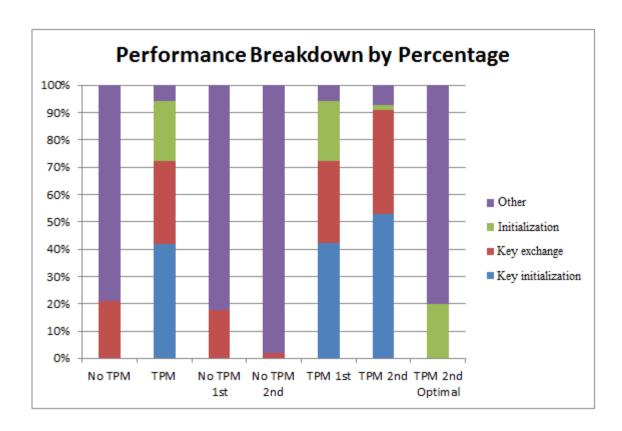

| Figure 4.2.Performance Breakdown by Percentage [2]    | 51 |

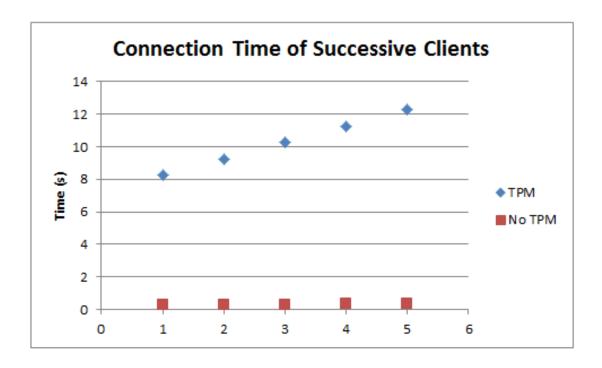

| Figure 4.3.Connection Time of Successive Clients [2]  | 51 |

| Figure 4.4. Control code Assembly breakdown           | 53 |

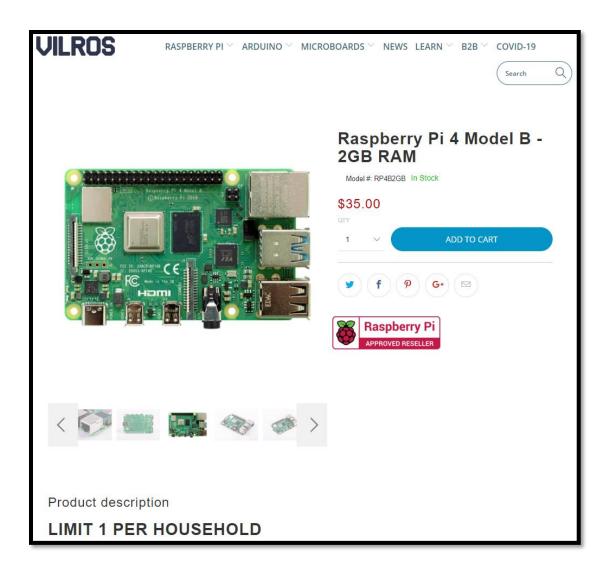

| Figure 4.5. Vilros stock limitation                   | 56 |

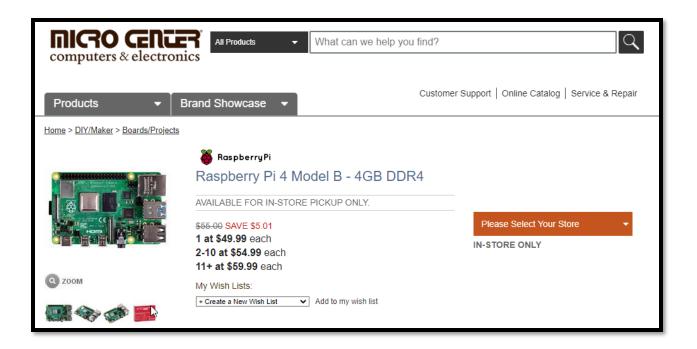

| Figure 4.6. MicroCenter order upcharge                | 57 |

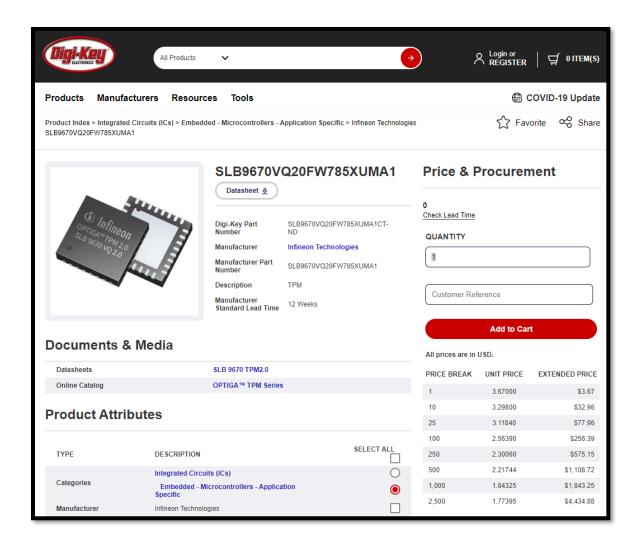

| Figure 4.7. TPM Economy of scale example              | 58 |

# LIST OF TABLES

| Table 1.1. Distributed energy resources by state [5] | . 4 |

|------------------------------------------------------|-----|

| Table 1.2. STRIDE Threat Model                       | . 6 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation

In recent years, the residential market has seen substantial penetration of sophisticated power electronics devices which expose a considerable attack surface, particularly for the power grid. Predominantly, these grid-connected devices such as solar inverters and battery energy storage systems (BESS) have little to no security. Too often, security is an afterthought of the design process, provided it is even a consideration to begin with. With rapidly developing grid technologies and smart-grid communities, the demand for smarter distribution systems is increasing leading to the necessity of secure power electronic systems. Electric transmission/distribution systems in which we deploy new distributed energy resources must still meet changing consumer needs while constantly battling new regulations and being aged [1]. With these demanding considerations in mind, security requirements must be extensive to protect new systems being put in place and to avoid interfering with other issues with maintaining a reliable grid, which were previously discussed.

Heightened grid complexity has a negative connotation because of increasing points of failure; however, smart power transmission systems provide more efficient and effective environments. Intelligent devices within the grid provide more robust situational awareness which yields quicker reaction times for dynamic systems. Even so, concerns with operation security and reliability are drawbacks to consider [2]. An underlying goal of this research is to bridge the gap between the more secure methods of information technology (IT) and the newer technologies being introduced to the operational technology (OT) spectrum.

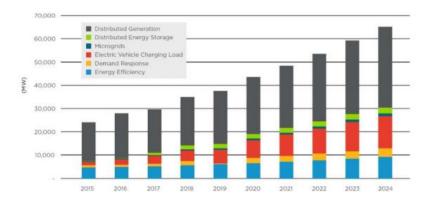

*Figure 1.1. U.S. annual installed DER power capacity additions by DER technology [4].*

This reference development will allow further innovation with less constraint and hasten technological developments within the power industry; all while meeting requirements to ensure the safe execution and management of all user data. This is particularly important to the field of Distributed Energy Resources (DER), considering the vast spread of these devices across a rapidly expanding market. As shown in Figure 1.1, the market will expand as much as 50% in the next five years. The existing complexity of modern system design can be egregious when considering all DER process variables. The desire of this work is to provide a design process that allows for rapid development in this field, as well as deliver different security options throughout the system design.

## **1.2 Security Principles**

Security is a measurement of safety. This implies that if a system is thoroughly secure, then no undesired influence may have any impact on the system. That said, no security is absolute, no matter the intricacies of the solution. Therefore, not only is it critical to protect against outsider threats, but also to understand that an intrusion event is imminent, and one must have the capability to mitigate any adverse effects an intrusion may have on the system. Simply

put, a system must not exclusively consider if an event will happen, but when it will happen and how to stop the event from causing harm.

In a cyber-physical system, the approach to security is relatively unique. Apart from being vulnerable to component failures, these systems are often predisposed to malicious attacks due to a direct opening to the once ignorant physical system created by the increase in communication and data flow now broadcasted to and from the device [3]. The proposed research investigates security from a layered perspective to the cyber-physical system. A layered approach considers security throughout the design phase rather than injecting security into a complete system. This aspect is critical to this approach due to the immature nature of merging IT and OT techniques to ensure protection at vital points of contact created using this method. Though immature and exposed, the operations coupling IT and OT will only become more prominent in the coming years [5]. This can be compared to any technological scramble to market; take smart phones for example. Like smart phones, this relatively new concept is rapidly pressing the market of distributed energy resources and expanding quickly, but without forethought on how to administer security to this field, these devices will succumb to the same setbacks. Many security exploitations became relevant to the attack surface, that is the smart phone platform, since this area had yet to be explored. Smart phones faced many new challenges with obstacles that could have been avoided with slightly more consideration to the security and the data that was to be protected. Challenges akin to infection of hostile, intrusive, or otherwise malicious software become far more significant to those whose livelihoods that depend on these resources [6, 7]. The residential and commercial markets both have substantial DER presence reported by the DOE and the More Than Smart working group: more than 42,500 MW of total distributed energy resources already established nationwide. Table 1.1. shows this on a state by

state breakdown and this is not even concerning those to come. Though slightly dated, this table alone shows the urgency to secure future devices

Table 1.1. Distributed Energy Resources by State [5]

|          | TOTAL      | DISTRIBUTED**   | STORAGE | ENERGY           | DEMAND <sup>4</sup> | CHP <sup>eq</sup>  | # ELECTRIC*** |

|----------|------------|-----------------|---------|------------------|---------------------|--------------------|---------------|

| STATE    | DER" (MW)  | GENERATION (MW) | (MW)    | EFFICIENCY T(MW) | RESPONSE (MW)       | INSTALLATIONS (MW) | VEHICLES      |

| AK       | 391        | 9               | 0       | 0                | 22                  | 360                | 155           |

| AL       | 1,263      | 522             | 0       | 22               | 610                 | 109                | 773           |

| AR       | 715        | 299             | 0       | 88               | 230                 | 99                 | 374           |

| AZ       | 1,136      | 646             | 0       | 228              | 226                 | 35                 | 4,361         |

| CA       | 8,387      | 3,149           | 5       | 584              | 2,998               | 1,651              | 126,283       |

| со       | 436        | 277             | 0       | 99               | 29                  | 32                 | 4,001         |

| СТ       | 520        | 119             | 0       | 47               | 88                  | 267                | 2,476         |

| DC       | 62         | 20              | 0       | 8                | 20                  | 14                 | 493           |

| DE       | 190        | 54              | 0       | 0                | 129                 | 7                  | 383           |

| FL       | 1,052      | 428             | 0       | 105              | 347                 | 173                | 10,383        |

| GA       | 1,212      | 775             | 0       | 102              | 197                 | 139                | 15,551        |

| HI       | 636        | 527             | 0       | 28               | 3                   | 78                 | 3,050         |

| IA       | 463        | 38              | 0       | 143              | 127                 | 155                | 928           |

| ID       | 860        | 70              | 0       | 252              | 472                 | 66                 | 409           |

| IL       | 533        | 33              | 0       | 12               | 54                  | 434                | 6,694         |

| IN       | 1,110      | 33              | 0       | 548              | 401                 | 127                | 1,697         |

| KS       | 141        | 10              | 0       | 2                | 45                  | 85                 | 750           |

| KY       | 565        | 64              | 0       | 96               | 358                 | 47                 | 701           |

| LA       | 825        | 520             | 0       | 80               | 0                   | 226                | 527           |

| MA       | 1,088      | 570             | 0       | 184              | 16                  | 319                | 4,612         |

| MD       | 597        | 183             | 0       | 124              | 191                 | 99                 | 5,028         |

| ME       | 604        | 504             | 0       | 19               | 0                   | 81                 | 695           |

| MI       | 659        | 181             | 1       | 160              | 28                  | 290                | 8,844         |

| MN       | 1,604      | 226             | 0       | 460              | 730                 | 188                | 2,775         |

| МО       | 302        | 100             | 0       | 65               | 29                  | 107                | 1,859         |

| MS       | 999        | 274             | 0       | 23               | 655                 | 47                 | 201           |

| MT       | 63         | 15              | 0       | 37               | 0                   | 11                 | 362           |

| NC       | 1,886      | 384             | 0       | 701              | 625                 | 175                | 3,384         |

| ND       | 373        | 11              | 0       | 4                | 311                 | 46                 | 91            |

| NE       | 496        | 6               | 0       | 46               | 409                 | 35                 | 579           |

| NH       | 97         | 41              | 0       | 9                | 0                   | 47                 | 761           |

| NJ       | 1,635      | 1,146           | 0       | 86               | 74                  | 329                | 6,021         |

| NM       | 213        | 70              | 0       | 70               | 43                  | 30                 | 637           |

| NV       | 301        | 83              | 0       | 36               | 158                 | 24                 | 1,509         |

| NY       | 1,256      | 441             | 0       | 214              | 37                  | 564                | 11,278        |

| ОН       | 874        | 155             | 0       | 371              | 198                 | 150                | 3,814         |

| OK       | 336        | 76              | 0       | 73               | 123                 | 65                 | 806           |

| OR       | 557        | 301             | 0       | 11               | 35                  | 211                | 5,681         |

| PA       | 936        | 343             | 0       | 120              | 101                 | 371                | 4,540         |

| RI       | 115        | 18              | 0       | 39               | n/a <sup>ls</sup>   | 58                 | 417           |

| SC       | 1,546      | 353             | 0       | 268              | 753                 | 172                | 1,056         |

| TN       | 1.054      | 228             | 0       | 162<br>50        | 100<br>703          |                    | 2,730         |

|          |            |                 |         |                  |                     |                    |               |

| TX       | 1,457      | 287             | 0       | 243              | 543                 | 384                | 9,925         |

| UT       | 273<br>701 | 35<br>398       | 0       | 53<br>17         | 120                 | 64                 | 1,565         |

| VA<br>VT | 69         | 398             | 0       | 12               | 142                 | 145                | 3,628<br>840  |

|          |            |                 |         |                  |                     |                    |               |

| WI       | 772<br>677 | 304<br>224      | 0       | 302<br>106       | 15<br>99            | 151                | 12,291        |

| WV       | 215        | 106             | 0       | 4                | 84                  | 248                | 2,429         |

| WY       | 44         | 2               | 0       | 7                | 4                   | 31                 | 73            |

| TOTAL    | 42,569     | 14,691          | 6       | 6,517            | 12,683              | 8,672              | 278,851       |

| 1 O I ME | 42,309     | 14,091          | 9       | 0,317            | 12,003              | 0,072              | 270,031       |

in this area and helps to better understand the need for this research. The need for energy storage and electric vehicles is also scaling quickly, and the same security principles can be applied to these areas. Diligence is important in a rapidly growing industry such as this, and any complacency could be detrimental to the residential market and those who inhabit it.

# 1.2.1 Security Modeling

There are many ways to approach security to determine vulnerabilities within a system. Most common methods involve an arrangement of considerations relating to the threats and risks of vital system operations. These arrangements are called models which help to guide policies or distinguish potential risks to a system; generally, a good starting point when assessing probable points of interest during the design process. The significance behind this, regardless of what method is chosen, is the visibility into the device and the resources being used. More precisely, this gives foresight on what the system is committed to doing, while mapping out interconnections and communications within a design process before truly assessing threats.

Different situations require specific measures when appending a security model, therefore various security assessments exist to help provide for the individual needs of most scenarios. Example standardized models include: CIA, STRIDE, DREAD, and Attack Trees. These models each focus on distinct aspects of exposure to a system, such as the STRIDE model; made as a mnemonic model by the Microsoft Corporation to identify computer security threats. The acronym defined in Table 1.2 considers threats associated with this model. Various other models exist to help define the risks and liabilities of cyber systems. Each model defines the approach differently, but the goals are all the same; to provide a proactive solution to understanding the vulnerabilities within a system and define countermeasures to nullify these exploits.

Table 1.2. STRIDE Threat Model

| S | Spoofing Identity      |

|---|------------------------|

| T | Tampering with Data    |

| R | Repudiation            |

| I | Information Disclosure |

| D | Denial of Service      |

| E | Elevation of Privilege |

#### 1.2.2 Modeled with CIA Triad

The model that will be considered for this research is the CIA model; sometimes identified as the AIC model as to avoid confusion with the Central Intelligence Agency. This model was designed specifically for organizations to guide policies for information security. Typically represented with a triangle, hence the name triad, emphasis within this research is focused on three key points in the acronym: Confidentiality, Integrity, and Availability. Many standards and third parties have partnered to provide users with the ability to manage their own privacy, durability, and legitimacy based on this model [8]. Subsequently, this research has defined the terms to represent vulnerabilities to be addressed with a security-in-depth approach. Each term is described here and explained in further detail in the following sections of the paper.

Confidentiality is considered a method of security intended to control the access to information. This means to ensure sensitive data is only available to those with authorized privilege can access this data. Two-way encryption contributes to confidentiality by mapping symbols, letters, and figures arranged to represent plain text messages and is commonly used to

prevent unauthorized access to concealed data. Hashing, like encryption, is another algorithm used to arrange information into a fixed length format for confidentiality among other uses.

Data integrity aims to protect the data from modification or removal. To do so, the data must only be modified by means that would not lead to system failure or as a baseline be recoverable. The idea is that one can trust the data that is in the system. If authentication is successful, the user must not be able to manipulate or interpret the data in a way that would be harmful to the user or system.

Lastly, availability is the most essential element in determining authorized users and the level of accessibility to the system. This component of the triad is focused on targeting hardware failures, power failures, and failovers to ensure that the data is attainable. Recovery is essential for the availability of data to stay accessible. In the event of data corruption, hardware failure, or malicious attack, the user and the system must still retain the ability to monitor and use the data as long as it can be trusted. A method to ensure the availability is to consistently backup critical data in a secured location secluded from the system. This guarantees that previous data can be accessed without worry of system level influence or interaction.

### 1.3 Thesis Objectives

The purpose of this thesis is to investigate methods in which to incorporate security into a cyber-physical system, as well as perform a cost/benefit analysis on the described system to portray the effectiveness of each layer of security and categorize the costs associated with each addition. From this analysis, the expectation is to realize a reference design that provides support in securing the power electronics design process. This reference design will demonstrate what base level functionality within a system may look like, different layers of the system, and how to approach security at each layer. A portion of this thesis will focus on the benefits of utilizing the

Trusted Platform Module, one way it is specifically used within this system, and further capabilities of this module pertaining to security and system overhead. Experimental results are based on the mitigation techniques used in this analysis to determine the functionality of each method used. Other system design considerations will be described to explain the reason for choosing certain system components, attack scenarios, and mitigation techniques.

# 1.4 Thesis Organization

The composition of this thesis is arranged sequentially by chapter as listed:

- Chapter 1 serves as an introduction to the concepts associated with this research such as basic security principles, security models, the chosen approach, and objectives.

- Chapter 2 provides an explanation of the background needed to understand the functionality of the cyber-physical system. This section also considers the integration of the TPM and how to further utilize the available resources for future development.

- Chapter 3 details the remainder of the system with experimental setup to depict the mitigation strategies that can be applied to a cyber-physical system.

- Chapter 4 presents a cost/benefit analysis of the mitigation techniques.

- Chapter 5 defines the summarized conclusion and introduces potential future work.

#### 1.5 References

- [1] D. Tan and D. Novosel, "Energy challenge, power electronics & systems (PEAS) technology and grid modernization," in CPSS Transactions on Power Electronics and Applications, vol. 2, no. 1, pp. 3-11, 2017.

- [2] Y. Jia, Z. Xu, L. Lai and K. P. Wong, "Risk-Based Power System Security Analysis Considering Cascading Outages," in IEEE Transactions on Industrial Informatics, vol. 12, no. 2, pp. 872-882, April 2016.

- [3] F. Pasqualetti, F. Dörfler and F. Bullo, "Attack Detection and Identification in Cyber-Physical Systems," in IEEE Transactions on Automatic Control, vol. 58, no. 11, pp. 2715-2729, Nov. 2013.

- [4] Federal Energy Regulatory Commission (FERC), "Distributed Energy Resources: Technical Considerations for the Bulk Power System," FERC, 2018.

- [5] P. Martini, T. Brunello, and A. Howley, "Planning for More Distributed Energy Resources on the Grid: A Summary for Policy-Makers on the Walk-Jog-Run Model",

- [6] M. La Polla, F. Martinelli and D. Sgandurra, "A Survey on Security for Mobile Devices," in IEEE Communications Surveys & Tutorials, vol. 15, no. 1, pp. 446-471, First Quarter 2013.

- [7] P. Srikantha and D. Kundur, "A DER Attack-Mitigation Differential Game for Smart Grid Security Analysis," in IEEE Transactions on Smart Grid, vol. 7, no. 3, pp. 1476-1485, May 2016.

- [8] Microsoft, The STRIDE Threat Model, Nov 2009. [Online] Available: https://docs.microsoft.com/en-us/previous-versions/commerce-server/ee823878(v=cs.20)?redirectedfrom=MSDN

- [9] S. Deepika and P. Pandiaraja, "Ensuring CIA triad for user data using collaborative filtering mechanism," 2013 International Conference on Information Communication and Embedded Systems (ICICES), Chennai, 2013, pp. 925-928.

#### **CHAPTER 2**

#### **BACKGROUND**

#### 2.1 Introduction

From Chapter 1, the motivation for this research is to implement layers of security within a cyber-physical device that will act as a model reference design. The device considered in this research is readying for a preproduction prototype, meaning that the controls and overhead are likely to become much more resource intensive due to complex secondary and tertiary control algorithms as well as protection schemes. To add, having each layer of security implemented in a singular location rather than placed throughout the architecture is not beneficial for reasons concerning basic security principles. These flaws in design display the need for a multi-level security architecture. The approach for the reference design architecture defines these layers and applies example securities that demonstrate protection against realistic threats.

# 2.2 Cyber-Physical System

A cyber-physical system is defined as the integration of computation, communication, and physical processes in order to complete various defined tasks. Analogous to the Internet of Things (IoT), specifically the Industrial Internet of Things (IIOT), these systems utilize a combination of actuators and sensors that communicate with control systems to operate certain physical procedures. Embedded control systems further consult with an elevated computing environment that monitors critical points within the system. There are considerable challenges with integrating these systems particularly due to the qualitative safety and reliability

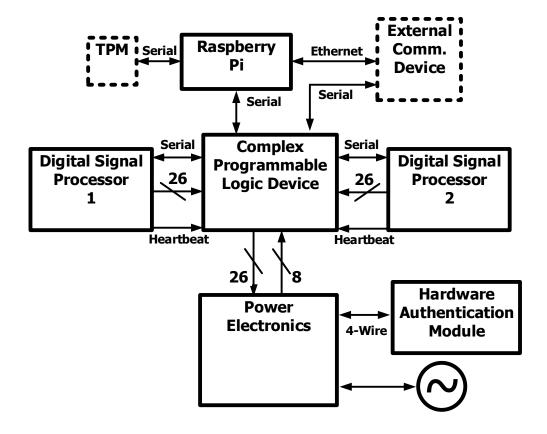

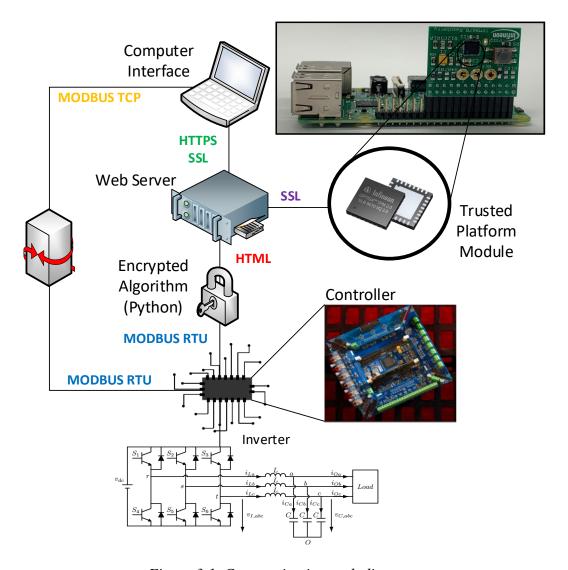

Figure 2.1. Reference design architecture.

requirements of the physical environment are fundamentally different from those same stipulations in computing [9]. Regardless of the challenges, the demand for such devices has grown exponentially as technology advances, and the importance for future growth is evident. For this precise reason, security will play an important role in cyber-physical systems, and this displays the need for implementing a reference design.

In relation to the field of distributed energy resources, this research realizes a base architecture of the critical layers to consider within a device. These layers to be examined are labeled the communication layer, control layer, and the physical or hardware layer. This approach uses components from Figure 2.1 and structures these interconnected pieces as displayed in Figure 2.2. This method appeals to the need for a reference design by describing the

vital components in the device, recognizing various risks in each layer, and how to address the foremost risks; all to define an outline for addressing vulnerabilities within a relatable system.

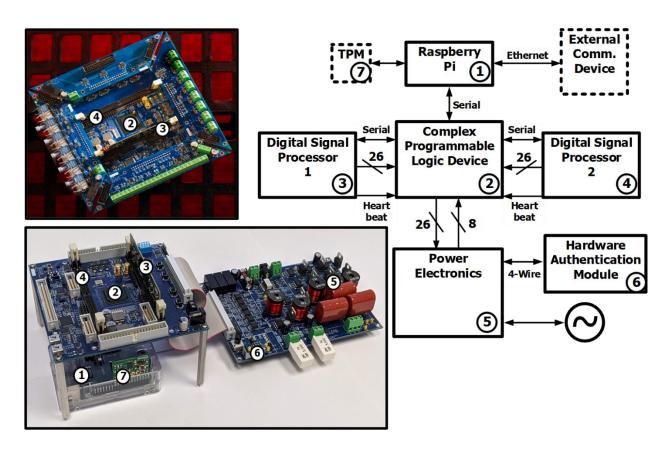

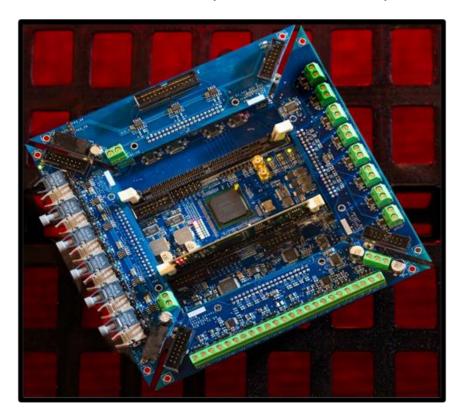

For a proper understanding to recognize the physical makeup of the reference design architecture, the components within the system are displayed in Figure 2.2. The following sections will reference Figure 2.2 to help realize the physical attributes of each device as they are explained in further detail below. The components are numbered chronologically to show where each component resides in the setup in the following order: Raspberry Pi, Complex Programable Logic Device, Digital Signal Processor 1, Digital Signal Processor 2, Power Electronics Hardware, Hardware Authentication Module, and the Trusted Platform Module (TPM). Each element listed will be described below when detailing the various layers.

Figure 2.2. Physical device architecture recognition.

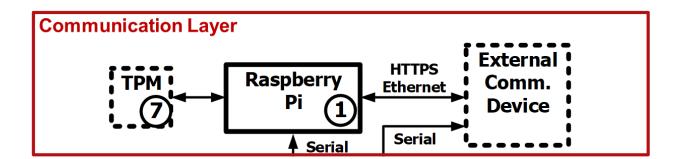

#### 2.2.1 Communication Layer

Within a cyber-physical system, some form of communication typically exists in order to communicate aquired data out of the system to be processed and utilized. It is necessary to verify that the data reported from within the system is correct and realistic. This data provides growth for companies within the power industry and supports the development of a robust smart grid [10]. This happens by monitoring the data received from the system to address any needs or concerns from the system. Issues observed within the system can then be documented and counteracted by either correcting the issue in the current system with an update or the development of a new revision to correct the design will also suffice. Collecting and monitoring system data through communication allows for better data management, data analysis, visualization, and processing of the data. Figure 2.3 defines a generic communication method chosen to be used in the reference design. Like many other elements of this reference design, the components within each layer can be replaced with similar devices to better address the user's needs. That is why this is considered a reference design. It grants the user the ability to conform to their own needs with the freedom to swap certain components for more suitable functionality.

Figure 2.3. Communication layer topology.

The current reference design contains a communication layer consisting of the Trusted Platform Module, a Raspberry Pi, and an external communications device. Also, not shown in the diagram

is one other communication device termed an XPort ethernet module. Each of these components has an important role within the communication layer and will be described in more detail below.

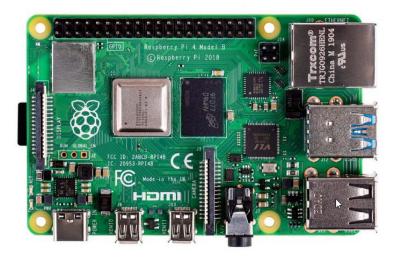

The primary component of the communication layer within the reference design is the Raspberry Pi. The Raspberry Pi is an embedded environment for the Linux operating system featuring multiple inputs and outputs for the user to interface with such as keyboard and mouse inputs for control and a display output, but more importantly direct access to the General Purpose Input/Output (GPIO) directly to the central processor. This provides direct communication with the processor over many standardized protocols in order to connect other devices such as the Trusted Platform Module for instance. For an idea of what the Raspberry Pi looks like, it can be seen in Figure 2.2. For a closer look, see Figure 2.4. The reasons for choosing the Raspberry Pi 4 in this instance is due to the quad core Arm processor that houses the Linux kernel, Gigabit ethernet port, serial interface, and abundant support from documentation and the community.

Figure 2.4. Raspberry Pi 4 Model B board layout.

Realistically, this portion of the reference design simply depends on any Arm processor platform that can support a Linux kernel. The Linux kernel here is the key component and the

Raspberry Pi architecture is designed for this. To elaborate on this concept, a kernel is the foundation of an operating system whereas an operating system is the software supporting the base computer functionality. For this reference design, a Raspbian operating system Linux kernel is used because it is open source and very well documented in capabilities, versatility, and support; though, any operating system could be used that contains similar functionality.

The purpose of this kernel is to accommodate the required communication link between the cyber-physical device and the outside world. This kernel provides an environment in which the system can execute programs for importing commands and exporting data, to and from the system. These programs are simply code that is executed within the device to serve various purposes such as gathering weather data and time of use pricing, hosting a web server, and addressing lower level registers in the system. Before accessing raw data, it must be scaled and formatted to be useful to the user. This formatting is done when addressing the lower level registers in the system. The data is manipulated and managed by a web server running within the system. The webserver acts as a hub to route important data to the appropriate destination. Here, the webserver can display the data in many ways to help the user visualize system states or operation of the system. The webserver also offers ease of access to the device through the external communication device which could be any remote terminal that has access to the network. This device could be any remote terminal connected to the same computing network as the Raspberry Pi. Since the primary access point to the device is through this connection, it is critical for this connection to be secure. The security methods used between the webserver and TPM are further detailed in the integration and testing procedure sections of this thesis.

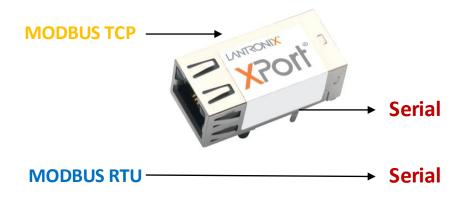

Figure 2.5. Lantronix XPort embedded ethernet module.

Another communication method utilizing the previously mentioned XPORT module is available as an alternative to the webserver communication path. Figure 2.5 details the two communication protocol standards chosen for the reference design. These two are Modbus TCP, which is utilized through the XPort module, and Modbus RTU otherwise. The web server communicates to the lower level control layer via a serial interface using the Modbus RTU protocol while the XPort supports the Modbus TCP protocol to communicate system information to the remote terminal. The remote terminal can also relay system commands back to the XPort module to be converted into Modbus RTU over serial back to the system. This decision on which communication type to depend on is made within the control layer. Even so, the control layer must only standardize on the Modbus RTU protocol and if the access is requested over Modbus TCP, then the XPort will handle the protocol translation.

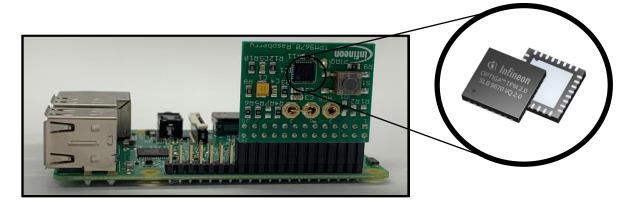

Lastly, the final element within the communication layer is the Trusted Platform Module, also known as the TPM. The TPM will be reintroduced in section 2.3 to be covered in extensive detail. For now, it is worth noting another key reason for choosing a Raspberry Pi was support for the Optiga TPM SLI 9760 evaluation board manufactured by Infineon. A snippet of the device and its connection to the Raspberry Pi can be seen in Figure 2.6. Choosing this

Figure 2.6. Optiga TPM SLI 9670 development board

board for the design hastened the development process substantially. Ideally, this TPM would rest on the control board layer to be connected directly to the communication bus to provide support in a full production model, however, this board was used for rapid protype development with the ability to neglect appending additional components on the control layer. Interfacing with the control layer would take more time to develop for considering a controller would also need to be developed within the CPLD using VHDL to be able to communicate with this device. Also, the Application Programming Interface (API) developed for this board utilized the Serial Peripheral Interface (SPI) protocol for which it is much easier to develop, given the team background.

## 2.2.2 Control Layer

The control layer is put in place to manage the behavior of the hardware devices within the cyber-physical system. This layer acts as a medium in order to facilitate the communication layer commands to the actuators, which are in the hardware layer. In addition, the control layer reports sensor data coming from the hardware layer back through the communication layer for

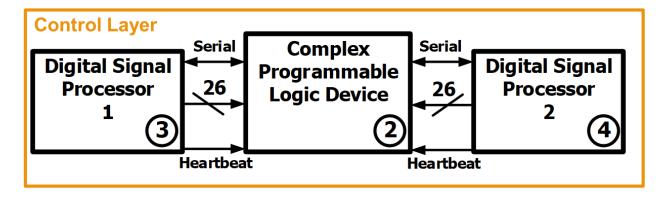

Figure 2.7. Control layer topology.

monitoring. The control layer can be completely autonomous or it can actuate from input commands. Regarding the cyber-physical reference design, this layer handles a combination of taking input commands for reference as well as autonomously following the reference through control system feedback. For any complex control system of a physical system, the autonomous control method uses feedback from the sensor data in order to maintain set output values (i.e. voltages and currents). The hardware control methods used within this research relate to power electronics hardware such as ac inverters, dc/dc converters, power regulators, and battery energy storage. To determine how these methods are used, the specific reference design control layer needs to be explained further.

The design illustrates the control layer with one Complex Programmable Logic Device (CPLD) and two Digital Signal Processors (DSP) as seen in Figure 2.7. A closeup of the control board can be seen in Figure 2.8. To further read about these processors, one may read sources [12] and [13]. The role of the DSP is to directly control the behavior of the power electronics. Particularly, for this cyber-physical system, a 3-phase inverter is receiving power from a Direct Current (dc) link and is providing a sinusoidal 3-phase Alternating Current (ac) output. The hardware description will be reintroduced in the next section in more detail. For now, all that

needs to be understood is that the DSP is in control of directing the power flow and reading measurements from the sensors. The DSP receives this sensor data through a control loop. Even though the complexity of the pre-production prototype controls constructed from similar control designs will increase as a result of incorporating secondary and tertiary control algorithms, the power flow will be further optimized. This displays the growth capability within the reference design. There is sufficient processing capability to handle advanced control system models, as long as the appropriate power electronics hardware is considered within the hardware layer of the design.

The CPLD considered in this reference design is an extremely fast integrated circuit that is a derivation of the Field Programmable Gate Array (FPGA). Typically, a CPLD can have anywhere from a thousand to ten thousand gate arrays, whereas FPGAs are known to have tens of thousands to millions of gate arrays on a single chip. Though FPGAs seem to be much larger, CPLDs are more economically efficient, and they can be much faster when considering execution and boot times. FPGAs require more interconnections which can lead to more flexibility in design choices but are more complex to design. CPLDs are architecturally simple compared to the FPGA, which allows for greater speeds. One important role for the CPLD in the reference design is to supply access to the gate array as a routing fabric for the digital signals in the system. In other words, all digital signals being transported through the control layer must travel to the CPLD. The CPLD then decides where to route each signal. Analog signals must be manually routed through the platform, as the CPLD does not support the routing of continuous signals. Routing each digital signal through the CPLD opens the reference design to a wide variety of functions. Some functions currently implemented have been described above. By routing communication signals through the CPLD, the ability to physically reroute and sever

communication signals based on predetermined conditions is available. This functionality is critical to the reference design control layer and will support many more functions which also allows for modularity. In Figure 2.8, the trapezoidal daughter boards serve many functions, and all follow the same standardized pinout. This allows for almost limitless expansion capabilities that would simply require a sensor/actuator daughter board design. That design could then attach to the controller board to enhance functionality and meet the needs of any user.

Figure 2.8. Reference design controller board.

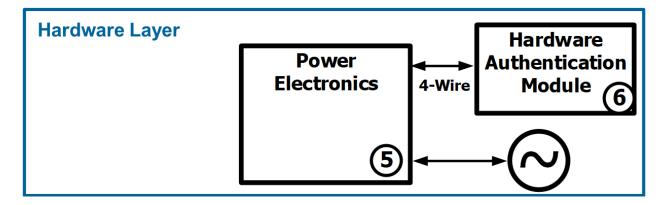

## 2.2.3 Hardware Layer

The hardware or physical layer of the device is the power electronics system, composed of all sensors and actuators in contact with the control layer of the cyber-physical system. The sensors within this system are voltage and current sensors set up throughout the power electronics, in order to monitor the system as well as provide feedback to the active control systems in the control layer. Actuators in this context could be the 3-phase motor, acting as a

load, while the power electronics within this platform are responsible for converting the control signals into the necessary output to drive this load. To further explain the hardware, the design of the power electronics evaluation board (PE-EVAL board) will be described in this section.

Figure 2.9. Hardware layer topology.

The sensors in the hardware layer are also reporting back to the DSP. The DSP has 16 on-board Analog-to-Digital Converter (ADC) inputs that allow for an analog signal, such as a voltage, to be converted into a scaled digital signal. This shows how the sensory data is carried out of the hardware layer. On the output of the 3-phase inverter, the grid connects to the device. This is where more complex control strategies could consider different modes of operation, such as islanded mode, grid feeding mode, and grid forming mode.

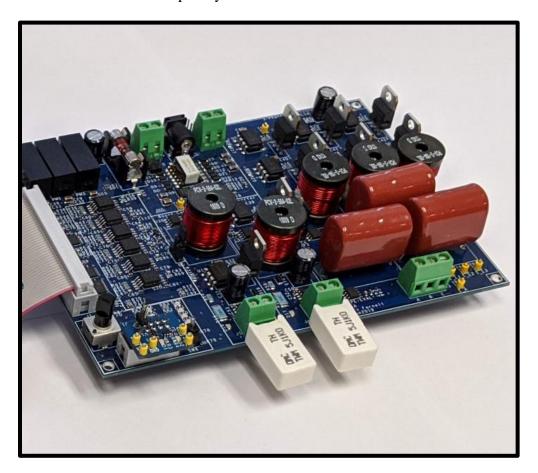

The breakdown of the PE-EVAL board has three separate topologies: a buck converter, boost converter, and a 3-phase inverter. For this reference design, only the 3-phase inverter is considered to be the hardware layer. This is for simplicity when denoting attack vectors on the system, however, these security principles can be applied to many power electronic scenarios. The PE-EVAL board can be seen in Figure 2.10. This is an arbitrary hardware topology selected because this design was considered when the controller architecture was designed. The

remainder of the power electronics design, that is not directly associated with the attack vectors, will not be discussed to avoid complexity and confusion.

Figure 2.10. PE-EVAL board.

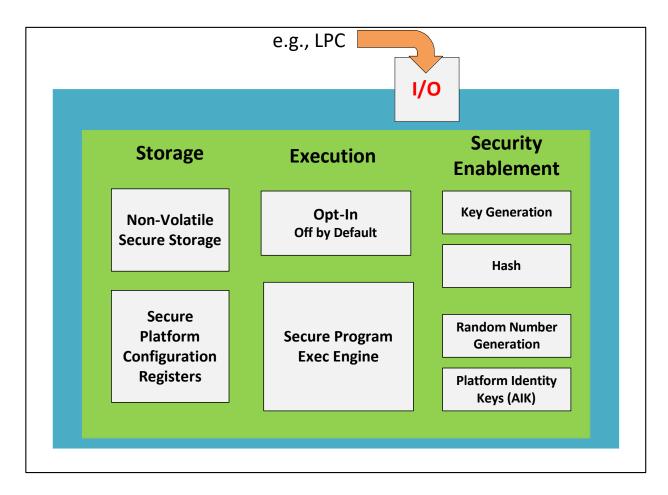

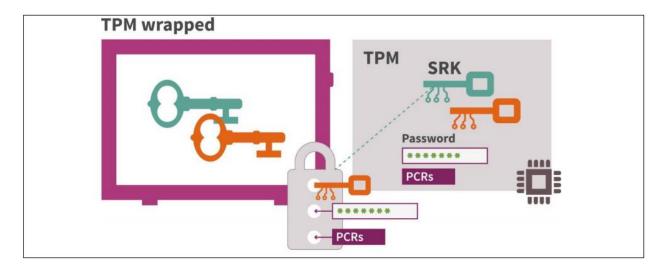

# 2.3 Trusted Platform Module

The Trusted Platform Module, also known as a TPM, is a microcontroller for imparting hardware authentication and tamper protections into a system. This module was created by the Trusted Computing Group (TCG), an international standards body of approximately 140 companies. These companies are involved in creating specifications that define PC TPMs,

Figure 2.11.Components of the TPM [1].

trusted infrastructure requirements, APIs, protocols necessary to operate a trusted environment, and trusted modules for other devices [1]. This integrated circuit comes well documented with the TPM 2.0 Library specification that has become an international standard administered by ISO/IEC JTC 1.

The TPM architecture, simplified in Figure 2.11, is comprised of a plethora of security modules such as non-volatile secure storage, secure platform configuration registers, a hardware random-number generator, hash, and isolated key generation and key storage. These functionalities can provide cryptographic keys, prevent private keys from being exported, protect pin values used for authentication, record and anonymously report on software loaded during the

boot process to protect against malware and attacks [1]. Each of these features are effective functions that can be utilized for security purposes before considering that the integrated chip is isolated from the system. Some features are worth noting and are described in more detail below.

Within distributed energy resources, cryptographic keys provide data access to users who possess certain credentials or attributes. In this case, the method for enforcing such policies is to employ a trusted server to store the data and mediate access control between the user and server [2]. Common practice exercises the encryption process and key storage on these mediums.

Although encrypted, these keys still reside on a shared local storage within the system. If the mandating server is compromised or physically jeopardized, a malicious entity could theoretically decipher the keys and decrypt the secured data if given enough time. The TPM improves on this process by physically isolating a portion of the cryptographic key within the hardware cryptographic module. In the case the event that the server is compromised, the TPM ensures that the attacker cannot gain access to the other portion of the encrypted private keys.

Various standard encryption practices for securely preserving keys and decrypted data rely on volatile memory while plaintext portions are loaded into cryptographic algorithms. This means that the private keys are subject to memory disclosure attacks that read unauthorized data from RAM. These attacks can be accomplished through software methods even if the integrity of the system's executable binaries is maintained, the Open SSL Heart Bleed attack for example. Physical attacks are also a potential threat, such as cold-boot attacks on RAM chips, even if the system is completely safe from software vulnerabilities [3]. Secure non-volatile storage helps alleviate this issue by ensuring that entire encryption process, including the storage of the RSA private keys, is completely secluded from the system. If the system is compromised, there is no risk of losing the stored private keys, since they are permanently attached to the TPM, and

cannot be exported, even as cyphertext. Therefore, this method blocks the attacker from gaining access to the keys in any way.

An additional core component required for adequate cryptography is a Random Number Generator (RNG). A random number generator is an instrument used to randomly generate strings of unpredictable numbers and symbols. These devices are not exclusive to cryptography, but are included in simulation environments, statistical sampling, stochastic optimization methods and image authentication watermarking. Within a software environment, a random number generator can be very close to random, but never truly random; namely, a Pseudo Random Number Generator (PSNG). PSNGs generate numbers that may seem random but are procedurally generated and can be recreated if the previous state of the PRNG is determined. This is inadequate for an effective cryptographic processor because the security of cryptographic algorithms depends on generating secret strings of data which are generated by RNGs to create cryptographic keys. To ensure that an RNG is secure, the output must be unpredictable and statistically indistinguishable from a true random sequence [4]. True Random Number Generators (TRNGs) are found to be stochastic and the same output cannot be intentionally reproduced. This is typically done by measuring a physical abnormality that is decidedly random. A trivial example could be electrical noise measured and polled to generate symbols based on the unpredictable noise with theoretically infinite entropy. Utilizing this method to generate cryptographic keys for encryption and secure storage cannot be intentionally recreated from another source, making the TRNG the ideal solution.

Lastly considered, the hardware hash is another distinct component that proves the TPM useful in contrast to a software solution. A hash is a hardware ID that is distinct to the individual device. The hardware ID typically contains information about the system, such as device serial

numbers, hard drive serial numbers, model numbers, and the manufacturer. These are some characteristics that could be described in a hardware hash, but not limited to these variables. The key here is to store information that is indicative of the device and could be used to uniquely identify this device [5]. For this use case, this feature is utilized for what is called remote attestation [6]. Remote attestation specific to this case would require a SHA-256 hash on the known hardware information at the time of startup. This hash is unique, meaning that no other input to this hashing algorithm could resolve to an identical output. Once the hash is complete, it is then compared to the next hash calculated on system startup. If the hash algorithm does not report the exact product as the previous calculation, then it is understood that the hardware has been tampered with. This protection contributes to system integrity in this case. This method is put in place to recognize any changes to the system to protect against any malicious additives.

Due to the increasing system complexity as the prototype develops, it is beneficial to offload portions of the security to help better the future overall utilization of the system, as well as providing a physical isolation provided with these types of hardware protections. As previously mentioned, the TPM provides many hardware security features useful to a full production model while taking a portion of the task handling away from the control system required for basic functionality. Though the current reference design does not utilize the full computing potential of the system, a more rigorous load on a production model could see performance benefits as well as enhanced security.

### 2.4 References

- [1] TCG, "Trusted Platform Module (TPM) Summary, " https://trustedcomputinggroup.org/wp-content/uploads/Trusted-Platform-Module-Summary\_04292008.pdf, April 2008.

- [2] J. Bethencourt, A Sahai and B. Waters, "Ciphertext-Policy Attribute-Based Encryption," 2007 IEEE Symposium on Security and Privacy (SP '07), Berkley, CA, 2007, pp. 321-334

- [3] L. Guan, J. Lin, B. Luo, J. Jing and J. Wang, "Protecting Private Keys against Memory Disclosure Attacks Using Hardware Transactional Memory," 2015 IEEE Symposium on Security and Privacy, San Jose, CA, 2015, pp. 3-19.

- [4] M. E. Yalcin, J. A. K. Suykens and J. Vandewalle, "True random bit generation from a double-scroll attractor," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 51, no. 7, pp. 1395-1404, July 2004.

- [5] Microsoft, The STRIDE Threat Model, Nov 2009. [Online] Available: https://docs.microsoft.com/en-us/windows/deployment/windows-autopilot/add-devices

- [6] Agari Inc., Secure Remote Attestation, Nov 2009. [Online] Available: https://eprint.iacr.org/2018/031.pdf

- [7] A. K. Kanuparthi, M. Zahran and R. Karri, "Feasibility study of dynamic Trusted Platform Module," 2010 IEEE International Conference on Computer Design, Amsterdam, 2010, pp. 350-355.

- [8] M. Hutter and R. Toegl, "A Trusted Platform Module for Near Field Communication," 2010 Fifth International Conference on Systems and Networks Communications, Nice, 2010, pp. 136-141.

- [9] E. A. Lee, "Cyber Physical Systems: Design Challenges," 2008 11th IEEE International Symposium on Object and Component-Oriented Real-Time Distributed Computing (ISORC), Orlando, FL, 2008, pp. 363-369.

- [10] J. Zhan, J. Huang, L. Niu, X. Peng, D. Deng and S. Cheng, "Study of the key technologies of electric power big data and its application prospects in smart grid," 2014 IEEE PES Asia-Pacific Power and Energy Engineering Conference (APPEEC), Hong Kong, 2014, pp. 1-4.

- [11] Raspberry Pi Trading Ltd., Raspberry Pi 4 Computer, June 2019. [Online] Available: https://static.raspberrypi.org/files/product-briefs/200206+Raspberry+Pi+4+1GB+2GB+4GB+Product+Brief+PRINT.pdf

- [12] Lattice Semiconductor, "MachXO2 Family Handbook," LCMX02-7000HC datasheet, May 2013.

- [13] Texas Instruments, "TMS320F2833x, TMS320F2823x Digital Signal Controllers (DSCs)," TPMS320F28335 datasheet, June 2007.

### **CHAPTER 3**

### TEST SETUP AND EXPERIMENTAL RESULTS

### 3.1 Introduction

The purpose of this section is to evaluate the vulnerabilities within the cyber-physical reference design and deploy mitigation strategies. The intent is to apply the results of this reference design prototype to a metric that will analyze the importance of each technique to gauge the impact it may have on the system. Before that happens, risks must be addressed within each layer of the design to identify the correct mitigation strategies that could be applied to the available attack surface. The base reference design does not contain any security features, which exposes the system to outsider threats. To protect these openings from malicious intent, the openings must first be discovered by determining which data or operations are valuable to the system. If the data is considered essential for operation, chances are that an attacker will be able to exploit this data against the user. It is important to realize where these weaknesses exist in the system in order to protect against them. Finding the exposures in the system defines the attack surface, where one can establish corrective measures to combat these deficiencies. Particular to the reference design mentioned, the test setup will elaborate on the attack surface considered and the approach taken to alleviate defined concerns. Every layer considered will have specific obstacles that require various levels of attention, which are determined by the significance behind each level being compromised. This will classify considered threats, determine what a malicious attack might look like, and measure, to what degree, it will affect the system.

### 3.2 Communication Layer Assessment and Results

As mentioned in the introduction, to prepare any layer for test, an assessment must be performed to understand the system and its vulnerabilities. The communication layer

encompasses all contact dealt outside the system, where much of this interaction occurs within the Raspberry Pi. Logically, this makes sense, considering the intention of installing the Raspberry Pi into the reference design was primarily to disclose information from the system. However, knowing that the attack surface within this layer consists of the Raspberry Pi, the next step is to learn the vulnerabilities of this portion of the system; namely, how important roles in this layer can be at risk of being attacked. Referenced in Chapter 1, the CIA Triad can contribute to discerning what threats are necessary to protect against. The confidentiality of the data is the greatest concern because the data could be used against the user in the event of exposure. Put simply, the confidentiality of the communication layer is the first step into realizing the vulnerabilities brought by disclosing sensitive information.

Cyber-physical systems rely on communications as a large portion supporting the functionality of the system. It is imperative that data traverse in and out of the system layers to function properly. That said, the user must prohibit interaction of this data with an assailant, or the data may be taken and manipulated to be exploited against the user. Once the attack surface is identified, understanding how to protect certain data and communication paths is done by realizing the vulnerabilities of the attack surface. To help determine how the data is at risk, the storage and transmission medium are decided to be an influential point of contact for malicious activity. Namely, how the data is being sent and stored must be protected. Due to the webserver being the main point of contact from outside the system, it was decided to direct the attack vector towards the outgoing communication path of the system, directly from the Raspberry Pi. To enhance visualization of the communication path in the test setup, Figure 3.1 will illustrate the path and protocol connecting these devices together.

Figure 3.1. Communication path diagram.

Confidentiality is a concern in many areas of communication security and cyber-attack methods that target and identify data in a system. There are many attack scenarios, or attack vectors, to consider; however, this reference design has decided to focus on two critical attack methods for the communication layer. These two attacks are Man-in-the-Middle attacks and Password Attacks, or password cracking. Other possible attack scenarios to be addressed can be considered for other design implementation. These are common attack categories when considering data sharing between one entity and another. In this case, the entities are the web

server and another endpoint device; whether it be a utility/client handled interface or data storage. Man-in-the-Middle attacks typically focus on any data that can be intercepted between the web server and an endpoint [3]. A password hack can take this approach one step further by "sniffing" for specific details (i.e. user credentials) when using a Man-in-the-Middle attack.

Initially, to secure this communication pipeline to the user interface, the SSH or Secure shell protocol was to be used for the user to access the web server from a remote terminal. Once implemented, this created a secure pipeline into the raspberry pi, where the web server is running. The TPM would then oversee encrypting this communication algorithm, while device communication was dormant. This implementation had a couple drawbacks to be considered. First, the SSH tunnel is secured in a similar manner to other transport layer protocols, such as TLS; however, this would grant the end user far too much access to the system outside of the web server. This is not recommended. If the authentication fails, an unauthorized user will have much more access to the system, which is not desired for malicious individuals. Secondly, this is a reference design meant for a power electronics engineer that is looking to develop production hardware, such as a commercial solar inverter. Having to log into the system, to manually run programs required to start the server, would be simple to a developer that is familiar with the backend, but this is not a practical production method. Also, the TPM was not being fully utilized, as it was only being used during down time. No end user would necessarily have the knowledge or the desire to deal with such maintenance overhead with a product. It simply is not enticing as a selling point and has little marketable value.

Alternatively, the web server requires remote access, to multiple users, that does not relinquish administrator access to the entire system. Using SSL, or Secure Sockets Layer, the traffic to and from the Raspberry Pi would be encrypted using TLS v1.3. This method is like

SSH encryption, in that the communication path is completely secure; however, this method only pushes requested data that the web server permits. The SSL link communicates directly with the web browser which can be used on multiple platforms by the end user, to access the data and control the system. Standard websites can be accessed through the web browser by a Hypertext Transfer Protocol (HTTP) link which is strictly an application layer protocol. With SSL, the Hypertext Transfer Protocol Secure (HTTPS) can be utilized to meet the TLS v1.3 standard. Using this method, the user is restricted from any content that the web server does not wish to publish outside of the system.

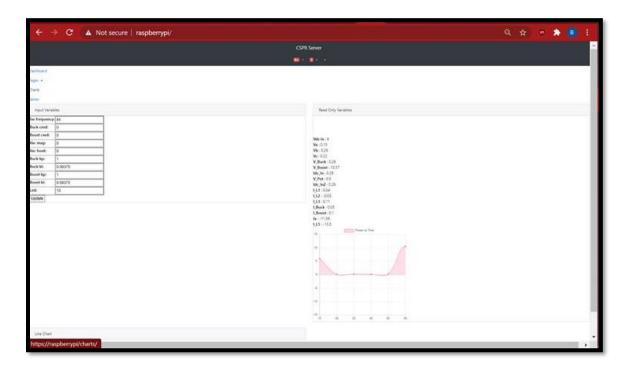

### 3.2.1 Web Server Implementation Overview

As mentioned in the previous section, the web server within the communication layer is one way in which the control layer can communicate information to the computer interface. Running the server on a Raspberry Pi 4 was a choice made for easy connectivity to the TPM. This decision was also made to host a Linux kernel, using a Raspberry Pi 4, for connecting an Apache HTTP server, that hosts the back end, with the Django web framework, which is in charge of the higher level web design [3, 4]. The web server interface can be viewed in any modern web browser such as Safari, Firefox, and Google Chrome. A preview of the web server user interface can be seen in Figure 3.2. The data shown in the interface is split into two different types: read and write variables. The read only variables are considered to simply be sensory data. This is data that you would never need to manually manipulate such as voltage and current readings. On the other hand, write variables are the control parameters that are put in place to manage the system in real time. These variables consist of the switching frequency, PI gain parameters, ac amplitude and frequency, and other parameters. Because the use of Django is incredibly versatile, the web interface is very flexible in that the developer has almost limitless

potential as to what data they want to display to the end user. An example of this is a simple graph, also depicted in 3.2, displaying the power over time plot. As long as data is accessible, the web interface can be built to incorporate new information. Django, as well as Apache, will be discussed in more detail below.

Figure 3.2. CSPR web server user interface.

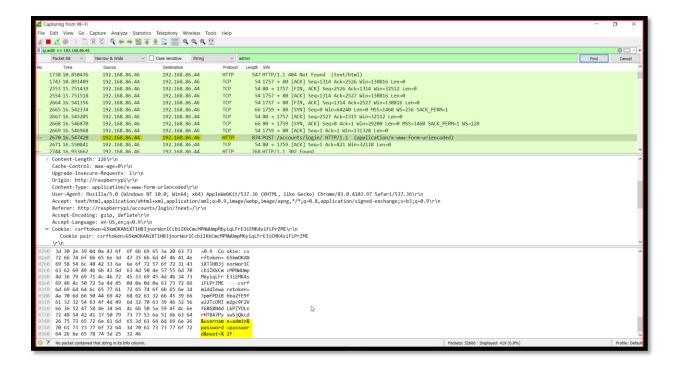

The two main components, Apache and Django, are critical to communication and displaying material to the end user. Apache is an HTTP server host for modern operating systems that meets current HTTP standards. There are many standard configuration parameters that allow for complete control of the server. Where security is concerned, the Apache server also has an HTTPS configuration being utilized in this system. This configuration adds additional security by protecting the user and server communication from attacks, such as man-in-the-middle attacks or password sniffing, using certificate authority and enhanced TLS v1.3 encryption. In typical HTTP traffic, all communication is sent over as unencrypted data, also known as plain text. This

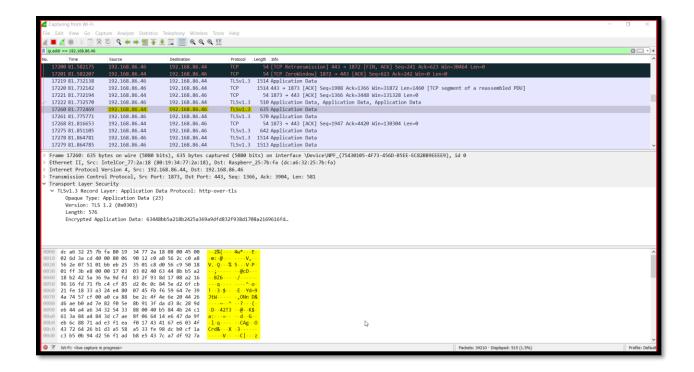

means that anyone with access to that line of communication, another user on the network for example, could interpret this data without any additional difficulty. To show an example of this, a test was initiated to try and obtain the credentials of a user logging in to a web server using a basic HTTP connection. In order to gain access to the web server data, the user must login, with approved credentials, to the main webpage. To capture network data, Wireshark v3.2.4 was used. Wireshark is a widely used network protocol analyzer that allows the user to monitor network activity at a very low level. This enables the network traffic to be monitored down to each induvial packet. Since the initial data was not protected by HTTPS, the account username and password were easily discovered in the network traffic. This test can be depicted in Figure 3.3. The highlighted regions show the starting and endpoint destinations as well as a verification of the HTTP protocol being used. Also highlighted below is the HTTP packet payload, which is comprised of the username "admin" and password "password"; each being unencrypted.

To prevent this issue, the Apache server will shift to the HTTPS, or SSL, configuration. In order to utilize the Apache SSL configuration, the server will first need to generate an SSL certificate. An SSL certificate is a file that typically resides on the server, hosting the website. This SSL certificate will also enable the SSL/TLS encryption as a result of holding the public key, and other important information to the web server. One drawback to normal server SSL certificate storage is the placement of the key used for the certificate generation.

Figure 3.3. HTTP packet Wireshark monitor.

If an assailant were to compromise the server SSL certificate, the attacker may gain unrestricted access to the system, as well as access to other users. To secure this certificate, the certificate can be stored in or protected by the TPM. Infineon claims, the greatest strength to the TPM is to enable an application the use of cryptographic keys, while keeping them safe within the TPM. It can both generate and import externally generated keys. Each key has individual security control, which could be a password or also an enhanced authorization policy. These keys can then be certified by the TPM and used to certify other keys as well. But in order to manage internal memory efficiently, the TPM has the capability to wrap keys (encrypt) within the parent key and store them (the encrypted key) outside the TPM, while maintaining the overall security of the system. When it is time to use the key, the key is loaded back into the TPM. Only the specific TPM used to wrap the key can unwrap and use it. To establish a TLS session between a client and server with OpenSSL and TPM2-TSS engine, one must create an Open SSL configuration

file. This file will have the configuration used to create the Root Certificate Authority (rootCA), server, and client certificates [5]. One can now create a Root CA which would establish a chain of trust to the end user, allowing for the secure connection between certificate authority and end users.

Figure 3.4. TPM 2.0 key wrapping [5].

Once the key has been generated and used to create the OpenSSL server certificate, the server can fully utilize the SSL configuration to host an HTTPS web server. The beginning of the session flow will show client and server greetings and acknowledge the key exchange. This can be viewed in Figure 3.5. Stated previously for this implementation, the focus is less on how the communication happens, but more on the confidentiality of the communication. Here, the TPM is an added layer of security, but not fully necessary to realize basic confidentiality of the HTTP packets. Regardless, the next step is to verify that this method can properly converse data to the end user without revealing information along the transmission path. To test this, a similar setup to the previous HTTP packet sniffing test was enacted, aiming to determine the contents of the packet payload. The same login process being tested was considered for the HTTPS service, as was HTTP. The results remained that each TLS packet was illegible, as expected. Seen in Figure

3.6. HTTPS packet Wireshark monitor, the user and endpoint address locations are the same as before, but now the packet type is TLS v1.3, encrypting the entire packet. The further highlighted section displays the properly encrypted payload with no legible login information confirming confidential communications.

Figure 3.5. OpenSSL client/server session flow [5].

Figure 3.6. HTTPS packet Wireshark monitor.

# 3.3 Control Layer Assessment and Results

Through this assessment of the control layer, the most critical concept to consider is maintaining the integrity of the control layer throughout the design process. The chosen area of focus is the DSP where all the power electronic controls are physically operating. To maintain this integrity means to keep the data free from corruption. In order to do this, the system must be monitored for what is considered "bad data" and compared to what is believed to be "good data." The system has current and voltage sensors that are measuring components of the 3-phase inverter in order to monitor the system health. The current and voltage sensors values are delivered to the control system through Analog-to-Digital Converters (ADC). As the name states, the ADC converts the analog voltages from the sensors to a 12-bit binary number stored within registers on the DSP, by successive approximation. More on how successive approximation works in [6]. With this value, the voltages can be compared digitally to one another for a system

health assessment. If the assessment fails to meet expected benchmarks, the system can be disconnected, or turned off, to prevent damage. This is whether the damage is from malicious intent or mechanical hardware failure.

For this test, the phase-A voltage is monitored under normal 3-phase load conditions. To obtain power flow, in this case, a low voltage 3-phase motor is acting as the load to achieve a constant 3-phase output. Once power is flowing, the voltage can be monitored and saved as a known legitimate value for comparing against unwanted measurement conditions. Measurements during test are polled by the ADC rapidly, but only saved periodically when each Modbus packet is transmitted, in order to insert a small delay to account for voltage noise transients. This is done for a couple reasons. The first reason being code simplicity that will require less system interrupts. Secondly, the Modbus transmission time is defined and can change to meet the needs of the system. Once polled, the value is stored in a register until the next cycle. When the measurement reoccurs in during the next cycle, the value is stored in another concurrent register to compare the current and previous voltage values. This is a similar approach to what some consider "de-bouncing." Essentially, the purpose of this method is to verify that the voltage has maintained it's value for some period longer than noise transients would typically occur. This technique will help rule out false positive evaluations on poor voltage readings.

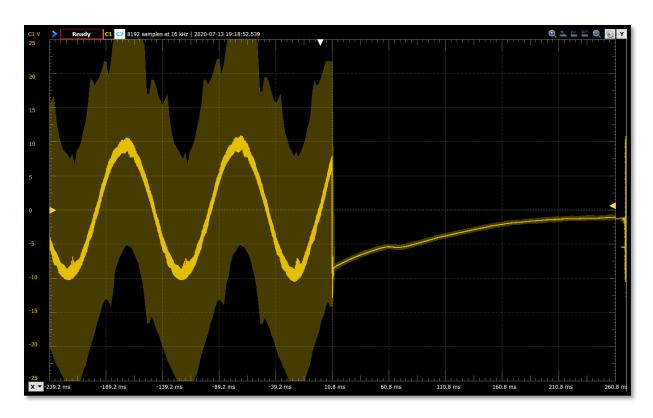

The system will rule that a bad condition has occurred when three consecutive hazardous voltage readings have been interpreted. If this occurs, the voltage amplitude will be commanded to zero, for the output of each phase. Following the test, the data was collected and can be observed in Figure 3.7. The beginning of the phase-A voltage output reading is observed as a typical ac sinusoidal waveform. This ac output voltage is directly related to the dc link input voltage of the inverter. Rather than feeding the ADC faulty data, the dc link input voltage was

incremented to physically step up the output voltage, and push the ADC reading out of a decidedly valid boundary. The results of this can also be seen in Figure 3.7 where the voltage is commanded to zero on the phase-A voltage leg. Do note that the output capacitor voltage takes time to bleed off into the load, which is the reason there is not an instantaneous jump to zero volts.

Figure 3.7. Phase-A voltage cutoff.

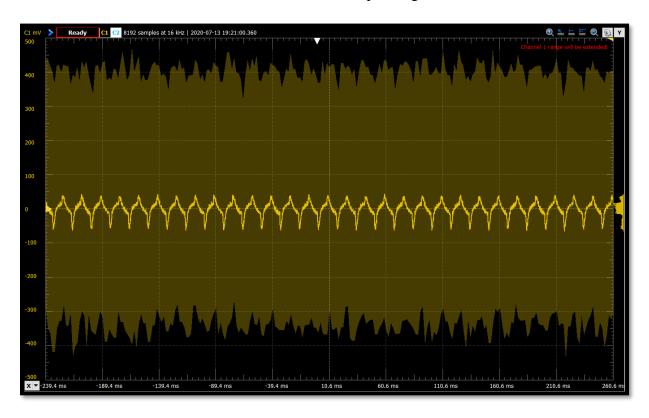

During the invalid output condition, it is important to note that the amplitude is simply commanded to zero, rather than the system being completely shut down. This can be verified in Figure 3.8, showing that low voltage switching noise can be seen once the output is commanded to zero. The system is not shut down entirely so that the other essential components can continue to be monitored, or changed, to combat the system failure, malicious or not. Once the output is commanded to zero, corrective measures can be taken to verify the state of the system and the

output. Whereas, if the entire system went without power, the system would possibly need to be isolated from the circuit before evaluation under safe operating conditions.

*Figure 3.8. Phase-A low voltage output switching.*

## 3.4 Hardware Layer Assessment and Results

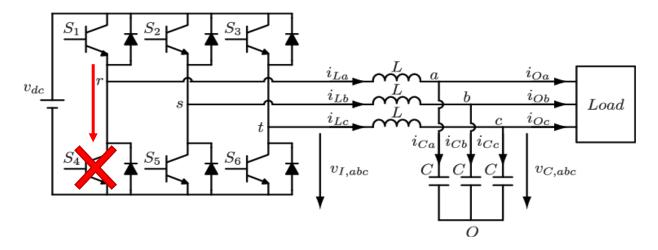

The leading focus of the hardware layer assessment will be the availability of the hardware. Meaning, that the hardware needs to be safe from defects or compromised controls. The chosen attack vector will target shoot-through currents on the individual legs of the inverter. The mitigation strategy of choice is forced dead band to employ shoot-through protection. Shoot-through occurs when two adjacent switches are active concurrently, resulting in a short circuit across the dc link. This is a key challenge when designing an effective protection approach, because the short circuit loop must be blocked in a very short time period, 3 to 10 µs [7]. A standard 3-phase inverter is shown in Figure 3.9, where the shoot through current can be

observed through leg one of the inverter, possibly destroying switch S4. The high current often comes from the dc link capacitor in parallel with the dc voltage source, which has stored energy that is now shorted across the switching leg. Typical shoot through current, seen longer than 10 µs, can be fatal to the switches as they are not made to handle that much current instantaneously.

Figure 3.9. Basic 3-phase inverter topology.

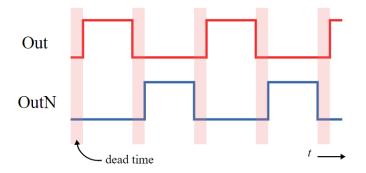

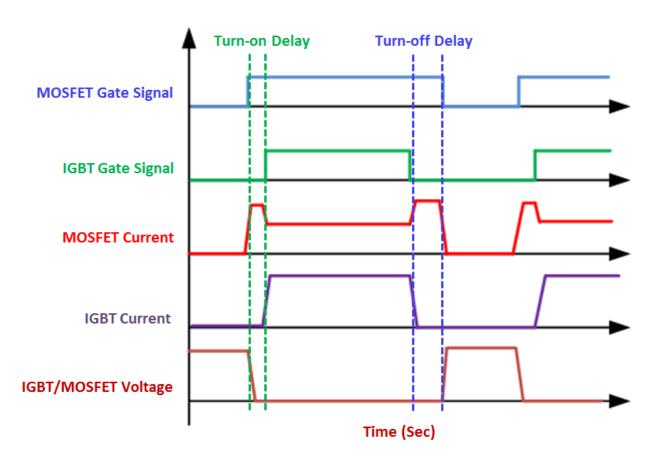

To protect against shoot through currents, most control systems implement dead time. Dead time is the time in between switching periods where neither switch is conducting, as to not short circuit the dc bus to ground. Ideally, the switches turn on and off instantaneously, but this is not the case in practice. Ideal dead time effect can be seen in Figure 3.10. A diagram of more accurate switching period waveforms can be seen in Figure 3.11. To learn more about the dead time effect, [8] does a good job of explaining the fundamentals when applied to a standard 3-phase PWM inverter.

Figure 3.10. Dead time effect.

Figure 3.11. Accurate on/off delay wave forms.