## University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

5-2020

# Investigations of New Fault-Tolerant Methods for Multilevel Inverters

Haider Mhiesan University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Power and Energy Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### Citation

Mhiesan, H. (2020). Investigations of New Fault-Tolerant Methods for Multilevel Inverters. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3701

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

# Investigations of New Fault-Tolerant Methods for Multilevel Inverters

## A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Haider Mhiesan

University of Kufa

Bachelor of Science in Electrical Engineering, 2007

University of Arkansas

Master of Science in Electrical Engineering, 2016

## May 2020 University of Arkansas

| This dissertation is approved for recomme     | endation to the Graduate Council. |  |

|-----------------------------------------------|-----------------------------------|--|

|                                               |                                   |  |

| H. Alan Mantooth, Ph.D. Dissertation Director |                                   |  |

| Roy McCann, Ph.D.                             | Yue Zhao, Ph.D.                   |  |

| Committee Member                              | Committee Member                  |  |

| Cynthia Sides, Ph.D. Committee Member         |                                   |  |

#### **ABSTRACT**

The demands of power electronics with high power capability have increased in the last decades. These needs have driven the expansion of existing power electronics topologies and developing new power electronics generations. Multilevel inverters (MLI) are one of the most promising power electronics circuits that have been implemented and commercialized in high-voltage direct current (HVDC), motor drives, and battery energy storage systems (BESS). The expanding uses of the MLI have lead to creation of new topologies for different applications. However, one of the disadvantages of using MLIs is their complexity. MLIs consist of a large number of switching devices, which can result in a reduction of system reliability. There are significant challenges to the design of a reliable system that has the MLI's capability with integrated fault-tolerance. In other words, design a system that can handle the fault, totally or partially, while maintaining high power capabilities and efficiency.

This aim of this dissertation is to investigate the fault-tolerance of MLIs from two different points of view:

- 1- Develop new solutions for existing MLI topologies. In other words, add some features to existing MLIs to improve their reliability when a fault occurs.

- 2- Design new MLIs that have a fault-tolerant capability.

A new open-circuit fault detection is proposed in this dissertation. The new fault detection method is based on monitoring the output voltage of each cell and leg voltage polarity along with each switch state. By monitoring each cell output voltage and leg voltage, the faulty cell can be detected and isolated.

A novel circuit to maintain system operation under the condition of one (or more) components suffering from a faulted condition is also proposed in this dissertation. This results in a topology that continues to operate at full capability.

Additionally, a new topology is proposed that offers reducing the number of batteries by 50%. Also, it has the ability to operate under non-unity power factor, which enables it to be suitable for battery energy storage systems, and static compensator (STATCOM) applications.

Another novel hybrid cascaded H-bridge (CHB), known as the X-CHB, for a fault-tolerant operation is proposed in this dissertation. It ensures seamless operation of the system under an open/short circuit switching fault or dc supply fault.

© 2020 Haider Mhiesan All Rights Reserved

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Prof. H. Alan Mantooth for helping me along this journey. To my committee, Profs. Roy McCann, Yue Zhao, and Cynthia Sides, thank you for taking the time to be a part of my committee. I appreciate the help from the colleagues, and friends on my dissertation work: Vinson Jones, Chris Farnell, Shuang Zhao, Joe Moquin and Hazzaz Mahmud. My gratitude also goes to my colleagues: Janviere Umuhoza, Kenneth Mordi, Dereje Woldegiorgis, Yuqi Wei, Robert Murphree, Maksudul Hossain, Luciano Garcia, Nicholas Blair, Rosten Sweeting III, Justin E. Jackson, Estefano Soria, and Sloan Becker.

Special thanks to the GRid-connected Advanced Power Electronics Systems (GRAPES) research center for the funding of my dissertation work.

Special thanks to the National Center for Reliable Electric Power Transmission (NCREPT) center for always making sure I have what I need. Thank you, Chris!

Last, but certainly not least, thank you to my entire family for always supporting me with everything that I do, especially my parents. I wouldn't be here if it wasn't for you all. Thank you.

# **DEDICATION**

| TT1 ' 1'          | . 1 1.                | 1 .              | · · · · · · · · · · · · · · · · · · · | 1 1 1 1                |

|-------------------|-----------------------|------------------|---------------------------------------|------------------------|

| This dissertation | n ic dadicata         | to my noran      | to my with and                        | n my zide              |

| THIS CHASCHAIL    | <i>.</i> 18 UCUICAICI | I IO IIIV DAIGI  | is invwingani                         | I IIIV KIUS.           |

| TIIID GIDDOITGG   | ii ib acaicate.       | * co iii, paicii | co, iii , viii c caii                 | <i>-</i> 111 / 111000. |

# TABLE OF CONTENTS

| CHAPTER 1                                                                     | 1  |

|-------------------------------------------------------------------------------|----|

| 1.1 Motivation and Problem Statement                                          | 1  |

| 1.2 Organization of the Dissertation                                          | 3  |

| CHAPTER 2                                                                     | 6  |

| 2.1 Reliability Considerations for MLIs                                       | 6  |

| 2.2 Fault Diagnostic Survey                                                   | 10 |

| 2.3 Reconfiguration Survey                                                    | 12 |

| 2.4 References                                                                | 17 |

| CHAPTER 3                                                                     | 20 |

| 3.1 Introduction and Motivation                                               | 20 |

| 3.2 System Description                                                        | 20 |

| 3.2.1 CHB Inverter and Modulation Strategy                                    | 21 |

| 3.2.2 Behavior Analysis of the CHB under Open-Circuit Faults                  | 24 |

| 3.2.3 Effect of Open-Circuit Fault                                            | 32 |

| 3.3 Quantified Description of CHB Under OC Fault                              | 32 |

| 3.4 Open-Circuit Fault Cell Detection                                         | 35 |

| 3.4.1 Identification of the Faulted Switch and Isolation                      | 37 |

| 3.5 Simulation Results of the Proposed Method                                 | 39 |

| 3.6 Experimental Results of the Proposed Method                               | 42 |

| 3.7 Conclusions                                                               | 46 |

| 3.8 References                                                                | 47 |

| CHAPTER 4                                                                     | 48 |

| 4.1 Introduction                                                              | 48 |

| 4.2 Operating of the Proposed Circuit                                         | 48 |

| 4.3 Analysis of Fault-Tolerant Operation in Different Scenarios               | 51 |

| 4.3.1 Case 1 - S <sub>11</sub> Has an Open-Circuit Fault                      | 52 |

| 4.3.2 Case 2 - S <sub>12</sub> Has an Open-Circuit Fault                      | 55 |

| 4.3.3 Case 3 - S <sub>13</sub> Has an Open-Circuit Fault                      | 57 |

| 4.3.4 Case 4 - S <sub>14</sub> Has an Open-Circuit Fault                      | 58 |

| 4.3.5 Case 5 - S <sub>11</sub> , and S <sub>12</sub> Have Open-Circuit Faults | 58 |

| 4.3.6 Case 6 - S <sub>21</sub> and S <sub>22</sub> Have Open-Circuit Faults                                     | 60  |

|-----------------------------------------------------------------------------------------------------------------|-----|

| 4.3.7 Case 7 - S <sub>11</sub> , S <sub>12</sub> , S <sub>21</sub> and S <sub>22</sub> Have Open-Circuit Faults | 60  |

| 4.4 Comparison                                                                                                  | 60  |

| 4.5 Simulation and Experimental Results                                                                         | 61  |

| 4.6 Conclusions                                                                                                 | 66  |

| 4.7 References                                                                                                  | 67  |

| CHAPTER 5                                                                                                       | 68  |

| 5.1 Introduction and Motivation                                                                                 | 68  |

| 5.2 Proposed Multilevel Boost X-CHB Inverter                                                                    | 69  |

| 5.2.1 Generalized X-CHB MLI                                                                                     | 69  |

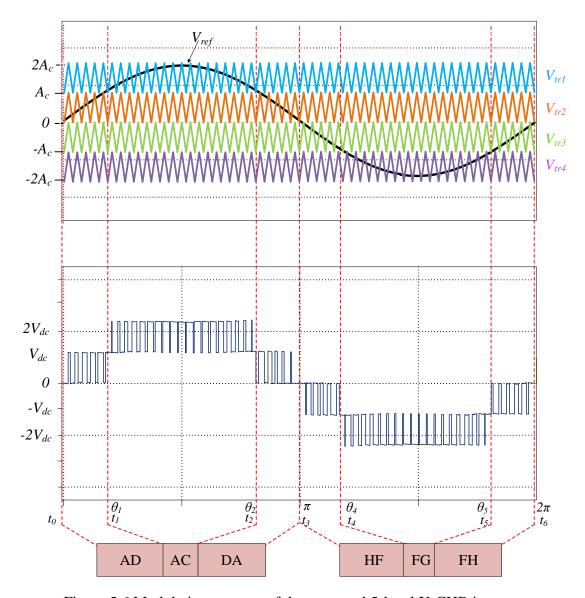

| 5.2.2 5-L Boost X-CHB Inverter                                                                                  | 72  |

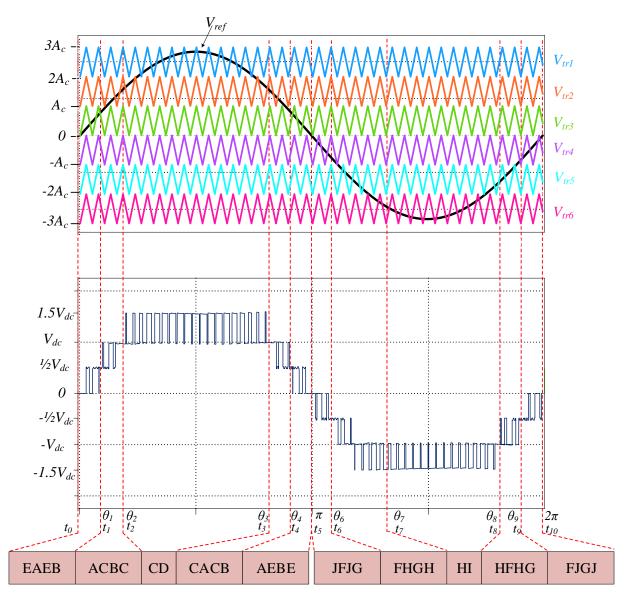

| 5.2.3 7-L Boost X-CHB Inverter                                                                                  | 75  |

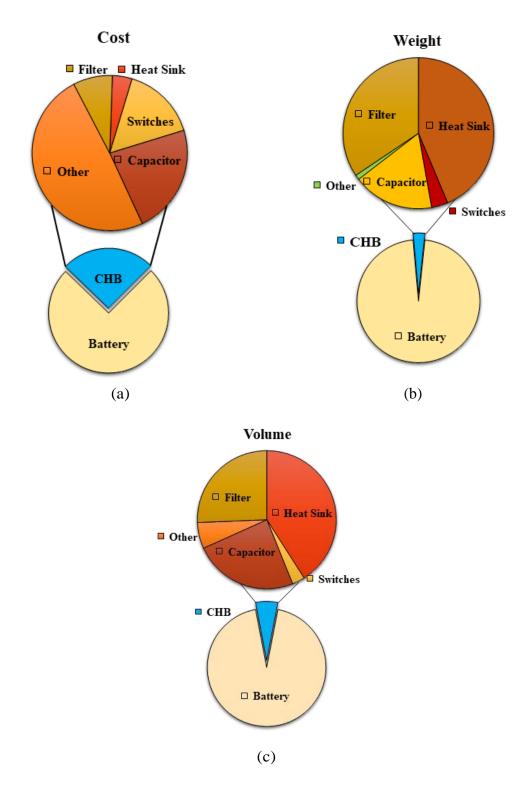

| 5.3 Cost/Weight/Volume Analysis                                                                                 | 78  |

| 5.4 Fault-tolerant Ability                                                                                      | 79  |

| 5.5 Comparison with other Topologies                                                                            | 81  |

| 5.5.1 5-L Boost X-CHB                                                                                           | 81  |

| 5.5.2 7-L Boost X-CHB                                                                                           | 83  |

| 5.6 Flying Capacitor Design                                                                                     | 84  |

| 5.6.1 5-Level Inverter                                                                                          | 84  |

| 5.6.2 7-Level Inverter                                                                                          | 86  |

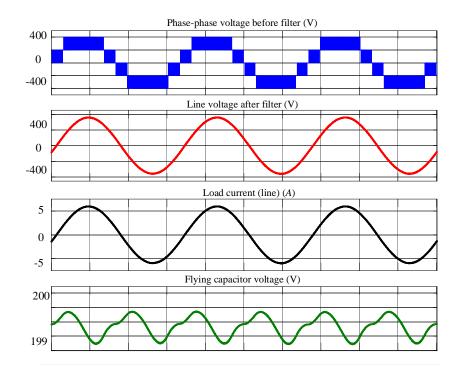

| 5.7 Simulation Results                                                                                          | 88  |

| 5.8 References                                                                                                  | 95  |

| CHAPTER 6                                                                                                       | 98  |

| 6.1 Introduction and Motivation                                                                                 | 98  |

| 6.2 Proposed Hybrid CHB                                                                                         | 102 |

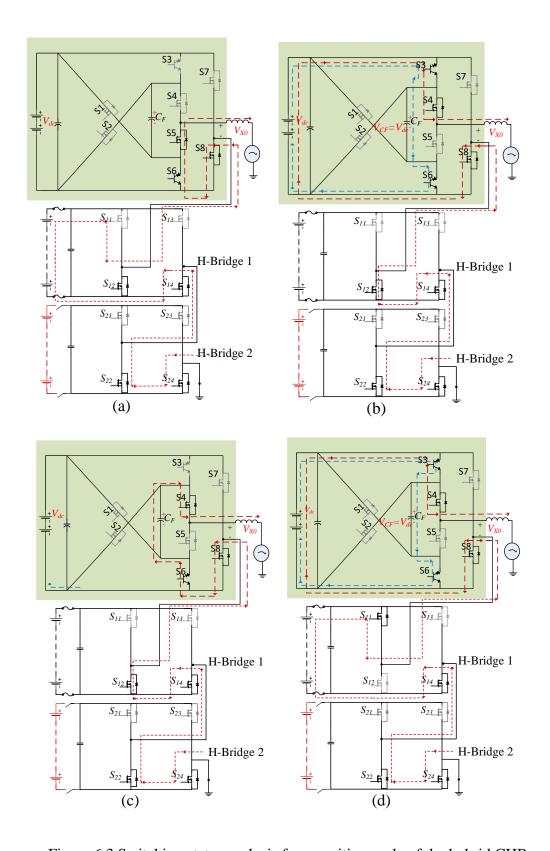

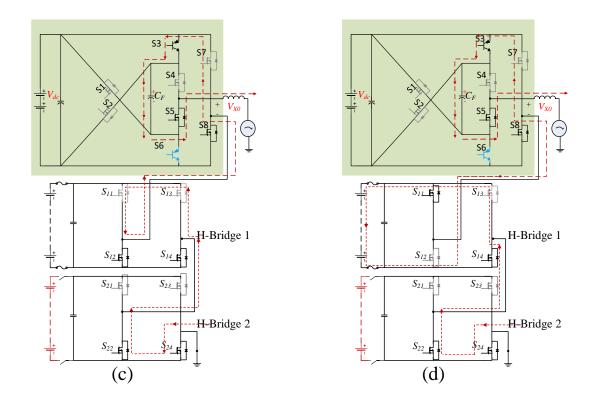

| 6.3 Operation Modes for the Proposed Hybrid CHB System                                                          | 103 |

| 6.3.1 Introduction to the Proposed Topology                                                                     | 103 |

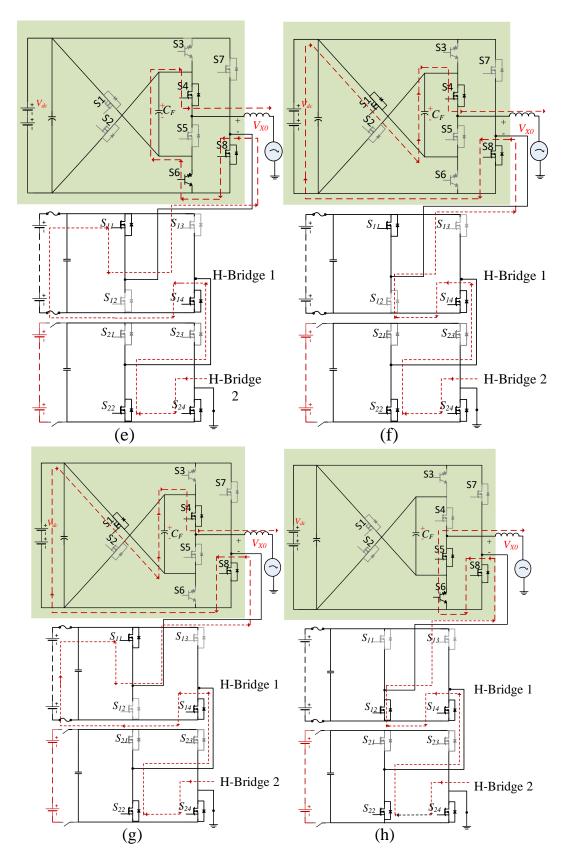

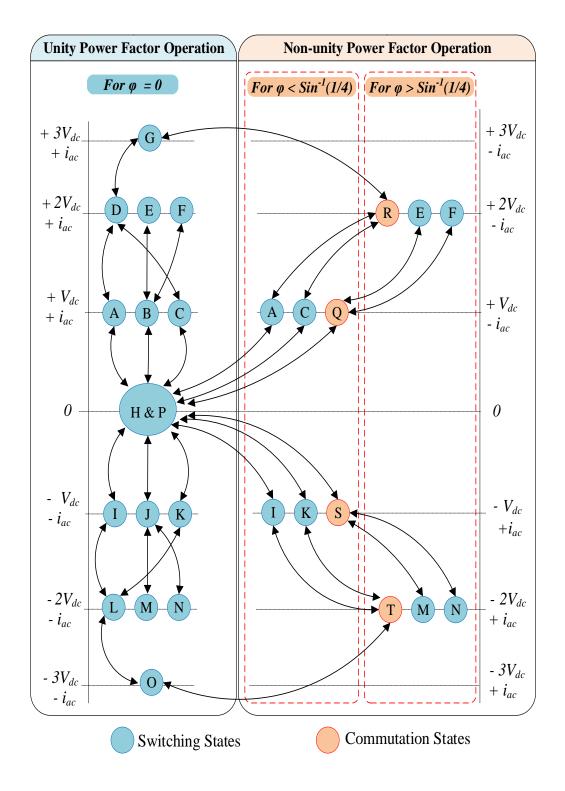

| 6.3.2 Operation of the Proposed Topology                                                                        | 104 |

| 6.4 Modulation Strategy                                                                                         | 109 |

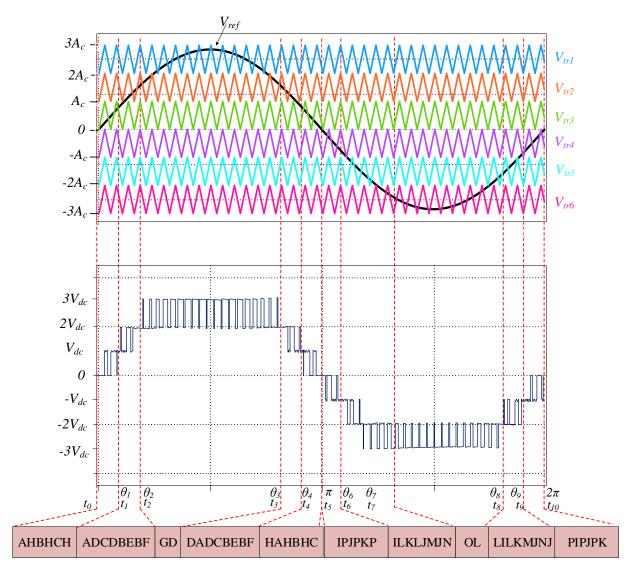

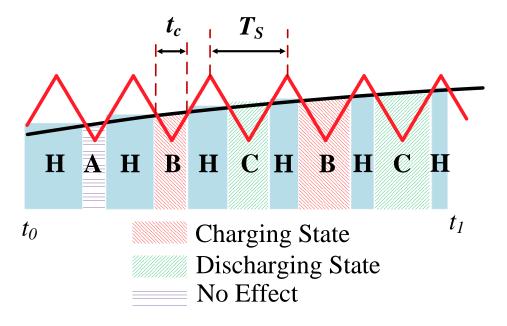

| 6.4.1 Unity Power Factor Operation                                                                              | 109 |

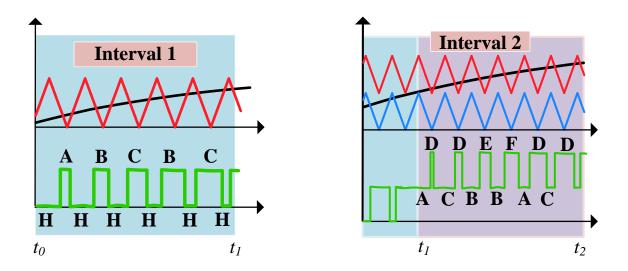

| 6.4.2 Interval 1 (t <sub>0</sub> to t <sub>1</sub> and t <sub>4</sub> to t <sub>5</sub> )                       | 110 |

|                                                                                                                 |     |

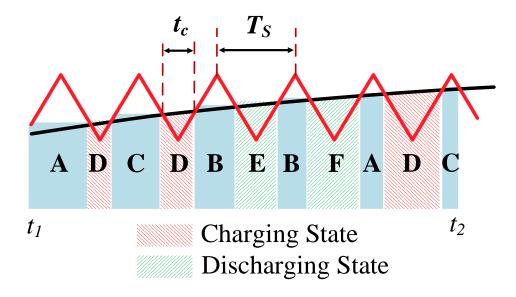

| 6.4.3 Interval 2 (t <sub>1</sub> to t <sub>2</sub> and t <sub>3</sub> to t <sub>4</sub> )  | 112 |

|--------------------------------------------------------------------------------------------|-----|

| 6.4.4 Interval 3 (t <sub>2</sub> to t <sub>3</sub> )                                       | 112 |

| 6.4.5 Interval 4 (t <sub>5</sub> to t <sub>6</sub> and t <sub>9</sub> to t <sub>10</sub> ) | 113 |

| 6.4.6 Interval 5 (t <sub>6</sub> to t <sub>7</sub> and t <sub>8</sub> to t <sub>9</sub> )  | 113 |

| 6.4.7 Interval 6 (t <sub>7</sub> to t <sub>8</sub> )                                       | 114 |

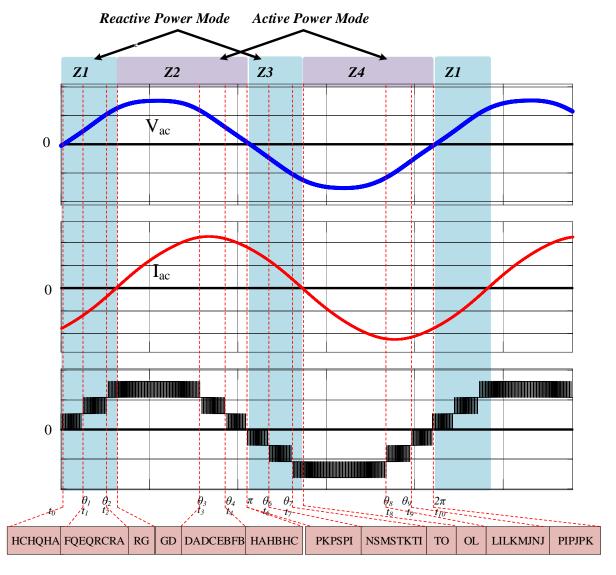

| 6.4.8 Non-Unity Power Factor Operation                                                     | 114 |

| 6.5 Flying Capacitor Design                                                                | 119 |

| 6.6 Simulation and Experimental Results                                                    | 120 |

| 6.7 Conclusions                                                                            | 130 |

| 6.8 References                                                                             | 131 |

| CHAPTER 7                                                                                  | 135 |

| 7.1 Conclusions                                                                            | 135 |

| 7.2 Future Work                                                                            | 136 |

| 7.2.1 PV Inverters                                                                         | 136 |

| 7.2.2 Electric Drives                                                                      | 137 |

| 7.2.3 High Power SiC Modules and Batteries                                                 | 137 |

|                                                                                            |     |

# LIST OF FIGURES

| Figure 1.1 Dissertation two-fold goal of achieving fault-tolerant solutions for new and existing multilevel inverters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Organization of the novelty chapters of this dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2.1 Distributions of faults in a power converter [2.7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 2.2 Distributions of fragile components [2.6].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

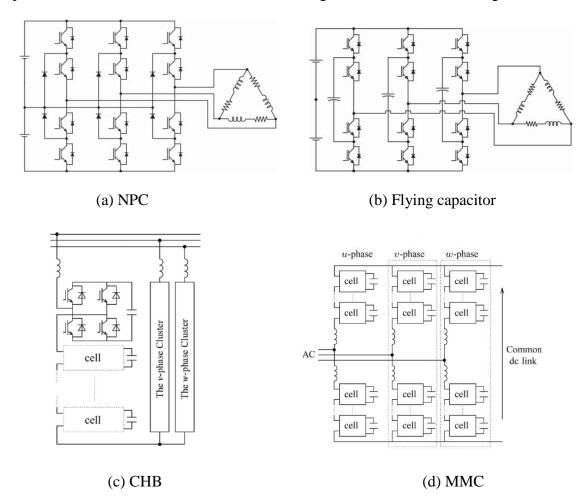

| Figure 2.3 MLI configurations (a) Neutral Point Clamped (NPC), (b) Flying Capacitor, (c) Cascaded H-Bridge, and (d) Modular Multilevel [2.9]                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

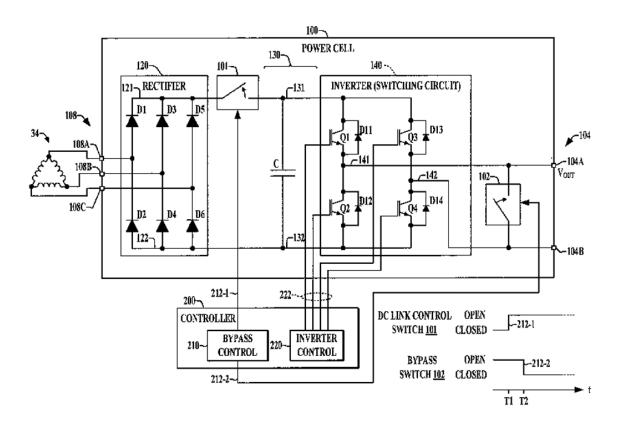

| Figure 2.4 A fault reconfiguration method using additional electromagnetic contactors (relays) in each cell [2.25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 2.5 A fault reconfiguration method using additional electromagnetic contactors (relays) in each cell [2.27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

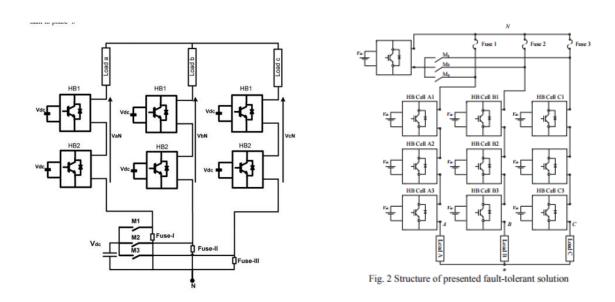

| Figure 2.6 Redundant reconfiguration methods [2.35]-[2.36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

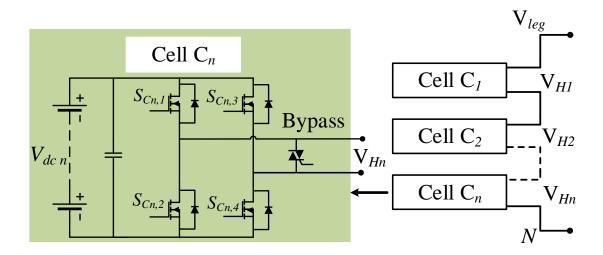

| Figure 3.1 Schematic of a CHB inverter leg. 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

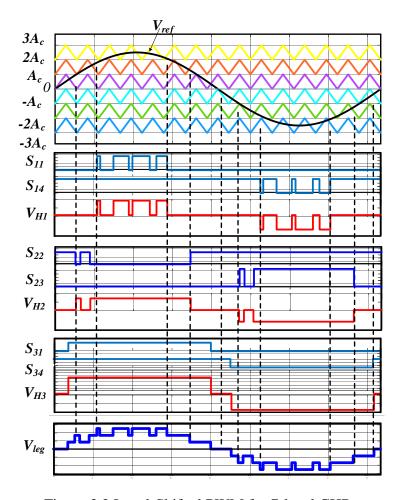

| Figure 3.2 Level-Shifted PWM for 7-level CHB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

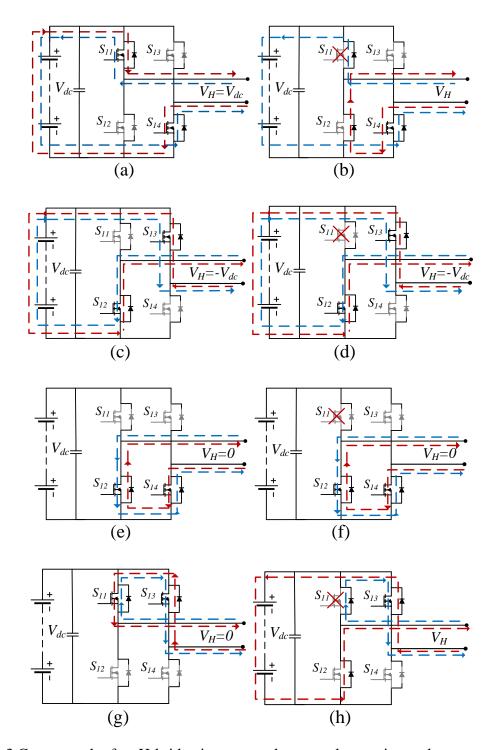

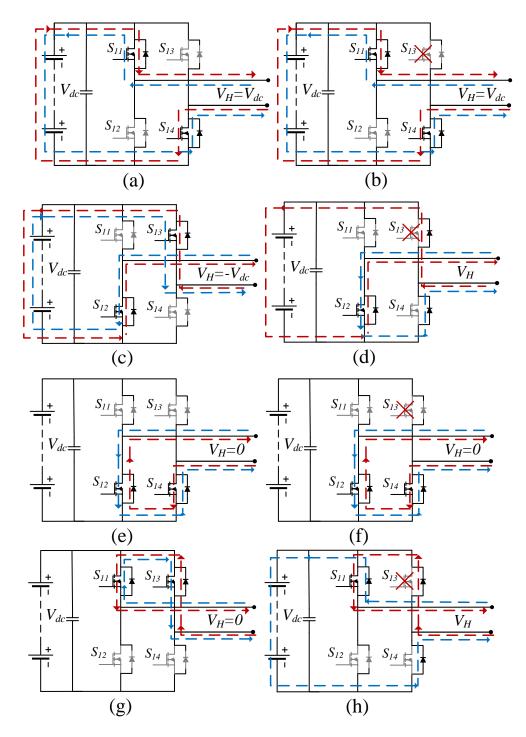

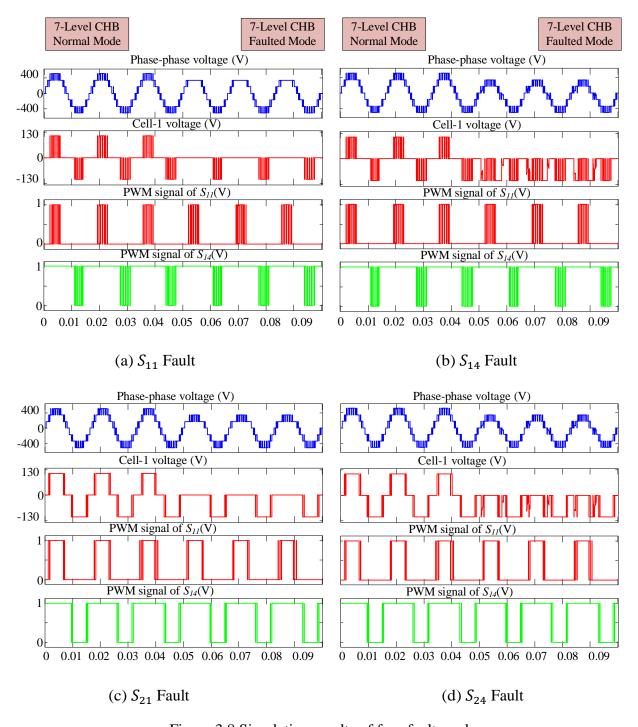

| Figure 3.3 Current path of an H-bridge inverter under normal operation and an open-circuit switch fault on $S11$ : (a) Normal operation, $S11$ , and $S14$ are turned-on, (b) an open-circuit switch fault on $S11$ , (c) Normal operation, $S12$ , and $S13$ are turned-on, (d) an open-circuit switch fault on $S11$ , (e) Normal operation, $S12$ , and $S14$ are turned-on, (f) an open-circuit switch fault on $S11$ ,(g) Normal operation, $S11$ , and $S13$ are turned-on, and (h) an open-circuit switch fault on $S11$ . The red dotted line represents $i > 0$ , and the blue $i < 0$ |

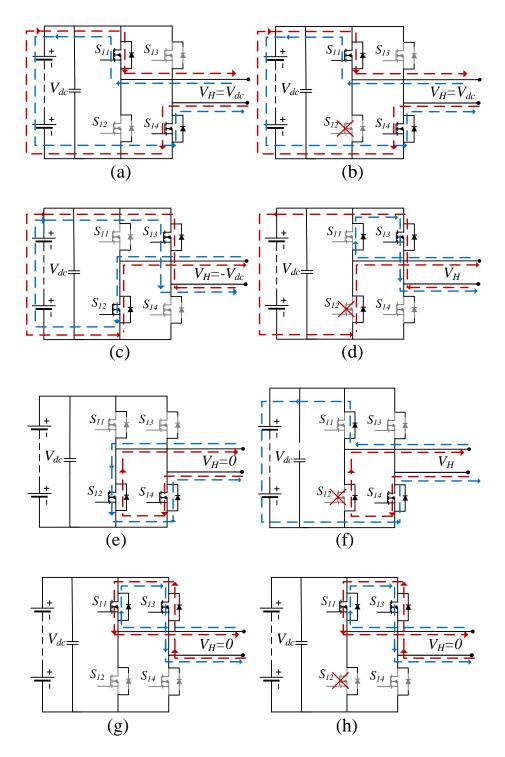

| Figure 3.4 Current path of an H-bridge inverter under normal operation and an open-circuit switch fault on $S12$ : (a) Normal operation, $S11$ , and $S14$ are turned-on, (b) an open-circuit switch fault on $S12$ , (c) Normal operation, $S12$ , and $S13$ are turned-on, (d) an open-circuit switch fault on $S12$ , (e) Normal operation, $S12$ , and $S14$ are turned-on, (f) an open-circuit switch fault on $S12$ ,(g) Normal operation, $S11$ , and $S13$ are turned-on, and (h) an open-circuit switch fault on $S12$ . The red dotted line represents $i > 0$ , and the blue $i < 0$ |

| Figure 3.5 Current path of an H-bridge inverter under normal operation and an open-circuit switch fault on $S12$ : (a) Normal operation, $S11$ , and $S14$ are turned-on, (b) an open-circuit switch fault on $S13$ , (c) Normal operation, $S12$ , and $S13$ are turned-on, (d) an open-circuit switch fault on $S13$ , (e) Normal operation, $S12$ , and $S14$ are turned-on, (f) an open-circuit switch fault on $S13$ ,(g) Normal operation, $S11$ , and $S13$ are turned-on, and (h) an open-circuit switch fault on $S13$ . The red dotted line represents $i > 0$ , and the blue $i < 0$ |

| Figure 3.6 Current path of an H-bridge inverter under normal operation and an open-circuit switch fault on $S12$ : (a) Normal operation, $S11$ , and $S14$ are turned-on, (b) an open-circuit switch fault on $S14$ , (c) Normal operation, $S12$ , and $S13$ are turned-on, (d) an open-circuit switch fault on $S14$ , (e) Normal operation, $S12$ , and $S14$ are turned-on, (f) an open-circuit switch fault on $S14$ ,(g) Normal operation, $S11$ , and $S13$ are turned-on, and (h) an open-circuit switch fault on $S14$ . The red dotted line represents $i > 0$ , and the blue $i < 0$ |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

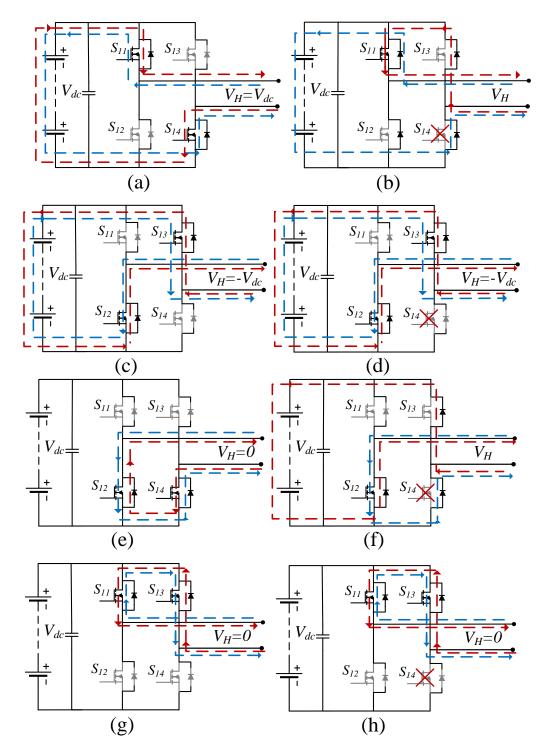

| Figure 3.7 Flowchart for the proposed open-circuit fault detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

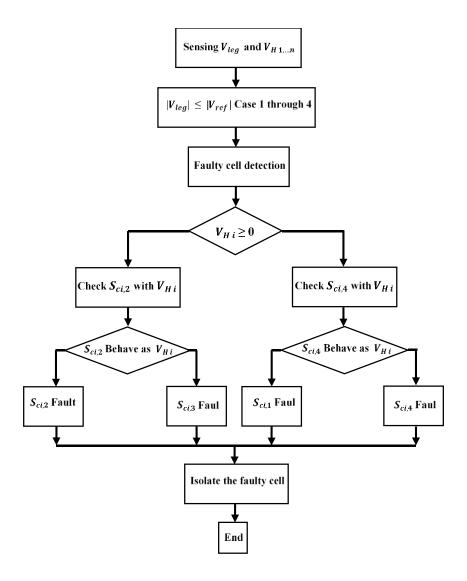

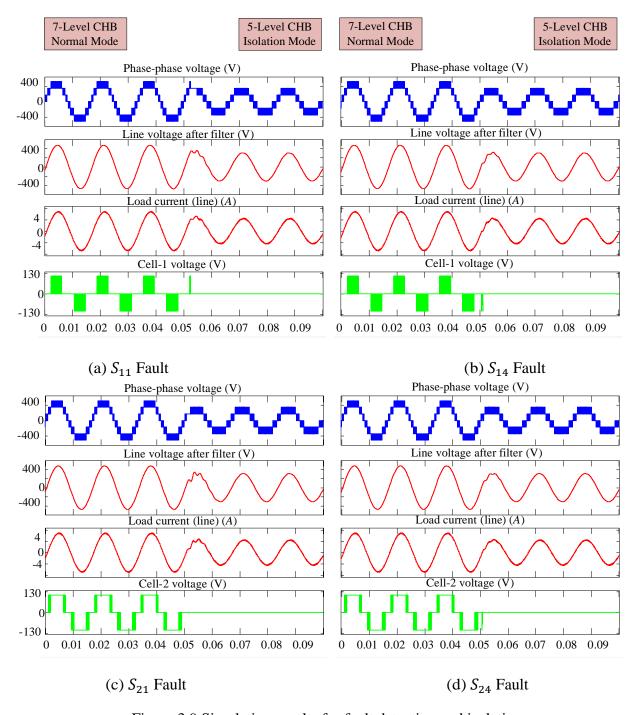

| Figure 3.8 Simulation results of four fault modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Figure 3.9 Simulation results for fault detection and isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Figure 3.10 Experimental test configuration – Photo by Author                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

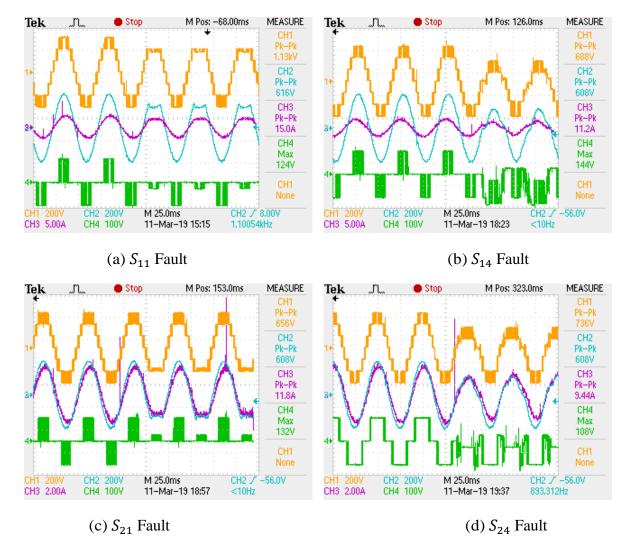

| Figure 3.11 Verification of the proposed fault detection method: inverter output voltage (ch1), Line voltage after filter (ch2), Line current (ch3), and (ch4) Output cell voltage                                                                                                                                                                                                                                                                                                                                                                                                              |  |

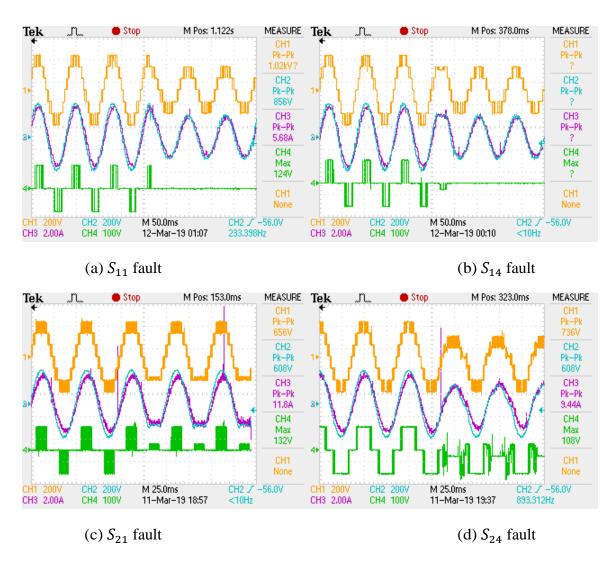

| Figure 3.12 Fault Detection and Isolation Method: (ch1), Line voltage after filter (ch2), Line current (ch3), and (ch4) Output cell voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

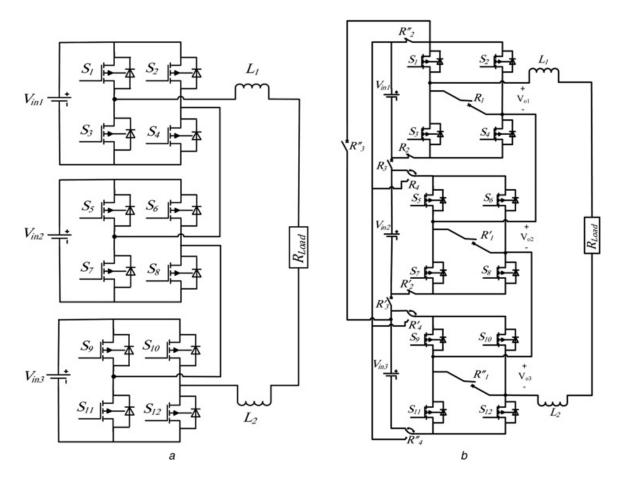

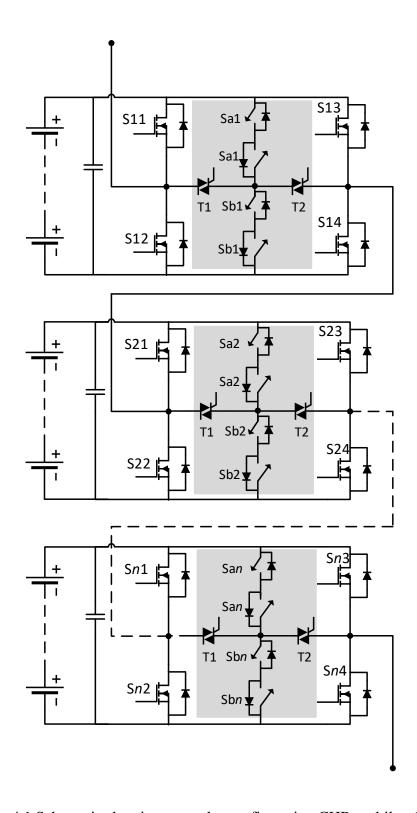

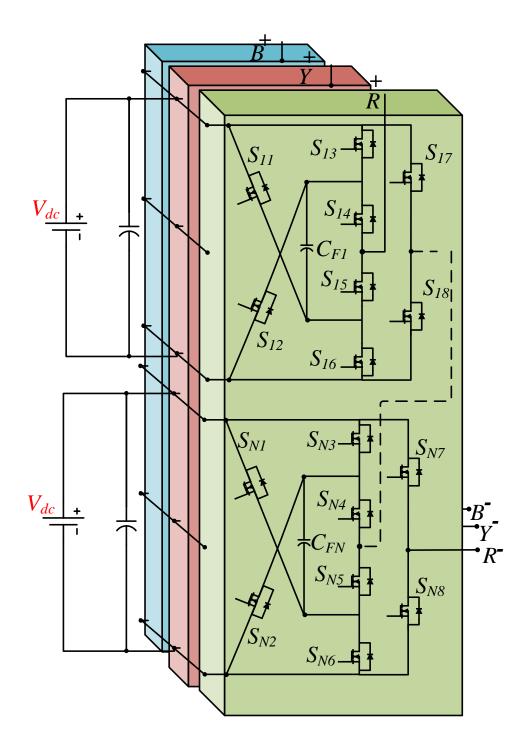

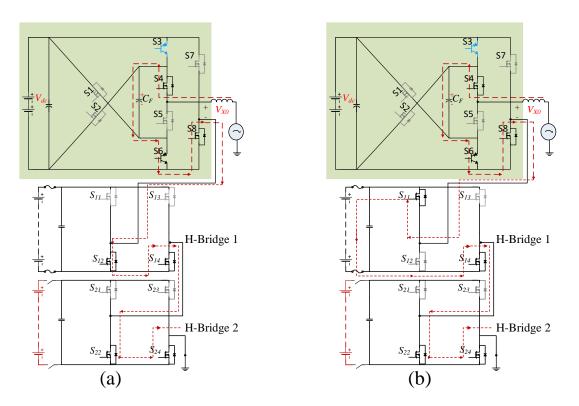

| Figure 4.1 Schematic showing a novel reconfiguration CHB multilevel inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

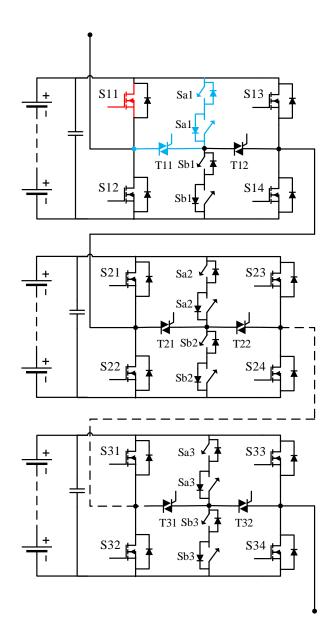

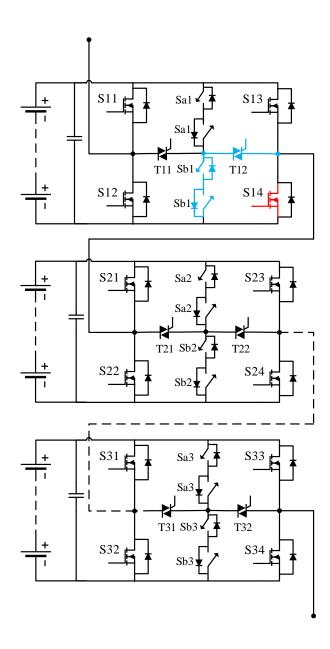

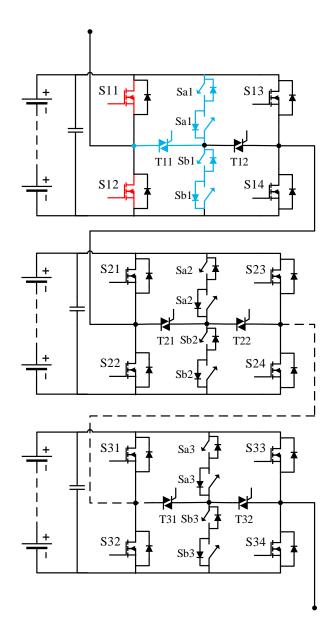

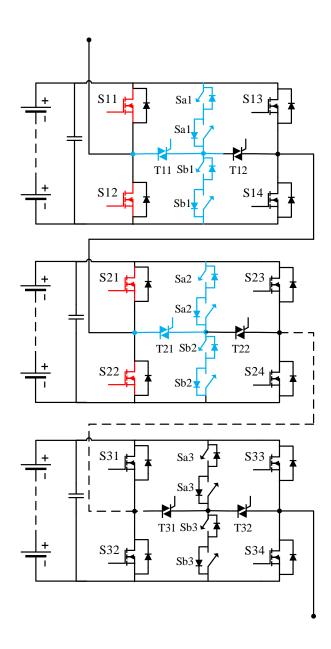

| Figure 4.2 Reconfiguration and open-circuit faults switch on $S_{11}$ , where blue lines indicate the reconfigurable path and red lines indicate the fault location                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

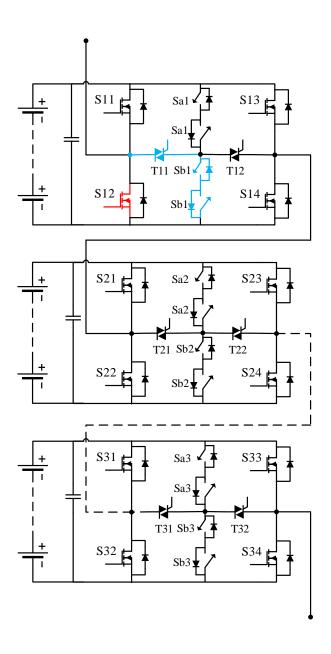

| Figure 4.3 Reconfiguration and open-circuit faults switch on $S_{12}$ , where blue lines indicate the reconfigured path and red lines indicate the fault location                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

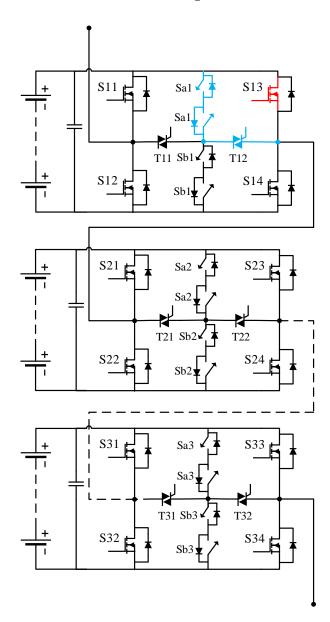

| Figure 4.4 Reconfiguration and open-circuit faults switch on $S_{13}$ , where blue lines indicate the reconfigured path and red lines indicate the fault location                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Figure 4.5 Reconfiguration and open-circuit faults switch on $S_{14}$ , where blue lines indicate the reconfigured path and red lines indicate the fault location.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Figure 4.6 Reconfiguration and open-circuit faults switch on $S_{II}$ and $S_{I2}$ , where blue lines indicate the reconfigured path and red lines indicate the fault location                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

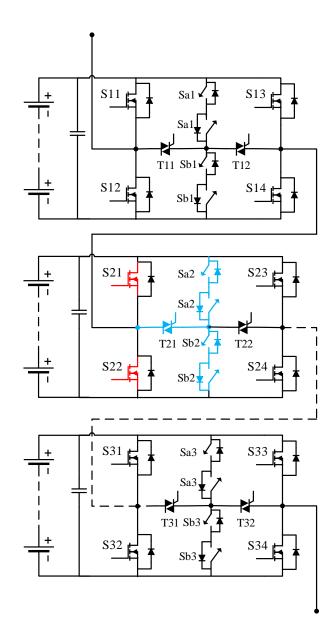

| Figure 4.7 Reconfiguration and open-circuit faults switch on $S_{21}$ and $S_{22}$ , where blue lines indicate the reconfigured path and red lines indicate the fault location                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Figure 4.8 Reconfiguration and open-circuit faults switch on $S_{11}$ , $S_{12}$ , $S_{21}$ and $S_{22}$ , where blue lines indicate the reconfigured path and red lines indicate the fault location                                                                                                                                                                                                                                                                                                                                                                                            |  |

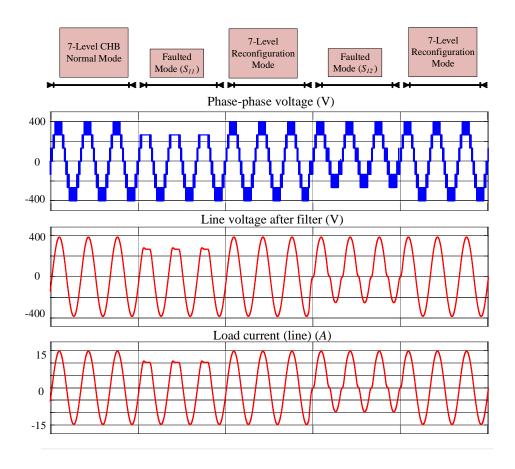

| Figure 4.9 Simulation result of reconfiguration and open-circuit faults switch on $S_{11}$ and $S_{12}$ 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Figure 4.10 Simulation result of reconfiguration and open-circuit faults switch on $S_{21}$ and $S_{22}$ 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

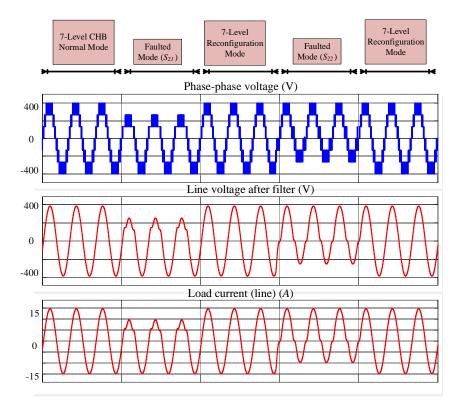

| Figure 4.11 (a) Top view shows the proposed reconfiguration circuit for CHB inverte Bottom view shows the gate drivers and the reconfigurable circuits—Photo by Author |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

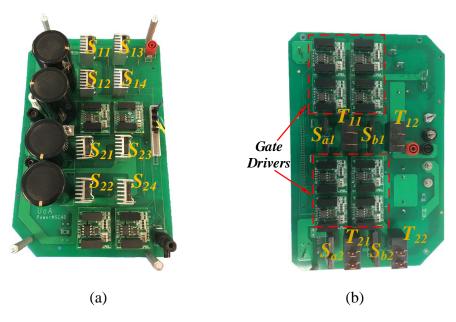

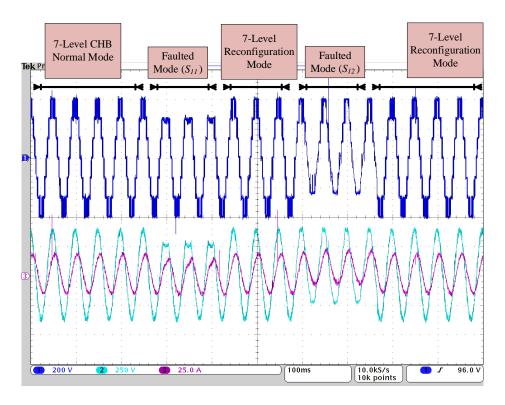

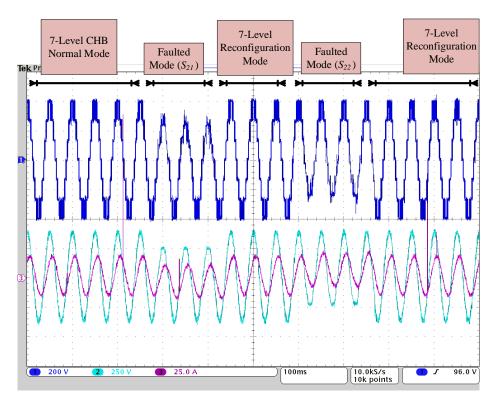

| Figure 4.12 Experimental result of reconfiguration and open-circuit faults switch on $S_{II}$ an                                                                       |     |

| Figure 4.13 Experimental Result of Reconfiguration and Open-Circuit Faults Switch on S <sub>2</sub>                                                                    |     |

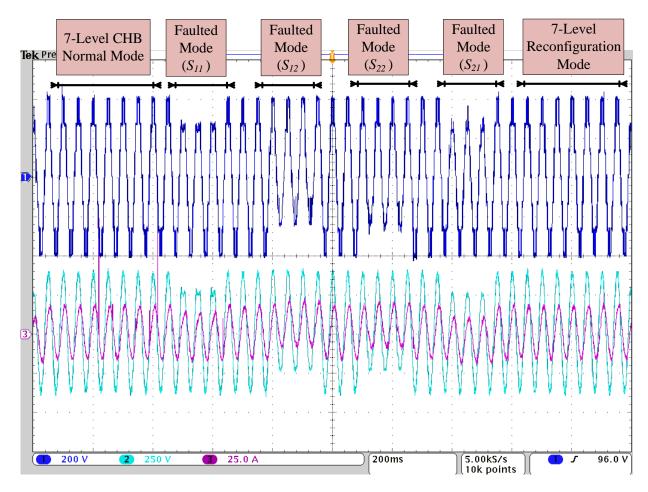

| Figure 4.14 Simulation result of reconfiguration and open-circuit faults switch on $S_{11}$ , $S_{12}$ , $S_{2}$                                                       | •   |

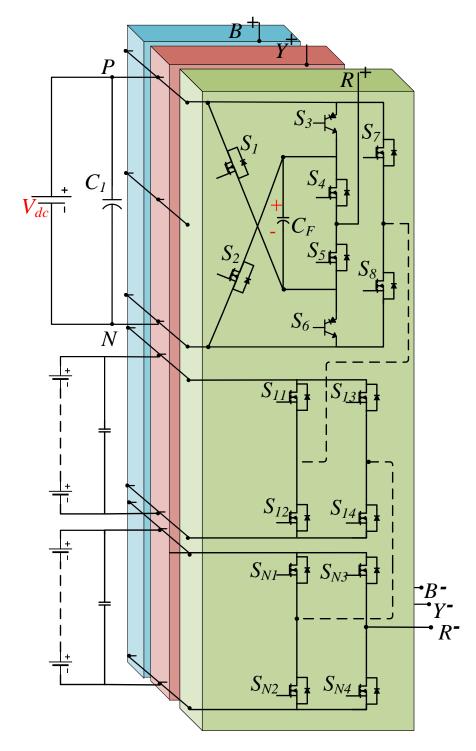

| Figure 5.1 Proposed <i>n</i> -level three-phase X-CHB inverter.                                                                                                        | 70  |

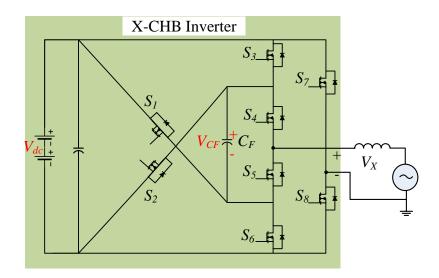

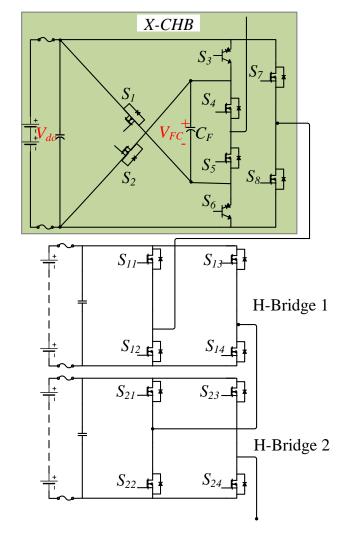

| Figure 5.2 A proposed X-CHB inverter cell.                                                                                                                             | 72  |

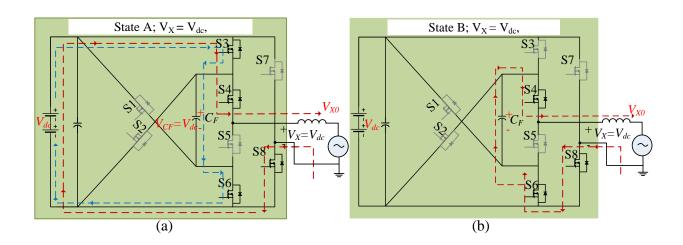

| Figure 5.3 Switching states analysis of the proposed 5-level X-CHB.                                                                                                    | 74  |

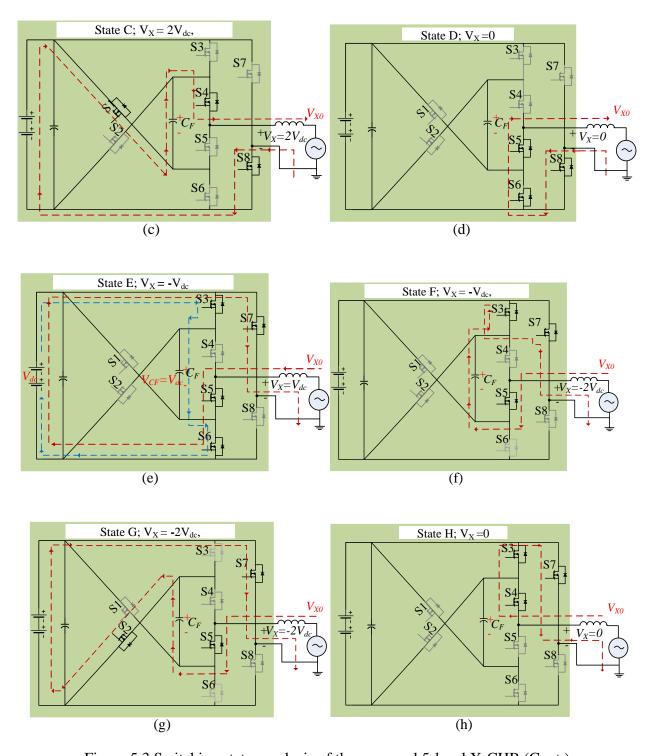

| Figure 5.4 Switching states analysis for a 7-level X-CHB inverter.                                                                                                     | 77  |

| Figure 5.5 (a) Cost, (b) Weight, and (c) Volume for 4.16 kV/325 kW BESS components.                                                                                    |     |

| Figure 5.6 Modulation strategy of the proposed 5-level X-CHB inverter.                                                                                                 | 85  |

| Figure 5.7 Modulation strategy of the proposed 7-level X-CHB inverter.                                                                                                 | 87  |

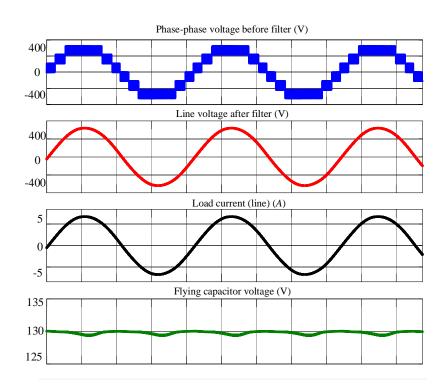

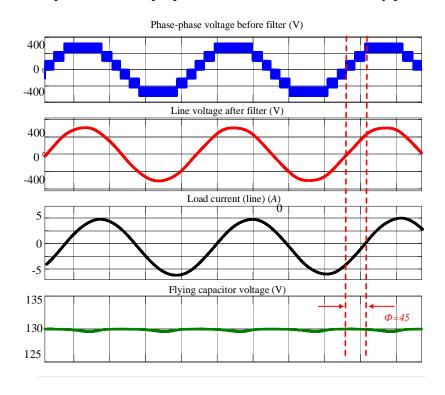

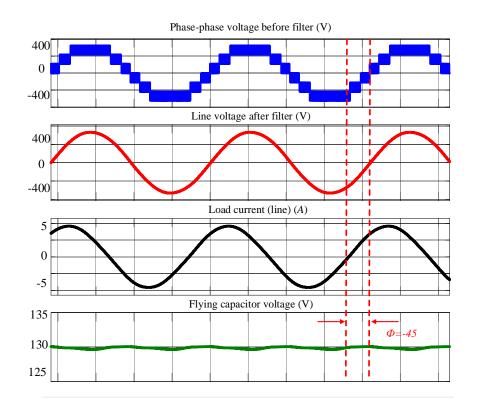

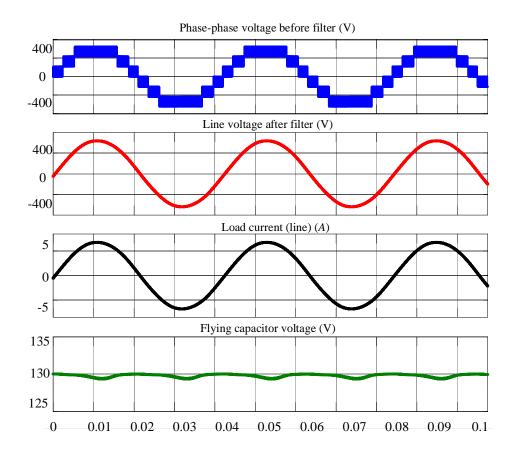

| Figure 5.8 Operation of the proposed 5-level inverter under unity power factor                                                                                         | 90  |

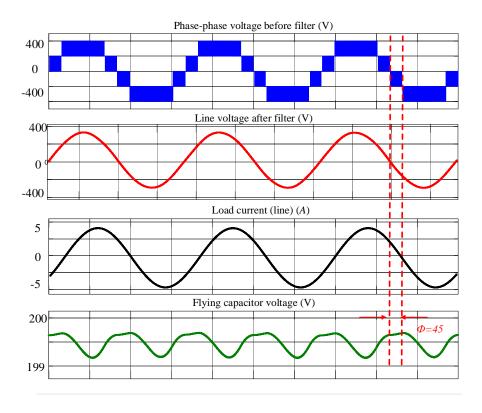

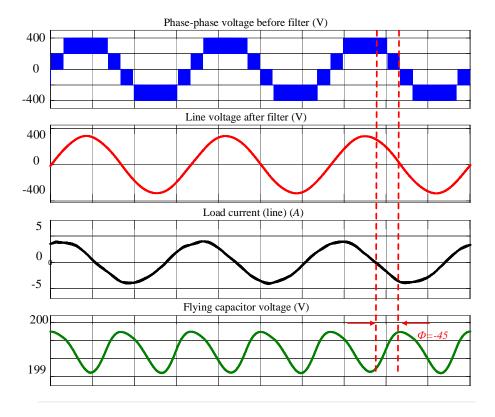

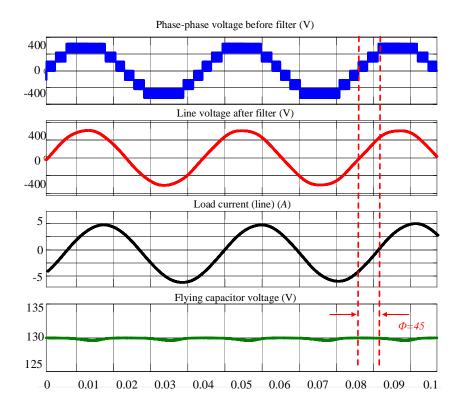

| Figure 5.9 Operation of the proposed 5-level inverter under lagging power factor                                                                                       | 91  |

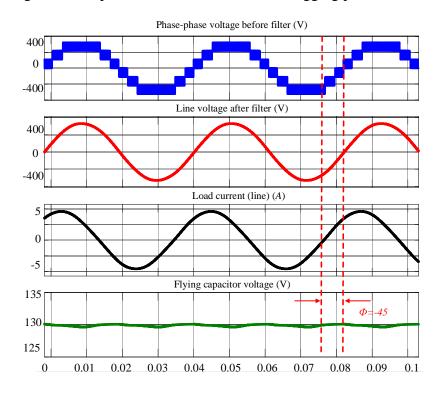

| Figure 5.10 Operation of the proposed 5-level under leading power factor                                                                                               | 91  |

| Figure 5.11 Operation of the proposed 7-level inverter under unity power factor                                                                                        | 92  |

| Figure 5.12 Operation of the proposed 7-level inverter under lagging power factor                                                                                      | 92  |

| Figure 5.13 Operation of the proposed 7-level inverter under leading power factor                                                                                      | 93  |

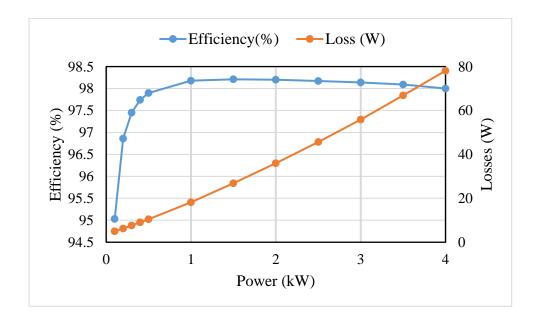

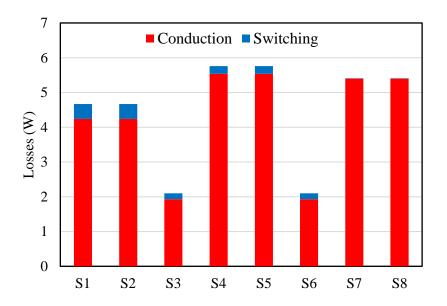

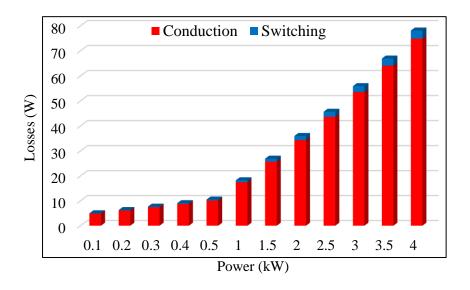

| Figure 5.14 Total losses and efficiency of the proposed topology versus output voltage                                                                                 | 93  |

| Figure 5.15 Distribution of semiconductor losses of the proposed X-CHB.                                                                                                | 94  |

| Figure 5.16 Total power losses variations versus output power.                                                                                                         | 94  |

| Figure 6.1 Proposed <i>n</i> -level three-phase hybrid CHB inverter.                                                                                                   | 101 |

| Figure 6.2 A 7-level single-phase hybrid CHB inverter.                                                                                                                 | 105 |

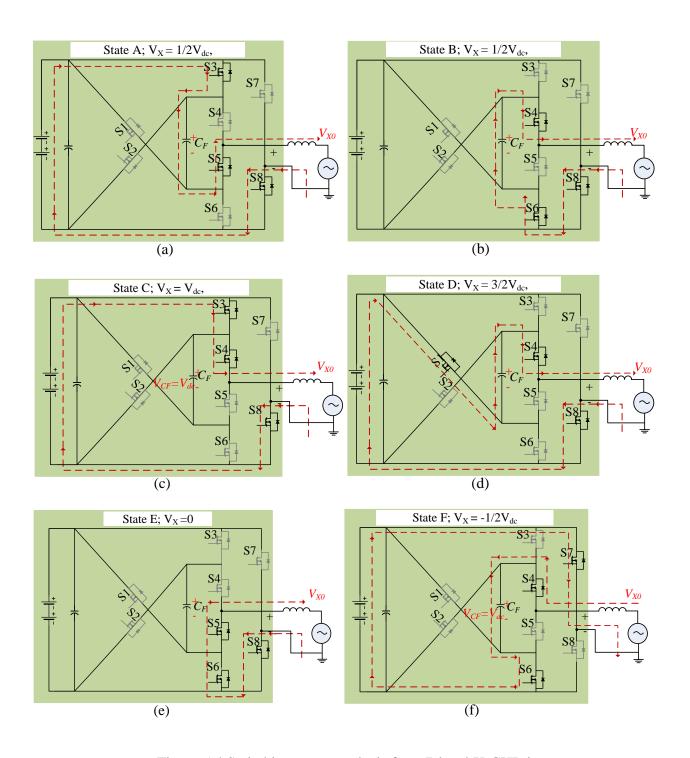

| Figure 6.3 Switching states analysis for a positive cycle of the hybrid CHB 107                                         |

|-------------------------------------------------------------------------------------------------------------------------|

| Figure 6.4 Modulation strategy of the proposed inverter under unity power factor                                        |

| Figure 6.5 The modulation for interval 1. Figure 6.6 The modulation for interval 2 111                                  |

| Figure 6.7 Modulation strategy of the proposed inverter under non-unity power factor 115                                |

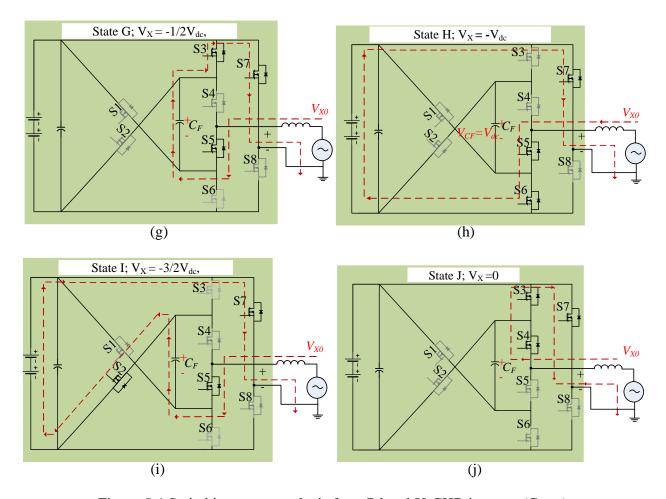

| Figure 6.8 Switching states analysis of the proposed 7-L Hybrid CHB inverter                                            |

| Figure 6.9 Switching states during unity and non-unity power factors                                                    |

| Figure 6.10 Illustration of charging/discharging of Interval 1                                                          |

| Figure 6.11 Illustration of charging/discharging of Interval 2                                                          |

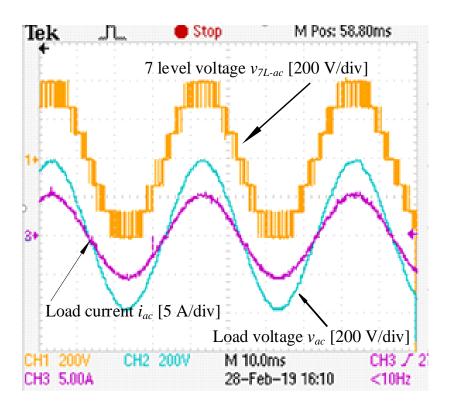

| Figure 6.12 Operation of the inverter under unity power factor                                                          |

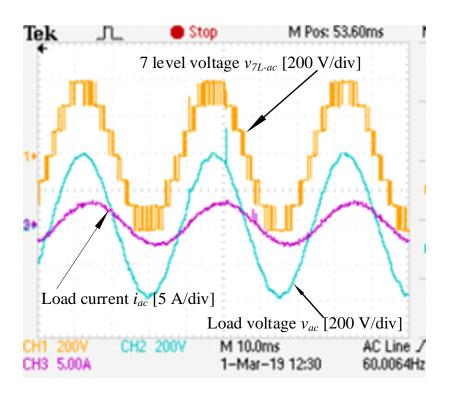

| Figure 6.13 Operation of the inverter under lagging power factor                                                        |

| Figure 6.14 Operation of the inverter under leading power factor                                                        |

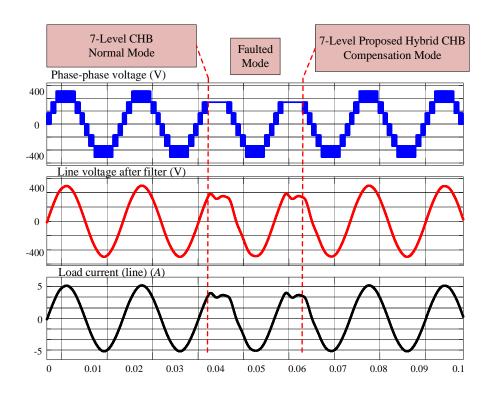

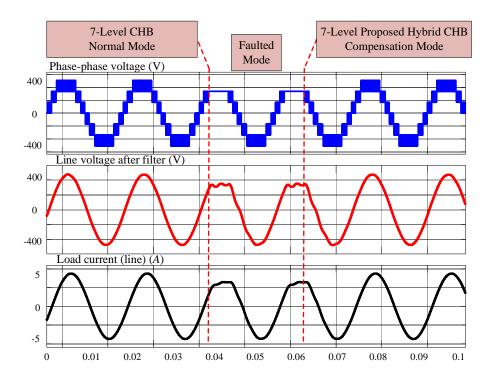

| Figure 6.15 Normal, faulted, and compensation modes (resistive load)                                                    |

| Figure 6.16 Normal, faulted, and compensation modes (inductive load)                                                    |

| Figure 6.17 Normal, faulted, and compensation modes (capacitive load)                                                   |

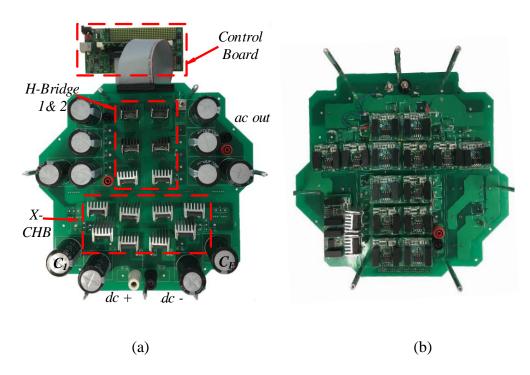

| Figure 6.18 (a) Top view shows the proposed hybrid CHB inverter, (b) Bottom view shows the gate drivers—Photo by Author |

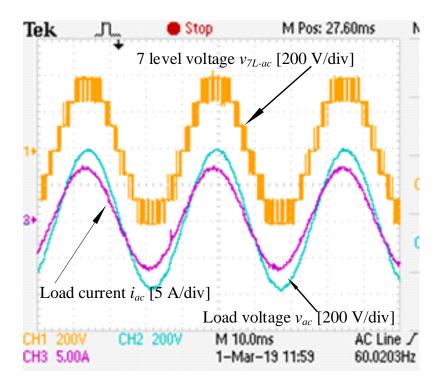

| Figure 6.19 Operation of the inverter under unity power factor                                                          |

| Figure 6.20 Operation of the inverter under lagging power factor                                                        |

| Figure 6.21 Operation of the inverter under leading power factor                                                        |

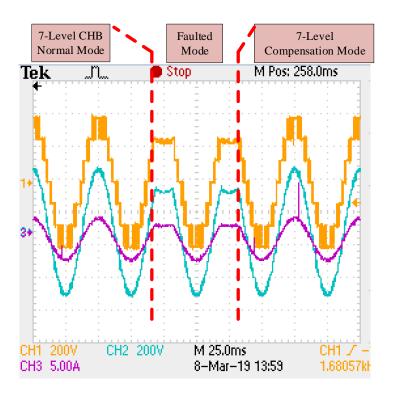

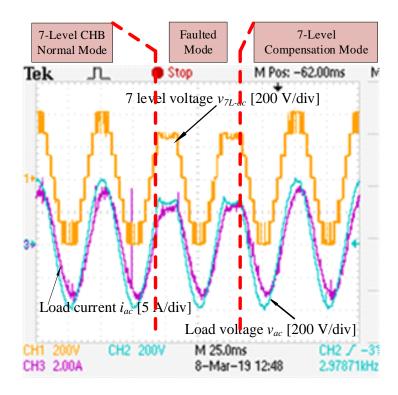

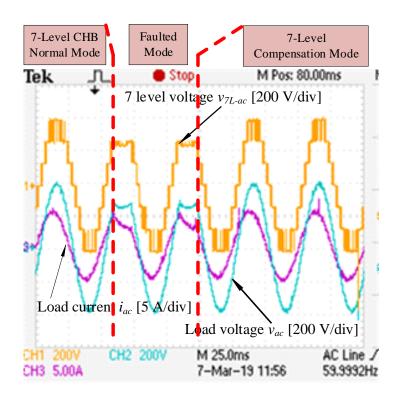

| Figure 6.22 Normal, faulted, and compensation modes (resistive load)                                                    |

| Figure 6.23 Normal, faulted, and compensation modes (inductive load)                                                    |

| Figure 6.24 Normal, faulted, and compensation modes (capacitive load)                                                   |

# LIST OF TABLES

| Table 3.1 Cell Switch Configuration and Corresponding Voltage                        | 22  |

|--------------------------------------------------------------------------------------|-----|

| Table 3.2 Cell <i>n</i> Output Voltage Change Due to Fault Occurrence in Each Switch | 31  |

| Table 3.3 Change in Cell Output Voltages Due to Fault Occurrence in Each Switch      | 34  |

| Table 3.4 Proposed Strategy to Detect the Faulty Cell                                | 37  |

| Table 3.5 Proposed Strategy to Detect the Faulty Switch                              | 38  |

| Table 3.6 Generalized the Proposed Strategy to Detect the Faulty Switch              | 39  |

| Table 3.7 Simulation Parameters                                                      | 41  |

| Table 3.8 Experimental Setup Parameters                                              | 44  |

| Table 4.1 Comparison of Fault-Tolerant Techniques (7-level – single phase)           | 61  |

| Table 5.1 Switching States of the Proposed 5-Level X-CHB Inverter                    | 75  |

| Table 5.2 Switching States of the Proposed 7-Level X-CHB Inverter                    | 78  |

| Table 5.3 Switching Action to Isolate the Cells in Case of a Short Circuit Fault     | 79  |

| Table 5.4 Comparison of 5-Level Topologies with the Proposed Topology                | 82  |

| Table 5.5 Comparison of 7-Level Topologies with the Proposed Topology                | 83  |

| Table 5.6 Simulation Parameters                                                      | 89  |

| Table 6.1 Switching States of the Hybrid CHB Inverter Under Fault                    | 108 |

| Table 6.2 Simulation and Experimental Parameters                                     | 121 |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation and Problem Statement

The increase in the use of renewable energies for grid-connection applications in recent years has led to a rapid increase in power electronics developments. One instance of this is transformerless power electronics, which increases the cost-effectiveness in grid-tied applications. The high-power requirements and needs also led to the development of a new generation of power electronics, the multilevel inverters (MLIs). MLIs provide a superior solution for high-voltage/power applications due to their modular nature. Other merits of using MLIs are reduction of the losses and electromagnetic interference (EMI), improvement of power quality, and the reduction of the switches' voltage stresses. However, one of the major disadvantages of using MLIs is increasing the system complexity. The high number of switches in MLIs will also increase the number of gate drivers and sensor/conditioning boards. Increasing the number of switches also increases the probability of switching failures, which in turn decreases system reliability.

This dissertation proposes new MLI circuits providing novel methods for maintaining system operation in case of one (or more) fault occurrences. The proposed topologies with fault-tolerant ability leads to a system that can produce the same output voltage/current after the fault happens. The advantages of the new circuit topologies with fault-tolerance capability are more visible in the application such as hospitals, airports, and transportation.

Some of the existing fault-tolerant circuit topologies require backup circuits that have no functionality until a fault occurs, which results in higher implementation costs. Other circuits provide reliable systems for faults, but the power quality of system is reduced.

Also, these methods cannot maintain the same control method after a fault. For instance, in a

battery energy storage system (BESS), it is required to balance all the batteries within their designed values. The battery pack for all the cells in one phase, and in all the phases, should be balanced. If there is fault in one cell, this cell is removed from the system. One of the suggested solutions is to replace the defective cell with a backup battery. The SoC (State of Charge) of the backup batteries is almost 100%, while the system batteries' are not. Consequently, adding the backup batteries to the system with different SoC percentages leads to control issues to maintain the balance of the entire system.

Previous methods in the literature cannot be implemented for all types of MLIs. In fact, most of these circuits are designed for a specific MLI while the proposed method can be implemented for a large variety of MLIs.

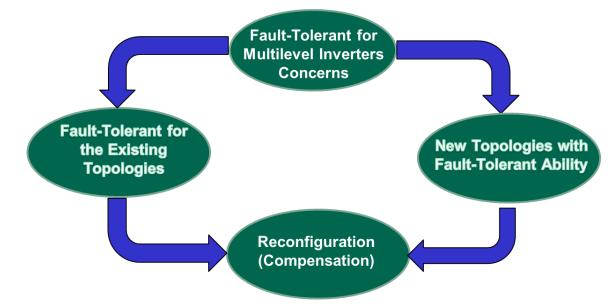

This dissertation explores fault-tolerant techniques for MILs. The goal was to both investigate a new fault-tolerant method for the existing topologies and to develop a new topology with fault-tolerance ability. Figure 1.1 demonstrates the goals of this dissertation.

Figure 1.1 Dissertation two-fold goal of achieving fault-tolerant solutions for new and existing multilevel inverters.

The focus of this research work is to develop novel methods and circuit topologies for faulttolerant operation as follows:

- 1- A simple and accurate novel switching fault detection and identification method for MLIs,

- 2- A new fault-tolerant topology that provides a reconfiguration ability for existing power electronics applications,

- 3- A novel inverter with a lower number of switches and boosting ability for fault-tolerant operation that can be suitable for different power system applications,

- 4- A novel multilevel inverter with fault-tolerance capability to ensure a reliable and robust operation of the converter in the event of an open/short circuit switching fault or dc supply faults, and

- 5- A fault detection and identification building block that can be applied to a wide variety of MLI topologies.

### 1.2 Organization of the Dissertation

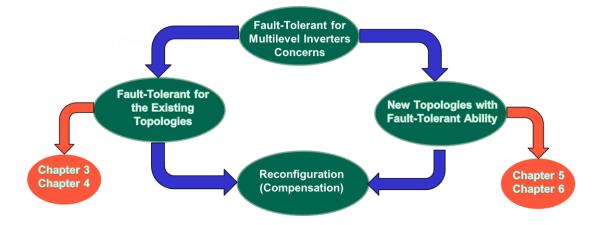

The chapters covering the main contributions are organized in Figure 1.2. This work is organized into seven separate chapters. The content of each chapter is summarized below:

Figure 1.2 Organization of the novelty chapters of this dissertation.

<u>Chapter 2</u>: A comprehensive survey of existing fault-tolerant topologies is presented with emphasis on their drawbacks. The requirements and needs for reliable MLIs are described as well.

<u>Chapter 3</u>: This chapter proposes a novel switching fault detection and identification method for MLIs. It presents a simple method to identify the defective faulty cell and switch in comparison to the existing methods. It is found that there is a relationship between the leg voltage polarity and PWM signals to detect the fault. Simulation and experimental verification of the proposed concept is demonstrated using a seven-level cascaded H-bridge CHB inverter.

<u>Chapter 4</u>: This chapter presents a new fault-tolerant topology that provides reconfiguration capability for power electronics applications. It enables the inverter to isolate the faulty device in a way that the circuit can continue operating as a pre-fault condition and, therefore, reduce the disruption of electrical power delivery upon fault occurrence. It is worth pointing out that all the above is implemented to achieve a cost reduction in the overall system. Simulation and experimental verification of the proposed concept is demonstrated using a seven-level CHB inverter.

<u>Chapter 5</u>: The main objective of this chapter is to develop a novel inverter with a smaller number of switches in combination with output voltage boosting ability. The proposed topology offers a reduction in the number of batteries by 50%. Also, it can operate under non-unity power factor, which makes it suitable for battery energy storage systems and STATCOM applications. Each cell of the proposed topology, the X-CHB topology, can generate either 5-level or 7-level output voltage waveforms.

<u>Chapter 6</u>: A fault-tolerant approach for a CHB inverter is described in this chapter. The added features ensure reliable and robust operation of the converter in the event of faults. The proposed

strategy uses an additional cross-coupled CHB (X-CHB) unit in combination with the existing CHB to support the output voltage and ensure continuity of operation in the event of an open/short circuit fault. The operation of the proposed X-CHB inverter is described in detail. Simulation and experimental verification of the proposed concept is demonstrated using a seven-level CHB inverter. Both simulation and experimental results validate the fault-tolerant operation of the CHB inverter for a battery energy storage system (BESS) in case of switch faults, such as open/short-circuit switch fault or a dc-source or battery failure.

<u>Chapter 7</u>: The final chapter focuses on the conclusions drawn from the efforts presented in this dissertation.

#### **CHAPTER 2**

#### BACKGROUND ON FAULTS IN MULTILIVEL INVERTERS

#### 2.1 Reliability Considerations for MLIs

By March 2017, 10% of US electricity was generated through solar photovoltaics and wind turbines [2.1]. This number is predicted to rise in the upcoming years. The energy produced through renewable sources requires power electronic converters to make it suitable for use in the electricity grid. This precedent has resulted in an expeditious rise of research and development on semiconductor devices. Providentially, the research in SiC devices has provided the capabilities for high switching frequencies and breakdown voltages that open doors to new applications. With the help of the new semiconductor devices, numerous advances have been made in expanding the topologies suitable for medium voltage applications. However, there is still a need for higher voltage switches to be developed. For instance, devices with more than 10 kV breakdown voltage are necessary for integration of Battery Energy Storage Systems (BESS) to a 13.8 kV grid. Since these devices have not been commercialized yet, the series connection of lower-rated devices is used to reach the desired breakdown voltage. Multilevel Inverter (MLI) is the term used for power electronic converters that consist of series-connected, or cascoded, devices to achieve the goal of achieving higher breakdown voltages.

Reliability is defined by the system's ability to maintain a high probability of successful operation with an desired lifetime goal. A reliable converter should be able to survive and tolerate any type of fault [2.2]. Increasing the reliability of power electronics system in a cost-effective and efficient manner has always been one of the main objectives of industrial and academic researchers in power electronics as means to guarantee robust power electronics applications. Consequently, more investigation into highly reliable power electronics is one of the most critical needs in the

power electronics research and industry. For many years, a substantial impediment to widespread deployment of grid-connected power electronics was the lifetime and reliability of silicon power electronics. This was exacerbated by the need to aggressively cool the silicon power electronics, which drives up system costs and further impacts reliability with redundant cooling systems. Wide bandgap power electronics, particularly silicon carbide, offer the opportunity to conquer these issues in electric power grid applications. This dissertation will address the circuit-level aspects of this equation.

Power electronics reliability studies can loosely be categorized into three studies as is described in the following [2.3].

- 1- Analysis: reliability studies for analysis of the power electronics failure causes.

- 2- Design: to design a reliable power electronics system. In other words, this is focusing on the reliability during the design stage.

- 3- Solution: techniques and control methods that ensure a reliable power electronics system that can handle all ramifications.

Other keen insights into the reliability concerns are as the following questions:

- 1- What electric components should be considered as the most critical components that might cause power electronics' failures and have a negative impact on the system reliability? Are power semiconductors the only device that should be considered?

- 2- Are the power electronics reliability concerns the same for all power electronics applications and topologies?

- 3- Are there limitations with the existing reliability solution methods?

Fault in any of the components can result in the failure of the overall power electronic system.

These components include semiconductor devices, capacitors, inductors, solder tracks, and PCB

boards. Each component has a different failure rate that can be calculated through various methods using the available standards in conjunction with the element losses, junction temperatures, etc.

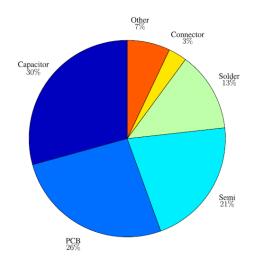

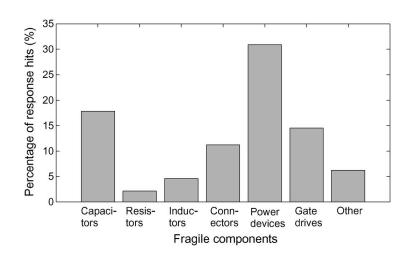

Figure 2.1 Distributions of faults in a power converter [2.7].

Figure 2.2 Distributions of fragile components [2.6].

[2.4]-[2.5] show that approximately 21% of the power converter failure is due to semiconductor faults as shown in Fig. 2.1. Additionally, 39% of the system failures are caused by the failure in the soldering and PCBs. A survey research conducted of more than 60 companies in [2.6] revealed that the semiconductor power devices have the highest hazard rate amongst power

electronic components and correspond to 31% of system failures. [2.6] further showed that 15% of the power converter failures are due to faults in the gate drivers as shown in Figure 2.2.

Figure 2.3 MLI configurations (a) Neutral Point Clamped (NPC), (b) Flying Capacitor, (c) Cascaded H-Bridge, and (d) Modular Multilevel [2.9].

An increase in the number of components translates into higher failure possibility. Multilevel inverters (MLIs) have been established as one of the most popular topologies in power electronics as they provide high power quality and effective performance. The different types of MLIs presented in the literature are shown in Figure 2.3. Prevalent instances of multilevel inverter topologies are the neutral point clamped (NPC), Flying Capacitor, and cascaded H-bridge (CHB). Among all the types of MLIs, the CHB inverter is the most suitable solution for Battery Energy Storage System (BESS) applications [2.8].

The large number of power semiconductor devices in MLI topologies increase the chance of device faults. These faults can be categorized into two groups: open-circuit and short-circuit faults [2.9]-[2.11]. Short-circuit fault detection and mitigation methods are provided with hardware solutions that are integrated with the commercialized gate drivers.

These methods are designed to soft turn-off off the device as soon as a fault occurs [2.12]. Despite these efforts, there are no hardware solutions capable of open-circuit fault detection. Open-circuit faults are the reason for 15% of the failures and may occur due to wire bond lift-off and cracking of the solder layers [2.13]. When this type of fault occurs with MLIs used for the BESS applications, it causes an unbalanced output current and voltage. This may result in the shutdown of the overall system supplied by the MLI. A system shutdown in medium and high-voltage scenarios can potentially result in disastrous and expensive downtime conditions for industrial and commercial loads.

### 2.2 Fault Diagnostic Survey

Numerous studies have been conducted on the failures in semiconductors. In order to conquer the reliability concerns in the event of open-circuit device failures, a simple, fast, and accurate solution for fault detection is required. Previous research in [2.14]-[2.15] reports approaches that can successfully identify the faulty cascaded H-bridge cell. However, these methods cannot detect the specific faulty switch. Consequently, these methods cannot lead to sufficient and accurate detection. Other work in [2.16]-[2.17] rely on at least two cycles required to identify the fault. These approaches result in a complicated and complex fault detection strategy. In addition, these methods require many sensor boards, which results in a higher fault location time, and higher overall system cost. The methods in [2.18] are designed for neutral point clamped inverters by monitoring the voltage polarity and its time frame. As a result, it can just detect a

general fault, but it cannot locate the fault.

In [2.19], the authors utilized the comparison of the predicted and measured values of an MLI for fault detection purposes. Once again, this method can only detect the faulted submodule (SM) and not the precise faulty switch. Furthermore, the detection time required for the method is an unsatisfying 33 ms. The approach in [2.20] cannot be applied to nonlinear loads, where nonlinear loads are common for most commercial and industrial loads. This approach causes reduced accuracy due to the lack of any other parameters used in the comparison other than the voltage.

Other detection approaches utilize observer and neural-network-based strategies for fault detection. [2.21] uses a sliding mode observer-based method to detect the faulty switch. It monitors the cells' capacitor voltages and each leg voltage. Nevertheless, this method requires a detection time of more than 200 *ms* for evaluating each cell for a fault. A neural-network-based method for switch fault identification is proposed in [2.22] that monitors the CHB output voltage for fault detection. The training data time in this method for covering the large operation regions results in inaccurate results. In [2.23], a detection approach was successfully implemented that could identify the defective switch in NPC converters feeding synchronous motor drives. However, this method requires a large number of current measurement boards in each of the NPC legs.

The method in [2.24] proposed another fault detection method using a neutral shift technique. This method is applicable to a specific kind of PWM (Phase-Shifted) strategy. However, this approach cannot be implemented with other PWM strategies.

All in all, there is a need for a highly reliable and rapid detection method that can guarantee:

1) cost-effective solutions, 2) fast response times, and 3) very high accuracy.

## 2.3 Reconfiguration Survey

Fault detection methods help find the defective switches, but what happens after the accurate fault detection? An approach is required that, in addition to fault detection, can isolate the defective switch as a means to increase the reliability of the converter and thus the renewable energy system as a whole. Moreover, power electronics are required for grid BESS to shape the voltage and frequency during heavy load, or reduced wind. The previously available literature can be divided into two categories. The first subset focuses on isolation of the defective cell that often causes lost functionality and degraded operation. Another subset revolves around utilization of a backup battery pack that noticeably increases the entire system cost.

As previously indicated, one of the approaches for MLIs facing faults is to bypass the defective cell. This is achievable through the addition of four electromagnetic contactors (relays) in each cell [2.25]-[2.33]. In case of faults, these electromagnetic contactors isolate the faults and connect the faulty dc link to a healthy cell, as displayed in Figures 2.4 and 2.5. This method is not practical in the case of medium-voltage applications for several reasons. The first reason is that adding a battery pack to a healthy cell would result in destroying the semiconductor devices since the voltage stress across each device will be doubled and each device has breakdown voltage limits that cannot be exceeded. Another reason is that in case of photovoltaic systems and BESS applications, the control system is required to balance the charging/discharging status. Transferring the defective cell batteries to a healthy cell will result in issues in the State-of-Charge (SoC) for the system batteries, and the controller may not be able to maintain the same balancing for the entire system's batteries under all circumstances (i.e., stability is not guaranteed). If the control system is adjusted to operate for certain SoC values, the controller cannot maintain the balance of the inverter's battery after the dc-link transfer since the expected SoC would change. The

expensive nature of this solution, due to the high cost of high-voltage circuit breakers, is another reason why this approach is not viable. These circuit breakers need to be capable of handling voltage levels equal to that of the phase voltage. Additionally, in these methods, the switches are required to be designed for higher breakdown voltages for handling the added battery voltages; resulting in an even higher implementation cost. In case of fault occurrence, the inverter voltage level would change significantly.

Figure 2.4 A fault reconfiguration method using additional electromagnetic contactors (relays) in each cell [2.25].

After disconnection of a cell, the change in the output voltages, current ripples, and THD are very high. In any power electronics design, the output current ripple and THD must be decreased to meet the standard requirements. For instance, the current ripple should not exceed 5% while

avoiding resonance frequency and maintaining low THD. The THD can be reduced using an output filter, which could be an L, LC, or LCL filter. The filter is required to smooth the output waveforms. With all the above considerations, the bypassing methods still have not addressed the concerns of the inverter output filter to meet worst-case scenarios.

Figure 2.5 A fault reconfiguration method using additional electromagnetic contactors (relays) in each cell [2.27].

The alternative solution is to use redundant sub-circuits, as shown in Figure 2.6. This solution would need either an extra cell of switches or standby batteries [3.34]-[3.36]. The standby sub-circuits would enter operation after the event of a fault. These approaches have multiple disadvantages. External batteries would be too costly for medium and high-voltage applications. Also, these redundant switches or batteries would not be utilized until a fault happens. In the case of a four-cell inverter, the batteries cost with an extra cell is raised by a factor of four for one phase.

Furthermore, these methods cannot continue fault-tolerant operation when another fault happens at the same phase. Consequently, the ability of this type of method is limited to address a fault per phase and cannot guarantee robust operation. To further grasp the problems that these methods cause for the SoC balancing, assume a failure occurs when the SoC is at 40%. The extra newly added battery SoC would be at 100%. In this case, the controllers would not be able to balance the entire system. The premise of the presented novel fault-tolerant reconfiguration method for CHB inverters under fault conditions is to address and solve these concerns.

Figure 2.6 Redundant reconfiguration methods [2.35]-[2.36].

Having said that, the existing fault-tolerant topologies still need improvement. Also, many studies relate the fault-tolerant topologies with the effect on the system power quality. There are few studies that create new fault-tolerant topologies for MLIs. In addition, there are studies which suggest new topologies that have the fault-tolerant ability. For these reasons, there is a need for a new method for fault-tolerance capability that has:

1- Cost-effectiveness of the designed topology resulting in the affordability of the system,

- 2- Simple operation under fault conditions where there is no need for changing the system's controllers,

- 3- A reliable system that operates under multiple fault conditions while maintaining the power quality for the systems,

- 4- A robust system for some specific military and navy applications that ensure continual operation under fault conditions, and

- 5- Resilience to operate at medium-voltage applications.

#### 2.4 References

- [2.1] EIA ,"Wind and solar in March accounted for 10% of U.S. electricity generation for first time" [Online]. Available at: <a href="https://www.eia.gov/todayinenergy/detail.php?id=31632/">https://www.eia.gov/todayinenergy/detail.php?id=31632/</a> [Accessed 9-Apr-2018]

- [2.2] D.L. Steiner,"Lay the Foundation for a Truly Reliable Electrical System" [Online]. Available at: <a href="http://www.dlsteiner.com/electrical-reliability-study/">http://www.dlsteiner.com/electrical-reliability-study/</a> [Accessed 9-Apr-2018]

- [2.3] U. M. Choi, F. Blaabjerg and K. B. Lee, "Study and Handling Methods of Power IGBT Module Failures in Power Electronic Converter Systems," in *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2517-2533, May 2015

- [2.4] H. Dan *et al.*, "Error-Voltage-Based Open-Switch Fault Diagnosis Strategy for Matrix Converters with Model Predictive Control Method," in *IEEE Transactions on Industry Applications*, vol. 53, no. 5, pp. 4603-4612, Sept.-Oct. 2017

- [2.5] P. Lezana, R. Aguilera and J. Rodriguez, "Fault Detection on Multicell Converter Based on Output Voltage Frequency Analysis," in *IEEE Transactions on Industrial Electronics*, vol. 56, no. 6, pp. 2275-2283, June 2009.

- [2.6] S. Yang, A. Bryant, P. Mawby, D. Xiang, L. Ran and P. Tavner, "An Industry-Based Survey of Reliability in Power Electronic Converters," in *IEEE Transactions on Industry Applications*, vol. 47, no. 3, pp. 1441-1451, May-June 2011.

- [2.7] Handbook for Robustness Validation of Automotive Electrical/Electronic Modules. Frankfurt, Germany: ZVEL, Jun. 2008

- [2.8] H. Akagi, "Classification, Terminology, and Application of the Modular Multilevel Cascade Converter (MMCC)," in *IEEE Transactions on Power Electronics*, vol. 26, no. 11, pp. 3119-3130, Nov. 2011.]

- [2.9] Euzeli dos Santos; Edison R. da Silva, "Power Electronics Converters Processing AC Voltage and Power Blocks Geometry," in *Advanced Power Electronics Converters:PWM Converters Processing AC Voltages*, 1, Wiley-IEEE Press, 2014, pp.376-4.

- [2.10] J. He, N. A. O. Demerdash, N. Weise and R. Katebi, "A Fast On-Line Diagnostic Method for Open-Circuit Switch Faults in SiC-MOSFET-Based T-Type Multilevel Inverters," in IEEE Transactions on Industry Applications, vol. 53, no. 3, pp. 2948-2958, May-June 2017.

- [2.11] J. Wang, H. Ma and Z. Bai, "A Submodule Fault Ride-Through Strategy for Modular Multilevel Converters With Nearest Level Modulation," in IEEE Transactions on Power Electronics, vol. 33, no. 2, pp. 1597-1608, Feb. 2018.

- [2.12] H. Zhao and L. Cheng, "Open-circuit faults diagnosis in back-to-back converters of DF wind turbine," in IET Renewable Power Generation, vol. 11, no. 4, pp. 417-424, 3 15 2017.

- [2.13] C. Brunson, L. Empringham, L. De Lillo, P. Wheeler and J. Clare, "Open-Circuit Fault Detection and Diagnosis in Matrix Converters," *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2840-2847, May 2015.

- [2.14] V. F. Pires, T. G. Amaral, D. Foito and A. J. Pires, "Cascaded H-bridge multilevel inverter with a fault detection scheme based on the statistic moments indexes," 2017 11th IEEE International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Cadiz, 2017, pp. 193-198.

- [2.15] H. W. Sim, J. S. Lee and K. B. Lee, "op," 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, 2014, pp. 2101-2106.

- [2.16] H. W. Sim, J. S. Lee and K. B. Lee, "Detecting Open-Switch Faults: Using Asymmetric Zero-Voltage Switching States," IEEE Industry Applications Magazine, vol. 22, no. 2, pp. 27-37, March-April 2016.

- [2.17] K. Thantirige, A. K. Rathore, S. K. Panda, S. Mukherjee, M. A. Zagrodnik and A. K. Gupta, "An open-switch fault detection method for cascaded H-bridge multilevel inverter fed industrial drives," IECON 2016 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, 2016, pp. 2159-2165.

- [2.18] T. J. Kim, W. C. Lee and D. S. Hyun, "Detection Method for Open-Circuit Fault in Neutral-Point-Clamped Inverter Systems," in *IEEE Transactions on Industrial Electronics*, vol. 56, no. 7, pp. 2754-2763, July 2009.

- [2.19] F. Deng, Z. Chen, M. R. Khan and R. Zhu, "Fault Detection and Localization Method for Modular Multilevel Converters," in *IEEE Transactions on Power Electronics*, vol. 30, no. 5, pp. 2721-2732, May 2015.

- [2.20] A. Anand, N. Raj, S. George and G. Jagadanand, "Open switch fault detection in Cascaded H-Bridge Multilevel Inverter using normalised mean voltages," 2016 IEEE 6th International Conference on Power Systems (ICPS), New Delhi, 2016, pp. 1-6.

- [2.21] S. Shao, P. W. Wheeler, J. C. Clare and A. J. Watson, "Fault Detection for Modular Multilevel Converters Based on Sliding Mode Observer," in *IEEE Transactions on Power Electronics*, vol. 28, no. 11, pp. 4867-4872, Nov. 2013.

- [2.22] S. Khomfoi and L. M. Tolbert, "Fault Diagnosis and Reconfiguration for Multilevel Inverter Drive Using AI-Based Techniques," in *IEEE Transactions on Industrial Electronics*, vol. 54, no. 6, pp. 2954-2968, Dec. 2007.

- [2.23] S. Farnesi, P. Fazio and M. Marchesoni, "A new fault tolerant NPC converter system for high power induction motor drives," 8th IEEE Symposium on Diagnostics for Electrical Machines, Power Electronics & Drives, Bologna, 2011, pp. 337-343.

- [2.24] L. Maharjan, T. Yamagishi, H. Akagi and J. Asakura, "Fault-Tolerant Operation of a Battery-Energy-Storage System Based on a Multilevel Cascade PWM Converter with Star Configuration," IEEE Transactions on Power Electronics, vol. 25, no. 9, pp. 2386-2396, Sept. 2010.

- [2.25] Zargari,, N., Xiao,, Y. and Wei,, L., Method and apparatus for bypassing cascaded H-Bridge (CHB) power cells and power sub cell for multilevel inverter. US9425705B2, 2012.

- [2.26] M. M. Haji-Esmaeili, M. Naseri, H. Khoun-Jahan and M. Abapour, "Fault-tolerant structure for cascaded H-bridge multilevel inverter and reliability evaluation," in IET Power Electronics, vol. 10, no. 1, pp. 59-70, 1 20 2017.

- [2.27] Peter Willard Hammond, "Device and system for bypassing a power cell of a power supply", US8441147B2, 2014.

- [2.28] Peter Willard Hammond, "Method for operating a multi-cell power supply having an integrated power cell bypass assembly", UUS20080174182A1, 2006.

- [2.29] Lixiang Wei, Yuan Xiao, Haihui Lu, Douglas B. Weber, ", Power cell bypass method and apparatus for multilevel inverter", US20140268928A1, 2013.

- [2.30] Peter Willard Hammond, "System for bypassing a power cell of a power supply", US20080079314A1, 2006.

- [2.31] Peter Willard Hammond, Integrated power cell bypass assembly and power supply including same, US7568931B2, 2006.

- [2.32] Peter Willard Hammond, Method and system for bypassing a power cell of a power Peter Willard Hammond, Integrated power cell bypass assembly and power supply including same, US7568931B2, 2006.supply, US20090073622A1, 2007.

- [2.33] P. Moamaei, H. Mahmoudi and R. Ahmadi, "Fault-tolerant operation of cascaded H-Bridge inverters using one redundant cell," 2015 IEEE Power and Energy Conference at Illinois (PECI), Champaign, IL, 2015, pp. 1-5.

- [2.34] M. Aleenejad, H. Iman-Eini and S. Farhangi, "Modified space vector modulation for fault-tolerant operation of multilevel cascaded H-bridge inverters," in *IET Power Electronics*, vol. 6, no. 4, pp. 742-751, April 2013.

- [2.35] W. Song and A. Q. Huang, "Fault-Tolerant Design and Control Strategy for Cascaded H-Bridge Multilevel Converter-Based STATCOM," in *IEEE Transactions on Industrial Electronics*, vol. 57, no. 8, pp. 2700-2708, Aug. 2010.

- [2.36] Zhongyuan Cheng, Navid Reza Zargari "Spare on demand power cells for modular multilevel power converter", US9812990B1, 2016.

#### **CHAPTER 3**

# A METHOD FOR OPEN-CIRCUIT FAULT DETECTION, IDENTIFICATION, AND ISOLATION IN CASCADED H-BRIDGE MULTILEVEL INVERTERS

#### 3.1 Introduction and Motivation

It was established in the previous chapters that MLIs and, in particular, CHBs are highly popular choices for medium-voltage and high-voltage applications due to the simplicity and ability to provide high power quality. However, due to the high number of semiconductor switches in these topologies, methods are required to be developed for an accurate and high-speed fault detection and isolation. This is due to the fact that a fault leads to a power outage in medium and high voltage levels can have disastrous economical results. Short-circuit fault detection approaches are conventionally implemented through gate driver hardware. However, there is a need for efficient and reliable methods for open-circuit (OC) fault detection for these converters. Consequently, a novel fault detection and isolation method for open-circuit fault detection is developed, implemented, and verified as follows.

## 3.2 System Description

This section contains a review of the CHB converter operation under healthy and fault conditions along with a brief description of the modulation strategy utilized. The conclusions in this subsection will later be used in an explanation of the proposed open-circuit fault detection method.

## 3.2.1 CHB Inverter and Modulation Strategy

Figure 3.1 displays the general structure of a CHB leg with N cells per leg that is used to create a 2N+1 level phase output voltage. A single phase of the inverter is displayed for simplification purposes. Each cell is made up of an H-Bridge configuration using four SiC MOSFETs. In the event of a fault in a CHB cell, two isolation approaches are conventionally utilized: soft isolation and hard isolation. Studies make use of relays for hard isolation of faulty cells; however, this study utilized soft isolation due to the faster response time and lower costs than it provides [3.1]-[3.2].

The CHB inverter phase output voltage consists of the sum of the output voltages of the series cells in that leg. The cell switching states can be defined as  $\{S_{cn,1}, S_{cn,2}, S_{cn,3}, S_{cn,4}\}$  where n is the number of respective cells and  $S_{cn,i}(t) \in \{-1,0,1\}$ . If the input dc-link voltage of each cell is  $V_{dc}$  and the output voltage of cell n can be denoted as  $V_{cn}$ , then  $V_{cn} \in \{-V_{dc}, 0, +V_{dc}\}$  depending on the cell switching states. It should be pointed out that the top switches  $S_1$  and  $S_3$  have complementary operations with  $S_2$  and  $S_4$ , respectively. Each cell of the CHB provides four unique cell states  $S_n(t)$ , as shown in Table 3.1.

Figure 3.1 Schematic of a CHB inverter leg.

Table 3.1 Cell Switch Configuration and Corresponding Voltage

| $[S_{cn,1}, S_{cn,2}, S_{cn,3}, S_{cn,4}]$ | Cell Output Voltage | Cell State $S_n(t)$ |

|--------------------------------------------|---------------------|---------------------|

| [0,1,0,1]                                  | 0                   | $0_{Lower}$         |

| [0,1,1,0]                                  | $-V_{dc}$           | -1                  |

| [1,0,0,1]                                  | $+V_{dc}$           | +1                  |

| [1,0,1,0]                                  | 0                   | $0_{Upper}$         |

|                                            |                     |                     |

The phase leg state can be described as a row matrix

$$L(t) = [S_1(t), S_2(t) \dots S_m(t)]$$

(3-1)

where m=4n. Therefore, there will be  $3^{4n}$  possible states for switches in each leg. Defining the leg voltage vector as  $v_L(t) = [v_{c1}, v_{c2}, ..., v_{cn}]$ , the anticipated leg voltage for each phase could be found as

$$v_{out} = L(t)v_L(t) (3-2)$$

Various Pulse Width Modulation (PWM) strategies, namely, the Space Vector PWM, Level-Shifted PWM, and Adaptive phase-shifted PWM (PS-PWM) can be utilized for control of the CHB inverter. Level-shifted PWM (LS-PWM) is the most common method due to the low harmonic content and the simplicity that it provides. It should be pointed out that some MLIs use variable dc links at the input. The OC fault identification approach proposed in this chapter is compatible with use of variable-time dc-link since this method only requires the dc-link voltage value to be known before the occurrence of a fault. To verify the performance of the presented fault detection technique, LS-PWM with in-phase disposition is used to control a 7-level CHB in sections 3.3 and 3.4. The principles of operation for this modulation scheme are shown in Figure 3.2. It can be

observed that in Figure 3.2,  $S_{cn,4}$  and  $S_{cn,2}$  are always conducting for  $V_{leg} > 0$  and  $V_{leg} < 0$ . It can further be noticed that for  $V_{leg} > 0$ ,  $V_{cn} \ge 0$ , and for  $V_{leg} < 0$ , this would always have  $V_{cn} \le 0$ . This covers the basic principle of operation for the presented OC fault detection approach, which is thoroughly elaborated in the following subsections.

Leg voltage using the above scheme for 7-level cascaded H-Bridge inverter can be calculated as

$$V_{leg} = (S_{11} - S_{13})V_{dc1} + (S_{21} - S_{23})V_{dc2} + (S_{31} - S_{33})V_{dc3}$$

(3-3)

Figure 3.2 Level-Shifted PWM for 7-level CHB.

#### 3.2.2 Behavior Analysis of the CHB under Open-Circuit Faults