University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2020

# Cybersecurity Methods for Grid-Connected Power Electronics

Stephen Joe Moquin University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, Power and Energy Commons, and the Systems Architecture Commons

#### Citation

Moquin, S. J. (2020). Cybersecurity Methods for Grid-Connected Power Electronics. *Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3680

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

Cybersecurity Methods for Grid-Connected Power Electronics

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Stephen Joe Moquin Auburn University Bachelor of Science in Philosophy, 2009 University of Arkansas Bachelor of Science in Electrical Engineering, 2017

> May 2020 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D. Thesis Director

Jia Di, Ph.D. Committee Member Roy McCann, Ph.D. Committee Member

Yue Zhao, Ph.D. Committee Member Chris Farnell Committee Member

#### Abstract

The present work shows a secure-by-design process, defense-in-depth method, and security techniques for a secure distributed energy resource. The distributed energy resource is a cybersecure, solar inverter and battery energy storage system prototype, collectively called the Cybersecure Power Router. Consideration is given to the use of the Smart Green Power Node for a foundation of the present work. Metrics for controller security are investigated to evaluate firmware security techniques. The prototype's ability to mitigate, respond to, and recover from firmware integrity degradation is examined. The prototype shows many working security techniques within the context of a grid-connected, distributed energy resource. Further work is expected in the Cybersecure Power Router project. Consideration is also provided for the migration of the present research and the Smart Green Power Node to realize a pre-production prototype.

©2020 by Stephen Joe Moquin All Rights Reserved

#### Acknowledgements

I would like to thank my advisor, Dr. Alan Mantooth, for taking a chance on me, affording many lessons on leadership, and the opportunity to participate in the environment he has so diligently cultivated over the years. It is an honor to work in the Power Mixed-Signal Computer Aided Design research group. Dr. Jia Di, Dr. Roy McCann, and Dr. Yue Zhao are owed much thanks for their advising and contributions to the success of my academic career. I owe a great deal to Chris Farnell, and have benefitted greatly from the years of mentoring and friendship he has provided me. The present work would not be possible without the edifice of work Chris Farnell has constructed, and the foundations laid by Dr. Mantooth and the fellow research faculty of the University of Arkansas. I am thankful for my teammates SangYun Kim and Nicholas Blair. Dr. Shannon Davis, Beth Benham, Karin Alvarado, Jamie Stafford, Cindy Pickney, Sharon Brasko, Connie Howard, and Tracey Long are owed thanks for their care and administration. Eric den Boer, Jeff Knox, and Mike Steger are owed thanks for their practical wisdom in life and in research. I am thankful for the support of my past and present fellow graduate students: Haider Mhiesan, Hamdi Albunashee, Haoyan Liu, Yuzhi Zhang, Janviere Umuhoza, Shuang Zhao, Yusi Liu, Sayan Seal, Andrea Wallace, and Audrey Dearien. Finally, I'd like to thank the Department of Energy and industrial partners who contributed to the Secure Evolvable Energy Delivery Systems research center for the funding of both the work and researchers of the Cybersecure Power Router.

| Chapter 1 - Introduction                         | 1  |

|--------------------------------------------------|----|

| Chapter 2 - Technical Background                 | 5  |

| Chapter 3 - Cybersecure Power Router             |    |

| 3.1 System Description                           |    |

| 3.2 Power Electronics                            |    |

| 3.3 Digital Signal Processor Board               |    |

| 3.4 Complex Programmable Logic Device Board      |    |

| 3.5 Signal Splitter                              |    |

| 3.6 Hardware Authentication Module               |    |

| 3.7 BeagleBone Black                             |    |

| 3.8 Test Bed                                     |    |

| 3.9 Power Flow                                   |    |

| 3.10 Data Flow                                   |    |

| 3.11 Control Multiplexing                        |    |

| 3.12 Firmware and Boot Management                |    |

| 3.13 Hardware Authentication                     |    |

| 3.14 Submodule Encrypted Communication           |    |

| 3.15 Hardware Protections                        |    |

| 3.16 Display                                     |    |

| Chapter 4 - Results                              |    |

| Chapter 5 - Future Work                          |    |

| 5.1 Multi-Mission Controls                       |    |

| 5.2 SGPN and CSPR Integration and Completion     |    |

| Chapter 6 - Conclusion                           |    |

| References                                       |    |

| Appendix                                         | 61 |

| Appendix A: Hardware and Software Design Details | 61 |

| Appendix B: EEPROM_WRITE_PASSWORD                |    |

| Appendix C: CSPR_V7.lpf                          |    |

| Appendix D: hardware_protections.vhd             |    |

| Appendix E: CSPR_MODULES.vhdl                    |    |

| Appendix F: top.vhdl                             |    |

## **Table of Contents**

# List of Figures

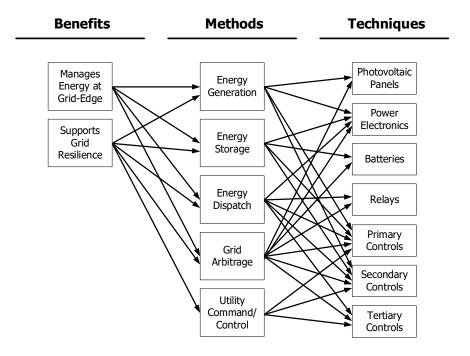

| Fig. 1. Design Inventory for Distributed Energy Resource                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

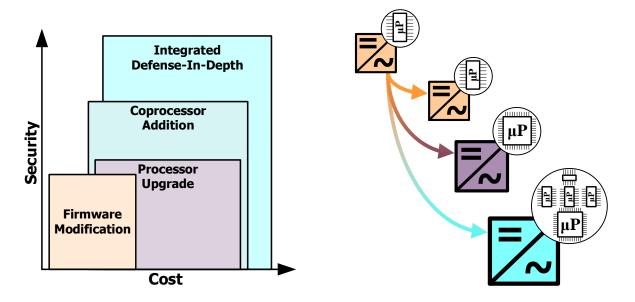

| Fig. 2: Cost/Performance regions (left) for various security solutions (right)                                                                                      |

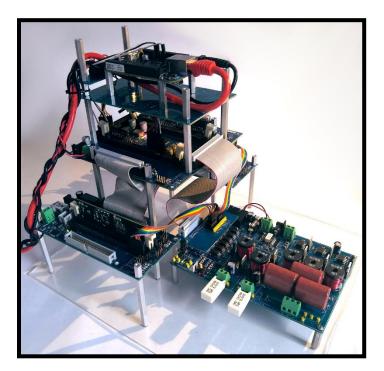

| Fig. 3. Cybersecure Power Router prototype                                                                                                                          |

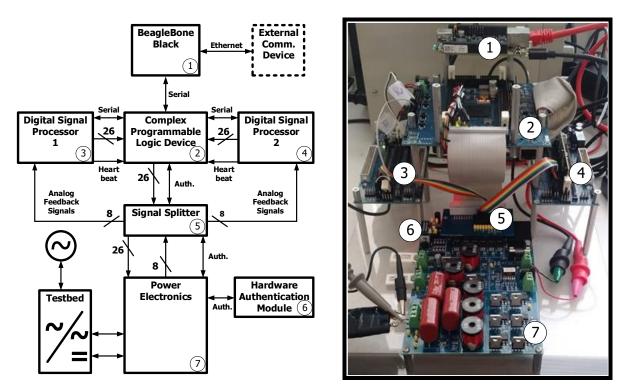

| Fig. 4. Block diagram (left) and figure (right) of Cybersecure Power Router prototype                                                                               |

| Fig. 5. Minimal configuration of Cybersecure Power Router prototype                                                                                                 |

| Fig. 6. Asynchronous buck converter schematic of Power Electronics Evaluation Board of the UCB project                                                              |

| Fig. 7. Asynchronous boost converter schematic of Power Electronics Evaluation Board of the UCB project                                                             |

| Fig. 8. 3-Phase inverter filter and current sensing schematic of Power Electronics Evaluation<br>Board of the UCB project                                           |

| Fig. 9. 3-Phase inverter/rectifier switching stage schematic of Power Electronics Evaluation<br>Board of UCB project                                                |

| Fig. 10. Power Electronics Evaluation Unified Controller Board, with Signal Splitter and Hardware Authentication Module, used in Cybersecure Power Router prototype |

| Fig. 11. USB to UART schematic of Digital Signal Processor board of the UCB project 20                                                                              |

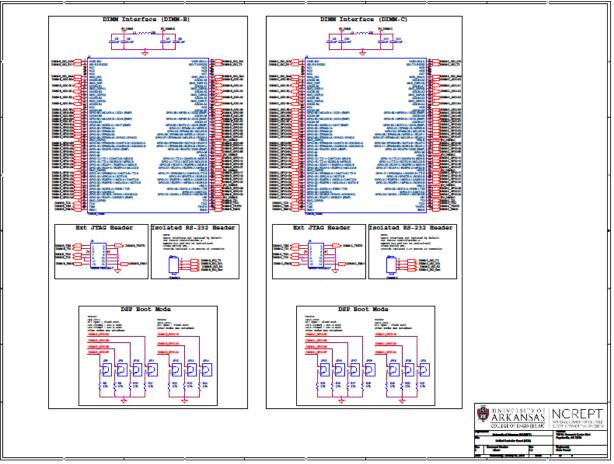

| Fig. 12. DIMM pinout of Digital Signal Processor board of the UCB project                                                                                           |

| Fig. 13. Majority of analog and digital I/O used by Digital Signal Processor board of UCB project                                                                   |

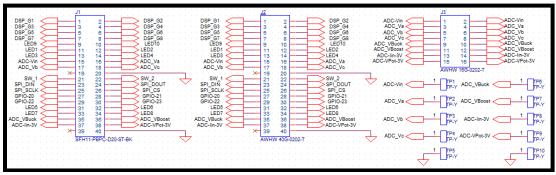

| Fig. 14. IDCs in Complex Programmable Logic Device Unified Controller Board                                                                                         |

| Fig. 15. PCB layout of Complex Programmable Logic Device board of UCB project                                                                                       |

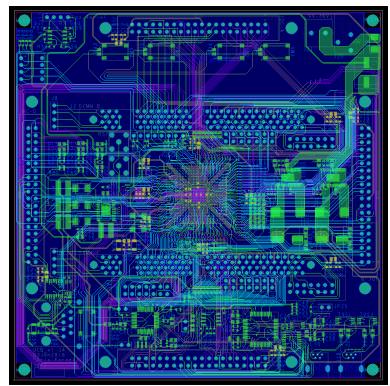

| Fig. 16. Fabricated Complex Programmable Logic Device board of UCB project used in<br>Cybersecure Power Router prototype                                            |

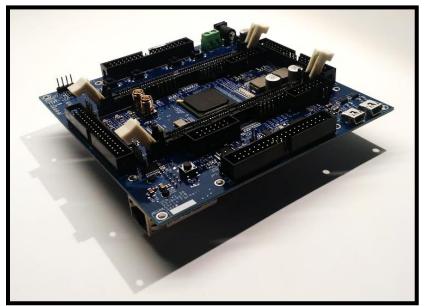

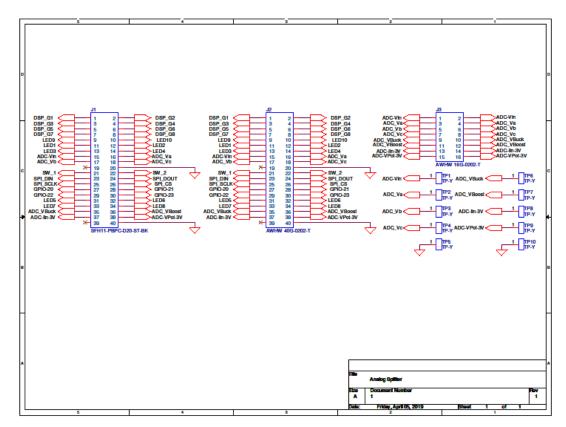

| Fig. 17. Complete schematic of Signal Splitter                                                                                                                      |

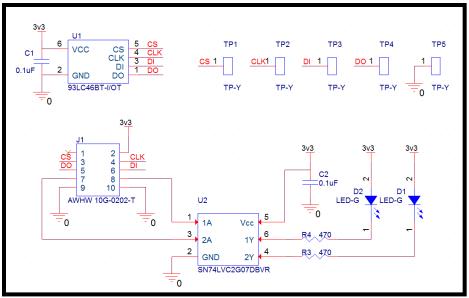

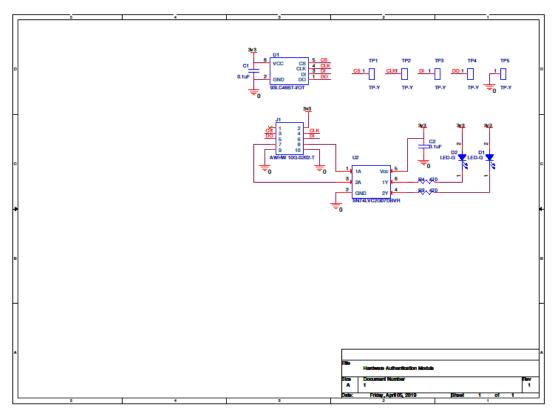

| Fig. 18. Complete schematic of Hardware Authentication Module                                                                                                       |

| Fig. 19. Hardware Authentication Module used in Cybersecure Power Router prototype                                                                                  |

| Fig. 20. BeagleBone Black                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 21. Block diagram of testbed used in Cybersecure Power Router project                                                                                                                                  |

| Fig. 22. Simplified block diagram of grid-connected power flow capabilities of UCB hardware and Cybersecure Power Router                                                                                    |

| Fig. 23. Block diagram of clock generation within Complex Programmable Logic Device of the Cybersecure Power Router                                                                                         |

| Fig. 24. Block diagram of data bus controller within Complex Programmable Logic Device of the Cybersecure Power Router                                                                                      |

| Fig. 25 .Block diagram of serial interface within Complex Programmable Logic Device of the Cybersecure Power Router                                                                                         |

| Fig. 26. Firmware code snippet to generate heartbeat from Digital Signal Processors                                                                                                                         |

| Fig. 27. Heartbeats of Controllers 1 and 2 while running identical firmware                                                                                                                                 |

| Fig. 28. Block diagram of control multiplexing using Digital Signal Processor signals and<br>Hardware Authentication Module within the Complex Programmable Logic Device of the<br>Cybersecure Power Router |

| Fig. 29. Block diagram of hot patching process                                                                                                                                                              |

| Fig. 30. Diagram of CSPR components involved in hardware authentication                                                                                                                                     |

| Fig. 31. Excerpt from EEPROM datasheet, with erroneous information noted                                                                                                                                    |

| Fig. 32: Hardware Authentication Module communication beside oscilloscope capture                                                                                                                           |

| Fig. 33. Block diagram of encrypted serial communication within Complex Programmable Logic Device used in the Cybersecure Power Router                                                                      |

| Fig. 34. Shoot-Through hardware protection                                                                                                                                                                  |

| Fig. 35. LED display diagram for Cybersecure Power Router                                                                                                                                                   |

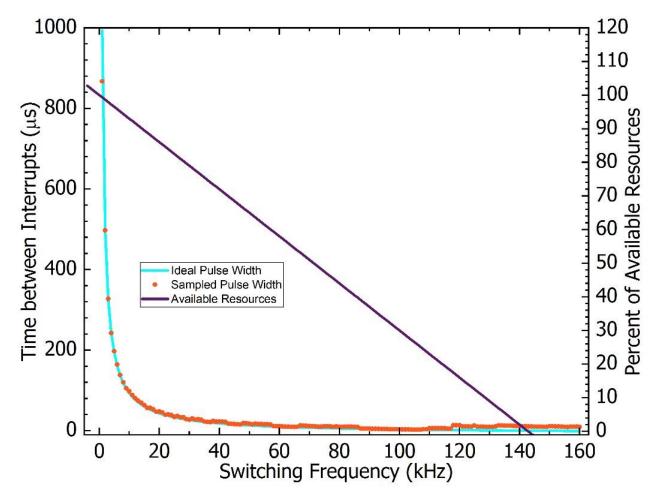

| Fig. 36. Time between execution cycles of controller firmware vs. switching frequency                                                                                                                       |

| Fig. 37. Detail of Figure 36                                                                                                                                                                                |

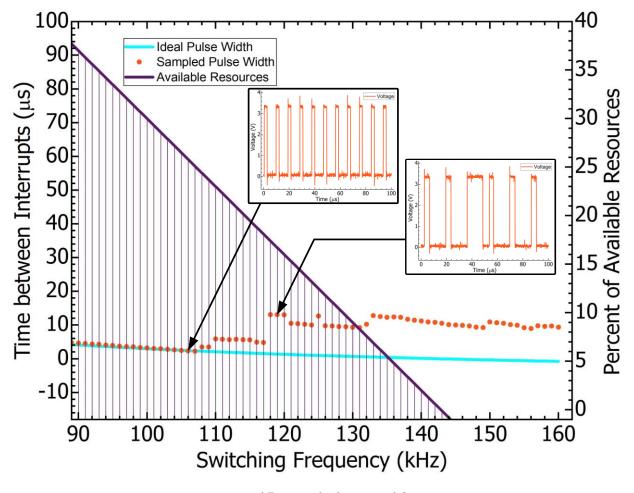

| Fig. 38. Inverter output voltage at 114, 118, and 128 kHz switching frequencies                                                                                                                             |

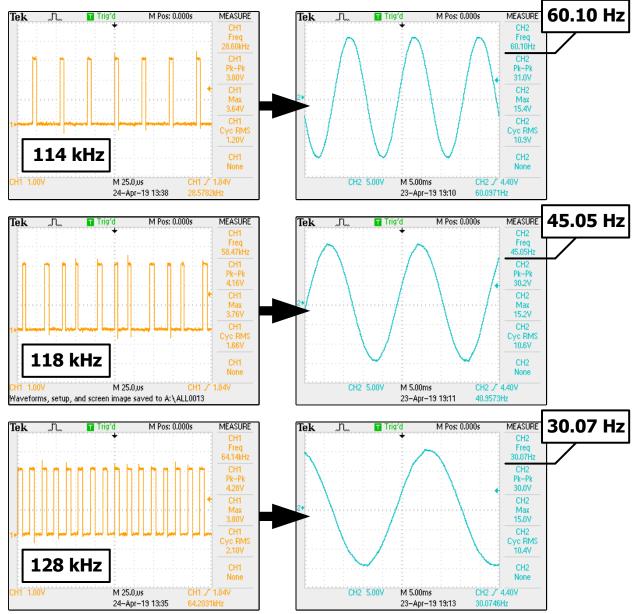

| Fig. 39. Inverter output during controller transition                                            | . 48 |

|--------------------------------------------------------------------------------------------------|------|

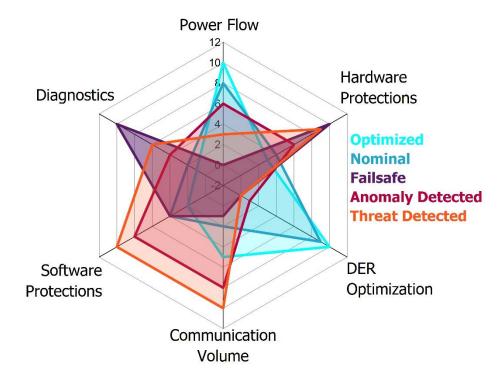

| Fig. 40: Radar chart of missions for controls                                                    | . 51 |

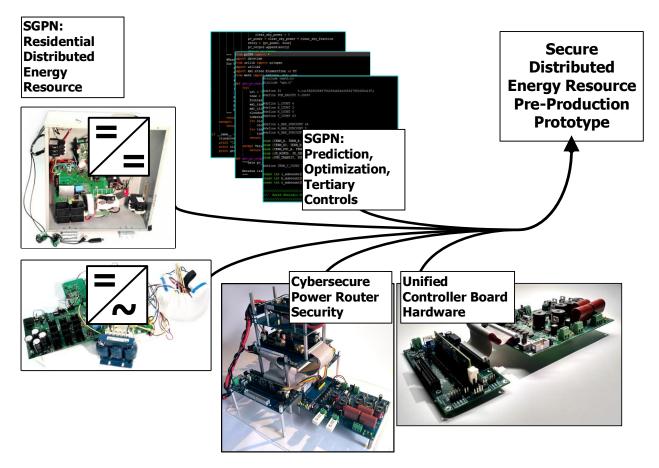

| Fig. 41: CSPR and SGPN migration                                                                 | . 52 |

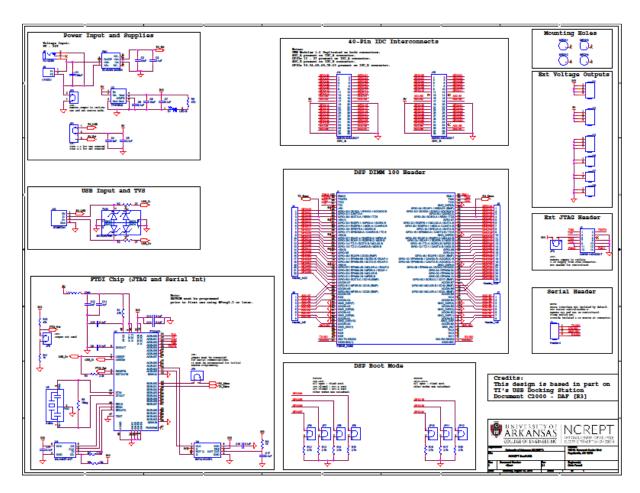

| Fig. 42. Digital Signal Processor Unified Controller Board schematic                             | . 61 |

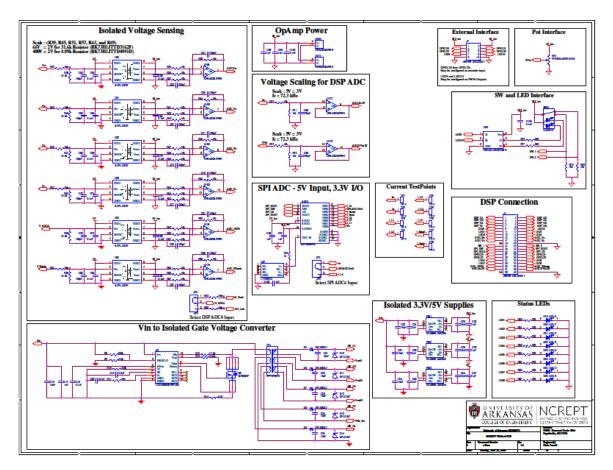

| Fig. 43. Power Electronics Evaluation Unified Controller Board schematic                         | . 62 |

| Fig. 44. Complex Programmable Logic Device Unified Controller Board schematic                    | . 63 |

| Fig. 45. BeagleBone Black schematic                                                              | . 64 |

| Fig. 46. Hardware Authentication Module schematic                                                | . 64 |

| Fig. 47. Analog Splitter schematic                                                               | . 65 |

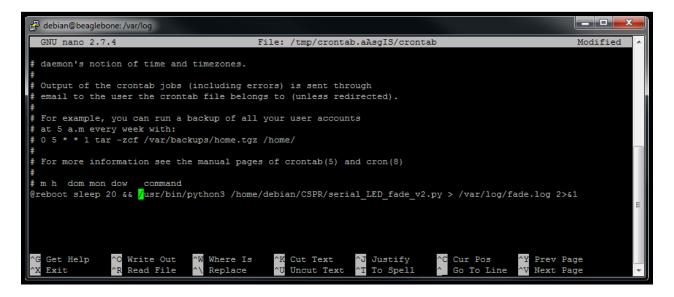

| Fig. 48. Crontab configuration on BeagleBone Black to run CPLD UCB LED control script or startup |      |

| Fig. 49. Content of LED control Python script running on the BeagleBone Black                    | . 66 |

# List of Tables

| TABLE I: Security-by-Design cycles      | 5    |

|-----------------------------------------|------|

| TABLE II: Defense-in-Depth Dependencies | 6    |

| TABLE III: Cyber-Physical Attack Matrix | . 15 |

| TABLE IV: MachXO2 Family Features       | . 24 |

| TABLE V: Available MCLK frequencies     | . 24 |

#### **Chapter 1 - Introduction**

The reliability and safety of the electrical grid face challenges. These challenges include aging infrastructure, tight regulatory environments, and the integration of new technologies. Power electronics are some of these new technologies, and provide a wide range of assets and liabilities to the electrical grid, its operation, and its evolution. Reactive power compensation, phase load balancing, battery energy storage systems, solar power, and flexible ac transmission are all potential assets. These devices may pose serious threats to both the electrical grid and interdependent critical infrastructure [1]. As these grid-connected power electronics permeate more of the electrical grid, the need for their security becomes greater [2].

A series of questions can begin this investigation of security for grid-connected power electronics, and establish appropriate security measures [3]. The first question is "what benefit does the device provide?" In the present case, the distributed energy device manages energy at the edge of the electrical grid, and supports grid resilience.

#### Fig. 1. Design Inventory for Distributed Energy Resource

The next question is "how does the device provide those benefits?" A distinction in method and technique is useful, here. The methods to realize energy management at the grid-edge are energy generation, storage, dispatch, and arbitrage (see "Methods" in Figure 1). These methods identify a particular process or type of system. The techniques to realize energy management at the grid-edge include the use of photovoltaic panels, dc converters, inverters, batteries, and hierarchical controls. These techniques identify the practical elements of a method, that is, of a process or system.

After arriving at a set of techniques, the next question is "what can happen to prevent this technique from working?" A boost converter or more complicated topology can be used to provide maximum power point tracking, current control, and hardware protection for a string of photovoltaic panels. In short, answering the question is difficult [4]. The hardware can fail, the switches can cause excessive electromagnetic interference, and noisy environments can corrupt transmitted data. Poor design can also cause various failures. The list of possible points and modes of failure is extensive for a complex system like a converter. Putting aside the incomplete answer, the next question is "what can be done to protect this technique?" In the case of a dc converter, more robust hardware can be used, filters can reduce electromagnetic interference, and error detection in communication can limit the use of corrupted data. This is not an exhaustive list of points and modes of failures or security measures. To better organize and address these questions, product lifecycle management and design dependency can be used (and will be discussed in greater depth in the next section). Product lifecycle management can be used to consider security of a device from specification all the way to end-of-life, and illustrates the security-by-design process. Design dependency can be used to build layers of security to protect an asset or the system as a whole, and illustrates the defense-in-depth method. A cyber-physical threat matrix is built on the

design dependencies listed and the implementation of security techniques to address the potential threats.

The Cybersecure Power Router (CSPR) uses the security-by-design process and defense-indepth method to realize a cybersecure distributed energy resource. The CSPR operates as a solar inverter and battery energy storage system. It has hierarchical controls and network communication, allowing a utility operator to control the device, its operation, and its power flow. Finally, it employs a number of security features for a wide range of functionalities. These security features include AES-128 encryption for network communication, hardware-assisted monitoring for improved firmware integrity during runtime, hardware protection during nominal operation, and more.

The Smart Green Power Node (SGPN) is a device developed at the University of Arkansas to manage energy resources at the grid edge, specifically in residential applications. The SGPN predicts and optimizes power flow of a solar inverter and battery energy storage system. Hierarchical controls and network communication are also included within the design of the SGPN. The system optimizes power flow of the energy resources through powerful predictive algorithms and weather data collection. The system is rated for 2 kW operation.

The Unified Controller Board (UCB) project is a set of hardware, firmware, software, and instructional material also developed at the University of Arkansas. The devices within the UCB project include a DSP docking station; a complex programmable logic device (CPLD) PCB; buck and boost converter and inverter PCB; and several expansion boards. The Unified Controller Boards are designed around flexible controls and modular hardware.

A real-world system of sophisticated, grid-tied power electronics is needed to show the practical demands and limits of security. The use of the Smart Green Power Node and the Unified

3

Controller Board devices as a prototype for the Cybersecure Power Router was used for such a real-world system. The SGPN is a distributed energy resource with many sophisticated assets. The 2 kW power rating of the system provides an appreciable power flow for grid-connected applications. The UCB devices are modular, allowing for rapid configurability of hardware and controls. The UCB software and firmware is extensible, allowing for the integration of security features and changes in control hierarchy. The combination of these two systems provides the necessary power flows, complexity, and direct results necessary for this cyber-security investigation.

The present work shows the security-by-design process and defense-in-depth method for a grid-connected, distributed energy resource prototype. The security features chosen are developed and tested within a grid-connected power electronics context. Security features to protect firmware integrity at runtime are specifically investigated. The ability for the CSPR prototype to quantify firmware integrity degradation and respond to firmware integrity failure is shown. This ability is provided by the CSPR prototype monitoring and maintaining liveness of controllers through control multiplexing. Future research into greater flexibility and resiliency of controls is discussed. Finally, the necessary work to migrate research from the Smart Green Power Node and the Cybersecure Power Router into a pre-production prototype is presented.

### **Chapter 2 - Technical Background**

Security-by-design ensures greater security of a device by considering both the processes

behind the development and life of a device, and the device itself. Product lifecycle management

[5] serves as the framework for security-by design. This process stands over and above the IEEE

standard for system, software, and hardware verification and validation [6].

| Lifecycle Stage         | Security Feature(s)                                                        |  |  |  |

|-------------------------|----------------------------------------------------------------------------|--|--|--|

| Hardware                |                                                                            |  |  |  |

| Specification           | IEEE Standards (e.g., 1547)                                                |  |  |  |

| Simulation              | Accurate Modeling, Thermal Co-Simulation                                   |  |  |  |

| Design                  | IEEE Standards (e.g., 3001, 3003), Thermal Co-Design                       |  |  |  |

| Verification            | Electrical Rule Checking, Design Review, Hardware-In-the-Loop              |  |  |  |

| Firmware                |                                                                            |  |  |  |

| Development             | Restricted Access, Version Control, Standard Protocols, Standard Libraries |  |  |  |

| Distribution            | Restricted Access, Message Digest, Server Authentication                   |  |  |  |

| Installation            | Message Digest, Error Detection and Correction                             |  |  |  |

| Run-Time                | Side Channel Analysis, Challenge-Response Authentication                   |  |  |  |

| Manufacture             |                                                                            |  |  |  |

| Fabrication             | Trusted Supplier, ISO 9001 Certification, Hardware Authentication          |  |  |  |

| Quality Control         | Burn-In Testing, Fuzz Testing, Standard Metrics                            |  |  |  |

| <b>Design</b> Iteration | Restricted Source Code and Design Files                                    |  |  |  |

| Operation               |                                                                            |  |  |  |

| Installation            | Certified Installers, Standard Connections, Lockout-Tagout                 |  |  |  |

| Use                     | Key Management, Challenge-Response Authentication, Behavior Analysis       |  |  |  |

| Aging                   | Hardware Health Diagnostics                                                |  |  |  |

| Attack                  | User Authentication, Command Whitelisting, Asset Segmentation              |  |  |  |

| Failure                 | Fails Safe, Hardware Protection, Resilient Communication                   |  |  |  |

| Recovery                | Startup Sequence, Sanity Check, Firmware Integrity Check                   |  |  |  |

| Maintenance             |                                                                            |  |  |  |

| Update                  | Patching, Maintained Uptime                                                |  |  |  |

| Replacement             | Modular Design                                                             |  |  |  |

| Upgrade                 | Modular Design, Reconfigurable Architecture, Flexible Controls             |  |  |  |

| End of Life             |                                                                            |  |  |  |

| Removal                 | Lockout-Tagout                                                             |  |  |  |

| Documentation           | Failure Modes, Effects, and Diagnostic Analysis (FMEDA)                    |  |  |  |

| Reiteration             | Restricted Access to Source Code, Specification and Quality Control        |  |  |  |

| Disposal                | Certified eWaste Recycling and Disposal                                    |  |  |  |

TABLE I: Security-by-Design cycles

Any device, a distributed energy resource in this case, has a lifecycle. It is specified, designed, fabricated, tested, installed, operated, uninstalled, and disposed of during that lifecycle. Each step in the lifecycle of a device serves some purpose. For instance, hardware specification creates the exhaustive list of design requirements for a device. The result of the hardware specification step is a list. How could security be applied to this step? The use of standards (in this case, IEEE 1547 for the design of utility electric power systems and distributed energy resources) provides greater assurance that the list created in the hardware specification step is exhaustive. Stated another way, the IEEE standards secures the intended result of hardware specification. The product lifecycle security approach also requires a designer to consider the full lifecycle of a device, not just the useful life. In the context of the electric grid, people install and remove distributed energy resources. By considering the lifecycle of a device, the safe installation and removal of a device is considered and included in the hardware and firmware design stages. For instance, a Lockout/Tagout technique can be designed for a solar inverter to keep both people and hardware safe during installation and removal [7].

Defense-in-depth provides layered security for assets of a device [8]. Returning to the "Design Inventory" from the introductory section, each technique in the design inventory process has dependencies. These dependencies arise from the techniques chosen to realize a device. An inverter depends on various switches, gate drivers, feedback signal chains, capacitors, other hardware components, and firmware to operate. Examples of these dependencies are listed in Table II, along with possible methods of security.

| Design Category       | Security Feature                                             |  |  |  |

|-----------------------|--------------------------------------------------------------|--|--|--|

| Component Health      | Hardware Authentication, Hardware Protections, Safety Factor |  |  |  |

| Feedback Signal Chain | Galvanic Isolation, Buffered I/O                             |  |  |  |

| Temperature Control   | Thermal Management, Current Limitation                       |  |  |  |

| Current Control       | Controller Current Limiting, Body Diodes, Fuses              |  |  |  |

TABLE II: Defense-in-Depth Dependencies

These dependencies are not spread across the lifecycle of a device, as illustrated in the securityby-design process. Rather, these dependencies are logical constituents of the design of a device, and are typically part of a complex, cyber-physical set of interdependencies [9]. For instance, how might one protect the current flow into the batteries from potentially damaging commands? Secure network communication [10] protects the battery energy storage system from noise and remote adversaries. If the secure network communication is defeated, current controls prevent harmful behavior of the device [11]. If the current controls are defeated, various design features (like galvanic isolation, buffered I/O, fuses, and over-design) allow the device to withstand or limit the harmful behavior [12]. In this case, the energy storage assets of the BESS are protected by layers of security.

Security features have a range of costs and performance gains [13]. Any change to the design of a system, including those to increase security, comes at a cost. This cost may include the price of more sophisticated integrated circuits, hardware to support increased power consumption, time to develop new firmware, or expertise to identify and execute security strategies. Improvements to security may come at a low cost. An existing system may extensively benefit from simple firmware management [14]. Such management, including revision, could greatly increase system security without incurring costs from additional hardware and hardware development. Beyond firmware management, an example of a firmware security feature is a checksum for network communication [15]. The inclusion of this security feature is lightweight: incurring a small increase in firmware size, computational load, and communication overhead. Checksums can prevent electromagnetic noise from corrupting communication, and weakly protect against a malicious actor tampering with communicated data. A checksum is an instance of a common security feature implemented in firmware, but is far from the full benefits of improved firmware management and security.

Fig. 2: Cost/Performance regions (left) for various security solutions (right)

Not all development leads to increased security. Consider the use of encrypted communication for a controller using a digital signal processor. The controller is responsible for the power flow through a solar inverter. Processing resources are required to encrypt and decrypt communication with the controller. The increased demands on the DSP during communication may cause overrun conditions [16] and degrade power processing. The system has more confidential communication, but at the cost of lower integrity of power processing. The general effect may be a less secure system, despite the addition of a security feature and the costs of development.

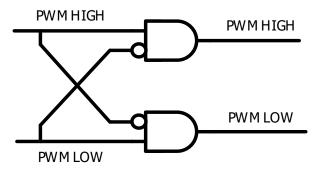

The cost/performance analysis for many security features used in the Cybersecure Power Router are readily available. The Advanced Encryption Standard 128-bit key (AES-128) is well defined [17],[18] and researched in various applications [19], [20], [21]. AES-128 is used in communication between hardware modules, and between outside controllers and the CSPR. The MD5 message-digest algorithm is also well researched [22], [23], [24]. The MD5 algorithm is used to protect the integrity of firmware as it passes from an outside controller, to the Cybersecure Power Router, and into any on-board controller. Hardware protections against overcurrent [25] and shoot-through conditions [26] are also well understood. Overcurrent and shoot-through conditions are used in both controller firmware and within the hardware logic of the Digital Signal Processors. These techniques are robust and well researched. Security techniques are still needed for other essential functions of any grid-connected power electronics.

Firmware security at runtime for power electronics is less researched and widely implemented [27]. Grid-connected power electronics typically use microprocessors, microcontrollers, or processors to run firmware. Microprocessors and microcontrollers often use watchdog timers to reset the device in the case firmware execution faults. If the controls of the power electronics run on the reset device, the power electronics will stop. The use of a watchdog timer may, therefore, be inappropriate for grid-connected power electronics, where downtime is to be minimized or eliminated [28]. Processors can provide more sophisticated techniques than microprocessors and microcontrollers to prevent, detect, identify, and recover from firmware execution faults, namely through using an embedded operating system [29], [30]. The choice of processors in grid-connected power electronics at runtime. Is there an option between a simple watchdog timer and a sophisticated embedded operating system? If so, how can the cost and performance of that runtime security be evaluated?

The two considered threats to CSPR firmware integrity during runtime are task overrun and firmware patching. Other threats are relevant [31], but fall outside the present scope of grid-connected power electronics. A task overrun condition occurs if a controller is not able to finish

the various tasks before another set of tasks are started [32]. The result is a degradation in the power flow of the power electronics, as shown later. Unlike task overrun, firmware patching is more likely to halt power flow altogether. The patching process requires the rebooting of the DSP running a controller, halting the controller during the process. The power flow through the electronics is, therefore, also halted as the DSP reboots.

Task overrun can be described as a controller's loss of liveness. Formally, liveness can be expressed as

$$\forall \alpha: \alpha \in S^*: (\exists \beta: \beta \in S^{\omega}: \alpha \beta \models P), \tag{1}$$

where  $\alpha$  and  $\beta$  are a sequence of states,  $S^*$  is a set of finite sequence states,  $S^{\omega}$  is a set of infinite sequence states, and P is a property (executability, in this case) [33]. Formally, this definition reads as there exists a state within an infinite set of states that satisfies a given property (executable), such that it does so given any arbitrarily sized sequence of compossible states. Or, simply, liveness means a task will be executed, even if there are many more tasks for a controller to complete. The tasks to be executed are part of interrupt service routines on the DSP, and in the present work are initiated every switching period. Each interrupt request (IRQ) initiating an interrupt service routine (ISR) is assigned a priority. The DSP resources handling an ISR are a critical section to other ISRs, especially those at the same priority. A critical section is a set of resources accessed or used by multiple processes [34]. For the present architecture, an IRQ can cause the interruption of an ISR in progress. This is also true if the ISR in progress and raised IRQ have the same priority. Here is an example from the Cybersecure Power Router. Assume the switching frequency is set at 30 kHz. Every 33.33 µs, a number of interrupt requests will be raised within the DSP. These IRQs signal the DSP to read various voltages and currents, perform mathematical operations, look up values, and set the pulse width modulation of several switches. Let's assume the DSP requires 80 µs to handle all of these tasks. While processing the last round of ISRs, new ISRs are created. The previous ISRs are interrupted and started again by the new IRQs. The tasks never complete, given their interruption and restart during processing. Theoretically, the result is the controller losing liveness.

A simple consideration of timing can maintain liveness. The controller has a maximum duration of time to complete its tasks:

$$T_{d,max} = \frac{1}{f_s},\tag{2}$$

where  $f_s$  is the switching frequency. In the example above, the 30 kHz switching frequency provides a maximum duration of 33.33 µs for the controller to complete its tasks. This is the theoretical maximum amount of time the controller can take to process the tasks of one switching period before being interrupted by the next switching period. The time the controller requires to complete the switching period tasks is not dependent on the switching frequency, however. The time required dependents more on the firmware, speed of the DSP, and competing interrupts (such as those from communication). This required time can be measured. This duration of time can vary, even if the firmware and processor remain the same. A mean time for the completion of tasks can be empirically found, and used to quantify available processing resources. The expected available resources can be articulated as

Available Resources (%) =

$$\left(1 - \left(T_{d,mean} * f_s\right)\right) * 100\%,$$

(3)

where  $T_{d,mean}$  is the mean of the duration of time the controller requires to complete switching period tasks, and  $f_s$  is the switching frequency. As this percentage approaches 0%, tasks are more likely to be interrupted, and liveness of the controller is more likely to be compromised.

The Cybersecure Power Router uses a signal sensitive to controller liveness and hardwareassisted monitoring to protect controller liveness. The next section details the design of the Cybersecure Power Router, especially the security features protecting controller liveness. Later sections provide the results and examination of the operation and performance of those security designs.

#### **Chapter 3 - Cybersecure Power Router**

#### 3.1 System Description

The Cybersecure Power Router is a set of switch-mode power electronics, controllers, and processors. The majority of controller devices used are from the Unified Controller Board project, developed by Chris Farnell at the University of Arkansas. These devices include the Power Electronics Evaluation Unified Controller Board (PE Eval UCB), Complex Programmable Logic Device Unified Controller Board (CPLD UCB), and the Digital Signal Processor Unified Controller Board (DSP UCB).

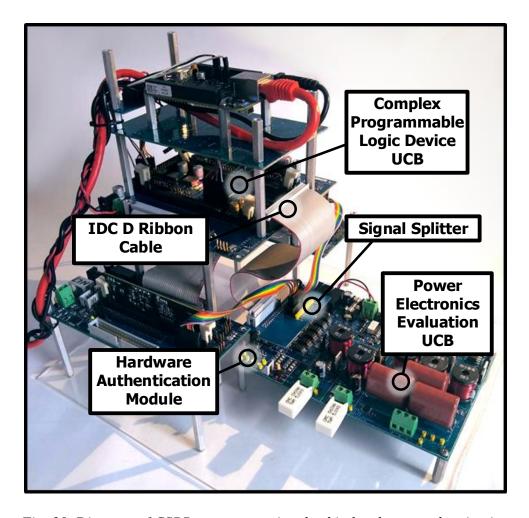

Fig. 3. Cybersecure Power Router prototype

The Digital Signal Processor Unified Controller Board uses many design features of the Texas Instruments' TMDSDOCK28335 Digital Signal Processor docking station. The power electronics of the PE Eval UCB are a buck converter, boost converter, and an inverter/rectifier. A testbed provides dc and ac power flow to provide safe and reliable conditions for testing. Two Digital Signal Processors are used in the prototype. Each DSP is capable of controlling the power electronics. A Complex Programmable Logic Device UCB provides many security features, and multiplexes the control signals of the DSPs. The Hardware Authentication Module is used to authenticate the power electronics and enable power flow. The Signal Splitter routes analog signals to both DSPs from the power electronics. Finally, a BeagleBone Black provides high-level control and Ethernet communication to the CPLD UCB.

*Fig. 4. Block diagram (left) and figure (right) of Cybersecure Power Router prototype* The CSPR prototype can be reconfigured. The modular design allows flexibility in both hardware and control. A more simplified configuration of the prototype could use one or two DSPs on the CPLD UCB, as shown below.

Fig. 5. Minimal configuration of Cybersecure Power Router prototype

The following table lists the security threats and mitigations chosen for the Cybersecure Power

Router.

| Asset                   | Threat                            | Mitigation                        |  |  |  |

|-------------------------|-----------------------------------|-----------------------------------|--|--|--|

| Communication           |                                   |                                   |  |  |  |

| Confidentiality         | System Surveillance [35]          | AES-128 Encryption [36]           |  |  |  |

| Integrity               | Corrupted Firmware [37]           | Error Detection                   |  |  |  |

| Availability            | Unauthorized User Access [38]     | HW-Asst. Monitor, Key Mgmt.       |  |  |  |

| Firmware                |                                   |                                   |  |  |  |

| Distribution            | Tampered Firmware [39]            | Encryption, Error-Detection       |  |  |  |

| Installation            | Reduced Integrity                 | MD5 Hash Check                    |  |  |  |

| Loading                 | System Downtime [40]              | Control Multiplexing              |  |  |  |

| Runtime                 | Operation Outside Parameters [41] | Heartbeat, HW-Asst. Monitor       |  |  |  |

| Hardware                |                                   |                                   |  |  |  |

| Authenticity            | Counterfeit Hardware [42]         | Hardware Authentication           |  |  |  |

| <b>Power Processing</b> |                                   |                                   |  |  |  |

| Quality                 | Harmonic Distortion [43]          | Robust Hardware/Controller Design |  |  |  |

| Availability            | System Downtime [44]              | Control Multiplexing              |  |  |  |

| Response                | Non-Recoverable State [45]        | Robust Controller Design          |  |  |  |

TABLE III: Cyber-Physical Attack Matrix

Chris Farnell's contributions to the Cybersecure Power Router project

The asset inventory, threats, and mitigations are not exhaustive. The above table shows the current

work done and where the security is implemented.

### **3.2 Power Electronics**

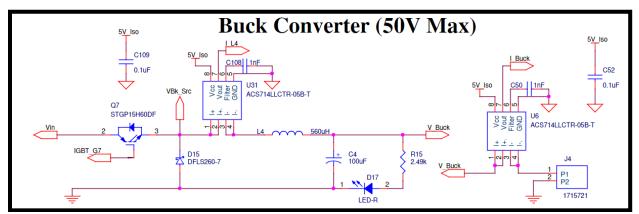

The power electronics of the Power Electronics Evaluation Unified Controller Board consist of switch-mode power supplies, signal chains for controls and feedback, isolated power supplies, voltage and current sensors, filters, ports, ancillary circuits, and human-machine interfaces. Control signals routed from the Complex Programmable Logic Device enter the Power Electronics Evaluation Unified Controller Board through a 40 pin insulation-displacement connector. The control signals then pass through 120  $\Omega$  resistors to trigger HCPL-3120-300E optocouplers. The optocouplers then drive the STGP15H60DF insulated-gate bipolar transistors that act as switches. An isolated, flyback regulator using the LT3748EMS integrated circuit energizes the optocouplers to drive switching. The switch-mode power supplies of the board include an asynchronous buck converter, an asynchronous boost converter, and a three-phase inverter/rectifier. The buck converter provides current sensing before and after the 560 $\mu$ H, 100 $\mu$ F LC filter; and output voltage sensing. The buck converter is rated for an input voltage of 9 to 50 Vdc, and an output voltage of 0 to 50 Vdc. The voltage ratings can be increased if higher voltage rated capacitors are used on the input and output of the buck converter.

Fig. 6. Asynchronous buck converter schematic of Power Electronics Evaluation Board of the UCB project

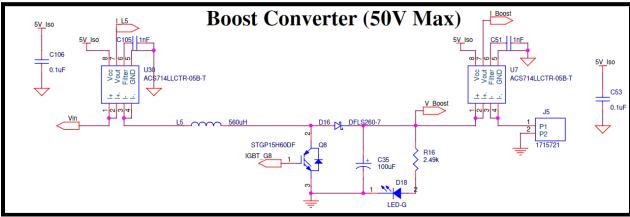

The asynchronous boost converter provides current sensing at the input and output; and output voltage sensing. The boost converter is rated for an input voltage of 9 to 50 Vdc, and an output voltage of 9 to 50 Vdc. The voltage ratings can be increased if higher voltage rated capacitors are used on the input and output of the boost converter.

Fig. 7. Asynchronous boost converter schematic of Power Electronics Evaluation Board of the UCB project

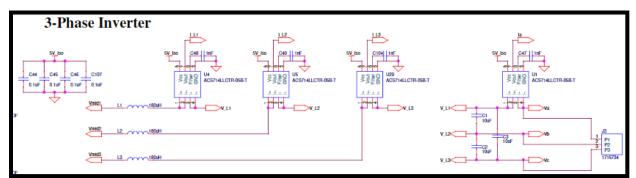

The three-phase inverter/rectifier can operate bi-directionally. When acting as an inverter, it can output a 1 Hz to +1000 Hz sinusoid from 0 to 50 Vac. The inverter is rated for 0 to 50 Vdc input. Current sensing is available on all three phases after the inductive filtering, and after capacitive filtering on phase A. Voltage sensing is available on the output of all three phases.

Fig. 8. 3-Phase inverter filter and current sensing schematic of Power Electronics Evaluation Board of the UCB project

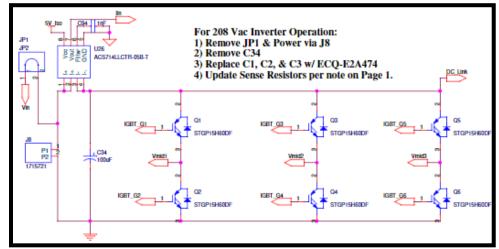

Three switching legs using STGP15H60DF insulated-gate bipolar transistors are the switching stage for the inverter/rectifier. As stated earlier, isolated power is provided to the gate drivers. The

low switches share the same isolated power rail. Jumper 1 (JP1) can be used to connect or disconnect the inverter/rectifier with the dc input used on the rest of the Power Electronics Evaluation board. Current and voltage sensing is provided between the dc bus and the capacitive filtering of the inverter/rectifier.

Fig. 9. 3-Phase inverter/rectifier switching stage schematic of Power Electronics Evaluation Board of UCB project

The PCB layout of the Power Electronics Evaluation board is shown below. Considerations were made for mixed analog/digital signals within the board. The isolated dc/dc power supplies and ACPL-C87B-000E optical isolation amplifiers provide isolation between analog signals in the mixed environment and the feedback signals supplied to the DSPs and CPLD.

Fig. 10. Power Electronics Evaluation Unified Controller Board, with Signal Splitter and Hardware Authentication Module, used in Cybersecure Power Router prototype

The total system provides buffered, isolated control and feedback signal chains; and common types of switch-mode power conversion capable of various power flows, with switching frequencies exceeding 100 kHz.

#### 3.3 Digital Signal Processor Board

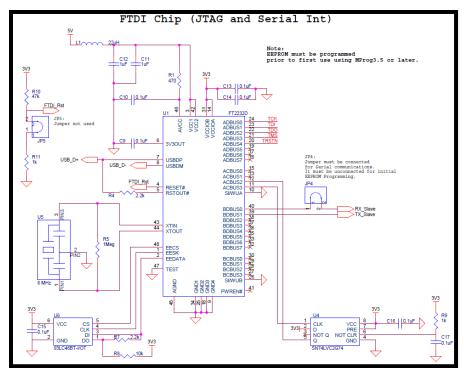

Two Digital Signal Processor Unified Controller Boards are used in the Cybersecure Power Router prototype. The modular designs of the Unified Controller Board allow two DSPs to slot into the Complex Programmable Logic Device Unified Controller Board. However, having two, standalone DSP boards provide advantages to the testing of the prototype. One advantage is greater accessibility of tools and probes to the I/O of the boards. Another advantage is more direct access to the serial communication ports of the DSPs. A third advantage to using the standalone DSP UCBs is the ability to apply power independent of the CPLD UCB. This allows DSPs to have controlled power disruptions while still allowing the rest of the CSPR prototype to continue operation. Serial communication with the DSPs in the DSP UCB is provided through a Future Technology Devices International (FTDI) Universal Serial Bus (USB) to Universal Asynchronous Receiver/Transmitter (UART) bridge. This USB to UART bridge is the FT2232D FTDI chip. The receive and transmit lines between the FTDI chip and the DSP are also accessible from the General Purpose Input/Output (GPIO)-28 and GPIO-29 pins. This configuration allows USB connectivity with a computer and with a UART device. For the Cybersecure Power Router prototype, the USB connectivity is used to control the DSP from Code Composer Studio and a LabVIEW script; and the UART connectivity is used to control the DSP from the CPLD UCB.

Fig. 11. USB to UART schematic of Digital Signal Processor board of the UCB project

The analog and digital I/O of the DSP within the DSP UCB is readily available to various tools and probes. A connection not pictured is the reset manually added to the TPS3828  $\overline{RESET}$  pin on

U6 of the F28335 DSP controller card. This reset connection cycles power to the DSP during firmware patching.

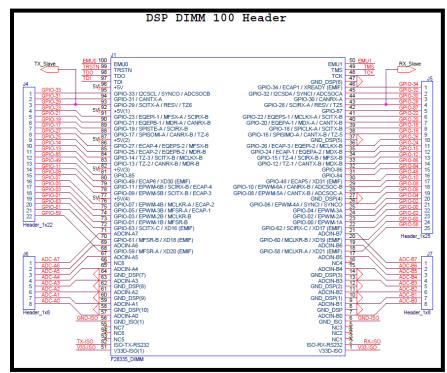

Fig. 12. DIMM pinout of Digital Signal Processor board of the UCB project

Two, 40-pin insulation-displacement connectors (IDCs) are used to bus analog and digital signals between the other Unified Controller Boards. The 28 digital signals use GPIO-00 through GPIO-27. The eight analog feedback signals use ADC-A0 through ADC-A7 for IDC A, and ADC-B0 through ADC-B7 for IDC B. Two 5 Vdc and Ground signals are provided within the 40-pin IDC.

Fig. 13. Majority of analog and digital I/O used by Digital Signal Processor board of UCB project

The Digital Signal Processor Unified Controller Board differs from the Texas Instruments C2000 DAF docking station source design. Mechanical holes are included to allow the use of standoffs. An isolated power supply provides steady power and noise rejection. The isolated power also overcomes ground loops that may be very problematic in noisy environments with long communication cables (such as those used in this prototype).

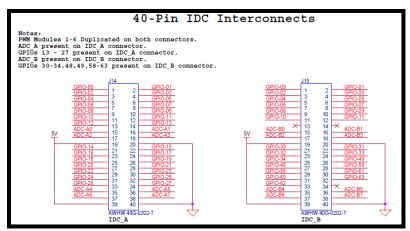

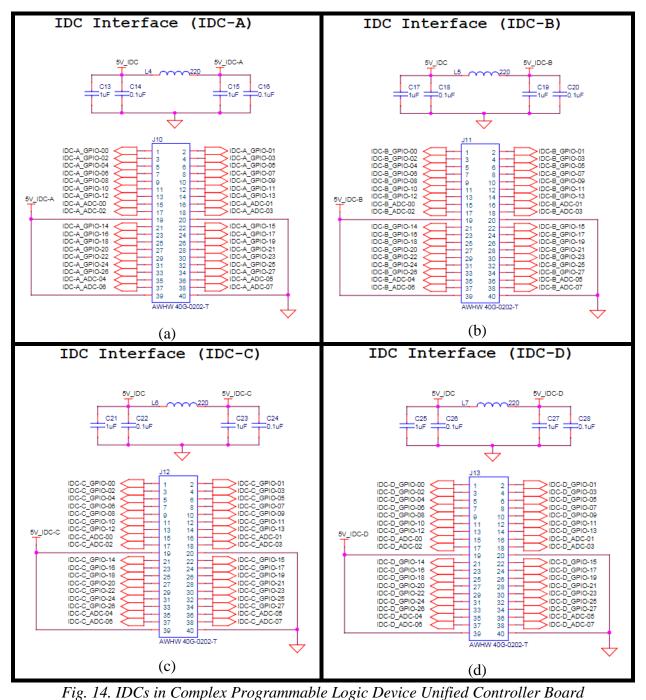

### 3.4 Complex Programmable Logic Device Board

The Complex Programmable Logic Device Unified Controller Board is the core of the Cybersecure Power Router. It routes digital control and communication signals between other Unified Controller Boards. It also instantiates the VHDL modules that provide functionality essential to the CSPR project. Four IDCs are provided to allow up to four converters or controllers to interface with each other. Presently, the IDCs allow converters or controllers to interface with one another and the CPLD. Each IDC provides 28 digital, GPIO channels; eight analog channels (typically as part of a feedback signal chain); two 5 Vdc output pins; and two Ground pins. High

frequency filtering is provided between the 5 Vdc power of the CPLD UCB and the 5 Vdc outputs of the IDCs.

The Complex Programmable Logic Device is Lattice's LCMXO2-7000HC. The IC is packaged as a TQFP with 144 pins. The XO2-7000 has the greatest resources of the MachXO2 family [46].

|                               |                    | XO2-256 | XO2-640 | XO2-640U <sup>1</sup> | XO2-1200 | XO2-1200U1 | XO2-2000 | XO2-2000U1 | XO2-4000 | XO2-7000 |

|-------------------------------|--------------------|---------|---------|-----------------------|----------|------------|----------|------------|----------|----------|

| LUTs                          |                    | 256     | 640     | 640                   | 1280     | 1280       | 2112     | 2112       | 4320     | 6864     |

| Distributed RAM (k            | bits)              | 2       | 5       | 5                     | 10       | 10         | 16       | 16         | 34       | 54       |

| EBR SRAM (kbits)              |                    | 0       | 18      | 64                    | 64       | 74         | 74       | 92         | 92       | 240      |

| Number of EBR SF kbits/block) | AM Blocks (9       | 0       | 2       | 7                     | 7        | 8          | 8        | 10         | 10       | 26       |

| UFM (kbits)                   |                    | 0       | 24      | 64                    | 64       | 80         | 80       | 96         | 96       | 256      |

| Device Options:               | HC <sup>2</sup>    | Yes     | Yes     | Yes                   | Yes      | Yes        | Yes      | Yes        | Yes      | Yes      |

|                               | HE <sup>3</sup>    |         |         |                       |          |            | Yes      | Yes        | Yes      | Yes      |

|                               | ZE <sup>4</sup>    | Yes     | Yes     |                       | Yes      |            | Yes      |            | Yes      | Yes      |

| Number of PLLs                | ł                  | 0       | 0       | 1                     | 1        | 1          | 1        | 2          | 2        | 2        |

| Hardened                      | I2C                | 2       | 2       | 2                     | 2        | 2          | 2        | 2          | 2        | 2        |

| Functions:                    | SPI                | 1       | 1       | 1                     | 1        | 1          | 1        | 1          | 1        | 1        |

|                               | Timer/Coun-<br>ter | 1       | 1       | 1                     | 1        | 1          | 1        | 1          | 1        | 1        |

TABLE IV: MachXO2 Family Features

The CPLDs of the MachXO2 family also provide a number of internal clock frequencies for use, in addition to the phase lock loops provided.

| MCLK (MHz, Nominal) | MCLK (MHz, Nominal) | MCLK (MHz, Nominal) |  |  |

|---------------------|---------------------|---------------------|--|--|

| 2.08 (default)      | 9.17                | 33.25               |  |  |

| 2.46                | 10.23               | 38                  |  |  |

| 3.17                | 13.3                | 44.33               |  |  |

| 4.29                | 14.78               | 53.2                |  |  |

| 5.54                | 20.46               | 66.5                |  |  |

| 7                   | 26.6                | 88.67               |  |  |

| 8.31                | 29.56               | 133                 |  |  |

TABLE V: Available MCLK frequencies

The extensive I/O of the MachXO2-7000HC is predominantly utilized by the GPIO of IDC A, B, C, and D; connections with the slots designed for DSP cards; serial peripheral interface with an analog to digital converter; Flash programmer/JTAG interface; button inputs; and an LED display. IDC A GPIO, dual in-line package (DIP) switches, push buttons, and four wire communication with the Lattice Flash Programmer connect to Bank 0 of the MachXO2-7000HC. Dual In-Line Memory Module (DIMM) slots connect DSPs cards to the MachXO2-7000HC. The connections between the DIMM-B slot and the MachXO2-7000HC are through Bank 1. The connections between the DIMM-C slot and the MachXO2-7000HC are through Bank 2. IDC C also connects with the MachXO2-7000HC through Bank 2. LED1 through LED8 interface with the MachXO2-

7000HC through Bank 1. The XPort connections interface with MachXO2-7000HC with the Lantronix Ethernet adapter. This interface is not currently developed. Serial communication interface (SCI) receive and transmit port are connected to Bank 3. The two, serial peripheral interface (SPI) analog to digital converters (ADCs) are also connected to Bank 3. The serial communication with the two FTDI chips (one for the DSPs, the other for the CPLD) interface at Bank 3. Bank 4 of the MachXO2-7000HC provides an external clock and reset signal. Finally, Bank 5 provides connections to the IDC D port.

*Fig. 15. PCB layout of Complex Programmable Logic Device board of UCB project* The components for the Complex Programmable Logic Device Unified Controller Board were reflowed using the Sikama 5/C reflow furnace in the Assembly Laboratory in the High Density Electronics Center at the University of Arkansas. A tin, silver, and copper alloy (SAC305) solder paste was applied using a stencil and squeegee. No solder paste was applied for the MachXO2-7000HC. A thin layer of no clean flux was applied to the pads of the TQFP footprint on the

Complex Programmable Logic Device Unified Controller Board PCB. After the application of solder paste, flux, and the population of surface mount components, the boards were flowed in the Sikama 5/C reflow furnace.

Fig. 16. Fabricated Complex Programmable Logic Device board of UCB project used in Cybersecure Power Router prototype

After inspection and debugging, the through-hole components were populated. Another round of visual, manual, and electrical inspection tested for shorts, unconnected legs, high integrity solder joints, and correct part orientation. Finally, a debug utility was flashed onto the CPLD and tested the I/O.

### 3.5 Signal Splitter

Two DSPs are used in the Cybersecure Power Router prototype. Two DSP Unified Controller Boards were used to interface the DSPs to the rest of the prototype. To route the analog feedback signals, eight Y connections needed to be created from the output of the Power Electronics Evaluation Unified Controller Board to the ADC input of the two DSP UCBs. A simple printed circuit board was designed and fabricated to provide this split analog feedback signal. No buffering is provided on the Signal Splitter on account of existing buffered output from the PE Eval UCB.

Fig. 17. Complete schematic of Signal Splitter

Test points are provided for each analog signal. Two ground test points are provided to reduce the size of the ground loop of a probe. Female/Female jumper wires connect the analog output of the Signal Splitter PCB to the ADC inputs of the two DSP UCBs.

# **3.6 Hardware Authentication Module**

An embedded, 1 kilobyte password is used to authenticate the power electronics of the Cybersecure Power Router. This password is continually checked by the hardware-assisted monitor instantiated in the CPLD UCB. The password is stored in both the Microchip 93LC46BT-I/OT EEPROM and within the memory of the hardware-assisted monitor.

Fig. 18. Complete schematic of Hardware Authentication Module

The Hardware Authentication Module and the CPLD UCB communicate with a four-wire protocol, through the IDC D port. A Texas Instruments SN74LVC2G0 is included to drive two indicator LEDs. The pins for power, ground, the four-wire protocol, and the two indicator LEDs are routed through a 10-pin header.

Fig. 19. Hardware Authentication Module used in Cybersecure Power Router prototype

This assembly plugs into the J7 header on the Power Electronics Evaluation Unified Controller Board. Test points are included for the four-wire protocol and a ground to minimize the ground loop during oscilloscope data collection.

# **3.7 BeagleBone Black**

Texas Instruments' BeagleBone Black provides an embedded Linux environment for sophisticated, high-level operations.

Fig. 20. BeagleBone Black

The BeagleBone Black uses a 1 GHz ARM Cortex-A8 processor, and runs Debian Linux. The CPLD UCB and the BeagleBone Black communicate serially. The embedded operating system provides a platform for Python scripts and powerful utilities for automation, analysis, and debugging.

### 3.8 Test Bed

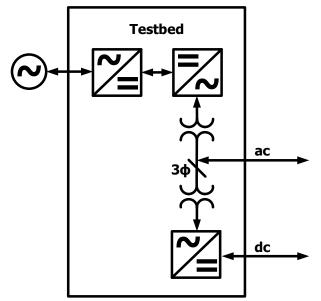

A testbed provides controlled ac and dc power flow to and from the Cybersecure Power Router.

Fig. 21. Block diagram of testbed used in Cybersecure Power Router project

The testbed functions like a microgrid, allowing power assets to be added in a variety of ways while maintaining controlled power flow and a utility frequency (independent of the utility frequency of the electrical grid). The ac power is three phase, and galvanically isolated through low frequency transformers.

#### **3.9 Power Flow**

The Cybersecure Power Router shows a security-by-design process and defense-in-depth methods for a Distributed Energy Resource (DER). The security-by-design process outlines both the assets and their dependencies to be secured. To create this inventory of assets and dependencies, a specific device or system must be chosen. Presently, a modular, grid-tied inverter/rectifier distributed energy resource is chosen. The power assets of this DER include onsite energy generation, energy storage, and bi-directional power flow with the grid.

Fig. 22. Simplified block diagram of grid-connected power flow capabilities of UCB hardware and Cybersecure Power Router

Other resources can be integrated within the system. The diagram shows a three-phase inverter/rectifier working in tandem with a photovoltaic panel and battery energy storage system. The PE Eval UCB includes an asynchronous buck and boost converter that may be used to interface dc energy resources, in addition to the three-phase inverter/rectifier provided.

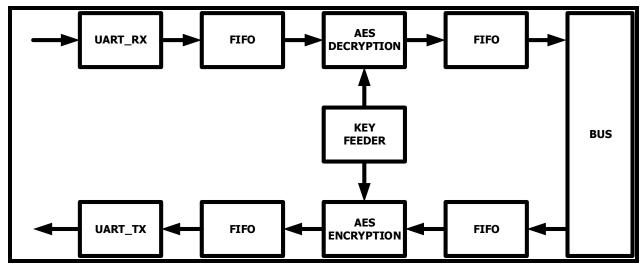

# 3.10 Data Flow

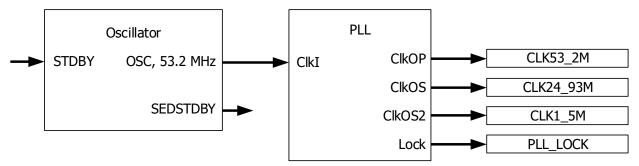

A hardware-assisted monitor and other utilities are instantiated within the complex programmable logic device on the CPLD Unified Controller Board. The monitor and utilities are developed in the Lattice Diamond integrated development environment. The monitor and utilities are developed using the Very high speed integrated circuit Hardware Description Language (VHDL). The complete source code is included in Appendix B. Not included in the appendix are the Intellectual Property (IP) cores used within Lattice Diamond, such as the phase-locked loop (PLL) or the digital memory. An oscillator is instantiated within the CPLD to provide an internal clock at 53.2 MHz. This clock is supplied to an internal phase-locked loop. A 53.2 ( $1 \cdot f_{clk}$ ), 24.93 ( $1/2 \cdot f_{clk}$ ), and 1.5 ( $1/32 \cdot f_{clk}$ ) MHz clock signal is derived from the original 53.2 MHz clock signal from the oscillator. The 53.2 MHz clock is used for the hardware-assisted monitor and other high speed applications. The 24.93 MHz clock is used for serial communication and the data bus. The 1.5 MHz clock is used for the four-wire communication with the Hardware Authentication Module.

Fig. 23. Block diagram of clock generation within Complex Programmable Logic Device of the Cybersecure Power Router

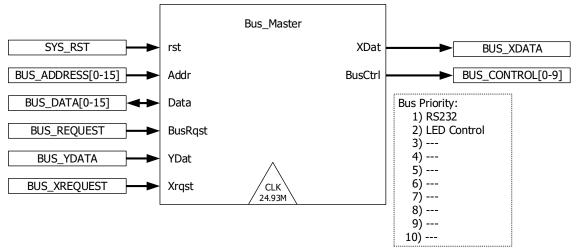

A data bus is instantiated to allow data flow between various modules. The bus uses 16-bit addresses and 16-bit data. Prioritized access to the bus is given to modules. Currently, ten modules can be prioritized according to access privileges. In addition to controlling the data bus, the Bus Master contains Randomly Accessible Memory (RAM). This memory is used as registers for various controls and functions. A separate memory allocation is used for the booting partition of the digital signal processors.

Fig. 24. Block diagram of data bus controller within Complex Programmable Logic Device of the Cybersecure Power Router

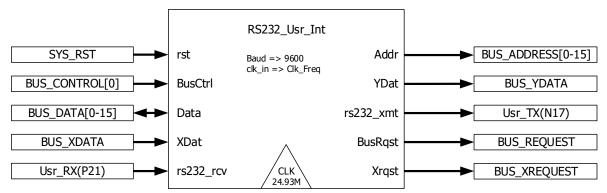

The serial communication with the modules instantiated in the CPLD uses a 9600 baud rate, and connects through Bank 3 of the MachXO2-7000HC CPLD. The current serial communication is designed for fixed packet lengths.

Fig. 25 .Block diagram of serial interface within Complex Programmable Logic Device of the Cybersecure Power Router

# 3.11 Control Multiplexing

A defense-in-depth approach to controller security is explored in the Cybersecure Power Router. Control multiplexing strengthens the availability and integrity of the hardware controller, and the entire system by extension. The concept of multiplexing is common in telecommunication [47], computer networks [48], and various signal conditioning and sampling [49] contexts. The concept is extended to an entire bus of control signals for the Cybersecure Power Router. The controllers running on the DSPs toggle a bit on GPIO-24 every time a switching cycle is completed. The firmware snippet is provided below.

| 783 |                                                  |

|-----|--------------------------------------------------|

| 784 | <pre>if (HeartBeat_High){</pre>                  |

| 785 | <pre>GpioDataRegs.GPASET.bit.GPI024 = 1;</pre>   |

| 786 | HeartBeat_High = false;                          |

| 787 | }else{                                           |

| 788 | <pre>GpioDataRegs.GPACLEAR.bit.GPI024 = 1;</pre> |

| 789 | HeartBeat_High = true;                           |

| 790 | }                                                |

| 791 |                                                  |

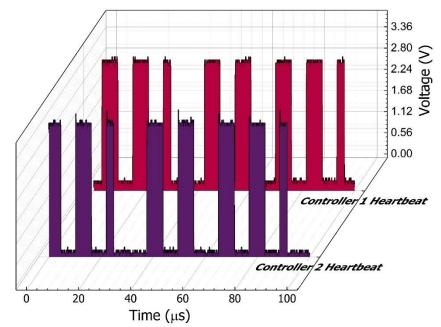

Fig. 26. Firmware code snippet to generate heartbeat from Digital Signal Processors

The toggled GPIO-24 pin creates a clock signal visible to external devices.

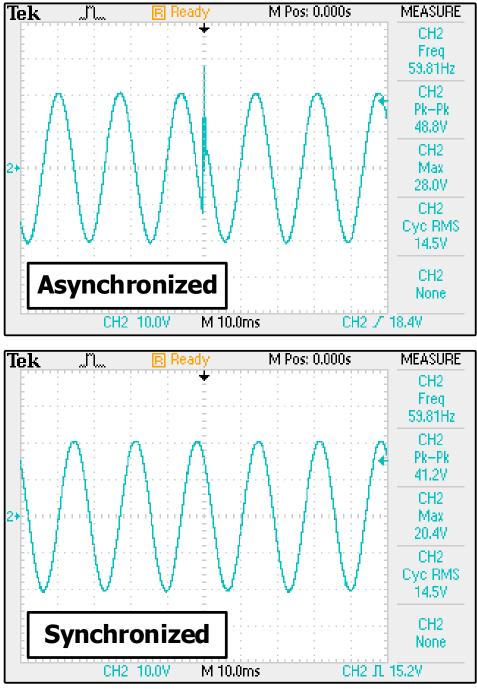

Fig. 27. Heartbeats of Controllers 1 and 2 while running identical firmware

This clock signal is the heartbeat of the controller, and is used by the Hardware Assisted Monitor to assess the liveness of the controller. Presently, if the heartbeat of a controller beats more often than 75  $\mu$ s, it is considered to maintain liveness. If the heartbeat takes longer than the given 75  $\mu$ s to toggle, the Hardware Assisted Monitor considers the controller to have lost liveness. The period

of the heartbeat is a function of the controller's clock rate and execution cycles of the firmware. A slower processor or a longer execution cycle would require a longer period between heartbeats.

The security features instantiated in the CPLD communicates with the Hardware Authentication Module on the UCB PE Eval board to authenticate the power electronic hardware. The password stored in the EEPROM of the UCB Hardware Authentication Module is checked against the password stored in the memory of the CPLD Hardware Authentication Module.

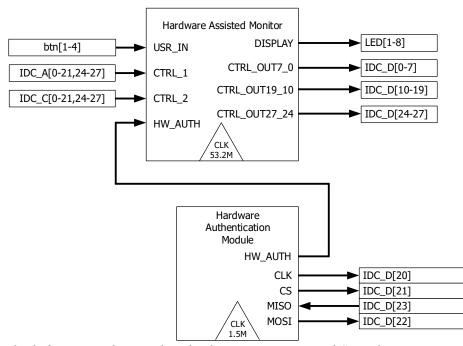

Fig. 28. Block diagram of control multiplexing using Digital Signal Processor signals and Hardware Authentication Module within the Complex Programmable Logic Device of the Cybersecure Power Router

If the two passwords match, then the "hardware is authorized" (HW\_AUTH) signal goes HIGH (TRUE). If there is a mismatch between the symmetric keys, then the HW\_AUTH signal goes LOW (FALSE). This mismatch will occur when the key stored in the power electronics (i.e., the Hardware Authentication Module) differs from the key stored in the controller (i.e., the Hardware Assisted Monitor).

The Hardware Assisted Monitor uses the liveness of the controllers and the authentication of the power electronics to decide the routing of control signals. When the hardware is authenticated, control signals from Controller 1 or Controller 2 are routed to the power electronics. The Hardware Assisted Monitor assigns priority to Controllers 1 over Controller 2 if both controllers have liveness. If only one controller has liveness, that controller's control signals are routed to the power electronics. If no controller has liveness, the hardware is held in a lockout state. User inputs from buttons 1 through 4 can override this logic to manually set the routing of control signals.

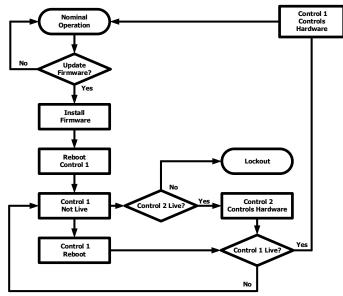

#### 3.12 Firmware and Boot Management

The control multiplexing behavior of the Hardware Assisted Monitor prevents downtime during firmware updates. The firmware is loaded into memory instantiated in the CPLD UCB allocated for boot loading. The firmware is loaded through encrypted serial communication and the internal data bus.

Fig. 29. Block diagram of hot patching process

When a command is given, the designated DSP is power cycled by the CPLD. The power cycled DSP boots from the allocated memory hosting the new firmware. The DSP boots using this new firmware. While the DSP is booting, hardware control is passed to the second DSP. The hardware

continues operating while the first DSP boots with the new firmware. When the first DSP resumes operation and provides a heartbeat with a period less than 75  $\mu$ s, it is either passed control of the hardware, or remains on standby. The above block diagram illustrates this process for Controller 1 being updated. A similar process is used for updating the firmware of Controller 2. As of the time of this writing, this uptime during update process is being developed.

Hot patching refers to modifying currently used data in system memory. Hot patching, strictly speaking, refers to a process that only applies to software. The present process is similar, but works at the firmware and hardware level. Here, the process modifies currently used data flow (like control signals) in a running system. The result of both techniques is the same: a running system while patches, updates, and other fixes are applied.

#### 3.13 Hardware Authentication

Authentication of the Power Electronics Evaluation Unified Controller Board requires the Hardware Authentication Module PCB, the PE Eval UCB, and the CPLD UCB. The process begins when power is applied to the PE Eval UCB. The on-board power is used to energize the Hardware Authentication Module PCB. The IDC D port is used to connect the PE Eval UCB and the CPLD UCB. In the CSPR prototype, the IDC D ribbon cable plugs into the Signal Splitter board, which plugs into the PE Eval UCB.

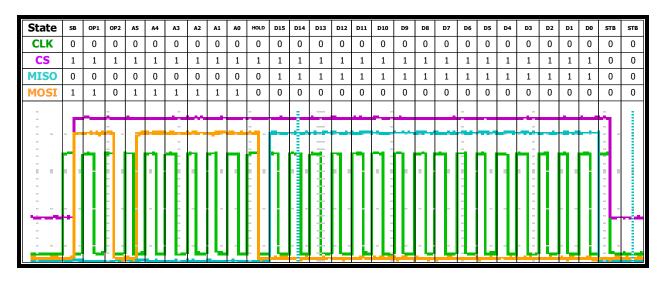

*Fig. 30. Diagram of CSPR components involved in hardware authentication* The CPLD UCB interfaces with the Hardware Authentication Module PCB through four connections in the IDC D connection. These four connections provide the chip select (CS), clock (CLK), master in slave out (MISO), and master out slave in (MOSI) signals between the EEPROM of the Hardware Authentication Module on the PE Eval UCB and the VHDL Hardware Authentication Module instantiated in the CPLD UCB. The clock signal provided is 1.5 MHz. Only the read command for the EEPROM is used in the authentication process. To read a specific memory address from the 93LC46BT-I/OT EEPROM [50], the following steps are required.

| Unaccounted clock cycle here.         TABLE 1-3: INSTRUCTION SET FOR X16 ORGANIZATION (93XX46B OF 93XX46C WITH ORG = 1) |        |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |