### University of Arkansas, Fayetteville

# ScholarWorks@UARK

Theses and Dissertations

5-2020

# A Virtual Space Vectors based Model Predictive Control for Three-**Level Converters**

Waleed Saad S. Alhosaini University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

#### Citation

Alhosaini, W. S. (2020). A Virtual Space Vectors based Model Predictive Control for Three-Level Converters. Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/3593

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

# A Virtual Space Vectors based Model Predictive Control for Three-Level Converters

# A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Waleed Saad S. Alhosaini

Jouf University

Bachelor of Science in Electrical Engineering, 2011

University of Arkansas

Master of Science in Electrical Engineering, 2015

# May 2020 University of Arkansas

| This dissertation is approved for recor | mmendation to the Graduate Council.   |  |

|-----------------------------------------|---------------------------------------|--|

| Yue Zhao, Ph.D. Dissertation Director   |                                       |  |

| Simon S. Ang, Ph.D. Committee Member    | Roy A. McCann, Ph.D. Committee Member |  |

| Shengfan Zhang, Ph.D. Committee Member  |                                       |  |

#### **ABSTRACT**

Three-phase three-level (3-L) voltage source converters (VSC), e.g., neutral-point clamped (NPC) converters, T-type converters, etc., have been deemed to be suitable for a wide range of medium- to high-power applications in microgrids (MGs) and bulk power systems. Compared to their two-level (2-L) counterparts, adopting 3-L VSCs in the MG applications not only reduces the voltage stress across the power semiconductor devices, which allows achieving higher voltage levels, but also improves the quality of the converter output waveforms, which further leads to considerably smaller output ac passive filters.

Various control strategies have been proposed and implemented for 3-L VSCs. Among all the existing control methods, finite-control-set model predictive control (FCS-MPC) has been extensively investigated and applied due to its simple and intuitive design, fast-dynamic response and robustness against parameter uncertainties. However, to implement an FCS-MPC on a 3-L VSC, a multi-objective cost function, which consists of a term dedicated specifically to control the dc-link capacitor voltages such that the neutral-point voltage (NP-V) oscillations are minimized, must be designed. Nevertheless, selecting proper weighting factors for the multiple control objectives is difficult and time consuming. Additionally, adding the dc-link capacitor voltages balancing term to the cost function distributes the controller effort among different control targets, which severely impacts the primary goal of the FCS-MPC. Furthermore, to control the dc-link capacitor voltages, additional sensing circuitries are usually necessary to measure the dc-link capacitor voltages and currents, which consequently increases the system cost, volume and wiring complexity as well as reduces overall reliability.

To address all the aforementioned challenges, in this dissertation research, a novel FCS-MPC method using virtual space vectors (VSVs), which do not affect the dc-link capacitor voltages of the 3-L VSCs, was proposed, implemented and validated. The proposed FCS-MPC strategy has the capability to achieve inherent balanced dc-link capacitor voltages. Additionally, the demonstrated control technique not only simplifies the controller design by allowing the use of a simplified cost function, but also improves the quality of the 3-L VSC output waveforms. Furthermore, the execution time of the proposed control algorithm was significantly reduced compared to that of the existing one. Lastly, the proposed FCS-MPC using the VSVs reduces the hardware cost and complexity as the additional dc-link capacitor voltages and current sensors are not required, which further enhances the overall system reliability.

© 2020 Waleed Saad S. Alhosaini All Rights Reserved

#### ACKNOWLEDGMENT

First and foremost, it is with sincere gratitude that I would like to thank my dissertation advisor, Dr. Yue Zhao, for his unyielding support and encouragement throughout my entire doctoral journey. Dr. Zhao's persistent advice and guidance have been pivotal in helping me grow immensely as a researcher. I cannot thank Dr. Zhao enough for his patience, thoughts, positive critique, inspiration, enthusiasm and motivation.

I would like also to acknowledge the members of my dissertation advisory committee, Dr. Simon Ang, Dr. Roy McCann and Dr. Shengfan Zhang, for their profound, insightful and constructive comments and suggestions to improve my work. Having them on my advisory committee has been a distinct honor; thus the sincere gratitude is also owed to them. I also owe debts of gratitude to my friends and lab mates, who technically contributed to my research: Mohammad Hazzaz Mahmud, Yuheng Wu and Fei Diao. I would also like to thank my other lab mates and friends with whom, I have many happy memories; so many thanks go to Edgar Escala, Dr. Luciano Garcia, Zhe Zhao, Vinson Jones, Haider Mhiesan, David Carballo, Dr. Shuang Zhao, Dr. Yufei Li, Nan Lin, Tylor Adamson, Zhuxuan Ma, Xinyuan Du, Eric Allee, Shamar Christian, Dr. Roberto Fantino, Zhongjing Wang. Finally, I would like to express my appreciation to my friend and lab mate Obaid Aldosari and his family. Together, we have shared so many enjoyable moments thousands of miles away from home.

I would like to acknowledge my doctoral sponsor, Jouf University, from which I earned my bachelor's degree, and wherein I will end to serve my country, for their financial support.

Lastly and most importantly, my beloved parents, Saad Alhosaini and Maryam Alafer, it is you who have made me who I am today; I am very proud of you and forever indebted to you. My wife,

Salma Alsabilah, without your love, patience, and support the doctoral journey would not have come to a good end.

# **DEDICATION**

This dissertation is dedicated to my parents, my siblings, my wife and my son "Saad".

# TABLE OF CONTENTS

| CHAPTER 1          | INTRODUCTION AND LITERATURE REVIEW                   | 1  |

|--------------------|------------------------------------------------------|----|

| 1.1 Traditional    | AC Power Grid and AC Microgrids                      | 1  |

| 1.1.1 Classit      | fication of Control Schemes of VSCs in AC MGs        | 7  |

| 1.1.1.1            | Control of Grid-Following VSCs                       | 7  |

| 1.1.1.2            | 2 Control of Grid-Forming VSCs                       | 10 |

| 1.1.1.3            | Control of Grid-Supporting VSCs                      | 13 |

| 1.1.2 Synch        | ronization of VSCs in AC MGs                         | 13 |

| 1.2 Classification | on of VSC Topologies for AC MGs                      | 15 |

| 1.2.1 Three-       | Phase 2-L VSCs                                       |    |

| 1.2.2 Three-       | Phase 3-L VSCs                                       | 16 |

| 1.2.2.1            | Three-Phase 3-L NPC VSCs                             | 17 |

| 1.2.2.2            | 2 Three-Phase 3-L T-Type VSCs                        | 18 |

| 1.3 Classification | on of Three-Phase 3-L VSC Control Methods            | 19 |

| 1.3.1 Conve        | ntional Linear and Nonlinear Control Methods         | 19 |

| 1.3.2 Finite       | Control Set Model Predictive Control (FCS-MPC)       | 21 |

| 1.3.3 DC-Li        | nk Capacitor Voltages Control                        | 23 |

| 1.4 Research Ob    | ojectives                                            | 25 |

| 1.5 Dissertation   | Organization                                         | 26 |

| CHAPTER 2          | MODELING OF THE GRID-CONNECTED AND CONVERTER SYSTEMS |    |

| 2.1 Introduction   |                                                      | 28 |

| 2.2 Modeling of    | Generic Three-Phase 3-L VSCs                         | 29 |

| 2.3 Modeling of    | f the DC Link                                        | 34 |

| 2.3.1 Contin       | nuous-Time Model for the DC-Link                     | 35 |

| 2.3.2 Discre       | te-Time Model for the DC-Link                        | 35 |

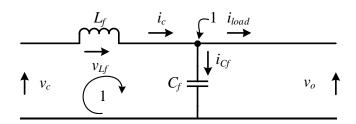

| 2.4 Modeling of    | f the VSC Output <i>LC</i> and <i>LCL</i> Filters    | 36 |

| 2.4.1 Model        | ing of the LC Filter                                 | 37 |

| 2.4.1.1            | Continuous-Time Model for the <i>LC</i> Filter       | 38 |

| 2.4.1.2            | 2 Discrete-Time Model for the <i>LC</i> filter       | 39 |

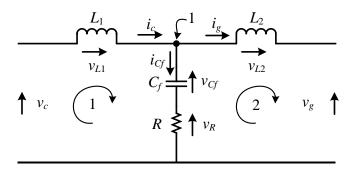

| 2.4.2 Model      | ing of the LCL filter                                                                     | 39 |

|------------------|-------------------------------------------------------------------------------------------|----|

| 2.4.2.1          | Continuous-Time Model for the <i>LCL</i> filter                                           | 41 |

| 2.4.2.2          | 2 Discrete-Time Model for the <i>LCL</i> filter                                           | 42 |

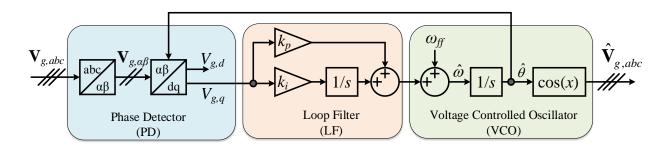

| 2.5 Modeling of  | f the SRF-PLL                                                                             | 43 |

| 2.5.1 Design     | n of the Proportional-Integral (PI) Control Gains in S-Domain                             | 47 |

| 2.5.2 Design     | n of the Proportional-Integral (PI) Control Gains in Z-Domain                             | 49 |

| 2.6 Concluding   | Remarks                                                                                   | 51 |

| CHAPTER 3        | AN ENHANCED MPC USIN VIRTUAL SPACE VECTORS FO                                             |    |

|                  | CONNECTED 3-L NPC CONVERTERS                                                              |    |

|                  | 1                                                                                         |    |

|                  | al MPC Strategies for 3-L NPC VSCs                                                        |    |

|                  | ol of the Grid-Following VSC                                                              |    |

|                  | ol of the Grid-Forming VSC                                                                |    |

| 3.3 Proposed M   | PC Strategies for 3-L NPC VSCs                                                            | 58 |

|                  | and Extended Switching States Synthetization                                              |    |

| 3.3.2 Gate S     | Signals Implementation                                                                    | 64 |

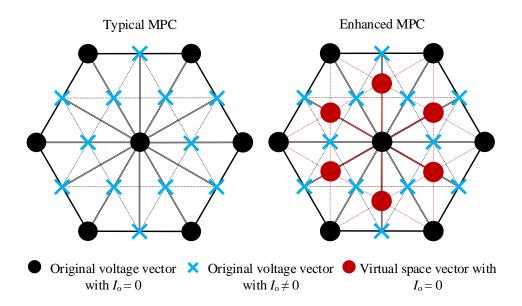

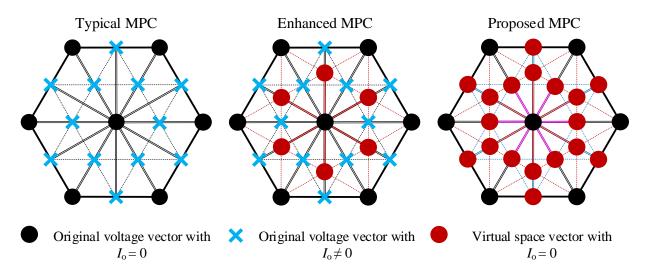

| 3.3.3 SV Di      | agram Comparison of Different MPC Strategies                                              | 64 |

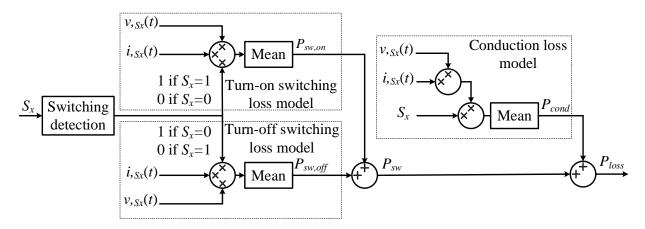

| 3.4 Power Loss   | Analysis                                                                                  | 65 |

| 3.4.1 Switch     | ning Power Loss Model                                                                     | 66 |

| 3.4.2 Condu      | action Power Loss Model                                                                   | 67 |

| 3.4.3 Three-     | Phase Power Loss Model                                                                    | 67 |

| 3.5 Simulation   | Studies                                                                                   | 68 |

| 3.6 C-HIL Impl   | ementation for the Various MPC Strategies                                                 | 79 |

| 3.6.1 C-HIL      | Test Setup                                                                                | 80 |

| 3.6.2 C-HIL      | Studies                                                                                   | 80 |

| 3.7 Concluding   | Remarks                                                                                   | 87 |

| CHAPTER 4        | A VIRTUAL SPACE VECTORS BASED MPC FOR INHERENT VOLTAGE BALANCING OF 3-L T-TYPE CONVERTERS |    |

| 4.1 Introduction | 1                                                                                         | 89 |

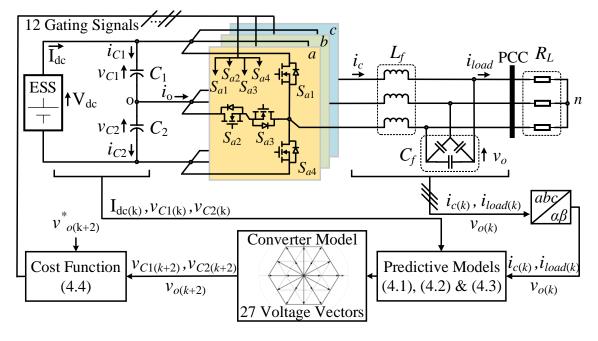

| 4.2 Typical and  | Proposed MPVC Strategies for Grid-forming VSCs                                            | 91 |

| 4.2.1 Comp       | ensation for the One-Step Calculation Delay                                               | 92 |

|                  |                                                                                           |    |

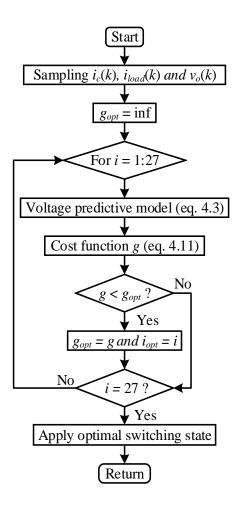

| 4.2.2 Conventional MPVC Algorithm                         | 93  |

|-----------------------------------------------------------|-----|

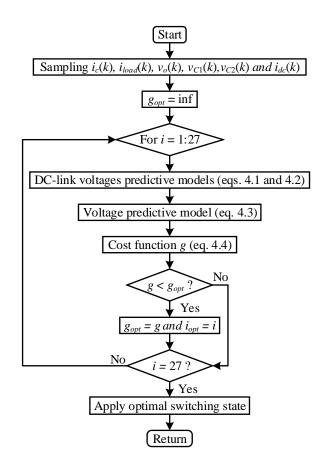

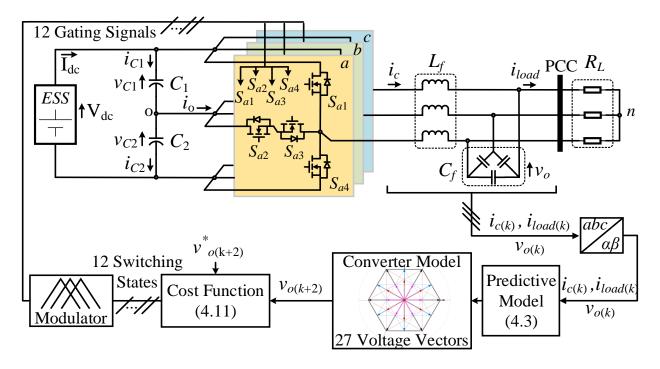

| 4.2.3 Proposed MPVC Algorithm                             | 95  |

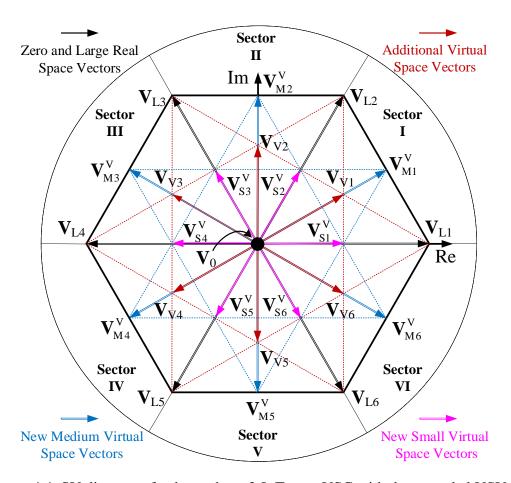

| 4.2.3.1 VSVs and Extended Switching States Synthetization | 96  |

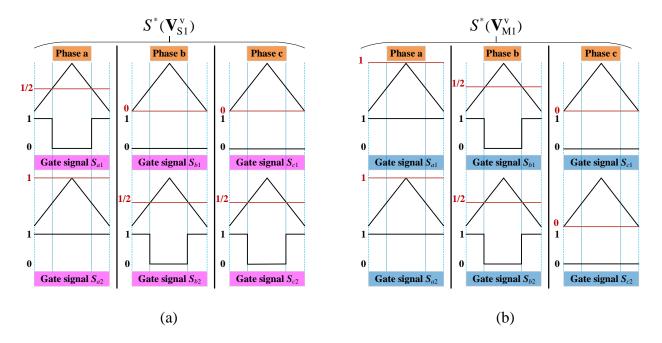

| 4.2.3.2 Gate Signal Implementation                        | 100 |

| 4.2.3.3 SV Diagrams Comparisons of Different MPCs         | 103 |

| 4.3 Power Loss Analysis                                   | 105 |

| 4.4 Simulation Studies                                    | 106 |

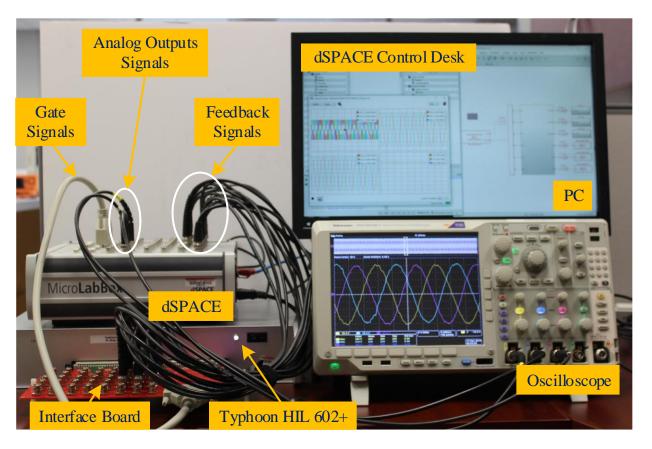

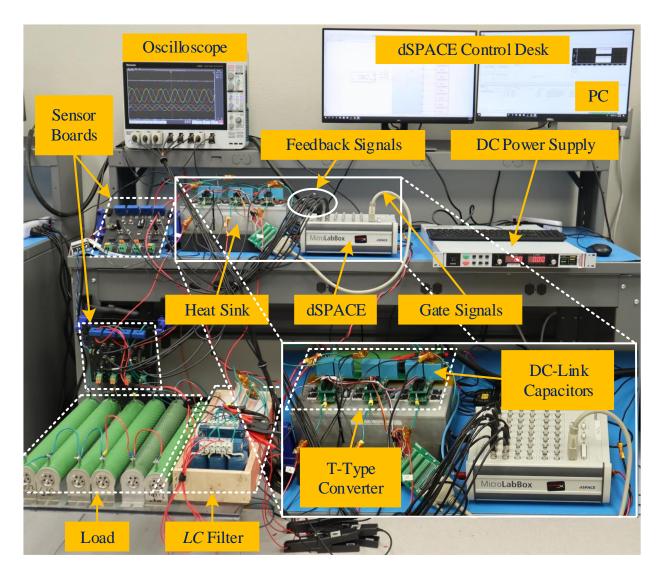

| 4.5 Practical Implementation for Various MPVC Methods     | 122 |

| 4.5.1 Experimental Test Setup                             | 122 |

| 4.5.2 Experimental Studies                                | 124 |

| 4.6 Summary                                               | 139 |

| 4.7 Concluding Remarks                                    | 144 |

| CHAPTER 5 CONCLUSIONS, CONTRIBUTIONS AND FUTURE WORK      |     |

| 5.1 Conclusions of This Dissertation                      | 146 |

| 5.2 Contributions of This Dissertation                    | 149 |

| 5.3 Future Research Work                                  | 151 |

| BIBLIOGRAPHY                                              | 153 |

# LIST OF FIGURES

# **CHAPTER 1**

| Figure 1.1: An illustration of the traditional electric power system.                   | 2  |

|-----------------------------------------------------------------------------------------|----|

| Figure 1.2: An illustration of an ac MG connected to the electric power system          | 6  |

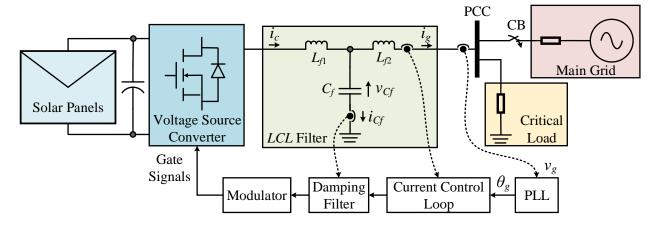

| Figure 1.3: One-line diagram of a grid-following PV inverter connected to the main grid | 8  |

| Figure 1.4: Passive-damping based control block diagram of a grid-following PV inverter | 9  |

| Figure 1.5: Active-damping based control block diagram of a grid-following PV inverter  | 9  |

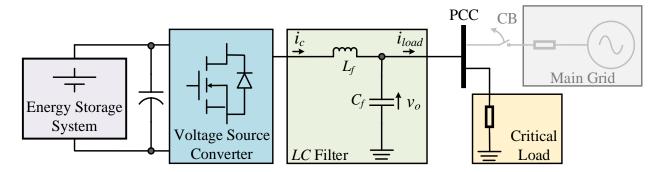

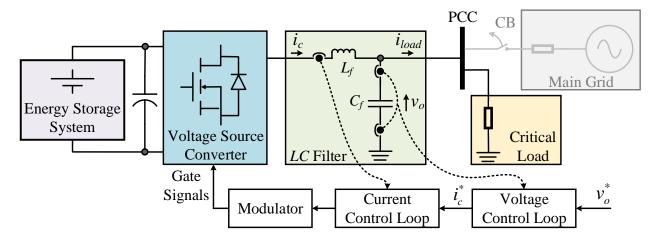

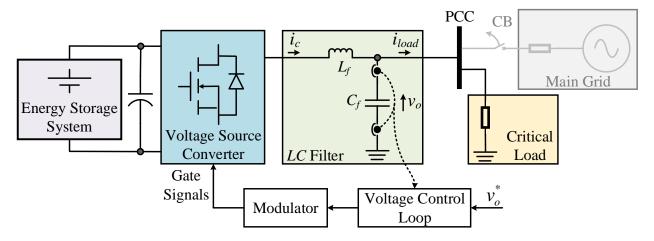

| Figure 1.6: One-line diagram of a grid-forming inverter connected to a critical load    | 11 |

| Figure 1.7: Dual-loop control block diagram of a grid-forming inverter.                 | 12 |

| Figure 1.8: Single-loop control block diagram of a grid-forming inverter.               | 12 |

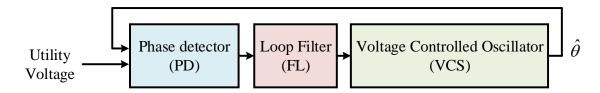

| Figure 1.9: Block diagram of a generic three-phase PLL system.                          | 14 |

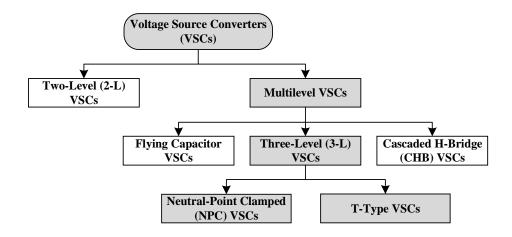

| Figure 1.10: Flow chart of the commonly used VSCs in MG applications.                   | 15 |

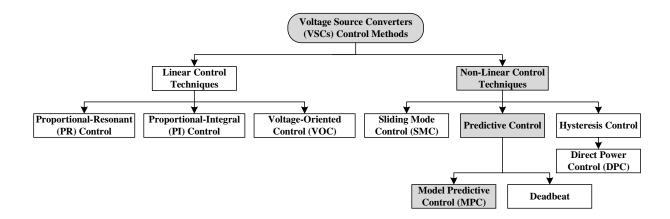

| Figure 1.11: Flow chart of common control methods for VSCs                              | 19 |

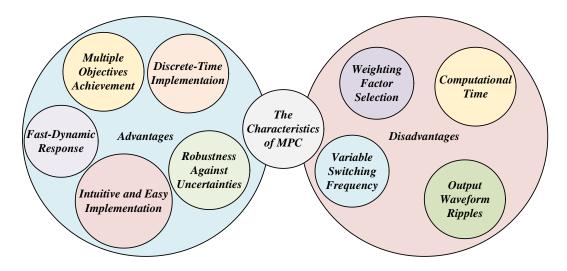

| Figure 1.12: Advantages and drawbacks of FCS-MPC.                                       | 22 |

| Figure 1.13: Reasons for FCS-MPC popularity in power electronics applications           | 23 |

| CHAPTER 2                                                                               |    |

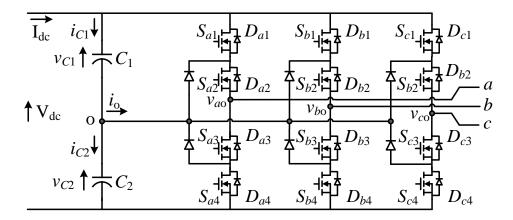

| Figure 2.1: Schematic of a three-phase 3-L NPC VSC.                                     | 30 |

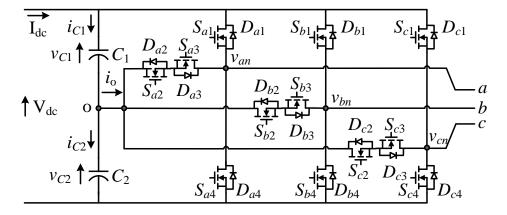

| Figure 2.2: Schematic of a three-phase 3-L T-type VSC                                   | 30 |

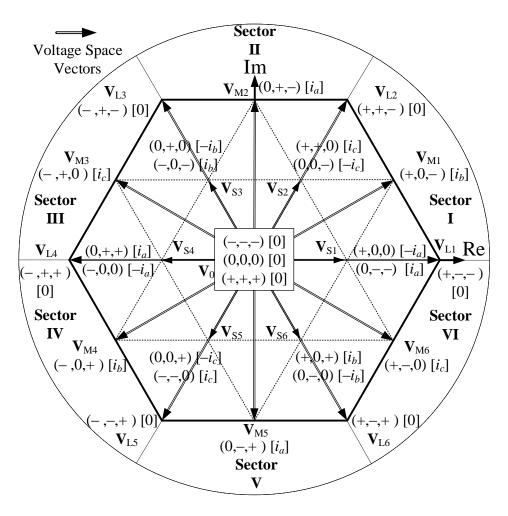

| Figure 2.3: SV diagram of the three-phase 3-L VSCs.                                     | 34 |

| Figure 2.4: One-line diagram of an <i>LC</i> filter.                                    | 37 |

| Figure 2.5: One-line diagram of an <i>LCL</i> filter.                                   | 41 |

| Figure 2.6: Control block diagram of an SRF-PLL.                                        | 44 |

| CHAPTER 3                                                                               |    |

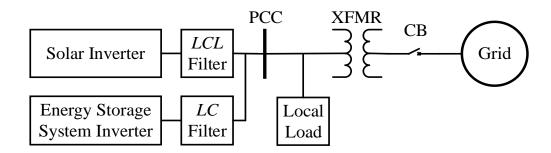

| Figure 3.1: One-line diagram of the MG systems studied in this chapter.                 | 53 |

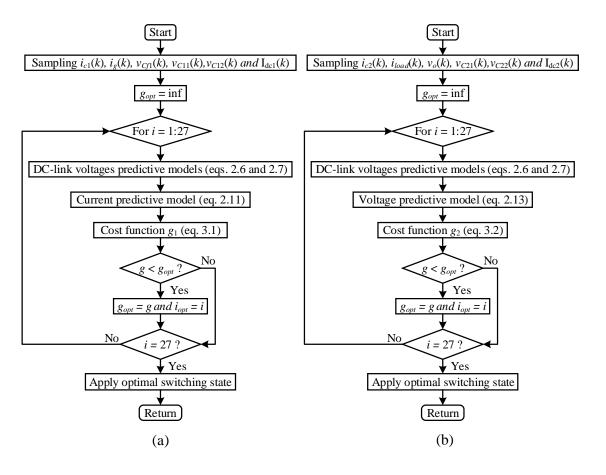

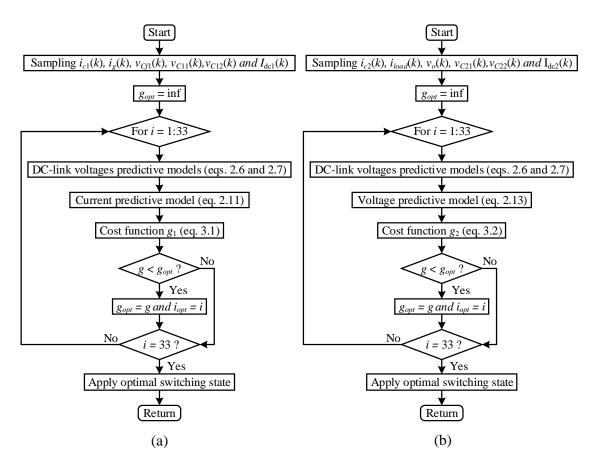

| Figure 3.2: Control algorithms of the typical MPC methods (a) MPCC and (b) MPVC 56                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

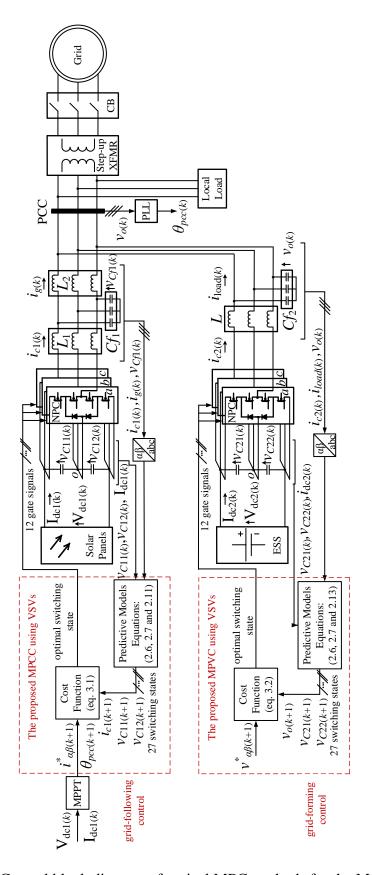

| Figure 3.3: Control block diagram of typical MPC methods for the MG systems                                                                                                                                                                    |

| Figure 3.4: Control block diagram of proposed MPC methods for different MG systems 61                                                                                                                                                          |

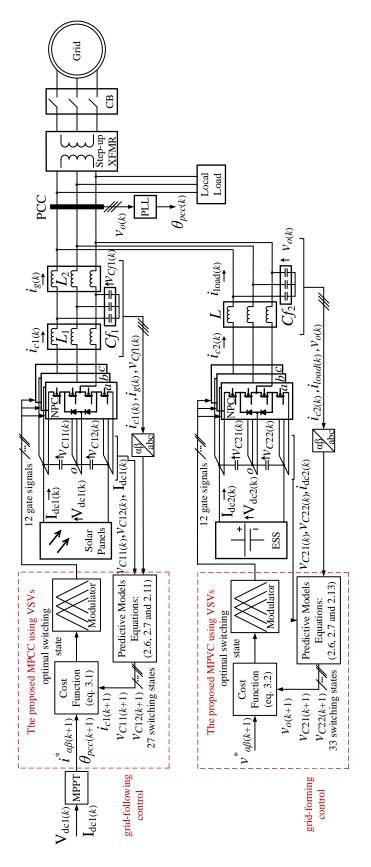

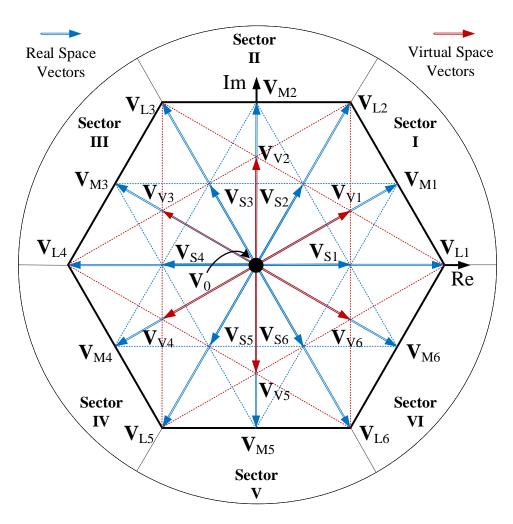

| Figure 3.5: SV diagram of a three-phase 3-L NPC VSC with the six VSVs                                                                                                                                                                          |

| Figure 3.6: Control algorithms of the proposed MPC methods (a) MPCC and (b) MPVC 63                                                                                                                                                            |

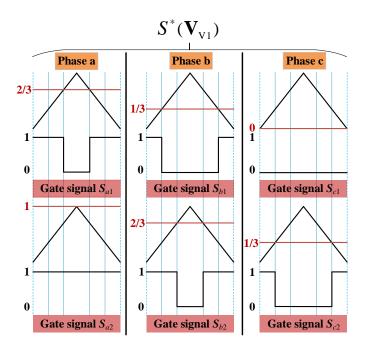

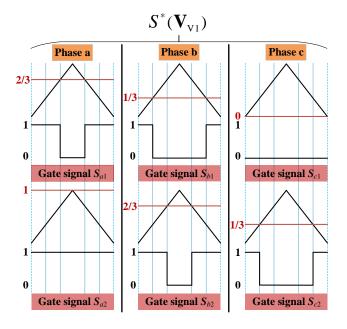

| Figure 3.7: An illustration of gate signal generation for $V_{V1}$                                                                                                                                                                             |

| Figure 3.8: An illustration of the impact of different voltage space vectors on the VSC NP-C 65                                                                                                                                                |

| Figure 3.9: Power loss model of a discrete power semiconductor device, $S_x$                                                                                                                                                                   |

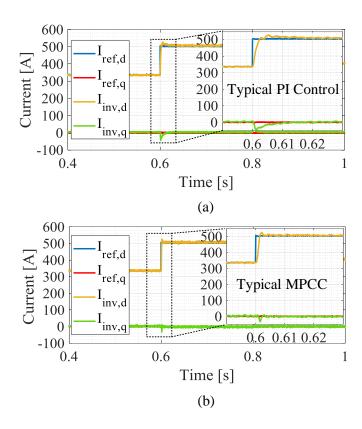

| Figure 3.10: Current dynamic response using the typical (a) PI controller and (b) MPCC 69                                                                                                                                                      |

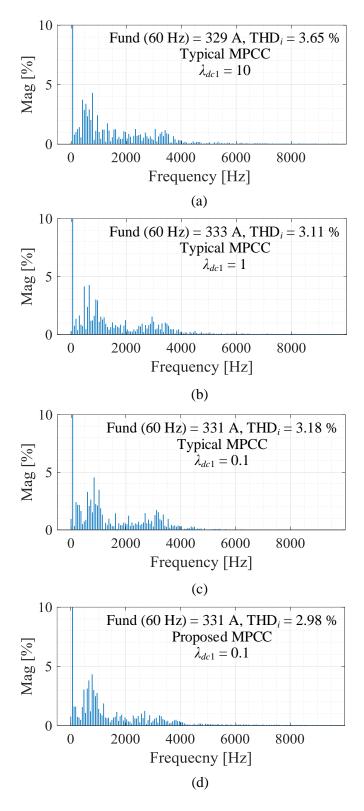

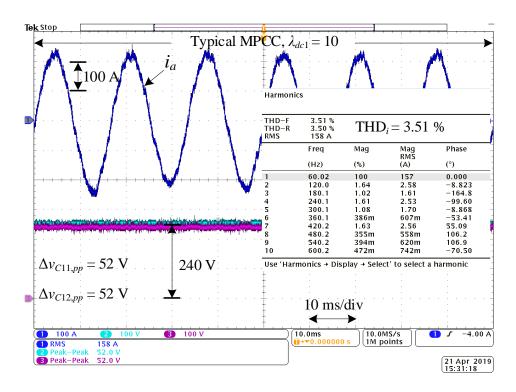

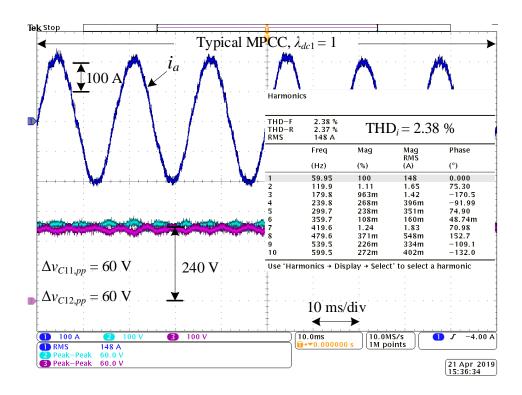

| Figure 3.11: PV inverter current spectra using (a) typical MPC with $\lambda_{dc1} = 10$ , (b) typical MPC with $\lambda_{dc1} = 1$ , (c) typical MPC with $\lambda_{dc1} = 0.1$ and (d) proposed MPC with $\lambda_{dc1} = 0.1$               |

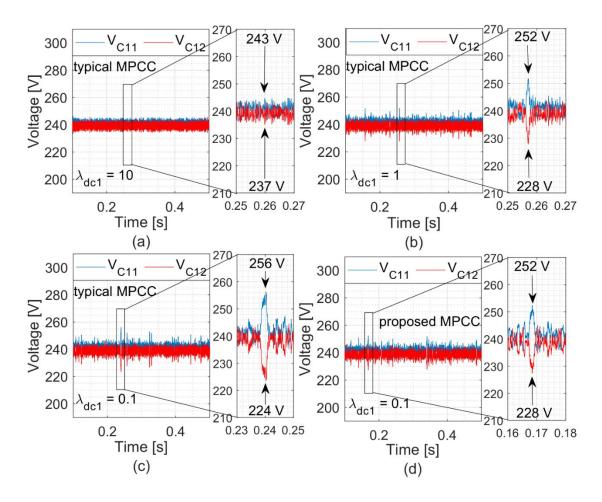

| Figure 3.12: PV inverter dc-link capacitor voltages using (a) typical MPC with $\lambda_{dc1} = 10$ , (b) typical MPC with $\lambda_{dc1} = 1$ , (c) typical MPC with $\lambda_{dc1} = 0.1$ and (d) proposed MPC with $\lambda_{dc1} = 0.1$ 72 |

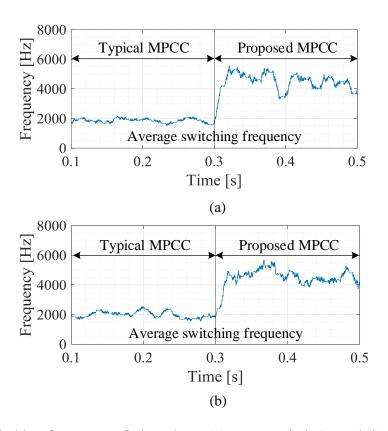

| Figure 3.13: Switching frequency of phase leg $a$ (a) upper switch $S_{a1}$ and (b) upper switch $S_{a2}$ . 73                                                                                                                                 |

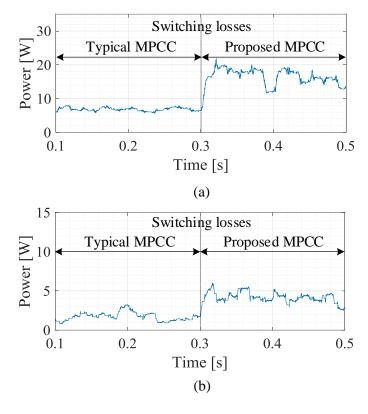

| Figure 3.14: Switching loss of phase leg $a$ (a) upper switch $S_{a1}$ and (b) upper switch $S_{a2}$                                                                                                                                           |

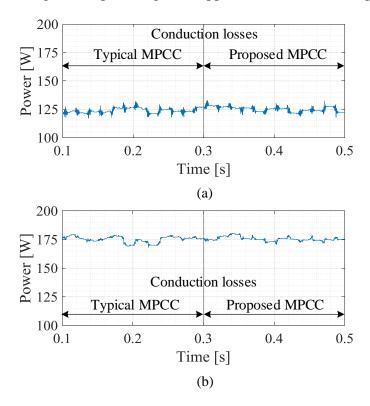

| Figure 3.15: Conduction loss of phase leg $a$ (a) upper switch $S_{a1}$ and (b) upper switch $S_{a2}$ 75                                                                                                                                       |

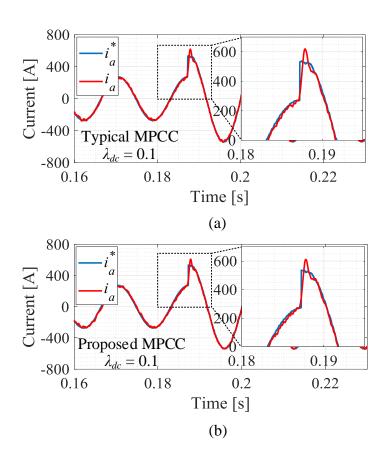

| Figure 3.16: Current reference-step change using (a) typical MPCC and (b) proposed MPCC 77                                                                                                                                                     |

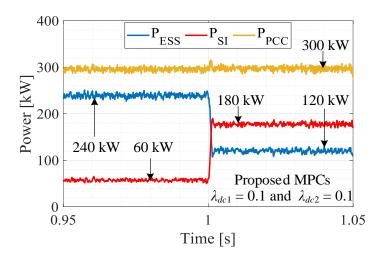

| Figure 3.17: Active power generated by the ESS inverter, the solar inverter and the total power consumed by the load at PCC                                                                                                                    |

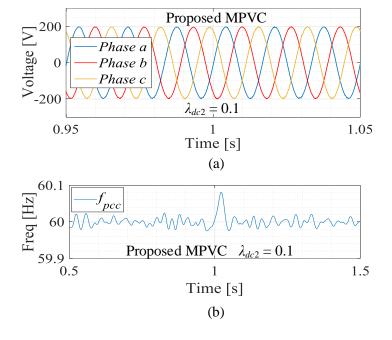

| Figure 3.18: Waveforms at the PCC (a) three-phase ouput voltage and (b) frequency                                                                                                                                                              |

| Figure 3.19: Controller hardware-in-the-loop test setup "photo by author"                                                                                                                                                                      |

| Figure 3.20: Solar inverter current and dc-link voltages using the typical MPCC with $\lambda_{dc1} = 10.83$                                                                                                                                   |

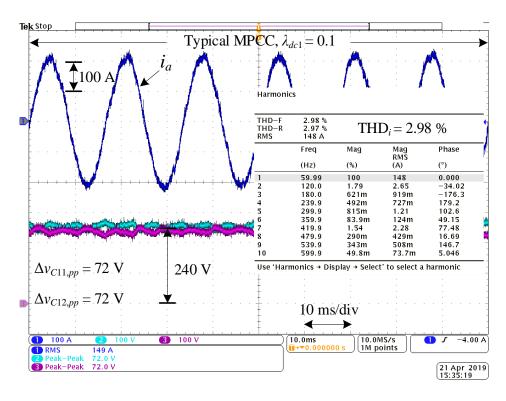

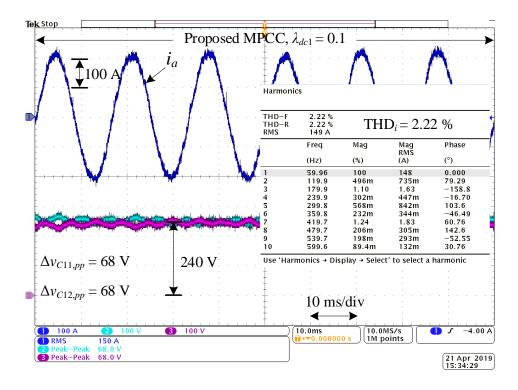

| Figure 3.21: Solar inverter current and dc-link voltages using the typical MPCC with $\lambda_{dc1} = 183$                                                                                                                                     |

| Figure 3.22: Solar inverter current and dc-link voltages using the typical MPCC with $\lambda_{dc1} = 0.1$ .                                                                                                                                   |

| Figure 3.23: Solar inverter current and dc-link voltages using the proposed MPCC with $\lambda_{dc1} = 0.1$                                                                                                                                    |

|                                                                                                                                                                                                                                                |

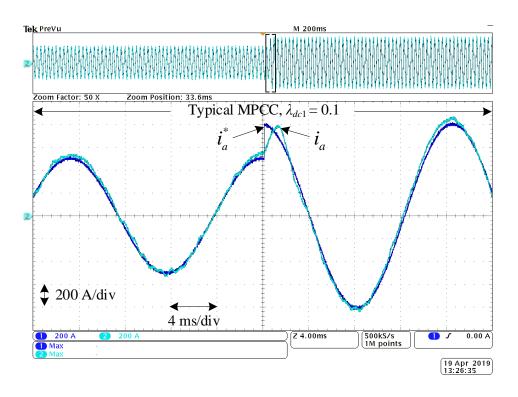

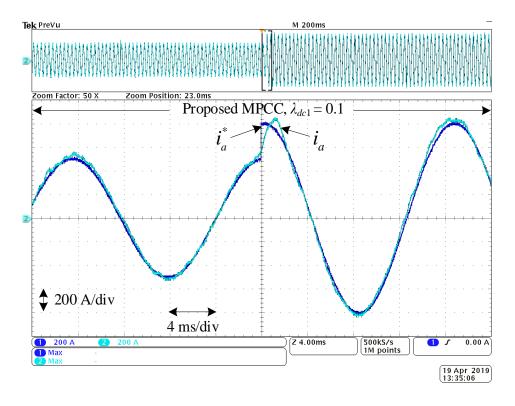

| Figure 3.24: Current reference-step change using the typical MPCC                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.25: Current reference-step change using the proposed MPCC                                                                             |

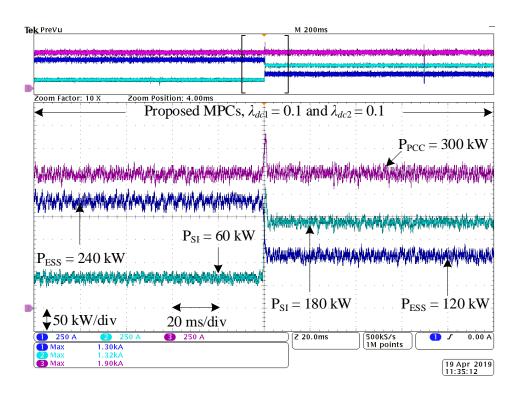

| Figure 3.26: Power generated by the ESS inverter, the solar inverter and the total power consumed by the load                                  |

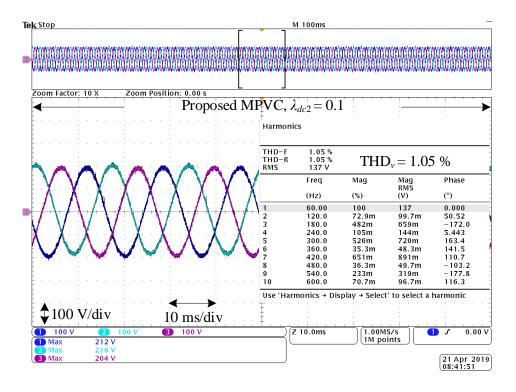

| Figure 3.27: Three-phase voltage and $THD_{\nu}$ analysis at the PCC                                                                           |

| CHAPTER 4                                                                                                                                      |

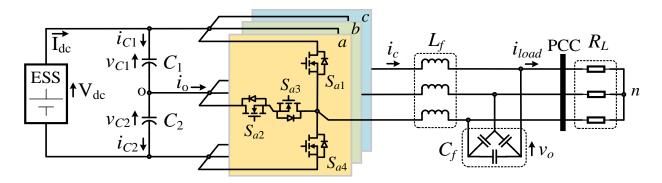

| Figure 4.1: Schematic diagram of the system to be studied                                                                                      |

| Figure 4.2: Control algorithm of the typical MPVC method.                                                                                      |

| Figure 4.3: Control block diagram of the typical MPVC method for the 3-L T-type VSC 94                                                         |

| Figure 4.4: SV diagram of a three-phase 3-L T-type VSC with the extended VSVs                                                                  |

| Figure 4.5: Control block diagram of the proposed MPVC method for the 3-L T-type VSC 99                                                        |

| Figure 4.6: An illustration of the gate signal generation for (a) small VSV, $\mathbf{V}_{S1}^{V}$ and (b) medium VSV, $\mathbf{V}_{M1}^{V}$ . |

| Figure 4.7: An illustration of the gate signal generation for the additional VSV, $\mathbf{V}_{V1}$                                            |

| Figure 4.8: Control algorithm of the proposed MPVC                                                                                             |

| Figure 4.9: An illustration of the impact of different voltage space vectors on the VSC NP-C. 104                                              |

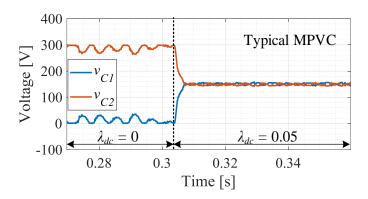

| Figure 4.10: Dc-link capacitor voltages during a weighting factor step change                                                                  |

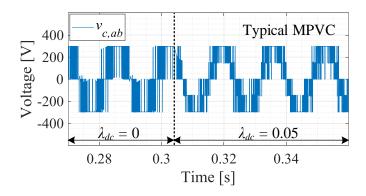

| Figure 4.11: VSC voltage during a weighting factor step change                                                                                 |

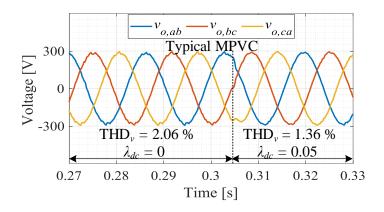

| Figure 4.12: Load voltage during a weighting factor step change                                                                                |

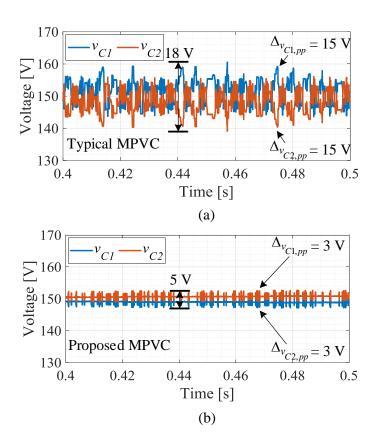

| Figure 4.13: Dc-link voltages during steady-state conditions using (a) typical MPVC (b) proposed MPVC.                                         |

| Figure 4.14: Converter voltage during steady-state conditions using (a) typical MPVC (b) proposed MPVC                                         |

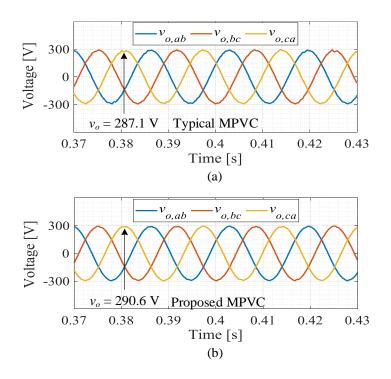

| Figure 4.15: Load voltage during steady-state conditions using (a) typical MPVC (b) proposed MPVC                                              |

| Figure 4.16: Load voltage spectra during-steady state conditions using (a) typical MPVC (b) proposed MPVC                                      |

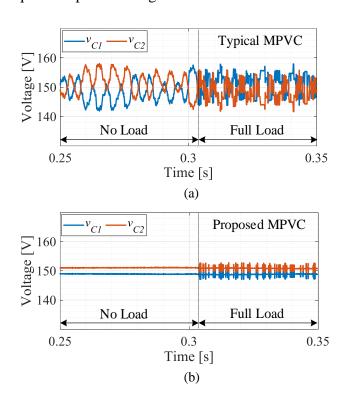

| Figure 4.17: Dc-link voltages during a load-step change using (a) typical MPVC (b) proposed MPVC               |

|----------------------------------------------------------------------------------------------------------------|

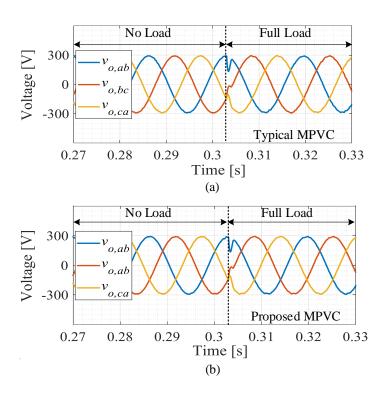

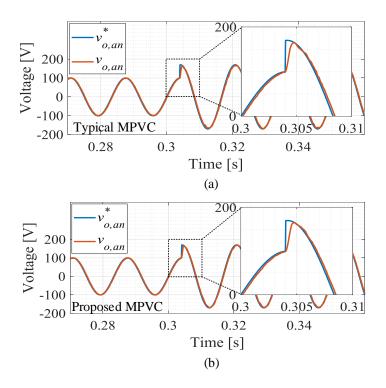

| Figure 4.18: Load voltage during a load-step change using (a) typical MPVC (b) proposed MPVC.                  |

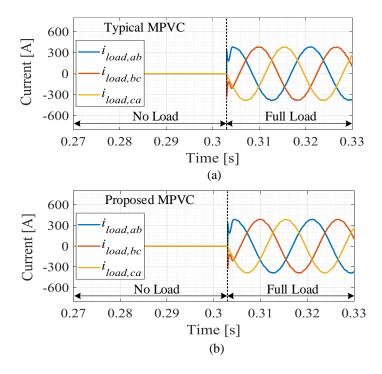

| Figure 4.19: Load currents during a load-step change using (a) typical MPVC (b) proposed MPVC.                 |

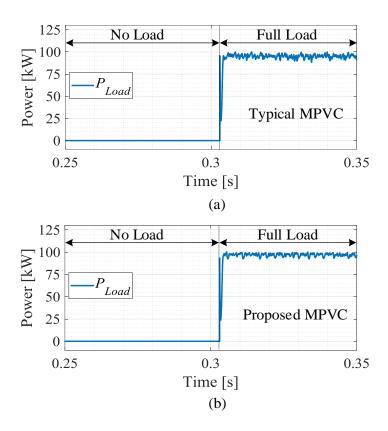

| Figure 4.20: Injected power during a load-step change using (a) typical MPVC (b) proposed MPVC                 |

| Figure 4.21: Voltage tracking during a reference-step change using (a) typical MPVC (b) proposed MPVC.         |

| Figure 4.22: Load voltage tracking considering $\Delta L = \pm 20$ % using (a) typical MPVC (b) proposed MPVC. |

| Figure 4.23: Load voltage tracking considering $\Delta L = \pm 40$ % using (a) typical MPVC (b) proposed MPVC. |

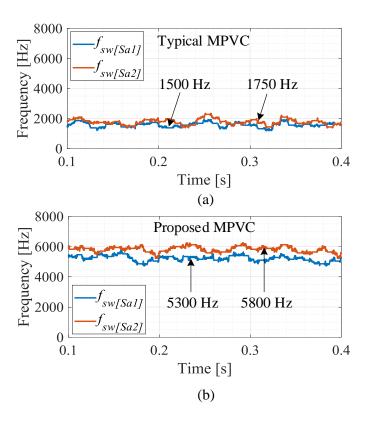

| Figure 4.24: Switching frequencies of $S_{a1}$ and $S_{a2}$ using (b) typical MPVC (b) proposed MPVC.          |

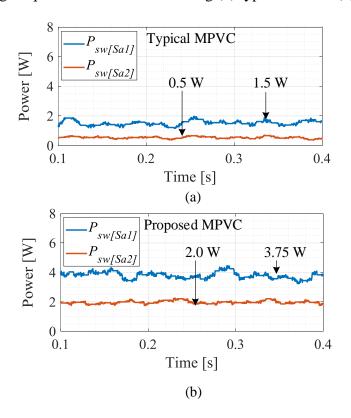

| Figure 4.25: Switching losses of $S_{a1}$ and $S_{a2}$ using (a) typical MPVC (b) proposed MPVC 120            |

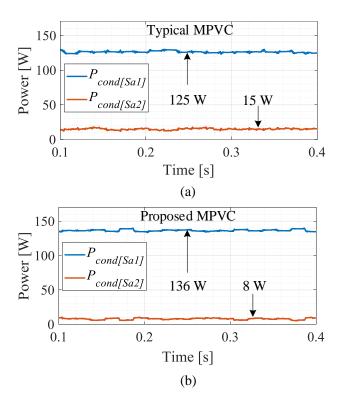

| Figure 4.26: Conduction losses of $S_{a1}$ and $S_{a2}$ using (a) typical MPVC (b) proposed MPVC 121           |

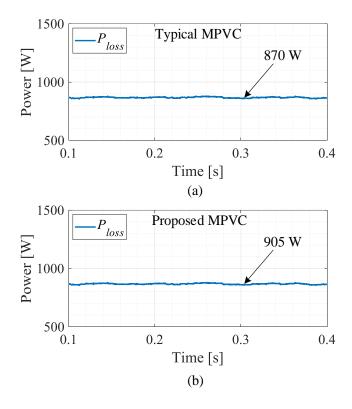

| Figure 4.27: Three-phase switching and conduction losses using (a) typical MPVC (b) proposed MPVC              |

| Figure 4.28: Experimental hardware test setup "photo by author"                                                |

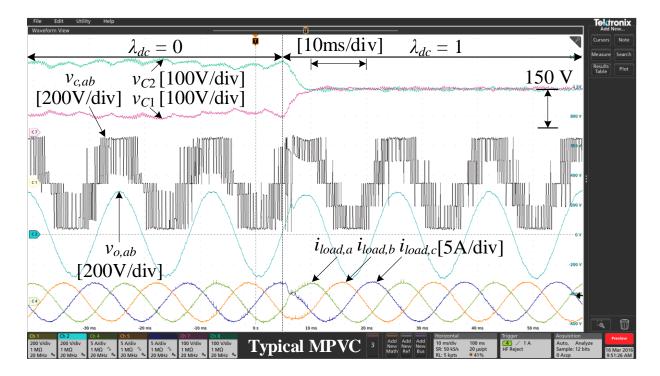

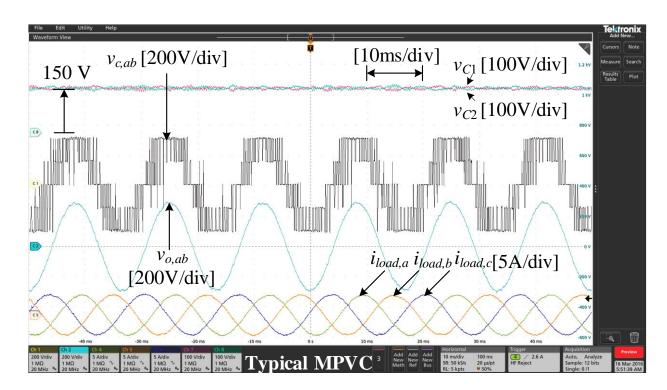

| Figure 4.29: Typical MPVC experimental results during a weighting factor step change 125                       |

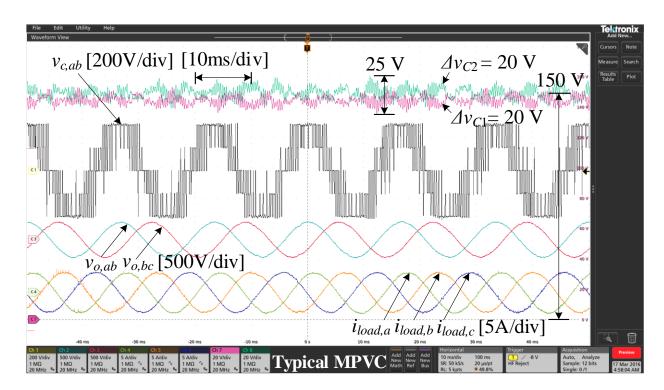

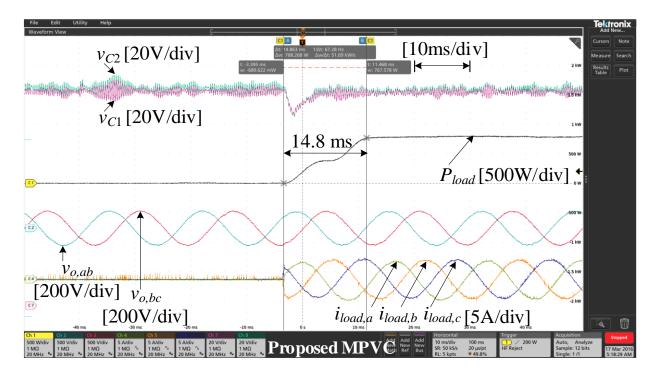

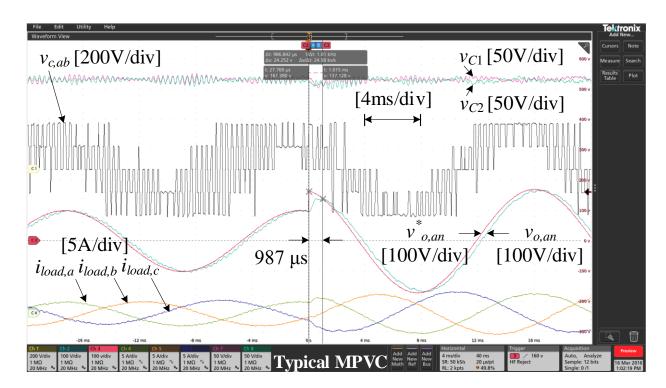

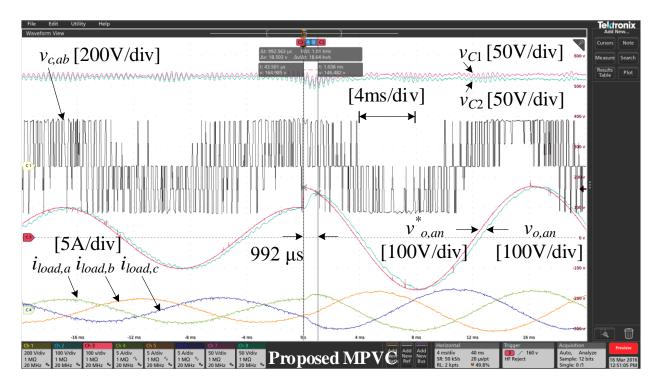

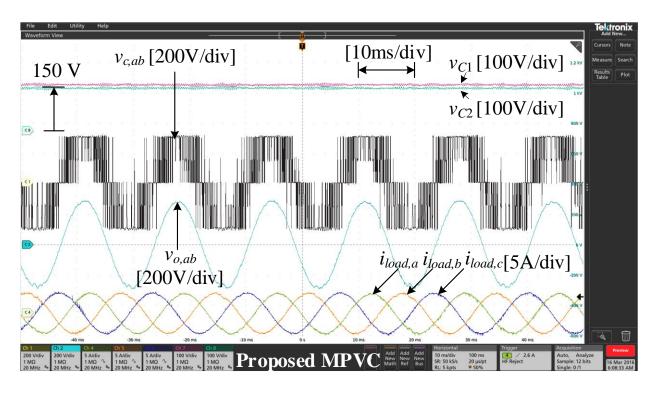

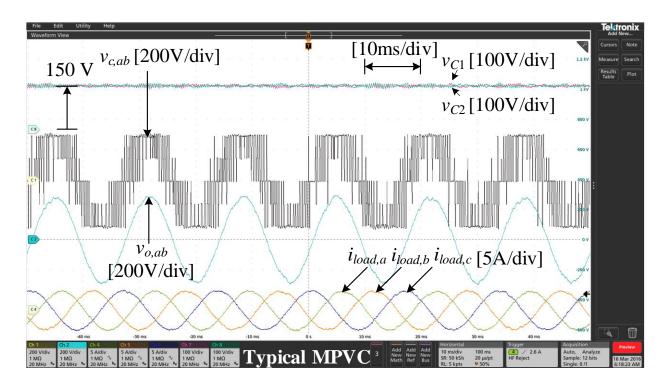

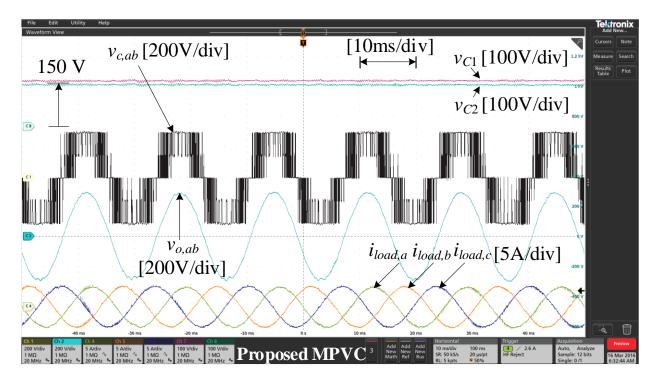

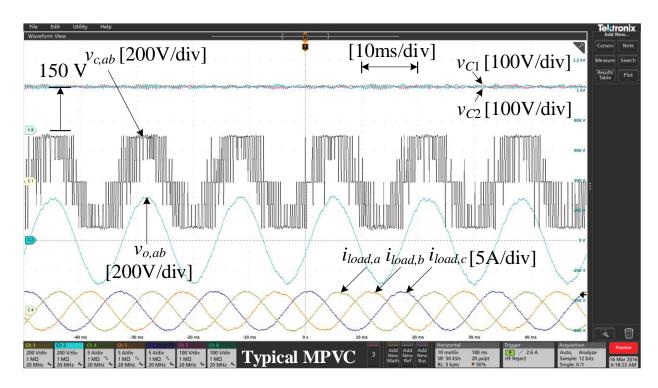

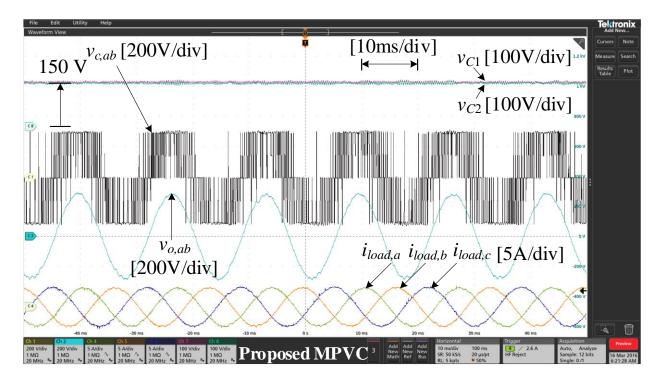

| Figure 4.30: Typical MPVC experimental results during steady-state conditions                                  |

| Figure 4.31: Proposed MPVC experimental results during steady-state conditions                                 |

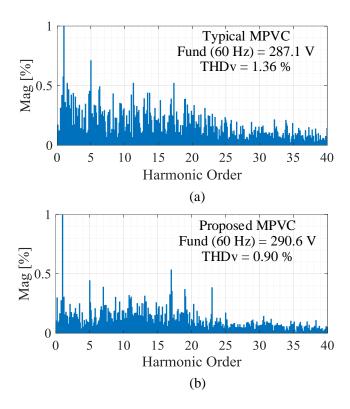

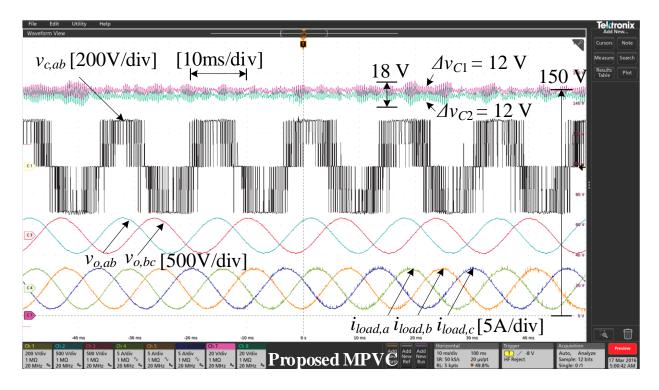

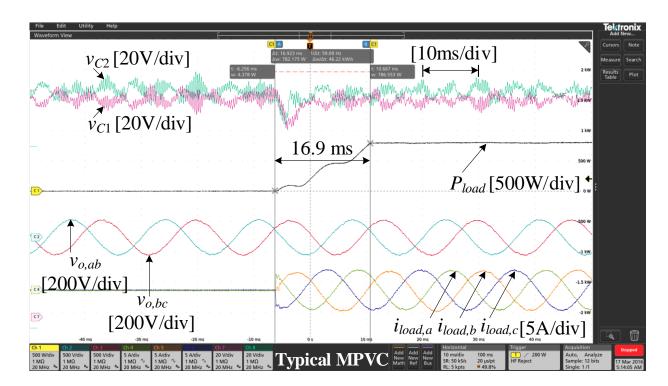

| Figure 4.32: Experimental results of load voltage spectra using (a) typical MPVC (b) proposed MPVC             |

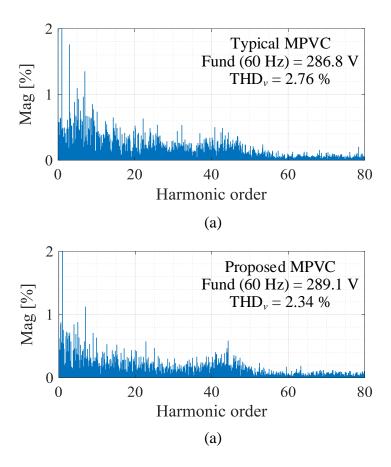

| Figure 4.33: Typical MPVC experimental results during a load-step change                                       |

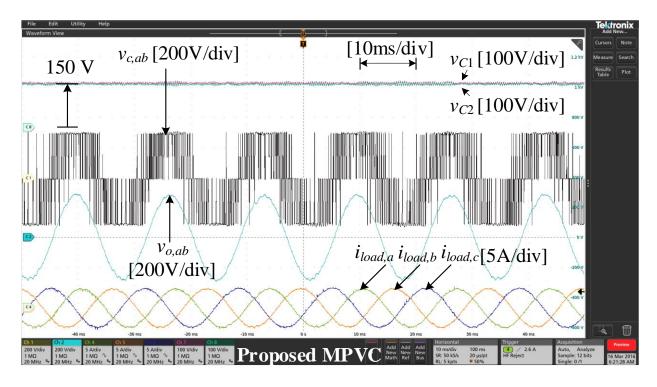

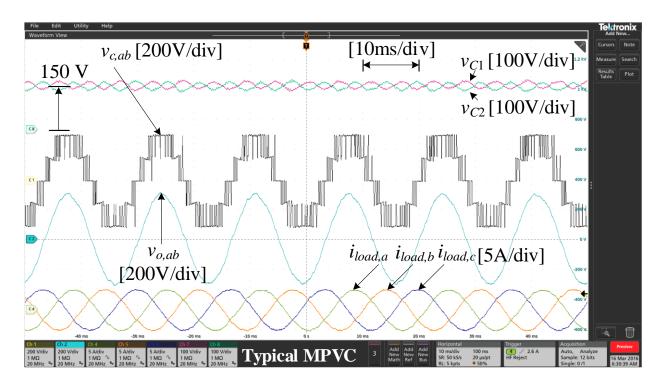

| Figure 4.34: Proposed MPVC experimental results during a-load step change                                      |

| Figure 4.35: Typical MPVC experimental results during a reference-step change                                  |

| Figure 4.36: Proposed MPVC experimental results during a reference-step change                                 |

| Figure 4.37: | Typical MPVC experimental results with $\Delta L = -20 \%$    | 134 |

|--------------|---------------------------------------------------------------|-----|

| Figure 4.38: | Proposed MPVC experimental results with $\Delta L = -20 \%$ . | 134 |

| Figure 4.39: | Typical MPVC experimental results with $\Delta L = +20 \%$    | 135 |

| Figure 4.40: | Proposed MPVC experimental results with $\Delta L = +20 \%$   | 135 |

| Figure 4.41: | Typical MPVC experimental results with $\Delta L = -60 \%$    | 136 |

| Figure 4.42: | Proposed MPVC experimental results with $\Delta L = -60 \%$ . | 136 |

| Figure 4.43: | Typical MPVC experimental results with $\Delta L = +60 \%$    | 137 |

| Figure 4.44: | Proposed MPVC experimental results with $\Delta L = +60 \%$   | 137 |

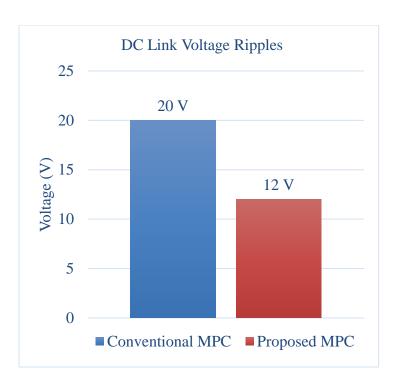

| Figure 4.45: | Comparison of the dc-link voltage ripples.                    | 141 |

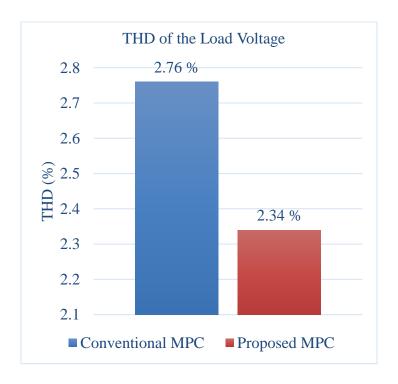

| Figure 4.46: | Comparison of the load voltage $THD_{\nu}$ .                  | 141 |

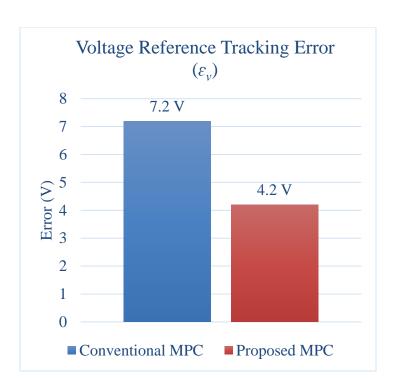

| Figure 4.47: | Comparison of the load voltage tracking accuracy.             | 142 |

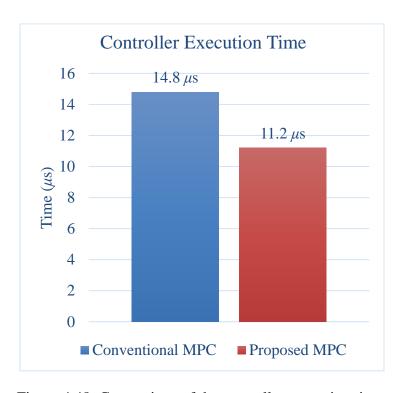

| Figure 4.48: | Comparison of the controller execution time.                  | 142 |

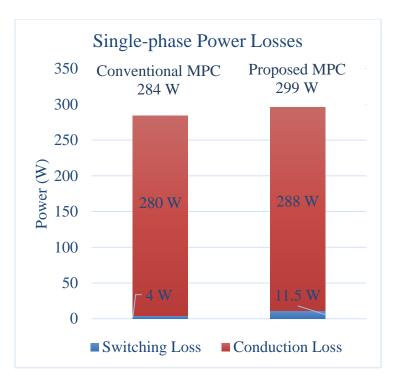

| Figure 4.49: | Comparison of the single-phase power losses                   | 143 |

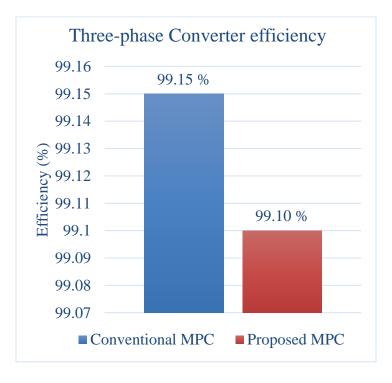

| Figure 4.50: | Comparison of the three-phase converter efficiency            | 143 |

# LIST OF TABLES

| CITA DET | 7D 1  |  |

|----------|-------|--|

| СНАРТІ   | 1.K I |  |

| Table 1.1 Characteristics of 2-L and M-L Power Converters                                                                  |

|----------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 2                                                                                                                  |

| Table 2.1 Relationship Between Switching State ( $S_x$ ) and Terminal Voltage ( $v_{xo}$ )                                 |

| Table 2.2 The Switching States ( $S_x$ ) and the Voltage Space Vectors ( $\mathbf{V}_i$ ) of the Three-Phase 3-L VSC       |

| CHAPTER 3                                                                                                                  |

| Table 3.1Summary for the Additional Six VSVs and Their Extended Switching States                                           |

| Table 3.2 Impact of Different Voltage Space Vectors on the VSC NP-C                                                        |

| Table 3.3 Investigated System Parameters                                                                                   |

| Table 3.4 3-L NPC VSC Power Loss and Efficiency Analysis                                                                   |

| CHAPTER 4                                                                                                                  |

| Table 4.1Summary for the New Small and Medium VSVs and Their Extended Switching States                                     |

| Table 4.2 Summary for the Additional Six VSVs and Their Extended Switching States 102                                      |

| Table 4.3 Impact of Different Voltage Space Vectors on the NP-C of the 3-L T-type VSC 104                                  |

| Table 4.4 Investigated System Simulation Parameters                                                                        |

| Table 4.5Load Voltage Reference Tracking Error Considering Different <i>LC</i> -Filter Inductor Values                     |

| Table 4.6 3-L T-type VSC Power Loss and Efficiency Analysis                                                                |

| Table 4.7 Investigated System Experimental Parameters                                                                      |

| Table 4.8 THD Analysis of Load Voltage Considering Different <i>LC</i> -Filter Inductor Values 133                         |

| Table 4.9 Comparision of Different Control Algorithms Implementation                                                       |

| Table 4.10 Load voltage, Number of Weighting Factors, Number of Voltage and Current Sensors, and Controller Execution Time |

#### CHAPTER 1

#### INTRODUCTION AND LITERATURE REVIEW

#### 1.1 Traditional AC Power Grid and AC Microgrids

The electric power grid has been experiencing tremendous development since the Pearl Street Electric Station was officially operated in early 1880s [1]-[3]. Ever since, a significant amount of money and effort have been invested to expand the electric grid from a small town to a nationwide network. As a result, the dramatic expansion of today's electric grid has allowed it to be seen as the largest system human beings have ever made [4]. This expansion could not have been achieved without the continuous advancements in power electronics technologies, protection systems, control theory and communication systems, to name a few [5].

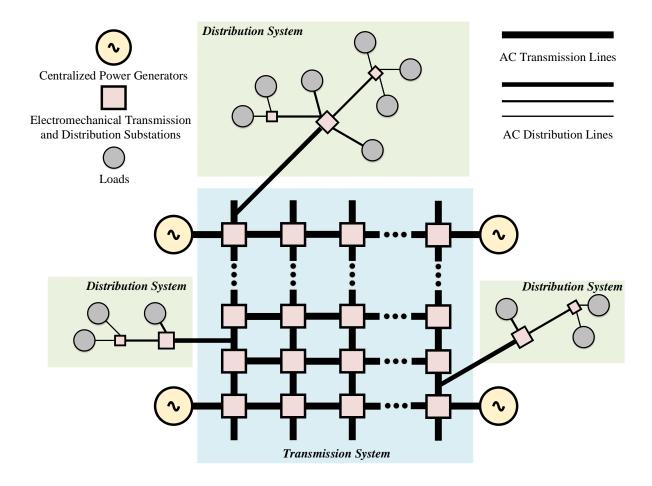

Traditionally, the legacy power system, presented in Figure 1.1, consists of power generation systems, power transmission systems and power distribution systems. The power generation is usually centralized. The produced electric power is normally transmitted through a transmission network to the distribution systems, which are usually featured as radial feeders, and reticulate the electric power to the end-users [6]. The power substations, which mainly have power transformers, are utilized to connect the three systems together forming the traditional electric power system [7]. While the step-up power transformers are used to achieve high-voltage level such that the power losses, especially the  $I^2R$ , at the transmission lines are significantly reduced, the step-down power transformers are mandatory to convert the high voltage at transmission level to the distribution voltage levels in order to allow various loads, which can be residential, commercial or industrial, to connect with the electric grid [8], [9].

Figure 1.1: An illustration of the traditional electric power system.

Centralized generations (CGs), as the ones demonstrated in Figure 1.1, are usually used to generate electric power, which is delivered to the end-users through massy passive transmission and distribution systems [10]. As such, the use of the CGs, transmission and distribution systems, results in unidirectional power flow. This hierarchical structure of the traditional electric power system is disadvantageous since large-scale power outages can result from extreme natural disasters such as hurricanes, severe thunderstorms, flooding, etc. [11]. Restoring the functionality of the electric power system from grave damage could last for weeks, which substantially reduces the reliability of the electric power system [12]. In addition, the passive transmission and distribution lines contribute in a significant reduction in the system overall efficiency due to the high power losses on the lines impedance, represented by  $I^2R$  [13]. The secure supply for the

rapidly and consistently growing power demand, which may lead to electric grid instability and/or electric power outages, is another challenging obstacle, which cannot always be addressed by increasing the capacity of the CGs due to the high cost of adding and operating enormous infrastructure of new power plants and transmission networks [14]. Furthermore, the major constituents of the conventional electric power system such as governors, automatic load tap changers, switched capacitor banks, etc. are electromechanical equipment, which decreases the operational life of these devices, and eventually leads to failure due to the excessive applied control actions [6]. The increased greenhouse gas emissions as well as the rapid depletion of fossil fuel reserves are also two primary challenges, attributed with the dependence on traditional fossil fuel based CGs [15], [16]. Consequently, the classical electric grid is facing many challenges to enhance the system reliability, resiliency, efficiency, sustainability, while reducing costs.

Therefore, in order to meet the considerably increasing challenges associated with the classical CGs and the massive transmission and distribution systems, distributed energy resources (DERs), which consist primarily of renewable energy sources (RESs) and energy storage systems (ESSs), have been recognized as a better alternative to the fossil fuels based CGs [17]. First, the development of the non-intermittent DERs technologies, e.g., ESSs, offers more advantages to the electric power system including electric system reliability improvement and electric power quality enhancement [18], [19]. Second, the DERs are usually installed at or near the end-use consumer [20], such that a significant improvement in the electric system efficiency can be achieved without routing the energy through the bulk transmission and distribution systems [21]. Additionally, compared to the conventional CGs, whose power capacity is costly and difficult to increase, the DERs, which are composed of technologies with accelerated price reduction [22], are easily installed next to the demand side to supply the rapidly growing loads [23]. Also, unlike the classical

CGs, which cause the rapid depletion of fossil fuel reserves and the increased harmful CO<sub>2</sub> emissions, the DERs are considered more sustainable solutions due to their capabilities to integrate the environmentally-friendly RESs such as photovoltaic (PV) systems, wind turbine (WT) technologies, etc. to the ac mains [24]-[26]. In addition, in contrast to the typical electric grid, which is equipped with the electromechanical devices, which has limited daily control actions [27], the reliable static power electronics technologies are the key components of the DERs [28]. Lastly, the strategic deployment of the DERs in the distribution system could also contribute in many advantages to today's electric power network such as enhanced electric grid voltage profile [29], improved power factor [30], fully-supplied peak load demand [31], etc.

However, despite the facts that 1) the cost of the various DERs technologies has recently seen drastic reduction [22]; 2) the high-power electronics technologies have undergone dramatic development due to the fast-switching and high-power semiconductor devices evolution and real-time digital controllers advancement [32]-[34]; and 3) governments have encouraged and supported the DERs installations by establishing new polices and providing incentives [35], the integration of the DERs with intermittent nature to the distribution system may result in multiple detrimental impacts on the low-voltage distribution system: among them 1) the reverse power flow, which impacts the protection equipment since they are not typically coordinated for a bidirectional power flow system; 2) the voltage rise and fluctuations, which change the feeder voltage profile and affect the connected loads; 3) the interference with the load-tap changers, voltage regulators and switched capacitor banks, which results in excessive use of these electromechanically devices [36], [37]; and 4) the increase of the harmonics contents, which may cause power quality issue and distribution lines overheat [22].

Therefore, since the integration of the various DERs into the electric grid has been experiencing drastic growth globally, and considering the uncontrollability of the DERs due to the intermittent nature of the RESs is a dilemma, numerous studies have recently focused on developing new and advanced control schemes to manage and operate the electric grid with high penetration of DERs [38], [39].

Hence, the concept of microgrids (MGs) was firstly proposed in [40] to exploit the advantages of the DERs. An MG is a small-scale electric grid, which consists mainly of one or more DER(s) managed and operated together to supply power to the load(s) with and/or without the main electric grid being connected [41]-[44]. This cluster of DERs leverages the advancement in power electronics technologies and their control strategies to ensure the efficient, reliable and safe operation for such DERs with the legacy electric grid, and also to secure the power supply for the critical loads during fault events [45], [46]. To explicate, an MG can be operated to regulate the line voltage by controlling the reactive power flow of the DERs along the distribution feeder [23]. In addition, the power drawn from the power substation can be minimized by means of MGs resulting a more efficient electric power distribution system [47]. The electric grid frequency regulation is another target, which can be accomplished using an islanded MG [48], [49], [50]. Resiliency, which is defined as the capability of the electric power system to adjust to unusual incidental situations and rapidly restore the electric distribution system from the disruptive events, is also achievable using the MG concept [51]-[54]. Generally, depending on how voltage source converters (VSCs) of an MG interact with the main grid, three different operating modes of power converters can be specified. These VSC operating modes are grid-following, grid-forming and grid-supporting [55]-[57].

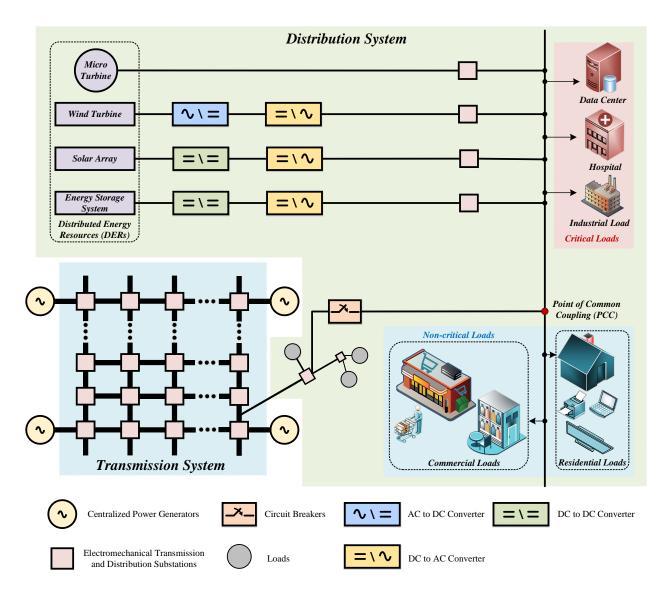

Figure 1.2: An illustration of an ac MG connected to the electric power system.

Figure 1.2 presents an illustration of a notional ac MG connected to the legacy electric grid through a circuit breaker. Both critical and non-critical loads are assumed to be connected to the point of common coupling (PCC), which is the point of interference of the DERs with ac mains. As demonstrated in Figure 1.2, different types of the DERs, i.e., intermittent and non-intermittent, can be used to supply power to the distinct loads. The non-intermittent power sources, i.e., the micro-turbine generator and the ESS, are critical in the MG design to secure the operation of the MG when the main electric grid is unavailable, and to smooth out the intermittent generated power

by the RESs. As displayed in Figure 1.2, various types of power electronics converters, i.e., dc-ac, ac-dc and dc-dc converters, can be utilized in the MG to perform the energy conversion.

### 1.1.1 Classification of Control Schemes of VSCs in AC MGs

An ac MG is capable of integrating and operating multiple VSCs, which are controlled to have different operating modes, i.e., the grid-following mode, the grid-forming mode, and the grid-supporting mode [58]. The vast majority of the VSCs in an MG are classified as the grid-following VSCs. The grid-forming VSCs are also essential in an MG to ensure secure and continuous power supply for critical loads during the main grid faulty events [59]. The grid-supporting VSCs also play also an important and decisive role in an MG as they can be controlled to maintain the variations of the MG voltage magnitude and frequency to be within the allowed levels [60]. In the work proposed in this dissertation, both the grid-following and grid-forming VSCs are considered to verify the proposed control algorithms. In this section, unlike the grid-supporting VSCs, which are briefly described, the grid-following and the grid-forming VSCs are explained in detail.

### 1.1.1.1 Control of Grid-Following VSCs

In MG applications, the grid-following, also referred to as grid-connected, grid-tied, grid-feeding or grid-interfaced, VSCs have been widely accepted and applied in various power electronics applications such as grid-connected PV [61], WT [62] technologies, etc. Having the VSCs to operate in the grid-connected mode, similar to the one presented in Figure 1.3, simply means the operation of these VSCs is strictly synchronized to the stiff electric grid, and the VSCs are controlled in current-control mode to inject specified power to the PCC, where the power converters are tied to the electric grid [63]. The generic model of a grid-following VSC is a current source in parallel with a high-output impedance. The operation of this kind of VSCs cannot be

accomplished without having these VSCs connected to a voltage source, which provides the voltage amplitude and frequency of the MG [64].

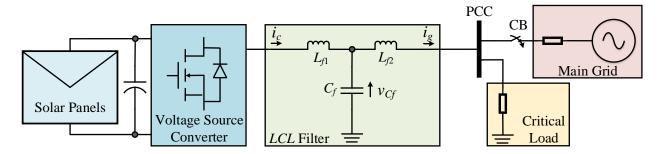

Figure 1.3: One-line diagram of a grid-following PV inverter connected to the main grid.

The grid-following VSCs are usually integrated with the electric grid through either an L or an LCL filter to suppress the harmonic contents resulting from the fast-switching power semiconductor devices. The first-order L filter is known for its easy design and control. Since the electric grid has an inductive impedance, resonances do not exist in such inductive systems. However, to suppress the high-frequency switching ripples, a bulky L filter, which increases the volume and the cost of the passive filter, is inevitable. Additionally, using the large L filters to connect the VSCs to the electric grid leads to high-voltage drop across the passive filter, which reduces the system efficiency and dynamic response [65]. On the contrary to the first-order L filter, the high-order low-pass LCL filter, which was firstly proposed in [66], has been determined to be more cost-effective and efficient to meet the electric grid interference standards, specified by IEEE Std. 519 and IEEE Std. 1547 [67]. This significant reduction in the *LCL*-filter inductors' size is the result of the high-harmonic contents attenuation of such filters. Nonetheless, the third-order LCL filters express more complexity in the closed-loop controller design due to the existence of the LCL-filter resonances. Thus, to limit the resonance effect on the closed-loop controller performance, two damping techniques, categorized as passive [68] and active [69], are established.

Demonstrated in Figure 1.4 is a generic control block diagram of the grid-interfaced solar inverter with the passive damping resistor,  $R_d$ , included in the system design. Though several configurations have been proposed to add the passive  $R_d$  to the circuit design, a common practice is to include the  $R_d$  in series with LCL-filter capacitor as depicted in Figure 1.4 [70]. Although the passive damping technique enhances the stability of the closed-loop controller by attenuating the peak resonances of the LCL filter [71], the  $R_d$  value should be selected carefully to minimize the power losses [72]. Another drawback of passively damping the LCL-filter resonances is that at high frequencies, the LCL filter behaves as a second-order system, and this deteriorates the ability of the filter to attenuate resonances [70].

Figure 1.4: Passive-damping based control block diagram of a grid-following PV inverter.

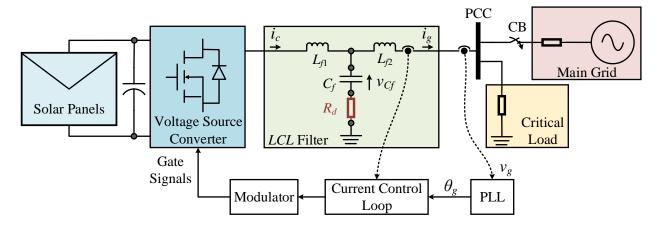

Figure 1.5: Active-damping based control block diagram of a grid-following PV inverter.

In contrast to the passive damping strategy, active damping algorithms have been proposed to avoid the cost and power losses associated with using an actual damping resistor [73]. A simple and straightforward design for the active damping scheme is to feed the output of the current-control loop to a damping filter, which can be a low-pass filter or a notch filter. The drawback of this kind of active damping techniques is that the controller performance is substantially sensitive to the parameter uncertainties [74]. Another active damping strategy, which has been commonly implemented due to its high robustness, is the capacitor-current feedback active damping. Using this control method, a virtual resistor is emulated by the proportional feedback of the *LCL*-filter capacitor current [75]. A generic control block diagram of this control technique is displayed in Figure 1.5.

### 1.1.1.2 Control of Grid-Forming VSCs

Recently, with the advancement of the ESSs technologies, grid-forming VSCs, presented in Figure 1.6, have become essential for any MG design since they ensure that critical loads are not affected by power outages [76]. Typically, when the MG is operated in the islanded operating mode, the grid-forming VSCs are responsible for establishing the voltage amplitude and frequency of the disconnected electric grid. The generic model of a grid-forming VSC is an ac voltage source, which has a low-output impedance. A common application for grid-forming VSCs is uninterruptible power supplies (UPSs) [58], which is normally included in applications like hospitals, data centers, etc. Since the applications, which have the VSCs operated in a grid-forming mode, require stable and high-quality sinusoidal ac voltage, numerous control schemes, which use *LC* filters to suppress switching ripples generated by the power switches, have been proposed. Typically, the control of the grid-forming VSCs concentrates only on rejecting the disturbance,

which is caused by the load variations [58]. Generally, the control strategies of grid-forming VSCs are classified as either dual-loop [77]-[82], or single-loop [83]-[88] controllers.

Figure 1.6: One-line diagram of a grid-forming inverter connected to a critical load.

On the one hand, dual-loop, referred to as double-loop, control strategies consist of an inner-current feedback loop and an outer-voltage feedback loop as shown in Figure 1.7. The *LC*-filter inductor current is mostly used as a controlled variable with the inner-current control loop; the *LC*-filter capacitor voltage is the controlled variable used in the outer-voltage control loop. In specific controller designs, the *LC*-filter capacitor current is selected as an inner-loop controlled variable so that disturbance rejection properties are improved. In order to achieve an accurate dual-loop controller design, the outer-voltage control loop should be characterized to have slower dynamics than the inner-current control loop so there is no potential interference between the two control loops. The drawbacks of these control strategies are the design complexity, which relies on the serial tuning for the current and voltage controllers and the slow dynamic response, which is caused by the different [80], [81]. However, the inherent damping effect, which attenuates the resonance occurs due to the *LC* resonant frequency variations, is achieved by the inner-current loop, which enhances the stability of the closed-loop controller against the load variations as it provides active damping [82].

Figure 1.7: Dual-loop control block diagram of a grid-forming inverter.

Figure 1.8: Single-loop control block diagram of a grid-forming inverter.

On the other hand, single-loop control techniques, demonstrated in Figure 1.8, have also been considered in the literature to provide alternative solutions to the classical dual-loop control methods. In this control strategy, the capacitor voltage is the only feedback signal to be used within the controller design. As a result, significant reduction in the controller design complexity is achieved. Because current sensors are not needed, a reduction in the system cost is also achieved. In addition, single-loop control methods present fast-dynamic response due to the fact that cascaded current-voltage control loops, which have different dynamics, are not part of the controller design. However, the hindrance of these control approaches is the high parameter

sensitivity; thus, a large *LC*-filter capacitor has to be considered in the passive filter design to guarantee high-quality output voltage [86], [88].

#### 1.1.1.3 Control of Grid-Supporting VSCs

Two different representations are usually used to describe grid-supporting VSCs. The distinct representations aim to regulate the voltage and frequency of the ac MG. Firstly, a grid-supporting VSC can work as a current source such that not only supplies power to loads, but also provides support for the MG voltage and frequency [60]. Secondly, operating the parallel grid-supporting VSCs as ac voltage sources allows sharing loads among the parallel converters according to the converters power ratings [89].

### 1.1.2 Synchronization of VSCs in AC MGs

Typically, for grid-feeding VSC control, properly synchronizing the grid-following VSCs with the voltage of the electric utility is an essential task to accomplish accurate grid integration and efficient operation of the DERs with the ac mains. To illustrate, in a three-phase electric system, the positive-sequence component of the electric utility voltage must be detected and used to ensure the energy transfer between the grid-tied VSC and the electric utility is well-synchronized. A synchronization method, hence, is mandatory to be included in the grid-tied VSC controller design to extract the electric utility positive-sequence voltage amplitude and phase angle so that the distinct DERs, which form the grid-interfaced MG, are carefully synchronized with the ac mains [90], [91]. A common synchronization strategy, which has been used in many electrical applications including the grid-connected VSCs, is the phase-locked loop (PLL). The PLL can be simply realized as a closed-loop system, whose output signal follows its input reference signal's phase and frequency. The three primary components of a generic three-phase PLL, which is

displayed in Figure 1.9 are a phase detector (PD), a filter loop (FL) and a voltage-controlled oscillator (VCO) [92], [93]. Chapter 2 of this dissertation will provide a detailed explanation for each part of the PLL. It is worth noting that the performance of the grid-interfaced MG is highly affected by the accuracy of the selected synchronization technique, a precise synchronization method should result in a more reliable MG operation and vice versa [60].

Figure 1.9: Block diagram of a generic three-phase PLL system.

When a fault occurs at the main electric grid, the MG is usually expected to operate independently in the islanded operating mode. Thus, for grid-forming VSCs, the synchronization method should have the capability to ensure precise signals during the islanding transition such that the electric grid voltage amplitude and frequency can be initiated by the grid-forming VSC [94]. When a complete stand-alone operating mode is accomplished, the synchronization method operates as an oscillator, which provides a reference voltage with a determined voltage amplitude and frequency. As soon as the fault is cleared out, and main electric grid is back in operation, the voltage of the grid-forming VSC has to be resynchronized with that of the mains [95].

Due to its simple design and high performance during ideal electric grid conditions [96], the conventional synchronous-reference-frame phase locked loop (SRF-PLL) is selected to synchronize different VSCs in the work demonstrated in this dissertation. A more comprehensive description for the SRF-PLL approach will be presented in Chapter 2.

Figure 1.10: Flow chart of the commonly used VSCs in MG applications.

### 1.2 Classification of VSC Topologies for AC MGs

The integration of the various DERs with the electric utility cannot become reality without the critical role, which is played by the power electronics converters. In MG applications, the most commonly adopted VSC topologies, which work as an interface for the DERs and the ac mains, can be classified into two major categories; two-level (2-L) and multi-level (M-L) VSCs. While the 2-L VSCs are mostly used in low- to medium-voltage applications, the M-L VSCs are usually preferred for medium- to high-voltage power electronics applications. As shown in Figure 1.10, unlike the single 2-L VSC topology, the M-L VSC topologies are further classified into three categories. The commonly adopted M-L VSC topologies include flying capacitor, cascaded H-bridge and 3-L VSCs. In the work presented later in this dissertation, the latter are selected due to their various advantages, which distinguish the 3-L VSCs from their 2-L counterparts. This section provides some backgrounds regarding the 2-L and 3-L VSC topologies.

### 1.2.1 Three-Phase 2-L VSCs

The classical 2-L VSCs dominate the market of low-voltage industrial applications since these VSCs present substantially simpler circuit design and significantly reduced cost [97]. Compared

to the conduction losses of a 3-L VSCs, the considerably reduced conduction losses of the power semiconductor devices in a 2-L VSC is another advantage, which contributed in making the 2-L VSCs become a standard industry choice to achieve the standard of grid-interfaced DERs. In addition, unlike the M-L VSCs, the control design for the 2-L VSCs is relatively simple since these power converters do not have a neutral point in the dc-link capacitor, which needs special attention and control. However, several limitations are hindering the adoption of this topology for the medium- and high-voltage applications. First, the power semiconductor devices in the 2-L topology have to be rated to block the full dc-bus voltage, which results in high dv/dt. This high dv/dt not only contributes in significant current ripples, but may also result in damaging the expensive power switches. Additionally, in applications, which require high-switching frequency, excessive switching losses across the power semiconductor devices are experienced. Moreover, bulky ac output passive filters have to be used to interface these VSCs with the electric grid, since the 2-L VSC output waveforms have higher total harmonic distortion (THD) [98].

### 1.2.2 Three-Phase 3-L VSCs

Two-level (2-L) voltage source converters (VSC) are widely adopted as an interface to connect DERs to MGs. However, for medium- and high-power applications, multilevel (M-L) VSCs are alternatives to typical 2-L converters due to their improved output waveform quality and reduced voltage stress across power semiconductor devices. Also, compared to 2-L VSCs, adopting M-L converters results in using smaller ac filters [99], [100]. Commonly used M-L converter topologies include flying capacitor converters, cascade H-bridge and three-level (3-L) neutral-point clamped (NPC) converters; the latter has been extensively used in a wide range of industrial applications [98], [101]. Nevertheless, as a result of the increase number of power semiconductor devices, 3-L NPC converters suffer from higher conduction losses relative to the

2-L converters. Thus, the 3-L T-type VSCs, which combine advantages of the 3-L NPC converters and the 2-L converters, have been used lately in high-power low-voltage applications [102], [103]. In the work presented throughout this dissertation, the most commonly used 3-L converter topologies, i.e., NPC VSCs and T-type VSCs, are utilized later to verify different control algorithms.

#### 1.2.2.1 Three-Phase 3-L NPC VSCs

In the early 1980s, 3-L NPC converter was first introduced by Nabae [104]. Ever since, this topology has shown its superiority over the conventional 2-L VSCs [105]. To explain, unlike the 2-L converters, this converter has been determined to be suitable for wide range of medium-voltage high-power applications. To start with, the power semiconductor devices, which compose the 3-L NPC, are exposed to low voltage stress, i.e., only half of the dc-bus voltage. Compared to 2-L converters, the same power semiconductor device in a 3-L NPC VSC can handle twice the power as if it is used in a 2-L topology [105]. This feature allows the converter to be connected to a higher voltage dc-bus resulting in achieving higher power. The 3-L converters output waveform quality is also significantly improved relative to that of the 2-L converters. Therefore, a substantially smaller ac output filter can be utilized. In addition, using 3-L NPC converter leads to reduced switching losses compared to switching losses generated by a traditional 2-L converter.

However, as a result of utilizing more power semiconductor devices in the 3-L NPC VSC, the cost will be increased. In addition, having high number of these power switches reduces the converter overall reliability and efficiency since the switching device conduction losses are significantly increased [106]. The power circuit of this topology with a comprehensive description of this topology will be provided in Chapter 2.

Table 1.1

Characteristics of 2-L and M-L Power Converters

| Topology                    | Switching<br>Losses | Conduction<br>Losses | Waveform<br>Quality | Output<br>Filter | Control<br>Complexity | Extra<br>Hardware      |

|-----------------------------|---------------------|----------------------|---------------------|------------------|-----------------------|------------------------|

| 2-L<br>Converters           | High                | Low                  | Low                 | Bulky            | Simple                | None                   |

| Fly Capacitor<br>Converters | Low                 | High                 | High                | Small            | Complex               | Flying<br>Capacitors   |

| CHB<br>Converters           | Low                 | High                 | High                | Small            | Complex               | Separate DC<br>Sources |

| 3-L NPC<br>Converters       | Low                 | High                 | High                | Small            | Complex               | Clamping<br>Diodes     |

| 3-L T-Type<br>Converters    | Medium              | Medium               | High                | Small            | Complex               | None                   |

#### 1.2.2.2 Three-Phase 3-L T-Type VSCs

As a result of the increased number of power semiconductor devices in the 3-L NPC VSCs, these converters suffer from higher conduction losses relative to the 2-L converters, which sacrifice the converter efficiency. As thus, the 3-L T-type converter, which combines advantages of the 3-L NPC converters and the 2-L converters, has been used lately in low- and medium-voltage high-power applications [103]. To clarify, the 3-L T-type converter has the major advantages of the 3-L NPC converter, which are reduced switching losses, improved VSC output waveform quality and reduced output ac filter. At the same time, the 3-L T-type converter shares the low conduction loss feature with the conventional 2-L converter [102]. This makes 3-L T-type converters a solution, between 2-L and 3-L NPC converters, for low-medium voltage medium-high power applications. The schematic and the detailed model of a typical T-type converter are presented in Chapter 2. Finally, Table 1.1 summarizes the main advantages and drawbacks of each

topology. The comparison is performed based on switching losses, conduction losses, output waveform quality, ac filter size, control complexity, and required extra hardware.

Figure 1.11: Flow chart of common control methods for VSCs.

#### 1.3 Classification of Three-Phase 3-L VSC Control Methods

Various control techniques have been proposed for 3-L converters since the NPC converter was introduced. Usually, the same control strategies, which are used for the 2-L VSCs can be extended and implemented for the 3-L VSCs [107]. Generally, the control strategies which are applied on the 3-L VSCs can be either linear on nonlinear [108]. Shown in Figure 1.11 is a chart which categorizes and demonstrates the different types of control methods used for grid-following and grid-forming 3-L power converters.

#### 1.3.1 Conventional Linear and Nonlinear Control Methods

As depicted in Figure 1.11, control schemes for 3-L VSCs can be in general classified as linear and nonlinear control strategies. Most of these control strategies are well developed, and they have been in use with different power electronic applications for decades [109].

Typically, to implement linear control strategies, a PWM modulator has to be cascaded with the current regulator. Following this design structure, the controller can exploit the merits of an open-loop modulator. These advantages mainly include a constant switching frequency and fixed harmonic spectrum [110]. The commonly deployed linear control schemes are the rotatingreference frame (RRF) and stationary-reference frame (SRF) proportional-integral (PI) control. The former is known for zero steady-state error since it forces the error, between the measured and reference signals, to be zero and ultimately achieves a good steady-state performance. Nevertheless, (RRF) transformation has to be applied such that the sinusoidal signals are converted to dc signals to be used in the control [111]. Since the dc signals, which are the direct and quadratic (d and q) axes, are time-invariant and dependent on each other, they disturb each other during the transient events, which deteriorates the controller overall performance [112]. The latter, i.e., SRF PR control, on the other hand, eliminates the steady-state error of a sinusoidal signal at a particular frequency by using infinite gains at the targeted frequency [113]. This simple control approach is sensitive to the fluctuations in the electric grid frequency, which may lead to instability during transients [112].

However, the main idea of linear control is to assume that the linearized system model is valid at a small range of operation. This limitation is exposed once a large operation range is the case. Operating a linear controller at a wider range could lead to instability or at most, poor performance. Assuming the model is fully linearizable is another problem associated with linear controllers. This is due to the fact that there are hard nonlinearities, which cannot be linearized due to their discontinuous nature. Model uncertainties contribute significantly to the deterioration of the linear controller's performance. Finally, linear control typically exhibits a complex control design due to the need for a modulation stage and signal transformations.

Therefore, for applications related to 3-L converters, where the fast-dynamic response and the certainty against parameter changes are desirable, nonlinear control strategies have shown considerable improvement in the system operation [108]. Some of the well-known nonlinear control methods are sliding mode control (SMC) and hysteresis control. Similar to the linear control methods, some of these nonlinear control strategies are known for being mature and well-established. For instance, hysteresis control, which includes direct power control (DPC), has been deployed on multiple power electronic applications. This control approach is known for being simple and effective in some applications. However, it suffers from the variable switching frequency, which may lead to resonance problems. Also, in order to improve the output waveform quality, hysteresis control has to be operated using high sampling time such that the controlled signal can always be within the defined hysteresis bands. Another powerful nonlinear control technique, which has been extensively implemented to 3-L VSCs, is model predictive control (MPC), which belongs to the family of predictive control. This control method is the core of this dissertation.

#### 1.3.2 Finite Control Set Model Predictive Control (FCS-MPC)

Recently, with the advancement of microprocessors, finite-control-set model predictive control (FCS-MPC) methods have been extensively studied and implemented for various power electronics applications including motor drives, active power filters, grid-connected and standalone converters, etc. [114]-[117]. Several advantages of FCS-MPC, hereafter referred to as MPC, have contributed to the widespread use of MPC in power electronics including the fast-dynamic response and robustness against disturbances. The intuitive implementation of MPC and the ease in including the nonlinearities and the constraints in the controller design have also increased the popularity of this control method. Additionally, within the same control loop, multiple objectives

can be achieved simultaneously by using MPC, which augments the usefulness of MPC [114]-[117]. The main merits and demerits of MPC are demonstrated in Figure 1.12.

Generally, MPC exploits the discrete nature of power converters. The discrete-time converter model is usually used to predict the future behavior of state variables over a time horizon with a fixed step size, which is an integer-multiple of the controller sampling time. Then, a cost function with either sole or multiple objectives is required to evaluate the error between the controlled variables and their corresponding references. Finally, a finite number of possible switching states is evaluated using the cost function, sometimes referred to as a quality function, to select the optimal switching state, which results in the minimal value of the cost function [114]-[117].

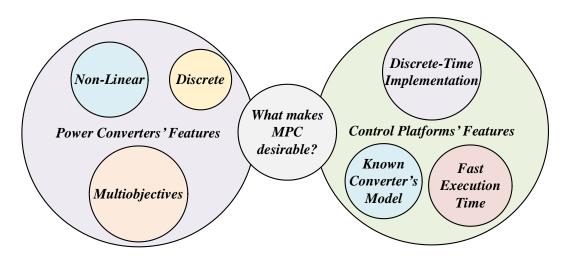

Finally, it can be summarized that two main reasons, depicted in Figure 1.13, have contributed to the dramatic increase of MPC in power electronics applications. The first reason is that the power electronic converter characteristics which are the nonlinear model, the discrete nature, and the need to control different objectives. Secondly, the excessive development in today's control platforms, which has led to overcoming the high number of mathematical calculations dilemma.

Figure 1.12: Advantages and drawbacks of FCS-MPC.

Figure 1.13: Reasons for FCS-MPC popularity in power electronics applications.

## 1.3.3 DC-Link Capacitor Voltages Control

Taking into considerations all the merits of 3-L VSCs and MPC, which have been previously described, this combination, MPC and 3-L converters, has been determined to be attractive for applications related to the DERs. However, other challenges are amplified as a result of this selection. To be more specific, despite the advantages of using 3-L VSCs, these converters may suffer from the unequal voltages between the two dc-link capacitors if the neutral-point voltage (NP-V) is not well-controlled [118]. The NP-V oscillations may even result in damaging the power semiconductor devices since some of them experience higher voltage stress than the others. Also, even moderate NP-V fluctuations can increase the harmonics in the converter output waveforms [99]. Therefore, to entirely exploit the advantages of the 3-L VSCs, the NP-V should be well-regulated. As a result of that, much research has been conducted to solve the NP-V oscillation issue for 3-L VSCs. Both linear and non-linear control methods such as the proportional-integral (PI) control and hysteresis control have been proposed [119]-[121]. This section focuses on the dc-link capacitor voltages control of the 3-L converters.

Thus far, the usefulness of the MPC has been validated on the 3-L VSCs. Typically, a 3-L VSC energized with a single dc voltage source requires MPC to use at least a dual-objective cost function, i.e., with one term dedicated to regulate the NP-V oscillations and other term(s) to achieve the primary control target(s) [122], [123]. Despite all advantages associated with MPC, the selection of weighting factors poses challenges, particularly when the number of the objectives is increased. In addition, an optimal selection for different weighting factors at a certain operating condition may be susceptible to the external disturbances and/or dynamic changes. Normally, designing proper weighting factors consumes a considerable amount of time and effort [124], [125].

Because the performance of the MPC is highly dependent on weighting factors, various MPC methods have been introduced to eliminate the weighting factors to enhance the performance of MPC. In [126], the weighting factor of the dc-link capacitor voltages balancing term has been eliminated from the cost function using a hierarchical control method. Nonetheless, a PI control, which is designed considering dc-link voltage dynamics that is ten times slower than that of MPC, was used specifically to regulate the NP-V fluctuations. This PI regulator not only increases the control complexity, but also decreases the system dynamic response. In [127], an MPC method using the discrete space vectors (DSVs) for a 3-L T-type VSC is proposed, which can reduce both the computational time and the output current ripples. However, the DSVs are designed without taking into consideration their impact on NP-V. Thus, a cost function is designed specifically to balance the dc-link capacitors voltages. In [128] and [129], the redundant voltage vectors are used to regulate the NP-V fluctuations without adding a term for the dc-link voltage balancing in the cost function. Nevertheless, this method cannot work if a medium voltage vector is the candidate to be selected by MPC, which limits the working region of the MPC to certain modulation indices.

Also, a vector shifted MPC method was proposed in [130] to simplify the cost function design. However, a proportional control, which requires tuning, is mandatory to adjust the dc-link capacitor voltages.

### 1.4 Research Objectives

The primary objective of the work presented in this dissertation is to develop a robust and effective MPC strategy specifically for the 3-L VSCs. The proposed MPC technique has the ability to overcome the challenges associated with the implementation of the classical MPC scheme on the 3-L VSCs. These resolved issues primarily include the complex cost function design, the high converter output waveform ripples, the expensive voltage/current sensors and the high execution time of the controller algorithm. The proposed MPC strategy, on the other hand, should retain the merits of the traditional MPC method, which essentially include the fast-dynamic response and robustness against parameter uncertainty.

The key objectives of the proposed MPC approach include

- Simplifying the MPC cost function design for the 3-L converters. This merit is accomplished by achieving inherent balanced dc-link capacitor voltages. As a result, the time-consuming weighting factors selection and tuning can be eliminated.

- Achieving significantly reduced NP-V oscillations of the dc-link capacitor voltages. This

major advantage can be achieved by using the concept of the virtual space vectors (VSVs),

which generate zero NP-C, which ultimately does not contribute in the NP-V oscillations.

- Reducing the converter output waveforms ripples. This merit can be realized as a result of

the increased average switching frequency due to the use of the VSVs as well as the

significantly reduced NP-V fluctuations. Having a smaller number of objectives in the cost

function also ensures the controller primary objective(s) receive more control attention and effort.

- Decreasing the system overall cost as less voltage/current sensors are used. This advantage

is accomplished because the proposed MPC algorithm can achieve inherent dc-link

capacitor voltages balancing, which eliminates the need to using voltage/current sensors to

regulate the dc-link capacitor voltages.

- Improving the system overall reliability as less sensor boards and feedback signals are used. This contribution reduces the chances of hardware failure. This advantage not only reduces the total cost and improves the system reliability as less hardware is required, but also decreases the size, weight and wiring complexity of the system.

- Reducing the controller execution time, which is accomplished as a result of the simplified MPC algorithm design. Since the cost function of the proposed MPC strategy does not include terms related to the NP-V regulation, predictive equations of the dc-link capacitor voltages are eliminated from the code, which reduces the number of calculations to be performed within a control sampling period.

## 1.5 Dissertation Organization

The rest of this dissertation is structured in the following manner

Chapter 2 provides a comprehensive description for two common 3-L converter topologies;

NPC and T-type converters. These topologies are modeled in this chapter considering the discrete nature of the power converters. Then, the dc-link of 3-L VSC topologies is modeled in continuous and discrete time. Brief reviews for different converter output ac filters followed by the continuous- and discrete-time derivation for these filters' models

are also provided. After that, a synchronization technique, i.e., synchronous reference frame phase locked loop (SRF-FLL), has been reviewed in detail. The control gains of the SRF-PLL have been also derived in continuous and discrete time.

- Chapter 3 describes the conventional MPC for 3-L NPC converters considering different power converter operating modes. An enhanced MPC for 3-L NPC converters, which uses the concept of the VSVs, is then described and compared with the conventional one. The implementation of the proposed MPC gate signals is also presented in this chapter. The 3-L NPC VSC efficiency analysis is also demonstrated. This chapter is concluded by providing simulation results which are validated using controller hardware-in-the-loop (HIL) studies.

- Chapter 4 explains and introduces both the conventional and proposed model predictive voltage control (MPVC) methods for the 3-L T-type converters. Additionally, the T-type gating signals generation is demonstrated. The topology efficiency analysis is also discussed, considering the typical and proposed MPVC. Comprehensive simulation results are also included. Finally, the experimental test setup is shown followed by comprehensive experimental results which verify the theoretical analysis and simulation studies.

- Chapter 5 includes the dissertation conclusions, contributions and recommendations for future research wok.

#### **CHAPTER 2**

# MODELING OF THE GRID-CONNECTED AND STAND-ALONE CONVERTER SYSTEMS

#### 2.1 Introduction