FACULTY OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING DEGREE PROGRAMME IN ELECTRONICS AND COMMUNICATIONS ENGINEERING

# **MASTER'S THESIS**

# EFFICIENT IMPLEMENTATION OF CHANNEL ESTI-MATION ALGORITHM FOR BEAMFORMING

Author Arttu Afflekt

Supervisor Prof. Olli Silvén

Second Examiner D.Sc. (Tech.) Tuomo Hänninen

Technical Advisor D.Sc. (Tech.) Jussi Salmi

Afflekt A. (2020) Efficient Implementation of Channel Estimation Algorithm for Beamforming. University of Oulu, Faculty of Information Technology and Electrical Engineering, Degree Programme in Electronics and Communications Engineering. Master's Thesis, 66 p.

#### **ABSTRACT**

The future 5G mobile network technology is expected to offer significantly better performance than its predecessors. Improved data rates in conjunction with low latency is believed to enable technological revolutions such as self-driving cars. To achieve faster data rates, MIMO systems can be utilized. These systems enable the use of spatial filtering technique known as beamforming. Beamforming that is based on the pre-acquired channel matrix is computationally very demanding causing challenges in achieving low latency. By acquiring the channel matrix as efficiently as possible, we can facilitate this challenge.

In this thesis we examined the implementation of channel estimation algorithm for beamforming with a digital signal processor specialized in vector computation. We present implementations for different antenna configurations based on three different approaches. The results show that the best performance is achieved by applying the algorithm according to the limitations given by the system and the processor architecture. Although the exploitation of the parallel architecture was proved to be challenging, the implementation of the algorithm would have benefitted from the greater amount of parallelism. The current parallel resources will be a challenge especially in the future as the size of antenna configurations is expected to grow.

Key words: telecommunications, 5G, MIMO, parallel architecture.

Afflekt A. (2020) Keilanmuodostuksen tarvitseman kanavaestimointialgoritmin tehokas toteutus. Oulun yliopisto, tieto- ja sähkötekniikan tiedekunta, elektroniikan ja tietoliikennetekniikan tutkinto-ohjelma. Diplomityö, 66 p.

# TIIVISTELMÄ

Tulevan viidennen sukupolven mobiiliverkkoteknologian odotetaan tarjoavan merkittävästi edeltäjäänsä parempaa suorituskykyä. Tämän suorituskyvyn tarjoamat suuret datanopeudet yhdistettynä pieneen latenssiin uskotaan mahdollistavan esimerkiksi itsestään ajavat autot. Suurempien datanopeuksien saavuttamiseksi voidaan hyödyntää monitiekanavassa käytettävää MIMO-systeemiä, joka mahdollistaa keilanmuodostuksena tunnetun spatiaalisen suodatusmenetelmän käytön. Etukäteen hankittuun kanavatilatietoon perustuva keilanmuodostus on laskennallisesti erittäin kallista. Tämä aiheuttaa haasteita verkon pienen latenssivaatimuksen saavuttamisessa.

Tässä työssä tutkittiin keilanmuodostukselle tarkoitetun kanavaestimointialgoritmin tehokasta toteutusta hyödyntäen vektorilaskentaan erikoistunutta prosessoriarkkitehtuuria. Työssä esitellään kolmea eri lähestymistapaa hyödyntävät toteutukset eri kokoisille antennikonfiguraatioille. Tuloksista nähdään, että paras suorituskyky saavutetaan sovittamalla algoritmi järjestelmän ja arkkitehtuurin asettamien rajoitusten mukaisesti. Vaikka rinnakkaisarkkitehtuurin hyödyntäminen asetti omat haasteensa, olisi algoritmin toteutus hyötynyt suuremmasta rinnakkaisuuden määrästä. Nykyinen rinnakkaisuuden määrä tulee olemaan haaste erityisesti tulevaisuudessa, sillä antennikonfiguraatioiden koon odotetaan kasvavan.

Avainsanat: tietoliikennetekniikka, 5G, MIMO, rinnakkaisarkkitehtuuri.

# TABLE OF CONTENTS

| ABS' | TRAC                           | cT                              |                                         |    |  |  |  |

|------|--------------------------------|---------------------------------|-----------------------------------------|----|--|--|--|

| TIIV | ISTEI                          | LMÄ                             |                                         |    |  |  |  |

| TAB  | LE OI                          | F CON                           | ΓENTS                                   |    |  |  |  |

| FOR  | EWOl                           | RD                              |                                         |    |  |  |  |

| LIST | OF A                           | BBRE                            | VIATIONS AND SYMBOLS                    |    |  |  |  |

| 1    | INTRODUCTION                   |                                 |                                         |    |  |  |  |

| 2    | MOBILE COMMUNICATION EVOLUTION |                                 |                                         |    |  |  |  |

|      | 2.1                            | Visions and Requirements        |                                         |    |  |  |  |

|      | 2.2                            | Towards New Frequencies         |                                         |    |  |  |  |

|      | 2.3                            | Multipath Propagation and OFDM1 |                                         |    |  |  |  |

| 3    | MUL                            | MULTIANTENNA SYSTEMS            |                                         |    |  |  |  |

|      | 3.1                            | Space Diversity                 |                                         |    |  |  |  |

|      | 3.2                            | Spatia                          | l Multiplexing                          | 22 |  |  |  |

|      | 3.3                            | Single                          | -User Beamforming                       | 23 |  |  |  |

|      | 3.4                            | Multi-User Beamforming          |                                         |    |  |  |  |

|      | 3.5                            | Summ                            | ary                                     | 26 |  |  |  |

| 4    | CHA                            | HANNEL ESTIMATION               |                                         |    |  |  |  |

|      | 4.1                            | Overv                           | iew                                     | 27 |  |  |  |

|      | 4.2                            | Chann                           | el Estimation in Single Antenna Systems | 28 |  |  |  |

|      | 4.3                            | Estima                          | ation in Multiantenna Systems           | 30 |  |  |  |

|      | 4.4                            | SRS Transmission in LTE and 5G  |                                         |    |  |  |  |

|      | 4.5                            | Summary                         |                                         |    |  |  |  |

| 5    | ALG                            | LGORITHM ARCHITECTURE MATCHING  |                                         |    |  |  |  |

|      | 5.1                            | Implementation Technologies     |                                         |    |  |  |  |

|      | 5.2                            | Hardware Accelerators           |                                         |    |  |  |  |

|      |                                | 5.2.1                           | Hardware-Software Partitioning          | 39 |  |  |  |

|      |                                | 5.2.2                           | Accelerator Architectures               | 41 |  |  |  |

|      | 5.3                            | Progra                          | mmable Architectures                    | 42 |  |  |  |

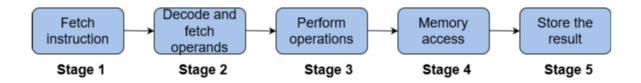

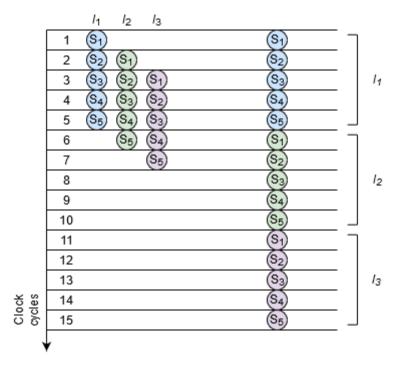

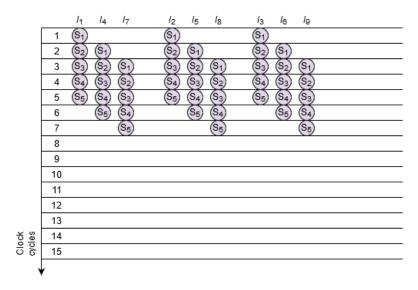

|      |                                | 5.3.1                           | Instruction Pipelining                  | 42 |  |  |  |

|      |                                | 5.3.2                           | Instruction Level Parallelism           | 45 |  |  |  |

|      |                                | 5.3.3                           | Parallel Processing of Data             | 47 |  |  |  |

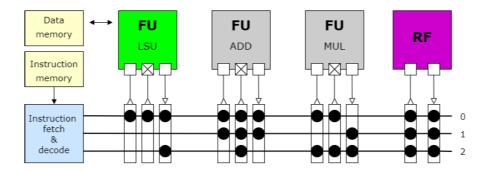

|      | 5.4                            | Expos                           | ed Data Path Architectures              | 48 |  |  |  |

|      |                                | 5.4.1                           | Transport Triggered Architecture        | 49 |  |  |  |

|      |                                | 5.4.2                           | Stanford ELM                            | 50 |  |  |  |

|      |                                | 5.4.3                           | Summary                                 | 50 |  |  |  |

| 6    | IMPI                           | IMPLEMENTATION AND EVALUATION   |                                         |    |  |  |  |

|      | 6.1                            | .1 Implementation               |                                         |    |  |  |  |

|      |                                | 6.1.1                           | Approach A                              | 52 |  |  |  |

|      |                                | 6.1.2                           | Approach B                              | 53 |  |  |  |

|      |                                | 6.1.3                           | Approach C                              | 54 |  |  |  |

|      | 6.2                            | Evalua                          | ation                                   | 54 |  |  |  |

|   |         | 6.2.1      | Elementary Comparison              | 55 |  |  |

|---|---------|------------|------------------------------------|----|--|--|

|   |         | 6.2.2      | 2RX Comparison                     | 56 |  |  |

|   |         | 6.2.3      | 4RX Comparison                     | 56 |  |  |

|   |         | 6.2.4      | 8RX Comparison                     | 57 |  |  |

|   |         | 6.2.5      | Implementation Specific Comparison | 58 |  |  |

|   | 6.3     | Summ       | ary                                | 60 |  |  |

| 7 | DISC    | DISCUSSION |                                    |    |  |  |

| 8 | SUMMARY |            |                                    |    |  |  |

| 9 | REFE    | ERENC      | CES                                | 64 |  |  |

### **FOREWORD**

First, I want to thank my supervisor Professor Olli Silvén for his continuous guidance and support through the writing process. I felt privileged to receive such detailed guidance. I also want to thank Nokia and my Technical Advisor Jussi Salmi for the great opportunity to work as a thesis worker as a part of his group. Your feedback has encouraged me and without your expertise, defining the final scope of this thesis all by myself would have been much more challenging. I would like to express my gratitude to the second examiner Tuomo Hänninen. I want to thank my senior colleagues. Their comments and insight have made this journey much more enjoyable.

I would like to extend particular thanks to my mother. I would like to thank you for providing me the opportunity to study so far. Without your valuable contribution I would have never reached this goal. You have always been there for me, even in difficult times.

My final and warmest thanks belong to my girlfriend Reetta for always believing in me. Your support and encouragement have been immeasurably valuable. The importance of the immense love you have given is beyond words. Thank you.

Helsinki, May 25, 2020

Arttu Afflekt

### LIST OF ABBREVIATIONS AND SYMBOLS

ASIC application specific integrated circuit

ASIP application specific instruction set processor

AWGN additive white gaussian noise BPSK binary phase shift keying

BS base station

CAZAC constant amplitude zero auto correlation

CPI cycles per instruction CPU central processing unit

CGRA coarse grained reconfigurable array

DFT discrete Fourier transform

DLP data level parallelism

DMA direct memory access

DM-RS demodulation reference signal

DOP degree of parallelism

DPC dirty paper coding

DSP digital signal processor

EDGE enhanced data rates for GSM evolution

FIR finite impulse response

FPGA field programmable gate array

GSM global system for mobile communications IDE integrated development environment

IEEE institute of electrical and electronics engineering

ILP instruction level parallelism ISI inter symbol interference

LOS line of sight

LTE long term evolution

LTE-A long term evolution advanced

MAC multiply and accumulate

MIMO multiple in multiple out

MISO multiple in single out

MMSE minimum mean square error

MU-MIMO multi-user multiple in multiple out

SU-MIMO single-user multiple in multiple out

NR new radio

NRE non-recurring engineering

OFDM orthogonal frequency division multiplexing

PRB physical resource block

PRACH physical random access channel PUCCH physical uplink control channel PUSCH physical uplink shared channel

RX receiving

SIMO single in multiple out SISO single in single out

SIMD single instruction multiple data SISD single instruction single data

SNR signal-to-noise ratio

SRS sounding reference signal SVD singular value decomposition

TDD time division duplex

TTI transmission time interval

TTA transport triggered architecture

TX transmitting UE user equipment

VLIW very long instruction word

WCDMA wideband code division multiple access QAM quadrature amplitude modulation

ZF zero forcing

$A_t$  area of the antenna aperture

$\alpha_n(t)$  amplitude of the nth multipath component

B bandwidth

$B_c$  coherence bandwidth

c speed of light C channel capacity

c(t) channel impulse response

$\mathbb{C}$  complex plane  $\delta$  Dirac delta function

*f* frequency

$G_r$  receive antenna gain  $G_t$  transmit antenna gain

$\begin{array}{ll} \gamma_{\Sigma} & \text{output SNR} \\ \mathbf{H} & \text{channel matrix} \\ \widehat{\mathbf{H}}_{LS} & \text{channel LS estimate} \\ \widehat{\mathbf{H}}_{LMMSE} & \text{channel LMMSE estimate} \end{array}$

I Identity matrix  $\lambda$  wavelength  $\lambda_i$  ith eigenvalue

m number of executed instructions

$m_u$  cyclic shift parameter n number of stages

$M_r$  number of receive antennas  $M_t$  number of transmit antennas  $N_{tr}$  length of the training sequence

n noise vectorN noise

P signal power

$\phi_n(t)$  Doppler phase shift of the nth multipath component

$P_i$  transmit power of *ith* stream

$P_r$  receive power  $P_t$  transmit power

R distance between receiver and transmitter

$\mathbf{R}_H$  channel correlation matrix

r(t) received signal

$\sigma_i$  ith singular value of  $\Sigma$

$\sigma^2$  noise variance

Δ diagonal matrix from SVDt time to execute one stage

$T_D$  time delay T(n) throughput

$\tau_n(t)$  delay of the nth multipath component

u beamforming vectorU unitary matrix from SVD

u(t) equivalent low-pass representation

$\mathbf{v}$ beamforming vector $\mathbf{V}$ unitary matrix from SVD $\mathbf{W}_Z$ zero forcing precoding matrix $\mathbf{x}$ transmitted signal vector $\mathbf{X}$ transmitted signal matrix $\mathbf{x}_{LS}$ general least squares solution $\mathbf{X}_k$ Zadoff-Chu base sequence

$X_{n,k}$  transmitted symbol at kth subcarrier of nth symbol in frequency domain

y received signal vector Y received signal matrix

$Y_{n,k}$  received symbol at kth subcarrier of nth symbol in frequency domain

# 1 INTRODUCTION

The evolution of mobile network generations has been steady from the introduction of 1G in the early 1980s until today. A new mobile network generation has been released every ten years and the fifth-generation mobile network should be deployed during this decade.

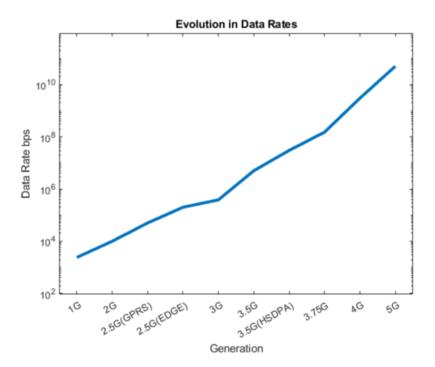

The increase in data rates as measured in bits per second has been exponential within successive generations. The growth of the data rates during the evolution of mobile networks is approximated in Figure 1 [1]. In the early days of the 2G network it was possible to achieve a data transfer rate approximately 15kbps using GSM technology. The introduction of EDGE technology made it possible to reach data rates up to 600kbps. Therefore, data rates experienced a forty-fold increase during a single mobile network generation.

3G network continued this trend by increasing the data rates up to 2Mbps with a new technology called WCDMA. Having the latest enhancements for the 3G network, it was possible to reach data rates around 40Mbps. Once again, tremendous increase in data rates was experienced within one generation. This trend continued with the 4G network whose latest enhancements increased data rates to gigabits per second [2]. The upcoming 5G network is not going to end this trend [1].

Figure 1. Approximate growth of data rates in logarithmic scale.

This massive growth in data rates has not been achieved just by increasing the transmission bandwidths. The latest mobile network generations (LTE and 5G), utilize advanced signal processing techniques to increase the spectral efficiency in conjunction with multiple input multiple output (MIMO) technology.

In theory, these techniques can increase data rates. However, utilizing these methods requires a great deal of heavy computation. Combining computationally demanding techniques with very low latency requirement is challenging. In order to meet the latency requirements, these methods must be implemented with an architecture specialized in signal processing. Furthermore, one needs to implement these tasks of significance as efficiently as possible in order to achieve the expected latency [3].

One of these methods is known as beamforming. Beamforming is based on a channel matrix that contains the channel state information for each antenna pair. Channel state information can be obtained by estimating the channel based on the known pilot symbols. These estimates are used later in the calculation of the beamforming coefficients. Since this process has to be performed beforehand, it has a great impact on the total system load caused by the beamforming.

Channel estimation can be performed in countless ways. By favouring a channel estimation scheme with low complexity and adequate accuracy, excess signal processing workload could be reduced. Current antenna configurations consist of numerous antenna elements which makes the channel estimation demanding. The size of the antenna configuration directly determines the size of the channel matrix. Because each element of the channel matrix must be estimated, large antenna configurations poses challenges to channel estimation. Although processing of very large matrices is cumbersome it can be facilitated by using a parallel architecture. To ensure good performance, one should evaluate the feasibility of used parallel architecture on a regular basis due to rapidly growing number of antenna elements. In this thesis, we review couple of beamforming techniques and discuss the topic of channel estimation in wireless communications. The discussion emphasis is in efficient implementation of the channel estimation for beamforming.

This thesis is organized as follows. In Chapter 2 an overview of 5G is provided by introducing the preliminary requirements and usage scenarios specified for 5G. In addition, a brief introduction to multipath propagation is provided. At the beginning of Chapter 3, the multipath channel is linked to the multiantenna systems by introducing conventional methods to increase the channel capacity via spatial diversity schemes. This is followed by discussion of beamforming techniques and spatial multiplexing. In Chapter 4, we discuss channel estimation in single and multi-antenna systems. The architecture exploration is provided in Chapter 5. In Chapter 6, we go through the implementations and present the results. Then, in Chapter 7, we discuss our findings and speculate on the future of the subject. Finally, in Chapter 8 we provide a brief summary of this thesis.

#### 2 MOBILE COMMUNICATION EVOLUTION

In this chapter the requirements and expectations towards the upcoming fifth mobile network generation are introduced. According to the specifications set by 3GPP, 5G will continue the trend of remarkable data rate growth seen between the previous successive generations [4]. In addition to significantly higher data rates, the network is expected to operate at ultra-low latency, even in challenging conditions such as when providing a solid and reliable experience for high mobility users. Initially, these visions and usage scenarios are reviewed. Since 5G is targeted to operate in much higher frequencies than the previous mobile network generations, we take a glance at the feasibility of the millimetre waves.

It is shown that the higher frequencies targeted for 5G offer significantly more bandwidth than ever before. Higher frequencies allow greater number of users to enter the network than previously. In crowded areas, current frequency resources are so heavily utilized that they cannot provide necessary capacity anymore so new frequency resources are required. Finally, to provide some preliminary knowledge for the future chapters, we take a look at the properties of the multipath channel.

# 2.1 Visions and Requirements

Continuous increase in the usage of the mobile networks has led to the development of a new mobile network generation. This mobile network generation is the fifth of its kind, hence the name 5G. 5G is also known as new radio, commonly abbreviated as NR. The standardization work of 5G is carried out by an organization called 3GPP. 3GPP is a collaboration of seven independent telecommunication standardization organizations [5]. One could view the role of 3GPP in 5G development as an author who maintains and develops the global rules and standards required for the future network. In the 3GPP specification release 15 the requirements for the 5G usage scenarios are the following [6][4]:

- Enhanced Mobile Broadband (eMBB) The requirement for eMBB is to provide better data rates for larger user density and mobility than 4G/LTE. Specification for the user densities and the data rates in both uplink and downlink are provided for different types of scenarios. One type use case is broadband access in a crowd. A rock concert could be a real-life example of this scenario. A specification is also provided for high speed vehicles and even for connectivity in airplanes.

- Critical Communications (CC) and the Ultra Reliable and Low Latency Communications (URLLC) This scenario corresponds to the situation where very low latency with very high service availability is required. From the radio access point of view the total latency can be reduced by improving the data processing in the radio and the baseband parts. Real scenarios could be for instance a process automation or a remote control such as self-driving cars.

- Massive Internet of Things (mIoT) Scenarios require support for very high density of devices.

- **Flexible Network Operation** Allows network to be configured in a more flexible way. This covers for example a network slicing, which gives the operator an ability to customize the network appropriate to the situation.

International Telecommunication Unions sector for radiocommunication (ITU-R) summarizes similar type of usage scenarios according to their importance in their document "IMT Vision – Framework and overall objectives of the future development of IMT for 2020 and beyond". These features are partially illustrated in Figure 2.1 [7] with numerical specifications for the possible future 5G network. [7]

In Figure 2.1 IMT-2020 and IMT-advanced are the specifications set by ITU for 5G and 4G, respectively. Furthermore, this figure visualizes the requirements for eMBB in compact form. Features such as mobility, connection density, traffic capacity and data rates can be compared to the corresponding values provided by 3GPP in table 7.1-1 in [4]. Although the values introduced in Figure 2.1 are said to be only target values for the research, it should be noted that the numbers given by the 3GPP specification predict very promising enhancements for the data transmission rates and the network capacity. Both features are promised also for high velocity users, e.g. train passengers.

As shown in the listing of 3GPP 5G-scenarios, as well as in Figure 2.1, the latency requirement is heavily emphasized. Reliable low latency network is naturally a mandatory requirement for self-driving cars, as one example. Low latency requirement addresses challenges towards the system design, which will be pointed out in the subsequent chapters.

In the following chapters it is noticed that the higher data rates are not achieved just by increasing the bandwidth. It is shown that a great deal of signal processing is required in order to achieve the expected specifications and to tackle the challenges set by the mobile environment. In order to meet the specifications, new technology must be developed and utilized.

#### Enhancement of key capabilities from IMT-Advanced to IMT-2020 User experienced Peak data rate data rate (Gbit/s) (Mbit/s) 2.0 100 IMT-2020 Area traffic Spectrum capacity efficiency (Mbit/s/m²) 10 0.1 50 1005 IMT-advanced Mobility Network (km/h)energy efficiency 10 Connection density (ms) (devices/km )

Figure 2.1. Comparison of fourth and fifth mobile network generations. © [2015] ITU

Several papers and publications provide summaries of the key enabling technologies for 5G [8][1][9]. Since new frequencies are considered essential, their feasibility for wireless communication is discussed in the next section.

### 2.2 Towards New Frequencies

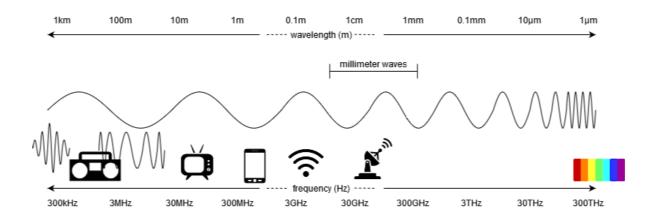

Fundamentally, wireless communication is implemented using electromagnetic waves. These waves are divided into different frequency ranges which together form the electromagnetic spectrum. The spectrum of electromagnetic radiation is shown in Figure 2.2 [10]. Parts from long wave radio towards higher frequencies are traditionally used in wireless communications as shown in Figure 2.2.

Figure 2.2. Spectrum of electromagnetic radiation.

Useable parts of the spectrum are allocated for the different wireless technologies. Today, the situation is that the lower parts of the frequency range are heavily occupied. The frequencies are from approximately hundreds of MHz up to a few GHz. For example, these frequencies are used by older mobile network generations. When all the frequency resources are utilized, in order to allocate bandwidth for new users, number of frequency resources must be increased. Since lower frequencies are already heavily occupied, new frequencies are found from the higher frequencies.

The new high frequency range envisioned for the use of 5G communications is often referred as millimetre waves. These millimetre waves correspond to the frequency range from 3GHz (some context 6GHz+) up to 300GHz [8]. Using the millimetre wave frequency range offers several evident enhancements for the network. High frequency carrier waves enable allocation of larger bandwidths for the same number of users compared to their lower frequency counterparts [1].

Above-mentioned property is also easily recognized by observing the famous theorem for channel capacity provided by C.E. Shannon. The theorem for additive white Gaussian (AWGN) channel where channel output corresponds to the input corrupted by noise is given by:

$$C = B \log_2 \left( 1 + \frac{P}{N} \right) \tag{2.1}$$

In Equation (2.1), C is the channel capacity in bits/s, B is the bandwidth in Hz, P and N are the signal power and the noise, respectively [11]. Given theorem states that the channel capacity increases linearly with respect to the transmission bandwidth, when signal-to-noise ratio (SNR) is assumed constant. Although we will see slightly different type of expressions for the channel capacity in the subsequent chapters, it should be noted that the same key findings considering

bandwidth and SNR still apply. Actually, the emphasis on the subsequent chapters is to enhance the capacity without increasing the bandwidth.

It is predicted in [8] that in terms of frequency these new wave lengths could increase the capacity by 10GHz or more. All the previous network generations operated only within couple of GHz. Compared to the previous generations, frequency resources envisioned for 5G are tremendous. With this approximation, 5G alone would consume many times more frequency resources than all the previous generations together. However, the question arises are these frequencies feasible for wireless communication in cellular networks?

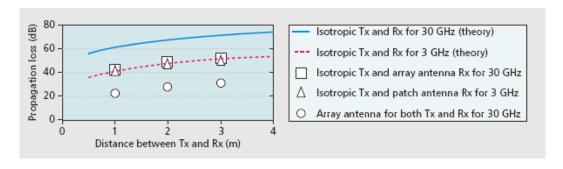

Free space propagation in line-of-sight (LOS) is often modelled using the Friis transmission equation. Generally adopted idea that the higher frequencies tend to have a lesser free space propagation follows from too narrow inspection of the previously mentioned equation. Friis formula can be written as [12]

$$P_r = P_t + G_t + G_r + 20 \log \left(\frac{c}{4\pi Rf}\right) [dBm], \qquad (2.2)$$

where  $P_t$  and  $G_t$  are the transmit power and the transmit antenna gain,  $P_r$  and  $G_r$  are the equivalent receive antenna quantities. f, R and c are the frequency, distance between the receiver and the transmitter and the speed of light, respectively.

By observing the rightmost term, it certainly seems that the high frequencies seem to have a greater attenuation compared to the lower ones. In fact, the received power would attenuate according to the formula, if the antenna gains  $G_t$  and  $G_r$  are assumed to be constant as well as less than or equal to unity [12]. Actually, this property holds for the omnidirectional isotropic antennas whose G terms equal to one. However, when we are dealing with the directional transmit antenna, the gain of the receiving antenna is given by [13]

$$G_t = \frac{4\pi A_t}{\lambda^2},\tag{2.3}$$

where  $A_t$  is the area of the antenna aperture and the wavelength is given by  $\lambda$ . Since the wavelength gets shorter as the frequency increases, it seems that the antenna gain is frequency dependent and it increases with the frequency.

The behaviour of both 3GHz and 30GHz signals in LOS was investigated in [12]. The propagation loss for the both frequencies is given as a function of a distance in Figure 2.3 [12]. From the figure we see that the both frequencies behave similarly, and the signals have attenuated by approximately the same amount [12]. According to these results, path loss is not a problem for short range LOS communications.

Figure 2.3. Signal attenuation in LOS scenario. © [2014] IEEE

However, it is pointed out in [9] that the millimetre waves handle physical obstacles poorly. If the signal is not under a line of sight, its attenuation doubles per decade. In addition to this, blocking loss of 15-40 dB is also introduced. Similar results are also highlighted in [14] and it is said that these high attenuations from the building materials can completely surpass the signal and prevent its access from outdoor radios to indoor devices. The signal's poor ability to penetrate certain construction materials can be ignored if separate networks are built indoors and outdoors. According to [14], heavy rain significantly attenuates the millimetre waves. The signal can experience a massive attenuation of 1-10dB/km depending on the rate of the rain. This challenge is tackled in [15] by pointing out that the current cell sizes are so small that this does not become a problem. This clearly suggests that rain is a negligible nuisance to dense networks.

Based on this quick review, the new frequencies envisioned for 5G seem to be potential but not problematic. To overcome the challenges related to the millimetre wave propagation many articles have suggested to take advantage of the short wavelengths and to use beamforming with (massive) MIMO antenna elements.

# 2.3 Multipath Propagation and OFDM

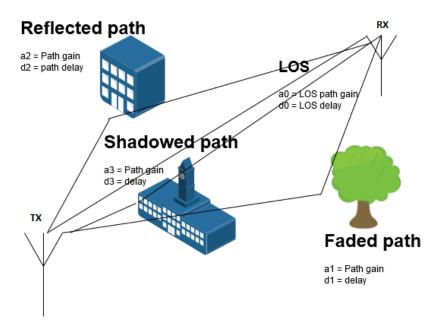

When a signal is transmitted across the wireless channel, it experiences several challenges that makes reliable communication harder. When the signal propagates through the free space, its power tends to attenuate as a function of distance. Adding obstacles such as buildings will introduce the signal to shadowing, which also attenuates the signal. These effects are known as large-scale propagation effects. There are also small-scale effects in the multipath channel, which are discussed in this section. [16]

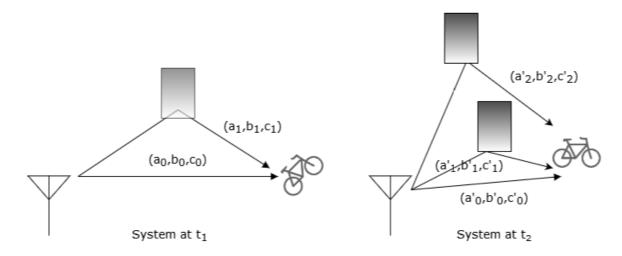

In multipath environment the received signal consists of one line of sight component and several multipath components, as shown in Figure 2.4. To put it simply, if a single pulse is transmitted, several delayed and distorted copies of this pulse are received.

Figure 2.4. Multipath environment.

If the transmitted signal s(t) is presented as  $s(t) = Re\{u(t)e^{j2\pi f_c t}\}$ , where u(t),  $f_c$  and t are the equivalent low-pass representation for the transmitted signal, the frequency of the carrier wave and time, respectively. The received signal can be expressed as

$$r(t) = Re \left\{ \sum_{n=0}^{N(t)} \alpha_n(t) u(t - \tau_n(t)) e^{j(2\pi f_c(t - \tau_n(t)) + \phi_{D_n})} \right\},$$

(2.4)

where N(t) gives the number of the multipath components at time t, n=0 corresponds to the LOS component and  $\tau_n(t)$ ,  $\phi_{D_n}$  and  $\alpha_n(t)$  are the delay, Doppler phase shift, and the amplitude of the nth multipath component, respectively [16]. Notice that the transmitted signal is not the only time-dependent variable in Equation (2.4). The variables that represent the properties of the multipath channel are time dependent as well. As shown in Figure 2.5 [16], the other party moving, the physical structure of the channel changes, and the channel is described with a new set of parameters.

Figure 2.5. Time-varying nature of the multipath channel.

Rearranging Equation (2.4), the received signal r(t) can be written as a convolution with the channel impulse response  $c(\tau, t)$  [16]

$$r(t) = Re\left\{ \left( \int_{-\infty}^{\infty} c(\tau, t) u(t - \tau) \right) e^{j2\pi f_c t} \right\}, \tag{2.5}$$

where  $c(\tau, t)$  is given by [16]

$$c(\tau,t) = \sum_{n=0}^{N(t)} \alpha_n(t) e^{-j\phi_n(t)} \delta(t - \tau_n(t)), \qquad (2.6)$$

where  $\phi_n(t)$  holds all the frequency and phase components. The Dirac delta function is denoted by  $\delta$ . [16] Channel impulse response-based modelling has also been used in the methods discussed in the following chapters. Another important property of the multipath transmission is

the distinction between narrowband and wideband signals. A well-known distinction between the wideband and the narrowband signals is done using a measure called coherence bandwidth. The coherence bandwidth is determined being approximately the inverse of the delay spread, i.e. the inverse of the time difference between the first and last multipath component  $B_c \approx \frac{1}{T_D}$  [16].

Narrowband signals tend to have a bandwidth significantly smaller than the coherence bandwidth. In this situation the fading of the signal is highly correlated, and the frequency response is ideally flat, thus it is called flat fading. Incidentally, when the signal bandwidth exceeds the coherence bandwidth it is considered as a wideband signal which experiences frequency selective fading. Wideband signals are also more vulnerable to a phenomenon called inter symbol interference (ISI). ISI is a type of interference where the consecutive symbols slightly overlap in time distorting the transmitted symbols [16]. Several techniques introduced in the later chapters will assume a narrowband model.

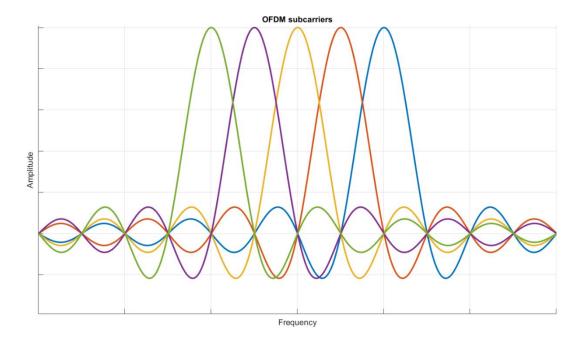

One way to reduce ISI and achieve narrowband signals is a modulation technique called orthogonal frequency division multiplexing (OFDM). OFDM is a modulation technique which is used in both LTE and 5G systems and is one of the key technologies used in the modern wireless systems [17]. Instead of producing a one high data rate stream with large bandwidth, OFDM divides the frequency in several orthogonal subcarriers that overlap in the frequency domain as illustrated in Figure 2.6 [18]. Although subcarriers are allowed to overlap, it can be seen that when one subcarrier reaches maximum, the rest are zero. As a result, we have many slowly modulated parallel narrowband channels that can be used to transmit the same information as the high data rate stream using one carrier wave [19]. In addition, since several MIMO techniques assume narrowband transmission, OFDM creates a robust basis for sophisticated MIMO communication systems.

Figure 2.6. Orthogonal frequency division multiplexing.

# 3 MULTIANTENNA SYSTEMS

In Chapter 1 we went through the evolution of mobile networks and witnessed a tremendous increase in data rates. In the previous chapter we learned that it is possible to enhance the data rates by increasing the transmission bandwidths. However, the increased data rates have not been accomplished just by continuously increasing the bandwidth. It is also possible to boost up the transmission rate by increasing the spectral efficiency. One way to enhance the data rates in terms of the spectral efficiency is to use multiple antennas for the transmission or the reception of the signal. Multiple antennas in conjunction with diversity or beamforming techniques can provide auspicious enhancements for the channel capacity and the data rates.

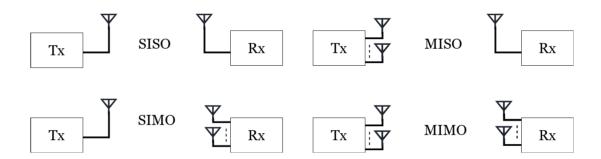

In this chapter, we discuss multiantenna systems. To begin with, we describe how the conventional transmit diversity methods affect the channel capacity. These methods take advantage of multiple antennas in either transmitting or receiving ends, hence they can be classified as single in multiple out (SIMO) or multiple in single out (MISO) systems. When multiple antennas are deployed in the both ends of the wireless channel, the system is naturally called a multiple in multiple out (MIMO) system. When MIMO system is used in a heavy multipath environment it is possible to enhance the channel capacity significantly more than with traditional methods.

Different type of antenna configurations seen in wireless communications are illustrated in Figure 3.1. MIMO techniques introduced in this chapter are referred as beamforming techniques due to the physical form of the radiation pattern that originates from the antenna elements [20]. Beamforming techniques are advanced precoding methods. They are used to increase the channel capacity by intelligently exploiting the diversity and multiplexing gains provided by MIMO. In addition, multiantenna systems can be utilized to generate a highly directional transmission using phased array technique. This provides a highly directional gain, which helps to reduce the inter-user interference and delay spread which helps fighting ISI [16].

In this thesis a channel estimation algorithm for beamforming was implemented. This chapter emphasizes the importance of the channel estimation in multiantenna systems. The majority of the schemes introduced in this chapter are based on the channel coefficients making the channel estimation mandatory. We see that beamforming techniques are computationally demanding. Because adapting heavy computation to low latency is challenging, this further emphasizes the importance of the efficient implementation of channel estimation.

Figure 3.1. Different type of antenna systems.

# 3.1 Space Diversity

Diversity techniques can be used to mitigate the effect of fading. As the signal attenuates, signal-to-noise ratio (SNR) declines, and this affects to the performance of the channel. By using multiple antennas for the transmission or the reception, several signal paths are formed between the TX and the RX-antenna pairs. Therefore, the same information can be sent through several independent paths improving the reliability of the transmission. [21] This type of diversity is called space diversity, antenna diversity or spatial diversity.

In order to exploit space diversity, attention must be paid to the separation of the antenna elements. When the antenna elements are separated by a sufficient spacing, it is expected that their signalling paths are statistically independent and do not experience deep fades simultaneously. Sufficient distance between the adjacent antenna elements depends on several things. However, since the antenna spacing is clearly more limited in the mobile devices due to their small size, low fading correlation can already be achieved with distance of  $\frac{\lambda}{4}$ , where  $\lambda$  is the wavelength of the signal. [22] High frequencies make the antenna spacing very practical. Since the wavelength shrinks as the frequency increases, multiple antenna elements can be integrated to a small area without losing the sufficient distancing. Diversity techniques can also be applied in terms of frequency or time diversity, where the signal replicas are transmitted using independent time or frequency resources [16]. However, these two techniques will require an expansion in bandwidth and are out of the scope of this thesis [16].

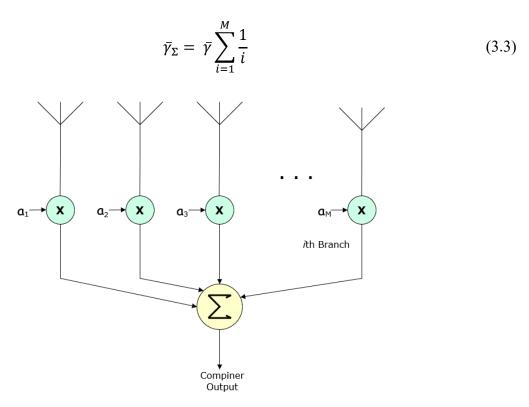

System with receiver diversity is a multi-antenna system with one transmit antenna and several receive antennas, which is essentially a SIMO system. The idea behind the receiver diversity is to bring robustness to the transmission by introducing several independent signalling paths between the RX-TX-antenna pairs. The performance gained from the receiver diversity depends on the technique which is used for combining the signals from the different antennas. Maximal-ratio combining (MRC) is a technique which combines all the received signals by cophasing the individual components and weighting them with an appropriate scaling factor in order to reach the maximal SNR. Most combining techniques including MRC are linear combiners which is illustrated in Figure 3.2 [16]. [16]

In MRC, the signal in every branch is multiplied by a coefficient  $\alpha_i = a_i e^{-j\theta_i}$ , where  $\theta_i$  is the phase of the signal on *ith* branch.  $\theta_i$  cancels the phase of every signal branch enabling coherent addition. If we assume an identical noise power spectral density (PSD) in every branch the total or the output SNR of the combiner  $\gamma_{\Sigma}$  can be expressed as follows [16]

$$\gamma_{\Sigma} = \frac{r^2}{N_{tot}} = \frac{1}{N_0} \frac{(\sum_{i=l}^{M} a_i r_i)^2}{\sum_{i=l}^{M} a_i^2},$$

(3.1)

where  $a_i$ ,  $r_i$  and  $N_0$  are the scaling coefficient, the received signal on the *ith* branch and the noise, respectively. Because MRC wanted to maximize SNR, coefficient  $a_i$  should be chosen accordingly. For example, it is possible to show using the Cauchy-Schwartz inequality that by weighing the signals by respective amplitudes will lead to the optimal SNR. Output SNR will correspond to the sum of the SNR of every branch. [16] When an equal average SNR is assumed on each individual branch with i.i.d. Rayleigh fading, the expected SNR achieved using the maximal-ratio combining is given by [16]

$$\bar{\gamma}_{\Sigma} = M\bar{\gamma},$$

(3.2)

where  $\bar{\gamma}$  denotes for the average branch SNR and M is the number of the RX-antennas. As seen from (3.2), using M receiving antennas, an M-fold increase in SNR was achieved on average. [16]

A much more straightforward combining method is called selection combining (SC). In selection combining the branch with the highest SNR would be chosen as the received signal. This approach eliminates the need for phase compensation leading to a reduced complexity. If we assume equivalent fading and noise with (3.2), the average SNR using the selection combining is given by: [16]

Figure 3.2. Illustration of the linear combiner.

The best efficiency from the selection combining is clearly achieved with two receiving antennas. Although MRC offered higher gain, SC offers a low complexity alternative making it also an interesting alternative for some purposes [16].

Space diversity can be exploited in the transmitting end as well. These setups can be classified as MISO type of antenna systems shown in Figure 3.1. If the channel is known to the transmitter in advance, i.e. the complex channel gain for the *ith* transmit antenna  $r_i e^{j\theta_i}$  is known, the transmitted signal s(t) is multiplied with a complex gain  $\alpha_i = a_i e^{-j\theta_i}$  before the transmission. It is immediately seen that the phase term  $\theta_i$  of the complex gain term  $\alpha_i$  corresponds to the conjugate of the corresponding channel gain. If all paths are co-phased according to their channel gain, a constructive interference should happen at the receive position. This sort of prefiltering is applied to all transmit antennas. As all the signals are pre-distorted according to their channel gains, channel acts as a matched filter and the received signal is a coherent combination of the transmitted signals. This method can provide similar SNR gain as its receiver counterpart. [16]

If the channel is not known to the transmitter, the previous method is inapplicable. Just by equally dividing the transmit power along the antennas no gain would be obtained in this situation [16]. However, using the well-known space-time coding method known as the Alamouti scheme it is possible to obtain transmit diversity to some extent [16]. When the Alamouti scheme is used with two transmit antennas, SNR at the receiver is given by [16]

$$\gamma_i = \frac{(|h_1^2| + |h_2^2|)E_s}{2N_0},\tag{3.4}$$

where  $h_1$  and  $h_2$  are the channel gains. In this section, we saw that by using multiple transmitter or receiver antennas, it was possible to achieve a better signal-to-noise ratio. Recalling Equation (2.1), by increasing the signal-to-noise ratio we also increase the channel capacity. Although, the increase is only logarithmic, the capacity still increases. This is especially important when the signal-to-noise ratio is very low. The increase in SNR is called array gain. Better SNR also increases the reliability of the transmission which in turn is called diversity gain [16]. By comparing the introduced transmit diversity schemes, we noticed that the schemes which utilized the channel information for filtering the transmitted signals achieved the best array gain. In addition, SNR at the receiver was maximized with the price of system complexity. We have already witnessed that the channel estimation plays an important role only by reviewing some of the conventional multiantenna techniques.

# 3.2 Spatial Multiplexing

When we are dealing with a multiantenna system that contains multiple transmitting and multiple receiving antennas, there exists a different type of technique to improve channel capacity. This technique is called spatial multiplexing. In order to use spatial multiplexing, we have to employ multiple antennas in both ends. This type of antenna configuration corresponds to the MIMO system shown in Figure 2.1. In principle, spatial multiplexing differs from the transmit diversity in that it sends different information via multiple spatial stream instead of sending the same symbol all over again. Each of these streams are capable of transmitting information independently, hence the name multiplexing.

The primary goal with the transmit and the receive diversity methods was to increase the channel capacity by fighting against fading. This led to an increased SNR, thus achieving a somewhat logarithmic increase in the channel capacity. Spatial multiplexing takes completely different approach in some sense. In a fading multipath environment, there is also the possibility of independent fading between different transmitting and receiving antennas. This makes communication via independent spatial stream possible [21]. For a system with n RX antennas and m TX antennas, it is shown that with a high SNR under i.i.d. Rayleigh-fading the channel capacity can be written as: [21]

$$C = \min\{n, m\} \log_2(SNR) \tag{3.5}$$

Although the capacity given by Equation (3.5) also requires certain other conditions to be fulfilled than high SNR, multiplicative increase in the channel capacity sounds promising.

More specifically, the number of antennas alone does not determine the increase in capacity. The key parameter is actually the number of spatial streams which is heavily dependent on the channel. A narrowband MIMO-system can be expressed as [16]

$$\begin{bmatrix} y_1 \\ \vdots \\ y_{M_r} \end{bmatrix} = \begin{bmatrix} h_{11} & \dots & h_{1M_t} \\ \vdots & \ddots & \vdots \\ h_{M_r1} & \dots & h_{M_rM_t} \end{bmatrix} \begin{bmatrix} x_1 \\ \vdots \\ x_{M_t} \end{bmatrix} + \begin{bmatrix} n_1 \\ \vdots \\ n_{M_r} \end{bmatrix}, \tag{3.6}$$

which can be simplified as  $\mathbf{y} = \mathbf{H}\mathbf{x} + \mathbf{n}$ . In the previous equation  $\mathbf{y}$  represents the  $M_r$ -dimensional vector of received symbols,  $\mathbf{H}$  is the channel matrix of size  $M_r \times M_t$  wherein each element represents the complex channel gain of the antenna pair determined by the subscript.  $\mathbf{x}$  is the  $M_t$ -dimensional vector of the transmitted symbols and  $\mathbf{n}$  is the noise vector. From Equation (3.6) we see that the received symbol  $y_m$  in the mth receive antenna is a linear combination of all transmitted symbols multiplied with the corresponding channel coefficients. If we imagine that the channel matrix  $\mathbf{H}$  was a diagonal matrix, then each received symbol would correspond to only one transmitted symbol. If this was the case, the symbols would be completely independent and resolvable. [16]

It is possible to present the channel matrix **H** as a product of three matrix by conducting the singular value decomposition (SVD) [16]

$$\mathbf{H} = \mathbf{U}\mathbf{\Sigma}\mathbf{V}^{\mathrm{H}},\tag{3.7}$$

where the matrices  $\mathbf{U}$  and  $\mathbf{V}$  are unitary matrices of size  $M_r \times M_r$  and  $M_t \times M_t$ , respectively, and  $\Sigma$  is a diagonal matrix of size  $M_r \times M_t$ . Furthermore, the columns of the matrix  $\mathbf{U}$  are called the left singular vectors of the matrix  $\mathbf{H}$  and the columns of the matrix  $\mathbf{V}$  are called right singular vectors of the matrix  $\mathbf{H}$ . The values  $\sigma_i$  that are on the diagonal of the matrix  $\Sigma$  are called the singular values of the matrix  $\mathbf{H}$ . [16]

The singular values on the diagonal of the matrix  $\Sigma$  can be either zero or non-zero. The number of non-zero singular values can be determined from the rank of the channel matrix H. When the channel retains a highly scattering environment, it is possible that H can achieve full rank. The other extreme would happen when the channel gains have very high correlation between each other. If the channel coefficients are highly correlated the rank of the channel matrix is one meaning that H has only one non-zero singular value. [16]

In fact, the number of non-zero diagonal elements, i.e. non-zero singular values, of the matrix  $\Sigma$  determine the maximum number of spatial streams. Since the rank of the channel matrix cannot exceed min  $(M_r, M_t)$ , the number of spatial streams is also limited by the number of antennas. Therefore, the number of spatial streams is determined by the size of the antenna configuration and the nature of the multipath channel. By conducting SVD on the channel matrix we were able to represent it as a diagonal matrix multiplied with two other matrices. This suggests that if the transmission could be precoded so that it sees the channel matrix as diagonal, it could be possible to receive independent symbols.

### 3.3 Single-User Beamforming

We have seen that by coherently combining the signals transmitted or received using multiple antennas provided array and diversity gains that enhanced the performance of the channel. The remaining topics in this chapter deal with increasing channel capacity in MIMO systems. In this section a beamforming technique called eigen-beamforming is discussed. When the eigenbeamforming is used to transmit a single spatial stream, it is evident that it has a lot in common

with the previously introduced spatial diversity techniques. If multiple spatial streams are used, eigen-beamforming has shown to be the optimal precoding strategy for single-user MIMO [20]. Both eigen-beamforming techniques using single and multiple spatial streams are introduced in this section.

In the case of single spatial stream both ends perform precoding and decoding on the transmitted and the received symbols. The transmitted symbol is precoded using the vector  $\mathbf{v}$  and the received symbol is decoded using vector  $\mathbf{u}$ , where  $|\mathbf{u}| = |\mathbf{v}| = 1$ . This results in a received signal: [20]

$$y = \mathbf{u}^{\mathrm{H}}\mathbf{H}\mathbf{v}x + \mathbf{u}^{\mathrm{H}}\mathbf{n} \tag{3.9}$$

It is shown in [20] that the channel can be seen as an AWGN SISO channel when this technique is used. Therefore, the channel capacity for single spatial stream case is given by: [20]

$$C = \log_2 \left( 1 + \frac{P_t}{\sigma^2} |\mathbf{u}^{\mathsf{H}} \mathbf{H} \mathbf{v}|^2 \right)$$

(3.10)

The vectors  $\mathbf{u}$  and  $\mathbf{v}$  should be chosen so that the signal-to-noise ratio is maximized. Furthermore, it is shown in [20] that the vectors  $\mathbf{u}$  and  $\mathbf{v}$  should be chosen as the first left and the first right singular vectors of the channel matrix  $\mathbf{H}$ . We saw in the context of spatial multiplexing that it was possible to identify the independent signalling paths using SVD. Eigen-beamforming-based transmission suggests that the path with the strongest gain should be used for the transmission. This technique can provide a  $\sigma_{max}^2$ -fold increase in SNR, where  $\sigma_{max}$  corresponds to the largest singular value of the channel matrix  $\mathbf{H}$  [16]. When the channel matrix is zero mean spatially white, the array gain, i.e. the increase in SNR is in the range between  $\max(M_t, M_r)$  and  $M_t M_r$  [16]. In contrast to the maximal-ratio combining where multiple antennas were deployed only on one side, SNR increased approximately with the numbers of antennas in the multiple antenna side. Under the above assumptions, eigen-beamforming using a single spatial stream can further improve the signal-to-noise ratio. Since this approach provided a better SNR, we achieved diversity and array gains. If we use eigen-beamforming utilizing several spatial streams, it is also possible to obtain multiplexing gains which can lead to even better capacity.

If multiple spatial streams are used, it is shown that the transmit precoding coefficients should be chosen as the right singular vectors of the channel matrix **H** [20]. This seems to suggest that all possible spatial streams should be used. In addition, if the receiver uses the left singular vectors for decoding the transmission, the channel model eventually simplifies and is written as: [20]

$$\mathbf{y} = \mathbf{\Sigma}\mathbf{x} + \mathbf{U}^{\mathrm{H}}\mathbf{n} \tag{3.11}$$

When reminding that  $\Sigma$  is a diagonal matrix whose number of non-zero elements is given by the rank of **H**, Equation (3.11) explicitly shows the independent nature of the spatial streams.

Channel capacity C for a system utilizing the eigen-beamforming with multiple spatial streams is given by [20]

$$C = \sum_{i=1}^{M} \log_2\left(1 + \frac{\lambda_i^2 P_i}{\sigma^2}\right),\tag{3.12}$$

where  $P_i$  is the transmit power of the *ith* stream and  $\lambda_i$  is the *ith* eigenvalue of  $\mathbf{H}\mathbf{H}^H$ . Earlier it was stated that the channel gain associated with the *ith* spatial stream was given by the *ith* singular value. Eigenvalues of  $\mathbf{H}\mathbf{H}^H$  are related to the singular values of  $\mathbf{H}$  as follows  $\sigma_i = \sqrt{\lambda_i}$  and are adopted due to practical reasons. [20]

From Equation (3.12) it can be seen that the capacity increases with respect to the number of spatial streams. In theory, if the gain of all spatial streams were one and their SNR were identical, Equation (3.12) would clearly correspond to the capacity of AWGN SISO channel given by Shannon's theorem (2.1) multiplied by the number of streams. Under these rather surrealistic assumptions, a multiplicative increase in the channel capacity would have been achieved without increasing the bandwidth. In reality, the channel gain is neither unity nor identical between the individual antenna elements. Therefore, the channel capacity is optimised by adjusting the transmit powers according to water-filling principle [20].

Overall it is clear that these methods offer significant increase in the channel capacity. However, the capacity is improved with the price of increased computation. Introduced beamforming techniques consists of computationally demanding operations such as matrix multiplications and decompositions. In order to meet the latency requirements, these features must be implemented as efficiently as possible. In this thesis we aim to ease the workload caused by the beamforming by investigating the properties of the mandatory channel estimation for beamforming and implementing it efficiently using a suitable architecture. This topic is discussed in the following chapters.

The computational efforts of beamforming can be further reduced by using limited feedback precoding, which consists of a codebook provided by the 3GPP specifications. This codebook is composed in order to reduce the computational load. The idea behind the codebook-based beamforming is to look up the parameters from the codebook instead of calculating them directly. [23]

#### 3.4 Multi-User Beamforming

Beamforming can also be applied in multi-user scenarios. The key difference between the multi-user and the single user beamforming is that all spatial streams are not addressed to the same user. Therefore, these undesirable signals must be considered in the precoding strategy [20].

In [24] it is shown that if the channel is subject to some additional interference and the distribution of the interference is known, using a proper precoding method it is possible to adapt the transmission to this interference. In addition, it has been shown that using this method the channel capacity would correspond to the capacity without the interference. This method is known as the dirty paper coding (DPC) and it has been suggested to be the theoretically optimal multi-user precoding strategy. However, it has been pointed out that this method is very hard to implement in reality which makes it impractical [20].

One popular multi-user beamforming technique is a linear precoding scheme called zero-forcing (ZF) beamforming. ZF has attracted attention due to its more feasibility. ZF is a computationally lighter option than DPC which does not lose too much relevant information. It is shown by Weasel *et.al* that ZF type of precoding is the optimal coding strategy under a total power constraint in MU-MIMO situation. Zero forcing precoding matrix  $\mathbf{W}_{\mathbf{Z}}$  under a total power constraint is given by [25]

$$\mathbf{W}_{\mathbf{Z}} = \mathbf{H}^{\mathbf{H}} (\mathbf{H} \mathbf{H}^{\mathbf{H}})^{-1}, \tag{3.13}$$

where,  $\mathbf{H} \in \mathbb{C}^{N \times M}$  is the channel matrix. M corresponds to the number of transmit antennas, N is the number of users and  $\mathbf{H}^H$  denotes the conjugate transpose of the channel matrix  $\mathbf{H}$ . ZF solution is said to transform the multiuser channel into the several independent subchannels which is done by finding the inverse channel of the given channel matrix  $\mathbf{H}$ . It is evident that the zero forcing method also relies heavily on the channel information. Multi-user beamforming is discussed in more detail in [20].

Beamforming techniques introduced in this chapter offered a method to improve the channel capacity via complex spatial signal processing tasks. As discussed earlier, this sets challenges towards the system design due to the strict latency requirements of the 5G network. This emphasizes the importance of the efficient implementation of these techniques. Naturally, it is very important to optimize the chosen beamforming technique itself like it was done with the eigenbeamforming. By using the eigenvalues of the channel covariance matrix instead of the singular values of the channel matrix additional computation is avoided and better efficiency is achieved [20].

#### 3.5 Summary

We found that the beamforming techniques presented in this chapter improved the channel capacity. However, these methods are computationally demanding and completely dependent on the channel matrix. By acquiring the channel coefficients that form the channel matrix efficiently, we can facilitate the attainment of the desired latency requirements on our part. This subject is addressed in the subsequent chapters.

### 4 CHANNEL ESTIMATION

We have seen that the multiantenna systems, especially MIMO systems can provide enhanced channel capacity via advanced beamforming schemes. However, these schemes were dependent on the channel matrix. Furthermore, since the multipath channel shifts the phase and scales the amplitude of the signal, in order to utilize high order modulations such as quadrature amplitude modulation (QAM), coherent detection of the signal also requires the channel parameters [26]. If the channel parameters were unknown, we would be limited to using differential modulation methods. This would significantly reduce the number of bits per symbol and decrease the signal-to-noise ratio [27]. In summary, channel state information also plays an important role in other parts of the system than beamforming. The parameters describing the channel are obtained from a process called channel estimation.

The channel between the UE and BS can change rapidly. Channel estimation should be performed within a short period of time in order to prevent the channel from becoming substantially different during the estimation. Because the estimation must be performed quickly and frequently, its efficient implementation is crucial. Recalling we are implementing a channel estimation algorithm for beamforming. The importance of the efficiency is emphasized by the fact that the estimation is part of an already computationally demanding entity. In this chapter we discuss channel estimation by getting to know its basics and presenting solutions to reduce complexity.

#### 4.1 Overview

In [28], channel estimation in OFDM systems is categorized into four different approaches: iterative channel estimation, parametric model-based estimation, channel frequency response based and estimation for MIMO-systems whereas frequency response-based estimation is referred as the traditional approach. In this chapter emphasis is on the latter two.

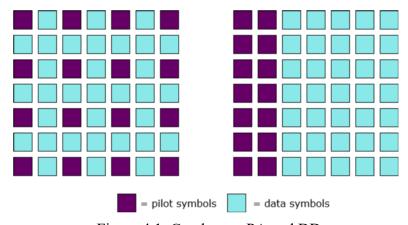

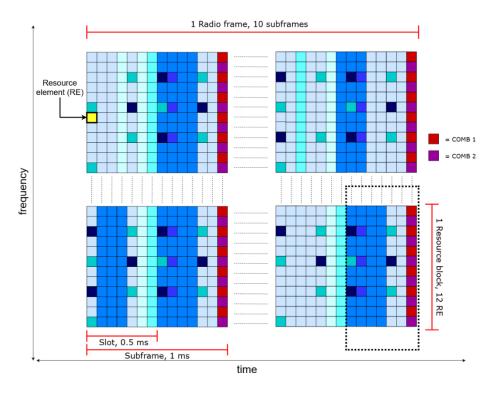

Channel frequency response-based channel estimation in OFDM is commonly further divided into two different categories. These categories are decision-directed estimation and pilot-assisted estimation. The graphical distinction between these schemes is provided in Figure 4.1 [28]. In the decision-directed approach the whole bandwidth is loaded with training symbols and they are utilized for the detection of subsequent data symbol. In pilot-assisted method, the pilot signals are inserted in either comb-type or block-type and the frequency responses on different data symbols can be obtained using different interpolation techniques [28].

Figure 4.1. Comb-type PA and DD.

Commonly, channel estimation methods assume a system model based on the time-varying channel impulse response introduced in the second chapter. When the general assumptions of the OFDM system are considered, the received signal at the kth subcarrier of the nth symbol  $Y_{n,k}$  is obtained from the channel frequency response as follows

$$Y_{n,k} = H_{n,k} X_{n,k} + W_{n,k}, (4.1)$$

where  $X_{n,k}$  denote the transmitted symbol e.g. pilot symbol and  $W_{n,k}$  stands for the additive Gaussian noise with zero mean.  $H_{n,k}$  is the corresponding channel frequency response. [28]

# 4.2 Channel Estimation in Single Antenna Systems

Since the received signal is corrupted by the noise and distorted by the time variant multipath channel, the acquisition of channel parameters is done by estimating them. A frequently encountered estimation approach is known as the least squares (LS) method. In LS, the goal is to find the parameters that minimizes the squared error of  $|\mathbf{A}\bar{\mathbf{x}} - \mathbf{b}|^2$ , where  $\mathbf{A}$  is  $N \times M$  matrix,  $\bar{\mathbf{x}}$  and  $\mathbf{b}$  are vectors of size  $M \times 1$  and  $N \times M$ , respectively. Least squares method is used to find an approximate solution to the systems that are overdetermined. This means that there are N equations, M unknowns and N > M. The solution is found to be a vector  $\bar{x}_{LS}$  for which  $\mathbf{A}\bar{x}_{LS}$  is the orthogonal projection of the vector  $\mathbf{b}$ . The general solution for the linear least squares is given by [23]:

$$\chi_{LS} = (\mathbf{A}^{\mathrm{H}}\mathbf{A})^{-1}\mathbf{A}^{\mathrm{H}}\mathbf{b} \tag{4.2}$$

The least squares approach is used especially when no statistical information regarding the channel is available, or it is ignored due to some other reason. When Equation (4.1) is presented in a vector form, the task to minimize the squared distance between **Y** and **XH** for the *nth* symbol is given by

$$\widehat{\mathbf{H}}_{LS} = \arg\min_{\{\mathbf{H}\}} |\mathbf{Y} - \mathbf{X}\mathbf{H}|^2, \tag{4.3}$$

where **H** and **Y** are the vectors containing the channel frequency responses and the received signals and are given as follows

$$\mathbf{Y} = [Y_0, Y_1, ..., Y_{K-1}]^T,$$

$\mathbf{H} = [H_0, H_1, ..., H_{K-1}]^T,$

where K denote the number of subcarriers. The transmitted signal  $\mathbf{X}$  is a  $K \times K$  diagonal matrix, where the transmitted symbols  $X_k$  lie on the diagonal according to their subscript. [28] In this situation the least squares estimate is given simply as [27]:

$$\widehat{\mathbf{H}}_{LS} = \mathbf{X}^{-1}\mathbf{Y} \tag{4.4}$$

The least squares estimate given by Equation (4.4) corresponds to the temporal estimate over one OFDM symbol. It is often pointed out in the papers that when the noise is additive white Gaussian noise, Equation (4.4) is equivalent to the maximum-likelihood estimation [28]. Although matrix inversion is considered a computationally demanding operation, in Equation (4.4) it is not a problem. Since **X** is a diagonal matrix its inversion only requires the inversion of the diagonal elements. Computationally, least squares-based approach in single antenna OFDM systems seems intriguing method since it only corresponds to elementwise multiplication of complex vectors.

In addition to least squares estimation, minimum mean square estimation i.e. MMSE, was also considered in [27]. Computationally, MMSE differs significantly from the LS estimate. MMSE assumes that the statistical distribution of the frequency responses is known, and it aims to minimize the error of the expected value of the squared error. MMSE estimate can be calculated as follows

$$\widehat{\mathbf{H}}_{LMMSE} = \mathbf{R}_H \left( \mathbf{R}_H + \frac{1}{\gamma} \mathbf{I} \right)^{-1} \widehat{\mathbf{H}}_{LS}, \tag{4.5}$$

where  $\mathbf{R}_H = E(\mathbf{H}\mathbf{H}^H)$  denote for the channel correlation matrix, and  $\gamma$  stands for SNR. In the equation for MMSE estimator a matrix inversion is required, which significantly increases the computational complexity of the method compared to LS. However, it is expected that the increased computational complexity would provide more accurate estimates. [28]

It is possible to reduce the significant gap in the computational complexity between LS and MMSE methods. Modified LS and MMSE estimators were suggested in [27]. These modifications exploited the properties of the channel impulse response. It was noticed that high energy channel taps were found from the first elements of the impulse response. Therefore, it was suggested that in order to reduce the complexity of MMSE estimator, it was decided to exclude the low energy taps from the estimation and rely on the information given by the taps with the higher energy. Additionally, they applied this exact same method to LS estimator structure even it was not necessary from the computational complexity point of view.

Since it was noticed that the first channel taps tend to have a bigger impact due to their relatively higher energy content, it is intuitively beneficial to exclude the lower energy taps from the LS calculation. Since the noise spectrum of AWGN is considered flat over the whole frequency range, by ignoring the low energy taps, presence of the noise could potentially be reduced. [27]

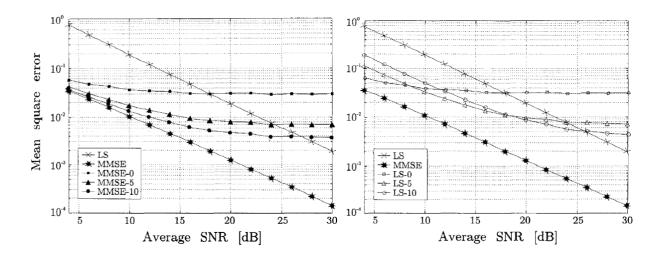

Transmission reliability results for the modified and conventional LS and MMSE estimators in a system using 16-QAM modulation are provided in Figure 4.2 [27]. Especially the modified LS estimator gained much better results in the low SNR region. However, this was achieved with at the expense of computational complexity, since after the exclusion of the non-significant channel taps, the method no longer corresponds to the simple form given in Equation (4.4).

Figure 4.2. Comparison of channel estimation schemes. © [1995] IEEE

According to the discussion above, channel estimation seems to be possible with very low complexity. The least squares estimate given in (3.4) would be a very pleasing method for efficient implementation since it involves only a highly parallelisable multiplication. Although the above results favour complex methods in terms of transmission reliability, the situation is a bit different for beamforming.

In [20] it is pointed out that whether the channel covariance matrix is calculated using a channel matrix with exact values versus one with a slightly erroneous values, the effect on the system performance should be negligible. However, it should be noted that the errors caused by the channel aging are considered harmful [20]. Channel estimation should be performed very frequently so that the aging does not cause problems. Since small inaccuracies are not considered harmful, a low complexity method would provide a good starting point for the efficient implementation of channel estimation. The conventional least squares method offered an incredibly simple estimation scheme. However, beamforming requires a MIMO system. This raises the question whether this simple method could also be utilized in the MIMO systems?

# 4.3 Estimation in Multiantenna Systems

The previous section introduced the basics of channel estimation in single antenna OFDM systems. It was noticed that it is possible to obtain reasonable estimates using the linear least squares method which offered very low complexity. Since our interest in channel estimation arose from the beamforming techniques, in this chapter, channel estimation in MIMO systems is discussed. At first, by providing a basic picture of the problem, a sort of general approach for the channel estimation in multiantenna system is introduced. In addition to this, we discuss techniques that aim to reduce the complexity of channel estimation.

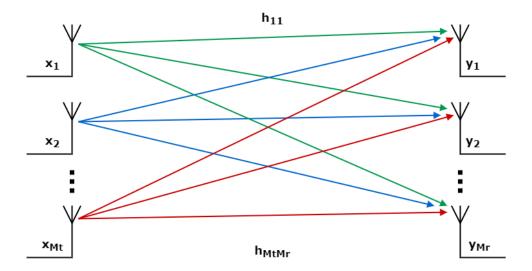

A narrowband MIMO system is illustrated in Figure 4.3 [16]. There are  $M_t$  transmit antennas,  $M_r$  receive antennas and the corresponding channel coefficient  $h_{tr}$  for the each transmit and receive antenna pairs. This model is often represented using the Equations (3.6) and (3.7) from the previous chapter.

Figure 4.3. Narrowband MIMO system.

The situation has changed quite a bit compared to the conventional single antenna system. If the received symbol  $Y_{n,k}^j$  at the *jth* receive antenna is observed, it seems to be a superposition of the transmitted signals from all transmit antennas and it is given by: [28]

$$Y_{n,k}^{j} = \sum_{i=1}^{M_t} H_{n,k}^{j,i} X_{n,k}^{i} + W_{n,k}^{j}$$

(4.6)

Since the received signal is now exposed to several channel parameters, the LS method cannot be directly utilized as in the previous section. A straightforward solution would be to perform the channel estimation individually for every transmit antenna by keeping all but one antenna silent. Then during the training period  $M_t = 1$  and Equation (4.6) would correspond to the single antenna case in (4.1). This simple solution does not sound promising since it would make the estimation very slow and reduce the spectral efficiency. Clearly the estimation should be performed on all antennas at the same time. [28]

A sort of basic approach for MIMO-OFDM channel estimation is described in [29]. As shown in Equation (4.6), the received symbol at the *jth* receive antenna can be expressed using the channel frequency response. The channel frequency response for the *ith* transmit antenna at the *kth* subcarrier of the *nth* symbol can be obtained by taking the discrete Fourier transform (DFT) from the channel impulse response as follows [29]

$$H_i[n,k] = \sum_{l=0}^{L-1} h_i[n,l] W_K^{kl}, \tag{4.7}$$

where L denotes the number of non-zero channel taps and  $W_K = e^{-j\left(\frac{2\pi}{K}\right)}$ . Therefore, the task is to find  $h_i$ 's which minimize the following function: [29]

$$\sum_{k=0}^{K-1} \left| Y_{n,k}^{j} - \sum_{i=0}^{N_t} \sum_{l=0}^{L-1} X_{n,k}^{i} h_{n,l}^{j,i} e^{-j\left(\frac{2\pi k l}{K}\right)} \right|$$

(4.8)

Direct calculation using the above expression will require an inversion of matrix of size  $M_t L \times M_t L$  [29]. So, by formulating the problem directly for the MIMO system, the computational complexity appears to be considerable.

Similarly, as with the single antenna systems a method that would ignore the small energy channel taps was suggested for this method as well. This would naturally reduce the size of the matrix, but as the matrix inversion is still required, the complexity is still very high. [28] The complexity of the method can be significantly reduced by careful pilot sequence design. It is shown in [26] that with proper pilot sequence the complexity of the scheme is significantly reduced. It is possible to select a pilot sequence so that the matrix to be inverted is reduced to a diagonal matrix which is much more feasible to work with.

The least squares estimate of channel matrix **H** for a narrowband MIMO system can be obtained as follows [23]

$$\widehat{\mathbf{H}}_{LS} = \mathbf{Y}\mathbf{X}^{\mathrm{H}}(\mathbf{X}\mathbf{X}^{\mathrm{H}})^{-1},\tag{4.9}$$

where **X** is an  $M_t \times N_{tr}$  and **Y** is an  $M_r \times N_{tr}$  matrix.  $N_{tr}$  is the length of the training sequence. Calculating the LS estimate directly from Equation (4.9) would be very cumbersome due to matrix inversion. If the transmitted pilot sequences are chosen to be orthogonal to each other, the product between the training symbol matrix and its Hermitian becomes  $\mathbf{XX}^H = N_{tr}\mathbf{I}$  where **I** is identity matrix of size  $M_r \times N_{tr}$ . Once again, by avoiding the matrix inversion the complexity of the estimation scheme reduced significantly. [23] As a result, the matrix inversion only corresponds to a division by the length of the pilot sequence and (4.9) is reduced to

$$\widehat{\mathbf{H}}_{LS} = \frac{1}{N_{tr}} \mathbf{Y} \mathbf{X}^{\mathrm{H}},\tag{4.10}$$

which is a matrix multiplication problem.

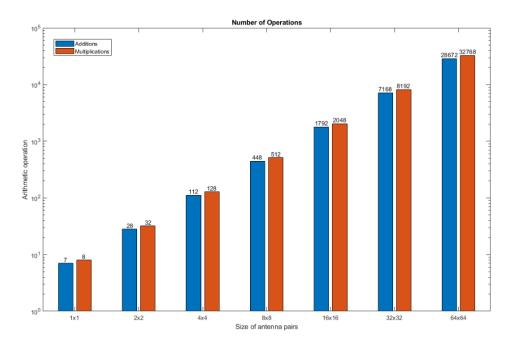

So far, we have seen a few techniques to facilitate the channel estimation in MIMO systems. Although orthogonal pilot sequences reduced the complexity of the channel estimation, one challenge has been ignored. The size of the matrices given in (4.10) are dependent of the size of the antenna configuration. Since it is expected that the number of antenna elements keeps growing in the future, this sets a prominent challenge towards the implementation. If Equation (4.10) is approached as a traditional matrix multiplication it can be broken down into two operations, multiplications and additions of complex numbers. It seems that calculating  $\mathbf{YX}^{H}$  requires  $N_t N_r N_{Tr}$  complex multiplications and  $N_t N_r (N_{Tr} - 1)$  complex additions. Furthermore, a complex multiplication would require four real multiplication with two real additions.

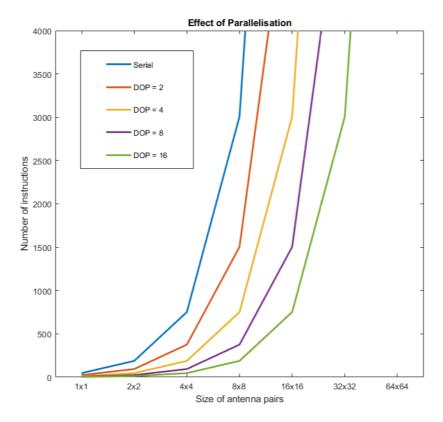

The number of required operations for different antenna configurations is illustrated in Figure 4.4. Although the number of pilot symbols used in this illustration is relatively small, it is clear when the size of the antenna pair doubles, the number of operations quadruples. While graphically, the number of operations seems to increase linearly, it should be noted that the scale is logarithmic, thus the number of operations increases exponentially. Although the result

is not surprising, it causes significant challenges towards the signal processing platforms because both the channel estimation and the beamforming depend on the size of the antenna configuration.

Figure 4.4. Number of operations with respect to antenna elements on logarithmic scale.

There are matrix multiplication algorithms which promise to reduce the computational complexity compared to the conventional approaches. For example, the Strassen's algorithm provides a reduction in the total number of multiplications compared to the conventional method. Strassen's algorithm alongside the other published matrix multiplication algorithms are usually considered useful for very large matrices. Naturally, the practicality of all advanced matrix multiplication algorithms depends on the platform on which they are implemented. For example, the elementary steps in the Strassen's algorithm require very much specific indexing operations. Therefore, fitting it to some specific system architecture can be very challenging and the reduced number of multiplications does not directly translate into better performance.

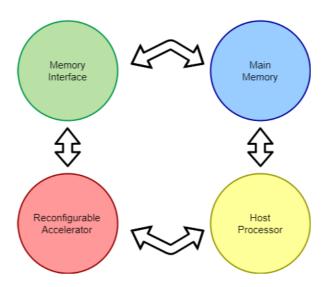

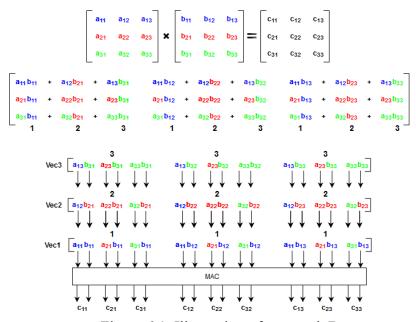

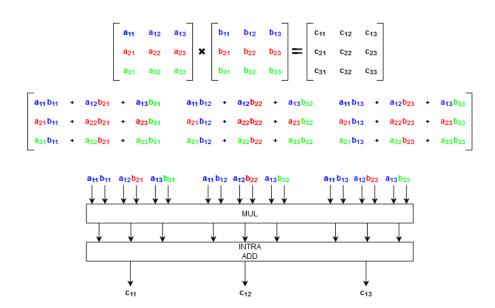

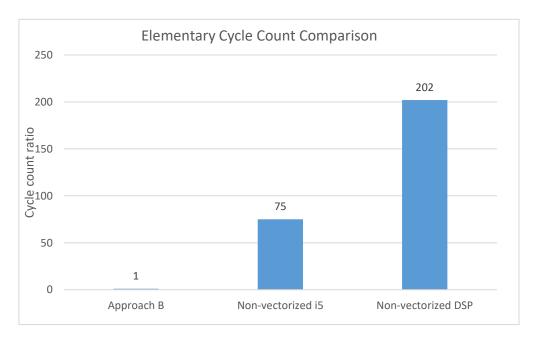

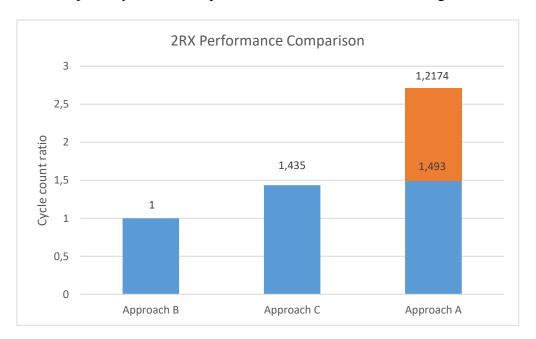

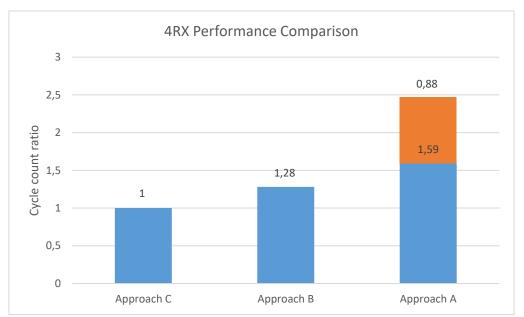

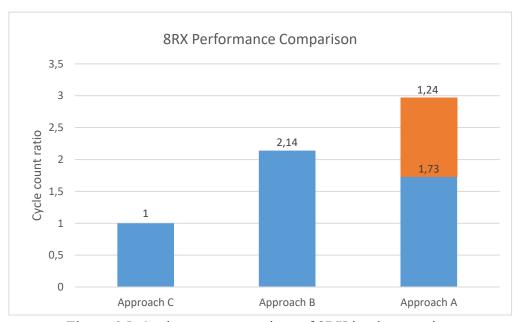

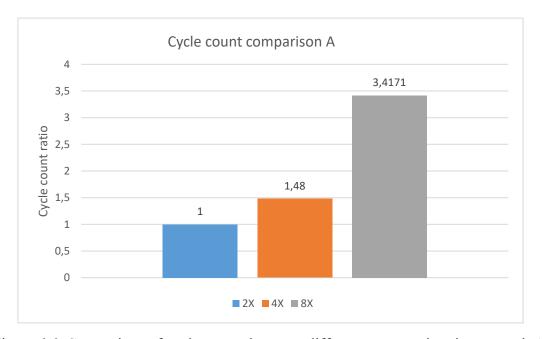

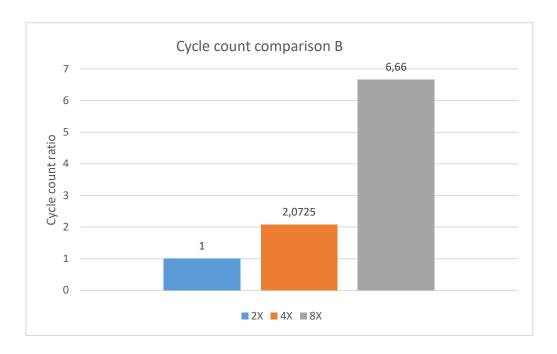

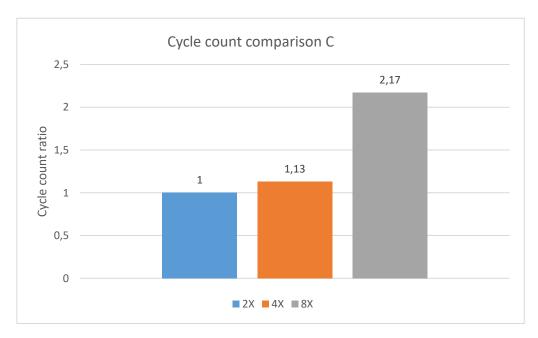

However, a very straightforward way to increase the efficiency of the estimation is to use a parallel architecture. Already an assumption was made that the complex arithmetic operations were considered as a single operation. This is a totally valid assumption when the algorithm is implemented using an architecture which offers complex arithmetic operations as elementary instructions.