# Université de Sherbrooke

Faculté de génie

Département de Génie Électrique et de Génie Informatique

Par

#### Bilal Hassan

### Modélisation distribuée et évolutive du GaN HEMT

Membres du Jury: **Professeur M. François Boone** (Directeur de thèse)

Université de Sherbrooke

Professeur M. Hassan Maher (Co-directeur de thèse)

Université de Sherbrooke

Professeur M. Ali Soltani

IEMN, Université de Lille

Professeur M. Serge Charlebois

Université de Sherbrooke

Docteur M. Rémy Leblanc

OMMIC, France

### Résumé

Mots-clés: GaN, HEMT, modélisation évolutive, résistance de grille distribuée

L'industrie de télécommunication et les satellites se base majoritairement sur les technologies Si et GaAs. La demande croissante des hauts débits de données entraine une facture élevée en énergie. En outre, la saturation de la bande des basses fréquences, le besoin des débits élevés et les exigences de la haute puissance imposait l'utilisation de la bande hautes fréquences. Dans le but de résoudre les problèmes cités auparavant, la technologie GaN est introduite comme un candidat prometteur qui peut offrir de la haute puissance, taille du circuit plus faible avec une meilleure stabilité mécanique aux environnements hostiles/milieux agressifs. À titre d'exemple, l'agence spatiale européenne sont en cours de développement d'un circuit à base du GaN sur substrat en Si pour faible cout, une hautes performance et une grande fiabilité.

La technologie GaN est assez mature pour proposer de nouveaux systèmes intégrés utilisés pour les puissances microonde ce qui permet une réduction considérable de la taille du système. Étant un semiconducteur à grande bande interdite, GaN peut offrir une haute puissance sous hautes températures (>225°C) avec une bonne stabilité mécanique. Elle présente un facteur de bruit faible, qui est intéressant notamment pour les circuits intégrés aux ondes millimétriques. À noter que la mobilité du GaN par rapport à la température est assez élevée pour proposer des amplificateurs dans la bande W.

Avec le progrès du procédé de fabrication du GaN, notre objectif est l'introduction de cette technologie dans des applications industrielles. À cette fin, on désire avoir un modèle du dispositif qui correspond à la meilleure performance. Ensuite, on veut le valider dans une modélisation du circuit. Cette thèse, basée sur la technologie GaN unique développée au 3IT, a pour objectif l'amélioration de l'outil de conception en réduisant son erreur avec une validation de son utilisation dans la conception du circuit. Ce travail est réalisé pour la première fois au 3IT avec des résultats de simulation pour une conception idéale d'un circuit MMIC ainsi que sa démonstration.

Une caractérisation des échantillons a été réalisée avec objectif d'extraction de données qui vont servir à l'alimentation de modélisation des transistors sur l'outil ADS. Une fois complétée, la modélisation a été validée par une modélisation des petits et grands signaux et a été testée par une mesure load-pull. Enfin, ce modèle a été utilisé lors de la conception d'un amplificateur pour les applications RF.

L'innovation de ce travail réside dans la modélisation de la résistance d'une grille large sous forme de quadripôles parallèles à structure 3D (ou à résistances de grille distribuées) du transistor MOSHEMT GaN. La conception et la fabrication de l'amplificateur à haute puissance (HPA) aux fréquences microondes (≤4GHz) sont réalisés au LNN du 3IT et inclus une couche d'oxyde de grille afin de réduire le courant de fuite notamment pour les tensions Vgs élevées, la grille du transistor forme un serpentin pour fournir une puissance de sortie élevée avec un encombrement spatial minimal et une grille présentant une électrode de champ pour permettre d'augmenter la tension de claquage.

### **Abstract**

**Keywords:** GaN, HEMT, Scalable modeling, distributed gate resistance

The telecommunication and satellite industry is mainly relying on Si and GaAs technologies as the demand for a high data rate is continuously growing, leading to higher power consumption. Moreover, the lower frequency band's saturation, the need for high data rate, and high-power force to utilize the high-frequency band. In pursuit of solving the issues mentioned earlier, GaN technology has been introduced as a promising candidate that can offer high power at a smaller circuit footprint and higher mechanical stability in harsh environments. For example, currently, the European space agency (ESA) is developing an integrated circuit with GaN on Si substrate for low cost, high performance, and high reliability.

GaN technology is sufficiently mature to propose integrated new systems which are needed for microwave power range. This technology reduces the size of the system considerably. GaN is a wide bandgap semiconductor which can offer remarkably high power at high temperature (> 225°C), and it is very stable mechanically. It presents a low noise factor, very interesting for a millimeter-wave integrated circuit. Finally, the mobility of GaN vs. temperature is sufficiently elevated to propose a power amplifier in W-Band.

With the improvement of the GaN process, our objective is to introduce this technology for industrial applications. For this purpose, we wish to have a better model of the device that corresponds to the best performance and then validate it by using this model in a circuit. Based on the 3IT's GaN process, which is unique in its context, this thesis aims to improve the design kit by reducing the design model's error and validating it by using it in circuit design. This work is the first to realize in 3IT with simulation results to design an MMIC circuit for demonstration.

I first characterized the new samples by performing different measurements than using these measurement data; transistor is modeled in ADS software. Once the model was completed, it is validated by small-signal modeling, and then the large-signal model is tested with non-linear capacitances, current source, and transconductance modeling. Finally, we used this model to design a power amplifier for RF application.

The innovation comes from modeling large gate resistance as distributed gate resistance for GaN MOSHEMT transistor and then designing high-power amplifier (HPA) in the frequency range ( $\leq$  4GHz) while using 3IT GaN process which includes first oxide layer to have low gate current and more voltage of V<sub>gs</sub>, the second transistor is meander to have high power and third, field plate - gate for high breakdown voltage.

## **Acknowledgments**

This thesis was carried out within the Microelectronics group III-V, directed by Professor Hassan MAHER and Professor François Boone from the Nanofabrication and Nano characterization (LNN), Sherbrooke, Quebec, Canada.

I express my deepest gratitude to Professor François Boone for having me under his supervision, the supervision's quality, and allowing me to benefit from the 3IT infrastructure to develop and enhance my skills. I am very grateful to him for his timely support, availability despite being very busy, the time he devoted to me, and the financial means he gave me during all of this work. I express my deepest gratitude to Professor Hassan MAHER for sharing his expertise with me and the confidence he placed in me in doing this work, and his help during research work.

My sincere thanks go to Professor Ali Soltani for his help and accepted the responsibility of evaluating this work in the rapporteur's capacity and that to Professor Serge Charlebois and Director Rémy Leblanc from OMMIC for being part of the Jury to evaluate my thesis.

I would like to sincerely thank the following people whose journeys have crossed the mine and helped me carry out this work and participated in my training. My office colleagues and friends: Adrien Cutivet to help me out at the beginning of my thesis, Christophe Rodriguez, Meriem Bouchilaoun, and Flavien Cozette for their help with transistors fabrication also thanks to Hassane Ouazzani Chahdi, Mohamed Najah, and Quentin Vandier for their help with PCB; and the entire characterization support team at 3IT: Pierre Langlois, Denis Pellé and Charles Bourcier Guérette; thanks to Soundoss Maher, Abderrahim El Amrani, Amanpreet Singh, Muhammad Sohail, Sabahat Ali Khan, Hasrat Ali, Nawzish, and Mustafa Bhai for their guidance and support.

I also want to thank my parents here for their permanent support and especially my brothers; with their help, I reach this far in life and be able to visit and experience the wonderful multicultural world.

# **Table of Contents**

| Rés  | sumé     |       |                                                                              | ا ا    |

|------|----------|-------|------------------------------------------------------------------------------|--------|

| Abs  | stract   |       |                                                                              | ا      |

| Acł  | know     | ledgr | nents                                                                        | III    |

| Tak  | ole of   | Cont  | tents                                                                        | 1      |

| List | t of A   | bbre  | viations and Acronyms                                                        | VII    |

| List | t of Fi  | gure  | s                                                                            | VIII   |

| List | t of Ta  | ables |                                                                              | XII    |

| Cha  | apter    | 1: In | troduction                                                                   | 1-1    |

| 1    | l.1      | Bac   | kground                                                                      | 1-1    |

| 1    | L.2      | Mai   | n Objectives of the research work                                            | 1-3    |

| 1    | L.3      | Out   | line of the thesis                                                           | 1-4    |

| Cha  | apter    | 2: W  | /hy GaN                                                                      | 2-5    |

| 2    | 2.1<br>5 | Con   | nparison based on the material's physical properties and electrical paramete | ers 2- |

|      | 2.1.     | 1     | Comparison based on material's physical properties                           | 2-5    |

|      | 2.1.     | 2     | Comparison based on electrical parameters                                    | 2-7    |

|      | 2.1.     | 3     | Comparison based on power and frequency application                          | 2-7    |

|      | 2.1.     | 4     | Comparison based on performance and Cost                                     | 2-8    |

|      | 2.1.     | 5     | Comparison based on analysis as part of a full product                       | 2-11   |

| 2    | 2.2      | Арр   | lications of GaN technology:                                                 | 2-12   |

| Cha  | apter    | 3: St | ate-of-the-art                                                               | 3-13   |

| 3    | 3.1      | Phy   | sical structure and operation of AlGaN/GaN HEMTs                             | 3-13   |

| 3    | 3.2      | Stat  | e-of-the-art GaN technology                                                  | 3-15   |

|      | 3.2.     | 1     | Our process:                                                                 | 3-17   |

|      | 3.2.     | 2     | The principle of GaN HEMT Operation                                          | 3-18   |

| 3   | .3          | Mod   | deling challenges of GaN HEMTs                                                      | 3-19  |

|-----|-------------|-------|-------------------------------------------------------------------------------------|-------|

|     | 3.3.        | 1     | HEMT compact models                                                                 | 3-20  |

|     | 3.3.        | 2     | Transistor equivalent model                                                         | 3-21  |

|     | 3.3.        | 3     | Small-signal modeling                                                               | 3-25  |

|     | 3.3.        | 4     | Large signal modeling                                                               | 3-38  |

| Cha | pter        | 4: In | troduction to distributive gate resistance                                          | 4–42  |

| F   | ésun        | né    |                                                                                     | 4–43  |

| 4   | .1          | Abs   | tract                                                                               | 4–44  |

| 4   | .2          | Intr  | oduction                                                                            | 4–44  |

| 4   | .3          | Den   | nonstration and extraction procedure                                                | 4–46  |

|     | 4.3.        | 1     | Assumptions and demonstration                                                       | 4–46  |

|     | 4.3.        | 2     | Two-port common-source case                                                         | 4–48  |

| 4   | .4          | Extr  | action procedure                                                                    | 4–49  |

| 4   | .5          | Ехр   | erimental results                                                                   | 4–49  |

|     | 4.5.        | 1     | Devices under test                                                                  | 4–49  |

|     | 4.5.        | 2     | Results and discussion                                                              | 4-50  |

| 4   | .6          | Con   | clusion                                                                             | 4-53  |

| 4   | .7          | Ack   | nowledgments                                                                        | 4-53  |

| Cha | pter        | 5: Sc | calable small-signal modeling                                                       | 5-54  |

| F   | ésun        | né    |                                                                                     | 5-55  |

| 5   | .1          | Abs   | tract                                                                               | 5-56  |

| 5   | .2          | Intr  | oduction                                                                            | 5-56  |

| 5   | .3          | Des   | cription and extraction procedure                                                   | 5-57  |

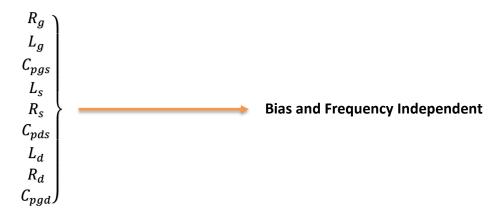

|     | 5.3.<br>(W) |       | Parameter description and relation with bias voltage, frequency, and gate v<br>5-57 | vidth |

|     | 5.3.        | 2     | Devices under test                                                                  | 5-58  |

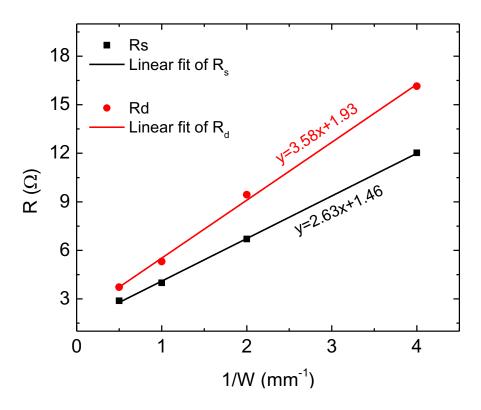

|     | 5.3.        | 3     | Extrinsic parameter extraction                                                      | 5-59  |

| 5.3       | .4      | Intrinsic parameter extraction                  | 5-60          |

|-----------|---------|-------------------------------------------------|---------------|

| 5.4       | Res     | sults and discussions5                          | 5-61          |

| 5.5       | Cor     | nclusion5                                       | 5-65          |

| 5.6       | Ack     | knowledgment5                                   | 5-65          |

| Chapter   | r 6: La | arge Signal Model Validation6                   | 5-66          |

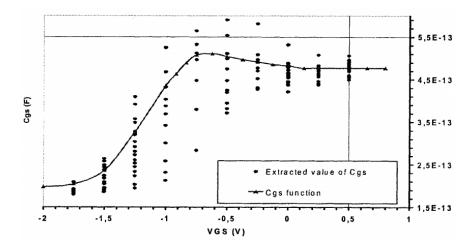

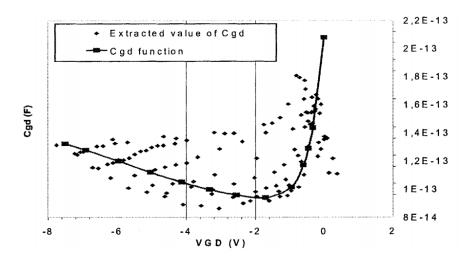

| 6.1       | Noi     | n-linear Capacitance modeling6                  | 5-66          |

| 6.2       | Tra     | nsient self-heating and Drain current modeling6 | 5-67          |

| 6.3       | Мо      | odel Convergence6                               | 5- <b>7</b> 1 |

| 6.4       | Circ    | cuit level model validation6                    | 5- <b>7</b> 1 |

| 6.4       | .1      | Simulation and layout of the HPA design         | ō-72          |

| Conclus   | sion a  | and Future Work                                 | 77            |

| Conclus   | ion e   | et perspectives                                 | 78            |

| List of P | ublic   | cation                                          | 79            |

| Referen   | ice     |                                                 | 81            |

# **List of Abbreviations and Acronyms**

AlGaN Aluminum Gallium Nitride

AlN Aluminum Nitride

InAlN Indium Aluminum Nitride

NSERC Natural Sciences and Engineering Research Council of Canada

GaN Gallium Nitride

GaAs Gallium Arsenide

Si Silicon

SiC Silicon Carbide

SiGe Silicon Germanium

InP Indium Phosphide

IGBT Insulated-gate bipolar transistor

FET Field-effect transistor

HEMTs High electron mobility transistors

MMICs Monolithic microwave integrated circuits

RF Radio Frequency

3IT Institut interdisciplinaire d'innovation technologique

LDMOS Laterally diffused metal oxide semiconductor

MESFET Metal-semiconductor field-effect transistor

MOSHEMT Metal-oxide-semiconductor high electron mobility transistor

MOCVD Metalorganic chemical vapor deposition

ADS Advance design system

DGRM Distributed gate resistance model

SSM Small-signal modeling

SSSM Scalable small-signal modeling

# **List of Figures**

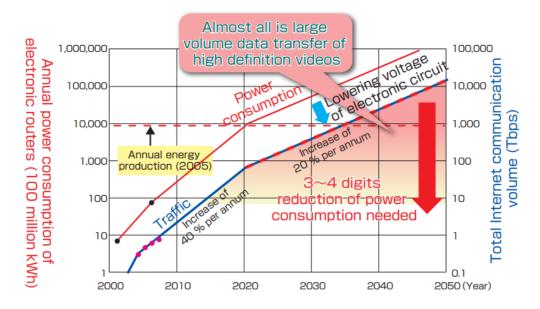

| Figure 1-1: The Internet communication volume vs. power consumption of the routers 1                                                                                            | [2]. 1-     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

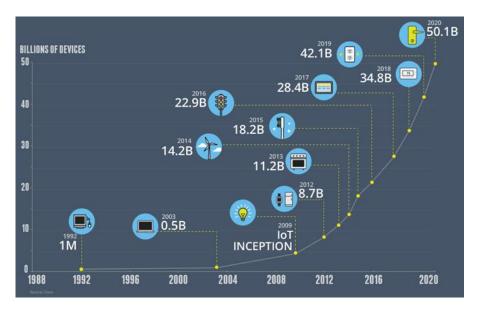

| Figure 1-2: Growth in the Internet of things [4]                                                                                                                                | 1-2         |

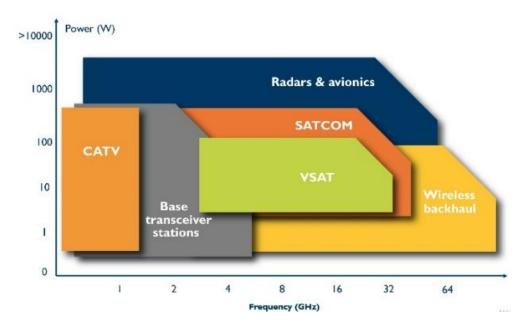

| Figure 1-3: Available market for GaN-related products [5] such as CATV (Community Al<br>Televisions), VSAT(Very Small Aperture Terminal), and SATCOM(Satellite Communic<br>etc. | cation),    |

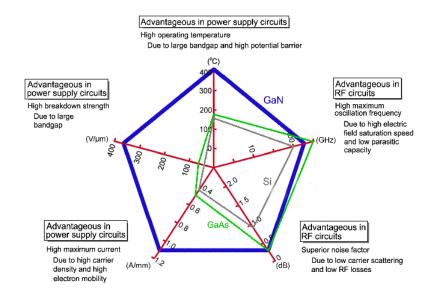

| Figure 2-1: Advantages of GaN in RF and Power supply circuits over GaAs and Si [10]                                                                                             | 2-6         |

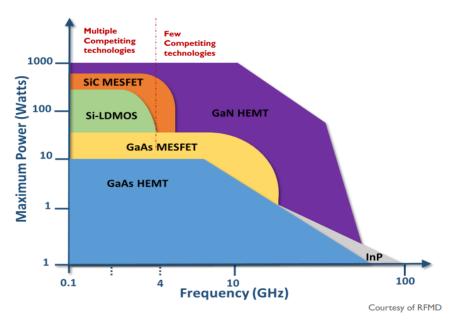

| Figure 2-2: Power and frequency region for different semiconductors [13]                                                                                                        | 2-8         |

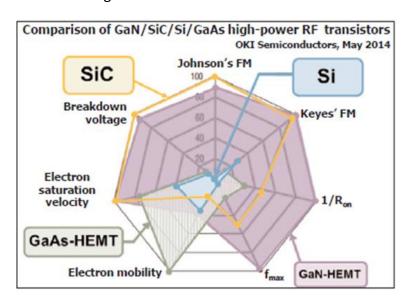

| Figure 2-3: Comparison of GaN/SiC/Si/GaAs high-power RF transistors [24]                                                                                                        | <b>2</b> -9 |

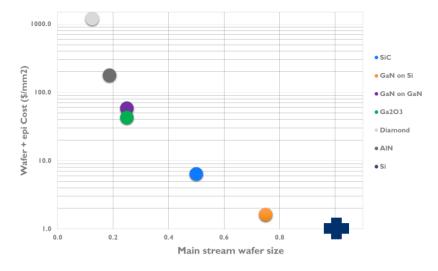

| Figure 2-4: WBG material cost and wafer size comparison [25]                                                                                                                    | 2-10        |

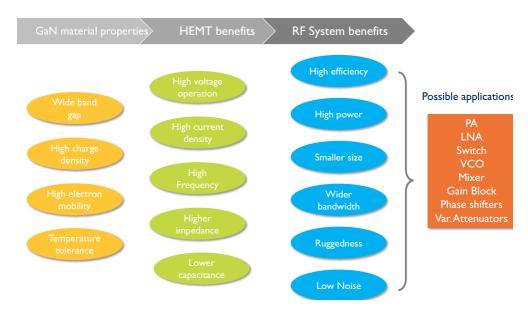

| Figure 2-5: GaN's added values at system level [27]                                                                                                                             | 2-11        |

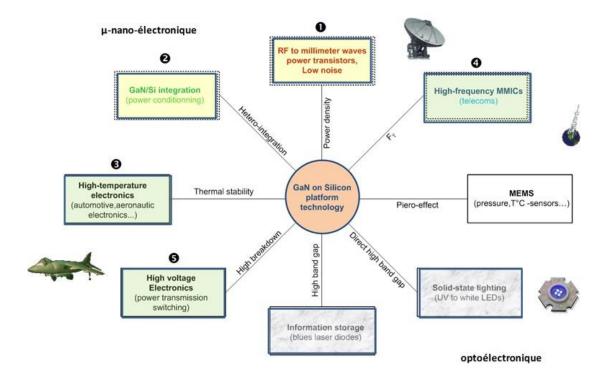

| Figure 2-6: Applications of GaN on Si                                                                                                                                           | 2-12        |

| Figure 2-7: Applications of GaN devices in RF Electronics Systems                                                                                                               | 2-12        |

| Figure 3-1: Typical HEMT structure [29]                                                                                                                                         | 3-13        |

| Figure 3-2: State of the art of GaN HEMT technology on Si and SiC (Power density in satuas a function frequency) [30]–[39], [41]–[49]                                           |             |

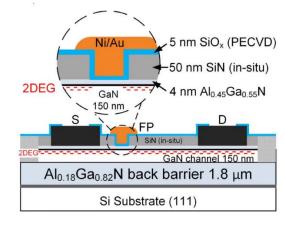

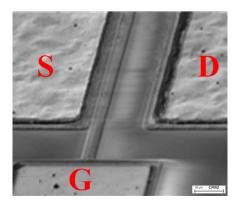

| Figure 3-3: Schematic of the fabricated MOSHEMT [50], [51]                                                                                                                      | 3-18        |

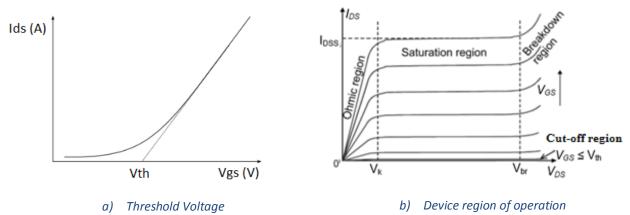

| Figure 3-4: Determine threshold voltage and region of operation of the device                                                                                                   | 3-19        |

| Figure 3-5: Type of large-signal models [52]                                                                                                                                    | 3-20        |

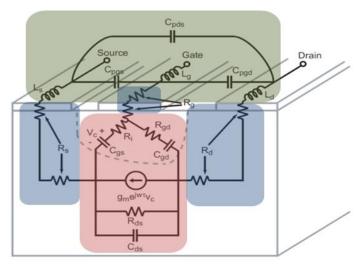

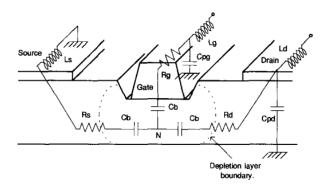

| Figure 3-6: AlGaN/GaN HEMT equivalent model in relation to the geometrical structu                                                                                              |             |

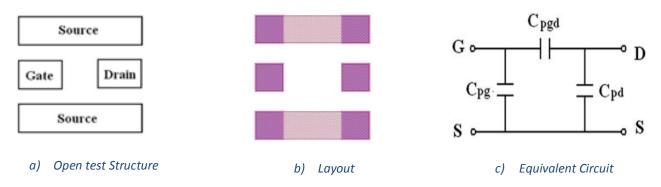

| Figure 3-7: Extraction of Parasitic capacitance [63]                                                                                                                            | 3-26        |

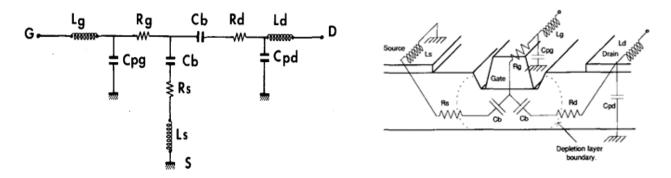

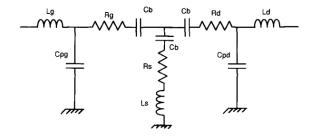

| Figure 3-8: Improved equivalent circuit for pinched-off FET at $V_{ds}$ = 0 [70]                                                                                                | 3-27        |

| Figure 3-9: Schematic cross-section of MESFET at V <sub>ds</sub> = 0 showing the physical or elements [70]                                                                      |             |

| Figure 3-10: The equivalent circuit model of the open test structure                                                                                                            | 3-28        |

| Figure 3-11: Short test structure and an equivalent model                                                                                                                       | 3-29        |

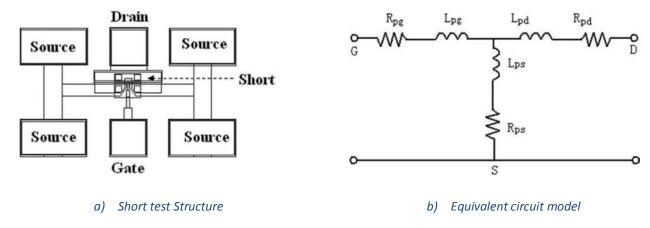

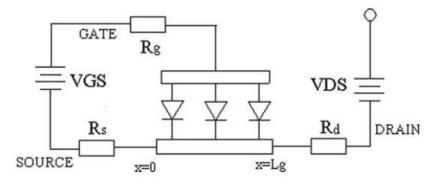

| Figure 3-12: The schematic for source resistance measurement representing distributed channel, $R_d$ and $R_s$ for measuring $I_g(V_{ds})$ and $I_g(V_{gs})$ [75]                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-13: Schottky diode model for FET with a floating drain or source [75] 3-31                                                                                                                                                                                                                                  |

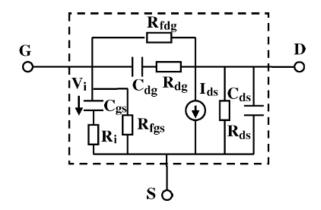

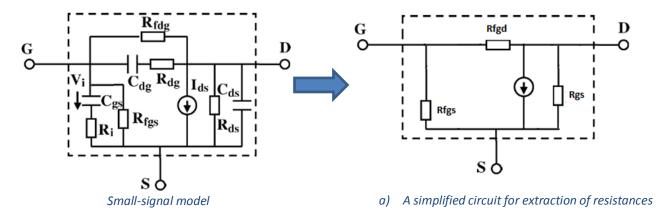

| Figure 3-14: Intrinsic part of the proposed 18-element small-signal model [72] 3-32                                                                                                                                                                                                                                  |

| Figure 3-15: Intrinsic structure and an equivalent model                                                                                                                                                                                                                                                             |

| Figure 3-16: Classical Small-Signal Model                                                                                                                                                                                                                                                                            |

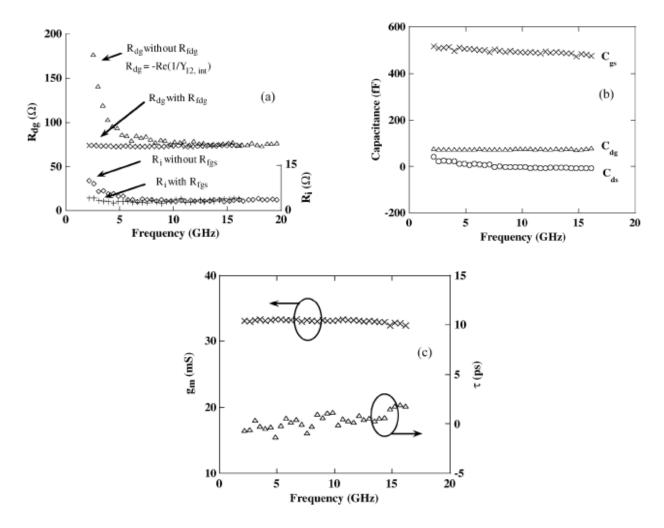

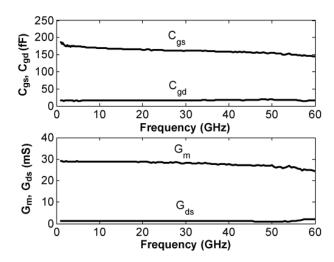

| Figure 3-17: Optimized intrinsic elements from the data measured at $V_{DS}$ = 4 V, $V_{GS}$ = -3 V, and frequencies from 2 to 20 GHz. (a) $R_i$ and $R_{dg}$ , with and without the differential resistances $R_{fdg}$ and $R_{fgs}$ considered. (b) $C_{dg}$ , $C_{gs}$ , and $C_{ds}$ . (c) $g_m$ and $\tau$ [72] |

| Figure 3-18: Extracted intrinsic capacitances and conductances versus frequency, at $V = 1:0 \text{ V}$ and $V = 10:0 \text{ V}$ , for a 0.5 um GaN HEMT with a 250 um gatewidth [72]                                                                                                                                |

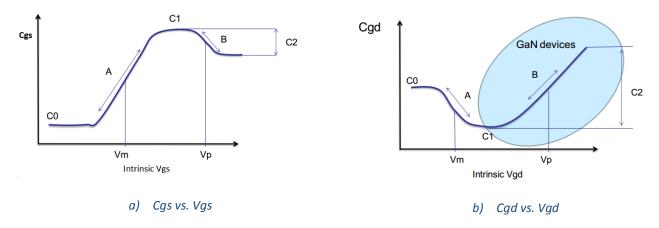

| Figure 3-19: General behavior of non-linear capacitances vs. voltages                                                                                                                                                                                                                                                |

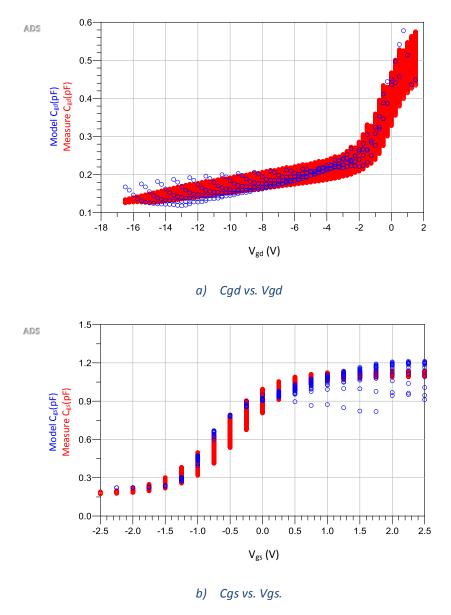

| Figure 3-20: Comparison of non-linear Capacitances [91] (a) $C_{gd}$ vs. $V_{gd}$ and (b) $C_{gs}$ vs. $V_{gs}$ .3–40                                                                                                                                                                                                |

| Figure 3-21: 3D representation of AlGaN/GaN HEMT structure and the proposed new large-signal electrical model                                                                                                                                                                                                        |

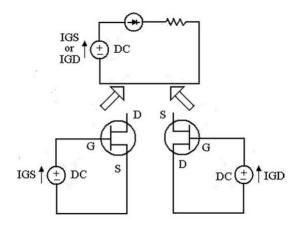

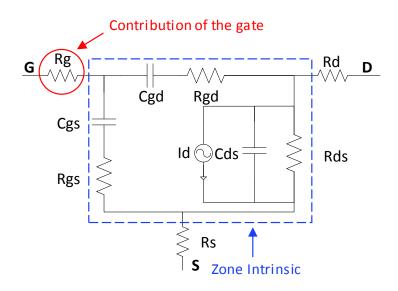

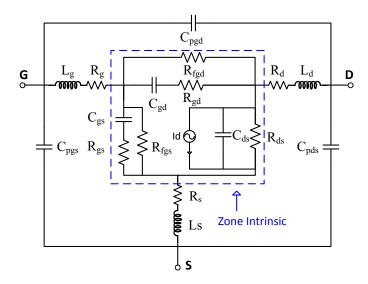

| Figure 4-1: Classic small-signal model                                                                                                                                                                                                                                                                               |

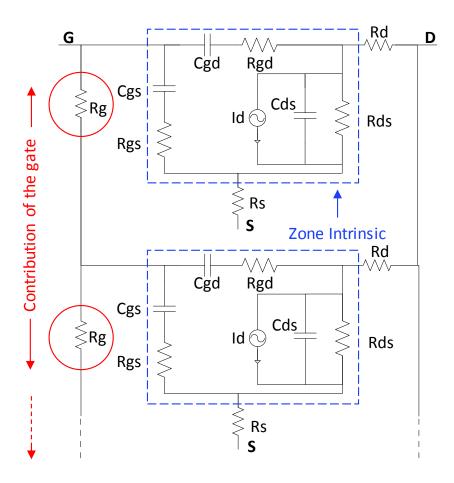

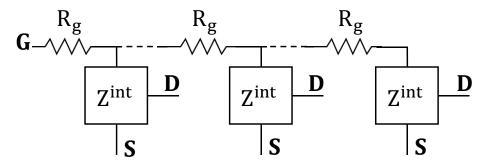

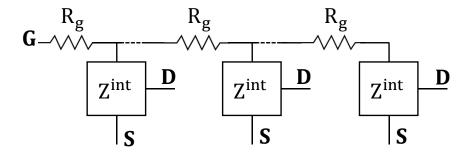

| Figure 4-2: A proposed approach for distributed gate resistance4–46                                                                                                                                                                                                                                                  |

| Figure 4-3: Three-ports equivalent schematics of a one-finger transistor with the considered assumptions                                                                                                                                                                                                             |

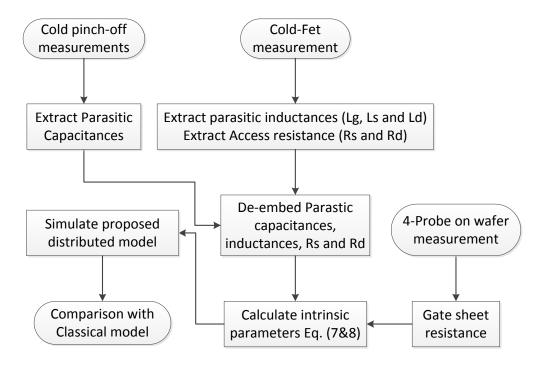

| Figure 4-4: Flowchart of the distributed model's extraction procedure4–49                                                                                                                                                                                                                                            |

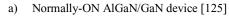

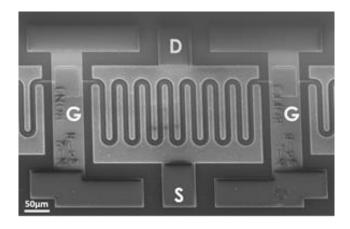

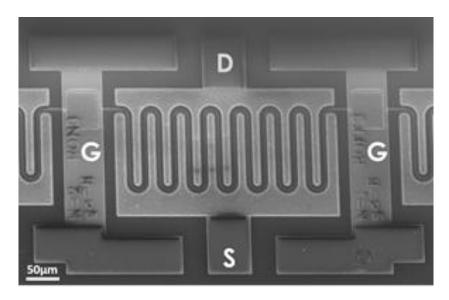

| Figure 4-5: Schematic and SEM image of the fabricated MOSHEMT device 4-50                                                                                                                                                                                                                                            |

| Figure 4-6: Current gain H <sub>21</sub> (dB) vs. frequency (GHz) for a measured, classic, and distributed model with W=2mm                                                                                                                                                                                          |

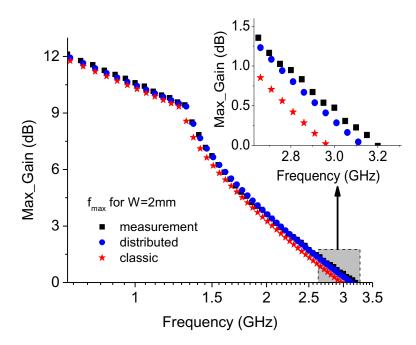

| Figure 4-7: Maximum gain (dB) vs. frequency (GHz) for a measured, classic, and distributed model with W=2mm. 4-52                                                                                                                                                                                                    |

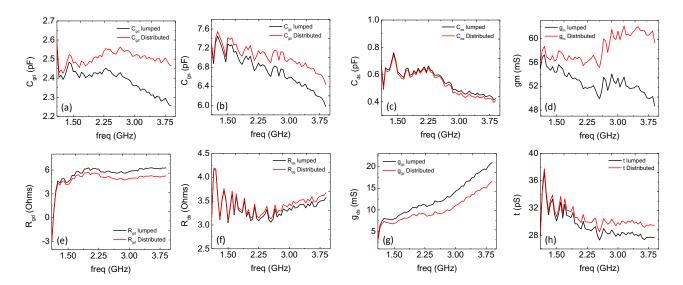

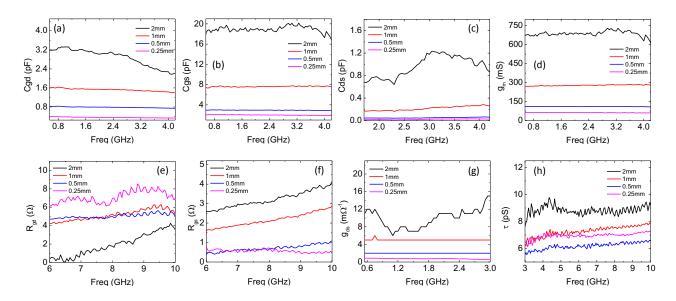

| Figure 4-8: Comparison between classical model (black) and distributed model (red) for extraction of all intrinsic parameters $C_{gd}$ (a), $C_{gs}$ (b), $C_{ds}$ (c), $g_m$ (d), $R_{gd}$ (e), $R_{ds}$ (f), $g_{ds}$ (g) and t (h) for W=2mm. 4-52                                                                |

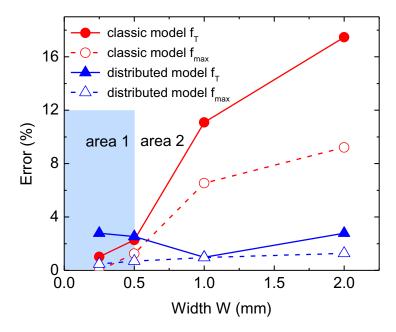

| Figure 4-9: Error (%) vs. width W (mm) between the classic and distributed model for $f_T$ and $f_{max}$                                                                                                                                                                                                             |

| Figure 5-1: Small signal equivalent model for AlGaN/GaN HEMT 5-57                                                                                                                                                                                                                                                    |

| Figure 5-2: Distributive gate equivalent schematics of a one-finger transistor with the considered assumptions                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-3: SEM image of two fingers fabricated MOSHEMT, W=2mm with $L_{\text{gd}}$ =6 $\mu$ m and $L_{\text{sd}}$ =9 $\mu$ m                                                                                                                          |

| Figure 5-4: Resistances (R <sub>s</sub> and R <sub>d</sub> ) vs. 1/W for scaling                                                                                                                                                                       |

| Figure 5-5: Behavior of all extracted intrinsic parameters $C_{gd}(a)$ , $C_{gs}(b)$ , $C_{ds}(c)$ , $g_m(d)$ , $R_{gd}(e)$ , $R_{ds}(f)$ , $g_{ds}(g)$ and $\tau(h)$ vs. the frequency for W=0.25, 0.5, 1 and 2mm at $V_{gs}$ =2.5V and $V_{ds}$ =16V |

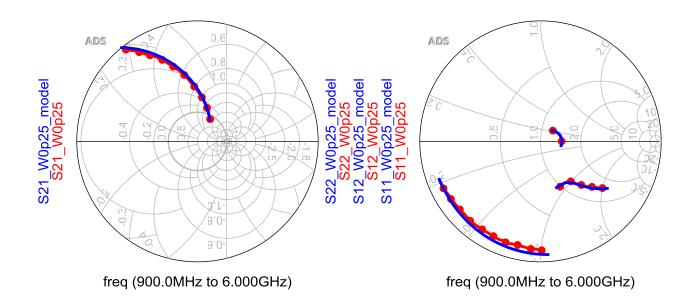

| Figure 5-6: Comparison between measured and modeled S-parameters ( $S_{11}$ , $S_{12}$ , $S_{21}$ , and $S_{22}$ ) for W=0.25mm at $V_{gs}$ =2.5V and $V_{ds}$ =16V                                                                                    |

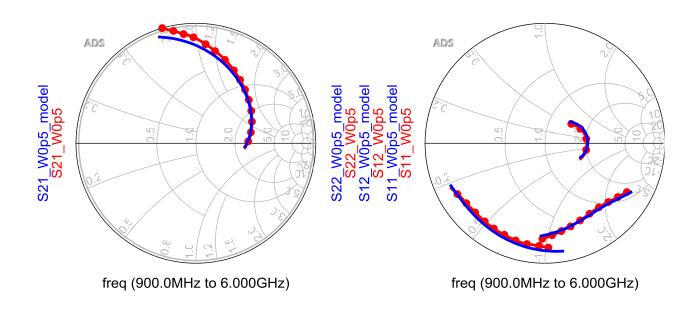

| Figure 5-7: Comparison between measured and modeled S-parameters ( $S_{11}$ , $S_{12}$ , $S_{21}$ , and $S_{22}$ ) for W=0.5mm at $V_{gs}$ =2.5V and $V_{ds}$ =16V                                                                                     |

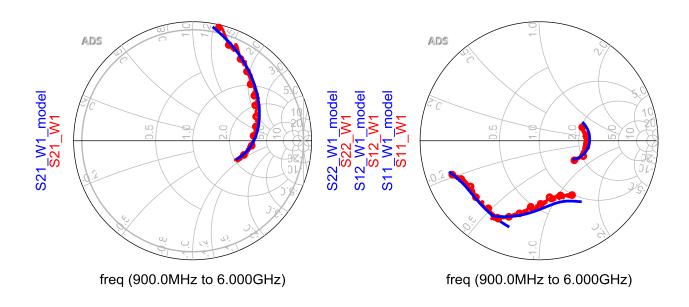

| Figure 5-8: Comparison between measured and modeled S-parameters ( $S_{11}$ , $S_{12}$ , $S_{21}$ , and $S_{22}$ ) for W=1mm at $V_{gs}$ =2.5V and $V_{ds}$ =16V                                                                                       |

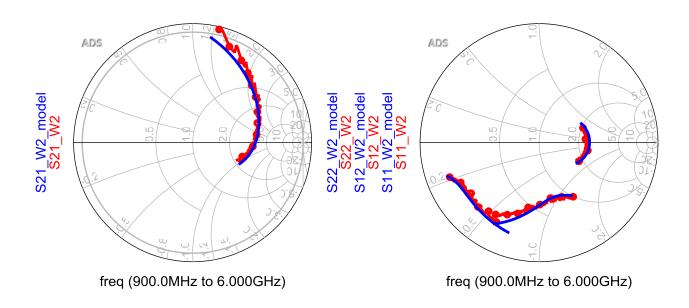

| Figure 5-9: Comparison between measured and modeled S-parameters ( $S_{11}$ , $S_{12}$ , $S_{21}$ , and $S_{22}$ ) for W=2mm at $V_{gs}$ =2.5V and $V_{ds}$ =16V                                                                                       |

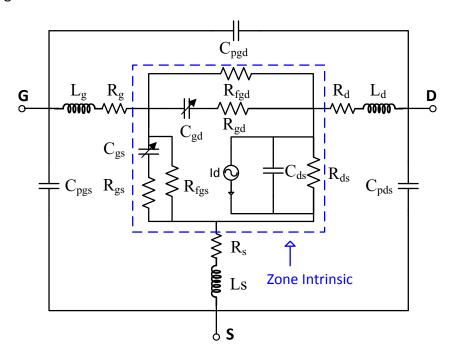

| Figure 6-1: Equivalent electrical model for AlGaN/GaN MOSHEMT with non-linear capacitances and current source                                                                                                                                          |

| Figure 6-2: Comparison of non-linear capacitances (C <sub>gs</sub> and C <sub>gd</sub> ) between measured and modeled                                                                                                                                  |

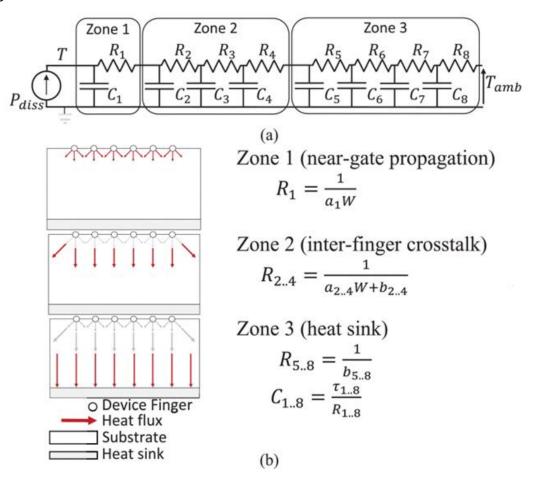

| Figure 6-3: (a) Equivalent thermal model based on an eight-order Cauer topology and subdivided into three zones. (b) Representation of the three-time periods of the heat flux propagation corresponding to the three zones of the model               |

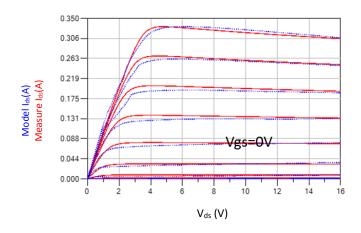

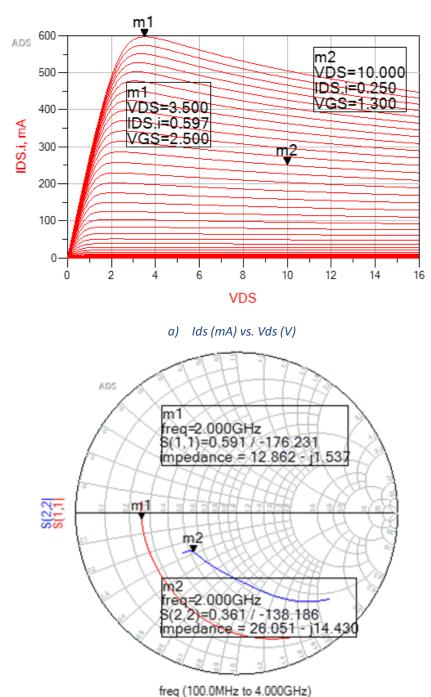

| Figure 6-4: Comparison between measurement and mod $I_d(A)$ vs. $V_{ds}(V)$ for different $V_{gs}(V)$ .6-68                                                                                                                                            |

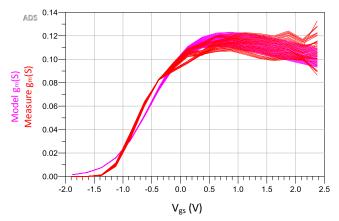

| Figure 6-5: Comparison between measured and modeled for Transconductance(S) vs. V <sub>gs</sub> (V)                                                                                                                                                    |

| Figure 6-6: Comparison between measurement and model Transconductance(S) vs. $V_{gs}(V)$ at specific $V_{ds}(V)$                                                                                                                                       |

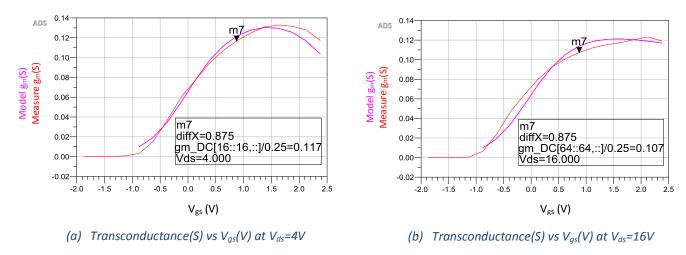

| Figure 6-7: Comparison between Curtice, Statz, and Angelov model for current source $I_{ds}(A)$ vs. $V_{ds}(V)$ and transconductance (S) vs. $V_{gs}(V)$ . The dotted lines are fitting curves, while solid lines are from the measurement             |

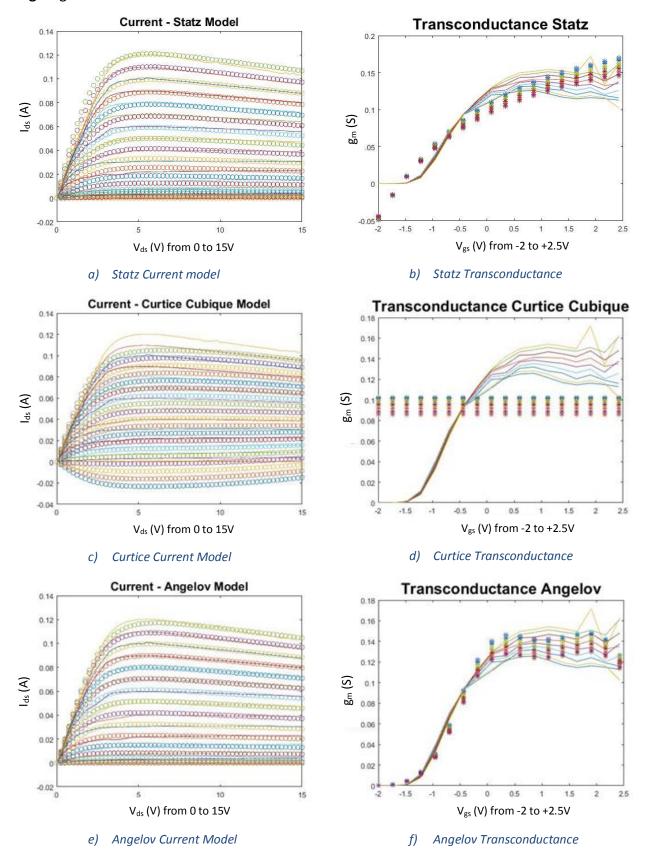

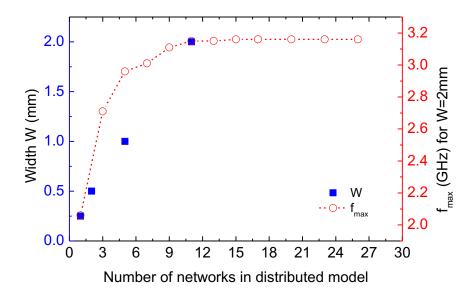

| Figure 6-8 A number of distributed network vs. widths (0.25, 0.5, 1, and 2mm) of the transistors and f <sub>max</sub> for large gate width 2mm                                                                                                         |

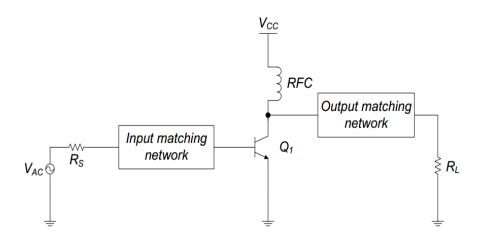

| Figure 6-9: Single-ended topology for a power amplifier 6-72                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------|

| Figure 6-10: $I_{ds}$ (mA) vs. $V_{ds}$ (V) plot for 2mm width gate transistor from -2.5V to +2.5V73                             |

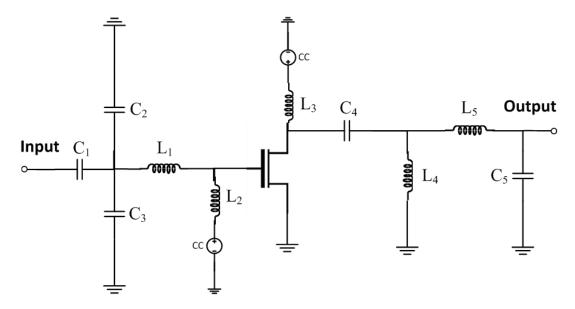

| Figure 6-11: Schematic of the PA with lumped components74                                                                        |

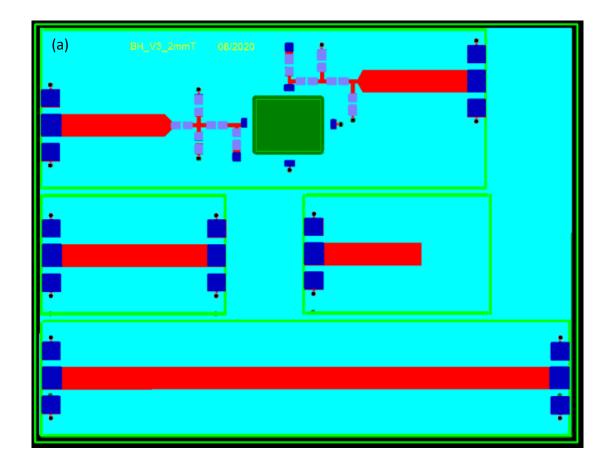

| Figure 6-12: The amplifier final a) Layout and de-embedding network (Dimensions of board are 30mm×23mm). b) Hardware prototype75 |

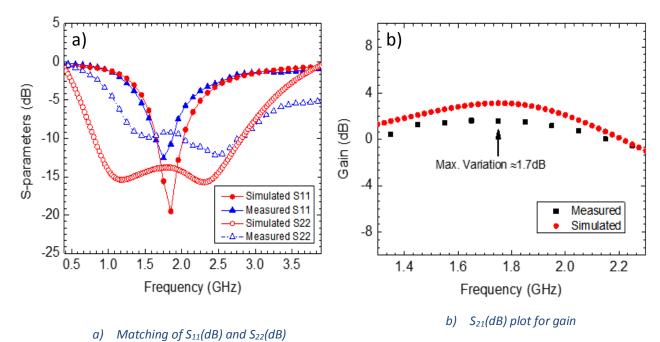

| Figure 6-13: Impedance matching represented for (a) $S_{11}$ and $S_{22}$ from 0.1GHz-4GHz and (b $S_{21}$ from 1.6GHz- 2.1GHz76 |

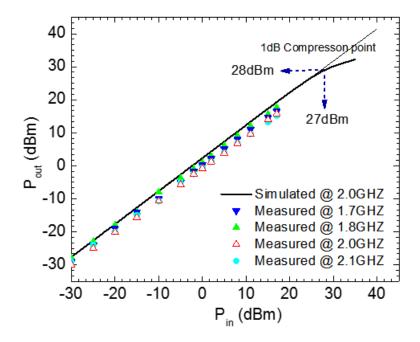

| Figure 6-14: Shows the simulated vs. measured P <sub>out</sub> vs. P <sub>in</sub> (dBm)76                                       |

# **List of Tables**

| Table 2-1: Material characteristic comparison between GaN and competitors [7]–[9] 2-6             |

|---------------------------------------------------------------------------------------------------|

| Table 2-2: Comparision of typical electrical figures of several semiconductor technologies [6]2-7 |

| Table 2-3: Manufacturing Cost and Capabilities for Different Technologies [6] 2-10                |

| Table 3-1: Comparison between different substrates available for GaN technology 3-14              |

| Table 3-2: State-of-the-art for GaN-on-SiC at different frequencies                               |

| Table 3-3: State-of-the-art for GaN on Si (111) at different frequencies 3-16                     |

| Table 3-4: State-of-the-art for GaN on Si (100) and Si (110) at different frequencies 3-16        |

| Table 3-5: Comparison of five main models [53]                                                    |

| Table 3-6: Physical description of extrinsic components                                           |

| Table 3-7: Physical description of intrinsic components                                           |

| Table 3-8: Pad Capacitances extracted by Dambrine, White and Open Test method 3-28                |

| Table 4-1: FT and fmax for measured, classic, and distributed model with different widths. 4-51   |

| Table 5-1 Small signal parameters vs. bias vol., frequency and gate width 5-59                    |

| Table 5-2 Extracted pad capacitances and inductances values                                       |

| Table 5-3 Error between measured and Simulated S-parameters vs. widths 5-62                       |

| Table 6-1: Comparison of different topologies of the Power Amplifier 6-72                         |

# **Chapter 1: Introduction**

#### 1.1 Background

The telecommunication industry is growing day by day, and the demand of the end-user for more data rate transfer and receive with high speed is increasing rapidly. The demand for more data is expected to increase in the next ten years by 2020. Each user needs about ten simultaneously connections of a mobile network because of the proliferation of electronic devices in our daily lives, which will need gigabytes per second data rate by the network providers [1]. Second, future technology or network has to be more intelligent and efficient with respect to its energy consumption and cost. For example, the Japan energy consumption of the IP routers will increase exponentially from less than 1TWh to about 100TWh between 2000-2020 and goes above 100,000TWh (100,000,000 million kWh) in 2050. Meanwhile, the date rate shows a similar behavior from 0.1Tbs to about 80Tbs till 2020. It will rise to above 10,000 Tbps in 2050 [2], as shown in Figure 1-1.

Figure 1-1: The Internet communication volume vs. power consumption of the routers [2].

Approximately 20% increase in traffic each year requires 3 to 4 digit power reduction. As a result, we need devices for RF application which can handle high power with minimum consumption & losses and provide high data rate also reduce the latency (time between transmitting and receiving data ) from currently 40ms-60ms to 1ms-10ms to enable the 5G technology. It is not possible by the existing network technology to handle such big data. As a result, we cannot afford such a power consumption by the existing devices, requiring continuous technological research to improve the system's transmission/reception chain.

Above estimated amount of power, the increase can be justified with another estimate growth in the internet of things per year given in Figure 1-2. It shows an estimation of about a 50% increase between 2017 and 2019, and devices number could reach 50.1 billion in total. That means we need a smaller size high power device with better power efficiency.

Another problem we are facing due to an increase in the data demand is that we need more equipment to handle massive power, so the equipment and power consumption are increasing. Besides that, the lower band of frequencies is becoming saturated, leaving us no option besides going to the high-frequency band. The telecommunication and satellite industry has been mainly on silicon and GaAs technology. However, now it is looking for a technology that can provide high power at high frequency, lead to a small size of the circuit, work at high temperature, have a high level of hardness and mechanical stability. For all the above demands, GaN technology is the solution [3].

Figure 1-2: Growth in the Internet of things [4]

RF Subsystem architectures are used in all radio communication and Radar products. RF tests, measurement equipment, and scientific instrumentation also make use of RF subsystems. In any subsystem, we are always constrained by the dynamic range of signal powers that can be processed and the power consumed to do the processing. The dynamic range is limited by the thermal noise on the weak signal end and by the subsystem linearity or voltage/current swing on the strong signal end. The power consumption constraint manifests itself as either a power efficiency or a thermal dissipation limit.

A wide bandgap semiconductor GaN HEMT process has advanced subsystem performance by providing a relatively low noise process with higher drain voltage swings than Si, GaAs, or SiGe. GaN devices also have better thermal conductivity and can support much higher channel temperatures than other processes.

Historically GaN HEMTS devices are being used for higher frequency band applications due to its ability to deliver high power at those frequencies. The available market for GaN-related products for different applications based on different power and frequency is given in Figure 1-3.

Satellite technology is proliferating and has a wide area of applications, increasing every day, such as broadband internet, satellite-HDTV, live video, telemedicine, interactive gaming, and video conferencing. It is also used for astronomy, weather forecasting, broadcasting, mapping, and many more applications.

To transmit the signal at the base station, it requires very high power. Currently, LDMOS or GaAs PA are being used for such an application. Still, GaN, due to its ability to deliver high power even at high temperatures, makes it as a potential competitor for the application in L-band (1-2GHz) and S-band (2-4GHz) of frequency.

3IT GaN process is available at a lower frequency (1-4GHz). However, most GaN devices development work today are focused on higher frequencies >15 GHz and higher powers >50W so it is interesting to look at amplification by improving medium power linearity (Less transconductance variation with RF Power) to have a high dynamic range and low noise amplifier devices in this band of frequency. Those characteristics are especially important for military, space, high-reliability applications, which are required an amplitude limiter to protect the receiver chain. Any efforts to research and develop GaN devices, which can enable the higher dynamic range performance (even at lower frequencies), will be well received by device manufacturers and their customers.

Figure 1-3: Available market for GaN-related products [5] such as CATV (Community Antenna Televisions), VSAT(Very Small Aperture Terminal), and SATCOM(Satellite Communication), etc.

To take the benefits and advantages mentioned above, we need an accurate description of the High-Electron-Mobility-Transistor (HEMT) in the form of a reliable and accurate large-signal model, which requires a small-signal model to develop it. Hence, a precise and stable small-signal model is critical to design an MMIC and optimize the circuits fabrication process. The focus of this thesis is to model AlGaN/GaN HEMT transistor with large gate width for S-Band frequencies application.

### 1.2 Main Objectives of the research work

The thesis's main objective is to improve the transistor model to better design power amplifiers operating in the device's saturation region for frequency until 4GHz and improve both linearity and efficiency. The research question is to improve the gate resistance model to have a better transistor model for PA design based on the hypothesis that as gate length increases, the classical model does not give accurate fit and is not adopted for equivalent circuits.

Typically, the assertions are:

- The intrinsic region is the same all along with the gate

- The gate resistance "seen" close to the gate contact pad is null while it is equal to  $R_g^{tot}$  at the finger edge

The currently available model of GaN HEMT transistor for RF application is for smaller gate width. However, as we increase the gate width, the traditional models are no longer valid because gate resistance is not fully included; that's what we have studied in this thesis.

#### 1.3 Outline of the thesis

Chapter 1 introduces the reader to the research field, provides a guideline to the thesis's general problem, and gives a clear picture of the research work's objectives.

Chapter 2 gives the background of GaN in detail and shows its importance compared to other technologies based on five different parameters: material physical properties, electrical parameters, power and frequency application, performance and cost, and analysis as a full product (system level), indicating it's application.

Chapter 3 is about state-of-art. It provides information about the structure of AlGaN/GaN HEMT, state-of-art GaN HEMT process, process information, detailing every step involved in modeling from extrinsic to intrinsic components, and non-linear components modeling.

Chapter 4 describes the distributed gate resistance model, model development, and extraction procedure and compares the classical model with a distributed model.

Chapter 5 Provides scalability of the distributed gate resistance model from extrinsic to intrinsic lever such scalability of the access resistances and intrinsic parameters, then validation of it by Sparameters comparison.

Chapter 6 shows model validation at the transistor for large-signal modeling and a circuit-level with a PCB based power amplifier design. In the end, the conclusions of this thesis are presented and an outlook of future work.

# Chapter 2: Why GaN

Microelectronics industries are encouraged and motivated to develop a market-oriented technological process to fulfill the end-user requirement (low cost, small size devices) and meet the industry's demand for an integrated circuit based on a lesser level complexity, better performance, and low cost. The competition among companies in the semiconductor industry is tough, and they are fighting each day to protect and expand their business to gain more market shares. For example, when it comes to implementing the radio frequency integrated circuits, microwave monolithic integrated circuits (MMIC), a system in package (SiP) or system on chip (SoC), whatever the circuits or system type are low cost, high performance, and high integration are vital parameters which each designer pay attention and for which companies always try to compete.

For doing analyses between GaN vs. other technologies, including Si and III-V technologies, it is essential to see their properties, characterizations, advantages, and limitations for comparison at material physical properties level, performance level, and analyzing them a full product. Each level of comparison provides us information for specific requirements or goals. Still, it's hard to judge which technology is better unless we make a comparison based on a specific application. However, we need to pay attention that only some semiconductor material is far better than others in physical material properties. Still, there are not mature in technology or other getting mature in technology. Still, there is no industrial process that exists so far; thus, these materials are out of the competition in both cases when it comes to application. The detail of each comparison is given the following:

# 2.1 Comparison based on the material's physical properties and electrical parameters

#### 2.1.1 Comparison based on material's physical properties

The detailed comparison of GaN with other technologies such as Ge, Si, GaAs, InP, SiC, and diamond is given in Table 2-1 for several material properties.

These technologies have proved their value for RF and millimeter-meter integrated products because the circuit design and implementation of it on the substrate is more feasible with III-V technologies than the silicon-based process. Silicon and Silicon-Germanium are catching upmarket due to increased performance and high integration capabilities. Still, they have competition with already market player GaAs technology. The GaN technology has been improved by reducing substrate thickness to have low thermal dissipation and smaller parasitic series resistors for high power and high-frequency circuit application. In comparison, InP has high mobility, which leads to high frequency practically greater than 100GHz but theoretically above 200GHz. However, it yields low power density because of the smaller bandgap.

SiC is better in case of thermal conductivity and high breakdown voltage, but the problem comes from its high cost and difficulty in the grown of other III-V material because of high lattice mismatch; thus, it does not offer 2DEG. Diamond is way better than all other technologies at the material properties level. Still, it is not mature at the technology level, and no process exists for it yet, so it is out of competition for MMIC design.

GaN is better in various physical parameters, which are very feasible for RF and millimeter-wave high power circuits [6]. It offers two-dimensional electron gas (2DEG), which offers a mature system

of very high mobility electrons even at low temperatures. It has several advantages over GaAs and Si in the power and RF application due to its superior physical material properties. This analysis is given in the radar chart Figure 2-1 according to five main physical properties of materials that define the technology limit.

| Materials                                                               | Ge                  | Si                  | GaAs                 | InP                  | SiC                 | GaN                      |

|-------------------------------------------------------------------------|---------------------|---------------------|----------------------|----------------------|---------------------|--------------------------|

| Bandgap (eV)                                                            | 0.67                | 1.12                | 1.43                 | 1.34                 | 3.2                 | 3.4                      |

| Dielectric constant                                                     | 16                  | 11.8                | 13.1                 | 12.5                 | 10                  | 9.5                      |

| Intrinsic resistivity                                                   | 47                  | 2.3×10 <sup>5</sup> | 1×10 <sup>8</sup>    | 8.6×10 <sup>5</sup>  | 10 <sup>12</sup>    | 10 <sup>10</sup>         |

| Electron mobility<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 3900                | 1350                | 8500                 | 4600                 | 1140                | 1000(Bulk)<br>2200(2DEG) |

| Hole mobility<br>(cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )     | 1900                | 480                 | 400                  | 150                  | 50                  | 850                      |

| Thermal conductivity (Wcm <sup>-1</sup> K <sup>-1</sup> )               | 0.6                 | 1.5                 | 0.46                 | 0.68                 | 3.7                 | 1.3                      |

| Breakdown field (E <sub>c</sub> )                                       | 1×10 <sup>5</sup>   | 3×10 <sup>5</sup>   | 6×10 <sup>5</sup>    | 5×10 <sup>5</sup>    | 3.5×10 <sup>6</sup> | 2×10 <sup>6</sup>        |

| Power density (Wmm-1)                                                   | N/A                 | 1.5                 | 0.67                 | 0.54                 | 4                   | 5-12                     |

| Saturation Velocity of electron at 300k (cms <sup>-1</sup> )            | 0.7×10 <sup>7</sup> | 1.0×10 <sup>7</sup> | 0.72×10 <sup>7</sup> | 0.67×10 <sup>7</sup> | _                   | 1.4×10 <sup>7</sup>      |

Figure 2-1: Advantages of GaN in RF and Power supply circuits over GaAs and Si [10]

As a result, it has advantages over competitive material such as GaAs and Si, similarly the competitive technology such as LDMOS and GaAs technology. Both LDMOS and GaAs are useful in

a specific range of frequency and power level [11], [12]. For example, GaAs products are suitable for high frequency but medium power up to 25W-50W applications [12]. GaAs does not behave well at high power due to low thermal conductivity. Second, LDMOS is useful for high power applications based on Si technology, but it only goes up to a maximum 3GHz-5GHz frequency [12]. However, GaN is an alternative of both because it is suitable for high power and frequency application.

#### 2.1.2 Comparison based on electrical parameters

After making this comparison based on the material physical properties, the next electrical parameters are essential to see differences among different technologies. The comparison is among GaAs, GaN, SiGe, and Si technologies, which are mature enough and have industrial processes given in Table 2-2. based on electrical parameters: cutoff frequency ( $f_T$ ), maximum oscillation frequency ( $f_{max}$ ), noise figure, phase noise, IP3/PDC, breakdown voltage, and power handling capability.

SiGe HBTs are useful to provide the highest cutoff frequency but not competitive to GaN HEMT and HBT GaAs, which are better in high efficiency, low noise figure, better power handling capability, and a high ration of linearity over dissipated DC power. Because of fully developed technology and existing platform Si (RF-CMOS) is perfect for large scale integration. On the other hand, it is not good competitive in other parameters and comes at the end among its competitor's technologies for typical electrical figures of comparison.

| Tachnalagy Davises | GaAs   |       |     | GaN  | SiGe | Si      |

|--------------------|--------|-------|-----|------|------|---------|

| Technology Devices | MESFET | PHEMT | нвт | HEMT | нвт  | RF-CMOS |

| f <sub>T</sub>     | L      | М     | Н   | М    | Н    | L       |

| f <sub>max</sub>   | М      | Н     | Н   | М    | Н    | L       |

| Noise figure       | М      | L     | М   | L    | М    | Н       |

| Phase Noise        | М      | Н     | L   | L    | L    | Н       |

| IP3/PDC            | Н      | М     | Н   | Н    | М    | L       |

| Breakdown voltage  | М      | Н     | М   | Н    | L    | L       |

| Power Handling     | М      | Н     | Н   | Н    | М    | L       |

Table 2-2: Comparision of typical electrical figures of several semiconductor technologies [6]

H=High, M=Medium, L=Low

#### 2.1.3 Comparison based on power and frequency application

Some specific applications and performance of the devices made from different semiconductor technologies need specific output power and frequency. The following Figure 2-2 gives an idea about specific technology's power and frequency [13].

Figure 2-2: Power and frequency region for different semiconductors [13]

Currently, the GaAs Power amplifier is widely used for the base station because of its capability to handle high power at high frequency. Silicon carbide also exists for this application but is limited with frequency. However, for the broadcasting station, communication satellites, and radar applications, we need high power at high frequency, for example, 125W at the 10-12GHz for communication satellites [14], so GaN enables new possibilities for both high-power and high-frequency.

Silicon or Gallium arsenide power amplifier is used for the cell phones because the required power is about 0.9W around 1GHz. Multiple technologies are competing below 3GHz. The choice of technology for a particular application is based on either cost or high-performance. For a low cost, Si is dominating, but for high-performance, SiC is mostly used. However, with the advancement in GaN technology, such as 6 inches wafer size (OMMIC) [15] and MACOM claimed that GaN on silicon transistor outperforms premium-priced GaN-on-SiC transistor [16], It shall gradually gain the market below 3GHz application.

#### 2.1.4 Comparison based on performance and Cost

Material physical properties and electrical parameters give the initial difference among technology, but we have to consider the relative performance and limitation of those technologies for better understanding. A figure of merit which is commonly used for active components is given by the following equation [17]–[19]:

$$FoM = f_T \times BV_{CRO} \tag{2-1}$$

where  $BV_{CBO}$  is the breakdown voltage is given in Voltage [V], and  $f_T$  is in giga-hertz [GHz]. In most cases, we need high power along with the high-frequency application. In those cases, Si RF-CMOS and SiGe BiCMOS have low breakdown voltage, limiting the voltage swing. Another problem comes from the low bandgap of silicon, which results in a critical electrical field compared to its competitor's III-V technologies.

GaAs and other III-V technologies, particularly GaN, provide high breakdown voltage and high frequency, which is advantageous in a significant trade-off between  $f_T$  and  $BV_{CBO}$  for millimeter-wave applications. It is better to have high power by having high voltage than having high current for good efficiency, so GaN suits well in this scenario.

There are other figures of merit depending on the application such as Johson figure of merit (JFOM) [20] which is for low-voltage transistors, Keyes [21] KFOM used to see thermal limitation to the switching behavior of transistor, Baliga [22] BFOM for determining conductive losses in low-frequency and most exciting figure of merit in our case is Baliga high-frequency FoM (BHFFOM) [23]. The detailed comparison for high power RF transistors is given in Figure 2-3 between GaN and other semiconductor technologies, which indicate that GaN is better for high power RF applications.

A performance comparison is fair but not enough unless we consider cost and the particular application from manufacturing to all development costs. Again here is another trade-off in Table 2-3. There is a comparison given about capabilities and manufacturing costs related to some parameters for different technologies.

Figure 2-3: Comparison of GaN/SiC/Si/GaAs high-power RF transistors [24]

The wafer size and wafer cost for GaN technology are large as compare to others. However, it's hard to judge which technology is better based on cost because we choose technology according to the application, such as designing a mixer or power amplifier. Nevertheless, cost and performance comparison gives us an estimate of what we can have or design in the available budget for the particular application.

There is another recent comparison about wide band-gap (WBG) material cost, and wafer size is done by Yole development with an 8-inch Si wafer as reference shown in Figure 2-4. Diamond and  $Ga_2O_3$  are future technology, don't exist yet. We can see that GaN-on-Si is the most exciting WBG technology in terms of cost and wafer size.

Table 2-3: Manufacturing Cost and Capabilities for Different Technologies [6]

Figure 2-4: WBG material cost and wafer size comparison [25]

| Materials           | GaN              | GaAs          | SiGe        | Si         |

|---------------------|------------------|---------------|-------------|------------|

| Technology Process  | 0.15 - 0.1 μm    | 0.25 - 0.1 μm | 180 – 55 nm | 65 – 20 nm |

| Devices             | HEMT             | НЕМТ          | HBT         | RF-CMOS    |

| Wafer size (inches) | 3 - 6            | 4 - 6         | 6 - 8       | 8 - 12     |

| Mask set cost (K\$) | 75 - 150         | 25 - 50       | 250 - 400   | 400 - 1000 |

| Wafer cost(k\$)     | 10 - 15          | 4 - 10        | 2 - 3       | 1 - 2      |

| CAD cost(k\$)       | 10 - 50          | 10 - 50       | 500 - 1000  | 500 - 1000 |

| Triple well process | NO               | NO            | YES         | YES        |

| Backside process    | YES              | YES           | NO*         | NO*        |

| Metal layers        | tal layers 2 - 3 |               | 4 - 6       | 8 - 12     |

| Metal material      | Au               | Au            | Al-Cu       | Al-Cu      |

| Integration level   | ration level Low |               | High        | High       |

<sup>\*=</sup> Through Silicon Via (TSV)

#### 2.1.5 Comparison based on analysis as part of a full product

The last level of comparison for different technologies is done by analyzing them at the full product level. It's most difficult because trade-off involves technological process, design rule, cost, and performance. It should also consider the cost of chemicals, gases, labor, process tool maintenance, number of processes, and technology process yield. Estimation of all the above costs is given in an index [18]; thus, we can better compare different technologies. However, it still does not cover everything. We need to consider a broader area in case of planning for a particular application, so it is difficult to define one function which can give us an estimate because of performance trade-off at each stage of each stage such as device level, at circuit level (topologies, biases control), at the interface level (filters, matching-network) or the product level (interconnections, packages).

The function called product-wise comparison parameter PcP is used for this purpose:

$$PcP = f\left\{\frac{\textit{Die per wafer,Num.of wafers}}{\textit{Wafer cost [K\$],Mask Cost [K\$]}}\right\} \cdot \frac{\textit{FoM}}{\textit{Process Yiel}} \cdot \frac{\textit{Num.of functions}}{\textit{CAD Costs [K\$]}}$$

(2-2)

The equation includes several parameters the die size, process yield, possible implemented number of functions also include FoM, even CAD cost. It is a complex function but can be very handy for industrial purpose use for any particular application.

For the challenges mentioned above, the GaN HEMT FET transistor offers to promise an alternative technology for highly competitive MMICs. There are some products in the markets due to the already vital research that has been done on this technology. However, this technology is not mature and far away from giving full potential due to specific issues, for example, the traping effect [26], which hinder the performance of the device, so research efforts are continuously required to overcome such issues and to optimize the cycle of technology from manufacturing to final modeling and design steps.

The summary of all the benefits or values added by GaN's technology and possible applications which it can offer at the system level are given in Figure 2-5.

Figure 2-5: GaN's added values at system level [27]

### 2.2 Applications of GaN technology:

Application for GaN devices, particularly for RF electronics systems, with respect to the frequency band and available other technologies, are given in Figure 2-7. Power amplifiers are the main area of GaN adoption for these applications.

There are several applications of GaN-on-Silicon in the micro-nano electronics and optoelectronics are given in Figure 2-6 below because of low cost, the thermal conductivity of silicon is almost the same as GaN, high electrical resistivity, large area available (> 8 "), Different crystalline orientations (111), (110), (001), MOS compatible technology and, finally easy to transfer/change exotic substrate (diamond, flexible, ...).

Figure 2-6: Applications of GaN on Si

Figure 2-7: Applications of GaN devices in RF Electronics Systems

# Chapter 3: State-of-the-art

This chapter explains device structure and operations layer by layer, presents state-of-art technologies based on GaN-on-SiC and GaN-on-Si (111, 100, 110) for comparison purposes. Once technologies are presented, afterward, challenges for modeling of GaN devices are mentioned. Several methods are explained for small and large signal modeling of such devices at an intrinsic and extrinsic level.

### 3.1 Physical structure and operation of AlGaN/GaN HEMTs

HEMT (High Electron Mobility Transistors) has two wide bandgap semiconductors (Large bandgap such as Al(Ga)N-ln(Ga)AlN on lower band gap-GaN), which are not doped. In this technique, electrons come from the wide-bandgap barrier layer's surface, composed the two-dimensional electron gas (2DEG) thanks to the polarization effect (spontaneous and piezoelectric polarization). It is crucial to know that in all HEMT structure layers, there is no doping. The transport properties show improved electron mobility and higher saturation velocity in the well. This effect implies a higher  $f_T$ , a better gain, and a noise figure (NF) than MESFET. HEMT based on heterojunction AlGaN/GaN was reported for the first time in 1994 in Khan's pioneering work [28].

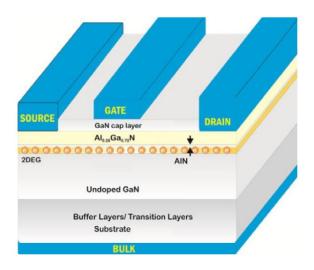

The typical layer structure of the AlGaN/GaN HEMT structure is shown below in figure Figure 3-1.

Figure 3-1: Typical HEMT structure [29]

The structure is composed of the following layer:

**Cap layer:** It is an optional layer (typically GaN, SiN) that allows the protection of the barrier layer (typically AlGaN), limits the currents. However, it decreases the height of the Schottky barrier [Liu et al., 2011]. We need this layer mostly when the heterostructure has many defects. Its thickness varies between a few nm to 50 nm.

**The barrier layer:** This is the layer with a high bandgap (In, Ga)AIN, which allows the formation of well at the interface with the GaN channel.

**The Spacer Layer:** This is an optional layer (typically AIN), which is the lower part of the barrier layer whose thickness is generally less than 2nm. It allows having good confinement of the electrons in

the 2DEG and increasing the electron mobility, reducing the interactions between the electrons of the 2DEG and the aluminum atoms present in the barrier layer.

**Channel Layer:** It is composed of undoped GaN and totally relaxed. The thickness varies between a few 10nm to a few 100nm. This layer has a lower bandgap in comparison with the barrier layer, and the 2DEG is formed in this layer.

Buffer Layer: It can be composed of a GaN layer, but it is preferred to use a back-barrier layer with a higher bandgap (typically, AlGaN, the aluminum is the function of application). Its thickness is generally greater than a few  $\mu$ m. Because of its high thickness, the buffer layer is fully or partially relaxed. If this layer is fully relaxed, it does not present a piezoelectric polarization. This layer's quality is very important for electronic application: It must act as an electrical insulator and have good thermal conductivity.

Stress Engineering Layers: These layers are composed of different layers between the nucleation and buffer layers. Their role is to reduce stress and dislocation rate. The thickness varies between a few 100nm to few  $\mu m$ .

**The nucleation layer:** It is the first layer to accommodate the substrate's lattice parameter with wide band-gap nitrides deposed by epitaxy. On the silicon substrate, this layer is typically aluminum nitride (AIN). Its thickness is 20-60nm.

**Substrate:** This is the support layer on which the growth of the different layers takes place. The substrates generally used for the growth of GaN are sapphire ( $Al_2O_3$ ), silicon (Si), silicon carbide (SiC), and GaN. Table 3-1 shows a comparison between the different substrates used for the growth of GaN, depending on cost, thermal conductivity, mesh mismatch, coefficient of thermal expansion, resistivity, and size availability.

HR-Si GaN SiC **Attribute** Sapphire (111)(Bulk) Thermal Conductivity (W/cm. K) 4.9 3.3 1.5 0.42 Lattice mismatch with GaN (%) ~ -17 ~ -16 ~ +3.5 0 Currently available wafer size (inch) 6 4 12 6 Cost (compared to Si) Very low High Low Very high 1×e<sup>5</sup>-Max 1×e<sup>4</sup> Resistivity (Ohms.cm) >1×e<sup>6</sup> Max 1×e<sup>13</sup> 1×e<sup>8</sup> Difference in heat expansion (x10<sup>-6</sup>-K<sup>-1</sup>) (300-7.5 4.2 2.6 5.6 1000K)

Table 3-1: Comparison between different substrates available for GaN technology

**Silicon:** It is one of the most attractive substrates for the growth of GaN, thanks to its price very competitive, its availability of large diameters, its good thermal conductivity (1.5 Wcm<sup>-1</sup>K<sup>-1</sup>), and its processing in standard silicon fabs (high productivity). The major disadvantage is that the GaN layers

elaborated on Si generally have a concentration of defects due to the mismatch in lattice parameters (17%) and a very large coefficient of thermal expansion(CTE).

**Sapphire (Al<sub>2</sub>O<sub>3</sub>):** It is a semi-insulating material that can withstand high growth temperatures and relatively cheap. On the other hand, it has very low thermal conductivity (0.5 Wcm<sup>-1</sup>K<sup>-1</sup>), large lattice mismatch (13%), and large CTE mismatch. Low thermal conductivity means it has a problem in heat dissipation as a result, not a good choice for high power applications.

**Silicon carbide (SiC):** Silicon carbide has very high thermal conductivity (4 Wcm<sup>-1</sup>K<sup>-1</sup>), low lattice mismatch (3%), and relatively low CTE mismatch. However, the problem is the high cost, and the technological process is more complicated.

### 3.2 State-of-the-art GaN technology

For the state-of-the-art GaN technology comparison, it is important to relate it with the substrate. Depending on the substrate, we have different performance because of certain advantages and disadvantages of each substrate. As mentioned in Table 3-1, SiC and Si are the most suitable substrate for GaN technology because of the advantages mentioned in chapter 2.

For GaN-on-SiC, the state-of-the-art is given in Table 3-2 at 4, 10, 18, 40, and 94GHz frequencies. These results are best obtained with the SiC substrate by having a low rate of mismatch with GaN and keeping excellent thermal conductivity. At 4GHz, the saturation output power 41.4 Wmm<sup>-1</sup> was achieved with PAE at 60% [30]. Similarly, at 94GHz, 1.51 Wmm<sup>-1</sup>, and 8.5% were measured P<sub>sat</sub> and PAE, respectively [31]. However, OMMIC claimed that they reached 4.5 Wmm<sup>-1</sup> at 94GHz with GaN-on-SiC.

| Frequency              | Gp(dB) | Psat<br>(W/mm) | PAE<br>(%) | Gate length<br>(nm) | Drain voltage<br>(V) |

|------------------------|--------|----------------|------------|---------------------|----------------------|

| @ 4GHz [30]            | 16     | 41.4           | 60         | 250                 | 135                  |

| @10GHz [32]            | 24     | 17.5           | 61         | 250                 | 55                   |

| @18GHz [33]            | 8.6    | 12             | 33         | 150                 | 50                   |

| @ 40GHz [34]           | -      | 10.5           | 34         | 160                 | 30                   |

| @ 94GHz [31],<br>OMMIC | 9      | 1.51           | 8.5        | 50                  | 9                    |

|                        | -      | 4.5            | -          | -                   | -                    |

Table 3-2: State-of-the-art for GaN-on-SiC at different frequencies

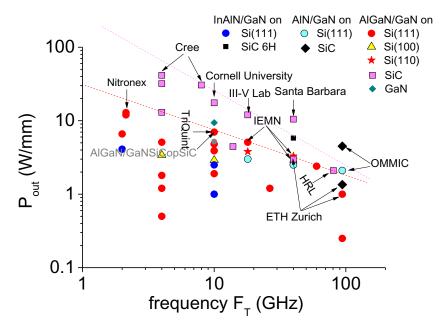

For more details, we can see the plot of power density as a function of frequency given in Figure 3-2. There is a clear shrinking in power as we go to high frequency.

There are three Si substrates possible depending on plane orientation, such as Si(111), Si(100), and Si(110). In the (111) plane, the crystalline silicon has a hexagonal triple symmetry surface suitable for GaN growth by epitaxy. Thus, it is commonly used as a substrate for the growth of

heterostructures dedicated to HEMT transistors and have given significant performance in terms of microwave power density. For GaN-on-Si(111), the state-of-the-art is given in Table 3-3 at 2.14, 10, 40, and 94GHz frequencies. At 2.14GHz, the saturation output power 12 Wmm<sup>-1</sup> was achieved with PAE at 52.7% [35]. Similarly, at 94GHz, 1.35 Wmm<sup>-1</sup>, and 12% was measured Psat and PAE, respectively [36]. However, OMMIC claimed that they reached 4.5 Wmm<sup>-1</sup> at 94GHz with GaN-on-SiC.

| HEMT       | Frequency       | Gp (dB) | Psat (W/mm) | PAE (%) | W(μm) | Meas. Condition |

|------------|-----------------|---------|-------------|---------|-------|-----------------|

| On Si(111) | @2.14GHz [35]   | 15.3    | 12          | 52.7    | -     | -               |

|            | @10GHz [37]     | -       | 7           | 52      | -     | -               |

|            | @18GHz [38]     | 9.1     | 5.1         | 20      | 2×50  | -               |

|            | @40GHz [39]     | 9       | 2.7         | 18      | 2×25  | -               |

|            | @ 94GHz [OMMIC] | -       | 2.1         | _       | _     | Pout max        |

Table 3-3: State-of-the-art for GaN on Si (111) at different frequencies

In the case of Si(100 and Si(110) substrates, there are also proven results given in Table 3-4. But the defect density of the heterostructures produced in these orientations is greater as compared to Si (111). However, the advantage lies in co-integration with CMOS technology.

| НЕМТ          | Frequency       | G <sub>p</sub><br>(dB) | P <sub>sat</sub><br>(dBm) | P <sub>sat</sub><br>(W/mm) | PAE<br>(%) | W<br>(µm) | Measurement condition |

|---------------|-----------------|------------------------|---------------------------|----------------------------|------------|-----------|-----------------------|

| On<br>Si(100) | @4GHz<br>[40]   | 19.3                   | 25.3                      | 3.4                        | 14.3       | 2×150     | Pout max              |

|               | @10GHz<br>[40]  | 7.5                    | 29.4                      | 2.9                        | 20.4       | 2×150     | Pout max              |

| On<br>Si(110) | @18GHz<br>[40]  | 15.6                   | 23.4                      | 3.76                       | 33         | 2×30      | Pout max              |

|               | @ 40GHz<br>[40] | 10.6                   | 23                        | 3.3                        | 20.1       | 2×30      | <del>-</del>          |

Table 3-4: State-of-the-art for GaN on Si (100) and Si (110) at different frequencies

Figure 3-2 gives the best results of GaN transistors on SiC, Si (111), Si (110), Si (100), and GaN substrates in terms of power density as a function of the measurement frequency.

Figure 3-2: State of the art of GaN HEMT technology on Si and SiC (Power density in saturation as a function frequency) [30]–[39], [41]–[49]

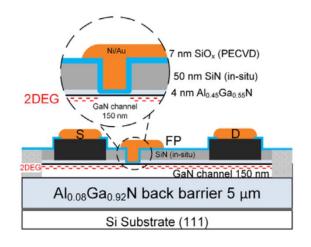

#### 3.2.1 Our process:

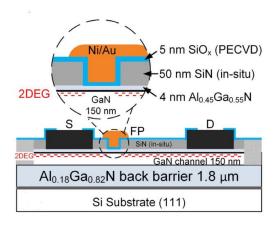

In the 3IT process, we have two types of devices, normally-on and normally-off transistors based on AlGaN/GaN thickness and different Aluminum (Al) concentrations in the barrier layer. In both cases, the AlGaN/GaN MOSHEMT structures were fabricated on a Si substrate and commercial HEMT wafer (supplied by EpiGaN) by using the Metal-Organic Chemical Vapor Deposition technique (MOCVD). The gate length is 1.5µm.

The epitaxial structure consists of a 150nm thick un-doped GaN channel layer and a thin 4nm  $Al_{0.45}Ga_{0.55}N$  top barrier layer. The epitaxial structure is capped with a 50nm thick in-situ SiN layer. However, the difference between normally-on and normally-off is that the structure consists of a 1.8 $\mu$ m thick  $Al_{0.18}Ga_{0.82}N$  back-barrier layer and  $5\mu$ m  $Al_{0.08}Ga_{0.92}N$  back-barrier layer, respectively, as shown in Figure 3-3 [50], [51]:

**Oxide layer – MOSHEMT:** In our process, we have SiOx deposited by PECVD, which acts as a gate insulator; consequently, it gives a very small gate leakage current in reverse and forwards bias condition. The thickness of the oxide layer is 5nm for normally-on MOSHEMT and 7-10nm for normally-off. It is very important to choose the oxide layer's proper thickness because it is a trade-off between better isolation to achieve low leakage current and high transconductance. To have more voltage on V<sub>gs</sub> also depends on the thickness of the oxide layer. For example, for 10nm, we can go up to 10V in case of forwarding bias.

**Meander shape:** We are using a meander shape for the transistor. Because of this shape, we can have a longer gate length in a small space; ultimately, it leads to high power density.

**Field-plate Gate:** We have a field-plate gate in our process. The purpose of using a field plate gate is to increase breakdown voltage by distributing the electric field at the wider area as reported in [22] the reduction of peak electric field 40% to 50% depending on the length of the plate towards the drain side.

**Recess gate:** In the case of a recessed gate, the gate metal deposited close to 2DEG to allow improved transconductance, linearity and to shift threshold voltage from negative to positive  $V_{gs}$  voltage. The control of the etch thickness obtained by digital etching (few cycles composed of two-step: dry oxidation followed by wet etching).

a) Normally-off AlGaN/GaN

b) Normally-on, AlGaN/GaN

c) SEM image of fabricated MOS-HEMT

Figure 3-3: Schematic of the fabricated MOSHEMT [50], [51]

#### 3.2.2 The principle of GaN HEMT Operation

A HEMT is a three-terminal device with a source, gate, and drain in which the gate electrode controls the current flow between drain and source (ohmic contacts). Its operation principle is based on the presence of 2DEG at the AlGaN/GaN heterostructure interface. By applied voltage at the gate electrode, it is possible to control the transistor channel's electron density, thus controlling the drain current (I<sub>DS</sub>).

**Normally-on Transistor**: This transistor has four regions of operation as shown in Figure 3-4 (Vth is negative)

$$Region of Operation = \begin{cases} Cut - off & V_{gs} \leq V_{th} \\ Ohmic & V_{th} < V_{gs} \& V_{Ds} \ll V_{K} \\ Saturation & V_{th} < V_{gs} \& V_{Ds} \geq V_{K} \\ Breakdown & V_{th} < V_{gs} \& V_{Ds} = V_{br} \end{cases} \tag{3-1}$$

where

$$V_K = V_{gs} - V_{th}$$

Looking at the  $I_{DS}$  vs.  $V_{gs}$  transfer curve (Figure) for a fixed  $V_{DS}$  voltage, the  $I_{DS}$  current increases with increasing gate bias. When a negative voltage is applied to the gate, the current  $I_{DS}$  decreases, thus depleting the channel under the gate. The value of  $V_{gs}$  for which the channel is cut-off is called the threshold voltage ( $V_{th}$ ).

**Cut-off region:** It is a region of operation in which the device channel is close means there is no conduction of electrons and no current. It occurs when the gate-source applied voltage is less than the threshold voltage.

**Ohmic/linear region:** The drain-source current varies linearly when drain-source voltage is low. In this case, the electric field is constant along the 2DEG, and electrons move in parallelepiped bar's shape homogenously. The current can be calculated by:

$$I_{DS} \approx V_{DS} \frac{q.\mu.n_s.W}{1 + q.\mu.n_s.W(R_D + R_S)}$$

(3-2)

**Saturation region:** Current is saturated because the channel is cut-off at the drain end and  $V_{DS}$  does not affect the channel any longer.

$$I_{DS} = q. v_{SAT}. n_s. W \tag{3-3}$$

**Breakdown region:** breakdown voltage is Vds' value to generate hot carriers by impact ionization, leading to an avalanche phenomenon and destroying the lattice.

Figure 3-4: Determine threshold voltage and region of operation of the device

Depending on the application, we use the transistor to operate in different regions, depending on the quiescent point's position.

### 3.3 Modeling challenges of GaN HEMTs

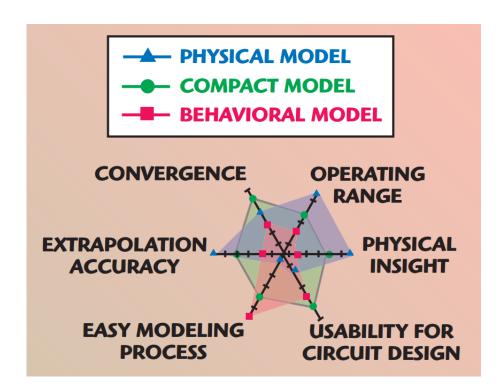

There are different literature models, which we can broadly divide into three main categories: physical model, compact model, and behavioral model. The physical model is based on the physic of the device. For this reason, these models are limited only to the device. The advantage of these models is the large operating range. However, these are time-consuming because of the complex equation used to model physical behavior.