#### PhD Programme:

COMPUTACIÓN AVANZADA, ENERGÍA Y PLASMAS

## HETEROGENEOUS PARALLEL COMPUTING FOR IMAGE REGISTRATION AND LINEAR ALGEBRA APPLICATIONS

## COMPUTACIÓN PARALELA HETEROGÉNEA EN REGISTRO DE IMÁGENES Y APLICACIONES DE ÁLGEBRA LINEAL

Directors:

DR. JOAQUÍN OLIVARES BUENO DR. JUAN GÓMEZ-LUNA

Author

**ORESTIS ZACHARIADIS**

Thesis submission date: 2 JUNE 2020

# TITULO: Heterogeneous parallel computing for image registration and linear algebra applications

AUTOR: Orestis Zachariadis

© Edita: UCOPress. 2020 Campus de Rabanales Ctra. Nacional IV, Km. 396 A 14071 Córdoba

https://www.uco.es/ucopress/index.php/es/ucopress@uco.es

THESIS TITLE: Heterogeneous parallel computing for image registration and linear algebra applications

PhD CANDIDATE: Orestis Zachariadis

DETAILED REPORT OF THE THESIS SUPERVISORS:

This PhD thesis stands as proof of high-quality research and, thus, qualifies the PhD candidate, Mr. Orestis Zachariadis, for the title of Doctor.

The contributions of this thesis encompass novel GPU programming and optimization techniques that can benefit a wide range of applications. First, this thesis takes advantage of in-depth architecture details of GPUs to significantly improve the execution time of medical image registration. The work of the PhD candidate provides clinical validation of the proposed registration method on a scenario of liver deformation due to inflation of the stomach during laparoscopic surgery. Second, this thesis repurposes the Tensor Core Units (TCUs), novel processing elements intended to accelerate deep-learning, which equip current GPU architectures, to accelerate the performance of Sparse Matrix-Matrix Multiplication (SpMM). SpMM is an operation widely-used in linear algebra, graph processing, etc.

During the development of this thesis, the PhD candidate has benefited from the collaboration with prestigious international institutions through the H2020 HiperNav project. A 3-month secondment at SIN-TEF (Norway) facilitated the induction to industrial research.

This thesis resulted in the following research papers:

Accelerating B-spline interpolation on GPUs: Application to medical image registration. O. Zachariadis, A. Teatini, N. Satpute, J. Gómez-Luna, O. Mutlu, O. J. Elle and J. Olivares, Computer Methods and Programs in Biomedicine, vol. 193, p. 105431, Sep. 2020

Accelerating Sparse Matrix-Matrix Multiplication with GPU Tensor Cores. O. Zachariadis, N. Satpute, J. Gómez-Luna, Joaquín Olivares, Computer and Electrical Engineering, 2020. [Revision submitted].

The PhD candidate showed his strong commitment to open research by publishing all source code and datasets.

For the above reasons, we authorize the presentation of this PhD dissertation.

Córdoba, 2 June 2020.

The supervisors of the doctoral thesis:

Joaquín Olivares Bueno

Juan Gómez-Luna

To everyone who supported me. This work would not be possible without them.

This doctoral thesis focuses on GPU acceleration of medical image registration and sparse general matrix-matrix multiplication (SpGEMM). The comprehensive work presented here aims to enable new possibilities in Image Guided Surgery (IGS). IGS provides the surgeon with advanced navigation tools during surgery. Image registration, which is a part of IGS, is computationally demanding, therefore GPU acceleration is greatly desirable. spGEMM, which is an essential part in many scientific and data analytics applications, e.g., graph applications, is also a useful tool in biomechanical modeling and sparse vessel network registration. We present this work in two parts.

The first part of this thesis describes the optimization of the most demanding part of non-rigid Free Form Deformation registration, i.e., B-spline interpolation. Our novel optimization technique minimizes the data movement between processing cores and memory and maximizes the utilization of the very fast register file. In addition, our approach re-formulates B-spline interpolation to fully utilize Fused Multiply Accumulation instructions for additional benefits in performance and accuracy. Our optimized B-spline interpolation provides significant speedup to image registration.

The second part describes the optimization of spGEMM. Hardware manufacturers, with the aim of increasing the performance of deep-learning, created specialized dense matrix multiplication units, called Tensor Core Units (TCUs). However, until now, no work takes advantage of TCUs for sparse matrix multiplication. With this work we provide the first TCU implementation of spGEMM and prove its benefits over conventional GPU spGEMM.

#### RESUMEN

Esta tesis doctoral se centra en la aceleración por GPU del registro de imágenes médicas y la multiplicación de matrices dispersas (SpGEMM). El exhaustivo trabajo presentado aquí tiene como objetivo permitir nuevas posibilidades en la cirugía guiada por imagen (IGS). IGS proporciona al cirujano herramientas de navegación avanzadas durante la cirugía. El registro de imágenes, parte de IGS computacionalmente exigente, por lo tanto, la aceleración en GPU es muy deseable. spGEMM, la cual es una parte esencial en muchas aplicaciones científicas y de análisis de datos, por ejemplo, aplicaciones de gráficos, también es una herramienta útil en el modelado biomecánico y el registro de redes de vasos dispersos. Presentamos este trabajo en dos partes.

La primera parte de esta tesis describe la optimización de la parte más exigente del registro de deformación de forma libre no rígida, es decir, la interpolación B-spline. Nuestra novedosa técnica de optimización minimiza el movimiento de datos entre los núcleos de procesamiento y la memoria y maximiza la utilización del archivo de registro rápido. Además, nuestro enfoque

reformula la interpolación B-spline para utilizar completamente las instrucciones de multiplicación-acumulación fusionada (FMAC) para obtener beneficios adicionales en rendimiento y precisión. Nuestra interpolación B-spline optimizada proporciona una aceleración significativa en el registro de imágenes.

La segunda parte describe la optimización de spGEMM. Los fabricantes de hardware, con el objetivo de aumentar el rendimiento del aprendizaje profundo, crearon unidades especializadas de multiplicación de matrices densas, llamadas Tensor Core Units (TCU). Sin embargo, hasta ahora, no se ha encontrado ningún trabajo aprovecha las TCU para la multiplicación de matrices dispersas. Con este trabajo, proporcionamos la primera implementación TCU de spGEMM y demostramos sus beneficios sobre la spGEMM convencional operada sobre dispositivos GPU.

The ideas, images and data that support this doctoral thesis have been published or are under review in the following works:

• Orestis Zachariadis, Andrea Teatini, Nitin Satpute, Juan Gómez-Luna, Onur Mutlu, Ole Jakob Elle, Joaquín Olivares Accelerating B-spline Interpolation on GPUs: Application to Medical Image Registration. Computer Methods and Programs in Biomedicine, 2020.

DOI: 10.1016/j.cmpb.2020.105431. Impact factor: 3.424

• [Revision submitted] Orestis Zachariadis, Nitin Satpute, Juan Gómez-Luna, Joaquín Olivares Accelerating Sparse Matrix-Matrix Multiplication with GPU Tensor Cores. Computer and Electrical Engineering, 2020. Impact factor: 2.189

#### Research data and source code

• Ole Jakob Elle, Andrea Teatini, Orestis Zachariadis Data for: Accelerating B-spline Interpolation on GPUs: Application to Medical Image Registration. Mendeley Data, 2020, v1.

DOI: 10.17632/kj3xcd776k.1.

- Orestis Zachariadis Source code for: Accelerating B-spline Interpolation on GPUs: Application to Medical Image Registration. Github, 2019.

URL: https://github.com/oresths/niftyreq\_bsi.

- Orestis Zachariadis Source code: tSparse: A GPU algorithm for sparse matrix-matrix multiplication. Github, 2020.

INIT the control of the control o

URL: https://github.com/oresths/tSparse.

#### Other works and collaborations

- Nitin Satpute, Rabia Naseem, Rafael Palomar, Orestis Zachariadis, Juan Gómez-Luna, Faouzi Alaya Cheikh, Joaquín Olivares Fast Parallel Vessel Segmentation. Computer Methods and Programs in Biomedicine, 2020. DOI: 10.1016/j.cmpb.2020.105431. Impact factor: 3.424

- Orestis Zachariadis, Juan Gómez-Luna, Joaquín Olivares Adaptive Threshold Acceleration on GPU: Application on Marker Detection. Jornadas Andaluzas de Informática, Málaga (Spain), 2017.

— Dalai Lama

#### GRATITUDE

In this section I would like to thank everyone that supported me during this work.

A special thank you to my parents and family for their unconditional support.

I would also like to thank my supervisors Joaquin and Juan who trusted me with this work. With their continuous support and encouragement they got me through my most difficult times.

Finally, I would like to thank all members of the lab, and especially Fran, Fernando and José Manuel who helped me with my adventure in a new country.

Thank You !!!

| i  | INTRO | DUCTIO          | ON 1                                                     |

|----|-------|-----------------|----------------------------------------------------------|

| 1  | INTR  | ODUCTI          | ION 3                                                    |

|    | 1.1   |                 | d for fast medical image regisration 4                   |

|    |       | 1.1.1           | High performance soft tissue navigation for liver cancer |

|    |       |                 | intervention 4                                           |

|    | 1.2   | Sparse          | e Matrix-Matrix Multiplication 5                         |

|    | 1.3   |                 | al-Purpose GPU computing 5                               |

|    | -     |                 | Processing hierarchy 5                                   |

|    |       | 1.3.2           | Memory hierarchy 6                                       |

|    |       | 1.3.3           |                                                          |

|    | 1.4   | Thesis          | s overview 8                                             |

| ;; | D CDI | TATE TAT        | FEDDOL ATION FOR IMACE RECICTRATION                      |

| 11 |       |                 | TERPOLATION FOR IMAGE REGISTRATION 9                     |

| 2  |       |                 | NG B-SPLINE INTERPOLATION AND IMAGE REGISTRATION 11      |

|    | 2.1   | Motiv           |                                                          |

|    |       | 2.1.1           | B-spline interpolation and previous work 12              |

|    | 2.2   | 2.1.2           | Pneumoperitoneum compensation 13                         |

|    | 2.2   | Object<br>Backg |                                                          |

|    | 2.3   |                 | 3.6.11.11.                                               |

|    |       |                 | Medical image registration 15 B-spline interpolation 16  |

|    | 2.4   |                 | ed Work 19                                               |

|    | 2.4   |                 | Medical image registration on GPU 19                     |

|    |       |                 | B-spline interpolation in medical image registration 21  |

|    | 2.5   |                 | nizing B-spline interpolation 23                         |

|    | 2.5   |                 | Overview 24                                              |

|    |       | 2.5.2           | Thread per Tile (TT) 24                                  |

|    |       | 2.5.3           | Thread per Tile with Linear Interpolations (TTLI)        |

|    |       | 2.5.4           |                                                          |

|    |       | 2.5.5           |                                                          |

|    |       | 2.5.6           | Off-chip memory to on-chip memory data movement 32       |

|    | 2.6   |                 | ation Methodology 33                                     |

|    |       | 2.6.1           | Dataset 33                                               |

|    |       | 2.6.2           | Accuracy 34                                              |

|    |       | 2.6.3           | Performance 34                                           |

|    |       | -               | Parameters 34                                            |

|    |       |                 | Implementations we compare with 35                       |

|    | 2.7   |                 | ts and Analysis 35                                       |

|    |       | 2.7.1           | Accuracy 35                                              |

|    |       | 2.7.2           | Performance on GPU 36                                    |

|    |       | 2.7.3           | Performance on CPU 40                                    |

|    | 2.8   | Clinic          | al validation of image registration implementation 41    |

|    |       | 2.8.1           | Experiment 1: Validation in liver patient-specific phan- |

|    |       |                 | tom. 42                                                  |

|    |       | 2.8.2           | Experiment 2: Validation in porcine study. 43            |

|    |       | 2.8.3           | Qualitative assessment of the registration procedure 43  |

|    |       | 2.8.4           | Quantitative assessment of the registration procedure 44 |

|    |       | 2.8.5           | Performance evaluation on clinical data 46               |

|    |       | 2.8.6           | Memory requirements 50                                   |

xiii

xiv Contents

```

2.9

Conclusion

2.10 Future work

iii sparse matrix-matrix multiplication

ACCELERATING SPARSE MATRIX-MATRIX MULTIPLICATION USING TEN-

SOR CORES

Motivation

3.1

56

Objectives

3.2

3.3

Background

Storage format

58

3.3.1

3.3.2

Sparse matrix-matrix multiplication

CUSP

60

3.3.3

3.3.4

Real numbers in digital computer systems

61

3.3.5

Matrix multiplication with CUDA

Challenges of spGEMM

3.3.6

Related work

3.4

63

Expansion Sorting Compression

3.4.1

Hash tables

3.4.2

64

Hybrid

65

3.4.3

Overview of our technique

3.5

Key insights

3.5.1

67

3.5.2

Components

3.6

Our technique in-depth

69

3.6.1

Creating the task list and allocating memory for tiles

3.6.2

Counting kernel

69

3.6.3

Multiplication kernel

Other components

3.6.4

3.6.5

Putting everything together

Evaluation Methodology

3.7

3.8

Results and Analysis

3.8.1

Times

3.8.2

Speedup

3.8.3

Conclusion

Conclusion

3.10 Future work

3.10.1 SpGEMM algorithm extensions

79

SpGEMM applications

DISCUSSION AND CONCLUSIONS

DISCUSSION

83

Accelerating B-spline interpolation

Accelerating sparse matrix-matrix multiplication: tSparse

84

4.2

CONCLUSIONS

85

B-spline interpolation

Sparse matrix-matrix multiplication

86

BIBLIOGRAPHY

```

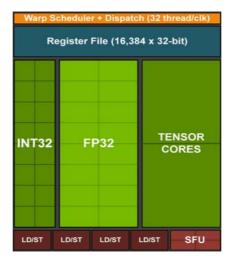

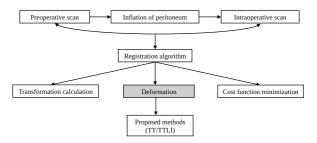

| Figure 1.1  | A part of the SM of Turing architecture that shows the    |

|-------------|-----------------------------------------------------------|

|             | distribution of int32, fp32 and tensor cores, as depicted |

|             | in Turing whitepaper [82]. 6                              |

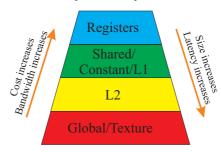

| Figure 1.2  | Memory hierarchy in CUDA. As we go up the pyra-           |

|             | mid, memory becomes more expensive and the band-          |

|             | width increases. As we go down the pyramid, memory        |

|             |                                                           |

| Г.          | becomes bigger and latency increases. 7                   |

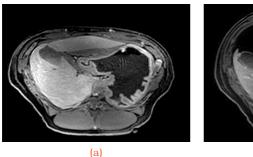

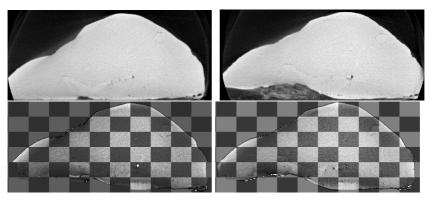

| Figure 2.1  | MRI scans, (Intra-modality) of porcine liver without      |

|             | (left) and with (right) pneumoperitoneum in prepara-      |

|             | tion for minimally invasive surgery 15                    |

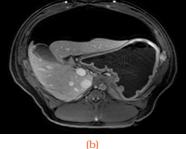

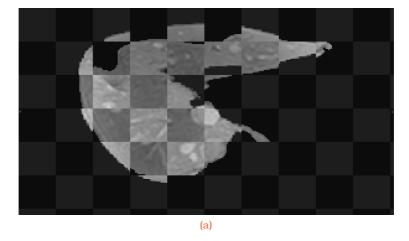

| Figure 2.2  | (a) Liver of a pig before registration, (b) The generated |

|             | deformation field overlaid on top of the reference im-    |

|             | age 16                                                    |

| Figure 2.3  | Cubes depicting the grouping in trilinear interpolations  |

|             | for a 3D control point grid 18                            |

| Figure 2.4  | Tile properties of a 2D image 18                          |

| -           |                                                           |

| Figure 2.5  | The building blocks of registration. 19                   |

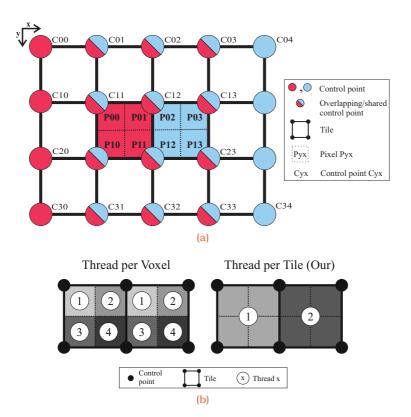

| Figure 2.6  | a) An example 2D grid with two tiles, b) Thread as-       |

|             | signment for Thread per Voxel (left) and Thread per       |

|             | Tile (right) approaches. The different threads are repre- |

|             | sented by different shades of gray, which correspond to   |

|             | the numbers 25                                            |

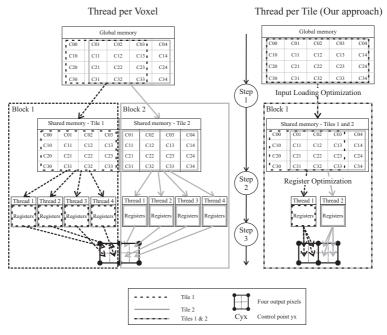

| Figure 2.7  | Comparison of input loading and register optimization     |

|             | for Thread per Voxel (left) and Thread per Tile (right)   |

|             | for the two neighboring tiles of Figure 2.6 26            |

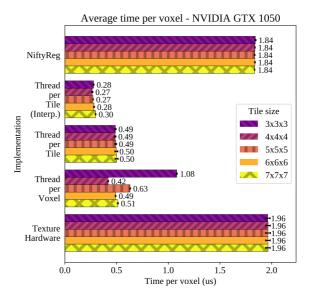

| Figure 2.8  | Average time per voxel of the five registration pairs for |

| 11gure 2.0  | various tile sizes on GTX 1050 GPU 36                     |

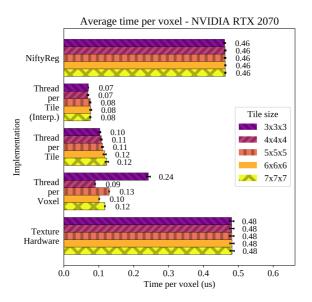

| Figure 2.9  | Average time per voxel of the five registration pairs for |

| riguie 2.9  |                                                           |

| Г.          | various tile sizes on RTX 2070 GPU 37                     |

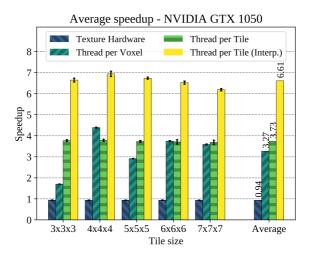

| Figure 2.10 | Average speedup of B-spline interpolation of the five     |

|             | registration pairs for various tile sizes on GTX 1050     |

|             | GPU. The B-spline interpolation of NiftyReg is the ref-   |

|             | erence of the speedup 38                                  |

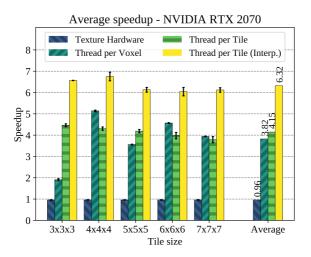

| Figure 2.11 | Average speedup of B-spline interpolation of the five     |

| _           | registration pairs for various tile sizes on RTX 2070     |

|             | GPU. The B-spline interpolation of NiftyReg is the ref-   |

|             | erence of the speedup 39                                  |

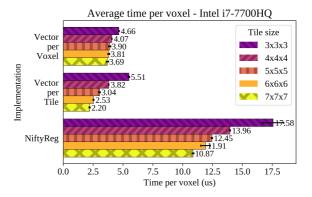

| Figure 2.12 | Average time per voxel of the five registration pairs for |

| 11gure 2.12 | various tile sizes on i7-7700HQ CPU 40                    |

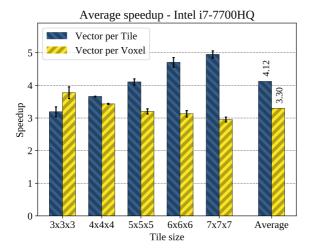

| Figure 2.12 | Average speedup of B-spline interpolation of the five     |

| Figure 2.13 | average specular of b-spinie interpolation of the live    |

|             | registration pairs for various tile sizes on i7-7700HQ    |

|             | CPU. The B-spline interpolation of NiftyReg is the ref-   |

|             | erence of the speedup 41                                  |

| Figure 2.14 | The association of our method in the pneumoperitoneum     |

|             | compensation workflow 42                                  |

| Figure 2.15 | DynaCT scans of the liver before deformation and af-      |

|             | ter deformation. The result of the registration shows a   |

|             | correctly performed registration 43                       |

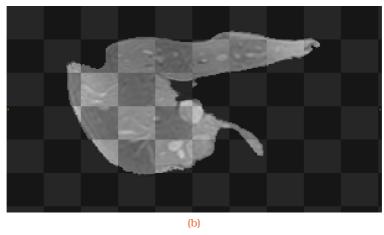

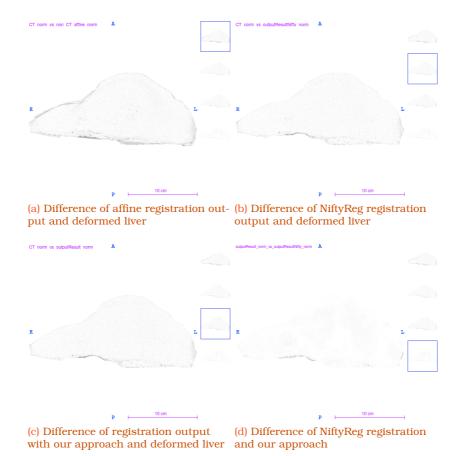

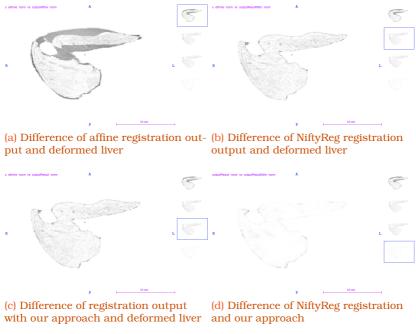

| Figure 2.16 | Comparison of registration through qualitative checker-                 |

|-------------|-------------------------------------------------------------------------|

|             | board assessment on porcine model. a) Affine registra-                  |

|             | tion, b) Non-rigid FFD 44                                               |

| Figure 2.17 | Comparison of registration through difference images                    |

|             | on liver phantom. 46                                                    |

| Figure 2.18 | Comparison of registration through difference images                    |

|             | on porcine liver. 47                                                    |

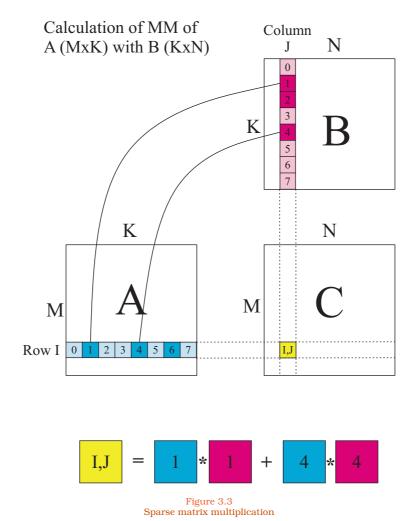

| Figure 3.1  | A 4 × 4 matrix in dense and COO formats. Element                        |

|             | "40", which is located at position [3, 0] of the dense                  |

|             | matrix, corresponds to [3, 0, 40] in COO format 58                      |

| Figure 3.2  | A $12 \times 12$ matrix in dense (left) and bitmap formats              |

|             | (bottom right). Tiles have a size of $4 \times 4$ and partition         |

|             | the $12 \times 12$ matrix in a $3 \times 3$ grid of tiles. Nonzero ele- |

|             | ments a8, a9, a11, a12 of the circled tile are represented              |

|             | as "1" in the bitmap. We store the nz elements of the                   |

|             | tile in consecutive locations in the element array. <i>Index</i>        |

|             | points to the first element of the tile. On the bottom                  |

|             | right of the figure, we circle the representation of the                |

|             | selected tile in bitmap format 59                                       |

| Figure 3.3  | Sparse matrix multiplication 60                                         |

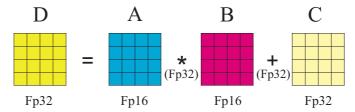

| Figure 3.4  | Mixed precision with CUDA TCUs. Inputs are stored                       |

|             | in fp16, whereas the output and addend are stored in                    |

|             | fp32. The multiplication and addition are performed in                  |

|             | full precision 62                                                       |

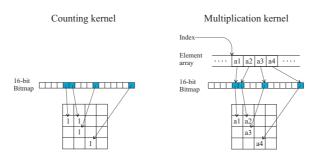

| Figure 3.5  | Comparison of counting and multiplication kernels. The                  |

|             | counting kernel (left) places "1"s at the locations indi-               |

|             | cated by the bitmap. The multiplication kernel (right)                  |

|             | loads the actual elements and places them at the loca-                  |

|             | tions indicated by the bitmap 71                                        |

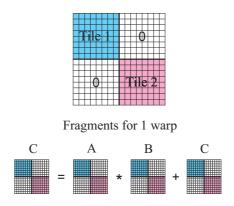

| Figure 3.6  | (Up) Placement of the two tiles in the fragment, (Down)                 |

|             | Tile placement during multiplication 71                                 |

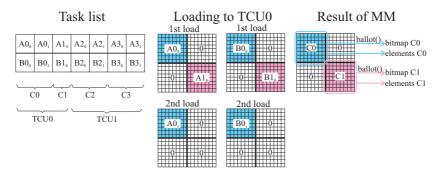

| Figure 3.7  | The multiplication kernel and its connection to the task                |

|             | list. Each TCU calculates two tiles of the output C. If                 |

|             | the accumulation of the two output tiles requires a dif-                |

|             | ferent number of addends, we fill with "o"s as appro-                   |

|             | priate. As output we get the elements of the two output                 |

|             | tiles, <i>C</i> , and the respective bitmaps (using ballot opera-       |

|             | tions). 73                                                              |

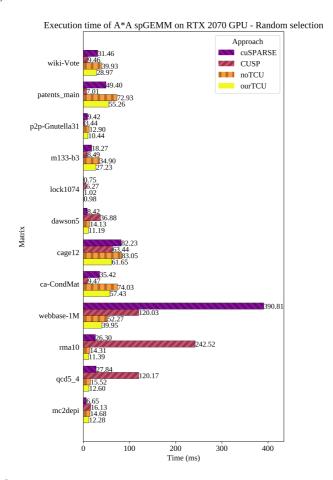

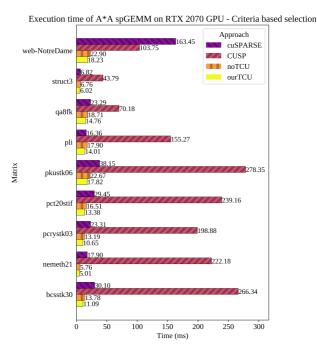

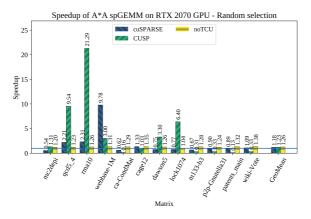

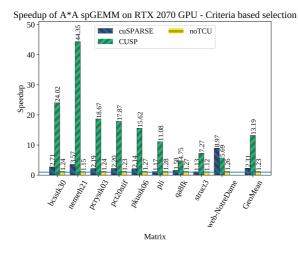

| Figure 3.8  | Absolute times of our approach on A*A spGEMM us-                        |

|             | ing randomly selected matrices 75                                       |

| Figure 3.9  | Absolute times of our approach on A*A spGEMM us-                        |

|             | ing matrices selected based on criteria 76                              |

| Figure 3.10 | Speedup of our approach on A*A spGEMM using ran-                        |

|             | domly selected matrices 77                                              |

| Figure 3.11 | Speedup of our approach on A*A spGEMM using ma-                         |

|             | trices selected based on criteria 77                                    |

#### LIST OF TABLES

# Table 2.1 Image characteristics. 33

Table 2.2 Average absolute difference of GPU approaches from high precision CPU implementation. Table 2.3 Average absolute difference of CPU approaches from high precision CPU implementation. Table 2.4 Mean absolute error (and standard deviation) for our dataset. Columns 2, 3, 4 compare the the deformed intra-operative image with the output of the registration for 3 methods: 1) affine, 2) non-rigid with NiftyReg, 3) non-rigid with our approach. The last column shows the mean absolute error between registration with NiftyReg and our approach. Table 2.5 Sum of squared errors (Left) on normalised outputs of affine registration and non-rigid registration with our approach and original NiftyReg, using the intraoperative image as reference. Structured Similarity Index Metric (Right) of the registration output, using the intra-operative image as reference). 1 pyramid level registration on GTX 1050. The table Table 2.6 shows the speedup of registration with our improved B-spline interpolation GPU approach. The iteration column shows the number of iterations of the cost function. 48 Table 2.7 3 pyramid levels registration on GTX 1050. The table shows the speedup of registration with our improved B-spline interpolation GPU approach. The iteration column shows the number of iterations of the cost function. Table 2.8 1 pyramid level registration on RTX 2070. The table shows the speedup of registration with our improved B-spline interpolation GPU approach. The iteration column shows the number of iterations of the cost function. 3 pyramid levels registration on RTX 2070. The table Table 2.9 shows the speedup of registration with our improved B-spline interpolation GPU approach. The iteration column shows the number of iterations of the cost function. Table 3.1 Matrix characteristics. We list the size of the matrix (number of rows (columns)), the density of the tiles, and the number of non-zeros of: the input (nnz(A)), the output (nnz(C)), the intermediate matrix (nnz(C)), the number of tiles  $(nnz(C_{tiles}))$ , and the number of tiles of the intermediate matrix (nnz( $\overline{C}_{tiles}$ )). The upper

> part corresponds to matrices that are commonly used in the literature, the bottom part to matrices we selected

based on their characteristics

#### ACRONYMS

1D

xviii List of Tables

2D 2-Dimensional

3D 3-Dimensional

AMG Algebraic Multigrid

API Application Programming Interface

AR Augmented Reality

ASIC Application Specific Integrated Circuit

AVX Advanced Vector Extensions

**BFS** Bread-First-Search

CC Compute Capabilities (of CUDA)

CNN Convolutional Neural Network

CPU Central Processing Unit

CR Correlation Ratio

CT Computed Tomography

**CUDA** Compute Unified Device Architecture

**ESC** Expand-Sort-Compress

FEM Finite Element Method

FLOPS Floating Point Operations per Second

FMA Fused Multiply-Add

FFD Free Form Deformation

**GEMM** General Matrix Multiplication

**GPGPU** General-Purpose Computing on Graphics Processing Units

**GPU** Graphical Processing Unit

HCC Hepatocellular Carcinoma

**HPC** High Performance Computing

IGS Image Guided Surgery

ILP Instruction Level Parallelism

ITK Insight Toolkit

List of Tables xix

LU Lower-Upper (decomposition)

LUT Look-Up-Table

MAC Multiplication-Accumulation

MAE Mean Absolute Error

MM Matrix Multiplication

MP MultiProcessor

MRI Magnetic Resonance Imaging

ms milliseconds

NCC Normalized Cross Correlation

NMI Normalized Mutual Information

nnz number of non-zero

nz non-zero

OpenCL pen Computing Language

PET Positron-emission Tomography

PSM Patient Specific Model

SAE Sum of Absolute Errors

SDK Software Development Kit

SIMD Single Instruction, Multiple Data

SM Symmetric Multiprocessor, equivalent to MultiProcessor

**SpGEMM** Sparse General Matrix Multiplication

**SSE** Streaming SIMD Extensions

SSE Sum of Squared Errors

**SSIM** Structured Similarity Index

TCU Tensor Core Unit

TH Texture Hardware (implementation)

TLP Thread Level Parallelism

TT Thread per Tile (implementation)

XX List of Tables

TTLI Thread per Tile with Linear Interpolations (implementation)

TV Thread per Voxel (implementation)

us Ultrasound

VCL C++ vector class library

VT Vector per Tile (implementation)

VV Vector per Voxel (implementation)

w.r.t with regards to

# Part I INTRODUCTION

1

### INTRODUCTION

## Contents

| 1.1 | A need for fast medical image regisration 4                    |

|-----|----------------------------------------------------------------|

|     | 1.1.1 High performance soft tissue navigation for liver cancer |

|     | intervention 4                                                 |

| 1.2 | Sparse Matrix-Matrix Multiplication 5                          |

| 1.3 | General-Purpose GPU computing 5                                |

|     | 1.3.1 Processing hierarchy 5                                   |

|     | 1.3.2 Memory hierarchy 6                                       |

|     | 1.3.3 Programming model 7                                      |

| 1.4 | Thesis overview 8                                              |

4 introduction

#### 1.1 A need for fast medical image regisration

Registration applies a geometric transformation to an object to transform it in a way that maximizes the similarity with a different view of the same object or with a different object entirely.

Objects are entities in 3D and 2D images. We obtain 3D images from tomographic modalities such as: CT, MRI, PET etc. 2D images are obtained from projections such as X-rays or individual cuts such as mode-B ultrasound. In medical applications each image depicts an anatomical region. The two views can come from the same patient which constitutes a problem of intra-patient registration, or they can come from different patients (inter-patient registration).

The inputs of a registration algorithm are the two images that you want to register, and the output is a geometric transformation, which maps the points in one image to the corresponding points in the other. The determination of an appropriate similarity criterion is specific to the domain of the images, in our case the human anatomy. For the registration to be useful, the mapping it produces must be able to assist medical doctors in the diagnosis and clinical treatment.

Registration plays a fundamental role in computer-assisted surgery in which preoperative medical images and graphic models are registered with the patient's anatomy during surgery. Registration techniques demand a high amount of computation on large amounts of data, i.e., execution time can be quite long extending the surgery time and increasing the risk for complications for the patient.

Therefore, image requires heterogeneous parallel computing. Thanks to the use of massively parallel structures, not only the execution times are significantly decreased but also the resolution of the images can be increased.

#### 1.1.1 High performance soft tissue navigation for liver cancer intervention

Primary liver cancer, typically caused by Hepatocellular Carcinoma (HCC), is the fifth most frequent cancer and the third most frequent reason of mortality by cancer [33]. In addition, the liver is a common target of metastases from other cancers, e.g., colorectal metastasis, with more than 100000 liver metastases in Europe [35]. The most common treatment for HCC is hepatic resection, which removes the tumor plus a safety margin from the liver, while saving as much of the healthy tissue as possible. However, not many patients are eligible for a resection. Therefore, it is vital to progress towards minimally-invasive methods that will increase the eligibility of patients and improve the survival prognosis [45].

HiperNav (High performance soft tissue navigation) project [45] aims to provide medical doctors with new tools for image-guided minimally invasive surgery. This thesis is encompassed within the HiperNav project and focuses

on the high performance computing (HPC) for image registration. As the main HPC platform we use GPUs.

#### 1.2 Sparse Matrix-Matrix Multiplication

In Image Guide Surgery we usually have a Patient Specific Model (PSM) which is created by CT, MR and other image modalities captured before the surgery. During the surgery the position of the patient on the operation table can be different than the one used when capturing the images. Furthermore, cutting, contact, inflation of the abdominal area during minimally invasive procedures like laparascopic surgery and ablation can deform the liver significantly. For this reason, we need to fuse the previously created PSM with live data that we capture during the surgery.

VESSEL REGISTRATION CT and MR scanning requires very specific conditions and facilities and usually is impractical during a surgery, unlike US which only requires a probe. Using the doppler mode of US, we can capture the shape of the vessels and subsequently use registration to find the location of the US in the PSM. However, vessels occupy only a small number of the image pixels, and therefore we have to deal with sparse images (i.e., images in which only a very small percentage of pixels contains valuable information). To that end, we are working on Sparse General Matrix Multiplication (SpGEMM). SpGEMM can facilitate the convolution stage of CNNs with sparse vessel images as inputs or graph matching operations.

#### 1.3 General-Purpose GPU computing

Graphics Processing Units (GPUs) typically process computer graphics. The use of a GPU for generic computational workloads is called General-Purpose GPU computing. CUDA [80] is a parallel computing framework and an API that provides easy access to the general purpose graphics processing unit (GPGPU) functionality of NVIDIA GPUs. In this section, we give a short introduction to the concepts of CUDA architecture that we use in this work.

#### 1.3.1 Processing hierarchy

A CUDA GPU is a multicore system, with a few tens of processing cores, which are called *MultiProcessors* (*MPs*) or Symmetric Multiprocessors (SMs). GPUs before with Compute Capabilities (CC) less than 7.x include cores for fp32 arithmetic, whereas the recent Volta and Turing architectures additionally include cores for integer arithmetic and tensor cores for matrix operations [82]. Figure 1.1 illustrates a part of the architecture of the SM on Turing GPUs. We can see the distribution of the processing cores.

Each SM deploys multiple *threads* which operate on data, similar to CPU threads. These threads are organized in groups of 32 threads, called *warps*. All threads that belong to the same warp execute the same instruction in lock-

6 Introduction

Figure 1.1 A part of the SM of Turing architecture that shows the distribution of int32, fp32 and tensor cores, as depicted in Turing whitepaper [82].

step. There are three characteristics that make GPU threads different from CPU threads: a) They work in lower frequencies, b) they are many more in number (> 1000), and c) they follow the SIMD (Single instruction, multiple data) model of the Flynn taxonomy [80].

#### 1.3.2 *Memory hierarchy*

CUDA GPUs deploy a multi-level memory hierarchy (Figure 1.2). Input and output data stay to the larger but slower off-chip memory, whereas frequently used data remain to the faster but smaller on-chip memory. Threads can access data from off-chip memory using three different memory spaces, optimized for different types of access. First, *global memory* stores the input and output data. Second, *texture memory* is optimized for texture processing. Three characteristics of texture memory are: a) it is read-only, b) it is optimized for spatial accesses, and c) dedicated hardware units for linear interpolation use the texture memory. Third, *constant memory* is a read-only memory which we use to store constants [80].

CACHES A CUDA GPU also has small, fast on-chip caches to reduce the cost of repeating data movements from off-chip memory. Four notable caches are: a) *shared memory*, a software-managed cache, b) *L1 cache*, a hardware-managed cache for global memory, c) *texture cache* for texture memory and d) *constant cache* for constant memory [80].

**REGISTERS** Each thread has access to its own *registers*, which are faster than shared memory and other caches. For any instruction (arithmetic, logical, etc) the input and output data *must* be in registers [80].

#### Memory hierarchy in CUDA

Figure 1.2 Memory hierarchy in CUDA. As we go up the pyramid, memory becomes more expensive and the bandwidth increases. As we go down the pyramid, memory becomes bigger and latency increases.

#### 1.3.3 Programming model

CUDA groups threads in *blocks* and each CUDA program can have many blocks of threads. Blocks can contain up to 1024 threads. The GPU schedules blocks to SMs, where the blocks stay until completion [80]. Constant and global memory are common for all blocks, whereas shared memory / L1 cache is private to each block [80].

8 introduction

#### 1.4 Thesis overview

This dissertation is organized in five chapters. The first chapter introduces the necessity for fast medical image registration and the utility of sparse matrix multiplication in medical computing. The second and third chapters present the two main parts of this dissertation. The first part focuses on our work on GPU acceleration of B-spline interpolation in the context of medical image registration. The second part focuses on our work on GPU acceleration of spGEMM. Both parts are presented in a similar way. We start by presenting the motivation and objectives. We continue with background and related work. Then we demonstrate our methods, followed by comprehensive results sections. Finally, we conclude each part and give some insights for future work. The last two chapters discuss our work and outline the conclusions and contributions of this work.

# Part II

# $\begin{array}{c} \text{B-SPLINE INTERPOLATION FOR IMAGE} \\ \text{REGISTRATION} \end{array}$

# ACCELERATING B-SPLINE INTERPOLATION AND IMAGE REGISTRATION

# Contents

| 2.1  | Motivation 12                                                  |

|------|----------------------------------------------------------------|

|      | 2.1.1 B-spline interpolation and previous work 12              |

|      | 2.1.2 Pneumoperitoneum compensation 13                         |

| 2.2  | Objectives 14                                                  |

| 2.3  | Background 15                                                  |

| ,    | 2.3.1 Medical image registration 15                            |

|      | 2.3.2 B-spline interpolation 16                                |

| 2.4  | Related Work 19                                                |

|      | 2.4.1 Medical image registration on GPU 19                     |

|      | 2.4.2 B-spline interpolation in medical image registration 21  |

| 2.5  | Optimizing B-spline interpolation 23                           |

|      | 2.5.1 Overview 24                                              |

|      | 2.5.2 Thread per Tile (TT) 24                                  |

|      | 2.5.3 Thread per Tile with Linear Interpolations (TTLI) 27     |

|      | 2.5.4 Implementation details of TT and TTLI 28                 |

|      | 2.5.5 Application of our methodology on CPUs 30                |

|      | 2.5.6 Off-chip memory to on-chip memory data movement 32       |

| 2.6  | Evaluation Methodology 33                                      |

|      | 2.6.1 Dataset 33                                               |

|      | 2.6.2 Accuracy 34                                              |

|      | 2.6.3 Performance 34                                           |

|      | 2.6.4 Parameters 34                                            |

|      | 2.6.5 Implementations we compare with 35                       |

| 2.7  | Results and Analysis 35                                        |

|      | 2.7.1 Accuracy <u>35</u>                                       |

|      | 2.7.2 Performance on GPU 36                                    |

|      | 2.7.3 Performance on CPU 40                                    |

| 2.8  | Clinical validation of image registration implementation 41    |

|      | 2.8.1 Experiment 1: Validation in liver patient-specific phan- |

|      | tom. 42                                                        |

|      | 2.8.2 Experiment 2: Validation in porcine study. 43            |

|      | 2.8.3 Qualitative assessment of the registration procedure 43  |

|      | 2.8.4 Quantitative assessment of the registration procedure 44 |

|      | 2.8.5 Performance evaluation on clinical data 46               |

|      | 2.8.6 Memory requirements 50                                   |

| 2.9  | Conclusion 50                                                  |

| 2.10 | Future work 51                                                 |

#### 2.1 Motivation

Image Guided Surgery (IGS) aims to provide surgeons with navigation capabilities for better, safer procedures and improved surgical outcome through better visualization [10]. Surgical navigation can guide surgeons through the use of volumetric images, such as Computed Tomography (CT), Magnetic Resonance Imaging (MRI) or UltraSonography (US) [12], and instrument tracking technologies [108]. As an example, during minimally invasive surgery, the laparoscope camera video feedback can be augmented with reprojected CT or MRI scans, a process known as Augmented Reality (AR) [68, 94]. However, the accuracy of image guided surgery is often undermined by movements of the organs, for example, manipulations performed by the surgeon such as resection (cutting) of ligaments during mobilization. Hence, due to the non-linear behaviour of soft tissue deformation, rigid or affine transformations are not sufficient to correctly reproduce the movements of the organs. Therefore, non-rigid registration [106] is a more accurate way to model more complex deformations and is necessary to model soft tissue deformations.

Non-rigid registration through Free Form Deformation (FFD) [96], based on cubic B-spline interpolation, can provide a suitable solution for non-rigid image registration tasks. By manipulating a grid of control points, the shape of the underlying 3D object (e.g., an organ captured by the laparoscope camera) can be changed using a smooth and C<sup>2</sup> continuous (i.e., continuous up to second order derivatives) transform. One important property of B-splines is that they deploy local support (i.e., each control point affects only its neighborhood), and therefore, the workload can be balanced among the execution threads running on multi-core processors.

Cubic B-spline interpolation or, simply, B-spline interpolation is a form of interpolation that is more accurate than the conventional linear interpolation, as B-spline interpolation better approaches the ideal sinc function interpolation [98, 113]. Many image processing (e.g., non-rigid registration) and visualization tasks [98] benefit from the additional accuracy. In this work we focus on the 3D version of B-spline interpolation, also called tricubic interpolation. B-spline interpolation is useful for handling 3D medical images and consequently IGS.

Registering pre-operative (before the surgery) models to intra-operative (during the surgery) reconstructed surfaces or to US images during IGS is particularly demanding. Graphics Processing Units (GPUs) can help achieve real-time requirements of IGS, as they offer massive computation performance in comparison to CPUs. A GPU deploys thousands of execution threads, which operate on large batches of data, and provide high throughput. GPU's multithreaded architecture makes it much more power-efficient than a CPU on multithreaded workloads [80]. As a result, GPUs can improve the performance of B-spline interpolation significantly [98, 104].

#### 2.1.1 B-spline interpolation and previous work

The intensive *data movement* of a large number of input samples between the memory and the GPU cores is the main bottleneck of cubic B-spline interpo-

2.1 MOTIVATION 13

lation implementations on a GPU [104]. Sigg et al. in [104] and Ruijters et al. in [98] achieve a substantial reduction in the number of input samples by representing the weighted sums as trilinear interpolation and utilizing the interpolation unit of the GPU texture unit. Later, Ellingwood et al. in [28] and Du et al. in [26] use GPU implementations of B-spline interpolation to improve the performance of registration. They improve input sample loading by aligning the control grid with the voxel grid of the volume [26, 28, 100]. However, even including the most recent improvements, the performance of B-spline interpolation is still limited by memory bandwidth, as indicated by our preliminary profiling results.

#### 2.1.2 Pneumoperitoneum compensation

This works focuses on image guide liver surgery. As a test case for image registration we use pneumoperitoneum, i.e., the inflation of the patient's abdomen during laparoscopic surgery. Pneumoperitoneum, along with the new position of the patient on the surgical table, deforms the shape of the liver [44, 54]. Consequently, on the day of the surgery, the liver has different shape than that of the pre-operative CT or MRI scans. The deformed shape causes great inaccuracy within IGS systems for laparoscopic liver resection surgery, because the plan of the surgery is based on the initial (pre-operative) CT or MRI scan. In order to correct the inaccuracies, we have to capture new images during the surgery and to match them to pre-operative scans with the help of non-rigid registration [89]. The drawback is that registration is computationally demanding, therefore it would benefit from an improved GPU approach. In Figure 2.14 we will show the role of image registration in matching the images before and after pneumonoperitoneum. We will also show the main components of registration. *Deformation*, which is the target of our optimizations, is highlighted.

#### 2.2 Objectives

The primary objective of this work is to accelerate medical image registration using General-Purpose computing on Graphics Processing Units (GPGPU). To that end, we form the following secondary objectives:

- Optimize one of the most computationally demanding parts of FFD nonrigid registration, i.e., B-spline interpolation.

- Test the performance of B-spline registration in regards to execution time and accuracy in a realistic medical scenario. In order to achieve this, we need to:

- Create a dataset of CT/MR images to test registration.

- Integrate our B-spline interpolation methodology in an existing registration library, NiftyReg [74]. NiftyReg is used as reference in recent works [89].

2.3 BACKGROUND

#### 2.3 Background

In this section, we first give an overview of medical image registration and deformation fields. Second, we introduce B-spline interpolation and the properties that play an essential role in our proposed optimizations.

#### 2.3.1 Medical image registration

The task of medical image registration is to find the correspondences between two medical images and bring them to the same coordinate system. Two common medical scenarios that we need registration for are: a) to find the correspondences between images that are used during planning of the surgery (i.e., diagnostic images) and images acquired during the surgery, and b) to find correspondences between images of different modalities that we acquire during the surgery (e.g., among US and stereoscopic camera feedback [68], [107]). Generally, image registration finds application in planning, navigation, data fusion, visualization, segmentation based on an atlas, automatic tissue recognition etc [102, 103].

**REGISTRATION INPUTS** Image registration requires a pair of images as input, the *reference* (also called *static*) image and the *target* (also called *floating* or *moving*) image. The target image needs to be transformed to match the shape and structures of the reference image.

#### PNEUMONOPERITONEUM COMPENSATION FOR LIVER REGISTRATION

Our goal in this work is to use registration to match the shape of the liver between scans that are acquired before and after pneumonoperitoneum, as in Figure 2.1. In this work, the targeted application is non-rigid registration, due to the viscoelastic nature of the liver [89].

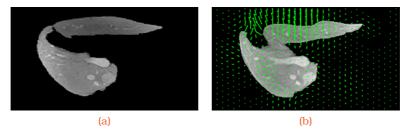

Figure 2.1 MRI scans, (Intra-modality) of porcine liver without (left) and with (right) pneumoperitoneum in preparation for minimally invasive surgery

### Deformation fields

Usually, we represent non-rigid transformation as a *deformation* or *displacement* vector field, which connects the corresponding points of the reference and the floating image space.

Figure 2.2 shows an example of a displacement field created after executing registration on the pig liver images described in Section 2.8.2. Figure 2.2a illustrates the floating image, whereas Figure 2.2b illustrates the displacement field overlaid over the reference image. The arrows connect the voxels of the reference image with the correspondent voxels of the floating image. Typically, medical images are 3D. Therefore, the deformation field consists of 3D vectors in the 3D space.

Figure 2.2 (a) Liver of a pig before registration, (b) The generated deformation field overlaid on top of the reference image

### 2.3.2 *B-spline interpolation*

In non-rigid registration, the interpolation of a deformation field describes the transformation. We prefer B-spline interpolation because it requires data only in a small neighborhood around the point of interest, thus reducing the computational complexity for large medical images [102]. B-spline interpolation is one of the most time consuming steps of the registration [74]. Therefore, by optimizing B-spline interpolation, we increase the total performance of image registration. Although the application in this work is image registration, B-spline interpolation can also be used for general image processing, like zooming and geometrical image transformation [48, 113]. In this section we provide the theoretical background of B-spline interpolation and we define the tiles, groups of elements with common properties.

### B-spline interpolation theory

It is easier to understand B-spline *interpolation* by comparison to linear interpolation. With conventional linear interpolation we have two known points and we want to estimate the *interpolant*, a third point between the other two. The value of the interpolant is the result of a first order function of the two known points (i.e., two arguments). Similarly, in B-spline interpolation, we have a number of known points and we would like to estimate the interpolant. B-spline based interpolation requires 4<sup>N</sup> (where N is the image dimension) neighboring known points as function arguments (owing to the limited sup-

2.3 BACKGROUND 17

port of B-splines). In comparison to linear interpolation, the function of the four known points is of the third order (cubic). This function is called the B-spline basis function and it is where the name B-spline interpolation comes from [98]. The known points are called *control points*, and they are arranged in a *control point grid* over the entire image.

In this work we work with 3D images in the context of medical imaging, therefore we focus on the theoretical background required for 3D images. We denote the elements of a  $n_x \times n_y \times n_z$  control point grid, with uniform spacing  $\delta_x \times \delta_y \times \delta_z$ , as  $\phi_{i,j,k}$ . The domain of the image volume is in the x,y,z coordinate space. We denote the function that calculates the interpolants as T(x,y,z) [96]:

$$T(x,y,z) = \sum_{l=0}^{3} \sum_{m=0}^{3} \sum_{n=0}^{3} B_{l}(u) B_{m}(v) B_{n}(w) \phi_{i+l,j+m,k+n}$$

(2.1)

where  $\mathbf{i} = \lfloor x/\delta_x \rfloor - 1$ ,  $\mathbf{j} = \lfloor y/\delta_y \rfloor - 1$ ,  $\mathbf{k} = \lfloor z/\delta_z \rfloor - 1$ ,  $\mathbf{u} = x/\delta_x - \lfloor x/\delta_x \rfloor$ ,  $\mathbf{v} = y/\delta_y - \lfloor y/\delta_y \rfloor$ ,  $\mathbf{w} = z/\delta_z - \lfloor z/\delta_z \rfloor$ . B are the B-spline basis function derived weights and  $\phi$  are the control points.

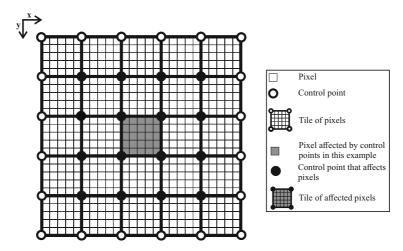

#### Tiles

Tiles are logical groups of voxels (voxel is the analogue of pixel in 3D space) that share common properties. Let us denote as  $\delta_{\alpha} \in \mathbb{Z}$  the spacing in voxels, where  $\alpha$  is one of x, y, z (for each of the three dimensions). Then, from Equation (2.1), we make two observations. First,  $\lfloor \alpha/\delta_{\alpha} \rfloor - 1$  increases by one every  $\delta_{\alpha}$  elements in the direction of  $\alpha$ . Second,  $\alpha/\delta_{\alpha} - \lfloor \alpha/\delta_{\alpha} \rfloor$  is periodic with period  $\delta_{\alpha}$ . Based on these two observations, we form tiles of  $\delta_x \times \delta_y \times \delta_z$  dimensions and we derive the following two important properties:

- The same set of control points affects all voxels inside the tile. In the case

of B-splines, there are four neighboring control points in each direction

that affect the voxels inside the tile.

- 2. B-spline weights depend only on the relative distance from the coordinate origin of the tile. We emphasize that when the voxel and control point grids are aligned, there is always the same number of equally spaced voxels between two control points. As a result, when the grids are aligned, all tiles in this voxel grid use the *same* set of B-spline weights.

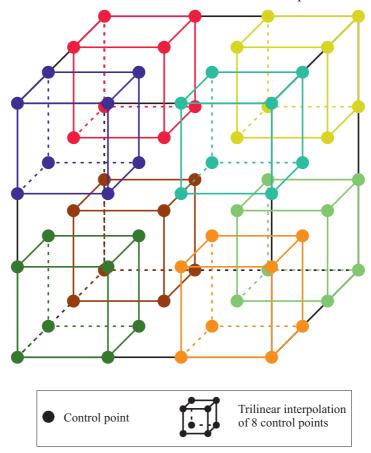

From Equation (2.1), it follows that  $4 \times 4 \times 4$  control points, forming a cube (Figure 2.3), affect each voxel (and consequently tile). In general, in N-dimensional images,  $4^N$  control points affect each voxel. Figure 2.4 highlights the tile properties of a 2D example. We present the 2-dimensional case because it is easier to understand. In this figure, the gray-colored area highlights the pixels that form a tile. The filled black circles delineate the  $4 \times 4$  control points that affect this tile.

We utilize tiles and their properties in our proposed optimization scheme to significantly reduce memory traffic between off- and on-chip memory.

The 4x4x4 neighboring control-points each thread requires. The 2x2x2 sub-cubes delineate trilinear interpolations.

Figure 2.3 Cubes depicting the grouping in trilinear interpolations for a 3D control point grid

Figure 2.4 Tile properties of a 2D image

2.4 RELATED WORK

### 2.4 Related Work

In this section we provide an overview of GPU-based medical image registration.

## 2.4.1 Medical image registration on GPU

In the following paragraphs we give a short review of medical image registration on GPU.

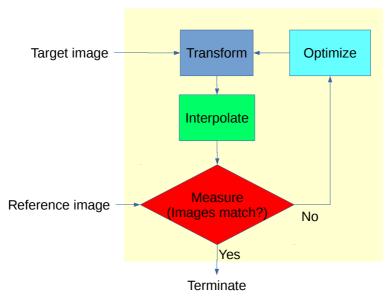

### Basic components of registration

The registration procedure can be divided into four basic components. These components are: 1) transformation, 2) interpolation, 3) measurement, and 4) optimization (Figure 2.5).

Figure 2.5

The building blocks of registration.

#### Transformations

The transformation component produces a transformation function that converts the target image based on parameters that the optimization component sets. Transformations can be classified as linear or non-linear (deformable). For linear transformations we use rigid and affine registration, whereas for non-linear transformations we use non-rigid registration [102]. Traditionally, we first apply rigid and affine transformations to capture the global deformations and, then, non-rigid transformation to capture the more fine-grained local transformations.

RIGID TRANSFORMATION Rigid transformation rotates and translates the target to best match the reference. The target object maintains its size and shape. These methods apply rotation and translation matrices to all pixels (or block of pixels) in a way that maximizes a similarity criterion [30, 90, 101].

AFFINE TRANSFORMATION Affine transformation extends rigid transformation by adding additional transformations, like scaling, shearing etc. Points and lines from the target match points and lines of the reference, respectively, and parallel lines remain parallel. Similarly to rigid, these methods apply small transformation matrices to the images [65, 74, 86].

DEFORMABLE TRANSFORMATION Rigid and affine transformations are fast and reliable for rigid or relatively rigid tissue (e.g. brain which has limited movement in the cranium, bones etc). Nevertheless, they do not adapt well to elastic deformations of more fluid tissues, e.g., breast [96, 102] or liver [45, 122].

A popular category of deformable registration is Demons, which is based on optical flow [103, 112] and is accelerated by CUDA [50, 75]. Another popular category is the one that is based on the parameterization of the displacement field by a number of control points [74, 96, 122]. Parametric methods often achieve better results than other methods when registering images of multiple modalities [103].

### Interpolation

After the transformation component defines the desired transformation of the pixels, an interpolation (or resampling) stage is necessary to determine the actual pixel intensities of the to-be-transformed image. Nearest neighbor, linear interpolation, B-spline interpolation, quadratic interpolation, Gaussian interpolation are possible interpolation methods [63]. Nearest neighbor is the fastest but gives the greatest error. The most commonly used is linear interpolation, with a good balance between computation time and error. B-spline interpolation has excellent performance in keeping the characteristics of the original image with a slight decrease in performance [63, 113].

### Measurement

After transformation and resampling we have to measure the similarity of the transformed image to the reference image. Some of the common similarity measures include Sum of Absolute Errors (SAE), Normalized Cross Correlation (NCC), Correlation Ratio (CR) [95] and Normalized Mutual Information (NMI) [101]. Although SAE and NCC are relatively trivial to implement on GPU [38], this is not the case for NMI and CR.

NORMALIZED MUTUAL INFORMATION Normalized mutual information is one of the most popular methods for registration with multiple modalities [91] and a performance critical component of the registration workflow [27]. NMI requires the computation of a joint image histogram. Histograms are

2.4 RELATED WORK 21

difficult to implement on GPUs because the access to the bins requires synchronization. Shams et al. avoid synchronization and atomic operations using sorting [101], whereas Gómez-Luna et al. employ many subhistograms to minimize conflicts [36].

CORRELATION RATIO Correlation ratio offers comparable results to NMI but, unlike NMI, needs only a 1D histogram, which makes CR more suitable for GPU implementations [64].

### Optimization

If the measurement component indicates that the matching between target and reference images is not sufficient according to the selected convergence criterion, we call the optimization component. Optimization searches the transformation parameter space to find a transformation that will improve the previous result. According to [102] the optimization can be categorized to gradient-based and gradient-free.

GRADIENT-BASED AND GRADIENT-FREE Gradient-based methods calculate the partial derivatives of a cost function in order to find the minimum of the cost function. A typical gradient-based method is gradient descent [93]. An example of gradient-free GPU approach is [43], where they use a symmetric explicit search at each pixel to find the neighbor that maximizes a pointwise mutual information metric. Typically, gradient-based methods converge in fewer iterations [102].

PARALLELIZATION The optimization component itself usually is inherently serial (e.g., a partial derivative that has to "wait" for the previous partial derivative). Moreover, in comparison to other steps of registration, optimization does not affect the execution time a lot, and therefore parallelizing the optimization is usually not practical [102, 103]. What is important with regards to improving the execution time of registration is the number of iterations until convergence.

#### 2.4.2 B-spline interpolation in medical image registration

Since one of the most suitable applications of B-spline interpolation is nonrigid registration for medical images, several attempts happened to accelerate B-spline interpolation for this context. Modat et al. [74], in NiftyReg library, optimize for GPU the FFD registration that Rueckert et al. [96] present. They observe that the most computationally demanding step is B-spline interpolation, which is used for the calculation of the deformation field.

Alignment of the control point grid with the voxel grid of the volumetric scan significantly improves the computational efficiency of B-spline interpolation. By aligning the grids, voxels are organized in tiles, which present beneficial properties that reduce redundant operations. To our knowledge, Shackleford et al. in [100], in their work on B-spline registration methods, are the first that use tile properties to reduce redundant operations and memory transfers.

Later, tile properties were also used by Ellingwood et al. in [28] and by Du et al. in [26] to improve the performance of their non-rigid registration algorithm.

PREFILTERING A drawback of acquiring a reconstructed function with cubic B-spline interpolation is that the function may not pass through the sample points, and thus the output may be more smoothed than necessary. One way to avoid over-smoothing is to add a prefiltering step before the B-spline interpolation step. For this reason, Ruijters et al. in [97], additionally to B-spline interpolation, they implemented on GPU the prefiltering step presented by Thévenaz et al. in [111]. Shortly after, Champagnat et al. [15] replaced the IIR filter filter of [97] with a FIR filter to improve the GPU performance of smaller image outputs. Ruijters et al. provide online as a library their GPU implementation of the prefiltering step along with cubic B-spline interpolation. This library is still actively used in recent literature [5, 14] etc. We will not use prefiltering in our implementations because it is not used in the calculation of the deformation field. Nevertheless, our approach can use the same prefiltering step from the literature. However, our approach is a suitable replacement for the interpolation step of the approaches of the previous paragraph.

In the following two sections we introduce two state-of-the-art GPU B-spline interpolation methodologies and their respective implementations.

### Texture Hardware (TH)

The work by Sigg et al. [104] is one of the first attempts on acceleration of B-spline interpolation using interpolation hardware of the GPU. Their approach utilizes the texture unit of the GPU, a special unit usually used for computer graphics, that is accessed through easy to use Application Programming Interfaces (APIs). They use the texture hardware unit to reduce the number of memory transfers by loading only the result of the trilinear interpolation, instead of loading the eight control points that the trilinear interpolation needs. Later, Ruijters et al. [98] implemented this method in CUDA. This method reduces memory transfers from off-chip memory significantly [98, 104].

If we define the dimensionality of the input image as N, each voxel is affected by the  $4^{\rm N}$  control points surrounding it. However, if we use the texture unit to calculate trilinear interpolation, only  $2^{\rm N}$  loads are required [104]. This is particularly useful for higher dimensional inputs, such as 3D medical images, where the required number of memory transfers from global memory is reduced from 64 loads to 8 loads of trilinear interpolation results. Figure 2.3 illustrates the control points of 3D input. Without using the trilinear interpolation hardware, we have to load all  $4\times4\times4$  control points in order to calculate each voxel. With trilinear interpolation hardware, we have to load only the results of trilinear interpolation of  $2\times2\times2$  sub-cubes. Each such sub-cube has a different color in the figure.

Hardware interpolation is fast but it brings two problems. First, its accuracy is very low, with only eight bits holding the interpolation result [80]. Second, although the number of coefficient loads are drastically reduced, these loads are dependent on the absolute position of each voxel. Therefore, there is no way to cache them for reuse by nearby voxels because the fetched values are unique. Texture Hardware B-spline interpolation is included in an easy-to-use library by Ruijters et al. [97] and is used by recent works [14].

By doing the trilinear interpolation in software, instead of hardware, we can create different thread assignment schemes that can increase the overlap between neighboring threads significantly, achieving even fewer memory transfers than TH. Moreover, we can take advantage of FMA instructions to decrease computational complexity and avoid the inaccuracies caused by the inherently low precision of trilinear interpolation of the texture unit of the GPU [80].

## Thread per Voxel (TV)

The basic mechanism of this approach is that each CUDA thread is assigned to a single element in a straightforward way, e.g., a thread for each voxel in the case of 3D images. Specifically, for each voxel position of the reference image one thread calculates the deformation vector using Equation (2.1). NiftyReg [74] uses this straightforward parallelization. This method can be further enhanced by utilizing the tile properties of Section 2.3.2. In this case, one or more blocks are assigned to each tile, with one thread for each voxel of the tile, as Ellingwood et al. [28] do. Since all voxels inside a tile need the same control points, these control points are loaded from global memory only once and are stored in shared memory for faster access.

The thread assignment scheme of this approach is more straightforward, and therefore easier to implement. However, for maximum performance, the tile size should be a multiple of the warp size (32 threads for CUDA). Otherwise, the rest of threads of each warp remain inactive due to hardware limitation. Essentially, this means that the users of this approach are not free to select the tile size that best fits their needs, but they have to choose between a small number of presets.

NIFTYREG LIBRARY NiftyReg [74] is a lightweight open-source medical image registration library, which contains optimized implementations of B-spline interpolation, both for CPUs and GPUs. It is open-source and well-maintained, with competitive performance against other state-of-the-art implementations [62]. For this reason, it is commonly used as the reference state-of-the-art non-rigid registration (e.g., [89]). The GPU implementation uses the simple, straightforward thread-per-voxel scheme, i.e., no tile properties, LUTs, etc. The CPU implementation uses multi-core and vectorization optimizations and does minor utilization of tile properties. We started this work by profiling NiftyReg to find the impact of B-spline interpolation on the entire registration process. The profiling results show that B-spline interpolation takes 30% of the total execution time. The main bottleneck is the memory latency due to saturation of cache bandwidth when loading the control points. Therefore, our initial goal is to minimize the memory transfers from global memory to on-chip caches.

## 2.5 Optimizing B-spline interpolation

This section describes our GPU implementation of B-spline interpolation and explains the logic behind assigning one GPU thread per tile. We present the most important GPU optimizations in detail, along with the computation complexity analysis that leads to our fastest GPU method. Furthermore, we apply our methodology to CPU to show that it is applicable to other platforms.

Finally, we define the number of required memory transfers for the various B-spline interpolation implementations.

Within this study, the implementation of GPU parallelization is specific to 3D medical images (CT, MRI or US volumes). Therefore, analysis and implementations focus on the 3D case, unless otherwise specified. To facilitate understanding of this section, we emphasize that, in the case of 3D images, each voxel is affected by the control points in its local  $4 \times 4 \times 4$  cubic neighborhood. Consequently, all voxels that belong to a tile are affected by the same  $4 \times 4 \times 4$  neighborhood.

#### 2.5.1 Overview

The key optimizations of our GPU implementation of B-spline interpolation are two. First, an entire tile of voxels is assigned to a single GPU thread, in contrast to the one-thread, one-voxel paradigm. Figure 2.6b compares the thread assignment between TV and the proposed approach. With this assignment, we minimize: a) the reads from off-chip memory by maximizing the overlap of the input control points and, b) the cache accesses by keeping the input points in registers and reusing them by many voxels. Although registers are very fast, which significantly benefits the performance of our implementation, 3D medical images require a large amount of them, which limits the number of active GPU threads. Nevertheless, the reduced number of required memory transfers enables us to hide their latencies efficiently by overlapping them with independent arithmetic operations, a method commonly known as Instruction Level Parallelism (ILP). Second, we replace the weighted sum of the basic formula of B-spline interpolation with independent trilinear interpolations. We calculate these trilinear interpolations with FMA instruction of the GPU. FMA increases both accuracy and speed in regards to typical multiplication and addition.

### 2.5.2 Thread per Tile (TT)

In the following paragraphs we describe the optimizations utilized in the proposed implementations. We show how our input loading and register optimizations reduce memory accesses. To better display how are work improves over the state-of-the-art, we describe our optimizations by comparing to the methods of TV.

### Input loading optimization

The main idea of this optimization is to reduce loads from global memory by taking advantage of the overlap of neighboring tiles.

In a TV implementation, each block of threads works on a unique tile of voxels. Each block stores the required 4<sup>N</sup> control points (Section 2.3.2) in a unique shared memory area. Therefore, for each tile we need to move 4<sup>N</sup> control points from global memory to shared memory. Step 1, of the left part of Figure 2.7, illustrates the required transfers from global memory to shared memory for a 2D example. In this example, we have two tiles and each tile is assigned to

Figure 2.6 a) An example 2D grid with two tiles, b) Thread assignment for Thread per Voxel (left) and Thread per Tile (right) approaches. The different threads are represented by different shades of gray, which correspond to the numbers

one block. The figure shows that the amount of transfers from global memory to shared memory, that the two tiles require, is  $4 \times 4 + 4 \times 4$  control points each.

We want to reduce the required amount of transfers from global memory to shared memory. Two important observations derive from Equation (2.1). First, only the four neighboring control points in each direction of a Cartesian coordinate system affect each tile. Second, tiles that are consecutive in a direction require control points that are consecutive in the same direction. Therefore, there is overlap among neighboring tiles. Figure 2.6a illustrates two tiles that are consecutive in the x-direction. The first tile has its pixels and necessary control points highlighted with red color and the second with blue. The first tile requires the first  $4 \times 4$  area of pixels (the square defined by vertices Coo and C33), whereas the second requires a  $4 \times 4$  area that is shifted by one in the x-direction (the square defined by vertices Co1 and C34). In total, the two tiles require  $4 \times (4+1)$  pixels. Step 1, of the right part of Figure 2.7, illustrates the reduction in transfers to shared memory, with overlap in the x-direction. Two tiles require only  $4 \times 5$  control points. In a real case scenario, with overlap in all directions, the benefits are more pronounced.

In the general 3D case, the cubic  $4 \times 4 \times 4$  control point neighborhood of each of the consecutive tiles overlaps with a stride of one for each direction. In the general 3D case, a group of tiles of size  $l \times m \times n$  with overlap in the x, y, z -directions, needs  $(4+l-1) \times (4+m-1) \times (4+n-1)$  control points in total.

We observe that there is significant overlap of control points for neighboring tiles. Our thread per tile assignment scheme takes full advantage of the overlap to reduce the ratio of data movements per voxel. Our approach requires fewer transfers from global memory than both TH and TV methods, as we detail in Section 2.5.6.

Figure 2.7

Comparison of input loading and register optimization for Thread per Voxel (left) and Thread per Tile (right) for the two neighboring tiles of Figure 2.6

## Register optimization

The two main ideas of this optimization are: a) to load the control points for all voxels of the tile from shared memory only once, and b) to keep the loaded control points to registers, which are the fastest on-chip memory, until the thread exits.

In a TV implementation, threads belonging to the same block work on individual voxels of the same tile. For every voxel belonging to the tile, the corresponding threads need to access the exactly same area of shared memory as the other threads of the block, in order to load the same set of control points. Step 2, of the left part of Figure 2.7, illustrates the required transfers from shared memory to registers for a 2D example. In this example, each tile comprises four pixels and each pixel is assigned to one thread. The figure shows that four pixels require four transfers (from shared memory to registers) of sixteen control points each.

Shared memory is faster than global memory, but before the GPU can execute any instruction on the control points, each thread has to move the entire set of control points to its registers first (Section 1.3). Thus, we want to minimize transfers from shared memory to registers. We make two improvements. First, we assign one thread for the entire tile. For every voxel belonging to the tile, the corresponding thread needs to access the same shared memory area exactly

once, in order to load the control points. Second, we utilize register tiling. The thread keeps the control points to (the faster than shared memory) registers [115] until it processes every voxel of the tile. Step 2, of the right part of Figure 2.7, illustrates a drastic reduction in memory transfers. A tile of four pixels requires only one transfer of sixteen control points.

### Other optimizations

In this section we present other optimizations, that are not part of our key optimizations.

LOOK-UP-TABLES (LUTS) LUTs are tables that hold pre-calculated values, so that we do not have to calculate them during execution of the program, saving computational resources for other tasks. Based on the second property of the tiles (Section 2.3.2), the B-spline basis functions weights remain the same among tiles when having uniform (aligned) grids. Therefore, they can be stored in LUTs in constant memory.

**SKIPPING SHARED MEMORY** According to Perrot et al. [88], at least for the case that the input is overlapping, it may be beneficial to load to registers directly, instead of first loading to shared memory and then from shared memory to registers. The control points needed by each group of tiles can be stored to registers directly (using instead only the hardware-managed caches). With this approach, we avoid pointer arithmetics and synchronization that the management of shared memory requires.

#### 2.5.3 Thread per Tile with Linear Interpolations (TTLI)

We extend TT by reformulating the triple sum of Equation (2.1) to *trilinear* interpolations. The basic idea is that a linear interpolation can replace an addition of two weighted summands. We can extend this to three dimensions, where we combine eight summands to a trilinear interpolation [104].

We calculate trilinear interpolation as a combination of seven linear interpolations (we do not use the hardware interpolation unit). Linear interpolations have the form a+w\*(b-a), so they can take advantage of FMA instructions. FMA instructions combine extended precision multiplication with addition. The benefits of FMA are two: First, owing to the increased precision of the intermediate product, the result is more accurate. Second, owing to the combination of multiplication with addition in the same instruction, the computational complexity is lower.

Figure 2.3 illustrates the  $4 \times 4 \times 4$  neighborhood of control points each voxel requires. Each one of the  $2 \times 2 \times 2$  colored sub-cubes of control points corresponds to one trilinear interpolation. For each voxel in the tile, the respective thread first calculates each one of the eight trilinear interpolations corresponding to each one of the colored cubes. Then, the thread calculates one last trilinear interpolation with the eight results of the eight trilinear interpolations that are corresponding to each one of the colored cubes.