# **Development of a Multichannel Wideband Radar Demonstrator**

By

# Kevin Carr

Submitted to the graduate degree program in Department of Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Master of Science.

Dr. Carl Leuschen, Chair

Committee members

Dr. Fernando Rodriguez-Morales, Co-chair

Dr. James Stiles

Date defended: \_\_\_\_\_ November 12, 2019

The Thesis Committee for Kevin Carr certifies that this is the approved version of the following thesis :

Development of a Multichannel Wideband Radar Demonstrator

Dr. Carl Leuschen, Chair

Date approved: \_\_\_\_\_ November 12, 2019

## Abstract

With the rise of software defined radios (SDR) and the trend towards integrating more RF components into MMICs the cost and complexity of multichannel radar development has gone down. High-speed RF data converters have seen continuous increases in both sampling rate and resolution, further rendering a growing subset of components in an RF chain unnecessary. A recent development in this trend is the Xilinx RF-SoC, which integrates multiple high speed data converters into the same package as an FPGA. The Center for Remote Sensing of Ice Sheets (CReSIS) is regularly upgrading its suite of sensor platforms spanning from HF depth sounders to Ka band altimeters. A radar platform was developed around the RFSoC to demonstrate the capabilities of the chip when acting as a digital backend and evaluate its role in future radar designs at CReSIS. A new ultra-wideband (UWB) FMCW RF frontend was designed that consists of multiple transmit and receive modules with a 6 GHz bandwidth centered at 5 GHz. An antenna array was constructed out of Vivaldi elements to validate radar system performance. Firmware developed for the RFSoC enables radar features such as beam forming, frequency notching, dynamic stretch processing, and variable gain correction. The feature set presented here may prove useful in future sensor platforms used for the remote sensing of snow, soil moisture, or crop canopies.

## Acknowledgements

This work was funded by the Department of Energy's Kansas City National Security Campus, operated by Honeywell Federal Manufacturing and Technologies, LLC, under contract number DE-NA0002839.

I would like to acknowledge the following people who made this work possible.

None of this could have been done without the teaching and guidance of my advisors Dr. Carl Leuschen and Dr. Fernando Rodriguez-Morales, who gave me the opportunity to working at CReSIS and included me on this project. They were always willing to answer my questions and provided extensive support throughout this project and beyond.

I would also like to thank Dr. James Stiles for providing a solid education in microwave engineering through all of the courses he taught.

Thanks to Dr. Daniel Gomez Garcia Alvestegui for bringing me up to speed on intricacies of radar design and always being able to answer questions.

Thanks goes to all of the CReSIS staff who keep everything running and help maintain a great work environment. Paulette Place trained me on proper electronic assembly and electrical wiring, Aaron Paden took care of the machining involved in this project, and Jennifer Laverentz cleared away any and all administrative hurdles during my time at CReSIS.

Thanks to Dr. Ambrose Wolf, Sean Garrison, and Adam Ferguson for continuing the radar consortium.

To Jill and Scott Carr, for always being there and supporting me.

# Contents

| 1 | Introduction |                                   |                                      |    |  |  |

|---|--------------|-----------------------------------|--------------------------------------|----|--|--|

|   | 1.1          | Background                        |                                      |    |  |  |

|   |              | 1.1.1                             | Overview of CReSIS Projects          | 1  |  |  |

|   |              | 1.1.2                             | Summary of FMCW Operating Principles | 2  |  |  |

|   | 1.2          | Thesis                            | Overview                             | 5  |  |  |

| 2 | Mul          | tichanno                          | el Radar System Design               | 7  |  |  |

|   | 2.1          | Digital                           | Backend Hardware                     | 8  |  |  |

|   | 2.2          | Transm                            | itter Design and Description         | 10 |  |  |

|   |              | 2.2.1                             | Transmitter IF Chain                 | 11 |  |  |

|   |              | 2.2.2                             | Switched Filter Bank                 | 12 |  |  |

|   |              | 2.2.3                             | Receiver Reference Signal            | 14 |  |  |

|   |              | 2.2.4                             | Mixer Bypass                         | 15 |  |  |

|   | 2.3          | LO Generation and Digital Control |                                      |    |  |  |

|   | 2.4          | Receiver Design                   |                                      |    |  |  |

|   |              | 2.4.1                             | Receiver RF Input Chain              | 20 |  |  |

|   |              | 2.4.2                             | Receiver Mixer LO Port               | 23 |  |  |

|   |              | 2.4.3                             | Receiver IF Chain Design             | 24 |  |  |

|   | 2.5          | System                            | Configuration and DC Power           | 29 |  |  |

| 3 | Ante         | enna Ar                           | ray Design                           | 32 |  |  |

|   | 3.1          | Overvi                            | ew of Antennas in CReSIS Systems     | 32 |  |  |

|   | 3.2          | Selection of Antenna Type         |                                      |    |  |  |

|   | 3.3  | Single  | Element Performance Tuning           | r |

|---|------|---------|--------------------------------------|---|

|   |      |         | 3.3.0.1 Microstrip Feed              | , |

|   |      |         | 3.3.0.2 Slot line and Taper          | , |

|   |      |         | 3.3.0.3 Mounting Structure           | , |

|   |      | 3.3.1   | Measurements                         | , |

|   | 3.4  | Array   | Construction                         | , |

|   |      | 3.4.1   | Array Measurements                   | , |

|   |      | 3.4.2   | Inter-Array Spacing                  | , |

|   | 3.5  | Dielec  | tric Loading                         | , |

| 4 | D!-! | 4 - 1 D |                                      |   |

| 4 | U    |         | cessing Aspects and Implementation61 |   |

|   | 4.1  | •       | n Operation and Storage              |   |

|   |      | 4.1.1   | Calibration                          | 1 |

|   | 4.2  | Chirp   | Generation                           | • |

|   |      |         | 4.2.0.1 Pattern Playback             | į |

|   |      |         | 4.2.0.2 DDS                          | , |

|   |      | 4.2.1   | Normalization and Frequency Notching |   |

|   |      |         | 4.2.1.1 Windowing                    | 1 |

|   |      |         | 4.2.1.2 Normalization Measurement    | , |

|   |      |         | 4.2.1.3 Implementation               | - |

|   |      |         | 4.2.1.4 Normalization Results        | ) |

|   |      | 4.2.2   | Mixer Product Minimization           | ! |

|   |      | 4.2.3   | Beam Forming                         | ) |

|   |      |         | 4.2.3.1 Steering on Transmit         | , |

|   |      |         | 4.2.3.2 Steering on Receive          | - |

|   |      | 4.2.4   | Stretch Processing                   | , |

|   | 4.3  | Respo   | nse Capture and Processing           | í |

|   |      | 4.3.1   | Digital Range Gating                 | ) |

|   |            | 4.3.2    | Stepped (   | Chirp Processing                      | •••     | . 90 |

|---|------------|----------|-------------|---------------------------------------|---------|------|

| 5 | Resu       | ilts and | Conclusio   | on                                    |         | 92   |

|   | 5.1        | Testing  | g and Perfo | ormance                               |         | . 92 |

|   |            | 5.1.1    | Delay Li    | ne Tests                              | •••     | . 93 |

|   |            |          | 5.1.1.1     | Full System Tests                     | •••     | . 95 |

|   |            |          | 5.1.1.2     | Synthetic Resolution                  | •••     | . 97 |

|   |            | 5.1.2    | Static Sir  | ngle Target                           | • • • • | . 99 |

|   |            | 5.1.3    | Dynamic     | Single Target                         | •••     | 102  |

|   |            | 5.1.4    | Dynamic     | Multi Target                          | •••     | 104  |

|   | 5.2        | Contin   | ued Opera   | tion and Future Work                  | •••     | 105  |

|   |            | 5.2.1    | Character   | rization                              | •••     | 106  |

|   |            |          | 5.2.1.1     | RF Frontend                           | •••     | 106  |

|   |            |          | 5.2.1.2     | Antennas                              | •••     | 106  |

|   |            |          | 5.2.1.3     | Radar Measurements                    | •••     | 107  |

|   |            | 5.2.2    | Design Ir   | mprovements                           | •••     | 107  |

|   |            |          | 5.2.2.1     | RF Improvements                       | •••     | 108  |

|   |            |          | 5.2.2.2     | Antenna Improvements                  | •••     | 109  |

|   |            |          | 5.2.2.3     | Digital Improvements                  | •••     | 110  |

| A | REN        | Module   | s and Cari  | rier Board                            |         | 119  |

| 1 | A.1        |          |             | d Assembly                            |         |      |

|   | A.2        |          | -           | ule                                   |         |      |

|   | 11.2       | A.2.1    |             | ter Components                        |         |      |

|   | A.3        |          |             | · · · · · · · · · · · · · · · · · · · |         |      |

|   | 11.0       | A.3.1    |             | Components                            |         |      |

|   | A.4        |          |             |                                       |         |      |

|   | A.4<br>A.5 | •        |             | Board                                 |         |      |

|   | А.Ј        | N1,20C   |             | ναια                                  | •••     | 123  |

| B | Radar Chassis Assembly           | 126 |

|---|----------------------------------|-----|

| С | Antenna Testing Setup            | 129 |

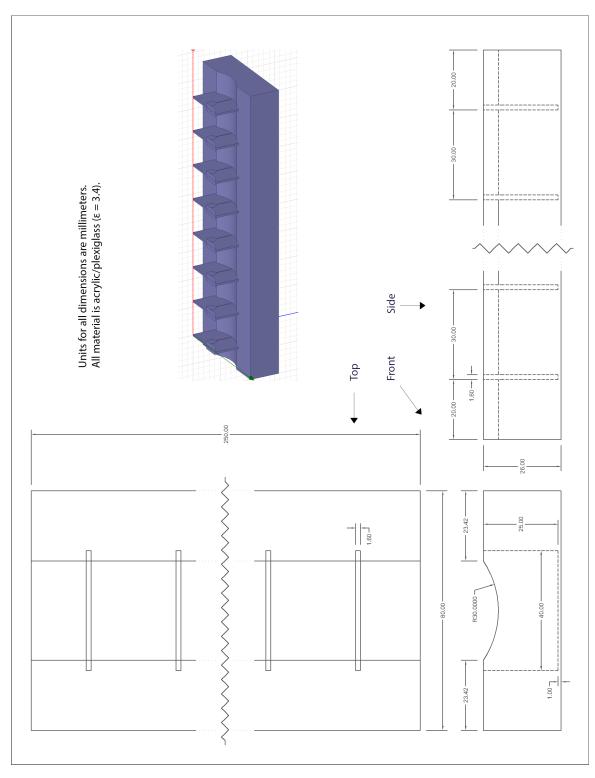

|   | C.1 Antenna Loading Structure    | 129 |

|   | C.2 Antenna Chamber Measurements | 129 |

| D | Full System Testing Setup        | 133 |

# List of Figures

| 1.1 | Simplified high level representation of FMCW architecture                          | 3  |

|-----|------------------------------------------------------------------------------------|----|

| 1.2 | Transmit and receive LFM waveforms in FMCW operation. Horizontal axis rep-         |    |

|     | resents time and vertical axis represents frequency.                               | 3  |

| 2.1 | High level block diagram of radar design. Only a single transmit and receive chan- |    |

|     | nel is represented.                                                                | 8  |

| 2.2 | An overview of the features included in the RFSoC. Image from [1]                  | 9  |

| 2.3 | Flow diagram of transmit module                                                    | 11 |

| 2.4 | Gain of the four transmission bands of the 9 assembled transmitter boards with     |    |

|     | respect to the input sweep, as measured by a VNA at the output port intended to    |    |

|     | drive the antenna (post amplifier). The mixer LO port was driven with a 0 dBm,     |    |

|     | 4.5 GHz tone for bands 1 and 3 and a 6 GHz tone for bands 2 and 4. The IF signal   |    |

|     | was a stepped frequency sweep from 10 MHz to 3.5 GHz at a constant -10 dBm. $$ .   | 14 |

| 2.5 | The gain of the receivers RF stage and mixer across varied levels of LO power      |    |

|     | to highlight the relatively invariant conversion loss. While constant across RF    |    |

|     | frequency, the gain from the IF stage has been approximated and subtracted out.    |    |

|     | See Figure 2.7 for the relevant component diagram.                                 | 15 |

| 2.6 | Synthesizer output chain                                                           | 16 |

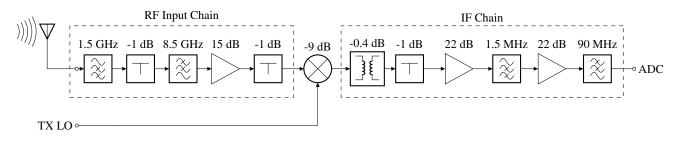

| 2.7 | Flow diagram of receive module. All numbers in (dB) represent component gain       |    |

|     | and all numbers in (Hz) imply the cut-off frequency of the filter component        | 18 |

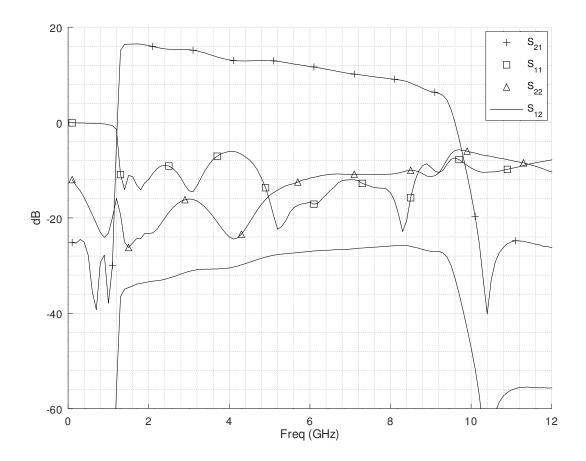

| 2.8 | The simulated S-parameters for the receiver RF input chain. The markers only       |    |

|     | identify traces and do not correspond to datapoints.                               | 21 |

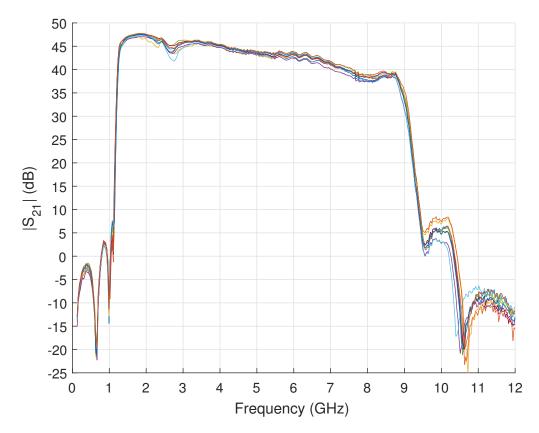

| 2.9  | The measured gain of the receiver across 9 boards. The in-band peak at 2 GHz is                    |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | 47.5 dB and the in-band minimum is 38.5 dB at 8 GHz.                                               | 22 |

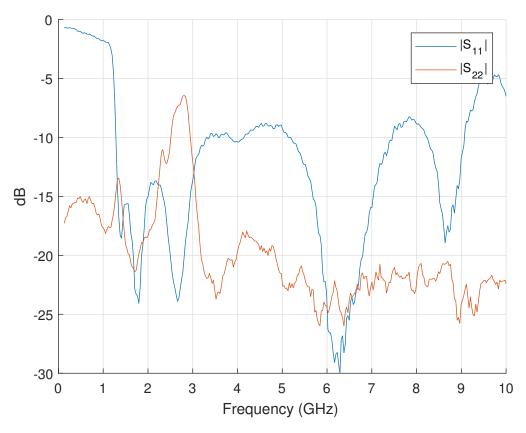

| 2.10 | The measured input impedance for the RF and IF ports on one of the receiver boards.                | 23 |

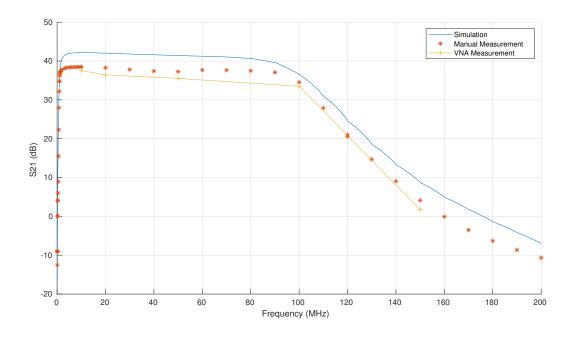

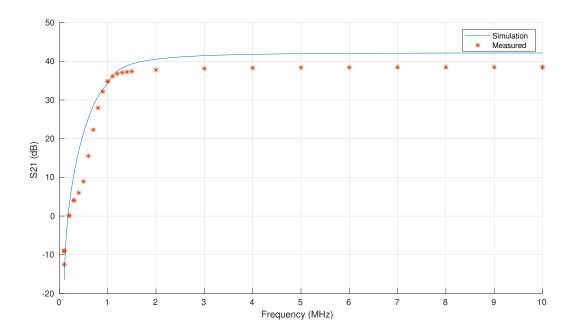

| 2.11 | $S_{21}$ of the receiver IF chain out to 200 MHz, as simulated and measured                        | 28 |

| 2.12 | $S_{21}$ of the receiver IF chain out to 10 MHz, as simulated and measured                         | 29 |

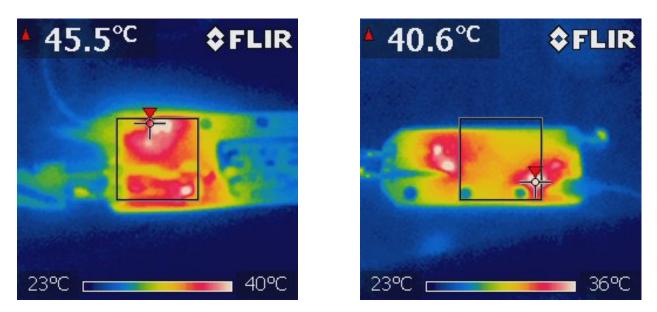

| 2.13 | Uncalibrated IR images of the transmitter (left) and receiver (right) boards. The                  |    |

|      | hottest chip is centered and the images were taken after 5 minutes of continuous                   |    |

|      | operation in a 20°C room with minimal active airflow                                               | 31 |

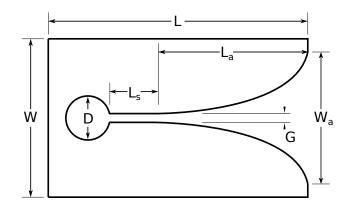

| 3.1  | Basic Vivaldi outline with characteristic dimensions labeled.                                      | 34 |

| 3.2  | The final Vivaldi design with no mounting structure. Left shows the slot line and                  |    |

|      | taper aperture and the right shows the microstrip and SMA connector feed on the                    |    |

|      | opposite side.                                                                                     | 36 |

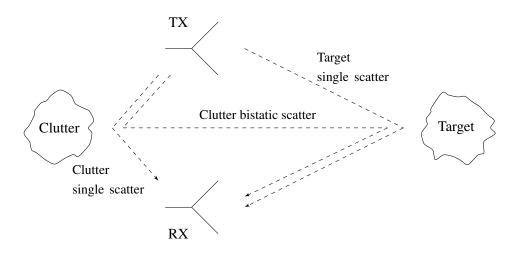

| 3.3  | Scatter resulting from rear positioned clutter                                                     | 38 |

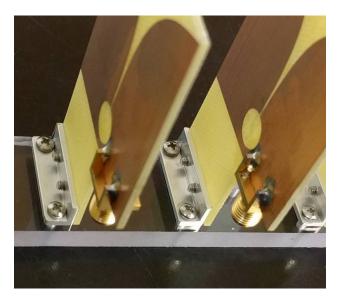

| 3.4  | The final antenna element design attached to the mounting structure with an alu-                   |    |

|      | minum bracket                                                                                      | 39 |

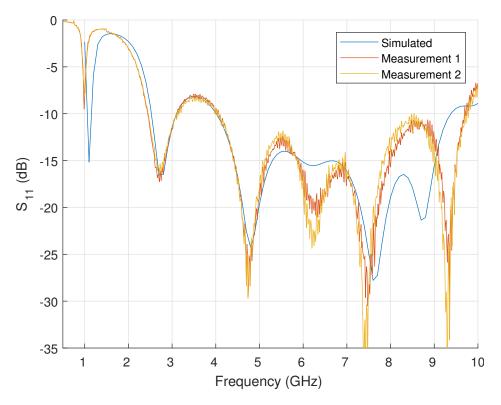

| 3.5  | The $S_{11}$ parameter of the antenna, as measured in the anechoic chamber and simu-               |    |

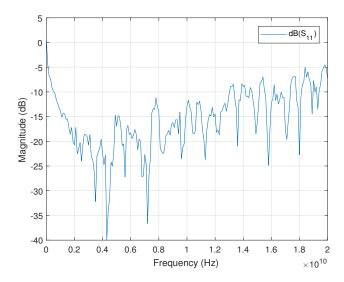

|      | lated. Cable loss has been calibrated out                                                          | 40 |

| 3.6  | The simulated elevation sweep of the directive gain (dBi) of an antenna element.                   |    |

|      | The antenna would be coplanar with this plot and oriented such that the end-fire                   |    |

|      | direction vector is pointing at $0^{\circ}$ .                                                      | 41 |

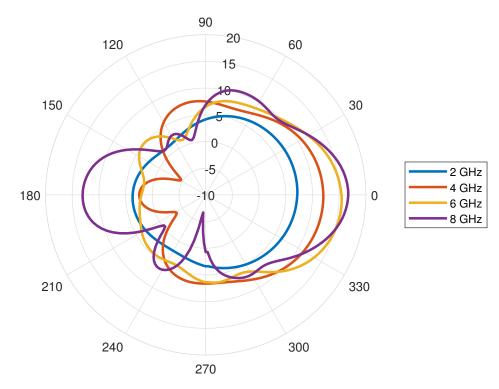

| 3.7  | The simulated azimuth sweep of the directive gain (dBi) of an antenna element.                     |    |

|      | The antenna is oriented such that the main lobe (end-fire direction) is pointing at $90^{\circ}$ . | 41 |

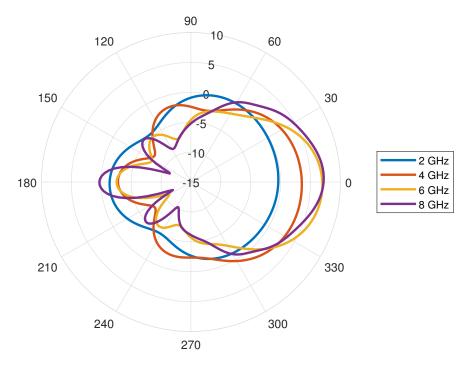

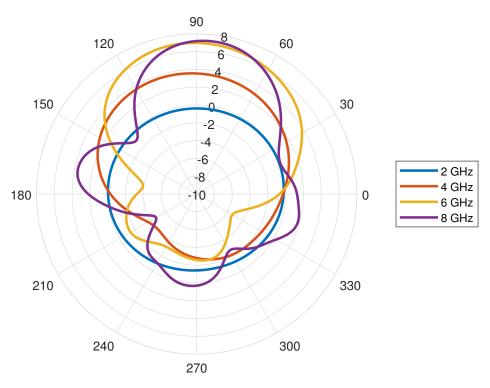

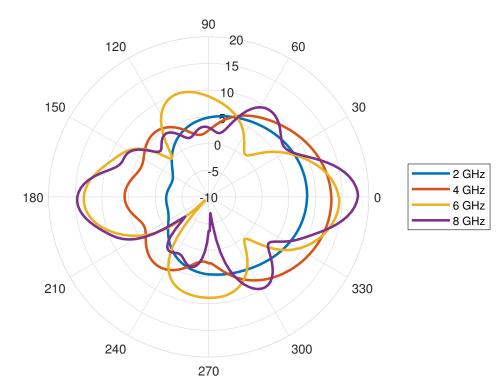

| 3.8  | The azimuth sweep of the radiation pattern measured in an anechoic chamber. This                   |    |

|      | is a relative measurement where the transmit and receive ratio is expressed in dB                  |    |

|      | and then normalized such that the maximum ratio is unity.                                          | 42 |

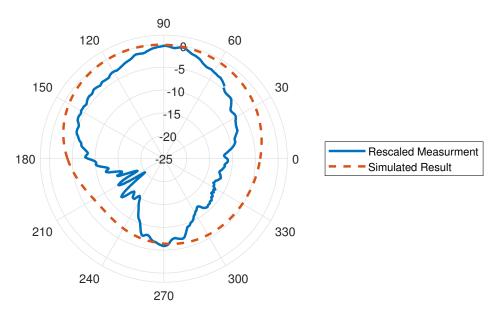

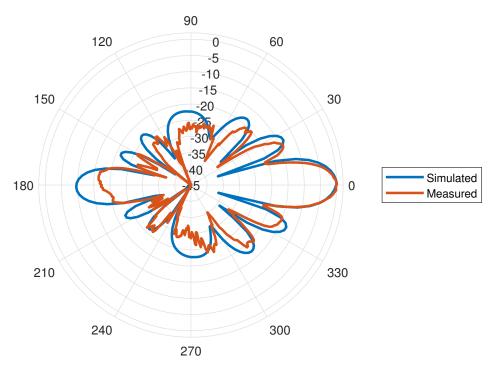

| 3.9  | A comparison between the measured radiation pattern and simulated directive gain      |    |

|------|---------------------------------------------------------------------------------------|----|

|      | pattern at 4 GHz. The simulated directive gain pattern has been normalized to have    |    |

|      | equal directivity with the measured pattern.                                          | 42 |

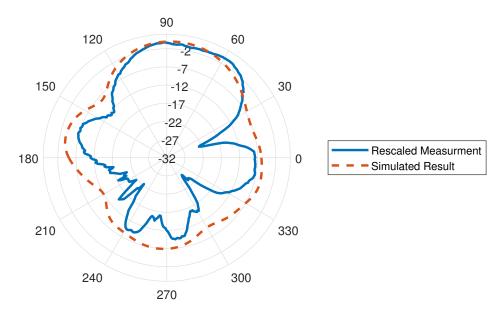

| 3.10 | A comparison between the measured radiation pattern and simulated directive gain      |    |

|      | pattern at 8 GHz. The simulated directive gain pattern has been normalized to have    |    |

|      | equal directivity with the measured pattern.                                          | 43 |

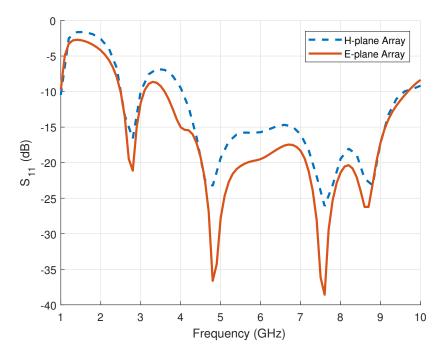

| 3.11 | The $S_{11}$ parameter of an E-plane and H-plane array of the Vivaldi design as simu- |    |

|      | lated in HFSS with uniform phase and amplitude. The physical spacing between          |    |

|      | phase centers for both arrays is 40 cm                                                | 44 |

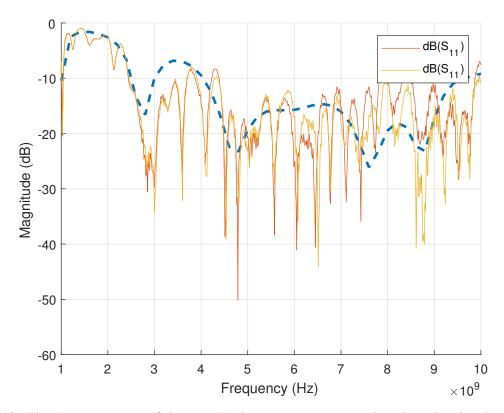

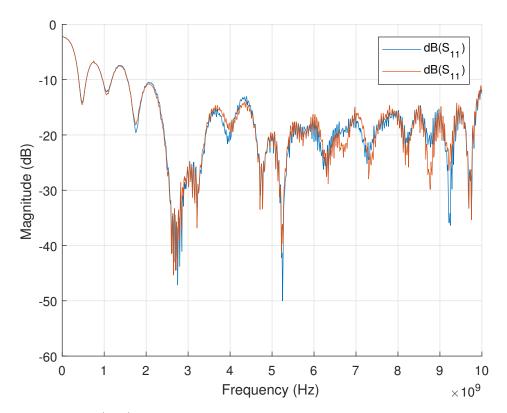

| 3.12 | The $S_{11}$ parameter of the two H-plane arrays compared against the simulated val-  |    |

|      | ues. The arrays are measured from behind a 1:8 resistive power divider                | 46 |

| 3.13 | The simulated elevation cut of the directive gain pattern (dBi) of an H-plane an-     |    |

|      | tenna array with 3 cm element separation. $\phi = 0$                                  | 47 |

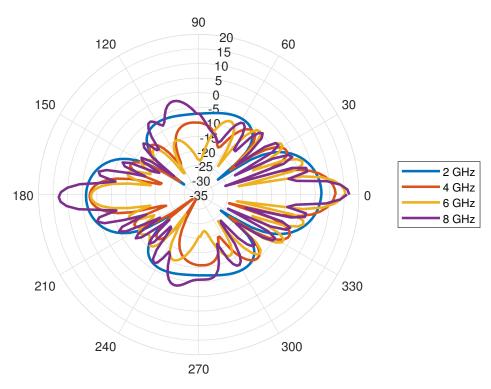

| 3.14 | The simulated azimuth cut of the directive gain pattern (dBi) of an H-plane antenna   |    |

|      | array with 3 cm element separation. $\theta = 0$                                      | 47 |

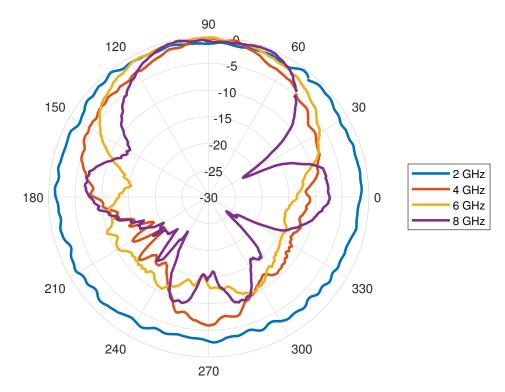

| 3.15 | The measured azimuth radiation pattern of a 3 cm H-plane array. This is a relative    |    |

|      | measurement where the pattern is normalized so the maximum across frequencies         |    |

|      | is always unity.                                                                      | 48 |

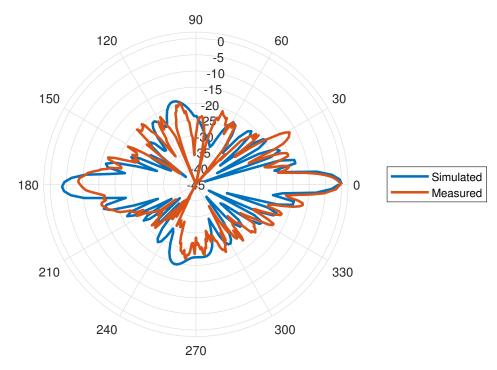

| 3.16 | A comparison across the azimuth between the measured radiation pattern and the        |    |

|      | simulated pattern at 4 GHz. Both patterns have been normalized to have the same       |    |

|      | directivity                                                                           | 48 |

| 3.17 | A comparison across the azimuth between the measured radiation pattern and the        |    |

|      | simulated pattern at 8 GHz. Both patterns have been normalized to have the same       |    |

|      | directivity                                                                           | 49 |

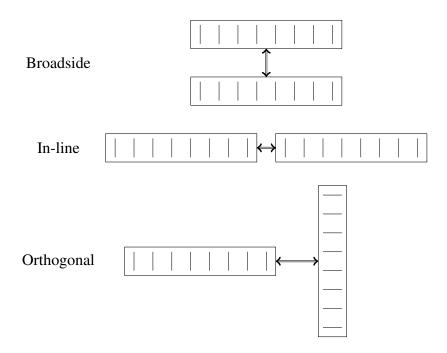

| 3.18 | Relative array positions for broadside, in-line, and orthogonal alignment. The lines  |    |

|      | inside each rectangle represent the orientation and spacing of individual antenna     |    |

|      | elements                                                                              | 51 |

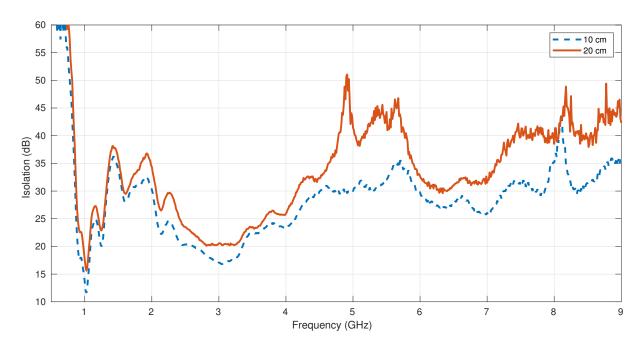

| 3.19 The isolation between two arrays arranged in-line (coplanar in the H-plane) 51                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.20 The isolation between two broadside arrays spaced 10 cm and 20 cm apart. The                                                                                                         |

| arrays were in the flipped orientation for both spacings                                                                                                                                  |

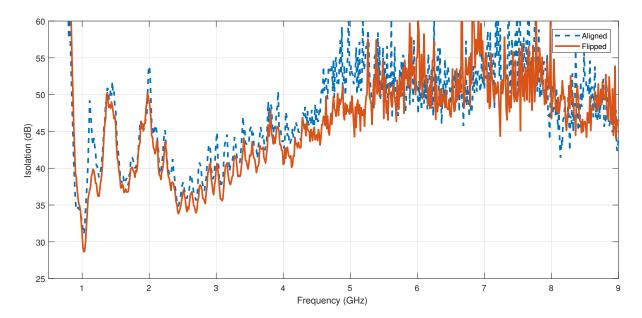

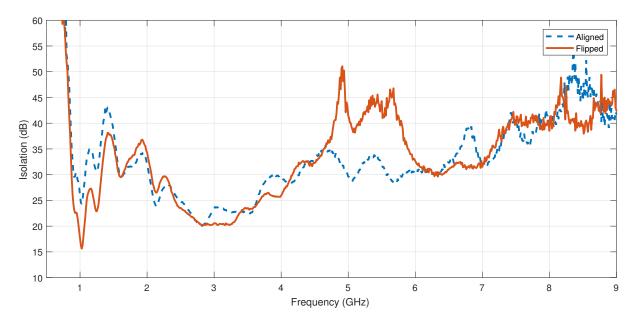

| 3.21 The isolation between two broadside arrays spaced 20 cm apart. Aligned indicates                                                                                                     |

| that the two arrays were oriented identically. Flipped indicates that one array is                                                                                                        |

| rotated $180^{\circ}$ relative to the other around the end-fire axis. $\dots \dots \dots$ |

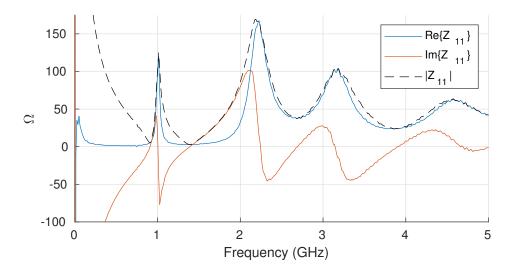

| 3.22 Measured input port impedance of a single antenna element                                                                                                                            |

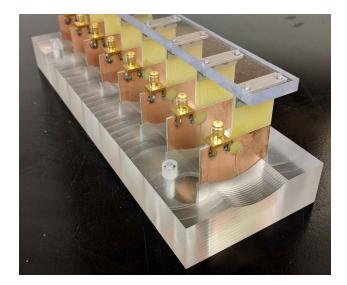

| 3.23 The polycarbonate dielectric loading structure with the antenna array slotted into it. 55                                                                                            |

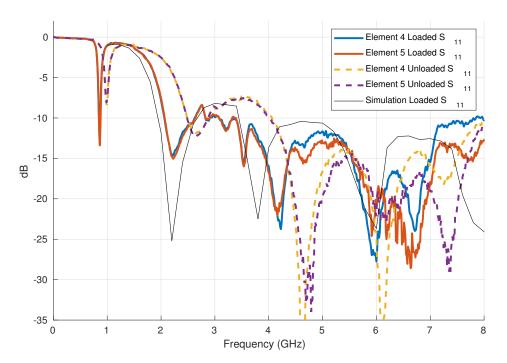

| 3.24 $S_{11}$ parameter for the antenna array, both with and without the loading structure.                                                                                               |

| The thin black line is from the HFSS simulation of the loading structure                                                                                                                  |

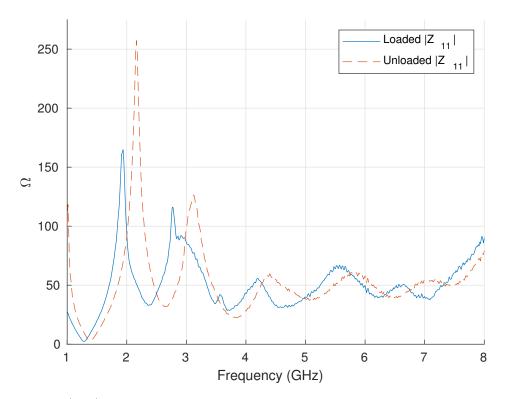

| 3.25 $ Z_{11} $ for an element in the array with and without the loading structure                                                                                                        |

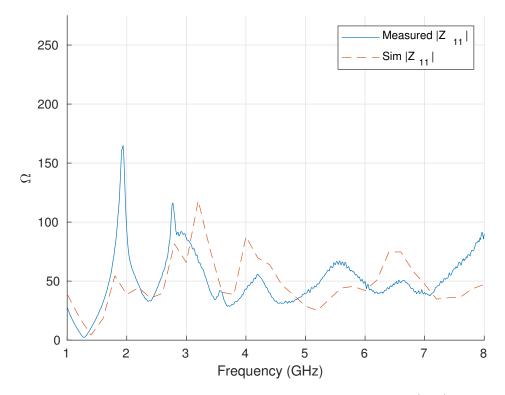

| 3.26 A comparison between the simulated and measured values of $ Z_{11} $ for a loaded array. 57                                                                                          |

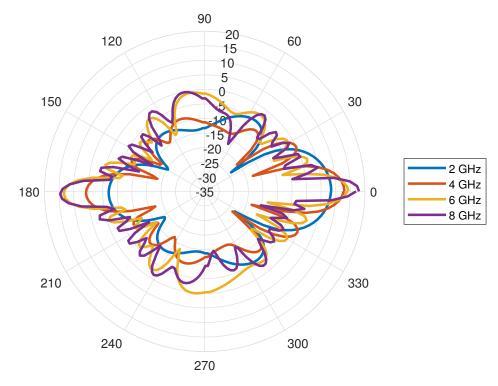

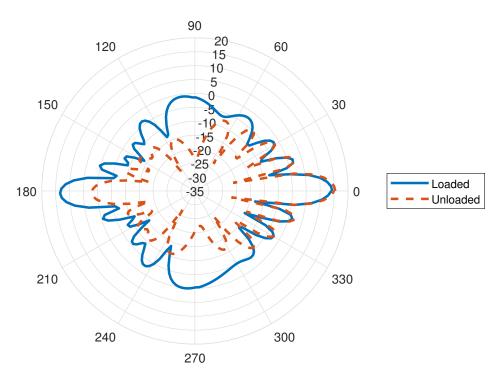

| 3.27 The azimuthal sweep ( $\theta = 0, 0 \le \phi \le 2\pi$ ) of the directive gain pattern for the                                                                                      |

| loaded array from the simulation                                                                                                                                                          |

| 3.28 The elevation sweep ( $\phi = 0, 0 \le \theta \le 2\pi$ ) of the directive gain pattern for the loaded                                                                               |

| array from the simulation                                                                                                                                                                 |

| 3.29 A comparison between the unloaded and loaded directive gain patterns at 6 GHz 59                                                                                                     |

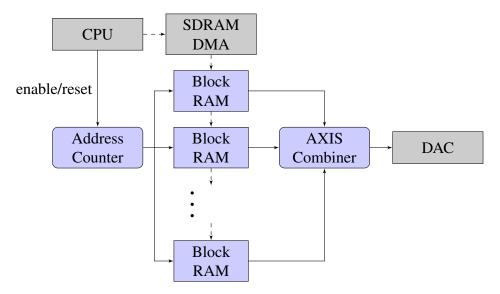

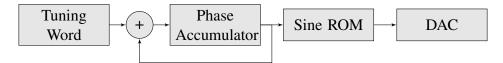

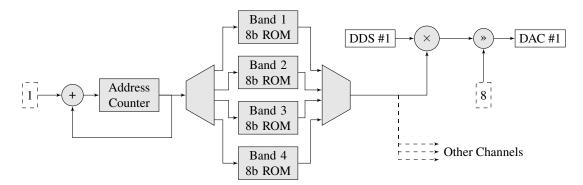

| 4.1 Block diagram of pattern playback to DAC                                                                                                                                              |

| 4.2 Basic DDS implementation where each element is synchronously clocked 67                                                                                                               |

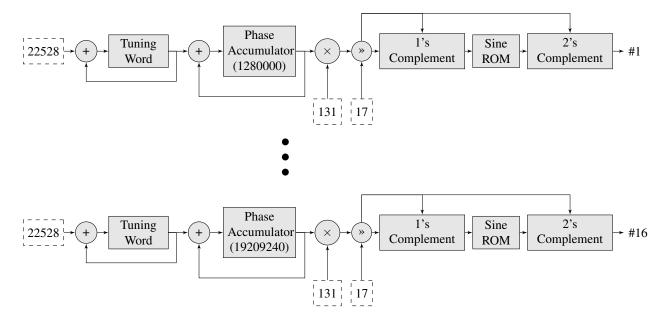

| 4.3 16 sample parallel DDS implementation                                                                                                                                                 |

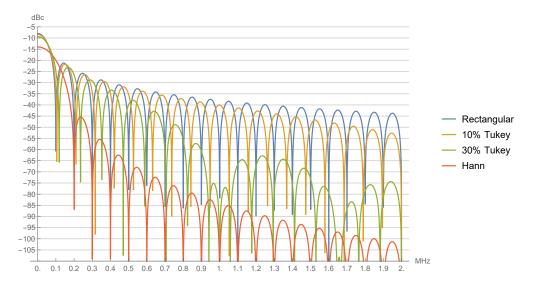

| 4.4 Power spectrum showing sidelobe levels for various levels of Tukey windowing                                                                                                          |

| for a 10 μs pulse                                                                                                                                                                         |

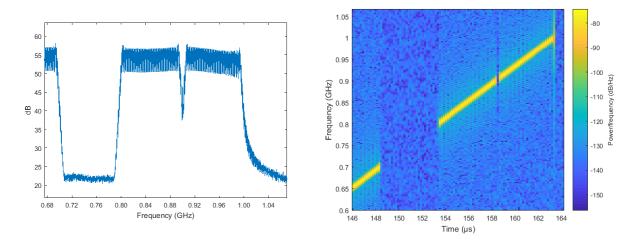

| 4.5 The PSD and spectrogram of a subsection of a chirp demonstrating an early attempt                                                                                                     |

| at frequency notching. Produced using pattern playback with a TI DAC38RF82                                                                                                                |

| and recorded using a 5 GS/s oscilloscope                                                                                                                                                  |

| 4.6 Simple structure for applying amplitude correction to DDS output                                                                                                                      |

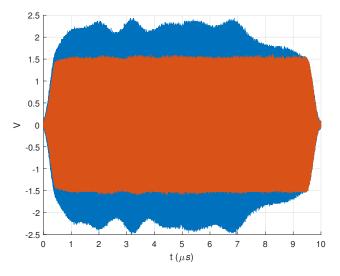

| 4.7  | Time domain peak-to-peak amplitude of a chirp from 4 GHz to 1.8 GHz with                                        |

|------|-----------------------------------------------------------------------------------------------------------------|

|      | (orange, foreground) and without (blue, background) normalization. Both have a                                  |

|      | 10% Tukey window applied. This was captured using a 50 GS/s oscilloscope 76                                     |

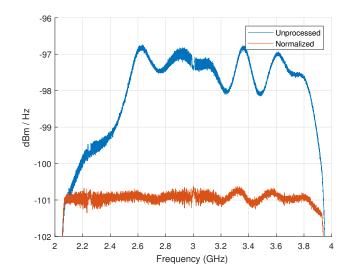

| 4.8  | PSD of normalized and non-normalized chirps displayed over unity region of Tukey                                |

|      | window. Orange shows the normalized results and blue shows the non-normalized                                   |

|      | results                                                                                                         |

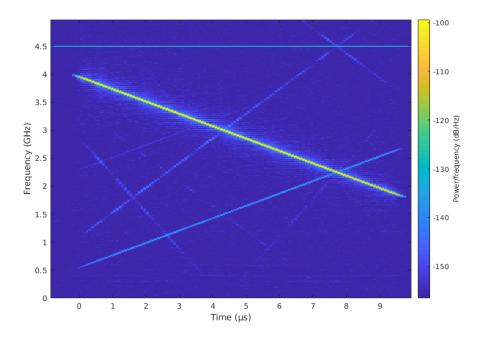

| 4.9  | $10 \ \mu s$ chirp up-converted to lowest operating band using reference mixer system 79                        |

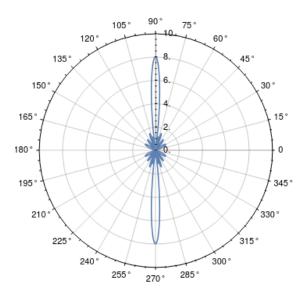

| 4.10 | Radiation pattern when array is steered broadside, along the <i>y</i> -axis. $\beta = 0$ 82                     |

| 4.11 | Radiation pattern when array is steered 45° off the y-axis in the yz plane, $\beta = \frac{\pi}{\sqrt{2}}$ . 82 |

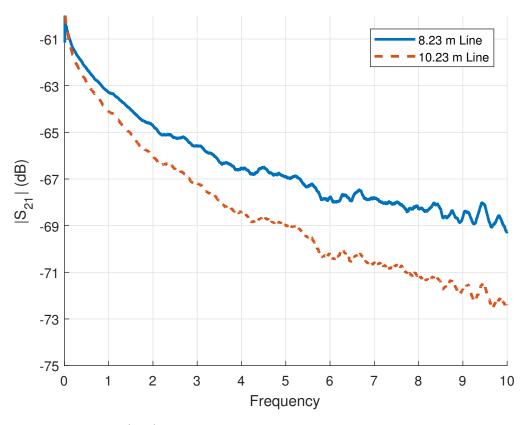

| 5.1  | The $ S_{21} $ of the delay line with and without the extra 2 m cable                                           |

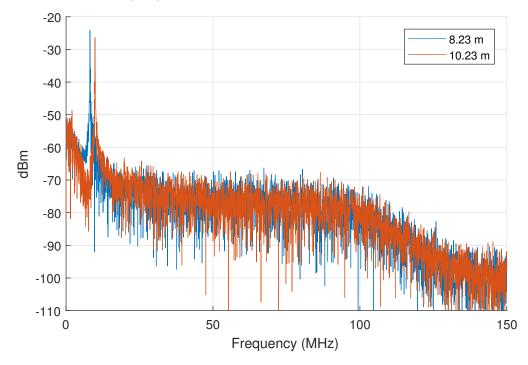

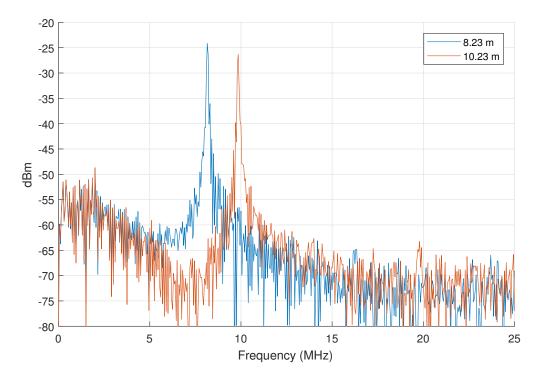

| 5.2  | Initial single-channel delay line tests in band 2 using two cable lengths. Transmit                             |

|      | power of 0 dBm and total attenuation of around 68 dB                                                            |

| 5.3  | Initial single-channel delay line tests in band 2 using two cable lengths. Transmit                             |

|      | power of 0 dBm and total attenuation of around 68 dB                                                            |

| 5.4  | Delay line test for all four bands in normal operation (captured by ADC as opposed                              |

|      | to scope)                                                                                                       |

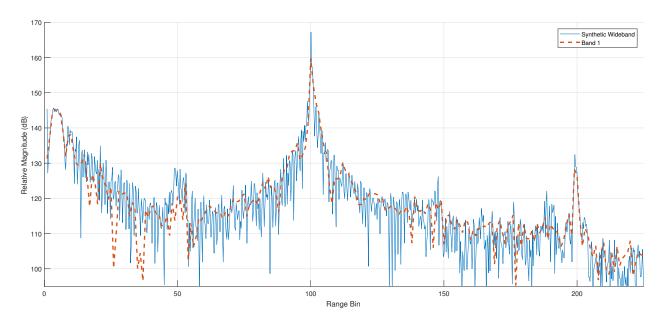

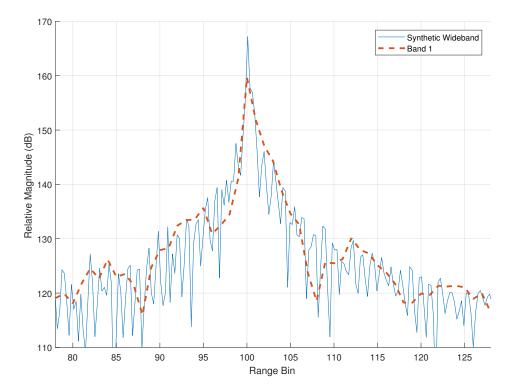

| 5.5  | Single band response and combined band response of the 10.23 m delay line 98                                    |

| 5.6  | Single band response and combined band response of the 10.23 m delay line 98                                    |

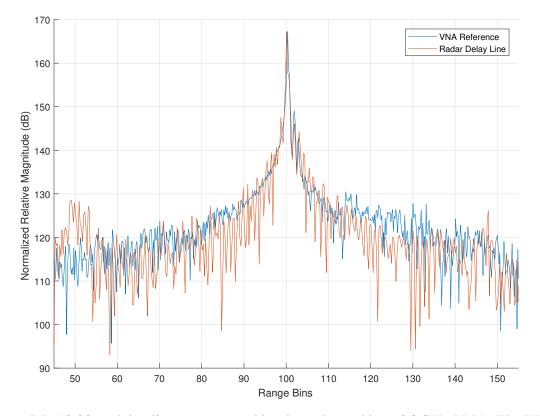

| 5.7  | 10.23 m delay line as measured by the radar and by a 26 GHz VNA. The VNA                                        |

|      | measurement has been normalized and aligned with the radar target response to                                   |

|      | compensate for the added cables                                                                                 |

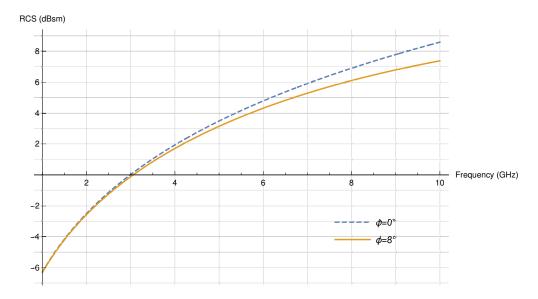

| 5.8  | Calculated co-polarized radar cross section of a 35.5 cm x 5.4 cm cylinder 101                                  |

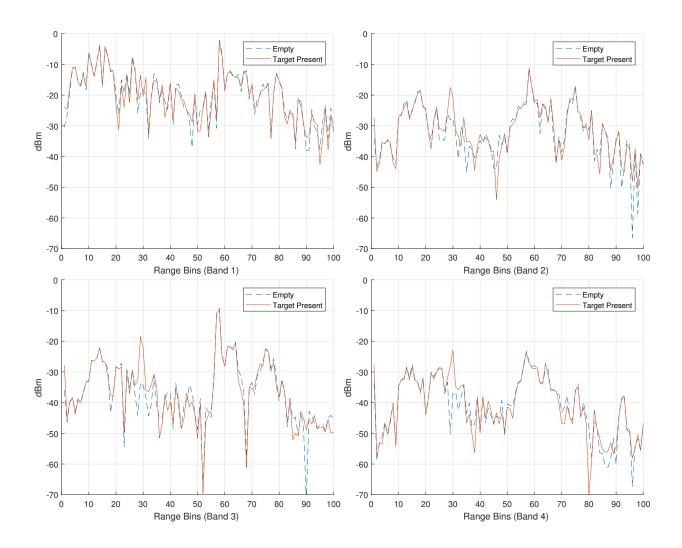

| 5.9  | Range profiles from each band for a single target at 2 m range. Returns without                                 |

|      | a target present are included to highlight what should be considered background                                 |

|      | clutter. Each range bin corresponds to 6.8 cm                                                                   |

| 5.10        | Background scene subtraction for each band for a centered target. The target was        |

|-------------|-----------------------------------------------------------------------------------------|

|             | placed 2 m out directly in front of the arrays and should appear around the 29th        |

|             | and 30th range bins                                                                     |

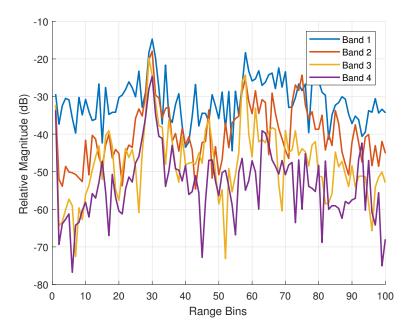

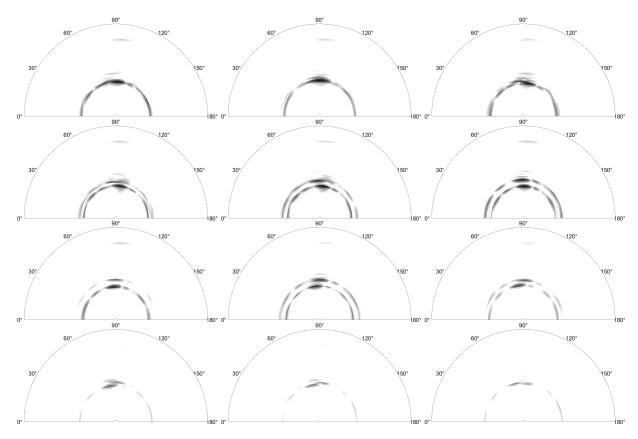

| 5.11        | Steering applied to the received data from bands 1 through 4. The color scale           |

|             | for each image covers a 40 dB range from the greatest magnitude in the return           |

|             | (darkest) to 40 dB less (lightest). 100 range bins (6.8 m) are shown and no spatial     |

|             | windowing was applied to the array                                                      |

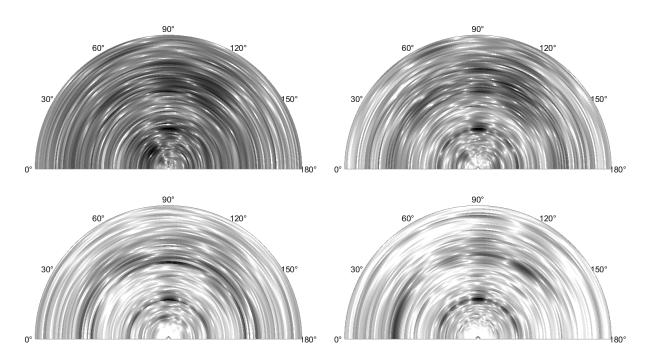

| 5.12        | Single target moved linearly across $60^\circ$ of the arrays FOV. Sequence follows left |

|             | to right, top to bottom. Each image shows 70 range bins of the third band (4.76 m)      |

|             | and all have the same fixed color scale spanning 40 dB                                  |

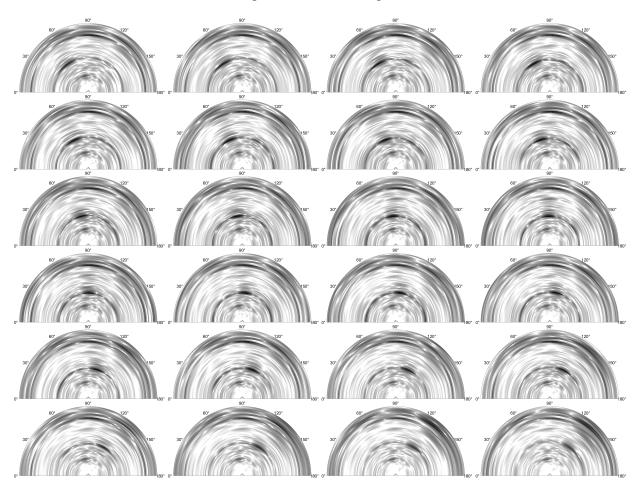

| 5.13        | Two targets rotated around each other 180°. Sequence follows left to right, top to      |

|             | bottom. Each image shows 70 range bins of the third band (4.76 m) and all have          |

|             | the same fixed color scale spanning 30 dB                                               |

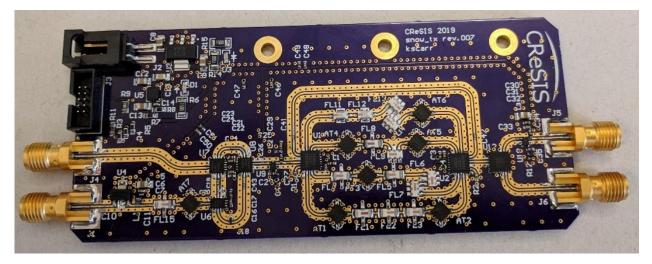

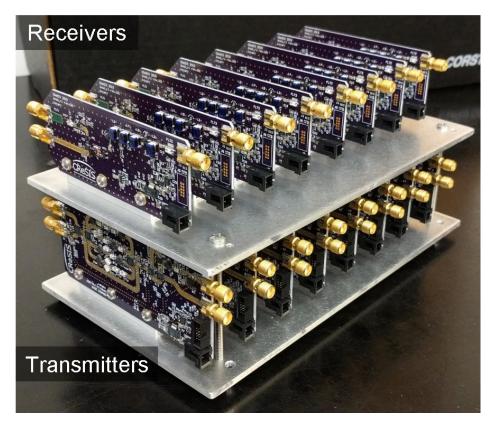

| A.1         | Photo of single transmit module                                                         |

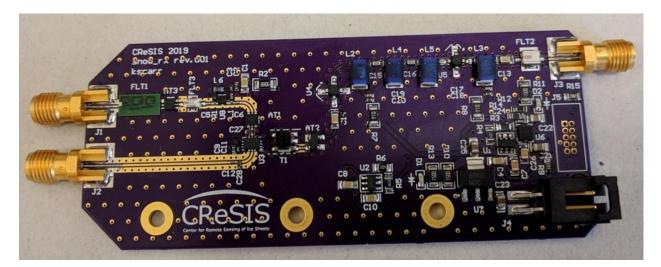

| A.2         | Photo of single receiver module                                                         |

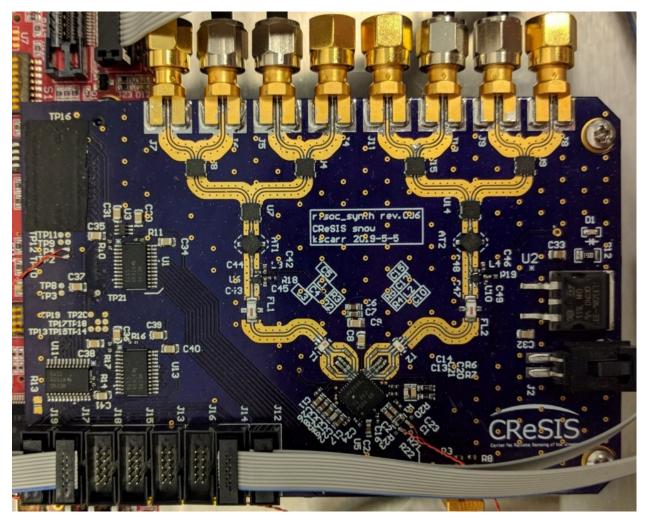

| A.3         | Photo of the synthesizer module                                                         |

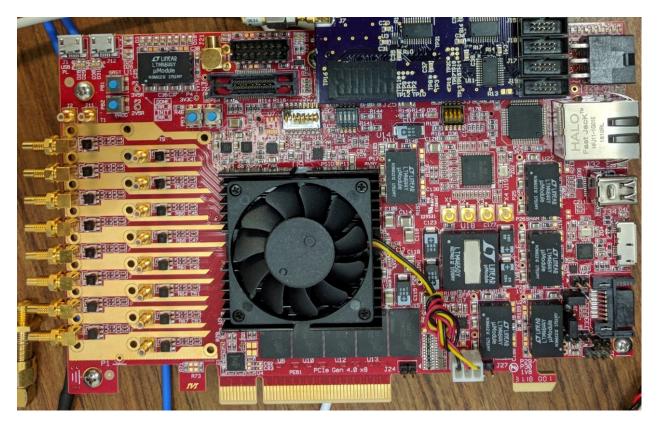

| A.4         | Photo of the RFSoC carrier board                                                        |

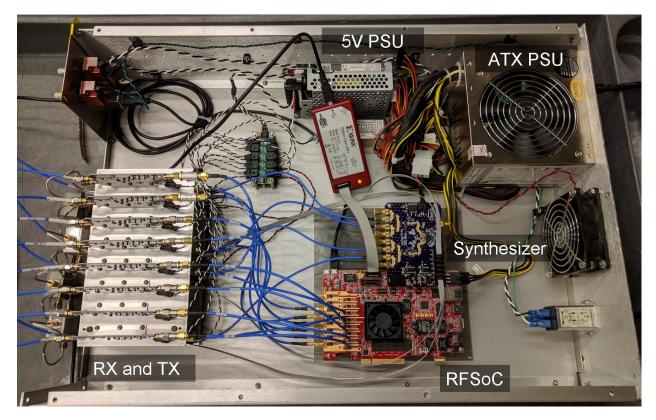

| <b>B</b> .1 | Image of the assembled radar chassis                                                    |

| B.2         | Profile view of the RF module assembly                                                  |

| C.1         | Dimensions of the loading structure as tested                                           |

| C.2         | Measured $ S_{11} $ parameter of antenna feed cables with an open attached in place of  |

|             | an antenna                                                                              |

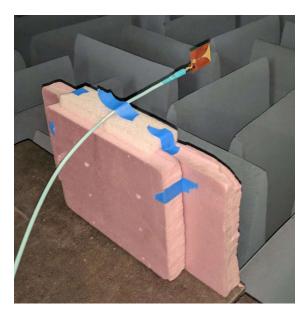

| C.3         | Single element mounting structure. More tape was added to increase stability of         |

|             | foam blocks and the feed cable was firmly affixed to the turntable to prevent pulling   |

|             | during table stepping                                                                   |

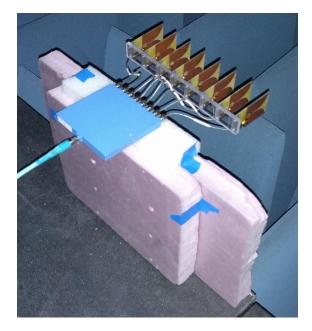

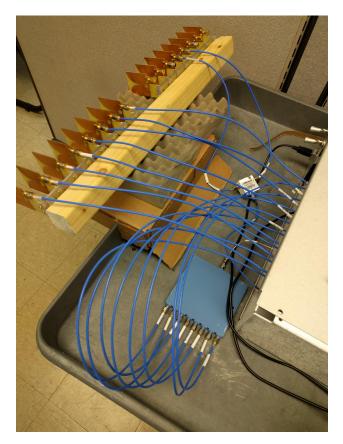

| C.4 | Power splitter and array mounting structure. Like the single element, more tape      |

|-----|--------------------------------------------------------------------------------------|

|     | was present during the actual measurements and the cable was properly attached       |

|     | to the table                                                                         |

| C.5 | Measured $ S_{11} $ of Pulsar Microwave 1:8 power divider/combiner used for testing  |

|     | radiation performance of the antenna arrays                                          |

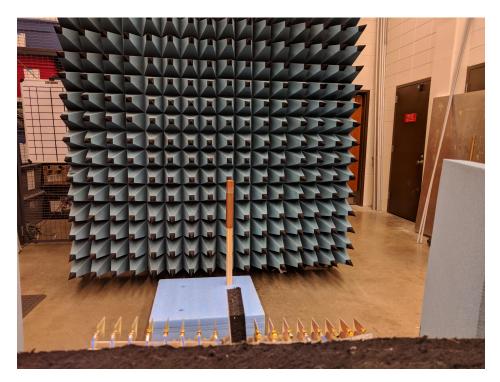

| D.1 | Photo of the antenna configuration used for system testing                           |

| D.2 | Photo of the placement of RF absorbing foam around the radar                         |

| D.3 | Photo of the target and its placement relative to the radar. The wall of absorber is |

|     | visible in the background                                                            |

# List of Tables

| 2.1 | Operating characteristics of RFSoC data converters [1]                          | 9   |

|-----|---------------------------------------------------------------------------------|-----|

| 2.2 | Filter band definitions                                                         | 13  |

| 3.1 | Dimensions of Vivaldi antenna element.                                          | 35  |

| 3.2 | Simulated antenna performance characteristics.                                  | 40  |

| 3.3 | Simulated antenna array performance characteristics.                            | 46  |

| 3.4 | Simulated antenna array performance characteristics with the dielectric loading |     |

|     | structure                                                                       | 55  |

| A.1 | Components used in the transmitter module. HPF = high pass filter, LPF = low    |     |

|     | pass filter.                                                                    | 121 |

| A.2 | Components used in the receiver module. HPF = high pass filter, LPF = low pass  |     |

|     | filter                                                                          | 123 |

# Chapter 1

## Introduction

#### 1.1 Background

#### **1.1.1** Overview of CReSIS Projects

The Center for Remote Sensing of Ice Sheets (CReSIS) regularly designs and deploys radars over the polar regions for monitoring properties such as ice sheet thickness, bedrock topography, seaice extent, and snow accumulation. A wide array of sensors are employed spanning from VHF and UHF sounding units to Ka-band altimeters [2]. Through Operation IceBridge (OIB) some of the sensors are used in conjunction with satellite-borne altimeters (ICESat, ICESat-2) to provide continuous operation during satellite downtime and extend the measurements with higher resolution data [3]. The original OIB sensor platform included two high resolution FMCW radars for altimetry and internal layer mapping of firn, a 2 GHz - 8 GHz snow radar [4] and a 12 GHz -18 GHz radar altimeter [5]. These systems were improved upon with the development of a higher performance 2 GHz - 18 GHz snow radar [6] that has seen continued upgrades [7]. While those radars are all airborne platforms, near-ground systems are in use as well. A 2 GHz - 18 GHz radar similar to the snow accumulation radar has been used for scattering analysis of wheat canopies [8] and a more compact system is under development for soil moisture monitoring [9].

The radar systems for snow and wheat measurements are all single channel, ultra-wide bandwidth (UWB) systems with high range resolution.<sup>1</sup> They are typically operated as bistatic synthetic aperture radars (SAR) with colocated horn antennas, building a depth profile in the along-track di-

<sup>&</sup>lt;sup>1</sup>The FCC currently defines UWB transmissions as any with bandwidths exceeding either 500 MHz or 20% of the arithmetic center frequency.

rection and sweeping the flight path over a region to effectively cover a 2D area. The cross-track beamwidth of these systems is fixed and no processing can be done on them. The systems at CRe-SIS using active arrays are lower bandwidth, higher power sounding units such as the Multichannel Coherent Radar Depth Sounder (MCoRDS) [2]. MCoRDS is a multi-receiver system that carries out SAR processing in the along-track direction and array processing in the cross-track direction. This added array processing allows for more comprehensive clutter reduction and a wider effective swath which means potentially fewer passes over a region to acquire an equivalent amount of high quality data.

In general, UWB systems require components capable of operating over a wider bandwidth than narrow bandwidth systems, which can increase design complexity and cost. Expanding a UWB system into a multichannel configuration creates the additional issue of maintaining phase alignment across several channels. This is difficult for higher frequencies as the decrease in wavelength means smaller physical and digital variations can have a greater effect and the manufacturing tolerances go down. The Xilinx RFSoC eliminates much of the complexity involved in keeping the data converters of each channel synchronized leaving only physical differences in the RF chain as potential sources of phase error, but the flexibility of the digital backend should allow a system to compensate for those differences as well.

### 1.1.2 Summary of FMCW Operating Principles

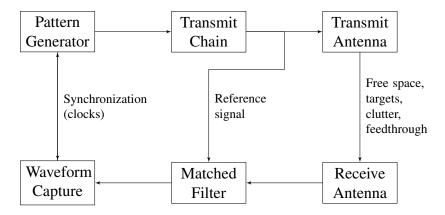

The high range resolution of the snow and wheat radars is achieved using a frequency modulated continuous wave (FMCW) radar architecture. Introducing frequency modulation is what allows a CW radar to distinguish range in addition to velocity. A high level view of the typical setup is shown in figure 1.1.

In the case of this system, the pattern generator produces a linear FM chirp waveform (LFM), a signal that sweeps linearly in frequency over time. Nonlinear waveforms are used as well [10, 11] as they provide some advantages over traditional LFM, however the processing requirements increase the complexity beyond what is useful for this review. The LFM chirp is passed through

Figure 1.1: Simplified high level representation of FMCW architecture

an RF conditioning chain (typically an LNA and filter) to the transmit antenna and to a matched filter. From the transmit antenna the signal is reflected off the target back to the receive antenna. In a monostatic setup only a single antenna is present and either a circulator or a transmit/receive switch is placed in front of the antenna to handle either simultaneous transmit and receive periods or non-overlapping transmit and receive periods respectively. The matched filter is implemented in this case with an RF mixer; the transmitted signal and received signal are multiplied in the time domain to produce the sum and difference products. The behavior of the two waveforms is shown in Figure 1.2. The two diagonal lines, increasing in frequency with respect to time, represent,

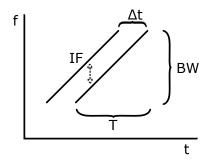

Figure 1.2: Transmit and receive LFM waveforms in FMCW operation. Horizontal axis represents time and vertical axis represents frequency.

left to right, the transmit and receive chirps. The duration of a single chirp is marked by T and the bandwidth by BW. For a given target at range R, the receive signal has been delayed in time relative to the transmit signal by  $\Delta t = \frac{2R}{c}$ , where c is the speed of propagation in that medium. This delay creates a difference in the instantaneous frequency of the two signals  $\Delta f$  that is dependent on the range of the target and the chirp rate k.

$$k = \frac{BW}{T} \tag{1.1}$$

$$\Delta f = k\Delta t = \frac{2Rk}{c} = \frac{2R(BW)}{cT} \tag{1.2}$$

The time-domain multiplication process of the reference transmitted signal and the received signal is usually called dechirping or deramping. This difference in frequency  $\Delta f$  is the difference product at the output of the mixer and forms the dechirped IF signal,  $f_{IF} = \Delta f$ . Other matched filters can be used and with sufficiently capable hardware the returned RF chirp can be directly captured for digital dechirping.

Expressing the range as a function of the IF yields Equation 1.3. As the transmit period and bandwidth are fixed for a single chirp, the ability to resolve range is dependent on the ability to resolve the frequency of the IF. The minimum resolvable frequency difference  $\delta f$  is inversely proportional to the duration of the chirp, which means the range resolution is solely dependent on the bandwidth of the chirp.

$$R = \frac{f_{IF}Tc}{2(BW)} \tag{1.3}$$

$$\delta f = \frac{1}{T} \tag{1.4}$$

$$\delta R = \frac{\delta f_{IF} T c}{2(BW)} = \frac{c}{2(BW)} \tag{1.5}$$

This expression for range resolution works well when dealing with perfectly linear and continuous LFM signals that are transmitted for a long period with respect to the range delay  $\Delta t$ . When one of those conditions does not hold, the resolution is degraded, and Equation 1.5 typically acquires a scalar multiplier to represent the effect. This means that range resolution is degraded when the transmitted or received signal is windowed, when the range delay is long with respect to the chirp duration, if the chirps themselves have nonlinearities, or if the propagation speed through the medium changes.

#### **1.2** Thesis Overview

This work presents the design for a multichannel radar system built around the Xilinx RFSoC, covering the RF frontend, the digital processing implementation, and the antenna array design. This is broken into five chapters and an appendix. After an initial introduction in the first chapter the three following chapters each detail the different aspects of the work. A final chapter presents full-system tests evaluating the operating capabilities of the radar and lists the tasks comprising future work.

*Chapter 1* provides the context surrounding this work and background information necessary to understand the rest of the material presented.

*Chapter 2* describes the architecture of the new radar system and the expected operating specifications. The design process for the transmitter and receiver modules is described and measurements of each modules performance in isolation are presented. Thermal performance, power consumption, and power supply are listed as well towards the end of the chapter.

*Chapter 3* outlines the design procedure for the antenna arrays used by the radar. Design steps and operating characteristics are given first for an individual element and then for the full array construction. Simulation results and measurements performed in an anechoic chamber are compared. The ability to affect array performance through dielectric loading of the antennas is investigated and more chamber measurements are compared to results from simulations.

*Chapter 4* describes the design of the digital backend of the radar system. Implementation details for the various capabilities enabled by the data converters are presented along with example results. This includes things like arbitrary waveform windowing and notching, gain normalization and phase correction, active phased array operation, system calibration, and dynamic stretch processing. The results of an attempt to implement mixer product minimization are presented along with analysis as to why it was unsuccessful.

Chapter 5 presents the results of the radar operation. Operation with simulated targets using

delay lines is demonstrated and used to characterize the system in a relatively controlled manner. Full system operation with the antennas follows, first showing performance detecting a single stationary target. The target is then swept across the antenna array's field of view to test beam steering performance. A second target is added to test the ability to distinguish multiple targets during steering.

Appendix A presents images of the assembled transmitter and receiver modules along with a list of the RF components used.

*Appendix B* presents images of the assembled radar chassis along with specifications such as the physical dimensions and weight. A photo of the final test setup is shown as well.

*Appendix C* presents images of the antenna test setups in the chamber along with characterizations of external components used in the antenna tests.

# Chapter 2

### Multichannel Radar System Design

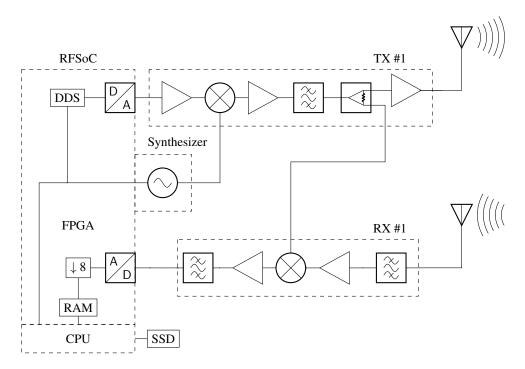

The design of this system is centered around improving on the functionality of the original snow radar [4], which helps set a basis for the desired minimum requirements of operation. The original snow radar was an airborne bistatic FMCW radar with a 6 GHz bandwidth centered at 5 GHz. It transmitted at no more than 23 dBm and was able to penetrate around 40 m beyond the top layer of snow. While the snow system was used as a basis, the new multichannel design differs in multiple ways. Unlike the snow radar, the new design has a lower maximum output power and would require external connectorized amplifiers to reach 23 dBm. Instead of offering a continuous 6 GHz of bandwidth a stepped chirp design is used, breaking up the bandwidth into 4 individual sub-bands, represented by the bandpass filter shown in the TX chain. Figure 2.1 provides a high level block diagram of the system design.

Eight transmit and receive channels will be present. Each channel consists of two single-board modules: one for the transmit chain and one for the receive chain. This means that there will be eight of each chain of components labeled *TX* and *RX* in Figure 2.1. Correspondingly there are two data converters for each channel: one DAC for each transmit chain and one ADC for each receive chain. These data converters are all housed inside the package of the RFSoC on a single carrier board labeled *RFSoC* in the diagram. Attached to the carrier board is another single-board module holding a synthesizer that provides the LO for the upconversion stage in all of the transmitter modules. The carrier board and synthesizer board together are responsible for controlling all aspects of the radar such as power sequencing, system configuration, and digital processing. The specifics of that functionality are described in Chapter 4. For each channel there are two antennas as well. Each transmitter module directly drives an element in the antenna array

Figure 2.1: High level block diagram of radar design. Only a single transmit and receive channel is represented.

and each receiver module is directly driven by an element in the antenna array. The specifics of the antenna arrays are described in Chapter 3. This chapter discusses the design of the transmitter, receiver, and synthesizer modules.

### 2.1 Digital Backend Hardware

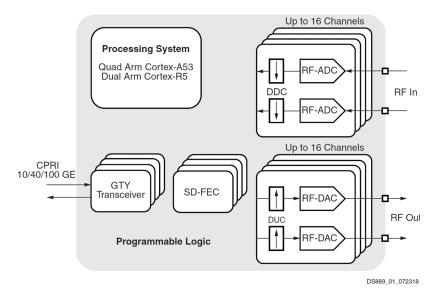

Xilinx released the Zynq UltraScale+ RFSoC (RF System on a Chip) line of products in 2018, integrating multiple high speed data converters into a single package along with programmable logic and several ARM processor cores [12]. An overview of the main features is shown in Figure 2.2. The benefits of bringing the converters into the same chip as the master FPGA are detailed in Chapter 4, but can be broadly summarized as the following improvements: reduced manufacturing complexity, lower digital implementation complexity, lower power consumption, and reduced physical size.

A development board with the ZU28DR model chip from the first generation of RFSoC released in 2018 was acquired from a third party manufacturer to investigate the performance and

Figure 2.2: An overview of the features included in the RFSoC. Image from [1]

benefits such a device would have in the development of a radar. Sourcing from the third party manufacturer came at the cost of support among other things, but the board boasts a more compact footprint and expanded set of peripherals relative to the Xilinx reference board. The operating characteristics of the DAC and ADC modules contained in the ZU28DR RFSoC are outlined in Table 2.1.

| Property                           | DAC        | ADC        |

|------------------------------------|------------|------------|

| Converter Count                    | 8          | 8          |

| Max Sample Rate (GS/s)             | 6.554      | 4.096      |

| Resolution (bits)                  | 14         | 12         |

| Interpolation/Decimation           | 2x, 4x, 8x | 2x, 4x, 8x |

| Analog Bandwidth (GHz)             | 4          | 4          |

| SFDR (dBc)                         | >82        | >82        |

| Channel Isolation (dBc)            | -70        | -70        |

| Termination (Ω)                    | 100        | 100        |

| Full-scale Power (dBm)             | 1, 5       | 1          |

| Absolute Maximum Input Voltage (V) | 2.1        | 2.1        |

Table 2.1: Operating characteristics of RFSoC data converters [1]

### 2.2 Transmitter Design and Description

The digital backend of the snow radar flown during the 2018 season [7] is capable of directly producing a signal spanning the entire operating bandwidth of the radar, which means that the final conditioning consists of only a bandpass filter and amplification stage. As the DACs available in the RFSoC are not capable of operating over the desired bandwidth, a different approach must be taken. Other radars at CReSIS [4][8][6] that use a DDS with a comparatively smaller analog bandwidth rely on either a PLL based multiplier or multiple stages of discrete frequency multipliers to produce a signal with the desired bandwidth. As the multipliers and up-converters shift the frequency higher, a following down conversion stage is needed to bring the signal back into the 2-18 GHz band. There are few commercially available frequency multipliers with an input bandwidth comparable to these DACs' analog bandwidth, and use of any multiplier will introduce extra inband signals that can be difficult to remove. On the same note, the hardware required to implement a PLL multiplier operating over such a wide bandwidth can be expensive. The corresponding down converter for both setups can also be large cost drivers in the design.

In the case of a multi-channel system, extra costs add quickly. As detailed in chapter 4, an active steering system requires precise control over the phase of the signal from individual channels. Any conditioning of the signal between the DAC and the antenna needs to be consistent and coherent across the channels to ensure a phase-aligned output at the antenna array. Meeting this requirement is accomplished most simply by using identical hardware for each channel. Any multi-channel design needs to be optimized for size and cost in order to meet the end goal of a compact system, as any increase or decrease in those parameters for the hardware of an individual channel translates out to an n-fold change, where n is the channel count.

This section presents a new compact transmitter design optimized around the multichannel digital hardware. The new design consists of eight identical transmit modules, one per DAC, and a controller board to keep the modules coherent. Each identical transmit module has a single up-conversion stage that feeds into a switched filter bank that divides the 2-8 GHz band into four over-lapping bands spanning 2.2 GHz each. The local oscillator (LO) signal used in the up-conversion is

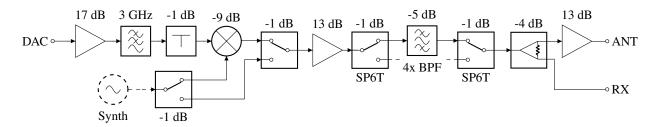

generated by a synthesizer on the controller board that is detailed in section 2.3. Figure 2.3 shows the high level signal flow diagram for the final transmitter design with the approximate gain for each component. A comprehensive list of each component in the figure is given in Section A.2.1.

Figure 2.3: Flow diagram of transmit module

#### 2.2.1 Transmitter IF Chain

The IF signal produced by the DAC is a chirp sweeping from 500 MHz to 2700 MHz. Various amplitude modulations are made to normalize and drop out regions for the different filter bands (see section 4.2.1), but the frequency limits are consistent. A 500 MHz gap is given between DC and the start of the chirp to provide a large enough transition region between the pass band and stop band of the filter used to cut out the LO feedthrough from the up-conversion. Below 500 MHz also happens to be where the insertion loss for the integrated balun inside the mixer starts to increase significantly [13]. A 500 MHz gap is also in place on the high side of the band as operating the DAC at 6.4 GS/s results in a Nyquist frequency of 3.2 GHz. The image then appears at 3.7 GHz, which provides 1 GHz of transition for a low-cost filter implementation to drop out the image.

The DAC blocks on the RFSoC are specified to be capable of a full-scale output power of either 1 dBm or 5 dBm depending on the supply voltage and which current mode is selected. Only the 1 dBm mode is available for use due to limitations of the carrier board. An impedance matching network and balun is placed in between the DAC terminals and the carrier off-board SSMC connector. From a simplified simulation this network should have a worst case insertion loss of 4 dB without accounting for routing and connector loss. In reality, the maximum power the DAC channels are capable of supplying off board is around -8 dBm. Post normalization this

number drops around 2 dB to -10 dBm. The mixer used has a 1 dB compression point of 15 dBm [13]. A 17 dB gain block amplifier with a low noise figure and relatively low gain roll-off is placed at the beginning of the IF chain. The reduced bandwidth requirement of the IF section means a lower cost amplifier can be used. An amplifier with a low  $S_{22}$  is desired to prevent reflections from the mixer getting back into the mixer and producing extra slightly delayed chirps, increasing the overall noise level.

A compact LTCC 3 GHz low pass filter (LPF) follows the amplifier to drop out the IF image in the second Nyquist band. In the case of DACs in the RFSoC the analog bandwidth is wide enough to allow for reasonable operation in the second Nyquist band, meaning that the analog roll-off is insufficient at curtailing the image. While operating in the second Nyquist band can be useful, in this application the image only serves to create more mixer products (see section 4.2.2). The filter chosen provides an insertion loss of at least 37 dB across 85% of the image band, and at least 20 dB over the remaining 15% [14].

The IF port is the only RF port on the mixer not buffered by an SPDT switch. The switches have an input return loss exceeding 20 dB and an insertion loss of 1 dB over the bands of interest. Inserting the switches grants an improvement in reflections relative to a direct connection between the mixer and amplifiers further down the chain. The extra insertion loss, from both the switch internals and the added routing loss, serves to attenuate potential reflections from other components as well. A wide-band, 1 dB pad is placed in front of the mixer IF port to similarly reduce reflections. The pad was chosen such that the footprint used would allow for easily changing to a pad of different value if it proved to be necessary.

#### 2.2.2 Switched Filter Bank

The mixer used in this design, like most mixers, produces several intermodulation distortion (IMD) products that interfere with the desired signal. The mechanism behind this is covered in more detail in section 4.2.2 along with a method to reduce in-band products. That method for in-band products is implemented during the digital signal generation process and does not affect some of the out-

of-band products. Out-of band (OOB) products must be attenuated using a physical band pass filter.

The IF band defined previously is 2.2 GHz wide. Tiling that 2.2 GHz across the desired 2 GHz to 8 GHz means that the range can be covered in four bands with the necessary overlap using only two LO frequencies: 4.5 GHz and 6 GHz. The resulting bands are then the high and low sides of the up-conversion, as presented in table 2.2.

| LO (GHz) | High-side (GHz) | Low-side (GHz) |

|----------|-----------------|----------------|

| 4.5      | 5 - 7.2         | 1.8 - 4        |

| 6        | 6.5 - 8.7       | 3.3 - 5.5      |

Table 2.2: Filter band definitions

Each filter is constructed using pairs of high-pass and low-pass LTCC MMIC filters from Mini-Circuits. Premade MMIC filters were chosen for their time and cost savings. Using this stackup, microstrip filters that achieve the necessarily large fractional bandwidths would be spatially large and require tighter manufacturing tolerances. Similarly, working with discrete components for filter design at these frequencies requires accounting for all the parasitics involved in their placement and manufacturing in turn increases in complexity. The initial design of both types is also time consuming relative to working from a restricted selection of already available ICs. This restriction in available filters was influential in the selection of the two LO frequencies. The first order LO feedthrough product from the mixer is the closest and usually most powerful OOB product. Having to select the sets of filters that could transition from the pass-band to the stop-band in 500 MHz to eliminate the LO feedthrough for four different bands is the reason why there are non-uniform band overlaps of 500 MHz, 700 MHz, and 500 MHz.

Arranging the filters during the early design was carried out through a quick optimization process with simulations using manufacturer provided network parameters. Pads were placed in between certain adjacent filters to improve their impedance match.

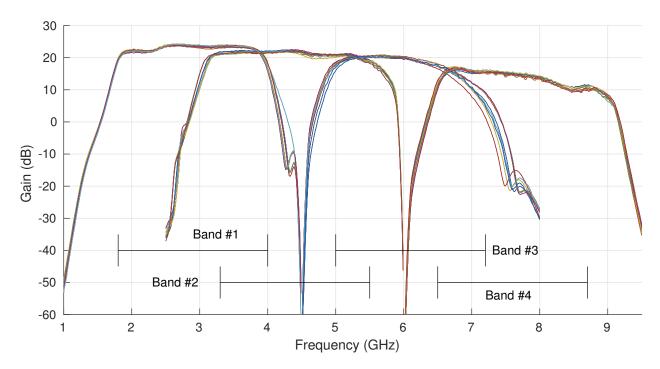

The noticeable 9 dB roll-off is expected and is due to the compounding roll-off of the active components in the chain. High roll-off is acceptable as long as the pass-band gain remains above

Figure 2.4: Gain of the four transmission bands of the 9 assembled transmitter boards with respect to the input sweep, as measured by a VNA at the output port intended to drive the antenna (post amplifier). The mixer LO port was driven with a 0 dBm, 4.5 GHz tone for bands 1 and 3 and a 6 GHz tone for bands 2 and 4. The IF signal was a stepped frequency sweep from 10 MHz to 3.5 GHz at a constant -10 dBm.

10 dB, which is the minimum gain required to transmit at 0 dBm given the driving power of the DAC.

In the default logic low switch state, both switches turn to a port terminated with a 50  $\Omega$  load. The terminated state serves an extra means to mute the majority of active devices in the transmitter without having to change the input signal. A passthrough channel is included as well to serve as a reference path for characterizing the devices around the filter banks without the band defined attenuation.

### 2.2.3 Receiver Reference Signal

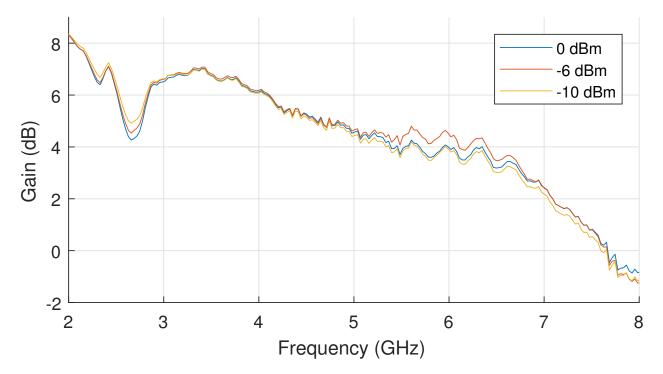

The signal the receiver uses as a reference for the dechirp is expected to be identical to the transmitted signal. A 1:2 power divider is included in the transmit module to provide that reference. Since the LO port of the RX mixer does not need, and could be damaged by, the maximum power at the transmitter output, the divider is placed in advance of the final TX gain stage. The signal routed to the receiver is around 13 dB lower than the transmitted signal and has a slightly different frequency response as it does not include the amplifier's roll-off. This means that an otherwise normalized transmit signal will appear at the receiver with a slight inverse roll-off. Fortunately the amplifier at the receive mixer's LO port means the performance of the mixer is relatively invariant to changes in the LO input power. This behavior is shown in Figure 2.5.

Figure 2.5: The gain of the receivers RF stage and mixer across varied levels of LO power to highlight the relatively invariant conversion loss. While constant across RF frequency, the gain from the IF stage has been approximated and subtracted out. See Figure 2.7 for the relevant component diagram.

#### 2.2.4 Mixer Bypass

The SPDT switches sitting at the LO and RF ports of the mixer form a simple mixer bypass network. A mixer bypass feature was added to increase the potential utility of the transmit module design by allowing for operation in other radar architectures. When enabled, the signal from the LO is passed directly through to the gain blocks and filter bank. If this is used in conjunction with

an RF synthesizer capable of quickly hopping frequencies and a wide-band IQ-demodulator, a potentially low cost stepped-frequency radar could be constructed. The switched filter bank should be able to eliminate many of the harmonics that are common to some lower cost RF synthesizers and the power divider preceding the final gain block would produce the reference signal for the demodulator. The switches controlling the filter bank have sub-µs switching times[15]. Assuming that multiple frequency steps are taken inside a single band, this module should impose minimal restrictions on the maximum average frequency step-rate.

### 2.3 LO Generation and Digital Control

An FPGA Mezzanine Card (FMC) module was developed to provide the necessary control signals for the transmit and receive modules. The module also generates the LO signal for all of the upconverters using a single synthesizer. This module style was chosen because the only exposed connector available on the carrier board is a Vita 57.4 FMC connector.

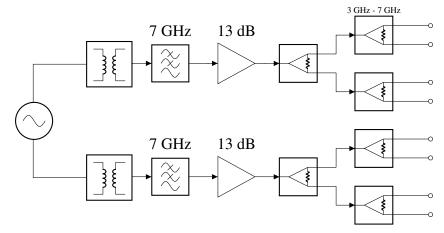

Figure 2.6: Synthesizer output chain

Figure 2.6 shows the RF conditioning chain at the outputs of the synthesizer chip. The synthesizer used is a PLL with built-in VCO that advertises low phase noise and fast PLL calibration and lock. It has two differential outputs with adjustable power up to 5 dBm. Following a balun at the output of the synthesizer the signal is passed through identical low-pass filters with a cut-off frequency of 7 GHz used to drop out the first harmonic at the lowest LO frequency: 9 GHz when

producing a 4.5 GHz tone. An amplifer is included in each chain to compensate for the 7 dB insertion loss incurred through the power splitter network. The power splitter was selected for its low phase unbalance to minimize phase error between adjacent transmit channels. The two channels of the synthesizer are phase aligned [16] so the bulk of the phase unbalance is introduced in either the splitter network or cables feeding the transmit channels.

Testing showed that the synthesizer module was capable of achieving lock in around 7 µs when the quick calibration settings were properly loaded. Since the switches on the transmit boards have a lower 10-90 RF switching time [15] the LO is only switched once during a full-bandwidth sequence of sweeps. The low and high sides of each LO are selected first before switching to the next LO frequency, resulting in the operating sequence being as follows:

1. Lock to 4.5 GHz.

- 2. Switch to band 1 (1.8 GHz 4 GHz) and chirp.

- 3. Switch to band 3 (5 GHz 7.2 GHz) and chirp.

- 4. Adjust PLL and lock to 6 GHz.

- 5. Switch to band 2 (3.3 GHz 5.5 GHz) and chirp.

- 6. Switch to band 4 (6.5 GHz 8.7 GHz) and chirp.

In addition to the synthesizer, the FMC module also contains multiple level translators and ribbon cable headers. The level translators are used to drive the 3.3 V logic on the transmitter boards from the 1.8 V logic on the FPGA. An additional translator is required to drive the synthesizer module as well. Extra header slots are exposed for both debugging purposes and for extending the GPIO capabilities of the carrier board for potential later additions such as external timing interfaces, other non-radar sensor control, or a GPS stream.

#### 2.4 Receiver Design

In this work the section of the radar that performs the dechirping of the received signal and the conditioning of the IF is referred to as the receiver. FMCW radar operation allows for a straight-forward receiver architecture: a mixer serves as the central component and performs the dechirping with some conditioning applied to each of the RF, LO, and IF ports.

The receiver section of the snow and wheat radars could be used in conjunction with this transmitter design, as they fully cover the bandwidth this radar is expected to operate over: both are high performance receivers that operate over 2-18 GHz. Given that bandwidth, a new low-pass filter on the RF port would be needed if those designs were to be reused in this radar as the 8-18 GHz band would only serve to raise the noise floor. In place of swapping out the band pass filter in one of those designs, a new lower cost, lower power receiver was designed and integrated into the system. Lower frequency components with smaller passbands are cheaper to acquire and reduce design constraints. Assembly time is typically reduced due to higher physical tolerances as well. The design is shown in Figure 2.7 with the associated insertion losses and filter cutoff frequencies.

Figure 2.7: Flow diagram of receive module. All numbers in (dB) represent component gain and all numbers in (Hz) imply the cut-off frequency of the filter component.

Before finalizing and assembly this design was simulated and adjusted using ADS and manufacturer provided scattering parameters. Insertion loss from the routing was mostly ignored. From the simulations, the receiver gain in the pass band rolls off linearly from 53.2 dB at 2 GHz to 42.4 dB at 8 GHz. The estimated noise figure  $F_{Rx}$  also rolls off from 3.55 dB to 6.80 dB across the RF pass band. The estimated (thermal) noise power at the output of the receiver is given in Equation 2.1.

$$P_n = \underbrace{F_{Rx}G_{Rx}kT_0}_{D_n} B_{IF} \tag{2.1}$$

Assuming an antenna noise temperature of  $N_{ant} = -174 \text{ dBm/Hz}$ , a noise power density ranging from  $D_n = -117.2 \text{ dBm/Hz}$  at 2 GHz to  $D_n = -124.8 \text{ dBm/Hz}$  at 8 GHz can be expected. Assuming a 125 MHz IF bandwidth (using  $|S_{21}| < 20 \text{ dB}$  as the cut-off), this works out to a total noise power around -36 dBm.

An ideal 12 bit ADC would have a maximum SNR of 6.02dB \* 12 + 1.76dB = 74dB. The 12 bit ADC has a full scale input of 1 dBm with a 100  $\Omega$  termination and a maximum noise spectral density of -147 dBFS/Hz below 240 MHz [12]. The effective IF bandwidth is 125 MHz with the FIR decimation enabled. Quantization noise power  $P_Q$  for the ADC is then  $D_Q * BW =$ -66 dBFS = -65 dBm. From section 2.2.1 the insertion loss of the balun and matching network in front of the ADC can be expected to be at least 9 dB. If a minimum quantization SNR of least 4 dB is expected then the minimum input signal power to the carrier board is -53 dBm and the maximum (full scale) input signal power is 10 dB, for a dynamic range of 63 dB.

Equation 2.2 is the calculation for the minimum discernible signal (MDS) of a system using pulse compression [17]. Pulse compressed systems introduce the compression gain  $G_c$  which is the equivalent of the time-bandwidth product of the input waveform. Pre-summing introduces the  $N_{presum}$  term which assumes multiple coherent signals will be combined digitally.  $N_{presum}$  is an integer count of the number of pre-sums performed by the system.

$$MDS = \frac{kTBF}{G_c N_{presum}}$$

(2.2)

Assuming a receiver temperature of 290 K, a worst case receiver noise figure of 6.8 dB, a 2.2 GHz bandwidth chirp lasting for 10  $\mu$ s, an IF bandwidth *B* of 125 MHz, and 4 pre-sums, the receiver has a MDS of around -135 dBm. Applying the 42 dB average gain of the receiver to a -135 dBm signal results in a -93 dB signal that is 37 dB lower than the ADC limited minimum input power

to the carrier board.

#### 2.4.1 Receiver RF Input Chain

The antennas perform moderately well over the bands of interest. Signals from outside the ideal operating bandwidth of the antennas will also be present at the output as the broadband nature of the antennas means the transition out of the usable radiating band is not sharp. A bandpass filter is needed in front of the RF port because of this. Like the transmit modules, this bandpass filter is constructed from COTS discretely packaged filters. The low pass filter is the same as the low pass filter used in the highest band of the switched filter bank in the transmitter. A multilayer organic (MLO) filter was chosen as the high pass filter. MLO packaging competes with LTCC in assembly density, as the low loss organic dielectric allows for a very dense stackup [18]. While this filter was selected in part as an evaluation and demonstration of the technology in a radar, the main selecting factors were the pass-band performance and high rejection below the cutoff. The stopband starts 150 MHz below the pass band and provides at least 44 dB of attenuation. It has a worst case insertion loss of 1.3 dB at 3.3 GHz, but for 90% of the pass band it is lower than 1 dB. At 3.3 GHz the return loss is around 7 dB which means around 20% of incident power at that frequency will be reflected back to the antennas and re-radiated. When picked up by adjacent antennas the reflections appear as extra clutter around the target, spreading out the target return. Despite this, no other COTS filter met this performance at this price point. A pad is placed in between the low and high pass filters to improve the match between them.

A LNA is included before the mixer to compensate for the bandpass filter insertion loss and conversion loss of the mixer, and to serve as a means of isolating the mixer RF port from the antennas. The LO to RF leakage in this mixer is rated as a maximum power level due to the embedded LO amplifier. At less than -25 dBm it is significantly greater than the minimum detectable signal (MDS) of the receiver [19]. The worst case inter-element coupling on the receive array is -11 dB at 2.5 GHz for immediately adjacent elements. If a -25 dBm LO-RF leakage were to pass unattenuated back to the antenna it would appear at the adjacent receiver as a -36 dBm signal, which

is significantly greater than the required MDS of the receiver. Inserting an amplifier with a low  $|S_{12}|$  reduces the amount of power from the mixer making it back to the antenna. From the RF input chain simulation, the  $S_{12}$  at the worst case frequency of 2.5 GHz is -32 dB, which means the power of the signal appearing at the other receiver as previously calculated is now -68 dBm. 1 dB of padding is inserted between the amplifier and the mixer to improve the match and further attenuate reflections from the amplifier before they reach the mixer. Such reflections would result in spreading of the target spectrum. The simulated scattering parameters for the RF input chain are presented in Figure 2.8. This simulation uses manufacturer provided parameters and does not account for insertion loss from board routing.

Figure 2.8: The simulated *S*-parameters for the receiver RF input chain. The markers only identify traces and do not correspond to datapoints.

The final assembly was characterized using the VNA offset frequency mode, and the final

forward gain of the assembled receiver boards is shown in Figure 2.9. The visible 9 dB roll-off is due mostly to the LNA as the mixer conversion loss only increases by 2 dB across the bandwidth. The dip at 2.8 GHz is most likely due to a mismatch between the high pass and low pass filter chain. Aside from those two issues the filters behave as desired and there is decent consistency in gain across the boards.

Figure 2.9: The measured gain of the receiver across 9 boards. The in-band peak at 2 GHz is 47.5 dB and the in-band minimum is 38.5 dB at 8 GHz.

The input impedance for the RF port and the IF port is shown in Figure 2.10. An acceptable return loss is seen at the RF port that improves on the expected simulated values in Figure 2.8. While plotted out to 10 GHz the IF port behavior only matters out to 250 MHz assuming out-of-band signals are sufficiently attenuated before returning to the mixer. It improves on the simulations as well and maintains >15dB return loss out to 1 GHz. The measurement stops at 10 MHz unfortunately, which means a less than ideal return loss could be visible in a valid operating region of the IF bandwidth.

Figure 2.10: The measured input impedance for the RF and IF ports on one of the receiver boards.

### 2.4.2 Receiver Mixer LO Port

The reference chirp produced by the transmitter should be relatively free of OOB signals as it is already filtered by the switched filter bank. No extra filter is needed in front of the LO port of the receive mixer; nothing else is present between the off-board (SMA) connector and the LO port aside from a small matching network to block DC and improve mixer return loss. While there is an amplifier for the LO built-in to the mixer, conversion loss increases as LO power drops out of the nominal -6 dBm to 6 dBm range. The LO signal from the transmitter is designed to remain within those bounds across the bands, but insertion loss from the cable and connectors should still be considered. In 1:1 operation, where there is one receiver for every transmitter, a three and a half inch flex-rigid cable is used to connect the transmitter LO output and the receiver LO input. Knowing the length of the cable is important in establishing the reference for feedthrough interference, as discussed further in Section 2.4.3. For 2:1 operation, where there are two receivers

for every transmitter, a 2 way power divider is connected to the transmitter and receivers via six inch flex-rigid cables. The connectorized resistive power divider was selected for its low phase unbalance to reduce variations in phase between the receivers [20]. 8:1 operation uses the same divider as the one used to test the antennas described in Section C.2, but is driven by the antenna output of the transmitter in place of the LO port.

One of the largest sources of interference in an FMCW radar is feed-through that presents a shortened path to the RF input port of the dechirping mixer. Any signal that couples from the LO reference path to the RF path will present a close range false target due to the minimal time delay. This is minimized through maximizing the isolation between the RF input chain and the LO input chain on the receiver. A dense array of fencing vias was placed between the two paths on the receiver module to bring the isolation between the two above 55 dB, which is the RF-LO isolation of the mixer, the weakest link in the chain. The receiver RF-LO isolation has only been simulated using Keysight ADS and physical measurements have not been taken regarding this. Beyond the receiver module another feedthrough path exists between the transmit and receive antennas. Past airborne snow radars have achieved greater than 80 dB antenna isolation by separating the antennas several meters and encasing them in metal enclosures lined with RF absorbing tiles [6]. Such a robust setup is not feasible with a ground platform so alternative methods must be taken. Section 3.4.2 presents the isolation between the transmit and receive antenna arrays with different physical separations. The isolation is maximized, or the  $S_{21}$  is minimized, through modifications to the relative positioning of the antenna arrays.

### 2.4.3 Receiver IF Chain Design

In an LFM radar architecture the signal incident on the receiver from the antennas is dechirped using a reference signal generated locally, frequently sourced from the same transmitted signal. This incident signal is comprised of reflections of the transmitted signal from the various targets in the scene, along with some noise. Each reflected signal arrives at the receiver delayed by the time required for it to travel the range (d) to the target and back:

$$t_d = \frac{2 \cdot d}{c} \tag{2.3}$$

When the received signals are mixed with the reference signal as a part of the dechirping process (the application of the matched filter) the output IF consists of tones where the frequency of each tone is directly related to the time delay and the chirp rate.

$$f_{IF} = \frac{BW_{chirp}}{T} \cdot t_d = k \cdot t_d \tag{2.4}$$

For an LFM chirp that is windowed in time, the maximum range of the system is then limited by the chirp duration T, as any reflection received after the chirp completes will have no reference to be matched with.

$$d_{max} = \frac{T \cdot c}{2} \tag{2.5}$$

The SNR for a target signal in this setup continuously decreases as the range to the target increases. This is a result of the increasing IF frequency; the overlap in time of the reference chirp and the signal from the target decreases as the time delay is increased. This assumes no stretch processing is carried out which would involve a modification to the matched filter process described previously. One example of this consists of generating a second reference chirp after the first to reduce the IF frequency for longer range targets. The received RF signal could also be directly captured, which would allow for directly applying the matched filter digitally. Both example techniques resolve the issue of range dependent SNR, but typically require either extra hardware or higher bandwidth digitizers than would otherwise be required for the architecture described above. The former technique has been tested and implemented on the snow radar deployed during the 2018 OIB season [7]. Methods for implementing both techniques with the hardware detailed in this section are described in Section 4.2.4.

Obtaining the range dependent design constraints for the IF chain requires applying Equation 2.4 to knowledge of the expected operating conditions. A radar operating at or near ground level and directed towards nadir will see close targets, with a well defined maximum range. Beyond that range it can be assumed the bulk of the response consists of off-angle clutter, multipath back scatter, and noise. As mentioned in section 2.4.2 the antenna feedthrough is a strong source of interference; the direct path from the transmit antenna to the receive antenna appears as a strong target return at the input since maintaining low antenna isolation is difficult. The IF corresponding to the feedthrough target return depends on the antenna spacing and the electrical length of the path to the antennas.

As this system is designed to be relatively compact, the antennas will be co-located with the rest of the system. For ease of handling and calculation, the transmit and receive antennas were both connected to the system using 14" (355.6 mm) flex-rigid cables with a PTFE dielectric sleeve. Assuming PTFE has a relative dielectric permittivity of  $\varepsilon_r = 2.1$  the propagation speed through the cable is around 69% that of the vacuum, and the travel time for a single cable then is 1.72 ns. If the antennas are spaced 3 cm apart at the closest point and 45 cm at the farthest, then the round trip travel time for a feedthrough signal ranges from 3.54 ns to 4.94 ns. With a chirp-rate corresponding to 2 GHz in 10 µs and a zero-length reference path those times result in a feedthrough IF band of 778 kHz to 1.08 MHz for example. The reference path as implemented is a few inches long which drives the IF lower than that of the previously assumed zero-length reference path. Increasing or decreasing the length of the cable delivering the reference signal from TX to RX can be used to externally adjust the expected IF in a fashion similar to raising or lowering the chirp rate.