## ABSTRACT

| Title of dissertation:    | SPINTRONICS-BASED ARCHITECTURES<br>FOR NON-VON NEUMANN COMPUTING                   |

|---------------------------|------------------------------------------------------------------------------------|

|                           | Ankit Mondal<br>Doctor of Philosophy, 2020                                         |

| Dissertation directed by: | Professor Ankur Srivastava<br>Department of Electrical and<br>Computer Engineering |

The scaling of transistor technology in the last few decades has significantly impacted our lives. It has given birth to different kinds of computational workloads which are becoming increasingly relevant. Some of the most prominent examples are Machine Learning based tasks such as image classification and pattern recognition which use Deep Neural Networks that are highly computation and memory-intensive. The traditional and general-purpose architectures that we use today typically exhibit high energy and latency on such computations. This, and the apparent end of Moore's law of scaling, has got researchers into looking for devices beyond CMOS and for computational paradigms that are non-conventional. In this dissertation, we focus on a spintronic device, the Magnetic Tunnel Junction (MTJ), which has demonstrated potential as cache and embedded memory. We look into how the MTJ can be used beyond memory and deployed in various non-conventional and nonvon Neumann architectures for accelerating computations or making them energyefficient.

First, we investigate into Stochastic Computing (SC) and show how MTJs can

be used to build energy-efficient Neural Network (NN) hardware in this domain. SC is primarily bit-serial computing which requires simple logic gates for arithmetic operations. We explore the use of MTJs as Stochastic Number Generators (SNG) by exploiting their probabilistic switching characteristics and propose an energyefficient MTJ-SNG. It is deployed as part of an NN hardware implemented in the SC domain. Its characteristics allow for achieving further energy efficiency through NN weight approximation, towards which we develop an optimization problem.

Next, we turn our attention to analog computing and propose a method for training of analog Neural Network hardware. We consider a resistive MTJ crossbar architecture for representing an NN layer since it is capable of in-memory computing and performs matrix-vector multiplications with O(1) time complexity. We propose the on-chip training of the NN crossbar since, first, it can leverage the parallelism in the crossbar to perform weight update, second, it allows to take into account the device variations, and third, it enables avoiding large sneak currents in transistor-less crossbars which can cause undesired weight changes.

Lastly, we propose an MTJ-based non-von Neumann hardware platform for solving combinatorial optimization problems since they are NP-hard. We adopt the Ising model for encoding such problems and solving them with simulated annealing. We let MTJs represent Ising units, design a scalable circuit capable of performing Ising computations and develop a reconfigurable architecture to which any NP-hard problem can be mapped. We also suggest methods to take into account the nonidealities present in the proposed hardware.

## SPINTRONICS-BASED ARCHITECTURES FOR NON-VON NEUMANN COMPUTING

by

Ankit Mondal

## Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2020

Advisory Committee: Professor Ankur Srivastava, Chair/Advisor Professor Bruce Jacob Professor Manoj Franklin Professor Donald Yeung Professor Mohammad Hajiaghayi © Copyright by Ankit Mondal 2020

## Dedication

To my parents, for their love and constant support.

#### Acknowledgments

I would like to thank several people who have been a part of my life, either in my professional environment or otherwise, in the last few years and with me in this incredible journey. First of all, I would thank my PhD advisor Prof. Ankur Srivastava for having always patiently guided me in my work. I owe him my gratitude for teaching me the basics of doing research. His invaluable advice in several circumstances has helped me to navigate through difficult situations. His knack for looking for the right research problems and the best ways to approach them always kept me motivated and hopeful.

I would like to thank my committee members Profs. Donald Yeung, Mohammad Hajiaghayi, Bruce Jacob and Manoj Franklin for their willingness to sit through and evaluate my work, and Profs. Franklin and Jacob for their useful feedback after my candidacy exam.

I would also express my gratitude towards my colleagues and friends in the lab, both in the past and in the present. During the start of my PhD, I could always look to my seniors Chongxi Bao, Zhiyuan Yang, Yang Xie and Yuntao Liu for guidance as they helped bridge any gap in communication and understanding with my advisor. Thanks are also due to Abhishek Chakraborty and Mike Zuzak whose experience I could count on in situations that were new to me. Them, and the new members of our lab Daniel Xing and Nina Jacobsen, and my other friends in College Park made sure that graduate student life wasn't monotonous.

Lastly, I would like to acknowledge the moral support and love that my parents have provided me during my time away from home and their faith in me.

## Table of Contents

| De  | edicat                            | ion                                                                                                                                                                                                                                                                                      | ii                                                                 |

|-----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Ac  | know                              | ledgement                                                                                                                                                                                                                                                                                | iii                                                                |

| Ta  | ble of                            | f Contents                                                                                                                                                                                                                                                                               | iv                                                                 |

| Lis | st of [                           | Tables                                                                                                                                                                                                                                                                                   | vii                                                                |

| Lis | st of I                           | Figures                                                                                                                                                                                                                                                                                  | iii                                                                |

| Lis | st of A                           | Abbreviations                                                                                                                                                                                                                                                                            | x                                                                  |

| 1   | Intro<br>1.1                      | oduction<br>Focus and outline of thesis                                                                                                                                                                                                                                                  | $\frac{1}{5}$                                                      |

| 2   | Preli<br>2.1<br>2.2<br>2.3<br>2.4 | 2.2.1Magnetic Tunnel Junction2.2.2Other spintronic devices2.2.3Memristive devices2.2.3Memristive devicesNon-conventional and Non-von Neumann Computing2.3.1The Resistive Crossbar ArchitectureNon-conventional computing paradigms2.4.1Approximate Computing2.4.2Probabilistic Computing | 7<br>9<br>11<br>12<br>14<br>15<br>18<br>20<br>21<br>21<br>21<br>21 |

| 3   | Stoc<br>3.1<br>3.2<br>3.3         | hastic Computing with MTJ for Neural NetworksIntroductionPreliminaries3.2.1Stochastic Computing3.2.2Computational units in SCMTJ-based Stochastic Computing3.3.1Characteristics of Magnetic Tunnel Junctions3.3.2MTJ as a Stochastic Number Generator3.3.3Proposed Biased MTJ-SNG        | $23 \\ 23 \\ 25 \\ 25 \\ 26 \\ 27 \\ 28 \\ 29 \\ 30 \\ 31$         |

|   | 3.4  | Energ   | y Efficient MTJ-based NN Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   |      | 3.4.1   | NN implementation in the SC/ISC domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|   |      | 3.4.2   | Problem Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|   |      | 3.4.3   | Optimizing a 1-layer NN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   |      | 3.4.4   | Optimizing 2-layer NNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|   | 3.5  | Regula  | arization and Constraints for Classification problems 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   |      | 3.5.1   | Regularization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|   |      | 3.5.2   | Classification Specific Customization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|   | 3.6  | Simula  | ation Methodology and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|   |      | 3.6.1   | Evaluation setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|   |      | 3.6.2   | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   | 3.7  | Concl   | usion $\ldots \ldots 50$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 4 | T.,: | 4 Thus: | ning of MTJ Neural Network Crossbar 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 4 |      |         | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|   | 4.1  |         | $1$ uction $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|   | 4.2  | 0       | round $\ldots \ldots 54$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

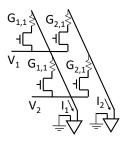

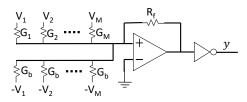

|   |      | 4.2.1   | Crossbar Architecture for Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|   | 4.0  | 4.2.2   | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|   | 4.3  |         | Crossbar based Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|   |      | 4.3.1   | Training Binary Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|   |      | 4.3.2   | The Motivation for In-situ Training                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|   |      | 4.3.3   | Network Binarization and MTJ as a synapse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|   | 4.4  |         | 1 Training of the NN Crossbar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|   |      | 4.4.1   | Overview of Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|   |      | 4.4.2   | Stochastic Learning of an MTJ Synapse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

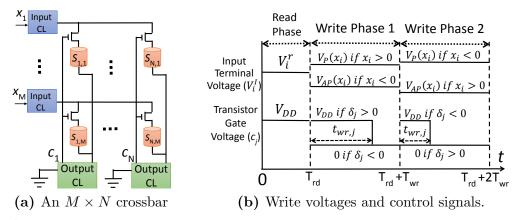

|   |      | 4.4.3   | The 1T1R Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|   |      |         | 4.4.3.1 Updating the crossbar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

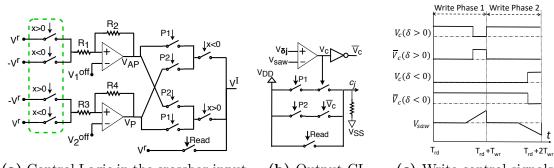

|   |      |         | $4.4.3.2  \text{Control circuits}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  67$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

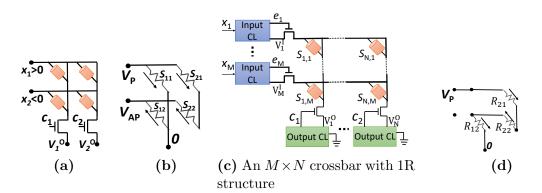

|   |      | 4.4.4   | The 1R Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

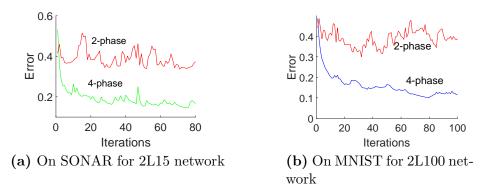

|   |      |         | $4.4.4.1  \text{Two-phase update}  \dots  \dots  \dots  \dots  \dots  \dots  69$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|   |      |         | 4.4.4.2 Four-phase Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|   |      |         | Multi-Layer NNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|   | 4.5  | Traini  | ng of Restricted Boltzmann Machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|   |      | 4.5.1   | Basics of RBM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|   |      | 4.5.2   | Deep Belief Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|   |      | 4.5.3   | Adaptation of the Contrastive Divergence algorithm 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|   |      | 4.5.4   | Training of RBM MTJ crossbar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|   |      | 4.5.5   | MTJs for hidden units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|   | 4.6  | Simula  | ation Setup and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|   |      | 4.6.1   | Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|   |      |         | 4.6.1.1 Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

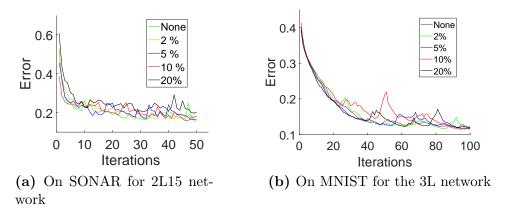

|   |      |         | $4.6.1.2  \text{Results}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

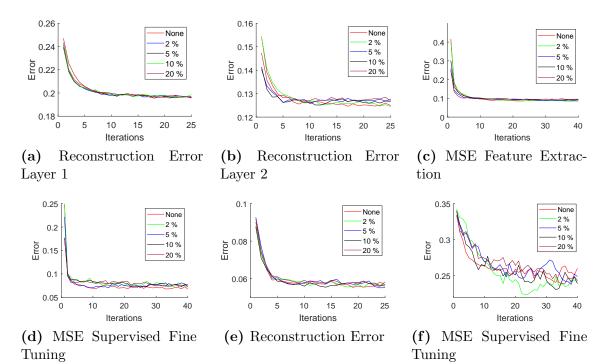

|   |      | 4.6.2   | Deep Belief Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|   | 4.7  | Discus  | ssion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|   | 4.8  | Conch   | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ |  |

| 5  | MT.    | J-based | Ising Model Architecture                 | 100   |

|----|--------|---------|------------------------------------------|-------|

|    | 5.1    | Introd  | luction and Related Work                 | . 100 |

|    |        | 5.1.1   | Related Work                             | . 101 |

|    |        | 5.1.2   | Our contribution                         | . 102 |

|    | 5.2    | The Is  | sing Model                               | . 103 |

|    | 5.3    | Ising-I | FPGA Framework                           | . 105 |

|    |        | 5.3.1   | Finding local optimum in the Ising model | . 105 |

|    |        | 5.3.2   | MTJ as an Ising spin unit                | . 106 |

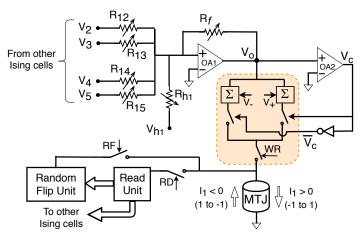

|    |        | 5.3.3   | MTJ-based Ising-FPGA cell                | . 110 |

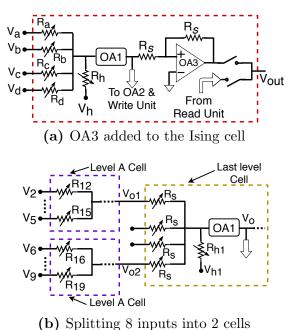

|    |        | 5.3.4   | Splitting inputs to multiple cells       | . 112 |

|    | 5.4    | Archit  | secture of the Ising-FPGA                | . 114 |

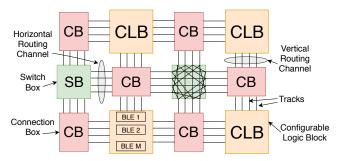

|    |        | 5.4.1   | Architecture of an FPGA                  | . 115 |

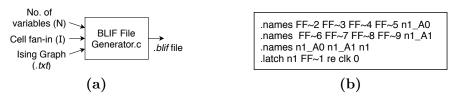

|    |        | 5.4.2   | Reconfigurable Ising model hardware      | . 116 |

|    |        | 5.4.3   | Signal Degradation and Recovery          | . 118 |

|    | 5.5    | Ising g | graphs of NP-hard problems               | . 121 |

|    |        | 5.5.1   | Maximum Cut                              | . 121 |

|    |        | 5.5.2   | Travelling Salesman Problem              | . 121 |

|    | 5.6    | Simula  | ation Setup and Results                  | . 123 |

|    |        | 5.6.1   | Methodology                              | . 123 |

|    |        | 5.6.2   | Results                                  | . 124 |

|    | 5.7    | Discus  | ssion                                    | . 127 |

|    | 5.8    | Conclu  | usion                                    | . 128 |

| 6  | Con    | clusion | and Future Work                          | 129   |

|    | 6.1    | Ising ( | Graph simplification                     | . 129 |

|    | 6.2    | 0       | morphic Computing with Spintronics       |       |

| Bi | bliogr | aphy    |                                          | 132   |

|    |        |         |                                          |       |

## List of Tables

| 3.1        | Comparison of Normal and Biased MTJ-SNG                                                                                                | . 31  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.2        | Notations for problem formulation of 1-layer NN                                                                                        | . 36  |

| 3.3        | Variation of 1-layer network energy and classification error rate on                                                                   |       |

|            | the MNIST test dataset                                                                                                                 | . 45  |

| 3.4        | Results for the MNIST 2-layer network for select values of error                                                                       |       |

|            | threshold of the outer layer                                                                                                           | . 46  |

| 4.1        |                                                                                                                                        |       |

| 4.1        | The write phase. Signs of $x$ , $\delta$ , and $\Delta W$ , required change in weight                                                  |       |

|            | W and conductance G, and the desired direction of switching of MTJ                                                                     | 60    |

| 4.0        | Synapse                                                                                                                                | . 60  |

| 4.2        | Boundary values of the parameters in the weight update eqn. $(2.3)$                                                                    | co    |

| 4.9        | and their counterpart in probabilistic switching of MTJ.                                                                               | . 63  |

| 4.3        | The coefficients that fit the model for both $AP \to P$ and $P \to AP$                                                                 | . 63  |

| 4.4        | switching                                                                                                                              |       |

| 4.4<br>4.5 | 4-phase weight update for the 1R configuration in fig $4.6(c)$ The stages of CD training when different currents (fig. $4.10(b)$ ) op- | . (1  |

| 4.0        | erate on the hidden units and the switches that are active                                                                             | . 84  |

| 4.6        | Notations for MTJ curve fitting                                                                                                        |       |

| 4.7        | Classification error rates for the 3 datasets with various NN and cross-                                                               | . 04  |

| т.1        | bar architectures under different training scenarios.                                                                                  | . 89  |

| 4.8        | Misclassification rates of NNs with stochastic training of 1T1R and                                                                    | . 05  |

| 1.0        | 1R architectures under different levels of device variations                                                                           | . 89  |

| 4.9        | Misclassification rates with hidden layers trained as RBM for the                                                                      | . 00  |

|            | MNIST and WBCD datasets, for different levels of device variations.                                                                    | 93    |

|            |                                                                                                                                        |       |

| 5.1        | Configuration of Ising cells as per their level                                                                                        |       |

| 5.2        | Descriptions of graphs for Maxcut simulations                                                                                          |       |

| 5.3        | Ising-FPGA hardware usage for Max Cut.                                                                                                 |       |

| 5.4        | Ising-FPGA hardware usage for TSP.                                                                                                     |       |

| 5.5        | Results of Ising simulations for TSP.                                                                                                  | . 127 |

# List of Figures

| 1.1                                    | Major computing frameworks driving the tech sector                                                                                                                                                                                   | 2                              |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

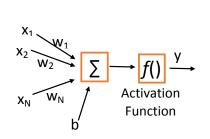

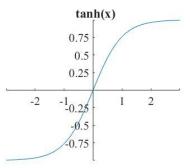

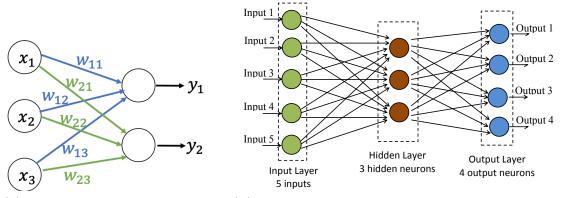

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Schematic of a neuron and the <i>tanh</i> activation function                                                                                                                                                                        | 8<br>9<br>12<br>13<br>19<br>20 |

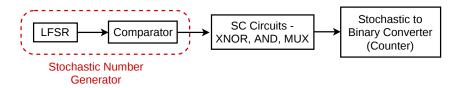

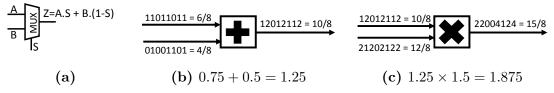

| $3.1 \\ 3.2$                           | Components used in SC and direction of flow of data                                                                                                                                                                                  | 26<br>26                       |

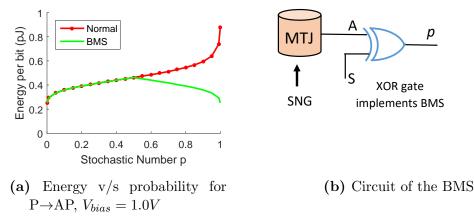

| 3.3                                    | The BMS and variation of energy with value of SN $p$ with and without BMS                                                                                                                                                            | 20<br>30                       |

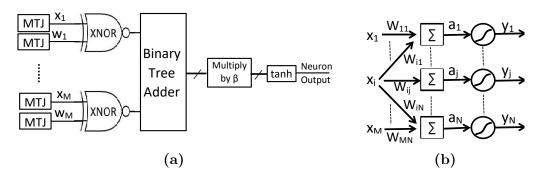

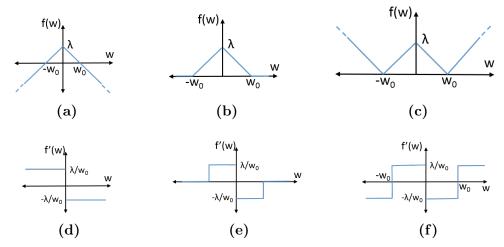

| $3.4 \\ 3.5$                           | Neuron implementation in ISC and Schematic of 1-layer NN Regularization function types 1,2 and 3 respectively and their derivatives                                                                                                  | 34<br>40                       |

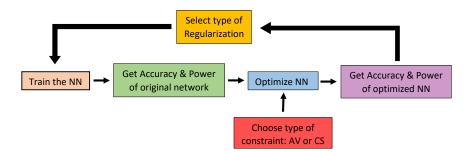

| 3.6                                    | Flow chart showing the process and network optimization and char-<br>acterization                                                                                                                                                    | 44                             |

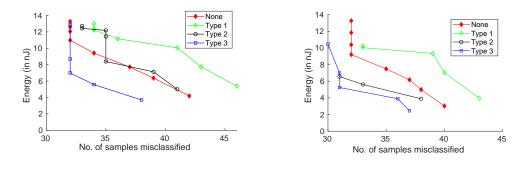

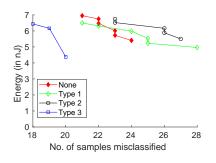

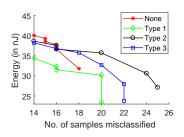

| 3.7                                    | Energy vs classification error rate curve for the MNIST dataset 1-<br>layer NN                                                                                                                                                       | 46                             |

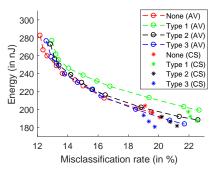

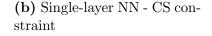

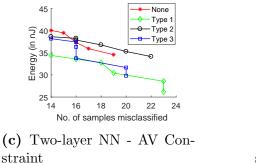

| 3.8                                    | Plot of classification error rate against energy for 2-layer NN of MNIST dataset with AV constraint.                                                                                                                                 | 47                             |

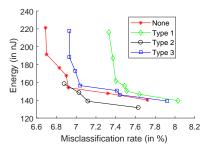

| 3.9                                    | Trade-off between network Energy and classification error rate for the Wine Quality test dataset                                                                                                                                     | 48                             |

| 3.10                                   | Energy v/s inaccuracy in classification for the SONAR dataset                                                                                                                                                                        | 49                             |

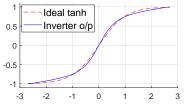

| 4.1<br>4.2                             | A $2 \times 2$ crossbar with selection transistors $\ldots \ldots \ldots \ldots \ldots$<br>Synaptic weights and activation function in each column of the crossbar. Comparison of the output characteristics of the inverter and the | 58                             |

|                                        | actual $tanh$ function                                                                                                                                                                                                               | 60                             |

| 4.3                                    | Comparison of the linear model and desired switching probabilities .                                                                                                                                                                 | 63                             |

| $4.4 \\ 4.5$                           | The 1T1R crossbar. (a) Schematic (b) Read & write phases signals .<br>Circuit of the crossbar's (a) Input, and (b) Output CLs, and (c) Write                                                                                         | 65                             |

| 1.0                                    | phase signals timing diagram                                                                                                                                                                                                         | 68                             |

| Alternate current paths in the 1R structure with 2-phase write strategy     | 69                      |

|-----------------------------------------------------------------------------|-------------------------|

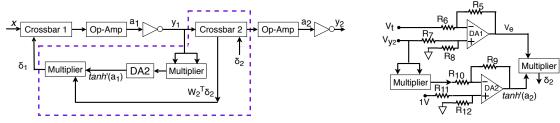

| Circuits for gradient descent and backpropagation                           | 72                      |

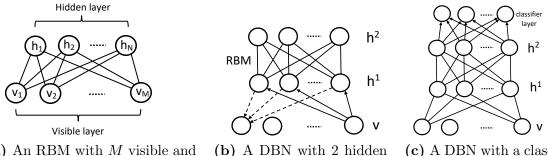

| Schematics of RBM and DBN                                                   | 76                      |

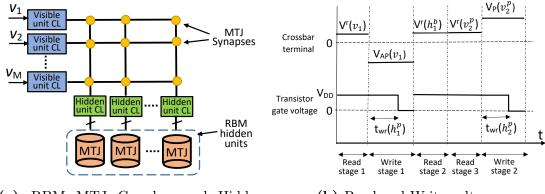

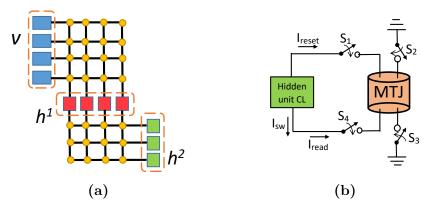

| (a) Crossbar implementation structure of the RBM with MTJs as               |                         |

|                                                                             |                         |

|                                                                             | 80                      |

| - •                                                                         |                         |

|                                                                             |                         |

|                                                                             | 84                      |

| - 0                                                                         |                         |

|                                                                             | 86                      |

|                                                                             |                         |

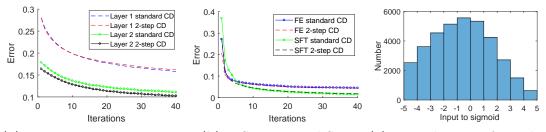

|                                                                             | 90                      |

|                                                                             |                         |

|                                                                             | 90                      |

|                                                                             | 94                      |

|                                                                             | 0 -                     |

| -                                                                           |                         |

|                                                                             | 95                      |

|                                                                             | 00                      |

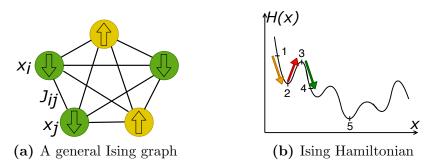

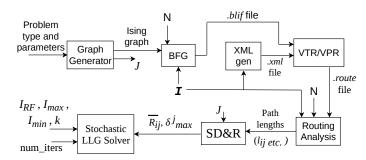

| Ising graph and Ising energy landscape                                      | 104                     |

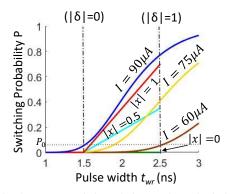

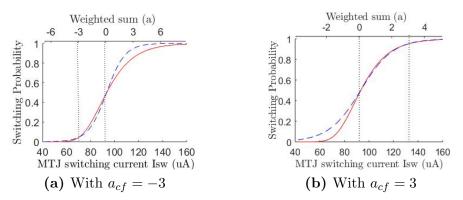

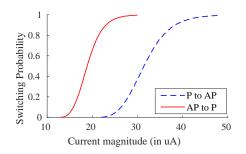

| Switching probabilities of the MTJ with $2ns$ pulse width $\ldots$ $\ldots$ | 107                     |

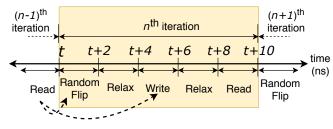

| Different stages of an iteration in the process of finding the ground       |                         |

| state of an Ising model                                                     | 109                     |

| The proposed Ising spin cell                                                | 111                     |

| The Modified Ising cell and multi-level Ising cells                         | 113                     |

| The FPGA architecture                                                       | 115                     |

| The BLIF File Generator and an excerpt from a BLIF file                     | 117                     |

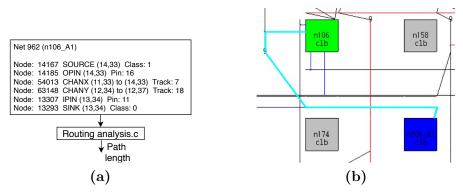

| Routing of nets in the Ising-FPGA                                           | 119                     |

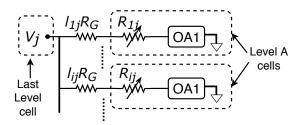

| Signal degradation model for paths from a last level cell (source) to       |                         |

| level A cells (destinations)                                                | 120                     |

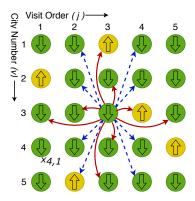

| Arrangement of Ising spin units for a 5-city TSP                            | 122                     |

|                                                                             |                         |

|                                                                             | 123                     |

|                                                                             |                         |

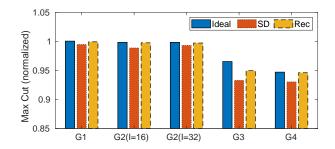

|                                                                             | 126                     |

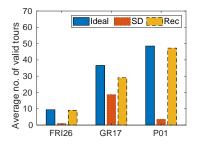

| Average (over 20 runs) no. of valid tours found in a run                    |                         |

|                                                                             | state of an Ising model |

## List of Abbreviations

| ANN                  | Artificial Neural Network         |

|----------------------|-----------------------------------|

| $\operatorname{SC}$  | Stochastic Computing              |

| DNN                  | Deep Neural Network               |

| ML                   | Machine Learning                  |

| AI                   | Artificial Intelligence           |

| MTJ                  | Magnetic Tunnel Junction          |

| STT-MRAM             | Spin-Transfer Torque Magnetic RAM |

| ASL                  | All Spin Logic                    |

| MAC                  | Multiply and Accumulate           |

| ADC                  | Analog to Digital Converter       |

| RRAM                 | Resistive RAM                     |

| SNG                  | Stochastic Number Generator       |

| SN                   | Stochastic Number                 |

| DBN                  | Deep Belief Network               |

| RBM                  | Restricted Boltzmann Machine      |

| MLP                  | Multi-layer Perceptron            |

| ISC                  | Integral Stochastic Computing     |

| FSM                  | Finite State Machine              |

| P/AP                 | Parallel/Anti-Parallel            |

| BMS                  | Biased MTJ-SNG                    |

| LFSR                 | Linear Feedback Shift Register    |

| MSE                  | Mean Square Error                 |

| AV                   | Absolute Value                    |

| $\operatorname{CS}$  | Classification Specific           |

| SNN                  | Spiking Neural Network            |

| STDP                 | Spike-Timing Dependent Plasticity |

| CD                   | Contrastive Divergence            |

| RRAM                 | Resistive RAM                     |

| 1T1R                 | 1-Transistor 1-Resistor           |

| $\operatorname{CL}$  | Control Logic                     |

| LLG                  | Landau-Lifschitz-Gilbert          |

| DA                   | Differential Amplifier            |

| $\operatorname{SFT}$ | Supervised Fine Tuning            |

| FPGA                 | Field Programmable Gate Array     |

| VTR                  | Verilog to Routing                |

| VPR                  | Versatile Place and Route         |

| CLB                  | Configurable Logic Block          |

| BLE                  | Basic Logic Element               |

| LUT                  | Look-up Table                     |

| $\operatorname{SB}$  | Switch Box                        |

| BLIF                 | Berkeley Logic Interchange Format |

| BFG                  | BLIF File Generator               |

| TSP                  | Travelling Salesman Problem       |

| CWF                  | Channel Width Factor              |

|                      |                                   |

#### Chapter 1: Introduction