# Low-power accelerators for cognitive computing

# Marc Riera Villanueva

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori in stitucion a l UPCommons (http://upcommons.upc.edu/tesis) i el repositori cooperatiu TDX (http://www.tdx.cat/) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA** La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<u>http://upcommons.upc.edu/tesis</u>) y el repositorio cooperativo TDR (<u>http://www.tdx.cat/?locale-attribute=es</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual **únicamente para usos privados enmarcados** en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (*framing*). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING** On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutional repository UPCommons (<u>http://upcommons.upc.edu/tesis</u>) and the cooperative repository TDX (<u>http://www.tdx.cat/?locale- attribute=en</u>) has been authorized by the titular of the intellectual property rights **only for private uses** placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# Low-Power Accelerators for Cognitive Computing

Marc Riera Villanueva

Doctor of Philosophy

Department of Computer Architecture Universitat Politècnica de Catalunya

Advisors: Jose-Maria Arnau, Antonio González

June, 2020 Barcelona, Spain

# Abstract

Deep Neural Networks (DNNs) have achieved tremendous success for cognitive applications, and are specially efficient in classification and decision making problems such as speech recognition or machine translation. Mobile and embedded devices increasingly rely on DNNs to understand the world. Smartphones, smartwatches and cars perform discriminative tasks, such as face or object recognition, on a daily basis. Despite the increasing popularity of DNNs, running them on mobile and embedded systems comes with several main challenges: delivering high accuracy and performance with a small memory and energy budget. Modern DNN models consist of billions of parameters requiring huge computational and memory resources and, hence, they cannot be directly deployed on low-power systems with limited resources. The objective of this thesis is to address these issues and propose novel solutions in order to design highly efficient custom accelerators for DNN-based cognitive computing systems.

As a first step, we characterize popular DNNs for different applications on General-Purpose-Architectures (GPAs) such as CPU and GPGPU. DNNs are composed of multiple layers of neurons whose core operation is the dot product between the inputs of each neuron and its weights. The weights of a DNN model are learned during the training procedure and used at inference. We observe that the main performance and energy bottleneck of GPA systems is the memory hierarchy due to the huge number of inputs, weights, and partial products, resulting in numerous data movements. Thus, we develop a baseline architecture for accelerating DNN inference based on a state-of-the-art DNN accelerator. After identifying the memory subsystem as the main bottleneck, we introduce an on-chip eDRAM memory to store the weights, and an SRAM buffer to store inputs and temporal partial results. The on-chip memories favor the reuse of data among different executions of the DNN, reducing the accesses to main memory, and improving the performance and energy efficiency of the accelerator.

Efficient support for DNNs on CPUs, GPUs and accelerators has become a prolific area of research, resulting in a plethora of techniques for energy-efficient DNN inference. However, previous proposals focus on a single execution of a DNN. Popular sequence processing applications, such as speech recognition or video classification, require many back-to-back executions of the same DNN to process a sequence of inputs (e.g., audio frames, images). In the first contribution of this thesis, we show that consecutive inputs exhibit a high degree of similarity, causing the inputs/outputs of the different layers to be extremely similar for successive frames of speech or images of a video.

Based on the high degree of input similarity observed, we propose DISC, a hardware accelerator implementing a Differential Input Similarity Computation technique to reuse some results of the previous execution, instead of computing the entire DNN. Computations related to inputs with negligible changes can be avoided with minor impact on accuracy, saving a large percentage of computations and memory accesses. Our results show that, on average, more than 60% of the inputs of any neural network layer tested exhibit negligible changes with respect to the previous execution. Avoiding the memory accesses and computations for these inputs results in 63% energy savings on average.

On the other hand, DNN quantization is a common optimization that reduces the precision of the inputs and weights, saving storage and simplifying the computations. Prior works exploit the weight/input repetition that arises due to quantization to avoid redundant computations in Convolutional Neural Networks (CNNs). However, in the second contribution of this thesis we show that their effectiveness is severely limited when applied to Fully-Connected (FC) layers, which are commonly used in state-of-the-art DNNs, as it is the case of modern Recurrent Neural Networks (RNNs) and Transformers.

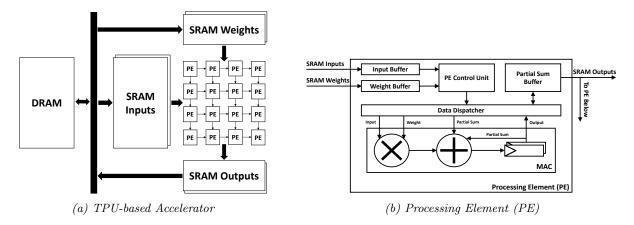

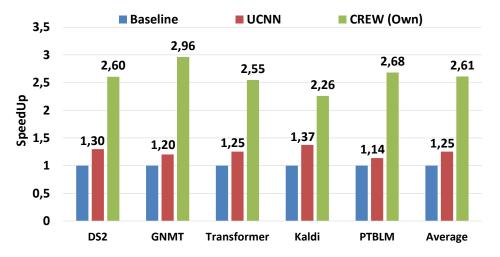

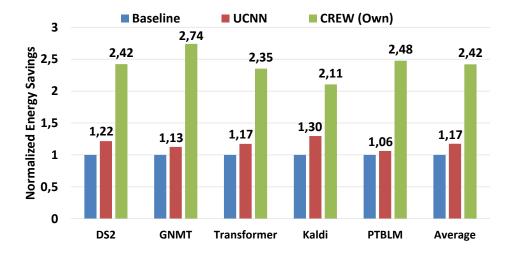

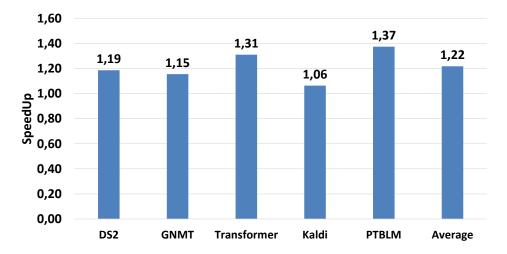

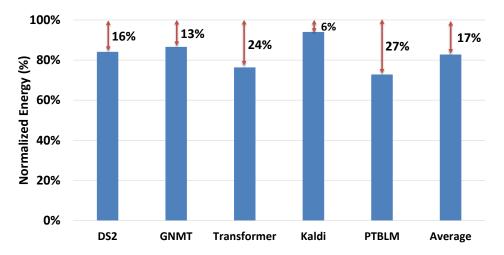

To improve energy-efficiency of FC computation we present CREW, a hardware accelerator that implements Computation Reuse and an Efficient Weight Storage mechanism to exploit the large number of repeated weights in FC layers. CREW first performs the multiplications of the unique weights by their respective inputs and stores the results in an on-chip buffer. The storage requirements are modest due to the small number of unique weights and the relatively small size of the input compared to convolutional layers. Next, CREW computes each output by fetching and adding its required products. To this end, each weight is replaced offline by an index in the buffer of unique products. Indices are typically smaller than the quantized weights, since the number of unique weights for each input tends to be much lower than the range of quantized weights, which reduces storage and memory bandwidth requirements. Overall, CREW greatly reduces the number of multiplications and provides significant savings in model memory footprint and memory bandwidth usage. We evaluate CREW on a diverse set of modern DNNs. On average, CREW provides 2.61x speedup and 2.42x energy savings over a TPU-like accelerator. Compared to UCNN, a state-of-art computation reuse technique, CREW achieves 2.10x speedup and 2.08xenergy savings on average.

Activation pruning has been previously proposed in Convolutional Neural Networks (CNNs) and Multi-Layer Perceptrons (MLPs) to avoid computations by dynamically removing connections whose input value is (close to) zero. However, fine-grained activation pruning results in sparse computations, reducing the efficiency of the hardware implementation, and heavily relies on ReLU activation functions that are unpopular in Recurrent Neural Networks (RNNs). RNN cells perform element-wise multiplications across the activations of different single-layer fully-connected networks, a.k.a. gates, sigmoid and tanh being the common activation functions. We observe that a significant percentage of activations are saturated towards either zero or one in different gates, which results in a large percentage of neuron outputs being multiplied by a value close to zero. We propose Coarse-Grained Pruning of Activations (CGPA) to avoid the computation of entire neurons, rather than pruning individual connections, based on the activation values of the gates. CGPA results in much less sparse computation and memory access patterns than previous proposals and, hence, it can be easily implemented on top of conventional accelerators such as TPU with negligible area overhead, resulting in 12% speedup and 12% energy savings on average for a set of widely used RNNs.

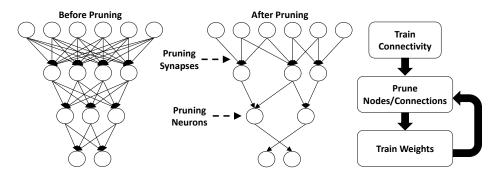

In spite of significantly reducing the size of the models and the number of computations for several DNNs, by using the proposed computation reuse schemes and optimizations, the memory hierarchy is still the main bottleneck of our accelerators. In the last contribution of this thesis, we explore different pruning methods. DNN pruning reduces memory footprint and computational work of DNN-based solutions to improve performance and energy-efficiency. An effective pruning scheme should be able to systematically remove connections and/or neurons that are unnecessary or redundant, reducing the DNN size without any loss in accuracy. We show that prior pruning schemes require an extremely time-consuming iterative process that requires retraining the DNN many times to tune the pruning hyperparameters. Then, we propose a DNN pruning scheme based on Principal Component Analysis and relative importance of each neuron's connection that automatically finds the optimized DNN in one shot without requiring hand-tuning of multiple parameters.

### Keywords

Machine Learning, Deep Neural Network (DNN), Hardware Accelerator, Low-Power Architecture, Computation Reuse, Input Similarity, Weight Repetition, Quantization, Pruning.

## Acknowledgement

Firstly, I would like to express my sincere gratitude to my two advisors, Jose-Maria Arnau and Antonio González, for their continuous support of my PhD study and related research, for their patience, motivation, and immense knowledge. I am very grateful to Prof. Antonio González for offering me the opportunity to start a research career at ARCO in UPC and supporting me during these years. I am always indebted to Prof. Jose-Maria for all that he taught me, the daily meetings and helpful discussions that I had with him, and also for giving me the fruitful ideas to help my work gets mature enough. The guidance of my two advisors helped me in all the time of research and writing of this thesis and the several publications. I could not have imagined having better advisors and mentors for my PhD study. It was, is and will be a great pleasure to work with them.

Besides my advisors, I would like to thank the rest of my thesis committee: Andreas Moshovos, David Brooks, and Jordi Tubella, for their valuable feedback and comments, but also for their questions which incented me to widen my research from various perspectives. I also thank the staff in the Department of Computer Architecture (DAC), human resources and other units of UPC for their kind help and support during these years.

I would also like to thank the various institutions that have granted me with the financial support to finish this thesis. This work has been supported by the the CoCoUnit ERC Advanced Grant of the EU's Horizon 2020 program (grant No 833057), the Spanish State Research Agency under grant TIN2016-75344-R (AEI/FEDER, EU), and the Spanish Ministry of Education under grant FPU15/02294.

I am also very thankful to all the members of ARCO, and specially to my fellow labmates ("The D6ers"). I was lucky enough to be part of a large, well-known and enriching research group. Special thanks to Reza Yazdani with whom I have collaborated, Hamid Tabani, Martí Anglada, Martí Torrents, Gem Dot, Enrique de Lucas, Franyell Silfa, Albert Segura, Dennis Pinto, Diya Joseph, Raúl Taranco, Pedro Exenberger, Jorge Sierra, and Josue Quiroga, for the stimulating discussions, and for all the good moments that we had at UPC in the last years.

Finally, last but by no means least, I would like to thank all my family, and especially my parents and my little brother for their endless love, continuous encouragement and support. I owe my deepest gratitude to my family and I would like to dedicate this thesis to them. I have been extremely fortunate in my life to have parents who have shown me unconditional love and support. The relationships and bonds that I have with my parents hold an enormous amount of meaning to me. I admire them for all of their accomplishments in life, for their independence and for all of the knowledge and wisdom that they have passed on to me over the years. My parents have played a key role in the development of my identity and shaping the individual that I am today. This thesis is dedicated to my family for their endless love, support and encouragement.

# Contents

| 1 | Intr | roduction                                       | 19 |

|---|------|-------------------------------------------------|----|

|   | 1.1  | Motivation                                      | 19 |

|   | 1.2  | Problem Statement, Objectives and Contributions | 22 |

|   |      | 1.2.1 Temporal Reuse                            | 23 |

|   |      | 1.2.2 Spatial Reuse                             | 25 |

|   |      | 1.2.3 Dynamic Pruning                           | 27 |

|   |      | 1.2.4 Static Pruning                            | 29 |

|   | 1.3  | Thesis Organization                             | 31 |

|   |      |                                                 |    |

| 2 | Bac  | kground and Related Work                        | 33 |

|   | 2.1  | Deep Neural Networks                            | 33 |

|   |      | 2.1.1 Fully-Connected Layers                    | 36 |

|   |      | 2.1.2 Convolutional Layers                      | 36 |

|   |      | 2.1.3 Recurrent Layers                          | 37 |

|   | 2.2  | DNN Accelerators                                | 38 |

|   |      | 2.2.1 DaDianNao                                 | 39 |

|   |      | 2.2.2 TPU                                       | 41 |

|   | 2.3  | DNN Optimizations                               | 41 |

|   |      | 2.3.1 Linear Quantization                       | 43 |

|   |      | 2.3.2 Pruning and Sparse Accelerators           | 43 |

|   | 2.4  | Main DNN Pruning Schemes                        | 45 |

|   |      |                                                 |    |

|          |     | 2.4.1 Near Zero Weights Pruning                  | 45 |

|----------|-----|--------------------------------------------------|----|

|          |     | 2.4.2 Node Pruning                               | 46 |

|          |     | 2.4.3 Similarity Pruning                         | 47 |

|          |     | 2.4.4 Scalpel                                    | 47 |

|          |     | 2.4.5 PCA Pruning                                | 48 |

|          | 2.5 | Computation Reuse                                | 49 |

| 3        | Exp | perimental Methodology                           | 51 |

|          | 3.1 | Hardware Acceleration Modeling and Evaluation    | 51 |

|          | 3.2 | DNN Software Implementations                     | 53 |

|          | 3.3 | DNN Models and Datasets                          | 54 |

| 4        | DIS | SC: Differential Input Similarity Computation    | 57 |

|          | 4.1 | Input Similarity and Temporal Reuse Analysis     | 57 |

|          | 4.2 | DISC Accelerator                                 | 60 |

|          |     | 4.2.1 DISC Architecture                          | 61 |

|          |     | 4.2.2 DISC for FC Layers                         | 61 |

|          |     | 4.2.3 DISC for CONV Layers                       | 63 |

|          |     | 4.2.4 DISC for Recurrent Layers                  | 64 |

|          | 4.3 | Evaluation Methodology                           | 64 |

|          | 4.4 | Experimental Results                             | 65 |

|          |     | 4.4.1 Reduced-precision Accelerator              | 69 |

| <b>5</b> | CR  | EW: Computation Reuse & Efficient Weight Storage | 71 |

|          | 5.1 | Unique Weights in FC Layers                      | 71 |

|          | 5.2 | Partial Product Reuse                            | 73 |

|          |     | 5.2.1 Partial Product Memoization                | 73 |

|          |     | 5.2.2 Partial Product Approximation              | 75 |

|          | 5.3 | CREW Accelerator                                 | 78 |

### CONTENTS

|   |     | 5.3.1 Architecture                            |

|---|-----|-----------------------------------------------|

|   |     | 5.3.2 Dataflow                                |

|   |     | 5.3.3 Design Flexibility                      |

|   | 5.4 | Evaluation Methodology                        |

|   | 5.5 | Experimental Results                          |

|   |     | 5.5.1 CREW Evaluation                         |

|   |     | 5.5.2 CREW-PPA Evaluation                     |

|   |     | 5.5.3 Overheads                               |

| 6 | CG  | PA: Coarse-Grained Pruning of Activations 87  |

|   | 6.1 | Analysis of RNN Activations                   |

|   | 6.2 | CGPA Accelerator                              |

|   |     | 6.2.1 CGPA Architecture                       |

|   |     | 6.2.2 CGPA for GRU Layers 92                  |

|   |     | 6.2.3 CGPA for LSTM Layers                    |

|   |     | 6.2.4 Design Flexibility                      |

|   | 6.3 | Evaluation Methodology                        |

|   | 6.4 | Experimental Results                          |

| 7 | PC. | A+UC: The (Pen-) Ultimate DNN Pruning 9'      |

|   | 7.1 | Weaknesses of Previous Static Pruning Schemes |

|   | 7.2 | PCA+UC Pruning Method                         |

|   |     | 7.2.1 Node Pruning Through PCA                |

|   |     | 7.2.2 Pruning Unimportant Connections         |

|   | 7.3 | Evaluation Methodology                        |

|   | 7.4 | Experimental Results                          |

|   |     | 7.4.1 Sensitivity Analysis                    |

|   |     | 7.4.2 PCA+UC Evaluation                       |

### CONTENTS

| 8 | Con | clusions and Future Work | 109 |

|---|-----|--------------------------|-----|

|   | 8.1 | Conclusions              | 109 |

|   | 8.2 | Contributions            | 111 |

|   | 8.3 | Open-Research Areas      | 112 |

# List of Figures

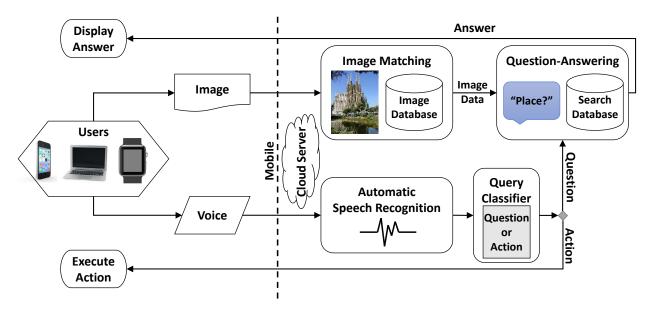

| Diagram of a Virtual Personal Assistant (VPA) Pipeline [29]                                                                                                                                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

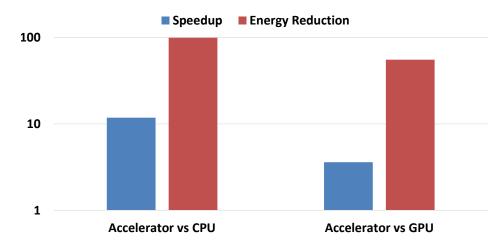

| Average speedup and energy reduction of several DNNs running on an accelerator based on DaDianNao [14]. Baseline CPU and GPU are the Intel i7 7700K and NVIDIA Geforce GTX 1080 respectively                                                                                                                                                                                                                                              | 21                                                                                                                                                                                                 |

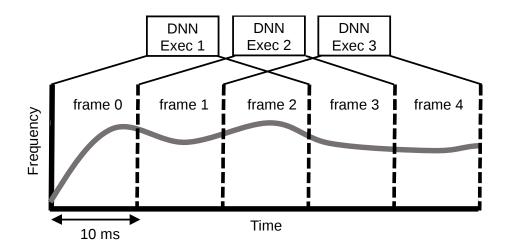

| In speech recognition, the audio signal is split in frames of 10 ms. The DNN is executed multiple times to classify the frames in phonemes. Each DNN execution takes as input a sliding window of several frames.                                                                                                                                                                                                                         | 24                                                                                                                                                                                                 |

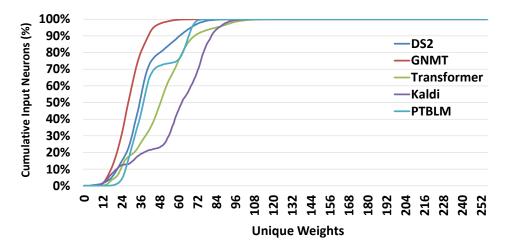

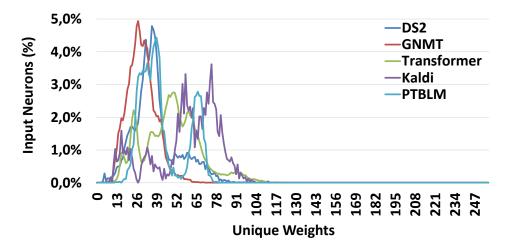

| Cumulative distribution of the unique weights per input neuron from all the FC layers of DeepSpeech2 [4], GNMT [97], Transformer [93], Kaldi [75] and PTBLM [103].                                                                                                                                                                                                                                                                        | 26                                                                                                                                                                                                 |

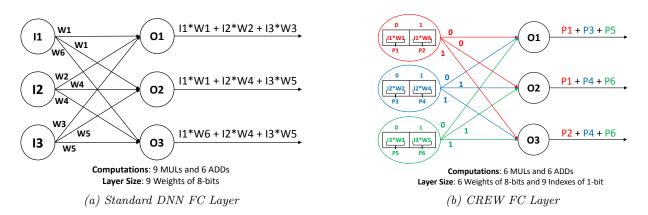

| Standard (a) vs CREW (b) DNN inference for a fully-connected (FC) layer. For<br>each input, CREW only performs the multiplications with unique weights, avoiding<br>redundant computations and memory fetches. Furthermore, it replaces weights by<br>indexes in the buffer of unique multiplications. In this example there are only two<br>unique weights per input, so the 8-bit quantized weights can be replaced by 1-bit<br>indexes | 27                                                                                                                                                                                                 |

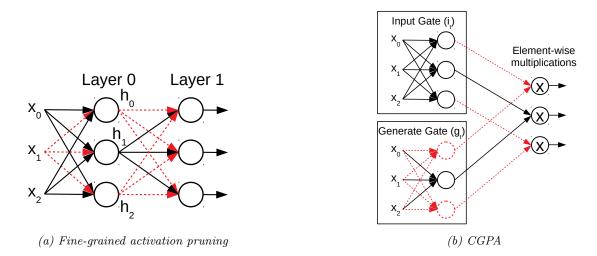

| Fine-grained (a) vs coarse-grained (b) activation pruning. Connections/neurons shown with red dashed lines are dynamically pruned                                                                                                                                                                                                                                                                                                         | 29                                                                                                                                                                                                 |

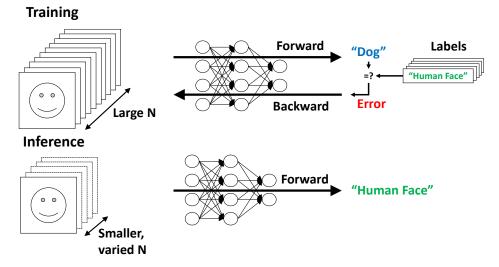

| Example of DNN training vs DNN inference.                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                                                                                                                                                                 |

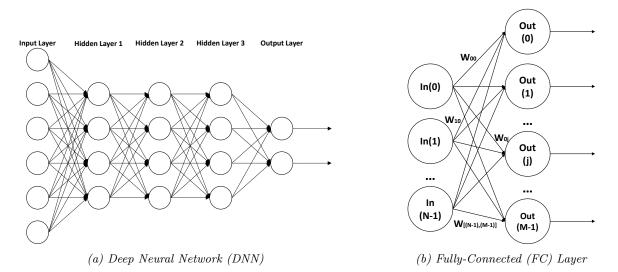

| Example of a DNN from the (a) MLP category composed of (b) FC layers. $\hdots$                                                                                                                                                                                                                                                                                                                                                            | 35                                                                                                                                                                                                 |

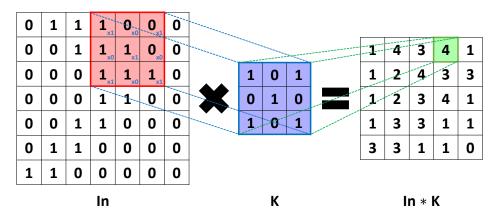

| Convolutional 2D layer                                                                                                                                                                                                                                                                                                                                                                                                                    | 36                                                                                                                                                                                                 |

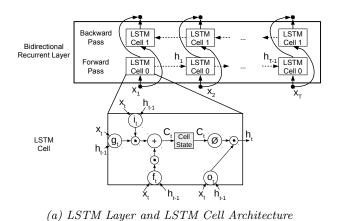

| (a) Bidirectional LSTM layer, architecture of an LSTM cell, and (b) LSTM cell Computations. $\odot$ , $\phi$ and $\sigma$ are element-wise multiplication, hyperbolic tangent and sigmoid function respectively.                                                                                                                                                                                                                          | 37                                                                                                                                                                                                 |

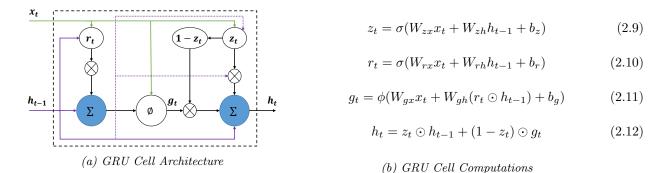

| (a) Architecture of a GRU cell, and (b) Computations performed in a GRU cell. $\odot$ , $\phi$ and $\sigma$ are element-wise multiplication, hyperbolic tangent and sigmoid function respectively.                                                                                                                                                                                                                                        | 38                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           | Average speedup and energy reduction of several DNNs running on an accelerator<br>based on DaDianNao [14]. Baseline CPU and GPU are the Intel i7 7700K and<br>NVIDIA Geforce GTX 1080 respectively |

### LIST OF FIGURES

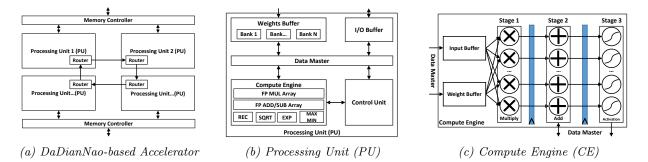

| 2.6 | Architecture of the baseline DaDianNao-based accelerator showing the (a) tile orga-<br>nization, and the main hardware components of the (b) Processing Unit (PU) and<br>the (c) Compute Engine (CE).                                                                                                                                                               | 40 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

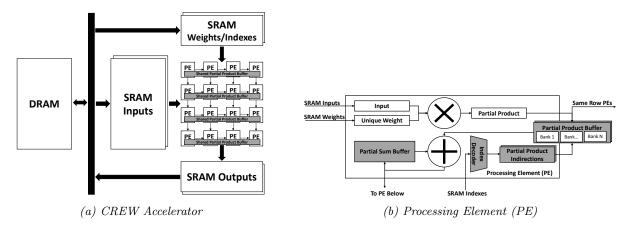

| 2.7 | Architecture of (a) the baseline TPU-based accelerator and (b) a Processing Element (PE)                                                                                                                                                                                                                                                                            | 41 |

| 2.8 | Example of static DNN Pruning.                                                                                                                                                                                                                                                                                                                                      | 44 |

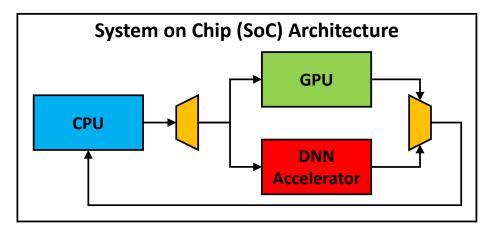

| 3.1 | The SoC architecture includes a CPU, GPU and a DNN accelerator. The CPU pre-<br>processes the inputs of the DNN. Then, the DNN accelerator performs the inference<br>of the DNN model. Finally, the CPU receives the results of the inference and executes<br>a post-processing step to decode the final outputs. In addition, the GPU is used for<br>DNN training. | 52 |

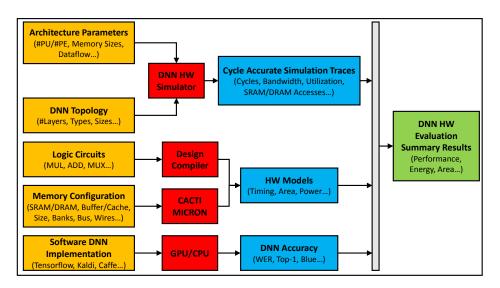

| 3.2 | Methodology flowchart to model and evaluate the DNN accelerators. The inputs to<br>the simulation tools are marked in yellow, the tools and platforms in red, the partial<br>results from the tools are marked in blue, and the final evaluation summaries in green.                                                                                                | 52 |

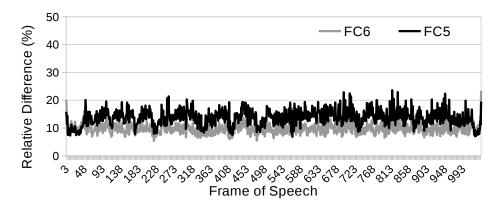

| 4.1 | Relative difference defined as the Euclidean distance between current and previous input vectors, divided by the magnitude of the input vector in the previous execution.                                                                                                                                                                                           | 58 |

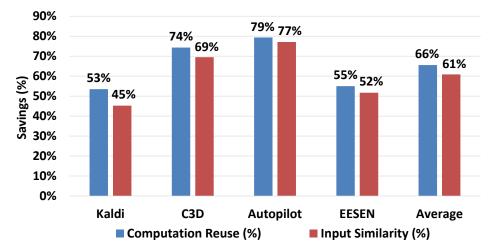

| 4.2 | Input similarity and computation reuse for various DNNs                                                                                                                                                                                                                                                                                                             | 60 |

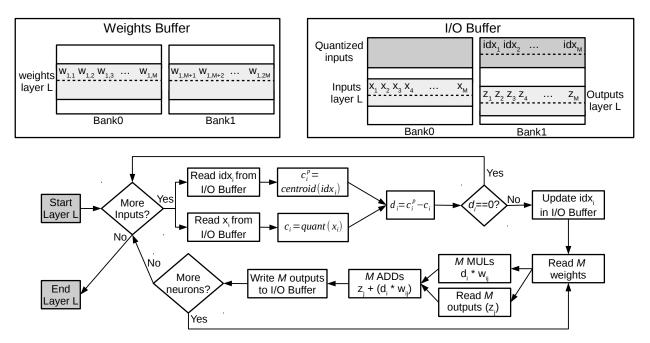

| 4.3 | FC execution in the DISC Accelerator.                                                                                                                                                                                                                                                                                                                               | 62 |

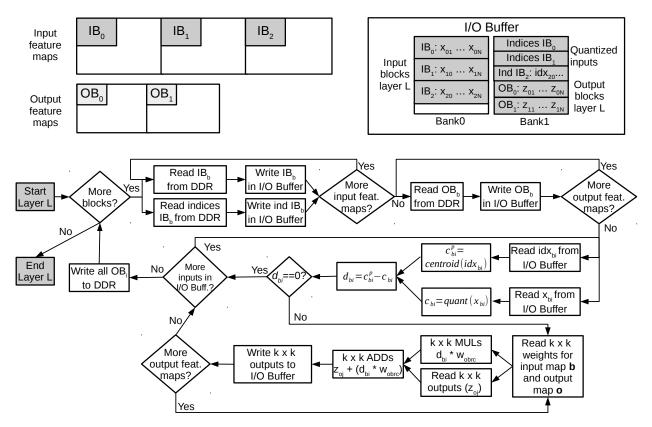

| 4.4 | Execution of a convolutional layer in the DISC accelerator. $IB_b$ means Input Block<br>from input feature map $b$ , whereas $OB_o$ means Output Block from output feature<br>map $o. \ldots \ldots$                                         | 63 |

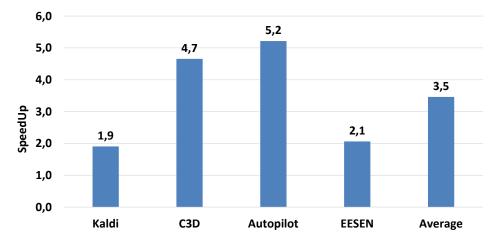

| 4.5 | Speedups achieved by DISC for each DNN. Baseline configuration is the DaDianNao-<br>based DNN accelerator without any computation reuse technique.                                                                                                                                                                                                                  | 66 |

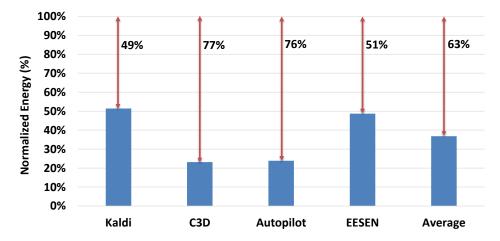

| 4.6 | Normalized energy of DISC for each DNN. Baseline configuration is the DaDianNao-<br>based DNN accelerator without any computation reuse technique.                                                                                                                                                                                                                  | 66 |

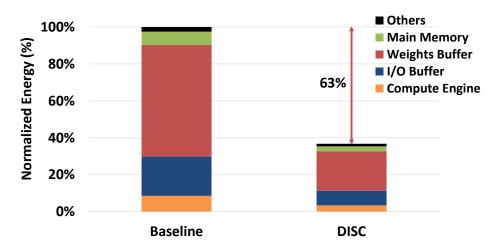

| 4.7 | Energy breakdown for the baseline DaDianNao-based DNN accelerator and the DISC accelerator using the computation reuse scheme.                                                                                                                                                                                                                                      | 67 |

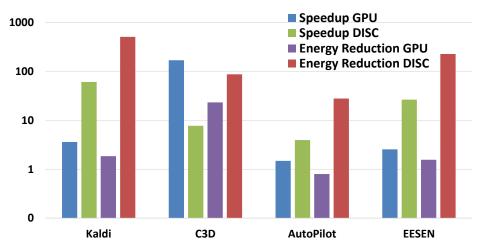

| 4.8 | Speedup and energy reduction of DISC compared to a high-end GPU. Baseline con-<br>figuration is the Intel i7 7700K CPU                                                                                                                                                                                                                                              | 68 |

| 5.1 | Histograms of the unique weights per input neuron from all the FC layers of DS2, GNMT, Transformer, Kaldi and PTBLM.                                                                                                                                                                                                                                                | 72 |

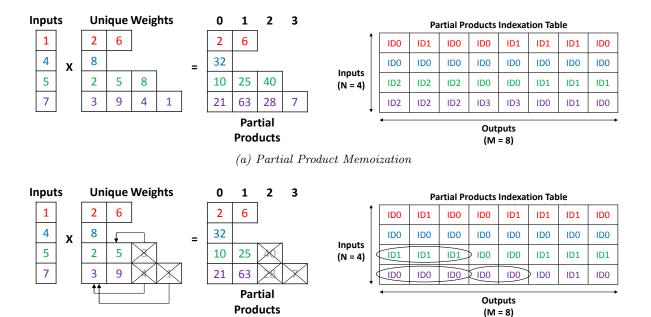

| 5.2 | Example of partial product memoization (a) vs partial product approximation (b) using a small FC layer                                                                                                                                                                                                                                                              | 74 |

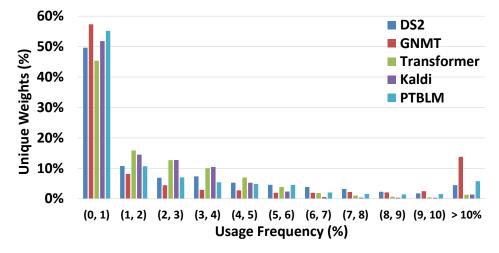

| 5.3  | Usage frequency histograms of the unique weights per input neuron for all the FC layers of DS2, GNMT, Transformer, Kaldi and PTBLM. The frequency of use is the number of times each unique weight is repeated divided by the total number of weights for each input neuron.                                                                                                                          | 76 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

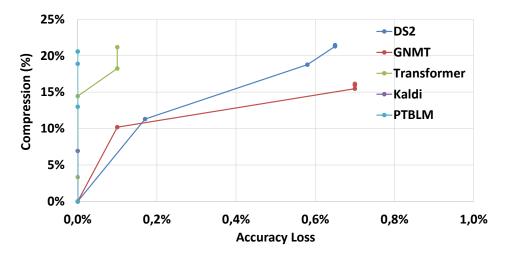

| 5.4  | Accuracy loss versus compression ratio over partial product memoization (CREW without approximation) for different thresholds of the heuristic for unique weight approximation. Thresholds tested go up to 20% in steps of 5%, where the initial 0% threshold means no weight approximation.                                                                                                          | 77 |

| 5.5  | Architecture of (a) the CREW accelerator and (b) a Processing Element (PE). The PE components shaded in gray represent the required extra hardware for CREW. The partial product buffer is shared among all or a subset of PEs of the same row of the array.                                                                                                                                          | 78 |

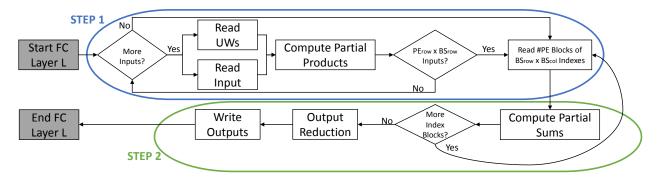

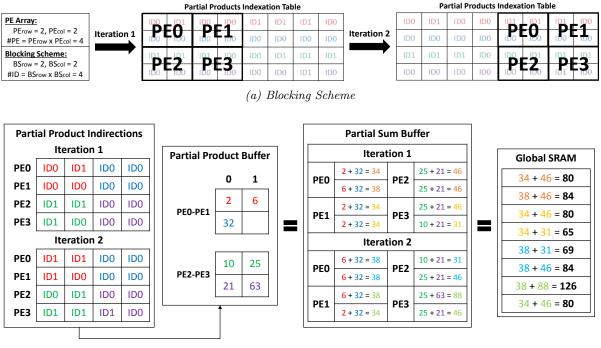

| 5.6  | CREW Execution Dataflow. $PE_{row}$ is the number of PEs per row in the systolic array, and $BS_{row}$ and $BS_{col}$ determine the block size, i.e. the number of indexes per block. $BS_{row}$ refers to the number of indexes relative to different input neurons, while $BS_{col}$ refers to indexes associated to the same input neuron but used in the computation of different output neurons. | 79 |

| 5.7  | FC Execution in the CREW Accelerator.                                                                                                                                                                                                                                                                                                                                                                 | 80 |

| 5.8  | Speedups achieved by CREW and UCNN for each DNN. Baseline configuration is<br>the TPU-like DNN accelerator without any computation reuse mechanism                                                                                                                                                                                                                                                    | 84 |

| 5.9  | Normalized energy savings for each DNN. Baseline configuration is the TPU-like DNN accelerator without the computation reuse technique.                                                                                                                                                                                                                                                               | 84 |

| 5.10 | Speedup of partial product approximation with less than 1% accuracy loss. Baseline configuration is the CREW accelerator.                                                                                                                                                                                                                                                                             | 85 |

| 5.11 | Normalized energy of partial product approximation with less than 1% accuracy loss.<br>Baseline configuration is the CREW accelerator.                                                                                                                                                                                                                                                                | 85 |

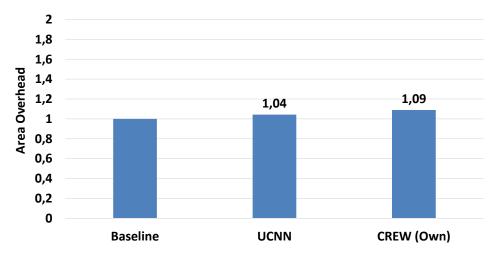

| 5.12 | Area overhead of UCNN and CREW. Baseline configuration is the TPU-like DNN accelerator without any computation reuse technique.                                                                                                                                                                                                                                                                       | 86 |

| 6.1  | Computations performed in (a) LSTM and (b) GRU cells. $\odot$ , $\phi$ and $\sigma$ are element-<br>wise multiplication, hyperbolic tangent and sigmoid function respectively                                                                                                                                                                                                                         | 88 |

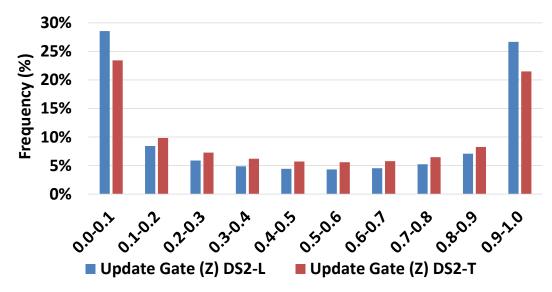

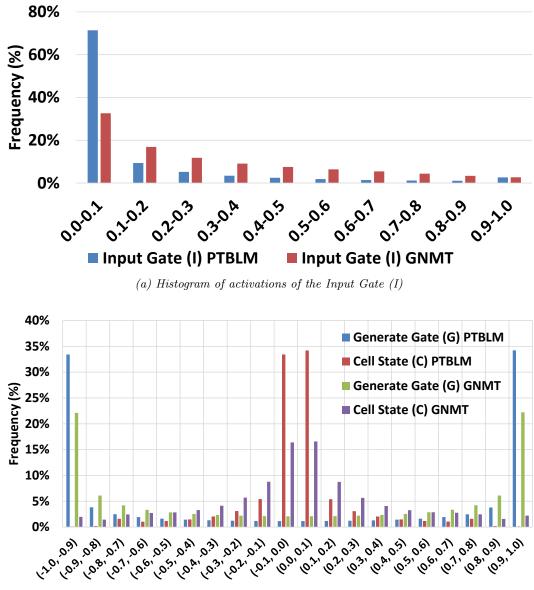

| 6.2  | Histogram of activations of the Update Gate (Z) for DS2-L and DS2-T. $\ldots$ .                                                                                                                                                                                                                                                                                                                       | 89 |

| 6.3  | Input Gate (I) (a), Generate Gate (G) and Cell State (C) (b) histogram of activations for the GNMT and PTBLM RNNs                                                                                                                                                                                                                                                                                     | 90 |

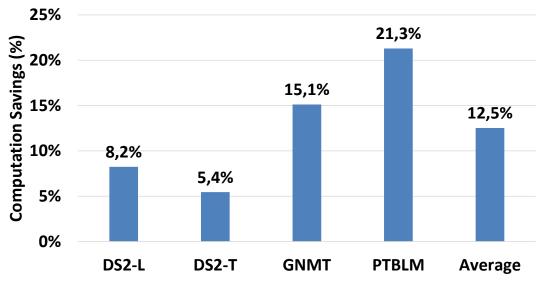

| 6.4  | Computation savings for each RNN.                                                                                                                                                                                                                                                                                                                                                                     | 91 |

### LIST OF FIGURES

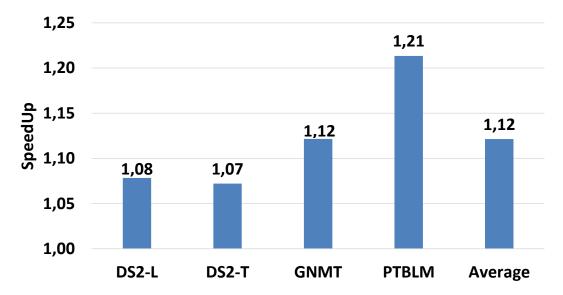

| 6.5 | Speedups achieved for each RNN. Baseline configuration is the TPU-like accelerator without CGPA                       |

|-----|-----------------------------------------------------------------------------------------------------------------------|

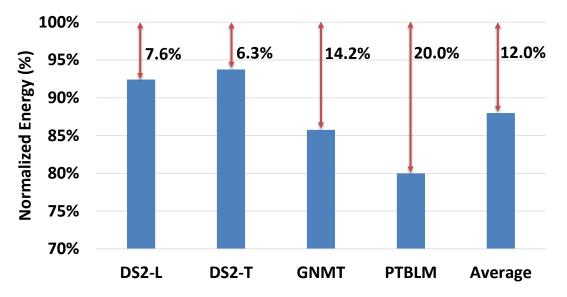

| 6.6 | Normalized energy for each RNN. Baseline configuration is the TPU-like accelerator without CGPA                       |

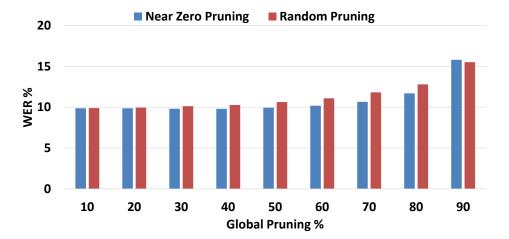

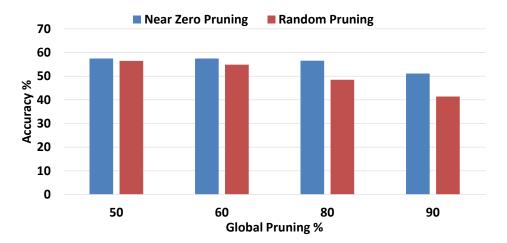

| 7.1 | Comparison between near-zero and random pruning of the Kaldi DNN for different percentages of global pruning          |

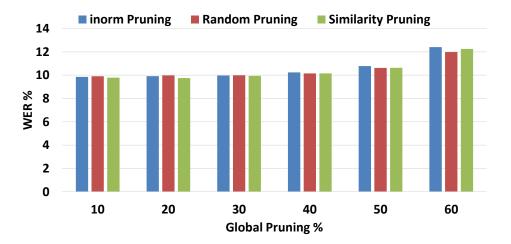

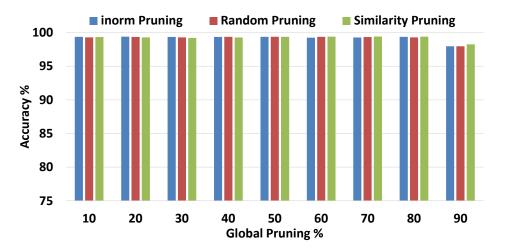

| 7.2 | Comparison between i-norm, similarity and random pruning of the Kaldi DNN for different percentages of global pruning |

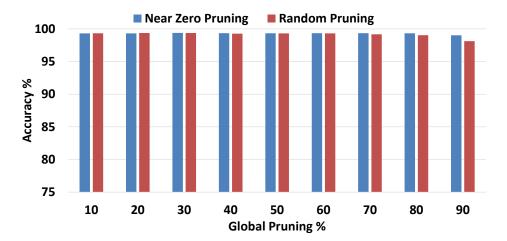

| 7.3 | Comparison between near-zero and random pruning of LeNet5 for different percent-<br>ages of global pruning            |

| 7.4 | Comparison between i-norm, similarity and random pruning of LeNet5 for different percentages of global pruning        |

| 7.5 | Comparison between near-zero and random pruning of AlexNet for different percent-<br>ages of global pruning           |

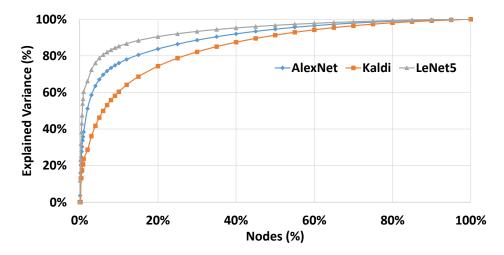

| 7.6 | Cumulative variance of a sample layer of AlexNet, Kaldi and LeNet5 103                                                |

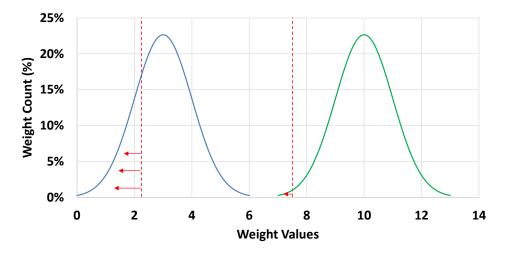

| 7.7 | Example of the weights distribution translation pruning problem                                                       |

# List of Tables

| 3.1 | Parameters of the CPU and GPU employed to evaluate the performance and energy consumption of the DNN software implementations.                                                                                                                                                                                                                                                              | 54 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | DNNs used in the experimental evaluation of the different proposals of this thesis.                                                                                                                                                                                                                                                                                                         | 54 |

| 4.1 | Deep Neural Networks employed for the analysis of computation reuse. The ta-<br>ble only includes Fully-Connected (FC), Convolutional (CONV) and Bidirectional<br>LSTM (BiLSTM) layers, as these layers take up the bulk of computations in DNNs.<br>Other layers, such as ReLU or Pooling, are not shown in the table for the sake of<br>simplicity.                                       | 58 |

| 4.2 | Parameters for the DISC accelerator                                                                                                                                                                                                                                                                                                                                                         | 65 |

| 4.3 | Memory overheads of the DISC accelerator implementing the computation reuse scheme.                                                                                                                                                                                                                                                                                                         | 68 |

| 5.1 | <b>UW/I</b> shows the average number of unique weights per input neuron. <b>MULs</b> is the percentage of multiplications of inputs by unique weights with respect to the total number of multiplications in the original model                                                                                                                                                             | 73 |

| 5.2 | Reduction in multiplications and storage.                                                                                                                                                                                                                                                                                                                                                   | 75 |

| 5.3 | Parameters for the accelerators                                                                                                                                                                                                                                                                                                                                                             | 82 |

| 5.4 | DNNs employed for the experimental evaluation of CREW. The model size accounts for the original FP parameters of the FC layers where CREW is applied                                                                                                                                                                                                                                        | 83 |

| 6.1 | RNNs employed for the evaluation. Only LSTM and GRU layers are included since these layers take up the bulk of computations in RNNs                                                                                                                                                                                                                                                         | 88 |

| 7.1 | DNNs employed for the pruning study. Kaldi is an MLP for acoustic scoring, AlexNet is a CNN for image classification and LeNet5 is a CNN for digit classification. The table only includes Fully-Connected (FC) and Convolutional (CONV) layers, as these layers take up the bulk of computations in DNNs. Other layers, such as ReLU or Pooling, are not shown for the sake of simplicity. | 98 |

### LIST OF TABLES

| 7.2 | Kaldi results after the PCA step (first step) of the proposed pruning scheme using different coefficients of variance. (Baseline WER=10.04%)                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.3 | Kaldi results after the unimportant connections pruning step (second step) of the proposed pruning scheme for different thresholds of the mean. (Baseline WER= $10.04\%$ ) 106 |

| 7.4 | Accuracy (WER) and percentage of weights and computations removed by different pruning schemes for the Kaldi DNN                                                               |

| 7.5 | Accuracy (Top-1) and percentage of weights and computations removed by different pruning schemes for LeNet5                                                                    |

| 7.6 | Accuracy (Top-1) and percentage of weights and computations removed by different pruning schemes for AlexNet                                                                   |

| 7.7 | Link Pruning Comparison for the Kaldi DNN. (Baseline WER=10.04%)                                                                                                               |

# Introduction

This chapter describes the motivation and objectives of this work, explaining the challenges for deploying cognitive computing applications in mobile and embedded devices, and presents a summary of the main proposals and contributions of this thesis in order to perform efficient DNN inference.

### 1.1 Motivation

Deep learning has transformed how mobile and embedded devices interpret and respond to many different types of information/data, as well as the way in which we interact with our devices. The interaction with smart devices in our homes, offices, cars, and pockets is changing and evolving by leaps and bounds. The traditional keyboard and mouse, and even the currently popular touch-screens are being left behind in favor of more intuitive and yet sophisticated interfaces based on cognitive applications such as image, text and speech recognition. Commercial examples of such applications include Virtual Personal Assistants (VPA) [36, 58, 45] like Google's Assistant, Apple's Siri, Microsoft's Cortana and Amazon's Alexa. Figure 1.1 shows an example of such an application. VPAs are meant to interact with an end user in a natural way (i.e. voice, text or images), to answer questions, follow a conversation and accomplish different tasks. These mobile applications are used on a daily basis by millions of people and are powered by efficient deep learning models.

Nowadays, deep learning, and machine learning in general, has expanded its use cases and can be found not only in most of our daily life devices but also in our cities and environment despite not being fully aware of it. Examples range from simple classification and perceptual tasks to control algorithms for autonomous systems [9] (ranging from home robots, to drones and cars) or medical health care systems [65] (e.g. medical diagnose or drug discovery and development). Moreover, we

Figure 1.1: Diagram of a Virtual Personal Assistant (VPA) Pipeline [29].

are witnessing how even mature system components and algorithms can have their performance and functionality improved by deep learning techniques. For example, computer architecture researchers are exploring the integration of neural networks for branch prediction [42], and also in computer system areas such as network protocols, data compression or encryption.

On the other hand, substantial amount of computation power is necessary for enabling cognitive computing applications, which usually comes at the expense of high energy consumption. These requirements make solutions for smart devices to rely on the internet to offload most computations to servers in the cloud. For instance, Apple uses a small local neural network to detect keywords such as "Hey Siri" [88], whereas the bulk of the speech recognition is done in the cloud. Although this approach is functional, the end-user experience is negatively impacted by the limited response time in situations of slow internet connection and the impossibility of interacting with the device if the user is in a place with no internet connection, either because requiring more reliability (e.g. autonomous systems), or due to security and privacy concerns (e.g. health care systems), making it undesirable to entrust our data to a remote server.

Furthermore, users of smart devices are increasingly demanding greater functionality of the applications they use while requiring fast and highly accurate responses. In consequence, leading companies such as Google are actively improving both their software and hardware to efficiently support on-device deep learning applications. In recent years, there is a growing interest in machine learning techniques such as neural networks, and computer systems that are specialized for cognitive applications. Accelerators offer better performance and energy efficiency than general purpose systems, which makes them especially attractive in portable devices such as smartphones and smartwatches, for which battery lifetime has a direct impact on the market share.

Deep Neural Networks (DNN) [82] represent a machine learning approach that delivers the most effective solution to a broad range of applications such as speech and image recognition [75, 48],

Figure 1.2: Average speedup and energy reduction of several DNNs running on an accelerator based on DaDianNao [14]. Baseline CPU and GPU are the Intel i7 7700K and NVIDIA Geforce GTX 1080 respectively.

language modeling [103] or machine translation [97]. Similarly to the human brain, artificial neural networks [56] are formed by different nodes (neurons) and connections (synapses). DNNs are composed of hundreds of layers of interconnected nodes according to the degree of relevance among them. A single execution of a DNN can demand the evaluation of hundreds of millions of model parameters (i.e. synaptic weights). Through a process of learning, these networks are able to adapt the weights in the synapses to accurately infer the sequences of phonemes of an audio signal or the objects in an image. DNN-based systems are ubiquitous and, thus, providing energy-efficient inference of DNNs is a key feature for current and future computing devices.

Accelerators for cognitive computing can deliver accurate and robust DNNs in smart devices. DNN accelerators [14, 43, 25] consist mainly of arithmetic and logical units, a memory system and control units that are integrated into the chip to perform cognitive computing much more efficiently than CPUs and GPUs. We have evaluated several DNNs on a CPU, a GPU and a baseline DNN accelerator. Figure 1.2 shows the average performance speedup and energy savings achieved by a DaDianNao-based DNN accelerator. As can be seen, the accelerator performs faster than both CPU (12x) and GPU (4x), while consuming much less energy (i.e. 100x and 55x compared to the CPU and GPU respectively). The memory system is a key component due to the huge storage capacity required to completely store the parameters of the neural networks, and the high bandwidth requirements.

Moreover, since the main bottleneck in cognitive accelerators is still the memory system, alternative architectural mechanisms for saving bandwidth to the off-chip memory, such as data compression, computation reuse and removal of ineffectual nodes, are effective ways to improve performance and reduce the energy consumption of these accelerators, while maintaining the accuracy of the DNN models. The efficiency of these mechanisms lies in the characteristics of cognitive algorithms, such as the level of parallelism, data reuse and redundancy, or the deterministic memory access patterns.

In summary, we focus on improving the performance and energy efficiency of DNN inference

for mobile and embedded devices. Deep learning techniques, and in particular DNNs, are already an essential component of cognitive computing applications and will have an even more pivotal role in the evolution of smart devices. Therefore, the design of efficient cognitive accelerators is fundamental. In this thesis, we propose novel accelerator architectures and optimizations based on the characteristics of cognitive applications with special emphasis on low-power designs.

### 1.2 Problem Statement, Objectives and Contributions

Recent advances in deep learning techniques have achieved human parity in cognitive applications such as speech recognition or machine translation [98, 97]. In order to achieve levels of accuracy similar to those of humans, DNNs have evolved and grown in complexity. From small Multilayer Perceptrons (MLPs) for simple tasks like recognizing written digits or characters, passing by large Convolutional Neural Networks (CNNs) for recognizing objects in images, to complex Recurrent Neural Networks (RNNs) and Transformers to reach the aforementioned human parity in speech recognition and machine translation. Each type of DNN and application has its own characteristics and challenges to be effectively deployed on mobile and embedded devices. In consequence, one of the objectives of this thesis is the study, characterization and analysis of the main cognitive algorithms and applications.

In parallel with the progress in accuracy, DNNs have become much more complex, increasing their size both in number of layers (i.e. deeper), and in amplitude (i.e. number of parameters per layer). Modern DNN models consist of hundreds of layers and billions of parameters with their respective computations and memory accesses. Therefore, the inference of DNNs requires huge computational and memory resources to be efficiently executed. Even popular commercial DNN accelerators, such as DaDianNao [14] and TPU [43], which have proven to be efficient hardware implementations for DNN inference, struggle to effectively run the latest models. Although stateof-the-art DNN accelerators can achieve high levels of parallelism and perform much faster than general purpose architectures, they still have to perform too many computations and memory accesses to be suitable for low-power devices. On the other hand, DNNs are known to be very fault tolerant [14]. Due to the difficulty to create and train DNNs from scratch, DNN models are usually oversized and include a high degree of redundancy. A popular line of research is to exploit this fault tolerance to statically and/or dynamically change the precision of the operations, prune redundant neurons and/or connections, or reuse previous computations. Although many works have been recently proposed in this regard, they focus on optimizing specific layers, DNNs or applications, still leaving plenty of room and potential for improvement. Another objective of this thesis is to propose different techniques to exploit the DNNs redundancy in order to reduce the number of computations and memory accesses, improving the energy efficiency of the DNN accelerators.

We devote Chapter 2 for presenting a detailed background on the most relevant DNN algorithms for a variety of applications. In addition, we describe common optimizations such as linear quantization to lessen the hardware requirements. Furthermore, we provide a summary of related work on DNN accelerators, pruning methods and computation reuse techniques.

The main objective of this thesis is to propose novel hardware architecture designs to improve the performance and energy efficiency of cognitive accelerators for deep learning applications. To this end, we have evaluated the most important cognitive algorithms for a diverse set of applications on different platforms including CPUs, GPUs, and state-of-the-art DNN accelerators. After discovering that the main bottleneck of all these systems is the memory hierarchy, we propose several optimizations and architectural mechanisms to relax the huge amount of computations, memory storage and memory bandwidth that are required to perform DNN inference.

First, we propose DISC, a novel computation reuse scheme with its corresponding hardware implementation to accelerate DNNs that processes temporal sequences of data such as voice or video. Despite sequence processing applications are very popular, little research has been done to exploit their unique characteristics. Second, we propose CREW, an accelerator implementing a spatial reuse mechanism to efficiently execute fully-connected (FC) layers. Modern MLPs, RNNs and Transformers are mainly composed of FC layers. CREW reduces the amount of computations and memory accesses required to perform inference of the latest FC-based DNN models, improving the performance and energy consumption with respect to state-of-the-art accelerators. Third, we propose CGPA, a technique to further accelerate the execution of RNNs by exploiting the dynamic pruning of activations at a coarse granularity. Finally, prior works have proposed methods to statically prune ineffectual neurons and connections, but we show that prior schemes are ineffective for modern DNNs, and propose a new mechanism to effectively apply pruning.

The following sections outline the problems we target, describe the approach we take to solve each problem and highlight the novel contributions of this thesis.

### 1.2.1 Temporal Reuse

The first technique proposed in this thesis aims to improve the execution of sequence processing applications. Sequence to sequence learning is a broad area with numerous and important applications such as speech recognition, machine translation, video description or language modeling. According to numbers published by Google [43], at least 29% of Google's datacenter workloads are sequence processing. Despite the relevance of these applications, hardware-accelerated DNN systems [14, 25, 3, 76] are commonly optimized for an isolated execution of the DNN. Our research is motivated by the observation that many computations and memory accesses are redundant if we take into account successive executions of a DNN, especially for applications that process a temporal sequence of inputs (e.g., speech, video).

Figure 1.3 illustrates the case of speech recognition, where a DNN is executed many times to classify a sequence of audio frames in phonemes. Consecutive DNN executions have extremely similar inputs due to two main reasons. First, the length of these frames is in the order of several milliseconds. The speech signal is quasi stationary for such a short interval and, therefore, consecutive frames exhibit a high degree of similarity. Second, the DNN uses context information (neighbor frames) to classify each audio frame and, hence, successive executions operate on overlapping windows of frames. Note that other applications such as video processing exhibit similar behavior, as consecutive images in a video tend to be very similar too.

Despite the high degree of similarity, floating point computations are not exactly the same in two successive DNN executions. Nevertheless, DNNs are known to be error tolerant [14]. We leverage this property to boost the potential of reuse across successive executions of the DNN. In

Figure 1.3: In speech recognition, the audio signal is split in frames of 10 ms. The DNN is executed multiple times to classify the frames in phonemes. Each DNN execution takes as input a sliding window of several frames.

particular, we found that linear quantization is a very effective mechanism to increase the ability of the technique to exploit redundancy. Linear quantization [76, 43] is a highly popular technique used to compress the weights of the model and reduce the complexity of the computations. Quantization maps a continuous set of values to a discrete set, favoring the appearance of repeated weights and/or inputs in consecutive executions of the DNN. We observed that by applying quantization to the inputs of various DNNs for speech recognition [107, 101, 87, 63], video classification [92] and selfdriving cars [9], more than 50% of the inputs of fully-connected, convolutional and recurrent layers remain unmodified with respect to the previous DNN execution, whereas quantization has negligible impact in accuracy.

Based on the high degree of redundancy for the inputs of consecutive DNN executions, we propose a mechanism that computes the outputs of each DNN layer by reusing the buffered results of the previous execution. A simple example helps to illustrate this proposal. Let us consider a neuron of a fully-connected layer with three inputs. For the first execution of the DNN, the output  $z^1$  is computed as follows:  $z^1 = i_1^1 w_1 + i_2^1 w_2 + i_3^1 w_3 + b$ , where i, w and b are the inputs, weights and bias respectively. In a similar way, the output of this neuron in the second DNN execution is  $z^2 = i_1^2 w_1 + i_2^2 w_2 + i_3^2 w_3 + b$ . However, if the first two inputs are the same in both executions, the output can be computed more efficiently as:  $z^2 = z^1 + (i_3^2 - i_3^1)w_3$ . In other words, we just need to subtract the old inputs that are different and add the new ones (multiplied by their respective weights). Note that in this case only one weight has to be fetched from memory instead of three, the bias is not required and only three computations are performed instead of six. Moreover, the subtraction of the two inputs can be reused for all the neurons in the same layer, so its cost is practically negligible and, in practice, for the above example the total cost approaches to just two operations. Therefore, for DNNs that exhibit some degree of input similarity across multiple executions, it is more efficient to compute the current output in this way rather than evaluating again the entire DNN from scratch. This mechanism reduces the number of memory accesses and computations by 66% on average.

In this work, we propose DISC, a hardware implementation of the Differential Input Similarity Computation reuse-based DNN inference mechanism. We extend the architecture of a state-ofthe-art DNN accelerator to buffer the outputs of the different layers and reuse them for the next execution. The accelerator quantizes the inputs of each fully-connected, convolutional and recurrent layer, and then it computes the output by using only the inputs that have changed with respect to the previous execution, avoiding the corresponding memory accesses and computations for the inputs that remain unmodified. The extra hardware required for the technique is modest, as the components already available for DNN computation can also be employed for most of the operations, such as quantization. In addition to small changes in the control unit, DISC only requires extra storage for the outputs of each layer. The extra memory represents a small increase in the on-chip storage of the accelerator. Our experimental results show that the overheads are minimal compared to the savings in memory fetches and computations, so the proposed scheme improves performance by 3.5x and reduces energy consumption by 63% on average for several DNNs.

To summarize, the first work of this thesis focuses on energy-efficient, real-time DNN inference. A computation reuse scheme for any sequence processing neural network is proposed. Due to the small overheads, only a small degree of input similarity across DNN executions is required to achieve savings in computations and energy. Chapter 4 presents the analysis of input similarity of several DNNs, describes the hardware implementation of the reuse-based DNN inference technique, and discusses the experimental results of DISC. This work has been published in the 45th IEEE/ACM International Symposium on Computer Architecture [77].

### 1.2.2 Spatial Reuse

The second technique proposed in this thesis improves performance and energy-efficiency of the inference of Fully-Connected (FC)-based DNNs. The complexity of the DNN models continues to grow along with its computational cost and memory requirements, making it difficult to support them on conventional computer systems. Accelerators adopting a systolic array architecture such as TPU [43] from Google, have proven to be efficient hardware implementations to perform DNN inference [13, 72, 59]. The systolic array architecture [50, 51], which was designed for massive parallelization and data reuse, is especially effective for Convolutional Neural Networks (CNNs) since the weights of a layer are shared across a large number of sliding windows and can be reused multiple times. In addition, there has been a plethora of recent proposals to further optimize CNN inference [33, 34, 1]. However, CNNs are just a subset of DNNs with very specific characteristics. Therefore, techniques targeting CNNs do not necessarily achieve similar benefits for other DNN architectures. The second proposal is motivated by the fact that state-of-the-art models for sequence-to-sequence problems are either Recurrent Neural Networks (RNNs) [97, 4] or very deep Multi-Layer Perceptrons (MLPs) such as the Transformer [93], which are both composed of fullyconnected (FC) layers. FC layers exhibit different characteristics with respect to CNNs: weights are not reused by different neurons and the compute to memory access ratio is significantly smaller, i.e., FC layers are more memory intensive.

FC layer computation mainly consists of dot products between a vector of inputs and a matrix of weights. The inputs are generated dynamically while the weights are static and learned during the training phase. Current DNN model sizes are in the hundreds of megabytes (MB) and require

Figure 1.4: Cumulative distribution of the unique weights per input neuron from all the FC layers of DeepSpeech2 [4], GNMT [97], Transformer [93], Kaldi [75] and PTBLM [103].

billions of floating-point (FP) computations to perform inference. Linear quantization is normally applied to compress the weights of the model and reduce the complexity of the computations, which as a side effect favors the appearance of repeated weights. We observed that, on average, more than 80% of the inputs among different FC layers of a set of DNNs are multiplied by less than 64 unique weights. Figure 1.4 shows the cumulative distribution of unique weights per input of DeepSpeech2 (DS2) [4], GNMT [97], Transformer [93], Kaldi [75] and PTBLM [103], which are popular models for speech recognition, machine translation, and language modeling. The average number of unique weights per input is 44 when applying an 8-bit quantization, and can never be higher than 256.

In this work, we show how to efficiently exploit weight repetition on FC layers. We first propose a mechanism (CREW) that dynamically computes and stores the partial products of each input by their associated unique weights in a given layer. This first step removes redundant multiplications due to repeated weights and their associated memory reads. Similar to sparse architectures [25, 72, 106 and their pruning mechanisms [26, 102], the weight repetition patterns are irregular, making it very challenging to achieve net benefits due to the sparse accesses and extra metadata that are required. The partial products stored by this mechanism have to be indexed similar to sparse algorithms. Since the unique weights are known statically, the indexation table can be generated offline. The second step of this mechanism produces the final outputs of a FC layer by accessing the partial products with the associated indices and adding all the required values for each output. The main advantage of this mechanism is that the size of the indices depends on the number of unique weights of each input. As previously described, the number of unique weights is typically lower than 64 so indices will be typically smaller than 7 bits. In consequence, the final size of the model can be further compressed and the memory bandwidth is further reduced. Figure 1.5 shows an example of a small FC layer computing the standard dot product (Figure 1.5a) and the CREW mechanism (Figure 1.5b), saving 33% of multiplications and 20% of storage. On a representative set of modern DNNs, this technique reduces the number of multiplications and memory accesses by 98% and 40% respectively on average. Furthermore, it replaces weights by indices in the buffer of partial results, resulting in 25% reduction of the model size.

Then, we present CREW, a novel accelerator that implements the above computation reuse

### **1.2. PROBLEM STATEMENT, OBJECTIVES AND CONTRIBUTIONS**

Figure 1.5: Standard (a) vs CREW (b) DNN inference for a fully-connected (FC) layer. For each input, CREW only performs the multiplications with unique weights, avoiding redundant computations and memory fetches. Furthermore, it replaces weights by indexes in the buffer of unique multiplications. In this example there are only two unique weights per input, so the 8-bit quantized weights can be replaced by 1-bit indexes.

and efficient weight storage scheme for FC layers. CREW is implemented on top of a TPU-like architecture, but it includes an enhanced weight stationary dataflow. The extra hardware required for the technique is modest since most of the components are already available in the baseline TPU-like architecture. CREW only requires small local buffers to store blocks of indices and some shared buffers to store partial results. The extra memory represents a small increase in the on-chip storage of the accelerator. Our experimental results show that the overheads are minimal compared to the savings in memory fetches and multiplications. CREW improves performance by 2.61x and reduces energy consumption by 2.42x on average over a TPU-like accelerator. Compared to UCNN [34], a recently proposed mechanism for computation reuse, CREW achieves 2.10x speedup and 2.08x energy savings on average.

To summarize, the second work of this thesis focuses on energy-efficient FC layer inference. Chapter 5 presents the analysis of unique weights per input of several DNNs, describes in detail the reuse scheme and hardware implementation of CREW, and discusses the experimental results. This work has been submitted for publication and is currently under review.

### 1.2.3 Dynamic Pruning

After proposing different computation reuse techniques, this thesis explores the pruning of input activations. Dynamic operation pruning [76], a.k.a. activation pruning [5], is an optimization technique to reduce the cost of evaluating MLPs and CNNs. Based on the observation that ReLU activations tend to generate a large number of zero values, activation pruning dynamically avoids computations when the synaptic weight is multiplied by a zero-value input. However, such a fine-grained activation pruning results in very sparse computations and memory accesses, since individual connections are selectively computed or skipped [2]. Sparse computations increase the complexity of a hardware accelerator, as it has to handle data representations based on indexes of non-zero values [72], which results in sparse memory access patterns that are challenging for the

hardware. On the other hand, ReLU activations are rarely used in Recurrent Neural Networks (RNNs) [35], leading to smaller potential for fine-grained activation pruning.

RNNs represent the state-of-the-art solution for sequence processing problems such as machine translation [97], speech recognition [4] or language modeling [103]. Unlike CNNs or MLPs, RNN units store information from past executions to improve the accuracy of future predictions. Deep RNNs consist of multiple RNN layers, a.k.a. cells, stacked on top of each other. The most successful RNN cell architectures are the Long-Short Term Memory (LSTM) [35] and the Gated Recurrent Unit (GRU) [15]. Chapter 2 shows the equations of LSTM and GRU cells. In both cases, each cell consists of multiple single-layer fully-connected networks commonly referred as gates. Furthermore, the evaluation includes element-wise multiplications across the outputs, i.e. activations, of different gates.

Note that RNN activation functions exhibit a very narrow range: sigmoid ranges from 0 to 1, whereas hyperbolic tangent (tanh) is constrained to the interval [-1, 1]. We observed that every time a neuron in the input gate  $(i_t)$  of an LSTM cell is saturated towards zero, evaluation of its peer neuron in the generate gate  $(g_t)$  can be safely avoided. In a similar manner, whenever the tanh activation of the cell state  $(c_t)$  is zero the corresponding neuron in the output gate  $(o_t)$  can be skipped. Our numbers show that more than 18% of the computations and memory accesses can be avoided by exploiting these zero-value activations in LSTMs. On the other hand, GRU cells exhibit similar behavior: when a neuron is saturated towards one in the update gate  $(z_t)$  of a GRU cell, computation of its peer neuron in the generate gate  $(g_t)$  can be skipped as the product  $(1 - z_t) \times g_t$ is granted to be zero. Our results show that more than 7% of neuron evaluations can be skipped based on this observation.

In this work, we propose to exploit the aforementioned saturations of activation functions to avoid computation of entire neurons in LSTM and GRU networks. We call this method Coarse-Grained Pruning of Activations (CGPA). Figure 1.6 shows the key difference between fine-grained activation pruning and CGPA. Under fine-grained activation pruning (Figure 1.6a), individual connections of a fully-connected or convolutional layer are dynamically skipped if their input value is zero, leading to sparse memory accesses. In this example, we assume  $x_1$ ,  $h_0$  and  $h_2$  are almost zero. In this case, neurons in layer 0 require accessing their respective first and third weights, whereas neurons in layer 1 only require accessing their respective second weight (pruned synapses are shown in red). Such fine-grained and sparse accesses are challenging for hardware. On the other hand, Figure 1.6b illustrates CGPA. In this example, neurons zero and two in the input gate of an LSTM cell are saturated towards zero. This means that neurons zero and two (peer neurons) in generate gate ( $g_t$ ) can be safely skipped, avoiding all their computations and memory accesses.

Note that CGPA is orthogonal to previous proposals of fine-grained activation pruning and static weight pruning. CGPA is applied at the neuron granularity by exploiting the element-wise operations of RNNs of GRUs and LSTMs and the saturations of the activation functions of the gates. CGPA dynamically prunes entire neurons which generates a compacted pruned model that avoids sparsity, unlike fine-grained activation pruning and static weight pruning which are applied at the connection granularity. Previous works such as Scalpel [102] have shown that in order to exploit the benefits of sparse models in CPU/GPU the degree of fine-grained pruning has to be extremely high, which cannot always be achieved without accuracy loss. In addition, a specific accelerator design to exploit sparse models is required, which in turn increases the complexity

Figure 1.6: Fine-grained (a) vs coarse-grained (b) activation pruning. Connections/neurons shown with red dashed lines are dynamically pruned.

of the hardware due to the overheads of managing the sparse data. Both fine-grained activation pruning and static weight pruning can provide high percentages of pruning, but they also require the accelerator to be able to manage sparse data. On the other hand, CGPA can achieve speedups and energy savings with lower pruning degrees, since CGPA requires minor changes to the hardware and can be used in any dense accelerator like TPU.

In this work, we implement CGPA on top of a TPU-like accelerator. We show that the technique has a very small hardware overhead, as it mainly requires a few additional comparators to detect saturation of activation functions and small changes to the control unit to selectively skip entire neurons. In case a neuron is evaluated, all its weights and inputs are fetched from memory and injected into the systolic array, whereas they are completely avoided in case the neuron can be safely skipped, reducing sparsity by a large extent compared to fine-grained activation pruning. CGPA provides, on average, 12% of speedup and 12% of energy savings.