## **Calhoun: The NPS Institutional Archive**

## **DSpace Repository**

Reports and Technical Reports

All Technical Reports Collection

1975-07

# System Test Methodology Vol. I

Bradley, G.H.; Howard, G.T.; Schneidewind, N.F.; Montgomery, G.W.; Green, T.F.

Monterey, California: Naval Postgraduate School

http://hdl.handle.net/10945/63316

This publication is a work of the U.S. Government as defined in Title 17, United States Code, Section 101. Copyright protection is not available for this work in the United States.

Downloaded from NPS Archive: Calhoun

Calhoun is the Naval Postgraduate School's public access digital repository for research materials and institutional publications created by the NPS community. Calhoun is named for Professor of Mathematics Guy K. Calhoun, NPS's first appointed -- and published -- scholarly author.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

# NPS555575072 A NAVAL POSTGRADUATE SCHOOL Monterey, California

|         | SYSTEM TEST METHODOLOGY VOL. I |  |

|---------|--------------------------------|--|

|         | by                             |  |

|         | G. H. BRADLEY                  |  |

| 11 a 11 | G. T. HOWARD                   |  |

|         | N. F. SCHNEIDEWIND             |  |

|         | G. W. MONTGOMERY               |  |

|         | T. F. GREEN                    |  |

|         | July 1975                      |  |

Approved for public release; distribution unlimited

Prepared for: Naval Air Development Center Warminster, Pennsylvania NAVAL POSTGRADUATE SCHOOL Monterey, California

Rear Admiral Isham Linder Superintendent Jack R. Borsting Provost

This work herein was supported by the Naval Air Development Center, Warminster, Pennsylvania.

Reproduction of all or part of this report is authorized.

Prepared by:

F. Schnei

Professor

G. H. Bradley Associate Professor

G. T. Howard Associate Professor

Reviewed by:

David A. Schrady, Chairman Department of Operations Research and Administrative Sciences

Released by:

Robert Fossum Dean of Research

| REPORT DOCUMENTATIO                                                                                                                                                                                                  | N PAGE                                                                                                                                                                         | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| NPS55SS75072                                                                                                                                                                                                         | 2. GOVT ACCESSION                                                                                                                                                              | NAME AND ADDRESS OF A DECIDENCE OF A                                         |

| . TITLE (and Subtitie)                                                                                                                                                                                               | 0 0                                                                                                                                                                            | 5. TYPE OF REPORT & PERIOD COVERED                                                                                                                      |

| SYSTEM TEST METHODOLOGY VOL. I                                                                                                                                                                                       |                                                                                                                                                                                | Technical Report                                                                                                                                        |

|                                                                                                                                                                                                                      |                                                                                                                                                                                | 6. PERFORMING ORG. REPORT NUMBER                                                                                                                        |

| G. H. Bradley G. W.<br>G. T. Howard T. F.<br>N. F. Schneidewind                                                                                                                                                      |                                                                                                                                                                                | 8. CONTRACT OR GRANT NUMBER(*)                                                                                                                          |

| PERFORMING ORGANIZATION NAME AND ADDRI                                                                                                                                                                               | ÉŚŚ                                                                                                                                                                            | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS                                                                                          |

| Naval Postgraduate School<br>Monterey, Ca. 93940                                                                                                                                                                     |                                                                                                                                                                                | N62269/75/RQ/02014                                                                                                                                      |

| 1. CONTROLLING OFFICE NAME AND ADDRESS                                                                                                                                                                               |                                                                                                                                                                                | 12. REPORT DATE                                                                                                                                         |

| Naval Air Development Cent<br>Warminster, Pennsylvania                                                                                                                                                               | er                                                                                                                                                                             | July 1975<br>13. NUMBER OF PAGES                                                                                                                        |

| 4. MONITORING AGENCY NAME & ADDRESS(II dilla                                                                                                                                                                         | erent from Controlling Offic                                                                                                                                                   | ce) 15. SECURITY CLASS. (of this report)                                                                                                                |

| al mondar sed (at )                                                                                                                                                                                                  | escille to ano.<br>Venilte instrue                                                                                                                                             | UNCLASSIFIED                                                                                                                                            |

| Sector Sector Sector Sector                                                                                                                                                                                          |                                                                                                                                                                                | 154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                                                                                                           |

| 6. DISTRIBUTION STATEMENT (of this Report)<br>Approved for public releas<br>7. DISTRIBUTION STATEMENT (of the ebetract ente                                                                                          | oonforence p<br>Marter of Sci                                                                                                                                                  | incol can enxel and the second back                                                                                                                     |

| Approved for public releas                                                                                                                                                                                           | oonforence p<br>Marter of Sci                                                                                                                                                  | incol can entit i vitati i<br>out ban nationalisti bai                                                                                                  |

| Approved for public releas                                                                                                                                                                                           | oonforence p<br>Marter of Sci                                                                                                                                                  | istoiran estdi velstel<br>out bas sansikarsess ba                                                                                                       |

| Approved for public releas<br>7. DISTRIBUTION STATEMENT (of the ebetrect ente<br>8. SUPPLEMENTARY NOTES                                                                                                              | red in Block 20, if differen                                                                                                                                                   | it from Report)                                                                                                                                         |

| Approved for public releas<br>7. DISTRIBUTION STATEMENT (of the ebetrect ente                                                                                                                                        | red in Block 20, if differen                                                                                                                                                   | it from Report)                                                                                                                                         |

| Approved for public releas<br>7. DISTRIBUTION STATEMENT (of the ebetrect ente<br>8. SUPPLEMENTARY NOTES                                                                                                              | red in Block 20, if differen                                                                                                                                                   | it from Report)                                                                                                                                         |

| Approved for public releas<br>7. DISTRIBUTION STATEMENT (of the ebetrect ente<br>8. SUPPLEMENTARY NOTES                                                                                                              | red in Block 20, if differen                                                                                                                                                   | nber)                                                                                                                                                   |

| Approved for public releas<br>7. DISTRIBUTION STATEMENT (of the ebetrect ente<br>8. SUPPLEMENTARY NOTES<br>9. KEY WORDS (Continue on reverse side if necessar)<br>0. ABSTRACT (Continue on reverse side if necessar) | red in Block 20, if different<br>r end identify by block num<br>and identify by block num<br>School has co<br>974 to 30 Jun<br>sponsorship co<br>port was subm<br>was to devel | nber)<br>onducted a research projec<br>a 1975, entitled System<br>of the Naval Air Develop-<br>aitted on 15 January 1975.<br>Lop a methodology and tool |

## UNCLASSIFIED

20. Continuation

Two areas which received major emphasis were prototype testing and maintenance testing. A methodology for conducting prototype tests was developed. In addition, a simulation model was prepared for aiding the designer and tester in identifying and diagnosing faults which may occur during prototype testing.

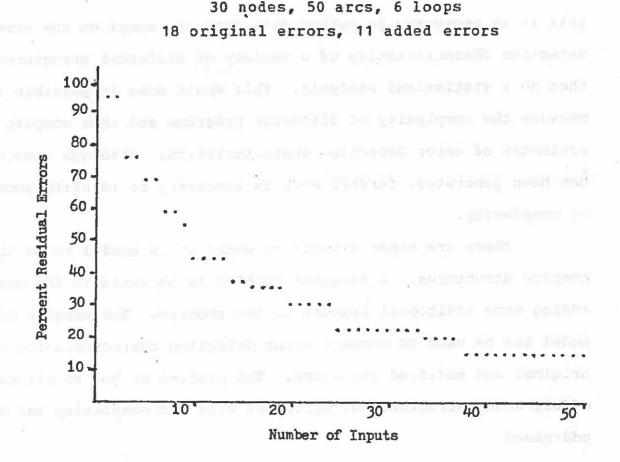

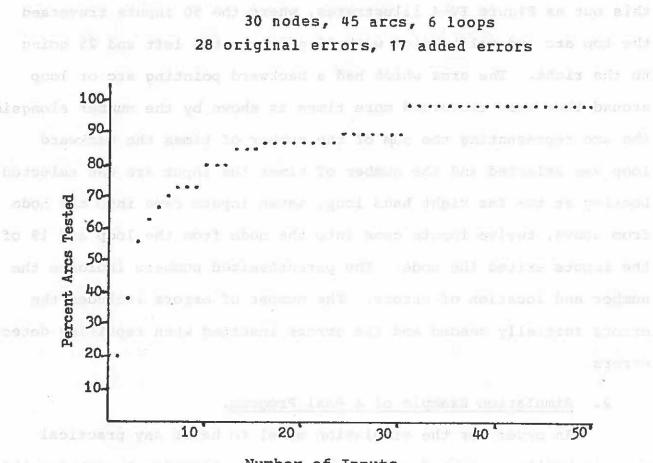

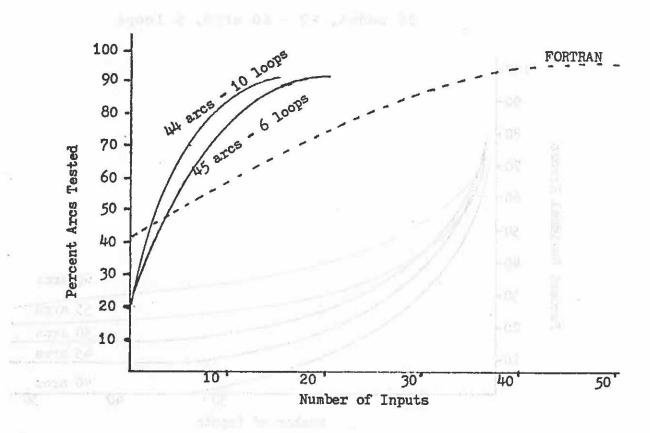

A maintenance testing methodology, which involves the use of tests to partition faults into subsets, was developed for identifying faults. In addition to the above areas, research was undertaken to develop models for investigating the relationship between error detection capability and program structure in computer software, using simulation and analytic approaches. The models would be employed during software design for identifying program structures with poor error characteristics and during test planning for the purpose of allocating test resources in accordance with error characteristics.

In addition to the progress and final reports, computer program source decks and operating instructions for the system (prototype) test simulation and the software error detection (simulation and analytic) models have been provided to NADC.

Lastly, three national conference proceedings publications and presentations and two Master of Science in Computer Science theses have resulted from this research project.

> UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE(When Data Entered)

## TABLE OF CONTENTS

| I.   | Introduction                                     | I-1   |

|------|--------------------------------------------------|-------|

| II.  | Prototype Testing                                | II-l  |

| III. | Maintenance Testing                              | III-1 |

| IV.  | Software Error Simulation                        | IV-1  |

| V.   | Analytical Results for the Error Detection Model | V-1   |

| VI.  | Issues in System Testing                         | VI-1  |

| VII. | Conclusions and Recommendations                  | VII-1 |

| Ψį   | List of References                               | R-1   |

#### the second second second second

|     | .721 |

|-----|------|

|     |      |

| (t) |      |

## INTRODUCTION

The Naval Postgraduate School has conducted a research project during the period 30 June 1974 to 30 June 1975, entitled System Test Methodology under the sponsorship of the Naval Air Development Center. This is the final report of the project. A progress report was submitted on 15 January 1975.

The purpose of this project was to develop a methodology and tools for conducting system tests of avionics or other complex hardware/software systems.

Two areas which received major emphasis were prototype testing and maintenance testing. These topics are covered in Section I and Section II, respectively. A methodology for conducting prototype tests is described in Section I. In addition, a simulation model is presented for aiding the designer and tester in identifying and diagnosing faults which may occur during prototype testing. A description of this model is contained in Appendix A.

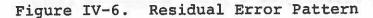

The maintenance testing methodology presented in Section III involves the use of tests to partition faults into subsets, so that the actual fault can be identified. In addition to the above areas, research was undertaken to develop models for investigating the relationship between error detection capability and program structure in computer software. A simulation approach and an analytic approach are described in Section IV and Section V, respectively. The models would be employed during software design for identifying program structures with poor error characteristics and during test planning

I-1

for the purpose of allocating test resources in accordance with error characteristics. An example of applying the error simulation model to an actual FORTRAN program appears in Appendix B; directions for use of the model will be found in Appendix C; and a listing of the simulation program is contained in Appendix D. A description of the analytic model computer program appears in Appendix E.

Various issues in testing which are germane to maintenance testing and recovery from errors are described in Section VI.

The major conclusions which resulted from each research effort and recommendations for possible applications and future work will be found in Section VII.

In addition to the progress and final reports, computer program source decks for the system (prototype) test simulation, the error simulation model, and the analytic error detection model have been provided to NADC.

Lastly, three national conference proceedings publications (References 9, 12, and 17) and presentations and two Master of Science in Computer Science theses have resulted from this research project.

wind tonation settion deriver derivering optimies (Lity and produces striction) h computer setters. A simularithe execution and an an antipute apprian ro described in deciding dy and forming a respect regent routed build be employed during and setter terrings for identifying program. setterments with tone open otherwelderivities and during rook standard

## II. PROTOTYPE TESTING

### A. MOTIVATION FOR SYSTEM TEST METHODOLOGY

Software is the major expense in computer systems today. As an example, the Air Force allocated between one billion dollars and one and a half billion dollars in 1972 for software development. This was about three times the annual expenditure on computer hardware and accounted for four to five percent of the Air Force budget for the year. Boehm [10, 11] indicates that these high figures are representative of the industry as a whole. He predicts that by 1985 software expenditures in the Air Force will account for ninety percent of the total ADP system costs. Of this enormous amount of money spent on software, a disproportionately large share was spent on testing and the trend is not one of improvement. Boehm states that "during the 1970s the Air Force can expect to spend almost half of its software budget for military space operations on the checkout and test phases of computer program implementation: two to three times as much as it will pay for having the program coded." With such an effort invested in testing software, it should be relatively error free but this has not been the case historically. The Apollo Manned Spaceflight Program had one of the most tested systems in the world, yet major software failures occurred in Apollos 8, 11, and 14. The failure on Apollo 11 occurred in the extremely critical phase of lunar landing. The situation is no better in other areas; each new release of OS/360 has approximately 1000 new software errors. It is not necessary to look at such large complicated systems to discover that present testing is inadequate. The person who has not had an encounter with a computer program error such as an incorrect billing is an unusual person in

today's society. Since testing consumes such a large proportion of the resources allocated to system development and has produced such poor results, it is time to develop a new approach to system testing.

#### B. TESTING PROBLEMS

## 1. Multiplicity of Testing Activities

Many of the terms used in the area of testing are subject to a wide variety of interpretations. The word "testing" has been misused and many non-testing activities have been associated with the word. Testing may be defined to be the process of determining if a system meets the stated functional specifications. Quite often debugging is thought of as a testing activity. This is incorrect. Debugging starts with a known error and works towards a correction [13]. Recently, a significant body of literature and activity have been addressed to designing computer programs in a structured fashion in order to eliminate or minimize the occurrence of software errors [14, 15]. The theme of some of these efforts is that if we design programs correctly through structured programming, there will be very little need for testing. Although these efforts do a lot to reduce the potential for errors, they do not act as a substitute for testing.

Other testing activities include verification, validation, certification, proof of correctness, and performance testing. Hetzel [13] discusses these activities in relation to program testing. Verification is concerned with the program's logical correctness based on execution of the program in a test environment. Validation is concerned with the logical correctness of a program in a given external environment. Certification implies an authoritative endorsement that a

program is of a certain quality. A proof of correctness deals with the logical correctness without regard to the environment. Performance testing involves an evaluation of the performance properties of a computer program or system, such as resource utilization. Each of these activities has much to offer. The problem arises when one of the approaches is assumed to equate to complete testing. It is clear that improved software quality must be approached from several fronts: improved design techniques, improved programming management and improved methodology.

## 2. Test Design

There are many fundamental questions that must be answered in designing a test of an information processing system. One such question is what should be tested? Too often a tester ends up testing an incomplete or modified version of the system that is easier to test than the real system. Often the tester is faced with a large set of input combinations to be tested. In this case, the question becomes: How can a subset of the test inputs best be selected to thoroughly test the system? Another important issue is how should the test efforts be organized? It is important to obtain the most information about the system from every test run. It is important to establish test data recording procedures at this time in order to insure that all error information will be recorded. This can be accomplished by properly organizing the tests in a logical sequence. Tests should be related to types and sources of errors. Gruenberger [16] states that "part of the art of testing is knowing when to stop testing." This exposes a two sided question the test designer must

face: When is the test finished and what can be said about the system when testing is stopped?

All these questions are further compounded by the fact that there can be no set rule. Every system requires an original test procedure designed to fit its special requirements. Gruenberger suggests "that the intellectual effort to test a program is of the same order as that which created it."

This section presents a test methodology that will help answer these questions. A model is presented that will serve as a framework for the construction of a logical approach to system testing.

## C. A MODULAR APPROACH TO PROTOTYPE TESTING

A modular approach to prototype testing offers many advantages for the design of the test and the development of the system. The modular design involves breaking a large system into many small parts called modules. The intra-module functions are independent; however, modules interact by means of standard interfaces. Each module performs a major function of the system.

Modularity improves system design and software portability. To an extent, modules may be transferred among machines and operating systems. With standardization of modules, they may be shared among many applications. With modules being shared in this manner, the programming effort is reduced and the reliability of modules is increased since the modules will be tested with each application. The modules may be expanded more easily and changes are easier to incorporate since the effect of a change is localized.

Testability is significantly improved when a modular approach is used. Testing of different modules may be carried out in parallel. Standardization of modules yields a set of assertations that may be used as test criteria for the modules. Modules may be compiled separately and can be stored in a program library and accessed independently. Modularity allows testing early in the construction of a system. Each module may be tested as soon as it has been constructed instead of waiting for the whole system to be completed before starting to test. Since modules may be reused in future systems, future programming and testing efforts are reduced.

A modular system was chosen for the prototype test model in order to take advantage of the above desirable properties of modularity.

## MODEL DESCRIPTION

## A. THE FUNCTIONAL MODULE CONCEPT

## 1. Module Definition

When representing a system with the functional model, the lowest element of the system is the module. Since the word module has had wide use throughout the computer industry, it is necessary to completely define the application of the word as used in the model. A module is an entity that performs a function within the system. A function is an activity performed by the system such as a fast Fourier transform. The physical embodiment of a module is the wiring and circuit boards of hardware, or the source or object programs recorded on punched cards or magnetic tape or programs resident in memory, for computer software. By defining a module in terms of functions, a module is freed from the distinction of being only hardware or software.

A module receives inputs and transmits outputs across a boundary. A boundary consists of a location within the system at which the inputs to a module or the outputs from a module may be measured. In order for the tester to assess these inputs or outputs the boundary must be identifiable. In order to accommodate this requirement for an identifiable boundary, it is necessary to consider the composition of modules. The composition of two modules would be a module performing the same functions as the original two modules. For example, one module might be a fast Fourier transform and the other a digital filter module. If it is impossible to identify a point to measure the output from the filter module to the Fourier transform module, the two could be considered as one module that performs the functions of filter and transform. Thus, the entire system could be viewed as a module or a module could be considered to be a small unit of program code. The proper level for identifying modules will be indicated by the functions performed by the system.

A module will be assumed to be free of internal errors for system test purposes. This assumption is predicated on the fact that all modules will receive extensive individual unit testing before the system is assembled. If an error still exists within a module, the test system will detect it only as the error affects intermodule communication. Assuming that the test plan is sufficient to detect all errors external to a module, the only way an error could go undetected would be if its actions were confined to the module itself.

The system may now be described as a collection of modules which has external inputs and external outputs. The selection of modules must be such that every portion of the entire system is

represented by a module and no portion is represented by more than one module.

In performing its function, the module utilizes system resources. These resources may be in the form of data, control signals, or physical resources including both hardware and software units. Thus a resource is an element of the system that is used by modules in performing a function of the system. Resources have two types of attributes. One type deals with the usage of the resource, which is the amount or size of the resource that is assigned or available to be assigned. The other type deals with resource contents, such as the contents of a memory location or the value of a particular control signal. Resources have states. These states indicate the status of the resource. Some examples of the state of a resource are: reading, writing, idle, file empty, file half full, or memory region assigned.

### 2. Task Definition

The work to be performed by a module may be represented as an ordered or random series of tasks. Tasks are the sub-functions performed by a module. A sub-function consists of a step in the algorithm which the module must execute in order to carry out its function. Examples of tasks are the computation of a simple function, storing the result in memory and outputting the result to the printer. This usage of the word task is synonymous with the use of the word "process" as it is used in the operating system literature. The precedence of tasks is determined by the algorithm the module must execute. These precedence constraints may be linear or they could include branching with or without cycles. It is also possible to have no precedence

constraints. In this case any task could be executed whenever the resources were available.

In order to execute a task, the module goes through a series of states. The state of a module is the status of the module at a given time. A partial list of states that a module can enter includes: compute, wait for memory, wait for input/output, wait for CPU, idle, input processing, wait for another module to complete a task, wait for a resource, and interrupted state. The particular state of a module is a function of the set of inputs to the module, resource states, and its previous state. The outputs of a module are a function only of the state of the module. A primary state is a state that a module is required to enter in order to perform a task. Primary states include compute, input processing and output processing. A secondary state is a state in which the module accomplishes no work. Examples of secondary states would be blocked state, wait for input or wait for CPU. The system state is the set of module states. The system state changes when one or more modules changes state.

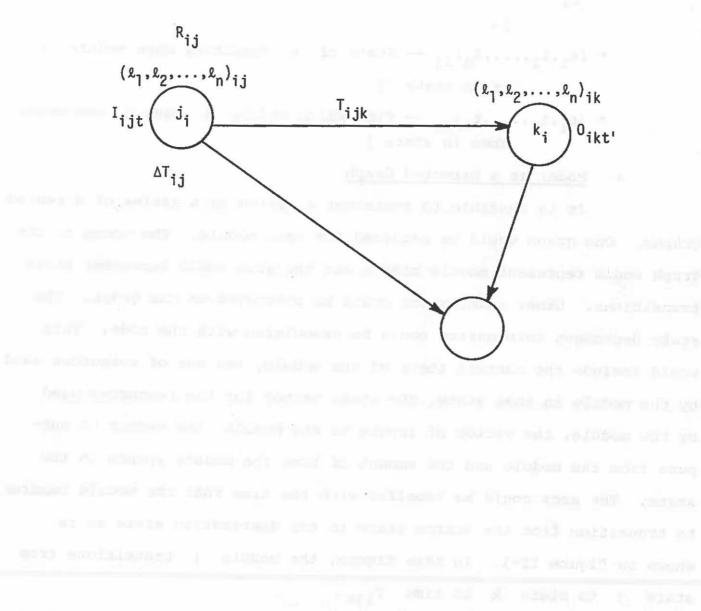

3. Model Notation

The following is a list of symbols used to describe the model. Each symbol is followed by the definition of that symbol as it is used in this system of notation.

- \* i ----- Module designation,

- \* j, ---- Current state of module i,

- \* k; ---- Next state of module i,

- \* I ijt -- Vector of inputs at module i when module is in state j and input starts at time t,

- \* 0<sub>ikt</sub> Vector of outputs from module i after the module has transitioned to state k and output starts at time t',

- \* T<sub>ijk</sub> -- Time at which transition of module i from state j to state k occurs,

- \* ΔT<sub>ij</sub> -- Amount of time which module i spends in state j, \* R<sub>ij</sub> --- Set of resources used by module i when in state j,

- \* (l<sub>1</sub>, l<sub>2</sub>,..., l<sub>n</sub>)<sub>ij</sub> -- State of n resources when module i

is in state j,

- \* (t<sub>1</sub>,t<sub>2</sub>,...,t<sub>n</sub>) -- Time which module i uses n resources when in state j.

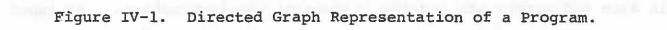

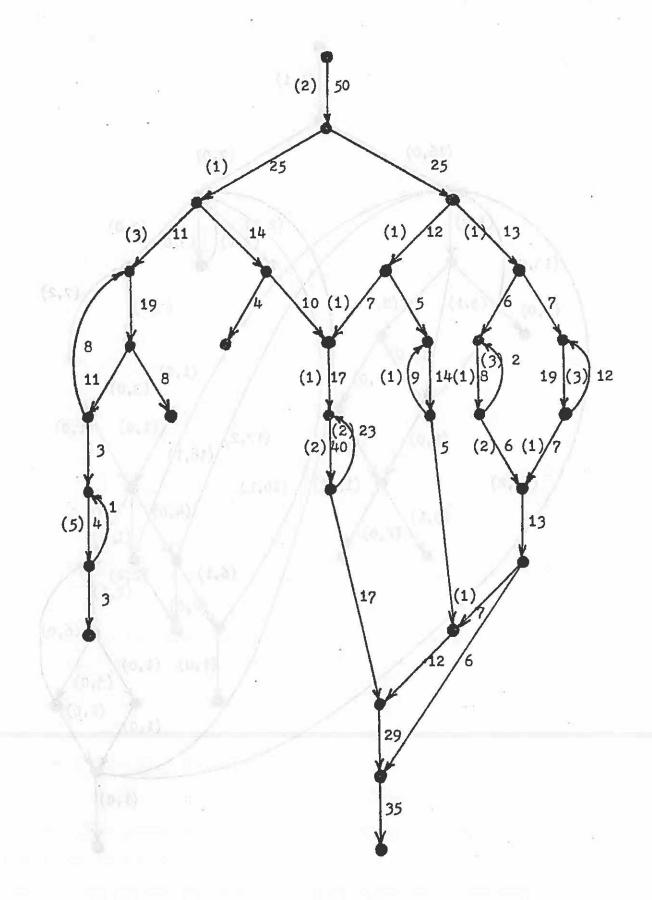

4. Model as a Directed Graph

It is possible to represent a system as a series of directed graphs. One graph would be required for each module. The nodes of the graph would represent module states and the arcs would represent state transitions. Other information could be portrayed on the graph. The state dependent information could be associated with the node. This would include the current state of the module, the set of resources used by the module in that state, the state vector for the resources used by the module, the vector of inputs to the module, the vector of outputs from the module and the amount of time the module spends in the The arcs could be labelled with the time that the module requires state. to transition from the source state to the destination state as is shown in Figure II-1. In this figure, the module i transitions from j to state k at time T<sub>ijk</sub>. state

These directed graphs would give the tester a convenient means of visually representing the activity of the module. The tester might prefer to show only the primary states of the module and the idle state instead of showing all possible states of the module.

Anthenine and a line of the second of

## Figure II.1. Directed Graph of Module States

provides the solar cally also provident animals of the module and the interest

## 5. Time Domain of a Module

A property of a module is that it uses the resources of the system only at certain times. One of the major problems of testing computer systems is to identify when two or more modules will be competing for the same resources. The problem is further compounded if the system possesses multiple CPU's which are running asynchronously. The concept of time domain will be useful to address this problem area. A time domain of a module consists of the times that resources are in use. A graph of the time domains of the modules of the system would be a useful abstraction of the system for the analysis of the timing problem. The resources of the system could be represented on the vertical axis with time expanding along the horizontal axis from the origin. Each area so represented should be labelled with the module and the amount of the resource required. The time domain of a module would be represented by the summation of the areas formed by the product of resources used by the time duration of use. Any intersection of time domains would represent a potential error only if the total demands of the modules exceed the maximum resources available.

One problem with this representation is to find a timing system that applies to all modules when modules are operating asynchronously. In this case the time axis would be the elapsed time from some critical event in the system. The changes in system state would be referenced to this event.

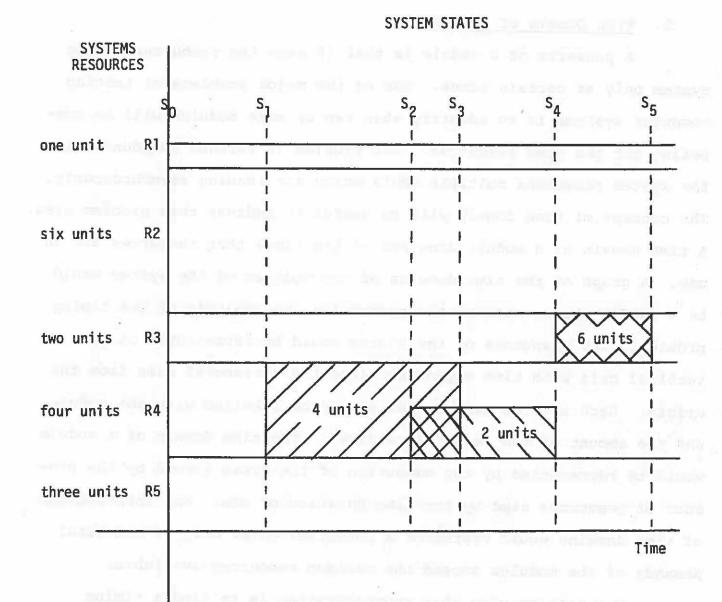

If we define a change in system state as any change in module state, it is possible to consolidate the module state representation into a system state representation and show resource usage conflicts in terms of system states as indicated in Figure II-2. In this figure

## Figure II.2. Resource Conflicts vs. System State

there are five types of resources available to the system. They are labelled Rl through R5. The amount of each resource is indicated on the vertical axis. For example, there are six units of R2 available. There are two resource conflicts portrayed in this system. One occurs in system state  $S_2$ . Here one module requires four units of resource R4 and another module requires two units of R4. The conflict occurs because there are only four units of R4 available. The conflict is denoted by a cross-hatched area. The other conflict is in system state  $S_4$ . A module has requested six units of resource R3 when only two units are available to the system.

The construction of such a graph would be infeasible to do by hand for a real system. A program could be written to produce this type of graph from the time domains of the modules. On this graph the computer could identify resource usage conflicts.

## B. APPLICATION OF MODEL TO TESTING

## 1. Functional Specifications

One of the more difficult processes in producing reliable software is translating user requirements into meaningful design specifications. Boehm, McClean, and Urfrig [4] vividly demonstrate the magnitude of the problem in their study of a large software project. The authors divided errors into two classes. These were design errors and coding errors. An error was considered a design error only if its correction caused a corresponding change to the design specifications. Of the total errors, 64 percent were design errors. This alone is enough to illustrate the need for a valid method of design specification. Even more disturbing was the time frame within the testing in which

the errors were discovered. Of the 54 percent that were not discovered until the acceptance, integration or delivery phases of testing, 45 percent were design errors. The remaining nine percent were coding errors. Errors discovered in these latter stages are more difficult to correct than those discovered during the coding stage. Thus, it is necessary to have a good system of describing design specifications. The functional model provides such a system.

When the functional model is used, the user should be required to define all functions of the system. The functional specifications would consist of a statement of the activities of the system and the associated inputs and outputs. By requiring functional specifications, designers are assured of having a complete detailed description of the system at the beginning of the project. This should reduce the number of design errors.

It is possible to over specify the design of a system. This could prevent the designer from choosing the most efficient method of designing the project. It could also introduce errors into the system design, if the user does not have a thorough knowledge of computers. This problem is avoided by using functional specifications. Details are presented as functions of the system, which is the area in which the user is most knowledgeable. The implementation of the functions is left to the designer, who is in a better position to determine the proper method.

Another pitfall of system design may be avoided by using functional specifications. Frequently, test specifications are not available early in a project because testability is not considered to be a design parameter. Instead, test requirements are formulated as an

afterthought when it is too late to influence the design [5]. Functional test specifications are defined as test specifications which are based on testing the stated functions and observing the corresponding outputs of the system. Functional specifications should be incorporated in the test specifications. Detailed design should not commence until this information is available.

## 2. Documentation

The need for complete and usable documentation should be a primary concern of anyone involved with system design, programming and testing. Poole [6] states "that the lack of good documentation usually means that testing is not performed as thoroughly as it should be and debugging is that much more complicated." Another use of documentation is for the maintenance of the system. Since the life of a system is much longer than the development phase, the designers will probably not be available to help maintain the system. In addition, many people may have access to the software. All changes which result must be documented.

The use of the functional model helps to provide adequate documentation throughout the life of the system. The concept is to force documentation to be an integral part of system development. Two documents have already been discussed. These are the functional specifications and the functional test specifications. These documents should form a segment of the documentation. These should be systematically updated as changes are made to the system.

The documentation should include other information as well. This could include a data base containing information about all errors that were found in the system to date. Unfortunately, there is a tendency to ignore this aspect and to think of this type of information as something to discard once the error has been corrected [6].

Every incident must be recorded because an outage that may appear insignificant to the user could be an important indicator once it is properly analyzed. The data base could be used to identify modules that are the source of the majority of errors. This classification could be used to direct future testing and debugging. It could also be used to determine which modules are the most unreliable. This would provide a starting point for improving the reliability of the system. This would be particularly applicable if the module that is most critical to the system's operation is also the most unreliable. The data base could also be classified as to type of errors. This would be valuable information when designing a similar system.

Another form of documentation that should be incorporated into the plan for system testing is assertions. These are statements that are introduced into the code by the programmer. These state a fact about the design of the program. These statements may be treated as a comment card or used to produce code to check for the validity of the assertions. The appropriate action would be determined by a parameter passed to the complier. Two types of assertions could be employed within the model. The first would be global assertions. These would be in the form of specifications for intermodular actions of the system. An example of such an assertion would be:

ASSERT RANGE OF ALL ARRAY INDICES IS 0 TO 100. The other level of assertions would be local. The local assertions would be defined by the programmer but within the design specifications.

An example of a local assertion would be:

ASSERT RANGE OF I IS 10 TO 20.

These assertions could be a permanent feature in the program. They could be activated on the local level to help test a module or on the global level to aid in introducing a change to the system. As such, these assertions would form an important part of the system documentation.

3. Test Inputs

Ideally, it would be proper to exhaustively test a system. This implies that every path in the logic of the program be executed and tested. Shooman [8] demonstrates that this will normally be impossible due to the large number of inputs required. The problem presented involved exhaustively testing an assembly language program which solved for the roots of a quadratic equation  $Ax^2 + Bx + C = 0$ . The computer was assumed to have a 12 bit word length and integer arithmetic was used. All syntactical errors had been eliminated and all known special cases such as A = 0 and imaginary roots had been accounted for. The input space to exhaustively execute this program involved 64 x 10<sup>9</sup> combinations of A, B, and C. The program had a run time of 240 microseconds per execution. The time to complete the entire execution of the program over the input space would have been approximately 5,000 hours. To test a program, solutions must be verified by some independent means such as a desk calculator or a different algorithm. This should be done in as many different ways as possible, since there is some probability that two independent approaches will result in the same wrong solution. Obviously, exhaustive testing is infeasible for even a small program.

The problem the tester must solve is how to best select the subset of test inputs from the universe of possible inputs. A method for selecting the inputs for a test is to first identify and rank the modules in a system by the criticality of the modules to the mission success. It is seldom the case that all modules are equally valuable. A technique for determining criticality is to ascertain the consequences to the mission of a module malfunction. A malfunction in some modules would cause a mission abort, while others would result in a degraded mode of operation. The modules are ranked according to criticality. This is based on the criticality of module outputs. The time spent in testing each module can then be allocated using this ranking. The time allocation can be further refined by ranking the criticality of each sub-function to the performance of the function by the module.

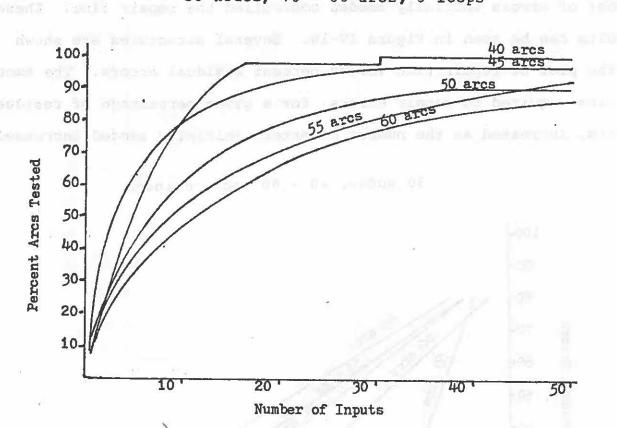

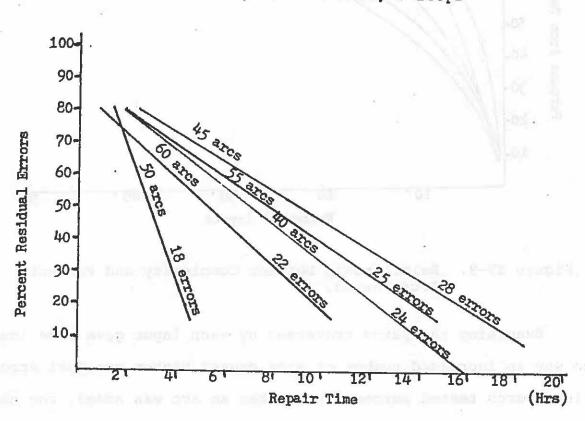

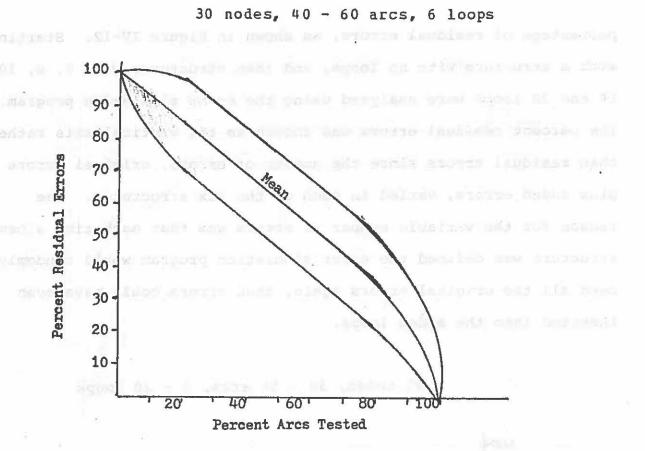

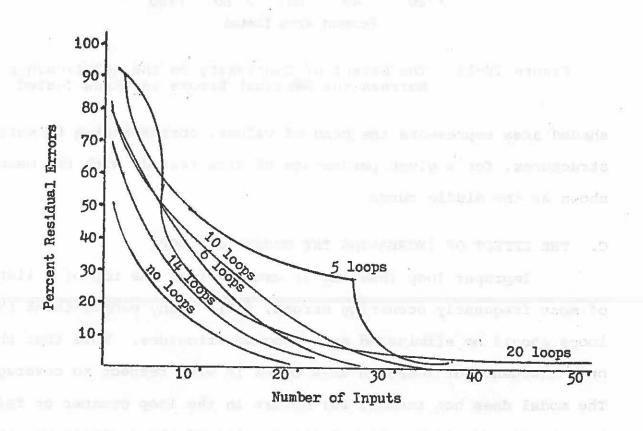

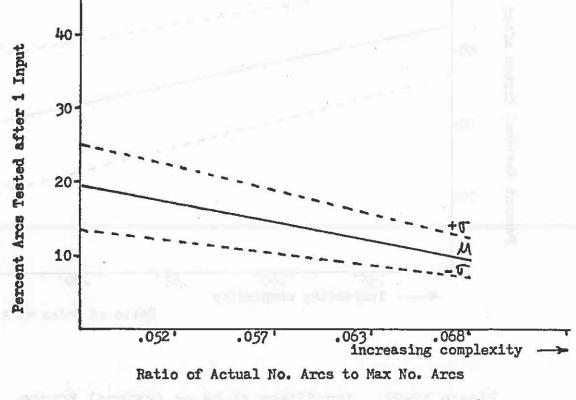

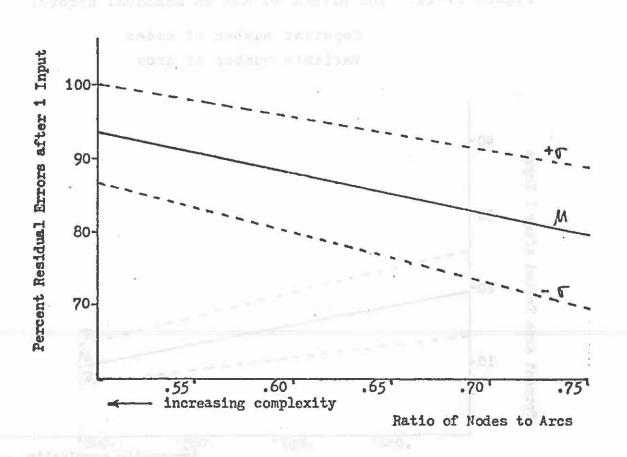

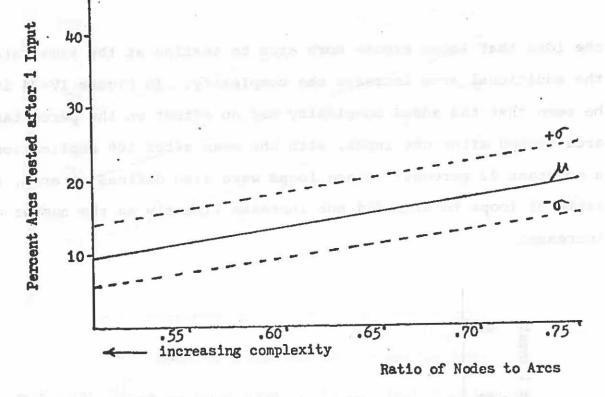

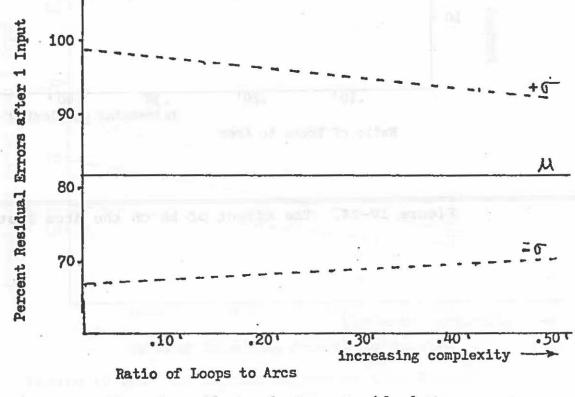

There are other factors that can be used to rank modules for testing purposes. One such crtieria would be forcasted errors. Schneidewind [9] has developed a model of the occurrence of errors detected during functional testing of command and control software. It would be possible to rank modules in order of forecasted errors. Work is progressing in the area of developing relationships between program structure, program complexity and the ability to detect errors in a program [12]. Another method of obtaining such a ranking would be through the use of simulation. Critical modules could be identified by their high rate of failure in the simulation.

Once the amount of testing resources allocated to each module has been determined, the proper number of inputs for testing each

module can be estimated. The problem then becomes one of selecting the inputs to thoroughly test each module. The module represents a function which maps the set of inputs into the set of outputs. The inverse mapping could be used to obtain the set of inputs. Given this set of inputs, test cases are selected in order to cover the input set and the program as thoroughly as possible. Particular attention must be given to inputs that are involved in the control flow of the program. Once this has been done, unusual cases are investigated. A possible source of unusual cases would be indicated by the set of inputs. Values are picked that are combinations of the extremes of the range of inputs.

## 4. System Representation

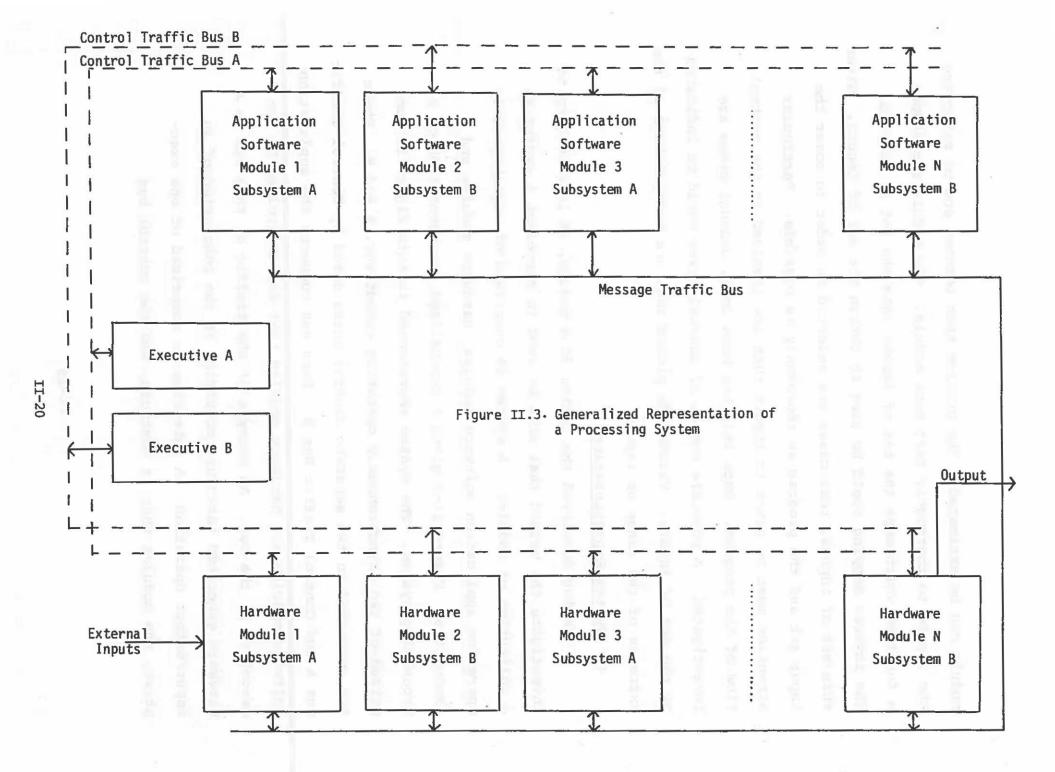

Having developed the notion of a module, it is necessary to investigate the method that will be used to represent a system as a collection of modules. A system is comprised of asynchronously operating application software modules, hardware modules and executives. Figure II-3 gives a generalized representation of a processing system. The system represented in this figure is comprised of two asynchronously operating executives, A and B. These are connected to two separate control buses noted by Control Traffic Bus A and Control Traffic Bus B. Each bus connects the application software modules and hardware modules that are controlled by the executive on the bus. An example of the traffic on this bus is a hardware generated interrupt occurring at the conclusion of an input/output operation. A subsystem is comprised of one executive, the modules that it controls, and the control bus

connecting the modules to the executive. There is a message traffic bus connecting all modules. An example of the traffic on this bus is a module passing a computed value to another application module. External inputs and outputs are identified.

This representation of a system has many useful applications to testing. The model may be used to verify the correct functioning of two types of intermodule communication. The first is message traffic. The traffic on the message bus could be checked against the functional test specifications for correctness. The second concerns control traffic. The traffic on the control buses could be checked in a similar manner. Other problem areas that could be investigated using the model include:

- \* Are the various state transitions possible, based on the values of the resource states?

- \* Are there any blocked or deadlocked states?

- \* Are the amounts of time in each state excessive?

- \* When a module state transition occurs, are the resource state vectors correct?

\* Are there times that a module holds resources excessively?

#### SIMULATION

A. A SIMULATION OF THE MODEL

A simulation of the model was constructed. The simulation was an event store type of simulation. It was written in FORTRAN IV to run on the Naval Postgraduate School's IBM 360/67. The simulation used the model representation with the user providing a description of the system to be simulated. This description required the number of modules, the number of tasks, the precedence among tasks, number of resources and resource usage. A complete description of the simulation appears in Appendix A.

The simulation showed that the model could represent a system. A simulation of this nature could be useful in testing.

#### B. USE OF SIMULATION IN TESTING

### 1. Investigation of Timing Problems

Timing problems are extremely difficult to investigate in a real system due to the fact that any test equipment installed internal to the system disturbs the timing of the system. Equipment installed external to the system may not be able to gain the required information either because of synchronization or access problems. By using a simulation of the system, the tester may observe various timing parameters. The tester is able to observe timing problems that could not be observed on the real system. This is accomplished without disturbing the timing of the real system.

Another problem area that could be investigated through the use of simulation is the reaction of the system to various rates of input. In the simulation it is possible to vary the mean time between arrival of inputs. This parameter could be decreased on each run to determine the maximum input rate that the system could receive and still process an acceptable number of inputs. Another method would be to plot average time to process a complete input versus input rate. This graph could be used to determine an acceptable range of input rate. This method of analysis could be used when testing a system that has to produce periodic outputs, such as a system with

a graphic display that has to be refreshed at a specified rate.

If the time that a module spends in a particular state is expressed as a variable instead of a constant, a simulation would be an invaluable aid to the tester in investigating the operation of the system. One approach would be to observe the operation of the simulated system with all modules functioning at the maximum time duration. Another method would be to use various combinations of module operating times to determine under what circumstances the system would fail or performance would be degraded. This can easily be done on a simulated system but would be impossible to do on a real system because the tester would be unable to control the time a module spends in a state.

Another timing problem facing the tester is the system clock rate. Often the tester would like to slow the system down or perhaps speed it up in order to observe some particular action of the system. This would be important if the tester was unable to measure the output of a real module because another output arrived before the first output could be measured. In a real system, it may be impossible to change the timing of each component of the system by the same amount. This would be particularly difficult in a multi-executive system. With simulation, the tester is able to adjust the timing of the system.

Some problems do not occur until the system has processed a large number of inputs. The tester may not be able to cycle the real system through a large number of inputs due to lack of time or equipment availability. However, in a simulation, the time scale may be greatly compressed, allowing the tester to cycle the system many

times. This would greatly increase the probability of discovering latent bugs. Similarly, in a simulation the user's ability to specify the initial state of the system allows starting tests under some artibrary condition that might only be achieved in an actual system by running for a long period.

## 2. Fault Insertion

Dijkstra [1] contends that "testing can only determine the presence of errors, not their absence." One approach would be to know the reaction of the system to every possible error and combination of errors. Using this knowledge, one could simply observe the reaction of the system and state what errors were or were not present. Unfortunately, the set of every possible error, combination of errors and system reaction is an immense set. Therefore, it is impracticable to prove the absence of faults by using the above approach. However, this approach using simulation, could be used to greatly expand the subset of errors that the tester could detect.

The tester may purposely introduce a fault into the simulated system. The reaction of the system to this fault could be catalogued for later reference. This information could be used to identify modules that are affected the most by a class of errors. This set of modules would be noted for special testing. This information could also be used to ensure the validity of the test plan. If the group of tests included in the test plan did not encompass the reactions observed in the simulation, then the tests would not be able to detect particular faults.

## 3. Partial System Simulation

Frequently the tester will not have the time, assets, or motivation to perform a simulation of the entire system to be tested. In this situation, simulation of certain parts of the system may be

desirable or the tester could choose to simulate the entire system in less detail. Campbell and Heffner [2] relate a case history illustrating this point. A simulation model was constructed of a system being developed. The skeleton system was working before the model was debugged. When the model was finally working, no one was certain which version of the real system the simulation results were meant to represent. However, some of the designers used simple simulations that they developed to study certain aspects of the system. The authors concluded that "ambitious large-scale models generated by professional model makers are less helpful than simpler work done by the system developers themselves." A simulation with less detail was more useful in this case than a complete simulation.

Quite often in prototype testing, a module or modules will not be present when the tests are scheduled to commence. This could be due to late delivery or to a module being modified after preliminary testing proved the module needed modification. This could also be caused by a planned action such as phased delivery. A simulation of this module would allow the tests for the rest of the system to continue. Simulating the missing module would be particularly easy if the system had been described in the form of a functional model. If all the information required to functionally represent the model is present, then a simulation can be constructed from this information.

Another use of simulation involving less than the whole system is the use of a test data generator. When a system is tested in the laboratory, it may be necessary to simulate the inputs to a system. Since there is no reason to believe that all modules will be present during the entire test phase, the tester may desire to have the test

data generator simulate the output from any module. Thus, the test data generator could also substitute for any missing module as the system was being tested. Not only would the generator act as an output generator, but it would also act as the termination for module outputs which are intended for missing modules. If these outputs must be accounted for, because the operation of the partial system would not be entirely representative of the operation of the complete system. Notice that this procedure is applicable to a top down testing approach because the test data generator could simulate inputs from dummy modules.

## 4. Pitfalls of Simulation

After having spent much time and effort to develop a simulation, the tester may find that the simulation addressed the wrong problem or solved no problem at all. The validity of a simulation is the consistency between the simulation and the real system it represents. Proof of the validity of a simulation is almost impossible, especially if the real system has not been constructed. By the time the real system has been constructed and the validity of the simulation has been disproved, irrevocable decisions may have been made based on test data from the simulation.

Although validity is a major problem in simulation, it is by no means the only problem. A list of problem areas that may cause a misunderstanding of the system being simulated is presented in Fishman [3]. These include incorrect input parameter specification, influence of initial conditions on data and misuse of estimates. The author provides suggestions on ways to control these problems.

Prototype testing may result in design changes. Each change requires a change in the simulation model. If the tester has not allowed for such an occurence in budgeting simulation resources, the model would not represent the real system. Also, there would be a time lag in modifying the model. This could have a serious effect on the test schedule if this contingency is not included in the test plan.

#### APPLICATION OF MODEL TO PROTOTYPE TESTS

## A. APPROACH

### 1. Test Plan

In order to apply the functional model to the problem of prototype test it is necessary to develop a test plan. A test plan should be created as part of the design plan. As a minimum the test plan should discuss the following major elements:

\* define modules,

\* define module states,

\* identify inputs and outputs for each module state,

\* identify module interfaces,

\* identify tasks,

\* define resources and resource states, and

\* identify resource usage for each module state.

The test plan must also include the system functional specifications and functional test specifications. In addition, it should include the test procedures. This would identify acceptance criteria, such as the allowable divergence between desired and actual output values, time duration of tests, allowable number and types of malfunctions, number and distribution of test replications, and methods for checking test results. The test plan should identify major testing milestones. These would identify major sections of testing that must be completed before system development can continue.

The test plan should document the subsystems that will be tested. This will require the development of a method of isolating a subset of the system to test it without the effects of the remaining system being introduced. These identified subsets of modules are called subsystems and will be used to test the system in stages.

Besides the modules in a subsystem, the test plan must also define a set of measurements which will indicate whether correct outputs are being produced for given inputs and define the hardware and software locations of the measurements. The plan must describe how to instrument the system in order to obtain these measurements.

The test plan should develop some organizational structure. This would include who is to do the testing and the resources to be used in testing. The plan should include who is responsible for maintaining the documentation. This would include test data, error information, design changes and test modifications.

2. Subsystem Testing

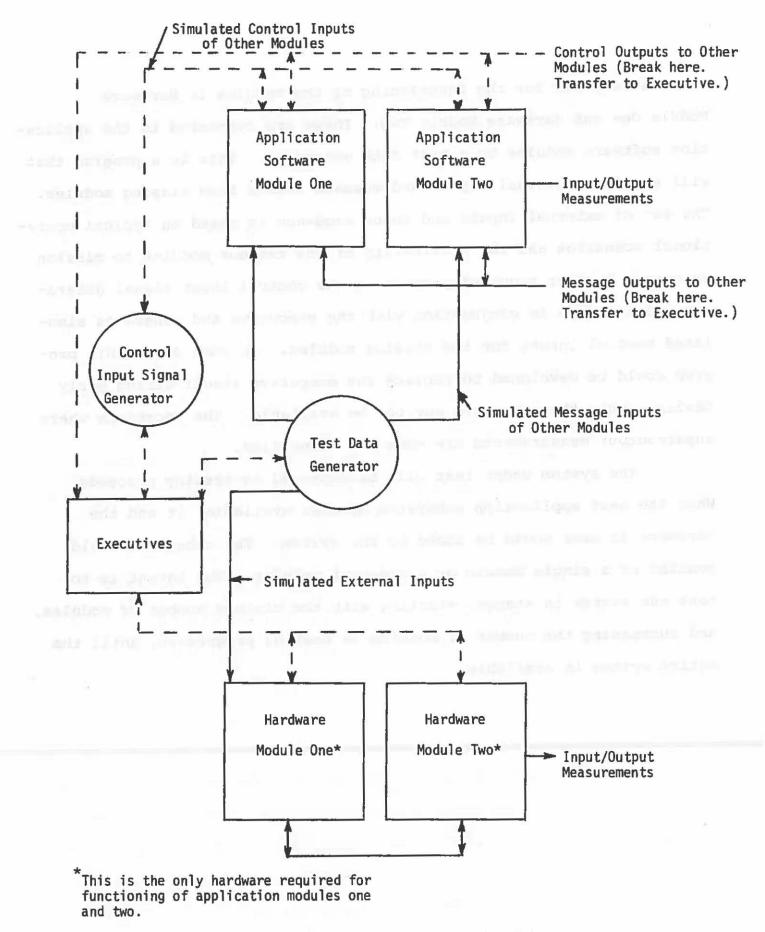

The modularity of the model allows the user to commence testing at an early date. This will require the testing of a subsystem. The subsystem is defined in the test plan and testing will commence as soon as all the modules of the subsystem are available. This is illustrated in Figure II-4. In this figure there are two application modules in the subsystem that are ready to be tested. The only hardware

II-28

Figure II-4. Prototype Test Configuration

that is required for the functioning of the modules is Hardware Module One and Hardware Module Two. These are connected to the application software modules by a test data generator. This is a program that will simulate external inputs and message inputs from missing modules. The set of external inputs and input sequence is based on typical operational scenarios and the criticality of the various modules to mission success. Another required program is the control input signal generator. This works in conjunction with the executive and generates simulated control inputs for the missing modules. In some cases this program could be developed to replace the executive itself during early testing, when the executive may not be available. The locations where input/output measurements are made are identified.

The system under test will be expanded as testing proceeds. When the next application subsystem becomes available, it and the hardware it uses would be added to the system. The subsystem could consist of a single module or a group of modules. The intent is to test the system in stages, starting with the minimum number of modules, and increasing the number of modules as testing progresses, until the entire system is available.

The state of any descent required for

Protections Protocol Test Confidence A-Stranger

**II-30**

# III. MAINTENANCE TESTING

the component level to the functional level. To this month we and

## A. INTRODUCTION

In this section we focus exclusively on the problem of maintenance testing. By maintenance testing we mean the testing which is done after a system has been released and placed into operational use. This is distinguished from prototype testing which is done on the original or prototype system for the purpose of determining whether the system actually constructed meets the design specifications and performance requirements established in the earlier stages of the development process. Prototype testing is essentially a certification process. Maintenance testing, on the other hand, is directed toward the question of whether a particular copy of a system remains in the same condition as it was when first placed in service.

Our goal is to present a method which might be used as the basis of maintenance testing. The idea of partitioning which we consider here is not a new idea. It has been explored and developed extensively in the context of testing digital circuitry [18], but it has apparently not been examined in the context of systems testing or software testing. After the idea is presented, a discussion of some of the problems in applying the method in a real testing situation is included.

## B. DISCUSSION OF SYSTEM FAULTS

We define a system fault as any hardware or software condition which causes the system to deviate from its design specification in an observable manner. Observations can be made at several levels from

the component level to the functional level. In this section we are not concerned about the level at which observations are made, but we do make some additional assumptions about the nature of system faults and it is important that these be clearly understood.

We assume that the faults under consideration are non transient in the sense that, whatever condition or fault occurs, it remains until corrected. Thus spurious results are not observed in the testing procedure. This means that when given the same initial state of the system the same input test conditions always produce the same test output. Thus the tests are repeatable in the sense that the system being tested is not changing during the test period. In a real testing situation it is often the case that apparently spurious results are obtained. The practical difficulty in reproducing them generally lies in the inability to reproduce the test conditions exactly. This often occurs because a sequence of tests interact. Earlier tests may change memory or write over critical values or otherwise change the state of the system. Thus for purposes of our discussion we will assume that the system under test has a reset capability so that the state of the system is the same before each test. The system may contain a fault, but it contains the same fault until fixed. The effect of this reset assumption is to make each test in a series of tests act independently so that exactly the same information is obtained by applying test 1 and then test 2 as is obtained by applying first 2 then 1.

In our discussion of partitioning we assume:

a) the set of all faults under consideration can be enumerated. We denote the faults by  $f_1, \ldots, f_n$  and we let  $f_0$  denote the condition of no fault,

- b) any fault in the system remains in effect until it is corrected (so that test results are repeatable as discussed above),

- c) the system being tested contains at most one fault,

- d) the system being tested is reset to some initial state before the application of each test.

The most restrictive of these assumptions is probably the first. In a complex system the number of things which can go wrong is immense and, to be able to detect and isolate individual faults, considerable precision is required to distinguish among the many similar faults.

The assumption that the system contains only a single fault when tested can perhaps be justified by assuming that the test procedure is repeated frequently, so that each fault is detected before others occur. This is obviously invalid for massive failures in which a number of faults arise simultaneously from the same cause. On the other hand, if certain combinations of faults are thought to be likely, they can be handled by defining them at the outset as a single fault.

C. DISCUSSION OF PARTITIONING

We denote by  $T_i$ , i = 1, ..., m the tests which can be applied to the system. It is convenient to think of the maintenance test procedure as being applied to a system containing an unknown one of the faults  $f_j$ , j = 0, ..., n. The purpose of the tests is to determine which of the conditions  $f_0, ..., f_n$  exists in the particular system under test.

The testing procedure consists of applying a sequence of tests to the system. Each test results in some observable outcome.

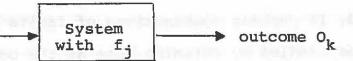

We assume that there is a finite set of possible outcomes which we designated  $O_k$  k = 1,...,p.

If we had a single test which was powerful enough, there would be a distinct outcome associated with each fault. Such a test would be comprehensive in the sense that no other tests would be required to isolate the fault. Such a test is said to have full resolution. A test of this type would be very extensive and complicated and, although it fits within our discussion here, our thinking is oriented toward less comprehensive tests. Thus we will suppose that the individual tests under consideration do not provide full resolution, but to be useful they must provide some resolution among the faults.

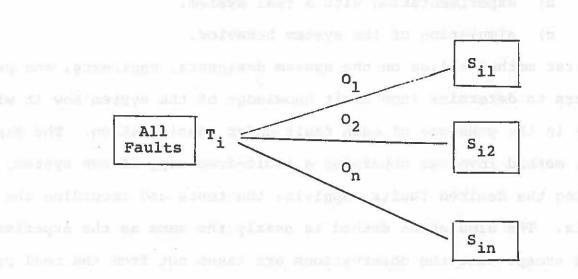

Figure III-l illustrates the process of applying test  $T_i$  to a system containing fault  $f_i$  with the result that outcome  $O_k$  is

Figure III-1. A Typical Test.

observed. It is necessary to fully characterize the performance of each test  $T_i$  in the presence of the faults  $f_j$ , and we imagine that for each test the resulting outcome is known in the presence of each fault. This is illustrated in Figure III.2.

Figure III-2. Typical Test Results for Test T;.

The data of the type shown in Figure III-2 can be obtained in several ways. These include:

- a) analysis of the system design,

- b) experimentation with a real system,

- c) simulation of the system behavior.

The first method relies on the system designers, engineers, and programmers to determine from their knowledge of the system how it will behave in the presence of each fault under consideration. The experimental method involves obtaining a fault-free copy of the system, inducing the desired faults, applying the tests and recording the results. The simulation method is nearly the same as the experimental method except that the observations are taken not from the real system but from a model of it, probably a computer simulation.

It is not intended that the tests, when applied to a system containing an unknown fault, result in a pass or fail. Some faults produce the same outcome under test  $T_i$  as the fault-free system. For example, the results in Figure III-2 indicate that  $f_0$  and  $f_n$  both produce outcome  $O_3$ , but it would be misleading to apply  $T_i$  to a system, obtain  $O_3$ , and claim that the system passed that test. Actually, the test  $T_i$  is unable to discriminate between  $f_0$  and  $f_n$ .

The application of a single test serves to partition the set of all possible faults into p mutually exclusive and collectively exhaustive subsets corresponding to the p possible outcomes.

For notational purposes we denote the set of all faults which produce outcome k when subjected to test i by  $S_{ik}$ . Thus when test i is applied with the result  $O_k$  we can conclude that the fault actually present is one of those in set  $S_{ik}$ . This is illustrated in Figure III-3.

Figure III-3. Partitioning the Faults with Test T.

Further testing can be applied to the sets  $S_{ik}$ . Suppose  $T_j$  is applied. This will result in one of the test outcomes say  $O_r$  with the conclusion that the system under test contains one of the faults which is in both the sets  $S_{ik}$  and  $S_{jr}$ .

The maintenance test problem is to select an efficient set of tests which can successively partition the set of possible faults in smaller and smaller sets so that ultimately the actual fault can be isolated. Possible criteria for test selection will be discussed after the examples.

D. SEQUENTIAL AND COMBINATIONAL TESTING

In any testing situation where a sequence of tests is to be applied to a system the question will arise whether later tests in the sequence are to be selected on the basis of the results from earlier tests or not. The case where earlier test results do influence the selection of later tests is called a <u>sequential</u> testing procedure, otherwise combinational.

Sequential testing is a more powerful method in that fewer tests will generally be required to isolate a fault since the sequential nature of the procedure allows the selection of later tests which are more capable of discriminating among the remaining possible faults. Combinational procedures, although independent of observed test results, may be easier to implement in checking out a software system since less storage space is required to store the tests and less logic required to implement them.

## Examples

To illustrate the ideas of partitioning consider the following data used in examples 1 and 2. The table entries 1, 2, and 3 refer to outcomes  $O_1$ ,  $O_2$ , and  $O_3$ .

| 1              | f <sub>0</sub> | f1 | f2 | f <sub>3</sub> | f4 | f <sub>5</sub> | f <sub>6</sub> | f <sub>7</sub> | f <sub>8</sub> |  |  |  |  |  |

|----------------|----------------|----|----|----------------|----|----------------|----------------|----------------|----------------|--|--|--|--|--|

| T <sub>1</sub> | 1              | 2  | 2  | 1              | 3  | 2              | 1              | 1              | 3              |  |  |  |  |  |

| т2             | 2              | 2  | 2  |                |    |                |                | 1              | 2              |  |  |  |  |  |

| т <sub>3</sub> | 2              | 1  | 3  | 1              | 2  | 2              | 3              | 2              | 3              |  |  |  |  |  |

| <b>T</b> 4     | 1              | 3  | 3  | 2              | 2  | 2              | 3              | 3              | 3              |  |  |  |  |  |

| т <sub>5</sub> | 2              | 3  | 1  | 3              | 3  | 1              | 3              | 2              | 2              |  |  |  |  |  |

| <sup>т</sup> 6 | 3              | 2  | 3  | 2              | 2  | 1              | 1              | 2              | 1              |  |  |  |  |  |

Table III-1. Data for Examples 1 and 2.

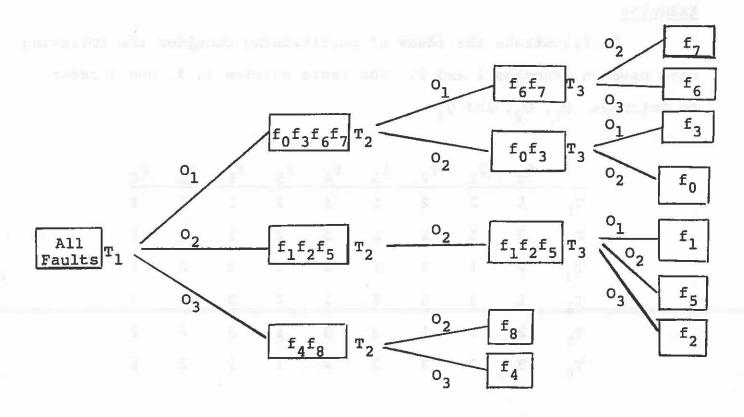

Example 1: A Combinational Test Procedure

In this example we illustrate the result of applying tests  $T_1$ ,  $T_2$ ,  $T_3$  in that order to a system containing one of the faults  $f_0, \ldots, f_8$ . The results are portrayed as a test tree. See Figure III-4.

Notice that the application of  $T_1$  partitioned the faults into three sets: The first, associated with outcome  $O_1$ , containing faults  $f_0$ ,  $f_3$ ,  $f_6$  and  $f_7$ . Subsequent application of  $T_2$  further partitioned this set into two sets containing faults  $f_6$  and  $f_7$ associated with outcome  $O_1$  and faults  $f_0$  and  $f_3$  associated with  $O_2$ . Notice that  $O_3$  is not possible since the actual fault in this case is known (after applying  $T_1$ ) not to be  $f_4$ . The test  $T_2$ is ineffective in the event that  $T_1$  yields outcome  $O_2$ .

Figure III-4. Test Tree for Example 1.

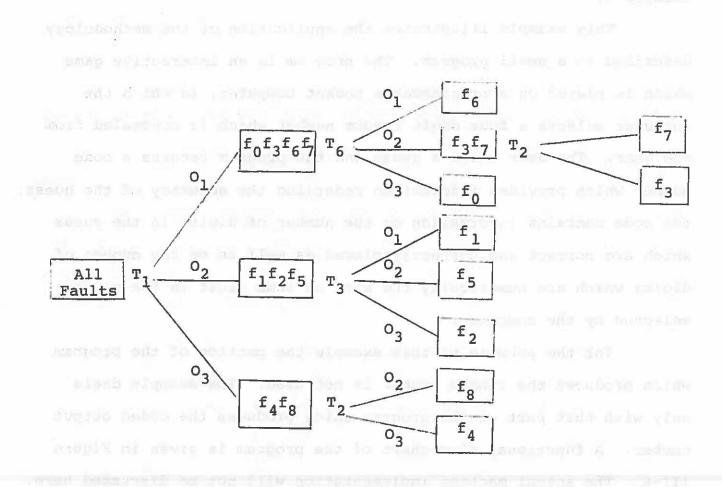

Example 2: A Sequential Test Procedure

In this example different tests are applied depending on the outcome of previous tests. The test tree is shown in Figure III-5. Notice that in this case, particularly when  $T_1$  yielded  $O_2$ , the later tests could be selected to make best use of the information already available.

Figure III-5. Test Tree for Example 2.

Reflecting on these possible test trees raises several questions: Should the test procedure be sequential or combinational, how shall possible test sequences be compared and what is the "best" procedure? For example, if the system is very likely to be faultfree, then a test sequence which begins with  $T_4$  is attractive unless  $T_4$  is very expensive or time consuming. On the other hand  $T_4$  is nearly worthless if the probability of having a condition other than  $f_0$  is large. After considering one more example, we will address these questions of test selection by considering several possible test objectives.

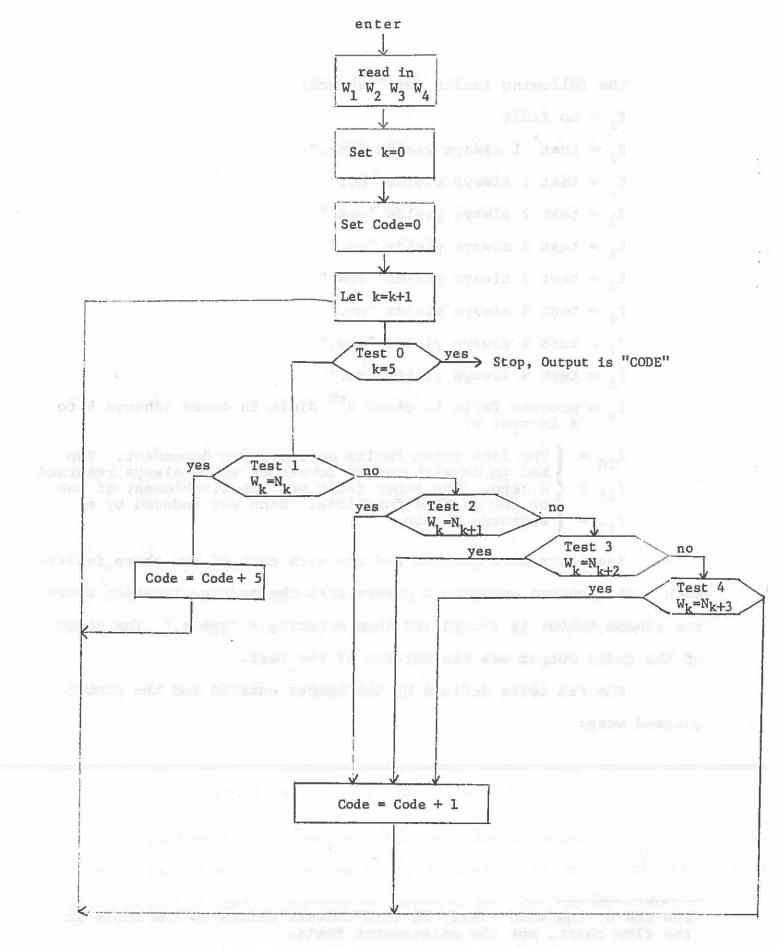

## Example 3:

This example illustrates the application of the methodology described to a small program. The program is an interactive game which is played on a programmable pocket computer, in which the computer selects a four digit random number which is concealed from the user. The user makes a guess and the program returns a code number which provides information regarding the accuracy of the guess. The code contains information on the number of digits in the guess which are correct and correctly placed as well as on the number of digits which are numerically the same as some digit in the number selected by the computer.

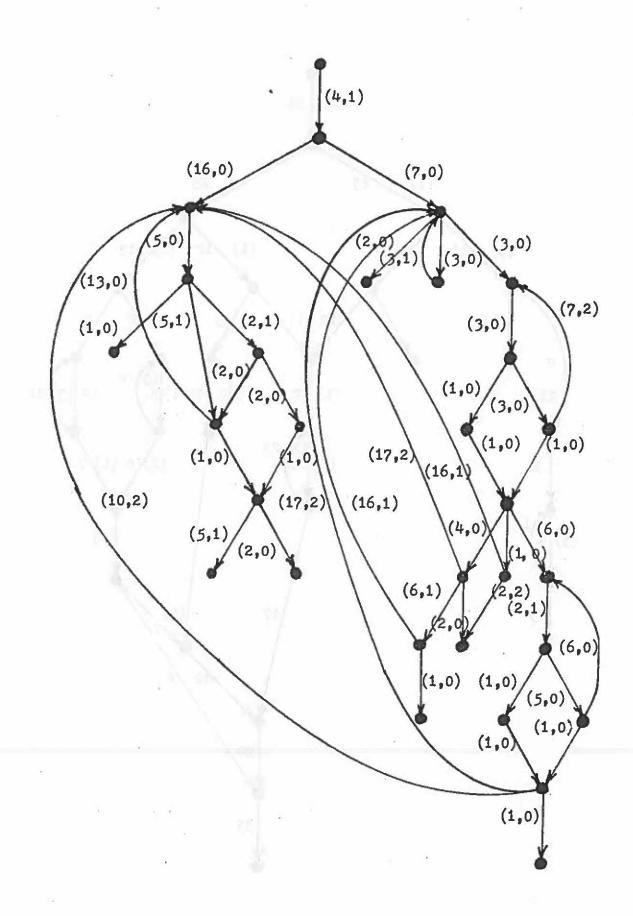

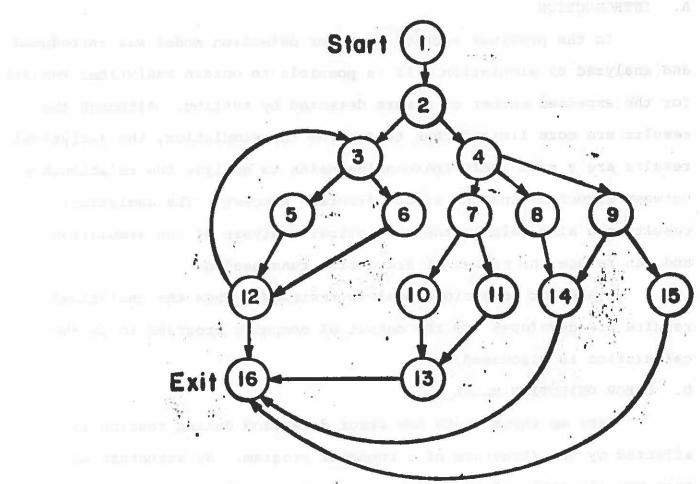

For the purpose of this example the portion of the program which produces the random number is not used. The example deals only with that part of the program which produces the coded output number. A functional flow chart of the program is given in Figure III-6. The actual machine implementation will not be discussed here. All the subscripts on N should be interpreted mod (4).

The program assumes the four digits of the actual number selected by the computer are  $N_1$ ,  $N_2$ ,  $N_3$ ,  $N_4$  in that order. The four digits of the guess are  $W_1$ ,  $W_2$ ,  $W_3$ ,  $W_4$ , respectively.

Figure III-6. Functional Flow Chart for Example 3.

The following faults were defined:

f<sub>0</sub> = no fault

f<sub>1</sub> = test<sup>\*</sup> 1 always yields "yes."

f<sub>2</sub> = test 1 always yields "no."

f<sub>3</sub> = test 2 always yields "yes."

f<sub>4</sub> = test 2 always yields "no."

f<sub>c</sub> = test 3 always yields "yes."

f<sub>6</sub> = test 3 always yields "no."

f<sub>7</sub> = test 4 always yields "yes."

f<sub>o</sub> = test 4 always yields "no."

f<sub>9</sub> = program fails to check 4<sup>th</sup> digit in guess (change 5 to 4 in test 0)

$f_{10} = \begin{cases} The last three faults were machine dependent. Two had to do with memory locations which always returned a zero. The other fault was the disablement of one of the machine functions. Each was induced by a software change. \end{cases}$

Ten tests were defined and run with each of the above faults. Each test involved entering a number into the machine location where the random number is stored and then entering a "guess." The value of the coded output was the outcome of the test.

The ten tests defined by the number entered and the number guessed were:

<sup>\*</sup>The use of the word "test" in this context refers to the tests in the flow chart, not the maintenance tests.

|                 |       | Т.             | Τ_             | T_             |                |                |                          |

|-----------------|-------|----------------|----------------|----------------|----------------|----------------|--------------------------|

|                 |       | -1             | -2             | -3             | <sup>T</sup> 4 | <sup>T</sup> 5 |                          |

|                 | enter | 1111           | 1111           | 1111           | 0123           | 0123           |                          |

|                 | guess | 1111           | 1234           | 0011           | 0000           | 0123           | in the state             |

|                 |       | <sup>т</sup> 6 | <sup>т</sup> 7 | <sup>т</sup> 8 | <sup>т</sup> 9 |                | onni3 <sub>D</sub> oreni |

|                 | enter | 0123           | 0123           | 0011           | 0011           | 0011           |                          |

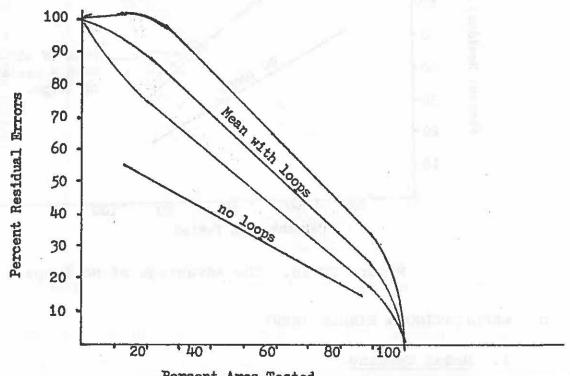

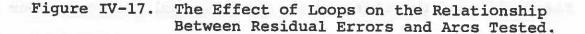

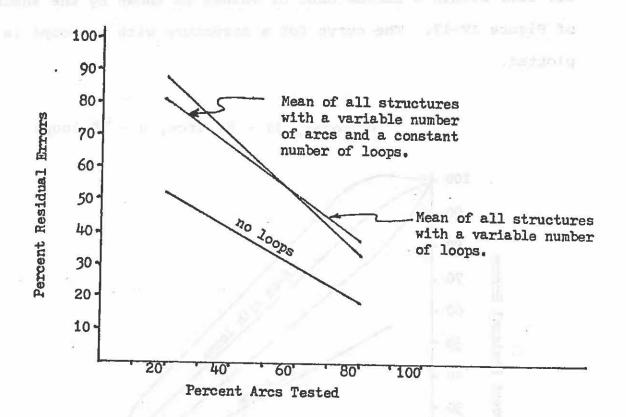

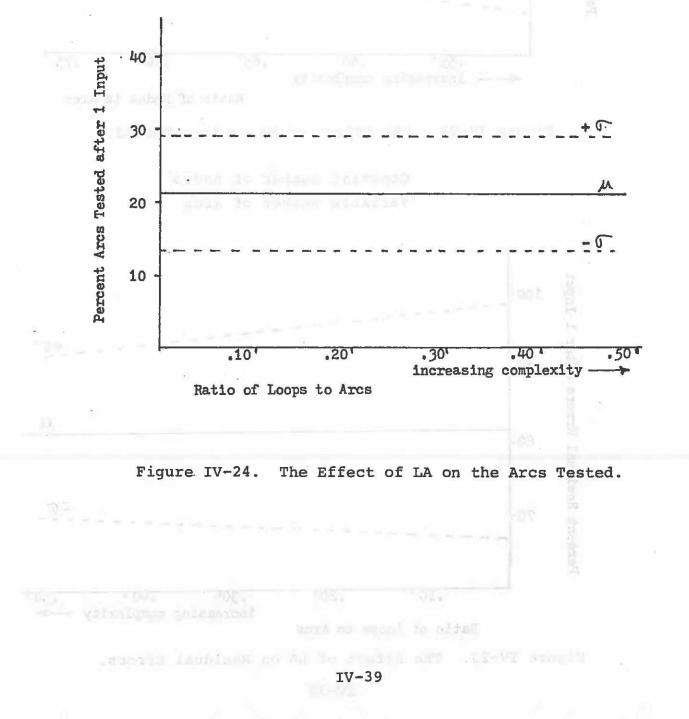

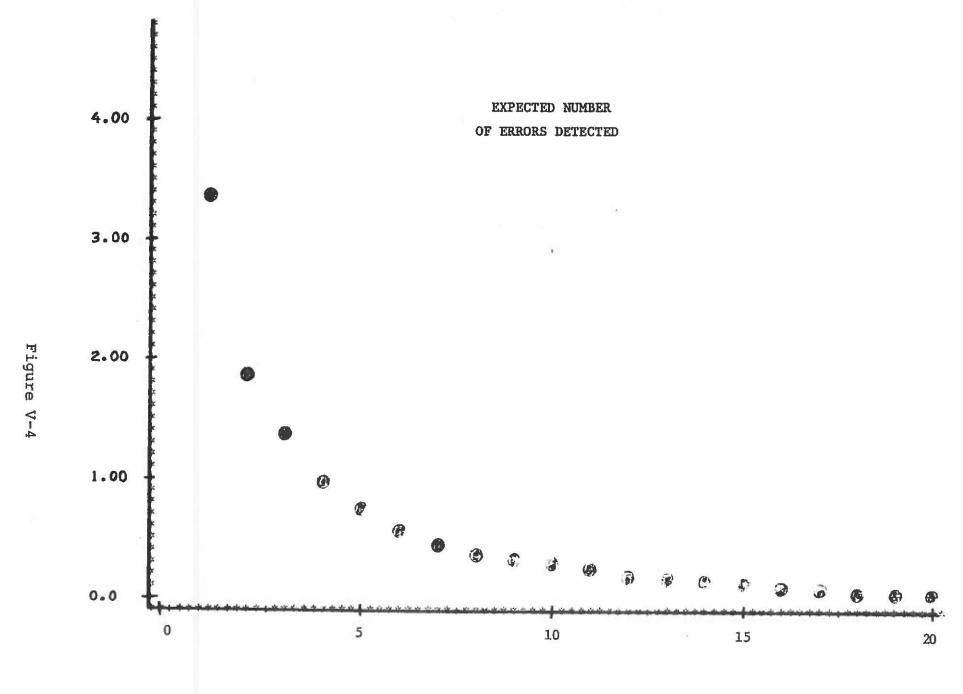

| antinensite 1.5 | guess | 3012           | 0011           | 1111           | 1234           | 0011           |                          |