# The Design, Implementation, and Evaluation of Software and Architectural Support for Nested Virtualization on Modern Architectures

Jin Tack Lim

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

#### COLUMBIA UNIVERSITY

2021

© 2020 Jin Tack Lim All Rights Reserved

#### Abstract

### The Design, Implementation, and Evaluation of Software and Architectural Support for Nested Virtualization on Modern Architectures Jin Tack Lim

Nested virtualization, the discipline of running virtual machines inside other virtual machines, is increasingly important because of the need to deploy workloads that are already using virtualization on top of virtualized cloud infrastructures. However, nested virtualization performance on modern computer architectures is far from native execution speed, which remains a key impediment to further adoption. My thesis is that simple changes to hardware, software, and virtual machine configuration that are transparent to nested virtual machines can provide near-native execution speed for real application workloads. This dissertation presents three mechanisms that improve nested virtualization performance.

First, we present NEsted Virtualization Extensions for Arm (NEVE). As Arm servers make inroads in cloud infrastructure deployments, supporting nested virtualization on Arm is a key requirement. The requirement has recently been met with the introduction of nested virtualization support for the Arm architecture. We built the first hypervisor using Arm nested virtualization support and show that, despite similarities between Arm and x86 nested virtualization support, performance on Arm is much worse than on x86. This is due to excessive traps to the hypervisor caused by differences in non-nested virtualization support. To address this problem, we introduce a novel paravirtualization technique to rapidly prototype architectural changes for virtualization and evaluate their performance impact using existing hardware. Using this technique, we introduce NEVE, a set of simple

architectural changes to Arm that can be used by software to coalesce and defer traps by logging the results of hypervisor instructions until the results are actually needed by the hypervisor. We show that NEVE allows hypervisors running real application workloads to provide an order of magnitude improvement in performance over current Arm nested virtualization support and up to three times less overhead than x86 nested virtualization. NEVE is included in the Armv8.4 architecture.

Second, we introduce virtual-passthrough, a new approach for providing virtual I/O devices for nested virtualization without the intervention of multiple levels of hypervisors. Virtual-passthrough preserves I/O interposition while addressing the performance problem of I/O intensive workloads as they perform many times worse with nested virtualization than without virtualization. With virtual-passthrough, virtual devices provided by a host hypervisor, the hypervisor that runs directly on the hardware, can be assigned to nested virtual machines directly without delivering data and control through multiple layers of hypervisors. The approach leverages the existing direct device assignment mechanism and implementation, so it only requires virtual machine configuration changes. Virtual-passthrough is platform-agnostic and easily supports important virtualization features such as migration. We have applied virtual-passthrough in the Linux KVM hypervisor for both x86 and Arm hardware, and show that it can provide more than an order of magnitude improvement in performance over current KVM virtual device support on real application workloads.

Third, we introduce Direct Virtual Hardware (DVH), a new approach that enables a host hypervisor to directly provide virtual hardware to nested virtual machines without the intervention of multiple levels of hypervisors. DVH is a generalization of virtual-passthrough and does not limit virtual hardware to I/O devices. Beyond virtual-passthrough, we introduce three additional DVH mechanisms: virtual timers, virtual inter-processor interrupts, and virtual idle. DVH provides virtual hardware for these mechanisms that mimics the underlying hardware and, in some cases, adds new enhancements that leverage the flexibility of software without the need for matching physical hardware support. We have implemented DVH in KVM. Our experimental results show that combining the four DVH mechanisms can provide even greater performance than virtual-passthrough alone and provide near-native execution speeds on real application workloads.

## Table of Contents

| Li | List of Figures                                |         |                                               |   |      |  |  |  |  |

|----|------------------------------------------------|---------|-----------------------------------------------|---|------|--|--|--|--|

| Li | ist of Tables                                  |         |                                               |   |      |  |  |  |  |

| Ac | cknov                                          | vledgen | ients                                         | ١ | viii |  |  |  |  |

| 1  | Intr                                           | 'n      | 1                                             |   |      |  |  |  |  |

| 2  | NEVE: Nested Virtualization Extensions for Arm |         |                                               |   |      |  |  |  |  |

|    | 2.1                                            | Archit  | ectural Support for Arm Nested Virtualization | • | 12   |  |  |  |  |

|    | 2.2                                            | Paravi  | rtualization for Architecture Evaluation      | • | 16   |  |  |  |  |

|    | 2.3                                            | KVM/    | ARM Nested Virtualization for Armv8.3         |   | 19   |  |  |  |  |

|    | 2.4                                            | Evalua  | ation of Armv8.3 Nested Virtualization        |   | 23   |  |  |  |  |

|    | 2.5                                            | NEVE    | E: NEsted Virtualization Extensions           | • | 29   |  |  |  |  |

|    |                                                | 2.5.1   | Architecture Specification                    |   | 31   |  |  |  |  |

|    |                                                | 2.5.2   | Recursive Virtualization                      |   | 36   |  |  |  |  |

|    |                                                | 2.5.3   | Architectural Impact                          | • | 37   |  |  |  |  |

|    |                                                | 2.5.4   | Implementation                                | • | 37   |  |  |  |  |

|    |                                                | 2.5.5   | Performance Impact                            |   | 39   |  |  |  |  |

|   | 2.6  | Evaluation of NEVE Nested Virtualization                                   |

|---|------|----------------------------------------------------------------------------|

|   |      | 2.6.1 Microbenchmark Results                                               |

|   |      | 2.6.2 Application Benchmark Results                                        |

|   | 2.7  | Enhanced Support for Nested Virtualization                                 |

|   | 2.8  | Related Work                                                               |

|   | 2.9  | Summary                                                                    |

| 3 | Virt | tual-passthrough: Boosting I/O Performance for Nested Virtualization 56    |

|   | 3.1  | I/O Virtualization for Nested Virtualization                               |

|   | 3.2  | Virtual-passthrough Design                                                 |

|   |      | 3.2.1 System Configuration                                                 |

|   |      | 3.2.2 Example                                                              |

|   |      | 3.2.3 Recursive Virtual-passthrough                                        |

|   |      | 3.2.4 Migration                                                            |

|   | 3.3  | Virtual-passthrough Implementation                                         |

|   | 3.4  | Experimental Results                                                       |

|   | 3.5  | Related Work                                                               |

|   | 3.6  | Summary                                                                    |

| 4 | Opt  | imizing Nested Virtualization Performance Using Direct Virtual Hardware 98 |

|   | 4.1  | Design                                                                     |

|   |      | 4.1.1 Virtual-passthrough                                                  |

|   |      | 4.1.2 Virtual Timers                                                       |

|   |      | 4.1.3 Virtual IPIs                                                         |

| Bil                              | Bibliography 13 |         |              |    |     | 136  |     |     |      |      |     |     |       |

|----------------------------------|-----------------|---------|--------------|----|-----|------|-----|-----|------|------|-----|-----|-------|

| 5 Conclusions and Future Work 13 |                 |         |              |    | 131 |      |     |     |      |      |     |     |       |

|                                  | 4.4             | Summa   | ıry          |    |     | <br> | ••• | ••  | <br> | <br> |     |     | . 130 |

|                                  | 4.3             | Related | Work         |    |     | <br> |     |     | <br> | <br> | ••• |     | . 128 |

|                                  | 4.2             | Evalua  | ion          |    |     | <br> |     | ••• | <br> | <br> |     |     | . 115 |

|                                  |                 | 4.1.6   | DVH Migrati  | on |     | <br> |     |     | <br> | <br> |     |     | . 114 |

|                                  |                 | 4.1.5   | Recursive DV | /H |     | <br> |     |     | <br> | <br> |     |     | . 113 |

|                                  |                 | 4.1.4   | Virtual Idle |    |     | <br> |     |     | <br> | <br> | ••• | ••• | . 111 |

## List of Figures

| 1.1  | Virtualization and Nested Virtualization          | 1  |

|------|---------------------------------------------------|----|

| 1.2  | Steps to Handle an Exit from a VM and a Nested VM | 3  |

| 2.1  | Arm Hardware Virtualization Extensions            | 13 |

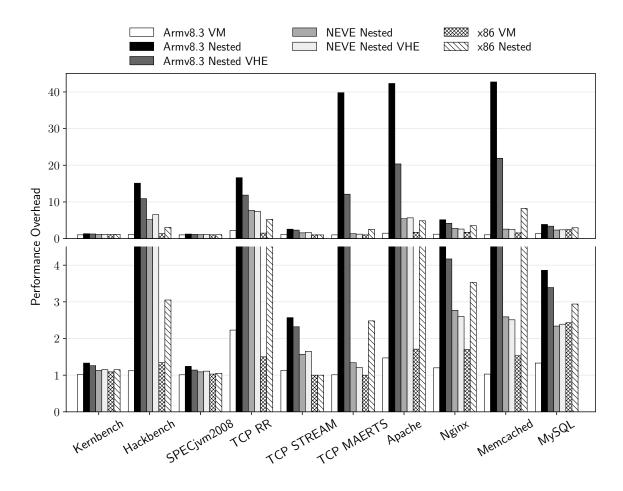

| 2.2  | Application Benchmark Performance                 | 45 |

| 3.1  | I/O Virtualization Models                         | 60 |

| 3.2  | Virtual-passthrough                               | 63 |

| 3.3  | I/O Write Operation with (Virtual) Passthrough    | 66 |

| 3.4  | Recursive Virtual-passthrough                     | 70 |

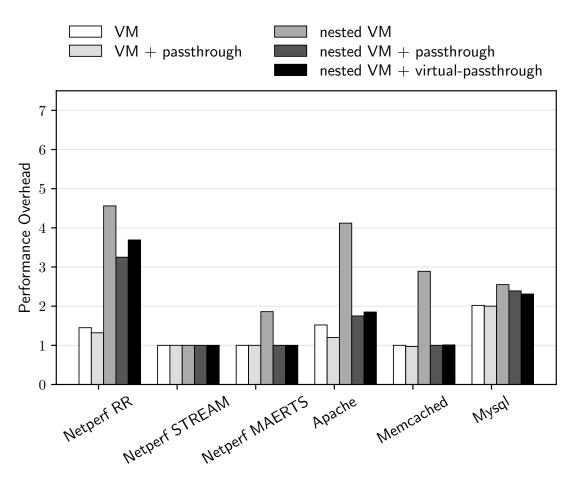

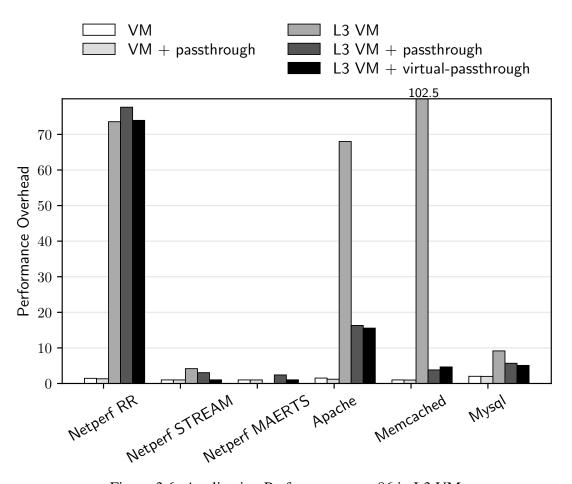

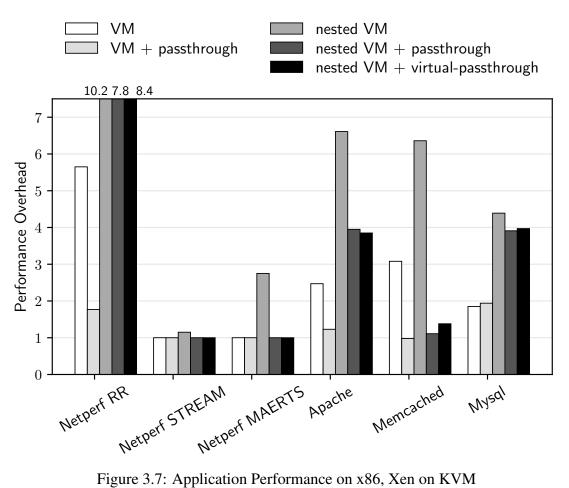

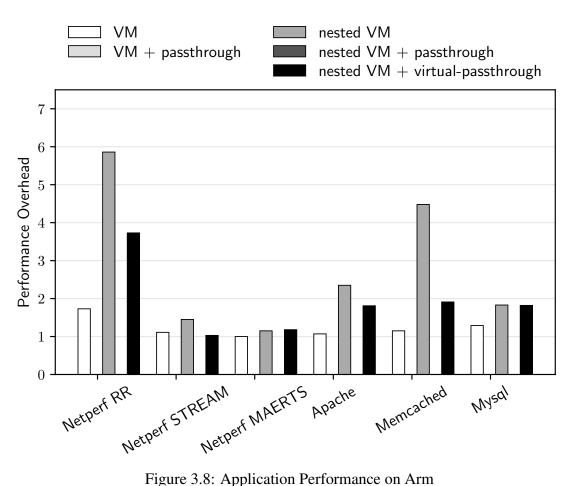

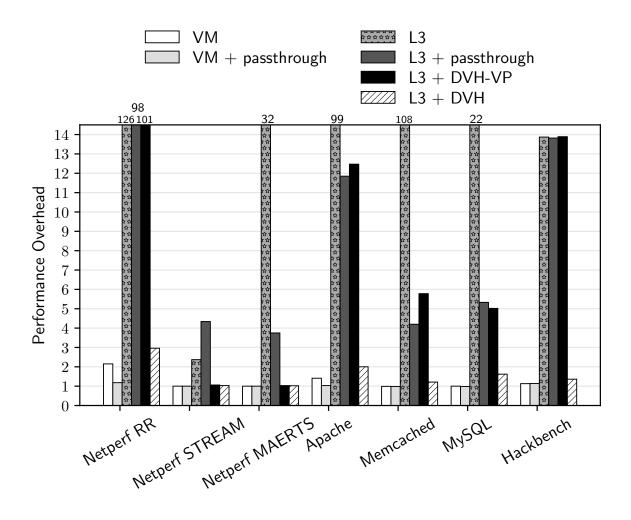

| 3.5  | Application Performance on x86                    | 83 |

| 3.6  | Application Performance on x86 in L3 VM           | 85 |

| 3.7  | Application Performance on x86, Xen on KVM        | 86 |

| 3.8  | Application Performance on Arm                    | 88 |

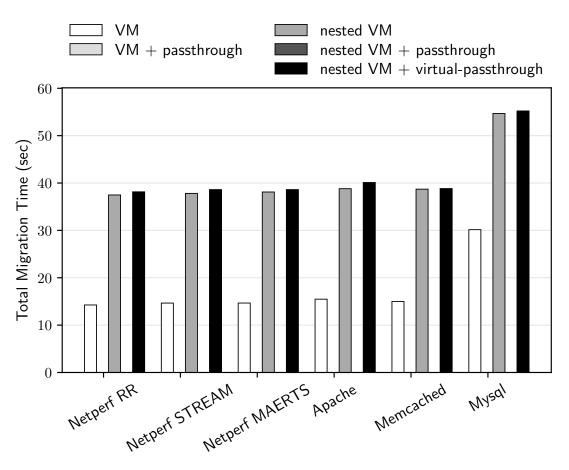

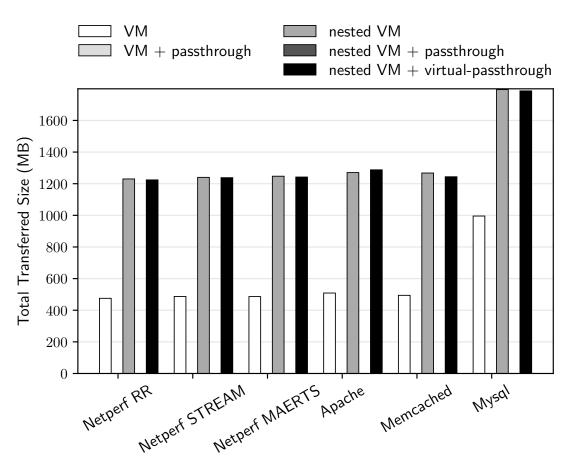

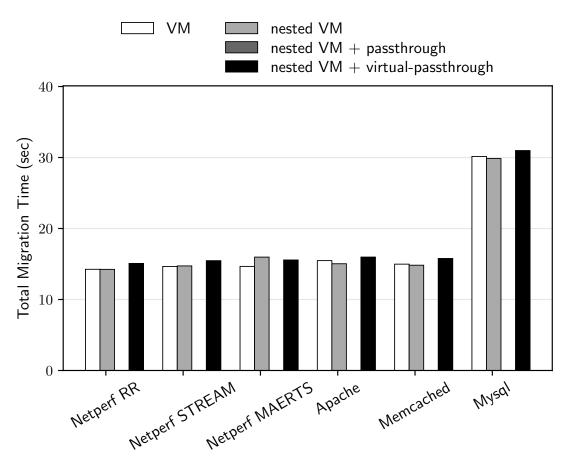

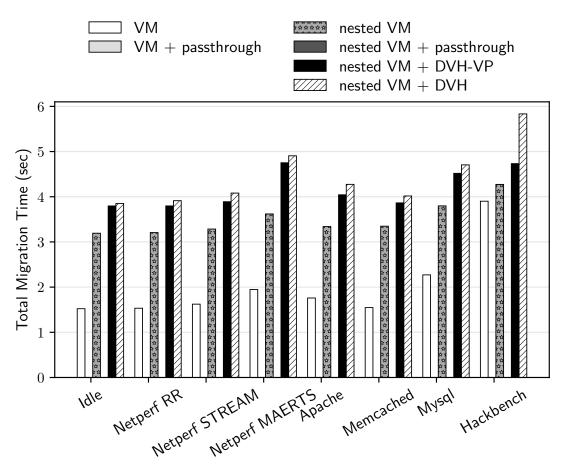

| 3.9  | Total VM Migration Time on x86                    | 89 |

| 3.10 | Total Transferred Size on x86                     | 90 |

| 3.11 | Total Nested VM Migration Time on x86             | 92 |

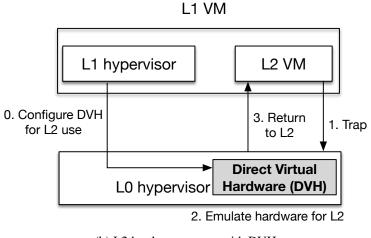

| 4.1  | Hardware Access from Nested VM                    | 00 |

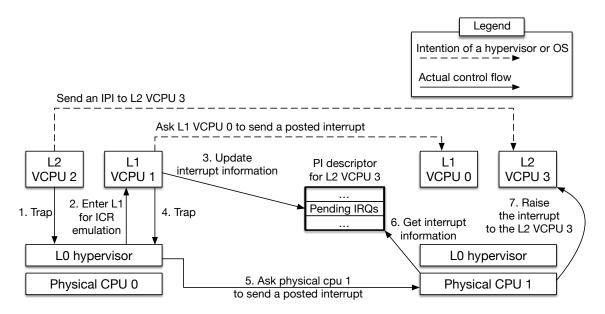

| 4.2 | Nested VM IPI Delivery                   |

|-----|------------------------------------------|

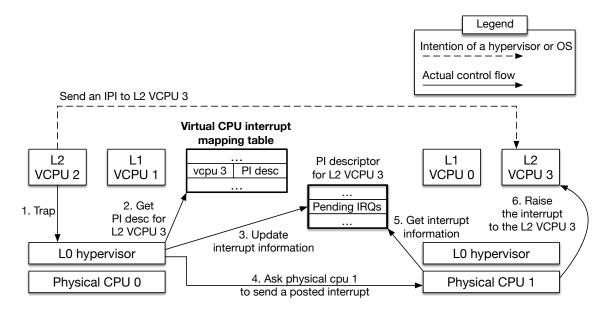

| 4.3 | Nested VM IPI Delivery with Virtual IPIs |

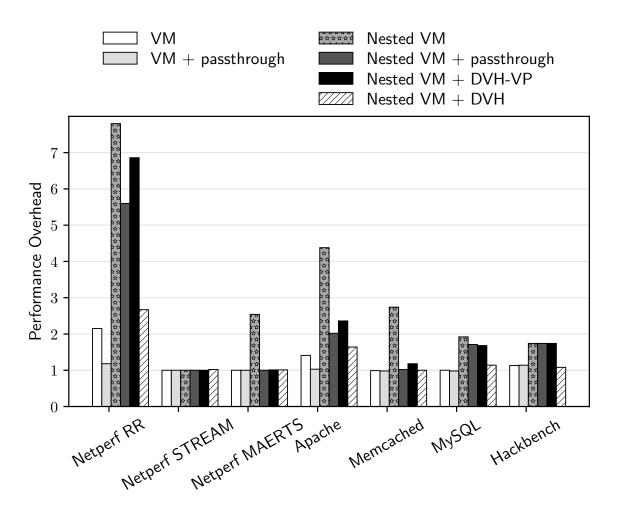

| 4.4 | Application Performance                  |

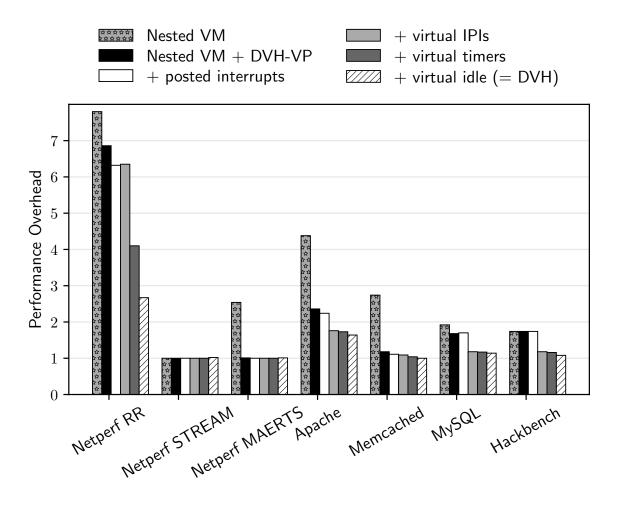

| 4.5 | Application Performance Breakdown        |

| 4.6 | Application Performance in L3 VM         |

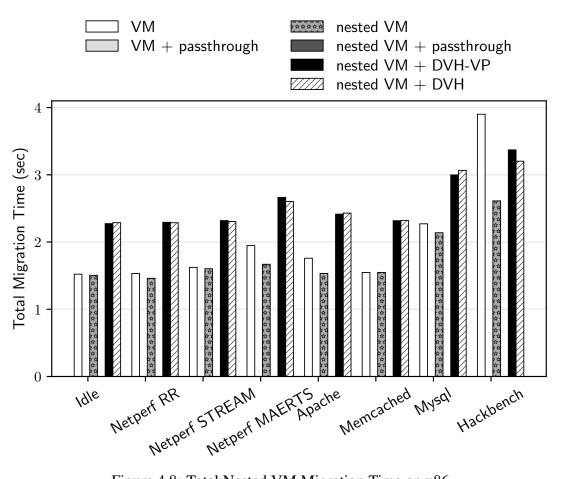

| 4.7 | Total VM Migration Time on x86           |

| 4.8 | Total Nested VM Migration Time on x86    |

## List of Tables

| 2.1 | Microbenchmark Cycle Counts                  | 25  |

|-----|----------------------------------------------|-----|

| 2.2 | VNCR_EL2 Register Fields                     | 31  |

| 2.3 | VM System Registers                          | 32  |

| 2.4 | Hypervisor Control Registers                 | 33  |

| 2.5 | Hypervisor Control GIC Registers             | 35  |

| 2.6 | Microbenchmark Cycle Counts                  | 42  |

| 2.7 | Microbenchmark Average Trap Counts           | 43  |

| 2.8 | Application Benchmarks                       | 44  |

| 2.9 | Application Benchmark Raw Performance        | 46  |

| 3.1 | Steps to Send a Packet for Each I/O Model    | 69  |

| 3.2 | Application Benchmarks                       | 81  |

| 3.3 | Application Benchmark Raw Performance on x86 | 82  |

| 3.4 | Application Benchmark Raw Performance on Arm | 87  |

| 4.1 | Virtualization Microbenchmarks               | 117 |

| 4.2 | Application Benchmarks                       | 118 |

| 4.3 | Microbenchmark Performance in CPU Cycles     | 119 |

| 4.4 A | Application Benchmark Raw Performance | 121 |

|-------|---------------------------------------|-----|

|-------|---------------------------------------|-----|

### Acknowledgements

The entire journey of this Ph.D. would not have been possible without the support of my family, friends, and colleagues. First and foremost, I want to thank my advisor, Jason Nieh. His amazing ability to capture the key ideas and present them in such an interesting and coherent way inspired me every time. Second, I want to thank the rest of my dissertation defense committee: Junfeng Yang, Larry Rudolph, Edouard Bugnion, and Ronghui Gu.

Christoffer Dall has been much more than a colleague; he has been a mentor and has become a sincere friend. He provided me with strong moral support throughout my Ph.D. life. Especially in my hardest times, he encouraged and influenced me to have confidence in my own work and push forward. Christoffer also nurtured me on many technical aspects, particularly while working on the NEVE project. The entire experience helped me level up my skills and abilities. To this day, many great moments from our time working together come to mind. Shih-Wei Li joined Columbia in the same year as me, and we went through some challenging moments together. His keen attention to detail and sharp comments amazed me time and time again. Furthermore, Naser AlDuaij and Alexander Van't Hof generously shared their valuable advice from prior experiences as senior Ph.D. students, which helped me a lot to navigate the Ph.D. program.

Much of my work was done interacting with the Linux and QEMU open-source com-

munities and CloudLab. Marc Zyngier provided helpful code reviews of KVM/ARM patches and took over the KVM/ARM nested virtualization patch series that I had worked on. Peter Xu provided insight to troubleshoot many issues related to passthrough and virtual IOMMU for x86. Eric Auger provided an early version of Arm SMMU emulation support, which allowed me to evaluate virtual-passthrough on Arm. Robert Ricci, Mark Harber, David M. Johnson, and Leigh Stoller helped with many questions related to using the CloudLab infrastructure, where most of my experiments were conducted.

Finally, I'd like to thank my family, who provided outstanding support throughout my journey despite the fact that it started in a later stage of life. My wife, Se Jin, made a huge sacrifice to give up a guaranteed future career in Korea to come to the US to support my dream. She has endured this long period with endless patience as my supporter and as a mother, all while continuing her fight to establish a new professional life. My parents and parents-in-law stepped up to provide the support we needed undergoing countless trips back and forth between Korea and the US. I can't even imagine how I would be where I am today without the amazing support of my family.

### Introduction

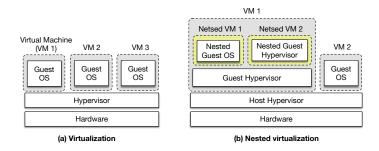

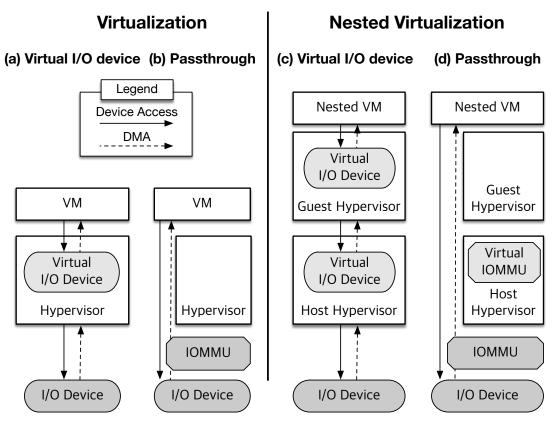

Virtualization is a key technology in cloud computing environments. Virtualization enables software that is designed to run directly on hardware, such as operating systems (OSes), to run inside virtual machines (VMs). A VM is an abstraction of the underlying physical machine, and a hypervisor is software that runs on hardware realizing the abstraction, as shown in Figure 1.1(a).

Nested virtualization involves running multiple levels of hypervisors to support running VMs inside VMs, as shown in Figure 1.1(b). We refer to the *host hypervisor* as the first hypervisor that runs directly on the hardware, the *guest hypervisor* as the hypervisor running inside a VM, and the *nested VM* as the VM created by the guest hypervisor. For more levels of virtualization, we refer to the host hypervisor as the L0 hypervisor, the VM created by the L0 hypervisor as the L1 VM, the guest hypervisor as the L1 hypervisor, the hypervisor running on top of the L1 hypervisor as the L2 hypervisor, and so on.

Figure 1.1: Virtualization and Nested Virtualization

Nested virtualization is increasingly important for cloud computing as deploying VMs on top of Infrastructure-as-a-Service (IaaS) cloud providers is becoming more commonplace and requires nested virtualization support [43, 45, 89, 27]. Furthermore, OSes including Linux and Windows have built-in hypervisors to support legacy applications [83] and enhance security [82]; these OS features require nested virtualization support to run in VMs.

While nested virtualization has many benefits, nested virtualization performance on modern computer architectures is far from native execution speed, and this remains a key impediment to its further adoption. In general, the main reason for virtualization overhead is hypervisor interventions during VM execution required to preserve the VM abstraction, which makes software running inside a VM run slower than it would on the physical machine. Current architectural and software support for nested virtualization incur significantly more hypervisor interventions than non-nested virtualization support because multiple levels of hypervisors involved, which leads to the poor nested virtualization performance.

While a VM can execute most instructions without hypervisor interventions, some instructions require hypervisor interventions to provide a proper execution environment for the VM and to protect other software running on the physical machine, such as the hypervisor and other VMs. For example, an instruction to shut down a machine from a VM should not shut down the physical machine, which would affect the hypervisor and other VMs' executions. The hypervisor needs to trap such instructions so that the VM exits its own execution and execution switches to the hypervisor so it can emulate the instruction that caused the trap.

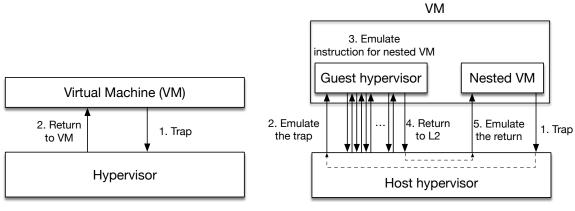

(a) Virtualization

(b) Nested virtualization

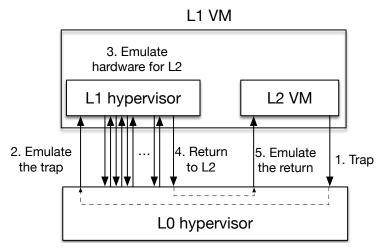

Figure 1.2: Steps to Handle an Exit from a VM and a Nested VM

Modern computer architectures, such as x86 and Arm, provide hardware virtualization support for this well-known trap-and-emulate virtualization technique [22]. On these architectures, a designated hypervisor mode of operation exists where a hypervisor can access architectural features for virtualization. For example, software running in hypervisor mode can execute a special instruction to run a VM. A VM runs in a different mode of operation, non-hypervisor mode. These architectures enable the hypervisor running in hypervisor mode to configure which instructions under what specific conditions are required to trap, allowing the hypervisor to emulate the instruction that VMs attempted to execute. For the previous shutdown example, the shutdown instruction would cause a trap from the VM to the hypervisor, which would then determine the reason for the VM exit was the shutdown instruction and transparently emulate that instruction by terminating only the VM. Figure 1.2(a) shows the steps of handling a trap from a VM.

Modern architectures also use trap-and-emulate to support nested virtualization. Since architectures, such as x86 and Arm, only provide single hypervisor mode, a VM that runs a hypervisor in it still has to stay in non-hypervisor mode. The architectures trap instructions that attempt to access virtualization support inside the VM to hypervisor mode, and the host hypervisor emulates the instructions. As a result, the guest hypervisor can indirectly leverage architectural support for virtualization transparently inside the VM, and can manage its own VMs, nested VMs. The host hypervisor multiplexes the hardware between the guest hypervisor and nested VMs, running both of them inside a VM.

Architectural support for virtualization based on trap-and-emulate incurs only modest performance overhead for non-nested virtualization because the time for emulation, which is based on the number of exits and the cost of handling exits, is small compared to VM execution. The same approach, however, is not efficient enough for nested virtualization. For example, switching between the hypervisor and a VM is a basic and frequent virtualization operation involving more hypervisor interventions for nested virtualization as shown in step 1, 2, 4, and 5 of Figure 1.2(b). The guest hypervisor's attempt to run its own VM, the nested VM, will not switch execution to the nested VM directly but will be trapped to hypervisor mode first because the guest hypervisor does not have permission to access virtualization features required to run a VM. The host hypervisor then switches to the nested VM as part of emulating the guest hypervisor's instruction. Similarly, on exiting the nested VM, execution always first switches to hypervisor mode, and the host hypervisor forwards the exit to the guest hypervisor as part of emulating an exit from the nested VM. Therefore, a switch between a nested VM and the guest hypervisor is indirect and involves twice as many hypervisor interventions compared to non-nested virtualization.

Furthermore, handling a nested VM exit in a guest hypervisor is more costly than handling an exit in a hypervisor for non-nested virtualization because virtualization features that guest hypervisors use will only be provided via trap-and-emulate, as shown in Figure 1.2(b) step 3. For example, accessing VM's states and inspecting its exit reason are frequent hypervisor operations, but they all need to be emulated if they are done by the guest hypervisor. Therefore, each exit from a nested VM can result in many more exits due to indirect hypervisor-VM switches and further virtualization operation emulations, a problem known as exit multiplication, which causes a dramatic increase in virtualization overhead.

My thesis is that simple changes to hardware, software, and virtual machine configuration that are transparent to nested virtual machines can provide near-native execution speed for real application workloads. This dissertation presents three mechanisms that improve nested virtualization performance by reducing the degree of exit multiplication in one of two ways. First, we eliminate the need for the guest hypervisor to exit when executing certain instructions to use virtualization features, avoiding the need to trap and emulate frequent hypervisor operations. This reduces exit multiplication by reducing the number of exits due to guest hypervisor execution. Second, we eliminate the need for the guest hypervisor to handle certain exits from a nested VM, avoiding the need for the host hypervisor to forward such exits to the guest hypervisor. This reduces exit multiplication by avoiding guest hypervisor execution, so it will not cause further exits.

First, we present NEsted Virtualization Extensions for Arm (NEVE) [75]. As Arm servers make inroads in cloud infrastructure deployments, supporting nested virtualization on Arm is a key requirement. The requirement has been met with the introduction of nested virtualization support in the Armv8.3 architecture. We built the first hypervisor using Armv8.3 nested virtualization support and show that, despite similarities between Arm and x86 nested virtualization support, performance on Arm is much worse than on x86.

This is due to excessive traps from the guest hypervisor to the host hypervisor caused by differences in non-nested virtualization support. To address this problem, we introduce a novel paravirtualization technique to rapidly prototype architectural changes for virtualization and evaluate their performance impact using existing hardware. Using this technique, we introduce NEVE, a set of simple architectural changes to Arm, that can be used by software to coalesce and defer traps by logging the results of hypervisor instructions executed by the guest hypervisor in the VM until the results are actually needed by the host hypervisor. This reduces exit multiplication by batching the handling of multiple hypervisor instructions on one exit instead of exiting for each individual hypervisor srunning real application workloads to provide an order of magnitude improvement in performance over the Armv8.3 nested virtualization support and up to three times less overhead than x86 nested virtualization. NEVE is included in the Armv8.4 architecture.

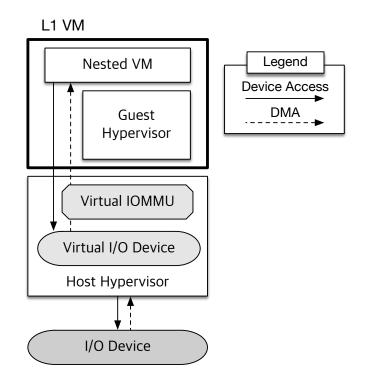

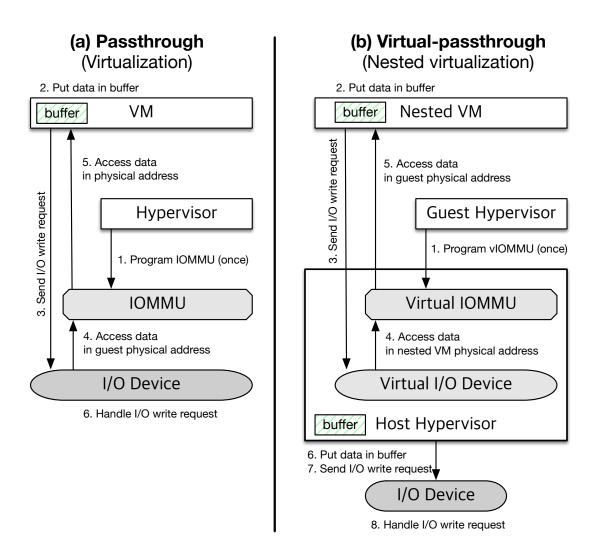

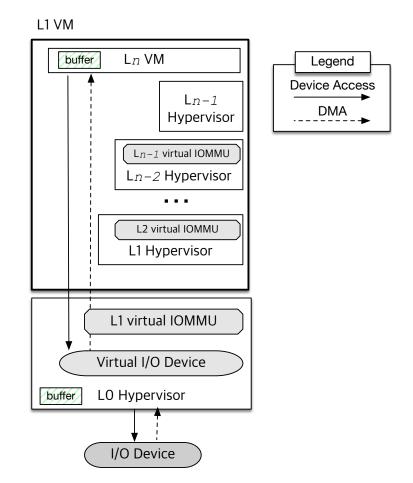

Second, we introduce virtual-passthrough, a new approach for providing virtual I/O devices for nested virtualization without the intervention of multiple levels of hypervisors. Virtual-passthrough preserves I/O interposition while addressing the performance problem of I/O intensive workloads as they perform many times worse with nested virtualization than without virtualization. With virtual-passthrough, virtual devices provided by a host hypervisor can be assigned to nested VMs directly without delivering data and control through multiple layers of hypervisors. Therefore, virtual-passthrough reduces exit multiplication by eliminating the need for guest hypervisor execution when the nested VM interacts with the assigned virtual I/O devices. The approach leverages the existing direct device assignment mechanism and implementation, so it only requires virtual machine

configuration changes. Virtual-passthrough is platform-agnostic and easily supports important virtualization features such as migration. We have applied virtual-passthrough in the Linux KVM hypervisor for both x86 and Arm hardware, and show that it can provide more than an order of magnitude improvement in performance over current KVM virtual device support on real application workloads.

Third, we introduce Direct Virtual Hardware (DVH), a new approach that enables a host hypervisor to directly provide virtual hardware to nested VMs without the intervention of multiple levels of hypervisors [73]. DVH is a generalization of virtual-passthrough and does not limit virtual hardware to I/O devices. Beyond virtual-passthrough, we introduce three additional DVH mechanisms: virtual timers, virtual inter-processor interrupts, and virtual idle. DVH provides virtual hardware for these mechanisms that mimics the underlying hardware and, in some cases, adds new enhancements that leverage the flexibility of software without the need for matching physical hardware support. Like virtualpassthrough, DVH reduces exit multiplication by eliminating the need for guest hypervisor execution when the nested VM accesses the virtual hardware. We have implemented DVH in KVM. Our experimental results show that combining the four DVH mechanisms can provide even greater performance than virtual-passthrough alone and provide near-native execution speeds on real application workloads.

### **Contributions**

The contributions of this dissertation include:

1. We build the first hypervisor to use Arm nested virtualization support. We show that

despite similarities between Arm and x86 nested virtualization support, performance on Arm is much worse than on x86.

- 2. We identify that the performance bottleneck of Arm nested virtualization is due to excessive traps from the guest hypervisor to the host hypervisor, which are caused by the architecture design.

- 3. We propose NEsted Virtualization Extensions for Arm (NEVE), a set of simple architectural changes to Arm that reduce the number of traps to the host hypervisor significantly.

- 4. We introduce a novel paravirtualization technique to rapidly prototype architectural changes for virtualization and evaluate their performance impact using existing hard-ware.

- 5. We implement and evaluate NEVE using the paravirtualization technique. NEVE provides an order of magnitude better performance than the existing Armv8.3 nested virtualization support.

- We discuss the inclusion of NEVE in the Armv8.4 architecture as Arm's Enhanced Support for Nested Virtualization.

- 7. We introduce virtual-passthrough, a new approach for providing virtual I/O devices for nested virtualization without the intervention of multiple levels of hypervisors. Virtual-passthrough preserves I/O interposition while addressing the performance problem of I/O intensive workloads.

- 8. We have applied virtual-passthrough in the Linux KVM hypervisor for both x86 and Arm hardware, and show that it can provide more than an order of magnitude improvement in performance over current KVM virtual device support on real appli-

cation workloads.

- 9. We introduce a new PCI device capability, the migration capability, and we implement the capability in a virtio virtual PCI device to support migration of unmodified nested VM using virtual-passthrough.

- 10. We introduce Direct Virtual Hardware (DVH), a new approach that enables a host hypervisor to directly provide virtual hardware to nested virtual machines without the intervention of multiple levels of hypervisors. DVH is a generalization of virtualpassthrough and does not limit virtual hardware to I/O devices.

- 11. Beyond virtual-passthrough, we introduce three additional DVH mechanisms: virtual timers, virtual inter-processor interrupts, and virtual idle. We implement them in KVM.

- 12. We show that combining the four DVH mechanisms can provide even greater performance than virtual-passthrough alone and provide near-native execution speeds on real application workloads while supporting important virtualization features such as migration.

- 13. We contribute to open source communities by providing source code for the first Arm nested virtualization support in KVM We also provide various bug fixes and reports related to x86 nested virtualization, PCI passthrough, virtual IOMMU, and virtio in KVM/QEMU. The changes are either upstreamed or in the process of being upstreamed.

#### NEVE: Nested Virtualization Extensions for Arm

While the x86 architecture has dominated the server and cloud infrastructure markets, the Arm architecture is leveraging its dominance in the mobile and embedded space to make inroads in cloud infrastructure deployments [18]. Because of the demand for nested virtualization in these markets, Arm introduced architectural support for nested virtualization in the Armv8.3 architecture [21]. However, no Armv8.3 hardware supporting nested virtualization exists yet and, as a consequence, no hypervisors have been developed for Arm that support nested virtualization. While nested virtualization can deliver reasonable performance on x86 [19], it remains an unexplored technology on Arm. Given the growing popularity of virtualization on Arm and attractive use cases for nesting, investigating the future for nesting support on Arm is important.

Because of the absence of Arm hardware with nested virtualization support, we introduce a novel approach for evaluating the performance of new architectural features for virtualization using paravirtualization. Paravirtualization is traditionally used to simplify hypervisor design and improve hypervisor performance by avoiding the use of certain architectural features that are difficult or expensive to virtualize. We instead use paravirtualization to enable a hypervisor to leverage new architectural features that do not exist in the underlying hardware by using existing instructions in the underlying architecture to mimic the behavior and performance of new architectural features. The approach enables us to evaluate the performance of new architectural features for virtualization on existing hardware with real application workloads and hypervisors at native execution speeds.

Using this approach, we build the first Arm hypervisor to support nested virtualization. We modified KVM/ARM [34] to support Armv8.3 nested virtualization features. Both the hypervisor design and Armv8.3 are based on a trap-and-emulate approach similar to how software supports nested virtualization on x86 where both architectures have singlelevel hardware virtualization support. Despite these similarities, we show that Armv8.3 nested virtualization performance is quite poor and significantly worse than x86. Our results provide the first quantitative comparison between Arm and x86 nested virtualization performance, and provide crucial insight regarding virtualization support on other emerging architectures. We identify for the first time how differences in the design of single-level hardware virtualization support, which do not cause significant performance impact for non-nested virtualization, end up causing a very significant performance impact for nested virtualization due to the Arm's RISC-style architecture.

To address this problem, we propose NEsted Virtualization Extensions for Arm (NEVE), a new architecture feature for Arm that can improve nested virtualization performance with minimal hardware and software implementation complexity. We observe that a primary source of overhead for nested virtualization on Arm is the cost of context switching between a VM and the hypervisor and between different VMs. On Arm, there are many instructions involved in these context switches that require hypervisor intervention. This cost is exacerbated when multiple levels of hypervisors are involved in running a VM for nested virtualization. Our insight is that many of these hypervisor instructions do not have an immediate impact on VM or hypervisor execution, but simply prepare the hardware for running a different execution context at a later time. NEVE takes advantage of this insight by logging the results of these hypervisor instructions executed in the VM and coalescing and deferring traps to the hypervisor that runs directly on the hardware until the execution context being affected is actually used, thereby significantly reducing the overhead of nested virtualization. NEVE supports completely unmodified guest hypervisor and OS software.

Using our paravirtualization approach for architecture performance evaluation, we have built a complete hypervisor for nested virtualization by modifying KVM/ARM to use NEVE on existing hardware. Our measurements on real application workloads show that NEVE can provide up to an order of magnitude better performance than the Armv8.3 architecture, and up to three times less overhead than x86 nested virtualization. Arm has revised its nested virtualization architectural support to include NEVE starting with the Armv8.4 architecture [49].

### 2.1 Architectural Support for Arm Nested Virtualization

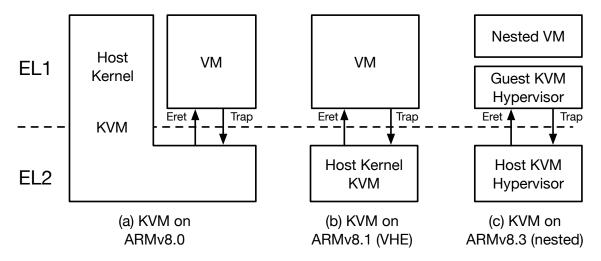

The Armv8 architecture [10] includes the Arm Virtualization Extensions (VE). VE adds a more privileged CPU mode, known as an exception level, called EL2. Arm CPU exception levels EL0, EL1, and EL2 are designed to run user applications, an OS kernel, and a hypervisor, respectively. Each exception level has different sets of system registers, which are only accessible from the same or more privileged exception level. For single-level trapand-emulate virtualization, VMs are executed in EL0 and EL1. CPU virtualization works

Figure 2.1: Arm Hardware Virtualization Extensions

by letting software executing in EL2 configure the CPU to trap to EL2 on events and instructions that cannot be safely executed by a VM, for example on hardware interrupts and I/O instructions. Memory virtualization works by allowing software in EL2 to point to a set of page tables, Stage-2 page tables, used to translate the VM's view of physical addresses to machine addresses, while Stage-1 page tables can be used and managed by the VM without trapping to the hypervisor to translate virtual to physical addresses. Interrupt virtualization works by allowing the hypervisor to inject virtual interrupts to VMs, which VMs can acknowledge and complete without trapping to the hypervisor.

Armv8.1 introduced the Virtualization Host Extensions (VHE) [30]. Without VHE, hosted hypervisors, which are integrated with an OS kernel, needed to split their OS and hypervisor functionality across EL1 and EL2, respectively [34], as shown in Figure 2.1(a). VHE allows running both the OS kernel and hypervisor functionality in EL2 as shown in Figure 2.1(b). VHE expands the capabilities of EL2 so that it can be functionally equivalent to EL1, including adding additional EL2 system registers. VHE supports running existing OS kernels written for EL1 in EL2 without having to modify the OS source code.

VHE transparently redirects EL1 system register access instructions to access EL2 system registers instead. New instructions are added for the hypervisor to access the EL1 system registers, which belong to the VM context.

Running nested hypervisors on Arm involves running the host hypervisor using EL2 as normal, but *deprivileging* the guest hypervisor to preserve protection so that instead of running in EL2, as it is designed to do, it runs in either EL0 or EL1. While it is functionally possible to run the guest hypervisor in EL0 and trap and emulate hypervisor instructions to the host hypervisor, there are at least two important drawbacks of that approach. First, delivering interrupts to the guest hypervisor has to be fully emulated in software and cannot leverage the VE support for virtual interrupts because the architecture does not support delivering virtual interrupts to EL0. Second, because the host hypervisor must trap hypervisor instructions, it must enable a feature to *Trap General Exceptions* (TGE), which has the unfortunate side effect of disabling the Stage-1 virtual address translations for the guest hypervisor running in EL0, making the host hypervisor overly complicated and likely results in poor performance.

A better alternative is running the guest hypervisor in EL1. Unfortunately, this does not work without Armv8.3 nested virtualization support. Hypervisor instructions do not trap to EL2 when executed in EL1, but cause exceptions directly to the guest hypervisor in EL1. This would typically lead to an unmodified hypervisor crashing if executed in EL1. For example, suppose the guest hypervisor wishes to configure its own page table base register. Since this EL2 register is accessed using a hypervisor instruction which does not trap to EL2 but instead causes an exception in EL1, attempts to change the register would cause an unexpected exception to the guest hypervisor executing in EL1, likely leading to a software crash. To address this limitation, Arm introduced architectural support for nested virtualization in the Armv8.3 architecture [21]. It works in three parts. First, it enables trapping of hypervisor instructions executed in EL1 to EL2. Second, it disguises the deprivileged execution by telling the guest hypervisor that it runs in EL2 if it reads the CurrentEL register, which contains the current exception level. Third, it supports using the EL2 page table format in EL1. The resulting configuration using KVM on Armv8.3 is shown in Figure 2.1(c).

**Comparison to x86** Armv8.3 nested virtualization support is similar to x86 in that guest hypervisor instructions can be configured to trap to the host hypervisor. However, the core hardware virtualization support is different. We limit our discussion of x86 to Intel VT as it is similar to AMD-V for all purposes discussed here. While Arm VE provides a separate CPU privilege level, EL2, with its own set of features and register state, Intel VT provides root vs. non-root mode, completely orthogonal to the CPU privilege levels, each of which supports the same full range of user and kernel mode functionality. Both Arm and Intel trap into their respective EL2 and root modes, but transitions between root and non-root mode on Intel are implemented with a VM Control Structure (VMCS) residing in normal memory, to and from which hardware state is automatically saved and restored when switching to and from root mode, for example when the hardware traps from a VM to the hypervisor. Arm instead, as a RISC-style architecture, has a simpler hardware mechanism to transition between EL1 and EL2, but leaves it up to software to decide what state needs to be saved and restored, providing more flexibility to optimize what is done for each transition.

Because of these differences in the core hardware virtualization support, Armv8.3 must provide some additional mechanisms not necessary for x86 to provide the same level of support for nested virtualization. First, since Arm augments the existing CPU privilege level for virtualization support, as opposed to introducing an orthogonal mechanism, Armv8.3 needs to disguise the CPU privilege level so that a hypervisor that normally runs in EL2 does not know that it is running in EL1 as a guest hypervisor. Second, because EL2 is a separate privilege level with its own page table format that differs from the EL1 page table format, Armv8.3 allows a hypervisor, which would normally use the EL2 page table format when running in EL2, to use the same format when running as a guest hypervisor in EL1.

### 2.2 Paravirtualization for Architecture Evaluation

Unfortunately, Armv8.3 hardware supporting nested virtualization is not available. As architectural support for virtualization is increasingly common, understanding the performance of these features is important, ideally before they become set in production hardware. However, evaluating new architecture features for virtualization is challenging because of costs associated with prototyping new hardware and the need to understand the interaction of both hardware and software. Chip vendors use cycle-accurate simulators to measure performance, but they are typically many orders of magnitude slower than real hardware, making it hard to evaluate real-life workloads. Booting a full virtualization stack including the hypervisor and VM can take days, and even then, measuring key application performance characteristics such as fast I/O performance using 10G Ethernet is still not

possible. Furthermore, simulators of commercial architecture designs are themselves quite complex to build and often closed and proprietary, limiting their availability in practice. Software developers often can only use simpler architecture models before hardware is available, at the cost of not being able to measure any real architecture performance.

To overcome this challenge, we introduce an existing idea, paravirtualization, in a new context. Paravirtualization allows for a software interface to a VM that differs slightly from the underlying hardware [108]. It is used to make hypervisors simpler and faster by avoiding certain architecture features that are complex or difficult to virtualize efficiently. We instead use paravirtualization to allow us to build hypervisors using new architecture features that do not exist on current hardware, and measure the performance of a full virtualization stack using new architecture features at native execution speeds on existing hardware.

Paravirtualization to evaluate new architecture features is only possible when the performance and functionality of the proposed feature can be closely emulated using instructions supported by available hardware. For core virtualization support in the architecture, changes often involve traps; either by adding features to trap on instructions that previously did not trap, or by adding logic to avoid costly traps. In both cases, paravirtualization can be used to replace instructions inside the VM with other ones supported by available hardware such that the resulting behavior and performance closely mimic that of a proposed architectural change.

For example, as discussed in Section 2.1, current Arm server hardware does not support nested virtualization, because when a hypervisor runs inside a VM on top of another hypervisor, various instructions that it executes do not trap to the underlying hypervisor for proper execution, but instead simply fail improperly. However, if we replace those hypervisor instructions with instructions that do trap on current hardware and the trap cost is expected to remain similar in future hardware, we can obtain similar relative performance to future hardware that supports nested virtualization with correct trapping behavior.

There are a couple key assumptions in this example. First, the approach is useful for evaluating the relative performance of an architecture feature compared to something else, not to estimate absolute performance of future hardware. For example, the approach can provide an accurate evaluation of the overhead of nested virtualization compared to native execution.

Second, the approach assumes that certain types of traps are interchangeable in terms of performance. For example, on Arm, the trap cost using an explicit trap instruction should be similar to the cost of any system register access instruction that traps. Only the cost of the trap itself needs to remain similar; the overall cost of handling the respective trap can be quite different. This assumption is likely to be true in most cases and we have validated it on Arm hardware, as discussed in Section 2.4.

Using this approach, it becomes possible to efficiently evaluate the performance of full virtualization stacks interacting with fast I/O peripherals, using many CPU cores, and with real-world workloads. It avoids the extremely slow performance, complexity, and limited availability of cycle-accurate simulators for recent architecture versions of commercial CPUs. Perhaps more importantly, the approach allows co-design and rapid prototyping of software and architecture together, reducing long feedback loops common today when the performance of full software stacks is not known until full OS support and hardware is released, which is long after the architecture design phase takes place.

#### 2.3 KVM/ARM Nested Virtualization for Armv8.3

Because Armv8.3 hardware is not yet available, we leverage our paravirtualization approach discussed in Section 2.2 to allow us to design, implement, and evaluate the first Arm hypervisor to support nested virtualization using Armv8.3 architectural support on existing Armv8.0 hardware, which was the newest publicly available Arm hardware at the time this research was conducted. Since both Arm and x86 provide a single level of architectural virtualization support, we take an approach similar to Turtles [19] for supporting nested virtualization on x86, where multiple levels of virtualization are multiplexed onto the single level of architectural support available. We have implemented nested virtualization support on Arm by modifying KVM/ARM [34], the widely-used mainline Linux Arm hypervisor. There are two kinds of modifications: (1) changes to KVM/ARM as a host hypervisor to support running guest hypervisors on Armv8.3, and (2) paravirtualization of KVM/ARM to run as a guest hypervisor on Armv8.0 with similar behavior as an unmodified KVM/ARM guest hypervisor on Armv8.3. We have posted the former to the Linux KVM community [74], and the patches are being upstreamed by the KVM/ARM maintainer [127].

CPU virtualization is accomplished by deprivileging a guest hypervisor so that instead of running in EL2, it runs in EL1 and traps on hypervisor instructions to the host hypervisor running in EL2, which emulates the instruction as needed. A guest hypervisor and its nested VMs all run in a single VM from the point of view of the host hypervisor. The host hypervisor emulates virtual CPUs, including the virtualization extensions, by providing a virtual EL2 mode, creating the illusion to the guest hypervisor running in the VM, that it runs on real hardware capable of running additional VMs. Once the host hypervisor emulates the full architecture including VE to a VM, nesting is recursively supported. Based on the support from the L0 host hypervisor, the L1 guest hypervisor can provide the same architecture environment in the L2 nested VM to run an L2 hypervisor. An L2 hypervisor will run in EL1 and trap on hypervisor instructions to the L0 host hypervisor, which can then forward it to the L1 guest hypervisor providing the emulated architecture for the L2 hypervisor. In this manner, nested virtualization can be done recursively as each hypervisor is limited to providing the architecture environment including VE for the next level hypervisor running in a VM, but is not concerned with further levels of hypervisors.

To mimic Armv8.3 behavior using Armv8.0 hardware so that hypervisor instructions run by the guest hypervisor trap as needed to the host hypervisor, we paravirtualize the guest hypervisor by replacing the hypervisor instructions with hvc instructions. An hvc instruction takes a 16-bit operand and generates an exception to EL2, which can read the 16-bit operand back from a system register. We encode the hypervisor instructions using the 16-bit operand so that on the trap to EL2, the host hypervisor is informed of the original guest hypervisor instruction that was replaced by an hvc and can emulate the behavior of that instruction.

Our paravirtualization technique can be implemented in multiple ways. We added wrappers around all candidate instructions at the source code level, which, depending on a configuration option, at compile time replaces hypervisor instructions with hvc instructions. In this way, we did not change any of the logic or instruction flow of the original KVM/ARM code base and thereby avoided unintentionally introducing bugs or departing from the original hypervisor implementation. It is also possible to paravirtualize the guest hypervisor using a fully automated approach, for example by binary patching a guest hypervisor image.

There are four kinds of hypervisor instructions that are paravirtualized to mimic Armv8.3 behavior so they trap if executed by the guest hypervisor on Armv8.0 hardware. First, instructions that can only run in EL2, such as those that directly access EL2 registers, are undefined when executed in EL1 on Armv8.0, so they are paravirtualized to trap to EL2 to access virtual EL2 state.

Second, instructions that run as part of the hypervisor and access EL1 registers are paravirtualized to trap to EL2 because they will now interfere with the execution of the guest hypervisor which is really running in EL1. For example, an Arm hypervisor will configure EL1 registers to run a VM with its guest OS in EL1. This works fine if the hypervisor is running in EL2 and writes to EL1 registers for the VM, but is problematic if the hypervisor is deprivileged running in EL1, because it will then unknowingly be overwriting its own EL1 register state. Instead, these EL1 access instructions must trap to the host hypervisor which will then emulate the instruction on virtual EL1 register state. The host hypervisor is then responsible for multiplexing EL1 state between the guest hypervisor and the nested VM by context switching the hardware EL1 state to the nested VM's virtual EL1 state when the nested VM runs. For some EL1 access instructions, existing Armv8.0 mechanisms are used by the host hypervisor to configure them to trap, avoiding paravirtualization of these instructions.

Third, the eret instruction is paravirtualized to trap to EL2 and reading the CurrentEL special register is paravirtualized to return EL2 as the current exception level. eret is used by a hypervisor to return to a VM. The guest hypervisor should not directly

return to a nested VM without the host hypervisor's intervention, but must trap to the host hypervisor. The nested VM's EL1 register state is emulated by the host hypervisor; entering the nested VM is only possible once the host hypervisor loads the emulated nested VM state to physical registers.

Finally, VHE adds a number of new instructions that are undefined on Armv8.0 which must be paravirtualized to trap to EL2 so they can be emulated. These new instructions are used to access EL1 state when running in EL2 with register access redirection enabled, as explained in Section 2.1. Because these instructions are not defined on Armv8.0, they generate an exception to EL1 when executed by a guest hypervisor, instead of trapping to EL2. To allow guest hypervisors to be configured with VHE on Armv8.0, these instructions are paravirtualized to trap as they would on Armv8.3. Because VHE is designed to make EL2 work the same way as EL1 and because the guest hypervisor already runs in EL1, running a VHE guest hypervisor works trivially without further changes.

Memory virtualization is done using shadow page tables [1] to handle additional levels of memory translation imposed by nested virtualization. Arm hardware supports only two stages of address translation via Stage-1 and Stage-2 page tables. Nested virtualization requires at least three: L2 VM virtual address (VA) to L2 VM physical address (PA), L2 VM PA to L1 VM PA, L1 VM PA to L0 PA. Similar to previous work [19], the host hypervisor creates shadow Stage-2 page tables to map from L2 VM PAs to L0 PAs by collapsing Stage-2 page tables from the guest and host hypervisors. The Stage-1 MMU translates L2 VAs to L2 PAs using the L2 guest OS's page tables, and the Stage-2 MMU then translates L2 VM PAs to L0 PAs using the shadow page tables.

Interrupt virtualization is accomplished by providing a hypervisor control interface to

a guest hypervisor via trap-and-emulate. This interface is used by a hypervisor to control virtual interrupts for higher-level VMs and is multiplexed onto the single-level Arm virtual interrupt support in the Arm Generic Interrupt Controller (GIC). When a guest hypervisor programs registers in the hypervisor control interface, this must trap to the host hypervisor to sanitize and translate the payload before writing shadow copies of the register payload into the hardware control interface. The hypervisor control interface is memory mapped with GICv2 and therefore trivially traps to EL2 when not mapped in the Stage-2 page tables, but GICv3 uses system registers and must use paravirtualization of the guest hypervisor to mimic Armv8.3's behavior of trapping EL1 accesses to EL2 on Armv8.0.

# 2.4 Evaluation of Armv8.3 Nested Virtualization

We present some experimental results that quantify the nested virtualization performance of Armv8.3 based on running our paravirtualized KVM/ARM guest hypervisor on our KVM/ARM host hypervisor on multicore Arm hardware. We also measure the performance of a KVM x86 guest hypervisor on top of a KVM x86 host hypervisor to compare against a more mature nested virtualization solution with a similar hypervisor design; KVM x86 is based on Turtles. These results provide the first measurements of Arm nested virtualization as well as the first comparison of nested virtualization between Arm and x86. Experiments were conducted using server hardware in CloudLab [41].

Arm measurements were done using HP Moonshot m400 servers, each with a 64-bit Armv8-A 2.4 GHz Applied Micro Atlas SoC with 8 physical CPU cores. Each m400 node had 64 GB of RAM, a 120 GB SATA3 SSD for storage, and a Dual-port Mellanox ConnectX-3 10 GbE NIC. x86 measurements were done using Cisco UCS SFF 220 M4 servers, each with two Intel E5-2630 v3 8-core 2.4 GHz CPUs. Hyperthreading was disabled on the nodes to provide a similar hardware configuration to the Arm servers. Each node has 128 GB of ECC memory (8x16 GB DDR4 1866 MHz dual-rank RDIMMs), a 2x1.2 TB 10K RPM 6G SAS SFF HDD for storage, and a Dual-port Cisco UCS VIC1227 VIC MLOM 10 GbE NIC. The x86 hardware includes VMCS Shadowing [55], the latest x86 hardware support for nested virtualization. All servers were connected via 10 GbE, and the interconnecting network switch easily handles multiple sets of nodes communicating with full 10 Gb bandwidth.

To provide comparable measurements, we kept the software environments across all hardware platforms and hypervisors the same as much as possible. For the host and guest hypervisors, we used KVM in Linux 4.10.0-rc3 with QEMU 2.3.50, with our modifications for Arm nested virtualization. KVM/ARM can be configured to run with or without VHE support; we ran experiments with both versions as guest hypervisors. KVM was configured with its standard VHOST virtio network, and with cache=none for virtual block storage devices [66, 99, 51]. All hosts and VMs used Ubuntu 14.04 with the same Linux 4.10.0-rc3 kernel and software configuration. All VMs used paravirtualized I/O using virtio-net and virtio-block over PCI.

We ran experiments in two configurations, in a VM (no nesting) and in a nested VM. The VM was configured with 4 cores and 12 GB RAM running on KVM with 8 cores and 16 GB RAM. The nested VM was configured with 4 cores and 12 GB RAM running on a KVM guest hypervisor with 6 cores and 16 GB RAM running on the host KVM hypervisor with 8 cores and 20 GB RAM. The CPU and memory configurations were

|                     |       | Armv8.       | x86              |       |              |

|---------------------|-------|--------------|------------------|-------|--------------|

| Micro-<br>benchmark | VM    | Nested<br>VM | Nested<br>VM VHE | VM    | Nested<br>VM |

| Hypercall           | 2,729 | 422,720      | 307,363          | 1,188 | 36,345       |

| Device I/O          | 3,534 | 436,924      | 312,148          | 2,307 | 39,108       |

| Virtual IPI         | 8,364 | 611,686      | 494,765          | 2,751 | 45,360       |

| Virtual EOI         | 71    | 71           | 71               | 316   | 316          |

Table 2.1: Microbenchmark Cycle Counts

selected to provide the same hardware resources to the VM or nested VM used for running the experiments while ensuring more than adequate hardware resources for the underlying hypervisor(s).

We leveraged the kvm-unit-test microbenchmarks [65] to quantify important microlevel interactions between the hypervisor and its VM. Table 2.1 shows the results for running kvm-unit-test in the VM and nested VM configurations for Armv8.3, with and without VHE, and x86. Measurements are shown in cycles instead of time to provide a useful comparison across hardware. Despite using a similar hypervisor architecture on Arm and x86, which both leverage trap-and-emulate hardware support for nested virtualization, as well as sharing the same architecture-independent parts of the KVM implementation, the measurements show that Armv8.3 has drastically worse nested virtualization performance than x86.

The Hypercall benchmark measures the cost of switching from a VM to the hypervisor, and immediately back to the VM without doing any work in the hypervisor. Compared to using a VM, making hypercalls from a nested VM to a guest hypervisor on Armv8.3 is 155 and 113 times more expensive using a non-VHE and VHE guest hypervisor, respectively. When a nested VM makes a hypercall, it first traps to the host hypervisor running in EL2. The host hypervisor then forwards this hypercall to the guest hypervisor by emulating an exception to the virtual EL2 mode in the VM. When the guest hypervisor processes the hypercall, it simply returns back to the nested VM. However, the process of transitioning between the guest hypervisor and the nested VM involves executing many hypervisor instructions that trap to the host hypervisor, which ends up being very expensive.

The Device I/O benchmark measures the cost of accessing an emulated device in the hypervisor. This is a frequent operation for many device drivers and provides a common baseline for accessing I/O devices emulated in the hypervisor. Device I/O is more costly than Hypercall because it emulates the device in addition to performing similar operations to Hypercall. This additional work reduces the relative overhead of running in a nested VM versus a VM, but the overhead is still hundreds of thousands of cycles on Armv8.3 compared to tens of thousands of cycles on x86.

The Virtual IPI (Inter Processor Interrupt) benchmark measures the cost of issuing a virtual IPI from one virtual CPU to another virtual CPU when both virtual CPUs are actively running on separate physical CPUs. This is a frequent operation in multicore OSes that affects many multithreaded workloads. Virtual IPI is more costly than Hypercall because it involves exits from both the sending VM and receiving VM. The sending VM exits because sending an IPI traps and is emulated by the underlying hypervisor. The receiving VM exits because it gets an interrupt which is handled by the underlying hypervisor. Compared to VMs, virtual IPIs between CPUs in nested VMs are more than 73 and 59 times more expensive using non-VHE and VHE guest hypervisors, respectively.

The Virtual EOI benchmark measures the cost of completing a virtual interrupt, also known as End-Of-Interrupt. The interrupt controllers of both platforms, GIC [9] on Arm and APICv [56] on x86, include support for completing interrupts directly in the VM with-

out trapping to the hypervisor. As a result, this operation is much less expensive than the other benchmarks which trap. The KVM host hypervisor provides support on both Arm and x86 so that nested VMs can use hardware-accelerated virtual interrupt completion, resulting in the same cost for both VMs and nested VMs.

In all cases except Virtual EOI, the cost of running the microbenchmarks in a nested VM on Armv8.3 is prohibitively expensive compared to running in a VM. Compared to x86, nested VM performance on Armv8.3 imposes more than an order of magnitude more overhead in terms of cycle counts, and up to 7 times more overhead in terms of relative performance compared to a VM. While trap-and-emulate nested virtualization provides reasonable performance on x86, it does not on Armv8.3.

To investigate the reasons behind the poor Armv8.3 performance, we measured the average number of traps to the host hypervisor when running the Hypercall benchmark. While Hypercall only causes a single trap when running in a VM, it causes 126 and 82 traps to the host hypervisor when running in a nested VM using a non-VHE and VHE guest hypervisor, respectively. Clearly, each trap, also known as an exit, from the nested VM results in a multitude of additional traps from the guest hypervisor to the host hypervisor. This is a major source of overhead for nested virtualization and is called the exit multiplication problem [19].

The guest hypervisor using VHE performs better than without VHE, because it traps less often. When KVM/ARM runs with VHE enabled, it uses EL1 system register access instructions wherever possible with the expectation that the hardware redirects these instructions to EL2 registers, as discussed in Section 2.1. When this is done as a VHE guest hypervisor running in EL1 on Armv8.0 hardware, it simply accesses EL1 registers directly without trapping to the host hypervisor, and the host hypervisor configures the EL1 hardware registers with the guest hypervisor's state. In contrast, a non-VHE guest hypervisor can only access EL2 state using EL2 system register access instructions, and each such access will trap to the host hypervisor since EL2 registers are not accessible at EL1. Despite this reduction in the number of traps for a VHE guest hypervisor, its nested virtualization performance remains poor.

Our measurements of Armv8.3 nested virtualization performance are based on replacing guest hypervisor instructions on Armv8.0 that do not trap as they would on Armv8.3 with hvc instructions, which are explicit trap instructions, to mimic Armv8.3 behavior. The replaced instructions are mostly system register access instructions along with a few eret instructions. On Arm, the cost of a trap should be evaluated in two parts: (1) finding out that you need to generate an exception, and (2) generating the exception. The first can range from expensive (memory fault) to being free (hvc instruction), with a system register trap being almost free. The second is a fixed cost for all instructions. As a result, the cost of traps for the replaced instructions is expected to be very similar to that of an hvc instruction on all implementations of the Arm architecture.

We further measured the trap cost of several different system register access instructions that trap on Armv8.0 hardware and compared their cost with an hvc instruction. In all cases, trapping from EL1 to EL2 was between 68 to 76 cycles, and returning from a trap to EL2 back to EL1 was 65 cycles. The difference in trap costs across different instructions was less than 10% overall and less than 10 cycles. These measurements on Armv8.0 hardware support our assumption that hvc instructions can be used as a suitable replacement to mimic Armv8.3 instructions that trap on system register accesses with similar performance.

# 2.5 NEVE: NEsted Virtualization Extensions

Nested virtualization support as introduced in Armv8.3 traps hypervisor instructions from a deprivileged guest hypervisor running in EL1 to a host hypervisor running in EL2. A single exit from a nested VM can result in the guest hypervisor issuing many hypervisor instructions, resulting in a multitude of additional traps from the guest hypervisor to the host hypervisor. Many hypervisor instructions need to trap because they access system registers. If we can reduce the number of accesses to system registers that need to trap, we can potentially reduce overhead and improve the performance of nested virtualization on Arm.

System registers accessed by the guest hypervisor can be loosely classified into two groups: VM registers, which only affect the VM, and hypervisor control registers, which directly affect hypervisor execution. A key observation is that VM registers do not have an immediate effect on the guest hypervisor's execution, but instead are used to prepare the hardware for running the nested VM when execution returns to the nested VM.

Based on this observation, we propose NEVE, an addition to the Armv8.3 architecture that avoids traps from the guest hypervisor to the host hypervisor for a wide range of hypervisor instructions that access system registers. NEVE supports unmodified guest hypervisors, both hosted and standalone designs, and unmodified guest OSes. NEVE has three key mechanisms. First, it avoids traps to the host hypervisor for VM registers and instead adds hardware support to store VM registers in memory until they are actually needed for VM execution. In Armv8.3, when a guest hypervisor accesses a VM system register, it traps to the host hypervisor, which simply stores this value in memory in a software-managed data structure, and later programs this value into physical registers when running the nested VM. NEVE instead supports this operation in hardware by using an architecturally defined storage format and transparently rewriting system register access instructions into normal memory accesses.

Second, NEVE reduces traps to the host hypervisor for hypervisor control registers by instead identifying and using equivalent registers that can be accessed without trapping. In Armv8.3, when the guest hypervisor writes to a hypervisor control register and traps to the host hypervisor, in many cases, the host hypervisor handles the trap by writing into an equivalent EL1 register. For example, the guest hypervisor will write the base address of the exception vector for itself in VBAR\_EL2 which will trap to the host hypervisor, which in turn needs to write the address to VBAR\_EL1, the equivalent EL1 register, so that the guest hypervisor running in EL1 will handle exceptions correctly. In cases where the EL1 and EL2 registers have the same format, NEVE instead supports this operation in hardware by transparently redirecting accesses to EL2 registers to EL1 registers without trapping to the host hypervisor.

Third, NEVE reduces traps to the host hypervisor when reading certain hypervisor control registers by keeping a cached copy in memory and redirecting register read instructions into normal memory accesses. Read instructions, in the absence of side effects, have no immediate impact on hypervisor execution and can be serviced from a memory cache to avoid traps.

## 2.5.1 Architecture Specification

NEVE introduces an EL2 Virtual Nested Control Register (VNCR\_EL2) which is managed exclusively by the host hypervisor. The host hypervisor can use the VNCR\_EL2 to enable and disable NEVE and to configure a *deferred access page* in memory used to store the values of VM system registers. Table 2.2 shows the bit fields in the VNCR\_EL2 register. The BADDR field contains the physical base address of the deferred access page. The layout of the deferred access page can be arbitrarily defined as long as each VM system register is stored at a well-defined offset from BADDR. The Enable bit completely enables or disables NEVE. When the Enable field is set to 1, and the Armv8.3 nested virtualization support is enabled, all accesses to the VM system registers which would otherwise trap to the host hypervisor are redirected to memory accesses to the deferred access page. Similarly, the register redirection described above for hypervisor control registers is enabled and disabled using the Enable field in the VNCR\_EL2.

| Fields      | Description                              |

|-------------|------------------------------------------|

| bits[52:12] | BADDR: Deferred Access Page Base Address |

| bits[11:1]  | Reserved                                 |

| bit[0]      | Enable                                   |

Table 2.2: VNCR\_EL2 Register Fields

It is up to the host hypervisor to determine when NEVE is enabled and when register values are copied to and from the deferred access page. In a typical workflow, the host hypervisor populates the deferred access page with the initial values of the registers and enables NEVE before running the guest hypervisor. During guest hypervisor execution, all accesses to VM system registers are redirected to the deferred access page. When the host hypervisor needs to use the VM register values, it simply accesses the deferred access

| Category        | Register       | Description                            |  |  |

|-----------------|----------------|----------------------------------------|--|--|

|                 | HACR_EL2       | Hypervisor Auxiliary Control           |  |  |

|                 | HCR_EL2        | Hypervisor Configuration               |  |  |

|                 | HPFAR_EL2      | Hypervisor IPA Fault Address           |  |  |

| VM              | HSTR_EL2       | Hypervisor System Trap                 |  |  |

|                 | TPIDR_EL2      | EL2 Software Thread ID                 |  |  |

| Trap<br>Control | VMPIDR_EL2     | Virtualization Multiprocessor ID       |  |  |

| Control         | VNCR_EL2       | Virtual Nested Control                 |  |  |

|                 | VPIDR_EL2      | Virtualization Processor ID            |  |  |

|                 | VTCR_EL2       | Virtualization Translation Control     |  |  |

|                 | VTTBR_EL2      | Virtualization Translation Table Base  |  |  |

|                 | AFSR0_EL1      | Auxiliary Fault Status 0               |  |  |

|                 | AFSR1_EL1      | Auxiliary Fault Status 1               |  |  |

|                 | AMAIR_EL1      | Auxiliary Memory Attribute Indirection |  |  |

|                 | CONTEXTIDR_EL1 | Context ID                             |  |  |

|                 | CPACR_EL1      | Architectural Feature Access Control   |  |  |

|                 | ELR_EL1        | Exception Link                         |  |  |

|                 | ESR_EL1        | Exception Syndrome                     |  |  |

| VM              | FAR_EL1        | Fault Address                          |  |  |

| Execution       | MAIR_EL1       | Memory Attribute Indirection           |  |  |

| Control         | SCTLR_L1       | System Control                         |  |  |

|                 | SP_EL1         | Stack Pointer                          |  |  |

|                 | SPSR_EL1       | Saved Program Status                   |  |  |

|                 | TCR_EL1        | Translation Control                    |  |  |

|                 | TTBR0_EL1      | Translation Table Base 0               |  |  |

|                 | TTBR1_EL1      | Translation Table Base 1               |  |  |

|                 | VBAR_EL1       | Vector Base Address                    |  |  |

| Thread ID       | TPIDR_EL2      | Software Thread ID                     |  |  |

#### Table 2.3: VM System Registers

page. For example, when the guest hypervisor runs the nested VM, it executes the eret instruction to enter the nested VM, which traps to the host hypervisor. The host hypervisor copies register values from the deferred access page to physical EL1 registers to run the nested VM and disables NEVE while running the nested VM so the VM can access its EL1 registers. Similarly, when the host hypervisor emulates an exception from the nested VM to the guest hypervisor, it copies the EL1 system register values from the hardware into the deferred access page, enables NEVE, and runs the guest hypervisor. The guest hypervisor can now access the VM system registers directly without trapping to the host hypervisor.

| NEVE                      | EL2 Register   | Description                            |  |  |

|---------------------------|----------------|----------------------------------------|--|--|

|                           | AFSR0_EL2      | Auxiliary Fault Status 0               |  |  |

|                           | AFSR1_EL2      | Auxiliary Fault Status 1               |  |  |

|                           | AMAIR_EL2      | Auxiliary Memory Attribute Indirection |  |  |

|                           | ELR_EL2        | Exception Link                         |  |  |

| Redirect to * EL1         | ESR_EL2        | Exception Syndrome                     |  |  |

| Rediffect to *_EE1        | FAR_EL2        | Fault Address                          |  |  |

|                           | SPSR_EL2       | Saved Program Status                   |  |  |

|                           | MAIR_EL2       | Memory Attribute Indirection           |  |  |

|                           | SCTLR_EL2      | System Control                         |  |  |

|                           | VBAR_EL2       | Vector Base Address                    |  |  |

| Redirect to *_EL1 (VHE)   | CONTEXTIDR_EL2 | Context ID                             |  |  |

| Rediffect to *_EET (VIIE) | TTBR1_EL2      | Translation Table Base 1               |  |  |

|                           | CNTHCTL_EL2    | Counter-timer Hypervisor Control       |  |  |

| Trap on write             | CNTVOFF_EL2    | Counter-timer Virtual Offset           |  |  |

| Trap on write             | CPTR_EL2       | Architectural Feature Trap             |  |  |

|                           | MDCR_EL2       | Monitor Debug Configuration            |  |  |

| Padiraat or trap          | TCR_EL2        | Translation Control                    |  |  |

| Redirect or trap          | TTBR0_EL2      | Translation Table Base                 |  |  |

#### Table 2.4: Hypervisor Control Registers

Table 2.3 lists the 27 VM system registers we identified as part of the Armv8.3 specification which do not affect the execution of the hypervisor directly. When enabled, NEVE redirects accesses to these registers to the deferred access page. The VM Trap Control registers control when certain operations performed by the VM trap to the hypervisor and other virtualization features such as Stage-2 translation and virtual interrupts. The VM Execution Control registers are system registers that belong to the VM itself and do not affect hypervisor execution. The Thread ID register, TPIDR\_EL2, is commonly used by hypervisors to store thread-specific data but does not affect the hypervisor's execution.

We distinguish two types of hypervisor control registers, normal system registers and GIC registers related to the hypervisor control interface used for interrupt virtualization, discussed in Section 2.3. When the guest hypervisor executes in virtual EL2, which really runs in EL1, accesses to these EL2 registers would normally trap to the host hypervisor, but

NEVE uses two techniques to avoid traps, register redirection and cached copies. Table 2.4 shows the 17 normal system registers we identified that affect the hypervisor's execution in EL2, and the techniques NEVE used to avoid traps.

Register redirection transparently redirects accesses from an EL2 register to its corresponding EL1 register if it exists and has the same format as the EL2 register. Since the guest hypervisor is really running in EL1, EL2 register accesses can be redirected to corresponding EL1 registers such that changes to the registers have the same impact on the hypervisor's execution when running deprivileged in EL1 as running in EL2 on real hardware. NEVE provides register redirection for 12 EL2 registers with corresponding EL1 registers as shown in Table 2.4, two of which are grouped separately (VHE) as they were added as part of VHE and are only relevant for VHE hypervisors.

Cached copies (shown as "Trap on write" in Table 2.4) transparently change reads from EL2 registers that don't have an equivalent EL1 to instead read a cached copy from the deferred access page. The host hypervisor copies the value of the virtual EL2 register to the deferred access page when running the guest hypervisor to cache the latest value of the register for reads from the guest hypervisor. Writes to these registers will trap, allowing the host hypervisor to update the content of the deferred access page as needed. Cached copies are used for four EL2 registers, two of which have similar EL1 registers but with different formats and thus cannot be used with register redirection from EL2 to EL1 registers, namely CNTHCTL\_EL2 and CPTR\_EL2.