# Open Archive Toulouse Archive Ouverte (OATAO)

OATAO is an open access repository that collects the work of some Toulouse researchers and makes it freely available over the web where possible.

This is an author's version published in: https://oatao.univ-toulouse.fr/26858

Official URL: https://doi.org/10.1007/s10009-019-00513-7

# To cite this version:

Mkaouar, Hana and Zalila, Bechir and Hugues, Jérôme and Jmaiel, Mohamed A formal approach to AADL modelbased software engineering. (2020) International Journal on Software Tools for Technology Transfer, 22 (2). 219-247. ISSN 1433-2779

Any correspondence concerning this service should be sent to the repository administrator: tech-oatao@listes-diff.inp-toulouse.fr

# A formal approach to AADL model-based software engineering

Hana Mkaouar<sup>1</sup> · Bechir Zalila<sup>1</sup> · Jérôme Hugues<sup>2</sup> · Mohamed Jmaiel<sup>1,3</sup>

#### **Abstract**

Formal methods have become a recommended practice in safety-critical software engineering. To be formally verified, a system should be specified with a specific formalism such as Petri nets, automata and process algebras, which requires a formal expertise and may become complex especially with large systems. In this paper, we report our experience in the formal verification of safety-critical real-time systems. We propose a formal mapping for a real-time task model using the LNT language, and we describe how it is used for the integration of a formal verification phase in an AADL model-based development process. We focus on real-time systems with event-driven tasks, asynchronous communication and preemptive fixed-priority scheduling. We provide a complete tool-chain for the automatic model transformation and formal verification of AADL models. Experimentation illustrates our results with the *Flight control system* and *Line follower robot* case studies.

**Keywords** Safety-critical software engineering  $\cdot$  Real-time systems  $\cdot$  Ravenscar profile  $\cdot$  AADL  $\cdot$  Formal specification  $\cdot$  Model-checking  $\cdot$  CADP

# 1 Introduction

Software engineering in safety-critical domains such as transport, health and aerospace industries is a quite delicate field in computer science. In such a context, designers often cope with large distributed, real-time and embedded systems with diverse requirements. Several approaches (modeling, verification, code generation and testing) have focused on simplifying such complex constructions with more abstraction in system design and automation in devel-

☐ Hana Mkaouar hana.mkaouar@redcad.org

> Bechir Zalila bechir.zalila@redcad.org

Jérôme Hugues jerome.hugues@isae.fr

Mohamed Jmaiel mohamed.jmaiel@redcad.org

- ReDCAD Laboratory, University of Sfax, National School of Engineers of Sfax, BP 1173, 3038 Sfax, Tunisia

- Institut Supérieur de l'Aéronautique et de l'Espace (ISAE-SUPAERO), Université de Toulouse, 31055 Toulouse Cedex 4, France

- Digital Research Center of Sfax, B.P. 275, 3021 Sakiet Ezzit, Sfax, Tunisia

opment tool-chains [56]. Among these approaches, we note the Model-Driven Engineering (MDE) methodology. It is a development trend based on modeling language, model transformation, production of documentation and code generation. Theoretically, MDE approaches aim to abstract the system representations and allow a coherent evaluation of the system from the specification until the final application. Technically, tools supporting MDE provide mainly automatic generation, analysis and simulation of models and code.

Other promising approaches are formal methods, which refer to mathematically rigorous techniques and tools for the specification and verification of systems. During the past decades, formal methods have become one of the advocated techniques in safety-critical software engineering [56]. Indeed, they are now accepted in certification processes (e.g., DO-333 [51], formal methods supplement to DO-178C and DO-278A standards for avionics systems) as a way to get certification credits by authorities. For these reasons, the integration of formal methods in MDE approaches seems rewarding.

However, their application requires a formal expertise: the considered system should be specified with a specific formalism such as automata and Petri nets, based on a formal semantics described using mathematical approaches, to be explored by dedicated analysis tools. In contrary, the seman-

tics of modeling (architectural) languages such as AADL and MARTE is often given in natural language (i.e., standard and manual documents). This lack of formal semantics makes modeling languages inappropriate for formal verification, they cannot be explored directly by formal analysis tools. Therefore, it is useful to provide an automatic model generation of the formal specification that can be used and reused to encourage the practice of formal methods and assist designers in system verification.

In this context, we aim to integrate a formal verification phase in an MDE approach based on the AADL (Architecture Analysis and Design Language) [1] language. AADL is an industrial architectural language for critical domains such as avionics, automotive electronics and robotics. It is considered as a leader in real-time modeling and ranked in [39] among the top-used languages in industry. AADL is standardized by the SAE<sup>1</sup>, and its second version was published in 2009 and revised in 2016.

Our contribution consists of two main parts. In the first one, we describe and justify a formal mapping of a realtime task model compliant with the Ravenscar profile [13] for safety-critical systems. This mapping is based on a conventional tasking model inspired from Liu and Layland [37] with rigorous semantics and strong requirements defined by the Ravenscar profile [13]. It is designed to be modular and comprehensible so that it can be easily extended and used in MDE approaches. We mainly support periodic and sporadic tasks, which are asynchronously connected and concurrently executed by a preemptive fixed-priority scheduler. Different model features are specified with the LNT<sup>2</sup> [14,23] formal language, which is a process algebra based on two standards LOTOS and E-LOTOS [23]. LNT provides sufficiently expressive operators for data and behavior with user-friendly notations to simplify writing and extension. The LNT language is supported by the CADP [22] (Construction and Analysis of Distributed Processes) toolbox. This analysis tool, developed since the mid-1980s, offers diverse formal methods like model-checking and simulation. It is a wellexperimented toolbox, used in many industrial applications (e.g., Airbus company [19]).

In the second part, we describe an AADL MDE approach integrating the formal verification at the modeling phase. This allows the early detection of deeper problems that can lead to serious errors in the final application. Especially for real-time systems that consider both concurrency and real-time requirements, it is necessary to validate temporal parameters such as periods, capacities, scheduling protocols, etc. This verification is supposed to be automatic and transparent to

simplify and encourage the practice of formal methods in software engineering.

For AADL formal verification, existing works often adopt the transformation of AADL models into other formal models such as timed automata [34], BIP [15], TASM [57] and FIACE [7], to allow their formal verification with existing analysis tools like Tina, UPPAAL and Polychrony. In general, the focus of these approaches is on the model transformation to generate a formal specification, without automating the next steps required to succeed the model verification. Indeed, providing the formal specification is an important step, but further steps are required to accomplish the verification. The formal techniques are applied on the state space of the system, built from the formal specification according to the language semantics. The properties (system requirements to be verified) should be also specified as graphs or temporal logic properties using dedicated formalisms. In addition, many existing AADL transformations ignore important issues concerning the generated analysis results (utility, usability, etc.), and the fact that the formal verification may fail because of scalability problems.

In our work, we propose and evaluate a transformation AADL2LNT from the AADL language to the LNT language. A basic proposal was discussed in [43], we presented a transformation from AADL into LNT about only periodic tasks. In this paper, we propose to optimize and complete the LNT mapping to support a Ravenscar compliant task model. The AADL2LNT transformation is implemented within the Ocarina [25] tool suite, a development environment for AADL modeling, in order to automatically generate an LNT specification ready for analyzing with the CADP toolbox. In addition, a script file, written in the SVL (Script Verification Language) [20] language, is also generated to assist the verification with CADP. This script ensures the generation of the state space of the LNT specification and the verification of a set of generic properties to check serious problems such as the deadlock detection, the schedulability test and the detection of connection failures. Finally, the verification phase ends with the generation of user-friendly analysis results, easily interpreted by non-formal-expert designers. As part of our experiment, a scalability study is carried out to show the effectiveness of the proposed solution in the case of large systems.

The remainder of this article is organized as follows: Sect. 2 presents some elements of both LNT and AADL languages required in our contribution. In Sect. 3, we develop an LNT formal mapping for a real-time task model. Section 4 details the *AADL2LNT* transformation. Experimental results are discussed in Sect. 5. Section 6 discusses related work. Finally, conclusions and future work end the paper in Sect. 7.

<sup>&</sup>lt;sup>1</sup> Society of Automotive Engineers.

$<sup>^2\,</sup>$  LNT is developed by the VASY and CONVECS teams from Inria for safety-critical systems.

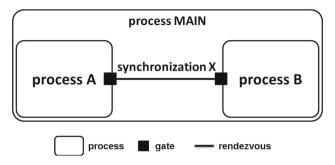

Fig. 1 LNT graphical representation

# 2 Background

In this section, we present the LNT language. Then, we briefly introduce a subset of the AADL language considered in our MDE application.

#### 2.1 LNT

The LNT [14] language combines features from process algebras and programming languages with a dynamic semantics based on the formal SOS (Structural Operational Semantics) rules.

The LNT specification distinguishes two parts: a data part that defines types and functions; and a control part that defines the behavior (within processes). The data part is a fully imperative language in syntax and semantics. The control part includes almost all data part and adds constructs for behavior like non-deterministic choice, process parallelism and communication.

In the rest of this section, we informally present some definitions of the LNT language (partially represented in Fig. 1). We adopt these identifiers following the LNT reference manual [14] notations: M for module,  $\Pi$  for process, B for behavior, I for statement, T for type, G for gate and  $\Gamma$  for channel.

*Module* The LNT specification typically consists of a set of LNT modules. An LNT module M (Listing 1) is named with the same name as its source file (\*.lnt). M can import other modules ( $M_0, ..., M_n$ ); thus, all the definitions of  $M_0, ..., M_n$  are visible and can be used in M definitions. These definitions include the LNT types, channels, functions and processes.

Listing 1 LNT module definition

```

egin{array}{llll} m{module} & M & [ & (M_0 \,, \, \dots \,, \, \, M_n \,) \,] & \mbox{is} \\ & & definition_0 & \dots definition_q \\ \mbox{end} & \mbox{module} \end{array}

```

*Type* The LNT language provides a set of predefined basic types (Boolean, Natural, Integer, Real, Character and String) with the associated predefined functions (basic operations such as addition and comparison) that are automatically available. In addition, the language allows the definition of

non-basic types (Listing 2). A non-basic type may be a list, a sorted list, a set, an enumerated or a range type (specified within the type\_expression, as illustrated with the  $T_{exp}$  type).

## Listing 2 LNT type definition

```

type T is

type_expression

end type

type T<sub>exp</sub> is -- example

list of BOOL

end type

```

Channel An LNT channel (Listing 3) is a gate type that fixes the types of values to be sent or received during the communication on a given gate. The channel may use user-defined or predefined basic types, as illustrated with the  $\Gamma_{exp}$  channel.

Listing 3 LNT channel definition

*Process* An LNT process (Listing 4) is an object describing a behavior. It can be parametrized with a list of formal gates, variables and exceptions. The behavior *B* comprises sequential composition, conditional behavior (if), variable declaration statement (var), loop behavior (loop), non-deterministic choice (select), parallel composition (par), communication, etc.

#### Listing 4 LNT process definition

Communication The LNT processes can be in communication through the gates and channels (Listing 5). Each process has a set of gate declarations to be synchronized with other processes. The same gate allows sending and receiving messages, compatible with a channel, with a rendezvous that blocks the sender until the reception.

# Listing 5 LNT Communication

```

\begin{array}{|c|c|c|c|c|c|} \hline \textbf{process} & \Pi & [G_0 : \varGamma_k, \ldots, G_m : \varGamma_l] & \textbf{is} \\ \hline & G_i & (\texttt{!V}) & -- & \texttt{output} & \texttt{of} & \texttt{expression} & \texttt{V} \\ \hline & G_i & (\texttt{?P}) & -- & \texttt{input} & \texttt{in} & \texttt{pattern} & \texttt{P} \\ \hline & \textbf{end} & \textbf{process} \\ \hline \end{array}

```

Non-deterministic choice An LNT select statement (Listing 6) allows a non-deterministic choice between behaviors  $B_0, \ldots, B_n$ .

#### Listing 6 LNT select statement

Variable declaration An LNT var statement (Listing 7) allows the definition of local variables with their names and their types. The scope of each variable is the statement I, in which it can be assigned values multiple times.

#### Listing 7 LNT var statement

```

var

variable_declaration0 , ..., variable_declarationn

in

I

end var

```

Parallel composition An LNT par statement (Listing 8) is used for behaviors  $(B_0, \ldots, B_m)$  parallelism and gates  $(G_0, \ldots, G_k \text{ and } G_{(i,0)}, \ldots, G_{(i,n_i)})$  synchronization. The behavior  $B_i$  often represents a process instantiation  $(\Pi [G_0, \ldots, G_k, G_{(i,0)}, \ldots, G_{(i,n_i)}])$ . The par composition allows two types of synchronization: global and interface. The global synchronization is defined by  $G_0, \ldots, G_k$ , this communication can happen only if all processes can make it simultaneously. The interface synchronization is defined by  $G_{(i,0)}, \ldots, G_{(i,n_i)}$ . In this case, if a process is waiting for a communication on a gate which belongs to its synchronization interface (e.g.,  $G_{(i,j)}$ ), this communication can happen only if all processes synchronized on the same gate (contain  $G_{(i,j)}$  in their synchronization interface) can make it simultaneously.

Listing 8 LNT parallel composition

```

\begin{array}{|c|c|c|c|c|c|c|c|c|} \hline \textbf{par} & [ \ G_0, & \dots, & G_k & \textbf{in} \ ] \\ & [ \ G_{(0,0)}, & \dots, & G_{(0,n_0)} & -> \ ] & B_0 \\ & | \ | & \\ & [ \ G_{(i,0)}, & \dots, & G_{(i,n_i)} & -> \ ] & B_i \\ & | \ | & \\ & [ \ G_{(m,0)}, & \dots, & G_{(m,n_m)} & -> \ ] & B_m \\ & \textbf{end} & \textbf{par} \end{array}

```

MAIN process In the LNT specification, the system is represented by a set of concurrent processes communicating through gates typed with channels. As shown in Fig. 1, a root process named MAIN should be added to define an entry point of the whole specification. The specification represents an executable semantics in which all parallel pro-

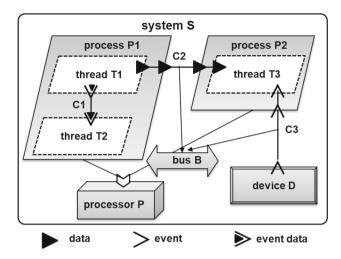

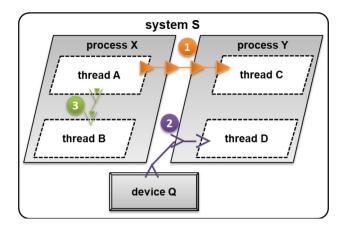

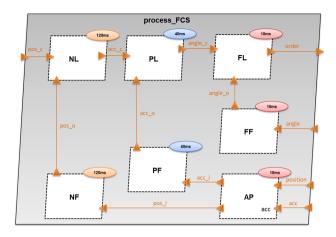

Fig. 2 AADL system graphical representation

cesses start execution and terminate at the same time with the possibility of synchronization by *rendezvous*.

## **2.2 AADL**

The AADL [1,18] language is an architecture description language for model-based engineering of embedded real-time systems. It defines notations, expressed using both a graphical and a textual syntax, to represent a full system with its software and hardware components in one model (architectural representation of the system).

As shown in Fig. 2, the core language describes a system as a hierarchy of components with their interfaces and connections. The AADL components are defined by a type (contains mainly the component interface elements called features) and zero or more implementations (present the component internal structure composed of subcomponents, calls, connections, flows, modes and properties). The components are grouped in three categories: software components (subprogram, subprogram group, data, thread, thread group and process); hardware components (processor, virtual processor, device, bus, virtual bus and memory); and system composition component (system). An AADL connection is a linkage established between components that can be port, parameter or access connections.

The AADL language brings the capability to enrich the model with additional information by a set of standard properties and annexes. Properties are used to complete the component definition and bind the whole system hierarchically. Big and specific additions are specified by separate annexes such as the Error-Model annex to specify the fault behavior/propagation, the ARINC653 annex for the avionics modeling and the Behavior annex [2] to specify the architectural behavior.

In the rest of this section, we briefly present some AADL elements (graphically represented in Fig. 2) that are supported in our work.<sup>3</sup>

Thread A thread component is a concurrent schedulable unit of sequential execution code. It should be declared within a process component, and it is bound to a processor component to be scheduled.

*Process* A process component is a virtual address space containing data, thread and subprogram associated with the process and its subcomponents.

*Processor* A processor component is an abstraction of hardware and software for the scheduling and execution of threads.

Device A device component is considered as an entity to interface with the external environment (such as sensors). A device component can interact with both hardware and software components (e.g., using port connections).

Port connection A port connection allows the transfer of data and/or event between two components (threads and devices), explicitly declared between two ports. As shown in Fig. 2, the ports are directional as *in*, *out* or *in out* ports. They are also typed as data, event or event data. In the case of data transfer, the port may be typed with a data component.

System A system component is a composite of system components (subsystems) or of software and hardware components. Figure 2 represents an AADL model example, in which a system component includes three threads and a device connected through the different port connection types (data, event and event data).

# 3 LNT mapping for a Ravenscar task model

In this first part of our contribution, we aim to define a formal mapping for a real-time system. We use the LNT language to generically specify a standard task model. The LNT syntax combines features of programming languages with concurrency primitives adopted from process algebras, which makes it suitable for specifying concurrent tasks and handling scheduling calculations. The formal representation should simulate the scheduling, the execution and the interaction of tasks. Ideally, the task and the scheduler are separately specified to provide a comprehensible modular mapping.

In this section, we first present the considered task model. Then, we develop the proposed mapping through three principal parts: scheduling mapping, communication and composition/synchronization. Finally, we close this section

with a discussion about the flexibility and the extensibility of our proposal.

# 3.1 A Ravenscar compliant task model

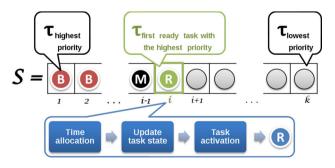

In verification context, a real-time system can be considered as a set of cooperative and concurrent tasks dispatched at regular intervals (periodic tasks) or with special events (aperiodic or sporadic tasks). The system is then abstracted as a task model with a set of real-time parameters, hiding the architectural complexity. In our work, we rely on a conventional tasking model inspired from Liu and Layland [37] real-time model. Formally speaking, we work with a set of k tasks denoted by  $S = \{\tau_1, \ldots, \tau_k\}$  whose each  $\tau_i$  is defined by two parameters  $C_i$  and  $T_i$ :  $C_i$  refers to the capacity or WCET (Worst Case Execution Time); and  $T_i$  is considered as the period and the relative deadline of each dispatch.

In addition, strong constraints are also considered since we deal with safety-critical systems that require certification to be used. In such a context, we mention the Ravenscar profile [13], which is defined to meet safety-critical real-time requirements (determinism, schedulability analysis, suitability for certification, etc.). This profile describes a set of restrictions of the Ada tasking features to allow the static analyses for high integrity system certifications.

The Ravenscar profile can be applied at the model level as a subset composed of a static set of tasks in interaction, run by one preemptive fixed-priority scheduler. In fact, to be Ravenscar compliant, the task model should mainly respect the following restrictions:

- All tasks must be either:

- periodic or time-driven tasks: they are synchronous (simultaneously released at the first time) and cyclic (progress periodically) tasks;

- sporadic or event-driven tasks: they have no fixed first activation, they are activated in response to asynchronous events (invocation-events) with a fixed minimal delay between two successive activations.

- All tasks are created at initialization and then activated and executed according to their priorities:

- All communications and synchronizations between the tasks are achieved using the protected objects<sup>4</sup> with these constraints:

- at most one task can wait on each object;

- sending and receiving operations are atomically executed through the protected object procedures.

<sup>&</sup>lt;sup>3</sup> More details about our AADL subset are provided in the *AADL2LNT* transformation definition (Sect. 4).

<sup>&</sup>lt;sup>4</sup> A protected object is a construction based on the well-known concept of monitors for synchronizations.

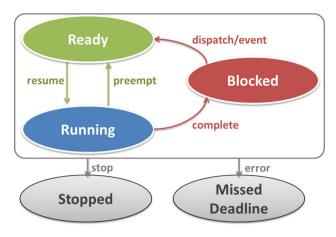

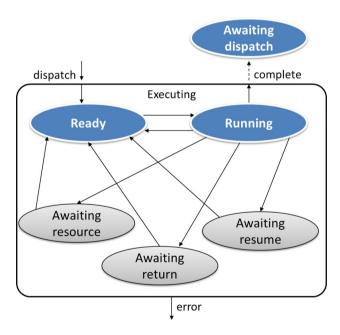

Fig. 3 Task state automaton

- Scheduling is based on FIFO-Within-Priorities policy as follows:

- each task has a fixed priority;

- a task may preempt a task of a lower priority.

The task execution can be represented as a state automaton drawn in Fig. 3. At any time, the task can be in one of these states (READY, RUNNING or BLOCKED). A task may be READY to run, i.e., the task is able to be executed by the processor. It can also be BLOCKED, i.e., the task cannot execute until an external event occurs. A BLOCKED task may become READY by a temporal event (dispatch for a new period) or an invocation-event (for sporadic task). The READY task can be resumed (selected by the scheduler); thus, it moves to the RUNNING state, i.e., the task is actually executing. While running, the task can be preempted and so it returns to the READY state or it can complete its execution and moves to the BLOCKED state.

Note that the task execution is simulated during a hyperperiod  $(H(\tau_{1...k}))$  which is the smallest time interval until the schedule repeats in a cycle of task executions.  $H(\tau_{1...k})$  is calculated as the least common multiple of all task periods (LCM  $(T_i)$ ), which is considered a sufficient time interval to study task models under a priority-based monoprocessor scheduling.

## 3.2 Scheduling mapping

The scheduling mapping concerns the task and the scheduler LNT representations. Generally described, tasks are mapped to LNT processes to be concurrently executed, each  $\tau_i$  is represented by one LNT process, named TASK. These TASKs are scheduled by a main process, named SCHEDULER, which represents the scheduler: the TASKs are synchronized (through the LNT gates and channels) with the SCHEDULER to be activated. Note that the LNT language is not a specific

real-time process algebra. It has no time operators, and all parallel processes start execution and terminate at the same time. There exist timed extensions for the CADP languages (ET-LOTOS [36], RT-LOTOS [16], etc.), but currently, they are not supported by its tools. Nevertheless, the use of the LNT language still sufficient for our purposes, since it provides a rich data part, used to specify real-time features and scheduling algorithms. Therefore, the time is a part of the proposed LNT mapping and it is smartly included (when needed) to provide LNT specifications with reduced state spaces. We define a COUNTER variable to represent the time (a timer to count units of time), used as required to perform the temporal calculations (e.g., dispatching, preemption). In addition, we define a HYPERPERIOD variable that represents  $H(\tau_{1...k})$ , thus, the timer COUNTER is bounded as (0 < COUNTER < HYPERPERIOD).

In the following, we, respectively, develop the TASK and SCHEDULER LNT definitions.

## 3.2.1 Task mapping

The TASK process is designed to represent the task as a schedulable concurrent unit with a potentially infinite sequence of activations (invocations or jobs) by the scheduler. To specify the considered dispatching model, we define a set of activation orders mapped to the LNT enumeration type exchanged between the TASK and SCHEDULER: T\_Dispatch\_Preemption, T\_Preemption,

T\_Preemption\_Completion, T\_Dispatch\_Completion,

T\_Completion, T\_Error and T\_Stop.

We include the TASK skeleton in Listing 9. The process declares an LNT gate, named ACTIVATION, to be synchronized with the SCHEDULER. The TASK behavior is an infinite loop whose body is a non-deterministic choice select in order to separate the *execution*, *error* and *termination* behaviors. The selected behavior is determined by the ACTIVATION communication with its different possible values.

The task state switch (Fig. 3) is mapped in the TASK execution behavior part. The ACTIVATION communication defines the TASK states: the current state is defined according to the received SCHEDULER order. Initially, the TASK is supposed at the READY state. It is suspended until the reception of a SCHEDULER order on the ACTIVATION gate. All the task transitions of Fig. 3 (resume, preempt, dispatch and complete) between the states are translated by suspensions on the ACTIVATION rendezvous with the SCHEDULER. At the reception of an activation order (T\_Dispatch\_Completion, T\_Preemption, T\_Dispatch\_Preemption and T\_Preemption\_Completion), the TASK moves to the RUNNING

state. After the execution, the TASK sends the label T\_Completion to the SCHEDULER meaning that the TASK has accomplished the activation order and it is no more at the RUNNING state. At this point, depending on the received order, the TASK may switch state as follows:

- T\_Dispatch\_Completion: it starts and completes the execution of the current period and enters the BLOCKED state;

- T\_Dispatch\_Preemption: it starts the execution in the current period but with a preemption, thus, it returns to the READY state;

- T\_Preemption: it progresses in execution but without reaching the completion time, so it returns to the READY state;

- T\_Preemption\_Completion: it finishes the execution of the current period and enters the BLOCKED state.

The TASK can also receive a T\_Error and T\_Stop orders, which are, respectively, used to mark a missed deadline and to stop the system simulation. This concerns the *error* and *termination* behaviors, which leads to define two additional task states MISSED\_DEADLINE and STOPPED included in the task state automaton as shown in Fig. 3, used for verification ends.

Note that periodic and sporadic tasks are represented with the same LNT skeleton, while the difference (dispatching model) will be in the activation mode controlled by the SCHEDULER. All the temporal calculations are encapsulated in the SCHEDULER which maintains that periodic tasks are executed with regular-orders, while sporadic tasks receive irregular orders according to the reception of invocationevents.

In our work, we support inter-task communications: a task can be connected with other tasks. At the LNT mapping level, exchanged data and events are generically mapped using an enumerative LNT type (labels DATA and EVENT). The connections are established through the LNT gates and channels. Thus, the TASK can have many gate declarations as required for its connections. The TASK interactions are also controlled through SCHEDULER orders that fix the input and output times as follows:

- T\_Dispatch\_Preemption (the start of execution time): the TASK receives inputs;

- T\_Preemption\_Completion (the completion time): the TASK sends outputs;

- T\_Dispatch\_Completion (the completion execution): the TASK receives inputs at the start time and sends outputs at the completion time.

#### Listing 9 TASK LNT skeleton

```

process TASK [ACTIVATION: LNT_Channel,

Dispatch,

-- other gate declarations

is

1000

select

select -- execution behavior

-- a complete execution

time

ACTIVATION (T_Dispatch_

Completion)

preemption

ACTIVATION (T_Dispatch_

Preemption);

ACTIVATION (T_Preemption)

ACTIVATION (T_Preemption_

Completion);

end select;

ACTIVATION (T_Completion)

[] -- error behavior

ACTIVATION (T_Error)

[] -- termination behavior

ACTIVATION (T_Stop)

end select

end loop

end process

```

# 3.2.2 Scheduler mapping

The SCHEDULER process encodes the scheduling algorithm to simulate the execution of the tasks. It is synchronized with all the TASKs through the ACTIVATION gates. The SCHEDULER construction depends on the set of tasks Sand the chosen scheduling protocol. Following the Ravenscar profile, the task execution is assumed by the preemptive fixed-priority scheduling in which priority of each task is statically fixed and the scheduler runs always the ready task with the highest priority. At any time, if a task with a higher priority becomes ready, the scheduler performs a context-switch preempting the current running task enabling the higher priority task to resume execution. In this paper, we consider the RM (Rate Monotonic) scheduling with a negligible contextswitch time. The task is defined by  $\tau_i = (C_i, T_i)$  whose index i represents the task priority, attributed according to its period  $T_i$  as the task with the smallest period takes the highest priority. To schedule  $\tau_i$ , we also define  $t_i^i$  for the date of the jth activation and  $d_i^i$  for the date of the jth deadline.

In Listing 10, we include the SCHEDULER LNT skeleton. The process declaration has k gates (ACTIVATION\_1, ..., ACTIVATION\_k) with n additional gates if S contains sporadic tasks (NOTIFICATION\_1, ..., NOTIFICATION\_n, with n is the number of sporadic tasks). The SCHEDULER behavior consists of three parts as follows:

- Initialization part: the SCHEDULER begins with a set of initializations needed for the temporal calculations, mainly the COUNTER and the set of tasks S.

- Operational part: this part implements the scheduling algorithm. While COUNTER has not reached the HYPERPERIOD, the SCHEDULER simulates the execution of tasks using Algorithm 1 (illustrated in Figs. 5 and 4).

- Stopping part: the termination of tasks is not allowed in the Ravenscar profile, but in our context of formal verification, we define a global system termination when COUNTER = HYPERPERIOD. Therefore, the SCHEDULER sends the T\_Stop order for all the tasks to mark the end of the simulation.

## Listing 10 LNT SCHEDULER skeleton

```

process SCHEDULER [

ACTIVATION_1 : LNT_Channel_Dispatch,

ACTIVATION_k : LNT_Channel_Dispatch,

NOTIFICATION_1 : LNT_Channel_Event,

NOTIFICATION_n : LNT_Channel_Event]

is

-- initialization part

S : LNT_Type_Task_Array,

in

S [i] := LNT_Type_Task (..);

loop

if (Counter < HYPERPERIOD) then</pre>

operational part

-- time allocation

-- update task state

-- task activation

-- notification for sporadic task

else -- termination part

ACTIVATION_1 (T_Stop)

ACTIVATION_K (T_Stop)

end if

end loop

end var

end process

```

The set of tasks S is statically included using an LNT array. Tasks are indexed within their fixed priorities according to their periods  $(T_{1...k})$ ,  $\tau_1$  (index 1) has the highest priority and task  $\tau_k$  (index k) the lowest one. This array represents the ready-queues in real systems: ready tasks are inserted/deleted at the head/tail according to their priorities in the ready-queue and at any time the scheduler selects the task with the highest priority for execution. In our mapping, we use a static structure where tasks have fixed indexes to mark their priorities, while their states are modifiable by the SCHEDULER itself. Each  $\tau_i$  is represented with an LNT array containing a set of fixed parameters and updated states (12 elements), mainly  $(C_i, T_i, t_j^i, d_j^i)$  and it is initialized as  $\tau_i = (C_i, T_i, t_0^i = 0, d_0^i = T_i)$ .

Note that a sporadic task is ignored until the reception of an invocation-event (considered at the BLOCKED state).

Thereby, the SCHEDULER should be notified for every new incoming invocation-event, which is ensured by the NOTIFICATION\_i gates.

## Algorithm 1: Operational part algorithm

```

while (i \in S) do

if (Blocked or Miss Deadline \tau_i) then

4

Move to \tau_{i+1};

5

6

else if (Ready \tau_i) then

Calculate Allocated_Time of \tau_i;

7

8

hp(i) = 1 \dots (i-1);

while (h \in hp(i)) do

9

if (\tau_i \text{ reaches } t_*^h) then

10

/* \tau_i is preempted by \tau_h

11

Update Allocated_Time of \tau_i;

12

end if

end while

13

/* if \tau_i respects all t_*^{hp(i)}, the

Allocated_Time contains the

required time to complete the

execution

14

Update \tau_i state:

Activate \tau_i;

15

Check sporadic tasks;

/* if we have a preemption, we

return to \tau_h; if we have a

notification from a sporadic

task, we return to \tau_1; else we

move to \tau_{i+1}

end while

18

19 end

```

During the scheduling, the SCHEDULER visits the tasks in loops in order of their priorities to find and run the ready tasks. From the highest to the lowest priority, each task is handled to determine its current state (READY or BLOCKED), thus the first task  $\tau_i$  fixed to the READY state, is always the ready task with the highest priority as shown in Fig. 4. Formally, the SCHEDULER compares  $t^i_j$  and  $d^i_j$  with the COUNTER value. Thus, it decides  $\tau_i$  state as follows:

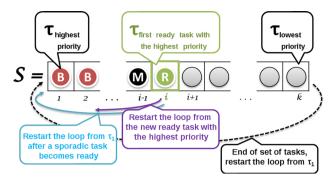

Fig. 4 SCHEDULER algorithm: ready task

Fig. 5 SCHEDULER algorithm: task-loops

- BLOCKED:  $\tau_i$  is an inactive sporadic task or it is a periodic task awaiting for the next dispatch  $(t_i^i)$ -COUNTER);

- MISSED\_DEADLINE:  $\tau_i$  has missed a deadline  $(d_j^i < \text{COUNTER})$ , in this case, the T\_Error label will be sent to the task:

- READY:  $\tau_i$  is initialized, preempted or dispatched  $(t_j^i \leq \text{COUNTER} < d_i^i)$ .

The BLOCKED or MISSED\_DEADLINE tasks are ignored and the SCHEDULER moves to  $\tau_{i+1}$ . Else, if  $\tau_i$  is asserted at the READY state, the SCHEDULER decides about the execution of  $\tau_i$  which moves to the RUNNING state.

At that level, the SCHEDULER can execute  $\tau_i$  with its whole capacity  $C_i$ , and then, it moves to handle other tasks. This can be sufficient for a non-preemptive scheduler of a set of periodic tasks. However, in our context, a task with a higher priority can become ready at any time. Similarly, a sporadic task with a higher priority can become ready by the reception of an invocation-event. These cases can lead to preempt the execution of the current running task, so they should be considered during the scheduling. The idea consists in interrupting the SCHEDULER task-loops and restarting the task-loop to consider new ready tasks as shown in Fig. 5. In the remainder of this section, we explain this algorithm through three steps achieving the execution of a given READY task  $\tau_i$ : time allocation, update task state and task activation. In addition, we include a sporadic task checking section added if S contains sporadic tasks.

Time allocation This step calculates the execution time of the current period for  $\tau_i$  and prepares an activation order that will be sent at the *task activation* step. We remind that  $\tau_i$  is the current ready task with the highest priority. We define the variable Allocated\_Time to compute the execution time. It can return the required time to achieve the execution in the current period, or it can return a part of the execution time, since  $\tau_i$  can be preempted by another task  $(\tau_{h < i})$  which is a new ready task with a higher priority. For this reason, in the calculation of the Allocated\_Time value, SCHEDULER

should always check the states of tasks with higher priorities. We define  $hp(i) = \{1 \dots i-1\}$  the set of indexes of tasks with higher priorities than  $\tau_i$ . Simply, the SCHEDULER checks  $t_{j+1}^{hp(i)}$  which are the next activation times of  $\tau_{hp(i)}$  by comparing COUNTER + Allocated\_Time value with all  $t_{j+1}^{hp(i)}$  value as shown in Algorithm 1 (lines 7–12). Three alternatives can be presented leading to fix different activation orders:

- 1. a complete execution time  $C_i$  is allocated, if  $\tau_i$  respects all  $t_{j+1}^{hp(i)}$  (COUNTER + Allocated\_Time  $< t_{j+1}^{hp(i)}$ ): T\_Completion\_Execution order

- 2. a preemption is imposed, if Allocated\_Time+COUNTER reaches an  $t_{j+1}^{h < i}$  of  $\tau_{h < i}$  (with  $h \in hp(i)$ ), thus (Allocated\_Time= $t_{j+1}^{h < i}$ -COUNTER) with two behav-

- 2.1. a preemption at the start time of the execution: T\_Dispatch\_Preemption order

- 2.2. a preemption in the middle of the execution: T\_Preemption order

- 3. a complete needed time is allocated when  $\tau_i$  is already preempted: T\_Preemption\_Completion order

Note that in the case of a preemption (alternative 2),  $\tau_i$  is preempted by  $\tau_{h < i}$  so the SCHEDULER restarts its task-loop from h to handle  $\tau_{h < i}$ , the new ready task with the highest priority as shown in Fig. 5.

Update task state At this point,  $\tau_i$  is considered at the RUNNING state, the SCHEDULER increments the COUNTER with the Allocated\_Time and updates the task array for the next activations. In the case of a preemption, the SCHEDULER conserves the task state and saves the executed time of  $\tau_i$  in order to complete the rest later. In the case of a non-preemption, the SCHEDULER prepares the task for a new period. A periodic task becomes  $(C_i, T_i, t^i_{j+1} = d^i_j, d^i_{j+1} = d^i_j + T_i)$ . In contrast, the parameters of a sporadic task cannot be predicted. the SCHEDULER has no values for its next activation or deadline. Currently, the sporadic task is viewed as  $(C_i, T_i, t^i_{j+1} \geq d^i_j, d^i_{j+1} = \infty)$  and it is ignored in the scheduling until the reception of a new notification.

Task activation The SCHEDULER sends to  $\tau_i$  its current order with the ACTIVATION\_i gate. It waits for a T\_Completion notification from  $\tau_i$  and then moves to  $\tau_{i+1}$  calculation. In the case of a missed deadline, the T\_Error label will be the last order sent to  $\tau_i$ , since it will be ignored in the rest of the simulation.

Sporadic task checking The global state of the set of tasks may change after each task activation (exchanging events and data, increase of the COUNTER, etc.). Particularly, the sporadic tasks may be activated by the invocation-events and may move to the READY state, so they should be considered in the scheduling with other periodic tasks. To this end, after each task activation, the SCHEDULER consults all the NOTIFICATION\_i gates. When receiving a notification at  $t_a^{\prime i}$ , the SCHEDULER applies the following steps:

- 1. marking  $t_a^{\prime i}$  equal to the current value of the COUNTER; 2. verifying  $t_a^{\prime i} \geq t_{a-1}^i + T_i$ : a notification can be ignored. Since we consider  $T_i$  as the minimal delay between two successive activations,  $\tau_i$  cannot be reactivated before  $t_a^i + T_i (t_{a+1}^{\prime i} \ge t_a^i + T_i);$

- 3. if (2) is verified, then,  $\tau_i$  moves to the READY state with these parameters  $(C_i, T_i, t_a^i = t_a^{\prime i}, d_a^i = t_a^i + T_i)$ . Thus,  $\tau_i$  is considered in the scheduling and served according to its priority:

- 4. if (2) is verified, then the SCHEDULER restarts the taskloop (return to  $\tau_1$ ): the SCHEDULER should recheck the set of tasks to find the new ready task with the highest priority, as shown in Fig. 5.

## 3.3 Communication

In our work, the tasks can be connected to each other to asynchronously exchange data or events. In the sporadic case, each task has at least one connection needed for its activation: the reception of an invocation-event activates the sporadic task that may move to the READY state.

The LNT processes communicate by bidirectional blocking rendezvous on gates. The LNT rendezvous on a gate allows the synchronization of n processes (several sending and receiving offers at the same time). In our case, we do not need such an advanced synchronization between processes. We consider the gates unidirectionally and we use only the synchronization between pair of processes (sender and receiver). The asynchronous inter-task connections cannot be mapped directly with synchronizations of the LNT gates since they denote blocking rendezvous. For this reason, we add an auxiliary process the CONNECTOR to represent the connection by means of the Ravenscar protected objects. CONNECTOR has two main gates (INPUT and OUTPUT) and a variable to save data/event.

In Listing 11, we give the CONNECTOR skeleton. The process behavior consists of three parts through an infinite loop whose body is a select statement to separate the sending and receiving data/event and the sporadic notification. Thus, only one operation can be executed at any time and the choice is solved by the possibility of communication on the gates.

Listing 11 LNT CONNECTOR skeleton

```

process CONNECTOR [

INPUT: LNT Channel Port,

OUTPUT: LNT_Channel_Port,

NOTIFICATION: LNT_Channel_Event]

(Queue_Size: Nat)

is

loop

select

-- inputs of event/data part

TNPUT

[]

output of event/data part

OUTPUT ()

[]

sporadic part

needed to notify SCHEDULER

when receiving a new event

NOTIFICATION ()

end select

end loop

end process

```

Each connection between two TASKs is mapped to a CONNECTOR synchronized (rendezvous point) with the sender on INPUT and the receiver on OUTPUT which assumes the atomicity of the two operations (sending and receiving) and the TASK unicity in awaiting at any time (respectively, on the INPUT and the OUTPUT gates).

Data are saved and kept until the next reception. Each time a new input is received, the last one is overwritten. In contrast, events are queued in an LNT list with a defined size. We use non-blocking FIFO, in which the new incoming input overwrites the previous events in the case of an overflow. In the case of an empty FIFO, the TASK receives an EMPTY message without blocking.

Since we consider a special invocation-event for the sporadic task activation, we add a third gate to the CONNECTOR process (named NOTIFICATION) to be synchronized with the SCHEDULER. We use this gate to notify the SCHEDULER of every new reception; thus, it considers the concerned task in the scheduling.

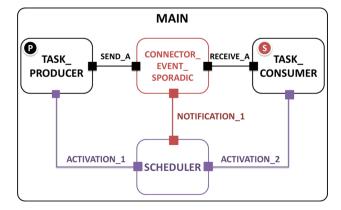

## 3.4 Composition and synchronization

We complete the proposed LNT mapping with two mandatory steps: composition and synchronization. All described LNT processes should be structured (connected) to form the main system. This step is ensured by the LNT par composition statement for the parallelism and the synchronization (global and interface) of the TASK, CONNECTOR and SCHEDULER processes. Thus, we assemble the whole system within the MAIN process.

Note that a set of the LNT types and channels are used for the TASK-CONNECTOR, CONNECTOR-SCHEDULER and TASK-SCHEDULER synchronizations. For example, we include in Listing 12 the type and channel for the TASK-SCHEDULER synchronization.

Listing 12 TASK-SCHEDULER: LNT type and channel

```

type LNT_Type_Dispatch is

T_Dispatch_Completion,

T_Dispatch_Preemption,

T_Preemption,

T_Preemption_Completion,

T_Completion,

T_Error,

T_Stop

end type

channel LNT_Channel_Dispatch is

(LNT_Type_Dispatch)

end channel

```

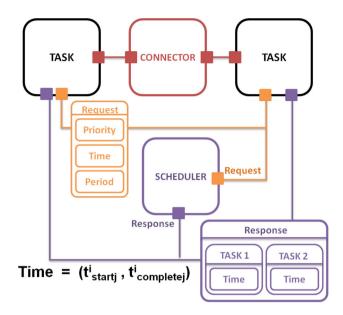

For further explanations, we include an example of a task model whose MAIN process is included in Listing 13 and graphically presented in Fig. 6. The initial task model  $(\tau_1, \tau_2)$  consists of a periodic task connected to another sporadic task running on a scheduler (*Producer–Consumer* system). The obtained LNT specification contains five processes synchronized in the MAIN process. The par composition is globally used for the following synchronizations:

- The TASK\_CONSUMER and CONNECTOR are synchronized on the RECEIVE A gate;

- The CONNECTOR and TASK\_PRODUCER are synchronized on the SEND\_A gate;

- The CONNECTOR and SCHEDULER are synchronized on the NOTIFICATION\_1 gate;

- The TASK\_CONSUMER, TASK\_PRODUCER and SCHEDULER are synchronized on the ACTIVATION\_1 and ACTIVATION 2 gates.

Fig. 6 Producer-consumer: LNT graphical MAIN

#### **Listing 13** *Producer–consumer*: LNT code MAIN

```

process MAIN [

ACTIVATION_1: LNT_Channel_Dispatch,

ACTIVATION 2: LNT Channel Dispatch,

NOTIFICATION_1: LNT_Channel_Event,

SEND_A: LNT_Channel_Port,

RECEIVE_A: LNT_Channel_Port

lis

par

ACTIVATION 1. RECEIVE A ->

TASK CONSUMER[ACTIVATION 1, RECEIVE A]

NOTIFICATION 1. SEND A. RECEIVE A->

CONNECTOR[SEND_A, RECEIVE_A, NOTIFICATION_1]

SEND_A, ACTIVATION_2->

TASK_PRODUCER[ACTIVATION_2, SEND_A]

ACTIVATION_1, ACTIVATION_2, NOTIFICATION_1 ->

SCHEDULER[ACTIVATION_1, ACTIVATION_2,

NOTIFICATION_1]

end par

end process

```

## 3.5 Discussion

The obtained LNT specification (the set of the LNT definitions composed in the MAIN process) represents a formal executable semantics for a real-time task model, where the TASKs are connected through the CONNECTORs and scheduled by the SCHEDULER. This mapping is flexible enough to support various task models with minor changes: periodic/sporadic tasks, independent/communicating tasks and preemptive/non-preemptive tasks.

In addition, the real-time features are modularly designed which increases the extensibility of the mapping: each feature can be separately completed or extended. For example, the TASK can be easily enriched with more behavior that can be specified in a separate LNT process or function and just called within the TASK skeleton.

Similarly, the scheduling mapping can be extended with other scheduling protocols since we specify an explicit SCHEDULER that encapsulates all the scheduling calculations. For example, we have developed the EDF (Earliest Deadline First) based on unfixed priority scheduling. The SCHEDULER skeleton is conserved. The modifications can be limited in the *operational part*, mainly, the *time allocation* operation. The other manipulations (*update task state*, *task activation* and *sporadic task checking*) can be conserved, and thus the TASK and CONNECTOR processes need no changes.

## **4 Model transformation**

In this section, we discuss the applicability of our LNT mapping as a software engineering practice. We aim at integrating the formal verification in a model-driven process based on

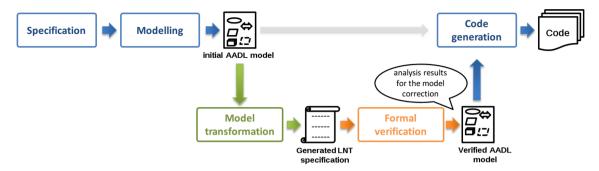

Fig. 7 AADL model-based development process

the AADL language. A basic proposal was discussed in [43], where we presented a transformation from AADL into LNT about the periodic threads with a preemptive RM scheduler. In this paper, we propose to refine this approach and extend the scope of our work.

As simply depicted in Fig. 7, throughout the development process, the system representation takes different forms (written specification, architectural model, source code) on many phases (specification, modeling and code generation). During the modeling phase, the formal verification of the AADL model seems useful and complementary to traditional syntactic and semantic analyses. To this end, we define the *AADL2LNT* model transformation from the initial AADL model into an LNT specification based on the proposed LNT mapping. This transformation achieves the automatic generation of an LNT specification compliant with the CADP toolbox and ready for verification.

In the remainder of this section, we develop our AADL subset. Then, we describe the *AADL2LNT* transformation rules with a discussion about the novelty and the improvements compared to our previous work [43]. Finally, we describe our implementations allowing the definition of a tool-chain for a development process based on the AADL language.

## 4.1 AADL subset

The AADL language describes different concepts of realtime embedded systems with a rich semantics detailed in its standard [1]. The language covers many important aspects (timing requirements, fault and error behaviors, time and space partitioning, safety properties, etc.) that cannot be wholly analyzed in one approach.

According to our verification purposes, we define an AADL subset whose elements are depicted in Fig. 8. Moreover, the consideration of the Ravenscar profile requires some additional restrictions applied at the model level, meaning that the AADL subset should be compliant with the profile. Mainly, the profile claims that the threads are either spo-

Fig. 8 High-level view of AADL2LNT transformation

radic or periodic and they are schedulable according to the Rate Monotonic analyses such as the *exact schedulability* test [37]: for a synchronous set of tasks S of n independent and periodic tasks, if  $U = \sum_{i=1}^{n} \frac{C_i}{T_i} \le n \left(2^{1/n} - 1\right) \approx 0.69$ , then S is RM-schedulable.

In our work, we aim at defining an executable formal semantics of the AADL model viewed as a set of communicating tasks in a real-time context. This abstraction allows different alternatives of verification, such as the schedulability analysis, the thread execution simulation and the verification of communication properties.

At the model level, we consider the system as a set of threads bound to a monoprocessor and communicating through the port connections. We do not support either AADL shared access or AADL flows/modes. The model is completed by a set of standard properties

attributed to different components. We support the following lists:

- properties specifying the constraints for the softwarehardware binding like the Actual\_Processor\_ Binding property, which can list only one processor;

- properties specifying the temporal and scheduling information such as Dispatch\_Protocol (periodic or sporadic), Compute\_Execution\_Time, Period, Input\_ Time (Start\_Time for all thread ports) and Output\_ Time (Completion\_Time for all thread ports);

- properties specifying the information for the port connections like Queue\_Processing\_Protocol (FIFO),

Queue\_Size, Overflow\_Handling\_Protocol (drop oldest) and Dequeue\_Protocol (one item).

In the AADL language, the system is modeled through a set of nested components whose top-level is the system component, as shown in Fig. 2 and Table 3.

The system implementation mainly contains: a set of subcomponents that can be data, process, processor or device; a set of connections to declare port connections of processes and devices; and a set of properties in which the Actual\_Processor\_Binding property is used to bind the processor with the processes.

The AADL2LNT transformation can be applied on an *instantiable* AADL system, which means that the model is successfully analyzed (syntactically and semantically) and can be completely bound, as when all threads are bound to the processor.

## 4.2 Transformation rules

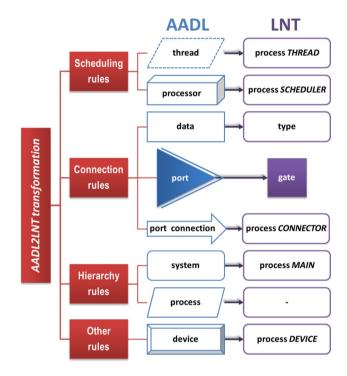

Model transformation plays a crucial role in MDE for various goals (modeling, optimization and analysis). It is the mechanism of generating a target model based on information extracted from a source one. This operation is based on our LNT mapping and requires a set of new LNT definitions to cover the considered AADL subset. The *AADL2LNT* transformation is described with a set of correspondence rules between AADL and LNT (summarized in Tables 1, 2, 3 and 4).

Basically, the LNT mapping (Sect. 3) is used as follows: we translate each AADL thread component into a TASK process; we represent the AADL ports by the LNT gates; the AADL port connections are mapped through the CONNECTOR processes; and the AADL processor becomes the SCHEDULER process. Figure 8 graphically represents these basic transformation rules, which are applied through four steps, respectively, developed in the rest of this section.

#### 4.2.1 Scheduling rules

The execution and scheduling rules concern the thread and processor components.

Thread rule The AADL thread is a schedulable unit that can be concurrently executed with other threads. Each thread executes a set of sequential instructions. It is declared within a process component, and it is bound to a processor component to be scheduled.

The thread component becomes the TASK process described in Sect. 3.2.1. As illustrated in Table 1, the TASK process takes the thread implementation name prefixed by "THREAD\_" and declares the ACTIVATION default gate to be synchronized with the SCHEDULER process.

The supported standard properties are used to specify the temporal parameters of the thread, as follows: the Dispatch\_Protocol property represents its dispatch model; the Period property represents its period  $T_i$ ; and the Compute\_Execution\_Time property represents its capacity  $C_i$ .

In the AADL language, the dispatch semantics is given for the standard dispatch protocols (periodic, sporadic, aperiodic, timed, hybrid, and background threads). Since we consider a Ravenscar compliant model, we support periodic and sporadic dispatch models, as described in the AADL standard:

- periodic threads: they are periodically dispatched at time intervals of the specified Period property value.

- sporadic threads: they are activated as the result of an event/event data (invocation-event) arriving at an event/event data port of the thread. The time interval between two successive dispatch requests will never be less than the associated Period property value.

As described in Sect. 3.2.1, the thread dispatching is ensured by the SCHEDULER through the defined activation orders (T\_Completion, T\_Dispatch\_Preemption, T\_Preemption\_Completion, T\_Dispatch\_Completion and T\_Preemption).

The dynamic semantics for an AADL thread is defined using a hybrid automaton (thread scheduling and execution states automaton) included in Fig. 9. The TASK mapping covers an important part of the AADL thread semantics of its dispatching, its scheduling and its execution. Compared to the standard thread hybrid automaton, the proposed state automaton of Fig. 3 excepts the awaiting states (shared resources, subprogram calls and background thread), that are non-covered by our work since we do not support either subprogram components or shared resources. In addition, the standard defines a sus-

Table 1 Scheduling rules

```

AADL

LNT

AADL thread transformation rule

process THREAD_T_IMPL [

ACTIVATION: LNT_Channel_Dispatch]

loop select

select

thread T

ACTIVATION (T_Dispatch_Preemption)

properties

Г٦

Dispatch Protocol => Sporadic/Periodic;

ACTIVATION (T Preemption Completion)

Compute_Execution_Time => min .. C_i; Period => T_i;

ACTIVATION (T_Dispatch_Completion)

ACTIVATION (T_Preemption)

thread implementation T.Impl

end select;

ACTIVATION (T_Complete)

end T.Impl;

ACTIVATION (T_Error)

ACTIVATION (T_Stop)

end select end loop

end process

AADL processor transformation rule

process SCHEDULER [

processor the_processor

ACTIVATION_1: LNT_Channel_Dispatch,

properties

ACTIVATION_K: LNT_Channel_Dispatch,

Scheduling Protocol => RMS;

INCOMING_EVENT_1: LNT_Channel_Event,

end the_processor;

INCOMING_EVENT_N: LNT_Channel_Event]

```

Fig. 9 AADL thread hybrid automaton [1]

pended AWAITING DISPATCH state for threads when completing the execution of the current dispatch, which corresponds to the BLOCKED state in the proposed LNT mapping.

Processor rule The processor is a hardware component that ensures the scheduling and execution of the threads. As shown in Table 1, the processor component becomes the SCHEDULER process developed in Sect. 3.2.2. Every link between the processor and a thread corresponds to an ACTIVATION\_i gate declaration in the SCHEDULER process. In the case of a sporadic thread, the corresponding NOTIFICATION\_i gate is also declared.

The task model  $S = \{\tau_1, \ldots, \tau_k\}$  with  $\tau_i = (C_i, T_i)$ , is extracted from the AADL model for the SCHEDULER generation. We distinguish different information required for the scheduling: the number of thread instances (k); the number of sporadic thread instances n; the set of values of each thread properties  $(T_{1...k}, C_{1...k})$  to compute the hyperperiod  $H(\tau_{1...k})$ , assign each thread priority and encode the task LNT array S of the *initialization part* (Sect. 3.2.2, Listing 10).

## 4.2.2 Connection rules

The thread components may declare (data, event or event data/in, out or in out) ports to be in interaction with other components. A port connection allows the transfer of data and/or event between two components, explicitly declared between two ports at process and system levels. The connection rules concern then the AADL ports (typed with

Table 2 Connection rules

```

LNT

AADL

AADL data transformation rule

type LNT_Type_Data is AADLDATA, EMPTY end type

data D

channel LNT_Channel_Port is

end D:

(LNT_Type_Data)

end channel

AADL port transformation rule

process Thread_TH [ACTIVATION: LNT_Channel_Dispatch,

PORT_A: LNT_Channel_Port] is

var A : LNT_Type_Data in

A := EMPTY;

thread TH

features

A : in event data port T;

ACTIVATION (T_Dispatch_Completion);

properties

PORT_A (?A);

Dispatch_Protocol => Sporadic/Periodic;

ACTIVATION (T_Dispatch_Preemption);

Period \Rightarrow T_i:

PORT_A (?A);

end TH:

[] ..

end select:

ACTIVATION (T_Completion)

end process

AADL port connection transformation rule

process[system] implementation P.Impl

process PERIODIC_DATA_CONNECTOR

subcomponents

A: thread[process] AA; B: thread[process] BB;

[INPUT: LNT Channel Port

connections -- data port

OUTPUT: LNT_Channel_Port]

AB: port A.a1 -> B.b1;

process[system] implementation P.Impl

process PERIODIC EVENT CONNECTOR

subcomponents

[INPUT: LNT_Channel_Port, OUTPUT: LNT_Channel_Port]

A: thread[process] AA; B: thread[process] BB;

connections -- event [event data] port

(Queue Size: Nat)

AB: port A.a1 -> B.b1;

process[system] implementation P.Impl

process SPORADIC_EVENT_CONNECTOR

subcomponents

[INPUT: LNT_Channel_Port,

-- sporadic thread

OUTPUT: LNT_Channel_Port,

A: thread[process] AA; B: thread[process] BB;

NOTIFICATION : LNT_Channel_Event]

connections -- event [event data] port

(Queue_Size: Nat)

AB: port A.a1 -> B.b1;

```

the data components) and their connections, which are declared at the process and system levels.

Data rule The data component is mapped into a generic LNT type. For a full abstraction, we use a generic type for all data and event exchanging (label AADLDATA as included in Table 2). A corresponding channel is also added to allow the communication. At this level, this representation is sufficient to draw connections between the threads since we do not handle the AADL data content.

Port rule The AADL ports are declared in the thread component for the transfer of control and data. They are transformed into the LNT gate declarations. Since they are

bidirectional, the LNT gates can represent *in* and *out* ports. In addition, we complete the behavior of the TASK skeleton of Listing 9 with an *initialization* part using the LNT var statement. As shown in Table 2, for each declared port, named A, we proceed as follows:

- a gate declaration PORT\_A:LNT\_Channel\_Port is added;

- a variable A: LNT\_Type\_Data is declared and initialized in the *initialization* part;

- a corresponding communication is added as follows:

```

for out port: PORT_A (!A)

```

- for in port: PORT\_A (?A)

Fig. 10 AADL semantics port connections

Note that data, event or event data ports are exactly mapped at the THREAD\_\* level, while the difference between these types (reception, queuing, etc.) is assumed by the communication mechanism using the CONNECTORS.

Port connection rule The port connections are ensured through the synchronizations of the CONNECTOR instances (Sect. 3.3) allowing unidirectional communications, so we consider only 1-to-1 connections with no *in out* ports. Each port connection becomes a CONNECTOR instance. The CONNECTOR should be synchronized on the INPUT and OUTPUT gates between two TASKs equivalent, respectively, to the threads of *in* and *out* ports.

In the AADL language, the port connection declarations follow the containment hierarchy of the threads, processes and systems or of devices and systems, as shown in Fig. 10. The CONNECTOR process represents the semantics port connection abstracting all the port connection declarations that follow the component containment in the instantiated system from an ultimate source (out port of a thread or a device) to an ultimate destination (in port of a thread or a device). Thus, the connection ①, ② or ③ of Fig. 10 is similarly transformed into a CONNECTOR instance, despite the difference in the declaration-level.

In our work, we consider the AADL asynchronous connections whose determinism is ensured by the Ravenscar constrained protected object as developed in Sect. 3.3. In the AADL semantics port connection, the content of incomings is frozen during the thread execution: the port variable content is not affected by the arrival of new incomings. Data and events arriving through *in* ports are available to the thread at a specified input time, fixed by the Input\_Time property. This communication model is assumed in the LNT specification through the INPUT synchronization (reading the port content) between the CONNECTOR and the THREAD\_\* corresponding to the thread of *in* port. According to our LNT mapping, the INPUT rendezvous is fixed at the start time of each period equivalent to the Start\_Time value of

the Input\_Time property. After the INPUT rendezvous, any new data or event arriving becomes available only at the next start time. In addition, the AADL port output is transferred to the other components at an output time specified by the Output\_Time property. The transfer of data or event corresponds to the OUTPUT synchronization with the thread of out port, which is fixed at the completion time of each period equivalent to the Completion\_Time value of the Output\_Time property.

According to the port type (data, event or event data) and the thread Dispatch\_Protocol property value (periodic or sporadic), we generate one of three CONNECTOR types, as included in Table 2. In the case of a data port and a periodic thread, the data port connection is mapped by a simple CONNECTOR without queuing or sporadic notifications. When exchanging events, we use a CONNECTOR with an input list for the event queuing, that implements the supported set of AADL properties. Finally, the NOTIFICATION gate is added in the case of a sporadic thread.

## 4.2.3 Hierarchy rules

The AADL components are hierarchically structured in both the process (a set of thread subcomponents) and the system components.

Process rule The process component represents a protected virtual address space that can be ignored in verification. So the processes have no equivalent in the obtained LNT specification and its dispatch semantics is omitted. The AADL model may contain a process with a composition of the threads. In this case, the corresponding THREAD\_\* instances are directly added in the MAIN process.

System rule The system component becomes the LNT MAIN process. This generation corresponds on the LNT synchronization and composition phase developed in Sect. 3.4. The MAIN generation can be summarized in three steps:

- Preparation of the list of thread instances: each process subcomponent corresponds to one or more of THREAD \* instances.

- \*\_CONNECTOR synchronizations: for each port connection, we create one \*\_CONNECTOR instance. We use the AADL connection name, prefixed by "SEND\_" and "RECEIVE\_" to represent two gates (e.g., the port connection Connect\_AB, of the example of Table 3, is represented by the SEND\_AB and RECEIVE\_AB gates). These gates are used in the synchronization between the THREAD\_\* and \*\_CONNECTOR instances as follows:

- the RECEIVE\_\* synchronization represents the reading of the port content by the thread of *in* port.

Table 3 Hierarchy rules

```

LNT

AADL

AADL system transformation rule

ACTIVATION_1: LNT_Channel_Dispatch,

system PC

ACTIVATION_2: LNT_Channel_Dispatch,

end PC;

SEND_AB: LNT_Channel_Port,

RECEIVE_AB: LNT_Channel_Port

system implementation PC.Impl

INCOMING_EVENT_2: LNT_Channel_Event] is

subcomponents

ACTIVATION_1,SEND_AB ->

Data Exp: data Alpha;

THREAD_P_IMPL[ACTIVATION_1, SEND_AB]

A: process AA.Impl;

B: process BB. Impl;

CPU: processor the_processor;

SEND_AB, RECEIVE_AB, INCOMING_EVENT_2 ->

connections

Event_Port[SEND_AB, RECEIVE_AB, INCOMING_EVENT_2](3)

AB: port A.A1 -> B.B1;

properties

ACTIVATION_2, RECEIVE_AB ->

THREAD_C_IMPL[ACTIVATION_2, RECEIVE_AB]

Actual_Processor_Binding => (reference (CPU))

applies to A:

Actual_Processor_Binding => (reference (CPU))

ACTIVATION_1, ACTIVATION_2, INCOMING_EVENT_2->

SCHEDULER

applies to B;

end PC.Impl;

[ACTIVATION_1, ACTIVATION_2, INCOMING_EVENT_2]

end par

end process

```

Table 4 Other rules

```

LNT

AADL

AADL device transformation rule

process Device_D [PORT_A: LNT_Channel_Port,

PORT_B: LNT_Channel_Port]

var A: LNT_Type_Data, B: LNT_Type_Data in

device D

A := AADLDATA; B := EMPTY;

features

loop select

A: out event port;

PORT_A (?A)

B: in event port;

Г٦

end D:

PORT B (!B)

end select end loop

end var

end process

```

- the SEND\_\* synchronization represents the transfer of the data or event from the thread of *out* port.

- Global composition: all THREAD\_\*s are synchronized with the SCHEDULER on ACTIVATION\_i gates. Similarly, all \*\_CONNECTORs are synchronized with the SCHEDULER on the NOTIFICATION i gates.

For the system transformation illustration, this rule is applied on an AADL simple *Producer–Consumer* model (two AADL threads running on one processor to exchange events), which is included in Table 3.

## 4.2.4 Other rules

At this level, the LNT mapping is used in the definition of the *AADL2LNT* transformation with minor changes. In addition, the transformation can be completed by rules concerning other AADL components such as devices.

Device rule The thread components can communicate with devices via ports. We do not consider the internal device behavior, but we provide a simple LNT specification sufficient for the thread-device port connections.

The device becomes an LNT process prefixed by "DEVICE\_". Unlike THREAD\_\*, DEVICE\_\* has no activation gate, but its port declarations are similarly mapped. The DEVICE\_\* behavior consists simply of a loop-select statement comprising the PORT\_\* communications as given in Table 4. The AADL device port connections are similarly mapped as the thread port connections through the CONNECTORs at the MAIN level.

## 4.3 Discussion

The description of a model transformation based on more generic LNT definitions was the purpose of our previous work published in [43] and depicted in Fig. 11 (the *Producer*–

Fig. 11 Old LNT mapping

consumer example). Mainly, the scheduling was differently ensured between the THREAD \*s and SCHEDULER. Compared to the actual SCHEDULER, the old one was generically defined to execute any task model: it has no information about the task model (no initialization part). Using only two gates (REQUEST and RESPONSE), the SCHEDULER gives a response according to a received request without a global view of the task model: the execution advances by exchanging time  $[t_{start_j}^i,\,t_{complete_j}^i]$  between the SCHEDULER and THREAD\_\*s. Each process (THREAD\_\* and SCHEDULER) has a local COUNTER. Each THREAD\_\* requests time for its execution  $[(t^i_{start_j}, t^i_{complete_j}), T_i, i]$  and waits for the SCHEDULER response. While the SCHEDULER computes start and completion execution time based on the tasks priorities and the advancement of its COUNTER. The THREAD\_\* manages its own temporal calculations (execution times, preemptions, etc.). At the reception of a response, the THREAD \* updates its COUNTER, executes the allocated time and then prepares a new request.

This first proposition brings generic SCHEDULER and THREAD\_\* constructions, favoring the reuse of our mapping. However, in the case of large systems, this mapping rapidly led to the state explosion problem during the analysis phase: the system state space may become very large, or even infinite, that cannot be explored with limited resources of time and memory (see Sect. 5.5). In this paper, we redefine the SCHEDULER and THREAD\_\* processes and their synchronizations in order to avoid and reduce this problem. We opt to get rid of the heavy requests and responses by abstracting the SCHEDULER-THREAD\_\* exchanges with a set of activation orders to restrict the enumerations in the analysis phase. In addition, we eliminate the time counters from

the THREAD\_\*s and maintain a unique counter of the whole system within the SCHEDULER. Thus, useless calculations are removed and time is managed only by the SCHEDULER.

For the same reasons, some restrictions were applied on the considered AADL subset concerning mainly the port connection rules. The *in out* ports and n-to-n connections can be supported in the *AADL2LNT* transformation since the LNT language provides bidirectional gates and n-to-n synchronizations. However, the resulting formal specifications rapidly explode, especially with highly connected models.

With these refinements, the resulting state spaces are significantly reduced at the analysis phase. Thus, we provide a scalable solution (see evaluation in Sect. 5.5) without restricting our purposes (preemptive priority-based scheduling, asynchronous communication, etc.).

In another direction, we aim to enrich the communication mapping by considering the content of exchanges. The *AADL2LNT* transformation is completed by the consideration of the AADL Behavior annex [2], which is used to specify the behavior handling inputs and outputs within the thread components. The mapping of the Behavior annex requires a new abstraction level where the thread behavior (described as a local state transition machine) and data content are considered in a new AADL subset. The Behavior annex transformation with the set of new rules about AADL thread and data components can be found in [42].

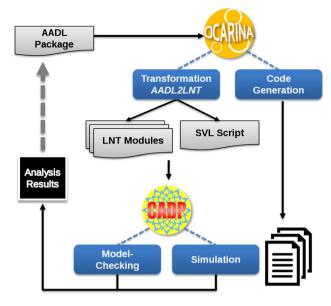

#### 4.4 Tool-chain

The model transformation description being defined, we reach the implementation phase to provide an automatic generation of the LNT specification from a given AADL model. A detailed description of our implementations can be found in [44]. In this section, we briefly describe the obtained tool-chain, depicted in Fig. 12, based on Ocarina [35] for architectural modeling and CADP [22] for formal verification:

- Ocarina<sup>5</sup> is an open-source tool suite for AADL modeling developed since 2004 and deployed on GitHub under the OpenAADL project. Ocarina can be used as a standalone compiler for the AADL language with the support of some annexes ARINC653, EMV2 and REAL. The tool suite is appropriate for an MDE approach since it provides basic analysis (syntactic and semantic), advanced model manipulations, formal verification (Petri nets) and code generation (toward the AADL runtime PolyORB-HI/Ada and C).

- CADP is a toolbox for the design and verification of concurrent systems, developed since 1986. It is avail-

<sup>&</sup>lt;sup>5</sup> https://github.com/OpenAADL/ocarina.

Fig. 12 Ocarina-CADP tool-chain

able with both academic and commercial licenses.<sup>6</sup> In addition to LNT, it supports many other input languages such as LOTOS, FSP and EXP. It also provides a scripting language SVL (Script Verification Language) [20] for the description of analysis scenarios. The toolbox offers a comprehensive set of tools for specification, interactive simulation, verification (model-checking, equivalence checking, etc.), performance evaluation, etc. To deal with complex systems, CADP provides a set of verification techniques such as the reachability analysis, on-the-fly verification and distributed verification.

## 4.4.1 Ocarina extension

The proposed *AADL2LNT* transformation is integrated within the Ocarina tool suite. The Ocarina compiler is designed with a modular architecture distinguishing three parts: a central library (a set of routines), the frontend (for model analyses) and the backend (for model manipulations and generations). Different model manipulations are handled using the ASTs (Abstract Syntax Tree) which are the internal representation of models (AADL, annexes and other languages).

Generally described, the *AADL2LNT* model transformation is implemented in the Ocarina backend. We assume that the AADL model should be successfully analyzed on the frontend and then transformed into an AADL AST. We do not use model transformation languages for our generation. We

directly apply the transformation rules on the AADL AST (without meta-model) to form a corresponding LNT AST. Then, this AST is scanned in order to produce the source code files (\*.lnt). In addition to the LNT modules, a script file (demo.svl) is also generated, containing a set of operations specified in the SVL language to orchestrate the analysis phase. This file is directly generated for each AADL system (without an SVL AST).

## 4.4.2 CADP formal verification

The formal verification allows designers to prove that a system satisfies its requirements. The verification techniques are applied on an abstract mathematical model of the system (system state space), built according to the considered specification language semantics. In addition, the verified properties (system requirements) should be specified as graphs or temporal logic properties, using specific formalisms. Then, the verification can be performed by the analysis tools. In our work, we mainly deal with the model-checking technique, which consists in checking whether the system satisfies a given property specified with a temporal logic.

Based on the Ocarina generated outputs, a formal verification phase can be performed by the CADP toolbox using the SVL script, which guides the compilation of the LNT specification and the verification of a set of behavioral and temporal properties. The generated LNT specification is firstly compiled into an LTS (Labeled Transition System) to be explored using the CADP model checkers. To automate this operation, we include the verified properties within the SVL script. Using the SVL property statement, we define a set of generic properties to verify some requirements of real-time systems such as deadlock, schedulability, communication problems (e.g., data loss) and queuing problems (e.g., overflow of buffers).

We thereby drew a tool-chain providing an automatic and transparent verification of the AADL model. The transformation is carried out by the Ocarina command line, then, the generated SVL script is simply invoked to begin the verification phase with the CADP toolbox. Finally, the analysis results help designers in AADL model correction and improvement. This operation can be iteratively applied after each modification, throughout the development process, until the generation of the final application.

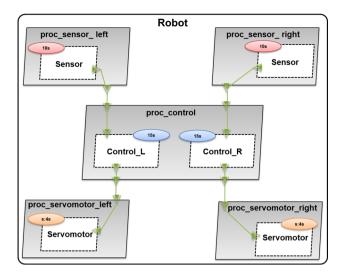

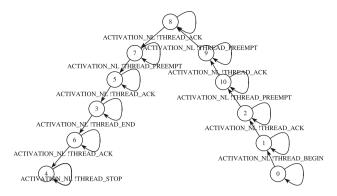

# 5 Experiments