#### Photodiodes and Image Sensors on Mechanically Flexible Ultra-Thin Silicon Chips-in-Foil

Von der Fakultät für Ingenieurwissenschaften Abteilung Elektrotechnik und Informationstechnik der Universität Duisburg-Essen

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

genehmigte Dissertation

von

Georgios C. Dogiamis aus Athen

Gutachter: Prof. Bedrich J. Hosticka, Ph.D. Gutachter: Prof. Dr. rer. nat. Roland Schmechel Tag der mündlichen Prüfung: 7. Juli 2014

### Preamble

This work was composed during my employment as a scientist at the chair Electronic Devices and Circuits (EBS) of the University of Duisburg-Essen. The presented results form part of the investigations conducted within the scope of the FLEXBild research project, which was founded by the German Research Foundation (DFG) for four consecutive years. The project has been successfully completed in collaboration with the Institute of Materials in Electrical Engineering, Chair 1 (IWE 1) of the RWTH Aachen University.

Here, I would like to express my deepest gratitude to my doctoral advisor and mentor, Prof. Bedrich J. Hosticka, Ph.D., for his support, encouragement, guidance and mainly for the invaluable technical discussions we have held. His enthusiasm and his ability to provide solutions to any challenging technical question has been my motivation throughout all these years conducting research by his side.

Moreover, I would like to thank the EBS Head, Prof. Dr. rer. nat. Anton Grabmaier for his productive criticism on this work and for creating such an exciting environment to conduct research. The same goes to Dr.-Ing. Reinhard Viga, who has assisted me in a multifaceted way in the completion of this thesis.

In addition, I would like to cordially thank Prof. Dr. rer. nat. Roland Schmechel for his readiness to become my second advisor.

I would like to cordially thank Prof. Dr. rer. nat. Wilfried Mokwa for his continuous support during this thesis. Here, I would like to thank all employees of IWE 1 in RWTH Aachen, who have played a major role in the thinning and encapsulation process of the ultra-thin chips employed in this work. Similarly, special thanks goes to all employees of the Optical Sensors and Systems (OSS) department of the Fraunhofer Institute for Microelectronic Circuits (IMS) in Duisburg, who provided valuable insight on various aspects during the design up to the fabrication of the CMOS chips employed in this work.

Special thanks go to Dr.-Ing. Okan Ecin and Unmesh Ghoshdastider, M.Sc. for their continuous support and for their willingness to proof-read the entire thesis.

I would like to express my gratitude to all scientists, students and staff of the chair Electronic Devices and Circuits (EBS) for all the fruitful discussions we had and suggestions they made throughout this work.

Last but not least, I would like to thank my family and especially my sister for her patience and encouragement throughout these invaluable experience in Germany.

### Zusammenfassung

CMOS-Bildsensoren haben in den letzten zwei Jahrzehnten enorme technologische Fortschritte erfahren und sich als eine wettbewerbsfähige Alternative gegenüber CCD-Bildsensoren auf dem Markt etabliert. Reduziert man die Chipdicke von CMOS-Bildsensoren von normal 725  $\mu$ m auf  $\leq 30$   $\mu$ m, erhält man mechanisch flexible Bildaufnehmer. Gewölbte CMOS-Bildsensoren würden für die optische Wahrnehmung völlig neue Möglichkeiten eröffnen (wie z. B. bei Insektenaugen). Betrachtet man die auf dem Chip integrierten Bauelemente und Schaltungen unter mechanischen Spannungen, stellt man fest, dass ihre elektrischen und optoelektronischen Eigenschaften von der ausgeübten mechanischen Spannung beeinflusst werden. Für den technischen Einsatz ist eine vom mechanischen Zustand des Bildsensors unbeinflusste Funktion erforderlich. Der Einfluss von mechanischer Spannung auf die Bauelemente- und Schaltungs-Charakteristiken und seine Minimierung bzw. Kompensation sind daher von besonderem Interesse.

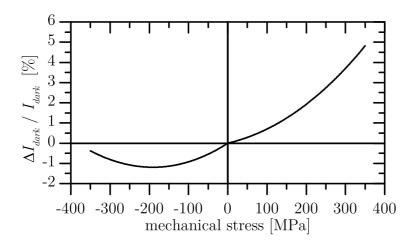

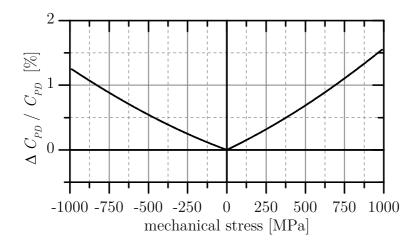

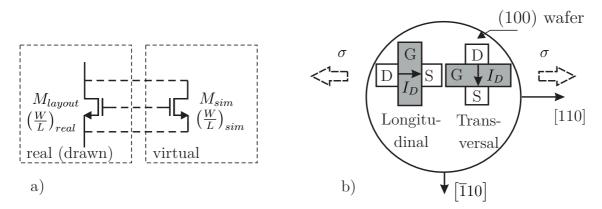

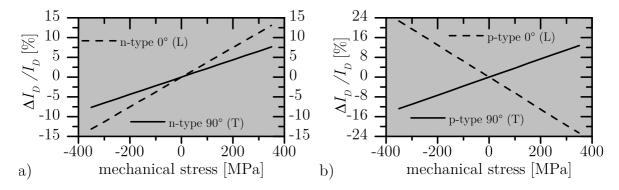

In dieser Arbeit wurden die optischen und elektrischen Eigenschaften von passiven und aktiven Bauelementen, sowie integrierten Schaltungen auf monokristallinen gedünnten flexiblen Siliziumchips unter mechanischen Spannungen untersucht. Der Einfluss von mechanischen Spannungen auf optische Eigenschaften (spektrale Lichtempfindlichkeit, Dunkelstrom und elektronisches Rauschen) einzelner p-n-Übergangbasierter Photodioden und Bildsensorarrays auf (100)-Siliziumwafern wurde theoretisch modelliert und experimentell charakterisiert. Weiterhin wurden die elektrischen Eigenschaften (Ladungsträgerbeweglichkeit, Schwellenspannung, 1/f Rauschen) von MOS-Feldeffekttransistoren in Bezug auf mechanischen Spannungen charakterisiert und ihre Abhängigkeit von der Orientierung zur Kristallorientierung des Substrats untersucht. Integrierte Schaltungen, wie Bandgap-Referenzspannungsquellen, Operationsverstärker und SC-basierte Schaltungen wurden unter mechanischen Spannungen theoretisch betrachtet, entworfen, gefertigt und experimentell charakterisiert.

Mit Hilfe des in dieser Arbeit vorgeschlagenen und eingesetzten Simulationskonzeptes, ist die Schaltungssimulation der obengenannten Abhängigkeiten möglich. Dadurch hat der Schaltungsentwickler die Möglichkeit Schaltungskonzepte zur Kompensation oder Minimierung der von der mechanischen Spannung hervorgerufenen Einflüsse zu simulieren. In dieser Hinsicht werden Schaltungskonzepte und Design-Regeln präsentiert, die den Einfluss von mechanischen Spannungen auf Bildsensorchips berücksichtigen und minimieren.

Im Rahmen dieser Arbeit wurde darüber hinaus ein mechanisch flexibler Bildsensorchip entworfen, simuliert und gefertigt, dessen Betrieb unabhängig von der ausgeübten mechanischen Spannung ist. Der ultra-dünne 20 µm Bildsensorchip ist geeignet auf zylindrisch gewölbte Oberflächen aufgebracht zu werden und erlaubt die Aufnahme raumrichtungsselektiver optischer Informationen im Sinne eines Panoramablicks.

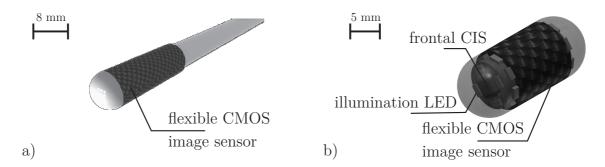

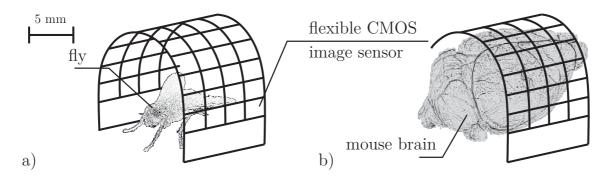

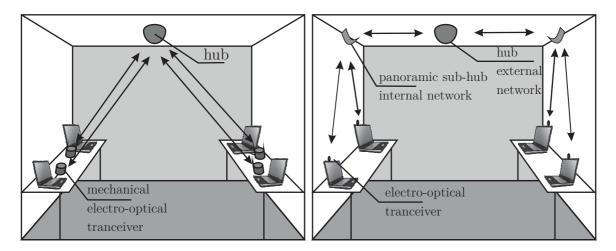

CMOS image sensors (CIS) have experienced the last two decades tremendous technological advances rendering them a viable alternative to charged couple devices (CCDs) not only in high volume applications but also in applications which require high spatial and temporal resolution, high dynamic range, low noise or high sensitivity levels. CISs are employed due to their increased chip thickness (ca. 750 µm) solely in the traditional planar image acquisition. If the chip thickness could be reduced down to or less than 30 µm, the silicon chips would become mechanically flexible. Such flexible CISs could substantially extend the application spectrum of image sensors in non-conventional imaging systems (e.g. imitating insect vision). However, the on-chip integrated devices and circuits exhibit stress-induced changes on their electrical and optoelectronic characteristics. Since a stress independent operation is striven, the minimization or compensation of the influence of mechanical stress on the characteristics of devices and circuits is of great interest.

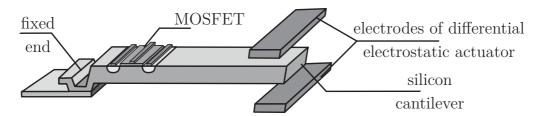

In this work optical and electrical properties of passive and active devices as well as integrated circuits on ultra-thin monolithic flexible silicon chips have been investigated under the application of mechanical stress. The influence of mechanical stress on the optical characteristics (spectral sensitivity, dark current and electronic noise) of p-n junction based photodiodes and image sensor chips on (100)-silicon wafers have been theoretically modeled and experimentally characterized. Moreover, the electrical characteristics (carrier mobility, threshold voltage and 1/f noise) of mechanically strained MOS field-effect transistors and their dependence on the channel orientation on the substrate have been investigated. Integrated circuits such as bandgap reference voltage sources, operational amplifiers and switched capacitor (SC) based circuits have been theoretically treated, designed, fabricated and experimentally characterized.

Within this framework a simulation technique has been proposed and deployed, which allows the simulation of the above mentioned stress dependence on device and circuit level. The analog circuit designer can employ the simulation technique toward the proposal of circuit topologies or techniques, which minimize or compensate the strain-induced changes on the circuit operation. In this direction, circuit concepts and design rules are proposed, which minimize the influence of mechanical stress on flexible CIS chips.

Within the scope of this work, a mechanically flexible CMOS image sensor chip has been designed, simulated and fabricated, which operation is stress independent. The developed ultra-thin 20 µm CIS chip can be wrapped around a cylindrically curved surface and thus record panoramic optical information.

## Table of Contents

| List of | Figur   | es xii                                                | i |

|---------|---------|-------------------------------------------------------|---|

| List of | Table   | s xvi                                                 | i |

| List of | Abbre   | eviations xx                                          | i |

| List of | Symb    | ols xxx                                               | i |

| 1 Intro | oductio | on 1                                                  | L |

| 1.1     | Motiv   | ation                                                 | 3 |

| 1.2     | Resear  | rch Goal and Scientific Approach                      | 5 |

| 1.3     | State   | of the Art                                            | 3 |

| 1.4     | Thesis  | s Outline                                             | 1 |

| 2 Theo  | oretica | l Background 17                                       | 7 |

| 2.1     | Elasti  | city Theory                                           | 3 |

|         | 2.1.1   | Stress                                                | 3 |

|         | 2.1.2   | Strain                                                | ) |

|         | 2.1.3   | Stress-Strain Relation                                | 1 |

| 2.2     | Funda   | mentals of Semiconductor Device Physics               | 2 |

|         | 2.2.1   | Silicon Crystal and Band Structure                    | 2 |

|         | 2.2.2   | p-n Junctions                                         | 9 |

|         | 2.2.3   | p-n Junction Based Photodiodes                        | 2 |

|         | 2.2.4   | Metal-Oxide-Semiconductor Capacitors                  | 9 |

|         | 2.2.5   | Metal-Oxide-Semiconductor Field-Effect Transistors 42 | 2 |

x Table of Contents

| 2.3    | CMOS Image Sensors                                        | 47  |

|--------|-----------------------------------------------------------|-----|

|        | 2.3.1 System Architecture                                 | 47  |

|        | 2.3.2 Photodiode and Pixel Considerations                 | 49  |

|        | 2.3.3 Readout Electronics Overview                        | 52  |

| 2.4    | Synopsis                                                  | 55  |

| 3 Mod  | leling Strain-Induced Effects on Devices and Circuits     | 57  |

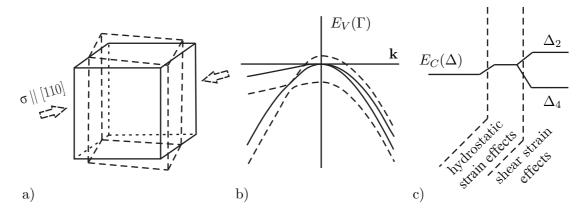

| 3.1    | Band Structure of Strained Silicon                        | 58  |

|        | 3.1.1 Strain-Induced Conduction Band Shift                | 60  |

|        | 3.1.2 Strain-Induced Conduction Band Degeneracy Lifting   | 61  |

|        | 3.1.3 Strain-Induced Valence Band Splitting               | 63  |

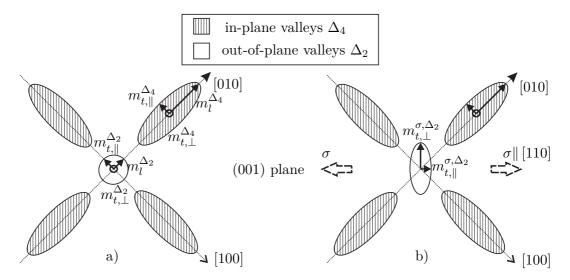

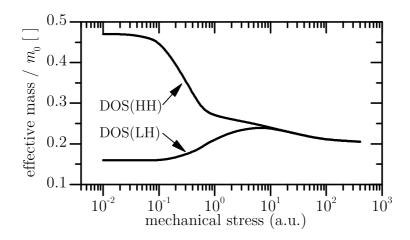

|        | 3.1.4 Strain-Dependent Effective Mass Variations          | 64  |

| 3.2    | Strained p-n Junction Based Photodiode                    | 66  |

| 3.3    | Strained Capacitor                                        | 71  |

| 3.4    | Strained MOS Transistor                                   | 72  |

| 3.5    | Basic Analog Circuits under Mechanical Stress             | 76  |

|        | 3.5.1 Current Mirrors and References                      | 76  |

|        | 3.5.2 Single- and Multiple-Transistor Amplifiers          | 79  |

|        | 3.5.3 Two-Stage Operational Amplifier                     | 87  |

| 3.6    | CIS Readout Circuits under Mechanical Stress              | 89  |

| 3.7    | Synopsis                                                  | 93  |

| 4 Simu | ulation of Strain-Induced Effects on Devices and Circuits | 95  |

| 4.1    | Band Structure of Strained Silicon                        | 96  |

| 4.2    | Strained p-n Junction Based Photodiode                    | 100 |

| 4.3    | Simulation Technique                                      | 102 |

| 4.4    | Basic Analog Circuits under Mechanical Stress             | 105 |

| 4.5    | CIS Readout Circuits under Mechanical Stress              | 110 |

| 4.6    | Synopsis                                                  | 114 |

| 5 Expe | erimental Methods                                         | 115 |

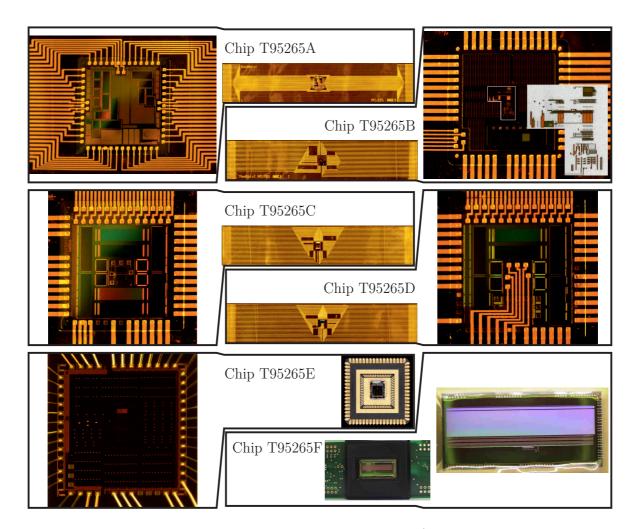

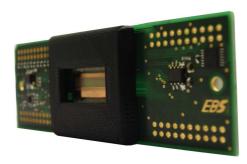

| 5.1    | Fabricated Test Chips                                     | 116 |

| 5.2    | Thinning and Encapsulation Processes                      | 122 |

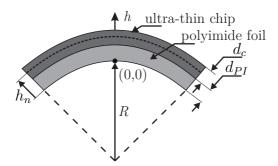

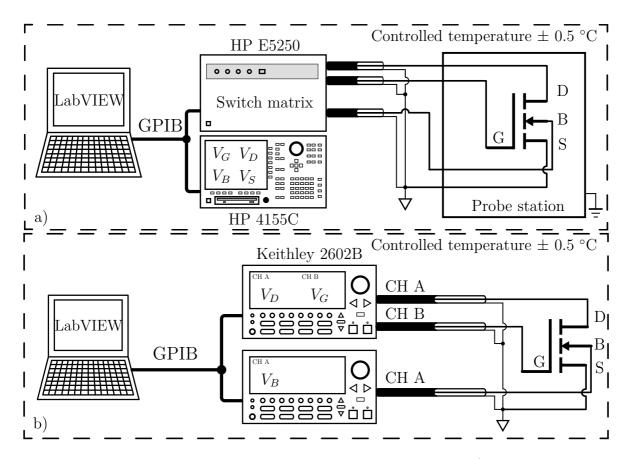

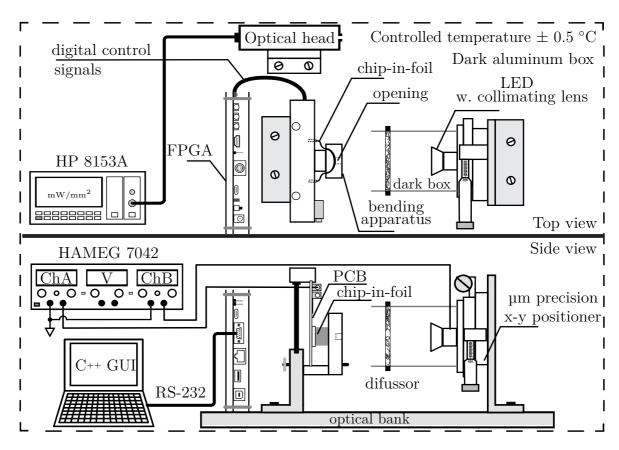

| 5.3    | Experimental Setups and Techniques                        | 123 |

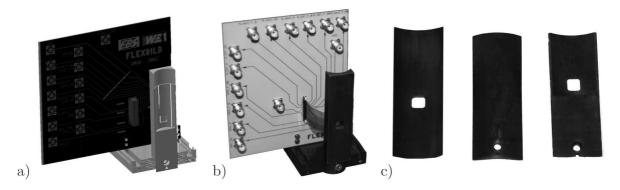

|        | 5.3.1 Bending Apparatus                                   | 124 |

|        | 5.3.2 Electrical and Optical Measurement Setups           | 127 |

Table of Contents xi

| 5.4     | Synopsis                                                                 | 132  |

|---------|--------------------------------------------------------------------------|------|

| 6 Expe  | erimental Results                                                        | 135  |

| 6.1     | Strained p-n Junction Based Photodiode                                   | 136  |

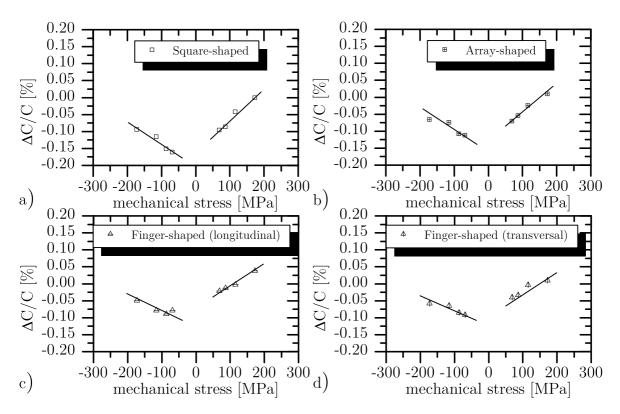

| 6.2     | Strained Capacitor                                                       | 149  |

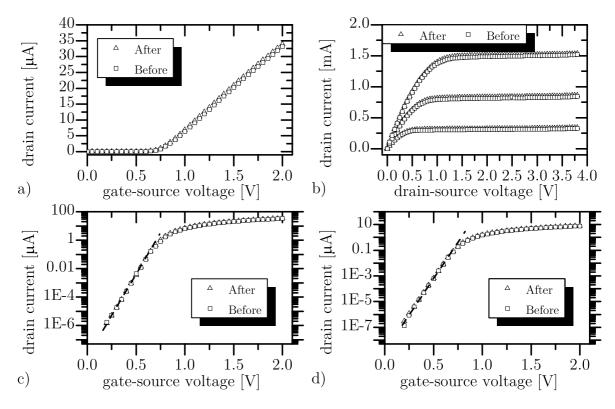

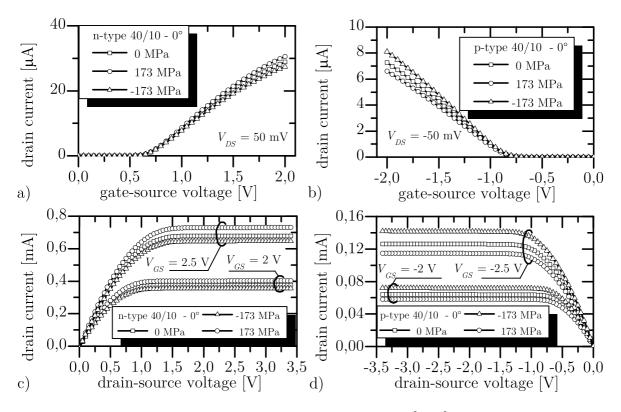

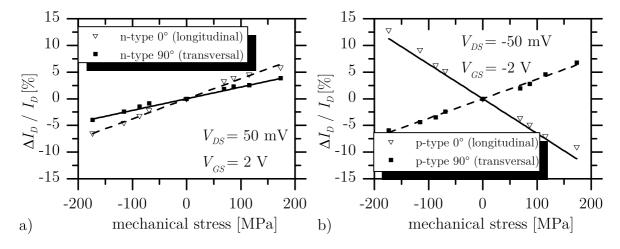

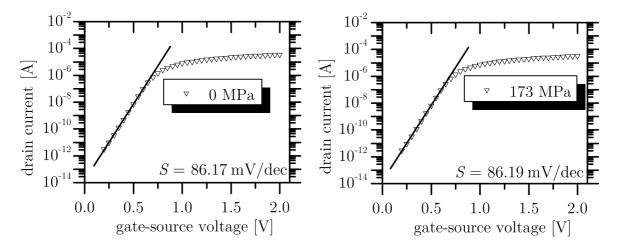

| 6.3     | Strained MOS Transistor                                                  | 150  |

| 6.4     | Bendable Image Test Sensors                                              | 161  |

| 6.5     | A Bendable Bandgap Voltage Reference                                     | 166  |

| 6.6     | A Flexible CIS for Bendable Applications                                 | 166  |

| 6.7     | Synopsis                                                                 | 168  |

| 7 Discı | assion                                                                   | 171  |

| 7.1     | Guidelines for a Stress Independent Circuit Operation                    | 172  |

| 7.2     | Potential Applications                                                   | 174  |

| 7.3     | Synopsis and Further Work                                                | 177  |

| Appen   | dix                                                                      | 181  |

| A.1     | Stress, Strain and Piezoresistivity Relations in Strained Silicon        | 181  |

| A.2     | Transistors under [110] Uniaxial Mechanical Stress on (100) Silicon      | 186  |

| A.3     | Round Transistors under [110] Uniaxial Mechanical Stress on (100) Silico | n187 |

| Bibliog | graphy                                                                   | 189  |

# List of Figures

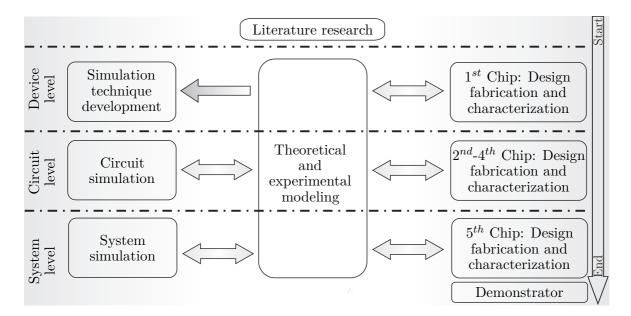

| rigure 1.1  | Scientific approach                                             | U  |

|-------------|-----------------------------------------------------------------|----|

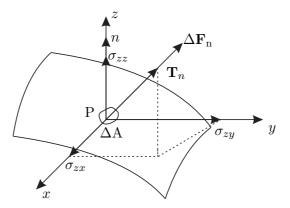

| Figure 2.1  | Resultant of forces acting over area $\Delta A$                 | 19 |

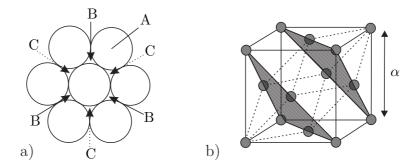

| Figure 2.2  | Atom stacking sequence and a simple fcc lattice                 | 23 |

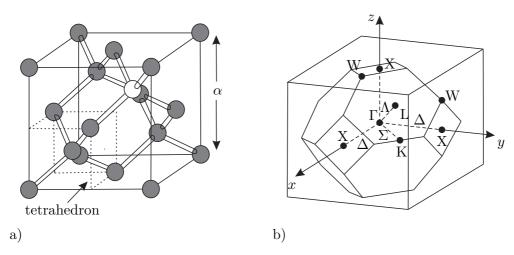

| Figure 2.3  | Silicon diamond crystal structure and first Brouillin zone      | 24 |

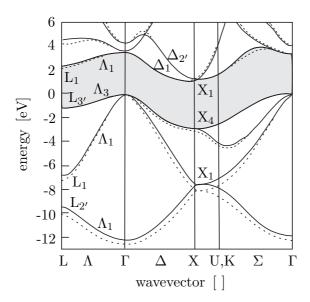

| Figure 2.4  | Silicon energy band structure                                   | 26 |

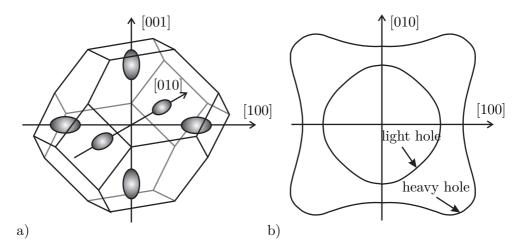

| Figure 2.5  | Constant energy surfaces of conduction and valence bands in     |    |

|             | silicon                                                         | 27 |

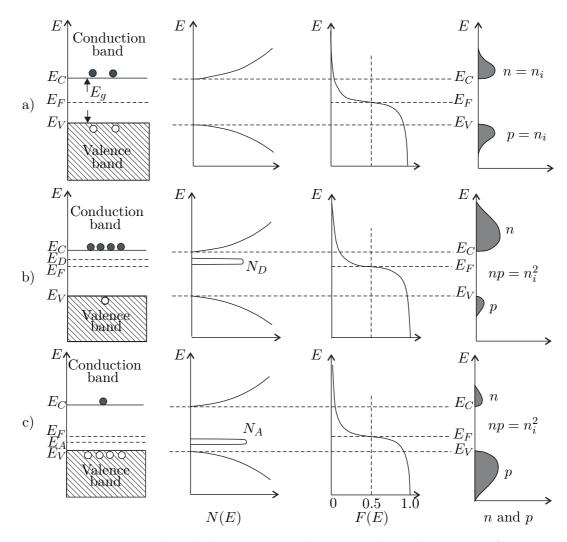

| Figure 2.6  | Energy band diagram and carrier distributions of an n-type and  |    |

|             | a p-type material                                               | 31 |

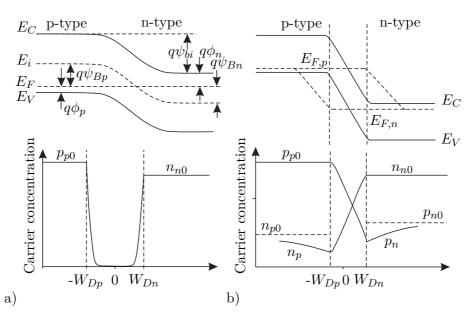

| Figure 2.7  | Energy band diagram of a p-n junction                           | 33 |

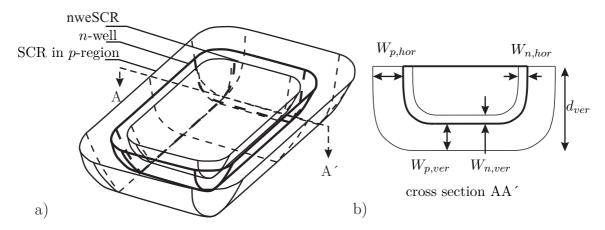

| Figure 2.8  | A three-dimensional aspect of a p-n junction                    | 37 |

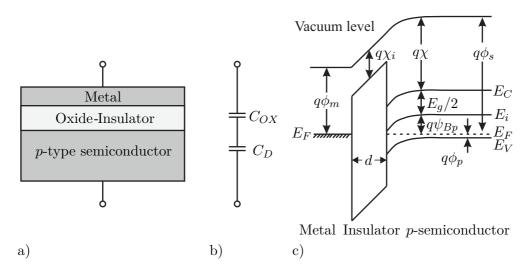

| Figure 2.9  | An ideal metal-oxide-semiconductor capacitor                    | 40 |

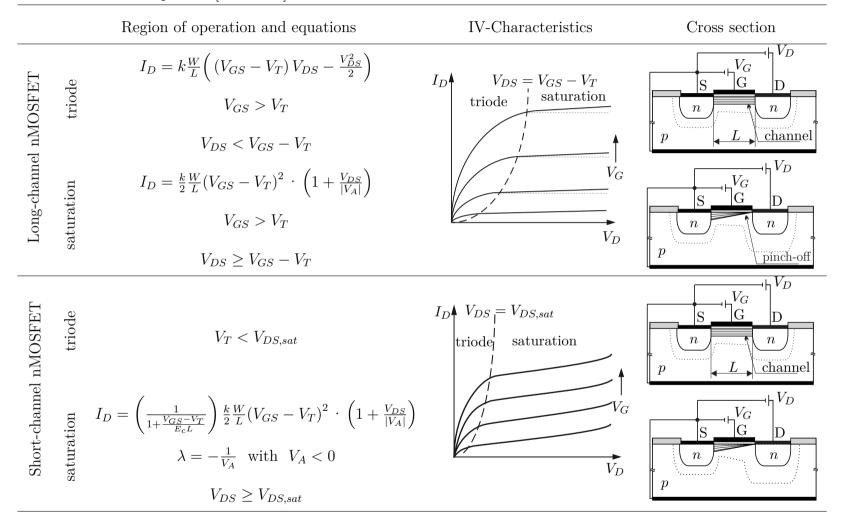

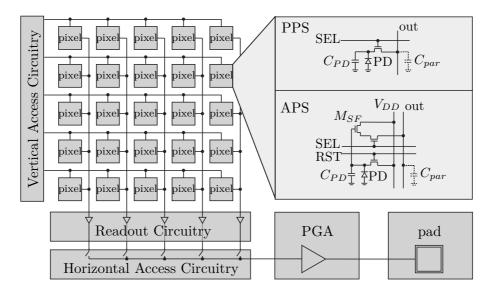

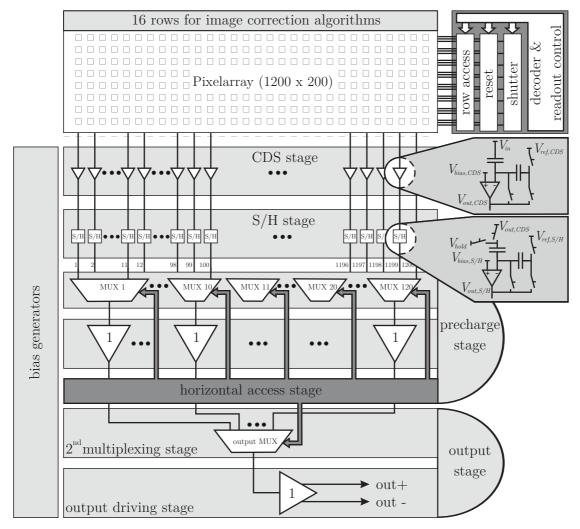

| Figure 2.10 | CMOS image sensor architecture                                  | 48 |

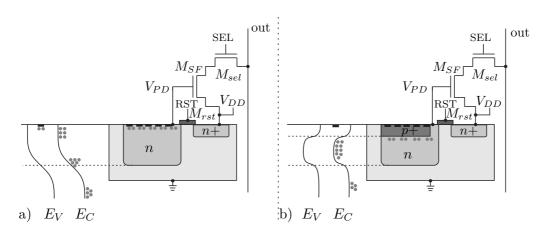

| Figure 2.11 | 3T active pixel sensor design                                   | 50 |

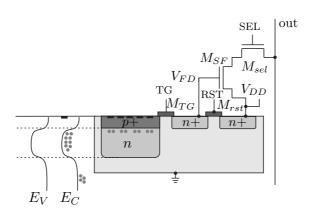

| Figure 2.12 | 4T active pixel sensor design                                   | 51 |

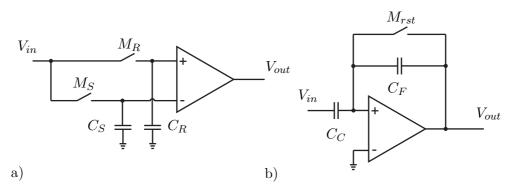

| Figure 2.13 | Circuit implementation of correlated doubled sampling $\dots$ . | 53 |

| Figure 3.1  | Deformation of a cubic crystal under mechanical stress and the  |    |

|             | induced band shifting                                           | 59 |

| Figure 3.2  | Conduction band constant energy surfaces                        | 65 |

| Figure 3.3  | Valence band DOS effective masses under mechanical stress. $$ . | 66 |

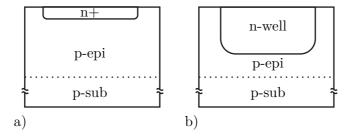

| Figure 3.4  | p-n junction based photodiodes                                  | 66 |

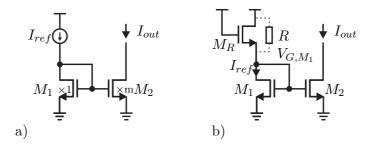

| Figure 3.5  | Current mirror configurations                                   | 77 |

xiv List of Figures

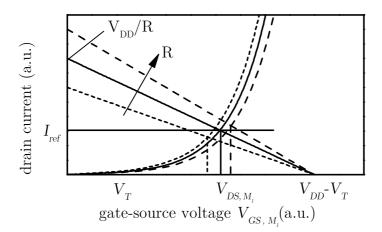

| Figure 3.6  | Superimposing the resistor load line on the MOSFET characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

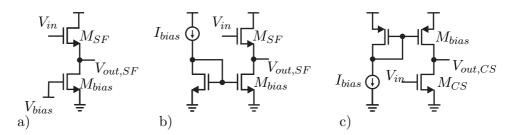

| Figure 3.7  | Source follower and common source circuit configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79  |

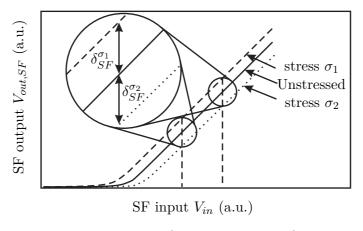

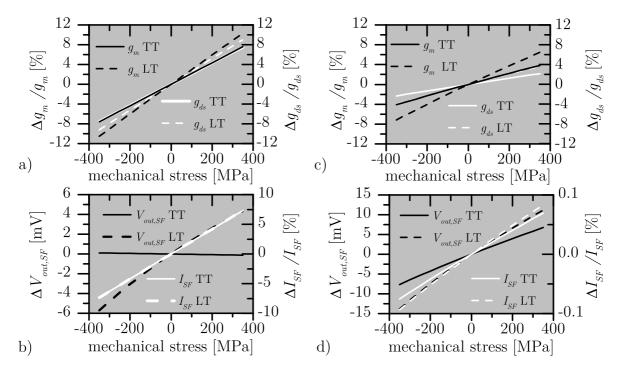

| Figure 3.8  | Source follower circuit voltage transfer characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82  |

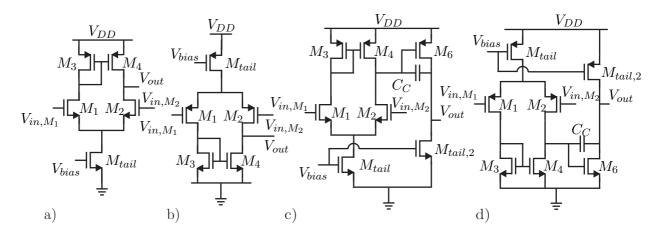

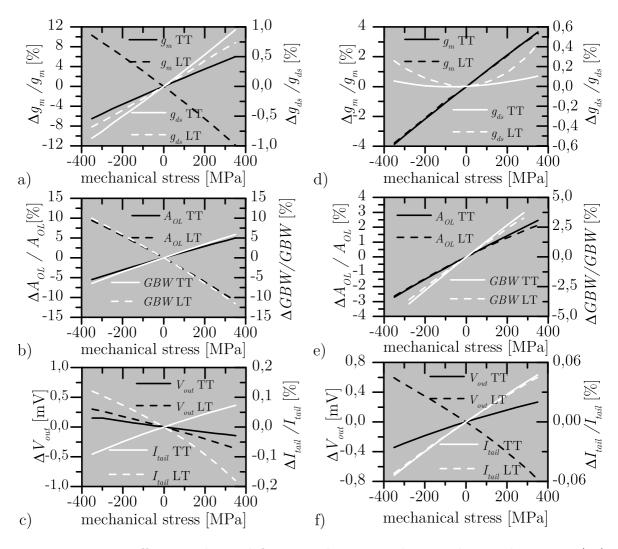

| Figure 3.9  | Differential and two-stage Miller amplifier topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85  |

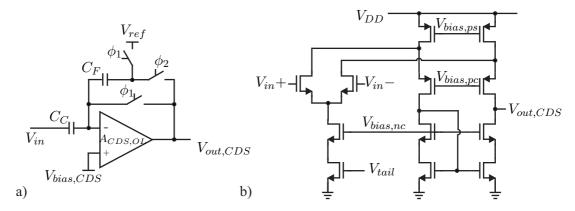

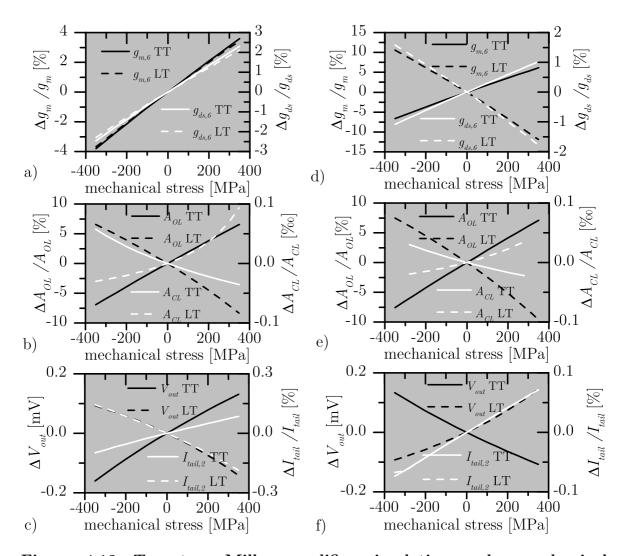

| Figure 3.10 | Correlated double sampling amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89  |

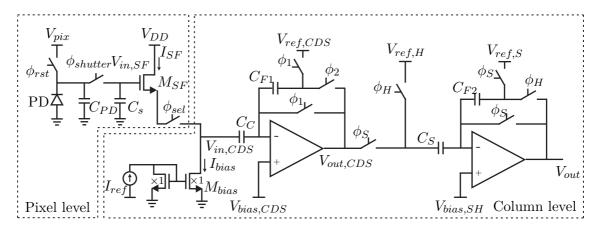

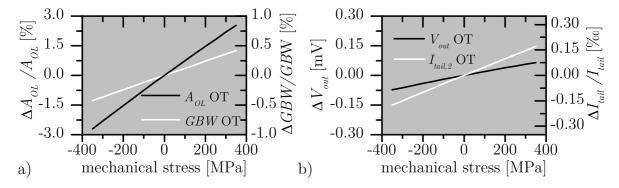

| Figure 3.11 | Pixel readout circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 91  |

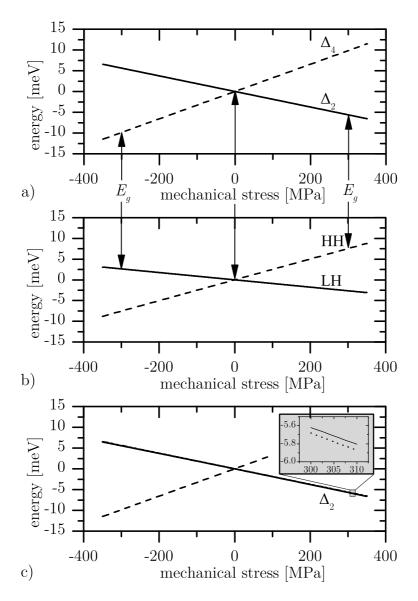

| Figure 4.1  | Strain-induced shifts of the energy band minima                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 98  |

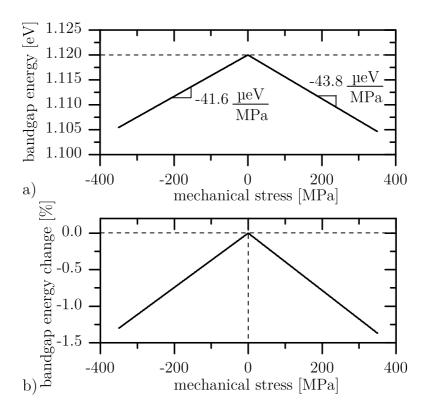

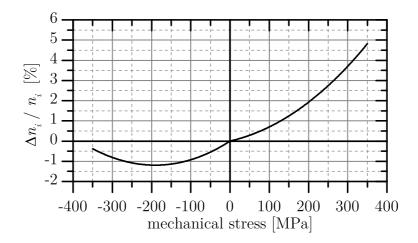

| Figure 4.2  | Strain-induced bandgap narrowing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 99  |

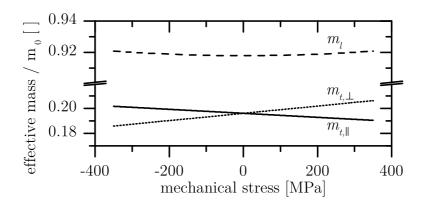

| Figure 4.3  | Conduction band $\Delta_2$ effective masses modeling under mechan-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|             | ical stress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 99  |

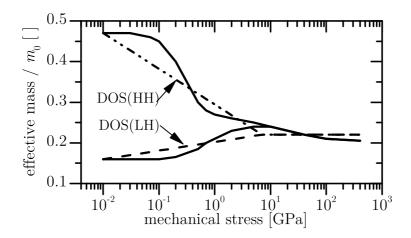

| Figure 4.4  | Valence band DOS effective mass modeling under mechanical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

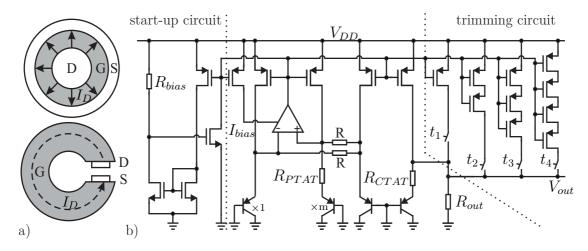

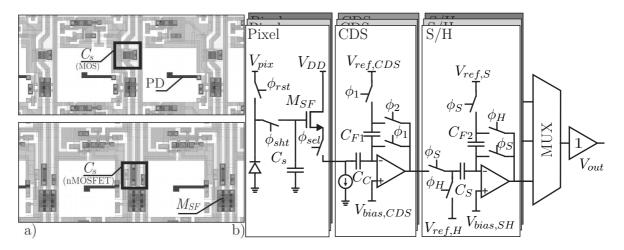

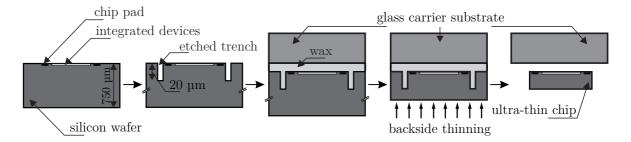

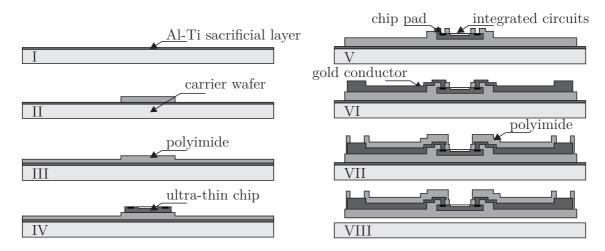

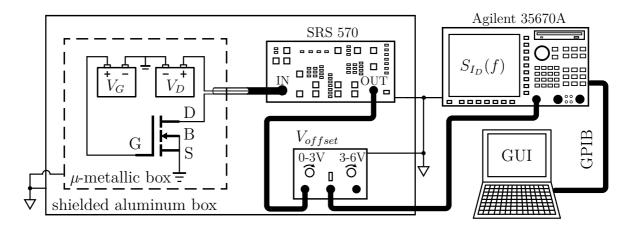

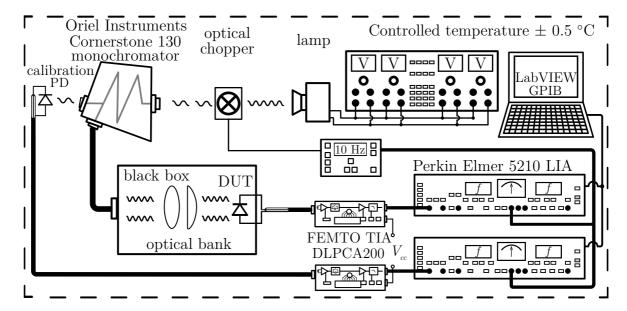

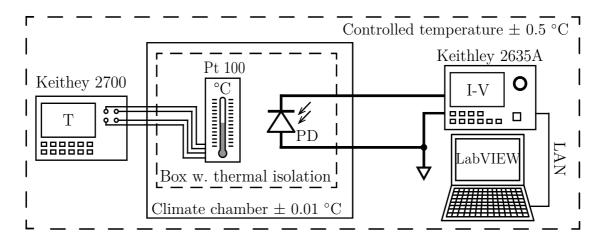

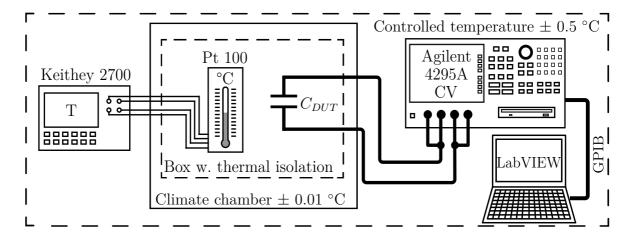

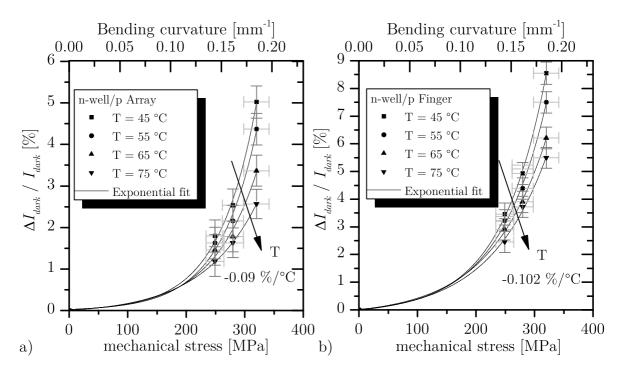

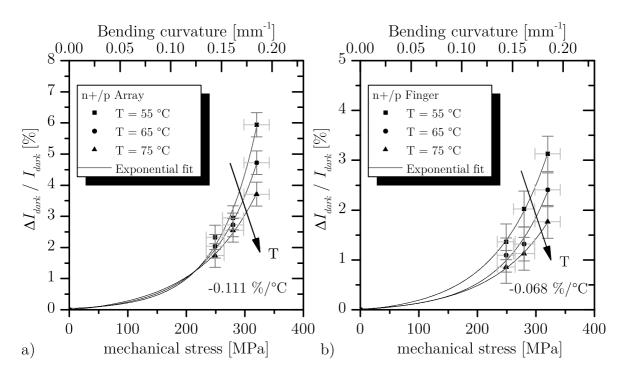

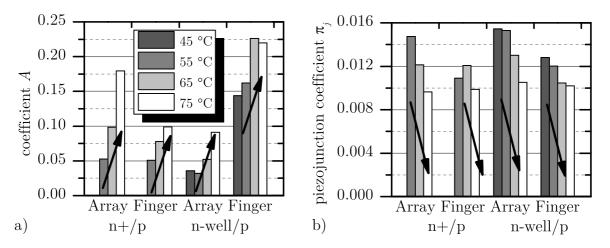

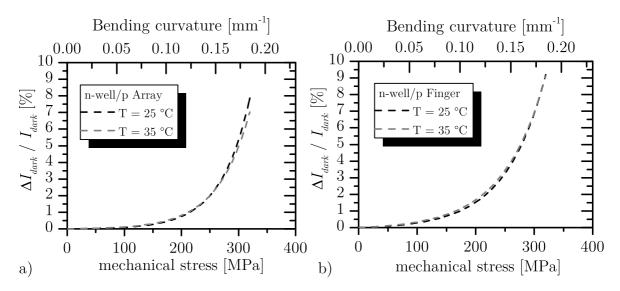

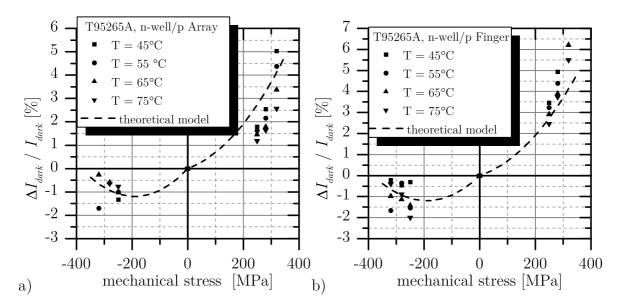

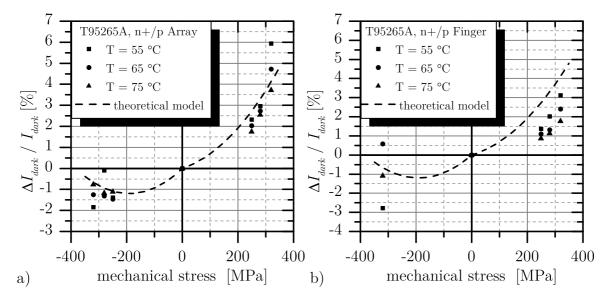

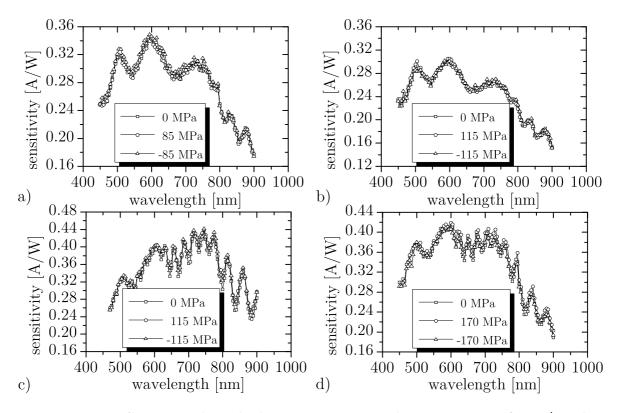

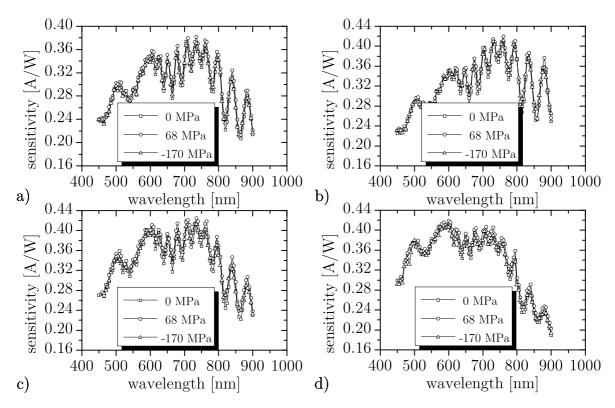

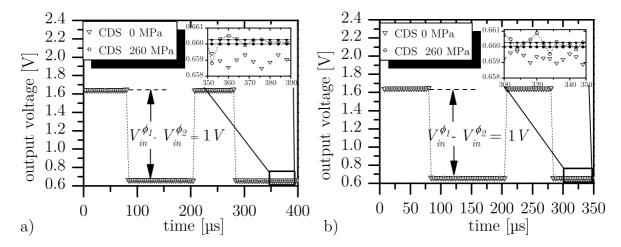

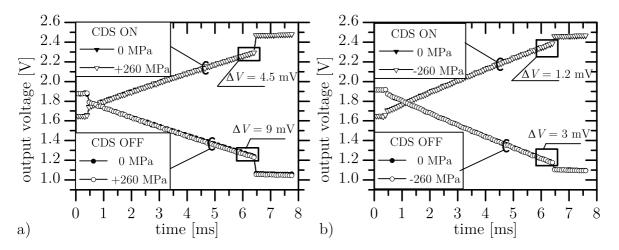

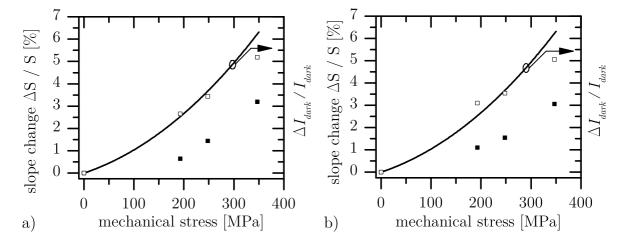

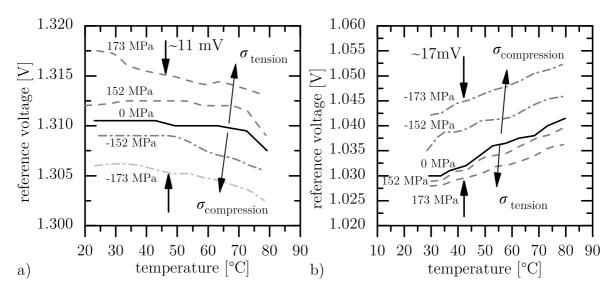

|             | stress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100 |