## High Temperature Thermoelectric Device Concept Using Large Area *PN* Junctions

Von der Fakultät für Ingenieurwissenschaften,

Abteilung Elektrotechnik und Informationstechnik

der

Universität Duisburg-Essen

zur Erlangung des akademischen Grades

Doktors der Ingenieurwissenschaften

genehmigte Dissertation

von

Ruben Chavez

aus

Guadalajara, Mexiko

1.. Gutachter: Prof. Dr. rer. nat. Roland Schmechel

2. Gutachter: Prof. Dr. rer. nat. Gerd Bacher

Tag der mündlichen Prüfung: 30. September 2015

## **Contents**

| 1 | Intr | oduction                                                                     | 5  |  |  |  |  |  |

|---|------|------------------------------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1  | The Energy Problem                                                           | 5  |  |  |  |  |  |

| 2 | Trai | nsport Theory                                                                | 9  |  |  |  |  |  |

|   | 2.1  | The Adapated Landauer Approach                                               | 9  |  |  |  |  |  |

|   | 2.2  | Electrical Current Due to Voltage Difference                                 | 10 |  |  |  |  |  |

|   | 2.3  | Electrical Current Due to Temperature Difference                             | 12 |  |  |  |  |  |

|   | 2.4  | Heat Current                                                                 | 16 |  |  |  |  |  |

|   | 2.5  | 5 Coupled Transport: Electricity and Heat                                    |    |  |  |  |  |  |

|   | 2.6  | The Peltier Effect in Bipolar Semiconductors                                 | 18 |  |  |  |  |  |

|   | 2.7  | The Thomson Effect                                                           | 22 |  |  |  |  |  |

| 3 | Con  | ventional Thermoelectric Generator: TEG                                      | 25 |  |  |  |  |  |

|   | 3.1  | Efficiency of the Thermoelectric Process                                     | 25 |  |  |  |  |  |

|   | 3.2  | From a Thermoelectric Material to a Conventional Thermoelectric Generator 29 |    |  |  |  |  |  |

|   | 3.3  | Thermal Matching: The TEG in Operating Conditions                            |    |  |  |  |  |  |

|   | 3.4  | O I                                                                          |    |  |  |  |  |  |

|   |      | 3.4.1 Silicon as a High Temperature Material                                 | 33 |  |  |  |  |  |

|   |      | 3.4.2 Large Temperature Gradients and Temperature Dependent Model .          | 37 |  |  |  |  |  |

|   | 3.5  | Summary: Conventional TEG                                                    | 39 |  |  |  |  |  |

| 4 | New  |                                                                              | 41 |  |  |  |  |  |

|   | 4.1  | Proposed Concept: PN-TEG                                                     | 41 |  |  |  |  |  |

|   | 4.2  | PN-TEG Proposed Theory                                                       | 44 |  |  |  |  |  |

|   |      | 4.2.1 Simulation Details: Discrete Onsager Network                           | 45 |  |  |  |  |  |

|   |      | 4.2.2 Electrical Transport                                                   | 46 |  |  |  |  |  |

|   |      | 4.2.3 Temperature Dependence of Electric Transport                           | 48 |  |  |  |  |  |

|   |      | 4.2.4 Current Loops Within the PN-TEG                                        | 52 |  |  |  |  |  |

|   |      | 4.2.5 Thermal Generation and Internal Resistance                             | 54 |  |  |  |  |  |

|   |      | 4.2.6 Efficiency                                                             | 57 |  |  |  |  |  |

|   |      | 4.2.7 Geometrical Optimization                                               | 61 |  |  |  |  |  |

|   | 4.3  | Summary: PN-TEG Theory                                                       | 62 |  |  |  |  |  |

| 5 |      | • • •                                                                        | 65 |  |  |  |  |  |

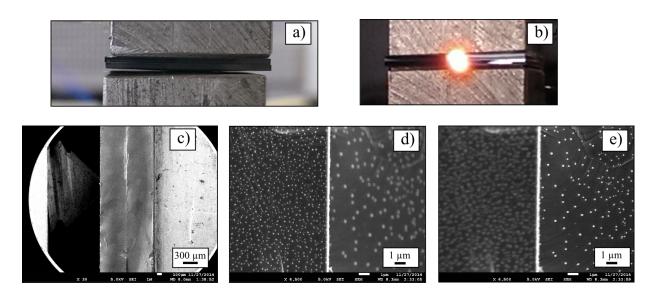

|   | 5.1  | From Silicon Nanoparticles to Bulk PN Junctions: Current Assisted Sintering  | 66 |  |  |  |  |  |

|   |      | 5.1.1 Nanoparticle Synthesis                                                 | 66 |  |  |  |  |  |

|   |      | 5.1.2         | Densification: Current Assisted Sintering                       |

|---|------|---------------|-----------------------------------------------------------------|

|   |      | 5.1.3         | Electrical Contacts                                             |

|   | 5.2  | From 1        | Photovoltaic silicon PN Junctions to PN-TEGs: Laser Annealed PN |

|   |      | Juncti        | ons                                                             |

|   |      | 5.2.1         | Sample Preparation: Laser Annealing                             |

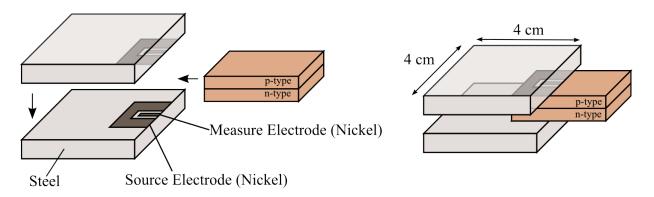

|   | 5.3  | Si PN         | Junctions from Wafers: Current Assisted Bonding                 |

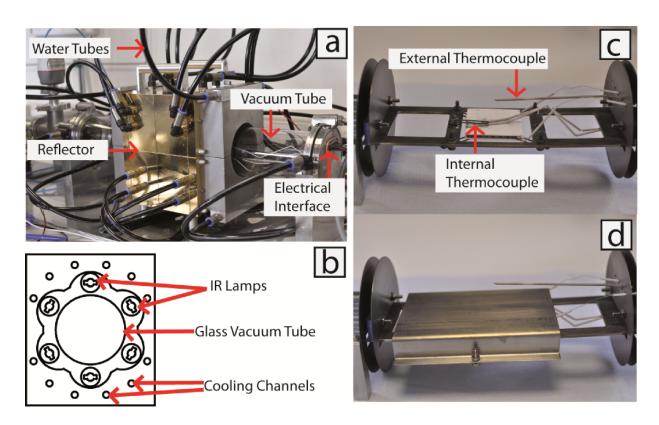

|   |      | 5.3.1         | Current Assisted Welding Setup                                  |

|   |      | 5.3.2         | Electrical Contacts                                             |

|   | 5.4  | Summ          | ary of Sample Preparation                                       |

| 6 | Met  | rology        | and Characterization 85                                         |

|   | 6.1  |               | ural Characterization                                           |

|   | 6.2  |               | onic Characterization of the PN Junctions                       |

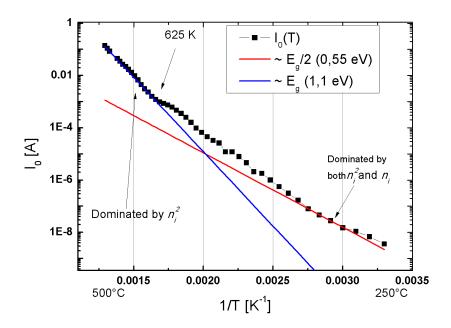

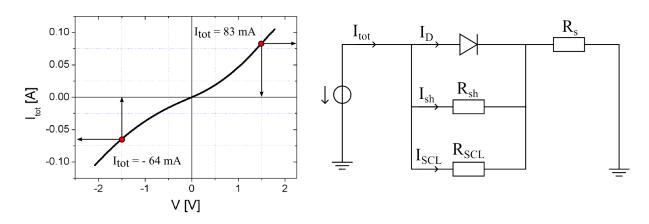

|   | ٠    | 6.2.1         | Equivalent Circuit and Extracted Parameters                     |

|   |      | 6.2.2         | Effective Bandgap                                               |

|   | 6.3  |               | toelectric Characterization of the TEGs                         |

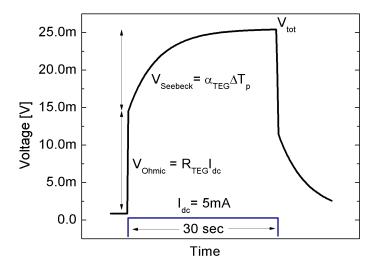

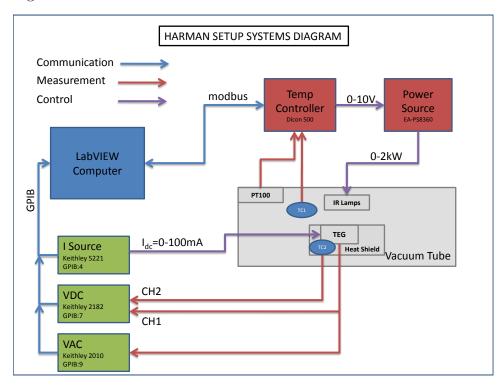

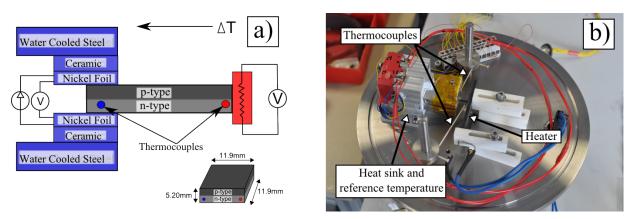

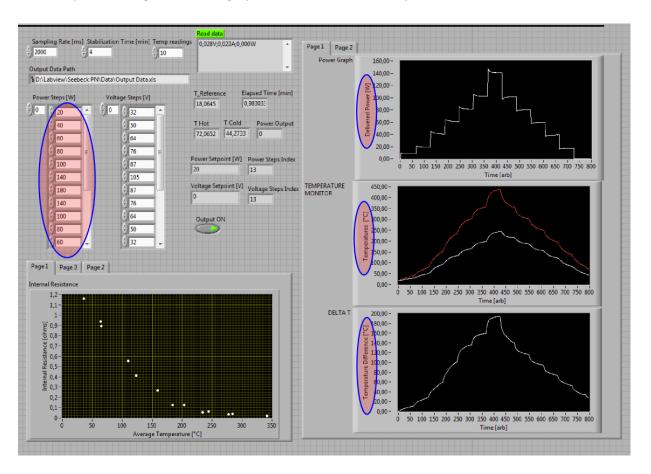

|   | 0.0  | 6.3.1         | The Harman Setup                                                |

|   |      | 6.3.2         | The Monkey Setup                                                |

|   |      | 6.3.3         | Electrical Measurements: Hardware                               |

|   |      | 6.3.4         | Electrical Conductivity-Conductance                             |

|   |      | 6.3.5         | Device "Seebeck" Coefficient                                    |

|   |      | 6.3.6         |                                                                 |

|   |      | 0.5.0         | Power Output                                                    |

| 7 | Resi | ults and      | d Discussion 113                                                |

|   | 7.1  | Struct        | ural Characteristics                                            |

|   |      | 7.1.1         | Current Assisted Sintering PN-TEGs                              |

|   |      | 7.1.2         | Laser Annealing PN-TEGs                                         |

|   |      | 7.1.3         | Wafer Welding PN-TEGs                                           |

|   |      | 7.1.4         | Summary of Structural Characteristics                           |

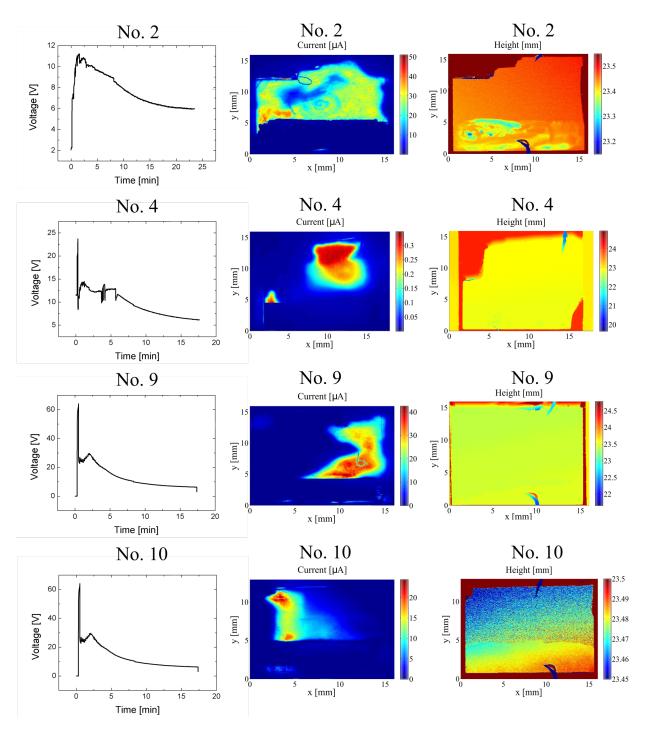

|   | 7.2  | Electri       | cal Characteristics                                             |

|   |      | 7.2.1         | Commercial Diode as Reference                                   |

|   |      | 7.2.2         | Electrical Properties: Current Assisted Sintering PN-TEGs 123   |

|   |      | 7.2.3         | Electrical Properties: Laser Annealed PN-TEGs                   |

|   |      | 7.2.4         | Electrical Properties: Wafer Welded PN-TEGs                     |

|   |      | 7.2.5         | Summary of Electrical Characteristics                           |

|   | 7.3  |               | toelectric Characteristics                                      |

|   |      | 7.3.1         | Effective Seebeck Coefficient                                   |

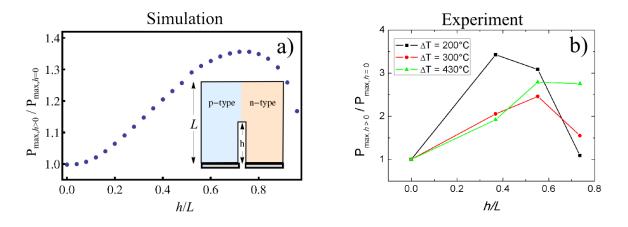

|   |      | 7.3.2         | Geometric Optimization                                          |

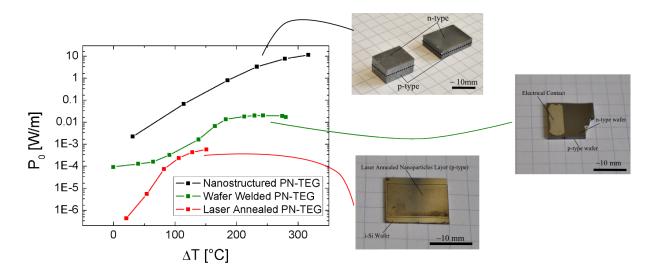

|   |      | 7.3.3         | Power Output                                                    |

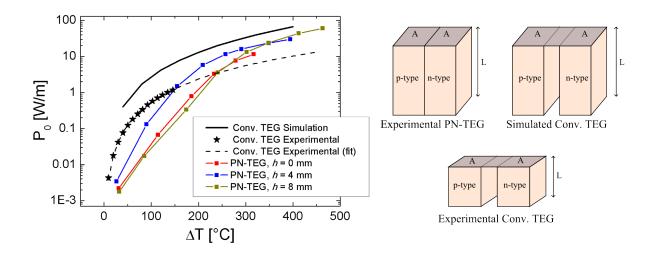

|   |      | 7.3.4         | PN-TEG and Conventional TEG: Comparison                         |

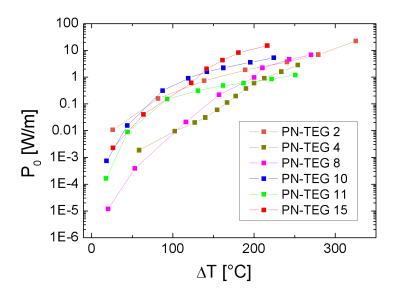

|   |      | 7.3.4 $7.3.5$ | High Temperature Stability and Reproducibility                  |

|   |      | 7.3.6         | Summary of Results and Discussion                               |

|   |      | ( . · ) . ()  | Dummary of Desums and Discussion                                |

| 8  | Conclusions and Outlook8.1 Conclusions |     |

|----|----------------------------------------|-----|

| 9  | Publications                           | 159 |

| 10 | Acknowledgments                        | 161 |

| Bi | bliography                             | 162 |

#### List of Symbols (unless otherwise stated)

- $\nabla$  Gradient

- $\alpha$  Seebeck coefficient

- $\Delta$  Change in ...

- $\epsilon$  Error

- $\varphi$  Electrochemical potential

- $\eta$  Efficiency

- $\eta_{\rm D}$  Ideality factor

- $\kappa$  Thermal conductivity

- K Thermal conductance

- $\lambda$  Mean free path

- $\mu$  Carrier mobility

- $\Pi$  Peltier coefficient

- $\Theta$  Heat capacity

- $\rho$  Electrical resistivity

- $\sigma$  Electrical conductivity

- $\Sigma$  Sum of ...

- $\tau$  Transit time

- $\omega$  Angular frequency

- $\Omega$  Ohms

- A Area

- D(E) Density of states

- ${f E}$  Electric field

- E Energy

- $E_{\rm F}$  Fermi level

- $E_{\rm g}$  Bandgap energy

f(E) - Fermi function

${\cal G}$  - Electrical conductance

h - Plank's constant

I - Electric current

$I_0$  - Reverse bias current

J - Electric current density

$\mathbf{J}_{\mathrm{q}}$  - Heat current density

$k_{\rm B}$  - Boltzmann constant

K - Kelvin

L - Length

m - Meters

$m_{\rm e}^*$  - Effective mass of electrons

$m_{\rm h}^*$  - Effective mass of holes

M(E) - Number of modes

$n_i$  - Intrinsic carrier concentration

N - Newton

$N_{\rm c}$  - Effective density of states in the conduction band

$N_{\rm v}$  - Effective density of states in the valence band

$N_{\rm A}$  - Acceptor doping concentration

$N_{\mathrm{D}}$  - Donor doping concentration

N(E) - Number of charge carriers

P - Power

q - Elementary charge

Q - Heat current

R - Electrical resistance

t - Time

${\cal T}$  - Temperature

T(E) - Transmission probability

$T_{\rm c}$  - Cold side temperature

$T_{\rm h}$  - Hot side temperature

$V_{\rm b}$  - Built in voltage

V - Volts

W - Watts

## 1 Introduction

The problem is, we think we have time.

Unknown

## 1.1 The Energy Problem

The main driving force that fuels the push for renewable energies and a reduction of fossil fuels does not seem to steam from a sense of responsibility or protection of the planet, but from an urgent need to satisfy the global energy demand as rising costs have made otherwise expensive alternative energies more competitive. Strictly speaking, thermoelectricity is not intrinsically a renewable energy because it may be implemented in the form of heat waste recovery where the wasted heat from the combustion of fossil fuel is harvested or in the form of a solar-thermal system in which solar energy is absorbed to produce heat. The latter case being the example of a renewable energy.

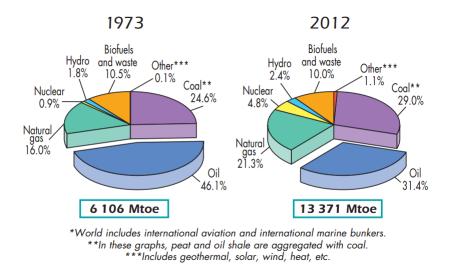

In order to realize the need and motivation (moral or practical) to search for alternatives to satisfy the world's energy demand, it is necessary to bring some perspective to know where renewable energies stand with respect to other energy sources and to what extent they can change the course of things. Figure 1.1 shows the distribution of fuels needed to satisfy the world energy demand in the years of 1973 and 2009. The category other\*\*\* contains the sum from alternative energies such as solar, geothermal, and wind. While

alternative energies have seen an 10-fold increase in the last 39 years, they are still lacking to be a global change as they only produce about 1 percent of the global energy today, hence research efforts should continue in order to develop successful renewable energy sources.

Figure 1.1: World energy as provided per different fuels [1]. (TOE is a unit of energy defined as the amount of energy released by burning one tonne of crude oil).

As far as the potential for thermoelectrics to play a role as an alternative energy, recall from Figure 1.1 that the vast majority of the world energy is produced by burning different forms of fossil fuels, which means that the efficiency of this thermodynamic process is limited by Carnot's efficiency which is defined by the operating temperatures. Carnot's efficiency for most combustion processes has remained between 20-50% [2], and this has to do with the difficulties in finding high temperature stable materials.

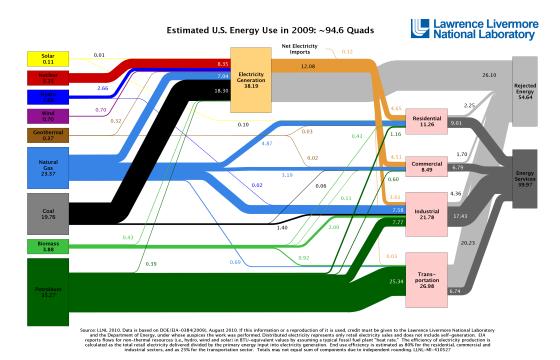

Figure 1.2 shows the energy distribution in the United States. The breakdown is interesting but the main point in this context is that around 60% of the total energy is wasted and most of that energy waste is in the form of heat since most of the energy comes from combustion of fossil fuels, hence theoretically there is much room where thermoelectric technologies could assist conventional fossil fuel system to be more efficient. If only 1% of all lost heat is recovered, thermoelectricity would contribute as much as all other

alternative energies combined, hence the potential for thermoelectricity is there.

Figure 1.2: Break down of energy resources in the U.S. (1 Quad =  $1.055 \times 10^{18}$  J).

Thermoelectricity despite discovered almost 200 years ago remains as a low efficiency technology and this has limited its applications to deep space exploration where solar energy is no longer available. On earth most of the usage of thermoelectric devices is as solid state heat pumps and very limited commercial electricity generation applications. Thermoelectric devices are traditionally made from semiconductor materials since their electrical properties can be readily tunned. Traditionally a thermoelectric device consists of an intercalating series of p-type and n-type semiconductors connected electrically in series and thermally in parallel, sandwiched between two substrates were the interconnects are located.

In this work a new device architecture is tested experimentally; a thermoelectric generator (TEG) is built by joining the complementary doped silicon legs together forming a large area PN junction that acts a mechanical and electrical junction. The combination

of a PN junction and a TEG gives rise to the therm PN-TEG. In a PN-TEG the hot side substrate is no longer needed, and this provides technological advantages because it eases the fabrication process and opens the door for high temperature applications. The nanostructured silicon PN-TEGs presented in this work are shown to be competitive with equivalent conventional technologies, and some of the fundamental working principles are proposed and experimentally demonstrated.

## 2 Transport Theory

Scientists are called to see what everyone else has seen and think what no one else has thought before.

Albert Szent-Gyorgyi

## 2.1 The Adapated Landauer Approach

In the following sections, some of the thermoelectric phenomenon relevant to this work are introduced using an adaptation on the Landauer model. In 1957 Landauer proposed a model for metallic electrical resistance, in which he considered current as an integral over the transmission probability [3]. This model was later adapted to explain thermoelectric phenomena [4, 5], and following this adaptation, some thermoelectric aspects will be introduced. The starting point for this approach is an elastic resistor where all scattering energy is conserved and inelastic contacts that maintain equilibrium conditions where all energy transfer occurs. From this starting point, relevant thermoelectric phenomena is introduced and most importantly, it will be shown that by starting Landauer model, great insight can be gained on fundamental mechanics of thermoelectric phenomena at the quantum level that are otherwise invisible.

## 2.2 Electrical Current Due to Voltage Difference

From conventional electronics theory, Ohm's Law, the proportionality between unipolar electrical current density J and electric field E is derived from Drude's model and written as:

$$\mathbf{J} = \underbrace{qn\mu}_{\sigma} \mathbf{E} \tag{2.1}$$

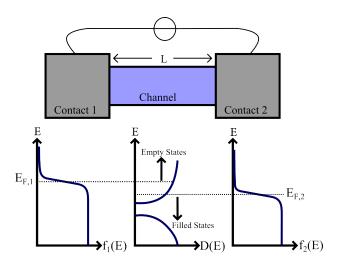

where q is the elementary charge, n the carrier concentration,  $\mu$  the mobility and  $\sigma$  the electrical conductivity. While equation 2.1 is extremely practical, it has abstracted much information that is important to understand some thermoelectric aspects. Consider the elastic resistor in Figure 2.1, recall that the channel is connected to ideal contacts that maintain near-equilibrium conditions. Each contact is described by a electronic thermodynamic occupation equilibrium described by the Fermi function:

$$f_{1,2}(E) = \frac{1}{1 + \exp\left(\frac{E - E_{F1,2}}{\kappa_B T_{1,2}}\right)}$$

(2.2)

where E is energy,  $E_{\rm F}$  is the Fermi level which depends on the voltage of the contacts,  $\kappa_B$  is Boltzmann constant, T the temperature of the contacts and the subscripts refer to the contact. The Fermi function is a probabilistic description of whether a given energetic state should be filled with an electron or not, and since the contacts are connected to a battery they will try to maintain this equilibrium condition by providing any needed electrons or removing them.

If one considers that the general expression for the number of carriers at every energy level is given by:

$$N(E) = D(E)f(E) \tag{2.3}$$

where D(E) is the density of states, then the differential change of the number of carriers at each contact (assume electrons for simplicity) due to a differential change in the Fermi

Figure 2.1: Current flow due to different Fermi functions.

function due to an applied voltage can be written as:

$$N_{1,2}(E)dE = D(E)f_{1,2}(E)dE (2.4)$$

If it is assumed that all non equilibrium carriers reach the opposite contact, then the rates for the number of electrons injected or extracted per unit time between the contacts and the channel can be written as:

$$\frac{dN_{1,2}(E)}{dt} = \frac{N_{1,2}(E) - N_0(E)}{\tau(E)}$$

(2.5)

where  $\tau(E)$  is the transit time and assumed to be the same for both contacts, and  $N_0(E)$  is the number of electrons in the channel. From the rate equations above as a starting point, the electrical current in the channel can be written using Landauer's expression for conductance as follows [5]:

$$I = \frac{2q}{h} \int \frac{\lambda(E)}{\lambda(E) + L} M(E) (f_1(E) - f_2(E)) dE$$

(2.6)

here h is Planck's constant,  $\lambda(E)$  is the mean free path of the charge carriers, M(E) is

known as the number of conducting channels (modes) and is related to D(E), and L is the length of the conducting channel. For further reference and simplicity, written as:

$$I = \frac{2q}{h} \int T(E)M(E)(f_1(E) - f_2(E))dE$$

(2.7)

and for small biases after a Taylor's expansion and differentiation rewritten as:

$$I = V \underbrace{\frac{2q^2}{h} \int T(E)M(E) \left(-\frac{\partial f_0}{\partial E}\right) dE}_{G}$$

(2.8)

V is the applied voltage and  $f_0 \approx f_1 \approx f_2$ . Equation 2.8 is basically Ohm's law in a very general form. The advantage of describing current flow using the Landauer formalism is that it can be applied to any dimensional system and explaining current flow follows directly from thermodynamic arguments. There are some restrictions to equation 2.8 but the take away is that electric current flows due to a difference of the Fermi functions. A final and important remark is that as long as T > 0 K electrical conduction occurs from contributions mainly from energy states between  $E_{F,1}$  and  $E_{F,2}$ , this is seen in Figure 2.1 and in equations 2.7 and 2.8. Seeing electrical current flow in this frame will provide very important insight to understanding thermoelectric phenomenon.

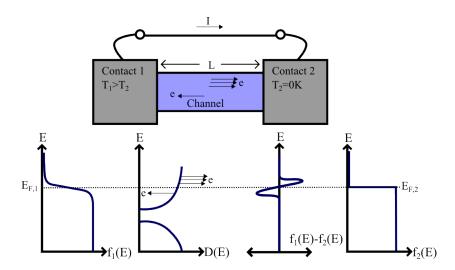

### 2.3 Electrical Current Due to Temperature Difference

From the previous section it is clear that electrical current will flow if either (or both) the Fermi level or the temperature on the contacts differ. The same elastic resistor from the previous section is again considered, but with two fundamental differences: this time with the contacts in a shortcut configuration such that  $E_F = E_{F,1} = E_{F,2}$  but at different temperatures. For simplicity the cold electrode is at  $T_2 = 0$  K with  $T_1 > T_2$ . A schematic

is shown in Figure 2.2.

Figure 2.2: Current flow due to different temperatures

Equation 2.7 can be combined with Figure 2.2 to realize that the contribution to the electrical current for energy levels below  $E_F$  is negative since  $f_1(E) - f_2(E) < 0$  for energies below  $E_F$ :

$$\frac{2q}{h} \int_0^{E_F} T(E)M(E)(f_1(E) - f_2(E))dE < 0$$

(2.9)

and similarly the contribution to the electrical current for energy levels above  $E_{\rm F}$  is positive since  $f_1(E) - f_2(E) > 0$  above  $E_{\rm F}$ :

$$\frac{2q}{h} \int_{E_F}^{\infty} T(E)M(E)(f_1(E) - f_2(E))dE > 0$$

(2.10)

The net direction of the current flow is determined by D(E), since  $M(E) \propto D(E)$ . In an n-type material with a parabolic band, D(E) is larger above  $E_{\rm F}$  than below and as a consequence more electrons flow in one direction than the other as sketched in Figure 2.2. For p-type semiconductors the model does not need to be modified; in the case of a p-type semiconductor, the Fermi energy is found in the valence band, and using the same analysis we can arrive at the conclusion that the direction of the electrical current will reverse. A couple of remarks that fall out from this model: 1) It is known from thermodynamics that heat is a high entropy form of energy; very disorganized, and so converting heat to electricity sounds like a tedious and inefficient process; one would have to effectively transfer every atomic vibration into electrical power. This idea is beautifully shown by the fact that D(E) does not differ by much below and above  $E_F$ . Although all together a large amount of current may flow, the net current output will be proportional to the difference in D(E) below and above  $E_F$  which is small for a parabolic band assumption. 2) From this last reason the motivation to lower scale and electronic band engineering structures becomes evident because since asymmetry in D(E) around  $E_F$  enhances the thermoelectric conversion process.

#### Seebeck Coefficient

The Seebeck coefficient  $\alpha$  is defined as  $\alpha = V_{\rm oc}/\Delta T$  where  $V_{\rm oc}$  is the open circuit output voltage of an isotropic material that is exposed to a small temperature difference  $\Delta T = T_h - T_c$  where  $T_h$  and  $T_h$  are the hot side and cold side temperatures at the two ends of the material where the voltage is measured. In some thermoelectric textbooks the Seebeck coefficient despite being one of the most important quantities in thermoelectricity is not derived from a solid state physics model (e.g. Boltzman theory) [6, 7, 8]. Perhaps the reason of avoiding the derivation lays in the mathematical complexity and assumptions needed to derive the Seebeck coefficient. Unfortunately this abstraction erodes insight into the inner workings of thermoelectricity. Using the Landauer approach it is possible to derive the Seebeck coefficient with much less mathematical rigor than it is required when deriving it from the Boltzmann transport equation. Here is not derived but shown how the Seebeck coefficient falls out from a solid state physics model with less mathematical rigor while retaining important information.

A starting point to see where how Seebeck coefficient comes out from the Landauer approach from is equation 2.7 since it is the general form describing electrical current. Since

the Fermi function is dependent on both the Fermi energy and temperature,  $f_1(E) - f_2(E)$  can be approximated using the first term of a Taylor's series expansion around  $E_F$  and T:

$$I = \frac{2q}{h} \int T(E)M(E) \left[ \frac{\partial f}{\partial E_F} \left( E_{F,1} - E_{F,2} \right) + \frac{\partial f}{\partial T} \left( T_1 - T_2 \right) \right] dE$$

(2.11)

allowing  $q\Delta V=E_{F,1}-E_{F,2}$  and after differentiation and rearrangement of terms:

$$I = \Delta V \underbrace{\frac{2q^2}{h} \int T(E)M(E) \left(\frac{-\partial f_0}{\partial E}\right) dE}_{G} + (T_1 - T_2) \underbrace{\left[-\frac{2q}{h} \int \frac{E - E_F}{T} T(E)M(E) \left(\frac{-\partial f_0}{\partial E}\right) dE\right]}_{G_s}$$

(2.12)

the first term is recognized as the electrical conductance (see equation 2.7) and the second term given the name  $G_s$ . Then the current is written in the more familiar way:

$$I = G\Delta V + G_s \Delta T \tag{2.13}$$

and given open circuit conditions a proportionality between  $V_{\text{oc}}$  and  $\Delta T$  appears which is the definition of the Seebeck coefficient

$$V_{\rm oc} = -\underbrace{\frac{G_s}{G}} \Delta T \tag{2.14}$$

Dividing the coefficients  $G_s$  and G from equation 2.12 shows how the Seebeck coefficient is related to some of the solid state properties of the material. This can also be shown from Boltzman theory, but in this case requiring less mathematical rigor.

$$\alpha = -\frac{k_B}{q} \frac{\int \frac{E - E_F}{k_B T} T(E) M(E) \left(\frac{-\partial f_0}{\partial E}\right) dE}{\int T(E) M(E) \left(\frac{-\partial f_0}{\partial E}\right) dE}$$

(2.15)

Lastly, noting that  $G_s = \alpha G$ , equation 2.13 is rewritten in the most familiar form:

$$I = G\Delta V + \alpha G\Delta T \tag{2.16}$$

#### 2.4 Heat Current

At the atomic level, temperature is a concept that is defined in terms of kinetic energy. When it said that something is hot, the atoms and electrons have gained high kinetic energy and it is said that magnitude of the atomic vibrations has increased for atoms and that valence electrons occupy higher energetic states. Heat is transported by the collective vibration of atoms, by the scattering of electrons and if electrical current is flowing, by electric current.

#### **Open Circuit Thermal Conduction**

When no electric current flows, phonons transport the heat in the form of lattice vibrations and electrons transport the heat by inelastic collisions. This is known as the linear approximation of Fourier's heat law [9]:

$$Q_{\text{open}} = -K_J \Delta T \tag{2.17}$$

with  $K_J = K_e + K_L$  where  $K_e$  is the electronic contribution and  $K_L$  the lattice contribution. Here care must be taken because while Fourier's law is defined in open circuit conditions, it is also valid in closed circuit conditions.

#### **Closed Circuit Thermal Conduction**

When electric current flows, electrons carry energy with them as they move along the crystal. The amount of energy that electrons carry due to current flow is measured with respect to the Fermi energy. Once again Landauer's expression for conduction in equation 2.7 is adapted easily to describe the heat that each electron will exchange at a the

abrupt interface of two materials, typically a metal-semiconductor interface. In this case each electron carries an amount of heat equal to  $E - E_F$  instead of an amount of charge q. Then replacing charge for heat, leads to almost the same expression as equation 2.7:

$$Q_{\text{closed}} = \frac{2}{h} \int (E - E_F) T(E) M(E) (f_1 - f_2) dE$$

(2.18)

As it was done with the Seebeck coefficient, expanding with a Taylor's expansion and differentiating equation (2.18), the electronic heat transport becomes  $[5]^1$ :

$$Q_{\text{closed}} = -\alpha T G \Delta V - K_E \Delta T \tag{2.19}$$

here the closed circuit thermal conductance  $K_E = \alpha \Pi G + K_J$  is introduced. Note that  $K_E$  includes the *open* circuit contribution  $K_J$ . This is because as mentioned earlier Fourier's law continues to be valid in closed circuit conditions. Finally using the substitution ( $\Pi = \alpha T$ ) where  $\Pi$  is the Peltier coefficient, and substituting  $\Delta V$  from equation (2.16), equation (2.19) becomes:

$$Q_{\text{closed}} = -\Pi I - K_J \Delta T \tag{2.20}$$

From equation (2.20) it follows that heat is transported when a material is subject to a temperature difference or to a voltage difference. The first term in equation (2.20) refers to the heat transported by the Peltier effect, which due to its importance in this work, will be have a dedicated section and the second term is the linear approximation of Fourier's law. Thermal conductivity measurements in short circuit conditions are very difficult, hence the thermal conductivity is usually measured in open circuit conditions ignoring the term  $\alpha\Pi G$ .

<sup>&</sup>lt;sup>1</sup>Page 88

## 2.5 Coupled Tranport: Electricity and Heat

A short but important note is the interrelation between heat and electronic transport. That means that if a  $\Delta T$  is applied to a material heat will flow, and (if connected to a load) electricity will flow as well. On the converse, if a  $\Delta V$  is applied, electric current will flow and as a consequence heat will flow as well. Hence, in semiconductor materials, heat transport implies electric transport and vice versa. Equations (2.16) and (2.20) can be rearranged and put in vector form next to each other and as follows from the application that Callen [10] made to Onsager's reciprocal relations [11], and most recently revisited by Goupil [9]:

$$\mathbf{J} = \sigma \mathbf{E} - \sigma \alpha \nabla T$$

$$\mathbf{J}_Q = \Pi \mathbf{J} - \kappa_J \nabla T$$

(2.21)

The relations in (2.21) describe thermal and electric transport for unipolar materials in near equilibrium conditions. Diffusion of charge carriers is neglected.

## 2.6 The Peltier Effect in Bipolar Semiconductors

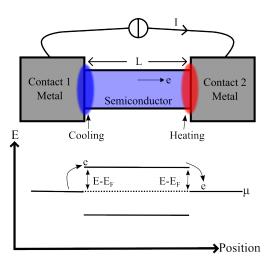

In the previous sections a Peltier coefficient  $\Pi$  resulted from the heat balance equations, but the physical mechanism was not explained and it will be seen in later chapters that the Peltier effect plays a critical role in this work, hence a full section is dedicated to it. When electric current flows through the interface of two materials with different band structure, such a metal-semiconductor interface, charge carries experience a change in energy with respect to the Fermi energy as they enter or leave the semiconductor and Peltier heating or cooling occurs as shown in Figure 2.3.

The amount of energy that each electron exchanges with the lattice at the interface is

Figure 2.3: Peltier effect in an n-type semiconductor

equal to  $E - E_F$ . This becomes clear when equation (2.15) is combined with Thomson's relation to write the Peltier coefficient:

$$\Pi = \frac{1}{q} \frac{\int (E - E_F) T(E) M(E) \left(\frac{-\partial f_0}{\partial E}\right) dE}{\int T(E) M(E) \left(\frac{-\partial f_0}{\partial E}\right) dE}$$

(2.22)

Figure 2.3 illustrates the Peltier effect and equation (2.22) the Peltier coefficient for unipolar conduction. The Peltier heat transport at an interface between two materials A and B is traditionally written as:

$$Q_{\text{Peltier}} = I \left( \Pi_A - \Pi_B \right) \tag{2.23}$$

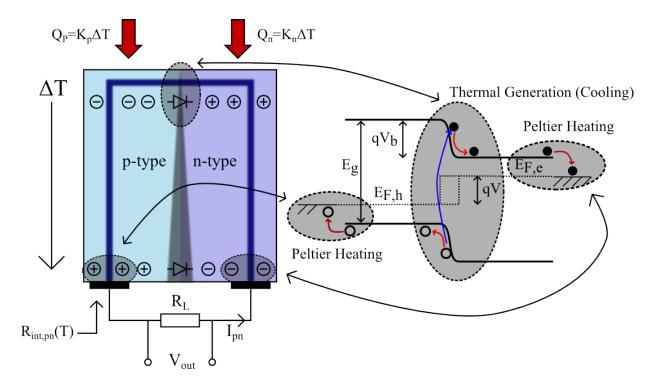

in equation (2.23) the assumption is that electric transport is unipolar and typically involves a metal-semiconductor interface and the Peltier coefficient of the metal is assumed to be zero. Despite extensive research and numerous publications by Gurevich and his collaborators, a question that remains open is the full description of the Peltier effect and heat fluxes in bipolar transport such as in a PN junction [12, 13, 14, 15, 16, 17].

If a bipolar device is considered, such as a PN junction, it is no longer possible to directly apply equation (2.23) to the metal-semiconductor and semiconductor-semiconductor inter-

faces, and a much more difficult case opens where special care needs to be taken to account for minority charge carriers. Amongst the first to identify this were R.N. Hall [18] in 1961 and W. Bullis in 1963 [19]. The Peltier effect can have 3 special cases in PN junctions and they are discussed in the following to show the different treatment that can be given to the thermoelectric phenomena of a PN junction.

#### Case 1: Non-Radiative Recombination

This is perhaps the case that fits best to the PN junctions discussed in this work, as there is no electroluminescence. In this case it is assumed that the n-type and p-type regions of the diode are much larger than the minority charge carrier diffusion length, and that all minority charge carriers recombine and releasing their energy as heat at the junction. For ease of discussion, it is assumed that they recombine in the space charge region of the diode, and ohmic voltage drops are ignored. Consider Figure 2.4 (only electrons are

Figure 2.4: Non-radiative recombination: the blue arrows indicate cooling while the red arrow indicates heating.

shown). At the contacts, the Peltier effect does not change with respect to the previous discussion, only the quasi-Fermi energies for electrons and holes  $E_{F,e}$  and  $E_{F,h}$  need to be considered instead of the Fermi energy  $E_{F}$ . However, at the junction each electron must absorb heat to overcome the built in potential barrier  $qV_{b}$ , and as it recombines, it releases the energy  $E_{g}$  which gets absorbed by the lattice leading to a localized heating of the junction. Hence the heating mechanism at the junction is technically not a Peltier effect, but a non-radiative recombination heating. It is interesting to note that this effect

is dependent on the applied Voltage V since it controls the built in barrier height. Given no radiative recombination the junction heating can be expressed as [20, 7]

$$Q_{\text{recomb}} = I \frac{E_g}{q} - I \left( V_b - V \right) \tag{2.24}$$

It is important to note that a Peltier coefficient does not appear in equation (2.24). That means that in the case of non radiative recombination, Peltier cooling occurs at the metal-semiconductor interfaces with special care to take the quasi-Fermi energy instead of the Fermi energy, while heating occurs at the PN junction.

#### Case 2: Radiative Recombination

The second case is radiative recombination. In a thought experiment if it is assumed that all recombined charge carriers produce photons, then the PN junction will see a refrigeration effect because the energy that charge carriers absorb from the lattice at the metal-semiconductor interface and at the potential barrier, is transferred to photons. And in fact in the highly ideal case, there are no sources of heat. In reality this is quite impractical because very high quantum efficiency (photon/electron) would be required for this type of cooling to be larger than the heating mechanisms (Joule heating and non-radiative recombination) [21]. However impractical, this shows that electrical energy can be transferred to electromagnetic energy leading to a cooling of the PN junction.

#### Case 3: Short-leg Approximation

The third case also shows a refrigeration effect at the PN junction but for different reasons. In the short-leg approximation the semiconductor legs are assumed to be shorter than the minority diffusion length such that recombination occurs at the contacts. That means that a cooling effect will be present at the PN interface as charge carriers overcome the potential barrier, but since the semiconductor material is shorter than the minority diffusion length, the charge carriers diffuse all the way to the ohmic contacts leading to a

net cooling of the PN junction and heating of the metal-semiconductor interfaces [22, 23].

#### 2.7 The Thomson Effect

It is noted and shown in [9] that in unipolar semiconductors the separation of the Thomson and the Peltier effect is artificial, and that they refer to the same effect which is a gradient of the Seebeck coefficient. Traditionally when spoken about the Peltier effect, the gradient in  $\alpha$  comes from having two different materials. However when the temperature gradient is steep enough,  $\alpha(T)$  will vary spatially, and differential slides of the material can be thought of as "different" materials.

Taking the divergence of the heat flux  $\mathbf{J}_Q$  gives

$$\nabla \cdot \mathbf{J}_Q = T\mathbf{J} \cdot \nabla \alpha + \mathbf{J} \cdot \mathbf{E} - \frac{J^2}{\sigma} - \nabla \cdot (\kappa_L \nabla T)$$

(2.25)

where the term  $T\mathbf{J} \cdot \nabla \alpha$  refers to the Peltier-Thomson term, and the other terms are the familiar expressions for electrical work, and electrical dissipation and heat conduction. Looking closer at the heat production from the Peltier-Thomson term one finds that

$$T\mathbf{J} \cdot \nabla \alpha = \mathbf{J} \cdot (\nabla \Pi - \alpha \nabla T) \tag{2.26}$$

and from equation (2.26) it becomes evident that the Peltier-Thomson term can take two forms: the first, in isothermal conditions the gradient in  $\Pi$  comes from the interface of two different materials,

$$\mathbf{J} \cdot (\nabla \Pi - \alpha \nabla T) = \mathbf{J} \cdot \nabla \Pi \tag{2.27}$$

equation (2.27) is related to the Peltier effect. A second term appears when a homogeneous

material under a temperature gradient is considered. In that case

$$\mathbf{J} \cdot (\nabla \Pi - \alpha \nabla T) = \mathbf{J} \cdot \left(\frac{d\Pi}{dT} - \alpha\right) \nabla T \tag{2.28}$$

and equation (2.28) is related to the Thomson effect. However both terms fall out from the same expression, hence the "artificial" separation. Typically, the Thomson effect is ignored because the theoretical models, the Landauer model and Onsager's relations in this case are based on a linear approximation for small disturbances which make use of temperature independent properties. In this work large temperature differences are applied, so care needs to be taken because although not treated explicitly, Thomson effects might be present.

## 3 Conventional Thermoelectric

**Generator: TEG**

Education is an admirable thing, but it is well to remember from time to time that nothing that is worth knowing can be taught.

Oscar Wilde

## 3.1 Efficiency of the Thermoelectric Process

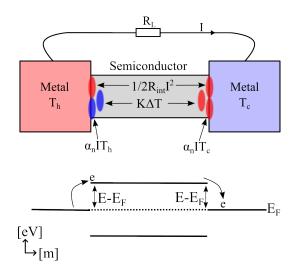

Although Altenkirch is credited as the first to inquire about the efficiency of the thermoelectric process in 1909 [24], Ioffe is credited as being the first to begin experimenting in the 1950's with the characterization of thermoelectric materials and devices to produce electricity using the thermoelectric figure of merit as it is known today [25, 26]. Before discussing a high temperature thermoelectric generator (TEG) as a device, the thermoelectric properties of the bulk materials is examined in the context of a constant property model (CPM). As seen in section 2.5 heat transport implies electronic transport and vice versa. This transport coupling makes thermoelectricity a challenging and interesting field. If a monopolar, isotropic material (in this case an n-type semiconductor) with resistance  $R_{int}$  and thermal conductance K is subject to a small temperature difference  $\Delta T = T_h - T_c$  and connected to a load resistance  $R_L$ , an electric current I will flow and from a one dimensional heat equation the different heating and cooling effects result.

In this case the efficiency of the thermal to electric conversion  $\eta$  is simply the ratio of the electrical power delivered at the load  $R_L$  and the heat extracted from the heat source on the hot side contact:

$$\eta = \frac{P_{\text{out}}}{Q_{\text{in}}} = \frac{I^2 R_L}{Q_{\text{peltier}} + Q_{\text{conduction}} - Q_{\text{joule}}}$$

(3.1)

Each term in the denominator of equation (3.1) is schematically shown in figure 3.1 where it is assumed that all heat transfer occurs at the electrodes. Considering the heat extracted at the hot side the efficiency can be written as:

$$\eta = \frac{R_L I^2}{\alpha T_h I + K\Delta T - \frac{1}{2} R_{\text{int}} I^2}$$

(3.2)

Figure 3.1: Heat fluxes in an n-type semiconductor. Heating is indicated in red and cooling in blue.

Equation (3.2) describes an ideal case for near equilibrium conditions and does not take into account convection and radiation transport. This equation is important because the same approach will be taken in order to describe the PN-TEG. After differentiation the maximum possible efficiency at a given  $\Delta T$  becomes [9]:

$$\eta_{\text{max}} = \frac{\Delta T}{T_h} \frac{\sqrt{1 + zT} - 1}{\sqrt{1 + zT} + \frac{T_c}{T_h}}$$

$$(3.3)$$

The first term is the Carnot efficiency, and zT is the widely used thermoelectric material figure of merit defined as:

$$zT = \frac{\alpha^2 \sigma}{\kappa_J} T \tag{3.4}$$

The figure of merit serves as very important parameter because it is a material property that allows different materials to be compared with respect to their potential to be used in thermoelectric devices.

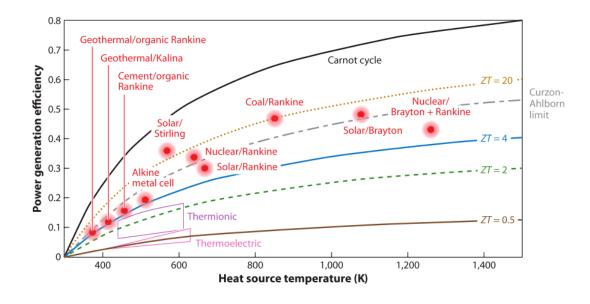

Figure 3.2: Efficiency of the thermoelectric process with  $T_c = 300K$ . From ref. [2].

Figure 3.2 puts the efficiency of the thermoelectric process into perspective with other heat engines. It is then obvious that to achieve a good thermoelectric efficiency, a large  $T_h$  and a large zT are required. But realizing a material with a high zT is not easy due to the

strong coupling and sometimes inverse relationships of the transport parameters  $\alpha, \sigma, \kappa$ . This is evident in the empirical but not precise Wiedemann-Franz law:

$$\kappa_e = \sigma L_H T \tag{3.5}$$

Where  $L_H$  is the Lorentz number. That means increasing  $\sigma$  increases  $\kappa$ . Moreover, there is an inverse relationship between the Seebeck coefficient and the electrical conductivity. This can be seen in equation (2.15). Hence, there is typically an optimal point with respect to the doping concentration of some semiconductors where the three transport coefficients yield the highest zT.

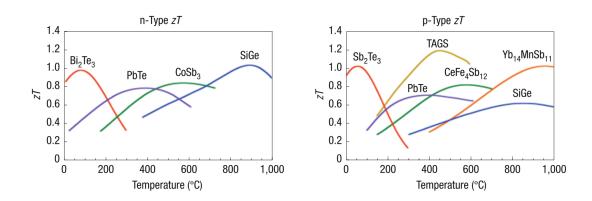

In the last years there has been an evolutionary approach to increasing zT and with quite success zT has gone from a peak of approximately 0.5 in the 1950s to a range between 1-2 (with some cases above 2) at the beginning of 2010 largely based on alloying and nanostructuring [27, 28, 2, 29]. It is pointed in [30] and shown in Figure 3.3 that most commercial materials today have a figure of merit of that peaks approximately at a value of 1, and most of these materials are measured in temperatures below 600°C.

Figure 3.3: Summary of zT for different comercially available materials. From ref. [30].

Therefore the efficiency on thermoelectrics limited by an upper limit on the operating temperature and the figure of merit. It seems then safe to say that a realistic value of the material figure of merit today is in the range of 0.5-1 and this sets the maximum theoretical efficiency of a thermoelectric generator in the range of 2-8% as seen in Figure 3.2. There are however efforts develop concentrated solar thermoelectric generators that reach a 15% efficiency [31].

# 3.2 From a Thermoelectric Material to a Conventional Thermoelectric Generator

There are far more aspects that can be mentioned in this work that need to be considered to make the transition from a thermoelectric material to a thermoelectric device. For example geometrical optimization of the thermoelectric legs [32, 33], of the heat exchanger [34, 35], and the electrical contacts [36], as well as the thermal and electrical load matching conditions [37, 38]. Although thermoelectric modules are commercially available today, they are mainly used as solid state coolers.

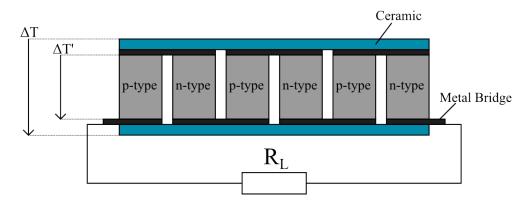

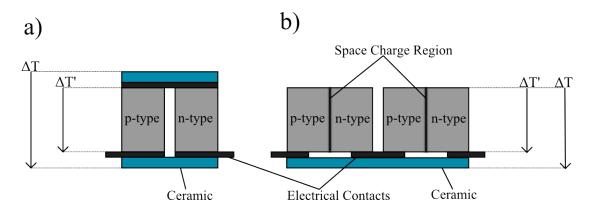

Figure 3.4: Architecture of a conventional TEG noting that  $\Delta T > \Delta T'$ .

A conventional thermoelectric generator (TEG), is traditionally described as alternating n-type and p-type semiconductor elements that are electrically connected in series and thermally connected in parallel as shown in Figure 3.4. A device figure of merit can be written by taking the effective electrical and thermal conductances as well as an effective

device Seebeck coefficient:

$$ZT = \frac{G_{\text{TEG}}\alpha_{\text{TEG}}^2}{K_{\text{TEG}}}T\tag{3.6}$$

In this definition of the device figure of merit  $G_{\text{TEG}}$  is the device electrical conductance and includes the parasitic resistances coming from the electrical contacts and the metal bridges,  $K_{\text{TEG}}$  is the device thermal conductance including parasitic effects, and  $\alpha_{\text{TEG}}$  can be approximated as the sum of the Seebeck coefficients of both materials. With these considerations the maximum efficiency of a TEG is written in basically the same form as for a bulk material:

$$\eta_{\text{max,TEG}} = \frac{\Delta T'}{T_h} \frac{\sqrt{1 + ZT} - 1}{\sqrt{1 + ZT} + \frac{T_c}{T_h}}$$

(3.7)

where care is taken to note that  $\Delta T'$  is the temperature drop across the semiconductor legs, as shown in Figure 3.4. A calculation of ZT as it appears in equation (3.6) would require the measurement of convoluted parameters such as  $G_{\text{TEG}}$ ,  $\alpha_{\text{TEG}}$ ,  $K_{\text{TEG}}$ , all of which are very difficult to measure individually in a TEG. For these reasons the device ZT is usually obtained by measuring the ratio of  $P_{\text{out}}/Q_{\text{in}}$  or by the Harman technique as described in section 6.3.1.

As mentioned in this section there are many technological and theoretical aspects to consider when bridging the gap between a material and a device. One aspect that is important in the operation of a PN-TEG is the issue of thermal matching. As shown in Figure 3.4 a temperature drop occurs at the substrate and this is of course not desired, and a large mismatch of the thermal conductances of the thermoelectric material and the substrate considerably hinders the power output as shown in the next section.

## 3.3 Thermal Matching: The TEG in Operating Conditions

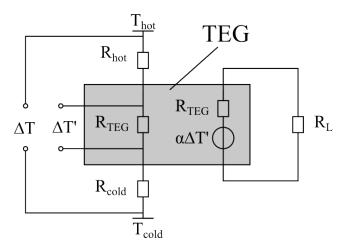

It has been pointed out that geometrical, cost optimizations and operating conditions need to be considered in order to continue to bring the technology forward [39, 40, 41]. In this section the impact of the ceramic substrates is considered. Analogous to electrical current, heat current can be modeled using thermal resistances as resistors and temperature differences as potential differences.

In the case of a TEG, the thermal resistances  $R_{\text{hot}}$  and  $R_{\text{cold}}$  arise from the substrates (see Figure 3.4) and the simplified equivalent thermal and electrical circuits are shown in Figure 3.5. That means that the total contact thermal conductance becomes  $K_{\text{contact}}^{-1} =$

Figure 3.5: Thermal (left) and electrical (right) circuits for a TEG in operating conditions.

$K_{\text{hot}}^{-1} + K_{\text{cold}}^{-1}$ , and the temperature drop across the semiconductor legs is written by the voltage divider rule

$$\Delta T' = \frac{K_{\text{contact}}}{K_{\text{TEG}} + K_{\text{contact}}} \Delta T \tag{3.8}$$

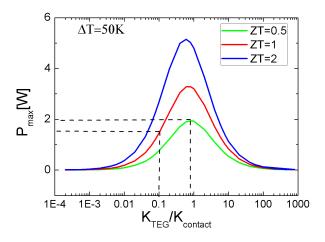

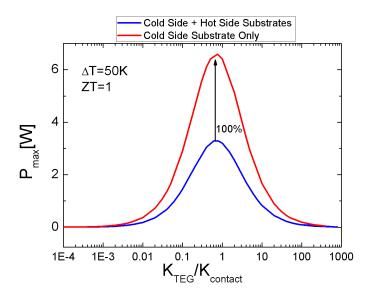

and provided that the electrical load resistance is matched to the internal electrical resistance, the maximum power output can be written as a function of the thermal conductances [39]:

$$P_{\text{max}} = \frac{(K_{\text{contact}}\Delta T)^2}{4(K_{\text{TEG}} + K_{\text{contact}})T} \frac{ZT}{1 + ZT + K_{\text{contact}}/K_{\text{TEG}}}$$

(3.9)

Equation (3.9) allows the evaluation of the power output as a function of the thermal conductances of the TEG including the thermal losses at the substrates at a given operation with fixed  $\Delta T$  and ZT. Thermal matching can play a role as important as the actual value of ZT. Equation (3.9) is plotted in figure 3.6 and shows that a TEG with optimized thermal matching and low figure of merit ZT = 0.5 can deliver more power output than a TEG with ZT = 1 and non-optimized thermal matching.

The thermal matching ratio that separates the two points in Figure 3.6 is a factor of 8 (it is assumed that  $R_{\rm hot} = R_{\rm cold}$ ). Hence the substrates play a critical role for a device in operating conditions because there is a temperature drop across each of the substrates. Hence the optimization of the thermal conductances is one of the device level optimizations that needs to be carefully considered in thermoelectric devices [42, 43]. It will be shown that in the new concept demonstrated in this work, the hot side substrate is not required, thus providing a tremendous advantage from thermal matching point of view, among other aspects that will be later discussed.

Figure 3.6: Maximum power as a function of the ratio of the thermal conductances. An optimized device with a lower figure of merit can outperform a device with a higher figure of merit if the thermal contacts of the latter are not optimized.

# 3.4 High Temperature Thermoelectrics

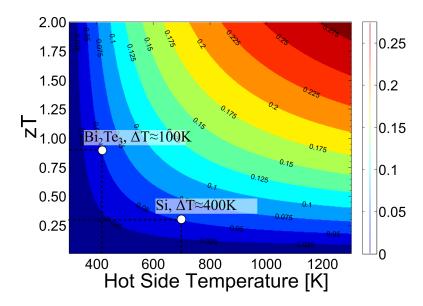

The first term in equation (3.7) is the Carnot efficiency limit and it tells us that  $\Delta T$  is as important as ZT. Therefore high temperatures are a necessary condition for a high efficient thermal to electrical conversion. In light of this a strategy that can be pursued is to take a known material such as silicon that has been studied for many years, is abundant, non toxic, and compatible with actual semiconductor technologies, and operate it in a large  $\Delta T$ . However this strategy does not apply only to silicon, recently Half-Heusler materials have been shown excellent thermoelectric properties at temperatures above 600°C for both n and p-type doping [44, 45].

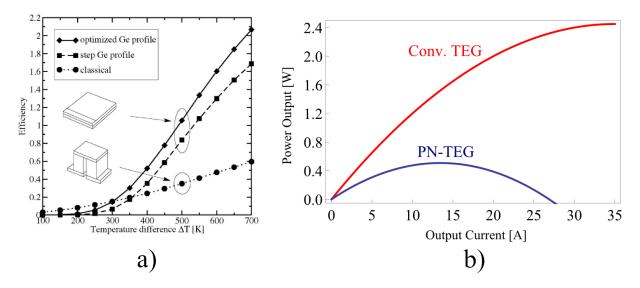

A two dimensional plot of equation (3.7) in Figure 3.7 shows that a TEG with a low ZT = 0.26 would yield the efficiency as a commercially available  $\text{Bi}_2\text{Te}_3$  TEG with ZT = 0.8 given that  $\Delta T$  is large enough. A high efficiency number is necessary for the scientific race, but ultimately what determines the scope of the market of an energy technology is the cost of W/\$ and combining waste energy which has no production cost with a low cost material such as silicon could provide the necessary ingredients to make thermoelectricity a more attractive technology.

# 3.4.1 Silicon as a High Temperature Material

A material that has the potential to operate at high temperatures is silicon. In addition to being non-toxic and abundant, silicon is stable at high temperatures, and it is the most widely used semiconductor in the industry, which means that processing technologies that are already established and can be borrowed to process silicon, rendering the processing cost lower.

Silicon fulfills the requirement for high temperature stability. There are however challenges that need to be addressed before it can be incorporated in a high temperature device.

Figure 3.7: Efficiency of the thermoelectric process with  $T_{\rm c}=300K.$

Firstly, intrinsic silicon is not a natural high performance thermoelectric material with a peak zT=0.2 at 800 K. However nanostructuring has achieved considerable reductions in the thermal conductivity resulting in increased zT values.

The highest zT values reported on silicon have been accomplished by nanowires. There are reports of silicon nanowires with values as high as zT=1 at low temperatures (200 K) [46] and reports of silicon nanowires with peak zT=0.6 at 300 K [47]. Silicon nanowire structures are further away from integration into a device than bulk materials for two important reasons: 1) Lack of corroboration or inter-laboratory reproducibility of the results due to the highly specific preparation and measurement techniques and 2) technological difficulties to integrate a nanowire TEG. Despite these difficulties silicon TEGs based on nanowires have been reported [48].

At the time of writing bulk materials seem to have the highest prospect to be integrated into a device, because they overcome to a higher degree the two challenges that nanowires still have to overcome, and offers other advantages such as scalability [49]. Nanostructuring (by nanostructuring we refer to nano-domains with a crystalline structure bounded by grain

boundaries) and/or alloying have allowed to increase the peak of both n-type and p-type bulk silicon to  $zT \approx 0.7$  [50, 51, 52], and even values as high as zT = 1.2 [53].

For these reasons, nanostructured silicon is the material used in this work. But if high temperature operation is desired the metallic contacts may be subject to undesired diffusion processes or alloying of the metal with thermoelectric material. Kessler et al. developed an anti-diffusion nickel layer to produce high temperature electrical contacts that were stable up to 600 °C [36, 54].

Higher operation temperatures would increase the Carnot efficiency and also would bring silicon into a temperature domain where its zT value peaks. A question that arises from this consideration is: If high  $\Delta T$ s are desired, how adequate is the constant property model in the description of the thermodynamics? since the derivations of the efficiency were done in a near equilibrium conditions.

#### Reduction of Thermal Conductivity Through Nanostructures

Much of the just mentioned progress in silicon as a thermoelectric material is a consequence of a significant reduction in the thermal conductivity without compromising the electrical conductivity. From the figure of merit it is clear that a good thermoelectric material should have a high electrical conductivity and a low thermal conductivity. This is intuitive; we would like to extract as many charge carriers as possible while rejecting as many phonons as possible. This concept is sometimes referred as the "phonon-glass, electron-crystal" idea [6] because glass has a very low thermal conductivity, while crystalline semiconductors have the highest carrier mobility.

The strategies used to reduce the thermal conductivity can be understood in light of the electrical current equation (2.7) and the heat current equation (3.10) where the subtle difference between them is that in equation (3.10) each phonon carries an energy  $\hbar\omega$  and follow a Bose-Einstein energetic distribution  $n=1/(\exp(\frac{\hbar\omega}{\kappa_B T})-1)$ . With this in mind it becomes clear that a strategy to reduce the lattice thermal conductivity is to reduce

the phononic mean free path  $\lambda_{\rm ph}$ , or in other words to increase the scattering centers for phonons.

$$Q_{\text{open}} = \frac{1}{h} \int (\hbar \omega) \frac{\lambda_{\text{ph}}(\hbar \omega)}{\lambda_{\text{ph}}(\hbar \omega) + L} M_{\text{ph}}(\hbar \omega) (n_1 - n_2) d(\hbar \omega)$$

(3.10)

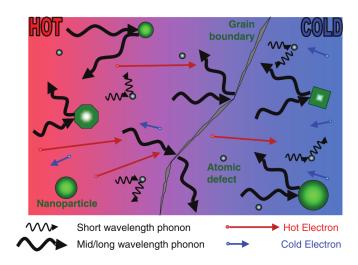

Figure 3.8: Schematic of the different phonon scattering mechanisms within a thermoelectric material. Point defects scatter short wavelength phonons while embedded nanoparticles and grain boundaries scatter longer wave phonons. From Ref. [27].

There are many strategies to reduce the phononic mean free path. For example alloying effectively introduces atomic defects that scatter phonons selectively over electrons, and in fact commercial thermoelectric devices are built on alloys of Bi<sub>2</sub>Te<sub>3</sub> and Sb<sub>2</sub>Te<sub>3</sub> [55]. Alloys of SiGe have also shown a reduction of the thermal conductivity for both doping types [53, 56, 52]. Other strategies are the inclusion of nanoparticles into the lattice or the introduction of grain boundaries in nanocrystalline materials [27]. Each scattering mechanism (atomic defect, nanoparticle, grain boundary) is more likely to scatter phonons with a given wavelength as shown in the schematic in Figure 3.8.

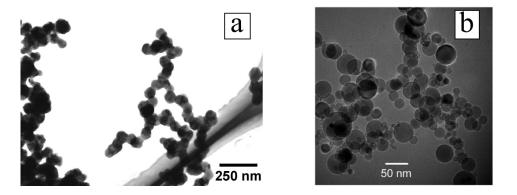

In this work the strategy is to introduce grain boundaries by compacting doped nanoparticles into bulk nanocrystalline silicon to reduce the lattice thermal conductivity. Reviews on nanostructured thermoelectrics can be found in references [27, 28, 57]. Bulk nanos-

tructured silicon in particular has been shown to have superior thermoelectric properties compared to crystalline silicon due to a reduction of the thermal conductivity by phonon scattering at grain boundaries [50, 29, 53]. Hence, the PN junctions used as thermoelectric generators are made from nanostructured bulk silicon.

# 3.4.2 Large Temperature Gradients and Temperature Dependent Model

A thermoelectric generator would be ideally operated in a large temperature difference, however the constant property model assumes small temperature differences because it allows the calculations for efficiency to be solved analytically. If large temperature gradients are applied, it is necessary to consider the temperature dependency of the transport coefficients:  $\alpha(T)$ ,  $\sigma(T)$ ,  $\kappa(T)$ .

Today it does not appear to be a clear consensus on how to tackle this issue. In one approach Borrego [58] showed using the same approach used in section 3.1 that it is possible to arrive to a material figure of merit  $z_{\text{eff}}$  which considers the temperature dependency of the transport coefficients

$$z_{\text{eff}} = \frac{\left(\int_{T_c}^{T_h} \alpha(T)dT\right)^2}{\Delta T \int_{T_c}^{T_h} \rho(T)\kappa(T)dT}$$

(3.11)

Note that in equation (3.11) the multiplication on both sides by the average temperature has been left out because the average temperature in a system where large  $\Delta T$ s are allowed becomes overly defined, and it depends itself on the material parameters. Borrego's idea points in the right direction, however he did not consider the Thomson effect, which can be left out in the constant property model, but not in the temperature dependent property model as shown in section 2.7.

In a series of papers Min et al. developed an alternative method to measure the figure

merit in more realistic operation conditions (i.e. large  $\Delta T$ s) in which he took into account the Thomson effect [59, 60, 61]. He arrived to the following expression for  $z_{eff}$ :

$$z_{\text{eff}} = \frac{\sigma_{\text{eff}} \left(\alpha_{\text{h}} - \beta \Delta T / 2T_{\text{h}}\right)^{2}}{\kappa_{\text{eff}}}$$

(3.12)

in this case  $\alpha_h$  is the value of the Seebeck coefficient at the hot side boundary,  $\beta$  the Thomson coefficient, and  $\sigma_{\text{eff}}$  and  $\kappa_{\text{eff}}$  are the effective electrical and thermal conductivities at a given  $\Delta T$ . There are however some problems with equation (3.12) because it was derived assuming that the open circuit thermal conductivity and the closed circuit thermal conductivity are equal  $\kappa_j = \kappa_E$ , and it fails to explain experimental data [59, 60].

The best approach to attack the issue of temperature dependent coefficients seems to be the Compatibility approach introduced by Snyder and Ursell [62, 63]. In this approach the starting point for the efficiency consideration takes a general form that does not require assumptions of near equilibrium conditions meaning that also Thomson transport is accounted for [62]:

$$\eta = \frac{P_{\text{out}}}{Q_{\text{in}}} = \frac{J \int_{T_c}^{T_h} \alpha dT - J^2 \int_{0}^{l} \rho dx}{J T_h \alpha_h + \kappa_h \nabla T_h}$$

(3.13)

Here the subscript h stands for the hot side heat boundary, and l for the length of the material. The compatibility approach has been used to optimize the local efficiency of the thermoelectric material by choosing the best local properties [63, 64]. However it would be interesting to see an optimization with respect of  $\Delta T$  for a temperature dependent material.

There does not seem to be an established agreement on how to attack the problem of temperature dependent transport coefficients [8], and in this work large temperature gradients are used which means that in the presentation of the results care is taken to consider that the results cannot be immediately compared to measurements done in near equilibrium conditions.

# 3.5 Summary: Conventional TEG

In this chapter the derivation of the thermoelectric process efficiency in the framework of a near equilibrium constant property model is shown to be important to be able to put the thermoelectric energy conversion process in context with other technologies. The thermoelectric figure of merit is a necessary but not sufficient indicator for the potential that a material has to perform as a thermoelectric material.

Aspects involving the transition from a thermoelectric material to a thermoelectric device are taken into account, and here it is pointed out that it can be misleading to concentrate all efforts and to evaluate the potential of a material merely on its zT value. There are other aspects such as the Carnot efficiency, and cost that need to be included to make a complete evaluation of a given thermoelectric material.

It is explained that silicon is chosen as a thermoelectric material because of its abundance, non-toxiticy, familiar processing technologies, and because recent advances in nanotechnology have led to a reduction in the thermal conductivity through nano-crystalls. Finally it is pointed out that if a material or device is operated in large temperature gradients, care needs to be taken when using the derivation of efficiency and zT as they might no longer seem appropriate.

# 4 New Device Architecture: PN-TEG

Efficiency is doing things right. Effectiveness is doing the right things.

Peter Drucker

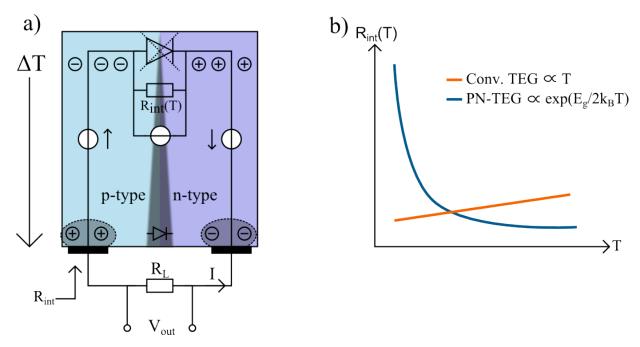

# 4.1 Proposed Concept: PN-TEG

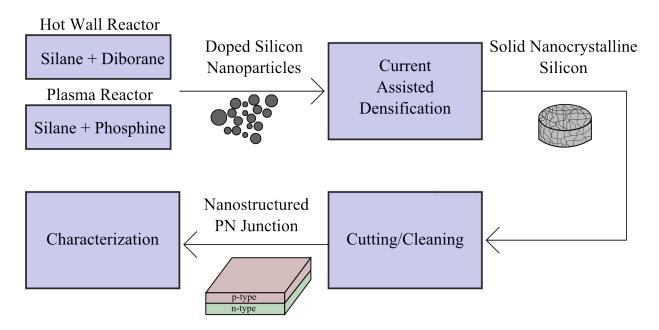

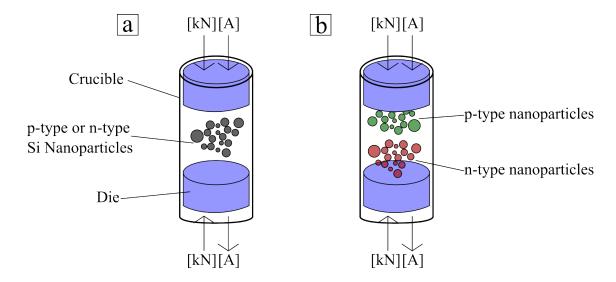

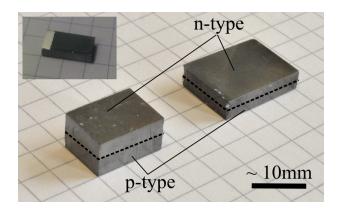

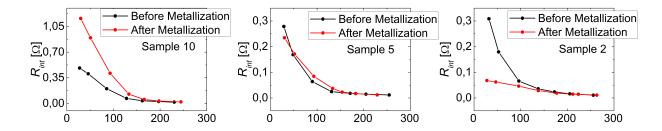

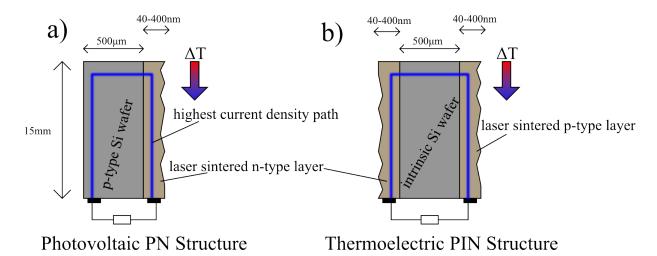

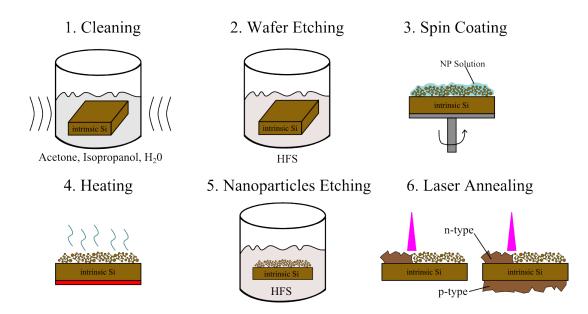

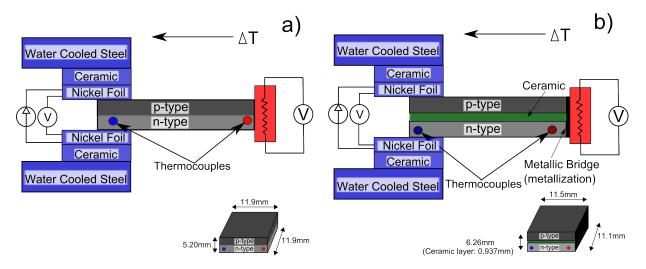

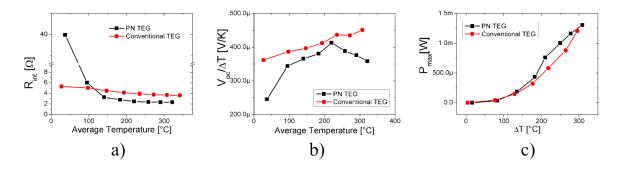

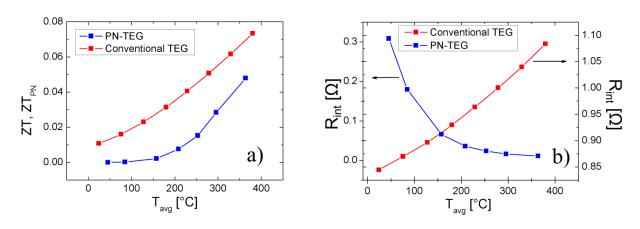

The heart of this work is the study of what we call a PN-TEG. The idea of a PN-TEG was formally proposed by Span et al. in a series of papers [65, 66, 67, 68] mainly with the idea to produce thin film technologies, but has also been independently investigated experimentally in bulk TEGs by [69, 70]. A PN-TEG is different form a conventional device because the electrical and mechanical connection between the n-type and p-type semiconductor legs is done by means of a PN junction as shown in Figure 4.1b.

The implications of the PN-TEG architecture are vast and condensed below. In the following chapters of this work each one of the following will be discussed.

#### • Advantages:

- 1. Electrical contacts and ceramic substrate are not required on the hotside.

- 2. Heat source can come in direct contact with the thermoelectric material, and higher hot side temperatures can be reached.

Figure 4.1: a) Conventional TEG architecture, b) PN-TEG architecture.

3. The fabrication process of a PN-TEGs is greatly simplified compared to that of a conventional TEG.

#### • Disadvantages:

- 1. At low temperatures, the space charge region acts like an electrical insulator limiting current flow.

- 2. As it will be shown, a PN-TEG develops internal electrical current vortices that reduce the power output.

#### • Theoretical Implications

- 1. The traditional figure of merit  $zT = (\sigma \alpha^2)/\kappa_J$  cannot be immediately applied to evaluate a PN-TEG.

- 2. Heat and electrical current do not always flow in the same direction, rendering the description of a PN-TEG a two dimensional problem.

- 3. A description of excess charge carriers due to thermal generation/recombination becomes non-trivial.

- 4. Peltier effects at the PN junction are not fully understood.

Having the electrical contacts exclusively on the cold side has the clear technological advantage that a metallization on the hot side and the substrate is not required, that means that the temperature losses across the hot side substrate are eliminated as shown in Figure 4.1a. As an example a plot of equation (3.9) in Figure 4.2 compares the maximum power output for a conventional device with cold and hot side substrates to a device with only one substrate. As seen, the power output for a conventional TEG would double if the thermal resistance is cut by half. Hence a tremendous advantage of a PN-TEG is the abscense of the hot side substrate and thermal losses. Bear in mind that Figure 4.2 describes a conventional TEG, not a PN-TEG.

Figure 4.2: Maximum power output plotted using equation (3.9). The thermal conductance  $K_{\text{contact}}$  was doubled from the blue line to the red line to mimic the absense of one of the substrates

In addition to the technological advantage of using one substrate, Wagner et al. suggested that the thermally generated charge carriers within the PN junction will contribute to the thermoelectric driving force suggesting that a PN-TEG should outperform a conventional device [65], but this claim remains an open question in this work. Despite the open question on the efficiency comparison, it is shown in this work that in addition to

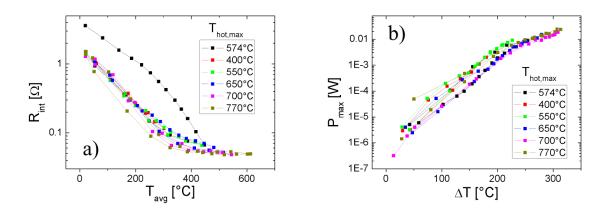

the tremendous technological advantages, nanostructured silicon PN junctions can work as thermoelectric generators, in a scalable manner, and can operate in temperature conditions that conventional commercially available generators are not able to operate. High temperature operation enables a higher Carnot efficiency and makes up for the relatively low figure of merit of silicon.

Although credit is given to Span et al. for the PN-TEG concept in their publications in late 2000 [65, 66, 67, 68]. Yang et al. recognized in 2001 that if a layer of p-type and n-type Bi<sub>2</sub>Te<sub>3</sub> are pressed together, the intrinsic region in the middle can be increasingly removed to approximate a conventional device leading to some of the technological advantages already mentioned [71, 69]. A PN structure was investigated as a thermionic/thermoelectric device in ref. [72] and theoretical work in [73, 74] explored a PN junction with a temperature gradient parallel to the junction interface, as it is done in this work, but with the difference that they were concerned exclusively in the internal current loops and did not consider the possibility of using the PN junction as a TEG.

# 4.2 PN-TEG Proposed Theory

One of the biggest challenges of developing a theoretical framework for the description of a PN-TEG the two-dimensional nature of the transport driving forces and hence a purely analytical description of the device is very difficult. So far a description of these type of systems seems only possible with numerical calculations as it has been previously done by others to describe such PN-TEG devices [68, 65, 66, 67, 73]. To aid in the theoretical description of the PN-TEG, Sebastian Angst is acknowledged with the development of a discrete Onsager network model which is used to provide much of the analytical description of the knowledge [75]. The proposed theory is divided into three subsections: Transport, Efficiency and Optimization.

## 4.2.1 Simulation Details: Discrete Onsager Network

The model here described is acknowledged to Sebastian Angst [75]. This model is used to test hypotheses and verify experimental results for conventional generators and PN-TEGs. The model is a discretization of Onsager's theory. The starting point of the model is the continuous form of equation (2.21) with the addition of an expression for Joule heating. The Electric current density, the heat current density and the volumetric heat production are written as [9]

$$\mathbf{J} = -\sigma \left( \frac{\nabla \varphi}{q} + \alpha \nabla T \right)$$

$$\mathbf{J}_{Q} = \alpha T \mathbf{J} - \kappa_{J} \nabla T$$

$$\nabla \cdot \mathbf{J}_{Q} = -\frac{\nabla \varphi}{q} \mathbf{J}$$

$$(4.1)$$

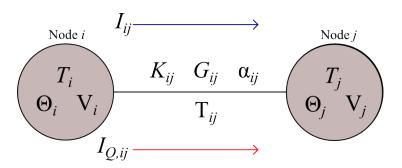

In the discretization every node is assigned a temperature T, an electrochemical potential  $\varphi$ , a specific heat capacitance  $\Theta$ , and every bond between two neighbors i and j is characterized by an electrical conductance  $G_{ij}$ , thermal conductance  $K_{ij}$ , average temperature  $T_{ij}$  and average Seebeck coefficient  $\alpha_{ij}$  as depicted in Figure 4.3.

Figure 4.3: A two node bond and its variables.

With this in consideration the electrical current between nodes is calculated as

$$I_{ij} = G_{ij} \left( \frac{\varphi_i - \varphi_j}{q} + \alpha_{ij} (T_i - T_j) \right)$$

(4.2)

in a similar fashion the heat current is calculated as

$$I_{q,ij} = K_{ij} (T_i - T_j) + \Pi_{ij} I_{ij}$$

(4.3)

with  $\Pi_{ij} = \frac{1}{2}(\alpha_i T_i - \alpha_j T_j)$ . Note that equations (4.2) and (4.3) are just discrete forms of the first two equations in (4.1). This model provides at tremendous tool in analyzing the internal distribution of the electrical current in a PN-TEG because temperature dependent parameters  $\alpha(T)$ ,  $\kappa(T)$ ,  $\sigma(T)$  can be implemented and it also provides first order approximations for the efficiency of a PN-TEG since the heat flow can be calculated in a simulation.

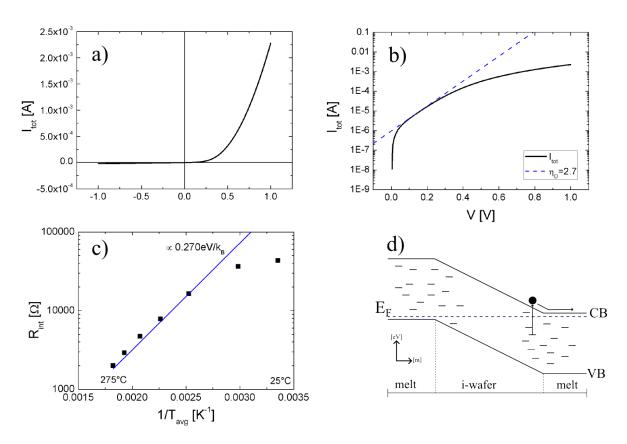

#### 4.2.2 Electrical Transport

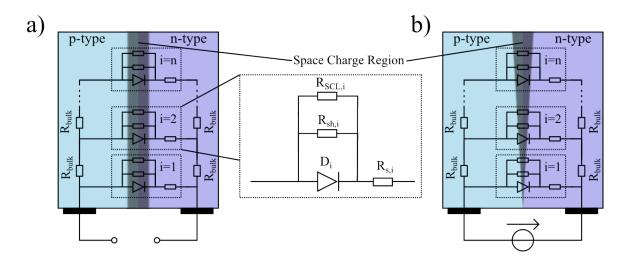

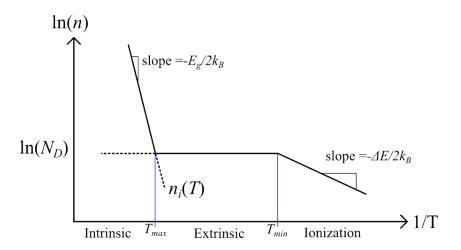

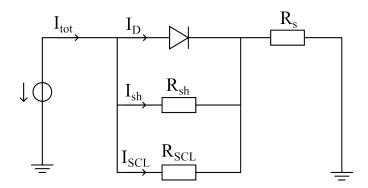

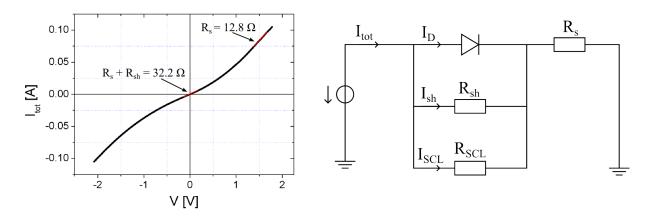

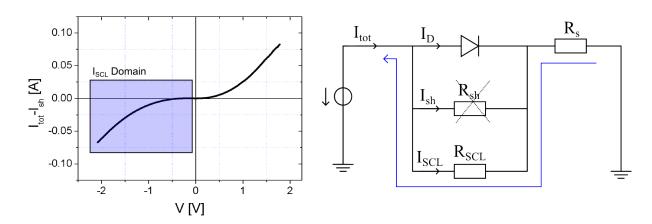

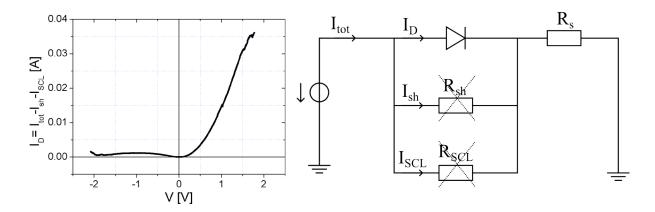

The description of a PN-TEG begins by considering a large area PN junction and breaking it into an array of differential elements because a larger temperature difference is desired, and it is well known from diode theory that the transport properties of a diode depend exponentially on temperature. The base model is given in thermodynamic equilibrium conditions ( $\Delta V = \Delta T = 0$ ); the PN junction is broken into differential diodes each with a linear shunt resistance  $R_{\rm sh}$ , a non-linear shunt resistance  $R_{\rm scl}$ , a series resistance  $R_{\rm s}$  and these elements are interconnected by a bulk resistance  $R_{\rm bulk}$ . In the junction of the two materials the space charge region is depicted as a shaded area as shown in Figure 4.4a.

If the PN junction is resting in thermal equilibrium, but biased with a voltage that is small enough to ignore Joule and Peltier effects and big enough to turn on the diode closest to the electrodes, the built-in potential and therefore the space charge region near the electrodes will shrink and the electrical current density will be higher near the electrodes as sketched in Figure 4.4b.

This treatment provides a limited general idea of the electrodynamics within the PN-

Figure 4.4: Electrical schematic of a PN junction in a) thermodynamic equilibrium and b) under a forward bias voltage.

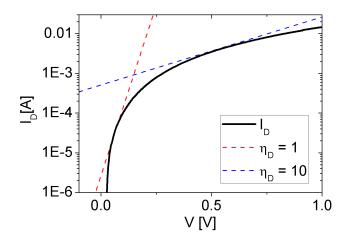

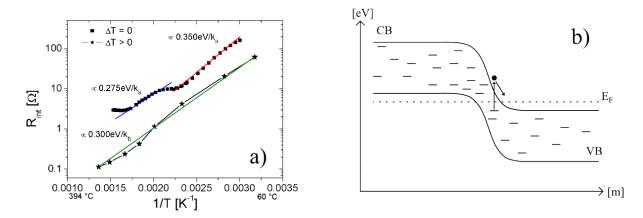

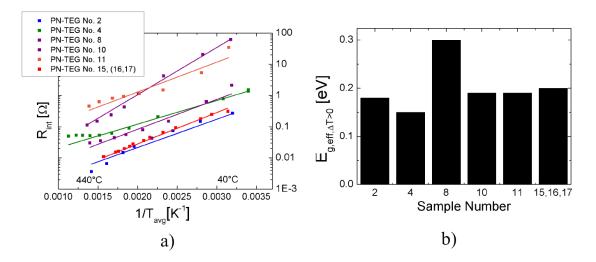

TEG, but such a treatment will prove crucial to understand thermoelectric effects. From this idea it is clear that the current density should be described in two dimensions, but for now we consider the macroscopic current I. Hence, the current across each diode element  $I_{D,i}$  can be approximated by adding the recombination and the diffusion currents given that  $V_i \gg \frac{k_BT}{q}$  [76]:

$$I_{\mathrm{D},i} \approx \underbrace{I_{\mathrm{diff}} \exp\left(\frac{qV_i}{k_B T}\right)}_{\mathrm{Diffusion Current}} + \underbrace{I_{\mathrm{R}} \exp\left(\frac{qV_i}{2k_B T}\right)}_{\mathrm{Recombination Current}}$$

$$I_{D,i} = I_0 \exp\left(\frac{qV_i}{\eta_D k_B T}\right)$$

$$(4.4)$$

where  $I_{\text{diff}}$ ,  $I_{\text{R}}$  and  $I_{0}$  are material specific constants,  $V_{i}$  the voltage drop across each diode and  $\eta_{\text{D}}$  is known as the ideality factor and it tells whether the current is dominated by diffusion of minority charge carriers or recombination within the space charge region.

The current across the non-linear resistor  $R_{SCL,i}$  is phenomenologically described by a space charge limited current [77], and the reasons for this are given in the Results Chapter.

$$|I_{\text{SCL},i}| = |V|^{\gamma+1}, \gamma > 0 \tag{4.5}$$

Finally the current across the linear resistances  $R_{\text{sh},i}$ ,  $R_{\text{s},i}$  are described by Ohm's law.

The most important take away from the discussion derived from Figure 4.4 is that the PN-TEG can be though of many diode elements connected in parallel, and that when a voltage bias is applied, electrical current will flow inhomogeneously, and close to the electrodes. The inhomogeneous current density means that analytical expressions to describe the electrical transport cannot easily be derived if at all possible. For example, how would an expression for the internal resistance look like? This is a critical point, and calls the necessity of numerical simulations, because this in turn means that the expressions needed to derive the efficiency of such a device are not available. This is discussed in detail in the Efficiency Section 4.2.6.

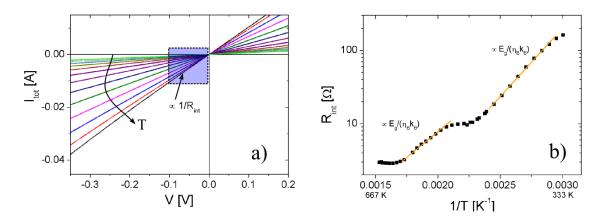

## 4.2.3 Temperature Dependence of Electric Transport

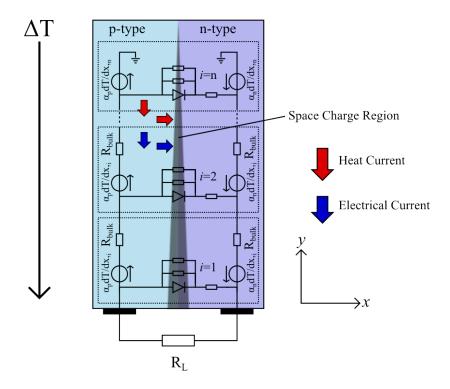

The next consideration is the following question: what happens to the electrical transport as a temperature gradient is applied to the PN junction turning it into a PN-TEG? An equivalent circuit of the PN-TEG under a temperature gradient is shown in Figure 4.5. In this schematic it is possible to see that electrical current flows in the x-direction, and that must mean that heat flows in the x-direction as well but the description of heat carried by bipolar transport is not well understood.

Another consideration is the appearance of differential voltage sources in the equivalent circuit, these voltage sources represent the thermoelectric driving force due to the Seebeck effect. The last point is that at large temperature differences the spatial symmetry of the space charge region is turned around; the space charge region becomes thinner on the hot end, and this changes the spatial current density map (compare Figures 4.4b and 4.5).

The reason for the shrinking of the space charge region on the hot end is due to an increase of intrinsic charge carriers. An indirect assessment of the space charge region can be carried by observation of the built-in voltage. The temperature dependent built in

Figure 4.5: Electrical schematic of a PN-TEG under a temperature difference.

voltage  $V_{\rm b}(T)$  of a non-degenerated diode is

$$V_{\rm b}(T) = \frac{k_B T}{q} \ln \left( \frac{N_{\rm A} N_{\rm D}}{n_{\rm i}^2(T)} \right) \tag{4.6}$$

where  $N_{\rm A}=N_{\rm D}=5\times 10^{19}\,{\rm cm}^{-3}$  are the acceptor and donor concentrations and are assumed to be constant over temperature. In order to calculate the temperature dependency of  $V_{\rm b}(T)$  it is necessary to consider the intrinsic charge carriers  $n_{\rm i}(T)$  that get thermally excited over the bandgap

$$n_{\rm i}(T) = \sqrt{N_{\rm c}(T)N_{\rm v}(T)} \exp\left(-\frac{E_{\rm g}(T)}{2k_BT}\right)$$

(4.7)

here  $N_{\rm C}(T)$  and  $N_{\rm V}(T)$  are the effective density of states at the conduction band and valence band respectively. For equation (4.7) one should consider the temperature dependency of the bandgap<sup>1</sup>

$$E_{\rm g}(T) = E_{\rm g}(0K) - \frac{\delta T^2}{T+\beta} \tag{4.8}$$

And finally, the temperature dependency of the effective density of states  $N_{\rm c}(T)$  and  $N_{\rm v}(T)$

$$N_{\rm c}(T) = 2\left(\frac{2\pi m_e^* k_B T}{h^2}\right)^{3/2} \tag{4.9}$$

$$N_v(T) = 2\left(\frac{2\pi m_h^* k_B T}{h^2}\right)^{3/2} \tag{4.10}$$

where  $m_{e,h}^*$  is the effective mass of electrons and holes respectively.

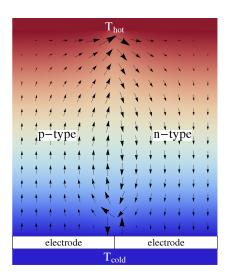

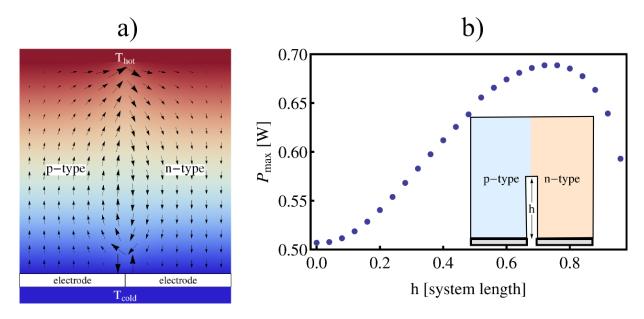

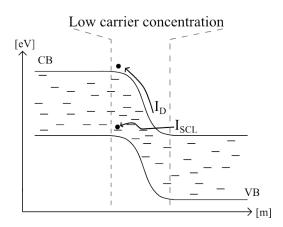

To get a general understanding of the electrodynamics of a PN-TEG a system consisting of ideal diodes with infinite shunt resistances is considered. A simulation of a PN-TEG using the model introduced in section 4.2.1 is shown in Figure 4.6a. In this Figure the temperature is coded using a blue to red scale for cold to hot. The temperature on the hot side is 1000 K and on the cold side 300 K. The size of the arrows is correlated to the magnitude of the electrical current density **J**. The built-in voltage  $V_b(T)$  for a highly doped ideal diode is calculated then using equations (4.6)-(4.10) and shown in Figure 4.6b and we note that for a highly doped system under large temperature differences, the difference in the built-in voltage between the cold side and the hot side can be of 0.45V. This spatially defined built-in voltage acts like an electrical "gate" that opens on the hot end of the PN-TEG and closes on the cold end of the PN-TEG.

Figure 4.6a shows that the electrical current crosses the PN junction through the open "gate" on the hot end of the device, while the closed "gate" on the cold end prevents that an internal current loop develops within the PN-TEG. The main reason for the spatially defined built-in voltage  $V_{\rm b}(T)$  is that the steep temperature gradient creates a steep gradient in the intrinsic charge carrier concentration  $n_{\rm i}(T)$ . As seen in Figure 4.6c the intrinsic

$<sup>^1</sup>E_{\rm g}(0K)=1.17\,{\rm eV}$  is the Bandgap of Silicon at 0K and the proportionality constants for Silicon  $\delta=4.9\times10^-4\,{\rm eV/K}$  and  $\beta=6.55\times10^2\,{\rm K}$  [78]

Figure 4.6: a) Electrical current density map for a PN-TEG with  $N_A = N_D = 5 \times 10^{19} \,\mathrm{cm}^{-3}$ . b) Built-in voltage  $V_{\rm b}(T)$  shows a reduced potential barrier on the hot side of the PN-TEG. c) The intrinsic carrier concentration  $n_{\rm i}(T)$  shows that the magnitude of  $n_i$  comes close to the doping concentrations  $N_{\rm A}, N_{\rm D}$  on the hot end.

carrier concentration varies by 8 orders of magnitude from the cold to the hot end. In the hot end the intrinsic carrier concentration is nearly of the same magnitude as the dopant carrier concentration.

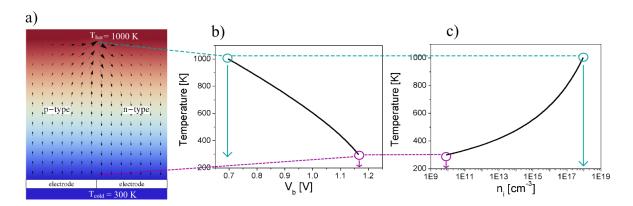

The charge carrier density n can be divided in three domains in temperature: The ionization domain, the extrinsic domain, and the intrinsic domain [76]. The ionization domain corresponds to the activation energy of the dopants  $\Delta E$  and in ranges in temperature from 0K to  $T_{\min}$ . The saturation domain is the temperature range  $T_{\min} < T < T_{\max}$  where all dopants are active and the carrier concentration is equal to the nominal doping ( $N_{\rm D}$  in this case) but the temperature is insufficient to generate carriers from the intrinsic silicon lattice. After a temperature  $T_{\max}$  intrinsic charge carriers from the silicon lattice begin to get activated over the bandgap and this is called the intrinsic domain. This behavior is sketched in Figure 4.7.

It is desired to operate the PN-TEG near the intrinsic temperature on the hot side because note from equation (4.6) is that if  $N_{\rm A} = N_{\rm D} = n_i$  the potential barrier goes to zero and we enter a flat band (zero potential barrier). The intrinsic temperature  $T_{\rm max}$  can

Figure 4.7: Plot of the carrier concentration for an n-type semiconductor. Adapted from [76].

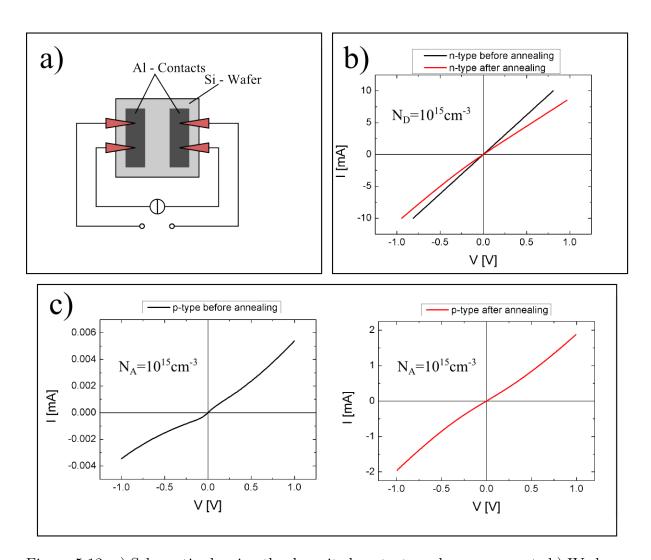

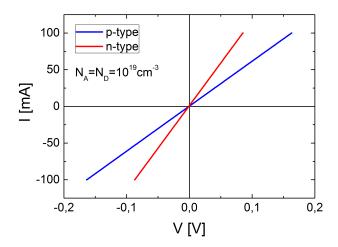

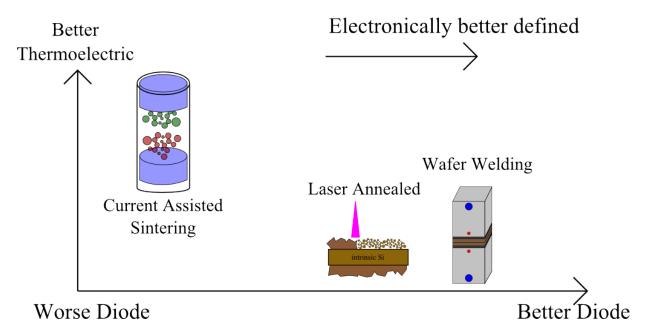

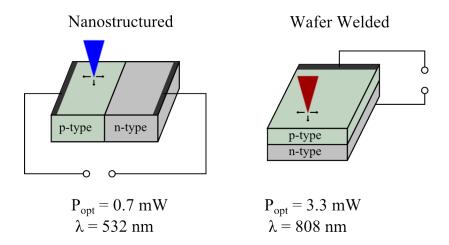

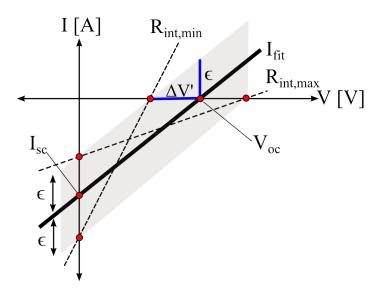

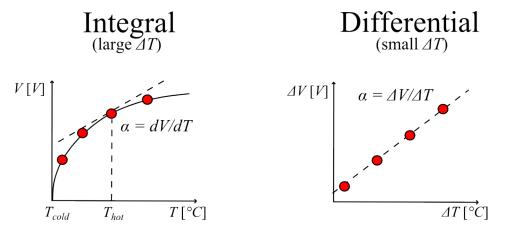

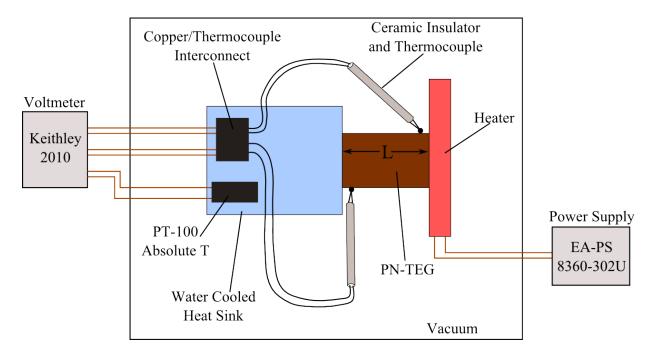

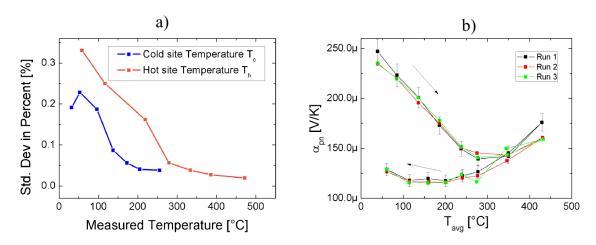

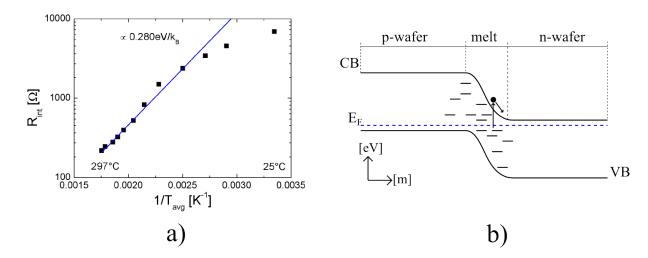

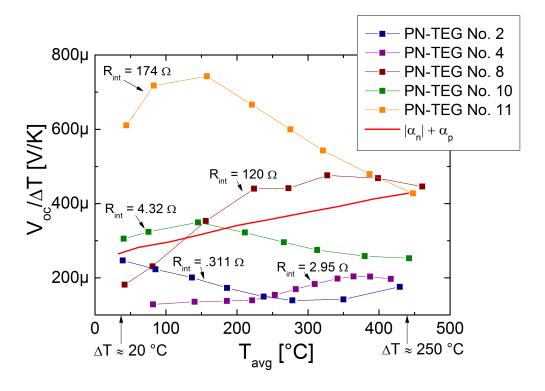

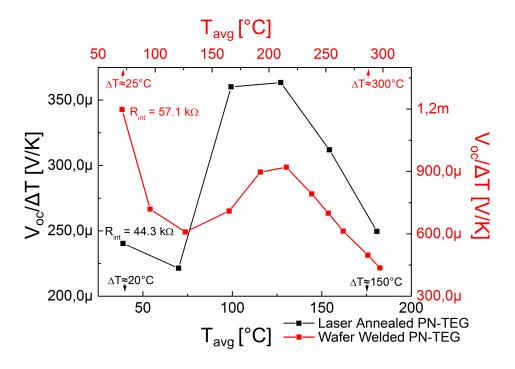

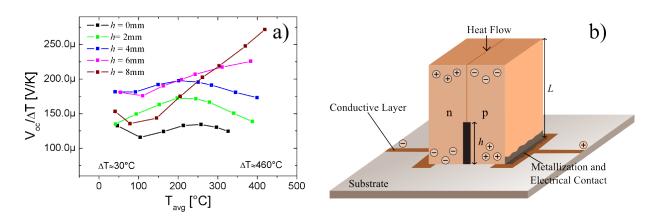

be obtained by setting the doping concentration in equation (4.7) equal to the intrinsic concentration: