# Time Synchronization in Multimodal Wireless Cyber-Physical Systems A Wearable Biopotential Acquisition and Collaborative Brain-Computer Interface Paradigm

Von der Fakultät für Ingenieurwissenschaften,

Abteilung Elektrotechnik und Informationstechnik

der

Universität Duisburg-Essen

zur Erlangung des akademischen Grades

Doktors der Ingenieurwissenschaften

genehmigte Dissertation

von

M. Sc. Unmesh Ghoshdastider

aus

Kalkutta

Gutachter: Prof. Ph. D. Michael Kraft

Gutachter: Prof. Dr.-Ing. Torben Weis

Tag der mündlichen Prüfung: 4. Dezember 2015

#### Zusammenfassung

Die Forschung zu Brain-Computer Interface (BCI) hat in den letzten drei Jahren riesige Fortschritte gemacht, nicht nur im Bereich der menschlich gesteuerten Roboter, der Steuerung von Prothesen, des Interpretierens von Wörtern, der Kommunikation in einer Virtual Reality Umgebung oder der Computerspiele, sondern auch in der kognitiven Neurologie. Patienten, die unter enormen motorischen Dysfunktionen leiden (letztes Stadium Amyotrophe Lateralsklerose) könnten solch ein BCI System als alternatives Medium zur Kommunikation durch die eigene Gehirnaktivität nutzen. Neuste Studien zeigen, dass die Verwendung dieses BCI Systems in einem Gruppenexperiment helfen kann die menschliche Entscheidungstreffung deutlich zu verbessern. Dies ist ein neues Feld des BCI, nämlich das Collaborative BCI. Einerseits erfordert die Durchführung solch eines Gruppenexperiments drahtlose Hochleistungs-EEG Systeme, basierend auf BCI, welches kostengünstig und tragbar sein sollte und Langzeit-Monitoring hochwertiger EEG Daten sicherstellt. Andererseits ist es erforderlich, eine Zeitsynchronisierung zwischen den einzelnen BCI Systemen einzusetzen, damit diese für ein Gruppenexperiment zum Einsatz kommen können. Diese Herausforderungen setzten die Grundlage dieser Doktorarbeit.

In dieser Arbeit wurde ein neuartiges, nicht invasives, modulares, biopotentiales Messsystem entwickelt: Dieses kann Breitband (0.5 Hz-150 Hz) Biopotentiale ableiten, bestehend aus Elektromyographie (EMG), Elektrokardiografie (EKG), Elektroencephalografie (EEG), wurde insgesamt bezeichnet als ExG bzw. das Messsystem als ExG-System benannt. Die Modularität des ExG-Systems erlaubt 8 bis hin zu 256 Kanäle zu konfigurieren, je nach Anforderung, ob in einen textilen Schlauch eingekapselt zur Erfassung von EMG Signalen, in eine textilen Weste zur Erfassung von ECG Signalen oder in eine textilen Kappe zur Erfassung von EEG Signalen. Der Einbau des ExG-Systems in eine Kappe wurde ebenfalls im Rahmen der Arbeit entwickelt. Der letzte Schritt des ExG-Systems zeigt niedriges Eingangsrauschen von  $\sim 7 \, \mu V_{\text{von-Spitze-zu-Spitze}}$ und benötigt 41 mW/Kanal Datenaufnahme im aktiven Zustand. Ein WiFi-Modul wurde für eine drahtlose Datenübertragung an einen ferngesteuerten PC in das ExG-System eingebaut. Um mit dem entwickelte System BCI Anwendungen zu ermöglichen, wurde ein akustisch und visuell evozierter Potenzialstimulator (SSVEP/AEP Stimulator) entwickelt. In eben diesem wurde ein Rasperry Pi als Zentralrechner benutzt und ein Bash basiertes Player-Skript einprogrammiert, das Mediadaten (Video, Audio, Ton) aus der Angabe einer Lookup Tabelle (LUT) in ihr *Linux* Betriebssystem spielt.

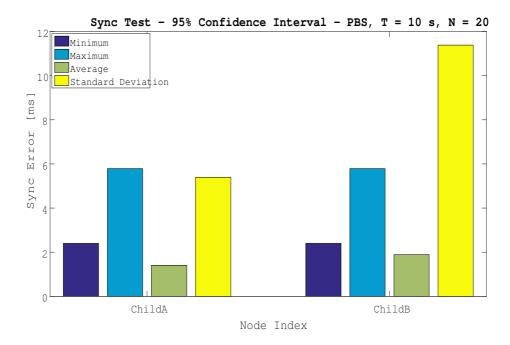

Im Rahmen der Arbeit wurde eine Zeitsynchronisierung an einigen dieser ExG-Systeme mit Hilfe von einer eingebetteten Hardware/Softwarelösung durchgeführt. Die Hardwareteile bestehen aus einigen Leiterplatten, nämlich Sync Modulen mit einem Quarzoszillator, einem Mikrocontroller und einem Funkmodul (Hierbei Bluetooth 4.0). Eines von diesen ist das Sync-Addon, das mit jedem Messsystem (z.B. ExG-System) das zu synchronisieren ist, angeschlossen wird. Das andere bezeichnet man als Sync-Center, das die Datenverarbeitungsrechner wird. Das angehängt Softwareteil übernimmt den Zeitsynchronisierungsmechanismus mit Hilfe eines funkbasierten Protokolls. Im Rahmen der Arbeit wurde ein neues energieeffizientes pairwise broadcast Zeitsynchronisationsprotokoll (PBS), welches nur theoretisch vorgestellt wurde, experimentell verifiziert. Außerdem wurde es mit anderen bestehenden Zeitsynchronisationsprotokollen auf dem aktuellen Stand der Technik evaluiert, basierend auf den Ergebnissen der gleichen Hardwareebene. In der letzten Iteration der Sync-Module wurde ein durchschnittlicher Synchronisationsfehler von ∼2 ms, den Konfidenzintervall von 95% berücksichtigend, erlangt. Da für Collaborative BCI, P300, ein Ereignis bezogenes Potenzial mit dem Auslöseimpuls, der 300-500 ms nach dem Vorgang eintritt, eingestellt wurde, ist die erreichte Synchronisationsgenauigkeit genügend, um solch ein Experiment durchzuführen.

#### **Abstract**

Brain-computer interface (BCI) has experienced the last three decades tremendous technological advances not only in the field of human controller robotics, or in controlling prosthesis, or in spelling words, or in interacting with a virtual reality environment, or in gaming but also in cognitive neuroscience. Patients suffering from severe motoric dysfunction (e.g. late stage of Amyotrophic Lateral Sclerosis) may utilise such a BCI system as an alternative medium of communication by mental activity. Recently studies have shown that usage of such BCI in a group experiment can help to improve human decision making. This is a new field of BCI, namely collaborative BCI. On one hand, performing such group experiments require wireless, high density EEG system based BCI which should be low-cost, wearable and provide long time monitoring of good quality EEG data. On the other hand time synchronization is required to be established among a group of BCI systems if they are employed for such a group experiments. These drawbacks set the foundation of this thesis work.

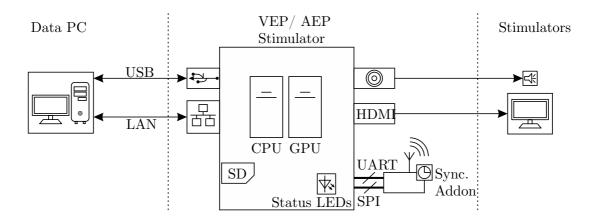

In this work a novel non-invasive modular biopotential measurement system which can acquire wideband (0.15 Hz–200 Hz) biopotential signals consisting Electromyography (EMG), Electrocardiography (ECG), Electroencephalography (EEG) together called ExG, following ExG-system was designed. The modularity of the ExG-system allows it to be configured from 8 up to 256 channels according to the requirement if it's to be encapsulated in a textile sleeve for recording of EMG signals, or in a textile vest for recording of ECG signals, or in a textile cap for recording of EEG signals. The assembly of the ExG-system in cap was also developed during the scope of the work. The final iteration of the ExG-system exhibits low input noise of  $\sim 7~\mu V_{\rm peak-to-peak}$  and require 41 mW/channel of data recording in active state. A WiFi module was embedded into the ExG-system for wireless data transmission to a remote PC. To enable the developed system for BCI applications a steady-state visually/auditory evoked potential stimulator (SSVEP/AEP stimulator) incorporating a Raspberry Pi as a main computer and a bash based player script which plays media data (video, pictures, sound) as defined in a lookup table in the Linux operating system of it.

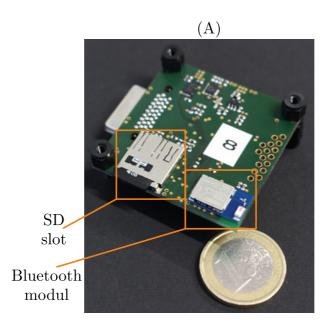

Within the scope of the work time synchronization among a group of such ExG-systems was further realized with the help of an embedded hardware/software solution. The hardware part consists of two different PCB sync modules that are incorporated with a crystal oscillator a microcontroller, a radio module (in this case *Bluetooth 4.0*). One of them is

called the sync-addon which is to be attached to each of the measurement systems (e.g. ExG-system) that are to be synchronized and the sync-center which is to be attached to the remote PC. On the software part, a wireless time synchronization protocol exchanging timtiming information among the sync-center and sync-addons must establish tight time synchronization between the ExG-system. Within the framework of this work, a novel time synchronization protocol energy efficient pairwise broadcast synchronization protocol (PBS) that was only theoretically proposed before but not evaluated on real hardware was experimentally evaluated with the developed sync modules. Moreover a benchmarking with other state-of-the-art existing time synchronization protocols based on the results from same hardware platform were drawn. In the final iteration of sync modules an average synchronization error of  $\sim$ 2 ms was achieved considering the 95% of confidence interval. Since for collaborative BCI, P300, an event related potential was triggered with the stimuli that occur 300–500 ms after the event, the achieved synchronization accuracy is sufficient to conduct such experiments.

#### **Table of Contents**

| Zusar  | mmenfassung                                               | ii     |

|--------|-----------------------------------------------------------|--------|

| List o | of Figures                                                | ix     |

| List o | of Tables                                                 | xviii  |

| List o | of Abbreviations                                          | xx     |

| List o | of Symbols                                                | xxiv   |

| 1      | Introduction                                              | 29     |

| 1.1    | Motivation                                                | 29     |

| 1.2    | Research Questions                                        | 33     |

| 1.3    | Scope of the Work                                         | 35     |

| 1.4    | Research Goal                                             | 36     |

| 1.5    | Thesis Outline                                            | 36     |

| 2      | Theoretical Background                                    | 39     |

| 2.1    | Biopotential Signals                                      | 40     |

| 2.1.1  | Introduction                                              | 41     |

| 2.1.2  | Biopotential Electrodes                                   | 43     |

| 2.1.3  | Noise and Interference                                    | 47     |

| 2.1.4  | Biopotential Amplifiers                                   | 49     |

| 2.2    | Brain-computer Interface                                  | 50     |

| 2.3    | Time Synchronization                                      | 52     |

| 2.3.1  | The Clock Synchronization Problem                         | 53     |

| 2.3.2  | Clocks                                                    | 54     |

| 2.3.3  | Sources of Time Delay and Uncertainties in Message Delive | ery 54 |

| 3      | Brain-computer Interface                                  | 59     |

| 3.1    | Bio-potential Acquisition System                          | 59     |

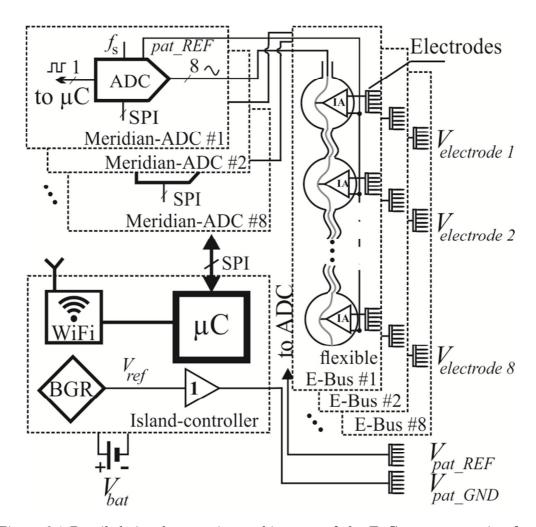

| 3.1.1  | Complete Architecture of ExG-system                       | 61     |

| 3.1.2  | Electrode-bus                                             | 62     |

| 3.1.3  | Meridian-ADC                                              | 69     |

| 3.1.4  | Island-controller                                         | 72     |

| 3 1 5  | Experimental Verification                                 | 81     |

| 3.1.6  | Experimental Results                            | 84  |

|--------|-------------------------------------------------|-----|

| 3.1.7  | Multichannel ExG-system Test                    | 88  |

| 3.1.8  | Wired Synchronization                           | 90  |

| 3.1.9  | Summary                                         | 92  |

| 3.1.10 | Final Iteration                                 | 93  |

| 3.1.11 | Encapsulation                                   | 98  |

| 3.2    | SSVEP- and AEP stimulator                       | 100 |

| 3.2.1  | System Design                                   | 100 |

| 3.2.2  | Software                                        | 102 |

| 3.2.3  | Time Accuracy                                   | 104 |

| 4      | Clock Synchronization                           | 107 |

| 4.1    | State-of-the Art Time Synchronization Protocols | 108 |

| 4.2    | Synchronization Concept                         | 109 |

| 4.2.1  | Mathematical Descriptions                       | 113 |

| 4.2.2  | Protocol Description                            | 116 |

| 4.3    | Implementation on a cBCI scenario               | 119 |

| 4.4    | Evaluation and Analysis                         | 126 |

| 4.4.1  | Experimental Setup                              | 127 |

| 4.4.2  | Measurement Techniques                          | 133 |

| 4.4.3  | Results                                         | 135 |

| 4.4.4  | Summary                                         | 140 |

| 4.4.5  | Final Iteration                                 | 141 |

| 5      | Discussion                                      | 147 |

| 5.1    | Analysis of the ExG-system                      | 147 |

| 5.2    | Analysis of the Time Synchronization            | 149 |

| 6      | Application Scenario & Future Work              | 153 |

| 6.1    | Classroom Experiment                            | 154 |

| 6.2    | Dynamic Setup                                   | 155 |

| 6.3    | Further Work                                    | 156 |

| Biblic | ography                                         | 157 |

| Appe   | ndix A                                          | 169 |

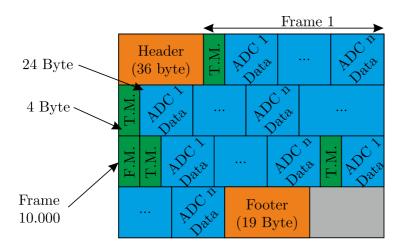

| A.1    | Data Traffic Estimation of the ExG-system       | 169 |

| A.2  | Data Structure of the Transmission Header            | 171 |

|------|------------------------------------------------------|-----|

| A.3  | Data structure of the <i>Transmission Footer</i>     | 172 |

| A.4  | Data Structure of the Transmission Data              | 173 |

| A.5  | Data Structure of the $Transmission\ Frame\ Marker\$ | 175 |

|      |                                                      |     |

| Appe | endix B                                              | 176 |

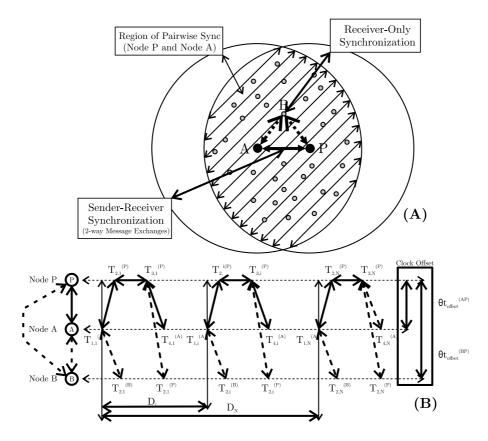

|      | Pairwise Sender-Receiver Synchronization             |     |

|      | Pairwise Sender-Receiver Synchronization             | 176 |

# List of Figures

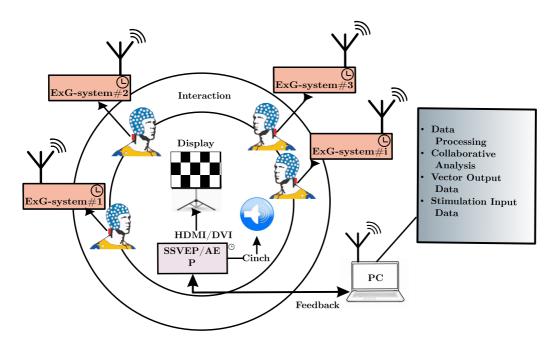

| Figure 1.1 | Overview of a cBCI scenario among a group of probands in a feed-back loop where each proband embodied with an EEG-system is stimulated with a common VEP/AEP-Stimulator As per the EEG signal characteristics the software running on the PC modulates tone and video                                                                                                                                                                                                                                                                                                                    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.1 | Amplitude and frequency characteristics of the biopotential signals, ECG, EEG, EMG and the correlating signals of the biopotential signals                                                                                                                                                                                                                                                                                                                                                                                                                                               |

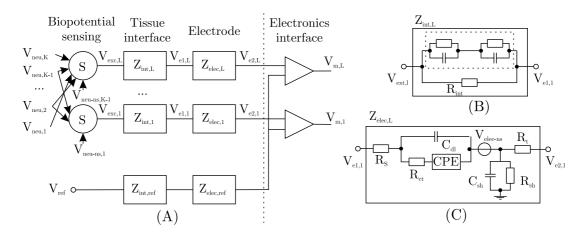

| Figure 2.2 | Lumped-element functional models of neural recording with a microelectrode array. (A) System model of extracellular neural recording from K neurons with an electrode array with L channels. The three components for each channels are biopotential sensing (S), tissue interface impedance $(Z_{int,j})$ and electrode equivalent impedance $(Z_{elec,j})$ (where j can range from 1 to L). (B) lumped-element equivalent circuit for impedance changes in the neural interface associated with reactive tissue responses. (C) lumped-element equivalent circuit of the electrode part |

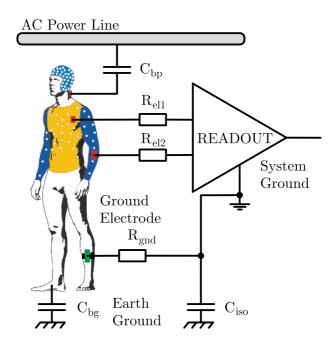

| Figure 2.3 | Electrostatic interference in terms of capacitive coupling between the main AC power line and human body, and between earth ground and the human body                                                                                                                                                                                                                                                                                                                                                                                                                                    |

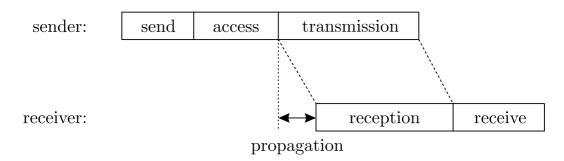

| Figure 2.4 | Block-diagram of sources of delays during a message delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

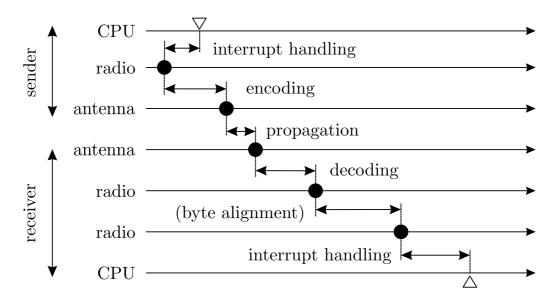

| Figure 2.5 | A simplified display of the timing of the transmission according to the software (CPU), radio module, and physical layer (antenna) of both sender and the receiver.                                                                                                                                                                                                                                                                                                                                                                                                                      |

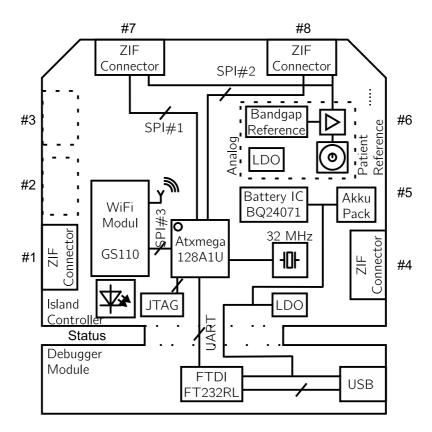

| Figure 3.1  | Detailed signal-processing architecture of the ExG-system starting from the analog bio-potential acquisition to its digitalization and transmission of the data wirelessly via WiFi module; BGR states the band-gap reference voltage and Vpat_REF, Vpat_GND refer to the reference electrode and patient's reference electrode respectively |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

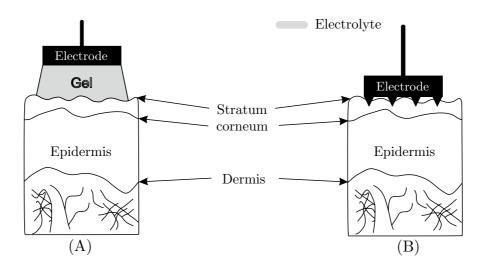

| Figure 3.2  | Application of biopotential electrodes: left : standard EEG wet electrode and right: dry EEG electrode                                                                                                                                                                                                                                       |

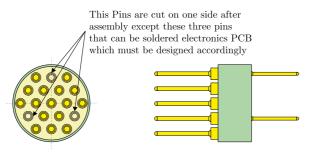

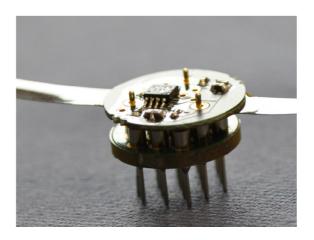

| Figure 3.3  | Mechanical design drawing of the dry electrode array 63                                                                                                                                                                                                                                                                                      |

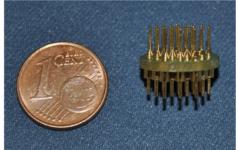

| Figure 3.4  | Dry electrode after production with 19 golden pin-array and euro-cent on the left as a comparison                                                                                                                                                                                                                                            |

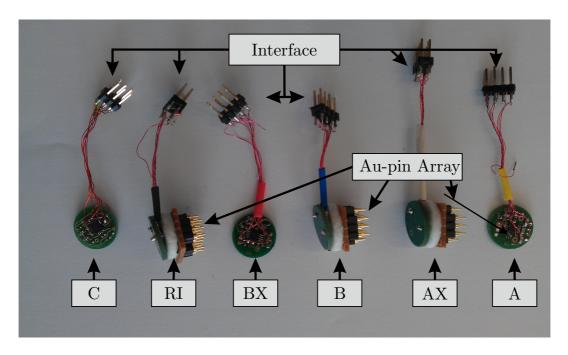

| Figure 3.5  | Active electrodes with different variations of IA and amplification factors which were designed and tested. Each of the variation has its name which is described in Table I 65                                                                                                                                                              |

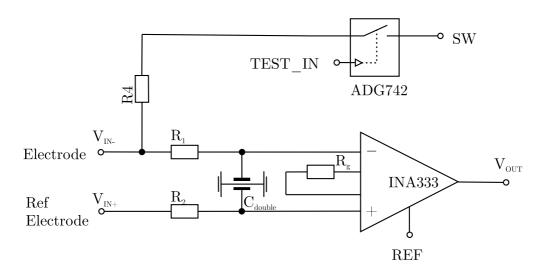

| Figure 3.6  | First amplification stage of differentially measured biopotential with INA, A low-pass filter for rejecting RFI using R1, R2 and Cdouble; Rg is responsible for setting the gain of the first amplification stage. A separate switch using ADG742 for impedance measurement option                                                           |

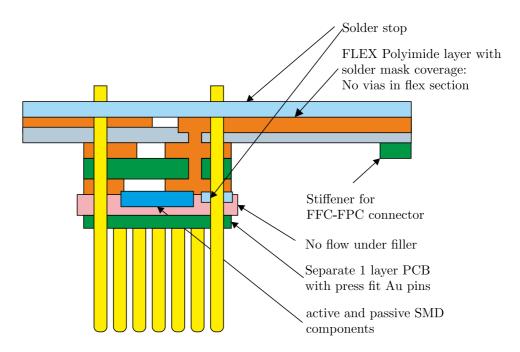

| Figure 3.7  | Conceptual sketch of the dry electrode in connection with the amplification circuitry and flexible bus                                                                                                                                                                                                                                       |

| Figure 3.8  | A flexible, flat electrode-bus containing 8 active electrodes. 69                                                                                                                                                                                                                                                                            |

| Figure 3.9  | Single active electrode with a IA circuitry on the top 69                                                                                                                                                                                                                                                                                    |

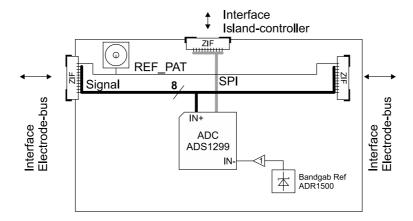

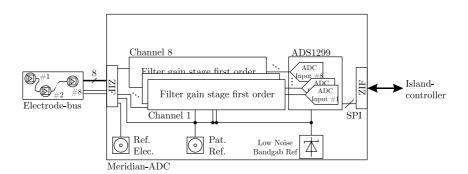

| Figure 3.10 | Top Level Design of Meridian-ADC71                                                                                                                                                                                                                                                                                                           |

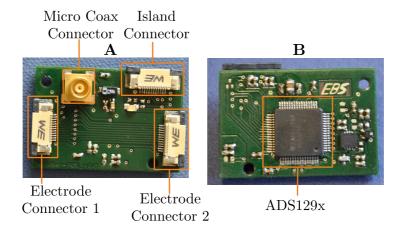

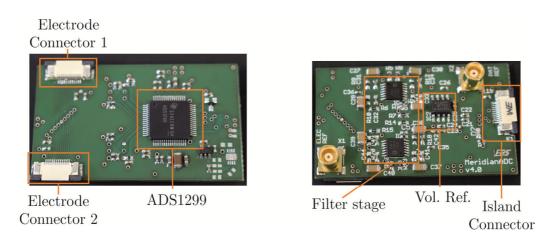

| Figure 3.11 | Manufactured PCB prototype of the Meridian-ADC; A) Top side of the Meridian-ADC with 2 ZIF connecters for connecting Electrode-busses, a shielded micro coax connected                                                                                                                                                                       |

|             | for reference electrode input; B) Bottom side of the Meridian-ADc with the ADC, ADS129x $(x = 8.9)$                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.12 | Concept diagram of the Island-controller with 8 ZIF connectors for connecting 8 Meridian-ADCs, a AVR XMEGA controller, a WiFi module, power management circuitry and necessary debug interfaces (JTAG, USB)                                                                                                   |

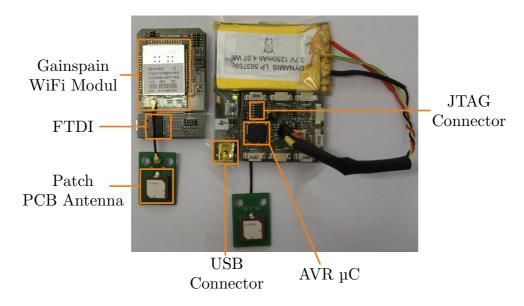

| Figure 3.13 | The first prototype of Island-controller. It is powered with a LiPo-Battery and the external patch antenna is connected through miniature coaxial RF connector                                                                                                                                                |

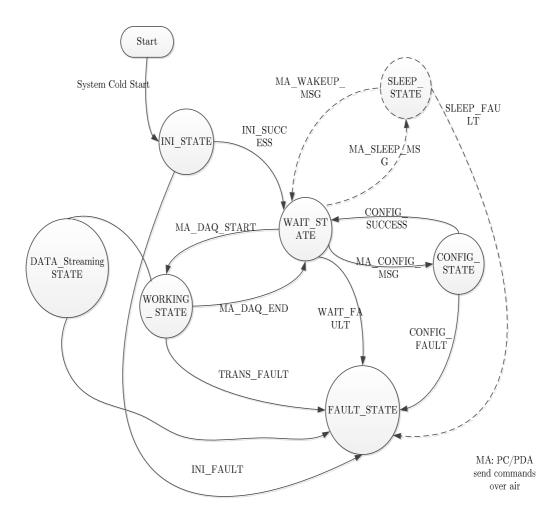

| Figure 3.14 | State-diagram of the firmware for the Island-controller with seven main states and their interaction                                                                                                                                                                                                          |

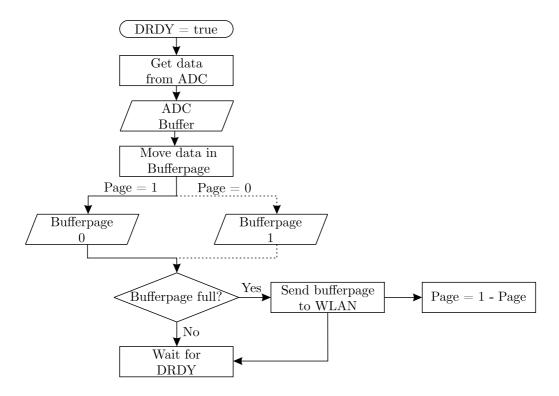

| Figure 3.15 | Flow-diagram of the implementation of the data acquisition from Meridian-ADC using the Island-controller                                                                                                                                                                                                      |

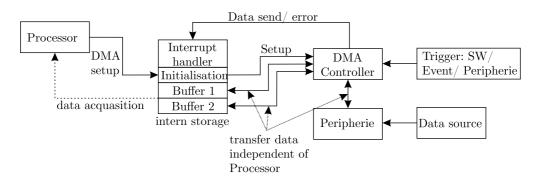

| Figure 3.16 | Working principle of the DMA in XMEGA80                                                                                                                                                                                                                                                                       |

| Figure 3.17 | Architecture of the measured data stream in which the recorded data from Meridian-ADC was first stored at the Island-controller and then transmitted wirlessly to a remote PC                                                                                                                                 |

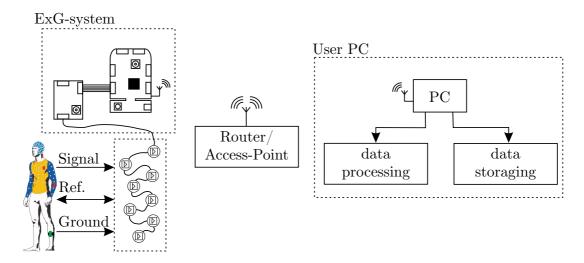

| Figure 3.18 | A generic view of the biopotential measurement setup in a local area network where a proband wore a ExG-system, a remote user PC transmited commands and received data from the ExG-system via Access-Point (AP)                                                                                              |

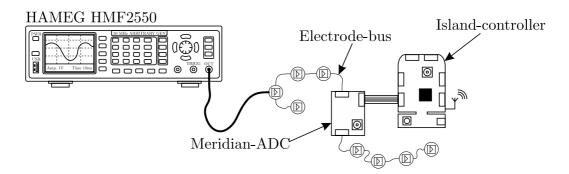

| Figure 3.19 | Measurement setup for calibration test where the signal (AC) was generated on a signal generator (HAMEG <i>HMF2550</i> ) and was fed to the differential inputs of the INA. After the signal was passed through the entire signal processing chain of ExG-system, the input signal was to be reconstructed 83 |

| Figure 3.20 | Faraday cage for short-circuit test (height: 37 cm, diameter: 32.5 cm)                                                                                                                                                                                                                                        |

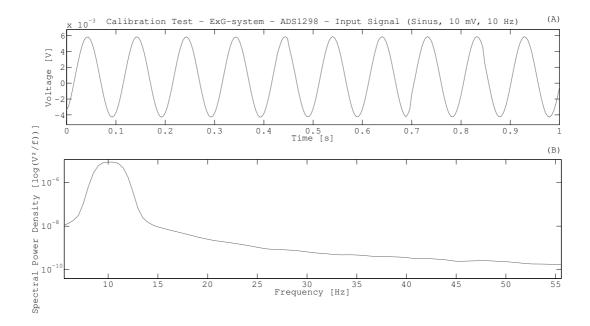

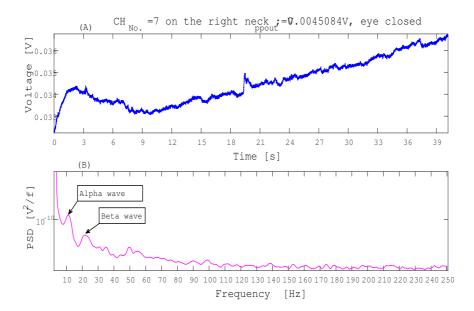

| Figure 3.21 | Calibration test with sinus signal. A) showing measured voltage over time and B) showing the power spectrum in frequency domain                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

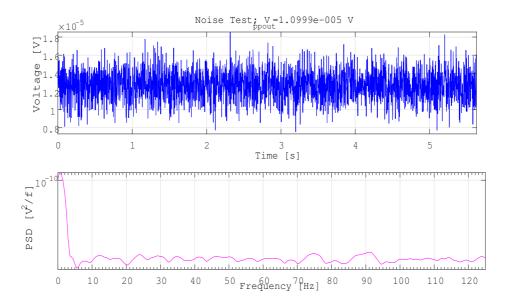

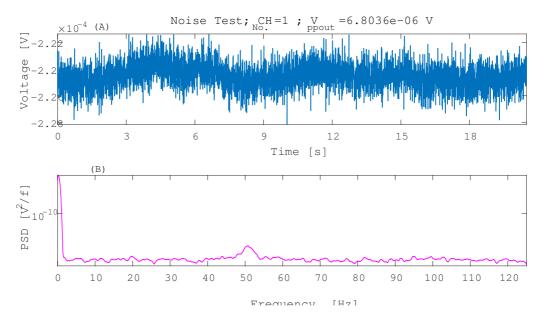

| Figure 3.22 | Short-circuit test; (A) showing the white noise in time domain and (B) showing the corresponding power spectral density (PSD) amplitude in frequency domain                                                                                                                                                                                                                                                                                                 |

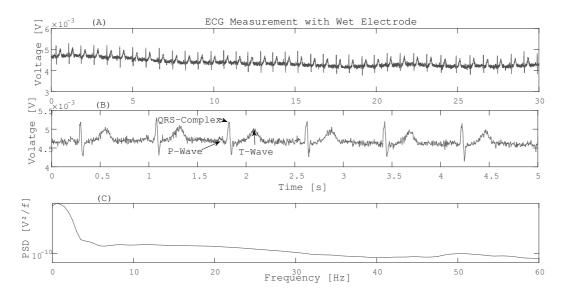

| Figure 3.23 | Raw data ECG measurement from a proband; A) a time span of 30 s, b) a time slot until 5s to visualize the QRS-complex, P-wave, T-wave, c) corresponding power spectrum in frequency domain. The frequency spectrum shows that the measured signal did not capture any surrounding 50-Hz noise from the main due the high CMRR of the INA                                                                                                                    |

| Figure 3.24 | (A) Visualization of raw data from an EEG measurement on a proband in time domain and (B) Alpha and Beta rhythm. The signal electrode was placed on the right side of the neck of the proband's head, the reference electrode behind the left ear and the patient's reference electrode behind right ear. The power spectrum (PSD) of the blocks of data reveals that the power near 10Hz and 20Hz shows two peaks, commonly known as alpha and beta rhythm |

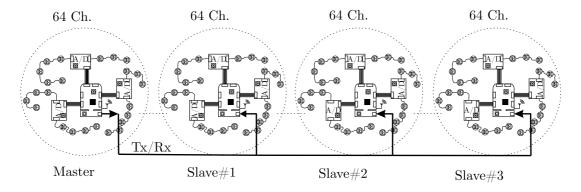

| Figure 3.25 | A wired synchronization concept of achieving 256 channel of biopotential data acquisition with 4 ExG-systems is presented. The master ExG-system sent a sync-character at a predefined regular interval (e.g. 20 s) over USART to all the slave ExG-systems and they caught this sync-character and inserted it into their data stream so that the measured data can be correlated with the help of the positioning of this sync-character                  |

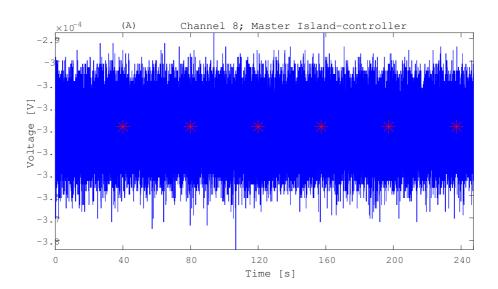

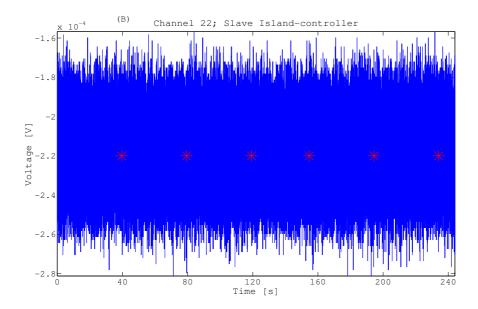

| Figure 3.26 | A test of time synchronization were performed on two Island-<br>controllers where sync points were inserted every 40 seconds;                                                                                                                                                                                                                                                                                                                               |

|             | (A) Master node which initiated the measurement and starts the recording of the sync character, Blue (dotted) is the data and red asterisks shows the sync points. (B) Synchronous measurement starts at the slave node and also records the sync points (red asterisk) with test data                                                                                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.27 | Module based schematic diagram of Meridian-ADC_v2 with interfaces towars Electrode-bus and Island-controller. The analog signal processing with filter gain stage of first order and further digitization with ADC1299 is sketched. The output coax interface of patient's reference (Pat. Ref. in the schematic) and input coax interface for reference electrode (ref. Elec. in the schematic) is also shown |

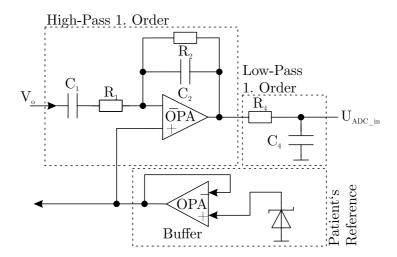

| Figure 3.28 | The circuitry of the filter gain stage of first order of Meridian-ADC is presented where OPA and INA are the abbreviations of operational amplifier and instrument amplifier respectively. The differentially output voltage $Vo$ from the Electrode-bus of a channel is taken as a input and $UADC_in$ as output from this filter gain stage as well as input for the ADS1299 are shown.                      |

| Figure 3.29 | The final iteration of Meridian-ADC, namely Meridian_ADC_v2 with 2 ZIF connectors for connecting Electrode-busses as shown in left and the new low noise voltage reference (Vol. Ref.) <i>ISL21090</i> from shown on the right.                                                                                                                                                                                |

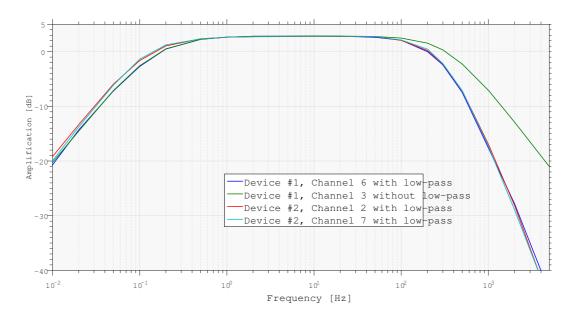

| Figure 3.30 | Experimental verification of the band-pass filter of Meridian-ADC_v296                                                                                                                                                                                                                                                                                                                                         |

| Figure 3.31 | Noise test for verifying the system resolution of the ExG-system using the Meridian-ADC_v2; (A) The read-out raw voltage data in the time domain and PSD amplitude in frequency domain                                                                                                                                                                                                                         |

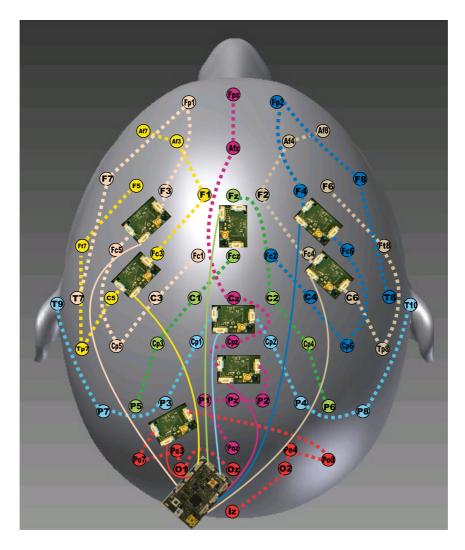

| Figure 3.32 | Placement of the ExG-system components according to the international 10—20 system for positioning electrodes 99                                                                                                                                                                                                                                                                                                       |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.33 | Encapsulated ExG-system showing the dry electrodes where the electrode-bus was woven into the middle layer of the textile cap on a Mannequin                                                                                                                                                                                                                                                                           |

| Figure 3.34 | Architecture of the SSVEP/AEP-stimulator and its interfaces towards PC and output modalities (speaker, monitor)                                                                                                                                                                                                                                                                                                        |

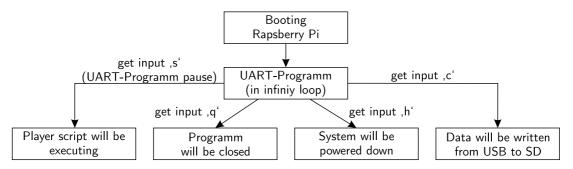

| Figure 3.35 | Flow-diagram of the main state machine running in Raspbian OS which is triggered by the commands over UART interface                                                                                                                                                                                                                                                                                                   |

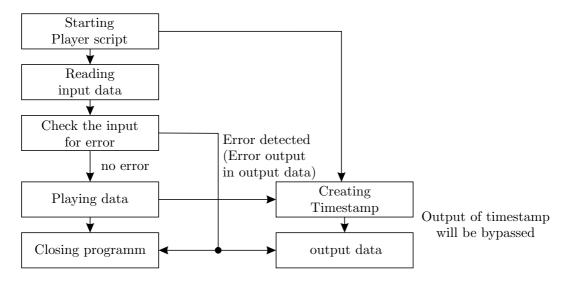

| Figure 3.36 | Flow-diagram of the $stimulator\_player$ shell script 103                                                                                                                                                                                                                                                                                                                                                              |

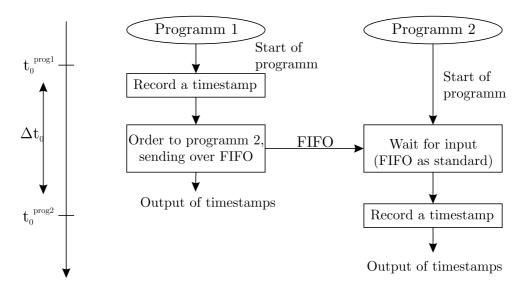

| Figure 3.37 | Flow-diagram of the programs used to determine the accuracy of the timestamps recorder at the beginning and the end of a media data                                                                                                                                                                                                                                                                                    |

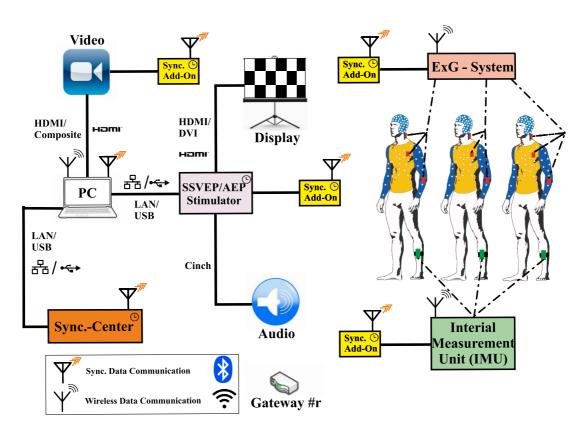

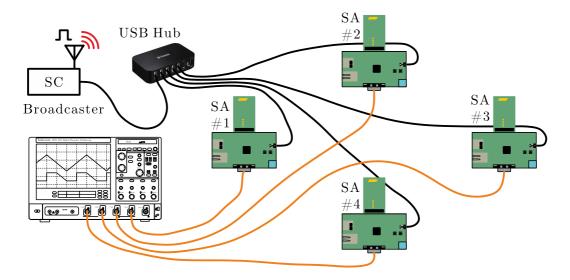

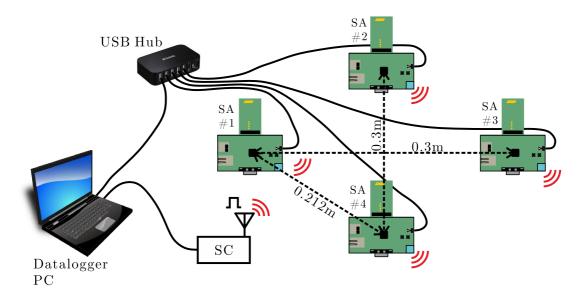

| Figure 4.1  | Enhancement of the cBCI scenario with the realization of time synchronization using synchronization-center and synchronisztion-addon                                                                                                                                                                                                                                                                                   |

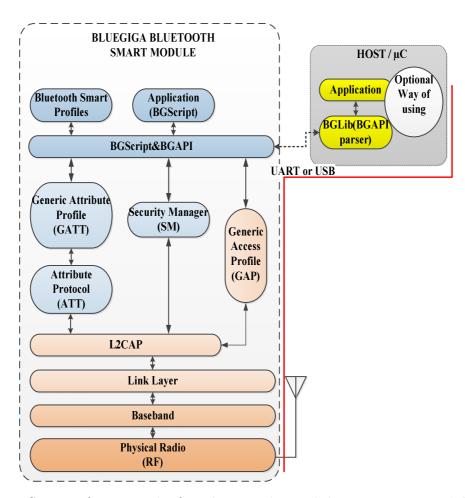

| Figure 4.2  | Smart software stack of a <i>Bluegiga</i> Bluetooth low energy 4.0 module and host $\mu$ C including the software interface (UART or USB). This visualizes the critical path (indicated in red) from the RF layer of the BLE stack to the application layer of the $\mu$ C. The time required for a message to travel the critical path defines the additional delay introduced by the proposed synchronization method |

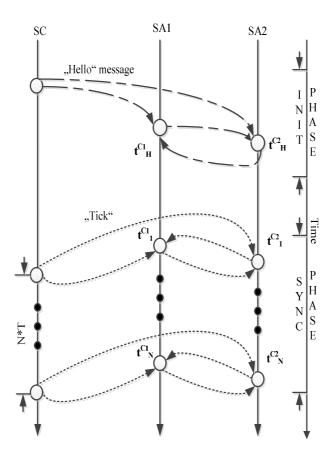

| Figure 4.3  | HBS protocol in two phases; INIT phase establishes the first handshaking to create the network; SYNC phase implements the message communication regulation to adjust skew and offset with each other                                                                                                                                                                                                                   |

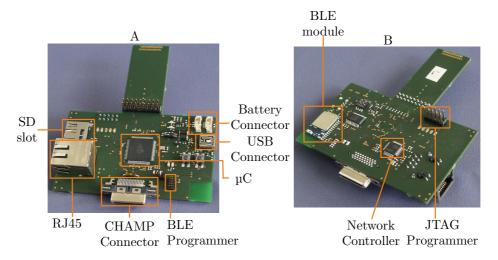

| Figure 4.4  | First prototype of the SA; A) Top side of the sync modules with SD slot for micro SD card, RJ45 for LAN connection, Champ connector for connecting biopotential amplifier and other debugging interfaces (programmer, USB); B) Bottom side of the sync module where BLE module, network processor for LAN and programming interface are visible. 121 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

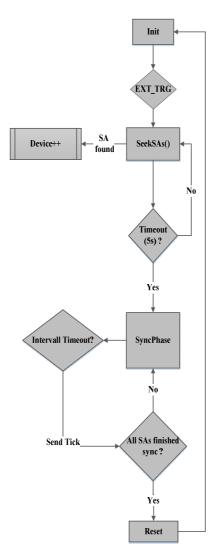

| Figure 4.5  | Simplified flow-diagram of the state-machine of the SC showing the interface (Device++) to the signal processing PC, network discovery (finding SAs) and synchronization phase                                                                                                                                                                       |

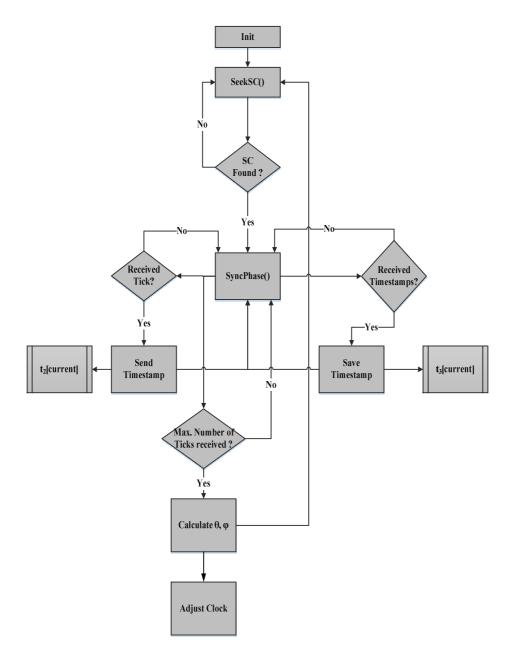

| Figure 4.6  | Simplified flow-diagram of the state-machine including the initialization (handshake) and synchronization phase of the SA                                                                                                                                                                                                                            |

| Figure 4.7  | Measurement setup for Chi-square test where the GPIO and GND lines of the SAs were connected to a Oscilloscope and a SC sends periodic broadcasts                                                                                                                                                                                                    |

| Figure 4.8  | Experimental setup for stationary sync modules; 4 SAs were spatially distributed on a table and a SC was placed adjacent to the Datalogger PC; All the modules were powered with USB and this interface was used for getting the timestamps at the Datalogger PC                                                                                     |

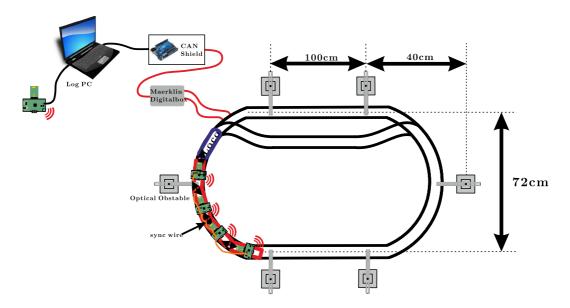

| Figure 4.9  | Dynamic Measurement setup with a model train on the right on which the locomotive from Maerkin carry the syncaddons; The speed of the model train was controlled by a Arduino Uno board. This was realised using a CAN shield which is connected to the digital control box of <i>Maerklin</i> (Maerklin Digitalbox)                                 |

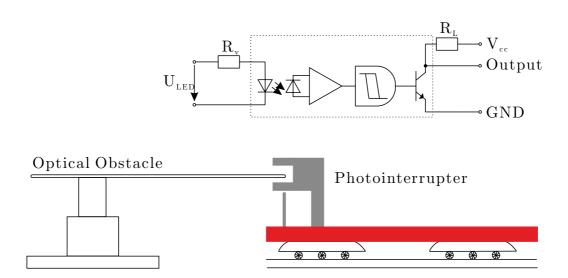

| Figure 4.10 | zoomed in view of the optical obstacle and the photointerupter with its corresponding circuit                                                                                                                                                                                                                                                        |

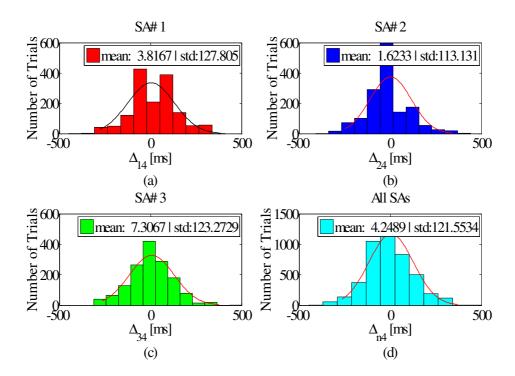

| Figure 4.11 | Histogram of the difference in reception time between the GTP SA#4 and the other 3 SAs. The mean and standard deviation (std) of the $\Delta nm$ (defined in equation) are calculated and shown in the legends of each distribution curve. The mean, std values are given in ms                                                                                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

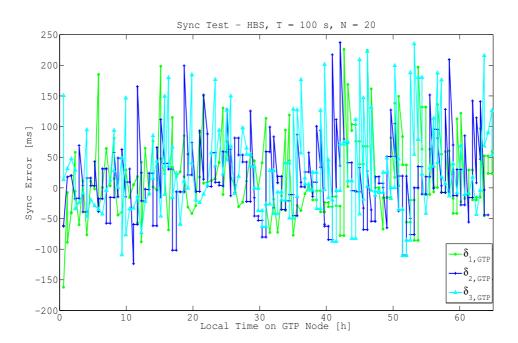

| Figure 4.12 | In the measurement setup 4 SAs were synchronized to find out the relative time difference on the SAs with respect to a fixed SA which the GTP. The plot shows a measurement result for the evaluation test of time synchronization accuracy among 4 SAs which was run for approximately 65 hours. An average relative difference in time was found to be 14.7 ms, 9.91 ms, 29.4 ms for $\delta$ 1, $GTP$ , $\delta$ 2, $GTP$ , and $\delta$ 3, $GTP$ , respectively. |

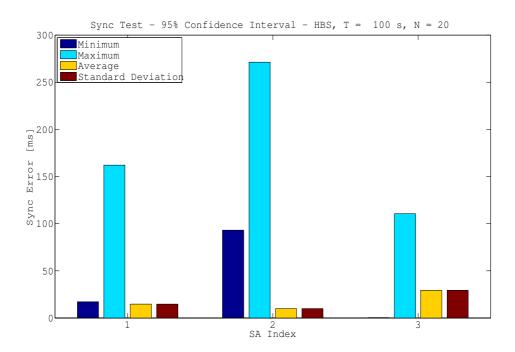

| Figure 4.13 | Statistical results of the HBS method, showing the minimum, maximum, average and standard deviation of the sync error on 3 SAs w. r.t. the GTP using the 95% confidence interval.                                                                                                                                                                                                                                                                                    |

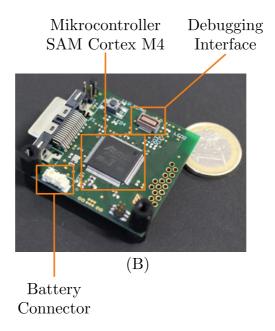

| Figure 4.14 | Top view of synchronisation-addon v2 with ARM Cortex SAM4 processor, a stable 16 MHz crystal crystal, connectors for battery, slim-slack connector for the debugger board, and connector for ExG-system                                                                                                                                                                                                                                                              |

| Figure 4.15 | Bottom view of the Synchronization Addon v2 with Bluetooth module BLE113, micro SD card holder                                                                                                                                                                                                                                                                                                                                                                       |

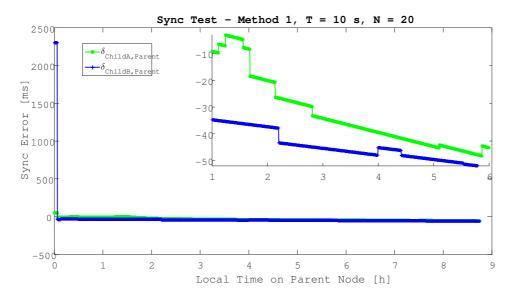

| Figure 4.16 | Approximately 9 hours long stationary time synchronization experiment with sync modules of final iteration; A zoomed inset diagram shows the plot with truncated axes                                                                                                                                                                                                                                                                                                |

| Figure 4.17 | Statistical results of the HBS method, showing the minimum, maximum, average and standard deviation of the sync error on the Children SA_v2s w. r.t. the Parent SA using the 95% confidence interval                                                                                                                                                                                                                                                                 |

| Figure 6.1 | A typical quasi-stationary group experiment scenario where a  |

|------------|---------------------------------------------------------------|

|            | group of attendants sited with less physical movement         |

|            | (quasi-stationary) of a conference listening and watching a   |

|            | keynote presentation. The attendants were wearing an EEG-     |

|            | cap and sync modules for recording the EEG data and to        |

|            | synchronize their clock at the rate of the global time        |

|            | provider                                                      |

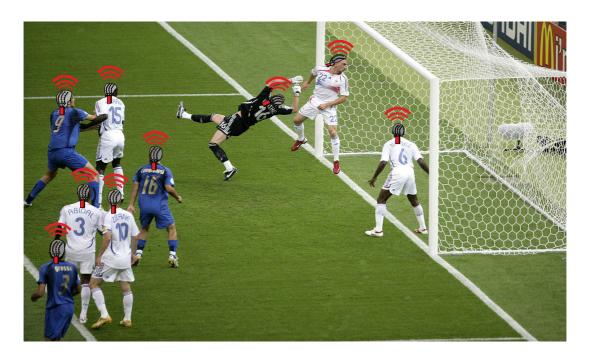

| Figure 6.2 | A dynamic scenario of group experiment where ERP of each      |

|            | proband (football players) are stimulated from the behavioral |

|            | changes of the other players, game, environment – probands    |

|            | equipped with mobile EEG-cap and sync modules                 |

## List of Tables

| Table 2-1 Range of amplitude and frequency of commonly used biopotential signals                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3-I Overview of first INA prototypes tested in the design phase of the active electrodes                                                                  |

| Table 3-II Specifications of the developed Meridian-ADC                                                                                                         |

| Table 3-III Data traffic estimation for the selection of radio module                                                                                           |

| Table 3-IV Data loss of a ExG-system at different settings of sample and number of Median-ADCs                                                                  |

| Table 3-V A comparison table with the important specifications of the state-<br>of-the-art Biopotential measurement systems                                     |

| Table 3-VI Compatible multimedia data formats for the SSVEP/AEP-Stimulator                                                                                      |

| Table 3-VII Determination of reaction time $\Delta t0prog1$ over FIFO 106                                                                                       |

| Table 4-I Structure of the timestamp clock variable                                                                                                             |

| Table 4-II Comparison of the accuracy of the timing variable used in the protocol implementation between MATLAB, Float64-software library and double of AVR-GCC |

| Table 4-III General test conditions                                                                                                                             |

| Table 4-IV Test conditions of stationary tests with SAs and SC 137                                                                                              |

| Table 4-V Overview of synchronization error of five time synchronization protocol for a 3 hours long measurement                                                |

| Table 4-VI Overview of the results of the time synchronization test on dynamic sync modules                                                                     |

## List of Abbreviations

| Abbreviation         | Meaning                                |

|----------------------|----------------------------------------|

| μС                   | microcontroller                        |

| AC                   | alternating current                    |

| AD                   | Analog Devices, Inc.                   |

| ADC                  | analog-to-digital converter            |

| AEP                  | auditory evoked potential              |

| API                  | application peripheral interface       |

| BCI                  | Brain-computer interface               |

| BGR                  | band-gap reference                     |

| BLE                  | Bluetooth low energy                   |

| BOLD                 | blood-oxygen-level-dependent           |

| CAN                  | controller area network                |

| cBCI                 | collaborative Brain-computer interface |

| CE                   | Conformité Européene                   |

| CMRR                 | common-mode rejection ratio            |

| $CONFIG\_STATE$      | configuration state                    |

| CPE                  | constant phase element                 |

| CPS                  | Cyber-physical system                  |

| CTS                  | clear-to-send                          |

| DAQ                  | data acquisition                       |

| DAMA CODEAMING COAME |                                        |

| DATA_STREAMING_STATE | data streaming state                   |

| DC                   | direct current                         |

| DMA                  | direct memory access                   |

ECoG electrocorticography

EEG electroencephalography

EGG electroglotography

EMF electromotive force

EMG electromyography

EMI electromagnetic interference

EOG somatosensory evoked potential

EOG electrooculogram

EP evoked potential

ERG electroretinogram

ERP event-related potential

FAULT\_STATE fault state

FCC Federal Communications Commission

FIFO first in first out

fMRI functional magnetic-resonance imaging

FoM figure of merit

FPU floating point unit

FSM finite state machine

FTSP Flooding Time Synchronization Protocol

GAP Generic Access Profile

GFSK Gaussian frequency shift keying

GPIO general-purpose input/output

GPS global position system

GTP global time provider

HBS Hybrid Broadcast Synchronization

HPF high-pass filter

IMU inertial measurement unit

INA instrument amplifier

INI STATE initialization state

INIT initialization phase

IoT Internet-of-Things

ISM industrial scientific and medical

LFP local field potential

LR linear regression

LiPo Lithium-Polymer

LL Link Layer

LUT lookup table

MAC medium access control

MBS Multi-hop Broadcast Synchronization

MEG magnetoencephalogram

PBS Pairwise Broadcast Synchronization

PCB printed circuit board

PCB personal computer

PPC posterior parietal cortex

PSD power spectral density

PSD power spectrum

PSP post-synaptic potential

Radio frequency RF

RBS Reference Broadcast Synchronization

RFI radio frequency interference

RISC reduced instruction set computing

RMS root mean square

RT reaction time

RTOS real-time operating system

RTS request-to-send

SA synchronization-addon SC synchronization-center

SD card secure digital memory card

SPI Serial Peripheral Interface

SYNC synchronization phase

sync error synchronization error

${\bf Transmission} \qquad {\bf Control} \qquad {\bf Protocol/Internet}$

TCP/IP Protocol

TDM time division multiplexing

TI Texas Instruments Incorporated

TPSN Timing-sync Protocol for Sensor Networks

TTL transistor-transistor logic

UART universal asynchronous receiver/transmitter

USART universal asynchronous receiver/transmitter

USB Universal Serial Bus

VEP visually evoked potential

WAIT STATE wait state

WORK STATE working state

WSN wireless sensor networks

## List of Symbols

#### Latin Characters

| Symbol           | Unit | Meaning                                                                     |

|------------------|------|-----------------------------------------------------------------------------|

| $T_{INTD}$       | s    | the interrupt handling time at the host controller                          |

| $ar{t}_i$        | s    | average of the local timestamps on node $i$                                 |

| $\overline{t_p}$ | s    | average of the local timestamps on node $p$                                 |

| $\Delta_{nm}$    | s    | pairwise difference                                                         |

| $A_x$            | s    | difference between timestamps                                               |

| $B_{x}$          | s    | difference between offsets                                                  |

| $C_1^x$          |      | ratio between $A_x$ and $B_x$                                               |

| $C_{bg}$         | F    | coupling capacitance between ground and human body                          |

| $C_{bp}$         | F    | coupling capacitance between main AC and human body                         |

| $C_{dl}$         | F    | Double layer capacitance                                                    |

| $C_{double}$     |      | double capacitor                                                            |

| $C_{iso}$        | F    | isolation capacitance between the ground of the amplifier battery and earth |

| $C_{sh}$         | F    | Capacitance between insulated electrode and tissue                          |

| $E_{hc}$    | V | Voltage source                                                                                                 |

|-------------|---|----------------------------------------------------------------------------------------------------------------|

| $I_D$       | A | displacement current passes from human body to the coupling capacitor                                          |

| $N_{M}$     |   | number of Meridian-ADCs                                                                                        |

| $R_1$ ,     | Ω | input resistance of the instrument amplifier                                                                   |

| $R_2$       | Ω | input resistance of the instrument amplifier                                                                   |

| $R_{ct}$    | Ω | resistance caused by Faradaic current                                                                          |

| $R_{el1}$   | Ω | input resistance of the amplifier                                                                              |

| $R_{el2}$   | Ω | input resistance of the amplifier                                                                              |

| $R_g$       | Ω | gain selecting resistance of the instrument amplifier                                                          |

| $R_{gnd}$   | Ω | coupled resistance between ground of the amplifier and human body                                              |

| $R_s$       | Ω | resistance to the ion movement in the diffusion region                                                         |

| $R_{sh}$    | Ω | shunt resistance from the insulated electrode to the tissue                                                    |

| $R_t$       | Ω | resistance in the electrode from electrode site to electronic interface                                        |

| $T_{BGLD,}$ | s | the time required to process the message by the application peripheral interface (API) of the Bluetooth module |

| $T_{GLD}$   | S | delay to transmit the message from the Link Layer                                                              |

|                        |              | (LL) to the Generic Access Profile               |

|------------------------|--------------|--------------------------------------------------|

| $T_{UARTD}$ ,          | $\mathbf{S}$ | the time to transmit the message over the UART   |

| $V_{CM}$               | V            | common-mode voltage                              |

| $V_{IN+}$              | V            | Non-inverting input of the instrument amplifier  |

| $V_{IN-}$              | V            | inverting input of the instrument amplifier      |

| $V_{out}$              | V            | Output voltage of the instrument amplifier       |

| $Z_{in}$               | Ω            | input impedance of the amplifier                 |

| $d_l$                  |              | Data loss in $\%$                                |

| $d_r$                  |              | number of received data bytes                    |

| $t_1$                  | S            | First timestamp                                  |

| $t_g$                  | S            | New global time of each node after adjustment    |

| $t_i$                  | S            | current time of each node                        |

| $t_i^k$                | S            | $k^{th}$ timestamp at the general node           |

| $t_k^{SA\#m}$          | S            | timestamp on node $SA\#n$                        |

| $t_k^{\mathit{SA\#n}}$ | S            | timestamp on node $SA\#n$                        |

| $t_p^k$                | S            | $k^{th}$ timestamp at the reference node         |

| $v_{elec-ns}$          | V            | lumped electrode intrinsic noise voltage sources |

| $\delta_{n,m}$         | $\mathbf{S}$ | sync error between the SA#n and SA#m             |

| $\Delta V_{IN}$        | V            | differential error signal                        |

| $\Delta t_k$           | S            | The difference between two successive timestamps |

|                   |          | subtracted by the interval $T$       |

|-------------------|----------|--------------------------------------|

| $\Delta f$        | Hz       | frequency range of interest          |

| F                 | 1/s      | sample rate of the ADC               |

| k                 | eVK-1    | Boltzmann's constant                 |

| $k^{th}$          |          | number of a timestamp                |

| M                 |          | number of incoming Framemarkers      |

| N.                |          | Number of messages                   |

| T                 | K        | Kelvin temperature                   |

| T                 |          | interval between messages            |

| $T_{duration} \\$ |          | duration of the synchronization test |

| Vcc               | V        | operating voltage                    |

| Z                 | $\Omega$ | electrode magnitude impedance        |

| G                 |          | Gain of the instrument amplifier     |

#### **Greek Characters**

| Symbol                  | Unit | Meaning                                            |

|-------------------------|------|----------------------------------------------------|

| $	heta_i^{d\_t}$        |      | offset difference of node $i$ w.r.t.t. parent node |

| $ar{	heta}_{min}$       |      | average of minimum offsets                         |

| $	heta_{min}^k$         |      | minimum of k number of offsets $\theta$            |

| $\varphi_i^{d\_t}$      |      | skew difference of node $i$ w.r.t.t. parent node   |

| $\varphi_i^{d\_\theta}$ |      | skew difference                                    |

| υ                       |      | velocity of the model train                        |

In this chapter the scientific basis of this thesis work will be created so that the motivation, need of the work, research problem and scientific innovation of it can be perceived. At first the motivation behind this work will be discussed. In line with motivation, the existing solution and its limitation will be introduced. This will lead to the research questions that were raised in the course of the formation of the work. To investigate the aroused questions, a scientific methodology that was followed during the work will be discussed. After that an overview of the scope of the work will be described before the concrete scientific goals and approach are being discussed.

#### 1.1 Motivation

Cyber-physical systems (CPS) have recently been gaining popularity and emerging as a frontier technology in robotics and biomedical engineering. This progress is contributing to the enhancement of brain-computer interfaces (BCI) [1] which is having significant impact in brain science. Brain-computer interfaces (BCIs) were introduced to address as an

alternative medium for individuals to bypass conventional channels of comcommunication (i.e. muscles and speech). This allowed communication and control between the human brain and physical devices by translating different patterns of brain activities into commands in real time [2]. Recording of electroencephalography (EEG) can be achieved either invasive using electrocorticography (ECoG) method or non-invasive. ECoG method involves a surgery so that electrodes can be placed directly on or inside the cortex that makes it a less popular alternative in respect to noninvasive BCI. Apart from EEG, magnetoencephalogram (MEG), bloodoxygen-level-dependent (BOLD) signals, and (de) oxyhemoglobin concentrations can be used as inputs for BCI systems [3]. EEG has been the most popular signal input for developing BCI system due to its convenience to be used in practice and relatively lower cost.

BCI based application has huge potential in several disciplines starting from neurophysiology, ambulatory medical diagnostics, bionics to gaming. BCI based robotics could assist paralyzed patients; group BCI can be used to understand how human brain works; BCI can be used in automated divining and many more potential applications. However, BCI technology has not succeeded in bringing laboratory demonstration to a real-life application [4], [5] as this imposes many challenges in terms of signal integrity, signal quality, miniaturization or form factor, signal-to-noise ratio (SNR), and system assembly [6]. For instance, the accuracy of a single-trial EEG classification using a binary finger-tapping task (left hand vs. right hand) in BCI Completion II ranged from 51% to 84% from 15 research groups [6]. Neuroimaging studies of human cognitive, sensory, and motor processes are usually based on noninvasive techniques such EEG, magnetoencephalography (MEG) or functional magnetic-resonance imaging (fMRI). These techniques have either inherently low temporal or low spatial

INTRODUCTION 31

resolution, and suffer from low signal-to-noise ratio and/or poor sensitivity at higher-frequency [4]. Currently many applications suffer from the low acaccuracy of single-trial classification. In achieving enhanced SNR, averaging methods were employed not only across multiple trials, but also on multiple subjects [6]. In event-related potential (ERP)-based BCI applications, averaging single trial is the common mean to improve system performance [7].

In such BCI application, the stimulus was played repeatedly many times to produce multiple trails from a single subject so that the averaging method could be applied. The main problem of this method arises when a real time access of the measured data is necessary. Moreover accessing multiple trails from a single subject is not practical in specific environments. A solution in such environments would be to fuse trials from multiple subjects. Statistically it was observed in human performance studies that a team of individuals always outperforms individuals especially when performance requires a collection of various skills, judgment and experience under time constraints [6]. An analogy from this fact can be utilized to state that a better performance could be expected if a single-trail EEG data from a group of people can be obtained, integrated, and time synchronously correlated. This hypothesis has triggered the development of the closed-loop collaborative method for BCI systems comprising wearable wireless EEG steady-state visual and auditory evoked systems, and potential (SSVEP/AEP) stimulator [8] that aims to improve BCI performance by fusing collaborative brain activities form a group of probands. In the BCI experiment as depicted in the Figure 1.1, the steady state visually and auditory evoked potential (SSVEP/AEP) stimulator together with an EEGsystem forms a feedback loop in which the stimulator triggers the ERP or evoked potentials (EP) in human brains [9].

Figure 1.1 Overview of a cBCI scenario among a group of probands in a feed-back loop where each proband embodied with an EEG-system is stimulated with a common VEP/AEP-Stimulator. As per the EEG signal characteristics the software running on the PC modulates tone and video

A practical framework of collaborative BCI system was proposed for motor action paradigm [10] and its feasibility, practicability and usability were analyzed. Collaborative BCI shows a significant improvement (from 75.8% to 91.4%) in the classification accuracy for human decisions [6]. Yet, the unsolved problems that prevent to bring collaborative BCI to real life applications include low signal quality of non-invasive EEG, high-cost, lack of modularity, high-power consumption, bulky system size, and the challenge of real-time signal processing on multiple BCI platforms.

INTRODUCTION 33

#### 1.2 Research Questions

In comparison to single user BCI, collaborative BCI face considerable technological challenges in both bio-potential data recording from several subjects as well as processing the data time synchronously. Task scheduling and collaborative signal processing among the various BCI systems require a global time prevailing in each EEG-system. For example, in a group experiment many users are stimulated with a sequential stimulus data (image, video and acoustic) for neurofeedback training. Neurophysiologist are then interested to correlate the EEG data from the group of subjects at an instantaneous time to find out the occurrence of ERPs on users with a positive peak (in the range of 2–5 μV) that appears between 300–600 ms after the stimulus. P300 is a common ERP which is used in non-invasive BCI [5]. Realizing a collaborative BCI using P300 ERP, arises the requirement of implementing time synchronization protocol for such group experiments. However, correlating in time the multimodal sensor data (EEG, video, audio) with each other is not trivial since each of the sensor nodes has its own clock with different frequency and stability.

As discussed in the paper [6], the framework for collaborative BCI system uses EEG as input signal. To realize a wireless collaborative BCI system, capable of transmitting data wirelessly to a remote PC being part of the same local area network, a biopotential acquisition system is required to be developed. The functionality of this biopotential acquisition system would require to be extended in such a way so that it could also be realized as a collaborative BCI. A stimulator for triggering ERPs and a live time synchronization using radio modules among EEG-systems are to be developed. Dealing with time synchronization in relation to collaborative EEG experiments has not been described in the literature to date, yet there

is a strong demand for time synchronization to enable further development of non-invasive BCI research. This thesis work strives to tackle these probproblems.

Biomedical electroencephalography signals such as, (EEG), electrocardiogram (ECG), and Electromyography (EMG) have very low amplitude and low frequency. The signal bandwidth of EEG and ECG signals range from 0.1 up to 200 Hz and the amplitude of EEG in in the range between 2–100 μV whereas the ECG signal amplitude lies in the range of 0.5 up to 4 mV [11], [12] It requires meticulous design methodologies in order to acquire and store these signals. Since developing a collaborative BCI requires the storage of data from multiple proband for long time, the system design should be optimized for low power consumption. The power consumption of the system should low enough, so that a 24 hours measurement with a light-weight Lithium-Polymer (LiPo) battery could be conducted. These specifications constitute the difficulty level of the system design. It is very uncomfortable for probands to wear conventional head-box containing wet passive electrodes which also hinders the proband's degree of freedom for long time and increase the risk of strangulation. This results in an increased demand of recording biopotentials with dry electrodes due to its minimal scalp preparation time. However dry electrodes have proved to be prone a voltage drift over time since the impedance between the skin and electrode varies. This is a trade-off of using dry electrodes for the development of biopotential measurement systems.

There exists a huge challenge in transferring the technology from the hospital to the homes of users. The designs of current solutions in hospitals are mostly too cumbersome, complex and gigantic to be brought outside the hospital environment and require expert assistance. Most of the EEG system with high channel density (over 64 channels) is huge box with lots of cables

INTRODUCTION 35

that are impracticable to use outside clinic. A miniaturized, modular system concept with wireless data transmission capability is required to eradicate the risk of strangulation with wireless data transferring mechanism.

#### 1.3 Scope of the Work

During the scope of this work it will be strived to develop a wireless, autarkic biopotential measurement system for long time recording of user data set to be used in collaborative BCI scenario. The system should comprise of interfaces that would let it to be enhanced into a functional collaborative BCI system. The corresponding steady-state visually or auditory evoked potential (SSVEP/AEP) stimulator will also be developed. Furthermore, a bunch of autarkic sync modules (comprising of a synchronization-center and several synchronization-addons) will developed. Those modules will be responsible for live time synchronization of the biopotential measurement system with the help of a suitable wireless time synchronization protocol communicating their timing information on a different channel than that of the biopotential measurement system. This work will additionally provide a full custom system solution including the necessary software components that are required for each of the developed hardware modules (biopotential measurement system, stimulator, sync modules) of the entire BCI system i.e. a firmware for the biopotential measurement system and, a firmware with live time synchronization algorithm for the sync modules. In order to integrate the developed system into a wearable cap, vest, and arm sleeve, assembling and encapsulation of the hardware into suitable clothing will be presented.

#### 1.4 Research Goal

The main three objectives of this thesis work are the following:

- a) Develop a modular, low-power biopotential measurement system that can record from 8—256 channels of biopotential data including both the analog to digital signal processing chain.

- b) Achieving a signal resolution of less than 10 μVpeak-to-peak.

- c) Develop a SSVEP/AEP stimulator that plays media (video, audio) data from as specified in a lookup table (LUT).

- d) Realizing synchronization wirelessly among the biopotential measurement systems so that they can me employed in collaborative BCI experiment scenarios for P300 based BCI applications.

#### 1.5 Thesis Outline

In the following Chapter 2 the theoretical background required for the design and implementation of both biopotential measurement system and time synchronization will be described.

The Chapter 3 of the thesis will talk about the design, prototyping and encapsulation of the biopotential measurement system. It will describe the system in a top-down manner where it'll start with the description of the complete architecture of the biopotential measurement system and then describing each of its sub-units.

In the Chapter 4, the realization of time synchronization with an additional hardware module attachable to existing biopotential measurement system without any hardware modification, described before in the Chapter 3, will be presented.

INTRODUCTION 37

The Chapter 6 will summarize and discuss the work. Thereafter a perspective for future work will be presented so that the system could go to pre-production phase from this research work.

At the end the Chapter 5 will introduce two novel group experiment scenarios where the developed time synchronized collaborative BCI system could be employed. One of them will introduce a quasi-stationary cBCI application scenario and another will introduce a dynamic cBCI application scenario.

# 2 Theoretical Background

Before starting the designing phase it is required to understand the basics of biopotential signals, biopotential electrodes and biopotential amplifiers. As this work is mainly focusing on the development of a time synchronized cBCI system, a brief introduction to BCI and diverse aspects of time synchronization will be discussed in this chapter.

## 2.1 Biopotential Signals

Below in the Table 2-I, the commonly used biopotentials signals, e.g. electrocardiography (ECG), EEG, electromyography (EMG), electroglotography (EGG), electroretinogram (ERG), electrocculogram (EOG), and evoked potentials e.g. auditory evoked potential (AEP), somatosensory evoked potential (SEP), visually evoked potential(VEP) with their typical characteristics are presented.

Table 2-I Range of amplitude and frequency of commonly used biopotential signals

| Signal       | gnal Frequency<br>[Hz] |              | Source              |  |

|--------------|------------------------|--------------|---------------------|--|

| ECG (Heart)  | 0.01-250               | 0.5 - 4      | [11], [13]          |  |

| EEG (Brain)  | 0.5–100                | 0.001 -100   | [11], [13]          |  |

| ECoG (Brain) | 0-500                  | 0.05 – 0.1   | [14], [15]          |  |

| EMG (Muscle) | 0.01-10                | 50-10        | [11], [13]          |  |

| EGG (Throat) | 0.02 – 0.2             | 0.0001-0.005 | [13]                |  |

| EUG (Uterus) | 0-200                  | 100-8000     | [13]                |  |

| ERG (Retina) | 0.2–200                | 0.01-0.1     | [11]                |  |

| EOG (Eye)    | 0-100                  | 0.005 – 0.2  | [11], [13]          |  |

| P300 (ERP)   |                        | $4-10\mu V$  | [16], [1 <b>7</b> ] |  |

Since in this work only EEG, ECG were recorded, so the technical background of these biopotentials will be discussed in the following section of this chapter.

#### 2.1.1 Introduction

Electrochemical activity of certain class of cells which are components of nervous, muscular, or glandular tissue acts towards the generation of biopotential signals. The potential of a membrane of an inactive cell is called resting potential. These cells can be considered as resting potentials in terms of electrical engineering and upon stimulation they generate action potential. Ion exchange through the cell membrane describes the electrical activity of each cell. At the rest state, the permeability of the membrane of the cell is more towards  $K^+$  than  $Na^+$ , and the concentration of  $K^+$  at the exterior of the cell is much lower than the exterior.

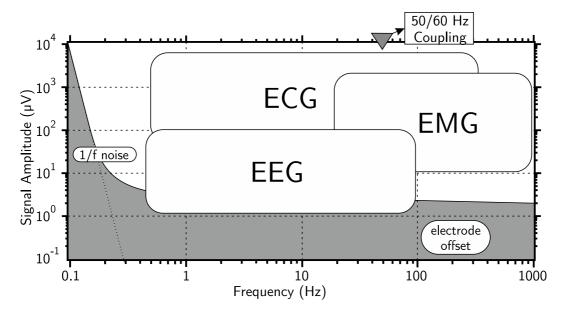

Figure 2.1 Amplitude and frequency characteristics of the biopotential signals, ECG, EEG, EMG and the correlating signals of the biopotential signals

That causes the occurrence of a diffusion gradient of  $K^+$  at the exterior of the cell, creating a potential difference with respect to the interior – resulting in an electrical field towards the interior of the cell. At steady state, this

electric field balances the diffusion gradient and a polarization voltage of nearly -70 mV is reached at equilibrium. When the central nervous system stimulates the cell electrically, the permeability of the membrane towards  $\text{Na}^+$  ions increases and a diffusion of  $\text{Na}^+$  inside the cell occurs – resulting potential increase of the interior of the cell. As soon as the potential of the cell reaches +40 mV, the permeability of the membrane towards  $\text{Na}^+$  decreases and increases towards  $\text{K}^+$  – resulting a sharp decrease in the membrane while reaching to the rest state. This cycle of the cellular potential is called action potential. The biopotential signals, e.g. EEG, ECG, EMG, etc. are the consequence of diverse action potentials that are produced by combination of different cells [18].

The EEG is represented by a difference in potential measured between various points on the scalp. The electrical activity of the brain created by a group of neurons is measured with EEG. The electrical activity on the scalp arises as a result of neural activity whose action can be regarded as a collection of distributed current sources embedded in a volume conductor (the head). During the active stage of the brain, communication patterns alter across large number of neurons, primarily in the form of synaptic state changes. How such synaptic activity lead to local changes in membrane do is explained above. The local change in potential is termed as post-synaptic potential (PSP) [19]. The local field potential (LFP) was generated due to the changes in ionic currents and LFP associated with a single cell synaptic activity is very small. However a substantial current source is created when a synchronized activation of large number of specific set of neurons in the cortex sharing similar orientation during brain activity causing sum of the LFPs. A diverse combination of current sources occurs due to different brain states. These current sources are mixed and filtered as they manifest as biopotentials on the scalp. As a consequence an ill-defined inverse problem

can be stated that reconstructs the position and geometry of such sources (here volumetric localization of neural activity). However, the temporal resoresolution of neural activity is unaffected and therefore the EEG contains accurate regarding timing of neural activation patterns [18]

Similarly ECG is the representation of electrical activity of heart. It is measured with electrodes placed on chest and it has three main feature characteristics. Those are P-wave, the QRS-complex, and the T-wave [20]. EMG is the electrical potential of the skeletal muscle cells, which is generated during the contraction of the muscle.

The distribution of amplitude and frequency of this standard biopotential signals EEG, ECG, EMG are shown in the Figure 2.1 that was measured with surface electrodes. There are three correlating signals that cause problem in extracting biopotential signals from human body. One of them is 1/f noise of the transistor present in the amplifier, secondly, 50-Hz interference from the mains, and the last one is the direct current (DC) differential electrode offset voltage between the biopotential electrodes and human skin. The readout circuit should be able reject, filter these unwanted signals, frequency present with the biopotential signals.

#### 2.1.2 Biopotential Electrodes