# Design Techniques for High-Performance SAR A/D Converters

### Mojtaba Bagheri

Department of Engineering University of Cambridge

This thesis is submitted for the degree of Doctor of Philosophy

#### **Declaration**

This thesis is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text. It is not substantially the same as any that I have submitted, or, is being concurrently submitted for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my thesis has already been submitted, or, is being concurrently submitted for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. It does not exceed the prescribed word limit for the relevant Degree Committee

Mojtaba Bagheri July 2019

#### **Abstract**

#### Design Techniques for High-Performance SAR A/D Converter

Mojtaba Bagheri

The design of electronics needs to account for the non-ideal characteristics of the device technologies used to realize practical circuits. This is particularly important in mixed analog-digital design since the best device technologies are very different for digital compared to analog circuits. One solution for this problem is to use a calibration-correction approach to remove the errors introduced by devices, but this adds complexity and power dissipation, as well as reducing operation speed, and so must be optimised. This thesis addresses such an approach to improve the performance of certain types of analog-to-digital converter (ADC) used in advanced telecommunications, where speed, accuracy and power dissipation currently limit applications. The thesis specifically focuses on the design of compensation circuits for use in successive approximation register (SAR) ADCs.

ADCs are crucial building blocks in communication systems, in general, and for mobile networks, in particular. The recently launched fifth generation of mobile networks (5G) has required new ADC circuit techniques to meet the higher speed and lower power dissipation requirements for 5G technology. The SAR has become one of the most favoured architectures for designing high-performance ADCs, but the successive nature of the circuit operation makes it difficult to reach  $\sim$ GS/s sampling rates at reasonable power consumption.

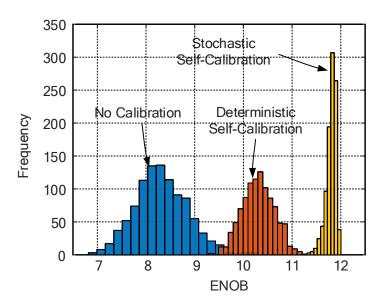

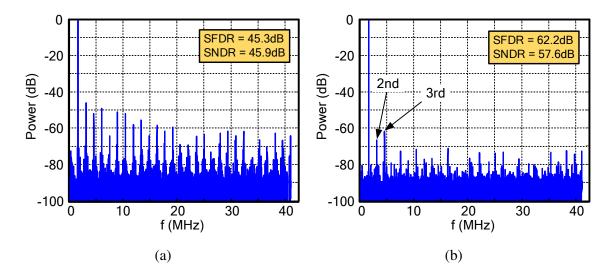

Here, two calibration techniques for high-performance SAR ADCs are presented. The first uses an on-chip stochastic-based mismatch calibration technique that is able to accurately compute and compensate for the mismatch of a capacitive DAC in a SAR ADC. The stochastic nature of the proposed calibration method enables determination of the mismatch of the CAP-DAC with a resolution much better than that of the DAC. This allows the unit capacitor to scale down to as low as 280aF for a 9-bit DAC. Since the CAP-DAC causes a large part of the overall dynamic power consumption and directly determines both the sizes of the driving and sampling switches and the size of the input capacitive load of the ADC and the kT/C noise power, a small CAP-DAC helps the power efficiency. To validate the proposed calibration idea, a 10-bit asynchronous SAR ADC was fabricated in 28-nm CMOS. Measurement results

show that the proposed stochastic calibration improves the ADC's SFDR and SNDR by 14.9 dB, 11.5 dB, respectively. After calibration, the fabricated SAR ADC achieves an ENOB of 9.14 bit at a sampling rate of 85 MS/s, resulting in a Walden FoM of 10.9 fJ/c-s.

The second calibration technique is a timing-skew calibration for a time-interleaved (TI) SAR ADC that calibrates/computes the inter-channel timing and offset mismatch simultaneously. Simulation results show the effectiveness of this calibration method.

When used together, the proposed mismatch calibration technique and the timing-skew calibration technique enables a TI SAR ADC to be designed that can achieve a sampling rate of  $\sim$ GS/s with 10-bit resolution and a power consumption as low as  $\sim$ 10mW; specifications that satisfy the requirements of 5G technology.

To my parents

#### Acknowledgements

There is an endless list of people who contributed to this thesis without the help of whom this thesis would have not been possible.

First, I'd like to thank my current supervisor, Dr. David Hasko, for his kind support and guidance, and also my former supervisor, Professor Arokia Nathan, who was an inspiring supervisor in academic matters and also an encouraging and very supportive friend.

My special thanks goes to Professor Bogdan Staszewski at University College Dubin who provided me with simulation tools as well as tape-out opportunity and also his team members specially Dr. Filippo Schembari and Naser Pourmousavian who helped me a lot with the design and lay-out of the chip. This thesis would have definitely not been possible without their help.

I would also like to gratefully thank Dr. Hashem Zare-Hoseini for his technical advice. He was very kind to be always available to answer my technical questions. He has had a great contribution to the design of the chip.

I'd like to acknowledge HiSilicon (Huawei) who provided funding for this project as well as technical support. I'd also like to thank TSMC for chip fabrication.

Finally, I would like to thank my parents and my brother for their continued love and support during this 4-year PhD.

## **Table of contents**

| Li | List of figures |         |                                                  |    |

|----|-----------------|---------|--------------------------------------------------|----|

| Li | st of t         | ables   |                                                  | i  |

| 1  | Intr            | oductio | on                                               | 1  |

| 2  | Fun             | dament  | tals of A/D Conversion                           | 5  |

|    | 2.1             | Ideal A | A/D Converter                                    | 5  |

|    | 2.2             | Non-Io  | deal A/D Converter                               | 7  |

|    |                 | 2.2.1   | Offset Error                                     | 7  |

|    |                 | 2.2.2   | Gain Error                                       | 7  |

|    |                 | 2.2.3   | Differential Nonlinearity Error (DNL)            | 8  |

|    |                 | 2.2.4   | Integral Nonlinearity Error (INL)                | 9  |

|    |                 | 2.2.5   | Dynamic Range                                    | 10 |

|    | 2.3             | ADC A   | Architectures                                    | 10 |

|    |                 | 2.3.1   | Serial ADC                                       | 10 |

|    |                 | 2.3.2   | Flash ADC                                        | 13 |

|    |                 | 2.3.3   | Interpolating ADC                                | 16 |

|    |                 | 2.3.4   | Folding ADC                                      | 17 |

|    |                 | 2.3.5   | Pipeline ADC                                     | 20 |

|    |                 | 2.3.6   | Oversampling ADC                                 | 23 |

|    |                 | 2.3.7   | SAR ADC                                          | 27 |

| 3  | SAF             | R ADC:  | Circuit Design Considerations and Implementation | 35 |

|    | 3.1             | Capac   | itive DAC                                        | 35 |

|    |                 | 3.1.1   | Architecture                                     | 35 |

|    |                 | 3.1.2   | Switching Schemes                                | 40 |

|    |                 | 3.1.3   | Redundancy                                       | 42 |

|    | 3.2             | SAR (   | Control Logic                                    | 46 |

**i** Table of contents

|   |      | 3.2.1    | Synchronous                                       | 46  |

|---|------|----------|---------------------------------------------------|-----|

|   |      | 3.2.2    | Asynchronous                                      | 49  |

|   |      | 3.2.3    | Special Techniques                                | 51  |

|   | 3.3  | Compa    | arator                                            | 54  |

|   |      | 3.3.1    | Double-Tail Comparator                            | 55  |

|   | 3.4  | Sampl    | ing Network                                       | 60  |

|   |      | 3.4.1    | Sampling Jitter                                   | 65  |

| 4 | Misn | natch (  | Calibration Techniques                            | 67  |

|   | 4.1  | Detect   | ion                                               | 67  |

|   | 4.2  | Correc   | etion                                             | 81  |

|   |      | 4.2.1    | Analog                                            | 81  |

|   |      | 4.2.2    | Digital                                           | 82  |

| 5 | Stoc | hastic N | Mismatch Calibration                              | 85  |

|   | 5.1  | Gaussi   | ian Error Function                                | 86  |

|   | 5.2  | Theore   | etical Background of Stochastic Quantization      | 86  |

|   | 5.3  | Calibra  | ation Process                                     | 90  |

|   |      | 5.3.1    | Computation of $\mu$ and $\sigma$                 | 91  |

|   |      | 5.3.2    | Mismatch Calibration                              | 91  |

|   |      | 5.3.3    | Auxiliary Comparator                              | 96  |

|   | 5.4  | Detern   | ministic vs. Stochastic Calibration               | 98  |

| 6 | A 10 | -bit 851 | MS/s SAR ADC with Stochastic Mismatch Calibration | 101 |

|   | 6.1  | Capaci   | itive DAC                                         | 103 |

|   | 6.2  | SARC     | Control Logic                                     | 106 |

|   | 6.3  | Compa    | arator                                            | 109 |

|   | 6.4  | Sampl    | ing Network                                       | 109 |

|   | 6.5  | Input S  | Sampling Signal                                   | 109 |

|   | 6.6  | Misma    | atch Calibration                                  | 110 |

|   | 6.7  | Design   | n for Testability                                 | 113 |

|   | 6.8  | Measu    | rement Protocol                                   | 113 |

|   | 6.9  | Test Se  | etup                                              | 115 |

|   |      | 6.9.1    | Prototype Chip                                    | 115 |

|   |      | 6.9.2    | Printed Circuit Board (PCB)                       | 115 |

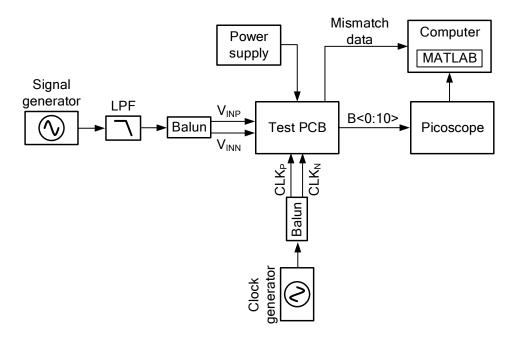

|   |      | 6.9.3    | Measurement Setup                                 | 117 |

|   | 6.10 | Measu    | rement Results                                    | 117 |

Table of contents i

|    | 6.11   | Further Discussion on the Calibration Method               | 122 |

|----|--------|------------------------------------------------------------|-----|

|    |        | 6.11.1 Area Overhead                                       | 122 |

|    |        | 6.11.2 Effect of Voltage/Temperature Variations            | 126 |

| 7  | Inte   | rchannel Mismatch Calibration in Time-Interleaved SAR ADCs | 129 |

|    | 7.1    | Offset Mismatch Calibration                                | 132 |

|    | 7.2    | Gain Mismatch Calibration                                  | 132 |

|    | 7.3    | Effect of Timing Mismatch                                  | 133 |

|    | 7.4    | Timing Mismatch Calibration Techniques                     | 139 |

|    |        | 7.4.1 Detection                                            | 139 |

|    |        | 7.4.2 Correction                                           | 149 |

|    | 7.5    | Proposed Calibration Technique                             | 151 |

|    | 7.6    | Nonidealities                                              | 159 |

|    |        | 7.6.1 Triangle Signal Non-Linearity                        | 159 |

|    |        | 7.6.2 Capacitive DAC and DTC Non-Linearity                 | 160 |

|    | 7.7    | Simulation Results                                         |     |

| 8  | Con    | clusion                                                    | 165 |

|    | 8.1    | Thesis Contribution                                        | 165 |

|    | 8.2    | Future Work                                                | 166 |

| Re | eferen | ces                                                        | 167 |

| Αı | pend   | ix Verilog Code for the Mismatch Calibration               | 183 |

# List of figures

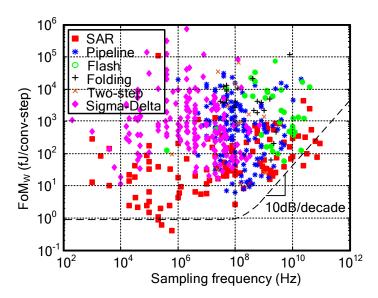

| 1.1  | Plot of Walden FoM vs Nyquist sampling frequency for all ADC papers presented at ISSCC and VLSI from 1997-2018                                                              | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

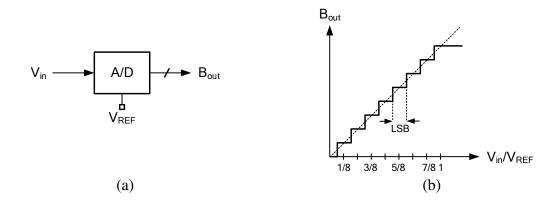

| 2.1  | Ideal A/D converter: (a) Block digram, (b) input/output transfer curve for a                                                                                                | 6  |

|      | 3-bit ADC                                                                                                                                                                   | 6  |

| 2.2  | The ADC model with the quantization error                                                                                                                                   | 6  |

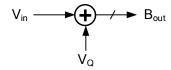

| 2.3  | Illustration of (a) offset error, (b) gain error. Offset error is the deviation of transfer curve from the first transition and gain error is the difference                |    |

|      | between the ideal (best-fit) and actual response curves                                                                                                                     | 8  |

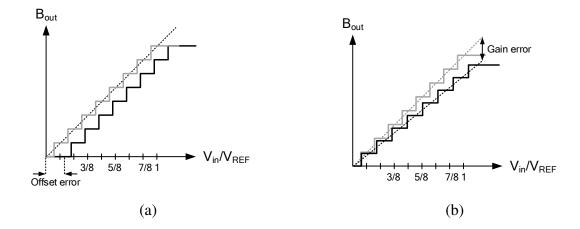

| 2.4  | Illustration of (a) DNL error and (b) INL error. DNL is the deviation of every code width from 1 LSB and INL is the deviation of the code transition from                   |    |

|      | its ideal location                                                                                                                                                          | 9  |

| 2.5  | Block diagram of a single-slope serial ADC. The counter stops counting once $V_{\text{ramp}}$ becomes equal to $V_{\text{in}}$ . This way, the binary output of the counter |    |

|      | would be proportional to the input voltage                                                                                                                                  | 11 |

| 2.6  | Dual-slope ADC (a) block diagram, (b) timing diagram for three different                                                                                                    |    |

|      | input voltages. The accuracy of this A/D converter does not depend on the                                                                                                   |    |

|      | time constant of the integrator                                                                                                                                             | 12 |

| 2.7  | Asynchronous digital-slope ADC: (a) block diagram, (b) timing diagram. Contrary to a synchronous serial ADC, here no high speed clock is required.                          |    |

|      | The counter is also replaced by delay elements                                                                                                                              | 13 |

| 2.8  | Block diagram of a Flash ADC. Owning to their simple structure, flash ADCs are inherently fast.                                                                             | 14 |

| 2.9  | Offset cancellation through offset storage: (a) input offset storage, (b) output                                                                                            |    |

|      | offset storage. Offset is reduced by a factor A                                                                                                                             | 15 |

| 2.10 | Realization of (a) factor 2, (b) factor 4 interpolation. Interpolation of factor                                                                                            |    |

|      | M reduces the number of pre-amplifiers by the same factor                                                                                                                   | 16 |

<u>i</u> List of figures

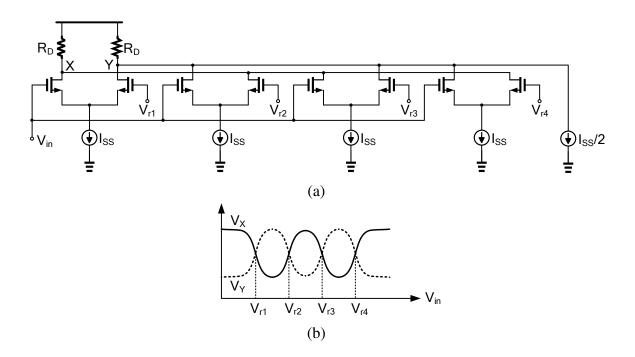

| 2.11 | (a) Block diagram of a folding ADC with a folding factor of $2^{N_1}$ , (b) input-output folding transfer curve for a folding factor of 4                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.12 | Factor 4 folding: (a) Implementation, (b) voltage of the folding nodes                                                                                                                                                                                        |

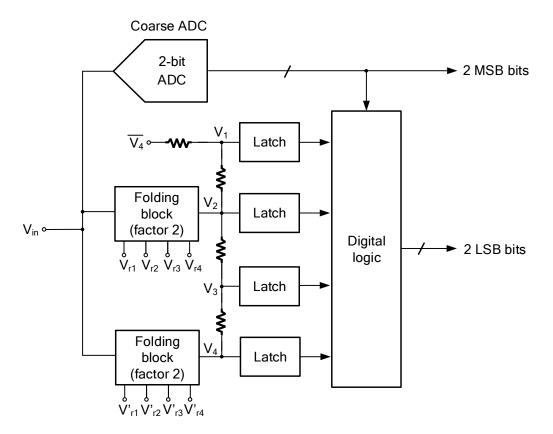

|      | A factor 4 folding-interpolating ADC                                                                                                                                                                                                                          |

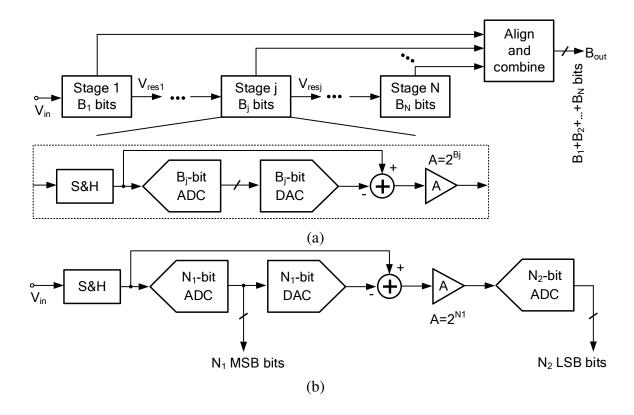

|      | Architecture of a pipeline ADC: (a) generic topology, (b) the specific case of a pipeline ADC with only two stages, also known as two-step ADC. In a pipeline ADC, different stages work in parallel, enabling this ADC to reach high speeds                  |

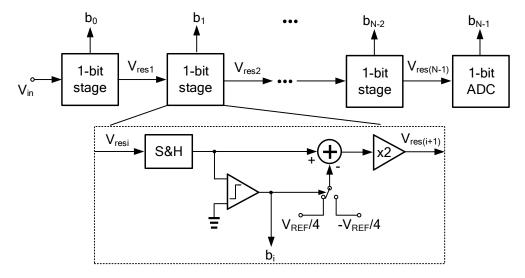

| 2.15 | A one-bit-per-stage pipeline ADC                                                                                                                                                                                                                              |

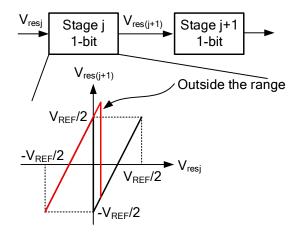

| 2.16 | Sub-ADC error for a 1-bit per stage pipeline ADC. Here, the residue voltage has fallen outside the allowable range $\pm V_{\rm REF}/2$ . This causes performance degradation                                                                                  |

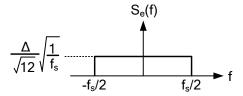

| 2.17 | The topology of a 1.5-bit per stage converter: (a) circuit implementation, (b) the input-output transfer curve. A 1.5b/stage converter can tolerate comparator offset as large as $\pm V_{\rm REF}/4$ without any degradation of the performance.             |

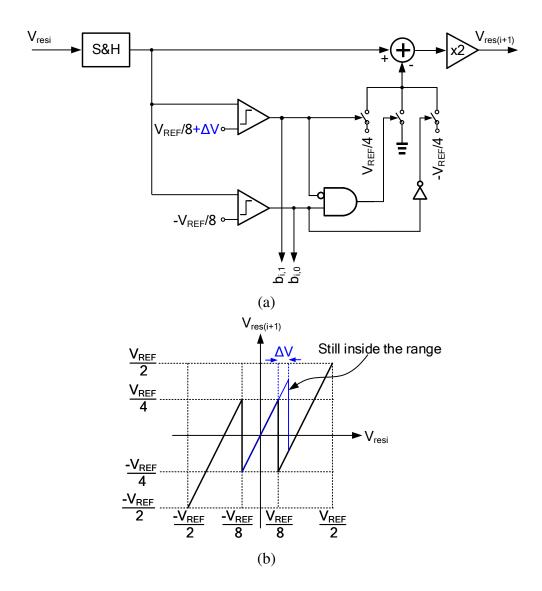

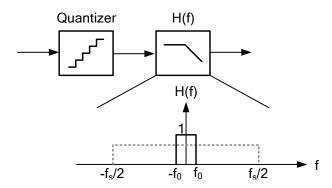

| 2.18 | Spectral density of the quantization noise. $\Delta$ is the quantization step                                                                                                                                                                                 |

|      | Filtering out the quantization noise using a low-pass filter. This enhances the                                                                                                                                                                               |

| /    | SQNR by a factor of $f_s/2f_0$                                                                                                                                                                                                                                |

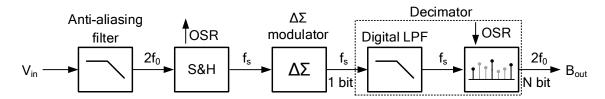

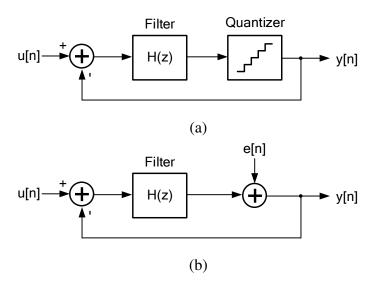

| 2.20 | Block diagram of an oversampling ADC with noise shaping. Noise shaping takes place in the $\Delta\Sigma$ modulator                                                                                                                                            |

| 2.21 | Principle of noise shaping: (a) Block diagram implementation, (b) linear model by replacing the quantizer with an injected noise. Noise shaping is a technique to push the unwanted noise out of the band of interest in order to achieve higher resolutions. |

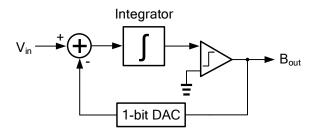

| 2.22 | Block digram of a first order modulator. This performs a first-order nosic shaping and improves the SQNR by 9dB/octave                                                                                                                                        |

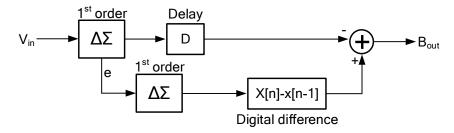

| 2.23 | MASH architecture: cascade of 1st order $\Delta\Sigma$ modulators to build a 2nd order one                                                                                                                                                                    |

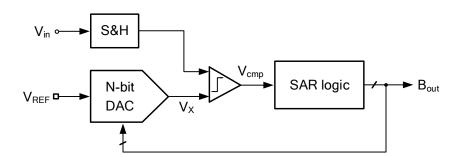

| 2.24 | Block diagram of a SAR ADC. SAR ADC is mainly made up of digital blocks. This is an advantage when migrating to a new technology                                                                                                                              |

| 2.25 | Signal flow diagram of the successive-approximation approach                                                                                                                                                                                                  |

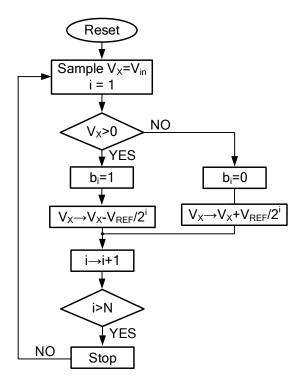

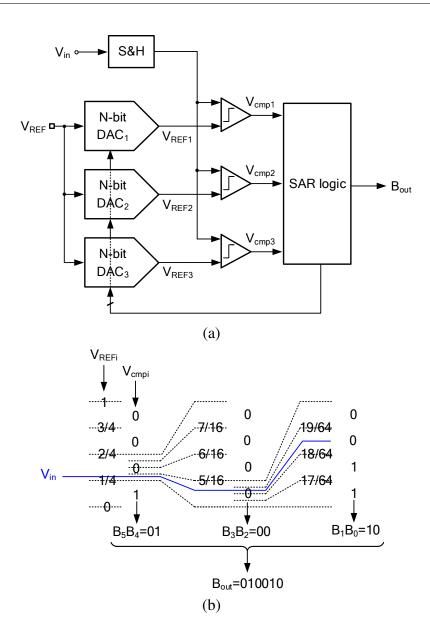

|      | Operation of a 5-bit SAR ADC: (a) sampling phase, when $V_{\rm in}$ is sampled on the top plate of the capacitor array, (b) bit cycling phase to determine the MSB bit. The position of the corresponding bottom plate switch is                              |

|      | determined based on the output of the comparator. The bit cycling process continues in the same manner until all the bits are resolved                                                                                                                        |

List of figures i

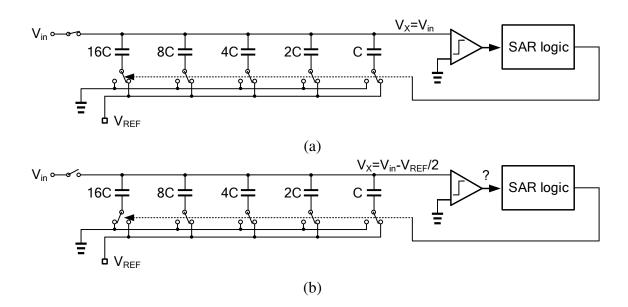

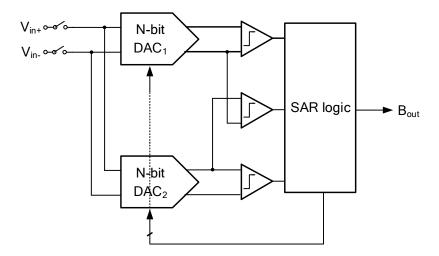

| 2.27 | (a) Block diagram of an $N$ -bit 2-bit/cycle SAR ADC, (b) conversion cycle for the case of $N=6$ . Theoretically, a 2-bit/cycle SAR ADC can operate         |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | twice as fast as its conventional 1-bit/cycle counterpart                                                                                                   | 30 |

| 2.28 | A 2b/cycle SAR ADC with interpolation. Here, interpolation helps to reduce                                                                                  |    |

|      | the number of the DACs by one                                                                                                                               | 31 |

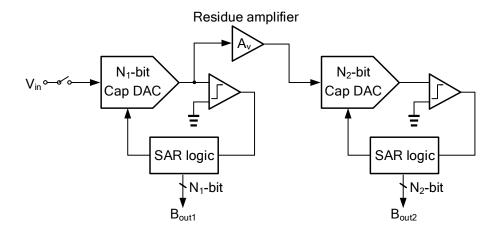

| 2.29 | Block digram of a pipeline SAR ADC. It is basically a two-stage pipeline                                                                                    |    |

|      | ADC with each stage being a SAR ADC                                                                                                                         | 32 |

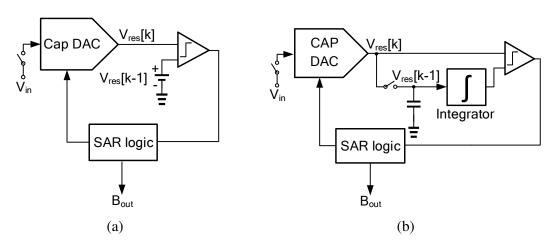

| 2.30 | Noise-shaped SAR ADC: (a) block diagram implementation, (b) improve-                                                                                        |    |

|      | ment of the noise shaping by adding an integrator. The noise shaping occurs                                                                                 |    |

|      | in the same manner as in a $\Delta\Sigma$ modulator                                                                                                         | 33 |

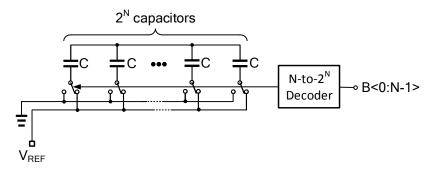

| 3.1  | Thermometer and conscitive DAC. This type of DAC is known for its small                                                                                     |    |

| 3.1  | Thermometer-code capacitive DAC. This type of DAC is known for its small DNL error. However, the need for a decoder as well as the large number of          |    |

|      | capacitors for high resolutions limit its application                                                                                                       | 36 |

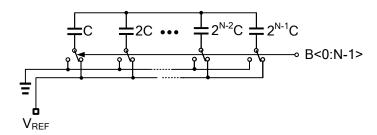

| 2.2  | Binary-weighted capacitive DAC. This type of DAC is probably the most                                                                                       | 30 |

| 3.2  |                                                                                                                                                             | 37 |

| 2.2  | popular one own to its simple structure                                                                                                                     | 31 |

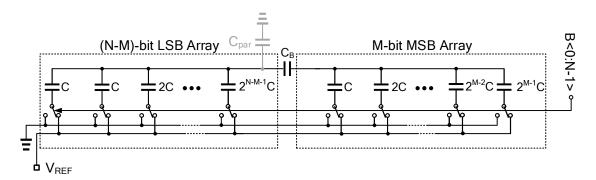

| 3.3  | Bridge-capacitor DAC. The parasitic capacitance on the left plate of $C_B$                                                                                  | 38 |

| 2.4  | degrades the linearity                                                                                                                                      | 30 |

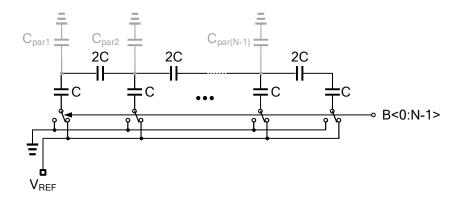

| 3.4  | C-2C DAC. This type of DAC requires only 3N unit capacitors and introduces                                                                                  | 20 |

| 2.5  | an input load of only 3C. However, the parasitic capacitors limit the linearity.  Passive Charge sharing based DAC. The reference voltage is sampled on the | 39 |

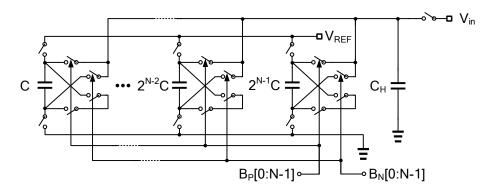

| 3.5  | Passive Charge-sharing-based DAC. The reference voltage is sampled on the                                                                                   |    |

|      | capacitive array before the conversion starts, and no current is drawn from it                                                                              | 20 |

| 2.6  | during the conversion.                                                                                                                                      | 39 |

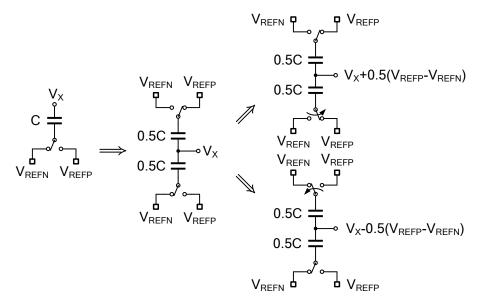

| 3.6  | Principle of the split capacitor switching scheme                                                                                                           | 41 |

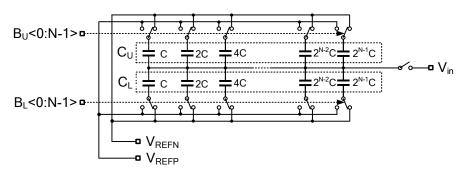

| 3.7  | An N-bit binary-weighted split-capacitor array. The split-capacitor archi-                                                                                  |    |

|      | tecture guarantees constant CM voltage and requires only two reference                                                                                      |    |

|      | voltages. However, it need two independent control signals which would call                                                                                 | 41 |

| 2.0  | for a more complex SAR logic circuit.                                                                                                                       | 41 |

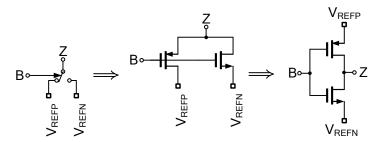

| 3.8  | Circuit implementation of the bottom-plate switch                                                                                                           | 42 |

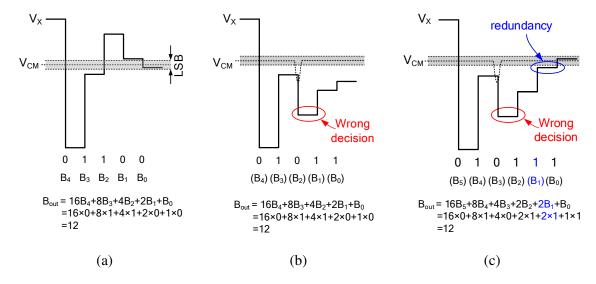

| 3.9  | Binary search (a) with no error, (b) with a wrong decision, (c) with correction                                                                             | 42 |

| 2.10 | through redundancy                                                                                                                                          | 43 |

|      | An implementation of non-binary capacitive array.                                                                                                           | 45 |

| 3.11 | Timing diagram of synchronous SAR scheme. The clock frequency should                                                                                        |    |

|      | be at least <i>N</i> times higher than the sampling rate of the ADC. Generation of                                                                          | 4. |

| 0.10 | this clock could be a real challenge especially for high speed SAR ADCs.                                                                                    | 46 |

| 3.12 | Basic block digram of a synchronous SAR logic controller. The building                                                                                      | ۸- |

|      | block is a DFF                                                                                                                                              | 47 |

<u>i</u> List of figures

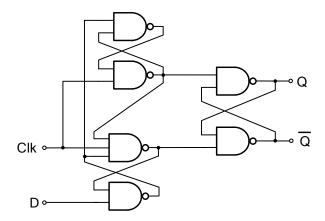

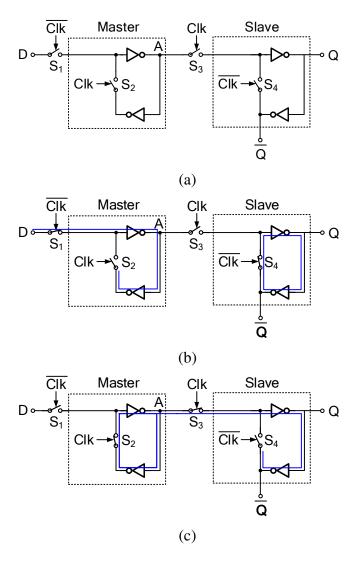

| 3.13 | Conventional logic-gate-based DFF. This type of DFF is not suited for high-speed applications.                                                          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.14 | Switch-base DFF: (a) topology, (b) clock is low and the previous data is stored by the back-to-back inverters of the Slave stage, (c) clock is high and |

|      | the current data is sampled on node A and Q                                                                                                             |

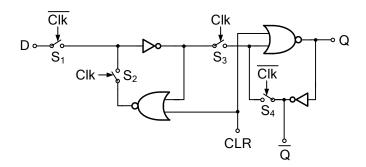

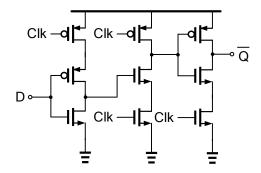

|      | Modification of Fig. 3.14 with the clear signal                                                                                                         |

| 3.16 | Dynamic DFF. This type of DFF, if designed properly, can achieve high speeds with low power consumption.                                                |

| 3 17 | Timing digram of the asynchronous SAR scheme along with the compara-                                                                                    |

| 3.17 | tor input/output signals. The comparator is reset right after a decision is                                                                             |

|      | made (plus a delay for the DAC settling) and the next comparison starts                                                                                 |

|      | immediately                                                                                                                                             |

| 3.18 | Asynchronous SAR ADC with an auxiliary delay path. In case if the com-                                                                                  |

| 2.10 | parator decision process takes longer that the delay of the auxiliary path, the                                                                         |

|      | valid signal will generated regardless                                                                                                                  |

| 3.19 | Parallel bypass SAR logic: (a) circuit implementation (b) timing diagram.                                                                               |

|      | This technique completely eliminates the delay of the SAR logic from the                                                                                |

|      | total loop delay.                                                                                                                                       |

| 3.20 | Asynchronous SAR ADC using N comparators. This technique completely                                                                                     |

|      | eliminates the delay of the DFFs in the SAR logic as well as the reset delay                                                                            |

|      | of the comparators                                                                                                                                      |

| 3.21 | StrongARM latch: (a) circuit implementation, (b) voltage of important nodes                                                                             |

|      | during one cycle                                                                                                                                        |

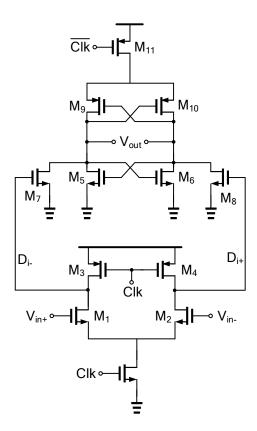

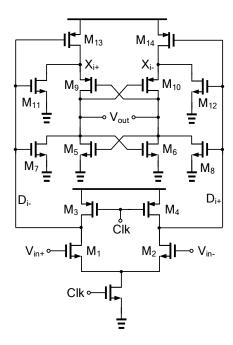

| 3.22 | Double-Tail comparator. Two separate tails are used for the input stage and                                                                             |

|      | the latch stage.                                                                                                                                        |

| 3.23 | Improved double-tail comparator                                                                                                                         |

| 3.24 | Reducing the effect of kickback noise by (a) putting switches between the                                                                               |

|      | input and the output of the latch, (b) capacitive neutralization                                                                                        |

| 3.25 | Kickback noise cancellation through a replica (dummy) comparator. This                                                                                  |

|      | technique is to cancel out both the static and the dynamic kick-back noise.                                                                             |

| 3.26 | Bottom plate sampling. The advantage of the bottom-plate sampling is the                                                                                |

|      | charge-injection independent sampling process                                                                                                           |

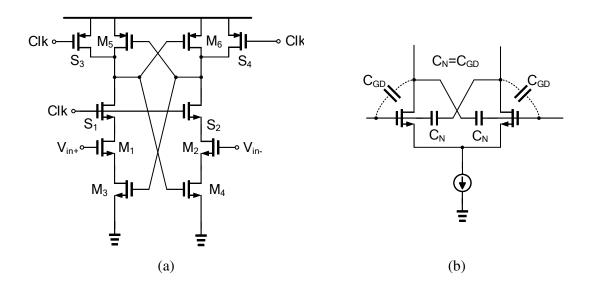

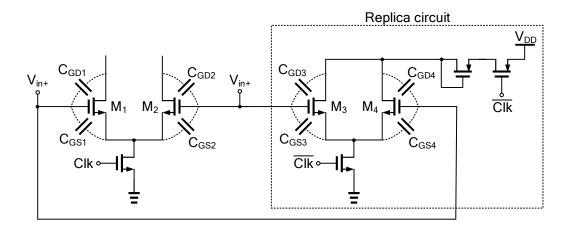

| 3.27 | Bootstrapped switch: (a) principal of operation, (b) circuit realization. Boot-                                                                         |

|      | strapping minimizes the on-resistance of the sampling switch and makes it                                                                               |

|      | input-independent                                                                                                                                       |

| 3.28 | Circuit implementation of the bootstrapped switch                                                                                                       |

List of figures

| 3.29 | Bootstrapped switch during the precharge phase                                                       | 63 |

|------|------------------------------------------------------------------------------------------------------|----|

| 3.30 | Bootstrapped switch during the tracking phase: (a) node $Z$ discharges to                            |    |

|      | ground, (b) $C_B$ appears on the gate-source of $M_S$                                                | 64 |

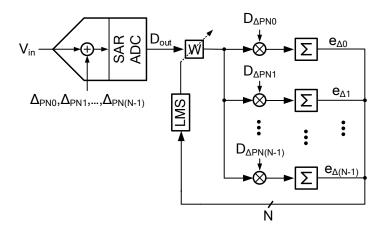

| 4.1  | Core idea of correlation-based calibration. The correlation of $D_{ m out}$ and $D_{\Delta_{ m PN}}$ |    |

|      | is zero only if the ADC is linear                                                                    | 68 |

| 4.2  | Block diagram of the perturbation-based calibration with dual conversion                             | 69 |

| 4.3  | Bit-weight extraction of the perturbation-based calibration through an LMS                           |    |

|      | algorithm                                                                                            | 69 |

| 4.4  | Another implementation of Fig. 4.3. Here <i>N</i> different dithering signals are                    |    |

|      | used                                                                                                 | 70 |

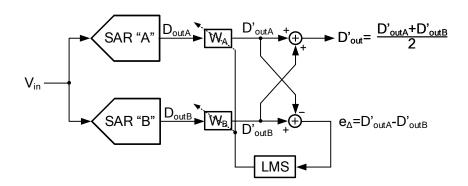

| 4.5  | Block diagram of the split ADC calibration. $e_{\Delta}$ is used to determine the ADC                |    |

|      | bit weights                                                                                          | 71 |

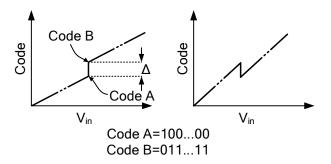

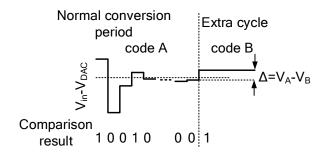

| 4.6  | Transfer characteristic of a SAR ADC with mismatch at MSB capacitor                                  | 72 |

| 4.7  | Mismatch calibration based on Fig. 4.6                                                               | 73 |

| 4.8  | A foreground mismatch calibration based on estimation of the DNL error                               | 73 |

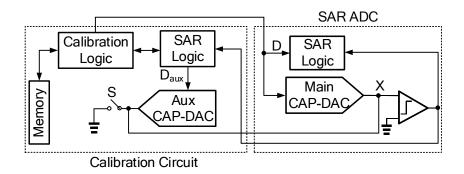

| 4.9  | Block diagram of self-calibration using an auxiliary CAP-DAC                                         | 74 |

| 4.10 | Circuit schematic of an <i>N</i> -bit CAP-DAC                                                        | 74 |

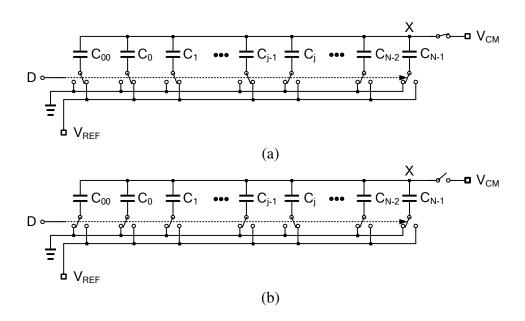

| 4.11 | Bottom-up self-calibration: (a) reset phase, (b) mismatch formation phase                            | 76 |

| 4.12 | Bottom-up approach to calibrate the mismatch of capacitor 32C: (a) reset                             |    |

|      | phase, where $X$ is precharged to $V_{\text{CM}}$ and $D = \{00111111\}$ , (b) error genera-         |    |

|      | tion phase, where the reset switch is open and $D$ changes to $\{01000000\}$ (c)                     |    |

|      | error correction phase, where the auxiliary DAC is progressively increased                           |    |

|      | until $V_X$ becomes zero and comparator output changes                                               | 79 |

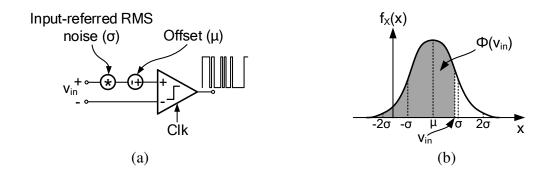

| 5.1  | (a) Model of a comparator with its input-referred noise and offset. (b)                              |    |

|      | Illustration of the input distribution function on the Gaussian curve                                | 87 |

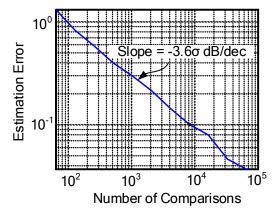

| 5.2  | Error of estimation by (5.8) versus the number of comparisons                                        | 88 |

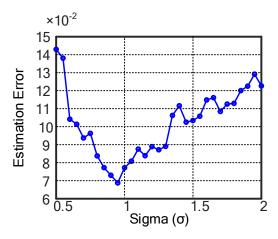

| 5.3  | Error of estimation by (5.8) versus $\sigma$                                                         | 89 |

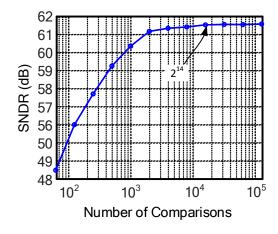

| 5.4  | Output SNDR of the ADC versus the number of comparisons                                              | 89 |

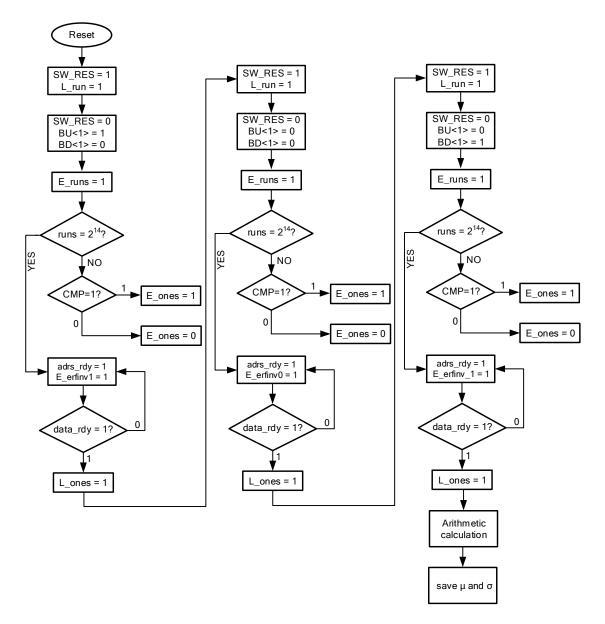

| 5.5  | ASM chart for $\mu/\sigma$ estimation                                                                | 92 |

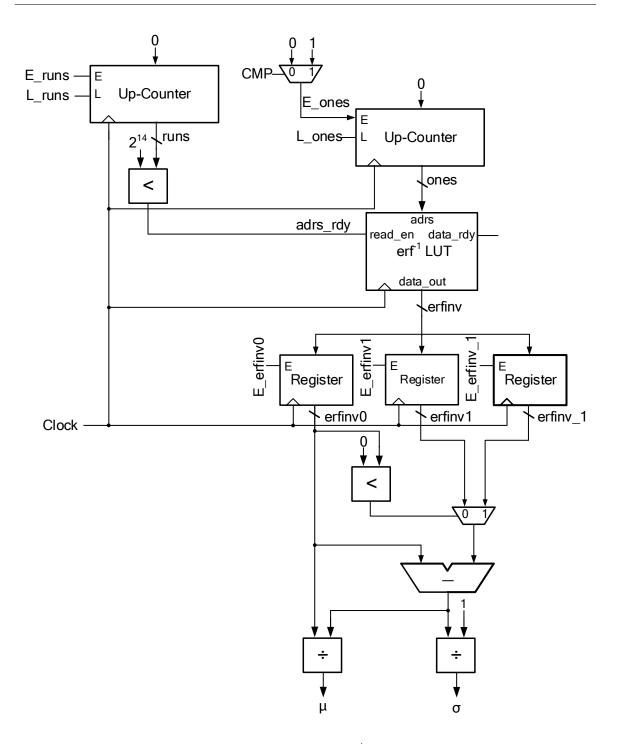

| 5.6  | Datapath circuit for $\mu/\sigma$ estimation                                                         | 93 |

| 5.7  | A differential capacitor array to demonstrate the process of stochastic mis-                         |    |

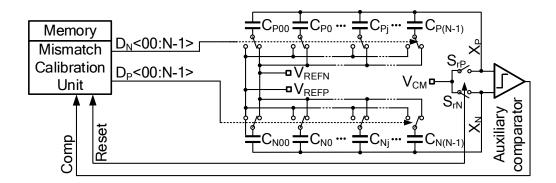

|      | match calibration                                                                                    | 94 |

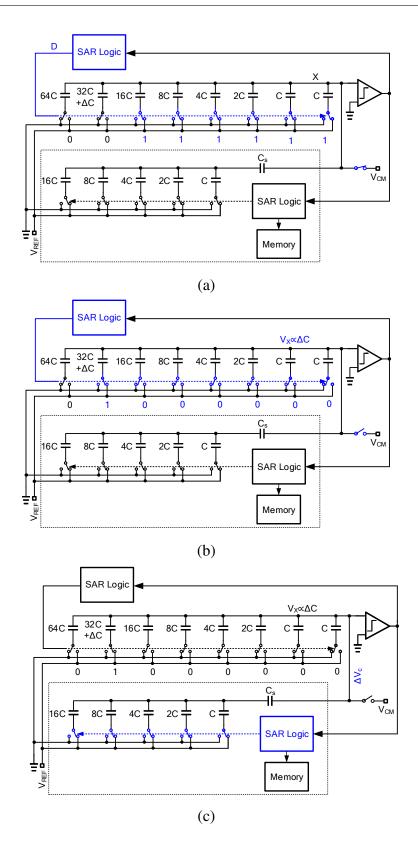

| 5.8  | CAP-DAC during the calibration process: (a) phase I, (b) phase II                                    | 94 |

| 5.9  | Circuit implementation of the auxiliary comparator used for the calibration.                         | 96 |

**i** List of figures

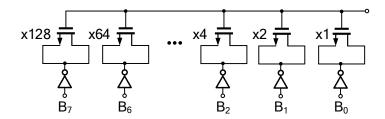

| 5.10 | Digitally controlled variable capacitor using MOSFET as a capacitor. This is for the purpose of offset calibration of the auxiliary comparator | 98  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

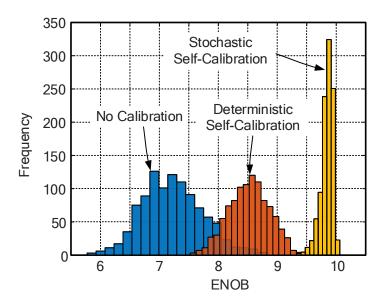

| 5.11 | A comparison between deterministic and stochastic approaches for a 10b                                                                         |     |

|      | ADC                                                                                                                                            | 99  |

| 5.12 | A comparison between deterministic and stochastic approaches for a 12b                                                                         |     |

|      | ADC                                                                                                                                            | 100 |

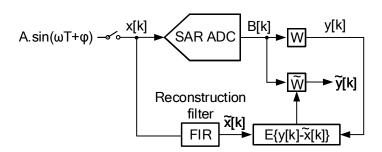

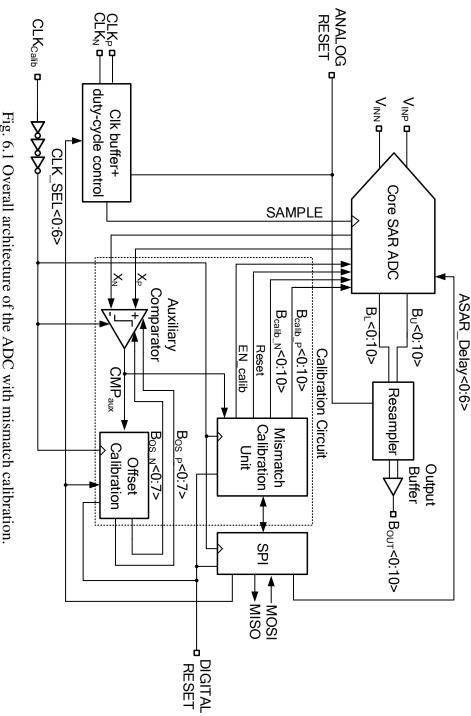

| 6.1  | Overall architecture of the ADC with mismatch calibration                                                                                      | 102 |

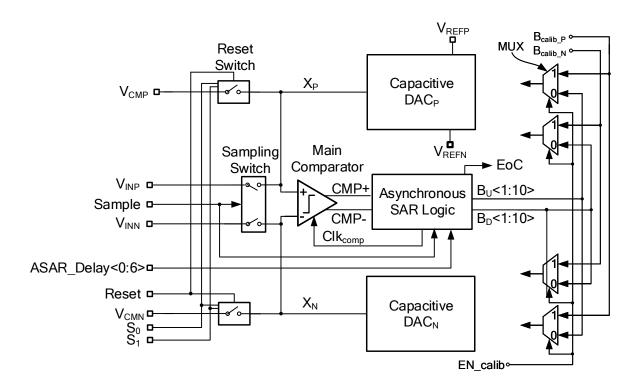

| 6.2  | Block digram of the SAR ADC core                                                                                                               | 103 |

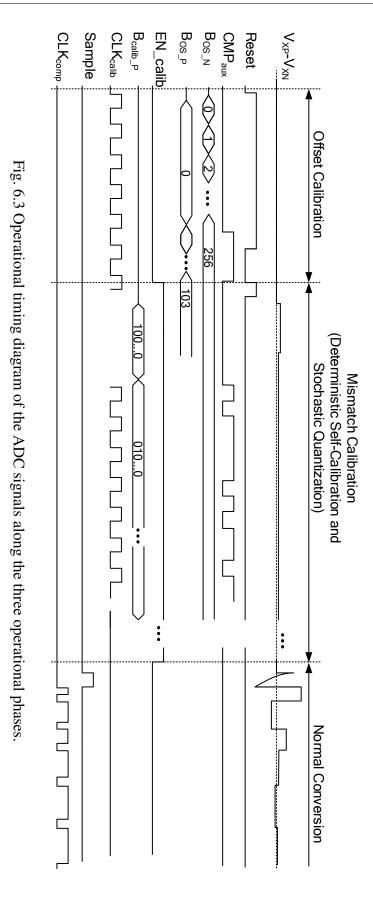

| 6.3  | Operational timing diagram of the ADC signals along the three operational                                                                      |     |

|      | phases                                                                                                                                         | 104 |

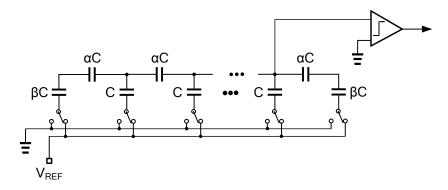

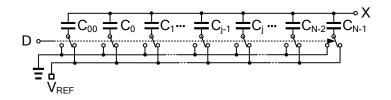

| 6.4  | A 9-bit binary-weighted split-capacitor array with redundancy at $8C$                                                                          | 105 |

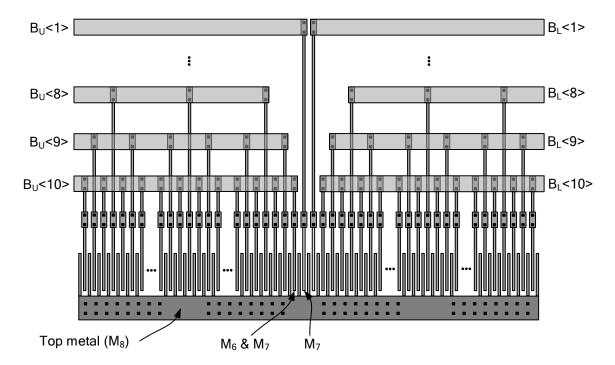

| 6.5  | Inter-digitized layout structure of the split-capacitor array                                                                                  | 105 |

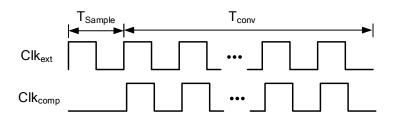

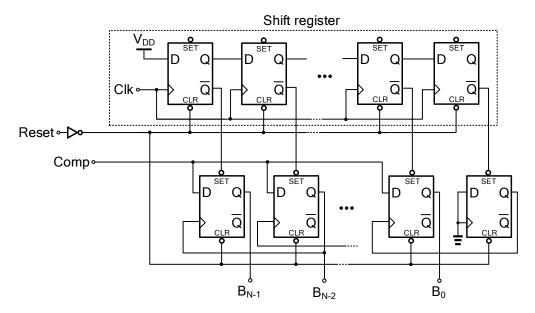

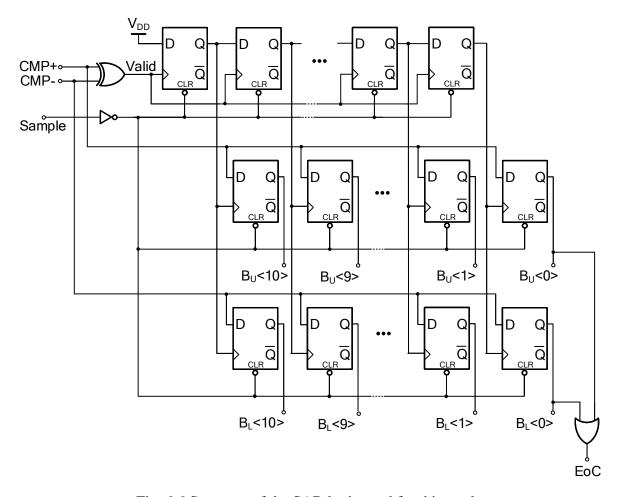

| 6.6  | Structure of the SAR logic used for this work                                                                                                  | 106 |

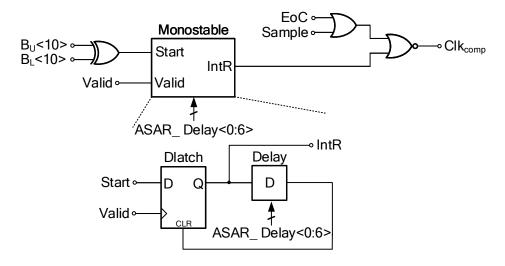

| 6.7  | Asynchronous clock generator of the SAR control logic                                                                                          | 107 |

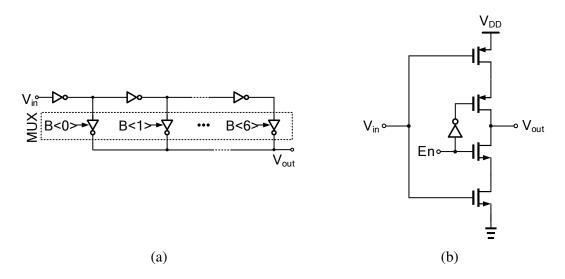

| 6.8  | (a) Implementation of the delay block used in the monostable (b) implemen-                                                                     |     |

|      | tation of the multiplexer                                                                                                                      | 107 |

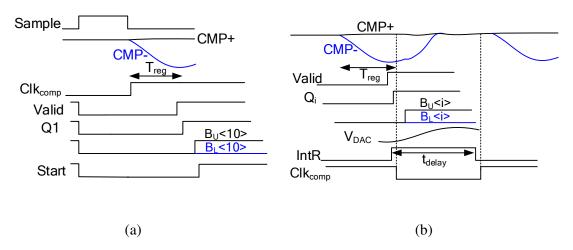

| 6.9  | Waveforms of the SAR logic (a) for the MSB bit, (b) for the bits MSB-1 to                                                                      |     |

|      | LSB                                                                                                                                            | 108 |

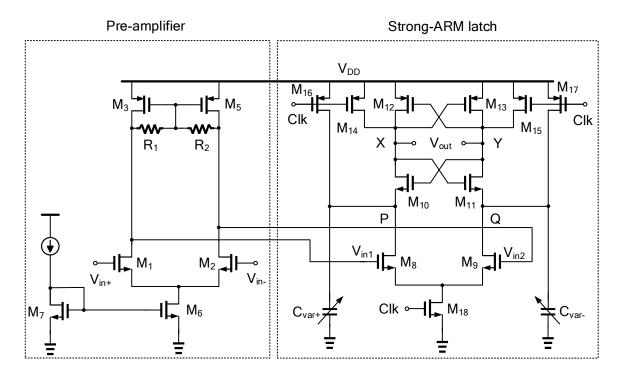

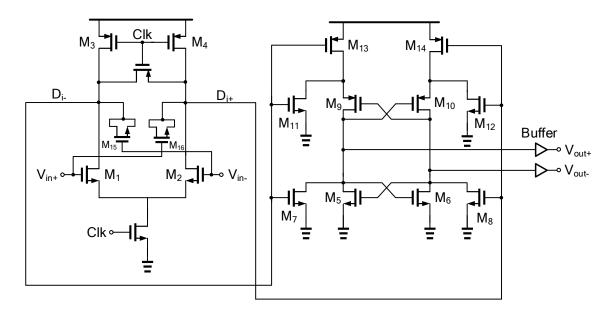

| 6.10 | Topology of the comparator used in this work                                                                                                   | 108 |

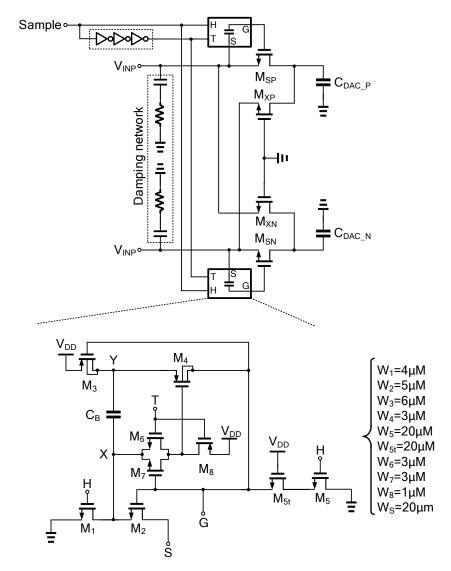

| 6.11 | Input Sampling network                                                                                                                         | 110 |

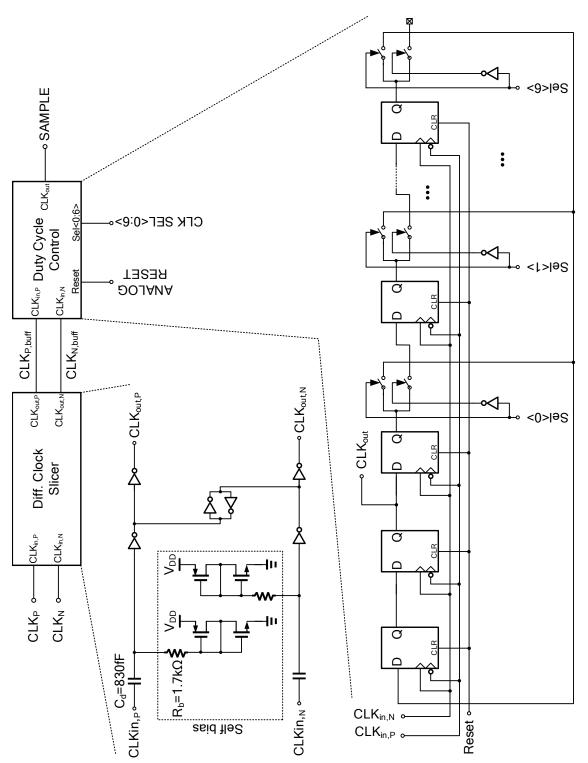

| 6.12 | Circuit to generate the sampling signal from the input differential clock                                                                      | 111 |

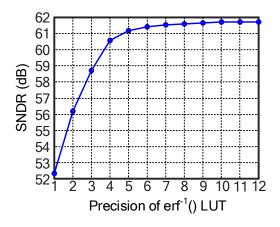

| 6.13 | Output SNDR of the ADC versus the precision of the LUT                                                                                         | 112 |

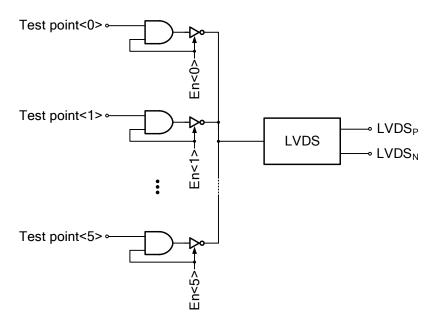

| 6.14 | Block digram of the test-point circuit                                                                                                         | 114 |

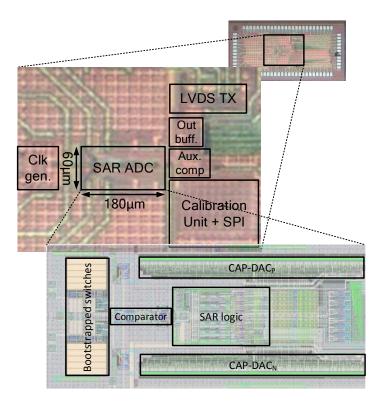

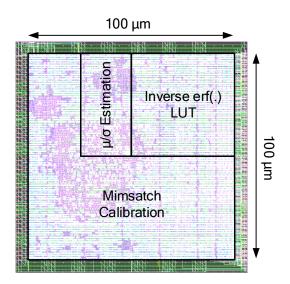

| 6.15 | Chip micrograph                                                                                                                                | 116 |

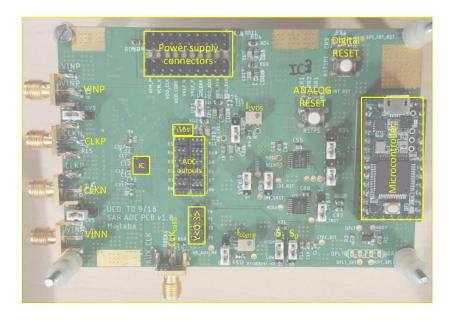

| 6.16 | PCB schematic                                                                                                                                  | 116 |

| 6.17 | Test setup used to characterized the prototype SAR ADC                                                                                         | 117 |

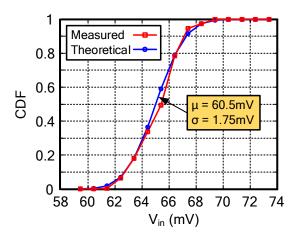

| 6.18 | CDF plot of the auxiliary comparator                                                                                                           | 118 |

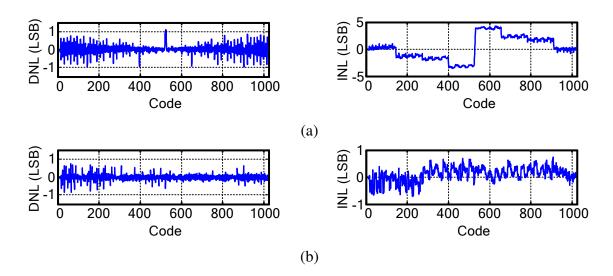

| 6.19 | Static performance of the ADC (a) before and (b) after calibration                                                                             | 118 |

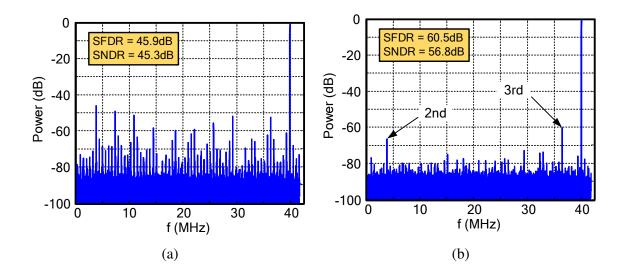

| 6.20 | ADC output spectrum at a sampling frequency of 85MS/s and a 1.5MHz                                                                             |     |

|      | input (a) before calibration, (b) after calibration                                                                                            | 119 |

| 6.21 | ADC output spectrum at a sampling frequency of 85MS/s and Nyquist-rate                                                                         |     |

|      | input (a) before calibration, (b) after calibration                                                                                            | 119 |

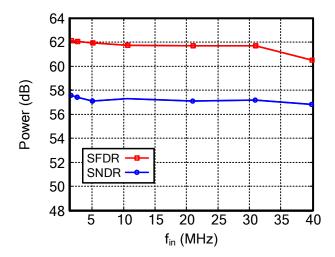

| 6.22 | SFDR and SNDR vs. input frequency at a sampling rate of 85MS/s                                                                                 | 120 |

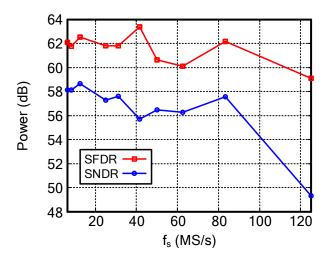

| 6.23 | SFDR and SNDR vs. sampling frequency for a 1.5MHz input                                                                                        | 120 |

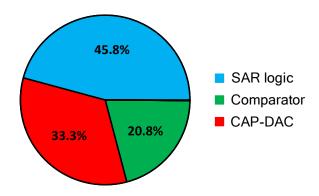

| 6.24 | ADC's power consumption breakdown. As can be seen, the SAR logic                                                                               |     |

|      | dissipates almost half the total power                                                                                                         | 121 |

List of figures i

| 6.25 | Comparison of this work with the ADCs published in ISSCC and VLSI from 1997 until 2018 | 122 |

|------|----------------------------------------------------------------------------------------|-----|

| 6.26 | Area breakdown of the calibration circuit                                              | 125 |

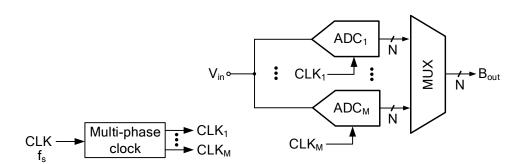

| 7.1  | Block digram of a TI ADC. It is composed of M channels in parallel, a                  |     |

|      | multi-phase clock generator and an output multiplexer                                  | 129 |

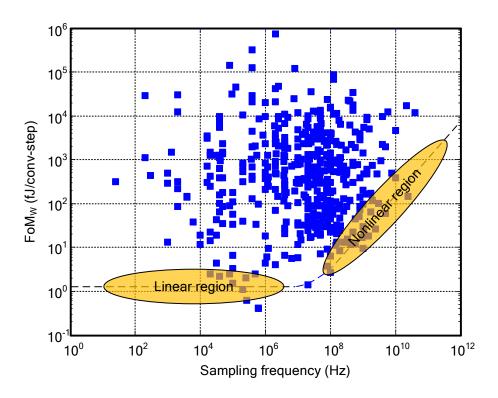

| 7.2  | Single-channel ADCs presented at the ISSCC and VLSI from 1997 until 2018               | 130 |

| 7.3  | Block diagram of the offset calibration for TI ADCs. This approach simply              |     |

|      | uses the average of sub-ADCs' output to estimate their offset                          | 132 |

| 7.4  | Block diagram of the gain calibration for TI ADCs. This approach uses the              |     |

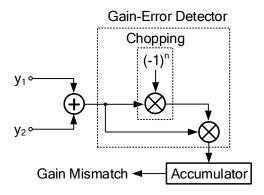

|      | variance of sub-ADCs' output to estimate their gain                                    | 132 |

| 7.5  | Gain mismatch detection using a frequency-domain method                                | 133 |

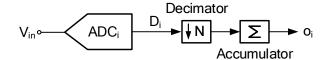

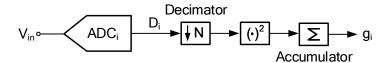

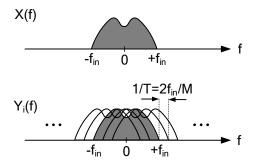

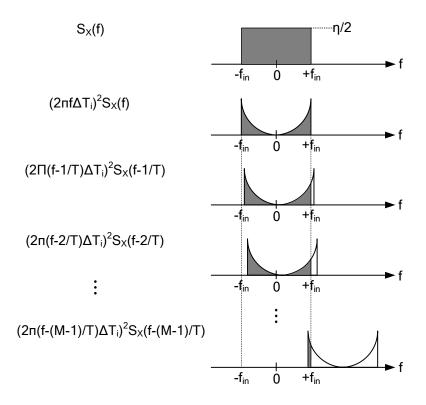

| 7.6  | Magnitude of the output spectrum of one channel of an <i>M</i> -channel TI ADC.        | 134 |

| 7.7  | Illustration of the timing mismatch error of one single channel as presented           |     |

|      | in (7.13) for a random input signal with flat power spectral density                   | 135 |

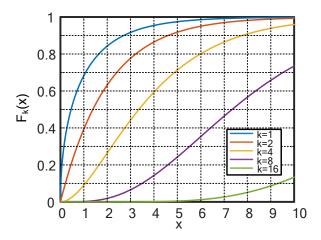

| 7.8  | CDF of chi-squared distribution with $k$ degrees of freedom                            | 137 |

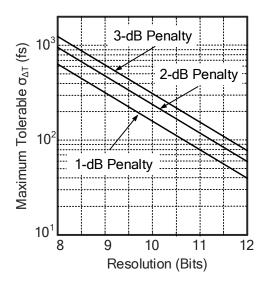

| 7.9  | Maximum tolerable timing error for different SNR penalties for a 16-channel            |     |

|      | TI ADC at $f_{in} = 720$ MHz                                                           | 139 |

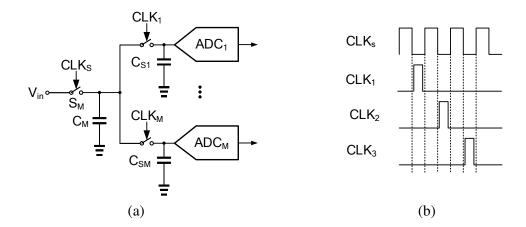

| 7.10 | Sampling using a master switch: (a) block diagram, (b) waveforms of the                |     |

|      | clocks for the first three channels                                                    | 140 |

| 7.11 | Illustration of timing skew calibration with an input ramp                             | 141 |

| 7.12 | Block diagram of a timing skew calibration technique using a pilot tone as             |     |

|      | the input                                                                              | 141 |

| 7.13 | Sampling voltages of a 4-channel TI ADC                                                | 142 |

| 7.14 | Zero-crossing detector: (a) simple implementation, (b) with high-pass filters          |     |

|      | to reduce the effect of the comparator offset                                          | 143 |

| 7.15 | Timing mismatch calibration in the frequency domain                                    | 143 |

| 7.16 | Timing mismatch detection topology based on the output difference of two               |     |

|      | consecutive channels                                                                   | 144 |

| 7.17 | Illustration of the autocorrelation as a function of timing mismatch                   | 146 |

| 7.18 | Timing mismatch detection by using the cross-correlation between the sub-              |     |

|      | ADC and the reference ADC                                                              | 146 |

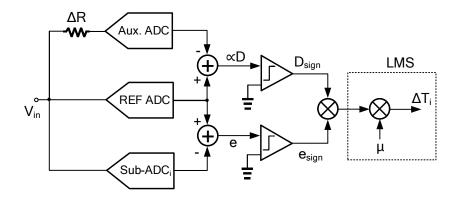

| 7.19 | A derivation-based timing mismatch detection scheme along with the LMS                 |     |

|      | implementation                                                                         | 147 |

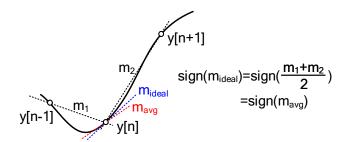

| 7.20 | Sign determination of the input derivative at the sampling moment                      | 148 |

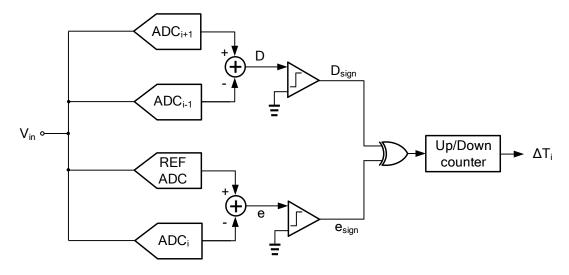

| 7.21 | Modification of Fig. 7.19 with the delayed auxiliary ADC replaced by two               |     |

|      | sub-ADCs and the LSM circuit by a counter                                              | 148 |

i List of figures

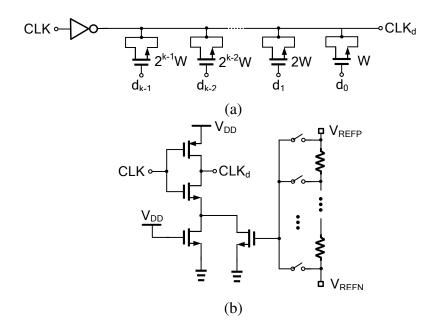

| 7.22 | Circuit implementation of a variable-delay line, using (a) binary-weighted                  |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | MOSCAPs, (b) a resistive DAC                                                                | 149 |

| 7.23 | An ideal discrete-time delay system                                                         | 150 |

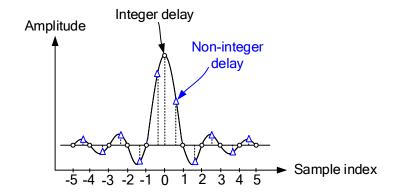

| 7.24 | Impulse response of an ideal delay filter with integer and non-integer delay.               | 151 |

| 7.25 | Block diagram of an M-channel TI ADC along with the extra circuitry for                     |     |

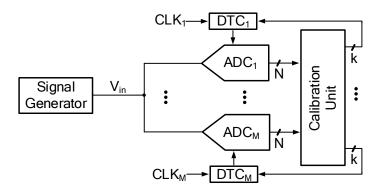

|      | the proposed timing-skew calibration                                                        | 152 |

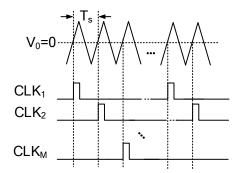

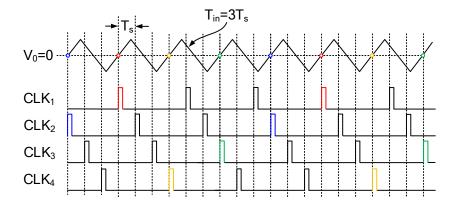

| 7.26 | Triangle signal for the purpose of calibration with period of $T_s$                         | 152 |

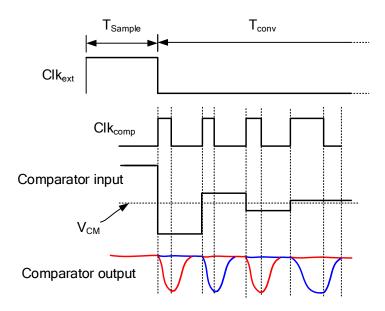

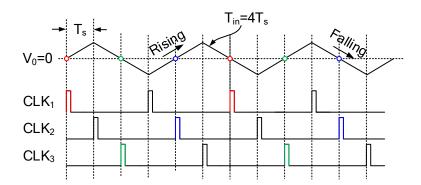

| 7.27 | Timing diagram for a 4-channel TI ADC with a triangle signal of period $3T_s$               |     |

|      | as the input                                                                                | 152 |

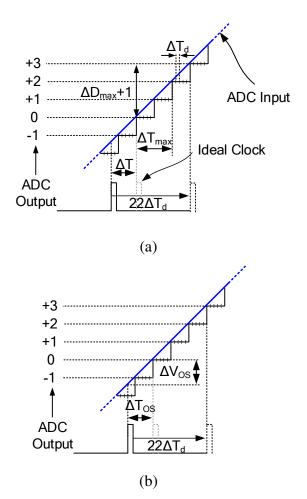

| 7.28 | Timing-skew calibration: (a) without offset, (b) with offset, where $\Delta T$ and          |     |

|      | $\Delta V_{\rm os}$ are the timing and offset error, respectively                           | 154 |

| 7.29 | Timing diagram for a 3-channel TI ADC with a triangle signal of period $4T_s$               |     |

|      | as the input                                                                                | 156 |

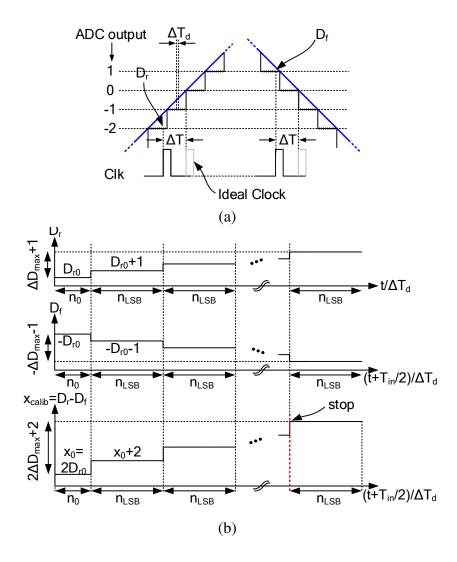

| 7.30 | (a) Position of the clock signal on the triangle waveform for a timing error of             |     |

|      | $\Delta T$ and zero offset error. (b) the sequence of numbers appearing at the ADC          |     |

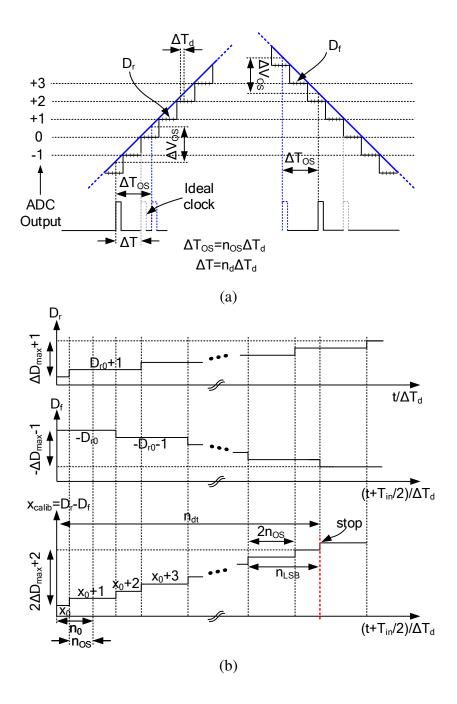

|      | output during the calibration                                                               | 157 |

| 7.31 | (a) Position of the clock signal on the triangle waveform for a timing error of             |     |

|      | $\Delta T$ and an offset error of $\Delta V$ . (b) the sequence of numbers appearing at the |     |

|      | ADC output during the calibration                                                           | 158 |

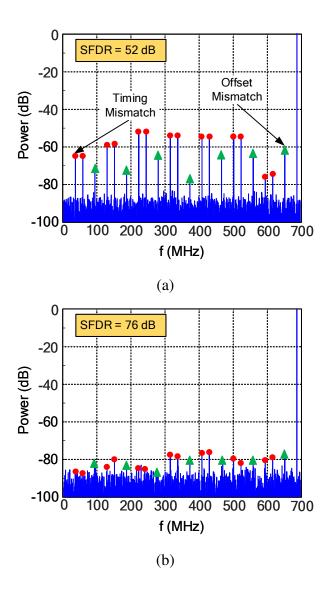

| 7.32 | Output SFDR (a) before calibration (b) after calibration                                    | 163 |

# List of tables

| 3.1 | Various switching schemes and their energy consumption                         |  |  |  |

|-----|--------------------------------------------------------------------------------|--|--|--|

| 6.1 | Performance comparison with ADCs with mismatch calibration 121                 |  |  |  |

| 6.2 | Performance comparison with 10b single-channel high-speed ADCs 122             |  |  |  |

| 6.3 | Minimum unit capacitor for 0.5b ENOB loss due to random mismatch and           |  |  |  |

|     | kT/C sampling noise                                                            |  |  |  |

| 6.4 | Minimum unit capacitor for 0.4b ENOB loss due to kT/C sampling noise only. 123 |  |  |  |

| 6.5 | Estimation of minimum area of the calibration circuit for 0.5b ENOB loss       |  |  |  |

|     | due to mismatch and kT/C noise                                                 |  |  |  |

| 6.6 | Area of the ADC with and without calibration                                   |  |  |  |

## Chapter 1

### Introduction

High-speed (~GSample/s) medium-resolution (~10 bits) analog-to-digital converters (ADCs) are widely used in high-speed communication systems, such as serial links, Ultra-Wide-Band (UWB), and OFDM-based receivers. In designs for digital TV and satellite receivers, the trend is towards software-defined radio, where the embedded A/D converter is moved closer to the antenna. Such ADCs require 8–10 bits of resolution, a large bandwidth to enable subsampling/down-conversion and a power consumption limited to a few hundred milliwatts, in order to be combined with the digital baseband processing in a single IC.

5G (5th generation mobile networks or 5th generation wireless systems) are the next major phase of mobile telecommunications standards beyond the current 4G/IMT-Advanced standards, and another domain where high-performance ADCs are required. 5G networks must be built to meet a number of individual end-user and enterprise needs [1]:

- 1 to 10 Gb/s data rates to support ultra-high definition video and virtual reality application;

- Less than one millisecond latency to support real time mobile control and vehicle-tovehicle applications and communications;

- Rapid switching time between different radio access technologies to ensure a consistently seamless delivery of services;

- Being able to support tens of millions of applications and hundreds of billions of machines;

- Increased battery life of terminal devices (handsets);

- Increased capacity in dense urban environments;

2 Introduction

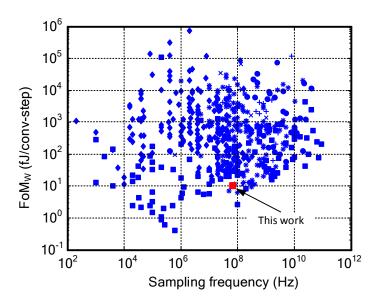

Fig. 1.1 Plot of Walden FoM vs Nyquist sampling frequency for all ADC papers presented at ISSCC and VLSI from 1997-2018.

• Coverage in airplanes and remote areas.

To support the required thousand-fold capacity increase, it will be necessary to simultaneously make efficient use of all of the available continuous and non-continuous electromagnetic spectrum. Furthermore, freeing up additional spectrum will be required. How this new spectrum will be used to achieve 10Gb/s for end users is a major challenge in designing future 5G systems. Specifically for A/D conversion, these 5G requirements call for an ADC with a conversion rate of at least 1GS/s and a resolution of at least 10 bits, together with a low power consumption.

The Successive-Approximation Register (SAR) ADC is a very promising candidate for applications where high-speed medium-resolution is desired. This ADC architecture relies on the high switching speed of certain device technologies, and so is known for its superior energy efficiency, small chip area, and good digital compatibility that can be easily scaled to a new CMOS technology. The attractiveness of the SAR ADC to achieve state-of-the-art performance can be seen in papers presented at important conferences. For instance, Fig. 1.1 illustrates the plot of Walden figure-of-merit (FOM<sub>W</sub>) [2] versus the maximum sampling frequency for all ADCs presented at the International Solid State Circuits Conference (ISSCC) and at the Symposia on VLSI Technology and Circuits (VLSI) from 1997 until 2018 [3]. The filled red square indicates SAR ADCs. As is clear from the graph, the majority of the ADCs that occupy the outer envelope use the SAR architecture.

When properly implemented, a SAR ADC also benefits from a rail-to-rail input swing and 100% capacitance utilization during input sampling (thus low kT/C noise). In principle, SAR

ADCs can be designed with no static power consumption. While the low-power characteristic of SAR ADCs is very attractive, the large number of decision cycles for a single conversion is a fundamental drawback for high-speed operations. Recent advances in process technology and smart circuit techniques have accelerated conversion speeds, but a single-channel SAR ADC is still unable to satisfy the requirements of 5G applications with low power dissipation. Interleaving multiple SAR ADCs in the time domain is a popular technique to increase the sampling rate. The overall performance of time-interleaved ADCs is very much bound to its constituent sub-ADCs. As such, design of a power-optimized sub-ADC is crucial in designing an efficient time-interleaved (TI) A/D converter.

Among all building blocks of a single-channel SAR ADC, the capacitive digital-to-analog converter (CAP-DAC) deserves the most attention. There are two reasons: first, the linearity of the SAR ADC is mainly determined by the linearity of the CAP-DAC; second, the capacitive DAC not only causes a great part of the overall ADC's dynamic power consumption, but also directly determines the size of the driving and sampling switches, the input capacitive load of the ADC and the kT/C noise power.

Although a small DAC unit capacitance is beneficial, it comes at the cost of a larger random mismatch between capacitors. If an accurate mismatch calibration circuit can guarantee to take care of the mismatch, the size of the capacitive DAC can be kept as small as dictated by the kT/C noise limit<sup>1</sup>. This underlines the importance of an effective mismatch calibration circuit for the SAR ADC.

In this thesis, a stochastic-based mismatch calibration technique is presented, which can compute the mismatch of the capacitors of the DAC with high precision. The calibration process occurs in the foreground. The detection of the mismatch error happens in the analog domain, and the correction occurs in the digital domain. The precision of the proposed calibration technique is not limited by the analog circuit and can be easily determined by a parameter, when designing the digital calibration circuit. A prototype SAR ADC using the proposed calibration technique was implemented in 28nm CMOS technology and measured in the lab. The improvement in the linearity of the ADC after the calibration was applied shows the effectiveness of this approach.

Another factor that needs to be carefully addressed in designing a TI ADC is the mismatch between different channels, e.g. gain mismatch, offset mismatch, bandwidth mismatch and sampling-time mismatch. Amongst these, timing mismatch, also known as timing-skew, is the most challenging to detect and correct. Moreover, the requirement on the accuracy of the timing-skew calibration circuit is tough to meet: for a Giga-sample-per-second TI ADC,

<sup>&</sup>lt;sup>1</sup>Another limit on the capacitive DAC is the dynamic range reduction due to the top-plate parasitic capacitors.

4 Introduction

even a few hundreds of fs timing mismatch can easily degrade the output signal-to-noise-and-distortion-ratio (SNDR) of the ADC by a few dBs.

In this thesis, we propose a timing-skew calibration technique that is not only able to calibrate the timing-skew errors of sub-channels of a time-interleaved ADC, but also to simultaneously correct for the offset mismatches. This calibration works in the foreground by detecting the mismatch errors in the digital domain and correcting them in the analog domain. The effectiveness of the proposed calibration method is validated through simulation.

The remainder of this thesis is organized as follows. Chapter 2 reviews the fundamentals of analog-to-digital conversion and the most common architectures of implementing an A/D converter are briefly covered. Chapter 3 discusses the detailed design and implementation considerations for the building blocks of a conventional SAR ADC, along with some of the state-of-the-art design techniques that are used to boost performance. Chapter 4 reviews some of the most important mismatch calibration techniques for SAR ADCs proposed in the literature. Chapter 5 presents details of the proposed mismatch calibration technique and chapter 6 explains the design details of the prototype ADC in which this calibration method is employed along with the measurement results. Chapter 7 also presents the proposed timing-skew calibration technique for TI ADCs with the simulated results. And finally, chapter 8 draws the conclusions and discusses future work.

## Chapter 2

### Fundamentals of A/D Conversion

In this chapter, we cover the fundamentals of analog-to-digital conversion. We begin with an ideal converter before discussing the practical limitations and terminology associated with non-idealities. Next, we briefly cover the most commonly employed A/D architectures, comparing their relative advantages and disadvantages.

#### 2.1 Ideal A/D Converter

An analog-to-digital converter (ADC) is a block that inputs an analog current or voltage signal and outputs (converts) the magnitude of this signal into an N-bit digital format (code), where N denotes the *resolution* of the ADC. The block digram of an ideal A/D converter is shown in Fig. 2.1.(a) and the input/output transfer curve is shown in Fig. 2.1.(b). Here,  $V_{\rm in}$ ,  $V_{\rm REF}$  and  $B_{\rm out}$  are the analog input signal, the reference voltage and the digital output, respectively. The time that is needed by the ADC to complete one conversion is called the *conversion time*. Sampling rate is defined as the frequency at which the ADC performers the conversion, which is the inverse of the conversion time. The quantization step is usually referred to as  $V_{LSB}$  or simply LSB, which is the change in the input voltage that corresponds to a single bit change at the output code. The fundamental equation that describes the ideal A/D converter of Fig. 2.1 is

$$\frac{V_{\text{REF}}}{2^N} \left( b_0 + b_1 2^1 + b_2 2^2 + \dots + b_N 2^{N-1} \right) = V_{\text{in}} + V_X, \tag{2.1}$$

where  $b_0 \sim b_{N-1}$  are the binary bits of the output digital code and  $V_X$  is the residue error due to the finite resolution of the A/D conversion, also known as the *quantization error*. The

Fig. 2.1 Ideal A/D converter: (a) Block digram, (b) input/output transfer curve for a 3-bit ADC.

quantization error of an ideal A/D is within one LSB voltage:

$$-\frac{V_{\rm LSB}}{2} < V_{\rm X} < +\frac{V_{\rm LSB}}{2} \tag{2.2}$$

Denoting the quantization error by  $V_Q$ , the ADC can be modelled as in Fig. 2.2. Assuming that  $V_Q$  has a uniform distribution function between  $-V_{\rm LSB}/2$  and  $+V_{\rm LSB}/2$ , it can be proven [4] that its RMS voltage is equal to

$$V_{\text{Q,RMS}} = \frac{V_{\text{LSB}}}{\sqrt{12}}.\tag{2.3}$$

Fig. 2.2 The ADC model with the quantization error.

For a random input voltage, the quantization error can be viewed as being "random", and is often referred to as "noise". In this case, we can define the signal-to-quantization-noise ratio (SQNR) of an ideal ADC as

$$SQNR = 20 \log \left( \frac{V_{in,RMS}}{V_{Q,RMS}} \right). \tag{2.4}$$

For a sinusoidal input between 0 and  $V_{\text{REF}}$ ,  $V_{\text{in,RMS}} = V_{\text{REF}}/2\sqrt{2}$ .  $V_{\text{Q,RMS}}$  is also given by (2.3). Therefore,

$$SQNR = 20\log \frac{V_{REF}/2\sqrt{2}}{V_{LSB}/\sqrt{12}}$$

(2.5)

$$=20\log\left(\sqrt{\frac{3}{2}}2^N\right) \tag{2.6}$$

$$= 6.02N + 1.76dB \tag{2.7}$$

(2.7) is a very useful equation that relates the SQNR of an ADC and the resolution N.

#### 2.2 Non-Ideal A/D Converter

In practice, there are non-idealities that cause the characteristics of an ADC to deviate from the ideal form. In the following, we review some of the most important limitations of an A/D converter.

#### 2.2.1 Offset Error

The *offset error* for an A/D converter is defined as the deviation of the first transition (bit change) that we denote by  $V_{00...01}$  from the ideal position (which is  $\frac{1}{2}$ LSB), that is

$$V_{\text{offset}} = \frac{V_{00...01}}{V_{\text{LSB}}} - \frac{1}{2} \text{LSB}.$$

(2.8)

This is illustrated in Fig. 2.3.(a).

#### 2.2.2 Gain Error

The *gain error* is defined as the difference at the full-scale value between the ideal and actual response curves, when the offset error has been removed. For an A/D converter, this is given by

$$V_{\text{gain}} = \left(\frac{V_{11...11}}{V_{\text{LSB}}} - \frac{V_{00...01}}{V_{\text{LSB}}}\right) - (2^N - 2),\tag{2.9}$$

which is shown in Fig. 2.3.(b). Offset and gain errors can be easily compensated by digital pre/post-processing. What is more crucial for the DC performance of an A/D converter is the linearity measures, and most importantly the INl and DNL.

Fig. 2.3 Illustration of (a) offset error, (b) gain error. Offset error is the deviation of transfer curve from the first transition and gain error is the difference between the ideal (best-fit) and actual response curves.

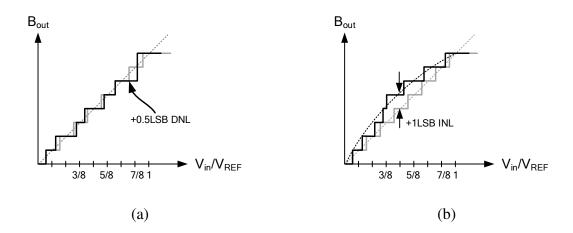

#### 2.2.3 Differential Nonlinearity Error (DNL)

For an ideal converter, each analog step size is equal to 1 LSB. *Differential nonlinearity* (DNL) is defined as the deviation of every code width from 1 LSB (typically, after gain and offset errors have been removed), or mathematically,

$$DNL[k] = W[k] - LSB, (2.10)$$

where W[k] is the width of the k-th code. This makes DNL a vector of size  $2^N$  that characterises the corresponding error associated with all possible output codes. If only one DNL was reported, that would be the maximum DNL value. It can be readily seen that the sum of all the DNLs is equal to zero:

$$\sum_{k=0}^{2^{N}-1} \text{DNL}[k] = 0.$$

(2.11)

An example of an ADC characteristic with non-zero DNL is shown in Fig. 2.4.(a). It is easy to understand that for an ADC, DNL must be larger than -1. In the case where DNL = -1, the code associated with that DNL will be *missing* from the A/D transfer curve and hence will not appear at the output of the ADC.

#### 2.2.4 Integral Nonlinearity Error (INL)

*Integral nonlinearity* (INL) is defined as the deviation of the code transition from its ideal location, when both the offset and gain errors have been removed, that is

$$INL[k] = \frac{T[k] - T[k,ideal]}{LSB},$$

(2.12)

where T[k] and T[k], ideal] denote the actual and ideal transition points, respectively. A straight line through the endpoints of the A/D transfer curve is usually considered as the reference for determining INL. An alternative reference would be the best-fit line that would represent the characteristic curve. It can be readily shown that

$$INL[k] = \sum_{i=0}^{k-1} DNL[i]$$

(2.13)

or equivalently

$$DNL[k] = INL[k] - INL[k-1]. \tag{2.14}$$

As for DNL, if only one INL was reported, that would be the maximum individual INL value. An example of an ADC characteristic with non-zero INL is shown in Fig. 2.4.(b).

Fig. 2.4 Illustration of (a) DNL error and (b) INL error. DNL is the deviation of every code width from 1 LSB and INL is the deviation of the code transition from its ideal location.

An A/D converter is called *monotonic* if the output always increases as the input increases. A converter is guaranteed to be monotonic if  $INL_{max} < 0.5LSB$  (or equivalently when  $DNL_{max} < 1LSB$ ). The DNL is *not* defined for the non-monotonic steps.

There are different techniques for measuring the DNL/INL of an ADC. One way, known as *code boundary servo*, is to use an adjustable voltage source to find the exact code trip points. Another very common technique is to apply a signal with known amplitude distribution to the input of the ADC and analyse the digital distribution at the output and is known as the *histogram testing*. Typically a sine wave is used as the input signal for the histogram-based method [5]. Although histogram testing is the most commonly used technique, there are some limitations [6] that should be taken into consideration when following this approach.

#### 2.2.5 Dynamic Range

The *dynamic range* of a converter is defined as the ratio between the maximum and minimum signal magnitudes that can be meaningfully processed. The minimum magnitude is usually determined by the noise level; however, it is still necessary to specify a merit to define the meaningful output. A popular merit is to use the signal-to-noise-and-distortion ratio (SNDR) and to define the maximum magnitude at which the SNDR drops by 3dB for a specific frequency. Similarly, *the effective resolution bandwidth* of an ADC is specified as the bandwidth over which the peak SNDR is within 3dB of its best value for a specific input magnitude. In this context, the *effective number of bits* (ENOB) is computed as

$$ENOB = \frac{SNDR - 1.76dB}{6.02} \text{ bits}, \qquad (2.15)$$

which is derived from (2.7) by substituting SNDR for SQNR; ENOB is merely a performance metric relating an actual ADC's performance to that of an ideal ADC.

#### 2.3 ADC Architectures

There exists a number of different architectures for realising an A/D converter. Every architecture comes with its own advantages and disadvantages in terms of the maximum achievable speed, resolution and linearity, power consumption, area, complexity and compatibility with technology scaling.

#### 2.3.1 Serial ADC

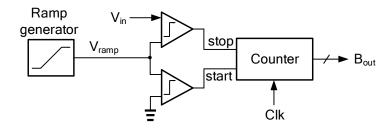

This type of ADC consists of a counter that serially counts the number of clock cycles until the input voltage becomes equal to a linearly increasing reference (usually a ramp). There are two ways of realizing a serial ADC, namely *single slope* and *double slope*.

2.3 ADC Architectures

#### Single-Slope

The single-slope topology is shown in Fig. 2.5. Once the ramp generator starts producing the ramp signal  $V_{\text{ramp}}$ , the counter starts counting, and the counter stops once  $V_{\text{in}} = V_{\text{ramp}}$ . Assuming a linear ramp signal, the output of the counter (which is the output of the ADC) is proportional to the input voltage. As can be seen in Fig. 2.5, this type of ADC has a very low complexity and is easy to implement. The linearity of the ADC is mainly determined by the linearity of the ramp signal, and not by component matching. The serial ADC is also inherently monotonic. The downside is the very low conversion speed for they require a digital counter at a highly oversampled clock rate. The generation of a linear ramp can also become challenging for when a high resolution is required. These issues can be alleviated by the dual-slope ADC.

Fig. 2.5 Block diagram of a single-slope serial ADC. The counter stops counting once  $V_{\text{ramp}}$  becomes equal to  $V_{\text{in}}$ . This way, the binary output of the counter would be proportional to the input voltage.

#### **Dual-Slope**

The dual-slope block diagram is shown in Fig. 2.6.(a). The conversion occurs in two phases. During phase (I),  $V_{\rm in}$  is integrated over a fixed period of time, which is  $2^N T_{\rm clk}$  where N is the resolution of the ADC and  $T_{\rm clk}$  is the clock period. This would generate a ramp at the output of the integrator,  $V_X$ , whose slope, and hence final value, is proportional to  $V_{\rm in}$ . In phase (II), the input of the integrator is connected to a constant reference voltage  $V_{\rm REF}$  and  $V_X$  is de-integrated until it reaches zero during which the counter is counting. Due to the constant slope during the second phase, the output of the counter would be proportional to  $V_{\rm in}/V_{\rm REF}$ . The operation of the dual-slope ADC is illustrated in Fig. 2.6.(b).

It can be shown that the accuracy of the dual-slope A/D converter does not depend on the time constant of the integrator. However, the offset of the op-amp used in the integrator results in the ADC offset, a problem that can be solved either by calibration or by utilizing a *quad-slope* ADC. As for the signal-slope ADC, the conversion speed is still very low. The

application of this type of ADC is mostly for laboratory digital voltmeters (DVM) where high speed is not required.

Fig. 2.6 Dual-slope ADC (a) block diagram, (b) timing diagram for three different input voltages. The accuracy of this A/D converter does not depend on the time constant of the integrator.

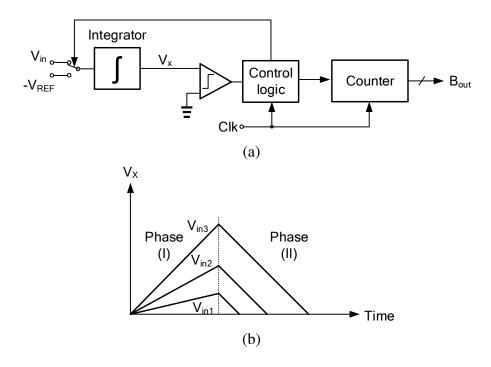

#### **Asynchronous Digital-Slope**

The speed limitation of the synchronous slope-based converter was solved in [7], where an asynchronous digital-slope architecture was introduced. The block diagram of this type of ADC is shown in Fig. 2.7.(a), and its time-domain behaviour is illustrated in Fig. 2.7.(b). As can be seen, the integrator in the dual-slope ADC is replaced by an asynchronous switched capacitor (SC) circuit. The quantization occurs in the time-domain using delay cells, memory cells and an encoder instead of a digital counter. The operation of the ADC is as follows. First, the input voltage is sampled on node *S*. Next, a pulse is applied to the input of the delay cell array and, in a domino manner, it propagates through delay cells one by one. In this way, the delay line acts like an asynchronous thermometer-encoded<sup>1</sup> counter which replaces the original synchronous binary-encoded counter. The array of capacitors, connected to the outputs of the delay line, implements a thermometer-encoded charge-redistribution DAC,

<sup>&</sup>lt;sup>1</sup>Thermometer encoding is a method of encoding a natural number, n, with n ones followed by a zero.

through which  $V_X$  is switched up 1 LSB step by step at a constant interval until it reaches  $V_S$ , at which point the comparator toggles and deactivates the delay line. The output thermometer code is then converted to a binary code via the encoder. Since the hardware complexity of the digital-slope ADC grows exponentially with the ADC resolution, this type of ADC does not lend itself to resolutions higher than 8 bits.

Fig. 2.7 Asynchronous digital-slope ADC: (a) block diagram, (b) timing diagram. Contrary to a synchronous serial ADC, here no high speed clock is required. The counter is also replaced by delay elements.

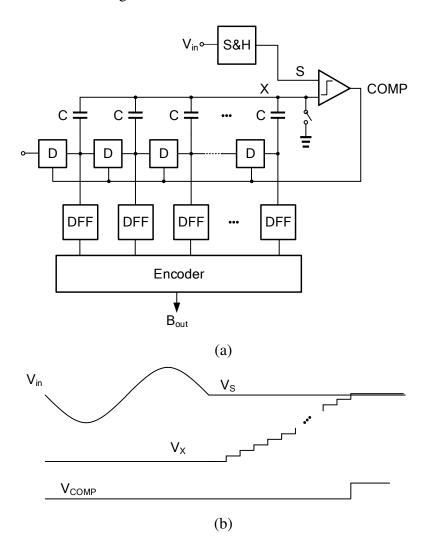

### 2.3.2 Flash ADC

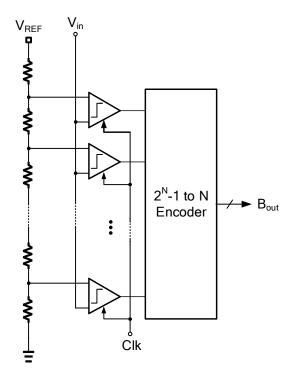

Flash ADC is probably the most straightforward way of realizing an A/D converter. In a flash converter, the input voltage is simply compared with  $2^N - 1$  voltages that are equally spaced

between zero and the reference voltage. The reference levels are generated by a reference generator and the comparisons are made by  $2^N$  comparators, as depicted in Fig. 2.8 for the specific case of N=3. Here, generating the reference voltages is realized by a resistor string, but it can be also implemented by capacitors [8]. The output of the comparators form a thermometer code, which is then converted to a binary code via a  $2^N$ -to-1 decoder.

Flash ADCs are inherently very fast [9–11] for they require only one clock cycle for every conversion. However, the complexity of the circuit increases exponentially with the number of bits, that is  $2^N - 1$  comparators are needed for an N-bit conversion. This exponential growth also holds for the input capacitive load of the converter, which must be driven by the input driver. In the following, we discuss the most important sources of error in a flash ADC:

Fig. 2.8 Block diagram of a Flash ADC. Owning to their simple structure, flash ADCs are inherently fast.

### **Comparator Offset**

The comparator offset is probably the most important source of error that can degrade the performance of a flash ADC. There exist several different design and calibration techniques to alleviate the problem of comparator offset. One of the simplest (yet powerful) offset calibration techniques is *resistor averaging* [12–14], which acts as a kind of spatial filtering [15], by simply connecting the output of the pre-amplifiers using resistors. The effectiveness

2.3 ADC Architectures 15

of this technique depends on the ratio  $R_2/R_1$ , which imposes a trade-off with the gain of the amplifiers. Another commonly used technique for offset cancellation is *offset storage*. In this approach, the offset voltage is measured and stored on a capacitor, and can be done in two different ways: *input offset storage* (IOS), shown in Fig. 2.9.(a) and *output offset storage* (OOS), shown in 2.9.(b). It can be shown that this method reduces the offset by a factor given by the pre-amplifier gain, A.

Fig. 2.9 Offset cancellation through offset storage: (a) input offset storage, (b) output offset storage. Offset is reduced by a factor *A*.

### **Bubble Error**

For the encoder to function properly, the outputs of the comparators should form a thermometer code with only one single transition. However, sometimes a lone 1 (the *bubble*) will occur within the string of 0s for various reasons. These bubbles usually occur near the transition point of the thermometer code. A very simple solution is to put a three-input NAND gate at the output of the comparators [16].

### **Comparator Metastability**

Metastability is a problem that occurs in all latching comparators, when the input is near the comparator decision point [17]. This problem occurs when the comparator takes more time to switch to a valid output state than is available in the sampling interval. Different gates interpret the metastable output differently, resulting in an invalid encoder output. Using more stages of latch in the comparator and *Grey coding* are two of a range of methods that can be used to decrease the adverse effect of metastability in flash ADCs.

## 2.3.3 Interpolating ADC

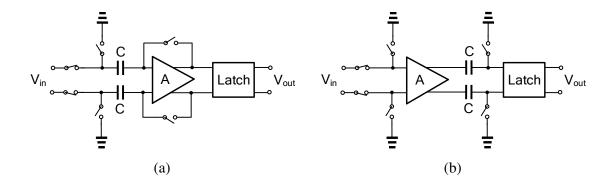

Interpolation can be used to reduce the number of latches by interpolating between the outputs of the pre-amplifiers [18]. An interpolation of factor M decreases the number of pre-amplifiers by a factor of M. Interpolation by factor 2 in a flash ADC is fairly straightforward; shown in Fig. 2.10.(a), this only requires rearrangement of the connections between the latches and the differential pre-amplifiers. To accomplish higher interpolation factors, extra circuitry is required. This can be achieved using resistors [19], capacitors [20] and current mirrors/current division [21, 22]. Fig. 2.10.(b) illustrates schematically the resistor-based method for a factor 4 interpolation. It is worth mentioning that capacitive interpolation has a side benefit of automatically performing comparator offset cancellation through the offset storage discussed in section 2.3.2.

Fig. 2.10 Realization of (a) factor 2, (b) factor 4 interpolation. Interpolation of factor M reduces the number of pre-amplifiers by the same factor.

For an interpolation topology to work without error it is necessary that the transfer curves of consecutive pre-amplifiers overlap; however, this limits the pre-amplifier gain. Moreover, the impedance of the interpolation network at the output of the pre-amplifiers typically

2.3 ADC Architectures 17

reduces the bandwidth and affects the maximum achievable speed. One of the important side-effect of interpolation is the reduction of DNL by the same factor as for the interpolation.

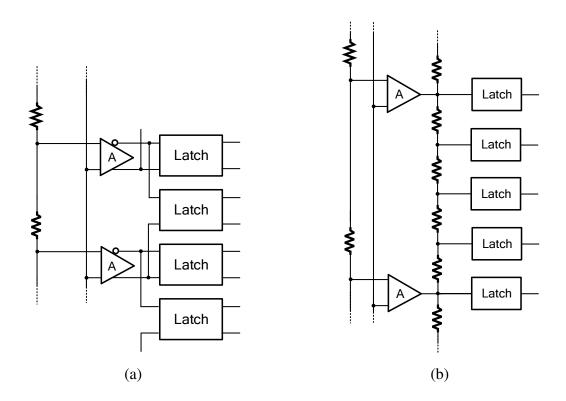

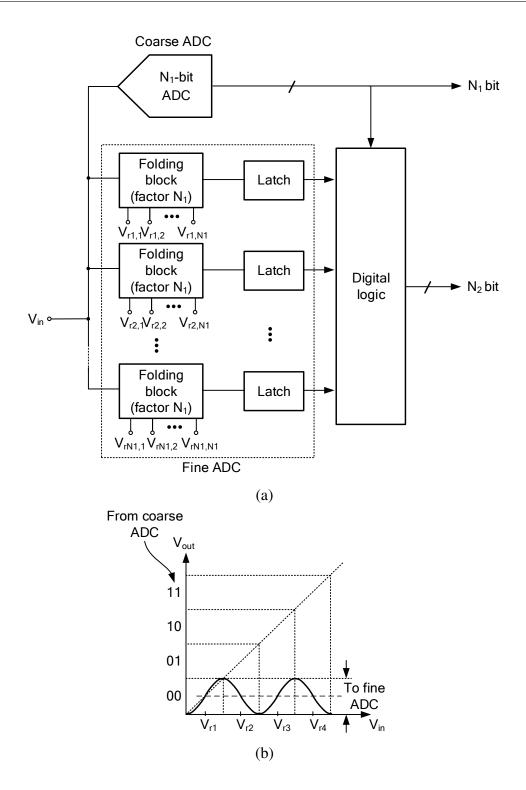

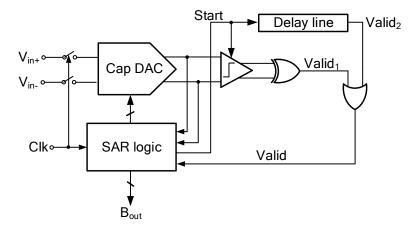

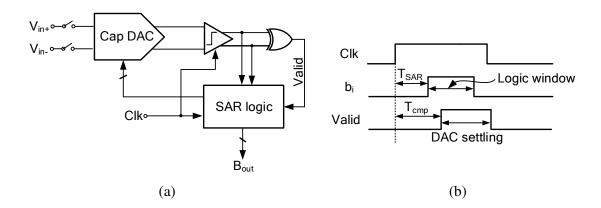

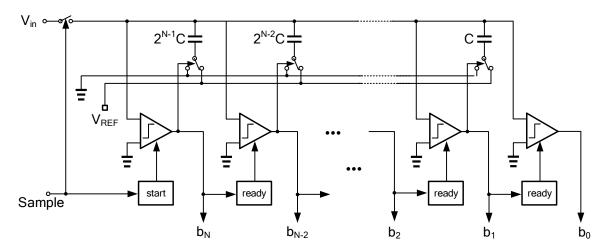

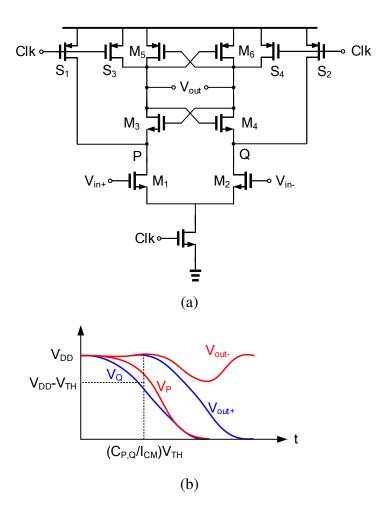

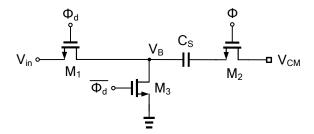

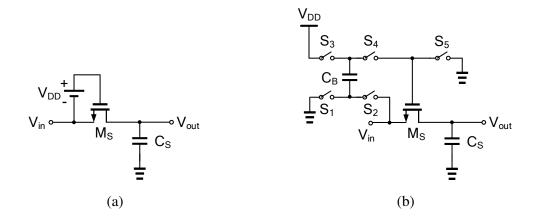

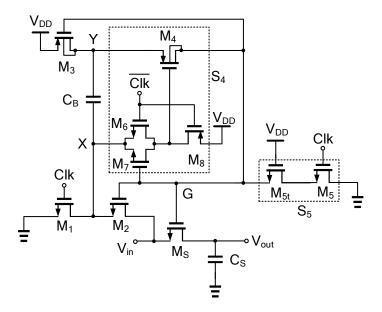

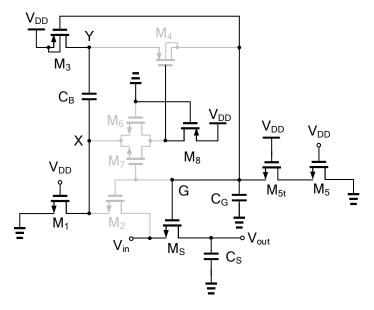

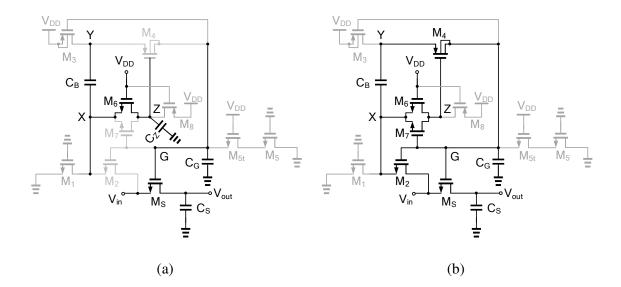

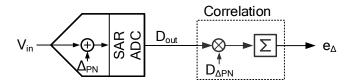

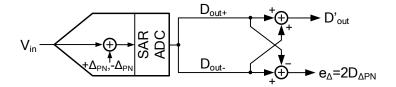

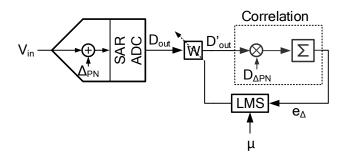

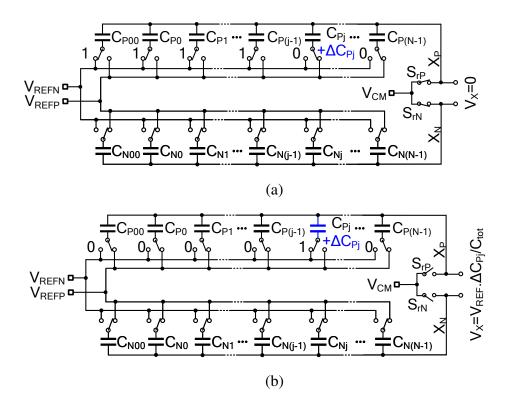

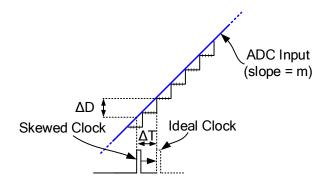

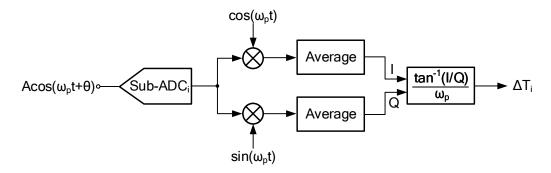

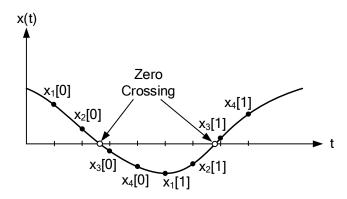

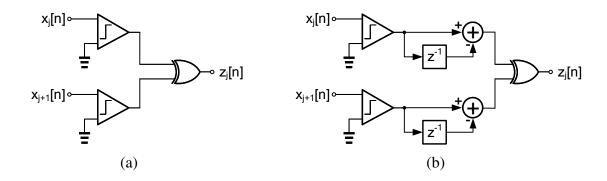

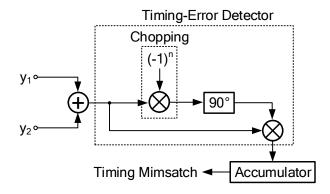

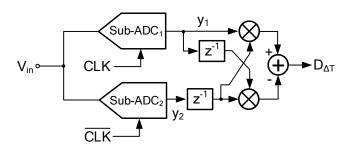

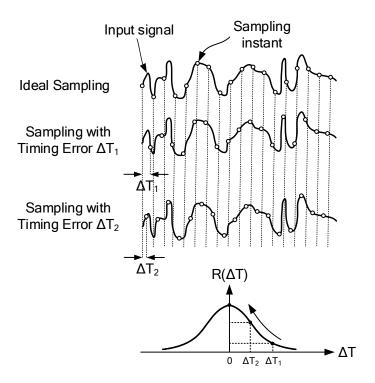

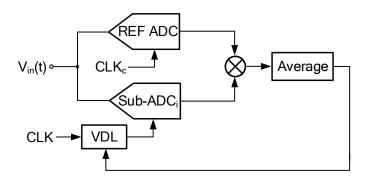

Interpolation reduces the number of pre-amplifiers, thereby reduces the input capacitive load of the ADC. Nevertheless, the number of latches stays the same. To decrease the number of latches, a technique called *folding* is usually adopted in combination with interpolating.