#### UNIVERSIDAD PÚBLICA DE NAVARRA

ESCUELA TÉCNICA SUPERIOR DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACION

## TRABAJO FIN DE MASTER

Diseño de circuitos integrados analógicos usando la terminal de body en transistores MOS

Departamento de Ingeniería Eléctrica y Electrónica

Alumno: Gonzalo Thomas Erviti

Director: Carlos Aristóteles de La Cruz Blas

Master en Comunicaciones

# **ÍNDICE**

| 1. | OBJ          | JETIVO                                                           | . 4 |

|----|--------------|------------------------------------------------------------------|-----|

| 2. | INT          | RODUCCIÓN                                                        | . 5 |

| 3. | . TRA        | ANSISTOR MOS                                                     | . 7 |

| 4. | EST          | TADO DEL ARTE                                                    | 12  |

|    | 4.1          | CIRCUITOS DE POLARIZACIÓN                                        | 13  |

|    | 4.2          | MÍNIMA ALIMENTACIÓN EN UNA ETAPA DIFERENCIAL                     | 15  |

|    | 4.3          | BODY DRIVEN GAIN BOOSTING                                        | 17  |

|    | 4.4<br>CLASE | CONTROL DE LA CORRIENTE EN REPOSO DE UNA ETAPA DE SALIDA DE E AB | 19  |

|    | 4.5          | MEJORA DE LA LINEALIDAD EN UN TRANSCONDUCTOR                     | 20  |

| 5. | . TRA        | ANSCONDUCTORES (usando técnicas bulk-driven)                     | 23  |

|    | 5.1          | MODELO ALTERNATIVO DE UN TRANSISTOR MOS (ALL REGION MODEL)       | 23  |

|    | 5.2          | ANALISIS DE DISTORSIÓN                                           | 25  |

|    | 5.2.         | 1 DISTORSIÓN EN TRANSCONDUCTORES                                 | 27  |

|    | 5.3          | ANALISIS DE LOS TRANSCONDUCTORES                                 | 29  |

|    | 5.3.         | 1 PAR DIFERENCIAL                                                | 30  |

|    | 5.3.2        | 2 PAR DIFERNECIAL CON DEGENERACIÓN REISTIVA                      | 33  |

|    | 5.3.3        | 3 PAR DIFERNECIAL CON DEGENERACIÓN REISTIVA Y USO DE BULK        | 35  |

|    | 5.3.4        | 4 CASCODE OTA                                                    | 38  |

|    | 5.3.5        | 5 CASCODE OTA CON DEGENERACION DE FUENTE Y USO DE BULK           | 43  |

|    | 5.4          | MULTIPLICADOR                                                    | 47  |

| 6. | CO           | NCLUSIONES                                                       | 52  |

| 7. | . LÍN        | EAS FUTURAS                                                      | 53  |

| 8  | REI          | FERENCIAS                                                        | 54  |

| 9. | ANI          | EXO 1 CÓDIGO MATLAB                                              | 58  |

### 1. OBJETIVO

El objetivo del presente TFM es el diseño analógico de circuitos integrados CMOS usando la terminal de body en los transistores MOS. Así, se realizará una revisión de las técnicas modernas de diseño, caracterización y análisis, así como la posterior aplicación a diversos sistemas usando estos dispositivos como elemento. Se propondrán nuevas celdas usando esta técnica, las cuales son validadas por resultados de simulación, análisis teóricos y resultados experimentales.

### 2. INTRODUCCIÓN

En la actualidad el diseño analógico de circuitos integrados CMOS está inmerso en una reducción progresiva de sus dispositivos para poder fabricar sistemas más completos en la menor área posible. Esta tendencia trae como consecuencia que los campos eléctricos en el interior de los dispositivos aumente considerablemente, por lo que para que sigan funcionando correctamente la fuente de alimentación debe ser reducida. En este escenario las técnicas de diseño tradicional tienen que ser revisitadas o adaptadas para desarrollar circuitos y sistemas fiables de alto rendimiento. Varias soluciones han sido propuestas en la literatura y la industria para hacer frente a este reto, tales como, floating-gates, quasifloating gates, bulk-driven, entre otras [1-3]. En este TFM centraremos la atención a la técnica basada en usar el body de los transistores MOS (bulk-driven) como una terminal activa por ser uno de las metodologías más prometedoras en el diseño de circuitos integrados.

En el diseño analógico de circuitos integrados CMOS el terminal de body de un transistor MOS ha sido conectado tradicionalmente al terminal de fuente, debido a que de esta manera se evitan cambios en el voltaje de umbral del transistor. El terminal de bulk en los transistores MOS había sido considerado como una fuente de efectos de segundo orden indeseados, sin embargo los diseñadores digitales han conseguido explotar satisfactoriamente este terminal, además de representar una gran oportunidad para el desarrollo de circuitos analógicos con fuentes de alimentación reducidas. En estas técnicas, el bulk es el terminal activo y la puerta es usada como un elemento complementario, dando lugar a una gran variedad y flexibilidad en varios campos del diseño analógico. Se han diseñado y probado múltiples prototipos usando transistores bulk-driven, que demuestran que estás técnicas son prometedoras para la mejora del diseño de circuitos integrados analógicos en escalas nanométricas.

La presente memoria del trabajo de fin de master consta de varias secciones. La primera de ellas es la sección Transistor MOS, en esta sección se abordarán las características más importantes de este dispositivo y se explicará su principal funcionamiento, para dotar al lector de los conceptos básicos que más tarde serán puestos en práctica. Se abordarán temas como las diferentes regiones de funcionamiento de un transistor, ecuaciones en gran señal, su modelado en pequeña señal, así como definiciones de los parámetros más relevantes de este dispositivo.

Posteriormente se realiza una revisión exhaustiva del estado del arte centrada en la técnica que se basa en el uso del terminal de body de forma activa. Los conceptos adquiridos en esta sección serán de gran importancia para la consecución del posterior trabajo. Se mostrarán diferentes circuitos cada uno de ellos con diferente aplicación, y se analizarán para comprender el funcionamiento de cada uno de estos dispositivos.

Una vez revisado el estado del arte se pasará a la sección de análisis de transconductores, la cual consta de varias partes. En la primera de ellas se analizará un modelo que describe la operación de un transistor MOS, diferente al usado comúnmente, ya que este aportará ventajas en el estudio posterior de varios dispositivos, debido a la simetría con la que este modelo trata al transistor MOS. En la siguiente sección, cuyo objetivo es análisis y caracterización de un transconductor propuesto, se realizará el análisis de varios transconductores hasta llegar al análisis del transconductor propuesto. Este análisis de distorsión se realizará de una manera innovadora, y que nunca ha sido realizada con anterioridad. Los resultados obtenidos son igual de fidedignos pero el cálculo matemático se ve reducido, lo cual favorece el análisis y caracterización para las topologías más complejas. La caracterización teórica de los dispositivos se comparará con los resultados obtenidos mediante simulación, y con los resultados medidos experimentalmente.

Acabado el análisis y caracterización de estos dispositivos se pasará al análisis de un multiplicador/divisor que de igual manera utilizará el terminal de bulk de forma activa.

La memoria termina con las secciones de Conclusiones y Líneas Futuras generales del TFM donde se abordarán los aspectos más importantes tratados a lo largo de la memoria.

### 3. TRANSISTOR MOS

En esta sección se va a explicar el funcionamiento básico de un transistor MOS. Se describirán las diferentes regiones de operación de este, saturación y triodo. Las ecuaciones en gran señal serán expuestas, así como el análisis en pequeña señal y sus parámetros más importantes. Todos los conceptos abordados en esta sección serán de gran importancia para el desarrollo de la memoria.

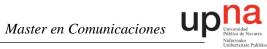

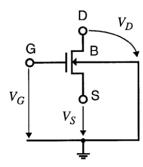

La tecnología más usada a la hora de diseñar y fabricar circuitos integrados es CMOS, esta tecnología hace uso de transistores MOS (metal-oxide semiconductor), se utilizan dos tipos de transistores complementarios, tipo "n" y tipo "p", los tipo "n" conducen corriente mediante electrones mientras que los tipo p conducen corriente usando huecos. En la figura 3.1 se muestra una sección transversal de un transistor MOS tipo "n". Como puede observarse consta de cuatro puertos, drenaje (*Drain*), puerta (*Gate*), fuente (*Source*) y bulk o body. Se empelan diferentes materiales aparte de semiconductores, como son el Aluminio para establecer contacto con el material semiconductor de la fuente y drenaje, dióxido de Silicio como material aislante, y polisilicio altamente dopada, en la puerta, lo que permite que la fabricación del transistor sea más exacta que si se usase metal en la puerta.

Figura 3.1. Sección transversal de un transistor MOS tipo n.

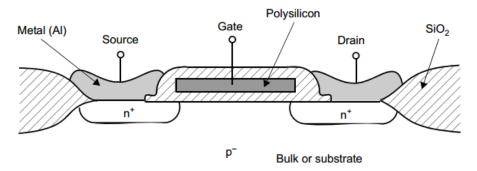

En la figura 3.2 se muestran los símbolos más utilizados para los transistores utilizados en la tecnología CMOS.

Figura 3.2. Símbolos de un transistores MOS, a) y c) corresponden a un transistor MOS tipo n, y b) y d) a un transistor MOS tipo p.

Para los casos *a*) y *b*), los transistores MOS es representado mediante únicamente tres terminales, puerta, drenaje y fuente, ya que se asume que el terminal de bulk está conectado a la fuente, por lo que puede obviarse. En los casos *c*) y *d*) su representación se realizada mediante cuatro terminales, esta vez incluyendo el terminal de bulk. Cabe resaltar dos aspectos importantes de

estas representaciones, el primero de esos es que la puerta se representa con una separación respecto a los demás terminales, lo que significa que están "aislados" prácticamente, lo que se traduce en que no circula corriente a través del terminal de puerta, por lo que su impedancia es muy alta. El segundo aspecto es la dirección de la corriente que atraviesa el transistor, que viene representada mediante una flecha, que en los casos a) y b) está situada en el terminal de fuente, mientras que en los casos c) y d) aparece en el terminal de bulk.

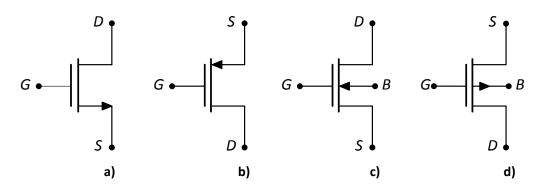

A continuación se procede a explicar el funcionamiento de estos dispositivos, en concreto para un transistor tipo "n", cabe notar que el funcionamiento para un transistor tipo "p" es similar, pero con el cambio apropiado en el signo de los voltajes aplicados. En la figura 3.3 se muestra una sección transversal de un transistor tipo "n", al cual se le aplica un voltaje positivo en la puerta, mientras que todos los demás terminales están conectados a tierra, esto provoca que las cargas positivas debidas a la tensión positiva en la puerta atraigan cargas negativas del drenaje y la fuente, lo cual da lugar a lo que se llama el canal, formado en este caso por electrones. Si se sigue aumentando el voltaje aplicado en la puerta, llega un punto en el que se igualan los electrones en el canal formado justo debajo de la compuerta a los huecos existentes en el substrato p, a este voltaje se le llama Voltaje Umbral ( $V_T$ ).

Como aproximación se postula que no fluye la corriente entre el drenaje y la fuente cuando en la puerta se aplica un voltaje menor que el voltaje de umbral, aunque realmente existe una corriente de fuga.

Posteriormente se aplica un voltaje positivo al drenaje, lo que hace que la densidad de carga no sea constante a lo largo del canal, sino que esta disminuye conforme se acerca al terminal de drenaje. En este caso la corriente que atraviesa el canal depende claramente de la diferencia de voltaje entre el drenaje y la fuente,  $V_{DS}$ . Si se sigue aumentando el voltaje aplicado al terminal de drenaje hasta que  $V_{DS}=V_{GS}-V_T$  el canal esta "pinched-off", y se elimina la dependencia de la diferencia del voltaje entre drenaje y fuente, y ahora la corriente depende principalmente en la diferencia del voltaje entre la puerta y la fuente.

Figura 3.3. Sección transversal con  $V_{DS} > V_{GS} - V_T$ .

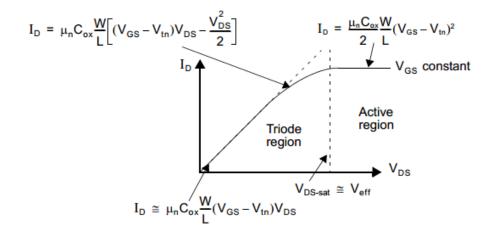

Con esto se pueden diferenciar dos modos de operación de un transistor MOS, la región triodo y la región de saturación (o Active Region), en la gráfica 3.4 se muestra la dependencia de la corriente frente al voltaje  $V_{DS}$  en los regiones de operación, como puede observarse en la región de saturación no existe dependencia de  $V_{DS}$ , en una primera aproximación.

Figura 3.4. Corriente frente a voltaje VDS, y las dos regiones de operación de un transistor.

Las ecuaciones que definen la corriente para estas dos regiones son:

Triodo:

$$I_{D} = \mu_{n} C_{ox} \left( \frac{W}{L} \right) \left[ (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

(3.1)

Saturación:

$$I_D = \frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right) (V_{GS} - V_T)^2 \tag{3.2}$$

Siendo  $\mu_n$  la movilidad de los electrones y  $C_{ox}$  la capacitancia de la puerta

Para ambas regiones de operación el voltaje de umbral se define como:

$$V_T = V_{T0} + \gamma \left( \sqrt{2\varphi_F - v_{BS}} - \sqrt{2\varphi_F} \right) \tag{3.3}$$

Donde  $V_{TO}$  es el "zero-bias threshold",  $\varphi_F$  es el potencial de Fermi y  $\gamma$  el parámetro correspondiente al "body effect", todos ellos son dependientes de la tecnología.

Destacar que el voltaje entre el drenaje y la fuente,  $V_{DS}$  en la región de triodo es  $V_{DS} < V_{GS}$ - $V_T$  y para la región de saturación  $V_{DS} \ge V_{GS}$ - $V_T$ .

Estas ecuaciones corresponden a la llamada "Ley Cuadrática" que es el modelo más extendido para describir la operación de un transistor MOS. Al uso de estas ecuaciones para el cálculo de las corrientes que atraviesan un transistor se le conoce como análisis en gran señal, y son capaces de describir con gran precisión la operación de un transistor. Sin embargo para el cálculo de parámetros tales como la ganancia, impedancia de salida etc. se define el análisis en pequeña señal. El análisis en pequeña señal es usado para describir el comportamiento de un dispositivo no lineal mediante ecuaciones lineales, se realiza linealizando alrededor del punto de polarización en DC del transistor. Esta aproximación es válida para un determinado rango de valores cercanos a ese punto por lo que los circuitos con transistores se pueden representar por sistemas lineales. Es de gran importancia la definición de las transconductancias "g", en este análisis, la cual se define como la variación de la corriente que atraviesa el transistor, respecto a los voltajes involucrados en la definición de esta corriente. En el caso de un transistor operando en la región de saturación, únicamente existirían dos transconductacias, la de la puerta  $g_m$ , y la del bulk  $g_b$ , y se definen como:

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \tag{3.4}$$

$$gm_b = \frac{\partial I_D}{\partial V_{SR}} \tag{3.5}$$

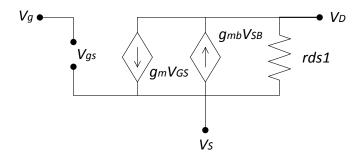

Una vez definida la tranconductancia, se muestra en la figura 3.5 el circuito equivalente en pequeña señal de un transistor MOS operando en saturación.

Figura 3.5. Modelo equivalente de un transistor en saturación en pequeña señal.

Los parámetros más importantes son las fuentes de corriente controladas por voltaje. Destacar que la transconductancia  $g_{mb}$ , se tiene en cuenta únicamente cuando el terminal de body y la fuente no están conectados, lo que implica una diferencia de potencial entre estos dos terminales. Cuando  $Vs=V_B$ , su diferencia de potencial es cero que al ser multiplicado por  $g_{mb}$ , da un aporte nulo de corriente.

En gran señal al conectar el terminal de body con la fuente, la diferencia de potencial entre estos es cero, por lo que  $V_T = V_{TO}$ , sin embargo al existir una diferencia de potencial entre estos dos terminales significa que  $V_T \neq V_{TO}$ . Tiene limitaciones ya que nunca puede ser mayor la diferencia de potencial entre los dos terminales que dos veces el potencial de Fermi. En la ecuación 3.3 se aprecia como si el voltaje  $V_{SB}$  es mayor que dos veces el potencial de Fermi, quedaría como resultado la raíz de un número negativo, lo que significa que el diodo formado por la unión n-p de la fuente y el body es polarizado en inversa hasta llegar al punto de ruptura, lo que rompería el transistor. De igual manera si el voltaje  $V_{SB}$  es negativo, y se supera la tensión umbral correspondiente al diodo formado por la fuente y el terminal de body se polarizaría en directa lo que daría lugar a una gran cantidad de corriente circulando entre esta unión lo que daría lugar a la ruptura del dispositivo igualmente.

Una de las técnicas más usada, en el bulk-driven, consiste en aplicar un voltaje en de a la puerta para activar el transistor y utilizar el terminal de bulk para introducir la señal. Como se comentó anteriormente al utilizar el terminal de bulk de forma activa, se crea una diferencia de potencial entre este terminal y la fuente, lo que supone que en el análisis en pequeña señal, exista otra fuente de corriente controlada por voltaje, siendo este voltaje la diferencia de tensión entre el terminal de body y la fuente,  $V_{SB}$ . La transconductancia correspondiente tiene un valor aproximado de hasta un orden de magnitud menor que la transconductancia de la puerta. En teoría la transconduncitancia del transistor bulk dirven,  $g_{mb}$ , puede llegar a ser mayor que la transconductancia de la puerta:

$$g_{mb} = \frac{\partial I_D}{\partial V_{SB}} = \frac{\gamma g_m}{2\sqrt{2\varphi_F - V_{BS}}}$$

(3.6)

La transconductancia de un transistor bulk-driven, puede exceder  $g_m$  si:

$$V_{BS} \ge 2\varphi_F - 0.25\gamma^2 \approx 0.5 V$$

De darse esta situación se asume que existirá una corriente significativa entre la unión p-n del sustrato y la fuente, por lo que debe tenerse cuidado para no quemar el dispositivo controlando el rango de voltaje de entrada que tendrá que ser muy reducido.

Otra desventaja es la capacitancia de entrada en esta topología [4]. Considerando el caso más típico de que la señal de entrada se aplique al terminal de puerta, el ancho de banda del dispositivo viene descrito por la frecuencia de transición  $f_T$ :

$$f_{T,gate-driven} \approx \frac{g_m}{2\pi C_{gs}}$$

(3.7)

Donde  $C_{gs}$  es la capacitancia de puerta-fuente. Para frecuencias mayores que  $f_T$ , la respuesta en frecuencia del transistor deja de ser plana, y pasa a sufrir una caída de varios dB por octava. Para el caso de un MOSFET, bulk-driven, la frecuencia de transición viene descrita por:

$$f_{T,bulk-driven-driven} \approx \frac{g_{mb}}{2\pi(c_{bs}+c_{bsub})}$$

(3.8)

Donde  $C_{bs}$  es la capacitancia entre-bulk-fuente, y  $C_{bsub}$ , es la capacitancia entre el bulk y el substrato. Sabiendo que la capacitancia  $C_{bs}$  puede ser comparable a  $C_{gs}$ , y que  $C_{bsub}$  depende de factores tales como densidad de dopado, área del substrato, área del terminal de bulk etc. se puede llegar a una aproximación que relaciona ambas frecuencia de transición:

$$f_{T,bulk-driven} \approx \frac{\eta}{3.8} f_{T,gate-driven}$$

(3.9)

Siendo  $\eta$ , el cociente entre  $g_{mb}$  y  $g_m$ , con un rango de valores típico entre 0.2 y 0.4. El ancho de banda puede reducirse en un orden de magnitud, sin embargo tiene una dependencia clara de la tecnología que se use. Con tecnologías futuras que permitan un menor escalado de los circuitos, la dependencia del  $C_{bsub}$  con el área disminuirá considerablemente, por lo que el ancho de banda no ha de ser un inconveniente a la hora de usar esta técnica.

Así en este TFM, se pretende dar el estado de arte de la técnica como también intentar dar alguna nueva propuesta enfatizando tanto sus puntos fuertes como los débiles.

### 4. ESTADO DEL ARTE

En este apartado se revisaran las aplicaciones más reseñables que ponen en práctica el uso del terminal de bulk de forma activa. El objetivo de esta revisión es el análisis exhaustivo de estas aplicaciones.

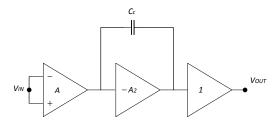

Unos de los dispositivos más usados en el diseño analógico y discreto es el amplificador operacional, el cual tiene como características ideales, una impedancia infinita de entrada, ganancia infinita, impedancia nula de salida y ancho de banda infinito, pese a que esto es imposible de conseguir de forma práctica sí que existen amplificadores operacionales, con características apropiadas. En la figura 4.1 se muestra el diagrama de bloques correspondiente al diseño típico de un amplificador operacional de dos etapas con compensación en frecuencia.

Figura 4.1 Diagrama de bloques opamp.

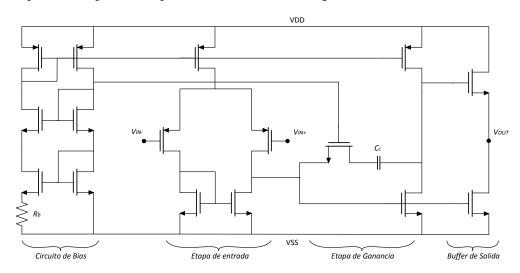

Las cuatro etapas mostradas en la figura 4.1 son, la etapa de entrada, etapa de ganancia, buffer de salida y la etapa que genera la corriente de bias. A continuación se muestra esta misma topología de un amplificador operacional pero a nivel de transistor, figura 4.2.

Figura 4.2. Etapas de un amplificador operacional.

En la figura 4.2 se muestra con más detalle el amplificador operacional, y se muestran sus diferentes etapas. La primera de ellas, el circuito de bias, compuesto por espejos de corriente, los cuales se encargan de generar la corriente de polarización necesaria para cada etapa. La etapa de entrada diferencial con un espejo de corriente como carga activa, una tercera etapa con un amplificador de fuente común y la compensación en frecuencia mediante el condensador  $C_C$ , y por ultimo un seguidor para conseguir una impedancia a la salida baja. Estos elementos son utilizados habitualmente en lazo cerrado, de hecho en el diseño de amplificadores operacionales, se tienen en cuenta este hecho para conseguir la estabilidad necesaria.

Otro elemento muy arraigado en el diseño de circuitos integrados es el OTA (Amplificador Operacional de Transconductancia), los OTAs ideales se consideran como una fuente de corriente controlada por voltaje, con ancho de banda, impedancia de entrada y salida infinitos. Volviendo a la figura 4.1, se observa como la etapa de entrada de un amplificador operacional puede ser vista como un OTA, ya que es una fuente de corriente controlada por voltaje. Esta corriente de salida se traslada a la etapa de ganancia y posteriormente a la etapa de salida, por lo que se puede ver la idea básica de un amplificador operacional como un OTA más una etapa de salida, para que la impedancia de salida sea baja, y se realice la conversión a voltaje.

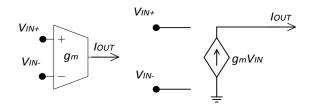

Los OTAs pueden ser usados en lazo cerrado o lazo abierto, dependiendo de la aplicación que se vaya a llevar acabo. En la figura 4.3 se muestra el símbolo de un OTA, y su modelo equivalente respectivamente.

Figura 4.3. Símbolos OTA.

La principal limitación de los OTAs es su rango dinámico, ya que si la señal de entrada es muy grande se produce mucha distorsión. Existe una investigación abierta al respecto, para mejorar el rango dinámico de entrada de estos dispositivos [5-21]. El OTA más sencillo es el utilizado para la etapa de entrada del amplificador operacional en la figura 4.1, su rango dinámico de entrada es muy bajo ya que para señales de entrada por encima de 0.5 V, la distorsión armónica empieza a ser notable. Existen varios OTAs, así como técnicas para mejorar este rango dinámico, y es aquí donde el uso del terminal de bulk de forma activa puede ser una solución a estos problemas.

A continuación se exponen varios circuitos donde se ha utilizado el terminal de bulk de forma activa [22], se empezará por etapas del amplificador operacional siguiendo el orden de polarización, par diferencial, etapas de salida y compensación. Posteriormente se tratara con los OTAs y las diferentes formas de obtener mejor linealidad. Por último un nuevo OTA será propuesto y se mostrará como mediante el uso del terminal de bulk se puede mejorar las prestaciones de este.

### 4.1 CIRCUITOS DE POLARIZACIÓN

Una de las etapas presentes en todo tipo de circuito analógico es la de bias, formada por espejos de corriente, que son los encargados de proporcionar la corriente necesaria a cada etapa del circuito. Existen numerosas topologías de espejos de corriente, sin embargo de nuevo se puede utilizar el bulk para mejorar las prestaciones de estos espejos de corriente. Uno de los espejos de corriente más usados en la actualidad es el HSC-CM (High-Swing Cascode Current Mirror), su topología es mostrada en la figura 4.4. El BE-HSC (Body Enhaced High Swing Cascode) se muestra en la figura 4.5, su topología es idéntica al HSC pero se introduce un amplificador diferencial, que sensa los voltajes de drenaje de M<sub>1</sub>y M<sub>2</sub> y ajusta los voltajes en el terminal de body en los transistores M<sub>3</sub>-M<sub>4</sub>. La estructura del amplificador diferencial se muestra en la figura 4.6. Las características son similares entre el HSC y BE-HSC salvo que aumenta la resistencia de salida:

$$R_{O-HSC} = \frac{g_{d4} + g_{d2} + g_{m4}}{g_{d2}g_{d4}} \tag{4.1}$$

$$R_{O-BEHSC} = \frac{g_{m4}(2A_X + X + 1)}{g_{d2}g_{d4}} \tag{4.2}$$

$$R_{O-RBD} = A \frac{g_{m3}}{g_{d3}g_{d2} \left(1 + \frac{g_{m4}g_{d6}}{g_{d2}(g_{m4} + g_{d6})}\right)}$$

(4.3)

Donde A y X son :

$$A = \frac{g_{m5}}{g_{d6} + g_{d8}} \tag{4.4}$$

$$X = \frac{g_{mb4}}{g_{m4}} \tag{4.5}$$

Evaluando las expresiones (4.1-3) con valores típicos de transconductancias, se obtiene una resistencia de salida mucho mayor para el espejo de corriente BE-HSC.

Figura 4.4. HSC-CM (High-Swing Cascode Current Mirror)

Figura 4.5. BEHSC-CM (Body Enhaced High-Swing Cascode Current Mirror)

Figura 4.6. Amplificador diferencial

Otra topología usando el terminal de body de forma activa para implementar espejos de corriente es RBD (Regulated Body-Driven), se muestra en la figura 4.7.

Figura 4.7. RBD (Regulated Body-Driven)

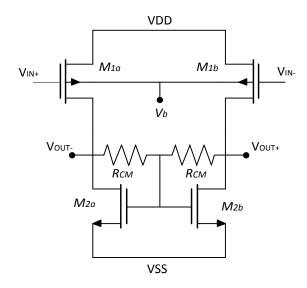

### 4.2 <u>MÍNIMA ALIMENTACIÓN EN UNA ETAPA DIFERENCIAL</u>

El par diferencial mostrado en la en la figura 4.8 puede ser usado como OTA y como entrada de un amplificador operacional. Es un par diferencial al cual se le ha quitado la corriente de bias, y se han añadido las resistencias  $R_{CM}$  que proporcionan control sobre el voltaje de modo común a la salida. Cabe notar que los transistores  $M_{2a\text{-}b}$  esta conectados como diodo para entrada de modo común.

Figura 4.8. Par diferencial con control de modo común.

Asumiendo en primer lugar que el voltaje del terminal de body en los transistores  $M_{1a}$  y  $M_{1b}$  es constante se obtienen las siguientes ganancias para modo común y diferencial.

$$A_{dm} = \frac{V_{out}}{V_{in,dm}} \approx -\frac{1}{2}g_{m1}R_{CM} \tag{4.6}$$

$$A_{cm} = \frac{V_{out}}{V_{in,cm}} = -\frac{g_{m1}}{gm_2} \tag{4.7}$$

Debido a la inexistencia de corriente de bias en la cola, se reduce la alimentación en un voltaje de saturación. A costa de esto la corriente en reposo depende de la temperatura, voltaje de alimentación, y variaciones en el modo común de entrada. Esto se traduce en que si esta etapa fuera a ser usada como etapa de entrada en un amplificador operacional, cuyas principales características son la ganancia, ancho de banda...estarían mal controladas.

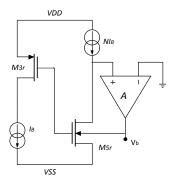

Para solucionar estos problemas se utiliza la terminal de body en los transistores  $M_{1a-b}$ . El voltaje  $V_b$  de estos será controlado mediante el circuito mostrado en la figura 4.9.

Figura 4.9. Circuito de control de Vb.

$M_{1ar}$ - $M_{1br}$  son réplicas de los transistores  $M_{1a-b}$ , como en el caso anterior el amplificador A tiene conectada su entrada negativa a tierra analógica, lo que fuerza a los drenajes de ambos

transistores a ese mismo voltaje modificando el voltaje  $V_b$ , además la corriente que atraviesa cada transistor es  $I_{BR}/2$ .

$M_{1a-b}$  y sus réplicas tiene el mismo  $V_{GS}$  y  $V_{BS}$  por lo que la corriente en el par diferencial original estará forzada a ser un múltiplo de  $I_{BR}$ .

Con este circuito complementario la ganancia de modo diferencial es aproximadamente igual a (4.6), sin embargo la ganancia de modo común ahora viene dada por:

$$A_{cm} = \frac{V_{out}}{V_{in,cm}} = -\frac{g_{m1}(1 + 2Ag_{mb1r}r_{BR}) - 2Ag_{m1r}g_{mb1r}r_{BR}}{gm_2(1 + 2Ag_{mb1r}r_{BR})}$$

$$= \frac{g_{m1}}{(1 + 2Ag_{mb1r}r_{BR})g_{m2}} + \frac{g_{m1}g_{mb1r} - g_{m1r}g_{mb1}}{g_{mb1r}g_{m2}}$$

(4.8)

Siendo A, la ganancia del amplificador y  $r_{BR}$  la resistencia de salida del generador de corriente. Suponiendo que las dimensiones de los transistores  $M_{1a-b}$  y  $M_{1ar-br}$  son las mismas,  $g_{m1r}g_{mb1}=g_{m1}g_{mb1r}$ , por lo que la ganancia de modo común se reduce en un factor de  $2Ag_{mb1}r_{BR}$  respecto a (4.7).

Las técnicas que implican el uso del terminal de bulk de forma activa no se reducen únicamente a su aplicación en OTAs o etapas de entrada de amplificadores, sino que puede aplicarse a varias posibles etapas, como una etapa de ganancia. A continuación se explica cómo puede aprovecharse el terminal de bulk para solventar alguno de los problemas que las etapas de ganancia implican.

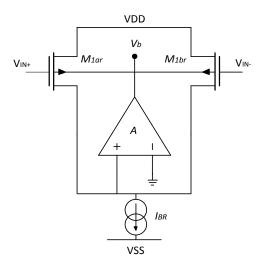

### 4.3 BODY DRIVEN GAIN BOOSTING

La ganancia de voltaje intrínseca de un transistor MOS en tecnologías casi nanométricas se ve desafortunadamente reducida. Al aumentar la dimensión del canal L para así aumentar la resistencia de salida del propio transistor tiene como consecuencia una reducción en el ancho de banda de este. Un posible remedio es usar amplificador con varias etapas en cascada, mediante etapas de ganancia de bajo voltaje. El requerimiento de mínima alimentación puede mantenerse, y la ganancia aumenta, sin embargo un amplificador con más de dos etapas de ganancias se vuelve inestable por lo que necesita corregirse su ancho de banda.

Una técnica para aumentar la ganancia y no tener que reducir el ancho de banda considerablemente es poner los transistores en cascodo, sin embargo esto conlleva un aumento en la alimentación, por lo que varías variantes de estas técnicas han sido propuestas.

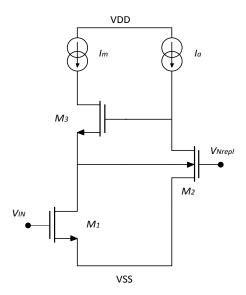

A continuación se presenta el amplificador "gain boosted" en la figura 4.10. El transistor  $M_1$  es un amplificador de fuente común, y  $M_2$  el transistor en cascodo siendo  $M_3$  la etapa auxiliar de "boosting". Las dos fuentes de corriente, Ia y Im han de ser implementadas para este tipo de aplicación sino la ganancia se vería afectada.

Figura 4.10. Amplificador "gain-boosted".

Para calcular la ganancia de este sistema se recurre a un análisis en pequeña señal, y se obtiene que la ganancia total es igual a:

$$A = -g_{m1}g_{m2}g_{m3}r_{d1}r_{d2}r_{03} (4.9)$$

Siendo el  $r_{03}$  la resistencia total en el drenaje del transistor  $M_3$ , y  $g_{m3}r_{03}$  el factor que aporta el transistor  $M_3$ .

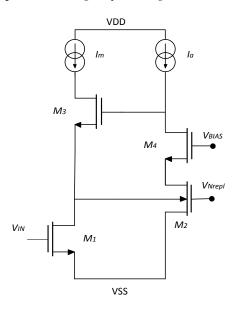

Es fácil ver que en este circuito la mínima alimentación necesaria es  $2V_T+3V_{DSsat}$ , por lo que es difícil alcanzar alimentaciones por debajo de 1V, ni siquiera suponiendo voltajes de umbral de 0.3 V. Para bajar la alimentación se utiliza el terminal de bulk de forma activa, y se muestra en la figura 4.11. El circuito es similar al de la figura 3.6 únicamente que el transistor  $M_3$  utiliza el bulk como entrada y la puerta de forma pasiva, manteniéndola a un voltaje constante  $V_{Nrepl}$ .

Figura 4.11. Amplificador "gain-boosted" con baja alimentación.

Al igual que en el circuito anterior se recurre a un análisis en pequeña señal del circuito para averiguar su ganancia, y el resultado es este:

$$A = -g_{m1}g_{m2}g_{mb3}r_{d1}r_{d2}r_{03} (4.10)$$

El único cambio es el de  $g_{mb3}$  siendo la transconductancia de body-fuente, que es típicamente un orden de magnitud menor que  $g_{m3}$ , la transconductancia de compuerta-fuente.

La alimentación mínima necesaria con esta topología es igual a  $V_T+3V_{DSsat}$ , se disminuye un voltaje de umbral aunque se pierde ganancia, debido a que la ganancia en la etapa de boostting proporcionada por  $M_3$  es dependiente de  $g_{mb3}$  y no de  $g_{m3}$ .

Figura 4.12. Amplificador "gain-boosted" con dos transistores en cascodo.

A este último circuito se puede añadir otra simple modificación mostrada en la figura 4.12. Se implementa  $M_4$  como un transistor en cascodo lo que aumenta la alimentación en un  $V_T$ , además la corriente de bias, Ia, ha de ser implementada teniendo en cuenta eso, sin embargo la expresión de la ganancia obtenida con un análisis en pequeña señal es de esta forma:

$$A = -g_{m1}g_{m2}g_{mb3}g_{m4}r_{d1}r_{d2}r_{d3}r_{04} (4.11)$$

De esta manera la ganancia aumenta adquiriendo dependencia de la transconductancia de M<sub>4</sub> y la resistencia total vista en su drenaje.

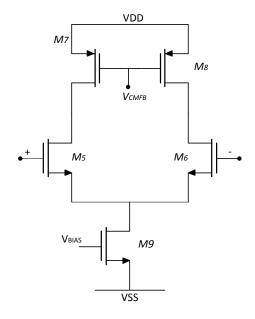

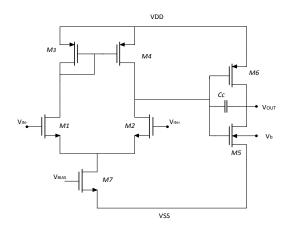

# 4.4 <u>CONTROL DE LA CORRIENTE EN REPOSO DE UNA ETAPA DE SALIDA DE CLASE AB</u>

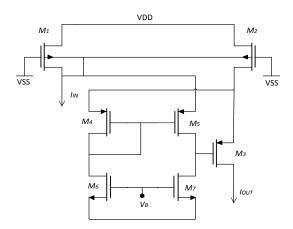

Se considera el amplificador operacional Miller de dos etapas, mostrado en la figura 4.13. Está formado por una etapa de entrada que consta de un par diferencial (M<sub>1</sub>-M<sub>2</sub>) el cual se sirve de la corriente de bias proporcionada por M<sub>7</sub>, y M<sub>3</sub>-M<sub>4</sub> que forman un espejo de corriente a su vez funcionando como carga. La siguiente etapa está formada por M<sub>5</sub> y M<sub>6</sub> siendo estos transistores de tipo *n* y *p* respectivamente. Sus puertas están conectadas directamente a la salida de la primera etapa, al igual que el condensador de compensación frecuencial C<sub>c</sub>, esto permite una operación de tipo AB a la salida, ya que la máxima de corriente alcanzable en las transiciones negativa y positiva es independiente de la corriente en reposo de los transistores M<sub>5</sub> y M<sub>6</sub>, pero está determinada por el máximo y mínimo voltaje a la salida de la primera etapa y por las dimensiones de estos. La principal desventaja de este circuito es la mala definición en la etapa de salida de la corriente en reposo, ya que depende fuertemente de las dimensiones correctamente diseñadas de M<sub>5</sub> y M<sub>6</sub>, ya que poseen diferente tipo de canal, del voltaje en reposo proporcionada por la primera

etapa y de los voltajes de alimentación, lo que impide el correcto diseño de esta corriente. Sin embargo utilizando la técnica de "body-biasing" se puede usar el terminal de body del transistor  $M_5$  para contralar esta corriente. El circuito que permite controlar esta corriente se muestra en la figura 4.14.

Figura 4.13. Amplificador operacional Miller de dos etapas.

Figura 4.14. Circuito de control de corriente.

Los transistores  $M_{3r}$  y  $M_{5r}$  son una réplica de  $M_3$  y  $M_5$  y la corriente IB es la mitad de la corriente proporcionada por  $M_7$ , además se asume que la corriente deseada para alimentar a  $M_5$  y  $M_6$  es N veces IB, lo que se traduce en que las dimensiones de  $M_6$  han de ser N veces las de  $M_3$ - $M_4$ , de otra manera debido a las diferencias de corrientes se produciría un offset no deseado. Como resultado el voltaje  $V_{GS}$  de  $M_5$  y  $M_{5r}$  es el mismo, destacar que el amplificador a que la corriente que atraviesa  $M_{5r}$  sea igual a N IB ya que la entrada negativa está conectada a tierra analógica  $(V_{DD}+V_{SS})/2$ , por lo tanto el drenaje de  $M_{5r}$  se forzará a tierra analógica modificando su voltaje en  $V_b$ . Este mismo voltaje  $V_b$  es utilizado para controlar el terminal de body de  $M_5$  que tiene la misma corriente en reposo que  $M_{5r}$

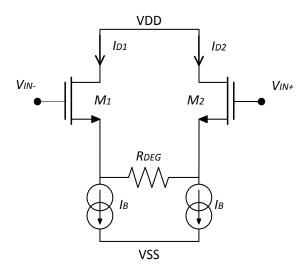

#### 4.5 MEJORA DE LA LINEALIDAD EN UN TRANSCONDUCTOR

Con la linealidad se hace referencia a la distorsión armónica total (Total Harmonic Distortion THD) que es su forma natural de medirlo. Como se ha comentado en secciones anteriores un transistor es un dispositivo no lineal, por lo que la conversión de voltaje a corriente en estos dispositivos no es lineal. Esta no linealidad se traduce en que en la corriente generada por el transistor aparecen componentes frecuenciales inexistentes en el voltaje de entrada que provocan la deformación de la forma de onda original. Para la obtención de la THD, se asume una entrada de voltaje sinusoidal haciendo una análisis en el dominio frecuencial se analizan las

amplitudes de las componentes superiores a la frecuencia fundamental del voltaje de entrada causadas por la no linealidad del dispositivo.

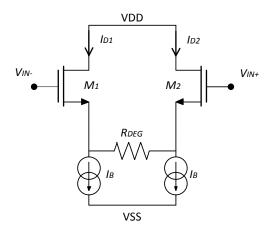

La linealidad en transconductores usados en filtros de tiempo continuo, o de etapas de entrada en un amplificador operacional, es uno de los aspectos más críticos y es por eso por lo que varios transconductores han sido propuestos a lo largo del tiempo, sin embargo una de las técnicas más usadas a la hora de diseñar un transconductor es la degeneración resistiva de fuente, tal y como se muestra en la figura 4.15. Con esta técnica la linealidad depende prácticamente de las propiedades lineales de una resistencia y de los buffer hechos con transistores.

Figura 4.15. Transconductor con degeneración de fuente.

De nuevo se puede utilizar el termial de body de forma activa para mejorar la linealidad de este transconductor [23], la topología se muestra en la figura 4.16. Los voltajes de control conectados al terminal de body de cada uno de los transistores del par principal  $M_1, M_2$  se obtienen mediante un par diferencial replicado en el cual la resistencia degenerativa de divide en tres resistencias. La condición que ha de tener este par diferencial replicado es un escalado, tanto es sus dimensiones como en las resistencias de degeneración, siendo,  $m=(W/L)_1/(W/L)_3$  y  $mR_{DEG}=R_2+2R_1$ .

Figura 4.16. Transconductor usando el terminal de body de forma activa.

Con esta técnica se pueden conseguir mejoras en la distorsión armónica total de hasta aproximadamente 10 dB en el mejor de los casos, sin pérdidas apreciables en el ancho de banda del transconductor.

Ha sido publicado recientemente otro artículo [24] en el que basándose en el transconductor de la figura 4.15, y utilizando el terminal de body de los transistores se consigue una mejora significativa en la THD de este. El transconductor se muestra en la figura 4.17.

Figura 4.17. Transconductor usando el terminal de bulk de forma activa.

Para probar la mejora de linealidad de este transconductor se recurre a un análisis en pequeña señal de los transconductores de las figuras 4.15 y 4.17, y se obtienen las siguientes transconductancias:

$$G_{mR} = \frac{g_{m1}}{(1 + g_{m1}R)} \tag{4.12}$$

$$G_{mRB} = \frac{g_{m1}}{(1 + (2n - 1)g_{m1}R)} \tag{4.13}$$

Siendo  $G_{mR}$  la transconductancia del circuito mostrado en la figura 3.17 y  $G_{mRB}$  la del mostrado en la figura 3.17. El término "n" se define como el " $slope\ factor$ " y toma valores entre 1.1 y 1.6, por lo que la transconductancia  $G_{mRB}$  es menor que  $G_{mR}$  y por tanto mejora su linealidad.

### 5. TRANSCONDUCTORES (usando técnicas bulk-driven)

Como consecución de un estudio exhaustivo del estado del arte sobre las diferentes aplicaciones en las que puede usarse de manera satisfactoria el terminal de body de un transistor MOS, se procede a aplicar las técnicas comentadas en el diseño de OTAs, primeramente para el aumento de linealidad y posteriormente para realizar bloques no lineales. Esto consta de varias partes, en la primera de ellas se procede a explicar un modelo de caracterización de un transistor MOS, diferente al comúnmente usado, ya que será beneficioso para ciertos análisis que implican topologías más complejas. El siguiente paso es explicar la técnica utilizada para el cálculo de la distorsión producida por los transconductores. Posteriormente se pasará al análisis y caracterización de varios transconductores hasta llegar a un transconductor propuesto y nuevo que mejorará la linealidad gracias al uso del terminal de bulk de forma activa. Para acabar se mostrará otro circuito, en este caso un multiplicador/divisor que de igual manera usará el terminal de bulk de forma activa usando una estructura novedosa.

# 5.1 <u>MODELO ALTERNATIVO DE UN TRANSISTOR MOS (ALL</u> REGION MODEL)

En la actualidad existen diversos modelos que describen con mayor o menor precisión la corriente que atraviesa un transistor. Como se ha comentado en capítulos anteriores el más usado es la "Ley Cuadrática", sin embargo implica una gran complejidad matemática en cuanto el terminal de bulk es usado de forma activa. Es por eso por lo que se estudió otro modelo en el cual se describiesen las corrientes que atraviesan un transistor de manera fidedigna y a su vez que el uso del terminal de bulk de forma activa no introdujese gran complejidad matemática.

Es un modelo derivado del modelo EKV [25], llamado All Region Model [26]. La principal característica es que a excepción de la Ley Cuadrática explota la simetría inherente del transistor referenciando todos los voltajes al terminal de bulk, tal y como se muestra en la figura 5.1.1. En este modelo la inversión de carga es controlada por  $V_p$ - $V_{ch}$ , donde  $V_{ch}$  es el voltaje del canal definido como la diferencia de los potenciales de Fermi entre las portadoras,  $V_p$  es el llamado pinch-off voltage, y se define como el valor particular de  $V_{ch}$  para el cual la inversión de carga en el canal es cero para un determinado voltaje aplicado en la puerta. Este último depende únicamente del voltaje en la puerta y puede ser interpretado como el efecto equivalente del voltaje aplicado en la puerta referido al canal.

El modelo persigue una mejor definición de las corrientes en diseños microelectrónicos de bajo voltaje, ya que la Ley Cuadrática no ofrece tanta precisión para este tipo de diseños.

Figura 5.1.1. Voltajes en un transistor MOS.

Si se asume que el substrato ha sido dopado uniformemente se puede definir la corriente que atraviesa el transistor como la diferencia entre dos corrientes (*forward y reverse*). El modelo obtiene las ecuaciones correspondientes para una operación en inversión débil, y las correspondientes a una operación en inversión fuerte, y posteriormente interpola ambas ecuaciones para obtener una definición que satisfaga las tres posibles operaciones, débil, moderada y fuerte. Las ecuaciones que describen la corriente:

$$I_D = I_F - I_R \tag{5.1.1}$$

$$I_{F(R)} = \frac{\beta}{2n} \left( V_{GB} - nV_{SB(DB)} - V_{T0} \right)^2$$

(5.1.2)

Siendo  $\beta = \mu_x C_{OX}(W/L)$ , y *n* el *slope factor* [27].

En el caso de que el transistor operase en saturación:

$$V_{DB} = \frac{V_{GB} - V_{T0}}{n} \tag{5.1.3}$$

Por lo que la corriente  $I_R$  se haría cero y solo existiría corriente  $I_F$ .

Este modelo también comparte muchas similitudes con la Ley Cuadrática, de hecho las formulas descritas en la Ley Cuadrática se pueden obtener a partir de las expuestas anteriormente, únicamente en el caso de que el terminal de body esté conectado a la fuente.

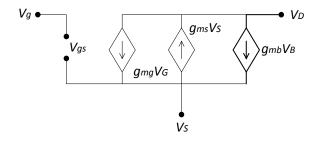

Las ecuaciones expuestas serían las correspondientes a un análisis en gran señal, sin embargo existe un análisis en pequeña señal para este modelo, el cual es de gran utilidad. A diferencia de la Ley Cuadrática, en este modelo se describen cuatro transconductancias [28-29], una por cada terminal del transistor, a continuación se definen:

$$g_{mg} = \frac{\partial I_D}{\partial V_G} \tag{5.1.4}$$

$$g_{ms} = -\frac{\partial I_D}{\partial V_S} \tag{5.1.5}$$

$$g_{md} = \frac{\partial I_D}{\partial V_D} \tag{5.1.6}$$

$$g_{mb} = \frac{\partial I_D}{\partial V_B} \tag{5.1.7}$$

Además pueden ser relacionadas de dos maneras:

$$g_{mg} + g_{md} + g_{mb} = g_{ms} (5.1.8)$$

$$g_{mg} = \frac{g_{ms} - g_{md}}{n} \tag{5.1.9}$$

El circuito equivalente en pequeña señal para un transistor en saturación se muestra en la figura 5.1.2.

Figura 5.1.2. Modelo en pequeña señal de un transistor en saturación.

Gracias a estas definiciones de las tranconductancias y al modelo equivalente en pequeña señal de un transistor descrito por este modelo, los cálculos pueden simplificarse y obtener resultados más claros, para variables que puedan ser descritas mediante un análisis en pequeña señal y hechas a mano.

El estudio de este modelo es justificado ya que, como se ha comentado con anterioridad, trata al transistor como un dispositivo simétrico, lo que es favorable para el cálculo de parámetros, ya sea en pequeña o gran señal, de topologías que usan el terminal de body de forma activa.

### 5.2 ANALISIS DE DISTORSIÓN

Cuando se está diseñando OTAs una característica importante es saber que tan lineal se comporta, así una técnica para medir esta cualidad se encuentra en el análisis de distorsión que se introduce en esta sección. El objetivo de esta sección es exponer la técnica usada para realizar los cálculos teóricos de distorsión armónica que producen los transconductores para poder compararlos y saber las técnicas más convenientes. Algunos de estos transconductores tienen una topología compleja de analizar, ya que cuentan con transistores en cascodo que operan en la región de triodo y en la región de saturación, además de utilizar el bulk de forma activa, lo que resulta en resolución de ecuaciones simbólicas implícitas y que proporcionan poca información al diseñador. Para mejorar la resolución de las ecuaciones implícitas se propondrá un método alternativo para calcular los coeficientes de la series de Taylor como se verá más adelante.

Para realizar el análisis de distorsión se utilizado típicamente un desarrollo en Series de Taylor [30-42] lo que proporciona una buena aproximación para el cálculo de distorsiones armónicas de diferente orden y en consecuencia la distorsión armónica total. Las series de Taylor se definen de la siguiente manera para una función no lineal f(x):

$$f(x) = \sum_{n=0}^{\infty} \frac{f^{(n)}(a)}{n!} (x - a)^2$$

(5.2.1)

El cálculo diferencial de las Series de Taylor, se ha de efectuar respecto a un punto de referencia, "a", de la función, siendo  $f^{(n)}$  es la derivada n-esima. El primer término que se obtiene en el desarrollo es una constante (f(a)), el siguiente de grado uno, equivale a una recta tangente a la función a aproximar en el punto "a", y sucesivamente la función se aproxima mediante parábolas de grado creciente.

Un punto importante a considerar cuando se usan las series de potencia es su radio de convergencia para saber hasta cuando es válida la aproximación, así según el teorema de Cauchy-Hadamard, para cada serie de potencias de tipo:

$$\sum_{n=0}^{\infty} a_n (x - a_0)^n \tag{5.2.2}$$

Se da uno, y únicamente unos de estos tres casos:

- 1. La serie sólo converge para  $x=a_0$ .

- 2. La serie converge absolutamente para todo  $x \in C$ .

- 3. Existe un número  $\rho > 0$  tal que para  $|x-a_0| < \rho$  la serie converge absolutamente y para  $|x-a_0| > \rho$  la serie diverge.

Según el teorema se da únicamente uno de los tres casos, a continuación se tomara como ejemplo una función básica, a partir de la cual se definirán conceptos que más tarde se utilizarán.

Conviene destacar conceptos como el círculo de convergencia, que se corresponde al rango de valores de la función para los cuales el polinomio obtenido mediante el desarrollo en series de Taylor de la función, realizan una buena aproximación. Por ejemplo en el caso del cálculo de la función seno, el círculo de convergencia sería un período completo de este, fuera de este periodo los valores que se obtienen de los términos del polinomio se alejan de la función seno. Existen funciones como la raíz cuadrada que tienen un dominio restringido, únicamente valores positivos. Tomando el ejemplo de la función:

$$f(x) = \sqrt{1+x} \tag{5.2.3}$$

El dominio de esta función es  $D=(-1,+\infty)$ , si se aproxima esta función mediante los polinomios de Taylor, evaluados para x=0, únicamente se obtendrá una aproximación valida dentro del rango de valores x=(-1,1). Esto se debe a que el radio del circulo de convergencia viene marcando por el punto donde se evalúa la función, x=0, hasta el punto que empieza el dominio de la función, x=-1. Notar que siempre que se da el tercer caso en el teorema de Cauchy-Hadamard, el número  $\rho$  equivale al radio de convergencia de la serie, siendo el circulo el descrito por su centro el punto  $a_0$ , y de radio  $\rho$ .

El objetivo final es el cálculo de la distorsión armónica utilizando las series de Taylor. Comúnmente se ha definido las distorsiones armónicas de diferente orden con expresiones que facilitan su cálculo. El orden de la distorsión armónica viene dado por el número de armónico al que se refiere, siendo así la distorsión de tercer orden la correspondiente al armónico de tercer orden. De esta manera atendiendo a las siguientes identidades trigonométricas:

$$\cos^2 \theta = \frac{1 + \cos 2\theta}{2} \tag{5.2.4}$$

$$\cos^3 \theta = \frac{3\cos\theta + \cos 3\theta}{4} \tag{5.2.5}$$

Se observa como el término de coseno al cuadrado tiene una componente equivalente al segundo armónico, y de igual manera el término coseno al cubo tiene una componente del tercer armónico. La distorsión armónica se define como la relación entre la variación producida en un armónico entre el fundamental. De esta manera se pueden obtener expresiones que determinan las distorsiones armónicas de diferente orden, atendiendo a las identidades trigonométricas correspondientes. Así, se definen la distorsión armónica de segundo y tercer orden como:

$$HD2 = \frac{1}{2} \frac{\alpha_2}{\alpha_1} X \tag{5.2.6}$$

$$HD3 = \frac{1}{4} \frac{\alpha_3}{\alpha_1} X^2 \tag{5.2.7}$$

Siendo  $\alpha_2$  el término que multiplica en la serie a  $X^2$ , correspondiente al segundo armónico,  $\alpha_3$  el término que multiplica en la serie a  $X^3$ , correspondiente al tercer armónico, y  $\alpha_1$  el termino en la serie que multiplica a X, correspondiente al fundamental. El término de  $\frac{1}{4}$  viene dado por la identidad trigonométrica  $\cos^3\theta$ , y el término  $\frac{1}{2}$  viene dado por la identidad trigonométrica del

### 5.2.1 DISTORSIÓN EN TRANSCONDUCTORES

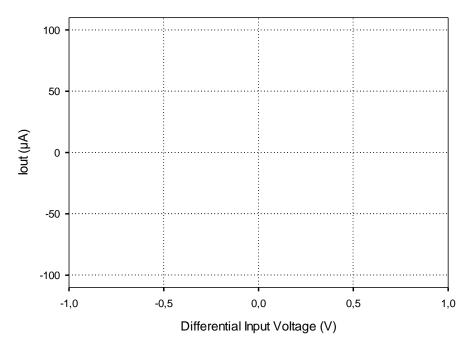

En el caso que incumbe, el cálculo de la distorsión armónica de un transconductor, la función a desarrollar, se describe perfectamente mediante las curvas *V-I*. En la figura 5.2.1.1 se muestra una curva *V-I*, estas curvas son la representación gráfica de la función que describe el comportamiento de un transconductor.

Figura 5.2.1.1. Curva V-I de un transconductor.

En este caso la variable x correspondería a  $V_{IN}$ , y si se evalúan los términos obtenidos en el desarrollo de la serie en el punto  $V_{IN}=0$ ,  $I_a=I_B$ , el primer término de la serie seria cero, el segundo término sería la recta tangente a la curva V-I, en el punto  $V_{IN}=0$ , lo que corresponde a la transconductancia, y posteriormente esta curva será aproximada mediante parábolas de grado creciente, según el término del desarrollo de la serie. Esta función tiene un dominio restringido igualmente, y este dominio viene dado por el rango dinámico del transconductor. Cuando se alcanza el punto máximo de corriente y esta es independiente del voltaje de entrada aplicado, es decir no incrementa su valor con el voltaje de entrada, se alcanza el máximo del rango dinámico. Para valores superiores a este voltaje la función es forzada a resolverse con números complejos, lo que indica una singularidad de la función en este punto. Recurriendo a la definición de círculo de convergencia de la función, y aplicando el teorema de Cauchy-Hadamard, al evaluar las series de Taylor obtenidas de esta función V-I, el círculo de convergencia viene descrito por las singularidades de los extremos de la función, cuando las series son evaluadas en el punto  $V_{IN}$ =0,  $I_a$ = $I_B$ . Para demostrar la aplicación de este teorema al caso que concierne se expone la figura 5.2.1.2:

Figura 5.2.1.2. Aproximación a la curva V-I mediante Series de Taylor.

En la figura 5.2.1.2 se aprecia como el rango dinámico del transconductor equivale a (-1,1) V. La primera aproximación mediante las series de Taylor, es el término constante, que en este caso equivale a cero. La siguiente aproximación es la recta tangente al punto en el que se ha evaluado la función,  $V_{IN}=0$ , equivalente a la transconductancia. Posteriormente se suman las aproximación parabólicas de grado tres y cinco, y tal y como se aprecia se cumple el teorema de Cauchy-Hadamard, ya que las aproximaciones son buenas hasta que se llega a las singularidades en los extremos de la función.

Puede existir una problemática a la hora de aplicar estas series para el cálculo de la distorsión armónica y es la complejidad matemática de la función. Para poder utilizar estas series se requiere despejar de la función la diferencia de corrientes,  $I_{OUT}$ , del voltaje de entrada,  $V_{IN}$ , quedando finalmente una expresión de este tipo:

$$I_{OUT} = f(V_{IN}) (5.2.1.1)$$

Al obtener este caso se aplicarían el desarrollo en series de la función,  $f(V_{IN})$ , y se obtendría directamente los coeficientes para el cálculo de la distorsión armónica. Sin embargo pueden darse casos que la relación  $I_{OUT}$  vs  $V_{IN}$  es implícita, por lo que el uso de las series de Taylor como se describió anteriormente queda descartado, sin embargo se pueden utilizar las series de Taylor formuladas de forma alternativa [43]. En este caso la función que se obtendría se puede convertir en:

$$F(x,y) = 0 (5.2.1.2)$$

Donde y=g(x), es decir una función de la variable x. Si se cambia x e y, por  $V_{IN}e$   $I_{OUT}$ , es posible obtener las series de Taylor de una función implícita, viniendo estas descritas por:

$$y_0 + \sum_{k=1}^{\infty} \frac{F_k(x_0, y_0)}{k!} x^k$$

(5.2.1.3)

$$g'(x) = -\frac{\frac{\partial F}{\partial x}(x, y)}{\frac{\partial F}{\partial y}(x, y)} = F_1$$

(5.2.1.4)

$$g''(x) = \frac{\partial F_1}{\partial x}(x, y) + \frac{\partial F_1}{\partial y}(x, y)F_1(x, y) = F_2$$

(5.2.1.5)

$$g'''(x) = \frac{\partial F_2}{\partial x}(x, y) + \frac{\partial F_2}{\partial y}(x, y)F_2(x, y) = F_3$$

(5.2.1.6)

Al igual que en las series de Taylor es necesario definir un punto alrededor de cual se realizará la aproximación en este caso es necesario tener definidos dos valores  $x_0$  e  $y_0$ . Con el uso de las series de Taylor de funciones implícitas es posible realizar un cálculo de distorsión de una manera menos compleja desde el punto de vista matemático, y será el procedimiento que se seguirá para realizar el análisis de distorsión. Debido a la imposibilidad de separar en la ecuación a desarrollar las variables  $I_{OUT}$  y  $V_{IN}$ , se decide realizar los cálculos para la corriente de una rama, por ejemplo  $I_a$ . Este procedimiento no afecta de ninguna manera al resultado final, ya que es equivalente al cálculo de la serie usando  $I_{OUT}$ . Esto se debe a que  $I_{OUT}=I_a$ - $I_b$ , por lo que a priori sería necesario el cálculo de las series para la corriente  $I_a$  y posteriormente para la corriente  $I_b$ . Sin embargo las series que se obtiene son idénticas, teniendo estas como única diferencia el signo de los términos, los términos pares tiene el mismo signo y mismo valor, y los términos impares tienen el mismo valor pero signo cambiado, por lo que al realizar la resta entre ambas series para obtener la serie correspondiente a  $I_{OUT}$ , los términos pares se restan y se eliminan, mientras que los términos impares se suman. Notar que esto únicamente pasa cuando existe un matching perfecto entre los transistores, es decir cuando las dimensiones, y características de los transistores en ambas ramas son idénticas.

#### 5.3 ANALISIS DE LOS TRANSCONDUCTORES

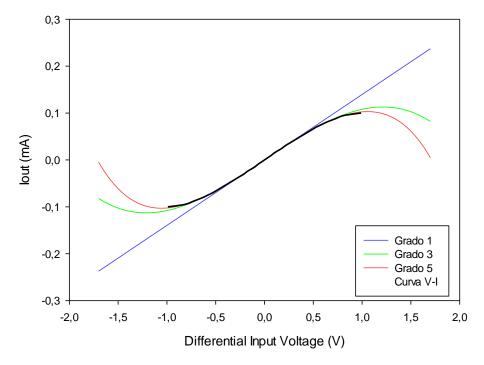

En esta sección se pasa a analizar la THD de varios transconductores, con diferentes topologías.

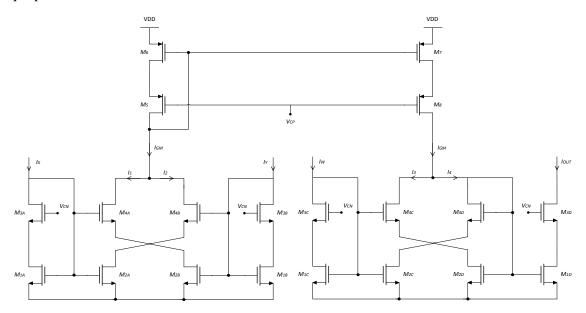

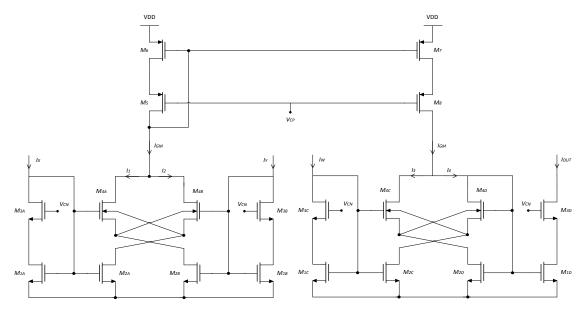

Figura 5.3.1. Transconductores a analizar.

En la figura anterior se muestran los diferentes transconductores a analizar. El primero de ellos, figura 5.3.1 a) es el par diferencial que consta únicamente de dos transistores operando en saturación. En la figura 5.3.1 b) se muestra el par diferencial con degeneración de fuente, en este caso al introducir una resistencia se mejora la linealidad ya que esta recae sobre las propiedades lienales de esta. La figura 5.3.1 c) muestra un par diferencial con degeneración de fuente y además este utiliza los terminales de bulk de forma activa para mejorar la linealidad. Los dos últimos figura 5.3.1 d) y e) son transocnductores los cuales utilizan transistores en cascodo para mejorar la linealidad, aparte de degeneración resistiva de fuente. El transconductor propuesto corresponde a la figura 5.3.1 e) el cual utiliza además los terminales de bulk de forma activa para lograr una mejor linealidad.

Todos ellos excepto el último han sido propuestos con anterioridad y testeados. Se realizaran graficas comparativas que prueban la validez de los resultados teóricos obtenidos, mediante la comparación de estos con resultados simulados y teóricos frente a los experimentales.

En todos los transconductores a analizar se seguirá el mismo procedimiento. En primer lugar se calculará su transconductancia efectiva utilizando el *All Region Model*, y posteriormente se realizará el análisis de distorsión armónica. Para el análisis de distorsión armónica, en todos los casos se calculara una función del tipo  $F(I_a, V_{IN})$ . Destacar que debido a la complejidad de los cálculos para el análisis de distorsión armónica, estos se llevaron a cabo utilizando la herramienta de MATLAB, MATLAB Mathematicts Toolbox. Los desarrollos de las series no serán expuestos debido a la longitud de estos, sin embargo se agregan los listados de Matlab.

Con el fin de llevar a cabo un estudio más exhaustivo de diferentes transconductores, y comprobar la técnica que se usará en el cálculo de distorsión, se realizaron los análisis de distorsión y se calculó la tansconductancia para diferentes transconductores. El modelo introducido, *All Region Model*, será muy útil para el cálculo de transconductancias, ya que se simplifica el circuito equivalente en pequeña señal. El análisis de distorsión se realizará con ambos modelos, *Ley Cuadrática y All Region Model*, en todos los transconductores. Estos resultados teóricos serán posteriormente comparados con los resultados obtenidos mediante simulación, se utilizará el programa *Cadence* el cual utiliza el simulador *Spectre* basado en el modelo BSIM. Para esta simulaciones se ha utilizado una librería con una tecnología de 0.5 μm. Para finalizar los resultados simulados y teóricos serán contrastados con resultados experimentales. Los resultados teóricos se obtendrán con datos propios de la tecnología de 0.5 μm.

Destacar que el cálculo de la distorsión armónica se realizada aproximando la THD mediante la distorsión armónica de tercer orden, aunque el procedimiento para el cálculo de los diferentes términos de las distorsión armónica es semejante al utilizado.

#### 5.3.1 PAR DIFERENCIAL

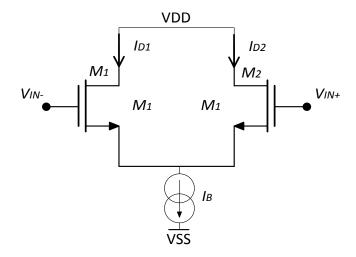

Un par diferencial está formado por dos transistores enfrentados, y por una fuente de corriente. En la figura 5.3.2 se muestra la topología de este circuito. Puede ser usado como un OTA o como una etapa de entrada a un amplificador operacional. Su característica más relevante es el bajo rango dinámico de este, así como su baja linealidad, y es poco usado en el diseño de circuitos integrados, aunque su principal uso es de tipo didáctico.

Figura 5.3.2. Par diferencial

Ambos transistores están en saturación, enfrentados entre sí, y sus fuentes comparten el mismo nodo. Para el cálculo de su transconductancia se recurriría a un modelo en pequeña señal, que en este caso no es necesario ya que la transconductancia de los transistores es  $g_m$ , y en este caso el cálculo exacto de la transconductancia puede realizarse de manera sencilla mediante su definición:

$$g_m = \frac{\partial I_D}{\partial V_{GS}} = \mu_n C_{ox} \left(\frac{W}{L}\right) (V_{GS} - V_T)$$

(5.3.1)

El siguiente paso es caracterizar la distorsión armónica del dispositivo, para ello e empezará con la Ley cuadrática, usando la ecuación (3.2) que describe la corriente para un transistor en saturación, se pueden escribir los voltajes  $V_{GSI-2}$ :

$$V_{GS1} = \sqrt{\frac{2I_a}{\beta}} + V_T \tag{5.3.2}$$

$$V_{GS2} = \sqrt{\frac{2I_b}{\beta}} + V_T \tag{5.3.3}$$

Las corrientes *Ia* e *Ib* se pueden relacionar con la corriente de bias de esta manera:

$$I_a + I_b = 2IB \tag{5.3.4}$$

La ecuación de tipo F(x,y)=0, que se usará a la hora de aplicar las series de Taylor de estas función implícita es:

$$V_{GS1} - V_{GS2} - V_{IN} = 0 (5.3.5)$$

Se desarrollan las series de Taylor de la función implícita (5.3.5), y se evalúan para el punto  $V_{IN}=0$ , Ia=IB. Posteriormente se aplica la ecuación que describe la componente de distorsión de tercer orden.

$$HD3 = \frac{\beta}{32IB} V_{IN}^2 \tag{5.3.6}$$

Esta expresión de la distorsión armónica de tercer orden se corresponde con la expresión obtenida mediante las series de MaClaurin, para este mismo par diferencial, por lo que se demuestra la validez del método aplicado para el análisis de distorsión.

El análisis realizado para la Ley Cuadrática se repite utilizando el *All Región Model*, utilizando la ecuación (5.1.2), sabiendo que los transistores están en saturación. La expresión de la función implícita en este caso es:

$$V_{GS1} - V_{GS2} - V_{IN} = 0 (5.3.7)$$

$$\sqrt{\frac{2nI_a}{\beta}} - \sqrt{\frac{2n(2IB - I_a)}{\beta}} - V_{IN} = 0$$

(5.3.8)

El principal cambio es el factor n, aunque el cambio no es del todo significativo ya que n, puede tomar valores entre 1.1 < n < 1.6. Repitiendo las cuentas realizadas para la Ley Cuadrática, la distorsión armónica de tercer orden es:

$$HD3 = \frac{\beta}{32nIB} V_{IN}^2 \tag{5.3.9}$$

Como puede observarse únicamente se introduce un factor n en el denominador, este factor lo único que proporciona es un pequeño cambio en la curva descrita, por la distorsión armónica de tercer orden.

A continuación se procede a realizar la comparación entre los resultados obtenidos mediante simulación y los teóricos. Para la obtención de estos se utilizarán los siguientes valores,  $\beta/2=15$   $\mu A/V$ ,  $W/L=50\mu m/10\mu m$ ,  $IB=50\mu m$  y n=1.15.

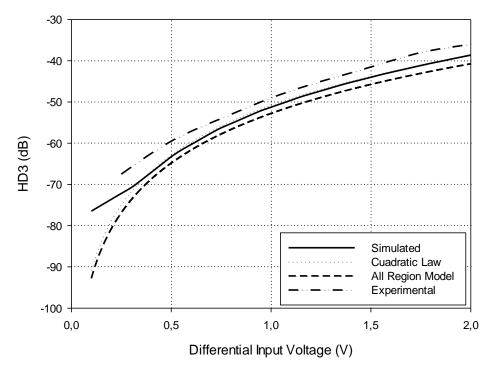

Figura 5.3.3. HD3 del par diferencial.

En la gráfica se muestran los resultados teóricos frente a los simulados. Entre ambos modelos como era de esperar existe una gran concordancia, ya que el único cambio en la caracterización de la distorsión armónica de tercer orden es el factor "n". Con respecto a los resultados simulados de igual manera se aprecia gran parecido entre estos y los teóricos. Debido a esta concordancia entre resultados, se aceptan los resultados teóricos obtenidos.

### 5.3.2 PAR DIFERNECIAL CON DEGENERACIÓN REISTIVA

El siguiente OTA a analizar es mostrado en la figura 5.3.4. Es una de las topologías más usadas en el diseño de circuitos integrados, debido a su sencillez de diseño y a que tiene una respuesta aceptable. La principal característica de este transconductor es que la linealidad total recae sobre las propiedades lineales de la resistencia colocada entre los dos terminales de fuente de los transistores. Esto implica que la transconductancia tiene aproximadamente un factor 1/R como transcoductancia.

Figura 5.3.4. Par diferencial con degeneración de fuente.

En primer lugar se realizará el análisis en pequeña señal del circuito, para obtener su transconductancia. Sabiendo que ambos transistores están operando en saturación, el circuito equivalente siguiendo el *All Region Model* es el que sigue:

Figura 5.3.5. Circuito equivalente en pequeña señal.

Al estar los transistores operando en saturación su modelo en pequeña señal viene descrito por tres fuentes de corriente controladas por voltaje, siendo estos voltajes, el voltaje aplicado a la puerta, el voltaje en la fuente, y el voltaje en el terminal de bulk. Para simplificar el cálculo y obtener un resultado más interpretativo se asume simetría entre los transistores, por lo que la transconductancia de cada uno de ellos es idéntica. Se han utilizado las equivalencias descritas en las ecuaciones (5.1.8-9) para que el cálculo de la transconductancia efectiva este únicamente en

función de la transconductancia de la puerta, *gm*. Resolviendo el circuito se obtiene que la transconductancia efectiva es igual a:

$$g_m = \frac{g_{mg1}}{(1 + g_{mg1}R)} \tag{5.3.10}$$

La transconductancia efectiva tiene una fuerte dependencia de R, al aumentar el valor de R, la transconductancia disminuye. Suponiendo que  $Rg_m >> 1$ , la transconductacia total se puede aproximar por  $gm \approx 1/R$ . Con esto se demuestra como la ganancia del dispositivo se ve fuertemente afectado por la resistencia de degeneración.

El siguiente paso es el análisis de distorsión armónica. Para el análisis se seguirán los mismos pasos que con el par diferencial. En primer lugar se muestra la ecuación que definirá la función implícita a desarrollar:

$$V_{GS1} - V_{GS2} + V_B - V_{IN} = 0 (5.3.11)$$

Siendo V<sub>B</sub> la diferencia de voltaje entre los bornes de la resistencia, que puede ser definido como:

$$V_B = I * R = (I_a - IB) * R$$

(5.3.12)

Sabiendo que 2xIB=Ia+Ib, y aplicando la Ley cuadrática se obtiene la siguiente ecuación:

$$\sqrt{\frac{2I_a}{\beta}} - \sqrt{\frac{2(2IB - I_a)}{\beta}} + (I_a - IB) * R - V_{IN} = 0$$

(5.3.13)

Se puede apreciar cómo se crea una dependencia directa con la resistencia de degeneración, siendo esta la única diferencia entre la ecuación (5.3.8) y la (5.3.13). Repitiendo los pasos realizados para el par diferencial, y evaluando de nuevo para el punto  $V_{IN}=0$ ,  $I_a=I_B$ , se obtiene el término de la distorsión armónica de tercer orden:

$$HD3 = \frac{\sqrt{2}\beta}{32 \, IB\left(\sqrt{2} + R\beta\sqrt{\frac{IB}{\beta}}\right)^3} V_{IN}^2 \tag{5.3.14}$$

Si se comparan las expresiones (5.1.9) y la (5.3.14) se distingue una dependencia de R para esta última, lo que hace que conforme mayor sea R menor será el término HD3, mientras que en la expresión de la distorsión armónica de tercer orden para el par diferencial, para disminuir esta distorsión es necesario aumentar la corriente de bias, I<sub>B</sub>. En este caso para mejorar la linealidad influyen estos dos factores pudiendo llegar a un mejor compromiso entre ambos.

Utilizando ahora el *All Region Model*, se calcula la ecuación implícita siendo la diferencia entre las ecuaciones obtenidas mediante este modelo y la Ley Cuadrática el término "n", semejante al caso anterior, y posteriormente se calculan las series de esta función implícita y se obtiene el término de la distorsión armónica de tercer orden.

$$HD3 = \frac{\sqrt{2}\beta n^2}{32 \, IB\left(\sqrt{2}n + R\beta\sqrt{\frac{IB}{\beta}}\right)^3} V_{IN}^2 \tag{5.3.15}$$

Al igual que en el anterior caso únicamente se crea una dependencia con el factor n, lo que no causa gran variación en el cómputo global.

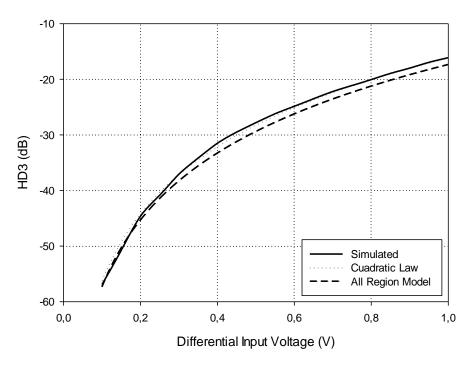

Se muestra una gráfica comparativa entre los resultados teóricos obtenidos con ambos modelos, los resultados simulados y experimentales. En este caso los parámetros usados son los siguientes,  $\beta/2=15 \ \mu A/V$ ,  $W/L=3 \mu m/3 \mu m$ ,  $IB=50 \mu m$ ,  $R=1K\Omega$  y n=1.15.

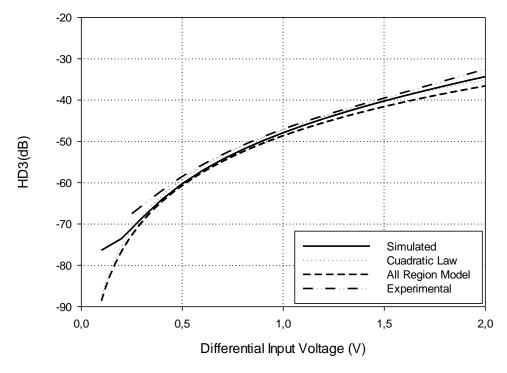

Figura 5.3.6. HD3 para el par diferencial con degeneración resistiva de fuente.

Como puede apreciarse existe prácticamente una total concordancia entre todos los resultados, teóricos, experimentales y simulados. Para voltajes de entrada menores que 0.3 V, es donde mayor variación existe, pero cabe notar que teóricamente para un voltaje de entrada de 0 V la distorsión armónica es nula, es decir menos infinitos dB, y es por eso por lo que las curvas descritas teóricamente definen peor la distorsión para voltajes de entrada tan bajos. Los resultados experimentales, debido a los equipos y el montaje experimental necesario, no son del todo fidedignos para voltajes menores que 0.25 V.

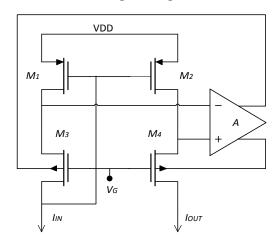

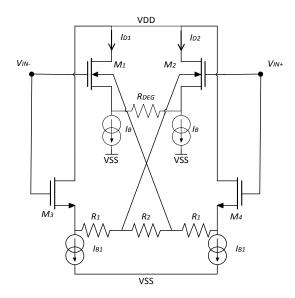

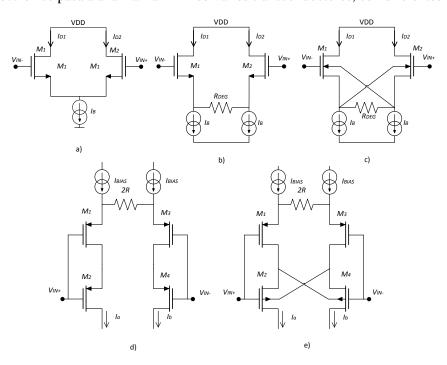

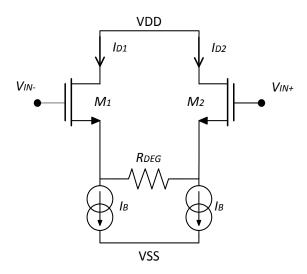

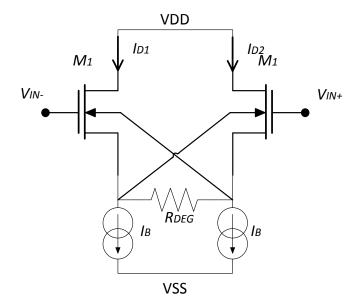

# 5.3.3 PAR DIFERNECIAL CON DEGENERACIÓN REISTIVA Y USO DE BULK

El transconductor a analizar se presenta en la figura 5.3.7. Este transconductor es similar al anterior, únicamente se le añade una conexión cruzada entre sus terminales de body, lo que produce una mejora en la distorsión armónica del OTA.

Figura 5.3.7. Par diferencial con degeneración de fuente y uso del terminal de bulk de forma activa.

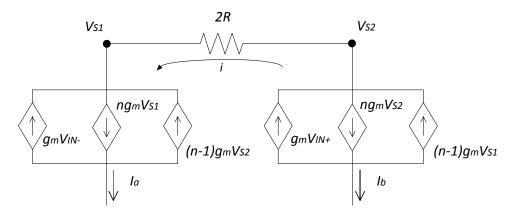

En análisis en pequeña señal de este transconductor no varía prácticamente con el análisis del transconductor con degeneración de fuente, pero si lo necesario para diferenciarlos:

Figura 5.3.8. Circuito equivalente en pequeña señal.

Debido a conexión cruzada de los terminales de bulk de ambos transistores, la fuente de corriente correspondiente a la transconductancia del bulk, esta vez está controlada por un voltaje diferente, lo que hace que resolviendo el circuito la tranconductacia efectiva de este es igual a:

$$g_m = \frac{g_{mg1}}{\left(1 + (2n - 1)g_{mg1}R\right)} \tag{5.3.16}$$

Debido a esta conexión se crea un factor en el denominador de 2n-1, sabiendo que n puede tomar valores entre 1.1 y 1.6, queda claro que la transconductancia efectiva total del dispositivo es menor que la transconductancia efectiva del transconductor con degeneración resistiva.

En este caso se volverán a utilizar los dos modelos para el cálculo del termino HD3, empezando por la ley cuadrática. Hay que tener en cuenta que el voltaje  $V_{GSI-2}$ , tiene ahora una dependencia del voltaje de umbral según lo expuesto en la ecuación 3.3. Por tanto la función implícita en este caso es de la siguiente forma:

$$V_{GS1} + \Delta V_{T01} - V_{GS2} - \Delta V_{T02} + V_B - V_{IN} = 0 (5.3.17)$$

Siendo:

$$\Delta V_{T01} = V_{T0} + \gamma \left( \sqrt{V_{SB1} + 2\varphi_F} - \sqrt{2\varphi_F} \right)$$

(5.3.18)

$$\Delta V_{T02} = V_{T0} + \gamma \left( \sqrt{V_{SB2} + 2\varphi_F} - \sqrt{2\varphi_F} \right) \tag{5.3.1}$$

Los voltajes  $V_{SB}$ , en este caso particular son el mismo que los voltajes en los bornes de la resistencia de degeneración, sabiendo que  $I_a=I_B+I_A$ , se puede expresar de la siguiente manera:

$$\Delta V_{T01} = V_{T0} + \gamma \left( \sqrt{(I_a - IB)R + 2\varphi_F} - \sqrt{2\varphi_F} \right)$$

(5.3.19)

$$\Delta V_{T02} = V_{T0} + \gamma \left( \sqrt{(IB - I_a)R + 2\varphi_F} - \sqrt{2\varphi_F} \right)$$

(5.3.20)

Sustituyendo estas expresiones y las correspondientes a los voltajes VGS1-2, se obtiene finalmente:

$$\sqrt{\frac{2I_a}{\beta}} - \sqrt{\frac{2(2IB - I_a)}{\beta}} + \gamma \sqrt{(I_a - IB)R + 2\varphi_F} - \gamma \sqrt{(IB - I_a)R + 2\varphi_F} + (I_a - IB) * R - V_{IN} = 0$$

(5.3.21)

Obtenida así la función implícita que describe el comportamiento de este transconductor se procede al cálculo de la distorsión armónica de tercer orden, y se obtiene la siguiente expresión:

$$HD3 = \frac{\left(\frac{3\sqrt{2}}{4\beta^{3} \left(\frac{IB}{\beta}\right)^{5/2}} + \frac{3R^{3}\gamma}{4(2\varphi)^{5/2}}\right)}{24\left(R + \frac{R\gamma}{\sqrt{2\varphi}} + \frac{\sqrt{2}}{\beta\sqrt{\frac{IB}{\beta}}}\right)^{3}} V_{IN}^{2}$$

(5.3.22)

A continuación se repiten los pasos para el *All Region Model*, obteniendo así la siguiente función implícita.

$$\sqrt{\frac{2I_a}{\beta}} - \sqrt{\frac{2(2IB - I_a)}{\beta}} + (2n - 1)(I_a - IB) * R - V_{IN} = 0$$

(5.3.23)

Como puede apreciarse se introduce el factor 2n-1, en la ecuación, que es similar a la ecuación (5.3.13). Obtenida así la ecuación implícita se pasa al cálculo de la distorsión armónica, obteniéndose la siguiente expresión, para el término de tercer orden:

$$HD3 = \frac{\sqrt{2}}{32\beta^3 \left(\frac{IB}{\beta}\right)^{5/2} \left(R(2n-1) + \frac{\sqrt{2}}{\beta\sqrt{\frac{IB}{\beta}}}\right)^3} V_{IN}^2$$

(5.3.24)

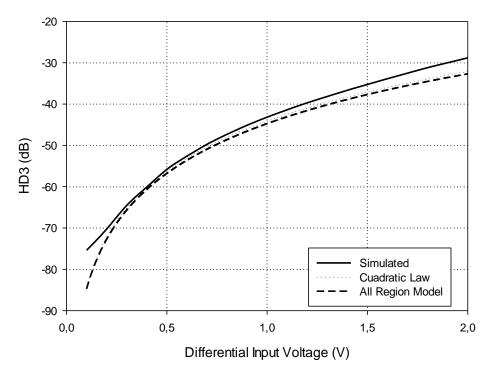

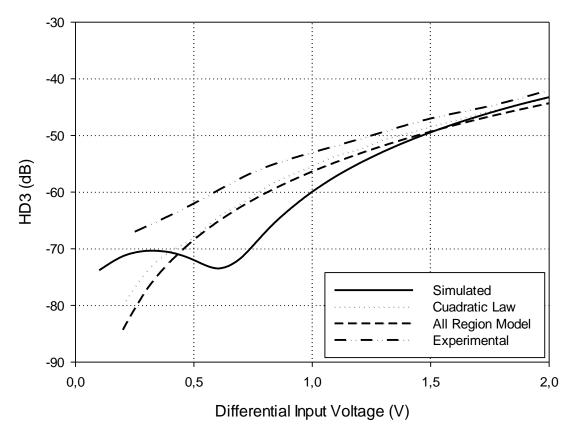

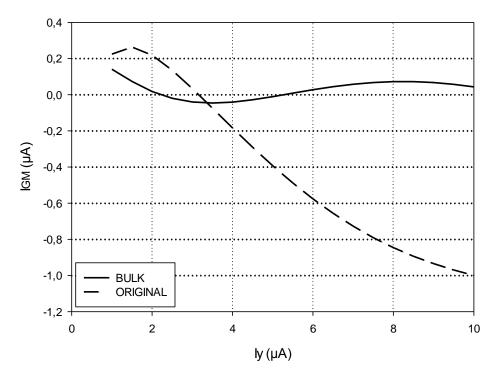

Una vez obtenidas las expresiones teóricas para la distorsión armónica de tercer orden, se pasa a graficar los resultados, comparando así los resultados teóricos frente a los obtenidos mediante simulación. Los parámetros utilizados para este transconductor son,  $\beta/2=15$   $\mu A/V$ ,  $W/L=15\mu m/1\mu m$ ,  $IB=20\mu m$ ,  $R=1K\Omega$  y n=1.15

Figura 5.3.9. HD3 para el transconductor con degeneración de fuente y uso de bulk de forma activa.

En la figura 5.3.9 se observa como los resultados teóricos se asemejan a los obtenidos mediante simulación. Entre los dos resultados obtenidos con los dos modelos, se aprecia una total concordancia, lo que pone de manifiesto la principal ventaja del All Region Model, ya que el análisis de este transconductor mediante este modelo es más sencillo que el análisis con la Ley Cuadrática.

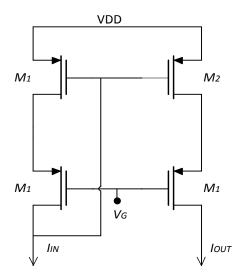

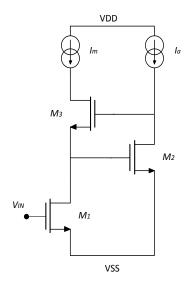

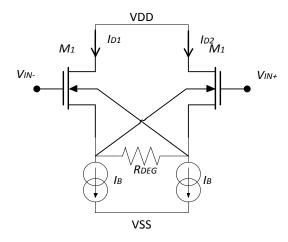

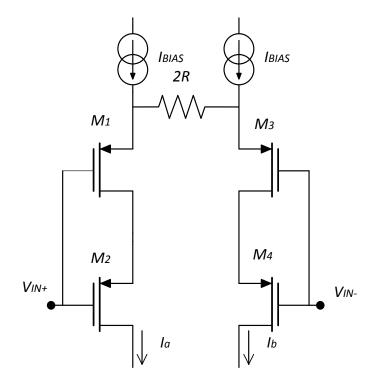

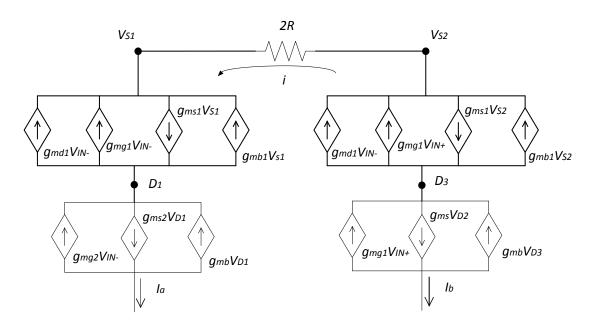

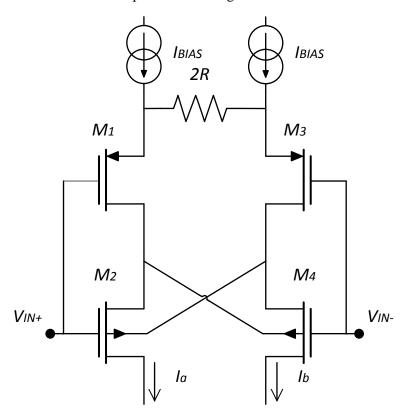

#### 5.3.4 CASCODE OTA

El OTA mostrado en la figura 5.3.10, es un transconductor que mejora las características del par diferencial con degeneración resistiva de fuente, utilizando dos transistores en cascodo [44]. En este caso los transistores  $M_1$  y  $M_3$  están operando en la región de triodo, mientras que los transistores  $M_2$  y  $M_4$  operan en la región de saturación. Cuenta con degeneración de fuente, lo que como en casos anteriores hace que gran parte de la respuesta del sistema recaiga sobre las propiedades lineales de la resistencia, dotando a este de una mejor respuesta.

Figura 5.3.10. Cascode OTA

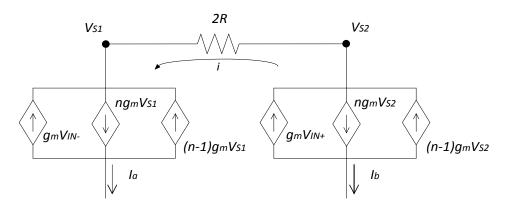

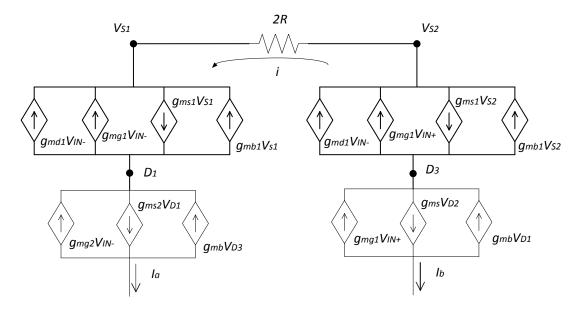

En primer lugar se procederá al análisis del circuito en pequeña señal, para el cálculo de su transconductancia. Para realizar este análisis se recurrirá al *All Region Model*, obtiene así el siguiente circuito equivalente:

Figura 5.3.11. Circuito equivalente en pequeña señal.

Notar que se ha asumido de nuevo que las dimensiones y características de los pares de transistores  $M_1$ - $M_3$  y  $M_2$ - $M_4$ , son idénticas, lo que significa que sus transconductancias respectivas son las mismas, lo que facilita el cálculo. Como puede observarse los transistores que operan en la región de triodo se describen mediante cuatro fuentes de corriente controladas por voltaje, siendo estos voltajes los correspondientes a los terminales del transistor. Para los

transistores en saturación, el circuito equivalente es idéntico a los presentados con anterioridad. Resolviendo el circuito se obtiene la siguiente transconductancia:

$$g_m = \frac{g_{mg2}(g_{md1} + g_{mg1})}{g_{md1} + g_{mg2}[1 + R(g_{ms1} - g_{mb1})]}$$

(5.3.25)

La transconductancia eficaz calculada es más difícil de interpretar que en casos anteriores ya que implica varias transconductancias, sin embargo si se considera que la resistencia de degeneración es mucho mayor que las otras transconductancias si se puede realizar la aproximación de que la transconductancia,  $gm\approx 1/R$ .

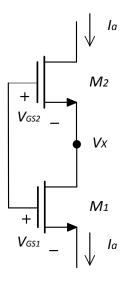

Una vez obtenida la transconductancia se pasa al análisis de distorsión. Al tener cuatro transistores en total, el análisis matemático de este circuito se complica, y más con transistores operando en ambas regiones, triodo y saturación. Sin embargo se puede conseguir una ecuación que defina la corriente que atraviesa dos transistores. Para ello se elige la dupla de transitores M<sub>1</sub> y M<sub>2</sub> (figura 5.3.12), por lo cuales pasa la misma corriente, *Ia*. El transistor M<sub>1</sub> opera en la región de triodo mientras que M<sub>2</sub> opera en la región de saturación.

Figura 5.3.12. Dos transistores en cascodo.

El voltaje  $V_X$ , es el mismo para el drenaje de  $M_1$  y para el terminal de fuente de  $M_2$ . Utilizando las ecuaciones que describen la corriente para un transistor operando en la región de saturación y para la región de triodo según la Ley Cuadrática:

$$I_a = \beta_1 \left( V_{IN} - V_S - V_T - \left( \frac{V_X}{2} \right) \right) V_X$$

(5.3.26)

$$I_a = \frac{\beta_2}{2} (V_{IN} - V_X - V_T)^2 \tag{5.3.27}$$

Despejando el valor de  $V_X$  de la ecuación (5.3.26), y sustituyéndolo en la ecuación (5.3.27), se obtiene la siguiente ecuación:

$$I_a = \frac{\beta_2 \beta_1}{2(\beta_2 + \beta_1)} (V_{IN} - V_S - V_T)^2$$

(5.3.28)

Utilizando el mismo método pero con las ecuaciones correspondientes al *All Region Model* se obtiene lo siguiente:

$$I_a = \frac{\beta_1}{2n} (V_{IN} - V_S - V_T)^2 - \frac{\beta_1}{2} (V_{IN} - (n-1)V_S - nV_X - V_T)^2$$

(5.3.29)

$$I_a = \frac{\beta_2}{2n} (V_{IN} - V_X - V_T)^2 \tag{5.3.30}$$

Realizando el mismo procedimiento que para la Ley Cuadrática se obtiene una única ecuación:

$$I_{a} = \frac{\beta_{2}n\left(\beta_{1}n - \beta_{1} + \sqrt{\frac{\beta_{1}(2\beta_{2} + \beta_{1} - \beta_{2})}{n}}\right)^{2}}{2(\beta_{2} + \beta_{1}n^{2})^{2}} (V_{IN} - V_{S} - V_{T})^{2}$$

(5.3.31)

De esta ecuaciones se deduce que la corriente que atraviesa dos transistores en cascodo, uno de ellos operando en saturación y otro de ellos en triodo, siguiendo la topología descrita en la figura 5.3.12, depende del voltaje aplicado a la puerta de estos, y del voltaje en el terminal de fuente del transistor  $M_1$ , y de una relación entre las dimensiones de ambos, es decir el voltaje  $V_X$  se fija para que  $V_{GS2}$  sea el necesario para que por el transistor  $M_2$  atraviese una corriente Ia, y para que a sus vez el voltaje en el drenaje de  $M_1$  sea el necesaria para que por este pase una corriente de Ia.

Mediante la descripción de la corriente que atraviesa dos transistores en cascodo, en una única ecuación, el análisis del OTA mostrado en la figura 5.3.10, se simplifica a la siguiente topología:

Figura 5.3.13. Circuito equivalente del Cascode OTA.

Es el mismo caso que para el par diferencial con degeneración de fuente, pero con un cambio, las dimensiones. En este caso ya no se trata de las dimensiones de un transistor sino del factor obtenido que relaciona las dimensiones de los transistores en cascodo, de esta manera se simplifica el cálculo sustancialmente, pudiendo utilizar el mismo procedimiento que el seguido para el par diferencial con degeneración de fuente de la figura 5.3.4. Notar que se evalúan las series en el punto  $V_{IN}$ =0, Ia=IB.

En primer lugar se obtiene la distorsión armónica de tercer orden con la Ley Cuadrática. Utilizando las ecuaciones descritas anteriormente. La expresión obtenida es:

$$HD3 = \frac{\sqrt{2}\beta}{32 \, IB\left(\sqrt{2} + R\beta\sqrt{\frac{IB}{\beta}}\right)^3} V_{IN}^2 \tag{5.3.32}$$

Siendo  $\beta$ :

$$\beta = \frac{\beta_2 \beta_1}{2(\beta_2 + \beta_1)} \tag{5.3.29}$$

Como cabe esperar es similar a la expresión obtenida para el par diferencial con degeneración de fuente, ya que el único cambio en el análisis son las  $\beta$ . Sin embargo es esta relación entre  $\beta$  de los transistores implicados, la que hace que la distorsión armónica de tercer orden disminuya.

Para el caso del *All Region Model*, la ecuación que se obtiene es la correspondiente a la obtenida en el caso del par diferencial con degeneración de fuente:

$$HD3 = \frac{\sqrt{2}\beta n^2}{32 \, IB\left(\sqrt{2}n + R\beta\sqrt{\frac{IB}{\beta}}\right)^3} V_{IN}^2 \tag{5.3.33}$$

Siendo  $\beta$ :