# ESCUELA TÉCNICA SUPERIOR DE INGENIEROS INDUSTRIALES Y DE TELECOMUNICACIÓN

Titulación:

INGENIERO DE TELECOMUNICACIÓN

Título del proyecto:

### DISEÑO DE CIRCUITOS CMOS DE ULTRA BAJO CONSUMO PARA ENERGY HARVESTING

AUTOR: Mª Pilar Garde Luque TUTOR: Antonio J. López Martín

Pamplona, 21 de Febrero de 2014

#### Agradecimientos

Aprovecho estas líneas para expresar mi agradecimiento a todos los que, de una forma u otra, han hecho posible la realización de este proyecto.

- En primer lugar me gustaría agradecer a mi tutor, Antonio López, por haberme ofrecido orientación durante este periodo de realización del proyecto, por haber estado siempre disponible y ayudarme cuando se presentaba algún problema.

- A mi familia, especialmente a mis padres y mi hermana, por el apoyo recibido no sólo durante el proyecto, sino a lo largo de toda la carrera.

- A Illya, por su paciencia y su palabras de ánimo cuando las necesitaba.

- A los compañeros de carrera, por haber hecho de estos años un período inolvidable.

- A las amigas, por haber sido mi vía de escape cuando necesitaba desconectar.

### Índice general

| 1. | MOTIV     | ACION Y OBJETIVOS                                  | 9  |

|----|-----------|----------------------------------------------------|----|

|    | 1.1. Ma   | rco del proyecto                                   | 9  |

|    | 1.2. Ob   | jetivos del proyecto                               | 10 |

| 2. | SISTEN    | MAS DE ENERGY HARVESTING                           | 13 |

|    | 2.1. Inta | roducción                                          | 13 |

|    | 2.2. Arc  | quitectura de un sistema de energy harvesting      | 14 |

|    | 2.2.1.    | Transductor de energía                             | 14 |

|    | 2.2.2.    | Convertidor de potencia                            | 16 |

|    | 2.2.3.    | Unidad de control                                  | 17 |

|    | 2.2.4.    | Buffer de energía                                  | 17 |

|    | 2.2.5.    | Regulador de tensión                               | 18 |

|    | 2.2.6.    | Unidad de aplicación                               | 18 |

| 3. |           | ITOS LÓGICOS DE ULTRA BAJO CONSUMO PARA SISTEMAS D |    |

| EN | NERGY F   | IARVESTING                                         | 21 |

|    | 3.1. Tra  | unsistor MOS de puerta cuasi-flotante (QFGMOS)     | 21 |

|    | 3.2. Pu   | erta NOT                                           | 25 |

|    | 3.2.1.    | Configuración básica                               | 25 |

|    | 3.2.2.    | Configuración basada en QFG                        | 26 |

|    | 3.2.3.    | Simulación y resultados                            | 28 |

|    | 3.2.4.    | Mediciones                                         | 30 |

|    | 3.2.1.    | Configuración básica                               | 32 |

|    | 3.2.2.    | Configuración basada en QFG                        | 33 |

|    | 3.2.3.    | Simulación y resultados                            | 34 |

|    | 3.3. Pu   | erta NOR                                           | 36 |

|    | 3.3.1.    | Configuración básica                               | 36 |

|    | 3.3.2.    | Configuración basada en QFG                        | 37 |

|    | 3.3.3.    | Simulación y resultados                        | 37 |

|----|-----------|------------------------------------------------|----|

| 3  | 3.4. Pu   | erta XOR                                       | 39 |

|    | 3.4.1.    | Configuración básica                           | 39 |

|    | 3.4.2.    | Configuración basada en QFG                    | 40 |

|    | 3.4.3.    | Configuración basada en QFG con Power On Reset | 40 |

|    | 3.4.4.    | Simulación y resultados                        | 42 |

| 3  | 3.5. DI   | Latch                                          | 44 |

|    | 3.5.1.    | Configuración básica                           | 45 |

|    | 3.5.2.    | Configuración basada en QFG                    | 46 |

|    | 3.5.3.    | Simulación y resultados                        | 46 |

| 3  | 3.6. Co   | nclusiones                                     | 48 |

| 4. | DISEÑ     | O DE LAZOS TRANSLINEALES DE BAJA TENSIÓN       | 49 |

| ۷  | 1.1. Inti | roducción                                      | 49 |

| ۷  | 1.2. Cir  | cuito de media geométrica                      | 51 |

|    | 4.2.1.    | Topología básica                               | 51 |

|    | 4.2.2.    | Topología FVF                                  | 53 |

|    | 4.2.3.    | Topología FVF mejorada                         | 54 |

|    | 4.2.4.    | Simulación y resultados                        | 55 |

| ۷  | 1.3. Cir  | cuito elevador al cuadrado                     | 58 |

|    | 4.3.1.    | Configuración básica                           | 59 |

|    | 4.3.2.    | Configuración FVF                              | 60 |

|    | 4.3.3.    | Configuración FVF mejorada                     | 60 |

|    | 4.3.4.    | Simulación y resultados                        | 61 |

| ۷  | 1.4. Mu   | ıltiplicador/divisor                           | 65 |

|    | 4.4.1.    | Configuración básica                           | 66 |

|    | 4.4.2.    | Configuración FVF                              | 67 |

|    | 4.4.3     | Configuración FVF meiorada                     | 67 |

|    | 4.4.4.      | Simulación y resultados                                | 68 |

|----|-------------|--------------------------------------------------------|----|

|    | 4.5. Cir    | cuito RMS-DC                                           | 72 |

|    | 4.5.1.      | Configuración básica                                   | 73 |

|    | 4.5.2.      | Configuración FVF                                      | 74 |

|    | 4.5.3.      | Configuración FVF mejorada                             | 74 |

|    | 4.5.4.      | Simulación y resultados                                | 75 |

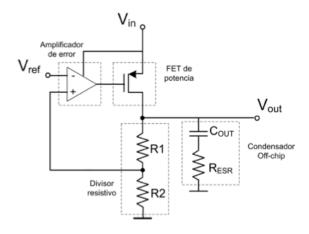

| 5. | REGULA      | ADOR DE TENSIÓN                                        | 79 |

|    | 5.1. Esqu   | ema básico del regulador lineal LDO                    | 80 |

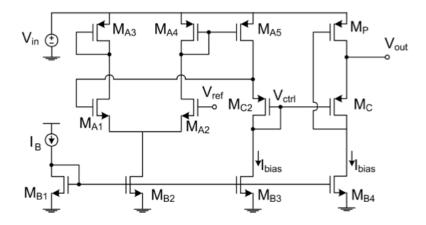

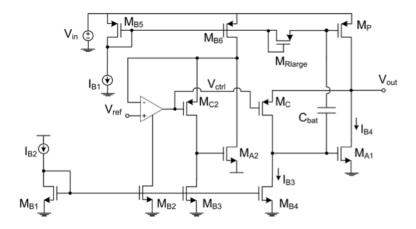

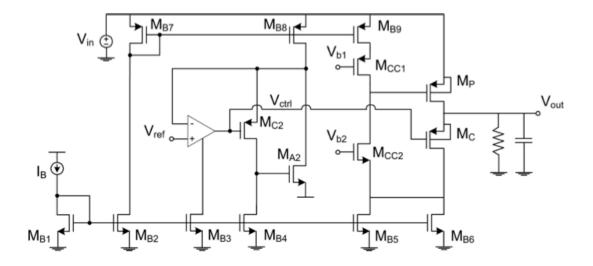

|    | 5.2. Singl  | le-Transistor-Control LDO basado en FVF                | 81 |

|    | 5.3. Regu   | lador de tensión LDO basado en SSF clase AB            | 82 |

|    | 5.4. Regu   | lador de tensión LDO basado en FVF clase A con cascodo | 83 |

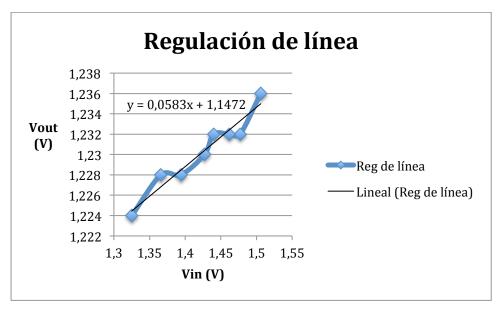

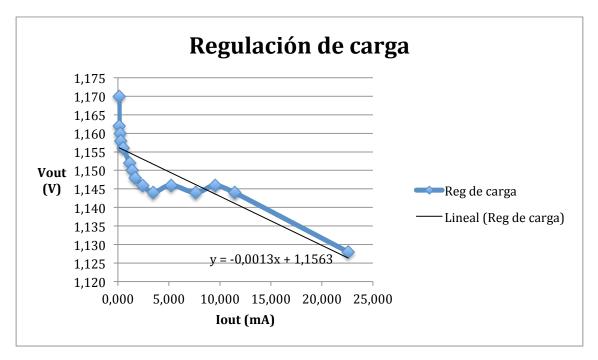

|    | 5.4.1. 1    | Mediciones                                             | 84 |

| 7. | CONCL       | USIONES Y LÍNEAS DE FUTURO                             | 91 |

|    | 7.1. Conc   | elusiones                                              | 91 |

|    | 7.2. Línea  | as futuras                                             | 92 |

| R  | ihlioorafía |                                                        | 93 |

#### 1. MOTIVACION Y OBJETIVOS

#### 1.1. Marco del proyecto

Las redes de sensores inalámbricas están logrando un desarrollo notable en multitud de aplicaciones, por lo que se prevé que sea una de las tecnologías de mayor desarrollo en los próximos años. En especial, su aplicación en entornos de Inteligencia Ambiental (*Ambient Intelligence*, AmI) es una de las más destacadas. Este término hace referencia a la perfecta integración de la tecnología en el entorno (hogar, automóvil, oficina, ecosistemas, etc.). Esto provoca que las inversiones de instituciones y capital privado sea cada vez mayor, generando así una gran expectativa. Sin embargo muchos escenarios AmI requieren una infinidad de nodos microsensores inalámbricos formando redes *ad hoc* para la captación, procesado, y transmisión de información. Esta visión no es energéticamente viable si no se logra una considerable reducción en el consumo de estos nodos. Para que el despliegue de estas redes de nodos alimentados por baterías sea factible, debería lograrse que estos microsensores fueran:

- 1) **Altamente integrados**. Una alta densidad de integración permite que el microsensor consista idealmente en un único encapsulado (conteniendo un chip simple o un módulo multi-chip) y el menor número de componentes externos posible, provocando que la manipulación de estos circuitos sea más sencilla.

- 2) Energéticamente eficientes. Una baja demanda energética implica que se pueda utilizar una batería más pequeña, que ésta no deba ser reemplazada e incluso que sea viable captar energía del entorno para complementar la energía proporcionada por la batería o incluso para sustituir la necesidad de tal batería.

Ambos factores permiten la reducción del tamaño del microsensor, de su coste y de su impacto medioambiental.

Un aspecto crítico en el diseño de microsensores inalámbricos y en el que se está investigando últimamente es la consecución de autonomía energética. Para lograrla, se

necesita avanzar en la electrónica utilizada para la captación, almacenamiento y gestión de la escasa energía disponible en el entorno, que complemente o sustituya a la energía aportada por una batería. Se está investigando activamente en la obtención de energía ambiental de tipo mecánico, electromagnético, solar y térmico. El elevado número de publicaciones recientes en el tema demuestra su relevancia e interés, y el intenso esfuerzo investigador que queda por hacer en este campo. Entre los objetivos más deseados se encuentran el desarrollo de sistemas electrónicos que permitan una mayor eficiencia en la captación de energía y al tiempo una mayor densidad de integración que minimice el tamaño del microsensor. Ambos aspectos están muy ligados ya que una mayor eficiencia permite reducir las dimensiones del transductor que capta energía (fotodiodo, acelerómetro, etc.)

Como se ha comentado, el proyecto pretende contribuir en esta línea mediante el desarrollo de circuitos microelectrónicos de alta eficiencia para la captación, almacenamiento y gestión de la energía disponible en el entorno.

#### 1.2. Objetivos del proyecto

Con este proyecto se pretende conseguir los siguientes objetivos:

- Revisión de conceptos básicos de microelectrónica analógica: operación del transistor CMOS, etapas básicas (par diferencial, espejo de corriente, etc), etc.

- Aprendizaje de construcción de puertas lógicas a partir de circuitos analógicos, en especial, a partir de transistores CMOS.

- Manejo de herramienta de diseño microelectrónico: entorno Cadence.

- Revisión bibliográfica de las principales técnicas existentes para la captación, almacenamiento y gestión de energía ambiental.

- Revisión bibliográfica de las técnicas existentes de diseño en baja tensión y bajo consumo, con énfasis en técnicas en puerta cuasi-flotante.

- Empleo de técnicas que permitan la reducción de las tensiones de alimentación y el consumo de un circuito para su aplicación en sistemas de energy harvesting. Para ello, se partirá de un análisis de las alternativas ya existentes en la literatura técnica. En especial, se estudiarán varias técnicas basadas en transistores QFGMOS.

- Estudio de topologías basadas en lazos translineales (circuitos de media geométrica, elevadores al cuadrado, conversores RMS-DC, etc.) y mediante la modificación de la topología básica, la mejora de varios parámetros, como son:

- Tensión de alimentación

- Ancho de banda, BW

- Precisión

- Linealidad (cuando se trate de circuitos de comportamiento lineal).

- Análisis comparativo de las prestaciones de las topologías propuestas mediante simulaciones.

- Mediciones experimentales de los circuitos una vez fabricados para la comprobación de los resultados simulados.

#### 2. SISTEMAS DE ENERGY HARVESTING

#### 2.1. Introducción

Los avances conseguidos en la fabricación de circuitos integrados han permitido la creación de sistemas microelectrónicos que realizan las funciones de sistemas discretos y además cuyas dimensiones se han reducido notablemente. Esto ha permitido acceder a nuevas áreas de trabajo donde el espacio es un factor limitante.

Anteriormente, las fuentes de alimentación empleadas para sistemas integrados se basaban en elementos de almacenamiento de energía (baterías). El problema es que este sistema presenta varios inconvenientes, como son:

- Estas baterías tienen un grado de integración escaso en los sistemas miniaturizados, lo que limita la capacidad energética y por tanto la vida útil de las baterías.

- En ocasiones, el acceso a los circuitos para reemplazar la batería es complicado e implica un gran coste si el proceso ha de repetirse periódicamente. Por ello, al aumentar el tiempo de vida del sistema, se reducen los costes a largo plazo.

- El uso de baterías es una de las principales fuentes de contaminación del medio ambiente. Al reducir su uso, se tiene un menor impacto medioambiental.

Para evitar todas estas desventajas, aparece la tecnología de "energy harvesting" o "energy scavenging", cuyo objetivo es la captación de energía del medio ambiente, su almacenamiento y gestión. Las principales razones por las que está teniendo tanto éxito son su utilidad en dispositivos portables (microsensores inalámbricos, sensores remotos o implantes biomédicos) en los que el coste o la dificultad de cambio de baterías son muy altos, o sistemas que requieren tamaños muy reducidos. Sin embargo, la reducción de tamaño y coste supone que el factor limitante sea la potencia que esta tecnología aporta al sistema.

Existen diversos orígenes de la energía captada del ambiente: calor, movimiento, luz, radiación electromagnética, etc. Sin embargo, este proceso sólo es útil cuando la energía generada por el transductor es mayor que el consumo del circuito de gestión de la energía del sistema. Por ello, no sólo hay que conseguir capturar la mayor cantidad de energía, sino también minimizar el consumo de estos circuitos, es decir, mejorar la eficiencia energética [1].

#### 2.2. Arquitectura de un sistema de energy harvesting

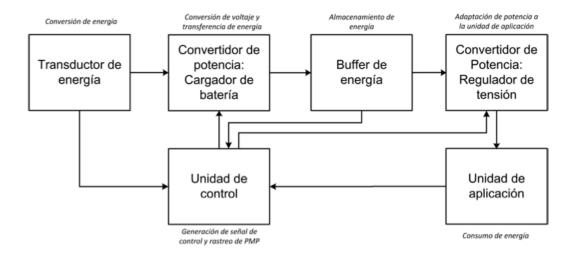

La figura 2.1 muestra los bloques que componen un sistema de energy harvesting, salvo alguna diferencia a nivel de arquitectura. A continuación se describirán los distintos bloques [2].

Fig. 2.1: Diagrama de bloques de un sistema de energy harvesting

#### 2.2.1. Transductor de energía

El transductor de energía es el encargado de la transformación de energía del ambiente en energía eléctrica. Como ya se ha mencionado antes, la energía tiene diferentes orígenes: radiación solar, corrientes de aire, movimientos mecánicos o vibraciones, gradientes térmicos, ondas radioeléctricas, etc. Todas estas fuentes tienen en común que se trata de fenómenos sin coste alguno, salvo los circuitos para la captación de energía.

Según las señales generadas, los transductores se clasifican en fuentes DC o AC. Las DC producen corriente y tensión continua (transductor fotovoltaico y termoeléctrico). Las fuentes AC, producen una señal alterna y oscilante con el tiempo (transductor piezoeléctrico y electromagnético). Además, la densidad de potencia depende del origen. La tabla 2.1 muestra valores de dicha densidad de potencia en función de su origen [3] [4].

| Fuentes de energía          | Densidad de potencia (μW/cm³)   |

|-----------------------------|---------------------------------|

| Solar (exterior)            | 150(nublado)-15000(luz directa) |

| Fotónica (interior)         | 6                               |

| Vibratoria (Piezoeléctrico) | 200                             |

| Dispositivos en zapatos     | 330                             |

| Térmica (ΔT=10°C)           | 15                              |

| Térmica (variación diaria)  | 10                              |

| RF (GSM)                    | 0,1                             |

| RF (WIFI)                   | 1                               |

|                             |                                 |

Tabla 2.1: Comparación de la densidad de potencia de distintos tipos de fuentes de energía

Como es de esperar, el transductor será diferente en función de dónde obtenga la energía. En el caso de obtención a partir de luz, se usa un transductor fotovoltaico. Si la energía se obtiene de la energía térmica, el transductor a utilizar es el termoeléctrico. Si la obtención se realiza a partir de movimientos vibratorios, existen tres tipos de transductores: electromagnético, electrostático y piezoeléctrico, siendo este último el más recomendado para su uso en energy harvesting, por ser fácilmente integrable y no necesitar sistema de arranque. Por último, si la energía se obtiene de ondas electromagnéticas, se utiliza un transductor electromagnético (consiste en una antena, una red de adaptación y un rectificador AC/DC).

Las fuentes DC, es decir, los transductores fotovoltaico y termoeléctrico, tienen en común que incorporan esquemas de rastreo del punto de máxima potencia, PMP, para asegurar la máxima potencia de salida.

#### 2.2.2. Convertidor de potencia

El convertidor de potencia acondiciona la potencia de salida del transductor para lograr así transferir la máxima potencia al resto del sistema. La energía que el transductor proporciona al sistema no está acondicionada, sino que:

- Su tensión de salida no está regulada y no se puede emplear para alimentar circuitos eléctricos directamente.

- Puede que no proporcionen una potencia continua e ininterrumpida.

- Normalmente generan una potencia media muy baja (10µW-10mW)

Por ello, se introduce el convertidor de potencia, que hace de administrador. Como se ha comentado antes, las fuentes de energía pueden proporcionar corriente continua o alterna, y según la aplicación a utilizar, hay que acondicionar esta corriente. Principalmente, hay dos formas de modificar las propiedades de la potencia obtenida: rectificadores AC/DC y convertidores DC/DC. Además, al usarse estos circuitos en energy harvesting, nos interesa que su consumo sea mínimo.

En caso de usar transductores de energía vibratoria o electromagnéticos, la corriente obtenida es una señal AC, y dado que la mayoría de aplicaciones necesita un suministro de potencia DC, se necesitan rectificadores AC/DC. En cuanto a rectificadores, interesa que sean de onda completa, para aprovechar mejor la potencia. La configuración más básica para conseguir este tipo de rectificador es el puente de diodos, pero no es la más conveniente, por necesitar un mínimo nivel de tensión de entrada, que en ocasiones no se alcanza. Por ello, posteriormente se han probado otras alternativas, como el uso de diodos Schottky (por tener una menor tensión umbral), diodos activos formados por un transistor PMOS y un comparador (no es adecuado, por la necesidad de un sistema de arranque), sistemas híbridos con un rectificador pasivo hasta alcanzar una tensión que permitía que el rectificador activo se activara o como se verá en este proyecto, el uso de tecnología de puerta flotante para construir conversores RMS-DC.

Por el contrario, si la señal obtenida es DC, la tensión puede no ser lo suficientemente alta para poder alimentar la aplicación. Para aumentar la tensión, se utilizan convertidores DC/DC. Existen dos tipos: electrostáticos, que usan condensadores para

almacenar la energía y acondicionar la potencia; y magnéticos, que usan condensadores para almacenar y bobinas para transferir la energía.

#### 2.2.3. Unidad de control

La unidad de control es la encargada de reducir las pérdidas de potencia del sistema y maximizar la eficiencia energética. Para conseguirlo, mide la potencia captada del transductor, el estado del buffer de energía y los requisitos de la unidad de aplicación, y con ello realiza cambios en los convertidores de potencia. En otras palabras, es el bloque que asegura el punto de máxima potencia (PMP) en todo momento, mediante esquemas de rastreo de PMP. Este esquema de rastreo debe tener un consumo lo más bajo posible. Existen varios esquemas de rastreo PMP, como son: Design Time Componente Matching (DTCM), Reference Voltage Tracking, Hill-Climbing (también llamado Perturb and Observe o "P y O"), y MPP Tracking for Hybrid Transducters.

Además, la unidad de control puede realizar otras operaciones como crear señales de reloj o la activación y desactivación de interruptores dentro del sistema de energy harvesting. Pero a mayor complejidad, mayor consumo de la unidad de control, es decir, mayores pérdidas de potencia.

#### 2.2.4. Buffer de energía

En él, se almacena la energía eléctrica generada. Existen dos posibles opciones para este almacenamiento: baterías o condensadores electroquímicos de doble capa (supercondensadores).

Las baterías tienen mayor densidad de energía (mayor capacidad para un volumen/peso dado) que los supercondensadores. Sin embargo, los supercondensadores tienen mayor densidad de potencia y se han utilizado para manejar picos de potencia de corta duración. Se ha estudiado su uso para el almacenamiento de energía, por ser mas eficiente y tener una vida útil más larga, sin embargo sufren corrientes de leakage, lo que los excluye para su uso en almacenamiento de energía a largo tiempo. También es posible el uso de ambas opciones simultáneamente, pero presenta el inconveniente del

decremento de eficiencia del sistema de captación de energía por necesitar más potencia para la administración del mecanismo de almacenamiento.

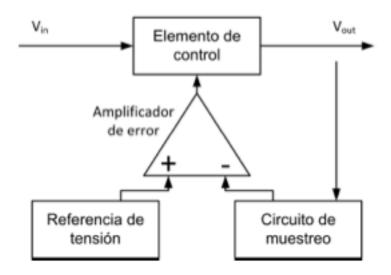

#### 2.2.5. Regulador de tensión

El regulador de tensión tiene como objetivo suministrar la potencia regulada a la unidad de aplicación. Este circuito mantiene una tensión constante a la salida para distintas resistencias de carga. Este bloque se utiliza muy frecuentemente, por la necesidad de suministrar una tensión constante como es la tensión de alimentación  $V_{DD}$  de muchos circuitos. Para ello, se parte de una tensión superior a la tensión a obtener. Esta diferencia se conoce como voltaje dropout. Si este voltaje dropout es muy bajo, el regulador se denomina LDO (Low Drop-Out regulator).

Su uso se ve justificado por las múltiples ventajas que presenta:

- Proporcionan una tensión constante para un amplio rango de resistencias de carga, y además no suponen una gran caída de tensión.

- Protegen a la unidad de aplicación frente a la descarga del buffer de energía (aunque disminuya la tensión de la batería o supercondensador, la tensión en su salida no varía)

- Presentan mucho menos ruido en la señal generada comparados con otros convertidores DC/DC y una gran eficiencia energética si el dropout se mantiene bajo.

#### 2.2.6. Unidad de aplicación

La unidad de aplicación puede estar formada por cualquier dispositivo que no necesite una gran potencia de alimentación (por ejemplo, sensores). Es necesario que este bloque haga un uso eficiente de la energía proveniente del sistema de energy harvesting. El caso ideal sería aquel en el que la aplicación sea capaz de funcionar completamente desconectado del sistema de captación de energía ambiental.

Para conseguir tal objetivo, se han estudiado varias técnicas. Todas se basan en intentar adaptar el rendimiento y el consumo de potencia de la aplicación a las variaciones del sistema de energy harvesting.

## 3. CIRCUITOS LÓGICOS DE ULTRA BAJO CONSUMO PARA SISTEMAS DE ENERGY HARVESTING

Como se ha descrito en el capítulo anterior, los sistemas de Energy Harvesting requieren circuitos de muy baja tensión de alimentación y muy bajo consumo, dada la naturaleza de las fuentes que generan energía. En este capítulo se propone una familia lógica adaptada a estas características.

Una puerta lógica es un dispositivo electrónico que implementa una función booleana. Es decir, las señales utilizadas se representan como "0" y "1", aunque en realidad se trate de tensiones eléctricas. Existen varios tipos de puertas lógicas, dependiendo de la función que realicen. Estas puertas se agrupan en familias lógicas, cada una con sus características distintivas. La familia lógica más empleada en la actualidad es la CMOS, debido a su muy bajo consumo estático y su adaptabilidad a las tecnologías convencionales.

En los siguientes párrafos se propone el empleo de transistores de puerta cuasi-flotante (QFGMOS) para disminuir la tensión de alimentación necesaria en las puertas lógicas CMOS. De esta forma se genera una nueva familia de puertas lógicas, que se denominará lógica QFGMOS. En concreto, se abordará el diseño de cuatro puertas lógicas: NOT, NAND, NOR y XOR.

#### 3.1. Transistor MOS de puerta cuasi-flotante (QFGMOS)

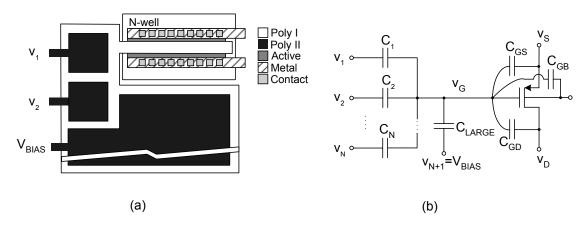

La figura 3.1 muestra el layout de un transistor PMOS de puerta flotante convencional de tres entradas en tecnología n-well, así como su circuito equivalente para el caso general de N+l entradas, incluidas las capacidades parásitas.

Fig. 3.1: Transistor PMOS de puerta flotante con múltiples entradas (MIFGT)

(a) Layout (b) Circuito equivalente

Como los terminales de entrada están capacitivamente acoplados a la puerta del transistor, si asumimos que la carga inicial atrapada es nula, la tensión de puerta  $V_G$  vendrá dada por

$$v_G = \frac{1}{C_T} \left( \sum_{k=1}^{N+1} C_k v_k + C_{GS} v_S + C_{GD} v_D + C_{GB} v_B \right)$$

(3.1)

donde  $C_k$  es la capacidad de acoplo de la k-ésima rama de entrada. La capacidad total vendrá dada por:

$$C_T = \sum_{k=1}^{N+1} C_k + C_{GS} + C_{GD} + C_{GB}$$

(3.2)

Un requisito en aplicaciones de muy baja tensión de alimentación es mantener la tensión en DC de la puerta flotante cercana a una de las dos tensiones de alimentación. Esta tensión debe ser cercana a  $V_{DD}$  si el transistor es PMOS y próxima a  $V_{SS}$  si se trata de un transistor NMOS. Para ello, la entrada  $V_{n+1}$  en la figura anterior se fija a una tensión de polarización  $V_{bias}$  adecuada, y el valor  $C_{LARGE}$  escogido para el condensador de acoplo correspondiente es mucho mayor que el resto. Así pues, podemos reescribir la ecuación (3.1) como

$$v_{G} = \frac{C_{LARGE}}{C_{T}} V_{BLAS} + \frac{1}{C_{T}} \left( \sum_{k=1}^{N} C_{k} v_{k} + C_{GS} v_{S} + C_{GD} v_{D} + C_{GB} v_{B} \right)$$

(3.3)

Sin embargo, esta topología tiene varios inconvenientes. El primero de ellos, inherente a los transistores de puerta flotante, es la necesidad de eliminar la carga atrapada en el terminal de puerta. La solución a este problema es relativamente sencilla, ya que la carga puede ser anulada bien con un simple borrador de memorias EPROM, o bien colocando varios niveles de contactos de metal sobre los terminales de las puertas flotantes, que descarguen la puerta en la deposición de las capas de metal, pero que la dejen otra vez flotante tras el proceso de "etching" de modo que al final del proceso de fabricación la puerta queda flotante y sin carga almacenada. Los otros dos inconvenientes están relacionados con las dimensiones del transistor  $C_{LARGE}$ :

- Por una parte, el área de silicio requerida aumentará de manera considerable, tal y como puede observarse en el layout de la figura anterior.

- Por otra parte, si el transistor forma parte del par diferencial de entrada de un amplificador, el gran tamaño del condensador  $C_{LARGE}$  contribuirá a una reducción considerable del *producto ganancia por ancho de banda (GBW)*.

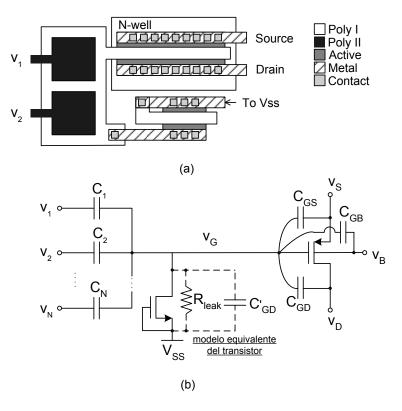

Estos dos problemas pueden ser solucionados sustituyendo el condensador  $C_{LARGE}$  por una resistencia de valor muy alto. El resultado será un transistor de puerta cuasiflotante (QFGT: Quasi-Floating Gate Transistor), cuyo circuito equivalente se muestra en la figura siguiente junto a su layout.

Los dos terminales de entrada están capacitivamente acoplados a la puerta cuasiflotante, pero la tensión en DC queda determinada por la tensión aplicada en el terminal de la resistencia, en este caso  $V_{SS}$ , sin necesidad de utilizar un condensador de gran tamaño. Esta resistencia de valor muy alto, se puede implementar mediante un transistor MOS operando en la región de corte, lo cual puede conseguirse cortocircuitando los terminales de puerta y fuente, siendo necesaria una superficie de silicio mucho menor que la ocupada por el condensador  $C_{LARGE}$ .

Fig. 3.2: Transistor pMOS de puerta cuasi-flotante (a) Layout (b) Circuito equivalente

Si analizamos la nueva configuración, obtenemos que la tensión de puerta vendrá dada por

$$V_{G} = \frac{sR_{leak}}{1 + sR_{leak}C_{T}} \left( \sum_{k=1}^{N} C_{k}V_{k} + C_{GS}V_{S} + C_{GD}V_{D} + C_{GB}V_{B} \right)$$

(3.4)

donde la capacidad total  $C_T$  será

$$C_T = \sum_{k=1}^{N} C_k + C_{GS} + C_{GD} + C_{GB} + C'_{GD}$$

(3.5)

En la ecuación (3.4) se observa que las entradas son sometidas a un filtrado paso alto con una frecuencia de corte  $I/(2\pi R_{leak}C_T)$ , la cual puede tomar valores muy bajos. Así pues, se produce una suma ponderada de las entradas determinada por las relaciones entre capacidades, más algunos términos parásitos, incluso para señales de muy baja frecuencia. Cabe destacar que el valor exacto de  $R_{leak}$  así como su dependencia con la tensión y con la temperatura no son factores importantes, puesto que la resistencia es lo suficientemente grande como para que la frecuencia de corte no se acerque nunca a la

frecuencia mínima a la que va a funcionar el circuito. Por este mismo motivo el valor exacto de  $C_T$  tampoco es relevante.

En este circuito la resistencia  $R_{leak}$  establece en la puerta del transistor una tensión igual a la tensión de alimentación negativa, y sobre ésta se superpone la tensión AC producida por el resto de entradas. De este modo, la tensión en la puerta puede ser menor que la alimentación negativa, lo cual es bastante común cuando el circuito está alimentado con tensiones inferiores a 1 V. Esto no supondrá ningún problema siempre y cuando  $V_G$  exceda a  $V_{SS}$  en un voltaje menor del que provoca que la unión p-n entre el sustrato y el drenador del transistor que implementa  $R_{leak}$  empiece a conducir. Este problema, que no existe si se trata de un amplificador realimentado, se puede evitar si se tiene en consideración a la hora de escoger las relaciones entre los condensadores a los que se acoplan las distintas entradas.

#### 3.2. Puerta NOT

#### 3.2.1. Configuración básica

La puerta lógica NOT realiza la inversión de la entrada. Su tabla de verdad se muestra en la tabla 3.1:.

| A | Ā |

|---|---|

| 0 | 1 |

| 1 | 0 |

Tabla 3.1: Tabla de verdad de la puerta NOT

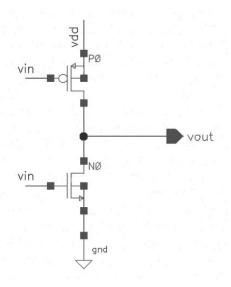

Se puede construir esta puerta con dos transistores, un NMOS y un PMOS, unidos por el drenador, tal y como muestra la figura 3.3. Cuando  $V_{in}=V_{DD}$ , el PMOS entra en corte, mientras que el NMOS está en saturación, por lo que la tensión de salida es nula. En el caso contrario, en el que  $V_{in}=0V$ , ocurre justo lo contrario, es decir, el NMOS entra en corte y el PMOS en saturación, con lo que la salida tendría una tensión de  $V_{DD}$ .

La mínima tensión de alimentación para la que este circuito trabaja de forma correcta es de aproximadamente  $V_{DD}=0^{\circ}7V$ . Esta tensión viene justificada a partir de las tensiones umbral de ambos transistores, que para el caso del transistor PMOS es  $V_{TP}\approx$ -0°95V y para el NMOS,  $V_{TN}\approx$ 0°65V.

Fig. 3.3: Circuito puerta NOT

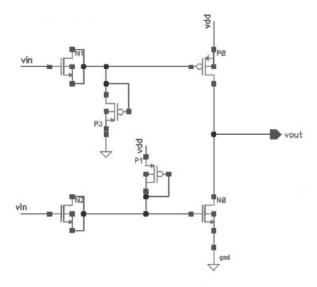

#### 3.2.2. Configuración basada en QFG

Una posible solución para disminuir la tensión de alimentación sería la técnica QFG antes descrita. Consiste en utilizar transistores de puerta cuasi-flotantes en el inversor, que se componen de transistores cuya puerta se conecta a la entrada mediante un condensador, y a su vez a cierta tensión de polarización (dependiendo del tipo de transistor) mediante una resistencia de valor muy alto. Al utilizar esta configuración, cada transistor consigue en su puerta un valor en DC, proveniente de la polarización a la que está conectada la resistencia, y un valor en AC proveniente de la señal de entrada. Así, al independizar la polarización de los transistores de la señal AC, se consigue operar con menores tensiones de alimentación. El circuito de estudio se muestra en la figura 3.4.

Fig. 3.4: Circuito puerta NOT con QFG

Cabe destacar que se han sustituido las resistencias de valores altos por transistores tipo P en corte y en configuración diodo (presentan mayor resistencia que los tipo N) y los condensadores por transistores tipo N cuyos drenadores y fuentes están conectados, actuando así como un capacitor.

Las dimensiones de los transistores que simulan los condensadores, se han calculado de forma que su capacitancia sea de en torno a los 150 fF. Para ello, hemos tomado una relación  $W/L = 36\mu m/3\mu m$ .

Sobre las dimensiones de los transistores en configuración diodo (es decir, los equivalentes a las resistencias de alto valor) hemos elegido una relación W/L=18µm/600nm, ya que nos interesa W y L mínimas. Dado que estamos trabajando con tecnologías de 0'6µm, éste es el valor mínimo posible para L. Acerca de W, debemos llegar a un compromiso entre el valor de la resistencia y el tamaño, dado que no nos interesa que el área del circuito sea muy grande.

Además, tenemos que tener en cuenta que los transistores que forman la puerta NOT (el tipo N y el tipo P) deben tener dimensiones distintas, ya que la transconductancia de estos dispositivos no es la misma. Para que suministren la misma corriente al estar activos, el tamaño del transistor PMOS debe ser unas tres veces el tamaño del NMOS. Por ello,  $W_{PMOS} \approx 3 \cdot W_{NMOS}$ , mientras que el parámetro L queda idéntico. Para ser más exactos,  $W_{PMOS}/L_{PMOS}=18 \mu m/0'6 \mu m$ , mientras que  $W_{NMOS}/L_{NMOS}=6 \mu m/0'6 \mu m$ .

A continuación, pasamos a analizar el modo de funcionamiento de esta puerta NOT con puerta cuasi-flotante.

Si la entrada es nula, la puerta del PMOS tendría una tensión nula, y la del NMOS tendría una tensión  $V_{DD}$ , porque visto desde los nodos  $V_{DD}$  y GND existe un filtro RC paso bajo, que sólo deja pasar las tensiones DC.

Pero si se conecta una señal que oscile entre 0 y  $V_{DD}$  V, ocurre algo totalmente distinto. Esta señal se puede descomponer como una componente en DC de valor  $V_{DD}/2$ , y otra componente en AC que fluctúa entre  $-V_{DD}/2$  y  $V_{DD}/2$ . En este caso, existe un filtro RC

paso alto entre la entrada y las puertas de los transistores, por lo que la componente DC no pasa, pero sí la componente AC.

Sabiendo esto, podemos calcular el rango de valores que tomará las tensiones en las puertas de ambos transistores. En el caso del PMOS, existe la componente AC, que oscila entre  $-V_{DD}/2$  y  $V_{DD}/2$  y la componente DC de valor nulo, por lo tanto, el voltaje en la puerta del PMOS estará en el rango  $[-V_{DD}/2, V_{DD}/2]$ . Por el contrario, en el caso del NMOS, tenemos la misma componente AC, pero la de DC tiene un valor  $V_{DD}$ , por lo que su valor oscila entre  $[V_{DD}/2, 3V_{DD}/2]$ .

Con esta mejora, se consigue disminuir la tensión mínima de alimentación, a cambio de tener mayor área del circuito, ya que tanto la resistencia de valor grande como el condensador se pueden construir mediante transistores, por lo que pasamos de tener 2 transistores en la configuración básica a tener 6 en la basada en la tecnología QFG.

#### 3.2.3. Simulación y resultados

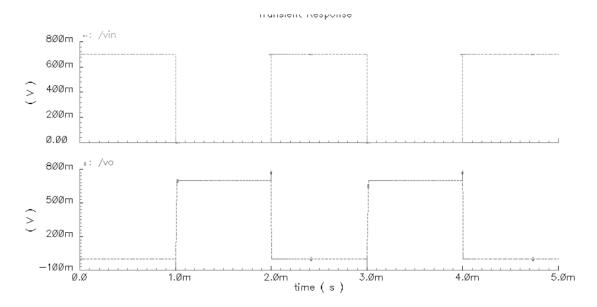

El objetivo de este proyecto es alcanzar la menor tensión de alimentación posible, con vistas a la aplicación en sistemas de Energy Harvesting. Con la simulación de ambos circuitos, la puerta NOT básica y la basada en puerta cuasi-flotante (o QFG) comprobamos que en el caso básico la tensión de alimentación mínima es algo superior al caso de la configuración QFG.

Para ello, llevamos a cabo análisis de tipo *transitorio*, es decir, realizamos simulaciones en el tiempo. Para ello, definimos la señal de entrada de la puerta como una señal cuadrada y periódica cuyo periodo es de 2ms. Tomamos el tiempo total de simulación como 5ms, para poder observar varios periodos.

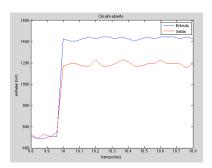

La figura 3.5 muestra las señales de entrada y salida de la configuración básica de la puerta NOT. Antes de llegar a esta gráfica, hemos realizado un análisis paramétrico para comprobar la tensión mínima de alimentación a la que la puerta trabaja correctamente. La conclusión a la que llegamos con dicho análisis paramétrico es que la tensión mínima de alimentación es  $V_{DD}=0.7V$ .

Fig. 3.5: Tensiones de la puerta NOT

Por otro lado, realizamos los mismos análisis con la puerta NOT basada en la tecnología QFG. Se muestra una simulación en la figura 3.6. Gracias al análisis paramétrico, comprobamos que la tensión mínima de alimentación es  $V_{DD}$ =0'5V, con lo que conseguimos disminuir este parámetro en 0'2V respecto al circuito básico.

Fig. 3.6: Tensiones de la puerta NOT con QFG

#### 3.2.4. Mediciones

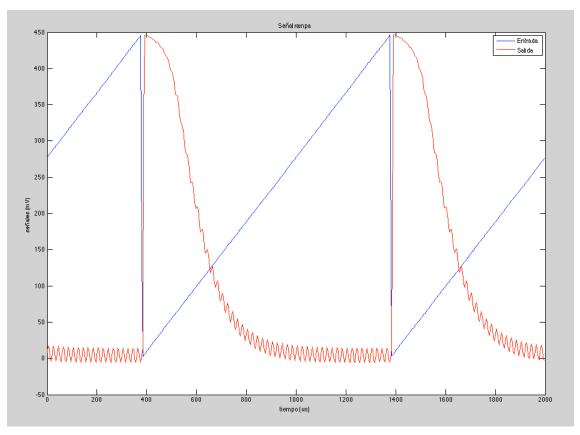

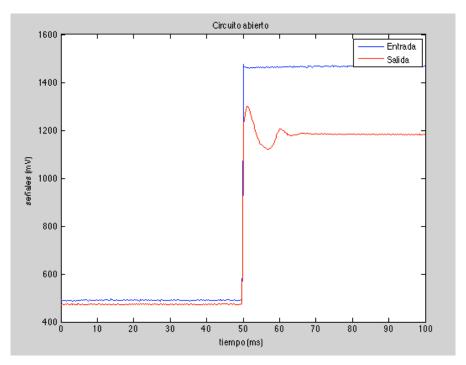

A partir del circuito ya fabricado en la tecnología CMOS empleada en las simulaciones, pasamos a tomar medidas, o mejor dicho, a comprobar el correcto funcionamiento del inversor. Para ello, introduciremos dos señales de entrada, con frecuencia muy baja (f=1Hz). Estas señales son una rampa periódica y una señal cuadrada periódica, ambas oscilantes entre  $V_{SS}$  y  $V_{DD}$ .

Partimos del hecho de que  $V_{SS}$  en nuestro caso es 0V, y a continuación comprobaremos cuál es la tensión mínima de alimentación  $V_{DD}$  a la que el circuito funciona correctamente.

Al introducir la rampa, mediante el osciloscopio, somos capaces de observar la figura 3.7.

Fig. 3.7: Respuesta del inversor QFG cuando la señal de entrada es una rampa periódica de f=1Hz y  $V_{DD}{=}450 mV$

La respuesta era la prevista, dado que comenzando la rampa en V<sub>SS</sub>=0V y aumentando progresivamente la tensión de entrada, debe realizarse una conmutación que concluya con un cambio del "1" lógico al "0". Al realizarse este cambio paulatinamente, también la transición se realiza lentamente. La medida realizada permite obtener una aproximación de la característica de transferencia en DC de la puerta NOT, que se correspondería a un periodo de la señal de salida. Se emplea para ello una tensión de entrada en rampa periódica de muy baja frecuencia y no una señal en DC dado que los circuitos QFG no operan en DC. Se puede apreciar en la característica de transferencia un comportamiento correcto para tensiones de alimentación de 450mV.

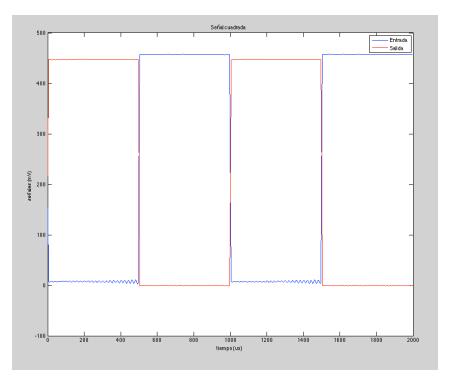

La siguiente medida consistió en obtener la salida de la puerta NOT a una señal cuadrada periódica. De esta forma se puede observar claramente el comportamiento transitorio de la misma. La Figura 3.8 muestra el resultado. Se ha empleado una señal de entrada de tan solo 1kHz debido a que el terminal de salida del inversor está conectado directamente al pad del chip, y por tanto su capacidad de carga es la capacidad parásita de este pad. Esto limita significativamente la frecuencia máxima que se puede aplicar.

Fig. 3.8: Respuesta del inversor QFG cuando la señal de entrada es una señal cuadrada periódica de f=1Hz y  $V_{\text{DD}}$ =450mV

Como era de esperar, el funcionamiento de la puerta NOT con QFG es el deseado para una tensión mínima de alimentación de  $V_{DD}$ =450mV. Se observa que el nivel en alto de la señal de salida es ligeramente inferior al de la señal de entrada. Esto puede deberse a la pequeña caída de tensión  $V_{DS}$  del transistor PMOS de salida para estas tensiones de alimentación tan bajas.

#### 3.3. Puerta NAND

#### 3.2.1. Configuración básica

En la figura 3.9 se presenta el circuito equivalente a la puerta lógica NAND. Está compuesto por dos transistores NMOS y otros dos PMOS, siendo los primeros los dos transistores inferiores y los segundos, los superiores. Para excitar esta puerta, se necesitan dos señales de entrada, que llamaremos A y B. Al haber 4 transistores, se les

Fig. 3.9: Circuito puerta NAND

aplica en sus correspondientes puertas estas señales. Cada una de las entradas excita a un transistor NMOS y a otro PMOS.

En el caso en que ambas entradas, A y B, sean nulas, conseguimos que los dos PMOS, P0 y P1, se encuentren en saturación, es decir, se pueden considerar como un circuito cerrado. De esta forma, conseguimos que  $V_{\rm OUT}$  esté conectado a la tensión de alimentación  $V_{\rm DD}$ .

En el caso en que una entrada sea nula y la otra sea "1" (o en nuestro caso cierta tensión, que tomaremos como  $V_{DD}$ ), sólo un PMOS y un NMOS conducen, consiguiendo así que  $V_{OUT}$  siga siendo  $V_{DD}$ , por estar uno de los NMOS en corte (es decir, en circuito abierto).

Por último, cuando ambas entradas, A y B, están activas, los dos PMOS se encuentran en corte y los dos NMOS en conducción. En consecuencia, la tensión de salida  $V_{OUT}$  será GND, es decir, la salida será nula.

En resumen, con este circuito conseguimos satisfacer la tabla de verdad de la puerta NAND, que se presenta en la tabla 3.2.

| A | В | $V_{OUT}$ |

|---|---|-----------|

| 0 | 0 | 1         |

| 0 | 1 | 1         |

| 1 | 0 | 1         |

| 1 | 1 | 0         |

Tabla 3.2: Tabla de verdad puerta NAND

#### 3.2.2. Configuración basada en QFG

Como en el caso de la puerta NOT, se trata de completar el circuito básico de la puerta NAND con la tecnología QFG, que consistía en colocar un condensador entre la señal de entrada y la puerta de cada transistor, y además una resistencia de alto valor entre la puerta y una tensión de alimentación, ya fuera GND para el caso de los PMOS o  $V_{DD}$  para el caso de los NMOS. Así, obtenemos el circuito mostrado en la figura 3.10.

Fig. 3.10: Circuito puerta NAND con QFG

La justificación por la que se obtienen tensiones superiores en las puertas de cada transistor es equivalente a la explicada en el caso de la puerta NOT. Recordemos que se debe a la descomposición de la señal de excitación (señal oscilante entre 0V y  $V_{DD}$  V) en dos señales, una DC de valor  $V_{DD}/2$  y otra AC que oscila entre  $-V_{DD}/2$  y  $V_{DD}/2$ .

Los tamaños de los transistores utilizados, tantos los equivalentes a los condensadores, como los transistores en configuración diodo (equivalentes a las resistencias) como los propios transistores que constituyen la puerta NAND, son los mismos que en el caso de la puerta NOT.

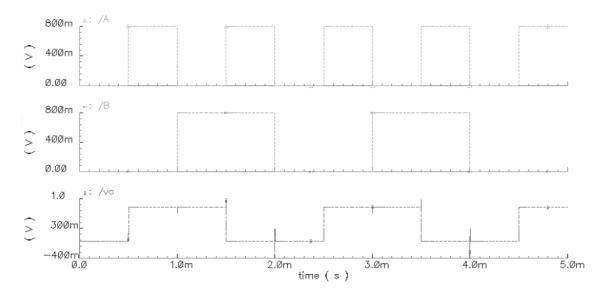

#### 3.2.3. Simulación y resultados

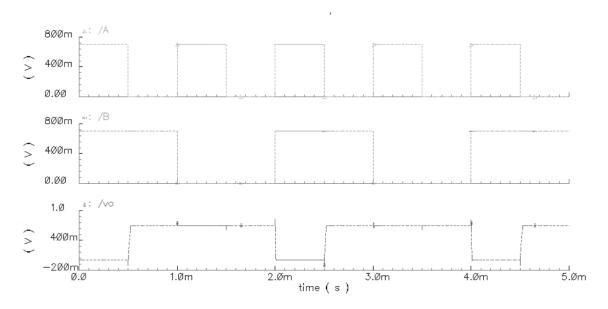

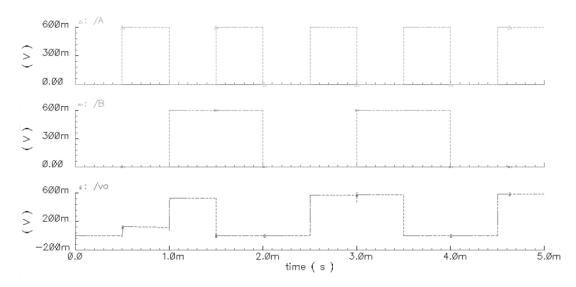

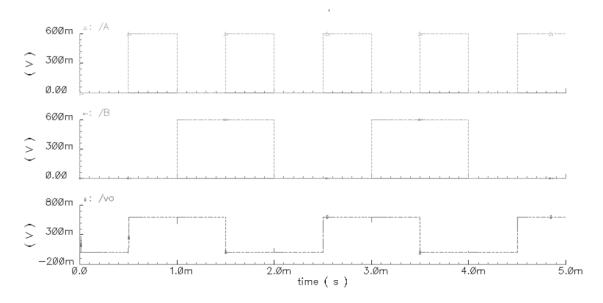

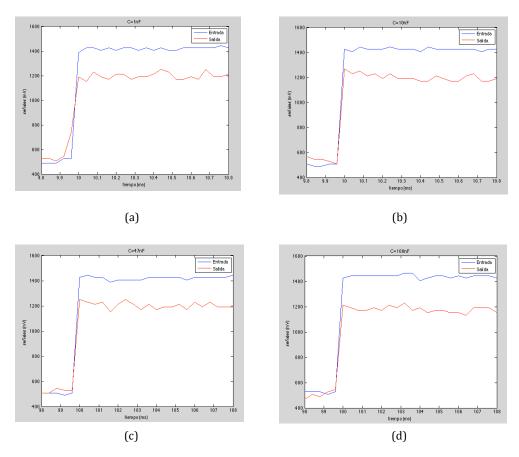

Al igual que en la simulación de la puerta NOT, se realizan análisis paramétricos para averiguar el valor de  $V_{DD}$  mínimo para el correcto funcionamiento de la puerta NAND, tanto en su configuración básica como en la basada en puerta cuasi-flotante (QFG).

Tras este análisis, y para justificar la correcta operación de las puertas, se establece como tensión de alimentación los valores obtenidos en los análisis paramétricos correspondientes.

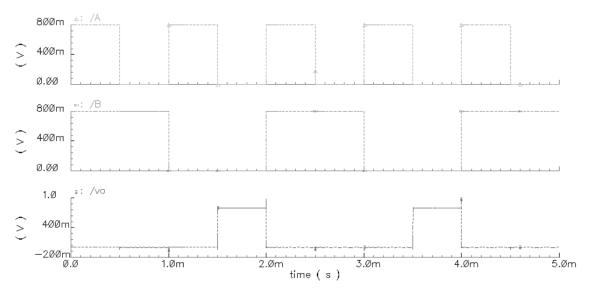

Como se puede comprobar, para la versión básica de la puerta NAND, la tensión mínima de alimentación es  $V_{DD}=0.7V$ , mientras que para el caso QFG,  $V_{DD}=0.6V$ .

Fig. 3.11: Tensiones de la puerta NAND

Fig. 3.12: Tensiones de la puerta NAND con QFG

Así, podemos concluir que hemos conseguido disminuir la tensión de alimentación mínima en 0'1V gracias a la configuración de puerta cuasi-flotante.

#### 3.3. Puerta NOR

#### 3.3.1. Configuración básica

La tabla de verdad de la puerta NOR se presenta en la tabla 3.3.

| A | В | $V_{OUT}$ |

|---|---|-----------|

| 0 | 0 | 1         |

| 0 | 1 | 0         |

| 1 | 0 | 0         |

| 1 | 1 | 0         |

Tabla 3.3: Tabla de verdad de la puerta NOR

Para que un circuito verifique esta tabla, necesitamos que la salida esté activa sólo cuando sus dos entradas sean nulas. Esto se consigue conectando dos transistores PMOS en serie, conectados a la tensión de alimentación superior, es decir, V<sub>DD</sub>. Para que la salida sea nula con cualquier otra combinación de entradas, conectamos dos transistores NMOS en paralelo, de forma que siempre que una de las dos entradas esté activa, se consiga una tensión de salida nula. Con todo esto, obtenemos el circuito mostrado en la figura 3.13, muy similar al anterior de la puerta NAND.

Fig. 3.13: Circuito puerta NOR

Cuando ambas entradas, A y B, son nulas, los PMOS están activos, pudiéndose considerar como corto circuitos. Se obtiene así una salida activa.

En cualquier otro caso, uno de los NMOS estará activo, conectándose así la salida a GND, por lo que la salida será nula.

# 3.3.2. Configuración basada en QFG

Partiendo del esquema básico, introducimos ciertas modificaciones para conseguir así la configuración de puerta cuasi-flotante, obteniendo el circuito mostrado en la figura 3.14.

Fig. 3.14: Circuito puerta NOR con QFG

Al igual que en las puertas anteriores, hemos mantenido el tamaño de los transistores.

# 3.3.3. Simulación y resultados

En la figura 3.15, vemos representada la evolución temporal de una puerta NOR básica cuando las señales de excitación son dos señales de periodo 1ms y 1'5ms respectivamente. Observamos que la tensión mínima de alimentación es de  $V_{DD}$ =0'8V.

Fig. 3.15: Tensiones de la puerta NOR

Sin embargo, cuando modificamos el circuito para transformarlo en uno de puerta cuasiflotante, esta alimentación disminuye a  $V_{DD}$ =0'6V, consiguiendo así una mejora de 0'2V.

Fig. 3.16: Tensiones de la puerta NOR con QFG

# 3.4. Puerta XOR

## 3.4.1. Configuración básica

La puerta XOR tiene sus salidas activas siempre y cuando las señales de entrada sean distintas, es decir, cuando A=0 y B=1 ó cuando A=1 y B=0. Cuando las entradas son iguales, la salida es nula. Estos casos se ven definidos en su tabla de verdad (tabla 3.4).

| A | В | $V_{OUT}$ |

|---|---|-----------|

| 0 | 0 | 0         |

| 0 | 1 | 1         |

| 1 | 0 | 1         |

| 1 | 1 | 0         |

Tabla 3.4: Tabla de verdad de la puerta XOR

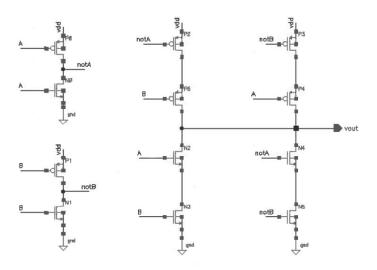

Para conseguir verificar esta tabla, la salida está conectada a cuatro ramas cuyas entradas son las cuatro posibles combinaciones entre A y B y sus correspondientes negaciones. Como la salida debe estar activa para los casos en que las entradas sean distintas, las ramas cuyas entradas son opuestas son las que se conectan a la tensión de alimentación superior, V<sub>DD</sub>, mientras que las dos ramas con entradas iguales están conectadas a GND. Esto puede verse con claridad en el circuito de la figura 3.17. Destacamos también la inclusión de dos circuitos equivalentes a la puerta NOT para negar ambas entradas. Además, las ramas superiores están constituidas por transistores PMOS, mientras que las inferiores por transistores NMOS.

Fig. 3.17: Circuito puerta XOR

Acerca de las dimensiones de los transistores, seguimos usando las empleadas en circuitos anteriores.

# 3.4.2. Configuración basada en QFG

Al introducir la mejora de puerta cuasi-flotante en el circuito anterior, el circuito pasa de utilizar 12 transistores a utilizar 36, por lo que el área a la hora de fabricar el circuito integrado aumentará considerablemente.

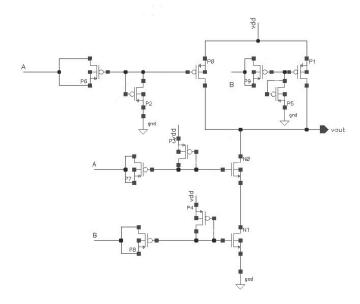

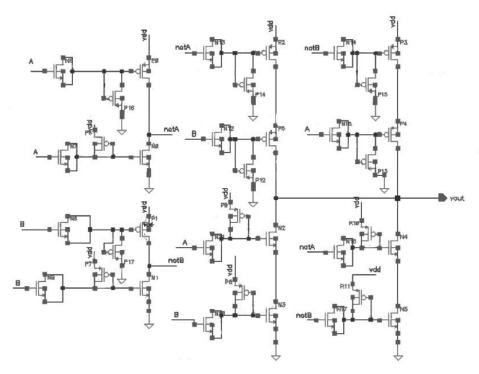

Tras modificar el circuito el resultado es el mostrado en la figura 3.18.

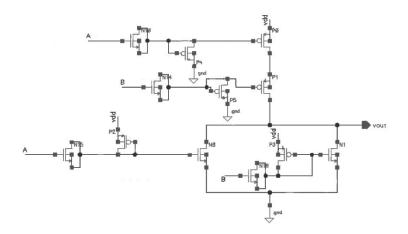

Fig. 3.18: Circuito puerta XOR con QFG

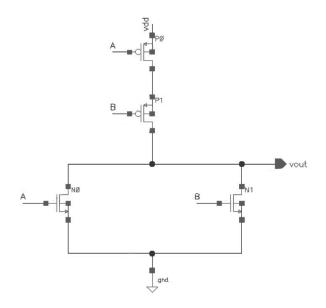

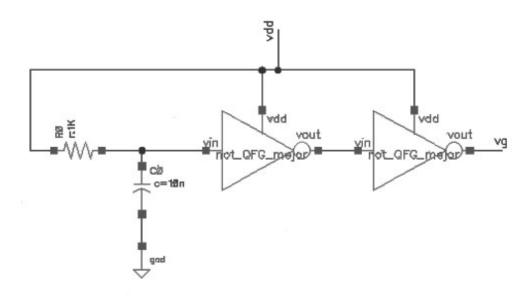

# 3.4.3. Configuración basada en QFG con Power On Reset

Como se podrá comprobar con posterioridad en el apartado de simulación y resultados, la puerta XOR con puertas cuasi-flotantes presenta un fallo en los primeros ciclos, debido a que debe transcurrir un tiempo de estabilización del circuito. Para solucionar

este problema, se añade al circuito una etapa de Power On Reset (POR), tal y como se muestra en la figura 3.19.

Fig. 3.19: Circuito Power On Reset

Si se cumple la condición  $R_{ON} \cdot C_b \le R \cdot C$ , siendo  $R_{ON}$  la resistencia del transistor que simula la resistencia de alto valor cuando  $v_G = 0V$ , y R y C la resistencia y condensador del circuito de POR, el circuito QFG se carga de manera correcta. Esto se consigue gracias a que el condensador C se va cargando con una constante de tiempo  $\tau \approx RC$ , en la que alcanza una tensión de  $v_1 \approx 0,63 V_{DD}$ . Como  $v_1$  es la señal de entrada al primer inversor, al alcanzar la tensión umbral del inversor, conseguimos que la salida del primer inversor cambie a 0V, y por tanto, la salida del segundo inversor,  $v_G$ , estará a nivel alto. Esta conversión tiene lugar al transcurrir un tiempo aproximado de  $t_0 \approx 0.8 RC$ . Además, la señal  $v_1$  habrá alcanzado el valor  $V_{DD}$  en aproximadamente  $t \approx 3RC$ .

Este circuito de Power On Reset debe conectarse a las puertas de los transistores que simulan las resistencias de alto valor, sustituyendo la configuración diodo que teníamos anteriormente. Esto puede observarse en la figura 3.20, donde también puede apreciarse que la fuente de dichos transistores está conectada a una tensión  $V_{\text{bias}}$ , que se fijará al mismo valor de la tensión  $V_{\text{DD}}$ , para conseguir que al funcionar las ramas inferiores (transistores NMOS) se alcance  $v_{\text{OUT}}$ = $V_{\text{DD}}$ .

Fig. 3.20: Circuito puerta XOR con QFG y PoR

# 3.4.4. Simulación y resultados

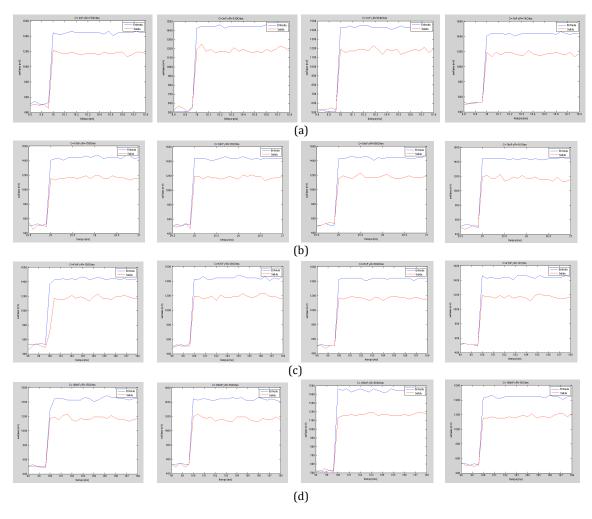

Llevamos a cabo análisis paramétricos para determinar la tensión mínima de alimentación de ambas puertas (básica y con puerta cuasi-flotante).

Como se ve en la figura 3.21, la tensión de alimentación para la configuración básica es de  $V_{DD}$ =0'8V. Además, comprobamos que su funcionamiento es el correcto, ya que cumple la tabla de verdad de la puerta XOR.

Fig. 3.21: Tensiones de la puerta XOR

Con la configuración QFG, vemos que también verifica la tabla de verdad de la puerta XOR, excepto en el segundo pulso de la secuencia simulada. Esto se debe a cierto tiempo de estabilización del circuito. Una vez transcurrido este tiempo, el circuito se comporta correctamente. Además, la tensión de alimentación se ha disminuido a  $V_{\rm DD}$ =0'6V, consiguiendo una mejora de 0'2V respecto a la configuración básica.

Fig. 3.22: Tensiones de la puerta XOR con QFG

Como ya se ha mencionado anteriormente, en el segundo ciclo, se observa que  $v_{OUT}$  no alcanza la tensión  $V_{DD}$ . Para solucionarlo, añadimos un circuito de Power On Reset (PoR), con el que conseguimos que la salida en este ciclo sí alcance la tensión de alimentación  $V_{DD}$ . Para ello, establecemos unos valores de  $R=1K\Omega$  y C=1nF. Cabe destacar que el añadir este circuito no supone un aumento en la tensión de alimentación, por lo tanto, seguimos obteniendo la mejora anteriormente conseguida.

Fig. 3.23: Tensiones de la puerta XOR con QFG y PoR

#### 3.5. **D** Latch

Aparte de la lógica combinacional descrita en párrafos anteriores, es preciso de circuitos secuenciales en la implementación de sistemas digitales. Uno de los elementos secuenciales básicos es el latch. Un latch es un circuito electrónico capaz de almacenar información en sistemas lógicos. En concreto, puede guardar un bit, aunque existen otros tipos de latches como los quad o los octal, capaces de almacenar 4 y 8 bits respectivamente. Existen latches asíncronos (es decir, sin entrada de reloj) o síncronos. En este caso, se simulará un latch síncrono, ya que sí utilizaremos una señal de reloj que hace que el estado del circuito cambie.

En particular, el latch de tipo D, o D latch, cumple la tabla de verdad establecida en la tabla 3.5.

| CLK | D | S | R | Q(t+1)                    |

|-----|---|---|---|---------------------------|

| 0   | 0 | 0 | 0 | Sin cambio                |

| 0   | 1 | 0 | 0 | Sin cambio                |

| 1   | 0 | 0 | 1 | <i>Q</i> =0: <i>Reset</i> |

| 1   | 1 | 1 | 0 | Q=1: Set                  |

Tabla 3.5: Tabla de verdad del D latch

Como se puede observar, el latch incorpora funciones de Reset y Set.

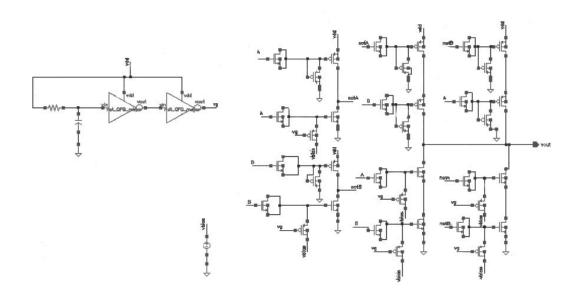

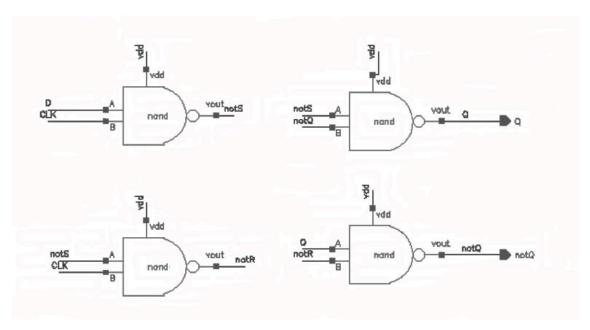

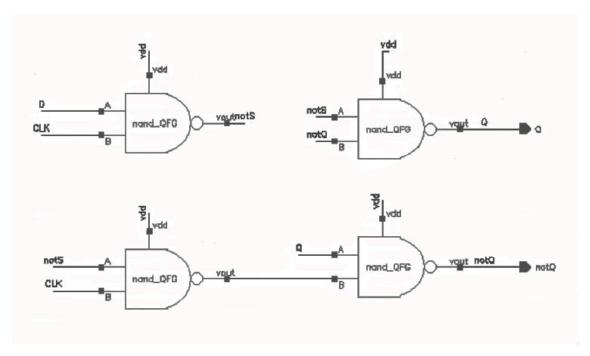

El D Latch está constituido por puertas NAND. Con anterioridad, se han estudiado dos tipos de puertas NAND, una en configuración básica y otra con puerta cuasi-flotante. Ayudándonos de estas puertas, simularemos las mismas versiones del D Latch para establecer en qué grado se consigue una mejora.

#### 3.5.1. Configuración básica

Como ya se ha mencionado anteriormente, el D latch se construye con puertas NAND, tal y como muestra la figura 3.24.

Fig. 3.24: Circuito D latch

La función de almacenamiento de un bit de este latch se consigue con una realimentación, ya que el estado de la salida es esencial para el cálculo del estado siguiente.

Cabe destacar que las puertas NAND no pueden introducir mucho retardo con respecto al periodo de la señal de entrada, ya que se crearían falsos estados en el circuito, dando origen a fallos no sólo en la señal de salida de ese instante sino también en los siguientes instantes, por depender la salida de los anteriores instantes.

# 3.5.2. Configuración basada en QFG

Gracias a las puertas NAND con puerta cuasi-flotante, podemos construir un D latch basado en la tecnología QFG. Como se puede ver en la figura 3.25, el circuito es igual al anterior, sólo que esta vez en vez de usar las puertas NAND básicas, se han utilizado las QFG.

Fig. 3.25: Circuito D latch con QFG

#### 3.5.3. Simulación y resultados

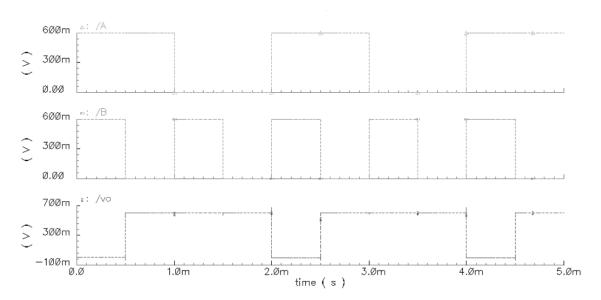

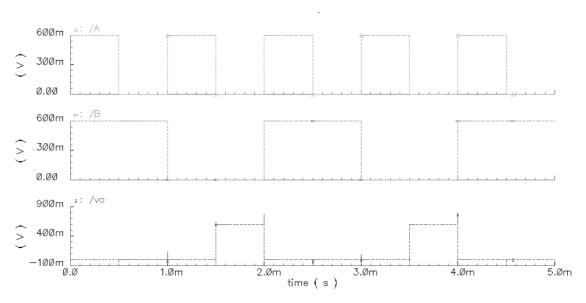

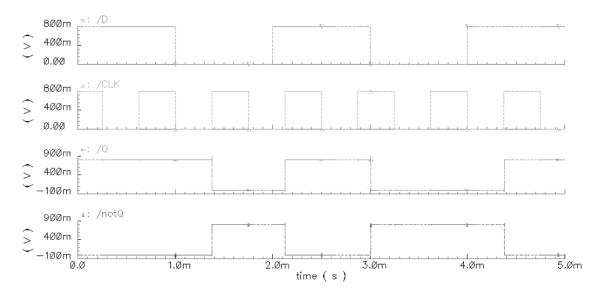

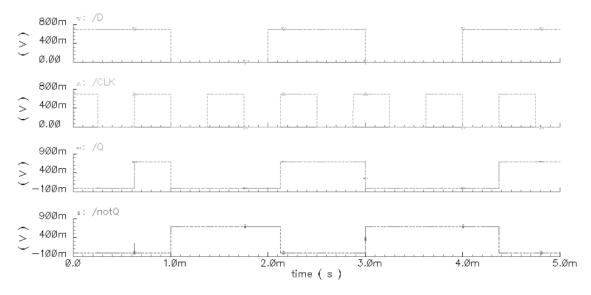

Se han establecido las señales de entrada, D y CLK, como señales cuadradas periódicas con distinto periodo. En particular, D tiene un periodo de  $T_D=2$ ms, y el reloj CLK tiene un periodo de  $T_{CLK}=0.75$ ms.

En la figura 3.26, vemos la simulación del circuito básico de D Latch. Comprobamos su correcto funcionamiento y determinamos que la tensión mínima de alimentación es de  $V_{DD}$ =0'8V.

Fig. 3.26: Tensiones del D latch

A continuación, en la figura 3.27, vemos la simulación de la versión de puerta cuasiflotante. Al no poder definir condiciones iniciales a la hora de simular, existe al igual que en el caso de la puerta XOR, un cierto tiempo en el que el circuito necesita estabilizarse. Por eso, durante los primeros pulsos no se verifica la tabla de verdad, lo que se soluciona al transcurrir cierto tiempo. Se observa que la tensión mínima de alimentación para este circuito es de VDD=0'7V.

Fig. 3.27: Tensiones del D latch con QFG

#### 3.6. Conclusiones

Tras el estudio de estos cinco circuitos con sus correspondientes mejoras, recopilamos la información importante de todos ellos en la tabla 3.6. En ella se observa la tensión mínima de alimentación de todos los circuitos, además de la mejora conseguida con la tecnología QFG.

|         | CONF. BÁSICA | CONF. QFG | $MEJORA\ V_{DD}$ | MEJORA % |

|---------|--------------|-----------|------------------|----------|

| NOT     | 0'7V         | 0'5V      | 0'2V             | 28.6%    |

| NAND    | 0'7V         | 0'6V      | 0' $1V$          | 14.3%    |

| NOR     | 0'8 $V$      | 0'6V      | 0.2V             | 25%      |

| XOR     | 0'8V         | 0'6V      | 0.2V             | 25%      |

| D LATCH | 0'8V         | 0'7V      | 0'1V             | 12.5%    |

Tabla 3.6: Recopilación de datos

Puede parecer que la complejidad de los circuitos no merezca la pena para una mejora de la tensión mínima de alimentación de en torno a 0'1V, pero tengamos en cuenta que esta tensión se obtiene de la energía ambiental, luego es imprescindible disminuir esta tensión al mínimo posible.

Recordar también que en ciertos circuitos de puerta cuasi-flotante debe transcurrir un tiempo hasta que el circuito sea totalmente estable. El circuito de Power on Reset propuesto permite disminuir este tiempo.

En definitiva: con la tecnología de puerta cuasi-flotante conseguimos una disminución en la tensión de alimentación mínima, a pesar de que el circuito está constituido por el triple de transistores que la configuración básica. Esto se debe a la mayor tensión en las puertas de los transistores gracias al acoplo capacitivo de la señal de entrada.

# 4. DISEÑO DE LAZOS TRANSLINEALES DE BAJA TENSIÓN

Otro elemento muy útil en procesado analógico son los lazos translineales. Estos circuitos permiten implementar funciones analógicas no lineales como la conversión RMS-DC, la elevación al cuadrado, la media geométrica, multiplicación y división, etc. Pueden ser de utilidad en sistemas de Energy Harvesting para aplicaciones tales como la detección de un determinado nivel de señal. Sin embargo, para ello es preciso emplear topologías que requieran baja tensión de alimentación. En este capítulo se exploran varias posibilidades en este sentido.

#### 4.1. Introducción

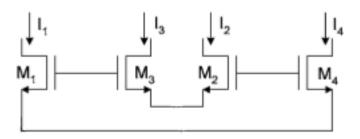

Se denomina lazo translineal a un lazo cerrado de transistores con un número par de uniones puerta fuente (o base emisor en el caso de transistores bipolares), donde la mitad está conectado en sentido de las agujas del reloj, y la otra mitad en sentido contrario. Se muestra un ejemplo en la figura 4.1.

Fig. 4.1: Esquema de un lazo translineal

Aplicando leyes de Kirchoff en el lazo, obtenemos una igualdad entre la suma de subidas y bajadas de tensión, es decir:

$$V_{GS1} + V_{GS2} = V_{GS3} + V_{GS4} (4.1)$$

Dado que en función del régimen de operación de los transistores conocemos las expresiones de la corriente que los atraviesa en función del voltaje  $V_{GS}$ , aparecen dos tipos de funcionamiento de este circuito.

# • Inversión fuerte y saturación

Cuando los transistores trabajan en este régimen, la expresión que define la corriente que circula a través de ellos es:

$$I_D = \frac{\mu . C_{OX}}{2} \left( \frac{W}{L} \right) (V_{GS} - V_{TH})^2 \tag{4.2}$$

donde la constante  $\mu$ . $C_{OX}$  puede renombrarse como  $K_n$ , W/L hace referencia a las dimensiones del transistor, y  $V_{TH}$  es el voltaje umbral del transistor.

Despejando V<sub>GS</sub> de esta ecuación 4.2 llegamos a

$$V_{GS} = \sqrt{\frac{2I_D}{K_n(\frac{W}{L})}} + V_{TH} \tag{4.3}$$

Suponiendo que tomamos W/L y  $V_{TH}$  iguales, podemos concluir, partiendo de la ecuación 4.1 y sustituyendo  $V_{GS}$  por la expresión 4.3, que

$$\sqrt{I_1} + \sqrt{I_2} = \sqrt{I_3} + \sqrt{I_4} \tag{4.4}$$

# Inversión débil y saturación

Si los transistores operan en inversión débil y saturación, la expresión que rige el comportamiento de la corriente que los atraviesa es:

$$I_D = I_0 e^{\frac{V_{GS}}{nV_t}} \tag{4.5}$$

donde n es el factor de pendiente y  $V_t$  es el voltaje térmico, que se define como  $V_t = \frac{kT}{q}$ , con k la constante de Boltzman, T la temperatura (en grados Kelvin) y q la carga del electrón.

Si despejamos de la expresión V<sub>GS</sub>, llegamos a

$$V_{GS} = nV_t ln\left(\frac{l_D}{l_0}\right) \tag{4.6}$$

A través de la fórmula que rige los lazos translineales (ecuación 4.1) y sustituyendo  $V_{GS}$  la expresión superior (ecuación 4.6), obtenemos que

$$I_1.I_2 = I_3.I_4 \tag{4.7}$$

Si trabajamos en condiciones de inversión fuerte y saturación, y a la vez forzamos ciertas condiciones (igualdad de corrientes mediante espejos de corrientes), podemos obtener topologías muy interesantes para las funciones que nos atañen en este proyecto. A continuación se explican varias.

# 4.2. Circuito de media geométrica

## 4.2.1. Topología básica

Si imponemos que las corrientes I<sub>3</sub> e I<sub>4</sub> sean iguales y de valor

$$I_3 = I_4 = \frac{I_1 + I_2 + 2I_{out}}{4} \tag{4.8}$$

e introducimos esta expresión en la fórmula que define el comportamiento de los lazos translineales cuando operan en inversión fuerte y saturación, obtendremos la siguiente fórmula

$$I_{out} = \sqrt{I_1 I_2} \tag{4.9}$$

A esta expresión se le puede añadir un factor de escala si las dimensiones de los transistores M<sub>3</sub> y M<sub>4</sub> no fueran iguales a las de M<sub>1</sub> y M<sub>2</sub>. En este caso, como tomamos los cuatro transistores iguales, este factor de escala no aparece.

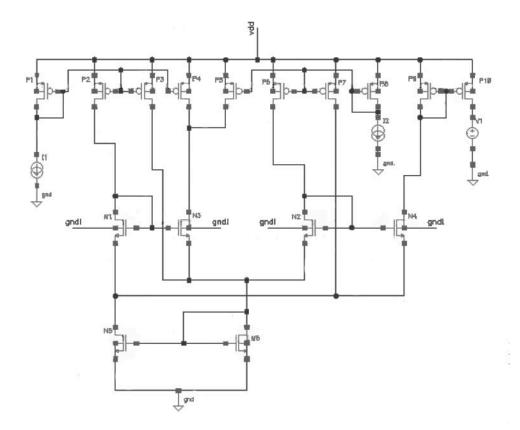

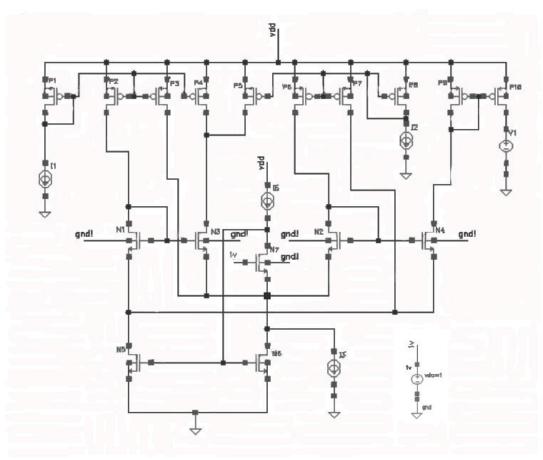

Para forzar que las corrientes I<sub>3</sub> e I<sub>4</sub> sean del valor mencionado anteriormente utilizamos espejos de corriente para obtener copias de I<sub>1</sub>, I<sub>2</sub> e I<sub>out</sub>, pudiendo escalarlas simplemente dimensionando los correspondientes transistores. Los tamaños correspondientes a todos los transistores se indicarán posteriormente en el apartado de simulación. Así, obtenemos el circuito que muestra la figura 4.2. Cabe destacar que los transistores usados para inyectar las correspondientes corrientes (es decir, los espejos de corriente situados en la parte superior del circuito) son transistores PMOS, que denominaremos M<sub>PX</sub>, con X el correspondiente número. Los transistores del propio lazo translineal y los usados para polarizar el circuito (ya sea el espejo de corriente inferior o en sucesivos circuitos los que forman los seguidores FVF) son NMOS, que denotaremos como M<sub>NX</sub> con X el número del transistor.

Fig. 4.2: Configuración básica del circuito de media geométrica

La desventaja de esta topología es que el voltaje en el nodo que conecta los drenadores de los transistores  $M_{\rm N2}$  y  $M_{\rm N3}$  no está fijado ya que depende de la corriente que circule por estos transistores, es decir, es un nodo flotante. Además, requiere una tensión de alimentación alta al apilar dos uniones fuente-puerta. Para resolver este problema, se añade un seguidor de tensión FVF o "flipped voltage follower".

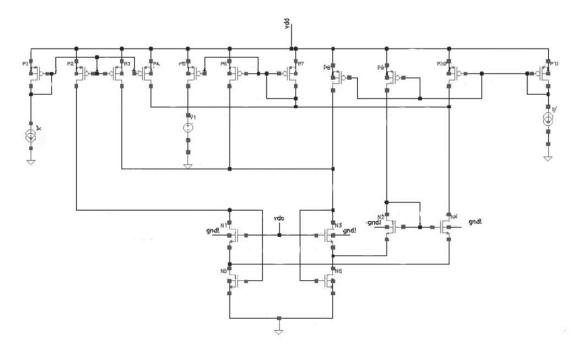

#### 4.2.2. Topología FVF

La figura 4.3 muestra el lazo translineal con el seguir de tensión FVF incluido. Como se puede ver se trata de una topología con realimentación negativa, formada por dos transistores, y una fuente de corriente I<sub>B</sub>. El nodo central del FVF es común al nodo central del lazo translineal. Para compensar la corriente inyectada por la fuente de corriente I<sub>B</sub>, debemos colocar otra fuente de corriente cuyo valor sea el mismo, para asegurarnos de que esa corriente no circula por el circuito.

Fig. 4.3: Configuración FVF del circuito de media geométrica

Con esta topología se consigue que el nodo central del lazo, que ahora está conectado al FVF, tenga un voltaje en DC controlable por la fuente de corriente I<sub>B</sub> y por las dimensiones del transistor cuyo drenador está conectado a dicho nodo. Cabe destacar que este voltaje es independiente de las señales tanto de entrada como de salida. Además, se mejora el ancho de banda del lazo translineal.

#### 4.2.3. Topología FVF mejorada

El circuito de la figura 4.4 es equivalente al circuito superior, en cuanto a comportamiento de corrientes, ya que los transistores  $M_{\rm NI}$ - $M_{\rm N4}$  son los que forman el lazo translineal, es decir, la fórmula que relaciona las corrientes es la misma que la del caso anterior. La diferencia es que los transistores  $M_{\rm N5}$  y  $M_{\rm N6}$  actúan como sumideros de corriente, haciendo que sea prescindible la fuente de corriente  $I_{\rm B}$  que teníamos en el caso anterior.

Fig. 4.4: Configuración FVF mejorada del circuito de media geométrica

La tensión mínima de alimentación de este circuito es de  $V_{TH} + 3V_{DSsat}$ , mientras que en el circuito anterior debemos aplicar una tensión mínima de alimentación de  $2V_{TH} + 3V_{DSsat}$ , lo que hace que la tensión de alimentación se reduzca significativamente,

consiguiendo así nuestro propósito de disminuir la tensión de alimentación del circuito, y por tanto la potencia consumida. Veremos datos más detallados de estos parámetros en la sección de *Simulación y resultados*.

Nótese también la tensión  $V_{dc}$  que debe aplicarse al nodo que conecta las puertas de  $P_{N1}$  y  $P_{N3}$ , ya que sino, ese nodo sería flotante. Tras la simulación del circuito, se observa que esta tensión  $V_{dc}$  debe ser superior a 1V para su correcto funcionamiento.

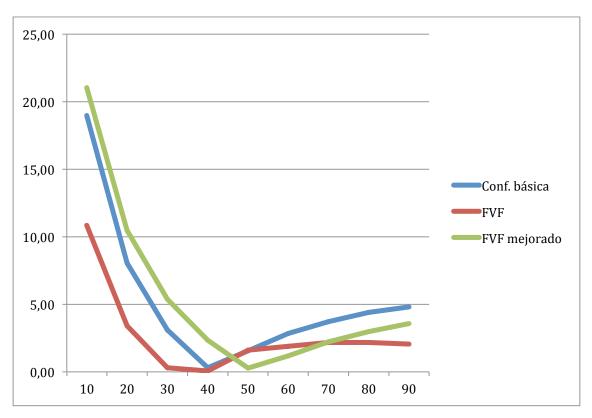

# 4.2.4. Simulación y resultados

En esta sección, pasamos a analizar los resultados de los tres circuitos de media geométrica explicados anteriormente. Sobre ellos, compararemos parámetros como el ancho de banda, la tensión de alimentación mínima  $V_{DDmin}$ , o su consumo. Pero antes, presentamos en las siguientes tablas el dimensionamiento (W/L) de los transistores de los tres circuitos.

| $P_1$ - $P_3$ | $P_4$ - $P_5$ | $P_{6}$ - $P_{10}$ | $N_1$ - $N_4$ | $N_5$ - $N_6$ |

|---------------|---------------|--------------------|---------------|---------------|

| 94′5μm        | 47′25μm       | 94′5μm             | 31′5µm        | 31′5μm        |

| $1'05\mu m$   | $1'05\mu m$   | $1'05\mu m$        | 600nm         | Зμт           |

Tabla 4.1: Relación W/L de la configuración básica del circuito de media geométrica

| $P_1$ - $P_3$          | $P_{4}$ - $P_{5}$ | $P_6$ - $P_{10}$       | $N_1$ - $N_4$      | $N_5$ - $N_6$          |

|------------------------|-------------------|------------------------|--------------------|------------------------|

| 94′5μm                 | 47′25μm           | 94′5μm                 | 31′5μm             | 31′5μm                 |

| $\overline{1'05\mu m}$ | $1'05\mu m$       | $\overline{1'05\mu m}$ | $\overline{600nm}$ | $\overline{1'05\mu m}$ |

Tabla 4.2: Relación W/L de la configuración FVF del circuito de media geométrica

| $P_1$ - $P_2$ | $P_3$ - $P_4$ | $P_5$                  | $P_6$ - $P_7$      | $P_8$                  |

|---------------|---------------|------------------------|--------------------|------------------------|

| 94′8μm        | 23′7μm        | 94′8μm                 | 47′4μm             | 23′7μm                 |

| $1'05\mu m$   | $1'05\mu m$   | $\overline{1'05\mu m}$ | $\overline{600nm}$ | $\overline{1'05\mu m}$ |

| $P_{9}$       | $P_{10}$      | $P_{11}$               | $N_1$ - $N_4$      | $N_5$ - $N_6$          |

| 94′8μm        | 23′7μm        | 94′8μm                 | 31′5μm             | 31′5μm                 |

|               | •             | •                      | •                  | •                      |

Tabla 4.3: Relación W/L de la configuración FVF mejorada del circuito de media geométrica

#### - Tensión de alimentación mínima V<sub>DDmin</sub>:

Realizando un análisis DC de las tres versiones de media geométrica, observamos que se verifica la hipótesis anteriormente presentada, de que la tensión mínima de alimentación disminuiría en un valor estimado de  $V_{DSsat}$ . En la tabla 4.4 se presentan los datos obtenidos.

|              | $V_{DDmin}$ | % mejora |

|--------------|-------------|----------|

| Conf. Básica | 2V          | 0%       |

| FVF          | 1 '7V       | 15%      |

| FVF mejorado | 1'6V        | 20%      |

Tabla 4.4: Resultados sobre la tensión mínima de alimentación V<sub>DDmin</sub> de los circuitos de media geométrica

#### - Ancho de banda:

Mediante un análisis AC, calculamos el ancho de banda de los tres circuitos, obteniendo los datos mostrados en la tabla 4.5.

|              | BW        | % mejora |

|--------------|-----------|----------|

| Conf. Básica | 6'113 MHz | 0%       |

| FVF          | 9'441 MHz | 5 '37%   |

| FVF mejorado | 25'89 MHz | 323'52%  |

Tabla 4.5: Resultados sobre el ancho de banda de los circuitos de media geométrica

Como se puede apreciar, el circuito con seguidor de tensión FVF mejorado presenta una gran mejora (323'52%) respecto a la configuración básica.

#### - Consumo:

En la tabla 4.6 se puede ver el consumo de los tres circuitos cuando se les aplica la tensión mínima de alimentación permitida para que el circuito funcione de manera correcta.

|              | P. Consumida | % mejora |

|--------------|--------------|----------|

| Conf. Básica | 36μW         | 0%       |

| FVF          | $30'6\mu W$  | 15%      |

| FVF mejorado | $22'4\mu W$  | 37'78%   |

Tabla 4.6: Resultados sobre la potencia consumida de los circuitos de media geométrica

Se observa una mejora del 37'78% en el caso del circuito FVF mejorado, consecuencia de la disminución en su tensión de alimentación mínima.

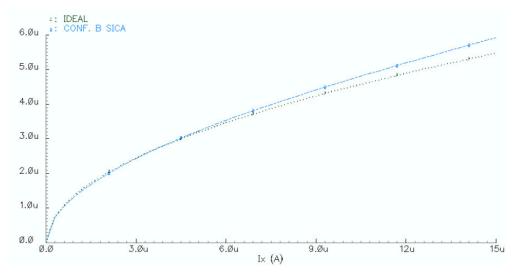

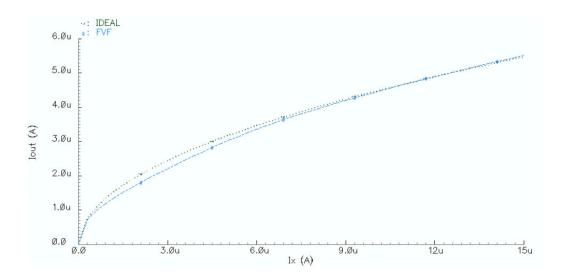

# - Precisión:

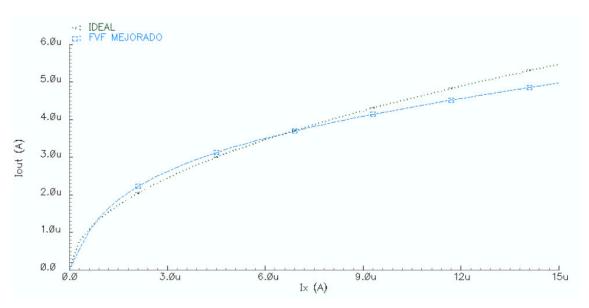

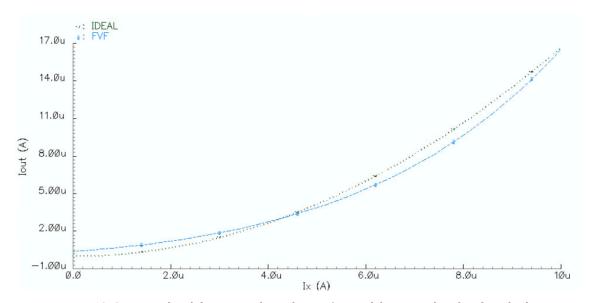

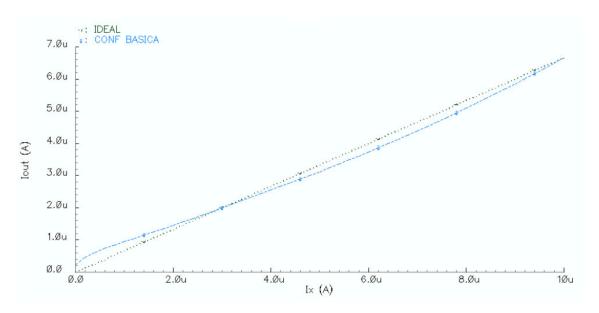

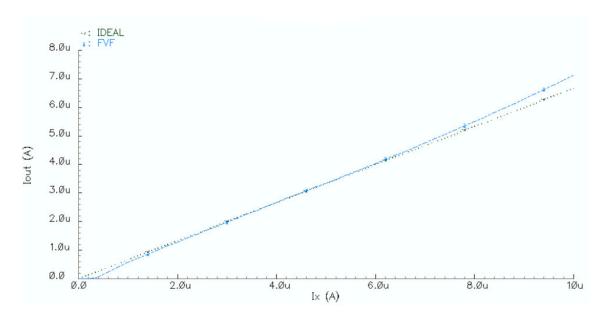

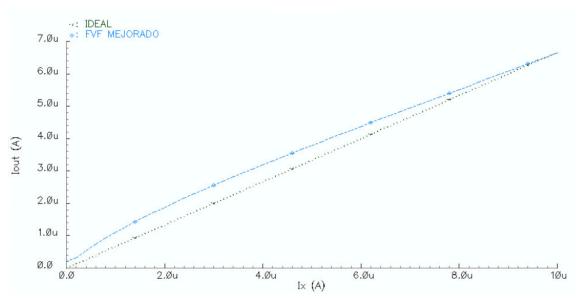

A continuación, se muestran las gráficas de simulación de la corriente de salida,  $I_{OUT}$ . Como se puede apreciar, se ven dos curvas: una la simulada (caso real) y otra la ideal (mediante la fórmula).

Fig. 4.5: Corriente de salida I<sub>OUT</sub> para la configuración básica del circuito de media geométrica

Fig. 4.6: Corriente de salida  $I_{\text{OUT}}$  de la configuración FVF del circuito de media geométrica

Fig. 4.7: Corriente de salida Iout de la configuración FVF mejorada del circuito de media geométrica

# 4.3. Circuito elevador al cuadrado

Partiendo del circuito de media geométrica, cuyo comportamiento viene definido por

$$I_z = \sqrt{I_x \cdot I_y} \tag{4.10}$$

podemos conseguir un circuito elevador al cuadrado, tan sólo tomando  $I_z$  como una entrada e  $I_y$  como salida. De esta forma, despejando de la expresión anterior, obtenemos:

$$I_{x} = \frac{I_{z}^{2}}{I_{y}} \tag{4.11}$$

Realizando este cambio en las tres versiones del circuito de media geométrica, obtenemos pues tres topologías distintas a comparar del circuito elevador al cuadrado.

Por similitud con el circuito de media geométrica, seguiremos llamando  $I_x$  a la tensión con la que hacemos el barrido DC, por tanto,  $I_z$  seguirá siendo la corriente de salida, así pues:

$$I_{z} = \frac{I_{x}^{2}}{I_{y}} \tag{4.12}$$

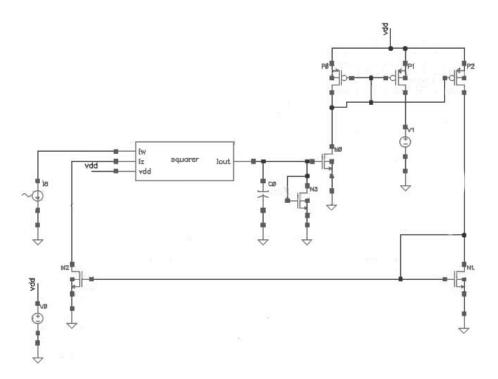

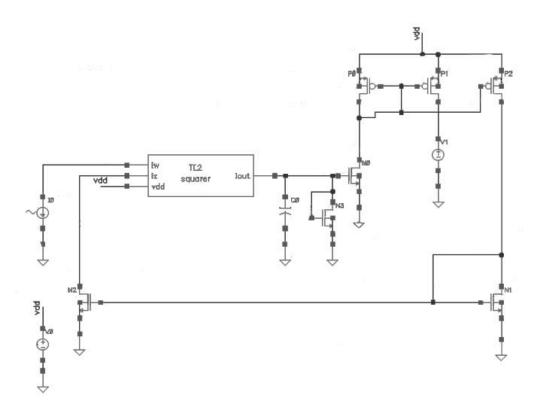

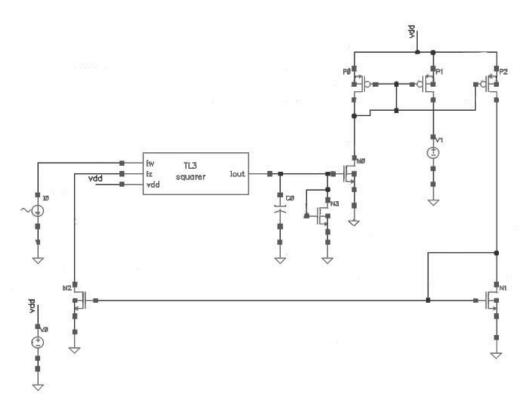

# 4.3.1. Configuración básica

En la figura 4.8 se presenta el circuito a simular para obtener un elevador al cuadrado.

Para ajustar mejor la salida al caso ideal, se han hecho unos cambios en las dimensiones de los transistores. Dichas modificaciones se indican en el apartado de *Simulación y resultados*.

Fig. 4.8: Configuración básica del circuito elevador al cuadrado

# 4.3.2. Configuración FVF

En la figura 4.9 se puede ver el circuito elevador al cuadrado con el seguidor de tensión FVF, que hará que mejore sus prestaciones, tal y como se verá en el apartado de *Simulación y resultados*.

Fig. 4.9: Configuración FVF del circuito elevador al cuadrado

# 4.3.3. Configuración FVF mejorada

La figura 4.10 presenta el circuito elevador al cuadrado con la configuración FVF mejorada, que como ya se ha comentado en el caso de media geométrica, tiene una menor tensión de alimentación, con una diferencia de aproximadamente  $V_{DSsat}$ .

Fig. 4.10: Configuración FVF mejorada del circuito elevador al cuadrado

# 4.3.4. Simulación y resultados

Al igual que en el caso de media geométrica, se realizará un análisis de varios parámetros de los tres circuitos presentados anteriormente.

Pero en primer lugar, presentamos las dimensiones de los circuitos, ya que como se ha comentado antes, se han modificado algunas medidas para ajustar lo mejor posible al caso ideal.

| $P_1$ - $P_3$          | $P_4$ - $P_5$ | $P_{6}$ - $P_{10}$ | $N_1$ - $N_6$          |

|------------------------|---------------|--------------------|------------------------|

| 94′5μm                 | 47′25μm       | 94′5μm             | 31′5μm                 |

| $\overline{1'05\mu m}$ | $1'05\mu m$   | $1'05\mu m$        | $\overline{1'05\mu m}$ |

Tabla 4.7: Relación W/L de la configuración básica del circuito elevador al cuadrado

| $P_1$ - $P_3$          | $P_4$ - $P_5$ | $P_6$ - $P_{10}$       | $N_1$ - $N_6$          |

|------------------------|---------------|------------------------|------------------------|

| 94′5μm                 | 47′25μm       | 94′5μm                 | 31′5μm                 |

| $\overline{1'05\mu m}$ | $1'05\mu m$   | $\overline{1'05\mu m}$ | $\overline{1'05\mu m}$ |

Tabla 4.8: Relación W/L de la configuración FVF del circuito elevador al cuadrado

| $P_1$ - $P_2$                           | $P_3$ - $P_4$                          | $P_5$                     | $P_{6}$ - $P_{7}$             | $P_8$                                                     |

|-----------------------------------------|----------------------------------------|---------------------------|-------------------------------|-----------------------------------------------------------|

| 94′8μm                                  | 23′7μm                                 | 94′8µm                    | 47′4μm                        | 23′7μm                                                    |

| $1'05\mu m$                             | $1'05\mu m$                            | $1'05\mu m$               | 600 <i>nm</i>                 | $1'05\mu m$                                               |

|                                         |                                        |                           |                               |                                                           |

| $P_9$                                   | $P_{10}$                               | $P_{11}$                  | $N_1$ - $N_4$                 | $N_5$ - $N_6$                                             |

| $\frac{P_9}{94'8\mu m \over 1'05\mu m}$ | $P_{I0} = \frac{23'7\mu m}{1'05\mu m}$ | P <sub>11</sub><br>94'8μm | $\frac{N_I - N_4}{31'5\mu m}$ | $\frac{N_5-N_6}{31'5\mu m} = \frac{31'5\mu m}{1'05\mu m}$ |

Tabla 4.2: Relación W/L de la configuración FVF mejorada del circuito elevador al cuadrado

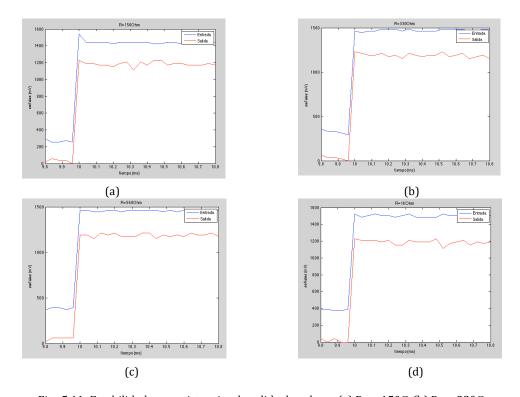

## - Tensión de alimentación mínima V<sub>DDmin</sub>:

Realizando un análisis DC paramétrico con las tres versiones de circuito elevador al cuadrado, observamos que las tensiones para las que mejor funciona el circuito son las presentadas en la tabla 4.10. Como era de esperar, la configuración FVF mejorada presenta los mejores resultados, obteniendo un porcentaje de mejora del 28'57%.

|              | $V_{DDmin}$ | % mejora |

|--------------|-------------|----------|

| Conf. Básica | 2'4V        | 0%       |

| FVF          | 1'9V        | 20'83%   |

| FVF mejorado | 1'8V        | 25%      |

Tabla 4.10: Resultados sobre la tensión mínima de alimentación V<sub>DDmin</sub> de los circuitos de media geométrica

Como era de esperar, la configuración FVF mejorada presenta los mejores resultados, obteniendo un porcentaje de mejora del 25%.

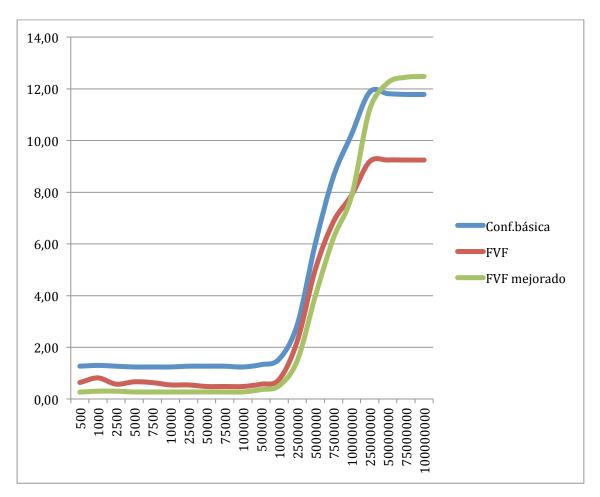

#### Ancho de banda:

Mediante un análisis AC, calculamos el ancho de banda de los tres circuitos, obteniendo los datos de la tabla 4.11.

|              | BW        | % mejora |

|--------------|-----------|----------|

| Conf. Básica | 6'288 MHz | 0%       |

| FVF          | 6'649 MHz | 5'74%    |

| FVF mejorado | 7'30 MHz  | 16'09%   |

Tabla 4.11: Resultados sobre el ancho de banda de los circuitos de media geométrica

Vemos que en el caso del circuito elevador al cuadrado, la tendencia a mejorar se mantiene al igual que en el caso del circuito de media geométrica. Es decir, la configuración básica tiene el menor ancho de banda, y la configuración de FVF mejorada, el mayor.

#### - Consumo:

En la tabla 4.12 se puede ver el consumo de los tres circuitos cuando se les aplica la tensión mínima de alimentación permitida para que el circuito funcione de manera correcta.

|              | P. Consumida   | % mejora |

|--------------|----------------|----------|

| Conf. Básica | 77'4 μW        | 0%       |

| FVF          | $61'275~\mu W$ | 20'83%   |

| FVF mejorado | $44'55 \mu W$  | 42'44%   |

Tabla 4.12: Resultados sobre la potencia consumida de los circuitos de media geométrica

Como era de esperar y debido al descenso de la tensión mínima de alimentación para cada topología, la potencia consumida disminuye en un factor equivalente a dicha reducción de tensión de alimentación. Así, con la configuración FVF mejorada, se consigue un ahorro energético del 42'44%.

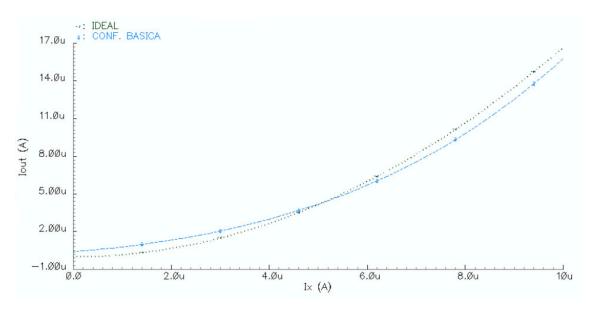

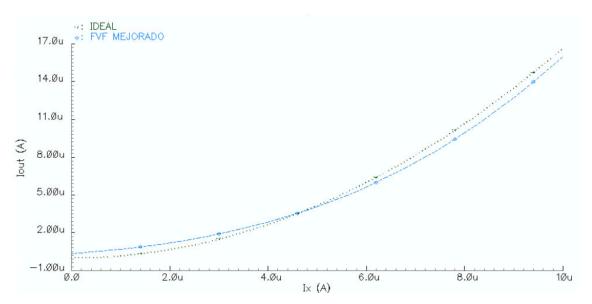

#### - Precisión:

Tal y como ha ocurrido antes, se presentan unas gráficas con la corriente de salida simulada (color azul) y la ideal (color verde). Para ello se realiza un barrido en DC de la corriente  $I_X$ .

Fig. 4.11: Corriente de salida  $I_{\text{OUT}}$  para la configuración básica del circuito elevador al cuadrado

Fig. 4.12: Corriente de salida  $I_{\text{OUT}}$  para la configuración FVF del circuito elevador al cuadrado

Fig. 4.13: Corriente de salida Iout para la configuración básica del circuito de media geométrica

# 4.4. Multiplicador/divisor

A partir de los circuitos de media geométrica y elevador al cuadrado, si los colocamos en cascada, es decir, primero el circuito te media geométrica y después el elevador al cuadrado, conseguimos un multiplicador/divisor. Esto se justifica a partir de las fórmulas que rigen ambos circuitos, ya que:

$$I_{OUT} = \frac{\left(\sqrt{I_X I_Y}\right)^2}{I_Z} = \frac{I_X I_Y}{I_Z} \tag{4.13}$$

Si se emplea el circuito como amplificador de ganancia variable, se puede analizar la linealidad del mismo. Esto se consigue calculando la distorsión armónica total (THD) y para evaluar la no linealidad dominante calculando la distorsión de primer y segundo orden, es decir, mediante la diferencia de entre el armónico principal y los siguientes armónicos.

#### 4.4.1. Configuración básica

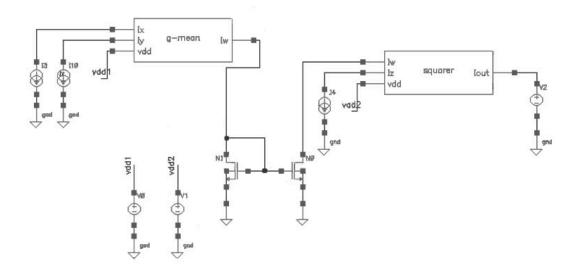

Tal y como se ha comentado en la introducción, el circuito multiplicador/divisor se consigue colocando en cascada el circuito de media geométrica y el elevador al cuadrado. Esto hace que tengamos de nuevo tres circuitos distintos, construidos mediante las tres versiones de circuitos analizadas con anterioridad.

Para un uso de estos circuitos de manera más fácil, se han creado unos símbolos de dichos circuitos, que se ven reflejados en la figura 4.14.

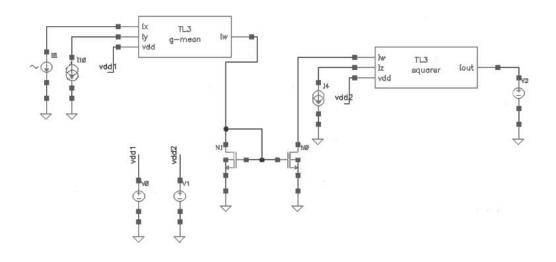

Fig. 4.14: Configuración básica del circuito multiplicador/divisor

Cabe destacar el uso de un espejo de corriente entre ambos circuitos. Si se conectara directamente la salida del circuito de media geométrica con la entrada  $I_W$  del circuito elevador al cuadrado, el segundo no funcionaría bien, debido a que el sentido de la corriente  $I_W$  debe ser saliente, no entrante.

Para un mejor ajuste al caso ideal, las tensiones de alimentación de los circuitos se tratan por separado, y así poder optimizar el resultado.

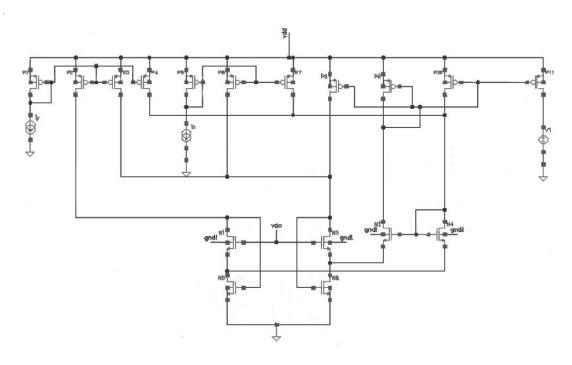

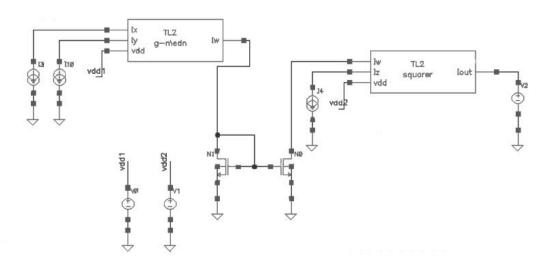

# 4.4.2. Configuración FVF

Tras la creación de los símbolos a partir de la topología FVF y partiendo del circuito de la figura 4.14, llegamos al circuito que se muestra en la figura 4.15. Es la versión FVF del circuito multiplicador/divisor.

Fig. 4.15: Configuración FVF del circuito multiplicador/divisor

# 4.4.3. Configuración FVF mejorada

Por último, colocando los símbolos de los circuitos FVF mejorados de media geométrica y elevador al cuadrado, conseguimos la versión FVF mejorada del circuito multiplicador/divisor.

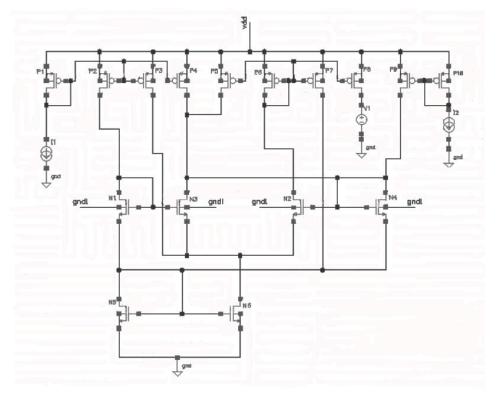

Fig. 4.16: Configuración FVF mejorada del circuito multiplicador/divisor

# 4.4.4. Simulación y resultados