#### Open Archive TOULOUSE Archive Ouverte (OATAO)

OATAO is an open access repository that collects the work of Toulouse researchers and makes it freely available over the web where possible.

This is an author-deposited version published in : <u>http://oatao.univ-toulouse.fr/</u> <u>Eprints ID</u> : 14562

**To cite this version** : Pelamatti, Alice and Goiffon, Vincent and Chabane, Aziouz and Magnan, Pierre and Virmontois, Cédric and Saint-Pé, Olivier and Bréart-de-Boisanger, Michel <u>Speed Analysis</u> <u>in Pinned Photodiode *CMOS* <u>Image Sensors based on a Pulsed</u> <u>Storage-Gate Method.</u> (2015) In: Proceedings of European Solid-State Device conference (ESSDERC), 15 September 2015 - 17 September 2015 (Gratz, Austria).</u>

Any correspondance concerning this service should be sent to the repository administrator: <a href="mailto:staff-oatao@listes-diff.inp-toulouse.fr">staff-oatao@listes-diff.inp-toulouse.fr</a>

### Speed Analysis in Pinned Photodiode CMOS Image Sensors based on a Pulsed Storage-Gate Method

# <u>A. Pelamatti<sup>1</sup></u>, V. Goiffon<sup>1</sup>, A. Chabane<sup>1</sup>, P. Magnan<sup>1</sup>, C. Virmontois<sup>2</sup>, O. Saint-Pé<sup>3</sup>, M. Bréart de Boisanger<sup>3</sup>

<sup>1</sup> ISAE, Image Sensor Research Team, Univ. of Toulouse, 31055 Toulouse, France

<sup>2</sup> CNES, 18 av. Edouard Belin, 31055, Toulouse, France

<sup>3</sup> Airbus Defence&Space, 31 Rue des Cosmonautes, 31400, Toulouse, France

#### ESSDERC 16/09/2015

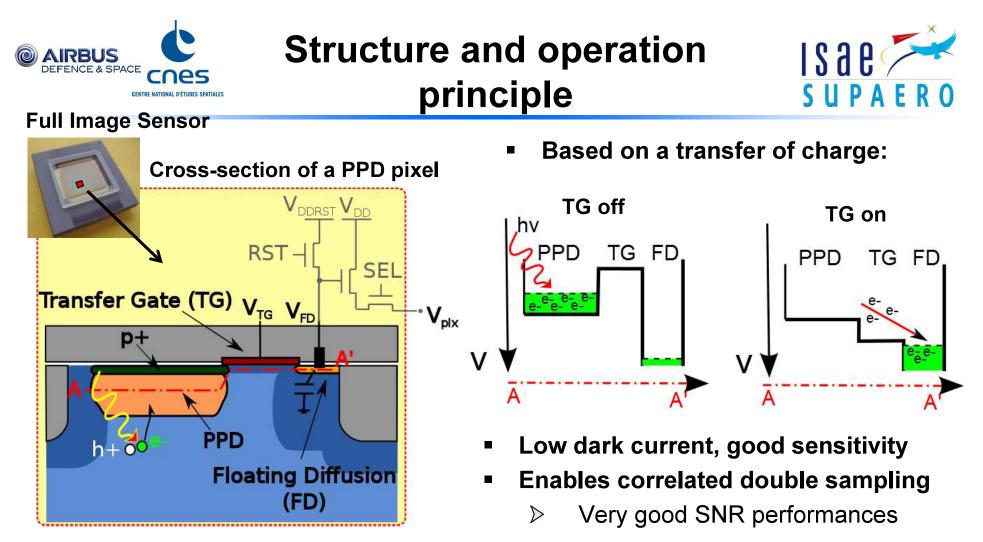

### **CMOS Image sensors**

- CMOS Image sensors (CIS): main technology for commercial imaging applications:

- Driven by massive development of <u>consumer</u> <u>electronics</u> (smart-phones, tablet ..)

- Multibillion \$ market

- Technological breakthroughs announced every year

- Scientific imaging applications:

- XX<sub>st</sub> century: mainly Charge Coupled Devices (CCDs)

- Thanks to the introduction of the <u>Pinned</u> <u>Photodiode (PPD)</u> technology, CIS now compete with CCDs in terms of:

- Sensitivity

- Low noise

- ▷ With all the advantages of CIS technology:

- Lower cost, smart functions integration, random access capabilities ...

- Good candidate for high temporal resolution applications (such as Time of Flight applications)

- Requirements of high resolution applications:

- ▷ Fast sampling of the incoming light waveform  $\rightarrow$  SPEED

- ▷ Readout of extremely low signal levels  $\rightarrow$  VERY GOOD SNR

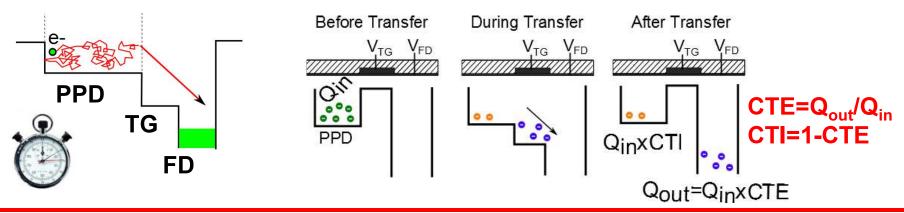

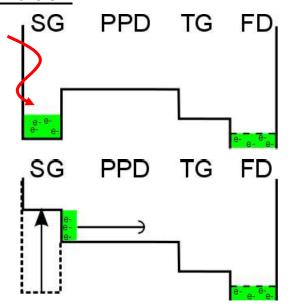

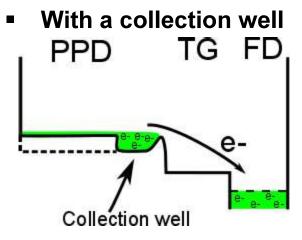

## Temporal resolution in PPD CIS

- Limiting temporal resolution = time to transfer electrons from PPD to FD

- Charge Transfer Inefficiency (CTI):

- > measures the ability of transferring the collected charge in a given time

Main Question: Which design/operation parameters affect the CTI?

#### Road-map:

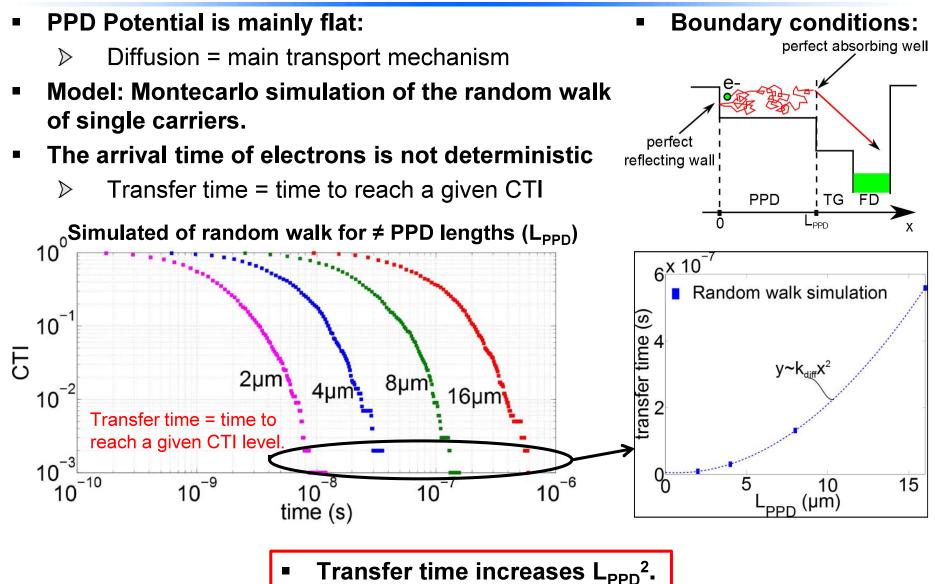

- $\triangleright$  Modeling and simulation of main charge transport mechanisms in PPD CIS

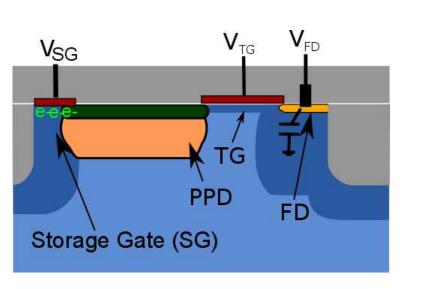

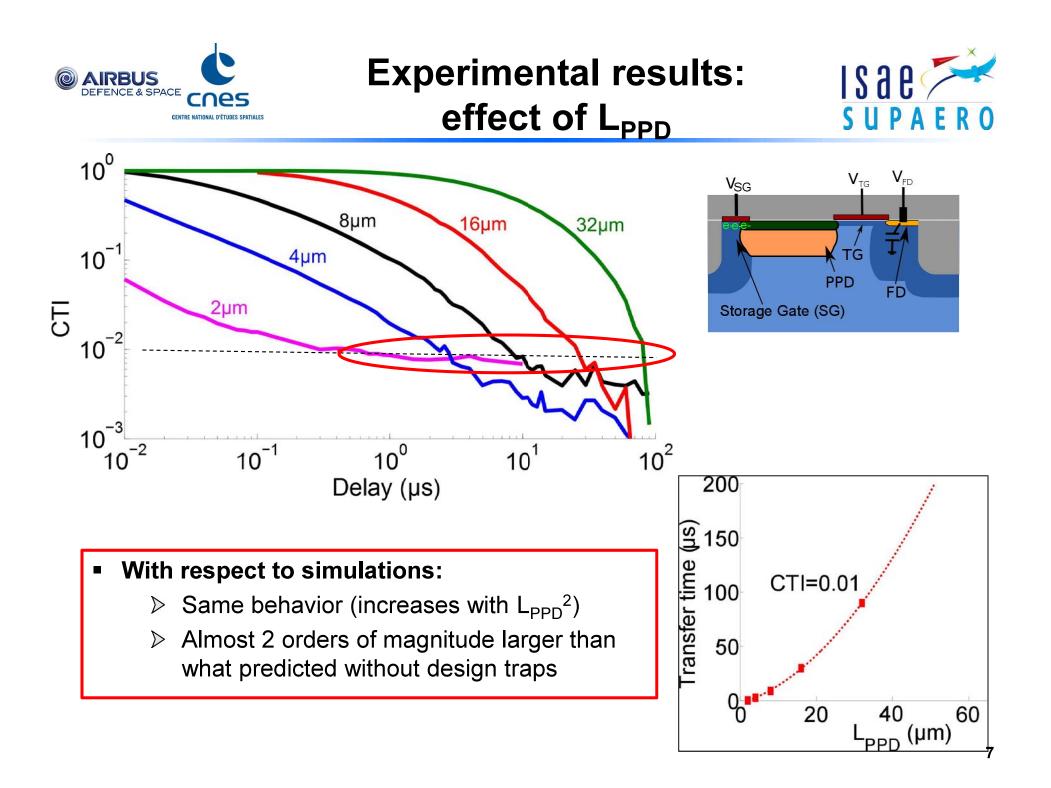

- Experimental measurements on dedicated Pulsed Storage-Gate pixels

- Identification of bottle-neck in terms of CTI by comparing the effect of different parameters on data and simulations

- <u>Goal of this study</u>: Provide tools to users and designers to find optimum trade-off between parameters to reach good CTI

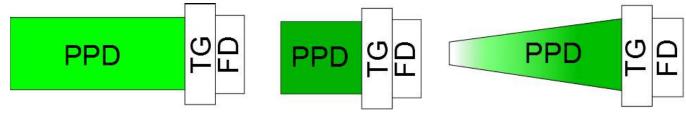

- Hard to compare CTI in pixels with different size and geometries

- > Different charge level and initial charge distribution

- Pulsed Storage-Gate pixels enable comparison:

- ▷ With same charge level and same initial charge distribution

- ➢ Reproducing a worst case transfer condition

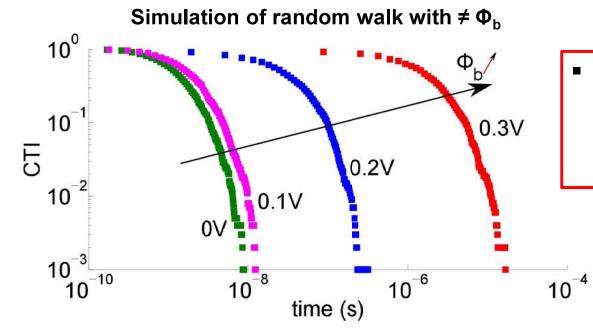

#### Simulation: Design traps

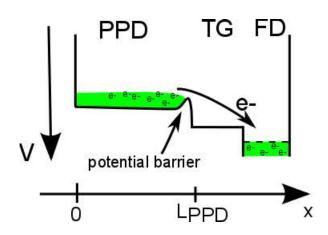

- There can be "design traps" along the charge transfer path (potential barrier/pocket)

- ▷ Usually located at the PPD-TG interface

- ▷ Electrons can

- "cross" the barrier by thermionic emission

- or "bounce" on the barrier

- > The probability of crossing is an exponential function of the barrier height ( $\Phi_b$ )

- Design traps significantly affect the transfer time

- Worsening of several orders of magnitude

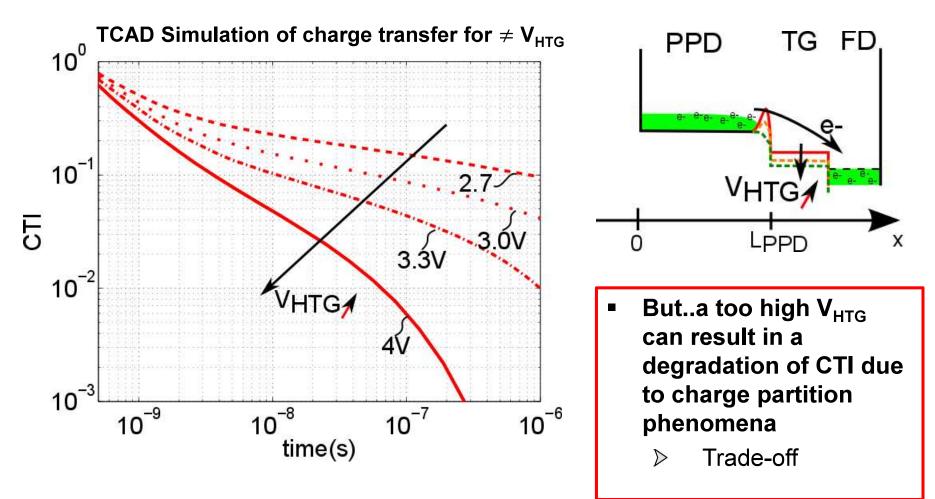

Φ<sub>b</sub> can be reduced by increasing the TG biasing voltage during transfer (V<sub>HTG</sub>)

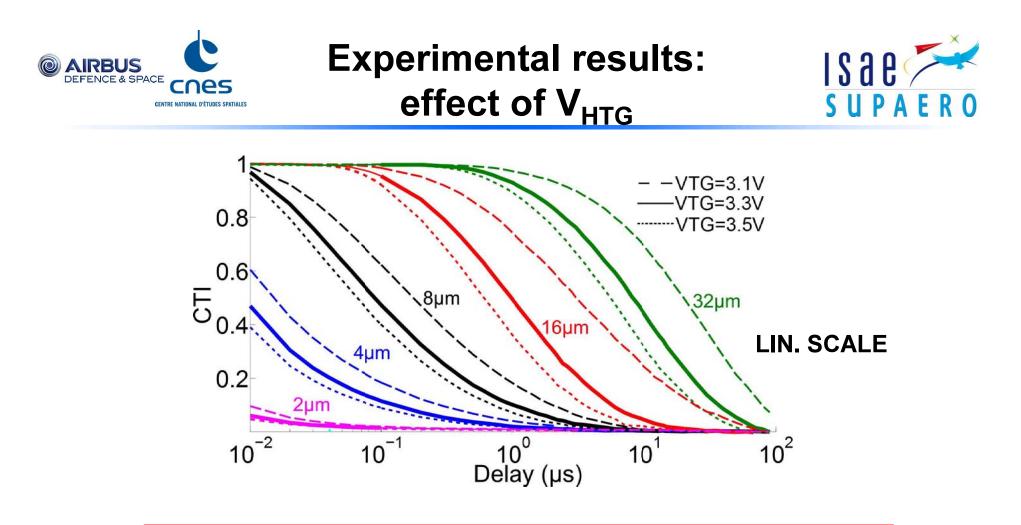

- CTI is significantly affected by VHTG

- ▷ even at typical biasing levels ( $V_{TG}$ =3,3V)

- These results have been confirmed by other measurements which also indicated that CTI is limited by a potential barrier at the PPD-TG interface

- Charge transfer mechanisms have been studied based on Montecarlo simulations and TCAD simulations

- Experimental measurements on dedicated pulsed storage-gate structure

- ▷ Enable fair CTI comparisons (on PPD lengths up to 32µm)

- This study showed that for this commercial technology CTI is limited by design traps even for long PPDs.

- This same approach can be used to identify the CTI bottleneck on other technologies

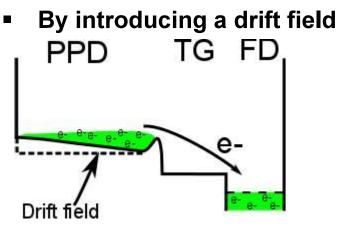

- Solutions to improve transfer time:

- $\triangleright$  Increasing V<sub>TG</sub> during transfer

- ▷ Increasing probability of crossing barrier by keeping electrons close to the TG

#### Thank you for your attention! Any questions?