# Coggins, David Paul (2010) Single-ended traveling wave fault location on radial distribution lines. PhD thesis, University of Nottingham.

### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/27951/1/523143.pdf

### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

- Copyright and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners.

- To the extent reasonable and practicable the material made available in Nottingham ePrints has been checked for eligibility before being made available.

- Copies of full items can be used for personal research or study, educational, or notfor-profit purposes without prior permission or charge provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

- · Quotations or similar reproductions must be sufficiently acknowledged.

Please see our full end user licence at: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

### UNIVERSITY OF NOTTINGHAM

# Single-Ended Traveling Wave Fault Location on Radial Distribution Lines

A thesis submitted in partial fulfillment for the degree of Doctor of Philosophy

in the Faculty of Engineering Department of Electrical And Electronic Engineering

February 2010

# **IMAGING SERVICES NORTH**

Boston Spa, Wetherby West Yorkshire, LS23 7BQ www.bl.uk

# ORIGINAL COPY TIGHTLY BOUND

# Abstract

In this thesis a single-ended traveling wave fault location algorithm is developed for autonomously locating short circuit faults on a radial distribution line using the high frequency traveling wave transients. The traveling wave pattern observed at the substation is correlated with the traveling wave pattern predicted using time tree analysis for different fault locations and fault resistance. Genetic search techniques are used to evolve an initial population of possible fault locations to determine the most likely fault location. It is shown through extensive EMTP simulations that the scheme is capable of finding the location of three phase faults, inter-phase faults and single-phase faults for fault resistances ranging from 0 - 1000 ohm on a radial distribution line with five sub-feeders.

A new high speed FPGA based data acquisition system is developed suitable for capturing traveling wave fault data from a radial distribution line with the necessary fidelity for the proposed fault location algorithm. The data acquisition system is deployed on a Medium Voltage distribution line in the Santa Caterina region of Brazil.

A branched communication network is constructed out of RG-58 coaxial cable and a Time Domain Reflectometry device is used to capture the reflection pattern under different fault conditions. The fault location algorithm is adapted to work with TDR as opposed to fault generated traveling waves. The location algorithm is capable of locating faults with resistance between 0 and 75 ohm up to three zones away from the injection point.

### *Publications*

The work in thesis has been published or is under consideration in several publications which are as follows

- 1. D. Coggins, D. W. P. Thomas, Y. Zhu, and B. R. Hayes-Gill, 'An FPGA Based Travelling Wave Fault Locator' International Conference on Field-Programmable Technology 2007 December 12th-14th, 2007 The Kitakyushu International Conference Center Kokurakita, Kitakyushu, JAPAN

- 2. D. Coggins, D. W. P. Thomas, Y. Zhu, and B. R. Hayes-Gill, 'A New High Speed FPGA Based Traveling Wave Fault Recorder for MV distribution Systems' The 9th International Conference on Developments in Power System Protection 2008 March 17th-20th, 2008 The Crowne Plaza Hotel, Glasgow, UK

- 3. D. P. Coggins, D. W. P. Thomas, B. R. Hayes-Gill, Y. Zhu, E. T. Pereira, and S. H. L. Cabral 'Initial Experiences with a new FPGA based traveling wave fault recorder installed on a MV distribution network', POWERCON2008 & 2008 IEEE Power India Conference Accepted for oral presentation

- 4. D. P. Coggins, D. W. P. Thomas, M. Sumner, 'Fault Location on a Branched Network using Time Domain Reflectometry' Submitted to the IEEE Journal on Industrial Electronics

- 5. D. P. Coggins, D. W. P. Thomas, 'Single-Ended Traveling Wave Fault Location on a Radial Distribution Line' Submitted to the IEEE Journal on Power Delivery

# Acknowledgements

I would like to express my sincere thanks to my supervisor Dr. Thomas who has provided advise and encouragement. Thanks also go to Dr. Zhu and Dr. Hayes-Gill for their guidance with the design of the fault recorder hardware. I would like to thank Dr. Pereira and Dr. Cabral at FURB university in Brazil for their hospitality and assistance. I would also like to pay thanks to CELESC power company for allowing access to their distribution network. I would like to express a special thanks to Hoang Nyugen who was involved in the design of the fault recorder hardware and has been a good friend over the past four years. Finally I would like to thank my family and friends who have encouraged me and helped me through some difficult times.

# Contents

| Ab  | stra  | ct      |           |                                     |   | i    |

|-----|-------|---------|-----------|-------------------------------------|---|------|

| Pu  | blica | ations  |           |                                     |   | ii   |

| Ac  | knov  | wledge  | ments     |                                     |   | iii  |

| Lis | st of | Figure  | es        |                                     | v | /iii |

| Lis | st of | Tables  |           |                                     |   | x    |

| Ał  | brev  | viation | s         |                                     |   | xii  |

| Ph  | ysic  | al Con  | stants    |                                     | 2 | civ  |

| Sy  | mbo   | ls      |           |                                     |   | xv   |

|     |       |         |           |                                     |   |      |

| 1   | Intr  | oducti  |           |                                     |   | 1    |

|     | 1.1   |         |           | Thesis                              |   | 1    |

|     | 1.2   |         |           | esis                                |   | 3    |

|     | 1.3   | Outlin  | e of Thes | is                                  |   | 5    |

| 2   | Fau   | lt Loca | ation     |                                     |   | 7    |

|     | 2.1   | Introd  | uction    |                                     |   | 7    |

|     | 2.2   |         |           | aults                               |   | 9    |

|     | 2.3   |         |           | lt location on Distribution Systems |   | 11   |

|     | 2.4   | Metho   | ds of Fau | llt Location                        |   | 11   |

|     |       | 2.4.1   | Impedan   | nce Based Methods                   |   | 12   |

|     |       | 2.4.2   | Traveling | g Wave Based Methods                |   | 13   |

|     |       |         | 2.4.2.1   | Correlation Techniques              |   | 23   |

|     |       |         | 2.4.2.2   | Time Tree Analysis                  |   | 24   |

|     |       |         | 2.4.2.3   | Wavelet Analysis                    |   | 25   |

|     |       |         | 2.4.2.4   | Application to Distribution Lines   |   | 26   |

|     |       | 2.4.3   |           | lge Based Methods                   |   | 28   |

|     |       |         | 2.4.3.1   | Expert Systems                      |   | 28   |

|     |       |         | 2.4.3.2   | Artificial Neural Networks          |   | 28   |

|     |       |         | 2.4.3.3   | Genetic Algorithms                  |   | 29   |

Contents

|   | 2.5 | Summary                                                                                   |  |  |  |  |  |  |

|---|-----|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3 | Тур | pical Fault Events                                                                        |  |  |  |  |  |  |

|   | 3.1 | Introduction                                                                              |  |  |  |  |  |  |

|   | 3.2 | Fault Events on Three Phase Systems                                                       |  |  |  |  |  |  |

|   |     | 3.2.1 Reflections at Impedance Discontinuities                                            |  |  |  |  |  |  |

|   |     | 3.2.2 Reflections at Fault Locations                                                      |  |  |  |  |  |  |

|   |     | 3.2.3 Modal Mixing                                                                        |  |  |  |  |  |  |

|   | 3.3 | Simulation of different types of faults                                                   |  |  |  |  |  |  |

|   |     | 3.3.1 Balanced three phase and balanced three phase to ground fault 38                    |  |  |  |  |  |  |

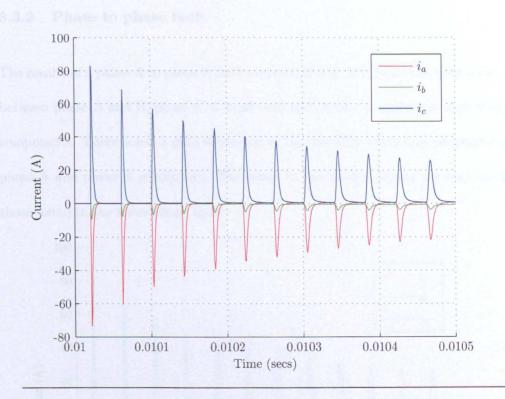

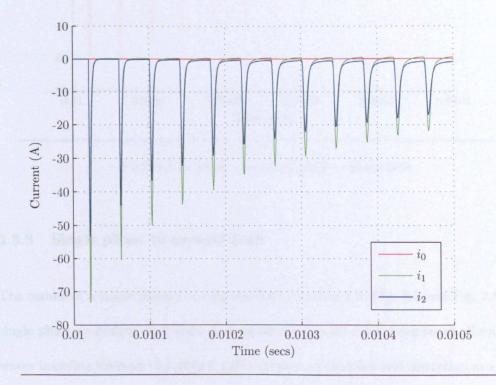

|   |     | 3.3.2 Phase to phase fault                                                                |  |  |  |  |  |  |

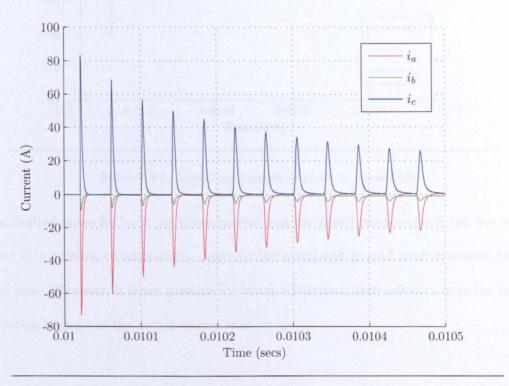

|   |     | 3.3.3 Single phase to ground fault                                                        |  |  |  |  |  |  |

|   | 3.4 | summary                                                                                   |  |  |  |  |  |  |

|   | m.  |                                                                                           |  |  |  |  |  |  |

| 4 |     | ne Tree Analysis of Power Networks 44                                                     |  |  |  |  |  |  |

|   | 4.1 | Introduction                                                                              |  |  |  |  |  |  |

|   | 4.2 | ATP/EMTP simulation software                                                              |  |  |  |  |  |  |

|   | 4.3 | Time Tree Concept                                                                         |  |  |  |  |  |  |

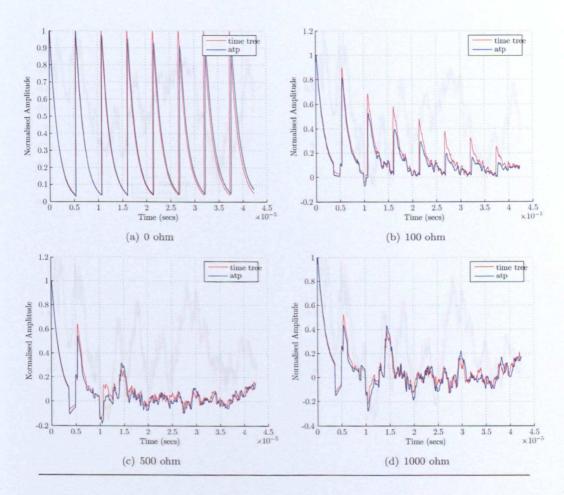

|   |     | 4.3.1 Comparison with ATP simulation                                                      |  |  |  |  |  |  |

|   | 4.4 | Genetic Search Algorithm                                                                  |  |  |  |  |  |  |

|   |     | 4.4.1 Selection                                                                           |  |  |  |  |  |  |

|   |     | 4.4.2 Crossover Operation                                                                 |  |  |  |  |  |  |

|   |     | 4.4.3 Mutation                                                                            |  |  |  |  |  |  |

|   |     | 4.4.4 Application to Traveling Waves                                                      |  |  |  |  |  |  |

|   |     | 4.4.5 Choice of parameters                                                                |  |  |  |  |  |  |

|   | 4.5 | .5 CELESC distribution line                                                               |  |  |  |  |  |  |

|   |     | 4.5.1 Three phase faults                                                                  |  |  |  |  |  |  |

|   |     | 4.5.2 Inter phase faults                                                                  |  |  |  |  |  |  |

|   |     | 4.5.3 Single phase faults                                                                 |  |  |  |  |  |  |

|   |     | 4.5.4 Performance of Genetic Algorithm                                                    |  |  |  |  |  |  |

|   | 4.6 | Limitations                                                                               |  |  |  |  |  |  |

|   | 4.7 | Application to other types of network                                                     |  |  |  |  |  |  |

|   | 4.8 | Summary                                                                                   |  |  |  |  |  |  |

| 5 | Fau | alt Recorder Hardware Design 103                                                          |  |  |  |  |  |  |

| · | 5.1 | Introduction                                                                              |  |  |  |  |  |  |

|   | 5.2 | System Requirements                                                                       |  |  |  |  |  |  |

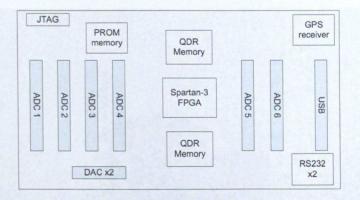

|   | 5.3 | Hardware Design                                                                           |  |  |  |  |  |  |

|   | 0.0 | 5.3.1 Overview of Hardware Component                                                      |  |  |  |  |  |  |

|   |     |                                                                                           |  |  |  |  |  |  |

|   |     | 등장과 (1) 1의 1일에 대한 대한 대한 경험 전 기업 이 전 기업 전 기업 전 기업 이 기업 |  |  |  |  |  |  |

|   |     | 5.3.1.2 QDR Memory                                                                        |  |  |  |  |  |  |

|   |     | 5.3.1.3 GPS Receiver                                                                      |  |  |  |  |  |  |

|   |     | 5.3.1.4 SD Card Reader                                                                    |  |  |  |  |  |  |

|   |     | 5.3.1.5 RS232 communication ports                                                         |  |  |  |  |  |  |

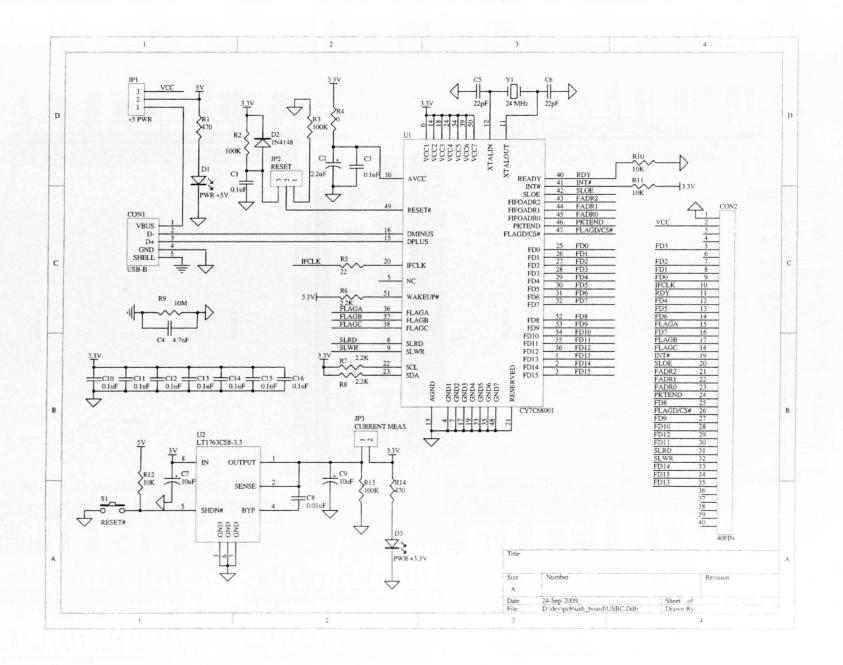

|   |     | 5.3.1.6 USB Daughter Card                                                                 |  |  |  |  |  |  |

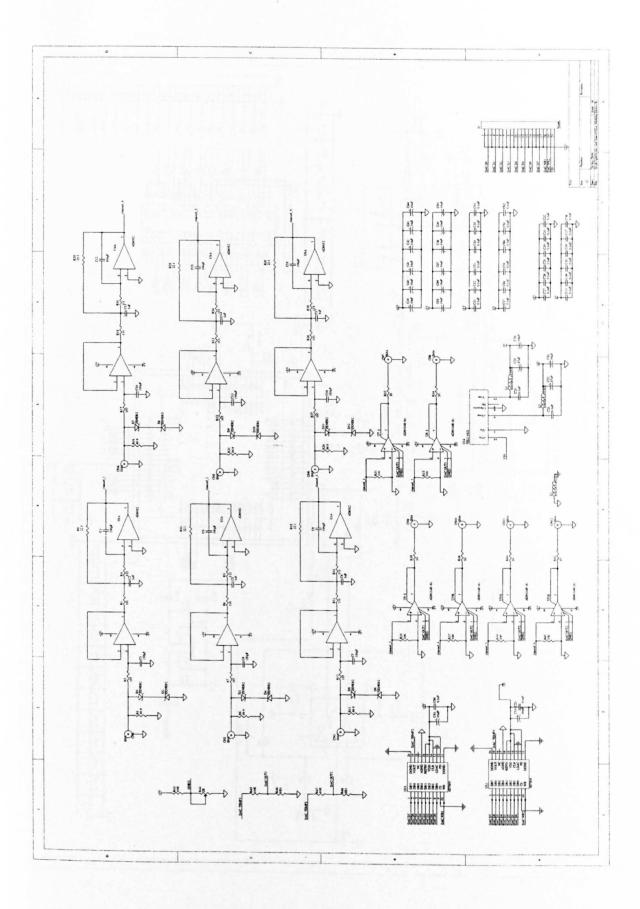

|   |     | 5.3.1.7 Front End Board                                                                   |  |  |  |  |  |  |

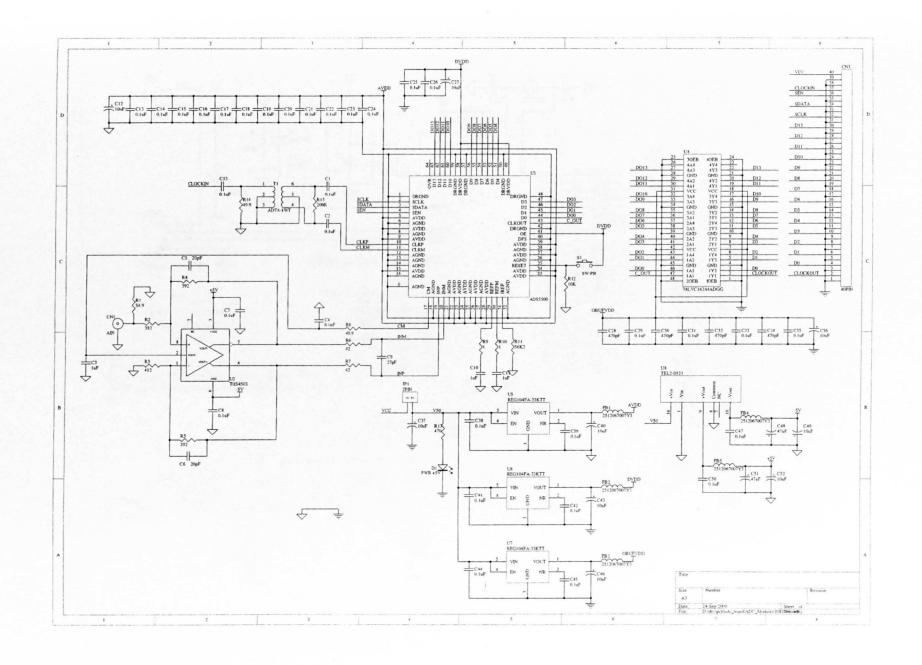

|   |     | 5.3.1.8 ADC Daughter Card                                                                 |  |  |  |  |  |  |

*Contents*

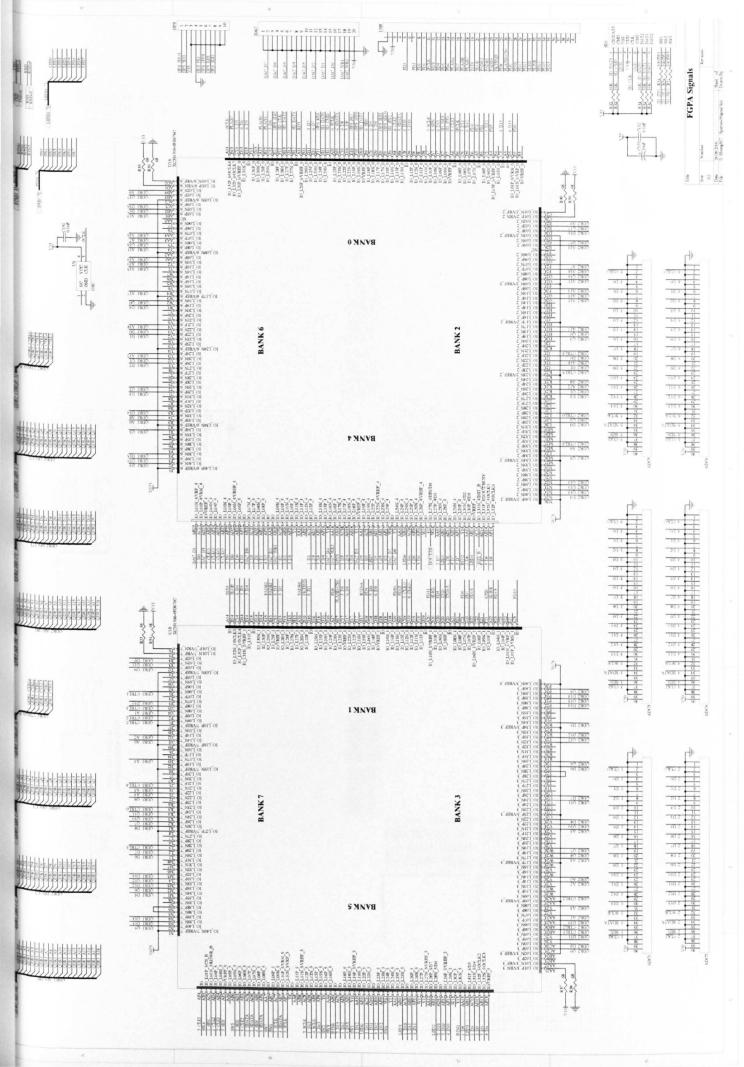

|   | 5.4   | FPGA System Design                                      |   |

|---|-------|---------------------------------------------------------|---|

|   |       | 5.4.1 Overview of system                                | 3 |

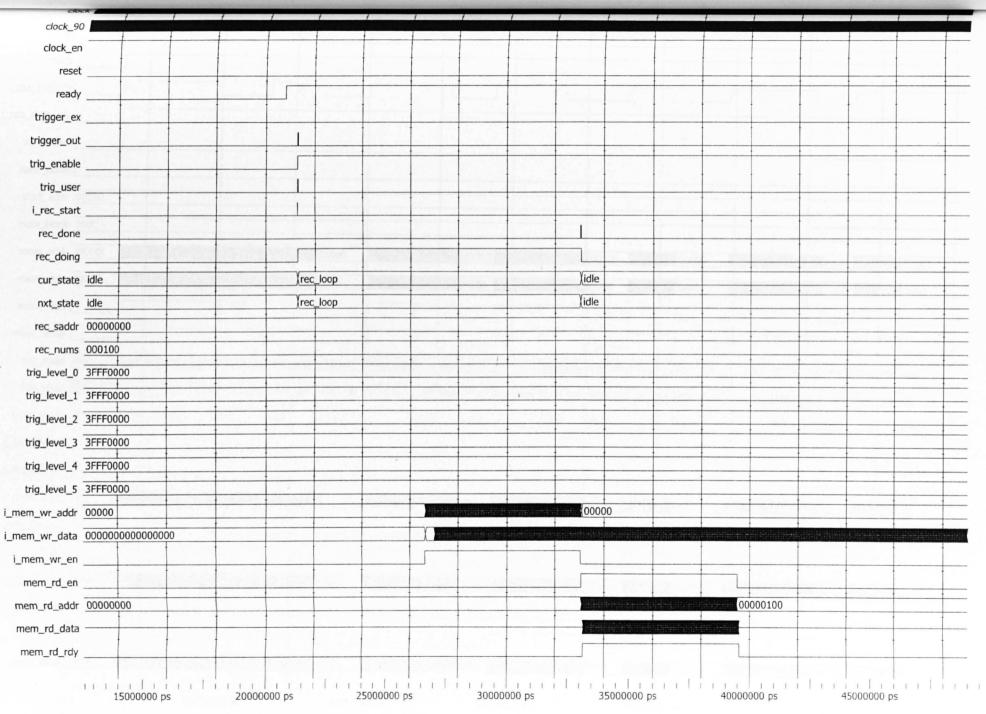

|   |       | 5.4.2 Capture Core                                      | 1 |

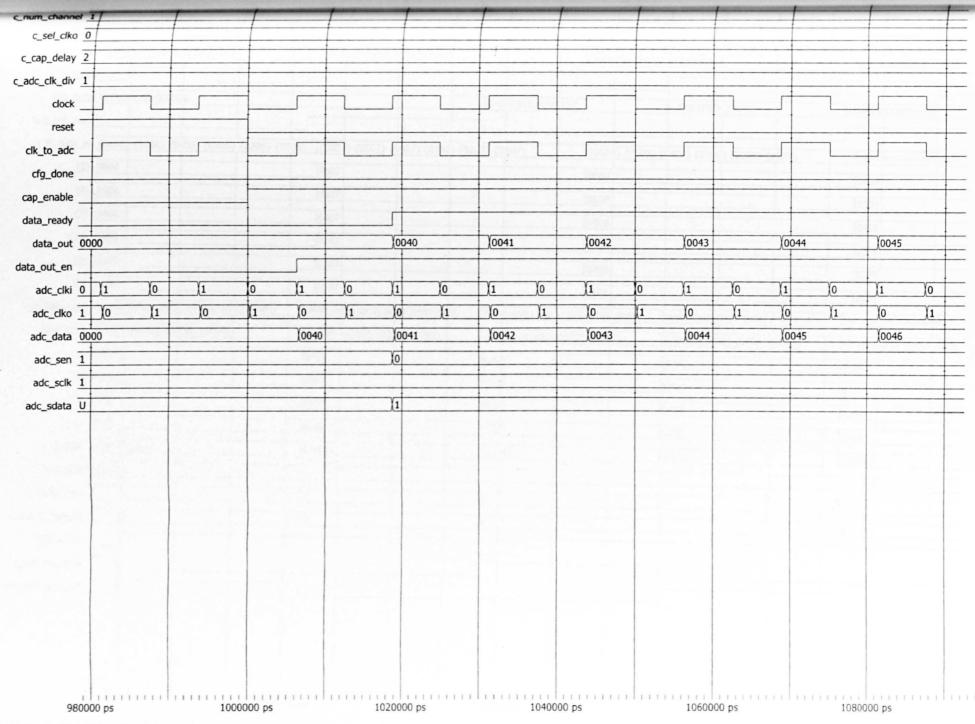

|   |       | 5.4.2.1 ADC Core                                        | í |

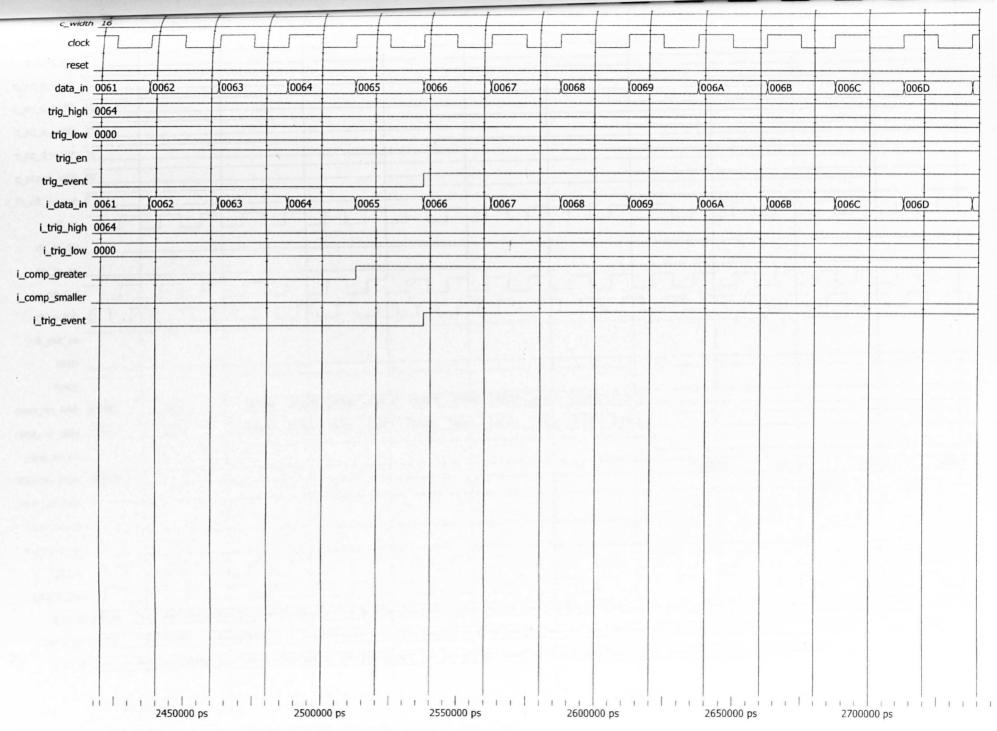

|   |       | 5.4.2.2 Trigger Detection Logic                         | ) |

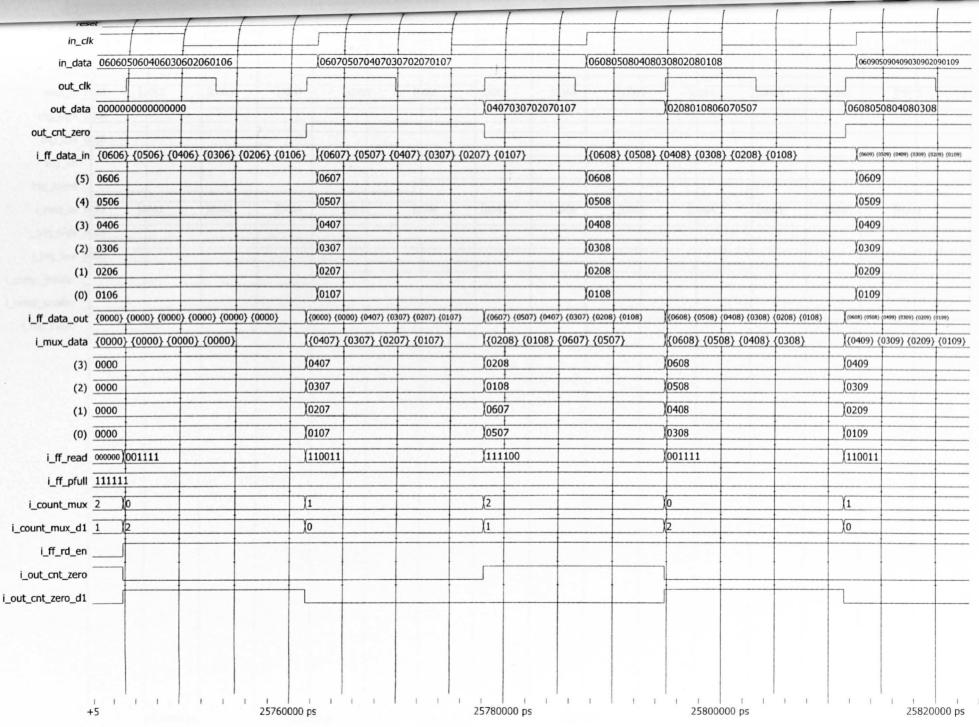

|   |       | 5.4.2.3 Multiplexer Controller                          | ) |

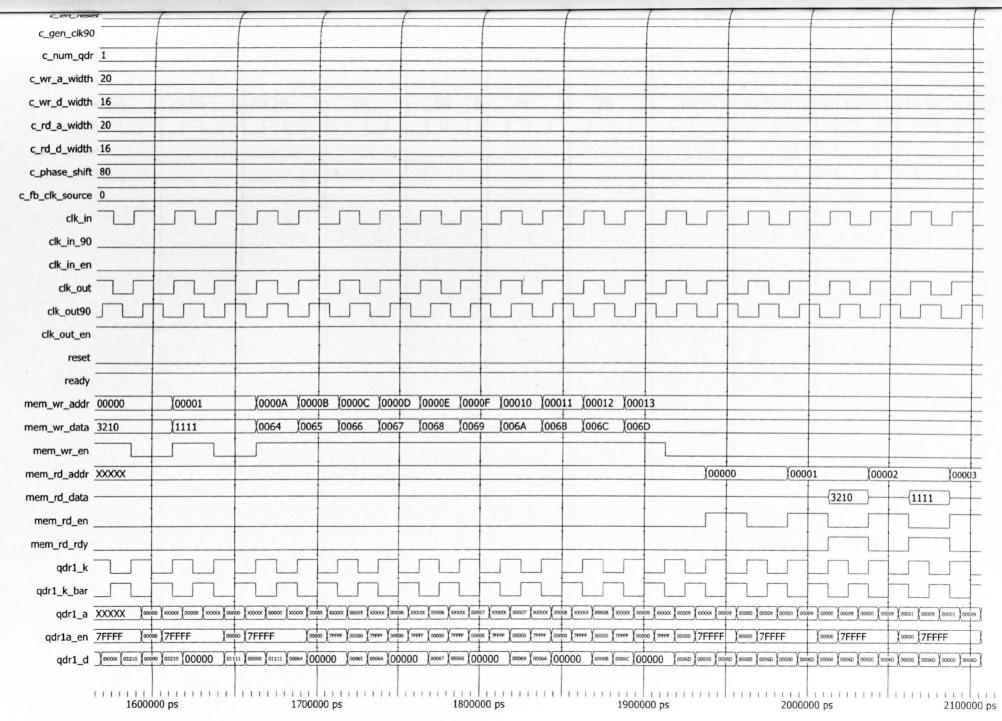

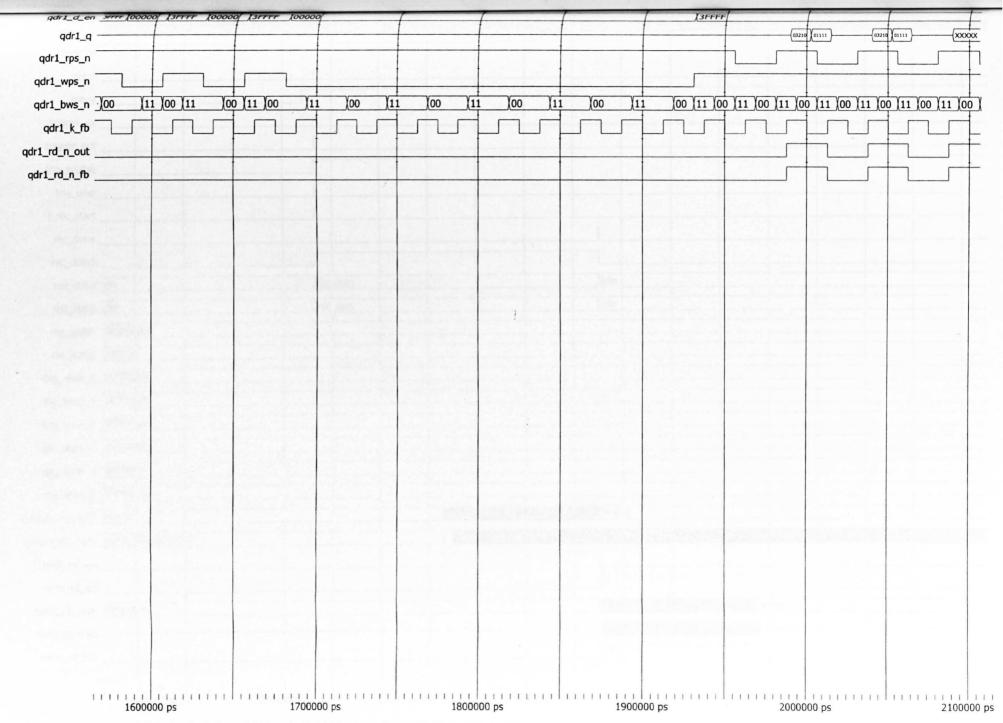

|   |       | 5.4.2.4 Memory Core                                     | 2 |

|   |       | 5.4.3 GPS Capture Core                                  | 1 |

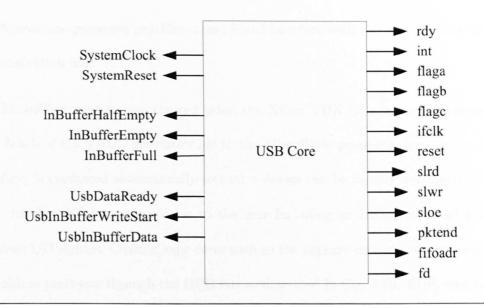

|   |       | 5.4.4 USB Core                                          | 5 |

|   |       | 5.4.5 MicroBlaze Processor                              |   |

|   |       | 5.4.5.1 Theory of Operation                             |   |

|   | 5.5   | Testing                                                 |   |

|   | 5.6   | Other Implementations                                   |   |

|   | 5.7   | Summary                                                 |   |

|   |       | 5.7.1 Hardware                                          |   |

|   |       | 5.7.2 FGPA                                              |   |

|   |       | 5.7.3 Software                                          |   |

|   |       | 5.7.5 Software                                          | , |

| 6 | Field | d tests and Laboratory tests 144                        | 1 |

|   | 6.1   | Introduction                                            | 1 |

|   | 6.2   | CELESC Distribution Line                                | 5 |

|   | 6.3   | Branched Communication Line                             | 5 |

|   |       | 6.3.1 Experimental Setup                                |   |

|   |       | 6.3.2 Results                                           |   |

|   |       | 6.3.3 Performance of Genetic Algorithm                  |   |

|   |       | 6.3.4 Limitations                                       |   |

|   | 6.4   | Summary                                                 |   |

|   |       |                                                         |   |

| 7 | Con   | clusions 170                                            | ) |

|   | 7.1   | Introduction                                            | ) |

|   | 7.2   | Time Tree Genetic Search Algorithm                      | 1 |

|   | 7.3   | Fault Recorder                                          | 3 |

|   | 7.4   | CELSEC distribution Line                                | 3 |

|   | 7.5   | Branched Communication Line                             | 5 |

|   | 7.6   | Suggestion for Further Work                             | 6 |

|   |       |                                                         |   |

|   |       |                                                         |   |

| A | Trav  | veling Wave Theory 17'                                  | 7 |

|   | A.1   | The Transmission Line Equation                          |   |

|   | A.2   | Multi-Phase Transmission Lines                          |   |

|   | A.3   | Fault Events on Single Phase Systems                    |   |

|   | 11.0  | A.3.1 Reflections at Impedance Discontinuities          |   |

|   |       | A.3.2 Reflections at Fault Locations                    |   |

|   |       | A.3.3 Reflections at Intersections of Multiple Lines    |   |

|   |       | 11.0.0 Treflections at Intersections of Withtiple Lines | 1 |

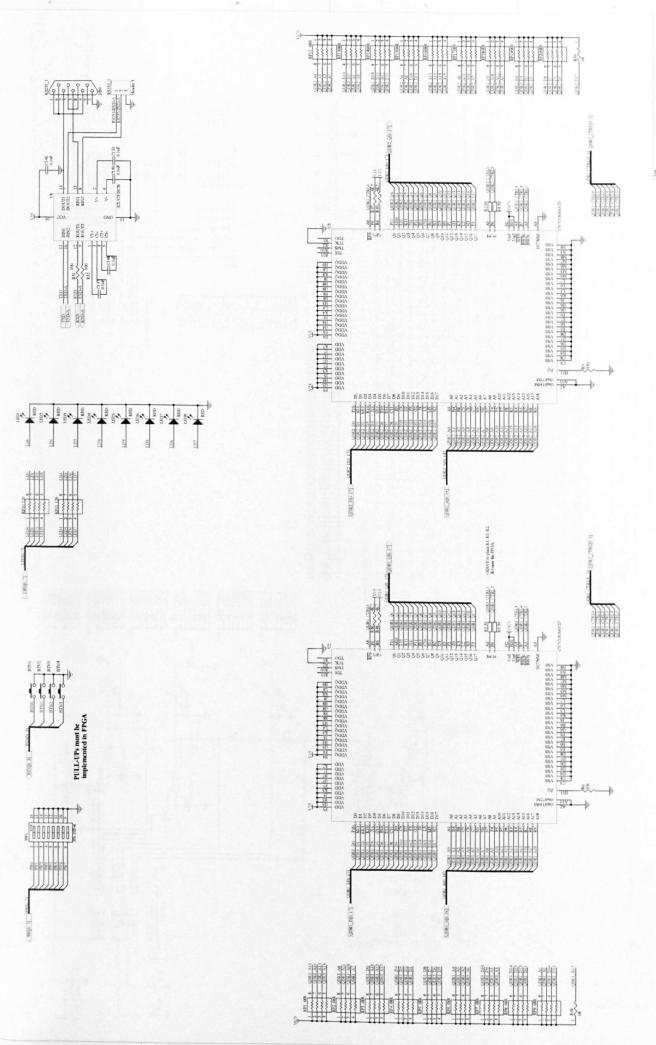

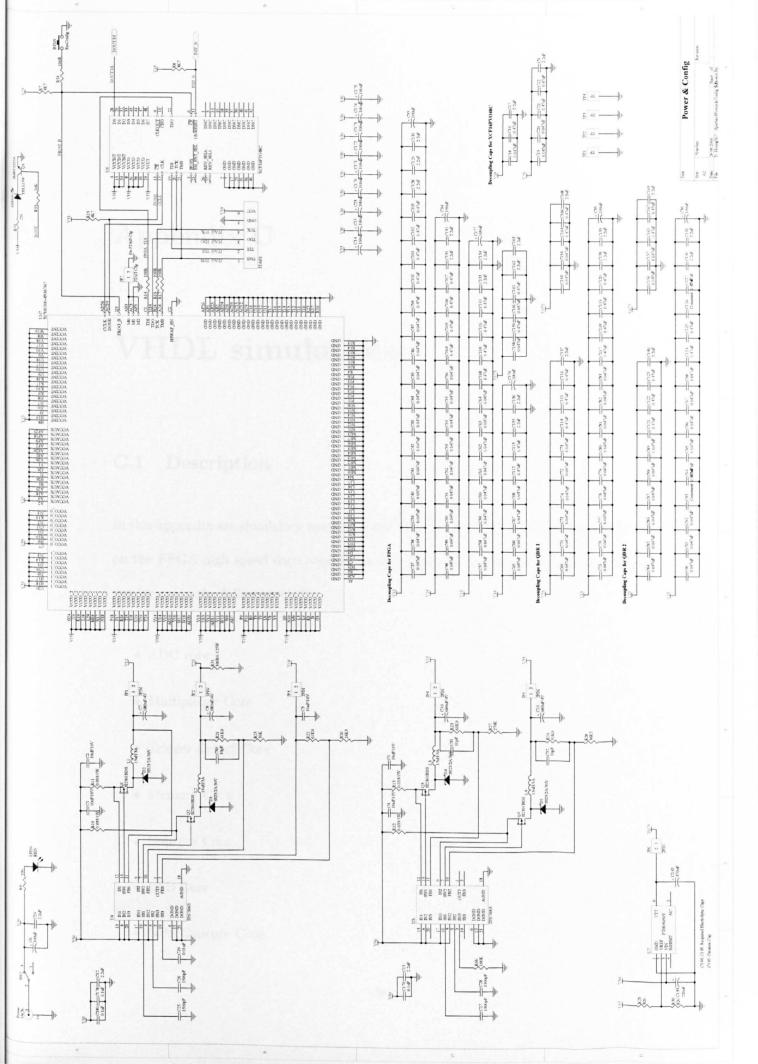

| В | Fau   | It Recorder Schematics 189                              | 9 |

|   | B.1   | Description                                             | 9 |

| Contents                           | vii        |

|------------------------------------|------------|

| C VHDL simulations C.1 Description | <b>190</b> |

| D.1 Introduction                   | <b>191</b> |

| Bibliography                       | 223        |

# List of Figures

| 2.1  | Types of Faults                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | Classification of fault location methods                                                                                                                       |

| 2.3  | Types of traveling wave fault location                                                                                                                         |

| 2.4  | Bewley lattice diagram                                                                                                                                         |

| 2.5  | Traveling wave pattern observed at substation A $\dots \dots $ |

| 3.1  | Fault Conductance Matrix                                                                                                                                       |

| 3.2  | One-line diagram of simple transmission line                                                                                                                   |

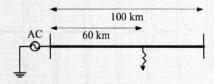

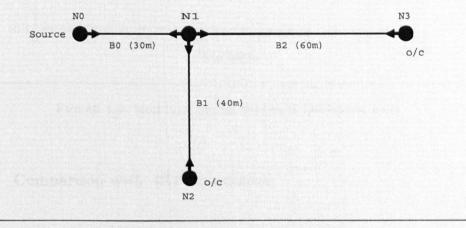

| 4.1  | Diagram of simple distribution line                                                                                                                            |

| 4.2  | Distance Branch Array Voltages                                                                                                                                 |

| 4.3  | Depiction of current flow                                                                                                                                      |

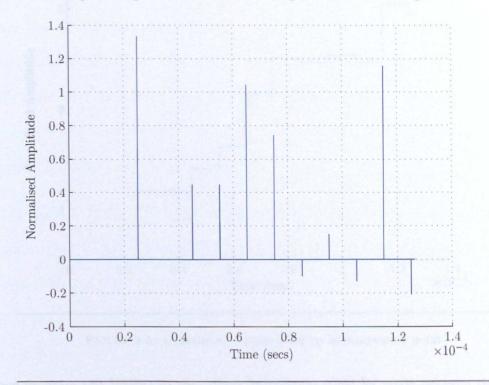

| 4.4  | Ideal fault current impulse at observation point                                                                                                               |

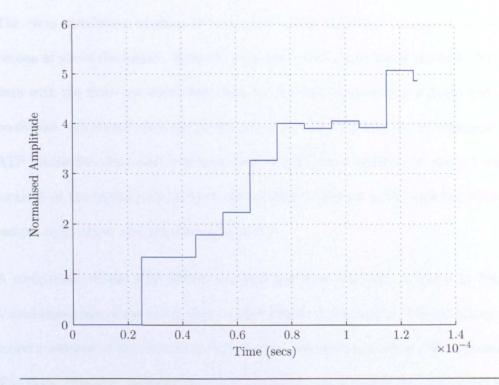

| 4.5  | Cumulative current build up at observation point                                                                                                               |

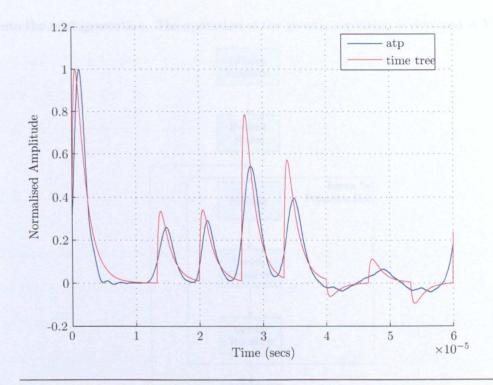

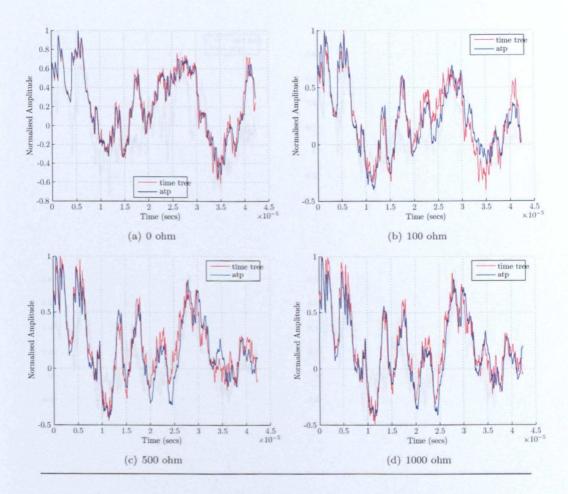

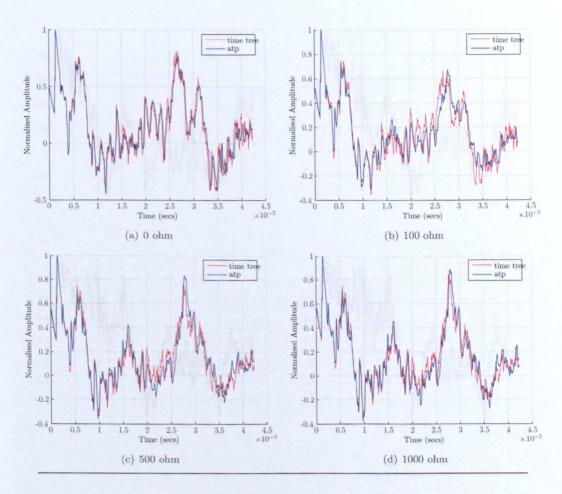

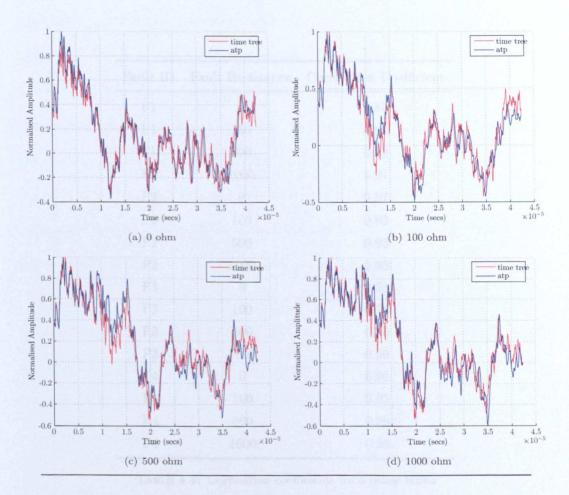

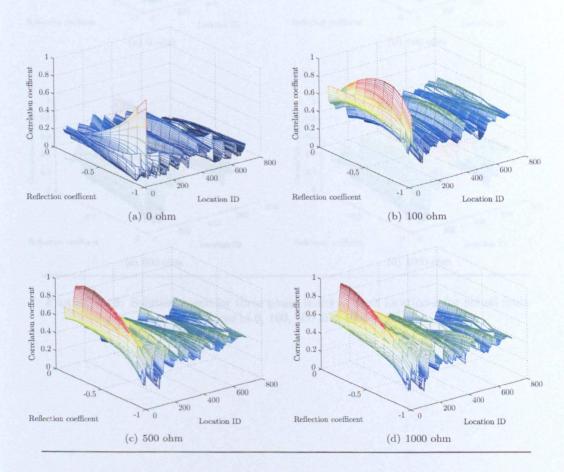

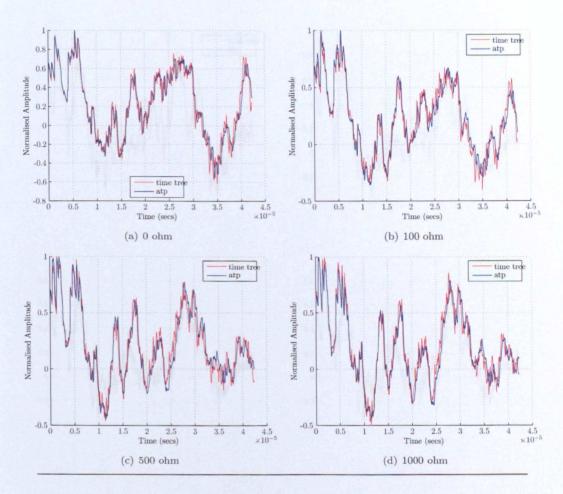

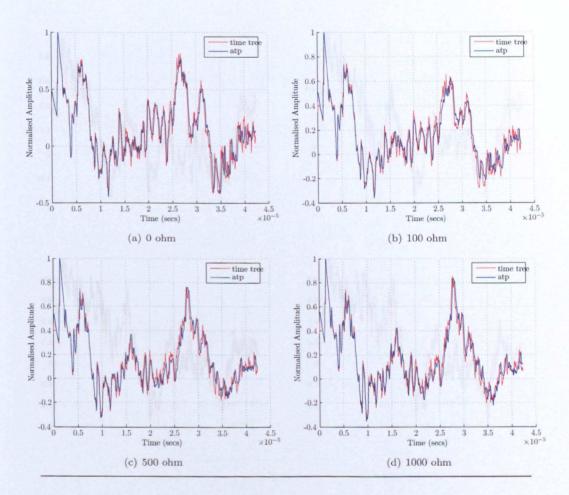

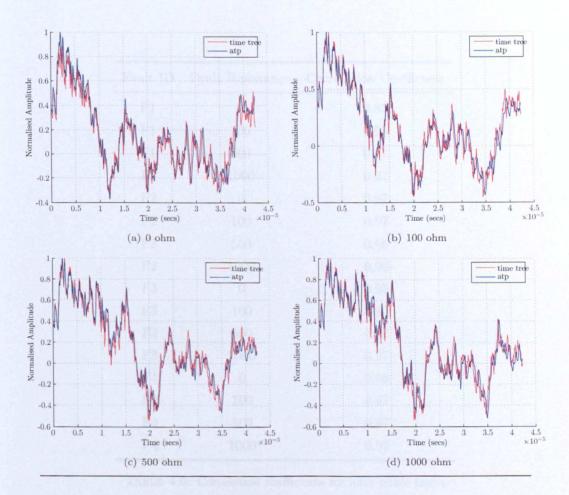

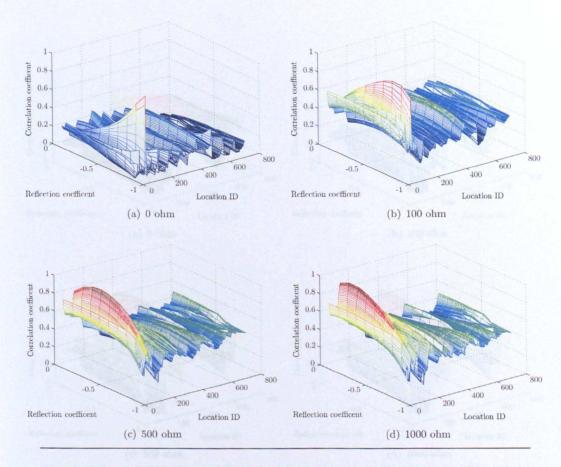

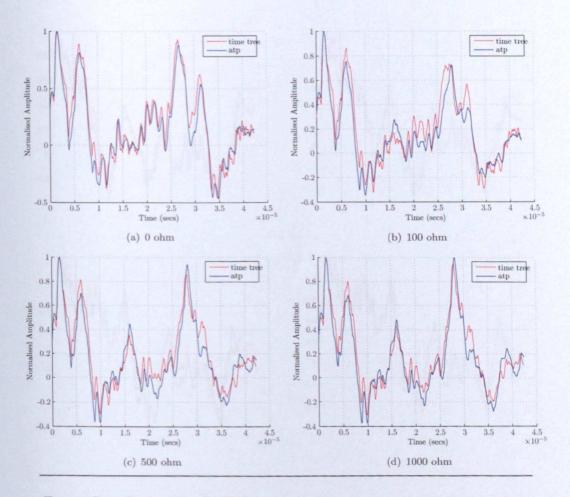

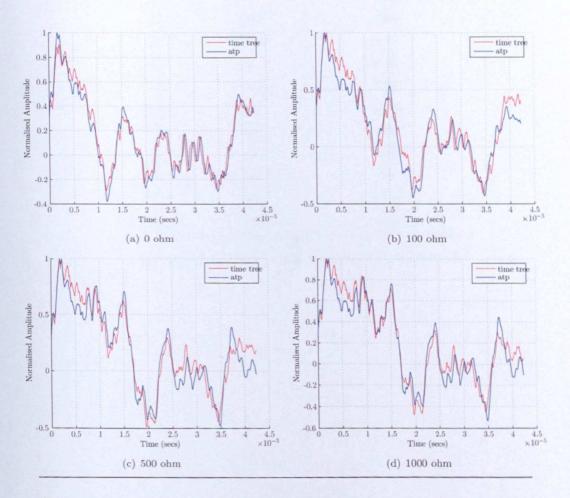

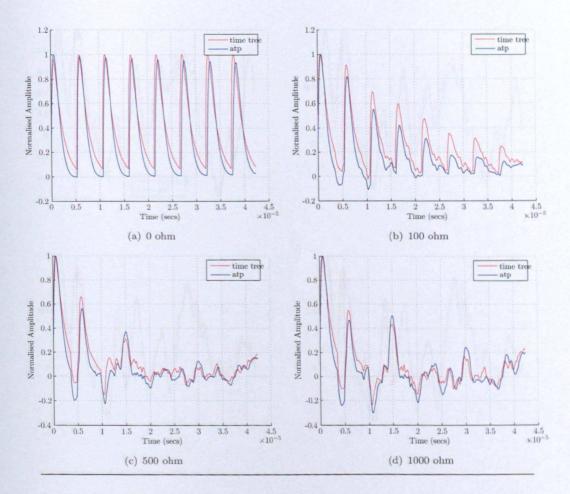

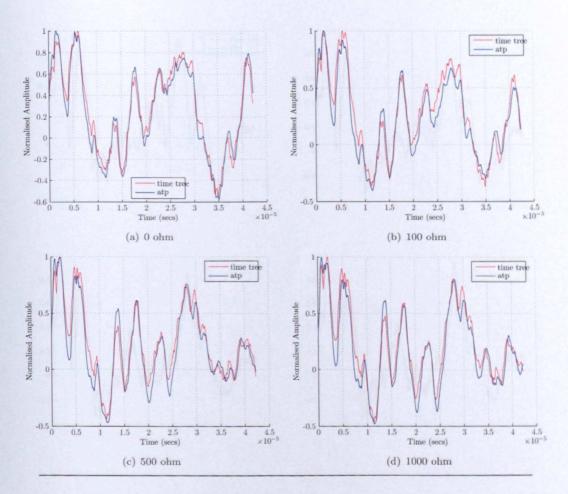

| 4.6  | Comparison of time tree simulation and ATP simulation for a three phase                                                                                        |

|      | fault                                                                                                                                                          |

| 4.7  | Diagram depicting operation of genetic algorithm                                                                                                               |

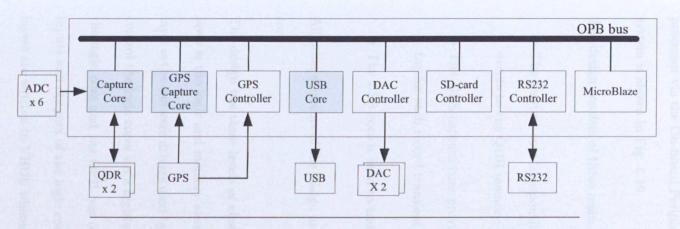

| 5.1  | High level block diagram of FPGA system                                                                                                                        |

| 5.2  | Photograph of main FPGA board without daughter cards 107                                                                                                       |

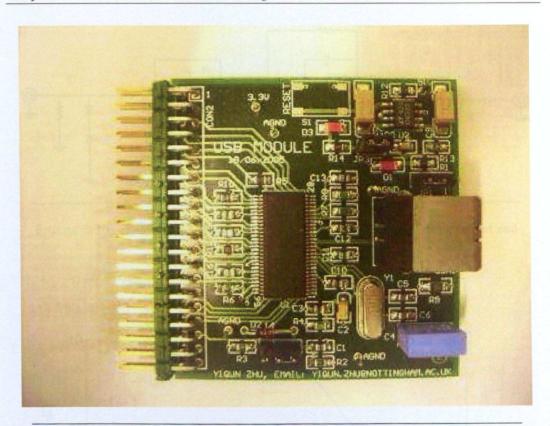

| 5.3  | Photograph of main FPGA board with daughter cards                                                                                                              |

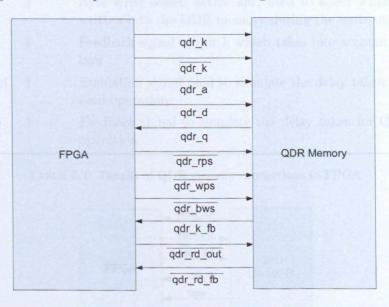

| 5.4  | Connections between FPGA and QDR memory                                                                                                                        |

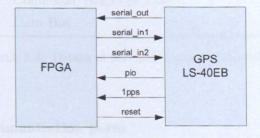

| 5.5  | Connections between FPGA and GPS Receiver                                                                                                                      |

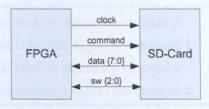

| 5.6  | Connections between FPGA and SD-card reader                                                                                                                    |

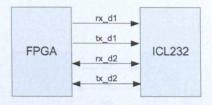

| 5.7  | Connections between FPGA and RS232 transceiver                                                                                                                 |

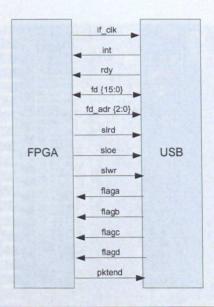

| 5.8  | Connections between FPGA and USB daughter card                                                                                                                 |

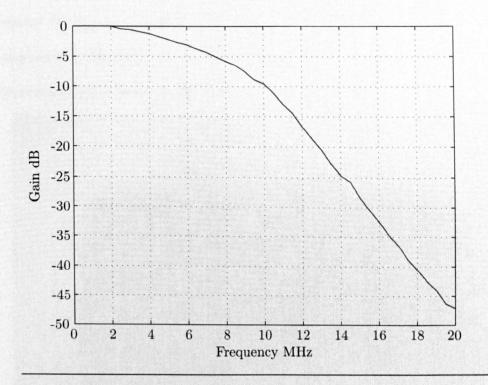

| 5.11 | Frequency response of anti-aliasing filter                                                                                                                     |

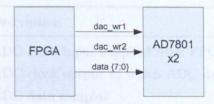

| 5.12 | Connections between FPGA and DACs on front-end board 116                                                                                                       |

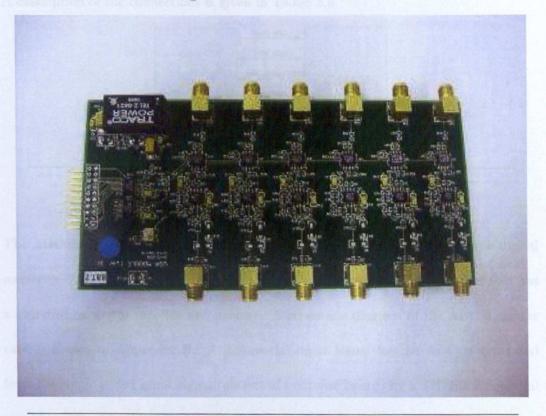

|      | Photograph of populated front end board                                                                                                                        |

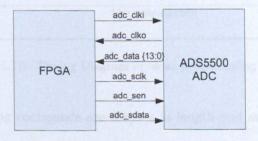

|      | Connections between FPGA and one ADC socket                                                                                                                    |

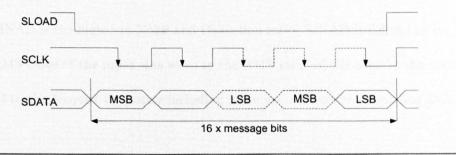

|      | Timing Diagram of serial programming interface                                                                                                                 |

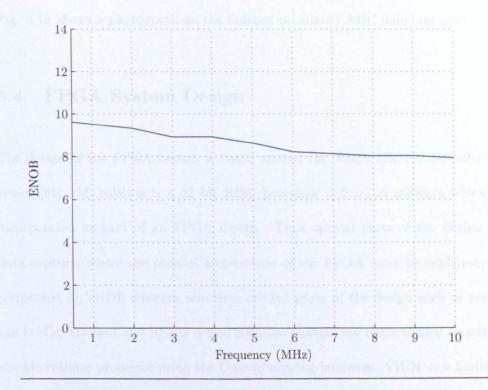

|      | ADC daugther card ENOB performance against frequency                                                                                                           |

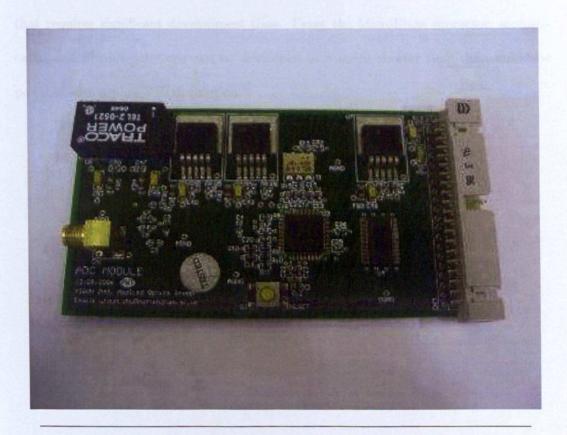

|      | Photograph of populated ADC daughter card                                                                                                                      |

|      | Top level diagram of FPGA system                                                                                                                               |

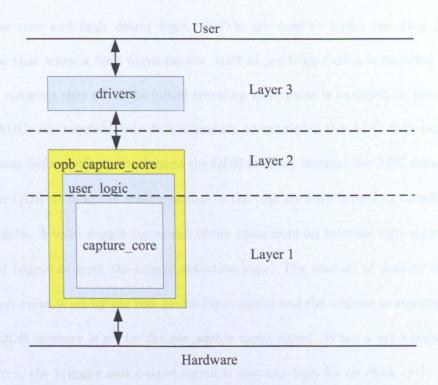

|      | Levels of abstraction                                                                                                                                          |

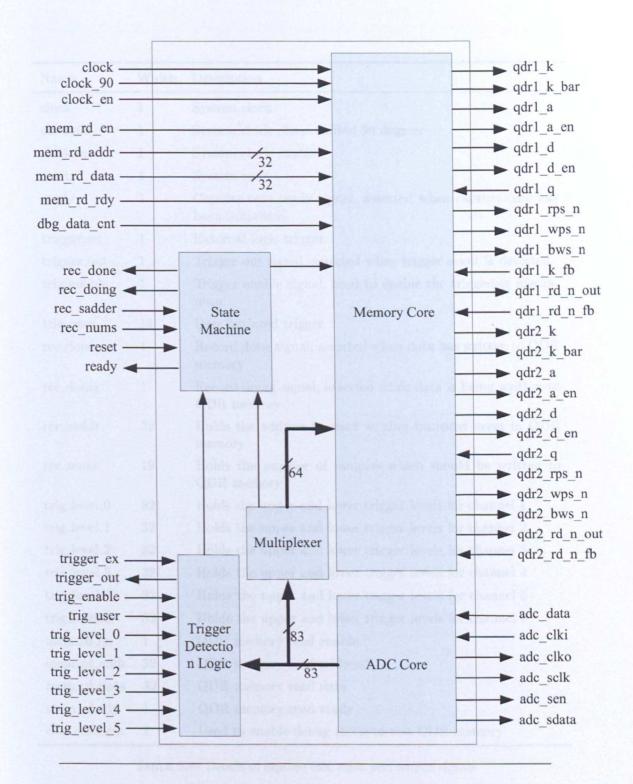

|      | Diagram of capture core                                                                                                                                        |

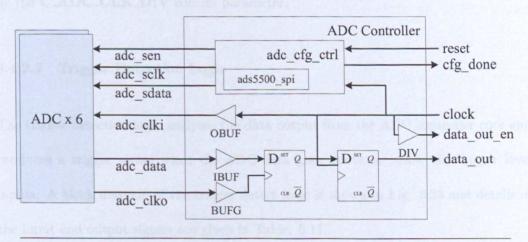

|      | Diagram of ADC controller core                                                                                                                                 |

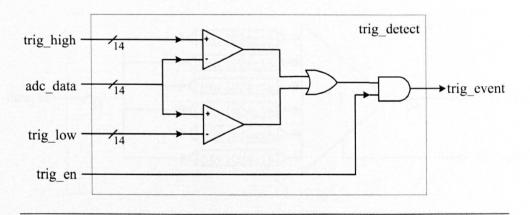

|      | Diagram of Trigger Detect Core                                                                                                                                 |

List of Figures

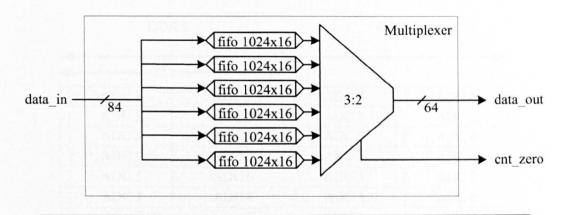

| 5.24 | Diagram of Multiplexer core                             |  |  |  |   | 131 |

|------|---------------------------------------------------------|--|--|--|---|-----|

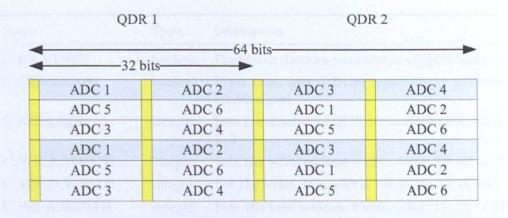

| 5.25 | Diagram showing how ADC data is stored in QDR memory    |  |  |  | ķ | 132 |

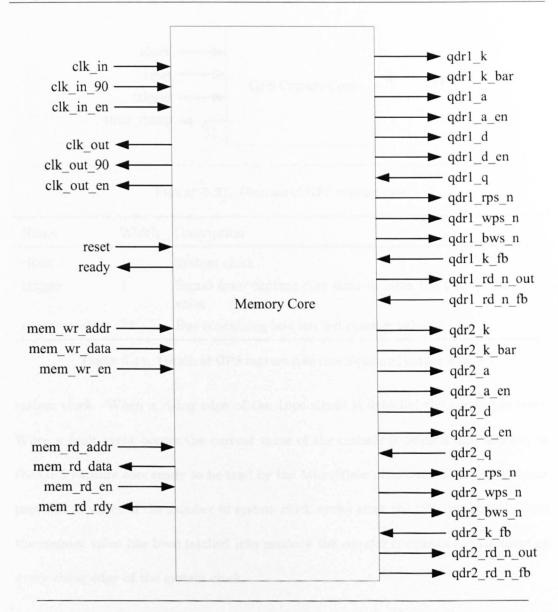

| 5.26 | Diagram of Memory Controller                            |  |  |  | ě | 134 |

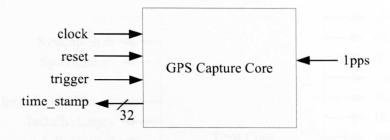

| 5.27 | Diagram of GPS capture core                             |  |  |  |   | 135 |

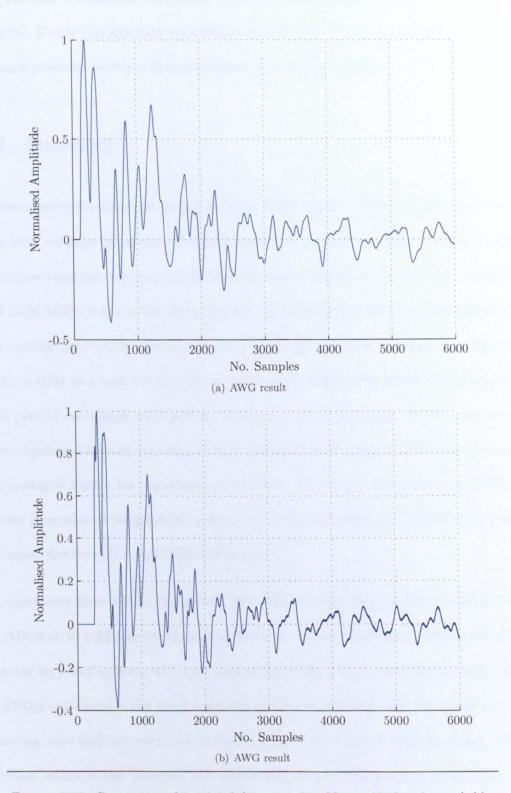

| 5.29 | Comparison of simulated and recorded data $\dots \dots$ |  |  |  | , | 140 |

| 10   |                                                         |  |  |  |   |     |

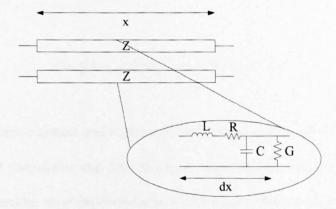

|      | Two conductor transmission line                         |  |  |  |   |     |

| A.2  | Equivalent circuit of initial fault condition           |  |  |  |   | 184 |

| A.3  | Reflection of a traveling wave at a fault location      |  |  |  |   | 186 |

| A.4  | Reflection between multiple lines                       |  |  |  |   | 187 |

|      |                                                         |  |  |  |   |     |

# List of Tables

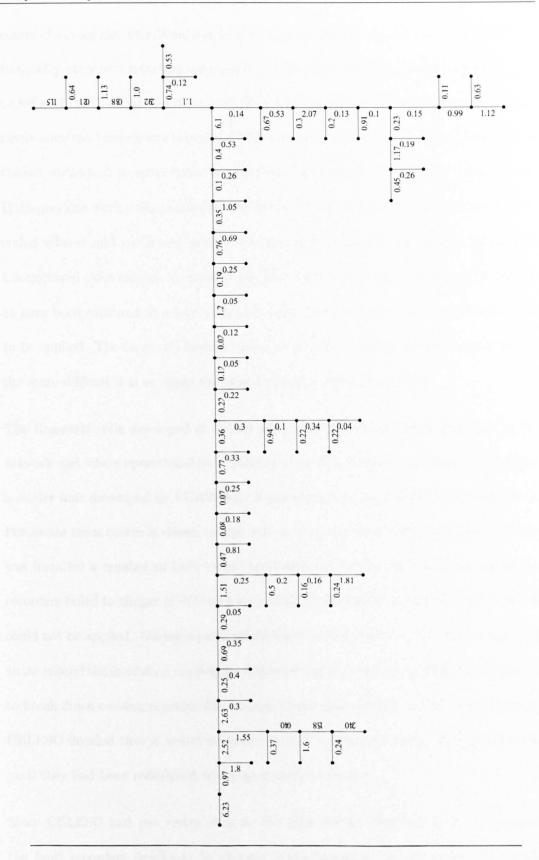

| 4.1  | Details of branch lengths                                                      |

|------|--------------------------------------------------------------------------------|

| 4.2  | Details of fault locations                                                     |

| 4.3  | Fault reflection coefficients                                                  |

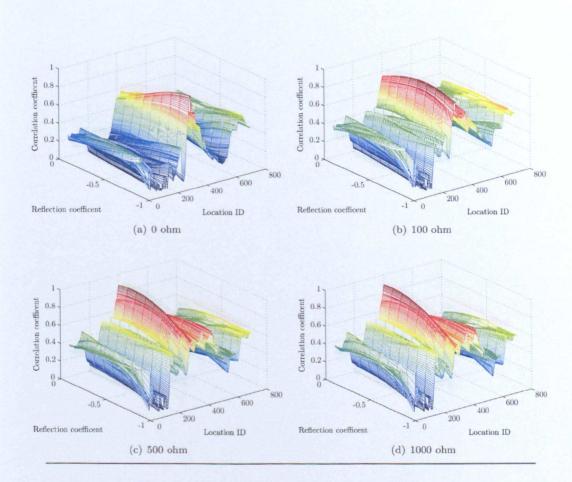

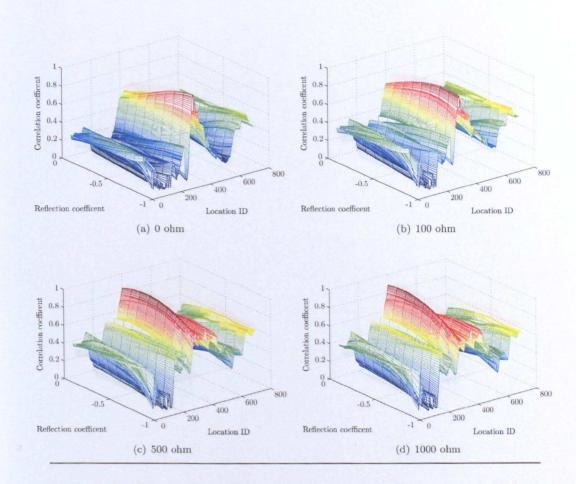

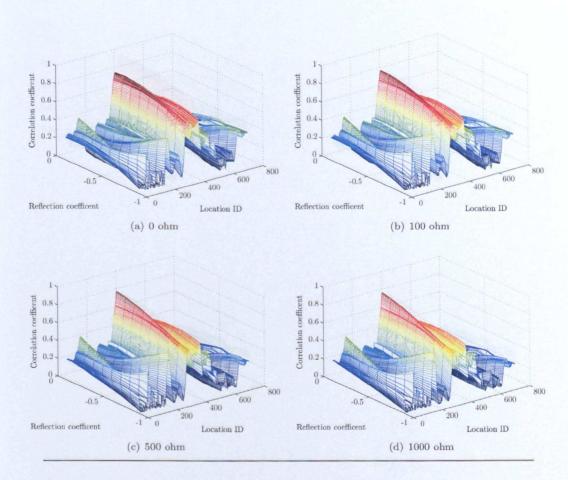

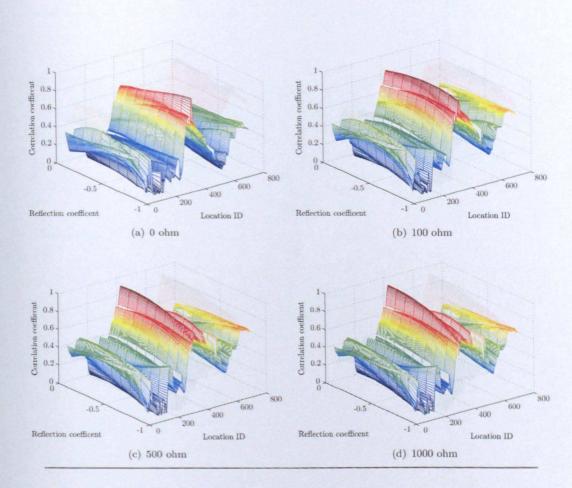

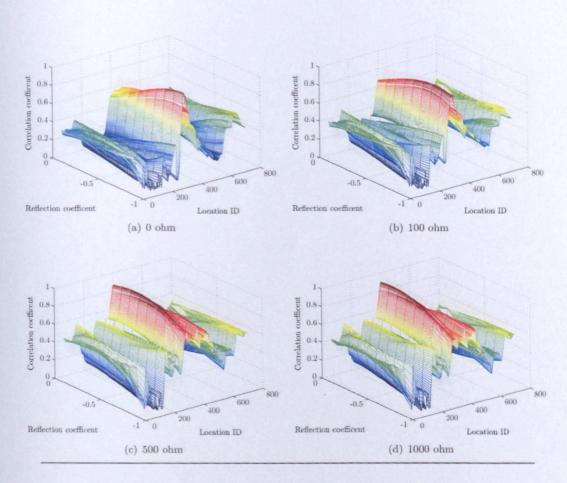

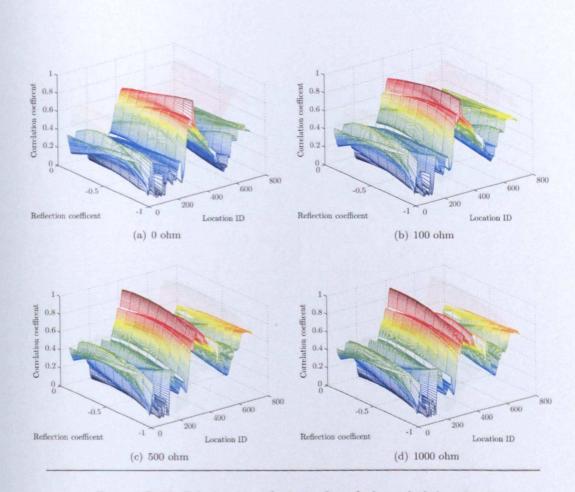

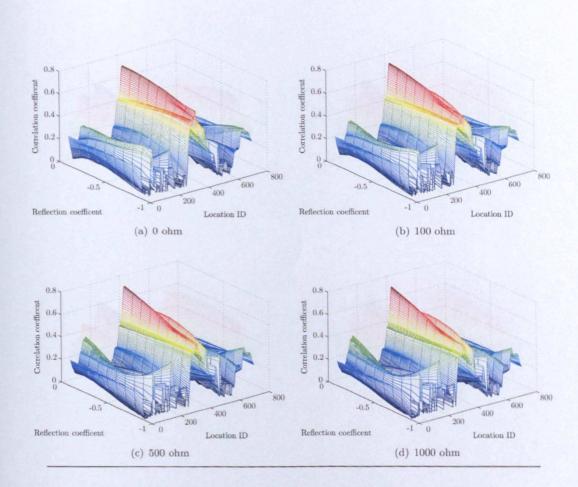

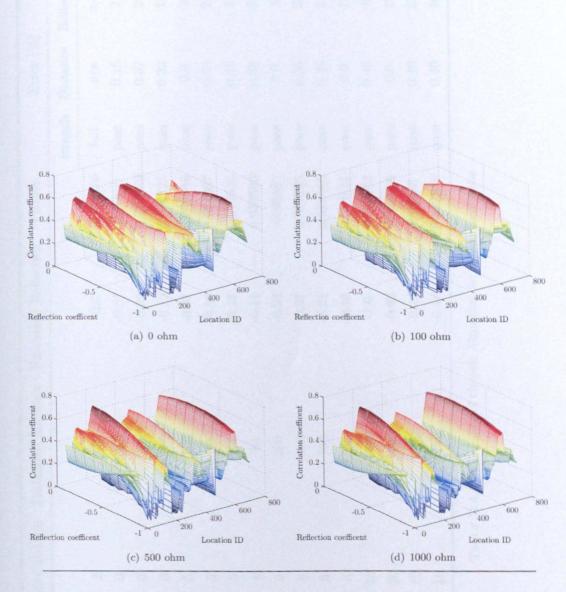

| 4.4  | Correlation coefficients for 3 phase faults                                    |

| 4.5  | Location ID for each branch in CELESC network                                  |

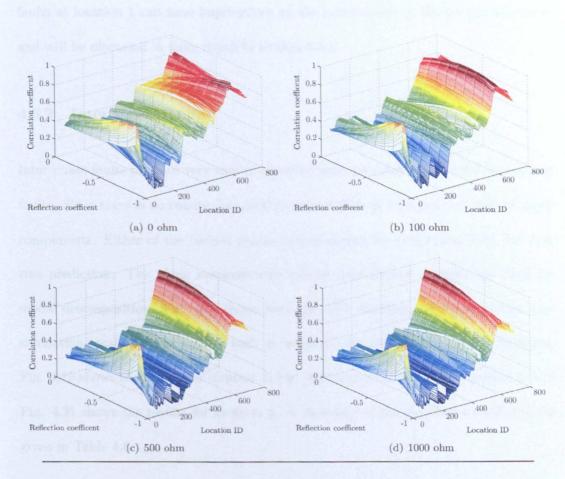

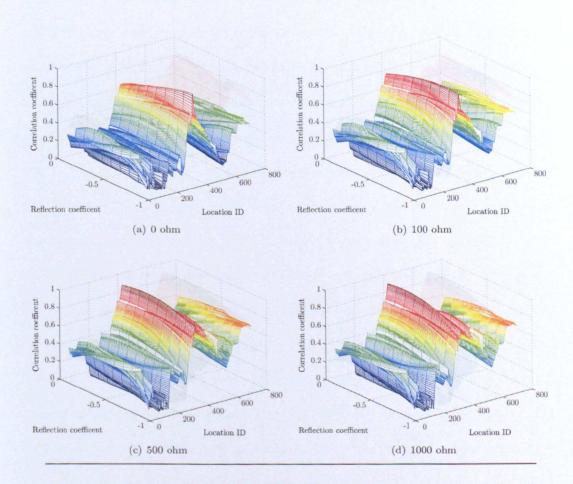

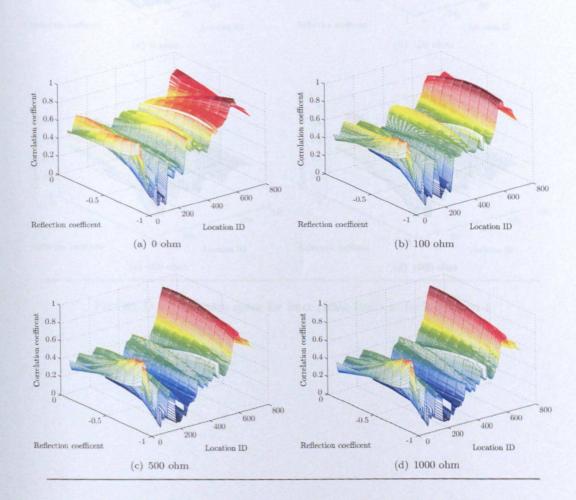

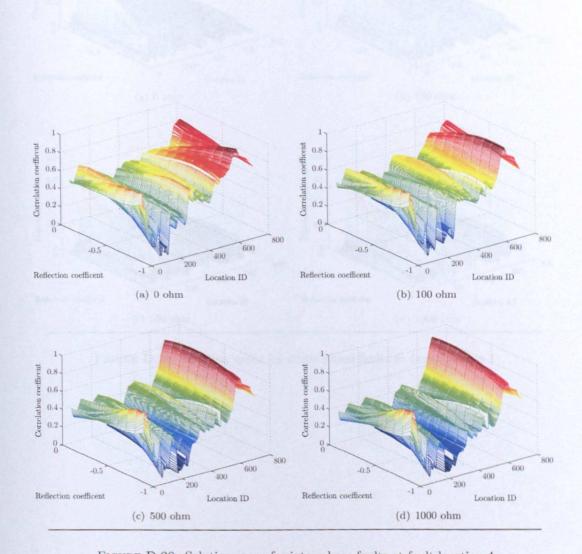

| 4.6  | Correlation coefficients for inter phase faults                                |

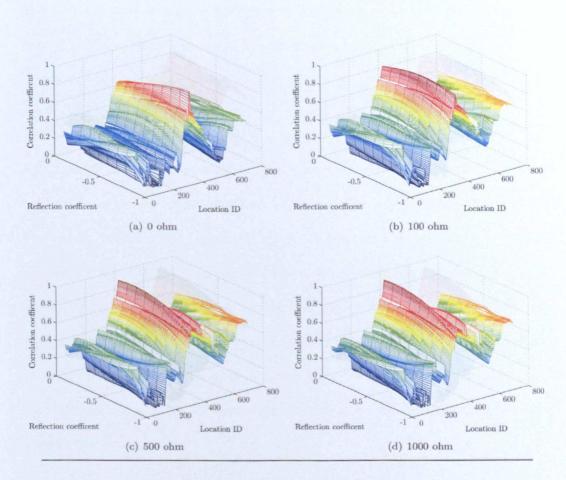

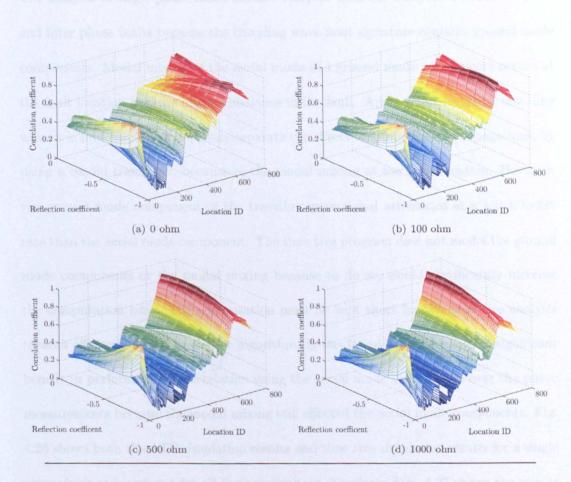

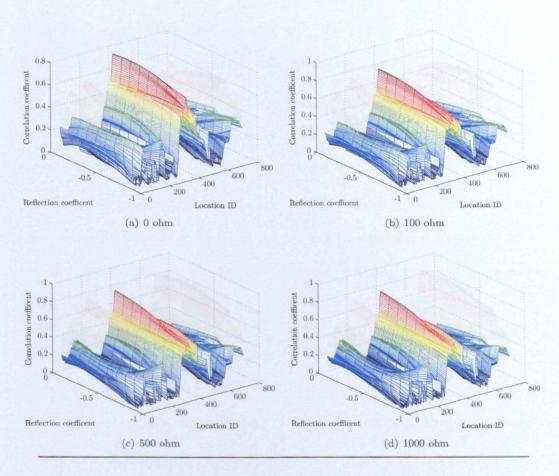

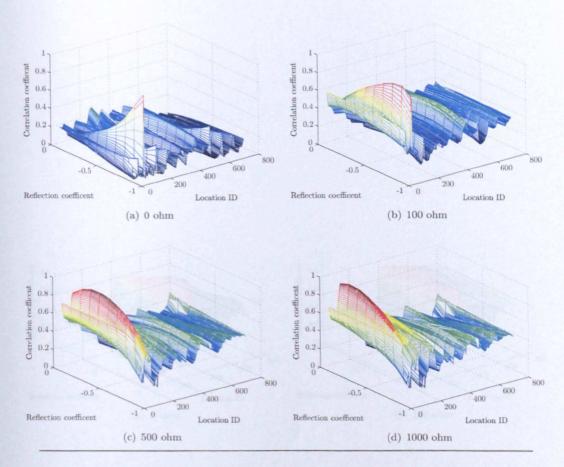

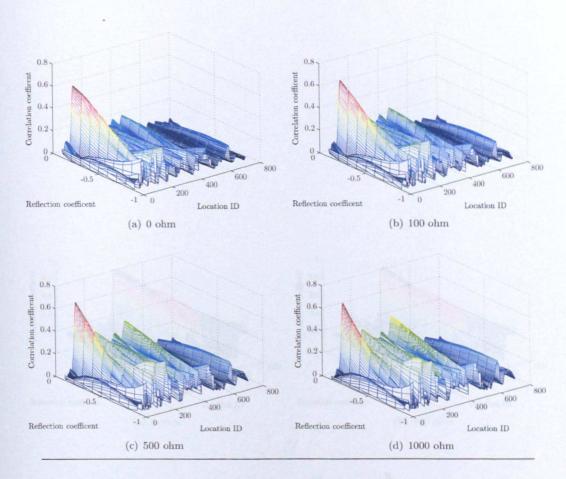

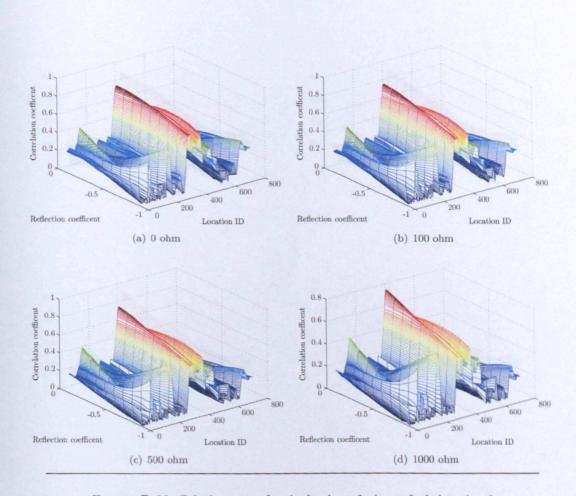

| 4.7  | Correlation coefficients for single phase faults                               |

| 4.8  | Performance of Genetic Algorithm for three phase faults                        |

| 4.9  | Performance of Genetic Algorithm for inter phase faults                        |

| 4.10 | Performance of Genetic Algorithm for single phase faults                       |

| 5.1  | Details of QDR memory connections to FPGA                                      |

| 5.2  | Details of GPS connections to FPGA                                             |

| 5.3  | Details of SD-card connections to FPGA                                         |

| 5.4  | Details of RS232 connections to FPGA                                           |

| 5.5  | Details of usb connections to FPGA                                             |

| 5.6  | Details of ADC connections to FPGA                                             |

| 5.7  | Details of Xilinx VHDL primitives                                              |

| 5.8  | Details of capture core input and output signals                               |

| 5.9  | Details of ADC core generic parameters                                         |

| 5.10 | Details of ADC core input and output signals                                   |

| 5.11 | Details of trigger detection input and output signals                          |

|      | Details of multiplexer controller input and output signals                     |

| 5.13 | Details of memory core generic parameters                                      |

| 5.14 | Details of memory core input and output signals                                |

| 5.15 | Details of GPS capture core core input and output signals                      |

| 5.16 | Details of GPS capture core core input and output signals                      |

| 6.1  | Details of fault locations                                                     |

| 6.2  | Details of branched communication line                                         |

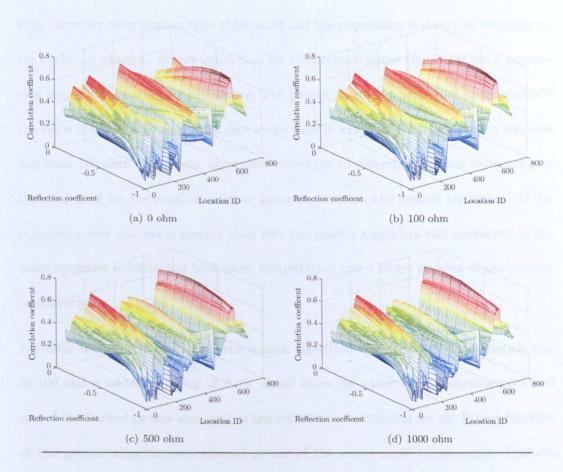

| 6.3  | Correlation coefficients for faults on RG-58 coaxial cable branched network159 |

| 6.4  | Performance of Genetic Algorithm on Branched Network using TDR                 |

|      | Analysis                                                                       |

| D.1  | Correlation coefficients for three phase faults                                |

| D.2  | Correlation coefficients for inter phase faults                                |

| D.3  | Correlation coefficients for singla phase faults                               |

| D.4  | Performance of Genetic Algorithm for three phase faults                        |

| List of Tables | X |

|----------------|---|

|----------------|---|

| D.5 | Performance of Genetic | Algorithm for inter phase faults  |

|-----|------------------------|-----------------------------------|

| D.6 | Performance of Genetic | Algorithm for single phase faults |

# **Abbreviations**

Acronym What (it) Stands For

AC Alternating Current

ADC Analogue to Digital Converter

ANN Artifical Neural Network

ATP Alternative Transient Program

AWG Arbitary Waveform Generator

CT Current Transformer

DAC Digital to Analogue Converter

DC Direct Current

DNO Distribution Network Operator

EHV Extra High Voltage

EMTP Electro Magnetic Transient Program

EMTDC ElectroMagnetic Transients including DC

ENOB Effective Number Of Bits

DCM Digital Clock Manager

DLL Digital Lock Loop

DSP Digital Signal Processor

EDK Embedded Development Kit

FIFO First In First Out

FPGA Field Programmable Gate Array

GA Genetic Algorithm

GPS Global Positioning System

JTAG Joint Test Action Group

MSPS Mega Samples Per Second

MV Medium Voltage

Abbreviations

OPB Onboard Peripheral Bus

PC Personal Computer

pps pulse per second

PROM Programmable Read Only Memory

QDR Quad Data Rate

SINAD Signal In Noise And Distortion

SPI Serial Programming Interface

TWFL Traveling Wave Fault Locator

USB Universial Serial Bus

UTC Coordinated Universal Time

VHDL Very high speed integrated circuit Hardware Description Language

VT Voltage Transformer

# **Physical Constants**

Speed of Light  $c = 2.997 924 58 \times 10^8 \text{ ms}^{-8}$

Electric Permittivity  $\epsilon_0 = 8.854 \ 187 \ 817 \times 10^{-12} \ \mathrm{Fm}^{-1}$

Magnetic Permeability  $\mu_0 = 4\pi \times 10^{-7} \text{ NA}^{-2}$

# Symbols

| C        | capacitance                    | F                  |

|----------|--------------------------------|--------------------|

| L        | inductance                     | Н                  |

| R        | resistance                     | Ω                  |

|          |                                |                    |

| ρ        | reflection coefficient         |                    |

| T        | transmission coefficient       |                    |

|          |                                |                    |

| ω        | angular frequency              | rads <sup>-1</sup> |

| $\gamma$ | propagation constant           |                    |

| α        | attenuation constant           |                    |

| β        | phase constant                 |                    |

|          |                                |                    |

| [S]      | modal voltage transform matrix |                    |

| [Q]      | modal current transform matrix |                    |

| [Y]      | admittance matrix              |                    |

| $[Z_s]$  | surge impedance matrix         |                    |

| [V]      | voltage matrix                 |                    |

| [I]      | current matrix                 |                    |

| [U]      | unit matrix                    |                    |

|          |                                |                    |

In memory of Dad...

# Chapter 1

# Introduction

### 1.1 Introduction to Thesis

The ability to successfully locate faults on power distribution systems has a significant impact on the reliability, safety, quality and economic performance of the network. There has been considerable investment in the power transmission system over the past two decades to develop a variety of different techniques to accurately and reliably locate faults. Transmission systems have been the main target for investment because of the widespread impact a fault can have on the performance of the network as well as the amount of time that is required to physically check the long transmission line lengths. In recent years however there has been increased interest and investment in applying fault location techniques to distribution networks.

Approximately 75 percent of all customer hours lost on the traditional power delivery system are as a result of faults that occur on the distribution network [1]. Since the introduction of deregulated market conditions and the emphasis on Distribution Network Operators (DNOs) to improve performance and promote efficiency, the importance of accurate fault location has increased.

Migrating the online fault location techniques developed for transmission networks to the distribution network is not a trivial task. There are many additional complexities introduced at the distribution level which must be accounted for if fault location methods are to be successful. These include, but are not limited to, the topologies of the network, the shorter lengths of the distribution lines, the loads connected to the network and the required accuracy. These factors must also be balanced with the financial investment required by the network operators.

Fault location techniques can be broadly classified into impedance based methods, traveling wave based methods and knowledge based methods. The work in this thesis investigates the transition of traveling wave based methods from transmission lines to branched radial distribution lines. When a short circuit fault occurs their is a sudden collapse of voltage at the fault location. The abrupt change in operating conditions causes high frequency traveling waves to be generated which propagate in both directions away from the fault. The location of the fault can be estimated by capturing the fault generated transient and making synchronised measurements at two or more locations on the transmission line and comparing the differences in the arrival times of the initial waves or by analysing the traveling wave pattern at one location and identify the time between the initial wave and the reflected wave from the fault location. Double ended methods have proven to be reliable on Extra High Voltage (EHV) transmission lines [2–5] but a consistently reliable single-ended scheme is more favourable because there is no need for a communication channel to exist between remote ends and there is also no need for accurate time synchronisation. The problem with existing single-ended fault location schemes is that it is difficult to always correctly identify the reflected wave from the fault location from other reflected waves.

On a distribution line the problem of identifying the wave reflected from the fault location

is made more difficult by the additional points of reflection resulting from sub-feeders that branch off the main line. For fault generated transients, reflections from sub-feeder junctions tend to dominate over the reflection from the fault location [6]. There have been a number of proposals of how to perform single ended traveling wave fault location on radial distribution lines [7–9]. Most schemes still involve analysis of the fault waveform (or the features extracted from the fault waveform) by a skilled engineer.

The majority of fault location schemes that have been proposed for branched distribution lines have only been applied to simulated data. There are very few examples of traveling wave fault location schemes which have been applied to real distribution line fault data [10]. Commercially available traveling wave fault recorders were originally designed to be operated on transmission systems [11] and as such are not suited to the shorter lengths of distribution lines and the added complexities their topologies introduce. A higher sampling frequency and higher bit resolution is required to capture the traveling wave data at sufficient fidelity.

## 1.2 Objective of Thesis

It has already been established [9] that a technique called time tree analysis gives a good approximation to the traveling wave pattern simulated for a fault at a given location on a radial distribution line. Time tree analysis uses the principle of the Bewley lattice diagram which is a visual representation of wave propagations and points of reflection in a network. Time tree analysis uses a computer program to keep track of all the waves on a network following a disturbance. The key advantages of time tree analysis is the speed at which the traveling wave pattern can be calculated and the ease at which the network can be reconfigured to represent different fault conditions. A thorough investigation

into the performance of time tree analysis will be conducted for the most common types of faults and fault resistances to establish the maximum size and complexity of radial distribution line that time tree analysis can successfully represent.

Impedance based fault location schemes which use optimisation techniques such as genetic algorithms have been proposed for transmission networks [12, 13] but so far have not been applied to traveling wave data. One of the main reasons for this is the long computation time that is required for traveling wave simulations. In this thesis the fast calculation and reconfigurability of time tree analysis will be exploited by using a genetic search optimisation algorithm to provide an autonomous fault location scheme for single ended traveling wave data on a radial distribution line. Initially this will be evaluated against simulated network data.

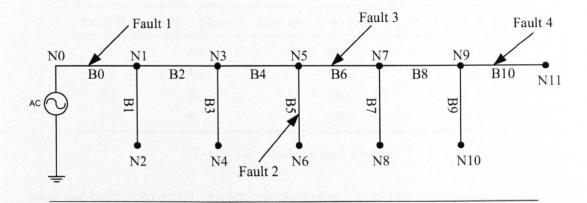

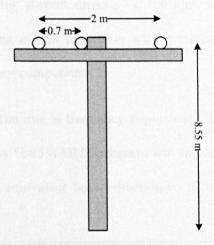

A new high speed fault recorder will be designed and constructed, capable of recording traveling wave fault data from distribution lines. The fault recorder will be deployed on a radial distribution line operated by CELESC power company. CELESC own and operate the distribution network in the Santa Caterina region of Brazil. They are currently involved in research activities with the Universidade Regional de Blumenau (FURB) to develop traveling wave based fault location schemes. They have kindly given access to part of their network.

It is proposed to evaluate the time tree genetic search algorithm with real fault data captured by the fault recorder installed in Brazil. To provide an alternative, if the recorder fails to record any fault data from the distribution line, a radial communication line will be used to evaluate the performance of the time tree genetic search algorithm. It will be shown that the time tree genetic search algorithm has numerous areas of applications other than power distribution lines.

The main objectives for the thesis are summarised below:

- Develop a genetic search algorithm based on the concept of time tree analysis to provide an automated single ended fault location scheme for branched distribution lines.

- Develop a new traveling wave fault recorder design for radial distribution systems

capable of recording high fidelity traveling wave data suitable for single ended fault

location as well as providing accurate time tagging of data so that double ended

fault location (where relative time is important) can also be applied.

- Evaluate the performance of the time tree genetic search algorithm against simulated and recorded data.

### 1.3 Outline of Thesis

The rest of this thesis is structured as follows.

Chapter 2 provides a comprehensive review of the existing techniques used for fault location on power systems as well as emerging schemes and technologies which have been proposed. An overview of the distribution network including typical network topologies, the types of faults that can occur and the most common methods of fault location are presented.

Chapter 3 looks at how traveling waves behave on a three phase power system and provides some examples of typical fault conditions.

Chapter 4 presents the proposed fault location method which combines the concept of time tree analysis with a genetic search algorithm to provide an autonomous method of estimating fault locations.

Chapter 5 gives an in depth description of the hardware design and FPGA/VHDL design of the new traveling wave fault recorder.

Chapter 6 presents the results and lessons learn from the deployment of the fault recorder on the distribution line in Brazil. The genetic algorithm is evaluated against a radial communication network which was constructed at the University of Nottingham.

Chapter 7 provides a summary of the work and the conclusions drawn. Areas for further work are identified.

# Chapter 2

# Fault Location

### 2.1 Introduction

This chapter reviews existing fault location methods and draws particular attention to the complications that the distribution network introduces. Fault location is one component of what is referred to as fault management, which includes fault protection, fault identification and system restoration. Although many of the analysis techniques described in this chapter have also been applied to fault protection, identification and to a limit extent restoration, their focus has been different. For example, fault protection is a real time technique in which the speed of operation is of primary concern. In contrast, fault location is an off-line analysis technique in which the speed of operation is not as crucial but accuracy is more important and time can be spent performing more complex calculations to improve the accuracy.

The traditional power delivery system consists of power generation, transmission, distribution, and consumption. Transmission networks deliver the energy generated at power stations over long distances to substations. The distribution network then delivers the power from the substation to the point of consumption. The distribution network differs from the transmission network in a number of key attributes [14]. The topology of transmission networks are normally point-to-point or mesh topologies connected through substation whereas the distribution network consist of many radial lines which are interconnected with each other. The topology of distribution networks are also more frequently subject to reconfiguration. The typical line lengths on transmission networks are of the order of hundreds of kilometres whereas on distribution networks, lengths are typically of the order of tens of kilometres. Sub-feeders that branch off the main distribution line are typically of the order of a kilometre or less. Unlike transmission networks, distribution networks have loads tapped off the main line at various points along its length. A more recent development has been the introduction of distributed generation to the distribution network. All of these differences introduce complications to the fault location at the distribution level. If the fault location schemes developed for the transmission network are to be adopted on the distribution network they must first be adapted to account for the additional complications. Further details of fault location techniques can be found in [15–17].

### 2.2 Short Circuit Faults

The causes of short circuit faults on a power network can vary largely. The frequency of certain types of faults depend on the geographical location of the network and the climate. For example, in tropical countries, a large proportion of faults are caused by lightning strikes. Power networks which are constructed from overhead lines are more susceptible to fault events. In most cases the cause of faults fall under one of the following categories [1]:

- Lightning

- Insulation failure

- Human Accident or Vandalism

- Vegetation or animals contacting the electrical circuits

Faults on an MV network can be either transient or permanent in nature. Transient faults are the most common type of faults and can be cleared by simply de-energizing the line for a short amount of time. Typically when a fault is detected on a network circuit breakers at the ends of the line operate to de-energize the line. After a short period of time an attempt is made to re-energize the line. If after a number of attempts, the circuit breakers still trip, the fault is assumed to be permanent and the line remains de-energized until the fault is located and repaired. Permanent faults require the fault location method to be as accurate as possible so that the fault can be identified, repaired and power restored in the shortest possible time.

For three phase power systems, faults can be classified as one of the following:

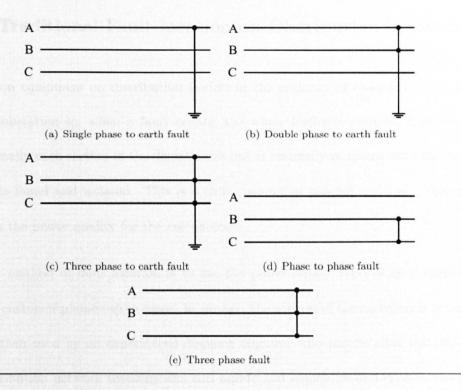

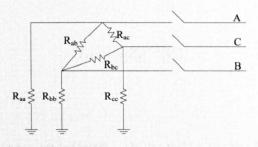

FIGURE 2.1: Types of Faults

- Single phase to earth fault. This can be either phase-A to earth, phase-B to earth or phase-C to earth. A phase-A to earth fault is shown in Fig. 2.1(a).

- Double phase to earth fault. This can be either phase-A to phase-B to earth, phase-A to phase-C to earth or phase-B to phase-C to earth fault. A phase-A to phase-B to earth fault is shown in Fig. 2.1(b).

- Three phase to earth fault. This is phase-A to phase-B to phase-C to earth and is shown in Fig. 2.1(c).

- Double phase fault. This can be either phase-A to phase-B, phase-A to phase-C or phase-B to phase-C. A phase-B to phase-C fault is shown in Fig. 2.1(d).

- Three phase fault. This is phase-A to phase-B to phase-C fault and is shown in Fig. 2.1(e).

### 2.3 Traditional Fault location on Distribution Systems

Protection equipment on distribution feeders in the majority of cases is only installed at the substation so, when a fault occurs, the whole feeder is removed from service. Traditionally each section of the distribution line is manually re-closed until the faulted section is found and isolated. This is a time consuming process and has a significant effect on the power quality for the customers.

Another method of fault location is to use the power outage reports from customers. When a customer phones up to report an outage, the address of the customer is recorded. This is then used by an experienced dispatch engineer who has detailed knowledge of the distribution network topology and can isolate and deploy ground crew to the most likely faulted section.

In both methods the location of the fault can only be resolved to the section of distribution line where the fault is located. This could represent a few kilometres of line length, depending on the network configuration, which would have to be manually patrolled to find the exact fault location. When a transient fault occurs, the dispatch engineer will not receive any outage reports as to when and where the fault occurred [14]. Transient faults may lead to permanent faults. Accurate information about transient faults can help DNO's take preventive action before the transient fault potentially becomes a permanent fault.

### 2.4 Methods of Fault Location

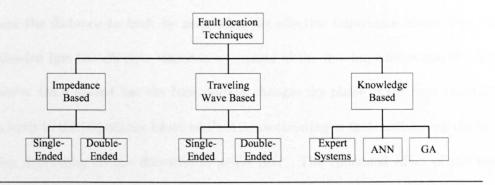

Fault Location methods can be broadly classified into impedance based methods, traveling wave based methods and knowledge based methods as shown in Fig. 2.2. Impedance

and traveling wave based methods can be further classified into single-ended and double-ended techniques. Double-ended methods require data to be recorded at two locations on the transmission or distribution line (typically at the line ends) and single-ended methods require data from one location only (typically at a substation).

FIGURE 2.2: Classification of fault location methods

### 2.4.1 Impedance Based Methods

Impedance based methods are concerned with measuring the power frequency phase voltages and currents to calculate the line impedance. The fault location is estimated by expressing the distance from substation to fault as a function of impedance. This can be achieved by single-ended or double-ended methods.

There are a number of examples proposed in the literature of both single-ended [18, 19] and double-ended [20, 21] fault location schemes. Impedance based methods are particularly attractive to DNOs because the phasor voltage and current measurements do not require expensive specialist measuring equipment.

The distribution network introduces complications to the impedance based methods in a number of ways [14, 15, 22]. Since most distribution lines have a radial or interconnected topology, a distance to the fault from the substation as a function of impedance can relate to more than one geographical location. Distribution lines that consist of both

underground and overhead lines do not have the same impedance along their length so there is not a simple linear relationship between distance and impedance. Distribution lines which have loads connected along their length contribute to the fault current and it is very difficult to predict their contributions in advance. Impedance based methods estimate the distance to fault by measuring the effective impedance of the line. On an unloaded line the effective impedance consists of the line impedance and the fault resistance. On a loaded line the fault current changes the phase of the fault resistance which leads to the impedance based method overestimating or underestimating the fault location depending on the direction of power flow. The combined effect of the fault resistance and load current is known as the reactance effect. A distribution system can either be solidly grounded, ungrounded or Peterson's coil / resistance grounded. Single phase faults that occur on the ungrounded and resistance grounded systems result in a much smaller fault current when compared with a solidly grounded distribution systems making it difficult to detect the fault.

Further details of impedance based fault location techniques which have been improved to cope with the additional complexities distribution lines present can be found in [23–25].

### 2.4.2 Traveling Wave Based Methods

Traveling wave fault location is a well known and established technique for accurately locating faults on E.H.V transmission lines [2–5, 26, 27]. There have been a number of schemes proposed for High Voltage Direct Current (HVDC) systems [28–30], underground power cables [31–33] and for radial distribution lines [6, 9, 34]. When a short circuit fault occurs on a transmission line or distribution line there is a sudden collapse in voltage at the fault location. The abrupt change in operation conditions causes high

frequency traveling waves, super imposed on the power frequency signal, to propagate in both directions away from the fault position. The traveling waves propagate at a velocity dictated by the electric permittivity and magnetic permeability of the surrounding medium. For overhead transmission lines, where the surrounding medium is air, the velocity of propagation is close to the speed of light. For underground cables the velocity of propagation is of the order of 2/3 the speed of light.

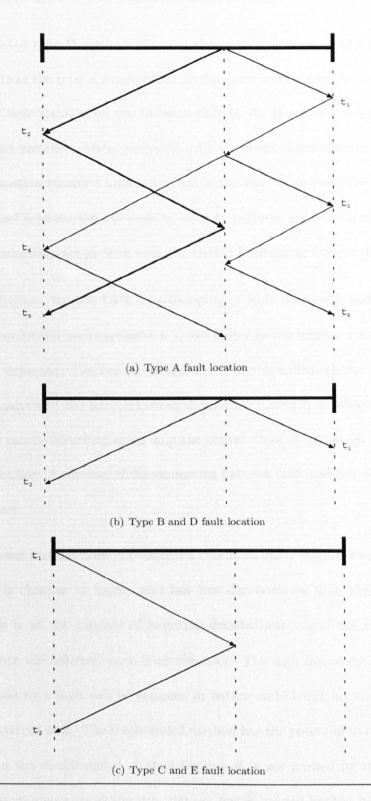

Traveling wave fault location is classified into types A, B, C, D and E modes of operation [35]. Their modes of operation are depicted in Fig. 2.3. Type A is a single-ended method which measures the fault generated transients at one location only and relies on identifying the second incident pulse reflected from the fault location. Type B and D are double-ended methods that require measurements from both ends of the line. In the type B method a timer is started when a traveling wave reaches the end of the transmission line nearest the fault. Traveling waves reaching the other end of the transmission line trigger a transmitter which sends a stop signal to the timer. The time delay can be used to calculate the distance to the fault. In the type D method the fault location is calculated using the absolute arrival times of the initial wave fronts at each end of the line. This is acheived by syncronising the recorders at each end using GPS timing. Type C method uses pulse generating equipment to inject a signal and can therefore only be used when the line is de-energised. Type E method uses the traveling waves generated from a circuit breaker re-closure when an attempt is made to re-energise the transmission line [27, 36]. Both methods work by measuring the time difference between the injection of a signal into the line at one end and subsequent reflection from the fault point.

The on-line methods are preferred to the off-line methods because they do not require special pulse generating equipment and can be used whilst the line is in operation.

FIGURE 2.3: Types of traveling wave fault location

On-line techniques are also able to identify transient faults.

The double-ended type D method has been shown on a number of deployments to be more reliable than the type A single-ended method and is currently the preferred implementation for fault location on transmission lines [4, 5]. However it requires twice the amount of fault recorders when compared with the single-ended scheme, and, since it requires information recorded from both ends of the line, there must also be a communication channel between the line ends in order to perform the calculation. To provide syncronised measurements at both ends the Global Positioning System (GPS) is used.

The communication channel, GPS time-stamping of fault transients, and multiple sets of recording equipment each represent a vulnerability to the scheme if any were to fail to operate as expected. The key advantage of the double-ended scheme is that is does not require analysis of the fault transient waveform to identify a reflected wave. The fault location can be identified using only the arrival times of the initial wave fronts at each end of the line. A method of discriminating between fault and non-fault transients is also necessary.

The single-ended method does not require a communication channel or accurate time-stamping so is cheaper to deploy and has less dependencies than the double-ended scheme. This is at the expense of requiring detailed analysis of the recorded wave-form to identify the reflected wave from the fault. The high frequency traveling wave patterns caused by a fault can be complex in nature and identifying the correct wave front is not a trivial task. The single-ended method has the potential to provide greater accuracy than the double-ended method because it is not limited by the accuracy of the GPS time-stamping (typically +/- 100 ns) but is instead limited by the sampling frequency of the recorder and the bandwidth of the transducers used to capture the

traveling waves. The closer a fault is to the fault recorder, the more difficult it is to identify the correct fault location using the single-ended scheme because the amount of time between the initial wave and the reflected wave is reduced.

In both the double-ended scheme and single-ended scheme, faults that occur close to zero inception angle are difficult to detect because the traveling waves which are produced are small. The advantages of traveling wave fault location over impedance based methods is the potential accuracy that is achievable. Typically impedance based methods at best can achieve an accuracy of between 2-5% of the line length [15], Traveling wave fault location has achieved accuracy to within 500m [4].

The accuracy of impedance based methods are affected by loads connected directly to the line because they contribute to the fault current and alter the effective impedance measured. Since most loads are inductive they appear as a large impedance at high frequencies so have little effect on the traveling waves propagating down the transmission line [37]. The same can be said for distributed generation that may be connected to the line [37].

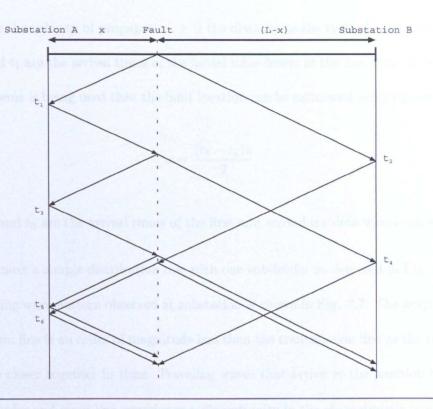

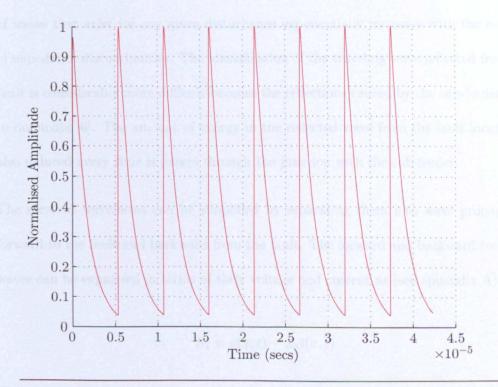

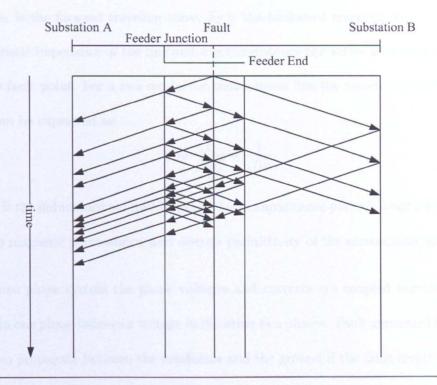

A Bewley lattice diagram [38] of a fault that has occurred on a transmission line is shown in Fig. 2.4. A fault has occurred a distance x from substation A. Traveling waves propagate in both directions towards substation A and substation B. Fig. 2.5 shows the traveling wave pattern observed at substation A for a fault that has occurred 1km from substation A. The total length of the transmission line is 3km. The signal has been high pass filtered to remove the power frequency component.

If the double-ended scheme is being used then the fault location can be estimated using equation (2.1):

$$x = \frac{(t_2 - t_1)u}{2} + \frac{L}{2} \tag{2.1}$$

Figure 2.4: A Bewley Lattice diagram depicting a fault that has occurred between substation A and substation B

Figure 2.5: Traveling wave pattern observed at substation A for a fault 1 km from substation A

where u is the velocity of propagation, x is the distance to the fault, L is the line length and  $t_2$  and  $t_1$  are the arrival times of the initial wave fronts at the line ends. If the single ended scheme is being used then the fault location can be estimated using equation (2.2)

$$x = \frac{(t_3 - t_1)u}{2} \tag{2.2}$$

where  $t_1$  and  $t_3$  are the arrival times of the first and second incident waves respectively.

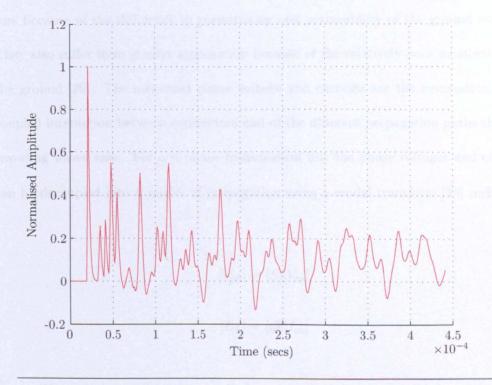

Consider next a simple distribution line with one sub-feeder as depicted in Fig. 2.6 and the traveling wave pattern observed at substation A shown in Fig. 2.7. The length of the distribution line is an order of magnitude less than the transmission line so the traveling waves are closer together in time. Traveling waves that arrive at the junction between the sub-feeder and main line experience a discontinuity in the characteristic impedance. This causes both reflected and transmitted traveling waves to be generated. The number of waves that exist for any given disturbance exponentially increases with the number of impedance discontinuities. The identification of the traveling wave reflected from the fault is considerably more difficult because the reflections caused by the sub-feeder tend to dominate [6]. The amount of energy in the reflected wave from the fault location is also reduced every time is passes through the junction with the sub-feeder.

The received waveforms can be simplified by separating them into wave propagating forward to the fault and backward from the fault. The forward and backward traveling waves can be expressed in terms of their voltage and current as (see appendix A):

$$S_1 = v(x,t) + Z_s i(x,t)$$

(2.3)

$$S_2 = v(x,t) - Z_s i(x,t) (2.4)$$

Figure 2.6: Bewley lattice diagram for a fault that has occurred on a distribution line with one sub feeder

FIGURE 2.7: Transient waveform observed at substation A for a fault that has occurred on a distribution line with one sub feeder

Where  $S_1$  is the forward traveling wave,  $S_2$  is the backward traveling wave,  $Z_0$  is the characteristic impedance of the line and x is the distance the waves have traveled away from the fault point. For a two conductor transmission line the velocity of wave propagation can be expressed as:

$$u = \frac{1}{\sqrt{LC}} = \frac{1}{\sqrt{\mu\epsilon}} \tag{2.5}$$

where L is the inductance per unit length, C is the capacitance per unit length, and  $\mu$  and  $\epsilon$  are the magnetic permeability and electric permittivity of the surrounding medium.

On a three phase system the phase voltages and currents are coupled together i.e. a current in one phase induces a voltage in the other two phases. Fault generated traveling waves can propagate between the conductor and the ground if the fault involves a conduction path to ground. Traveling waves that propagate in the ground have a velocity of propagation much lower than traveling waves that propagate just between the conductors because of the difference in permittivity and permeability of the ground medium. They also suffer from greater attenuation because of the relatively poor conductivity of the ground [39]. The measured phase voltage and currents are the summation of the coupled interaction between conductors and of the different propagation paths that the traveling waves take. For a n phase transmission line the phase voltages and currents can be decoupled into n modes of propagation using a modal transform [38] such that:

$$[V_{ph}] = [S][V_m] \tag{2.6}$$

$$[I_{ph}] = [Q][I_m]$$

(2.7)

where  $[V_m]$  are the modal voltages,  $[I_m]$  are the modal currents,  $[V_{ph}]$  are the phase voltages,  $[I_{ph}]$  are the phase curres, [S] is the modal voltage to phase voltage transform

matrix and [Q] is the modal current to phase current transform matrix. For a balanced three phase system, mode 0 (commonly known as ground mode), contains signals which have propagated through the ground. For a fully transposed line this is equivalent to the zero sequence component. Modes 1 and 2 (commonly known as aerial modes) contain signals which have traveled only between the conductors.

The characteristic impedance can be expressed in terms of the transmission lines inductance and capacitance per unit length as:

$$Z_s = \sqrt{\frac{L}{C}} \tag{2.8}$$

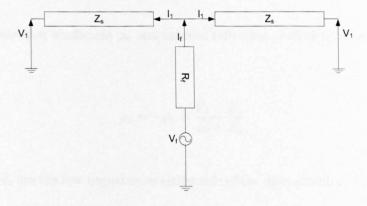

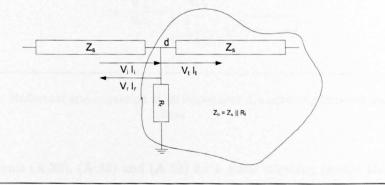

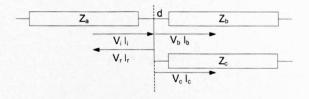

When a traveling wave reaches a discontinuity in the characteristic impedance of the line, such as at a busbar at a substation, a junction with a sub feeder, or the fault location itself, two waves are formed; one which is reflected and one that continues past the discontinuity. The amount of energy in the reflected and refracted wave is related to the ratio of the characteristic impedances at the discontinuity as (see appendix A):

$$\rho_v = -\rho_i = \frac{Z_b - Z_a}{Z_b + Z_a} \tag{2.9}$$

where  $\rho_v$  is the voltage reflection coefficient,  $\rho_i$  is the current reflection coefficient,  $Z_a$  is the impedance of the line containing the incident wave and  $Z_b$  is the impedance seen looking into the discontinuity. The transmission coefficient is defined as (see appendix A):

$$T_v = 1 + \rho_v \tag{2.10}$$

where  $T_v$  is the voltage transmission coefficient and  $T_i$  is the current transmission coefficient. The propagation, reflection and refraction of traveling waves continues until the energy has been dispersed and a new steady state is reached.

#### 2.4.2.1 Correlation Techniques

Correlation is a popular technique used in single-ended fault location on transmission lines to identify the reflected wave from the fault location. Correlation is used to measure the similarity between two signals. The cross-correlation function of two signals, x(t) and y(t) is defined as:

$$r_{xy}(\tau) = \frac{1}{T_0} \int_0^{T_0} x(t)y(t+\tau)dt$$

(2.11)

The auto correlation of a signal is defined similarly to the cross-correlation but instead measures the similarity between a signal and a time shifted version of itself.

$$r_{xx}(\tau) = \frac{1}{T_0} \int_0^{T_0} x(t)x(t+\tau)dt$$

(2.12)

Correlation can either be performed as an auto-correlation of the initial traveling wave or by separating the traveling waves into forward and backward components and cross-correlating the initial backward traveling wave with all other forward traveling waves [40]. In both techniques a peak in the cross-correlation function occurs at a time  $\tau$  which is equal to the round trip time of the traveling wave from the fault location.

To obtain the forward and backward traveling waves,  $S_1$  and  $S_2$  in equations 2.3 and 2.4 requires both the high frequency voltage and high frequency current signals. Measuring

the current is a relatively simple task that can be achieved by measuring the current in the secondary of an existing current transformer and using a suitable current probe to extract the high frequency components [6] because conventional CTs have a bandwidth wide enough to include the traveling wave components. However, extracting the high frequency voltage using conventional CVTs is not so straight forward because CVTs are tunned to the power frequency bandwidth. They have a very poor high frequency response and filter out the high frequency traveling waves [41].

In [2] a method was proposed for inferring the high frequency voltage transients by estimating the instantaneous impedance of the busbar to which the transmission line is connected to. This is achieved by simultaneously measuring the current in at least two other transmission lines that are connected to the same busbar. Using the estimated bus bar impedance, the high frequency voltage signals can be inferred.

Both the auto correlation and cross correlation methods work well for a low impedance fault on a single transmission line but are less reliable for high impedance faults where the reflection from the fault location is small or when the transmission line is connected to other lines as part of a larger network. Under these circumstances it is harder to differentiate the peak in the cross correlation function relating to the fault from other points of reflection.

#### 2.4.2.2 Time Tree Analysis

It has been shown that correlating simulated data with recorded fault data produces very high degrees of correlation under a variety of fault conditions including single phase faults [42]. The downside of such an approach is the long simulation times required to accurately simulate different fault locations and fault conditions. Distribution networks are subject to reconfiguration on a regular basis so the exact layout of the network must be known at the time of the fault and the simulation model changed accordingly.

Time Tree Analysis was first proposed by [4] as a method of fault location. The technique works by keeping a record of the amplitude and path traveled by each wave, starting at the fault point, and propagating throughout the network. An observation point on the network is specified and a pulse array is generated representing the time and amplitude of every pulse that arrived at the observation point. The pulses can then be shaped to estimate the wave shaping caused by the network.

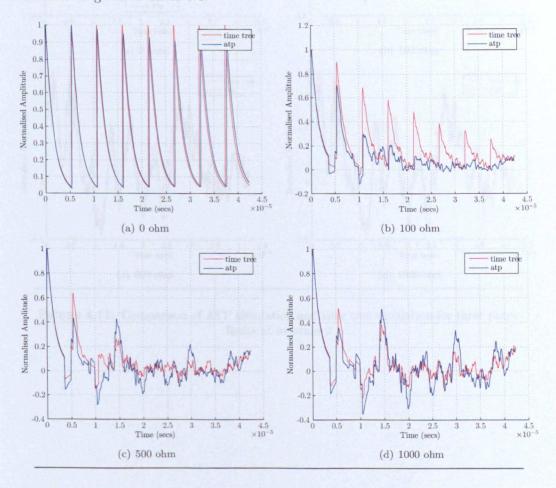

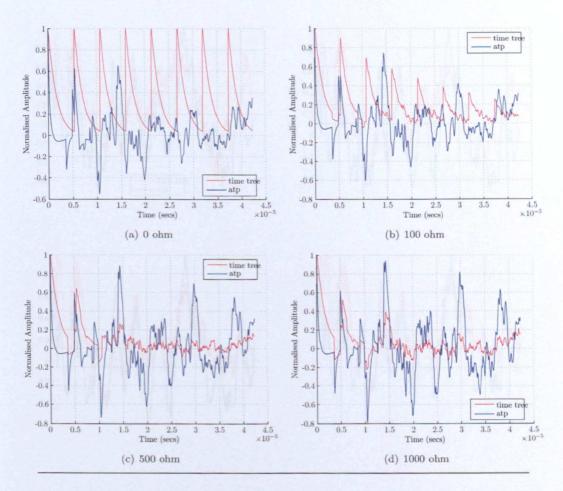

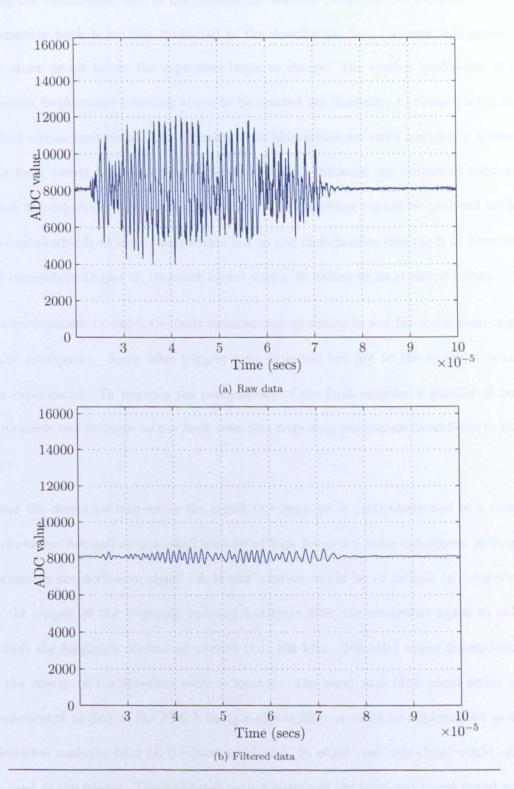

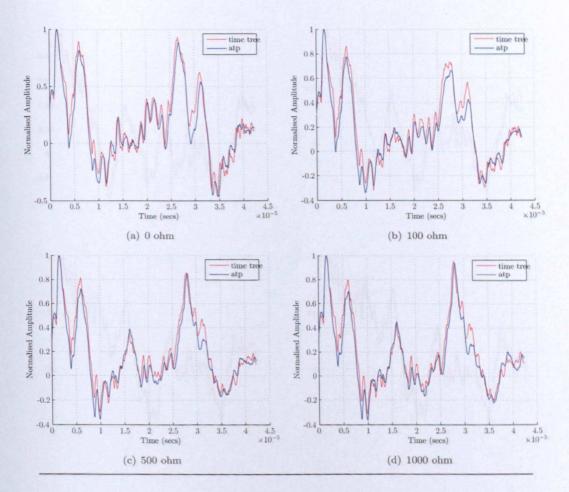

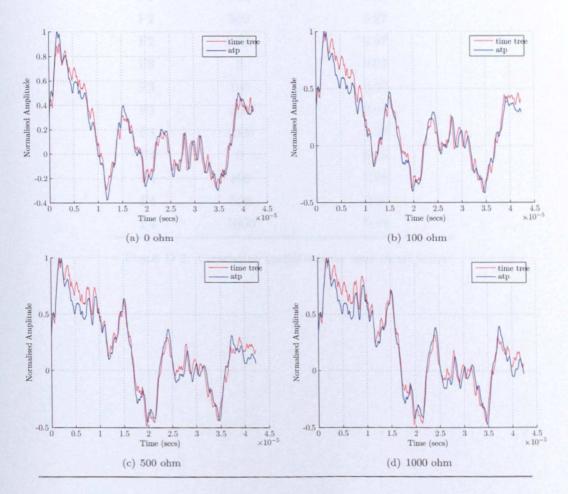

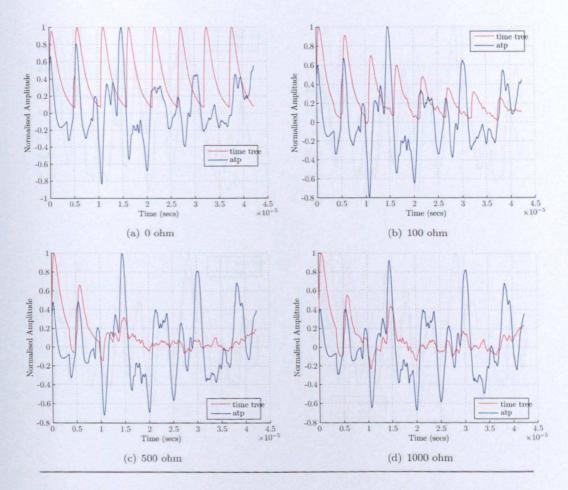

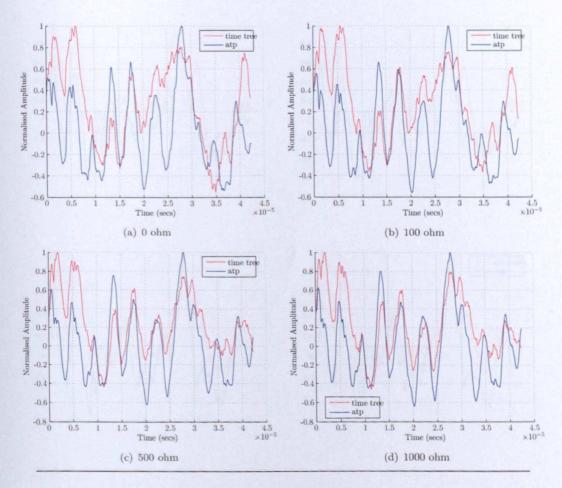

In [9], time tree analysis was applied to single-ended traveling wave analysis on a radial distribution line. It was shown that time tree analysis showed very strong correlation with EMTP simulations of the same network. The advantage of time tree analysis is the short computation time and the speed at which the time tree can be reconfigured to represent a new fault condition when compared with traditional simulation programs. Using the time tree technique over a hundred fault scenarios can be predicted in under a second for a typical network configuration. EMTP simulations in contrasts require manual reconfiguration of the network topology to insert a fault and recalculation of the affected transmission line sections. Time tree analysis is therefore an ideal candidate to form the basis of an automatic search algorithm which is recognised by [4] but so far has not been implemented.

#### 2.4.2.3 Wavelet Analysis

In both the double-ended and single-ended schemes the precise identification of the beginning of the traveling wave fronts is crucial to accurate fault location. As a wave propagates along a transmission line it suffers from attenuation and distortion which changes the shape of the wave front. The wavelet transform is a signal processing technique which has been widely adopted as a method of identifying the exact arrival times of traveling waves for both double-ended [7, 43] and single-ended schemes [34, 44]. Wavelet analysis allows a signal to be analysed whilst being localised in both frequency and time which makes it ideally suited to the analysis of transient signals which only exist for a short period [44]. Wavelets are mathematical functions that analyse the input signal at different frequencies. The shape of the wavelet changes with frequency so that is most suited to the analysis at each particular frequency scale. A whole family of wavelets is derived by scaling and translating a mother wavelet. Narrow wavelets are used for the analysis of high frequency components and broad wavelets are used for the analysis of low frequency components. Wavelet analysis can either be performed as a Continuous Wavelet Transform (CWT) [45] or as a Discrete Wavelet Transform (DWT). A CWT considers all possible scaling values to produce a continuous time-scale domain analysis of the signal. As a result, CWT is computationally intensive. A DWT considers only a discrete number of scales and can be implemented efficiently as a series of cascading band pass filters. There are also examples of where wavelet analysis has been used to de-noise traveling wave signals [46].

#### 2.4.2.4 Application to Distribution Lines

The implication of a radial network topology is that the traditional single-ended correlation technique, which calculates the distance to fault, can correspond to more than one fault location. Further analysis of other wavefronts is necessary to discriminate the most likely fault location. Since there are many more sets of traveling waves reverberating around the network when a disturbance occurs, at certain positions in the network waves can either constructively or destructively interfere with each other. This further adds to the difficulty in identifying the origins of the wavefronts.

If a fault occurs on a sub feeder the double ended method (that uses relative arrival times) can only resolve the position of the fault to the point where the sub-feeder joins the main line. In [8] and [7] schemes are proposed that place fault recorders at the end of each sub-feeder to provide total coverage of the distribution line but this is very costly and there may also not be suitable places to install all the recorders. In [6] a method is proposed where single-ended methods are combined with double-ended methods to correctly identify a fault that has occurred on a sub-feeder. First the faulty feeder is identified using the double-ended method and the fault distance along the feeder is estimated using the single ended method.

In [47] a scheme for identifying the faulted section of the distribution line is proposed by analysing the sums of squares of the wavelet transform coefficients. It is shown that the lower scale wavelet coefficients which correspond to the high frequency traveling wave data exhibit distinguishable responses depending on which section of the distribution line the fault is located. Using this method the exact location along the faulted section cannot be estimated and the author suggests the use of more conventional impedance based approach once the faulted section has been identified. The idea of using wavelet analysis as a feature extraction method is developed further in [48] for fault location on a rural inefficiently grounded distribution line. The faulted section is first identified by comparing the energy in the wavelet coefficients and then type C traveling fault location is performed to inject a short duration high voltage pulse into the distribution line. The reflected wave from the fault is identified with knowledge of the faulted section to estimate the fault location.

#### 2.4.3 Knowledge Based Methods

Knowledge based methods are those that take a heuristic approach to arrive at a solution as opposed to an algorithmic approach. Heuristic approaches are particularly suited to complex problems where it would otherwise be too difficult or impossible to formulate the problem deterministically.

#### 2.4.3.1 Expert Systems

An expert system is a software system that attempts to provide the same service as a human expert or group of human experts would on a particular subject. This is achieved by creating a knowledge base and a rule base relating the knowledge. The expert system is interrogated by posing questions and using an inference engine it is able to deduce information through logical reasoning. There are a number of examples in the literature of expert systems being used to locate faults on distribution systems[49, 50]. In [49] an expert system is used to emulate the behavior of an experienced dispatcher in diagnosing distribution system faults. The expert system consists of a database containing information about feeder circuit configuration and geographical maps of feeder locations. When a fault occurs on the network phone calls from interrupted customers are received. The addresses of the interrupted customers are fed into the expert system which then deduces the most likely locations of the fault.

#### 2.4.3.2 Artificial Neural Networks

An artificial neural network is a computational model based on biological networks similar to those that exist in nature and was inspired by research on the central nervous system. The network consists of a large number of node elements which are connected through a series of weighted connections. The nodes and connections are organised into layers such that nodes only have connections with preceding node layers. The first layer represents the input and the final layer represents the output with one or more hidden layers existing in between. The network is trained with given input patterns to produce desired output patterns which are obtained by altering the weighting on the connections between nodes. The great advantage of the neural network approach is that through a period of training the network learns by its self rather than having to be programmed. It does not have to be told a specific set of rules like expert systems but instead establishes its own set of rules based on the data it is trained with. However, it is noted [51] that the ability to learn means that the ANN cannot explain to the user how it arrived at its conclusions. Another important point raised by [51] is that whilst ANNs are very good at interpolating data they are poor at extrapolation which means that the training data must be chosen very carefully and comprehensively to include all of the solution space. There are a number of examples in the literature [52, 53] that show that once sufficient training has been performed neural networks can make accurate predictions of fault locations under a variety of fault conditions and fault resistances.

#### 2.4.3.3 Genetic Algorithms

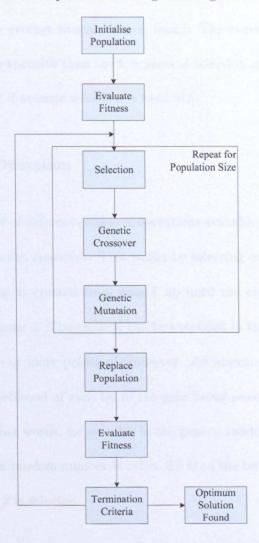

A genetic algorithm is a search technique used to optimise a problem using the mechanics of natural selection. Each solution parameter is encoded, usually as a numerical string, in such a way that for each possible solution a unique numerical gene exists. An initial population is created, usually at random, of genes representing possible solutions. For each gene a value of fitness is calculated which is a measure of its worth to the problem being optimised. Genes are selected to form the next generation of population based on their fitness value. Genes with a higher fitness value on average tend to survive

whilst genes with lower fitness values do not. Genes that are selected for the next generation undergo a process of "cross-over" which is a method of combining two genes to produce a new gene containing components of both its parents and a process of mutation which introduces random genetic variation. This process of selection, cross-over, and mutation continues over a number of generations until the algorithm converges on an optimum solution. In [54] and [55] genetic algorithms are used as an optimisation technique for waveform matching the power frequency phasor measurement of fault events on transmission lines. In [55] the technique is applied to situations where only sparsely recorded data is available. Genetic algorithms have so far not be applied to waveform matching of traveling wave data. One of the main reasons for this is the long computation times that traveling wave simulations require and the time it takes to reconfigure the simulation model to represent a different fault condition. However using time tree analysis these problems have been resolved.

### 2.5 Summary

In this chapter a review of the different techniques used for fault locating on both transmission and distribution lines has been presented. There is no single technique that performs well under all circumstances; the impedance based methods are heavily influenced by real time operating parameters whereas the traveling wave based methods struggle with close up faults and close to zero incident fault angles.

The use of knowledge based systems such as artificial neural networks and expert systems allows multidimensional relations between data to be established that would have otherwise been difficult to identify. Genetic algorithms have proven to be particularly effective at rapidly searching a large solution space to find the optimum maximum.

The potential accuracy of traveling wave fault location and its relatively low susceptibility to system operating parameters when compared with impedance based methods makes it attractive as a fault location scheme and is one of the main reasons why its was chosen for this research project. Although the waveforms produced are far more complex than those on transmission lines it has been demonstrated [9] that using the time tree analysis, a waveform closely representing that predicted by simulation can be produced, in a very short computation time. Instead of trying to identify a single reflected wave, the entire fault signature is considered. An absolute location can be specified instead of just a distance to fault which addresses the problem of multiple fault locations on a radial topology.

A genetic search algorithm which exploits the speed of time tree analysis will be developed to efficiently search the fault solution space of a radial distribution line to find the most likely fault location autonomously without the need for interpretation of a complex waveform by a specialised engineer.

## Chapter 3

# Typical Fault Events

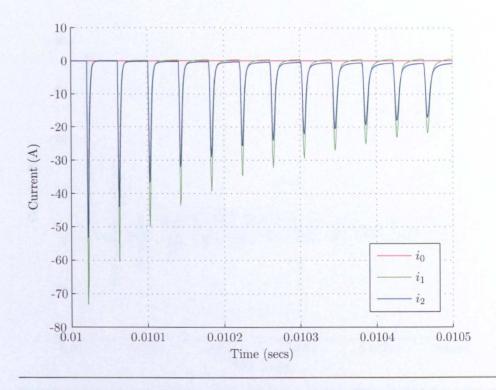

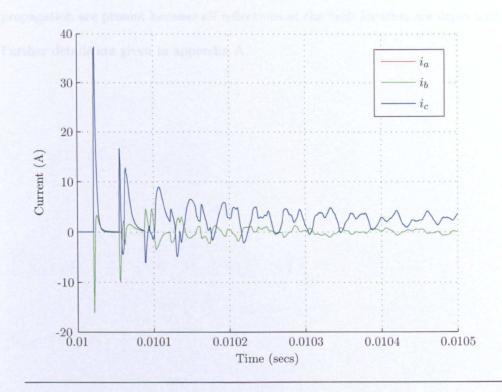

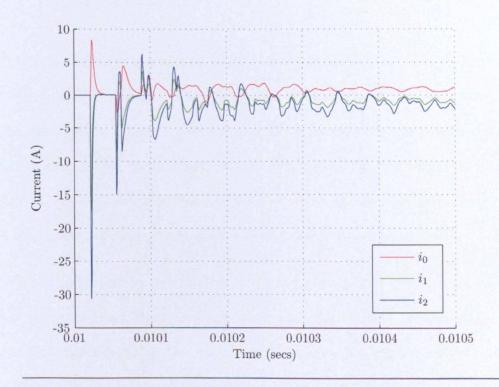

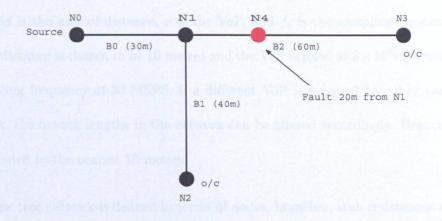

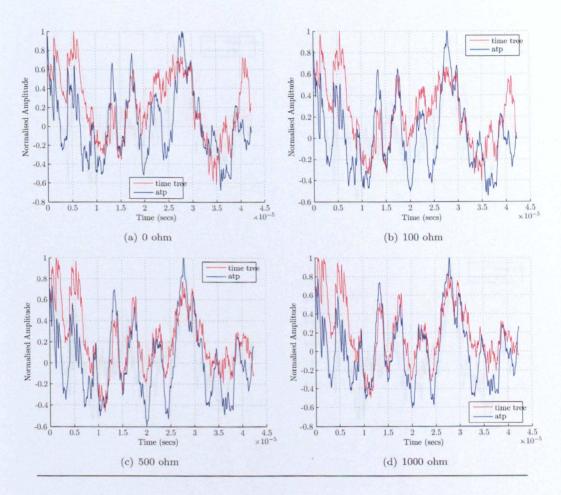

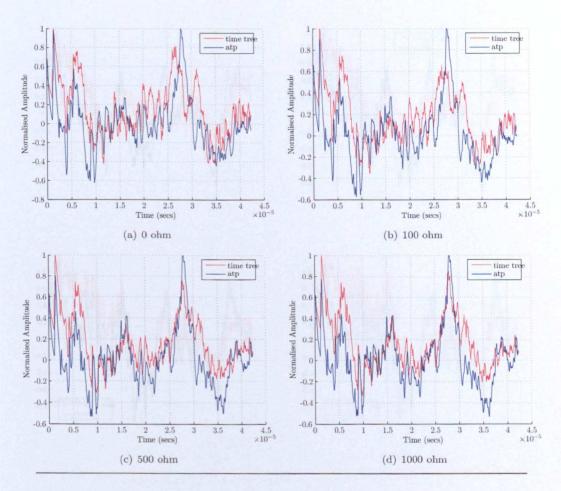

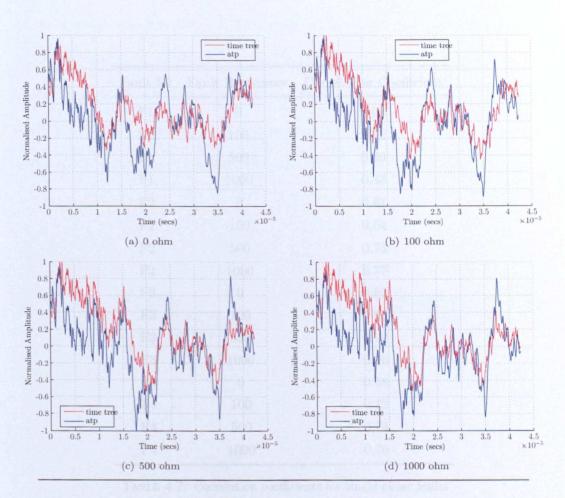

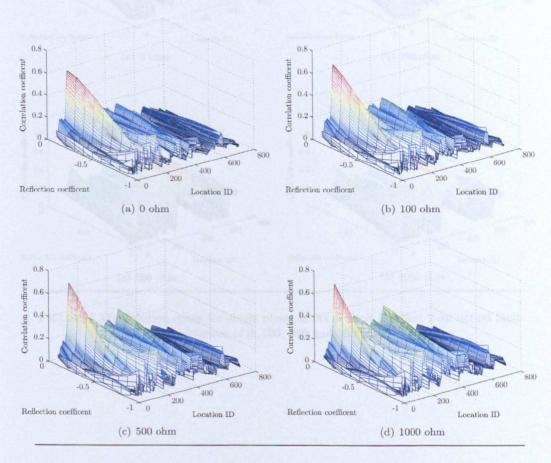

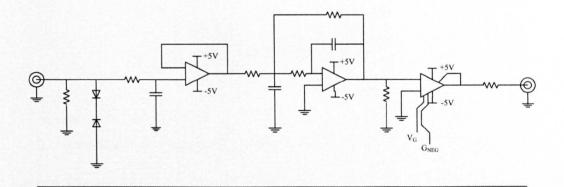

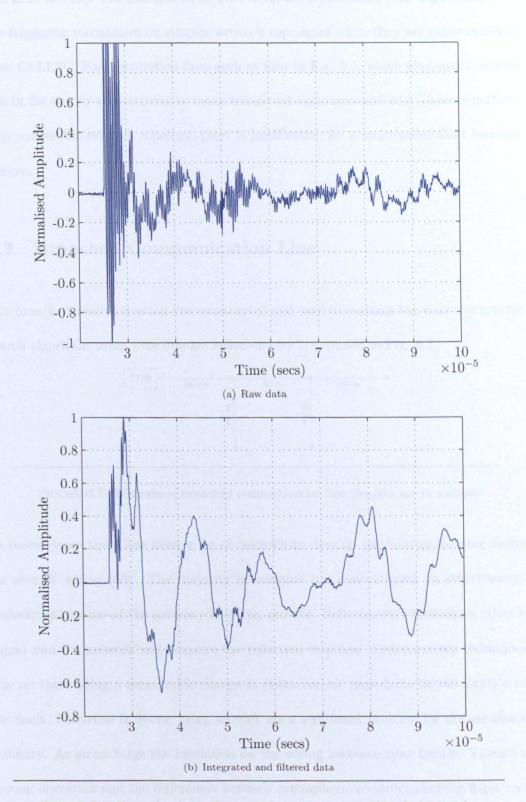

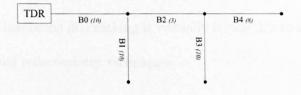

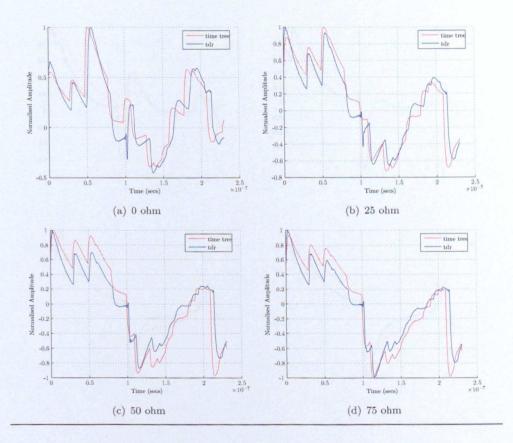

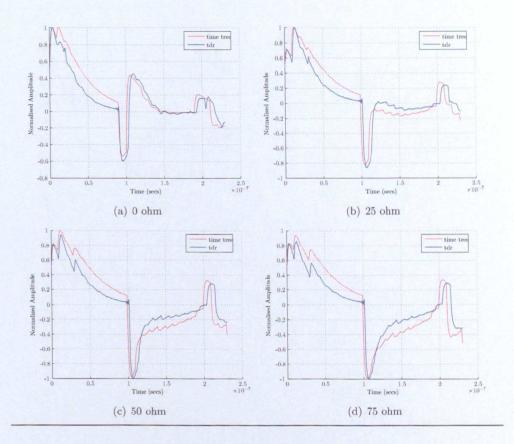

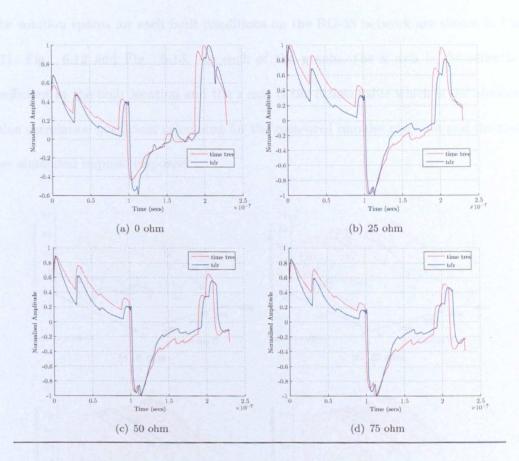

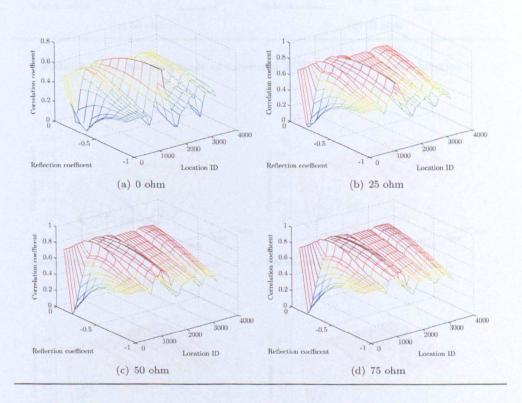

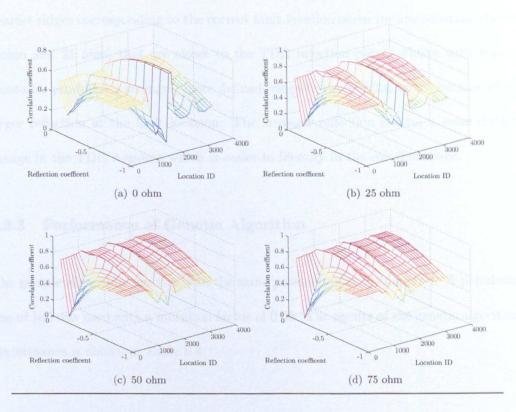

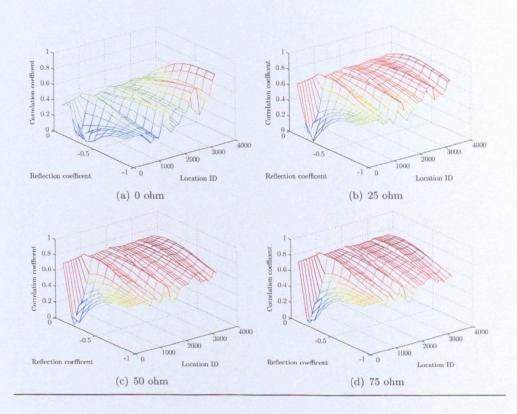

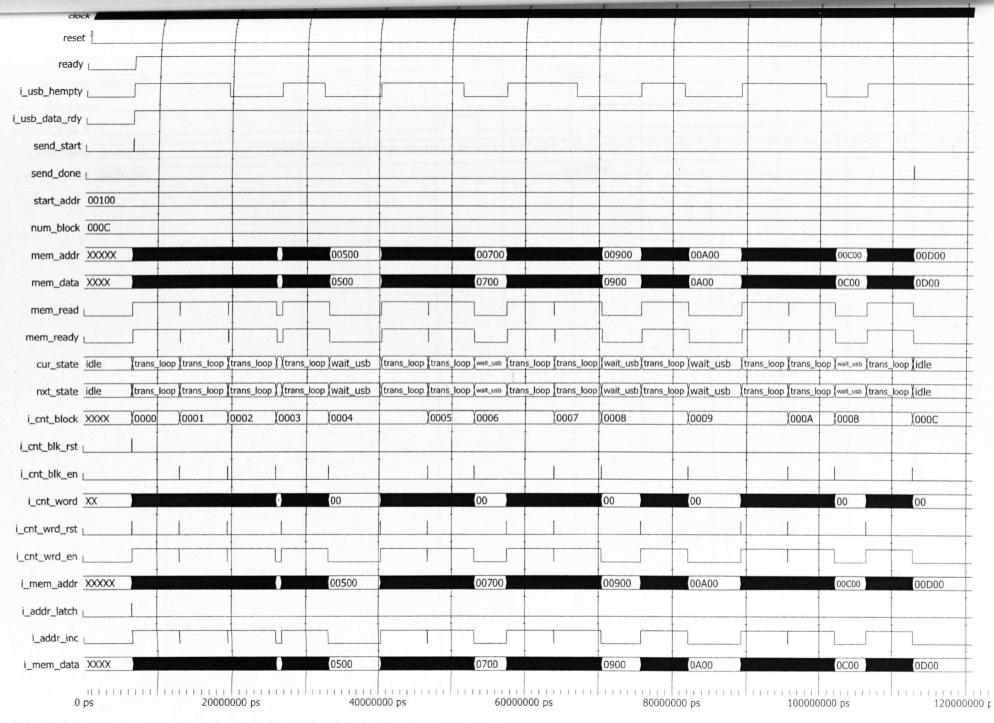

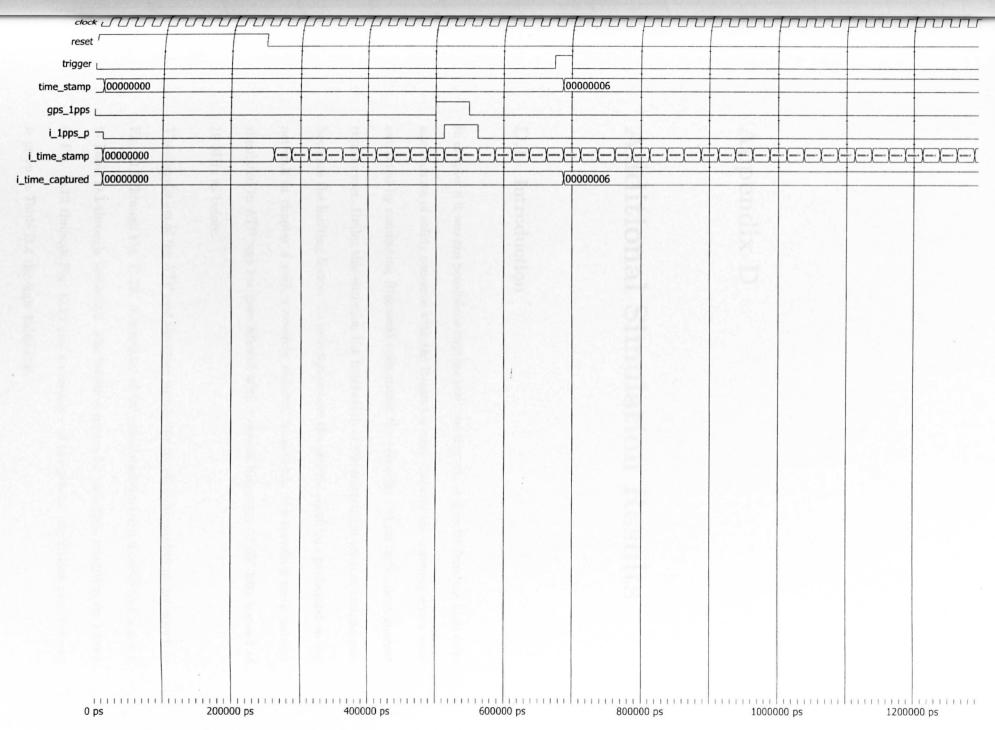

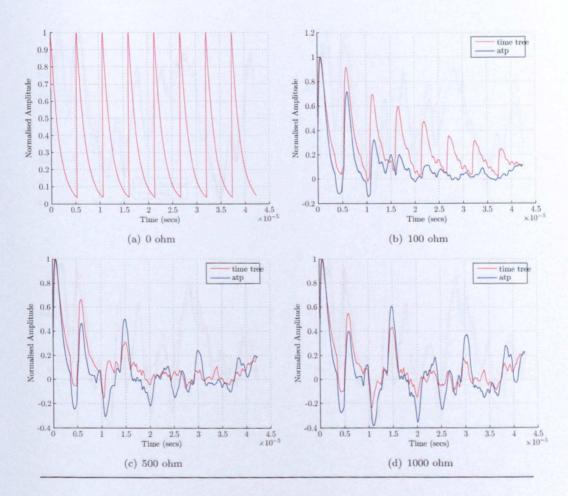

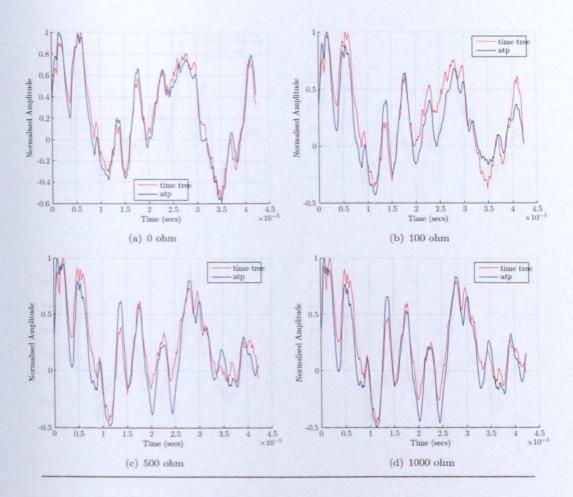

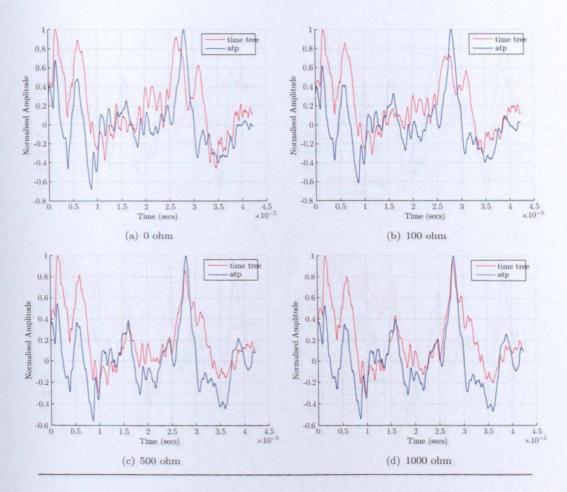

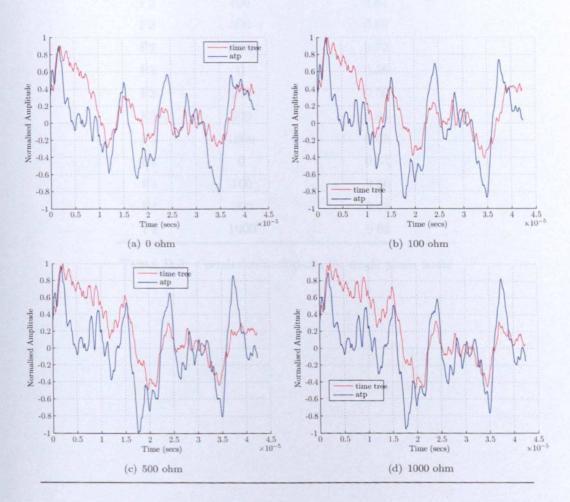

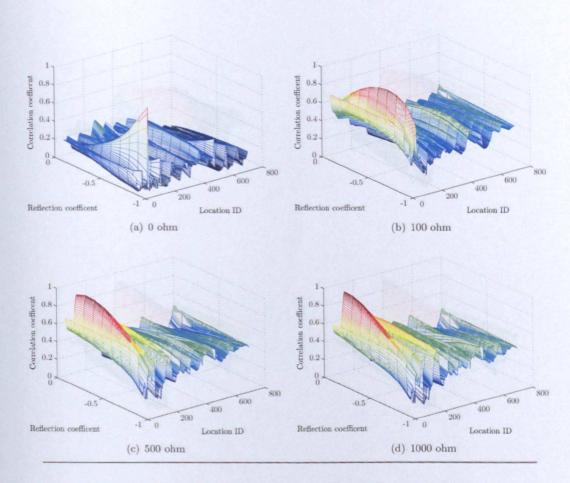

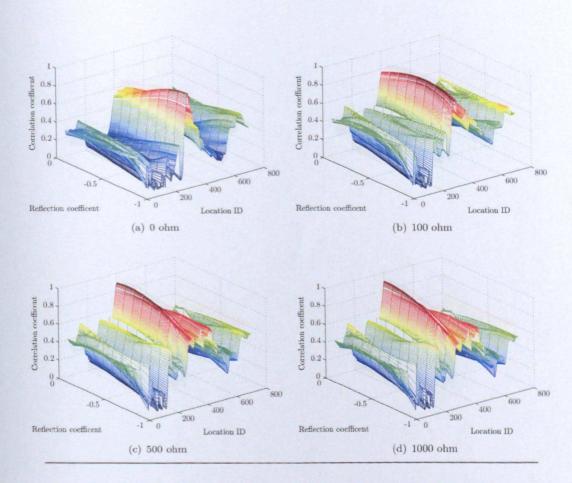

#### 3.1 Introduction