# Improving Fault Coverage and Minimising the Cost of Fault Identification when Testing from Finite State Machines

A thesis submitted in fulfilment of the requirement for the degree of Doctorate of Philosophy

# Qiang Guo

School of Information Systems, Computing and Mathematics

Brunel University Uxbridge, Middlesex UB8 3PH

United Kingdom

January 9, 2006

To my parents, and to Yuyan ...

# Acknowledgements

I would like to thank Professor Robert M. Hierons of Brunel University, who is my first supervisor, and Professor Mark Harman of King's College London, who is my second supervisor, for their excellent supervision and support throughout this research.

My thank also goes to people from VASTT (Verification and Analysis using Slicing, Testing and Transformation) and ATeSST (The Analysis, Testing, Slicing, Search and Transformation) research groups in Brunel University, and the EPSRC funded FORTEST and SEMINAL networks for their valuable comments and advice.

This work is funded by Brunel Research Initiative and Enterprise Fund (BRIEF) Award from Brunel University for the first year, and then departmental bursary from school of information systems, computing and mathematics, Brunel University, for the second and third years.

# Related publications

- Qiang Guo, Robert M. Hierons, Mark Harman and Karnig Derderian, "Computing unique input/output sequences using genetic algorithms", Formal Approaches to Testing (FATES'03), in LNCS 2931:164-177, 2004.

- Qiang Guo, Robert M. Hierons, Mark Harman and Karnig Derderian, "Constructing multiple unique input/output sequences using metaheuristic optimisation techniques", *IEE Proceedings Software*, 152(3):127-130, 2005.

- Qiang Guo, Robert M. Hierons, Mark Harman and Karnig Derderian, "Improving test quality using robust unique input/output circuit sequences (UIOCs)", *Information and Software Technology*, accepted for publication, 2005.

- Qiang Guo, Robert M. Hierons, Mark Harman and Karnig Derderian, "Heuristics for fault diagnosis when testing from finite state machines", Software Testing, Verification and Reliability, under review, 2005.

#### Abstract

Software needs to be adequately tested in order to increase the confidence that the system being developed is reliable. However, testing is a complicated and expensive process. Formal specification based models such as finite state machines have been widely used in system modelling and testing. In this PhD thesis, we primarily investigate fault detection and identification when testing from finite state machines.

The research in this thesis is mainly comprised of three topics - construction of multiple Unique Input/Output (UIO) sequences using Metaheuristic Optimisation Techniques (MOTs), the improved fault coverage by using robust Unique Input/Output Circuit (UIOC) sequences, and fault diagnosis when testing from finite state machines. In the studies of the construction of UIOs, a model is proposed where a fitness function is defined to guide the search for input sequences that are potentially UIOs. In the studies of the improved fault coverage, a new type of UIOCs is defined. Based upon the Rural Chinese Postman Algorithm (RCPA), a new approach is proposed for the construction of more robust test sequences. In the studies of fault diagnosis, heuristics are defined that attempt to lead to failures being observed in some shorter test sequences, which helps to reduce the cost of fault isolation and identification. The proposed approaches and techniques were evaluated with regard to a set of case studies, which provides experimental evidence for their efficacy.

# Contents

| 1 | Intr | oduction                                         |

|---|------|--------------------------------------------------|

|   | 1.1  | About testing                                    |

|   | 1.2  | Validation and verification                      |

|   |      | 1.2.1 Validation                                 |

|   |      | 1.2.2 Verification                               |

|   |      | 1.2.3 Validation vs. verification                |

|   | 1.3  | Formal specification languages                   |

|   | 1.4  | Test cost and fault coverage                     |

|   | 1.5  | Fault observation and diagnosis                  |

|   | 1.6  | Testing with MOTs                                |

|   | 1.7  | The structure of this thesis                     |

| 2 | Pre  | iminaries and notation 1                         |

|   | 2.1  | Graph theory                                     |

|   |      | 2.1.1 Directed graph                             |

|   |      | 2.1.2 Flows in networks                          |

|   |      | 2.1.3 The maximum flow and minimum cost problems |

|   |      | 2.1.4 The Chinese postman tour                   |

|   | 2.2  | Metaheuristic optimisation techniques            |

|   |      | 2.2.1 Genetic algorithms                         |

|   |      | 2.2.2 Simulated annealing                        |

|   |      | 2.2.3 Others                                     |

| 3 | Test | t gener  | ration - a review                            | <b>3</b> 5 |

|---|------|----------|----------------------------------------------|------------|

|   | 3.1  | Introd   | uction                                       | 35         |

|   | 3.2  | Adequ    | acy criteria                                 | 35         |

|   | 3.3  | Black-   | box and white-box testing                    | 37         |

|   | 3.4  |          | ol flow based testing                        | 38         |

|   | 3.5  | Data f   | flow based testing                           | 42         |

|   | 3.6  | Partiti  | ion analysis                                 | 47         |

|   |      | 3.6.1    | Specification based input space partitioning | 48         |

|   |      | 3.6.2    | Program based input space partitioning       | 49         |

|   |      | 3.6.3    | Boundary analysis                            | 50         |

|   | 3.7  | Mutat    | ion testing                                  | 51         |

|   | 3.8  | Statist  | tical testing                                | 54         |

|   | 3.9  | Search   | n-based testing                              | 55         |

| 4 | Tes  | ting fro | om finite state machines                     | <b>5</b> 9 |

|   | 4.1  | Introd   | uction                                       | 59         |

|   | 4.2  | Finite   | state machines                               | 60         |

|   | 4.3  | Confo    | rmance testing                               | 63         |

|   | 4.4  | Test se  | equence generation                           | 68         |

|   | 4.5  | Optim    | isation on the length of test sequences      | 69         |

|   |      | 4.5.1    | Single UIO based optimisation                | 69         |

|   |      | 4.5.2    | Multiple UIOs based optimisation             | 76         |

|   |      | 4.5.3    | Optimisation with overlap                    | 80         |

|   | 4.6  | Other    | finite state models                          | 82         |

| 5 | Con  | struct   | ion of UIOs                                  | 84         |

|   | 5.1  | Introd   | uction                                       | 84         |

|   | 5.2  | Consti   | ructing UIOs with MOTs                       | 85         |

|   |      | 5.2.1    | Solution representation                      | 85         |

|   |      | 5.2.2    | Fitness definition                           | 86         |

|   |      | 5.2.3    | Application of sharing techniques            | 88         |

|   |      | 5.2.4    | Extending simple simulated annealing         | 90         |

|   | 5.3  | Model    | s for experiments                            | 90         |

#### CONTENTS

|   | 5.4 | Working with genetic algorithms                                       | <b>)</b> 3  |

|---|-----|-----------------------------------------------------------------------|-------------|

|   |     | 5.4.1 GA vs. random search                                            | <b>)</b> 3  |

|   |     | 5.4.2 Sharing vs. no sharing                                          | )4          |

|   | 5.5 | Working with simulated annealing                                      | )6          |

|   | 5.6 | General evaluation                                                    | 12          |

|   | 5.7 | Parameter settings                                                    | 18          |

|   | 5.8 | Summary                                                               | 21          |

| 6 | Fau | alt coverage 12                                                       | 22          |

|   | 6.1 | Introduction                                                          | 22          |

|   | 6.2 | Problems of the existing methods                                      | 24          |

|   |     | 6.2.1 Problems of UIO based methods                                   | 24          |

|   |     | 6.2.2 Problems of backward UIO method                                 | 25          |

|   | 6.3 | Basic faulty types                                                    | 27          |

|   | 6.4 | Overcoming fault masking using robust UIOCs                           | 29          |

|   |     | 6.4.1 Overcoming type 1                                               | 29          |

|   |     | 6.4.2 Overcoming type 2                                               | 32          |

|   |     | 6.4.3 Construction of B-UIOs                                          | 34          |

|   |     | 6.4.4 Construction of UIOCs                                           | 37          |

|   | 6.5 | Simulations                                                           | 37          |

|   | 6.6 | Summary                                                               | 13          |

| 7 | Fau | alt isolation and identification 14                                   | <u> 1</u> 6 |

|   | 7.1 | Introduction                                                          | 16          |

|   | 7.2 | Isolating single fault                                                | 17          |

|   |     | 7.2.1 Detecting a single fault                                        | 18          |

|   |     | 7.2.2 Generating conflict sets                                        | 18          |

|   | 7.3 | Minimising the size of a conflict set                                 | 18          |

|   |     | 7.3.1 Estimating a fault location                                     | 19          |

|   |     | 7.3.2 Reducing the size of a conflict set using transfer sequences 15 | 52          |

|   |     | 7.3.3 Reducing the size of a conflict set using repeated states 15    | 54          |

|   | 7.4 | Identifying a faulty transition                                       | 55          |

|   |     | 7.4.1 Isolating the faulty transition                                 | 55          |

#### CONTENTS

|   |       | 7.4.2 Identifying the faulty final state | 156 |

|---|-------|------------------------------------------|-----|

|   | 7.5   | A case study                             | 157 |

|   | 7.6   | Complexity                               | 162 |

|   |       | 7.6.1 Complexity of fault isolation      | 162 |

|   |       | 7.6.2 Complexity of fault identification | 163 |

|   | 7.7   | Summary                                  | 164 |

| 8 | Con   | aclusions and future work                | 166 |

|   | 8.1   | Contributions                            | 167 |

|   | 8.2   | Finite state machine based testing       | 167 |

|   | 8.3   | Construction of UIOs                     | 168 |

|   | 8.4   | The improved fault coverage              | 168 |

|   | 8.5   | Fault diagnosis                          | 169 |

|   | 8.6   | Future work                              | 170 |

| R | efere | nces                                     | 188 |

# List of Figures

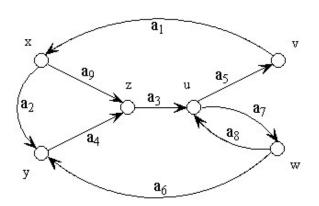

| 2.1 | An example of labelled digraph                                                      | 15  |

|-----|-------------------------------------------------------------------------------------|-----|

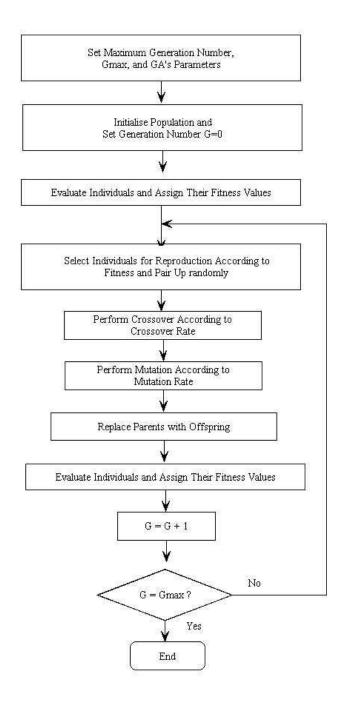

| 2.2 | The flow chart of simple GA                                                         | 26  |

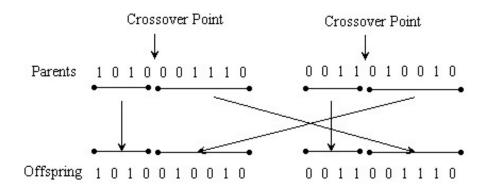

| 2.3 | Crossover operation in simple GA                                                    | 28  |

| 2.4 | Mutation operation in simple GA                                                     | 29  |

| 2.5 | The flow chart of simulated annealing algorithm                                     | 33  |

| 2.6 | The flow chart of tabu search algorithm                                             | 34  |

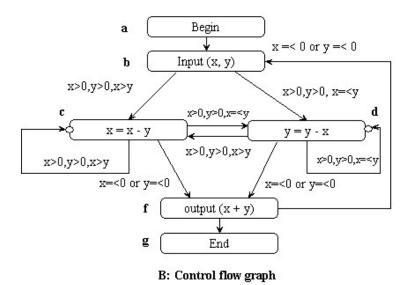

| 3.1 | An example of control flow graph                                                    | 39  |

| 3.2 | An example of the statement coverage                                                | 40  |

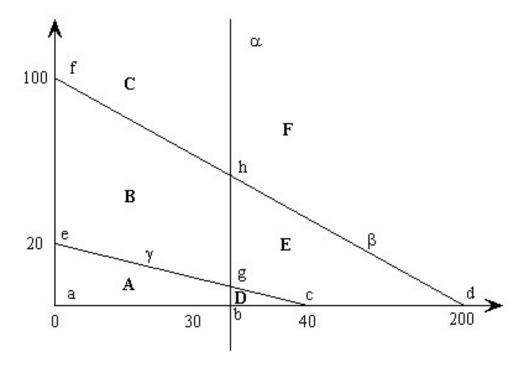

| 3.3 | Partition of the input space of DISCOUNT INVOICE module.                            |     |

|     | $\alpha, \beta, \gamma$ : borders of the subdomains; a,b,,h: vertices of the subdo- |     |

|     | mains; $A,B,,F$ : subdomains                                                        | 49  |

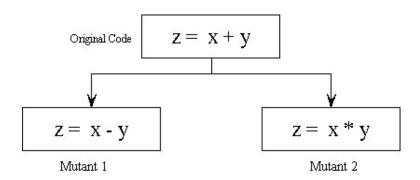

| 3.4 | An example of mutation testing                                                      | 52  |

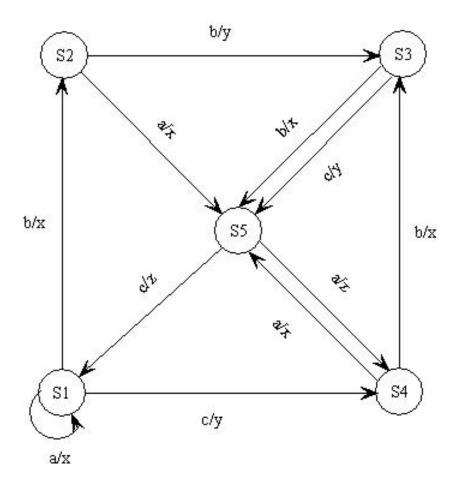

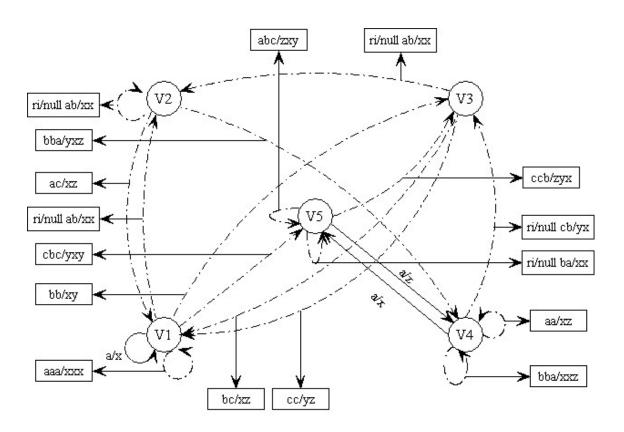

| 4.1 | Finite state machine represented by digraph cited from ref. (ATLU91)                | . 6 |

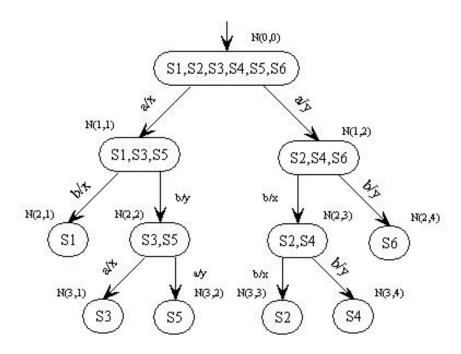

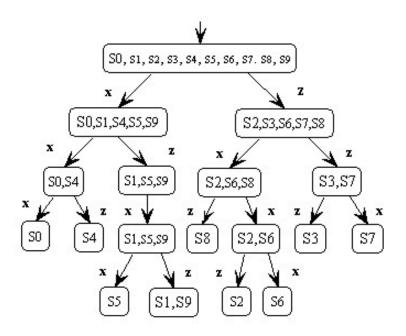

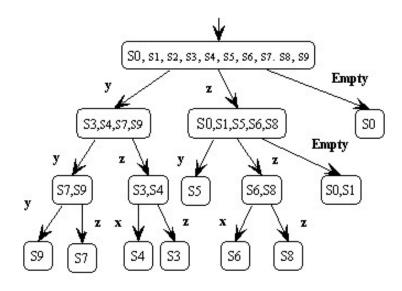

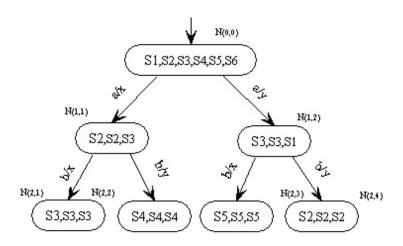

| 4.2 | A pattern of state splitting tree from an FSM                                       | 66  |

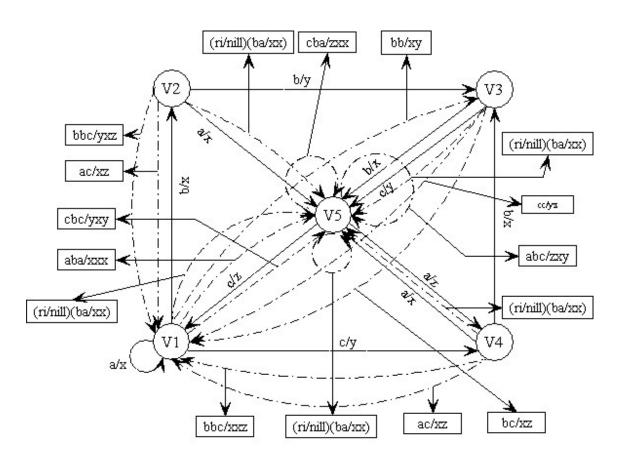

| 4.3 | Test control digraph of the FSM shown in fig. 4.1 using single UIO                  |     |

|     | for each state                                                                      | 72  |

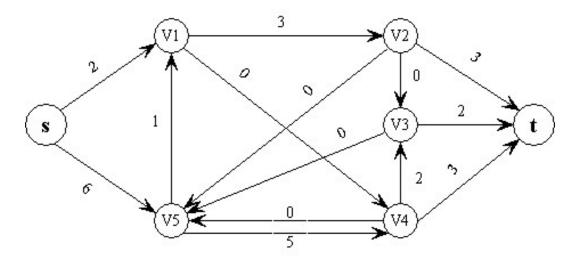

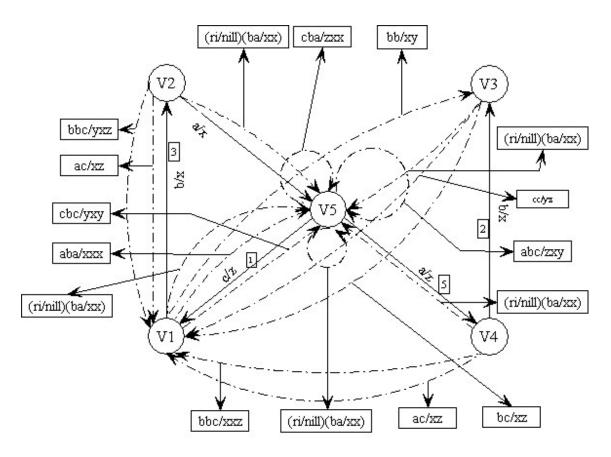

| 4.4 | The flow graph $D_F$ of the digraph $D^{'}$ with the maximum flow and               |     |

|     | minimum cost                                                                        | 74  |

| 4.5 | Symmetric augmentation from fig. 4.3. Number in an edge indi-                       |     |

|     | cates the times this edge needs to be replicated                                    | 75  |

| 4.6 | Test control digraph of the FSM shown in fig. 4.1 using multiple                    |     |

|     | UIOs for each state                                                                 | 77  |

## LIST OF FIGURES

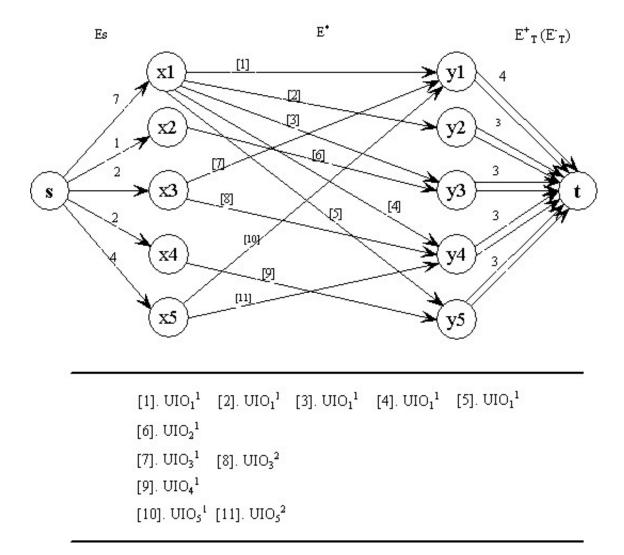

| 4.7  | Flow network used for the selection of UIOs to generate optimal                                                                         |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | test control digraph for the FSM shown in fig. 4.1                                                                                      | 78  |

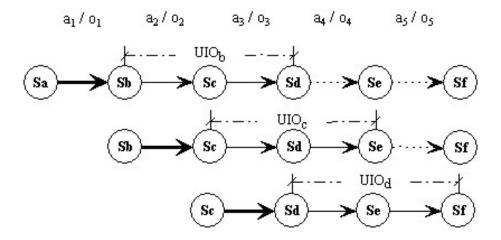

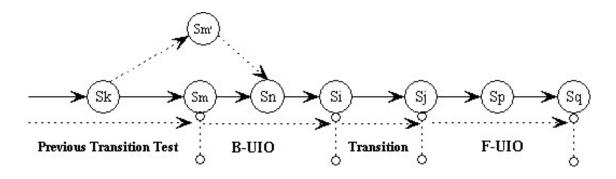

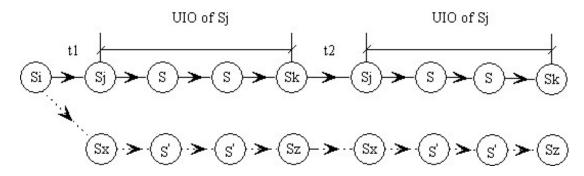

| 4.8  | Structure of UIO Overlap                                                                                                                | 80  |

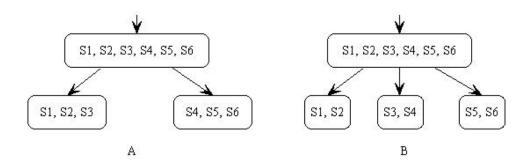

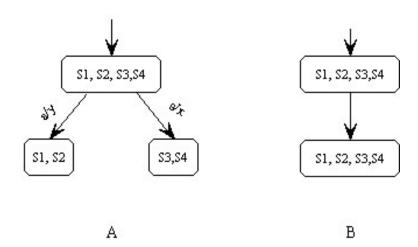

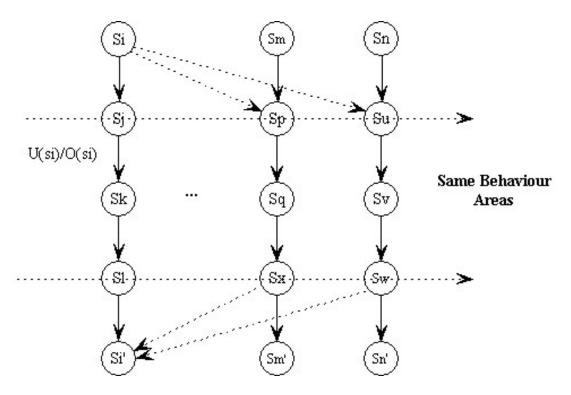

| 5.1  | Two patterns of partitions                                                                                                              | 87  |

| 5.2  | Patterns of valid partition (A) and invalid partition (B)                                                                               | 89  |

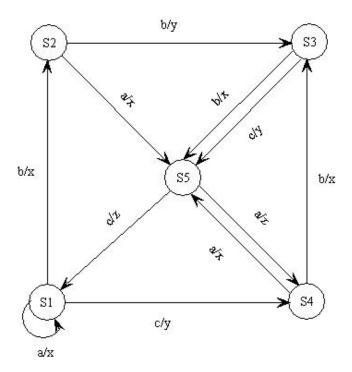

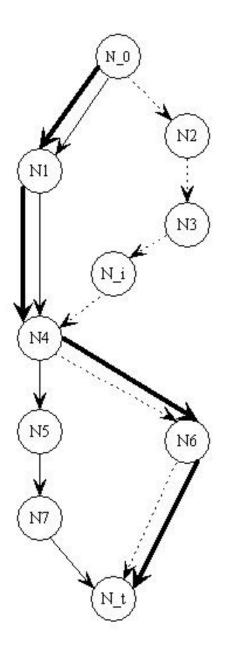

| 5.3  | The first finite state machine used for experiments: model ${\bf I}.$                                                                   | 91  |

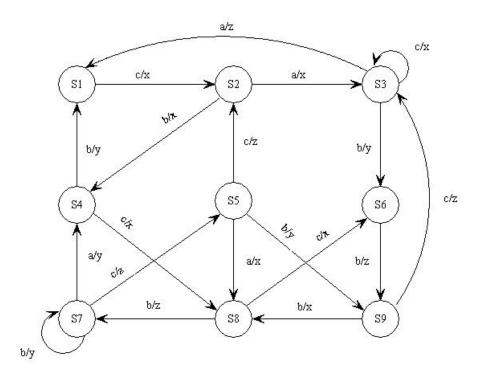

| 5.4  | The second finite state machine used for experiments: model ${\bf II}.$ .                                                               | 91  |

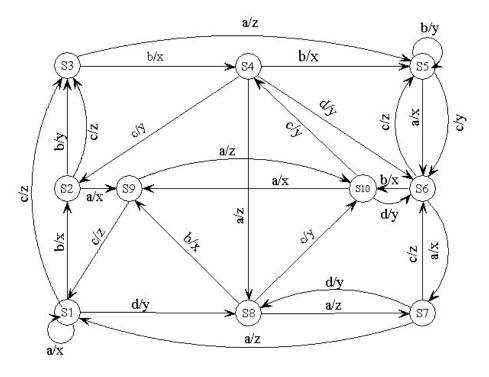

| 5.5  | The third finite state machine used for experiments: model ${f III.}$ .                                                                 | 92  |

| 5.6  | Solution recombination                                                                                                                  | 96  |

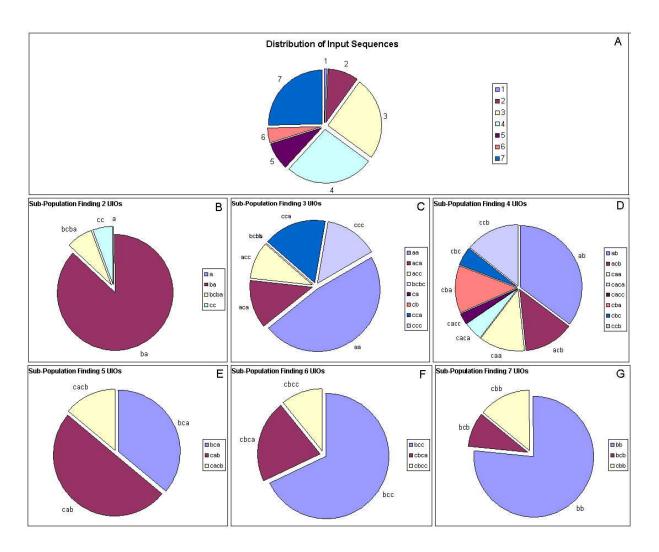

| 5.7  | Average fitness value - input space $\{a,b,c\}$                                                                                         | 97  |

| 5.8  | Average fitness value - input space $\{a,b,c,\sharp\}$                                                                                  | 98  |

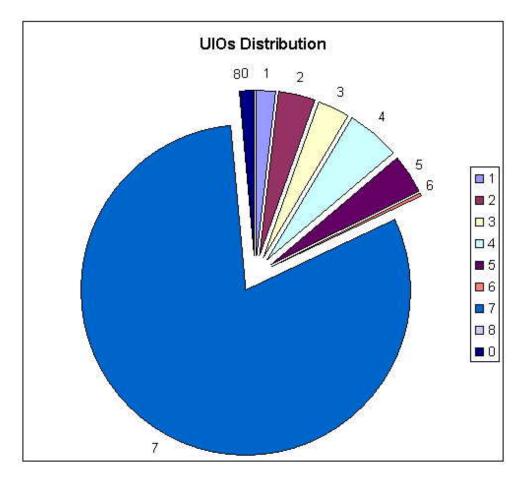

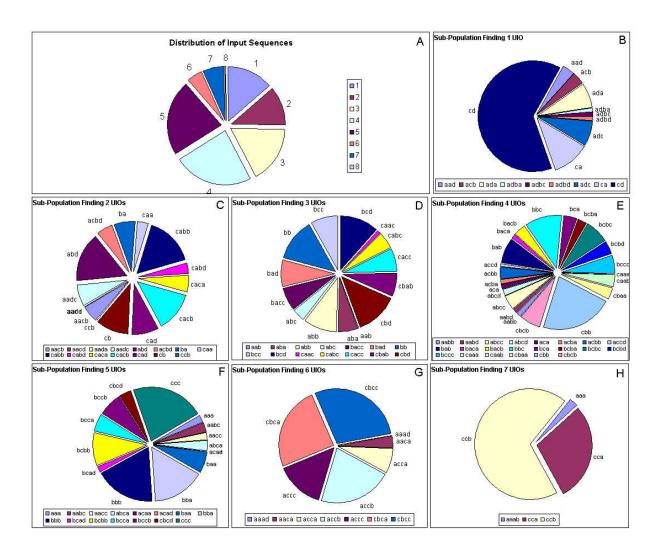

| 5.9  | UIO distribution using GA without sharing for model III; Legends                                                                        |     |

|      | indicate the number of states that input sequences identify                                                                             | 105 |

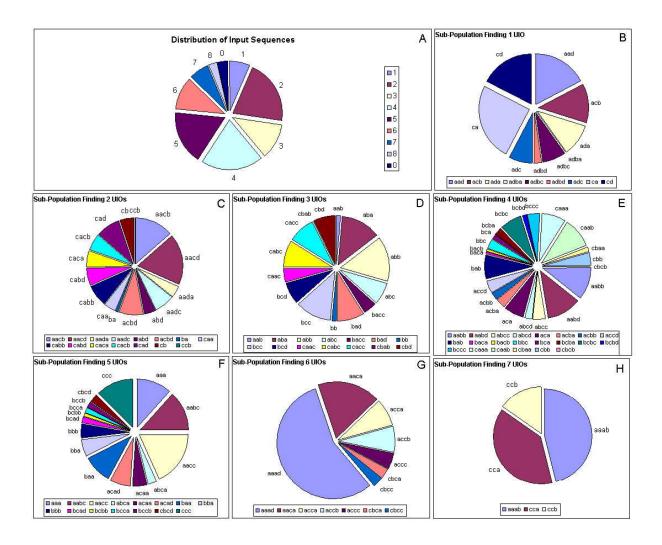

| 5.10 | UIO distribution using GA with sharing for model III                                                                                    | 107 |

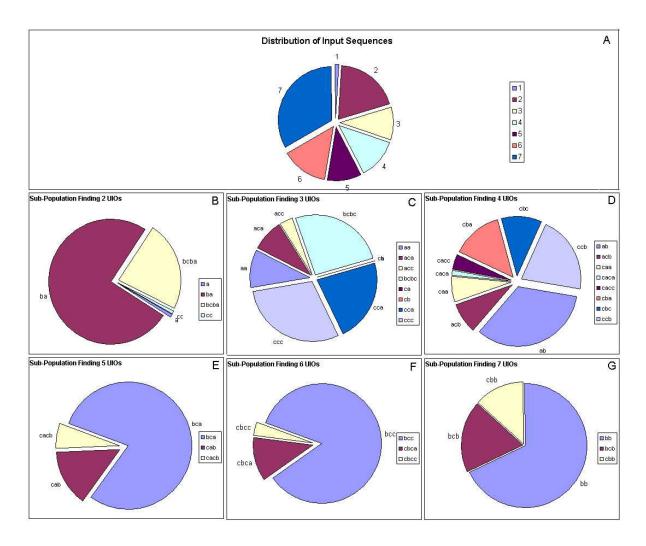

| 5.11 | UIO distribution using GA with sharing for model II                                                                                     | 108 |

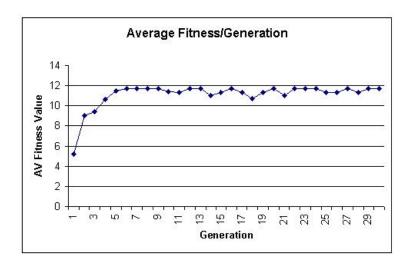

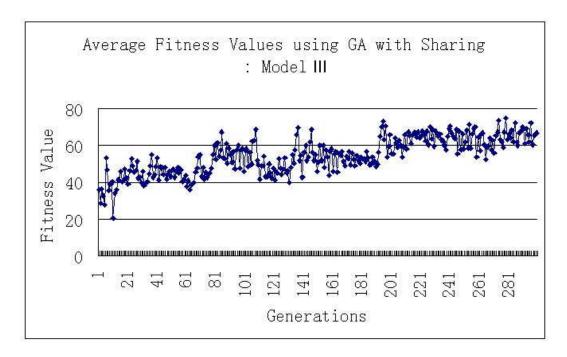

| 5.12 | Average fitness values when constructing UIOs using GA for model                                                                        |     |

|      | $\mathbf{III}$                                                                                                                          | 109 |

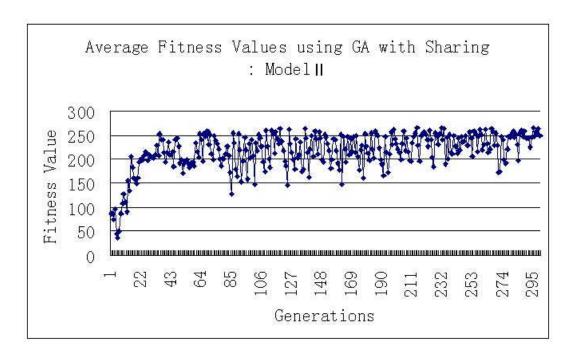

| 5.13 | Average fitness values when constructing UIOs using GA for model                                                                        |     |

|      | $\mathbf{II.}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                                                | 109 |

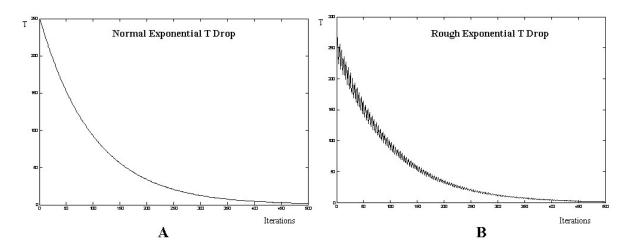

| 5.14 | Simulated annealing temperature drop schema; A: normal expo-                                                                            |     |

|      | nential temperature drop; B: rough exponential temperature drop.                                                                        | 110 |

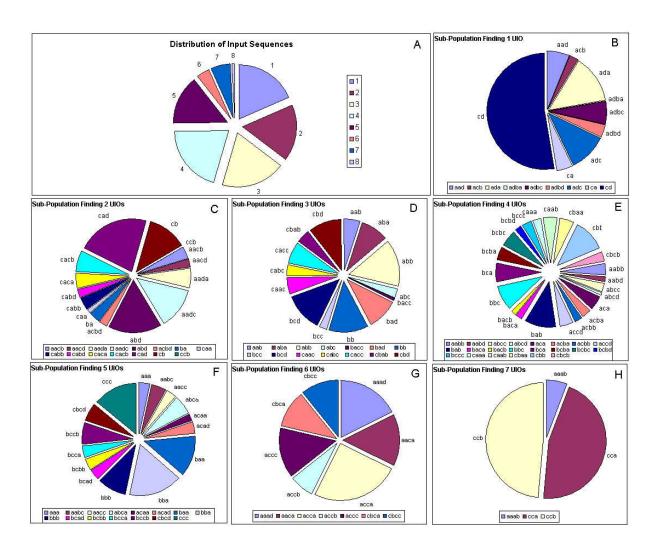

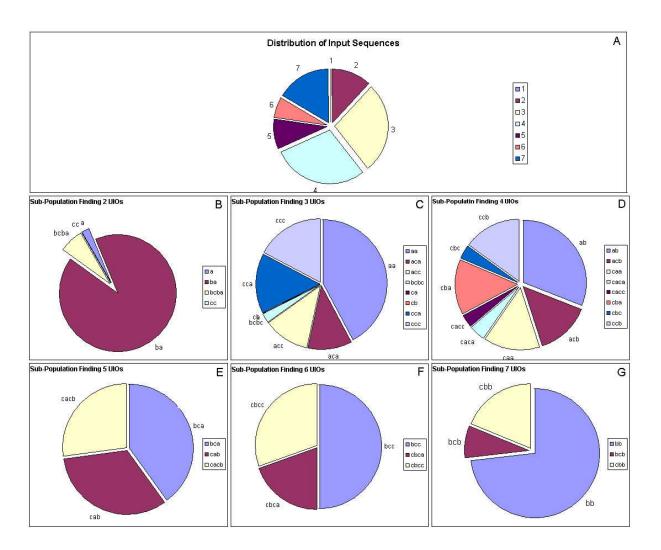

| 5.15 | UIO distribution using SA with normal temperature drop for model                                                                        |     |

|      | $\mathbf{III}$                                                                                                                          | 111 |

| 5.16 | UIO distribution using SA with rough temperature drop for model                                                                         |     |

|      | $\mathbf{III}$                                                                                                                          | 113 |

| 5.17 | UIO distribution using SA with exponential temperature drop for                                                                         |     |

|      | $\bmod el \ \mathbf{II}.  \dots $ | 114 |

| 5.18 | UIO distribution using SA with rough temperature drop for model                                                                         |     |

|      | $\mathbf{II.}  \dots $            | 115 |

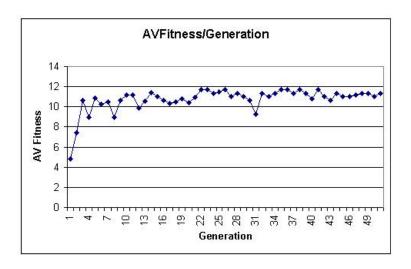

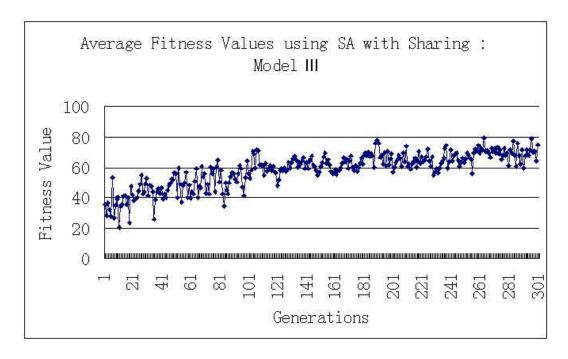

| 5.19 | Average fitness values when constructing UIOs using SA (rough T                                                                         |     |

|      | drop) for model III                                                                                                                     | 116 |

## LIST OF FIGURES

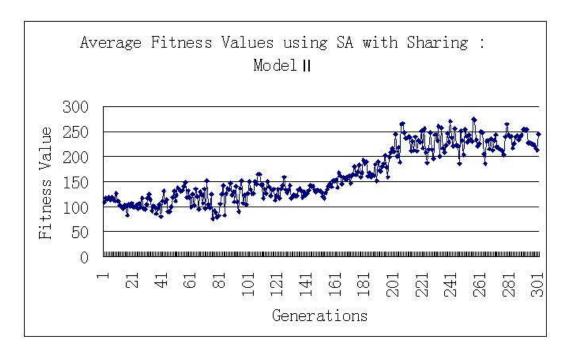

| 5.20 | Average fitness values when constructing UIOs using SA (rough T        |      |

|------|------------------------------------------------------------------------|------|

|      | drop) for model II                                                     | 117  |

| 5.21 | Two patterns of state splitting tree generated from model ${\bf III.}$ | 119  |

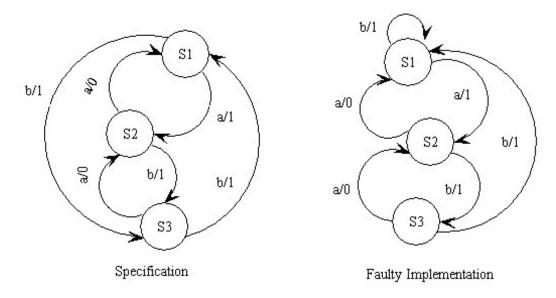

| 6.1  | A specification finite state machine and one faulty implementation     |      |

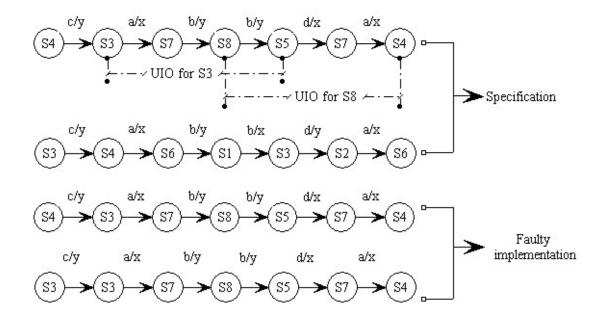

|      | cited from ref. (CVI89)                                                | 125  |

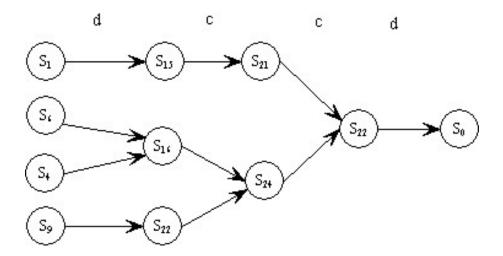

| 6.2  | "dccd/yyyy": Backward UIO sequence of $S_0$ in the finite state        |      |

|      | machine defined in table $6.1$                                         | 126  |

| 6.3  | Problems of the B-method                                               | 126  |

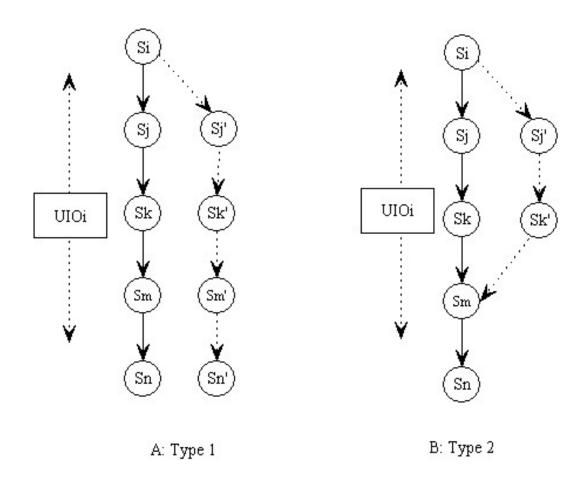

| 6.4  | Types of faulty UIO implementation                                     | 128  |

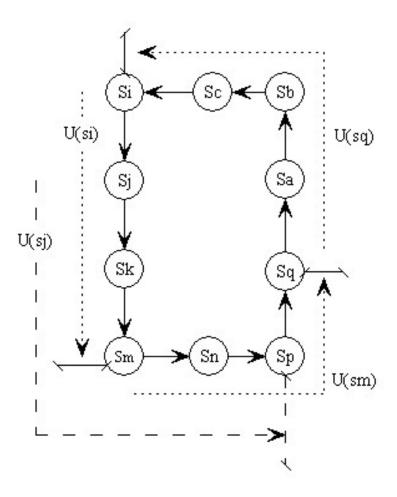

| 6.5  | Construction of UIOC sequences using overlap scheme                    | 129  |

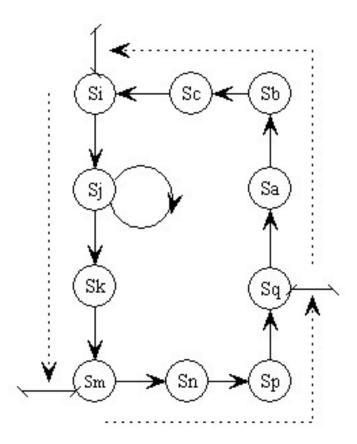

| 6.6  | Construction of UIOC sequences using internal state sampling scheme    | .133 |

| 6.7  | Rule on selection of a state                                           | 135  |

| 6.8  | The pattern of a state merging tree from an FSM                        | 136  |

| 6.9  | UIOC sequence for $s_4$ in the FSM with 10 states and the faulty       |      |

|      | implementation that causes the fault masking in the UIOC sequence.     | 143  |

| 7.1  | Fault Masked UIO Cycling                                               | 151  |

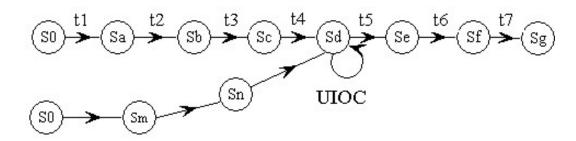

| 7.2  | Reducing the size of a conflict set by applying transfer sequence .    | 152  |

| 7.3  | Reduce the size of a conflict set by considering the repeated states   | 154  |

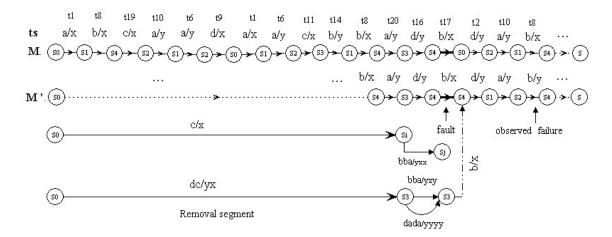

| 7.4  | Fault detection and identification in $M^{'}$                          | 160  |

# List of Tables

| 3.1  | Fitness function cited from (TCMM00)                                   | 57  |

|------|------------------------------------------------------------------------|-----|

| 4.1  | Finite state machine represented by state table                        | 62  |

| 4.2  | UIO sequences for the states of the FSM shown in fig.4.1               | 71  |

| 4.3  | Test control trails of transitions in the FSM shown in fig. 4.1        | 73  |

| 4.4  | An optimal test sequence for the FSM shown in fig. 4.1 by using        |     |

|      | single UIO for each state                                              | 75  |

| 4.5  | Multiple UIO sequences for the states of the FSM shown in fig.4.1.     | 76  |

| 4.6  | The optimal test sequence for the FSM shown in fig. 4.1 by using       |     |

|      | multiple UIOs for state verification                                   | 76  |

| 5.1  | The minimum-length UIOs for model $\mathbf{I}.$                        | 93  |

| 5.2  | UIOs for model II                                                      | 93  |

| 5.3  | UIOs for model <b>III</b>                                              | 94  |

| 5.4  | Final sequences obtained from model I - input space $\{a,b,c\}$        | 98  |

| 5.5  | Final sequences obtained from model I - input space $\{a,b,c,\sharp\}$ | 99  |

| 5.6  | Solutions obtained from the historical record database                 | 99  |

| 5.7  | Average result from 11 experiments                                     | 100 |

| 5.8  | Solutions obtained using by random search                              | 101 |

| 5.9  | UIO sequences for model ${\bf II}$ found by random search              | 102 |

| 5.10 | UIO sequences for model II found by GA                                 | 103 |

| 5.11 | Missing UIOs when using model III; GA:simple GA without shar-          |     |

|      | ing; SA:simple SA without sharing; GA/S:GA with sharing; SA/N:SA       | L   |

|      | with sharing using normal T drop; SA/R:SA with sharing using           |     |

|      | rough T drop                                                           | 116 |

## LIST OF TABLES

| 5.12 | Missing UIOs when using model II; GA:simple GA without shar-                |

|------|-----------------------------------------------------------------------------|

|      | ing; SA:simple SA without sharing; GA/S:GA with sharing; SA/N:SA            |

|      | with sharing using normal T drop; SA/R:SA with sharing using                |

|      | rough T drop                                                                |

| 6.1  | Specification finite state machine with 25 states used for simulations. 138 |

| 6.2  | Examples of faulty implementations that F- and B-method fail to             |

|      | detect                                                                      |

| 6.3  | Numbers of F-UIOs and UIOCs that lost the property of unique-               |

|      | ness in the faulty implementations                                          |

| 6.4  | Mutants that pass the test                                                  |

| 6.5  | Lengths of the test sequences                                               |

| 7.1  | Specification finite state machine used for experiments                     |

| 7.2  | Unique input/output circuit sequences for each state of the finite          |

|      | state machine shown in Table 7.1                                            |

| 7.3  | Injected faults                                                             |

# Chapter 1

# Introduction

# 1.1 About testing

Development of software systems is comprised of three stages. In the first stage, developers of the system derive a set of requirements from their customers. These requirements are normally represented in a requirements specification. Then, in consultation with these requirements, a design is built. After that, Coding, or implementing takes place where the design is translated into code using some programming language. Errors might be introduced at this stage, but can be discovered by verification and testing. Testing is an integral and important part in the life cycle of software development. A testing process aims to check whether the implementation under test is functionally equivalent to its specification.

"Testing is the process of executing a program or system with the intent of finding errors, or, involves any activity aimed at evaluating an attribute or capability of a program or system and determining that it meets its required results" (Het88; Mye79).

The process of testing begins with test design. A set of tests is normally created through the analysis of the system under test. This set of tests is used to check whether the system has been correctly implemented. In the phase of test design, a test model is often required in order that the generation of tests is formalised. This model describes the system behaviour with abstracted information, aiming to reduce the complexity of the description of the system being developed. The test model can be constructed by using either informal spec-

ification languages or formal specification languages. Due to the properties of imprecision and ambiguity, informal specifications often lead to misunderstandings and make testing difficult and unreliable. By contrast, formal specification languages are based upon mathematics and have a formally defined semantics. The mathematical nature of formal specification languages leads to precise and unambiguous descriptions. Section 1.3 gives a brief review on the major formal specification languages.

After a test model is built, a test strategy needs to be defined for the generation of test cases. A test strategy is an algorithm or heuristic to create test cases. Two measurements are applied for the evaluation of efficiency of a test. One of the measurements is test cost while the other is fault coverage. A good test strategy needs to embody the two measurements in two aspects: (1) test cases generated with such a strategy should cover, as much as possible, all faults that the system under test may have; (2) test cost associated with these test cases should be relatively low.

When design is complete, a set of test cases is then applied to the system under test to check its correctness. With the input set of a test case being applied to the system, an output set will be received. The application of a test case is classified as pass or fail by comparing the output set to that defined in the specification. Failure caused by any test case suggests the existence of faults in the system under test.

The procedure of testing is summarised as four major steps:

- 1. Identify, model, and analyse the responsibilities of the system under test.

- 2. Design test cases based on this external perspective.

- 3. Develop expected results for each test case or choose an approach to evaluate the pass/fail status of each test case.

- 4. Apply test cases to the system under test.

Unfortunately, detecting all faults is generally infeasible. Howden (How76) suggests that there is no algorithm to find consistent, reliable, valid, and complete test criteria. Complete testing is in general a very difficult process. Instead,

testing provides a level of confidence in the correctness of an implementation with regard to the constraint of some test criteria. Exhaustive testing, where the test cases consist of every possible set of input values, is the only way that will guarantee complete fault coverage. This technique, however, is not practical. The size of the input domain makes exhaustive testing infeasible (And86).

Regardless of the limitations, testing is an expensive process, typically consuming at least 50 % of the total costs involved in the development (Bei90) while adding nothing to the functionality of the product. It has been suggested that manually generating test cases could be very difficult even for moderately sized systems (Mye79). Although, for some systems, it is possible to generate test cases manually, the process tends to be costly and inefficient. Automation of the testing process is thus required, which could be desirable both to reduce development costs and to improve the quality of (or at least confidence in) software.

#### 1.2 Validation and verification

Validation and verification are essential in the life cycle of system development. Without rigorous validation, verification and testing that the specification meets the customer's requirements and that the implementation is consistent with its specification, the development of a system is not complete.

#### 1.2.1 Validation

Validation is defined as "the process of evaluating a system or component during or at the end of the development process to determine whether it satisfies specified requirements" (IEE90). Validation checks that the system being developed conforms to the user's requirements. It generally answers the question, "Did we build the right system?" (Boe81).

Early validation of the system specification is very important. Before being translated into an implementation, a specification needs to be checked for validity, consistency, competence, realism and verifiability.

The process of validation is classified into two stages - *informal validation* and *formal validation*. In system development, once the writing of specification and the coding of implementation are complete, a set of validation tests needs

to be developed. The set of tests aims to report the majority of problems in the system being developed. This activity is referred to as informal validation since tests are run informally, and some system features are expected to be missing. Informal validation provides early feedback to software engineers. This feedback provide the system developers with foundations for system modifications, which help to increase confidence that the system being developed complies with the customer's requirements.

After informal validation is complete, the process comes to formal validation. A set of tests is designed and applied to the implementation under test with the purpose of bug correction. At this stage, the specification used for system coding is assumed to be valid and complete. The process of testing aims to check whether the implementation under test conforms to the specification. A formal test model is often defined. Formal approaches are applied for the derivation of test cases.

Validation is usually accomplished by verifying each stage of the software development life cycle. It should be noted that, in reality, specification validation is normally unlikely to discover all requirements problems. Some flaws and deficiencies in the specification can sometimes only be discovered when the system implementation is complete.

#### 1.2.2 Verification

Verification is defined as "the process of evaluating a system or component to determine whether the products of a given development phase satisfy the conditions imposed at the start of that phase" (IEE90). Verification involves checking that the implementation produced conforms to the specification. It addresses the question, "Did we build the system right?" (Boe81). Many techniques have been proposed for the verification but they all basically fall into two major categories: static verification and dynamic verification.

#### I. Static verification

Static verification is concerned with analysing the system being developed without executing it. Properties of the system such as syntax, parameter matching between procedures, typing and specification translation have to be checked for their correctness.

Software inspection (AFE84) is one of the static verification techniques that has been widely used. "A software inspection is a group review process that is used to detect and correct defects in a software work-product. It is a formal, technical activity that is performed by the work-product author and a small peer group on a limited amount of material. It produces a formal, quantified report on the resources expended and the results achieved" (AFE84).

During inspection, either the code or the design of a work-product is compared to a set of pre-established inspection rules. Inspection processes are mostly performed along checklists which cover typical aspects of the software behaviour.

Another static verification technique is walk-through (Tha94). Walk-throughs are similar peer review processes that involve the author of the program, the tester and a moderator. The participants of a walk-through create a small number of test cases by simulating the computer. Its objective is to question the logic and basic assumptions behind the source code, particularly of program interfaces in embedded systems (Tha94).

Proofs are usually used for the verification, either informally or formally. At an informal level, proofs work on step-by-step reasoning involved in an inspection of the system while, at a more formal level, mathematical logic is introduced. A formal proof is based upon a set of axioms and inference rules. If the test model is constructed with a formal language, a set of formal proofs can be derived to prove the conformance of implementation to its specification. As formal proofs can be checked automatically in a formal language, an automatic proof checker can be used for the construction of proofs.

However, it is usually difficult to prove the conformance to the specification for a large scale system. This can be alleviated through the use of refinement. Specification, in some formal notation, can be converted into an implementation using a series of simple refinements, each of which is capable of being proven. By such an operation, no fault should be present in the implementation.

## II. Dynamic verification

Dynamic verification involves the execution of a system or component. A number of test inputs are chosen. Corresponding test outputs are used to determine the gap between the test model and the real implementation. These test inputs are called *test cases* and the process is called *testing*.

Testing consists of three major stages, namely, unit or module testing, integration testing and system testing. In the stage of module testing, modules are tested individually, aiming to find defects in logic, data, and algorithms. In the stage of integration testing, modules are grouped with regard to their functionalities, each group being tested as an integrated whole. Once integration testing has finished, testing comes to the stage of system testing where the implementation is thoroughly tested as a system, taking more comprehensive factors into account.

Testing can be further divided into three categories - functional testing, structural testing, and random testing.

#### A: Functional testing

Functional testing aims to identify and test all functions of the system defined in the specification. Involving no knowledge of the implementation of the system, functional testing is a type of black-box testing. Category partition (OB89) is the most widely used technique in functional testing. It involves five steps:

- 1. Analyse the specification to identify individual functional units;

- 2. Identify parameters and environment variables of the functional unit;

- 3. Identify the categories for each parameter and environment variable;

- 4. Partition each category into a set of choices and possible values;

- 5. Specify the possible results and the changes to the environment.

Two advantages can be noticed in category partition method. First, the test set is derived from the specification and therefore has a better chance of detecting whether some functionalities are missed from the implementation. Second, the test phase can be started early in the development process and the test set can be easily modified as the system evolves.

However, it is difficult to formally define categories and choices. This could make it very hard to assess whether the criteria used for partition are adequate. As a result, the generation of partitions relies heavily on the experience of testers.

#### B: Structural testing

Structural testing is a type of white-box testing. It uses the information from the internal structure of the system to devise tests to check the operation of individual components. Three scopes are addressed in structural testing - Statement Coverage, Branch Coverage and Path Coverage. If, in a test, the test set causes every statement of the code to be executed at least once, then statement coverage is achieved, while, if the test set causes every branch to be executed at least once, then branch coverage is achieved. In other words, for every branch statement, each of the possibilities must be performed on at least one occasion. If the test set causes every distinct execution path be taken at some point, then path coverage is achieved.

#### C: Random testing

Random testing randomly chooses test cases from the test domain. It provides a means to detect faults that remain undetected by the systematic methods. Exhaustive testing where the test cases consist of every possible set of input values is a form of random testing. Although exhaustive testing guarantees a complete fault coverage for the system being developed, it is impossible to accomplish in practice (And86).

#### 1.2.3 Validation vs. verification

Validation and verification are highly related to software quality. With the increasing complexity of systems, validation and verification become more and more important. Without validation, an incomplete specification might be acquired, leading to an inadequate design and an incorrect implementation; while, without verification, no proof is exhibited that an implementation conforms to its

specification. Planning for validation and verification is often viewed as a very important step from the beginning of the development.

Validation and verification can be conducted in parallel within a project as they are not mutually exclusive.

# 1.3 Formal specification languages

Writing specification from customer requirements is a key activity in the development of systems. A well-defined requirement specification language is considered to be a prerequisite for efficient and effective communication between the users, requirements engineer and the designer. Specification languages provide frames where problems are defined and solved. They provide operators that are used in analysing, manipulating and transforming the system description.

Requirements specification languages may be classified into two major classes: informal specification languages and formal specification languages. Formal specification language have a mathematical (usually formal logic) basis and employ a formal notation to model system requirements (AG88) while informal specification languages use a combination of graphics and semiformal textual grammars to describe and specify system requirements. Despite some 'formalising' efforts at the specification and design, informal specifications tend to be ambiguous and imprecise, which might lead to misunderstanding and makes it difficult to detect inconsistencies and incompleteness in the specification.

By contrast, by using the formal notation, precision and conciseness of specifications can be achieved. As a formal notation can be analysed and manipulated using mathematical operators, mathematical proof procedures can be used to test (and prove) the internal consistency and syntactic correctness of the specifications. In addition, by using formal notation, the completeness of the specification can be checked in the sense that all enumerated options and elements have been specified.

Three main types of formal specification languages have been proposed for the system description, these being:

#### 1. Model oriented specification languages

- 2. Algebraic specification languages

- 3. Process algebras

## Model oriented specification languages

Model oriented specification languages are aimed to build up a mathematical model for the system being developed. The specification is written with a model oriented language where objects such as data structures and functions are mathematically described in details. These mathematical objects are structurally similar to the system required. During the design and implementation, mathematical objects are transformed in ways that preserve the essential features of the requirements as initially specified.

It is characteristic of model oriented languages that the model of the system is given by describing the state of the system, together with a number of operations over that state. An operation is a function which maps a value of the state together with values of parameters to the operation onto a new state value.

The most widely known model oriented specification languages are VDM-SL, the specification language associated with VDM (Jon90), the Z specification language (Spi88; Spi89) and the B specification language (Abr96).

# Algebraic specification languages

Algebraic specification languages such as OBJ3 (GW88) specify information systems using methods derived from abstract algebra or category theory. Abstract algebra is the mathematical study of certain kinds or aspects of structure abstracted away from other features of the objects under study. Algebraic methods are beneficial in permitting key features of information systems to be described without prejudicing questions that are intended to be settled later in the development process (implementation detail).

# Process algebras

Process algebras are best described as a set of formalisms for modelling systems that allow for mathematical reasoning with respect to a set of desired properties, be it equivalence, absence of deadlocking or some safety properties. Process algebras involve defining a set of agents and the manner in which these agents interact, and thus are good at modelling situations in which there are a number of entities that interact by communicating with each other. By expressing concurrency, process algebras allow the analysis of this concurrency.

It is usually the case that process algebras are used for model concurrent systems and communication systems. The best known process modelling languages are CSP (Hoa85), CCS (Mil89) and LOTOS (fSI88).

Finite state machines (Koh78) are a less general type of process algebra. In chapter 4, testing from finite state machines is discussed. However, the use of finite state machines has disadvantages where they are not able to express non-determinism and concurrency either as elegantly or as powerfully as the more general process algebras.

The formal languages above look at systems in different ways and, consequently, represent information in different forms. The selection of a type of formal specification language for modelling a system depends upon the nature of the system being developed.

It should be noted that the use of formal specification languages might also lead to some disadvantages. One major issue is that requirements usually change during a project, which makes the procedure of determining a final specification expensive. It was suggested that it is very expensive to develop a formal specification of a system, and it is even more expensive to show that a program meets that specification (AG88).

# 1.4 Test cost and fault coverage

Two factors, test cost and fault coverage, are tightly coupled with the evaluation of a test. Test cost involves the numbers of test data that are used for the verification of the system under test while fault coverage considers the percentage of faults that have been detected by such a test. It is always desirable that a test will achieve complete fault coverage with the lowest test cost.

Test cost and fault coverage, however, sometimes counteract one another. On one hand, a system needs to be tested with enough test data in order that the complete fault coverage has been achieved. The more test data are applied, the more deficiencies will be detected. Exhaustive testing guarantees the complete fault coverage for the system under test. However, tests that guarantee complete fault coverage are sometimes too long for practical applications, which will consequently result in a higher test cost. Tests using less test data are always preferred; on the other hand, too little test data might cause some deficiencies to be missed by the test, leading to an incomplete test. The problem of test cost leads to the study of test optimisation while the problem of fault coverage leads to the study of test quality.

An effective test often requires a trade-off to be made between the test cost and the fault coverage. A good test generation strategy needs to compromise between the two factors in two aspects: (1) test cases generated with such a strategy should cover, as much as possible, all faults that the system under test may have; (2) the test cost associated with such test cases should be comparatively low.

Optimisation on test cost with regard to fault coverage has been thoroughly studied when finite state machines are applied (ATLU91; Hie97; MP93; SLD92; YU90). In chapter 4, testing from finite state machines is discussed. This PhD work has investigated the problem of test quality when testing from finite state machines. In the work, robust Unique Input/Output Circuit (UIOC) sequences were defined for state verifications. Based on rural Chinese postman algorithm, a new test generation algorithm is given. Experimental results suggest that the proposed method leads to a more robust test sequence than those constructed with the existing methods without significantly increasing the test length. The work is discussed in chapter 6.

# 1.5 Fault observation and diagnosis

An important yet complicated issue associated with testing is fault diagnosis. The process of testing aims to construct test cases that could be used to provide confidence that the implementation under test conforms to its specification.

Usually, a system is modelled as a set of functional units (components), some of which are connected with others through input and output coupling. Each unit is assigned with two attributes: an I/O port and an internal state. I/O

port provides testers with an interface for the observation of outputs when inputs are sent, while, the internal state is not visible and can only be inferred through exhibited input/output behaviour. Once a test case is constructed, it is applied to an implementation, all units being executed successively. I/O differences exhibited between the implementation and the specification suggest the existence of faults in the implementation. The first observed faulty I/O pair in an observed I/O sequence is called a *symptom*. A symptom could have been caused by either an incorrect output (an *output fault*) exhibited by the unit being tested, or an earlier incorrect state transfer (a *state transfer fault*) that remains unexhibited in the units that have already been executed by the checking data. It is therefore important to define strategies to guide the construction of test data. These data could be used to (effectively) isolate the faulty units in the implementation that will explain the symptoms exhibited.

The process of isolating faults from the implementation with regard to the symptoms observed is called *fault diagnosis* (LY96).

However, fault diagnosis is very difficult. Very little work has been done for the diagnostic and the fault localisation problems (GB92; GBD93). Steinder and Sethi (SS04) proposed a probabilistic even-driven fault propagation model where a probabilistic symptom-fault map is used for the process of fault diagnosis. The technique utilises a set of hypotheses that most probably explains the symptoms observed at each stage of evaluation. The set of hypotheses is updated with the process going further, maximising the probabilities of hypotheses for the explanation of observed symptoms.

Ghedamsi and Bochmann (GB92; GBD93) modelled the process of fault diagnosis with finite state machines. A set of transitions is generated whose failure could explain the behaviour exhibited. These transitions are called *candidates*. They then produce tests (called distinguishing tests) in order to find the faulty transitions within this set. However, in the approach, the cost of generating a conflict set is not considered.

Hierons (Hie98) extended the approach to a special case where a state identification process is known to be correct. Test cost is then analysed by applying statistical methods. Since the problem of optimising the cost of testing leads to

NP-hard (Hie98), heuristic optimisation techniques such as *Genetic Algorithms* and *Simulated Annealing* are suggested.

This PhD work studied the problem of fault diagnosis. In the work, heuristics are defined for fault isolation and identification when testing from finite state machines. The proposed approach attempts to lead to a symptom being observed in some shorter test sequences, which helps to reduce the cost of fault isolation and identification. The work is discussed in chapter 7.

# 1.6 Testing with MOTs

Metaheuristics Optimisation Techniques (MOTs) such as Genetic Algorithms (GAs) (Gol89) and Simulated Annealing (SA) (KGJV83) are widely used in the problems of search and optimisation. More recently, MOTs have been successfully applied in software engineering, including automating the generation of test data. Examples of such applications can be found in structural coverage testing (branch coverage testing) (JES98; MMS01), worst case and best case execution time estimation (WSJE97), and exception detection (TCMM00).

MOTs are search techniques that simulate nature. When using MOTs, an objective function is defined to guide the search of solutions for the problem under investigation. The objective function is called the *fitness function*. The search process could be aimed at either maximising or minimising the fitness function. An iteration scale is defined to determine the computational times. At each step of the computation, a new solution is provided. By evaluating its fitness value, the solution will be either accepted or rejected. In chapter 2, some MOTs are introduced.

Automating the generation of test data is of great value in reducing the development cost and improving the quality in software development. MOTs provide means to automate such a process. The reasons that MOTs are used in the generation of test cases are: (1) the problem of generating test cases is equivalent to a search problem where good solutions need to be explored in the input space of the system being developed. Usually, the input space is large. This could make the search a costly and inefficient process when traditional algorithms are applied. This problem, however, can be alleviated by heuristic search, such as MOTs;

(2) some problems in testing such as the construction of unique input/output sequences are NP-hard problems and MOTs have proved to be efficient in providing good solutions for NP-hard problems.

This PhD work investigated the construction of multiple Unique Input/Output (UIO) sequences by using MOTs. In the work, a fitness function is defined to guide the search of input sequences that constitute UIOs for some states. The fitness function works by encouraging the early occurrence of discrete partitions in the state splitting tree constructed by an input sequence while punishing the length of this input sequence. The work and the experimental results are discussed in chapter 5.

#### 1.7 The structure of this thesis

This thesis is comprised of eight chapters. It is organised as follows: chapter 1 briefly introduces the background of testing; chapter 2 defines the preliminaries and notation used in this thesis; chapter 3 reviews the major test generation techniques; chapter 4 reviews the automated generation of test cases when testing from finite state machines; chapter 5 studies the construction of Unique Input/Output (UIO) sequences and proposes a model for the construction of multiple UIOs using Metaheuristic Optimisation Techniques (MOTs); chapter 6 investigates the fault coverage in finite state machine based testing and proposes a new type of Unique Input/Output Circuit (UIOC) sequence for state verification. Based upon Rural Chinese Postman Algorithm (RCPA), a new approach is proposed for the generation of test sequences from the finite state machine under test; chapter 7 looks at fault diagnosis when testing from finite state machines, and proposes heuristics for fault isolation and identification; in chapter 8, conclusions are drawn. Some future work is also suggested in chapter 8.

# Chapter 2

# Preliminaries and notation

# 2.1 Graph theory

The automated generation of test cases benefits from the applications of graph theory when testing from finite state machines. In this section, preliminaries and notation of graph theory are introduced. Terminologies, notation and algorithms are mainly cited from ref. (BJG01).

# 2.1.1 Directed graph

**Definition 2.1.1** A graph G is a pair (V, E) where V is a set of vertices, and E is a set of edges between the vertices  $E \subseteq \{\{u, v\} | u, v \in V\}$ .

Figure 2.1: An example of labelled digraph.

**Definition 2.1.2** A labelled digraph  $G = (V, E, \Sigma)$  is a directed graph with vertex set V, label set  $\Sigma$  and edge function  $E \colon V \times \Sigma \to V$ ,  $E(u, \sigma) = v$  where  $u, v \in V$  and  $\sigma \in \Sigma$ .

An example of a labelled digraph is illustrated in Figure 2.1 where V(D) =  $\{u, v, w, x, y, z\}$ ,  $E(D) = \{(u, v; a_5), (u, w; a_7), (w, u; a_8), (z, u; a_3), (x, z; a_9), (y, z; a_4), (v, x; a_1), (x, y; a_2), (w, y; a_6)\}$  and  $\Sigma = \{a_1, a_2, a_3, a_4, a_5, a_6, a_7, a_8\}$ . A labelled digraph is a special case of digraph where each edge is labelled with characters, indicating the relation between two vertices of the edge.

The number of vertices in a digraph D is called the *order* or *size*. An edge  $(u,v) \in E(D)$  leaves u and enters v. u is the *head* of the edge and v the *tail*. The head and tail of an edge are its *end-vertices*; the end-vertices are *adjacent*, i.e. u is adjacent to v and v is adjacent to u. For a vertex  $v_i \in V$ , the *in-degree*,  $d^+(v_i)$ , is the number of inward edges to  $v_i$ ; the *out-degree*,  $d^-(v_i)$ , is the number of outward edges from  $v_i$ . The index of a vertex  $\xi(v_i)$  is defined as the difference between the out-degree and in-degree of this vertex,  $\xi(v_i) = d^-(v_i) - d^+(v_i)$ . For example, the order of the labelled digraph shown in Figure 2.1 is 6; in the digraph, edge (x,y) leaves vertex x and enters y; x is the head of (x,y) and y the tail;  $d^+(x) = 1$  while  $d^-(x) = 2$ ;  $\xi(x) = 1$ .

**Definition 2.1.3** A digraph D is symmetric if, for every vertex  $v_i \in V$ ,  $d^+(v_i) = d^-(v_i)$ .

**Definition 2.1.4** A walk in D is an alternating sequence  $W = v_1 e_1 v_2 e_2 v_3 ...$   $v_{k-1}e_{k-1}v_k$  of vertices  $v_i \in V(D)$  and edge  $e_i \in E(D)$  such that the head of  $e_i$  is  $v_i$  and the tail of  $e_i$  is  $v_{i+1}$  for every i = 1, 2, ..., k-1. The length of a walk is the number of its edges.

The set of vertices  $\{v_1, v_2, ..., v_k\}$  in a walk W is denoted by V(W) and the set of edges  $\{e_1, e_2, ..., e_{k-1}\}$  is denoted by E(W). W is a walk from  $v_1$  to  $v_k$  or an  $(v_1, v_k)$ -walk. A walk W is closed if  $v_1 = v_k$  and open otherwise. If  $v_1 \neq v_k$ , then the vertex  $v_1$  is the initial vertex of W, the vertex  $v_k$  is the terminal vertex of W, and  $v_1$  and  $v_k$  are end-vertices of W. A walk W is a trail if all edges in W are distinct; a vertex  $v_i$  is reachable from a vertex  $v_j$  if D has an  $(v_i, v_j)$ -walk.  $W_1 =$

v(v, x)x(x, y)y(y, z)z(z, u)u(u, w)w and  $W_2 = v(v, x)x(x, y)y(y, z)z(z, u)u(u, v)v$  are two walks in Figure 2.1 where  $W_1$  is open while  $W_2$  closed. Edges in both walks are distinct and, therefore, both walks are trails; vertex w is reachable from vertex v. v is the initial vertex of  $W_1$  while w is the terminal.

**Definition 2.1.5** A walk W is a path if the vertices of W are distinct; W is a cycle if the vertices  $v_1, v_2, ..., v_{k-1}$  are distinct,  $k \geq 3$  and  $v_1 = v_k$ .

$W_1$  shown above is a path while  $W_2$  is a cycle. A path P is an  $[v_i, v_j]$ -path if P is a path between  $v_i$  and  $v_j$ , e.g. P is either an  $(v_i, v_j)$ -path or an  $(v_j, v_i)$ -path. An  $(v_i, v_j)$ -path  $P = v_1 v_2 ... v_n$  is minimal if, for every  $(v_i, v_j)$ -path Q, either V(P) = V(Q) or Q has a vertex not in V(P).

**Definition 2.1.6** A tour is a walk that starts and ends at the same vertex. An Euler tour in a digraph D is a tour that contains every edge of E(D) exactly once. A postman tour of a digraph D is a tour that contains every edge of E(D) at least once. A Chinese postman tour is a postman tour where the number of edges contained in the tour is minimal.

It is easy to see that an Euler tour is also a Chinese postman tour.

**Definition 2.1.7** A digraph D is strongly connected (or, simply, strong) if, for every pair  $v_i$ ,  $v_j$  of distinct vertices in D, there exists a  $(v_i, v_j)$ -walk and a  $(v_j, v_i)$ -walk. In other words, D is strongly connected if every vertex of D is reachable from every other vertex of D. A digraph D is weakly connected if the underlying undirected graph is connected.

**Definition 2.1.8** A digraph H is a subdigraph of a digraph D if  $V(H) \subseteq V(D)$ ,  $E(H) \subseteq E(D)$  and every edge in E(H) has both end-vertices in V(H). H is said to be a spanning subdigraph (or a factor) of D if V(H) = V(D).

**Definition 2.1.9** The edge-induced subgraph D = (V', E') of a digraph D for some set  $E' \subseteq E$  is the subgraph of D whose vertex set is the set of ends of edges in E' and whose edge set is E'. D = (V', E') is an edge-induced spanning subgraph of D if V' = V.

**Lemma 2.1.1** (Kua62) A digraph D contains an Euler tour if and only if D is strongly connected and symmetric.

**Lemma 2.1.2** (EJ73) An Euler tour of a symmetric and strongly connected digraph D can be computed in linear time O(n) where n is the number of edges in D.

#### 2.1.2 Flows in networks

**Definition 2.1.10** A network  $\mathcal{N} = (V, E, l, u, b, c)$  is a directed graph D = (V, E) associated with the following functions on  $V \times V$ : a lower bound  $l_{ij} \geq 0$ , a capacity  $u_{ij} \geq l_{ij}$ , a cost  $c_{ij}$  for each  $(i, j) \in V \times V$  and a balance vector  $b: V \to \mathbb{R}$  that associates a real number with each vertex of D. These parameters satisfy the condition that for every  $(i, j) \in V \times V$ , if  $(i, j) \notin E$ , then  $l_{ij} = u_{ij} = 0$ .

**Definition 2.1.11** A flow x in a network  $\mathbb{N}$  is a function  $x : E \to \mathbb{R}$  on the edge set of  $\mathbb{N}$ ; the value of x on the edge (i, j) is denoted as  $x_{ij}$ . An integer flow in  $\mathbb{N}$  is a flow x such that  $x_{ij} \in \mathbb{Z}$  for every edge (i, j).

For a given flow x in  $\mathbb{N}$  the *balance vector* of x is the following function  $b_x$  on the vertices:

$$b_x = \sum_{vw \in E} x_{vw} - \sum_{uv \in E} x_{uv} \qquad \forall v \in V.$$

(2.1)

A vertex v is a source if  $b_x(v) > 0$ , a sink if  $b_x(v) < 0$ , and otherwise v is balanced  $(b_x(v) = 0)$ . A flow x in  $\mathcal{N} = (V, E, l, u, b, c)$  is feasible if  $l_{ij} \leq x_{ij} \leq u_{ij}$  for all  $(i, j) \in E$  and  $b_x(v) = b(v)$  for all  $v \in V$ . A circulation is a flow x with  $b_x(v) = 0$  for all  $v \in V$ .

The cost of a flow x in  $\mathcal{N} = (V, E, l, u, c)$  is given by

$$c^T x = \sum_{ij \in E} c_{ij} x_{ij}. \tag{2.2}$$

where  $c_{ij}$  is the cost of edge  $x_{ij}$ .

The notation of (s,t)-paths in a digraph D can be generalised as that of flows. If P is an (s,t)-path in a digraph D=(V,E), then an (s,t)-flow x can be

described in the network  $\mathcal{N}(V, E, l \equiv 0, u, c)$  by taking  $x_{ij} = k, k \in \mathbb{Z}^+$  if (i, j) is an edge of P and  $x_{ij} = 0$  otherwise. This flow has balance vector:

$$b_x(v) = \begin{cases} k, & \text{if } v = s \\ -k, & \text{if } v = t \\ 0, & \text{otherwise} \end{cases}$$

The value of an (s, t)-flow x is defined by

$$|x| = b_x(s) \tag{2.3}$$

A path flow f(P) along a path P in  $\mathbb{N}$  is a flow with the property that there is some number  $k \in \mathbb{Z}^+$  such that  $f(P)_{ij} = k$  if (i,j) is an edge of P and otherwise  $f(P)_{ij} = 0$ ; a cycle flow is defined as flow f(C) for any cycle C in D. The edge sum of two flows x, x', denoted x, x', is simply the flow obtained by adding the two edge flows edge-wise. Two path flow x, x' of the same trail can be merged into a new flow  $x'' = x \oplus x'$  as long as the edge sum of each edge does not exceed its capacity.  $\oplus$  indicates that x and x' are decompositions of x''.

**Theorem 2.1.1** (BJG01) Every flow x in  $\mathbb{N}$  can be represented as the edge sum of some path and cycle flows  $f(P_1)$ ,  $f(P_2)$ ,...,  $f(P_{\alpha})$ ,  $f(C_1)$ ,  $f(C_2)$ , ...,  $f(C_{\beta})$  with the following two properties:

- 1. Every directed path  $P_i$ ,  $1 \le i \le \alpha$  with positive flow connects a source vertex to a sink vertex.

- 2.  $\alpha + \beta \le n + m$  and  $\beta \le m$ .

n is the number of vertices and m the number of edges in the network.

**Lemma 2.1.3** (BJG01) Given an arbitrary flow x in  $\mathbb{N}$ , one can find a decomposition of x into at most n + m path and cycle flows, at most m of which are cycle flows, in time O(nm).

Theorem 2.1.1 and Lemma 2.1.3 indicate that a flow x in a network  $\mathbb{N}$  can be decomposed into a number of path flows in polynomial time. This provides foundation for maximising the flow in  $\mathbb{N}$ . If a flow in  $\mathbb{N}$  can be decomposed into two sets of path flows where one is maximised (some edges in the path flow are

saturated) and the other, in terms of capacities, has allowances, one can then augment flows along unsaturated paths. Once no augmentation flow is found in  $\mathcal{N}$ , the flow obtained is maximal. The problem of the maximum of flows is discussed in the next section.

**Definition 2.1.12** For a given flow x in network  $\mathbb{N} = (V, E, l, u, b, c)$ , the residual capacity  $r_{ij}$  from  $v_i$  to  $v_j$  is defined as:

$$r_{ij} = (u_{ij} - x_{ij}). (2.4)$$

The residual network with respect to flow x is defined as  $\mathcal{N}_r = (V, E_{(x)}, l \equiv 0, r, c)$  where  $E(x) = \{(i, j) : r_{ij} > 0\}$ . A residual edge is an edge with positive capacity. A residual path (cycle) is a path (cycle) consisting entirely of residual edges.

#### 2.1.3 The maximum flow and minimum cost problems

Two issues that are highly coupled with flows in a network are the maximum flow problem and the minimum cost problem. In this section, these two issues are introduced separately.

#### A. The maximum flow problem

The study of (s,t)-flows in a network  $\mathbb{N}$  considers a special type of network  $\mathbb{N} = (V, E, l \equiv 0, u)$  where  $s, t \in V$  are special vertices that satisfy  $b_x(s) = -b_x(t)$  and  $b_x(v) = 0$  for all other vertices. s is called the source and t the sink of  $\mathbb{N}$ . An edge  $(i,j) \in \mathbb{N}$  is called saturated if  $x_{ij} = u_{ij}$ . As theorem 2.1.1 states, every (s,t)-flow x can be decomposed into a number of path flows along (s,t)-paths and some cycle flows<sup>1</sup>, each flow of such paths being a path flow. x is also said to be a flow from s to t. Its value |x| is denoted by  $|x| = b_x(s)$ . An (s,t)-flow of value k in a network  $\mathbb{N}$  is called a maximum flow if k is of the maximum value. The problem of finding a maximum flow from s to t is known as maximum flow problem. It is easy to see that an (s,t)-flow in a network  $\mathbb{N}$  is maximal if every (s,t)-path in  $\mathbb{N}$  uses at least one saturated edge  $(i,j) \in \mathbb{N}$ .

$<sup>^{1}</sup>$ It should be noted that the values of these cycle flows do not affect the value of the flow x.

Let x be an (s,t)-flow in  $\mathbb{N}$  and P be an (s,t)-path such that  $r_{ij} \geq \epsilon > 0$  for each edge (i,j) on P. Let x'' be an (s,t)-path flow of value  $\epsilon$  in  $\mathbb{N}(x)$  that is obtained by sending  $\epsilon$  units of flow along the path P. Let x' be a new flow that is obtained by  $x' = x \oplus x''$ . x' is of value  $|x| + \epsilon$ . P is called an augmenting path with respect to x. The capacity  $\delta(P)$  of P is given by:

$$\delta(P) = \min\{r_{ij} : (i,j) \in \mathcal{N}\}. \tag{2.5}$$

An edge (i, j) of P is a forward edge if  $x_{ij} < u_{ij}$ ; (i, j) and a backward edge if  $x_{ji} > 0$ . It is obvious that an (s,t)-flow x is not maximal, if there exists an augmenting path for x.

**Theorem 2.1.2** (CCPS98) A flow x in  $\mathbb{N}$  is a maximum flow if and only if  $\mathbb{N}$  has no augmenting paths.

**Theorem 2.1.3** (CCPS98) If all of the edge capacities in  $\mathbb{N}$  are integral, then the there exists an integer maximum flow.

The *minimum cut problem* is closely related to computing the maximum flow from a network. In the minimum cut problem, the input is the same as that of the maximum flow problem. The goal is to find a partition of the nodes that separates the source and sink so that the capacity of edges going from the source side to the sink side is minimum.

**Definition 2.1.13** An (s,t)-cut is a set of edges of the form  $(S, \bar{S})$  where  $S,\bar{S}$  form a partition of V such that  $s \in S$ ,  $t \in \bar{S}$ . The capacity of an (s,t)-cut  $(S,\bar{S})$  is the number  $u(S,\bar{S})$ , that is, the sum of the capacities of edges with tail in S and head in  $\bar{S}$ .

**Definition 2.1.14** A minimum (s,t)-cut is an (s,t)-cut  $(S, \bar{S})$  with  $u(S, \bar{S}) = min\{u(S', \bar{S}'):(S', \bar{S}') \text{ is an } (s,t)\text{-cut in } \mathcal{N}\}.$

It can be noted that the value of any flow is less than or equal to the capacity of any (s,t)-cut. Any flow sent from s to t must pass through every (s,t) cut, since the cut disconnects s from t. As flow is conserved, the value of the flow is limited by the capacity of the cut. This leads to Ford and Fulkerson's max-flow/min-cut theorem (FFF62).

**Theorem 2.1.4** (FFF62) The maximum value of any flow from the source s to the sink t in a capacitated network is equal to the minimum capacity among all (s,t)-cuts.

It is easy to prove that Theorem 2.1.2 and Theorem 2.1.4 are equivalent. Theorem 2.1.2 and 2.1.4 motivate the augmenting path algorithm of Ford and Fulkerson's (FFF62) where flow is repeatedly sent along augmenting paths. This process terminates when no such paths remain. If the original capacities in the network are integral, then the algorithm always augments integral amounts of flow. This operation is initiated by Theorem 2.1.3. Ford and Fulkerson's augmenting path algorithm was modified by Edmonds and Karp (EK72) where the shortest paths (by considering the number of edges) are always preferred for augmentation. Edmonds and Karp proved that the algorithm has complexity  $O(nm^2)$  where n is the number of vertices and m the number of edges.

#### B. The minimum cost flow problem

Given a network  $\mathcal{N} = (V, E, l, u, b, c)$ , a problem is to find a feasible flow x whose value of the cost is minimal. This problem is known as the minimum cost flow problem. As stated before, the cost of a flow x is given by  $C(x) = \sum_{ij \in E} x_{ij} c_{ij}$ . The goal of the problem is thus to find a feasible flow x where C(x) is minimised.

Residual network can be used to check if a given flow x in  $\mathbb{N}$  has minimum cost among all flows with the same balance vector. Let W be a cycle in  $\mathbb{N}$  and it has the cost c(W) < 0. Let  $\delta$  be the minimum residual capacity of an edge on W. Let x' be the cycle flow in  $\mathbb{N}$  that sends  $\delta$  units around W. If such a cycle flow exists in  $\mathbb{N}$ , a new flow x'' can then be constructed by  $x \otimes x'$ . The cost of x'' is  $c^Tx + c^Tx' = c^T + \delta c(W) < c^T$  (since c(W) < 0). The cost of x is therefore not minimal.

**Theorem 2.1.5** (BJG01) A flow x in  $\mathbb{N}$  is a minimum cost flow if and only if  $\mathbb{N}$  contains no negative cost residual cycles.

### 2.1.4 The Chinese postman tour

A problem in digraph theory intends to find a postman tour T in a directed and strongly connected digraph D where the sum of numbers of edges contained in T is minimal. This problem is known as the *Chinese postman problem* (Kua62), and such a tour is called a *Chinese postman tour*.

As one can see that, if a digraph D is strongly connected and symmetric, it contains an Euler tour (see Lemma 2.1.1). Since an Euler tour contains each edge in D only once, it is therefore a Chinese postman tour as well. Thus, when D is strongly connected and symmetric, the Chinese postman problem can be reduced to that of finding Euler tour. However, if D is strongly connected but not symmetric, then a Chinese postman tour contains every edge in E at least once, but perhaps more than once. Given a postman tour T of D, let  $\psi(v_i, u_j) \geq 1$  be the number of times edge (i,j) is contained in T. If, by replicating edge (i,j)  $\psi(v_i,u_j)$  times, a symmetric digraph D' is obtained, and D' is called a symmetric augmentation of D. According to Theorem 2.1.1, an Euler tour exists in D'. It is easy to prove that an Euler tour in D' is a Chinese postman tour in D if and only if the sum of the cost of replicated edges from the corresponding symmetric augmentation of D is minimal. Finding a Chinese postman tour in a digraph D is thus reduced to two steps:

- 1. augment D to derive a minimal symmetric digraph D';

- 2. find an Euler tour in D'.

Construction of minimal symmetric augmentation can be accomplished by using a flow network. This has been discussed by Kuan (Kua62). Here, we describe the algorithm in overview.

Given a digraph D=(V,E), the index of a vertex  $v_i \in V$  is  $\xi(v_i) = d_{v_i}^- - d_{v_i}^+$  where  $d_{v_i}^+$  is the in-degree of  $v_i$  and  $d_{v_i}^-$  the out-degree. Let  $\{s,t\}$  be a set of vertices where s is the source and t the sink. Let  $E^+$  and  $E^-$  be two sets of edges where  $E^+ = \{(s,v_i) : \forall v_i \in V, b_{v_i} > 0\}$  and  $E^- = \{(v_i,t) : \forall v_i \in V, b_{v_i} < 0\}$ . A flow graph  $D_f = (V_f, E_f)$  is constructed from D as follows:  $V_f = V \cup \{s,t\}$  and  $E_f = E \cup E^+ \cup E^-$ .

Let each edge in  $E^+$  and  $E^-$  has the cost of zero and capacity  $c(s, v_i) \equiv b_{v_i}$ ,  $c(v_j, t) \equiv b_{v_j}$ . The remaining edges in  $E_f$  have the same costs with their corresponding edges defined in D. For convenience, each edge in D is assigned a cost of 1. Each of the remaining edges has infinite capacity. A flow x on  $D_f$  is then a function  $x: E_f \to \mathbb{Z}^+$  that satisfies the following conditions:

1.

$$\forall v_i \in V_f - \{s, t\}, \quad \sum_{(v_i, v_i \in E_f)} x(v_i, v_j) = \sum_{(v_i, v_i \in E_f)} x(v_j, v_i).$$

2.

$$\forall (v_i, v_j) \in E_f$$

,  $x(v_i, v_j) \leq c(v_i, v_j)$  where  $c(v_i, v_j)$  is the capacity of  $(v_i, v_j)$ .

The cost of the flow x is given by

$$C(x) = \sum_{(v_i, v_j) \in E_f} C(v_i, v_j) x(v_i, v_j).$$

(2.6)

The problem is then converted to find a maximum-flow/minimum-cost flow x in  $D_f$ . Since x is a maximum flow and all edges in D has infinite capacity, all edges  $(v_i, v_j) \in E(D)$ , by replicating  $\psi(v_i, v_j)$  times, saturate to s or t, namely,  $x(s, v_i) = b_{v_i}, \forall v_i, b(v_i > 0)$  and  $x(v_i, t) = b_{v_i}, \forall v_i, b(v_i < 0)$ . The final augmented digraph D' is symmetric and, consequently, contains an Euler tour. Since the flow is also a minimum-cost flow, the number for replicating edges in D is minimal. Thus, the Euler tour in D' is a Chinese postman tour in D.

**Lemma 2.1.4** (ATLU91) An Euler tour P of a rural symmetric augmentation D' of D corresponds to a rural Chinese postman tour of D.

Finding Chinese postman tour in a directed graph is of great value in the automated generation of test sequences in finite state machine based testing. This is discussed in Chapter 4.

# 2.2 Metaheuristic optimisation techniques

Optimisation has been attracting the interests of researchers for many years. In general, the problem is described as follows. Suppose f(X) is a function with a set of parameters,  $X = \{x_1, ..., x_m\}$ , the problem is to find the set of X such that,

<sup>&</sup>lt;sup>1</sup>It should be noted that edges in  $E^-$  have negative capacities since  $b_{v_i} < 0$ .

after applying X to the function, f(X) is either maximised or minimised. Many algorithms have been proposed for solving the problem, among which Metaheuristic Optimisation Techniques (MOTs) such as Genetic Algorithms (GAs) (Gol89) and Simulated Annealing (SA) (MRR<sup>+</sup>53) are used to find optimal solutions in the problems with a large search space.

Recently, MOTs have been introduced in software engineering for the generation of test data. Applications can be found in structural coverage testing (branch coverage testing) (JES98; MMS01), worst case and best case execution time estimating (WSJE97), and exception detecting (TCM98; TCMM00). In this section, some major MOTs are introduced. Testing with MOTs is reviewed in Chapter 3.

### 2.2.1 Genetic algorithms

Genetic Algorithms (GAs) (Gol89) work on the simulation of natural processes, utilising selection, crossover and mutation. Since Holland's seminal work (1975) (Hol75), they have been applied to a variety of learning and optimisation problems. Many versions of GAs have been proposed and they are all based on the simple GA.

#### I. Simple GA

A simple GA starts with a randomly generated population, each element (chromosome) being a sequence of variables/parameters for the optimisation problem. The set of chromosomes represents the search space: the set of potential solutions. The representation format of variable values is determined by the system under evaluation. It can be represented in binary, by real–numbers, by characters, etc. The search proceeds through a number of iterations. Each iteration is treated as a generation. At each iteration, the current set of candidates (the population) is used to produce a new population. The quality of each chromosome is determined by a fitness function that depends upon the problem considered. Those of high fitness have a greater probability of contributing to the new population.

Selection is applied to choose chromosomes from the current population and pairs them up as parents. Crossover and mutation are applied to produce new

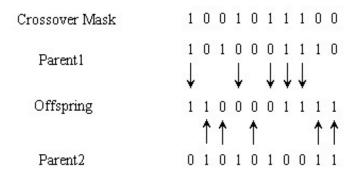

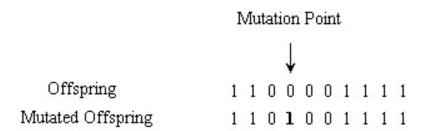

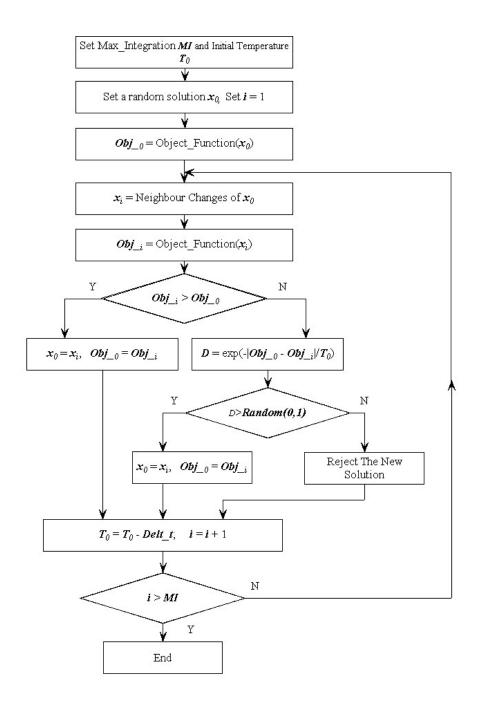

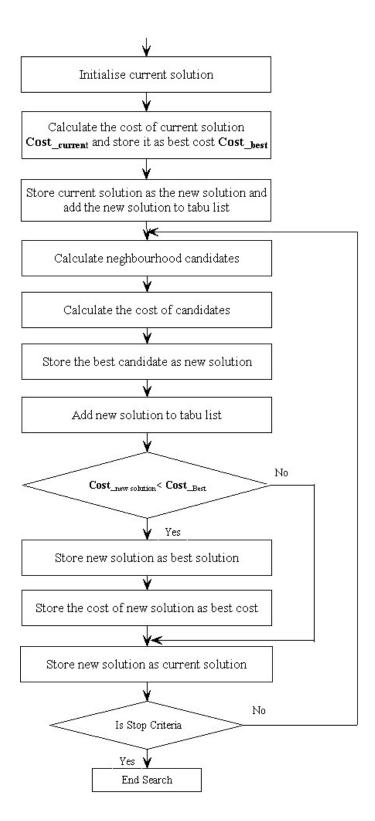

Figure 2.2: The flow chart of simple GA.

chromosomes. A new population is formed from new chromosomes produced on the basis of *crossover* and *mutation* and may also contain chromosomes from the previous population.

Figure 2.2 shows a flow chart for a simple GA. The following sections give a detailed explanation on *Selection*, *Crossover* and *Mutation*. All experiments in this work used roulette wheel selection and uniform crossover.

#### II. Encoding

In order to apply GAs, a potential solution to a problem should be represented as a set of parameters. These parameters are joined together to form a string of values (often referred to as a *chromosome*). Parameter values can be represented in various forms such as binary, real-numbers, characters, etc.

Obviously, the encoding strategy is central to the successful application of GAs. However, at present, there is no theory that enables a rigorous approach to the selection of the best encoding method for a particular problem. One principal that an encoding strategy needs to stick to is that the representation format should make the computation effective and convenient.

#### III. Reproduction

During the reproductive phase of a GA, individuals are selected from the population and recombined, producing children. Parents are selected randomly from the population using a scheme which favours the more fit individuals. Roulette Wheel Selection (RWS) and Tournament Selection (TS) are the two most popular selection regimes that are used for reproduction. RWS involves selecting individuals randomly but weighted as if they were chosen using a roulette wheel, where the amount of space allocated on the wheel to each individual is proportional to its fitness, while TS selects the fittest individual from a randomly chosen group of individuals.