# Amankwah, Emmanuel K. (2013) A parallel hybrid modular multilevel converter for high voltage DC applications. PhD thesis, University of Nottingham.

Access from the University of Nottingham repository: http://eprints.nottingham.ac.uk/13845/1/Thesis Emmanuel.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

- Copyright and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners.

- To the extent reasonable and practicable the material made available in Nottingham ePrints has been checked for eligibility before being made available.

- Copies of full items can be used for personal research or study, educational, or notfor-profit purposes without prior permission or charge provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

- · Quotations or similar reproductions must be sufficiently acknowledged.

Please see our full end user licence at: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

## A Parallel Hybrid Modular Multilevel Converter for High Voltage DC Applications

Emmanuel Kwaku Amankwah, MSc, BSc

Submitted to the University of Nottingham for the degree of Doctor of Philosophy, August, 2013.

#### Abstract

Reliability and efficiency of power transmission has been at the forefront of research for some time and is currently being given critical consideration due to the increased dependence on electrical energy. With the increased demand for electricity, engineers are considering different methods of supply arrangement to improve the security of electricity supply. High Voltage Direct Current (HVDC) transmission is a technology that avails itself for distance power transmission, interconnection of asynchronous networks and cross sea or offshore power transmission. The main element of an HVDC system is the AC/DC or DC/AC power converter.

Recently, a new breed of power converters suitable for HVDC transmission has been the subject of considerable research work. These converters are modular in structure with high efficiency and their operation results in higher power quality, with reduced filtering components when compared to the use of Line Commutated and two-level or three-level Voltage Sourced Converter (VSC) based transmission systems. One such modular circuit is the Parallel Hybrid Modular Multilevel Voltage Source Converter (PH-M2L-VSC).

This research investigates the operation and control of the PH-M2L-VSC for HVDC applications. Control schemes supporting the operation of the converter as would be expected of an HVDC VSC are proposed, including operation with an unbalanced AC network. Simulation results from a medium voltage demonstrator and experimental results from a laboratory scale prototype are presented to validate the methods proposed and enable a performance comparison to be made with other topologies.

### Acknowledgements

I would like to express my sincere gratitude to my supervisors Prof Jon Clare, Prof Pat Wheeler and Dr Alan Watson for their guidance during the period of this research. It is an honour to have worked with you. I would also like to thank Prof Stephen Finney and Prof Christopher Johnson for sparing their time to examine me and to grace my examination with their wealth of knowledge. To the University of Nottingham, I am humbled by the honour of been named among the Dean of Engineering Research Scholars. The financial support from Alstom Grid and the IGBT modules from Dynex Semiconductors, both, towards the experimental prototype construction are gratefully acknowledged.

I also appreciate each member of the PEMC group for the privilege to experience you during my time at the University of Nottingham.

I am most grateful to my parents the late Nana Kofi Nketiah and Elizabeth Appiaah for their unwavering support in the pursuit of my interests and their foresights. To my siblings Adwoa, Yaa, Akua, and Kwame for your support and encouragement, I am grateful. To my spouse Nana Cheraa Amankwah I really appreciate your patience, support, and encouragement during this phase of my life. Ama Amankwah, my dear daughter, your innocent and warm smiles, and the times we shared together kept me going during this study and I am more than grateful to have you around.

Finally, I would like to appreciate the Lord God for introducing this phase into my life and the grace to experience it fully.

### Contents

|   |      |                                       | Page |

|---|------|---------------------------------------|------|

| 1 | Intr | $\mathbf{r}$ oduction                 | 2    |

|   | 1.1  | Background to research project        | 2    |

|   | 1.2  | Project objectives                    | 7    |

|   | 1.3  | Thesis structure and content          | 8    |

|   | 1.4  | Contribution of thesis                | 10   |

| 2 | Hig  | h Voltage Direct Current Transmission | 12   |

|   | 2.1  | Introduction                          | 12   |

|   | 2.2  | LCC HVDC transmission                 | 14   |

|   |      | 2.2.1 Components of LCC HVDC systems  | 15   |

|   |      | 2.2.1.1 The power converter           | 15   |

|   |      | 2.2.1.2 The converter transformer     | 16   |

CONTENTS

|   |     |         | 2.2.1.3 AC and DC filters                                                   | 16 |

|---|-----|---------|-----------------------------------------------------------------------------|----|

|   |     | 2.2.2   | Configuration of LCC HVDC systems                                           | 17 |

|   | 2.3 | VSC-I   | HVDC transmission                                                           | 23 |

|   |     | 2.3.1   | Components of VSC-HVDC transmission system                                  | 24 |

|   |     |         | 2.3.1.1 The power converter                                                 | 24 |

|   |     |         | 2.3.1.2 The converter transformer                                           | 31 |

|   |     |         | 2.3.1.3 High voltage DC circuit                                             | 31 |

|   |     |         | 2.3.1.4 Auxiliary power conversion equipment                                | 32 |

|   |     | 2.3.2   | Comparison of the benefits of LCC HVDC and VSC-HVDC transmission systems    | 32 |

|   | 2.4 | Conclu  | usions                                                                      | 34 |

| 3 | Mo  | dular I | Multilevel VSCs for HVDC Transmission                                       | 35 |

|   | 3.1 | Introd  | uction                                                                      | 35 |

|   | 3.2 | The d   | ouble star modular multilevel VSC (M2LC)                                    | 42 |

|   | 3.3 | The se  | eries hybrid modular multilevel VSC (SH-M2L-VSC)                            | 47 |

|   | 3.4 | The p   | arallel hybrid modular multilevel VSC (PH-M2L-VSC)                          | 52 |

|   |     | 3.4.1   | Loss comparison of the PH-M2L-VSC and the M2LC $\ .$                        | 55 |

|   |     | 3.4.2   | Comparison of the energy storage requirement of the PH-M2L-VSC and the M2LC | 57 |

CONTENTS v

|   | 3.5  | Conclusions                                                        | 60  |

|---|------|--------------------------------------------------------------------|-----|

| 4 | The  | PH-M2L-VSC and its control for HVDC Transmission                   | 62  |

|   | 4.1  | Introduction                                                       | 62  |

|   | 4.2  | Operating principle of the PH-M2L-VSC                              | 63  |

|   | 4.3  | Three phase medium voltage PH-M2L-VSC used for the control studies | 69  |

|   |      | 4.3.1 Number of cells in a converter chainlink                     | 69  |

|   |      | 4.3.2 The converter transformer                                    | 71  |

|   |      | 4.3.3 DC and AC inductors                                          | 71  |

|   | 4.4  | Converter chainlink cell voltage control                           | 72  |

|   |      | 4.4.1 Dynamics of cell capacitor voltages                          | 72  |

|   |      | 4.4.2 Balancing the energy level in the chainlink cells            | 78  |

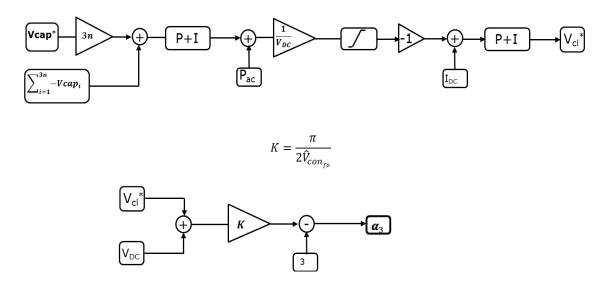

|   | 4.5  | Converter modulation ratio control                                 | 85  |

|   | 4.6  | Total chainlink voltage control                                    | 85  |

|   | 4.7  | AC/DC power flow control                                           | 88  |

|   |      | 4.7.1 Decoupled vector current control of the PH-M2L-VSC           | 93  |

|   | 4.8  | Modulation and gating signal generation                            | 95  |

|   | 4.9  | Simulation results                                                 | 98  |

|   | 4.10 | Conclusions                                                        | 103 |

CONTENTS vi

| 5 | Оре            | eration of the PH-M2L-VSC during grid unbalance                                                                                                           | 104                             |

|---|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   | 5.1            | Introduction                                                                                                                                              | 104                             |

|   | 5.2            | Effect of unbalanced grid voltage on converter operation                                                                                                  | 106                             |

|   | 5.3            | Proposed control strategy for sustainable operation of the PH-M2L-VSC during grid voltage unbalance                                                       | 113                             |

|   |                | 5.3.1 Determining the values of $\alpha_a, \alpha_b, \alpha_c$ to ensure equal power exchange between the AC grid and the respective converter chainlinks | 116                             |

|   | 5.4            | Implementation of the proposed voltage unbalance control                                                                                                  | 119                             |

|   | 5.5            | Conclusions                                                                                                                                               | 127                             |

|   |                |                                                                                                                                                           |                                 |

| 6 | Exp            | perimental Converter                                                                                                                                      | 128                             |

| 6 | <b>Exp</b> 6.1 | Introduction                                                                                                                                              | 128<br>128                      |

| 6 |                |                                                                                                                                                           | 128                             |

| 6 | 6.1            | Introduction                                                                                                                                              | 128<br>128                      |

| 6 | 6.1            | Introduction                                                                                                                                              | 128<br>128<br>133               |

| 6 | 6.1            | Introduction                                                                                                                                              | 128<br>128<br>133<br>136        |

| 6 | 6.1            | Introduction                                                                                                                                              | 128<br>128<br>133<br>136<br>139 |

| 6 | 6.1            | Introduction                                                                                                                                              | 128<br>128<br>133<br>136<br>139 |

CONTENTS vii

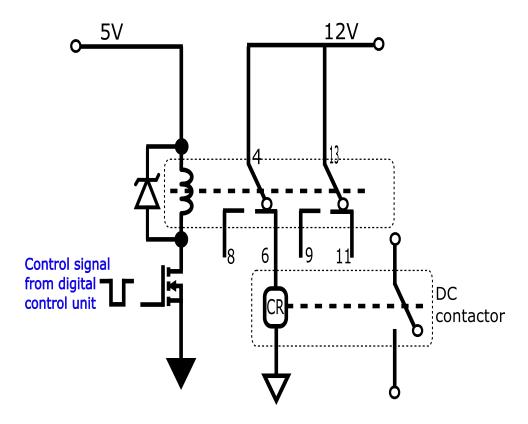

|   |     | 6.3.2   | The Pre-charge control circuit                                                     | 141 |

|---|-----|---------|------------------------------------------------------------------------------------|-----|

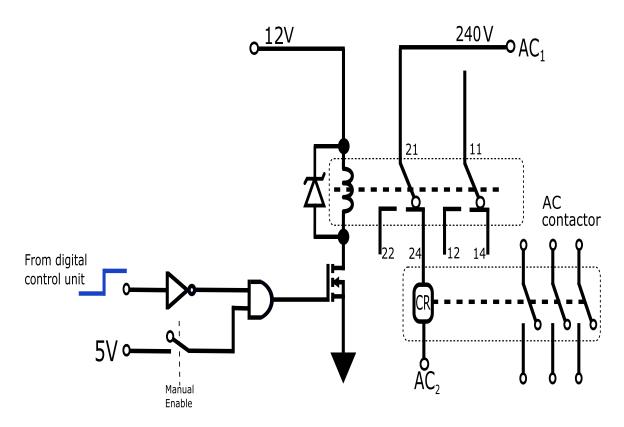

|   |     | 6.3.3   | AC contactor control circuit                                                       | 144 |

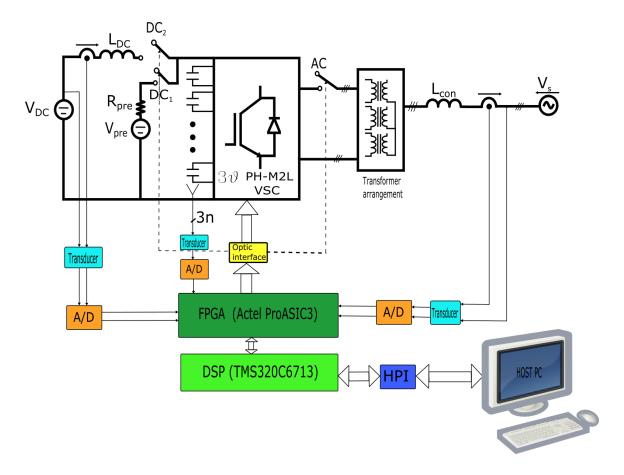

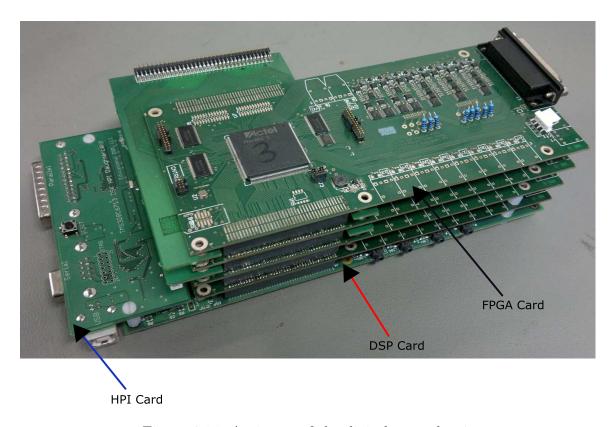

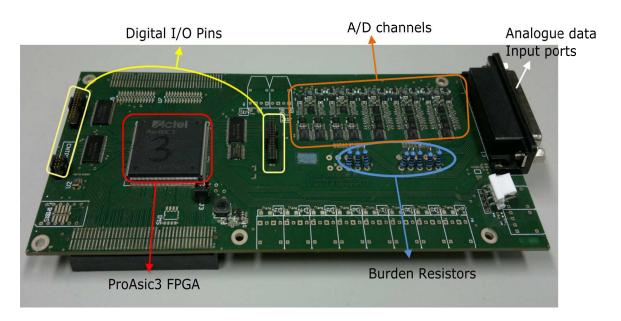

|   |     | 6.3.4   | Digital control unit                                                               | 144 |

|   |     |         | 6.3.4.1 The TMS320C6713 DSP board                                                  | 146 |

|   |     |         | 6.3.4.2 The FPGA                                                                   | 147 |

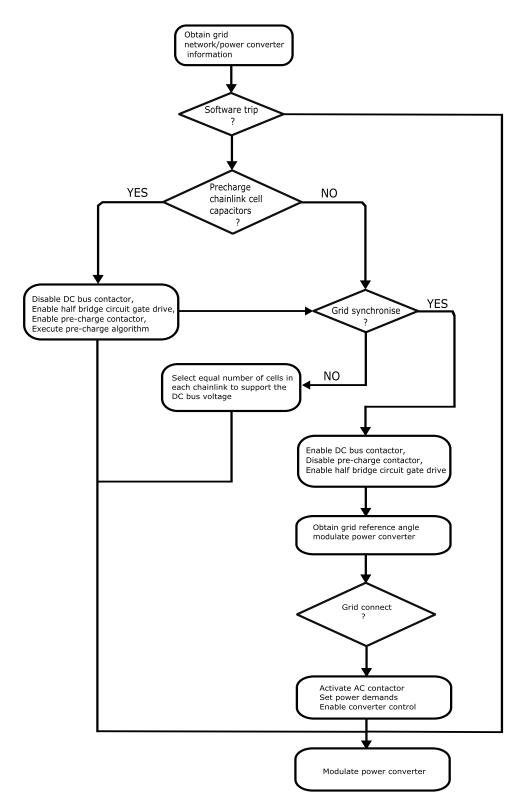

|   | 6.4 | Contro  | ol software implementation                                                         | 150 |

|   | 6.5 | Conclu  | asions                                                                             | 153 |

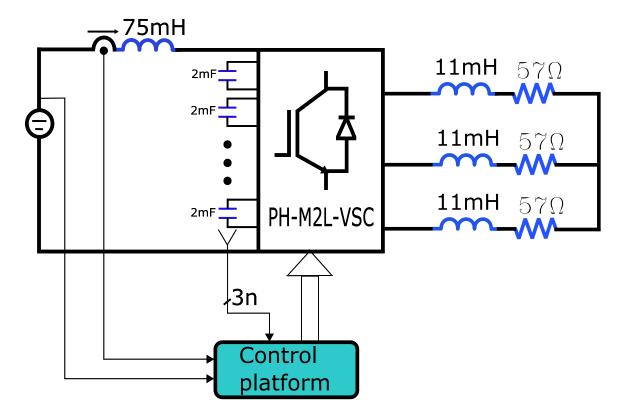

| 7 | Exp | erimei  | ntal Results                                                                       | 154 |

|   | 7.1 | Introd  | uction                                                                             | 154 |

|   | 7.2 | Conve   | rter inverting into an RL load                                                     | 155 |

|   |     | 7.2.1   | Converter operating as an inverter with an RL load and no modulation ratio control | 155 |

|   |     | 7.2.2   | Converter operating as an inverter with an RL load with modulation ratio control   | 163 |

|   | 7.3 | Effect  | of non-ideal power electronic switches                                             | 173 |

|   | 7.4 | Conve   | rter operation when connected to the grid                                          | 179 |

|   | 7.5 | Conclu  | isions                                                                             | 191 |

| 8 | Con | ıclusio | ns                                                                                 | 192 |

|   | 8.1 | Summ    | ary of contributions                                                               | 195 |

| CONTENTS | vii |

|----------|-----|

|----------|-----|

|              | 8.2 Further work                                                              | 196             |

|--------------|-------------------------------------------------------------------------------|-----------------|

| $\mathbf{A}$ | Published Journal and Conference Papers                                       | 206             |

| В            | Limits of third harmonic voltage injection                                    | 208             |

| $\mathbf{C}$ | Chainlink current expressed in terms of AC current                            | 211             |

| D            | Power exchange between a converter chainlink and a balanced AC network        | □<br><b>213</b> |

| ${f E}$      | Effect of unbalance on H-bridge switching time instants                       | 215             |

| $\mathbf{F}$ | Converter chainlink voltage and power exchange with the grid during unbalance | -<br>218        |

# List of Figures

|     |                                                    | Page |

|-----|----------------------------------------------------|------|

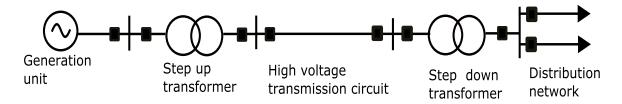

| 1.1 | Structure of a conventional power network          | . 3  |

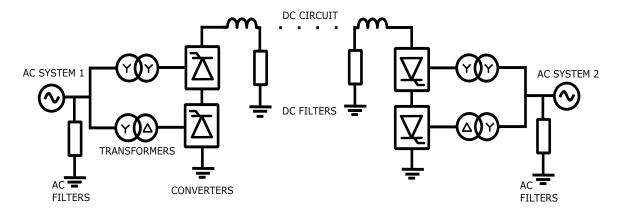

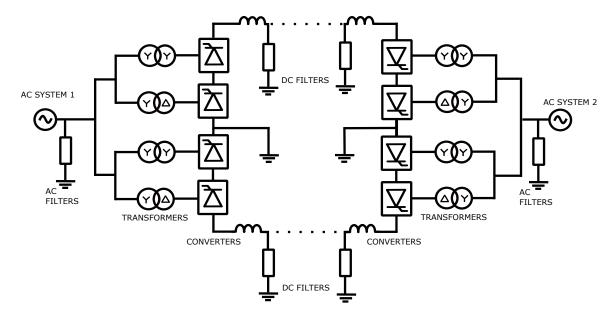

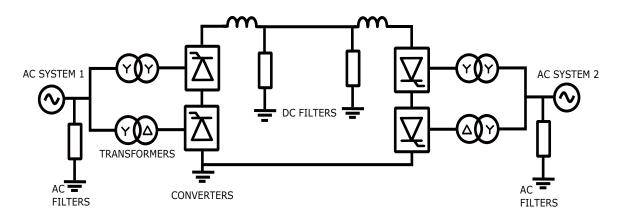

| 1.2 | LCC-HVDC transmission system                       | . 4  |

| 1.3 | A thyristor module (Source: Alstom)                | . 5  |

| 1.4 | A thyristor valve (Source: Alstom)                 | . 6  |

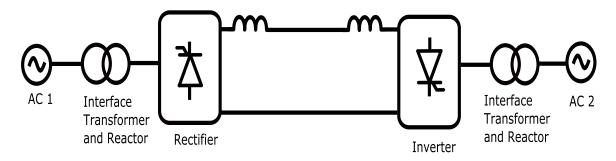

| 1.5 | VSC-HVDC transmission system                       | . 6  |

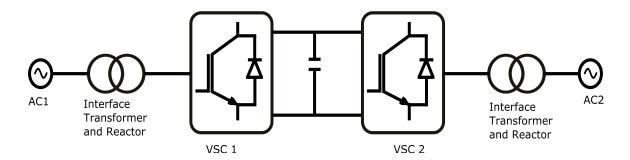

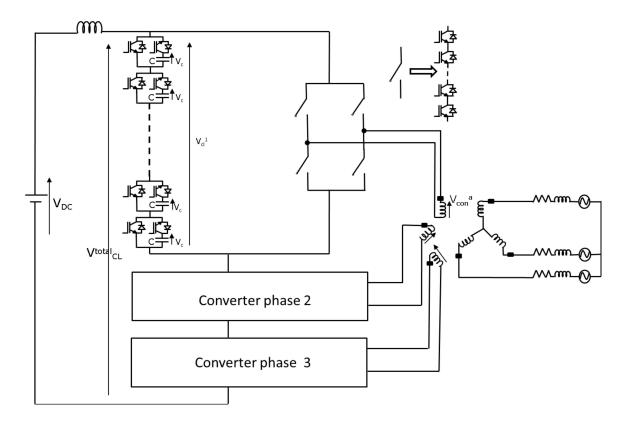

| 1.6 | Three phase parallel hybrid modular multilevel VSC | . 8  |

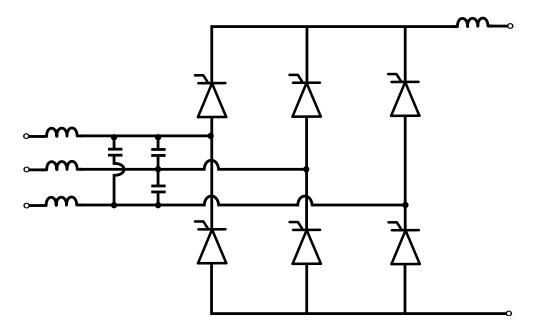

| 2.1 | Six-pulse current source converter                 | . 16 |

| 2.2 | A monopolar link HVDC transmission system          | . 20 |

| 2.3 | A bipolar link HVDC transmission system            | . 20 |

| 2.4 | A Back-to-Back HVDC system                         | . 21 |

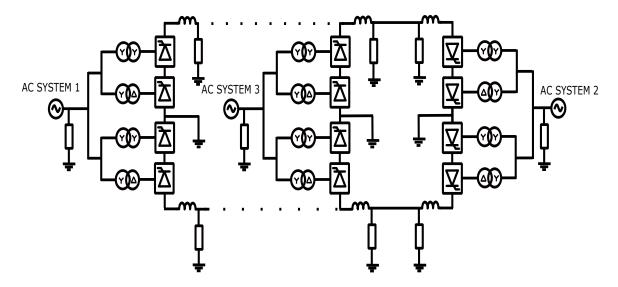

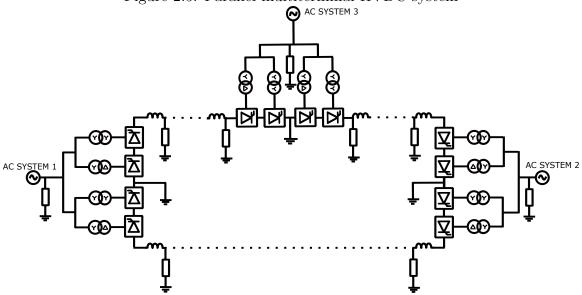

| 2.5 | Parallel multiterminal HVDC system                 | . 22 |

| 2.6 | Series multiterminal HVDC system                   | . 22 |

LIST OF FIGURES x

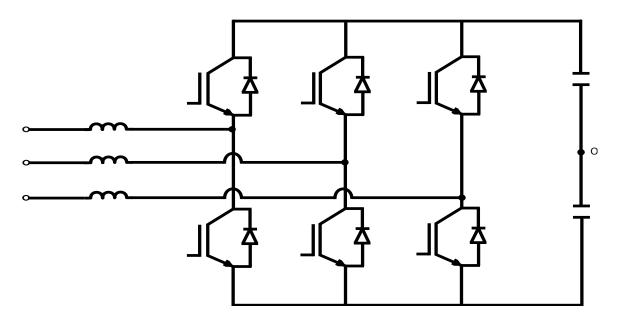

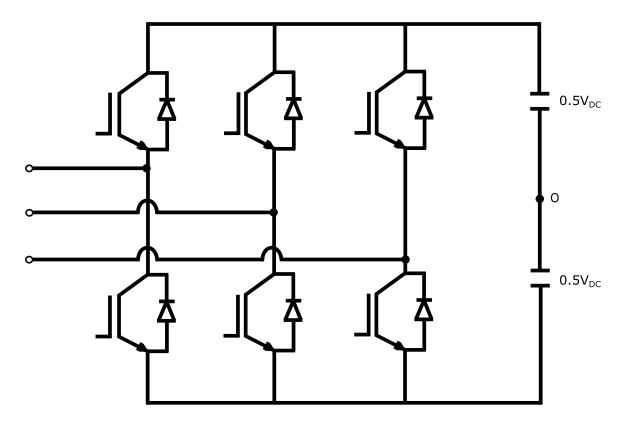

| 2.7  | Two-level VSC                                                                                                         | 26 |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

| 2.8  | Three-level NPC VSC                                                                                                   | 26 |

| 2.9  | Two level VSC terminal voltages: a) Phase-neutral voltage, b) Phase-phase voltage                                     | 27 |

| 2.10 | NPC terminal voltages: a) Phase-neutral voltage, b) Phase-phase voltage                                               | 28 |

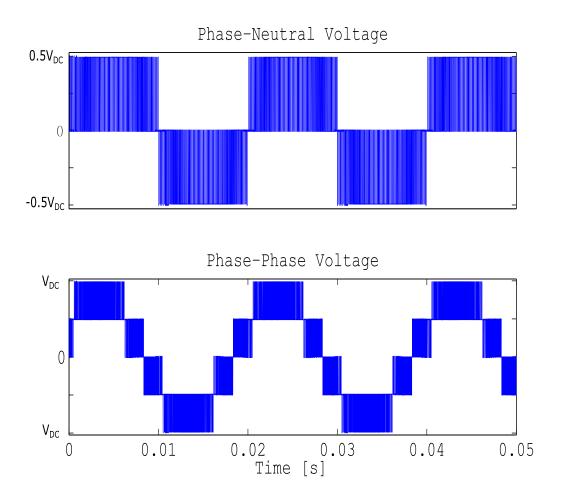

| 2.11 | A modular multilevel VSC                                                                                              | 29 |

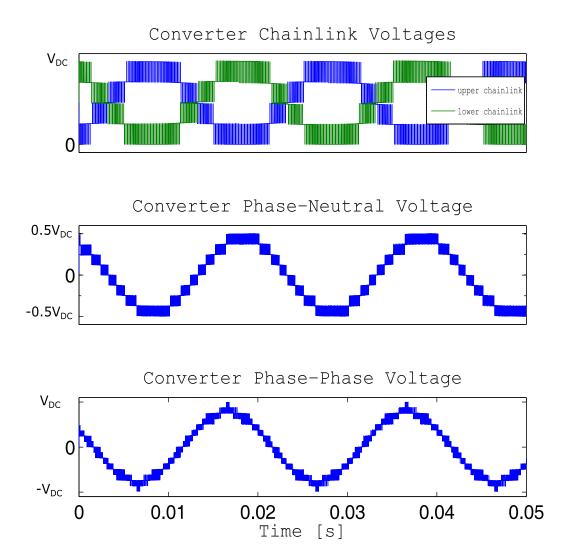

| 2.12 | M2LC terminal voltages a) Chainlink voltages, b) Converter phase-neutral voltage, and c)Converter phase-phase voltage | 30 |

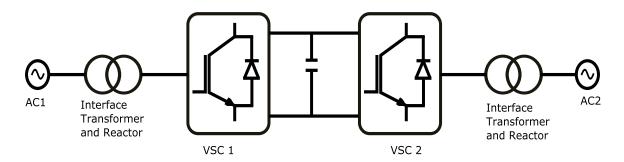

| 3.1  | Schematic of a typical VSC-HVDC system                                                                                | 36 |

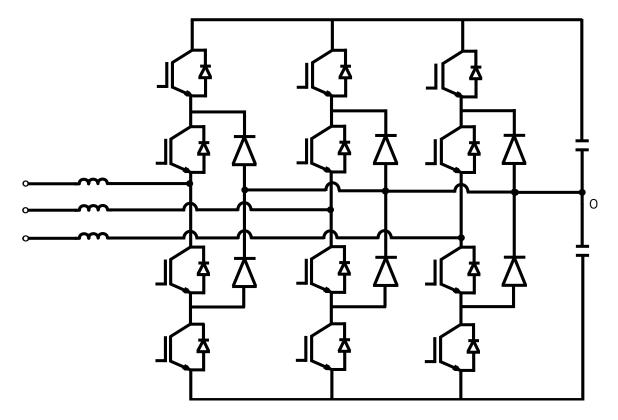

| 3.2  | Two level VSC                                                                                                         | 37 |

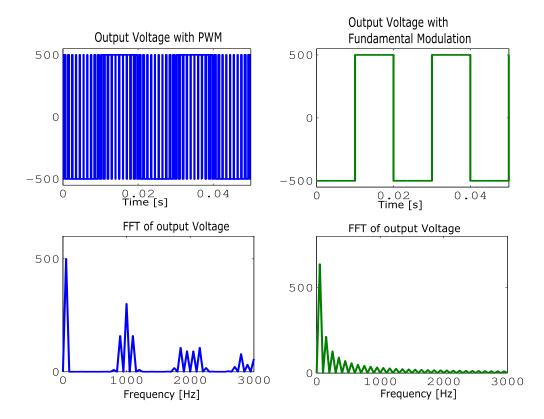

| 3.3  | Converter output voltages from the two-level converter                                                                | 38 |

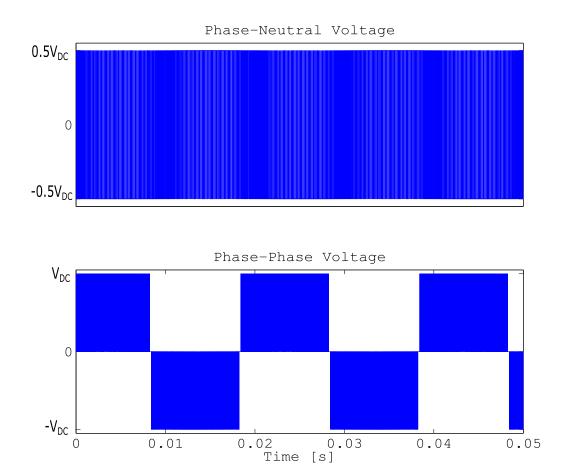

| 3.4  | Three phase three-level NPC                                                                                           | 39 |

| 3.5  | Three phase three-level flying capacitor converter                                                                    | 40 |

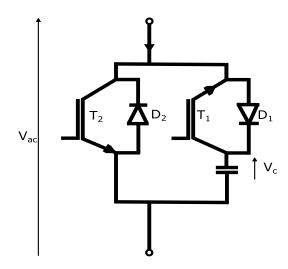

| 3.6  | A half bridge converter cell structure                                                                                | 41 |

| 3.7  | A full bridge converter cell structure                                                                                | 41 |

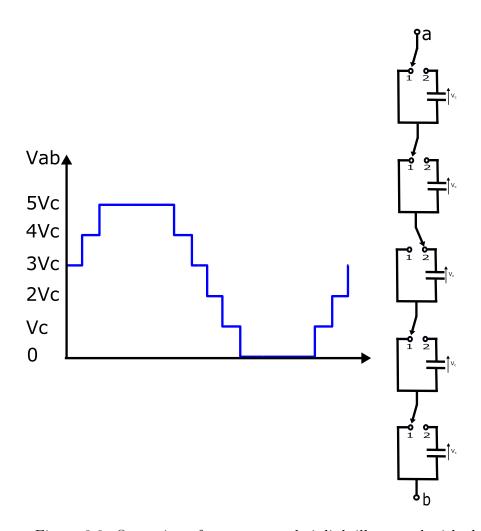

| 3.8  | Operation of a converter chainlink illustrated with the half bridge cell                                              | 42 |

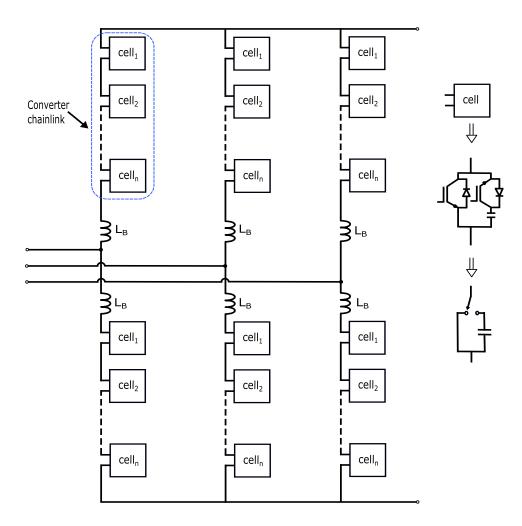

| 3.9  | Three phase double star modular multilevel VSC                                                                        | 43 |

| 3.10 | Phase circuit of the double star modular multilevel VSC                                                               | 45 |

| 5.11 | modular multilevel VSC                                                                                                                               | 45 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

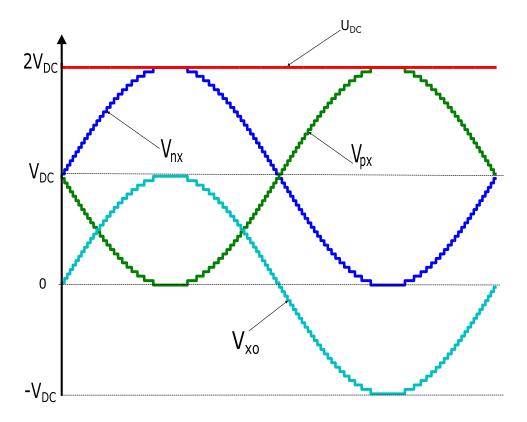

| 3.12 | The concept of voltage synthesis in the double star modular multilevel VSC                                                                           | 47 |

| 3.13 | Three phase series hybrid modular multilevel VSC                                                                                                     | 48 |

| 3.14 | Phase circuit of the SH-M2L-VSC                                                                                                                      | 50 |

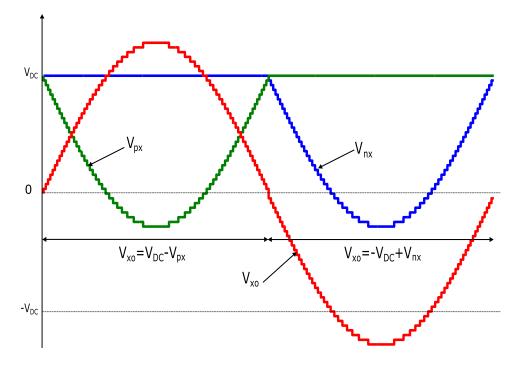

| 3.15 | Voltage synthesises in the SH-M2L-VSC                                                                                                                | 50 |

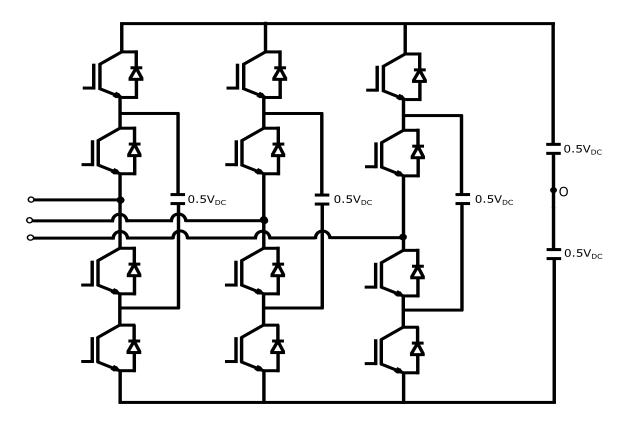

| 3.16 | Three phase circuit arrangement of the alternate SH-M2L-VSC                                                                                          | 51 |

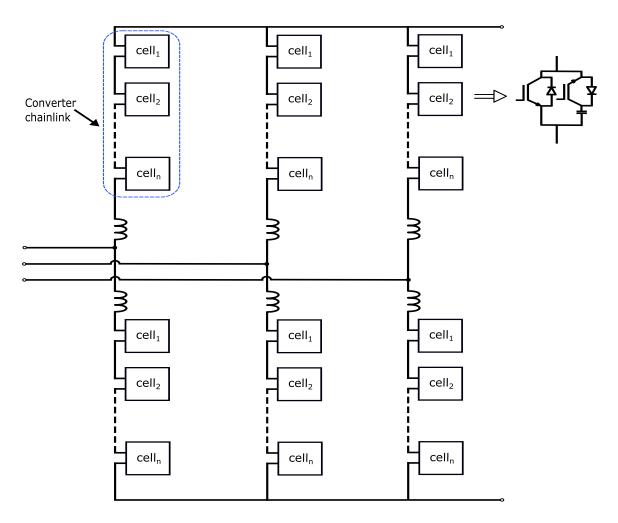

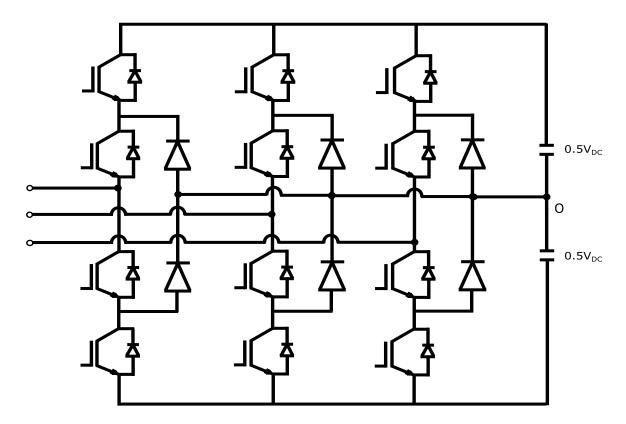

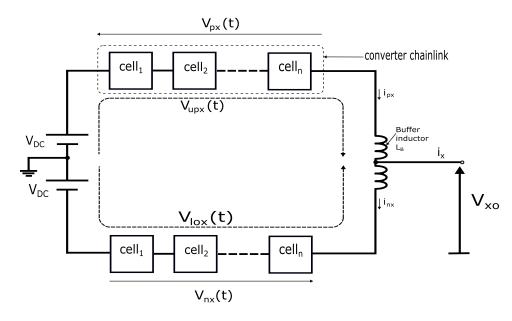

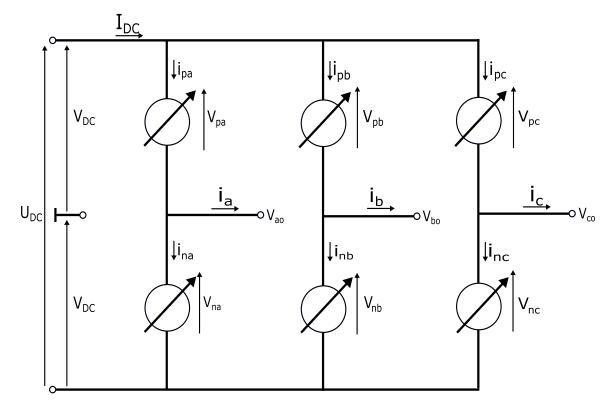

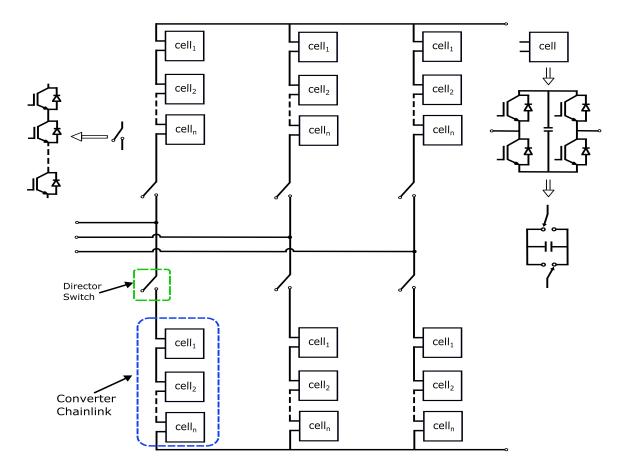

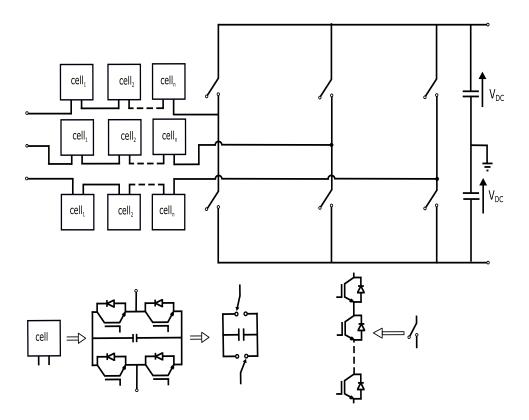

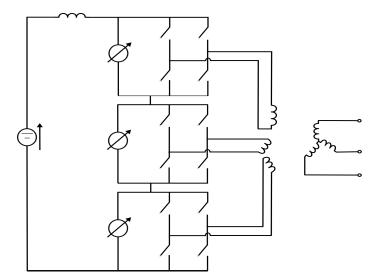

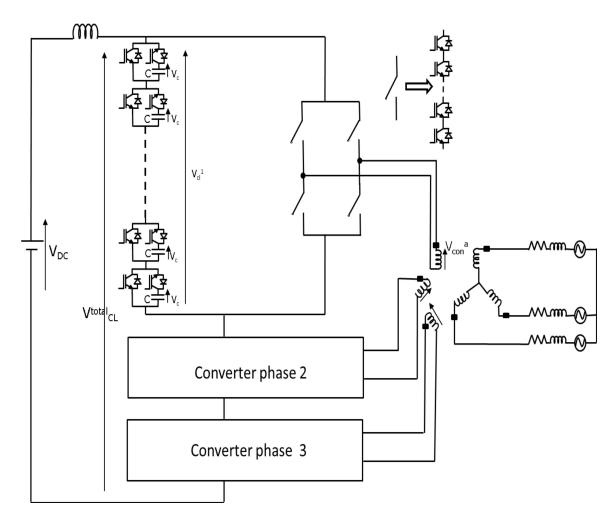

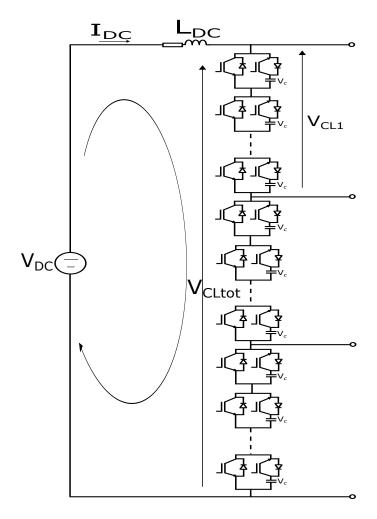

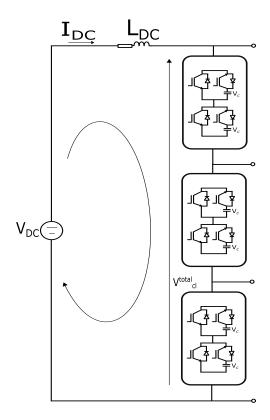

| 3.17 | A three phase arrangement of the PH-M2L-VSC                                                                                                          | 53 |

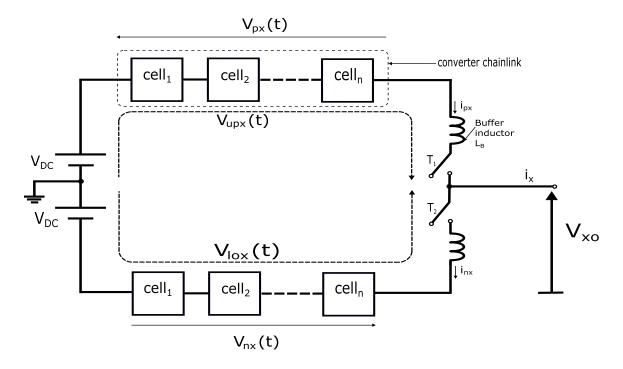

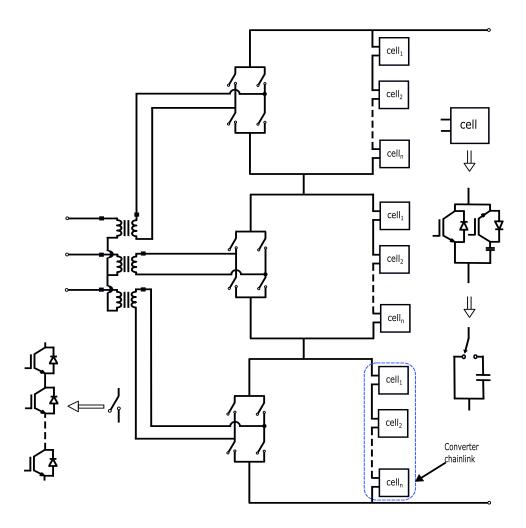

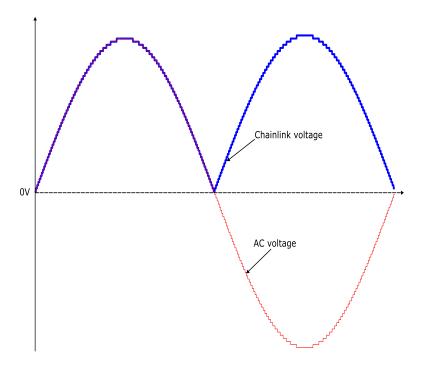

| 3.18 | Voltage synthesis in the PH-M2L-VSC                                                                                                                  | 54 |

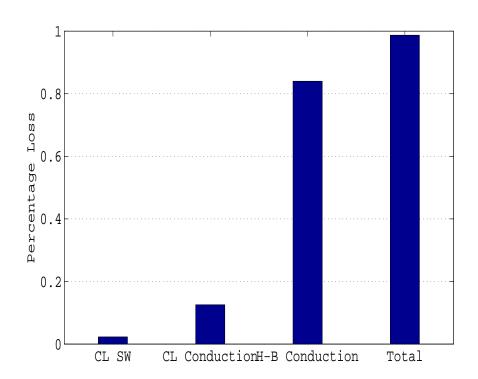

| 3.19 | Semiconductor loss breakdown for the PH-M2L-VSC during 20MW power exchange                                                                           | 56 |

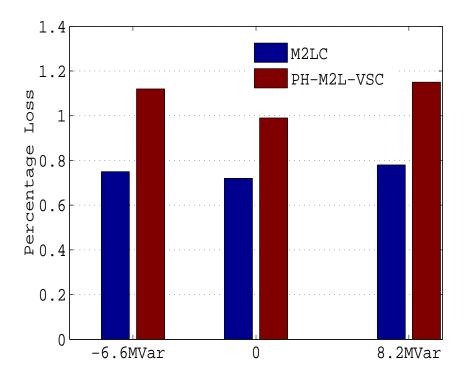

| 3.20 | Comparison of the percentage semiconductor loss in the M2LC and PH-M2L-VSC for a $20 \mathrm{kV}/11 \mathrm{kV}$ AC, $20 \mathrm{MW}$ converter unit | 57 |

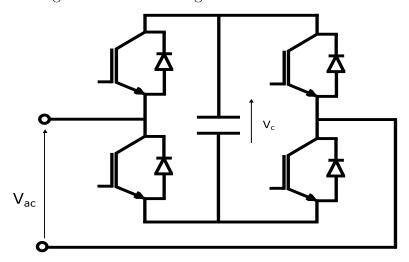

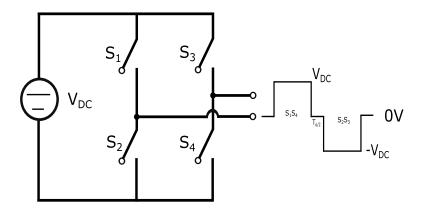

| 4.1  | Three-level voltage generation from an H-bridge using a 'constant' DC source                                                                         | 63 |

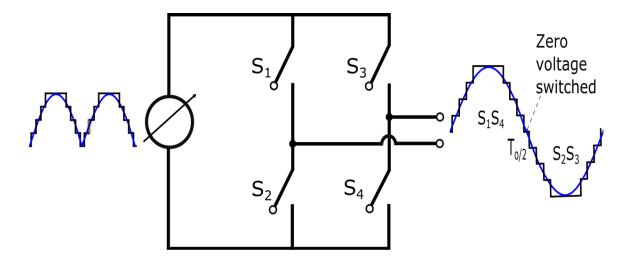

| 4.2  | Concept of multilevel voltage synthesis using an H-bridge arrangement                                                                                | 64 |

| 4.3  | Three phase PH-M2L-VSC arrangement                                                                                                                   | 64 |

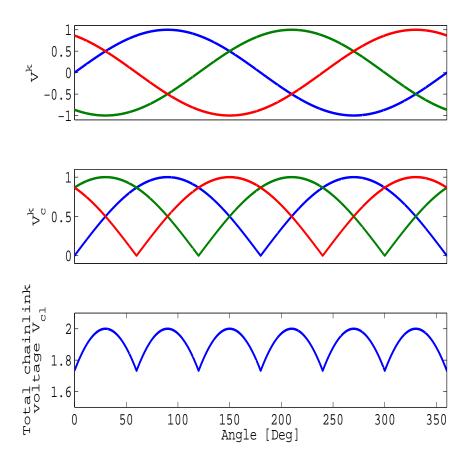

| 4.4  | Converter target voltage waveforms                                                                                                                   | 66 |

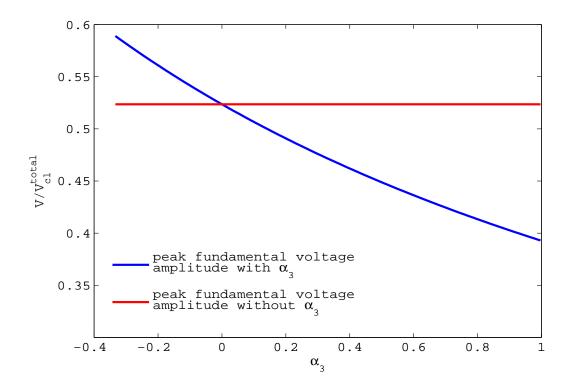

| 4.5  | Variation of fundamental voltage amplitude with third harmonic voltage $(\alpha_3)$ injection                                                        | 67 |

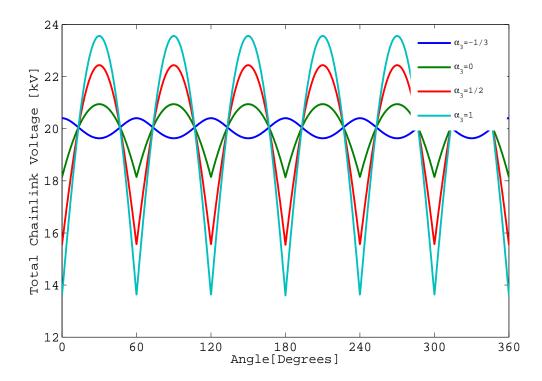

| 4.6  | Effect of third harmonic voltage ( $\alpha_3$ ) injection on total chainlink voltage illustrated with a 20kV/11kV system | 68       |

|------|--------------------------------------------------------------------------------------------------------------------------|----------|

| 4.7  | Detailed 20kV three phase PH-M2L-VSC system                                                                              | 70       |

| 4.8  | DC circuit analysis                                                                                                      | 74       |

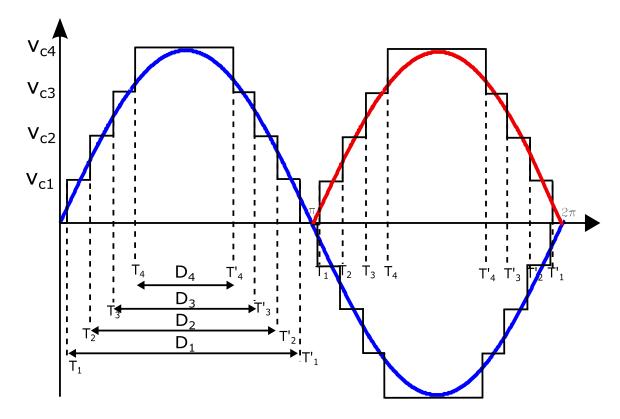

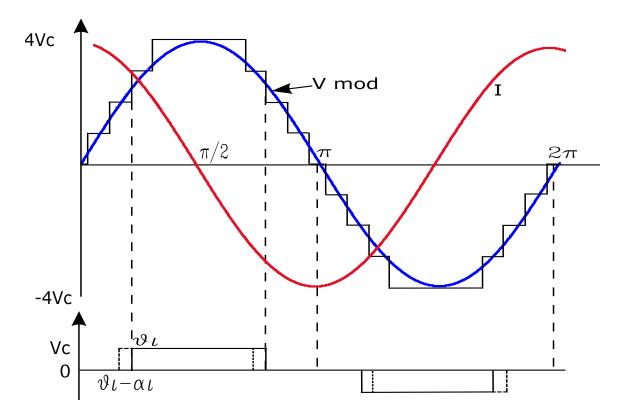

| 4.9  | Direct staggered modulation illustrated with a four cell chainlink converter                                             | 76       |

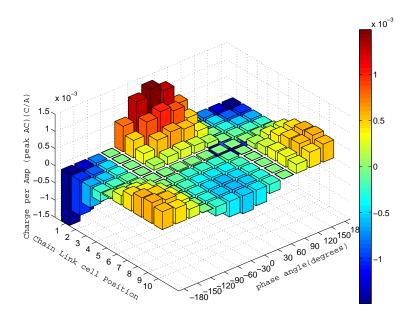

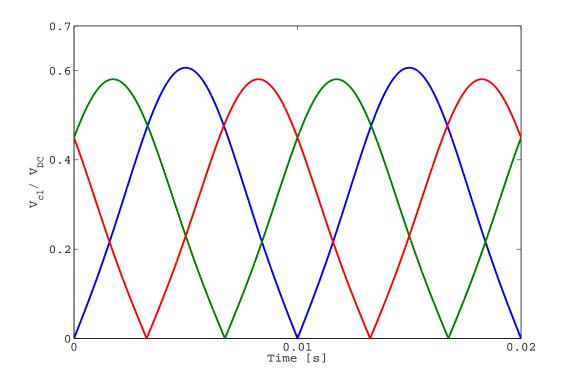

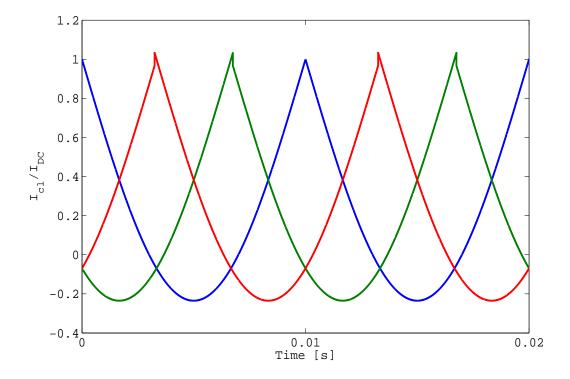

| 4.10 | Converter chainlink cell capacitor charge-discharge characteristics for a 10-cell chainlink converter                    | 77       |

| 4.11 | Cyclic pulse pattern control scheme applied to 9-level cascaded H-bridge converter                                       | 79       |

| 4.12 | Edge movement pulse pattern control applied to Static Var Generator                                                      | 80       |

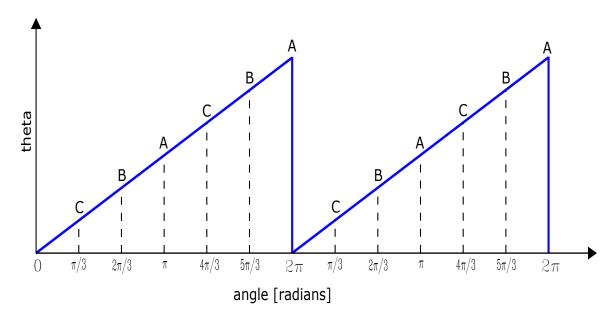

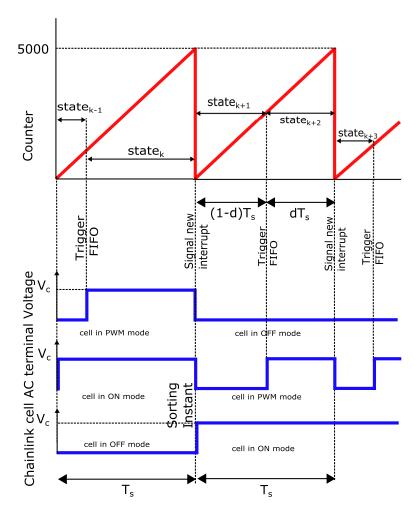

| 4.13 | Sorting instants for chainlink cell voltages                                                                             | 83       |

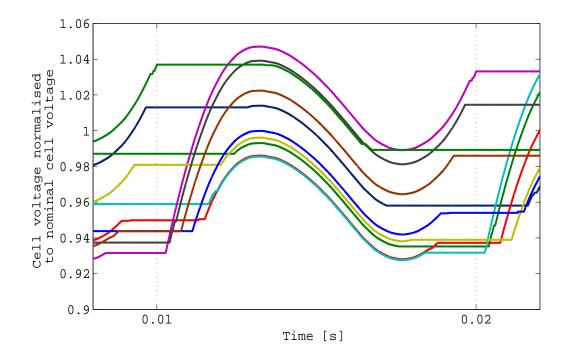

| 4.14 | Capacitor voltage variation when converter inverts into an RL load<br>(R=579 L=35mH, nominal cell voltage=30V)           | 2,<br>84 |

| 4.15 | A cascade PI control system for chainlink voltage control                                                                | 86       |

| 4.16 | Single line diagram of the PH-M2L-VSC connected to the grid                                                              | 89       |

| 4.17 | Voltage space vector in the abc reference frame                                                                          | 90       |

| 4.18 | Voltage space vector in the $\alpha\beta$ reference frame                                                                | 91       |

| 4.19 | Schematic of a three-phase converter connected to the grid                                                               | 93       |

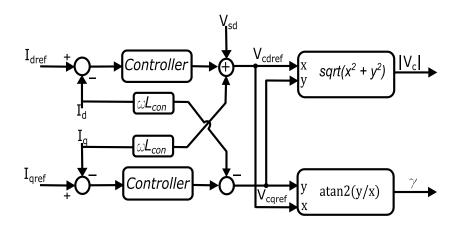

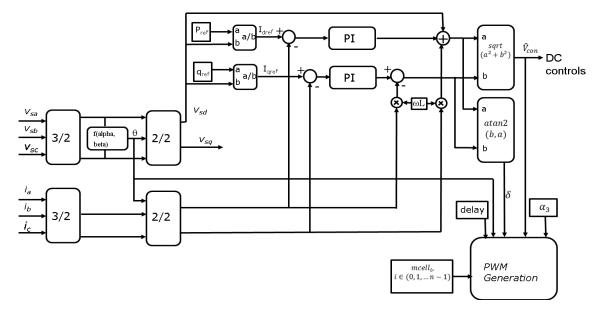

| 4.20 | Vector current control scheme                                                                                            | 95       |

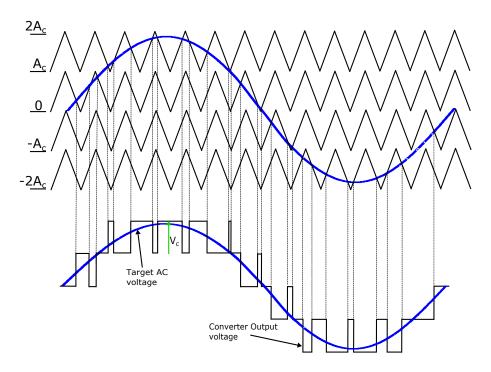

| 4.21 | Standard IPD level-shifted PWM for AC voltage control of a multilevel converter                                                                     | 97  |

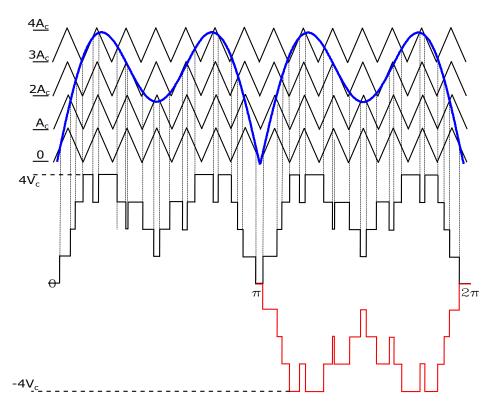

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.22 | IPD level-shifted PWM as applied to PH-M2LC-VSC modulation with third harmonic injection                                                            | 97  |

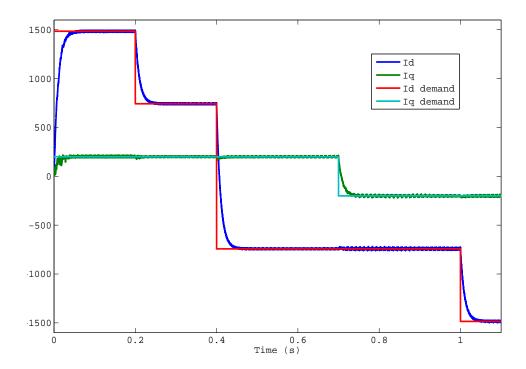

| 4.23 | Converter DC side currents for converter operation through the conditions in Table 4.6                                                              | 99  |

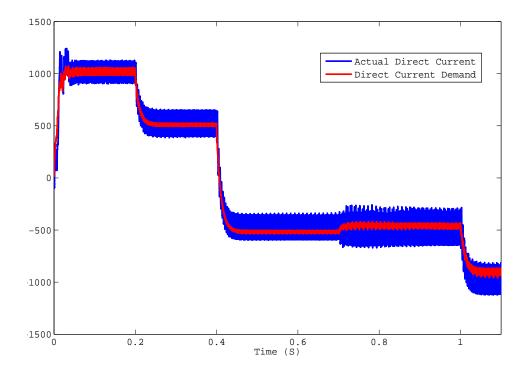

| 4.24 | d-axis and q-axis current components in the dq reference frame for converter operation through the conditions in Table 4.6                          | 100 |

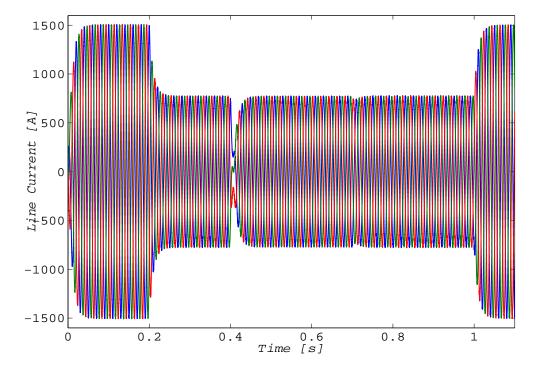

| 4.25 | Line currents in the abc frame at the PCC for converter operation through the conditions in Table 4.6                                               | 100 |

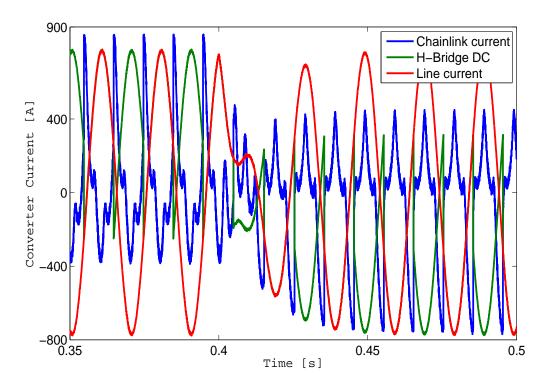

| 4.26 | Converter chainlink current and 'main' bridge DC side current during a transition from 10MW,4MVar to -10MW,4MVar                                    | 101 |

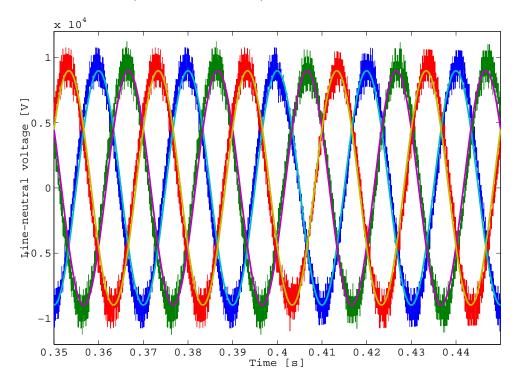

| 4.27 | Converter and grid line-neutral voltages during a transition from 10MW , 4MVar to -10MW, 4MVar                                                      | 101 |

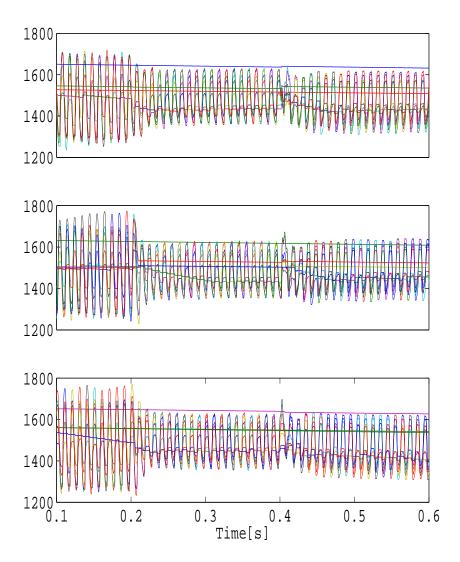

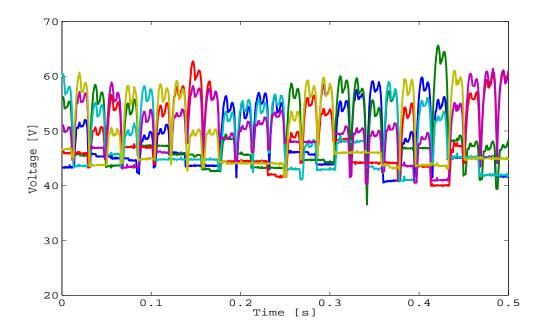

| 4.28 | Converter chainlink cell voltages during power profile traversal from 20MW, 4MVar before 0.2s to 10MW, 4MVar after 0.2s and -10MW, 4MVar after 0.4s | 102 |

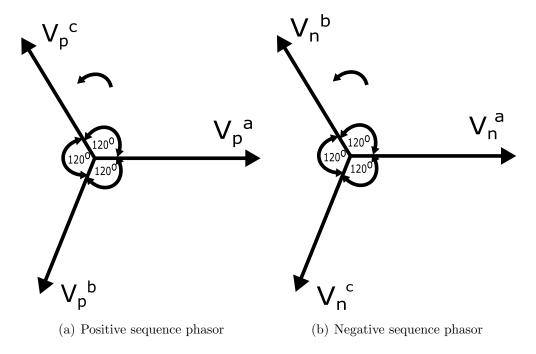

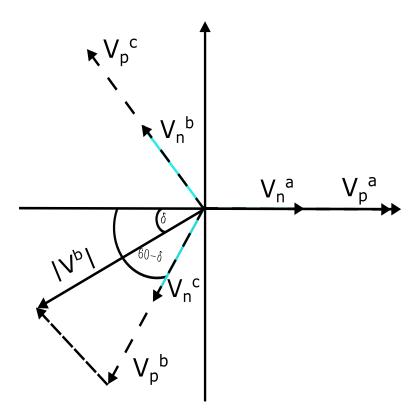

| 5.1  | Phasor representation of positive and negative sequence quantities                                                                                  | 107 |

| 5.2  | Converter chainlink voltages with 3% voltage unbalance                                                                                              | 109 |

| 5.3  | Converter chainlink current with 3% voltage unbalance                                                                                               | 109 |

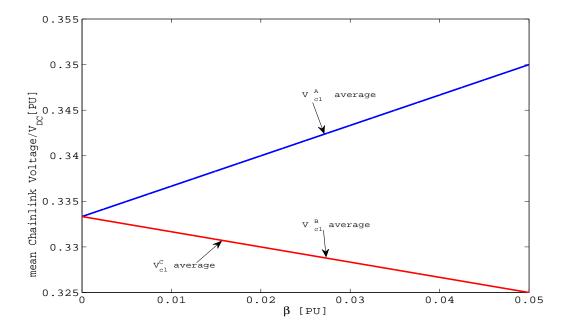

| 5.4  | Mean converter chainlink voltage with increasing voltage unbalance factor $(\beta)$                                                                 | 110 |

LIST OF FIGURES xiv

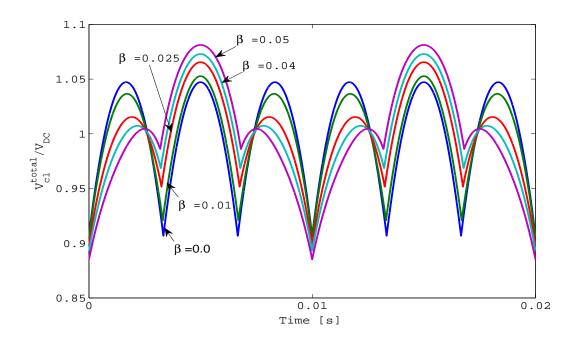

| 5.5  | Instantaneous total chainlink voltage $(V_{cl}^{total})$ with increasing voltage unbalance factor $(\beta)$                                                                                       | 111  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

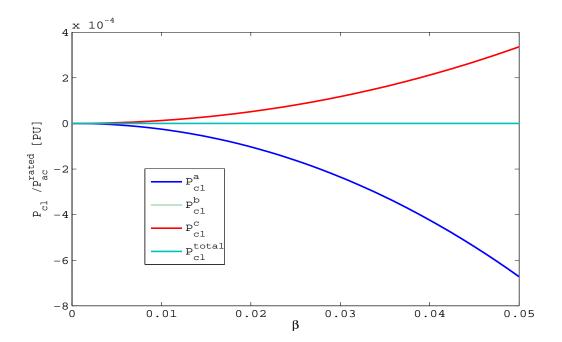

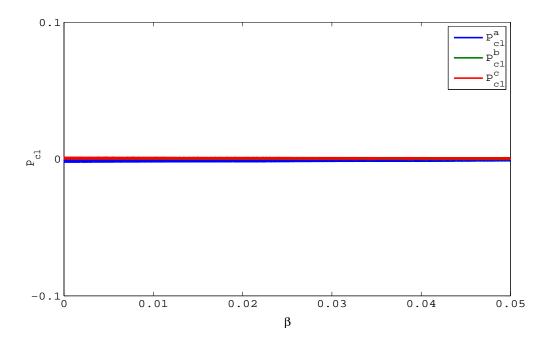

| 5.6  | Change in active power in each converter chainlink for increasing voltage unbalance factor ( $\beta$ ) at unity PF operation for a 20MW/20kV (DC), 11kV (AC) system                               | 112  |

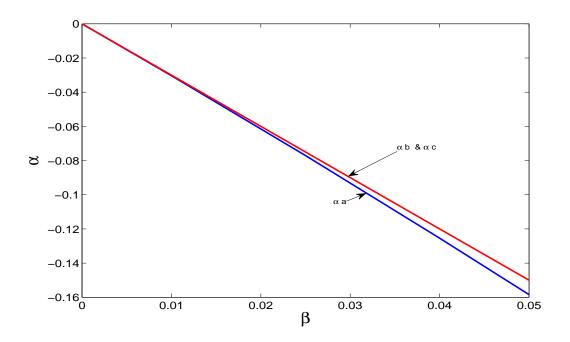

| 5.7  | Amount of third harmonic voltage injected ( $\alpha$ [PU]) for increasing voltage unbalance factor ( $\beta$ [PU])                                                                                | 118  |

| 5.8  | Active power exchange between the converter chainlinks and the AC grid with increasing voltage unbalance factor $(\beta)$ when the converter operates with the proposed voltage unbalance control | 119  |

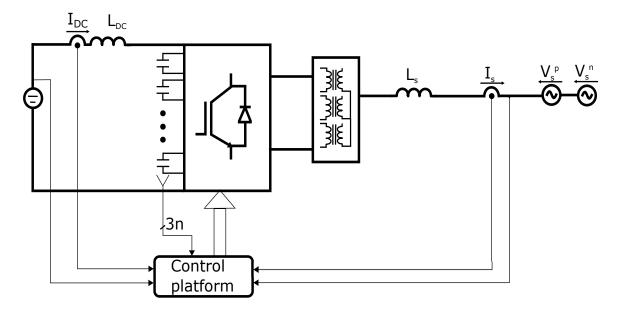

| 5.9  | A PH-M2L-VSC connected to an unbalanced AC network                                                                                                                                                | 120  |

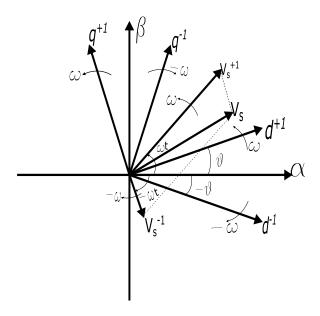

| 5.10 | Voltage vectors in the double synchronous reference frame (DSRF)                                                                                                                                  | 121  |

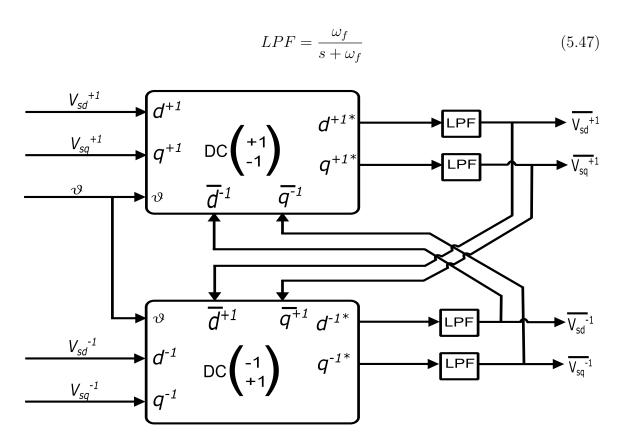

| 5.11 | Structure of the Frame Decoupling Network                                                                                                                                                         | 122  |

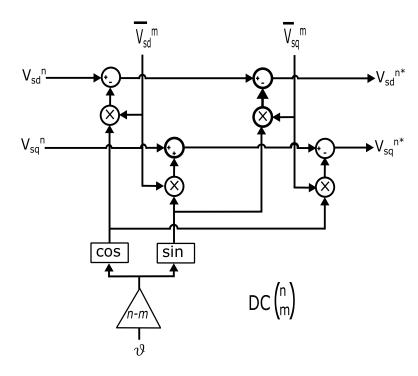

| 5.12 | Decoupling cell for cancelling the effect of $V^m_{sdq}$ on $V^n_{sdq}$                                                                                                                           | 123  |

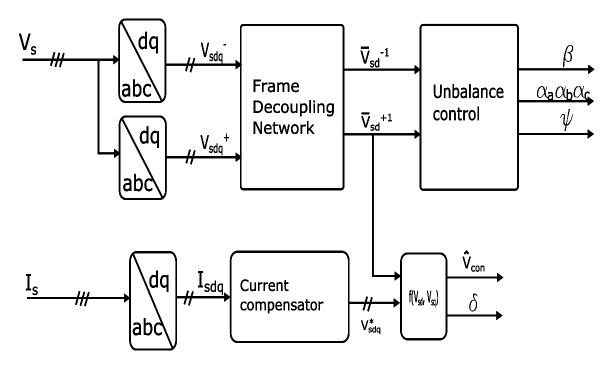

| 5.13 | Decoupled vector current control structure during grid voltage imbalance                                                                                                                          | e123 |

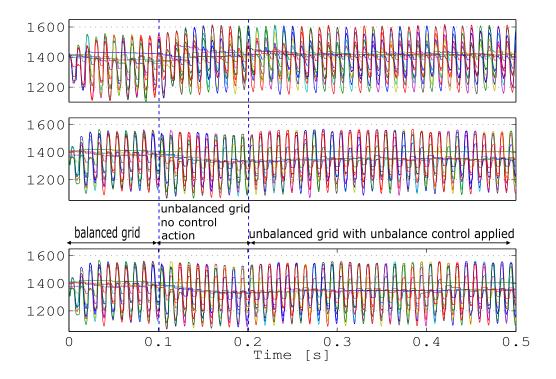

| 5.14 | Converter chainlink cell voltages during converter inversion into an 11kV grid network with 5% voltage unbalance: third harmonic unbalance control is applied at 0.2s                             | 124  |

| 5.15 | $20\mathrm{MW}/20\mathrm{kV}$ System performance during grid voltage unbalance contro                                                                                                             | 1125 |

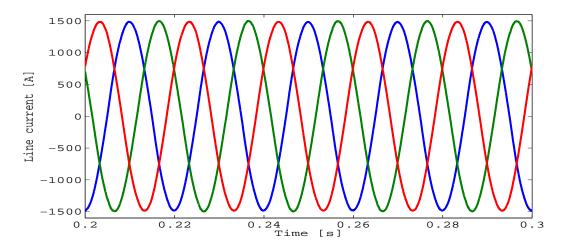

| 5.16 | Third harmonic current on grid side during unbalance control                                                                                                                                      | 126  |

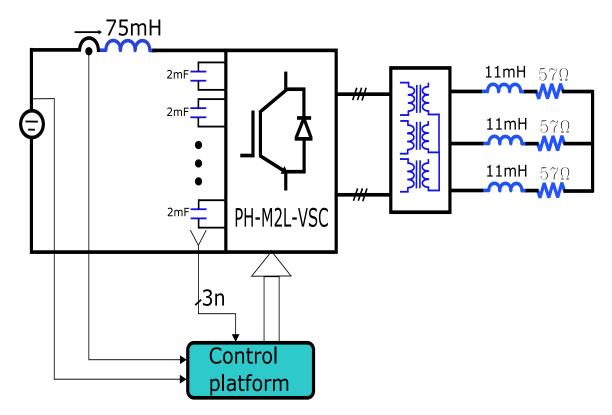

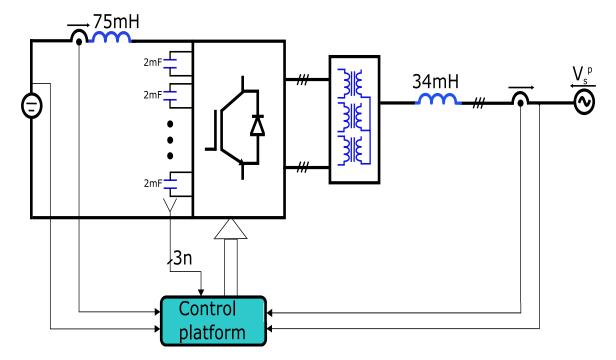

| 6.1  | A 6-cell chainlink three phase PH-M2L-VSC                                                                                                                                                         | 129  |

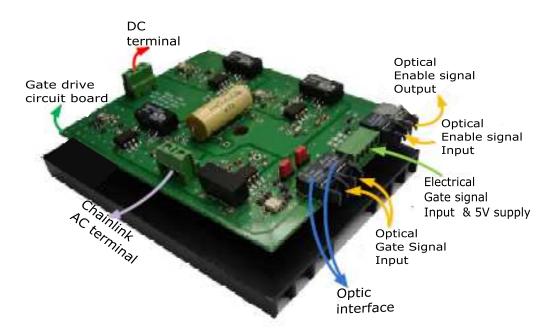

| 6.2  | A picture of the H-bridge converter                                                                                                            | 130  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

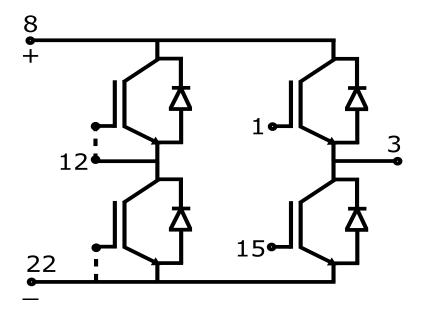

| 6.3  | Schematic of the modified half bridge converter                                                                                                | 131  |

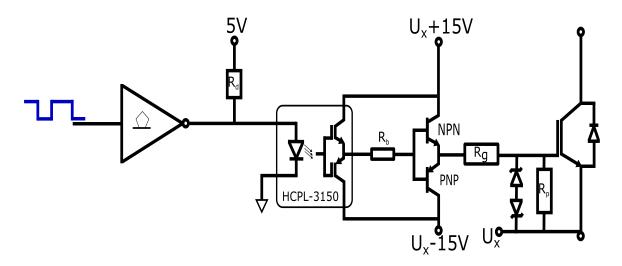

| 6.4  | A picture of the main bridge gate drive                                                                                                        | 132  |

| 6.5  | Schematic of the gate drive circuit                                                                                                            | 132  |

| 6.6  | Layout of the experimental system                                                                                                              | 134  |

| 6.7  | Experimental setup showing the main components                                                                                                 | 135  |

| 6.8  | Converter DC circuit loop                                                                                                                      | 136  |

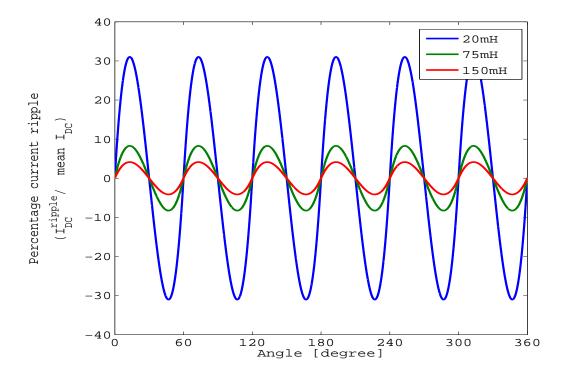

| 6.9  | DC link current ripple for different values of DC link inductor expressed as a percentage of mean DC link current for a 750V (DC), 10kW system | ı138 |

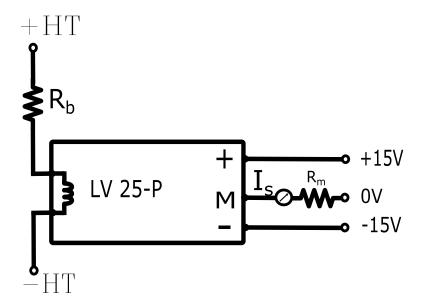

| 6.10 | Connection diagram of the LEM LV 25-P voltage transducer                                                                                       | 140  |

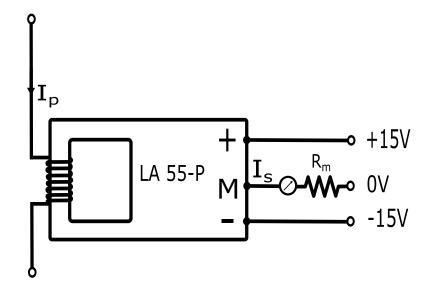

| 6.11 | Connection diagram of the LEM LA 55-P current transducer                                                                                       | 141  |

| 6.12 | Chainlink cell pre-charge control circuit                                                                                                      | 142  |

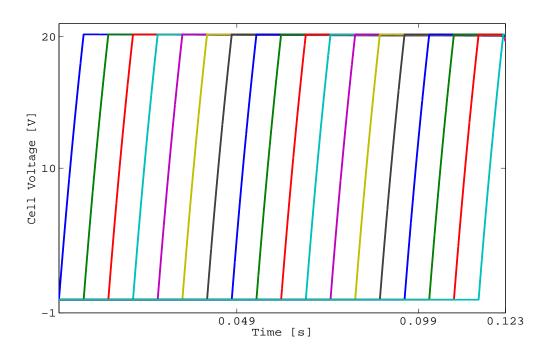

| 6.13 | Simulation results of pre-charge circuit                                                                                                       | 143  |

| 6.14 | AC contactor control circuit                                                                                                                   | 145  |

| 6.15 | A picture of the digital control unit                                                                                                          | 146  |

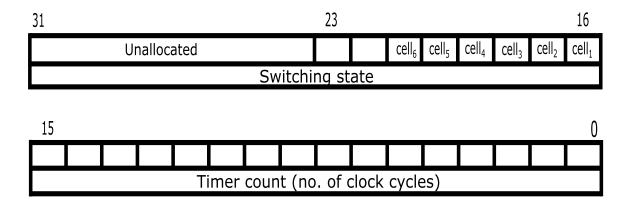

| 6.16 | Memory register used for holding the switching vectors                                                                                         | 148  |

| 6.17 | PWM signal generation using two switching vectors                                                                                              | 149  |

| 6.18 | A picture of an FPGA board                                                                                                                     | 150  |

| 6.19 | Vector control structure as implemented in DSP                                                                                                 | 151  |

| 6.20 | A flow diagram illustrating the sequence of execution of the control software                                                                      | 152  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 7.1  | Schematic of test circuit for converter operation without modulation ratio control                                                                 | 156  |

| 7.2  | Experimental result for converter terminal voltage (phase) when the converter inverts into an RL load at 0.998 PF without modulation ratio control | 157  |

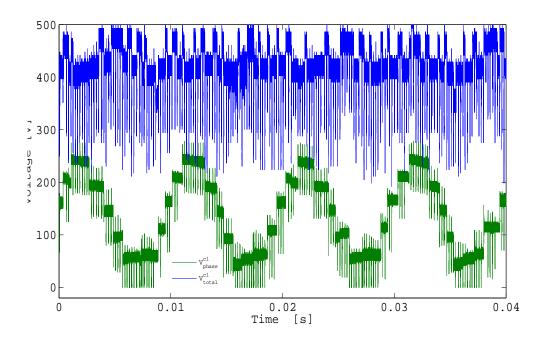

| 7.3  | Experimental result for total chainlink voltage and a converter chain-<br>link voltage when the converter operates without modulation ratio contro | l157 |

| 7.4  | Simulation result for converter terminal voltage (Phase) when inverting into an RL load at 0.998 PF without modulation ratio control               | 159  |

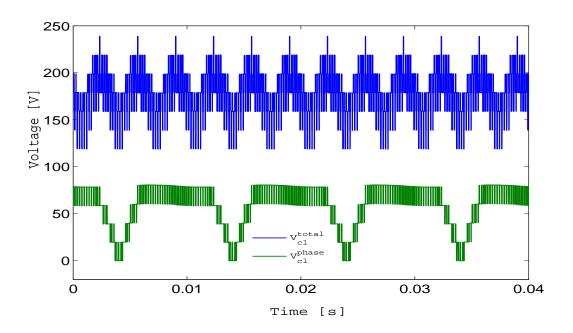

| 7.5  | Simulation result for total chainlink voltage and a converter chainlink voltage when the converter operates without modulation ratio control       | 159  |

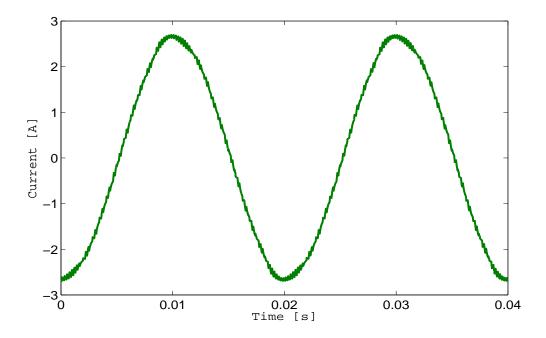

| 7.6  | Experimental result for load current when inverting into an RL load at 0.998 PF without modulation ratio control                                   | 160  |

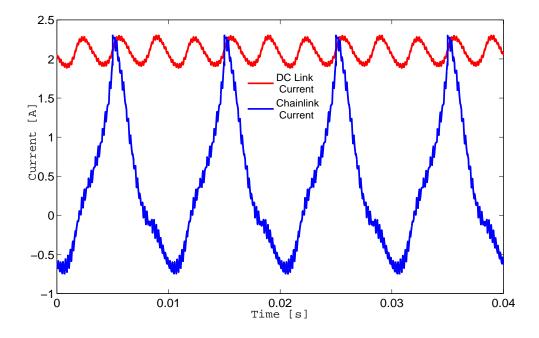

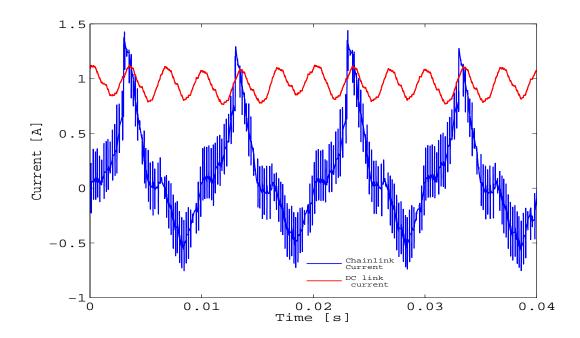

| 7.7  | Experimental result for DC and chainlink currents when inverting into an RL load at 0.998 PF without modulation ratio control                      | 160  |

| 7.8  | Simulation result for load current when inverting into an RL load at 0.998 PF without modulation ratio control                                     | 161  |

| 7.9  | Simulation result for DC and chainlink currents when inverting into an RL load at 0.998 PF without modulation ratio control                        | 161  |

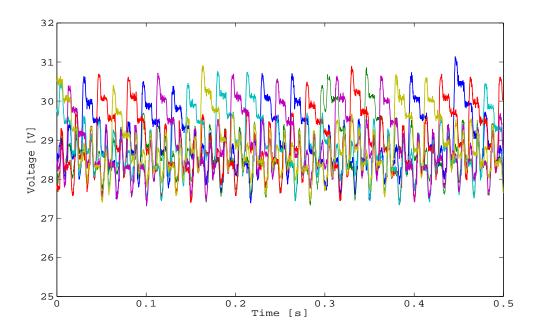

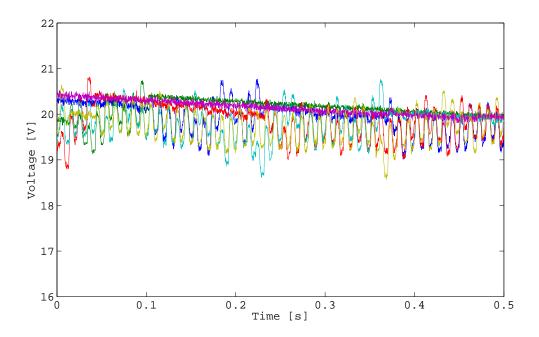

| 7.10 | Experimental result for chainlink cell voltages (Phase A) when inverting into an RL Load at $0.998~\mathrm{PF}$ without modulation ratio control   | 162  |

| 7.11 | Simulation result for chainlink cell voltages (Phase A) when inverting into an RL load at 0.998 PF without modulation ratio control            | 162 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.12 | Schematic of test circuit used for validating modulation ratio control of power converter                                                      | 163 |

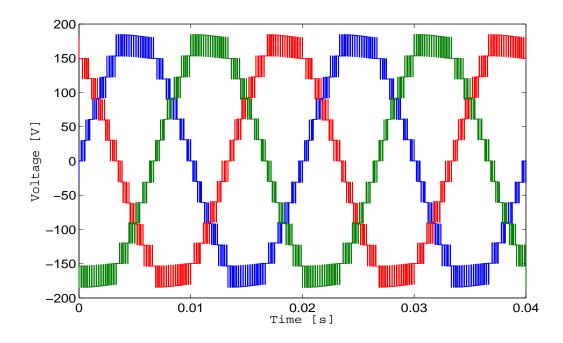

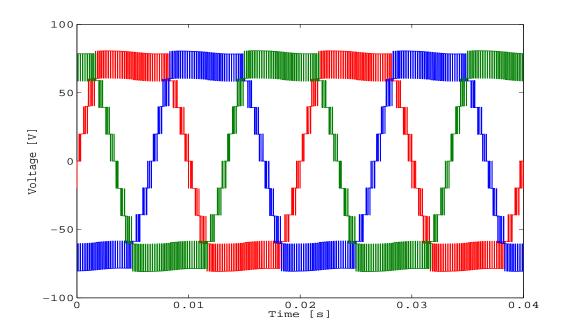

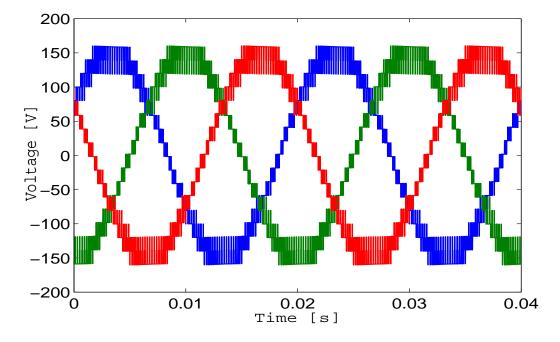

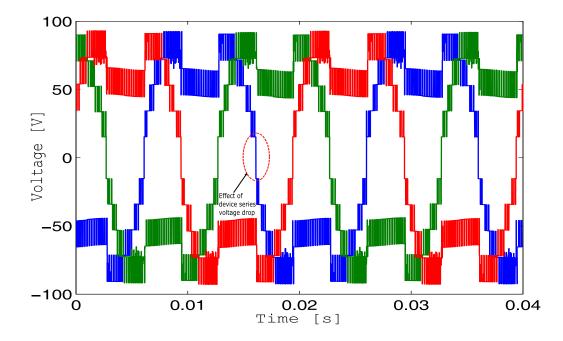

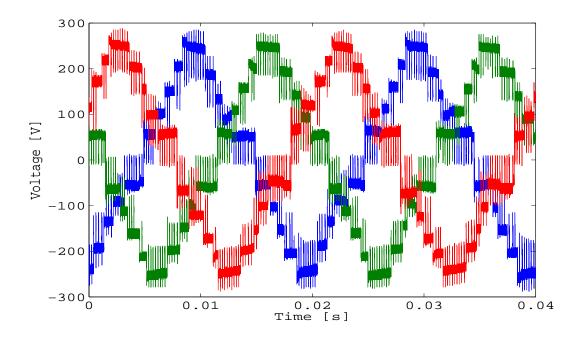

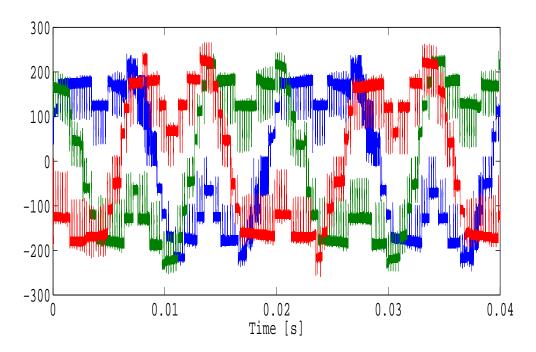

| 7.13 | Experimental results for H-bridge terminal voltages (phase) when inverting into an RL load with modulation ratio control                       | 165 |

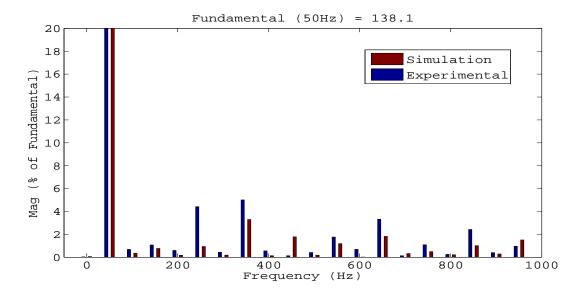

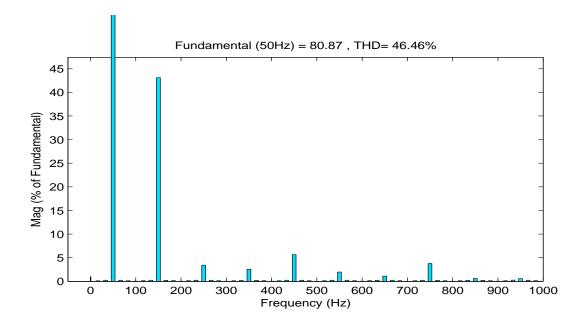

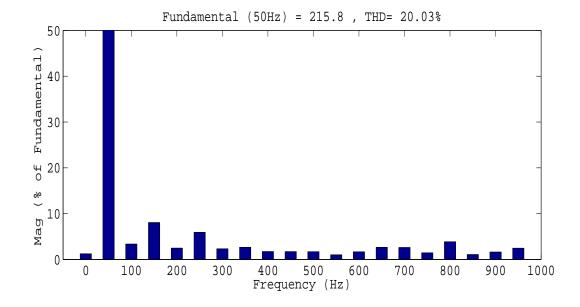

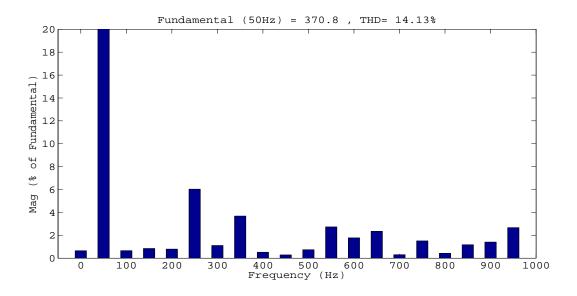

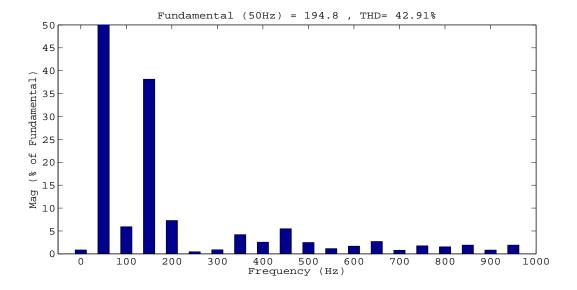

| 7.14 | FFT Spectrum of the corresponding phase voltage when inverting into an RL load with modulation ratio control                                   | 165 |

| 7.15 | Simulation results for H-bridge terminal voltages (phase) when inverting into an RL load with modulation ratio control                         | 166 |

| 7.16 | Simulation results for converter terminal voltage (line-line) when inverting into an RL load with modulation ratio control                     | 166 |

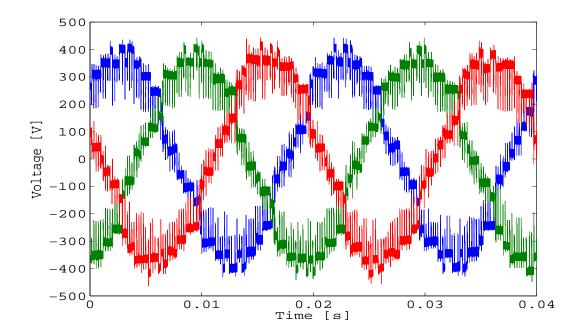

| 7.17 | Experimental results for converter terminal voltage (Line-Line) when inverting into an RL load with modulation ratio control                   | 167 |

| 7.18 | FFT spectrum of the corresponding line-line voltage when inverting into an RL load with modulation ratio control                               | 167 |

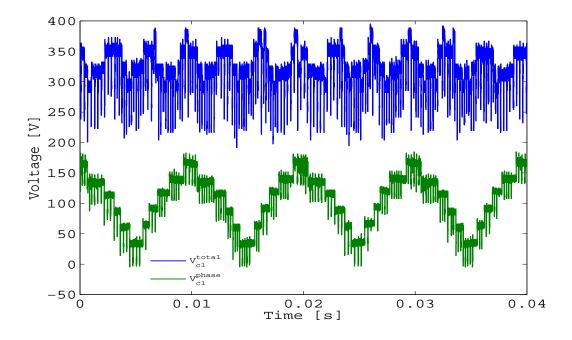

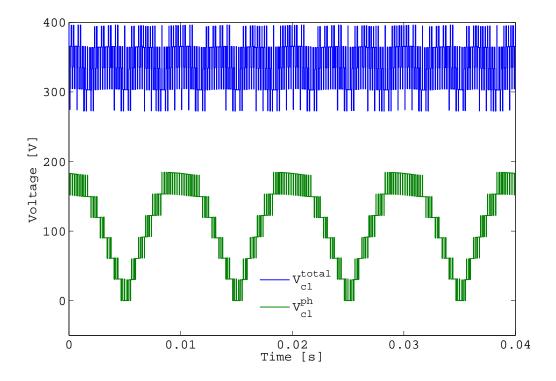

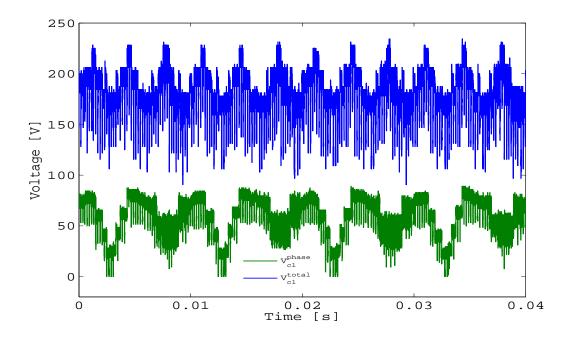

| 7.19 | Experimental result for total chainlink voltage and a converter chainlink voltage when inverting into an RL load with modulation ratio control | 169 |

| 7.20 | Simulation results for total chainlink voltage and a converter chainlink voltage when inverting into an RL load with modulation ratio control  | 169 |

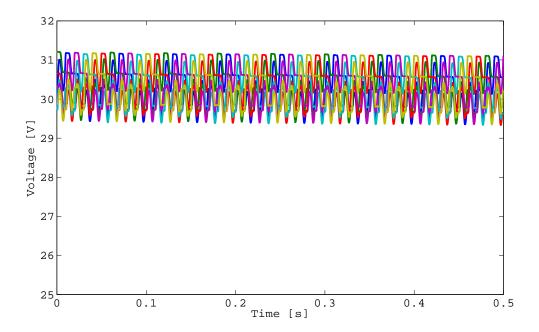

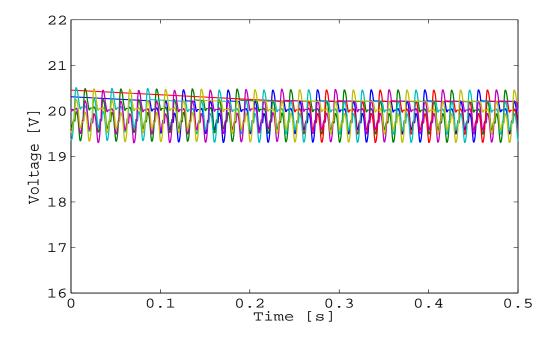

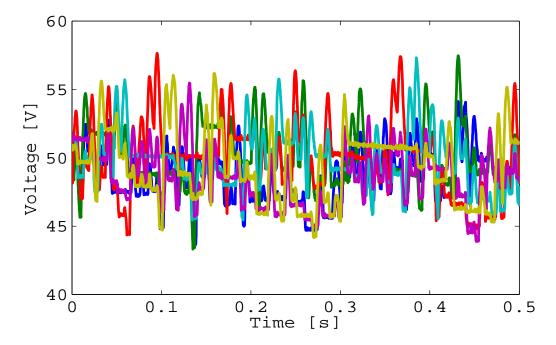

| 7.21 | Experimental result for chainlink cell voltages (phase A) when inverting into an RL load with modulation ratio control                         | 170 |

| 7.22 | Simulation result for chainlink cell voltages (phase A) when inverting into an RL load with modulation ratio control                                     | 170  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

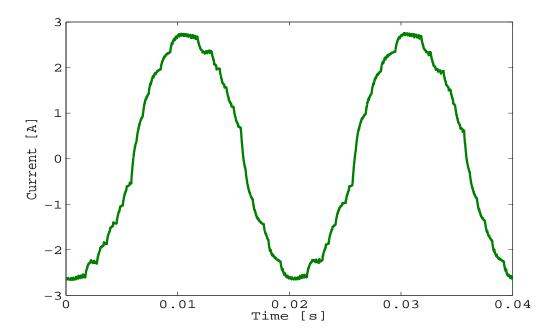

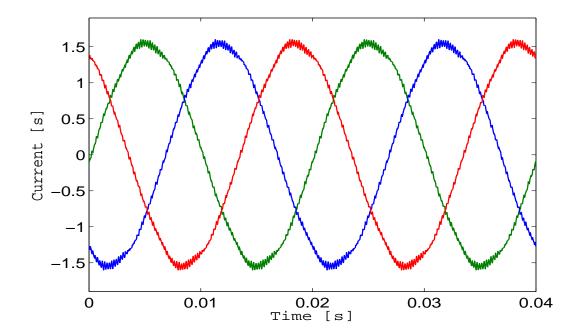

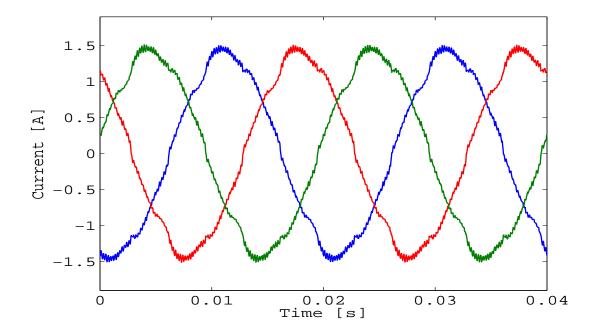

| 7.23 | Experimental result for load currents when inverting into an RL load with modulation ratio control                                                       | 171  |

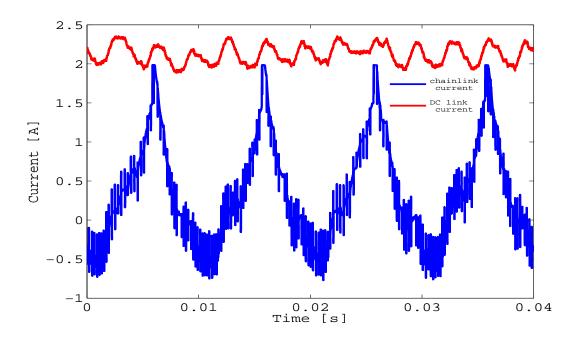

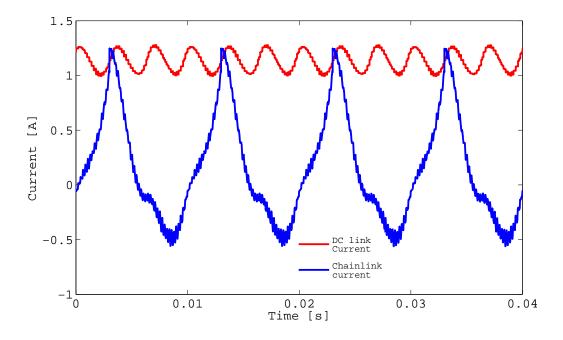

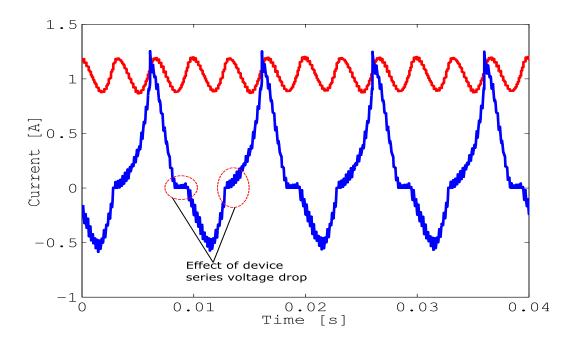

| 7.24 | Experimental result for DC link and converter chainlink currents when inverting into an RL load with modulation ratio control                            | 171  |

| 7.25 | Simulation result for load currents when inverting into an RL load with modulation ratio control                                                         | 172  |

| 7.26 | Simulation result for DC link and converter chainlink currents when inverting into an RL load with modulation ratio control                              | 172  |

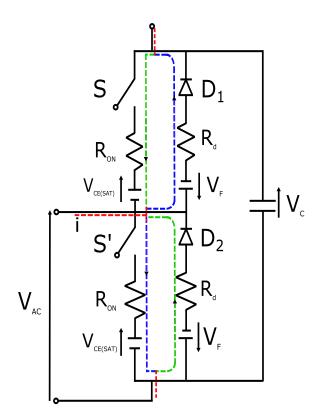

| 7.27 | Half bridge model considering device non-idealities                                                                                                      | 174  |

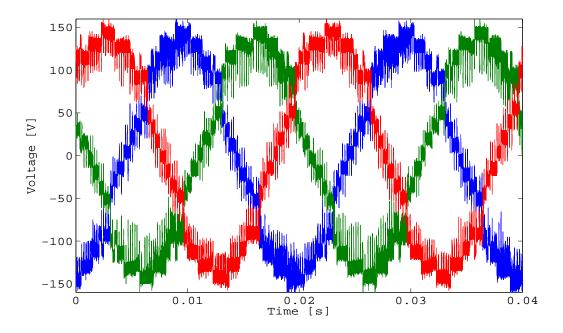

| 7.28 | Simulation results considering the effect of power electronic switch non-idealities on the simulation results presented in Figure 7.15                   | 176  |

| 7.29 | FFT spectrum of converter terminal phase voltages considering effect of device non-idealities                                                            | 177  |

| 7.30 | Simulation results showing the load current when inverting into an RL load considering the effect of the power electronic switch non-idealities          | 177  |

| 7.31 | Simulation results for the DC and chainlink currents when inverting into an RL load considering the effect of the power electronic switch non-idealities | 178  |

| 7.32 | Schematic of the PH-M2L-VSC connected to the grid for test validation                                                                                    | n179 |

LIST OF FIGURES xix

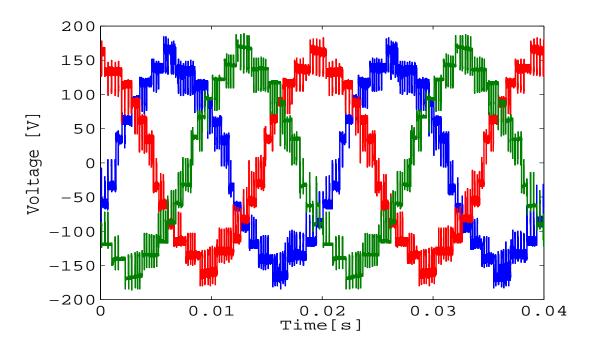

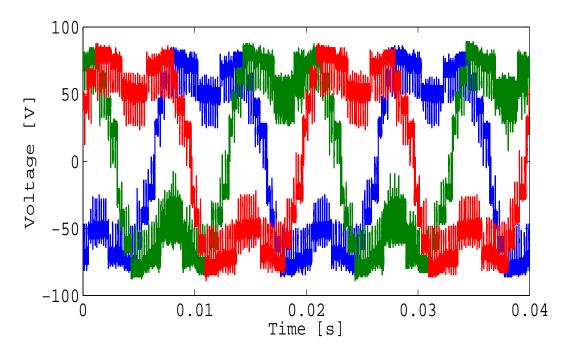

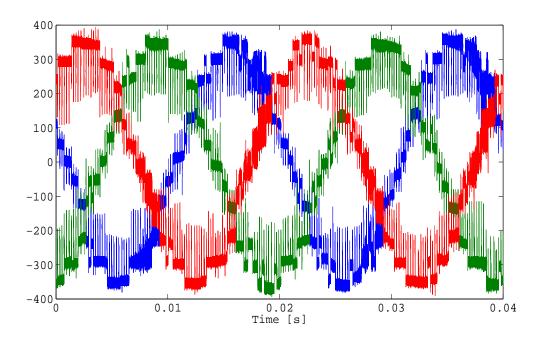

| 7.33 | Experimental result for converter H-bridge terminal voltages when the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | converter with system parameters listed in Table 7.3 is operated as an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|      | inverter (exporting 1.6kW to the grid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 181   |

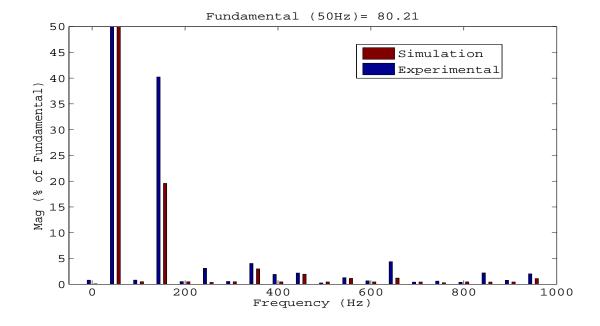

| 7.34 | FFT analysis of experimental result for converter H-bridge terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|      | voltages when the converter with system parameters listed in Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|      | 7.3 is operated as an inverter (exporting 1.6kW to the grid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 181   |

| 7.35 | Experimental result for converter voltages (Line-Line) when the con-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|      | verter with system parameters listed in Table 7.3 is operated as an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|      | inverter (exporting 1.6kW to the grid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 182   |

| 7.36 | FFT analysis of experimental result for converter voltages (Line-Line)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|      | when the converter with system parameters listed in Table 7.3 is op-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|      | erated as an inverter (exporting 1.6kW to the grid) $\ \ldots \ \ldots \ \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 182   |

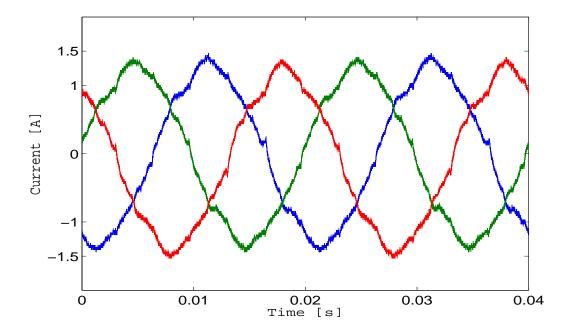

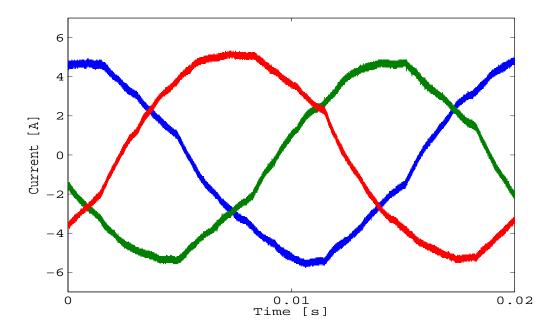

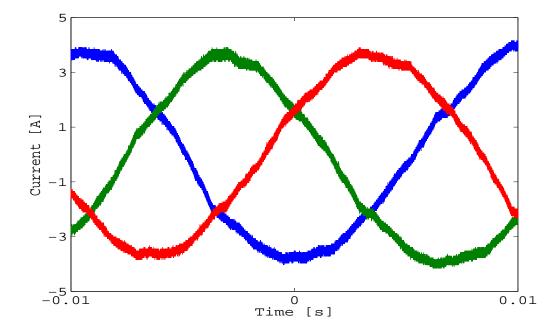

| 7.37 | Experimental result for line currents at the PCC when the converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|      | with system parameters listed in Table 7.3 is operated as an inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|      | (exporting 1.6kW to the grid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 184   |

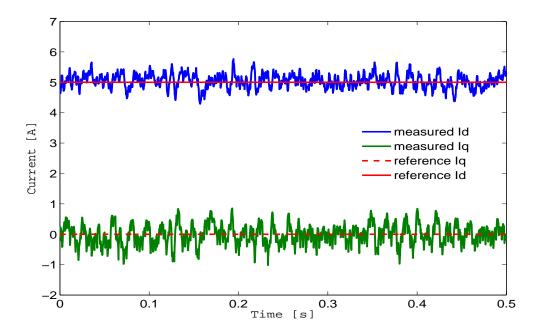

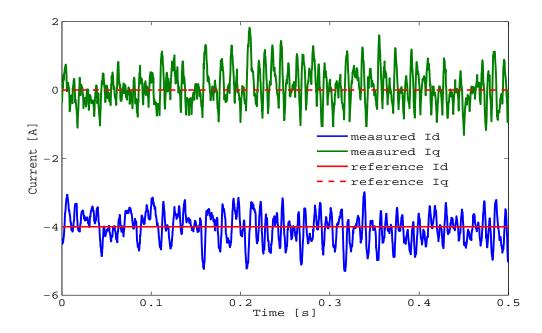

| 7.38 | Experimental result for line currents in the $dq$ reference frame when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|      | the converter with system parameters listed in Table 7.3 is operated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

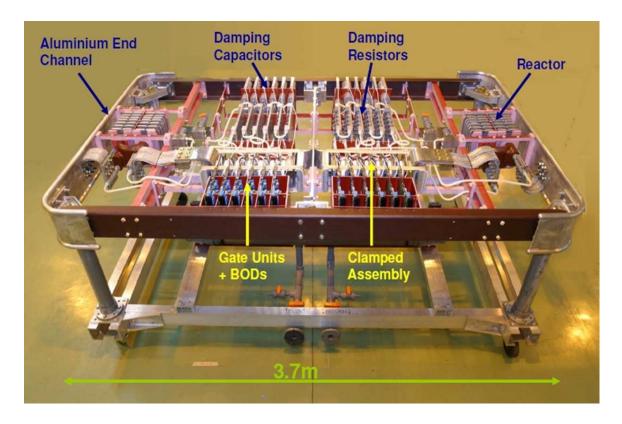

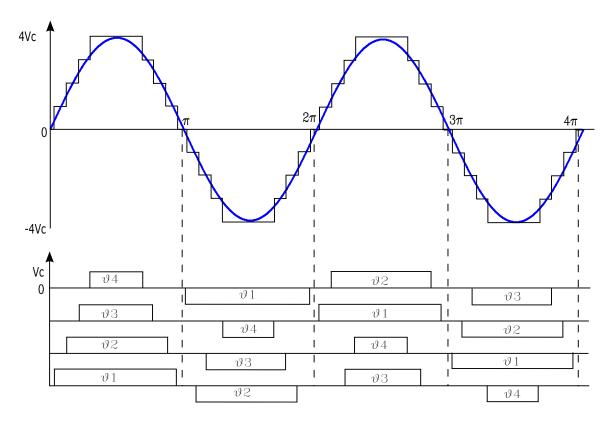

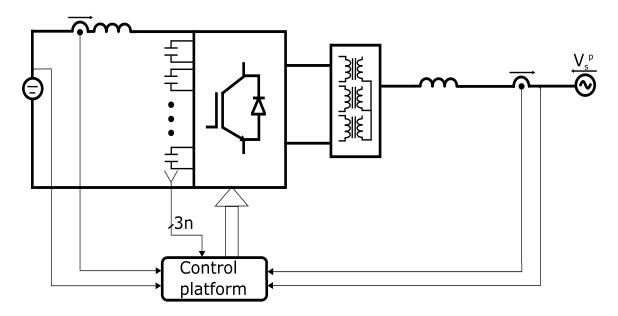

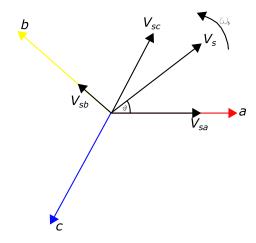

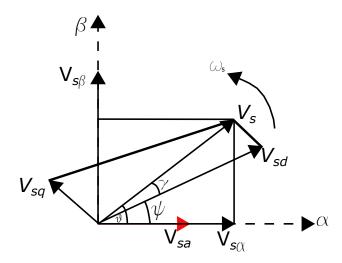

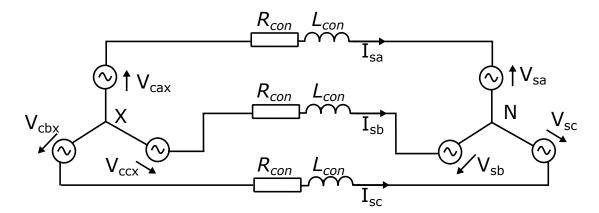

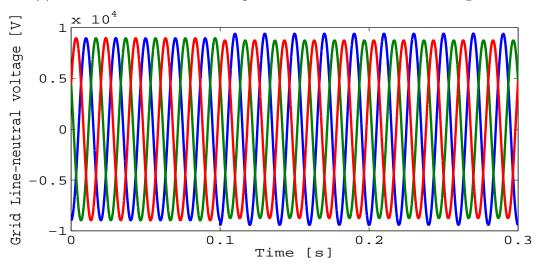

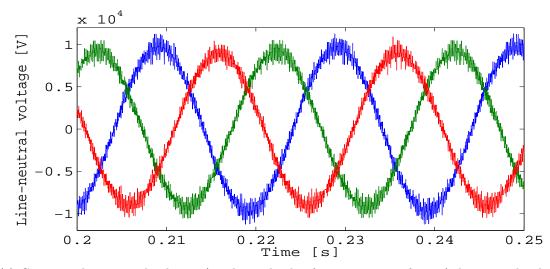

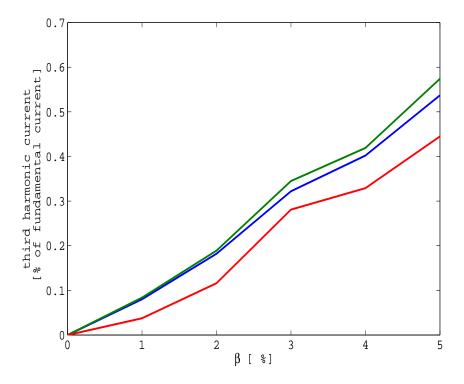

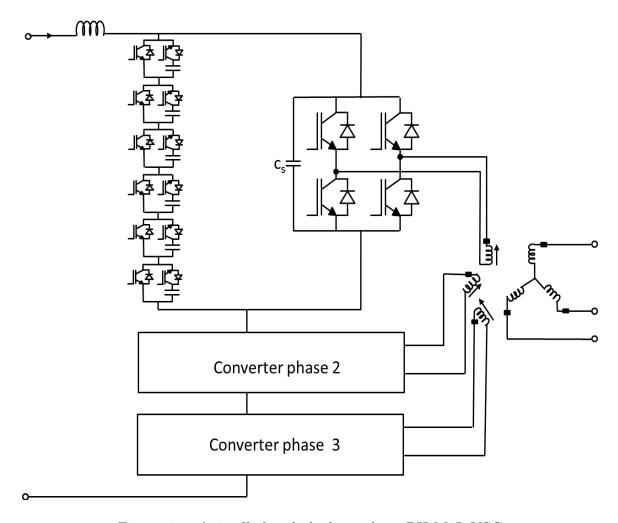

|      | as an inverter (exporting 1.6kW to the grid)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 184   |