Harrison, Andrew (1995) ASIC based recorders of electrophysiological signals. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/13305/1/282846.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

- · Copyright and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners.

- To the extent reasonable and practicable the material made available in Nottingham ePrints has been checked for eligibility before being made available.

- Copies of full items can be used for personal research or study, educational, or notfor-profit purposes without prior permission or charge provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

- · Quotations or similar reproductions must be sufficiently acknowledged.

Please see our full end user licence at: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

# ASIC BASED RECORDERS OF ELECTROPHYSIOLOGICAL SIGNALS

by

# Andrew Harrison

Department of Electrical and Electronic Engineering

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy, May, 1995

# **CONTENTS**

### **ABSTRACT**

# **ACKNOWLEDGEMENTS**

| CHA | PTER | 1. | INTR | ODII | CTI | ON |

|-----|------|----|------|------|-----|----|

|     |      |    |      |      |     |    |

|     | 1.1.    | Long term ambulatory recording                                                                                     |             |

|-----|---------|--------------------------------------------------------------------------------------------------------------------|-------------|

|     | 1.2.    | Electrophysiological signals                                                                                       | 3           |

|     | 1.3.    | Initial application areas of ASIC based ambulatory monitors 1.3.1. HRV studies 1.3.2. Monitoring in obstetrics     | 3<br>4<br>4 |

|     | 1.4.    | Initial recorder requirements 1.4.1. Adult HR recorder 1.4.2. General electrophysiological signal recorder         | 5<br>5<br>6 |

|     | 1.5.    | Initial ASIC design 1.5.1. Adult HR recorder (mode 1) 1.5.2. General electrophysiological signal recorder (mode 2) | 7<br>7<br>7 |

|     | 1.6.    | Development strategy                                                                                               | 9           |

|     | 1.7.    | Structure of thesis                                                                                                | 9           |

| CH. | APTER 2 | 2: INTRODUCTION TO ASIC TECHNOLOGY                                                                                 |             |

|     | 2.1.    | Introduction                                                                                                       | 12          |

|     | 2.2.    | Advantages of ASICs                                                                                                | 13          |

|     | 2.3.    | Custom IC design                                                                                                   | 13          |

|     | 2.4.    | Introduction to FPGA technology                                                                                    | 14          |

# CHAPTER 3: ADULT HR RECORDER USING AN FPGA

| 3.1.    | Introduction 3.1.1. The ECG                                                    | 15<br>15 |

|---------|--------------------------------------------------------------------------------|----------|

|         | 3.1.2. Heart rate                                                              | 17       |

|         | 3.1.2.1. Clinical importance of HR                                             | 17       |

|         | 3.1.2.2. HR in sports and exercise                                             | 18       |

|         | 3.1.2.2. The his sports and exercise 3.1.3. Commercially available HR monitors | 18       |

|         | 3.1.3. Commercially available The monitors                                     | 10       |

| 3.2.    | Description of FPGA based HR                                                   | 19       |

|         | 3.2.1. Analogue front end circuitry                                            | 20       |

|         | 3.2.2. Digital FPGA circuitry                                                  | 21       |

| 3.3.    | Results                                                                        | 28       |

| 3.4.    | Conclusions                                                                    | 38       |

|         |                                                                                |          |

| CHAPTER | 4: THE DESIGN OF A MIXED ANALOGUE AND DIGITAL ASIC                             |          |

| 4.1.    | Introduction                                                                   | 39       |

| 4.2.    | Overall ASIC design                                                            | 39       |

| 4.3.    | Choosing a process and a CAD tool                                              | 41       |

|         | 4.3.1. The Eurochip scheme                                                     | 41       |

|         | 4.3.2. Process options                                                         | 42       |

|         | 4.3.3. CAD options                                                             | 43       |

|         | 4.3.4. Process and CAD selection                                               | 45       |

| 4.4.    | Testing out the analogue circuitry with ES2 sample chips                       | 47       |

|         | 4.4.1. The dual slope integrating ADC                                          | 48       |

|         | 4.4.2. ADC design factors                                                      | 51       |

|         | 4.4.3. Bread-boarding the dual slope ADC                                       | 54       |

|         | 4.4.4. Performance of ES2 op-amps                                              | 55       |

| 4.5.    | Design of the ES2 ASIC using Solo1400                                          | 56       |

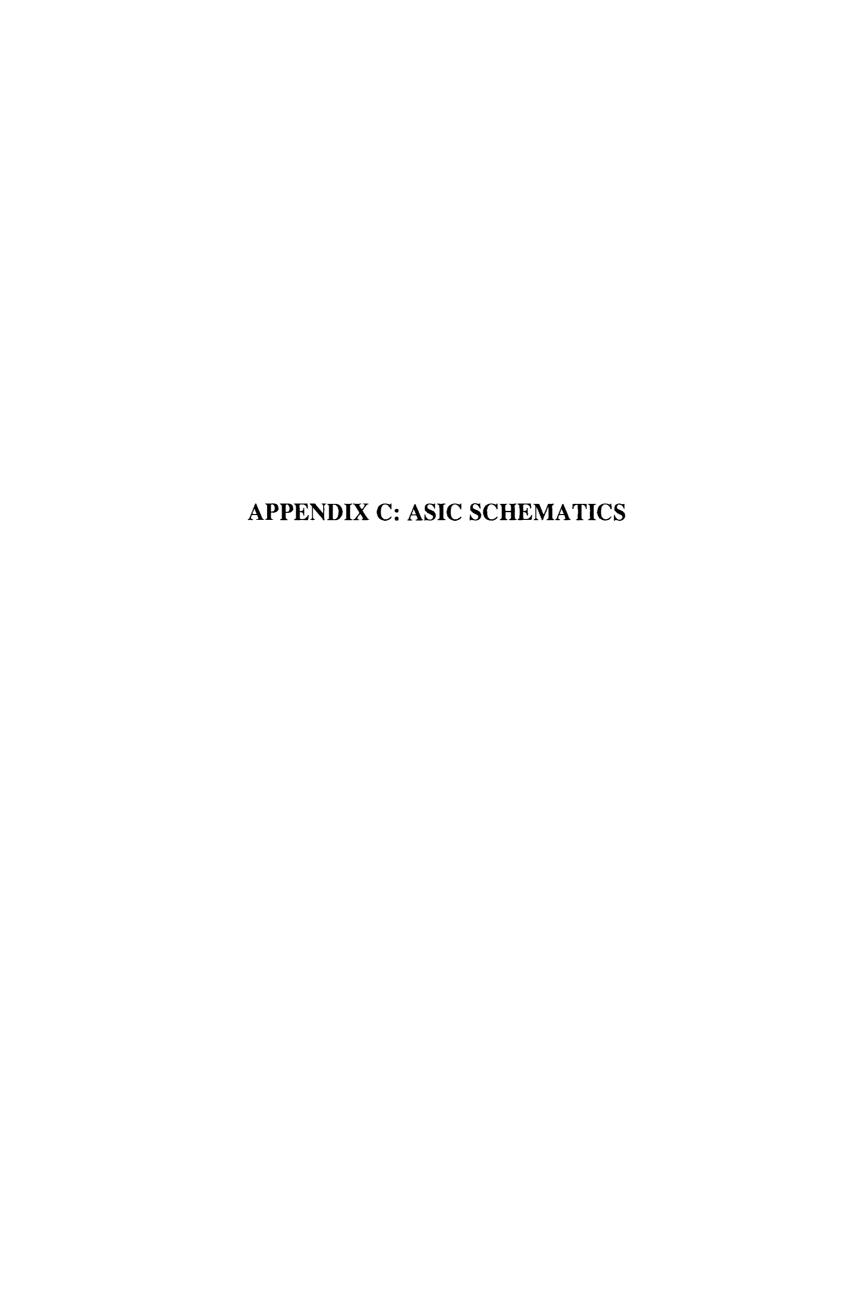

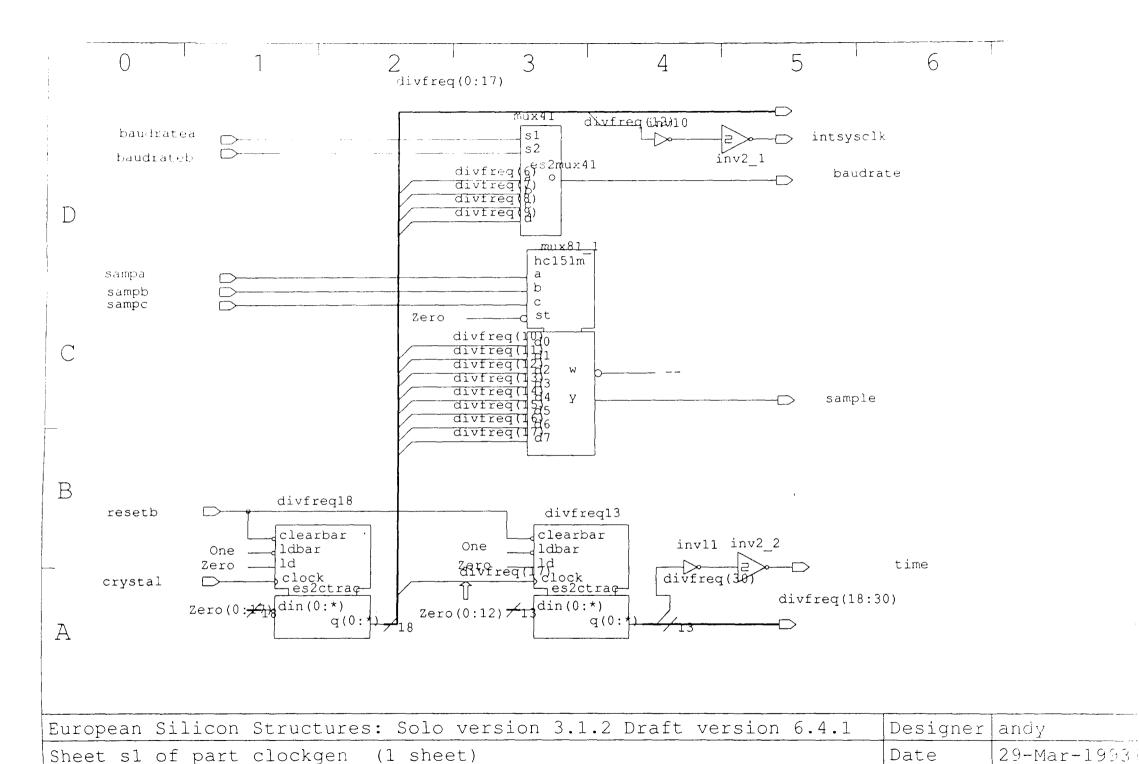

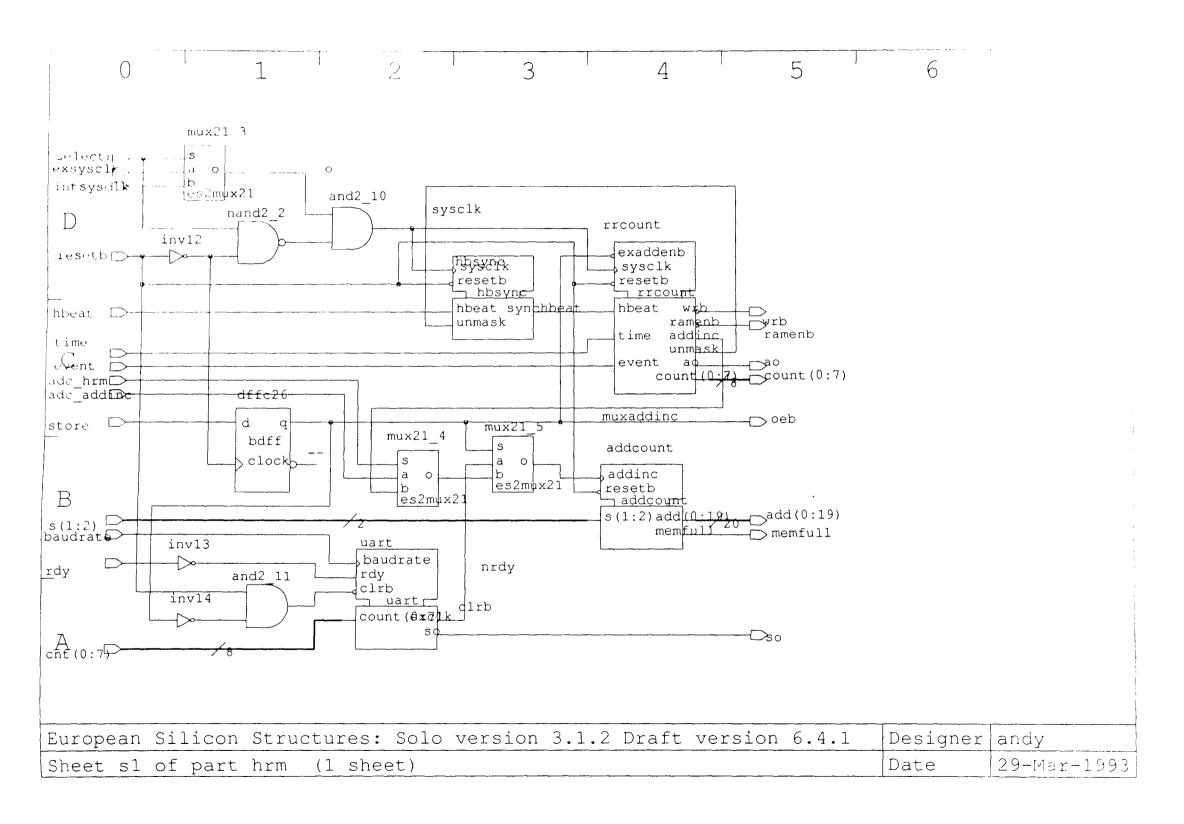

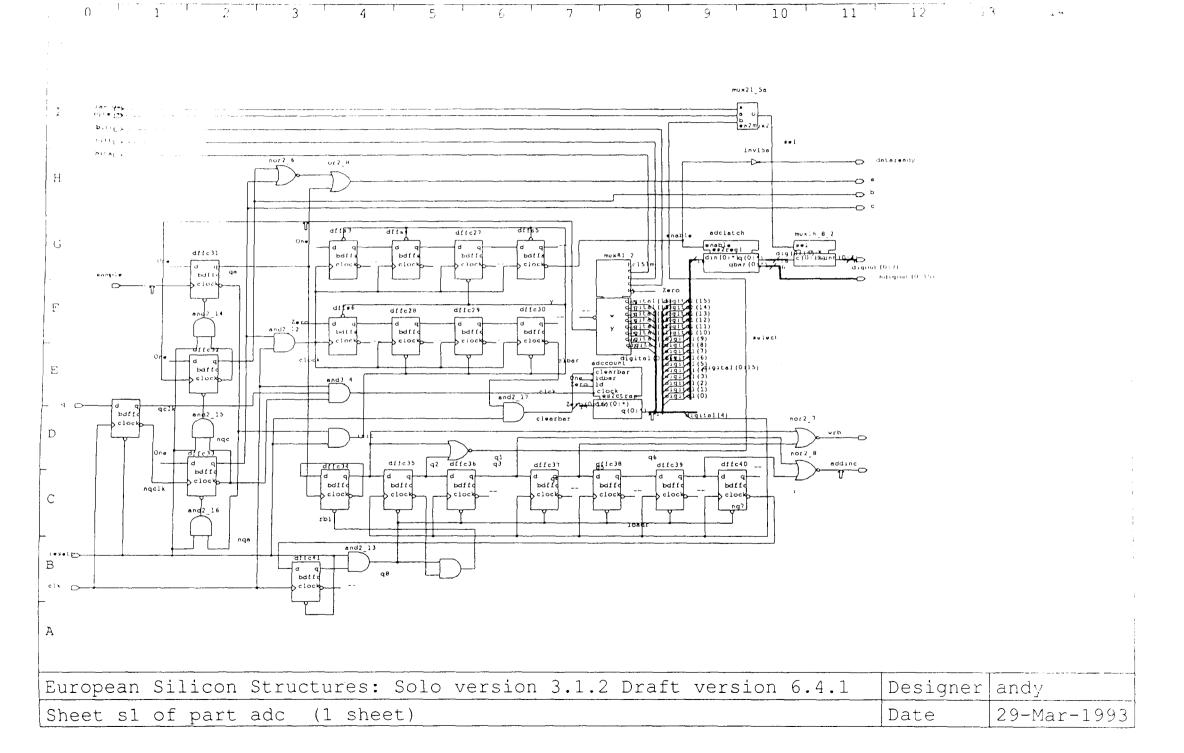

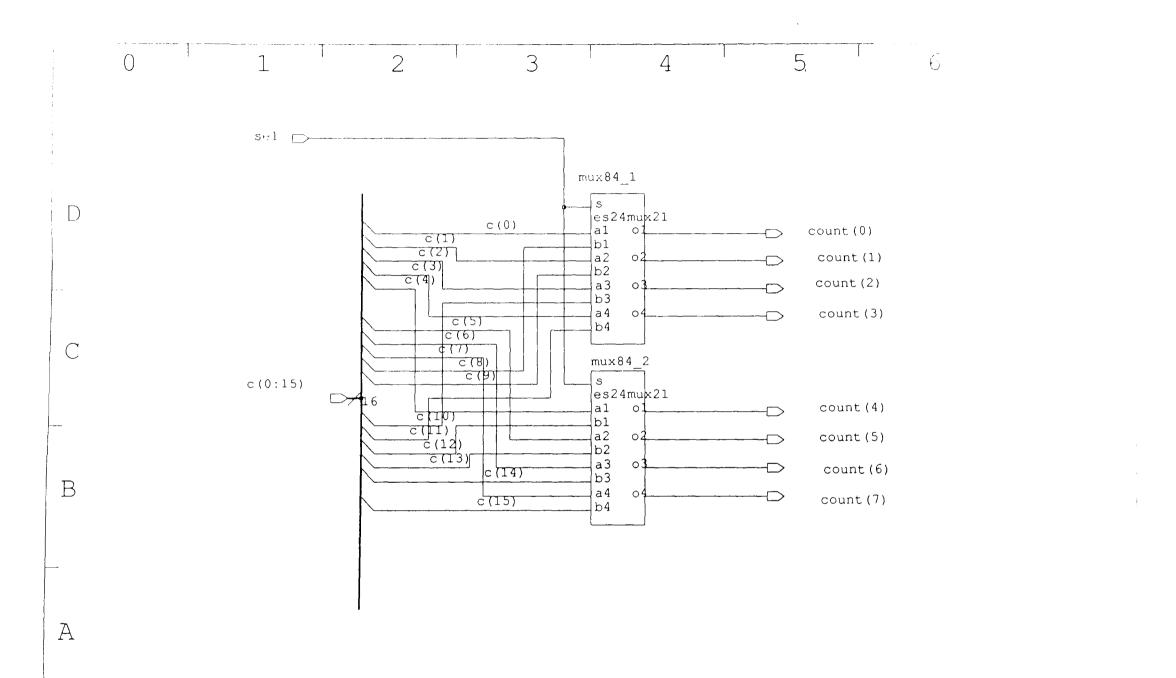

|         | 4.5.1. Schematic capture                                                       | 58       |

|         | 4.5.2. Description of ASIC schematics                                          | 58       |

|         | 4.5.3. ASIC simulation                                                         | 62       |

|         | 4.5.4. ASIC pinout and power supplies                                          | 63       |

|         | 4.5.5. ASIC layout and bonding                                                 | 64       |

| 4.6.    | The ES2 ASIC I/Os                                                              | 64       |

|         | 4.6.1. Multiplexing the I/Os                                                   | 65       |

|         | 4.6.2. Function of I/Os                                                        | 65       |

|         | 4.6.3. I/O settings                                                            | 67       |

|         | ·                                                                              | - •      |

| 4.7.         | Testing and results                                                                                                                                                                                                                                                                                                                                                      | 69                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 4.8.         | Conclusions                                                                                                                                                                                                                                                                                                                                                              | 70                                                        |

| CHAPTER      | 5: ADULT HR RECORDER USING AN ES2 ASIC                                                                                                                                                                                                                                                                                                                                   |                                                           |

| 5.1.         | Introduction                                                                                                                                                                                                                                                                                                                                                             | 72                                                        |

| 5.2.         | Improvements made to HR recorder design 5.2.1. Improvements to analogue circuitry 5.2.1.1. Instrumentation amplifier with filtering 5.2.1.2. R-peak detection circuit 5.2.1.3. Other modifications to analogue circuitry 5.2.2. Improvements made to the digital circuitry 5.2.2.1. Reduction of the fixed count 5.2.2.2. Reduction of the interval between time markers | 72<br>73<br>73<br>76<br>78<br>79<br>79                    |

| 5.3.         | Validation of HR data and initial testing                                                                                                                                                                                                                                                                                                                                | 81                                                        |

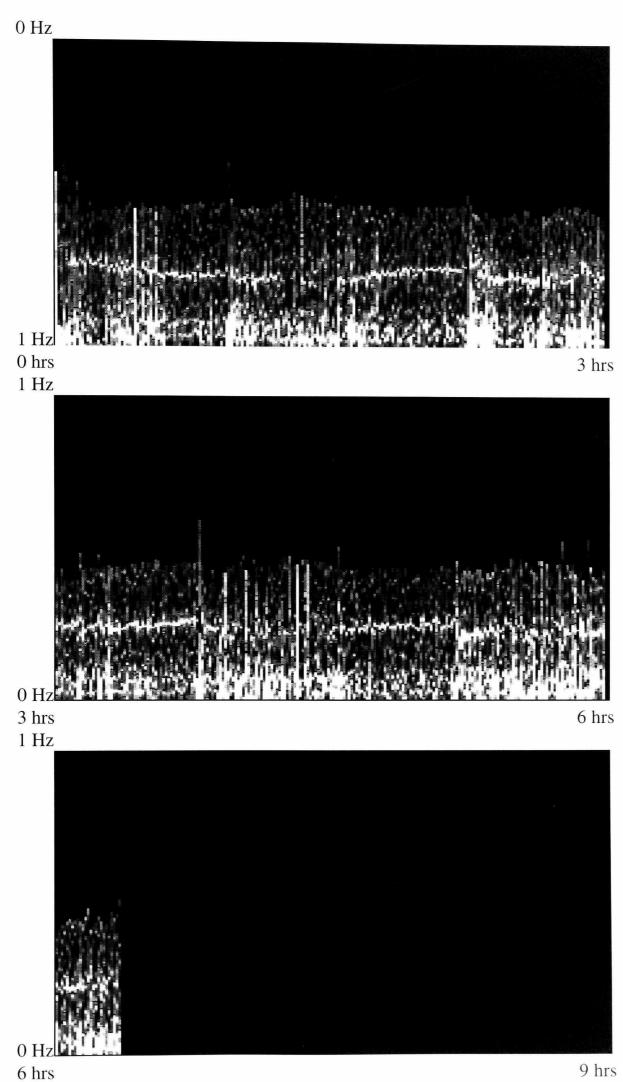

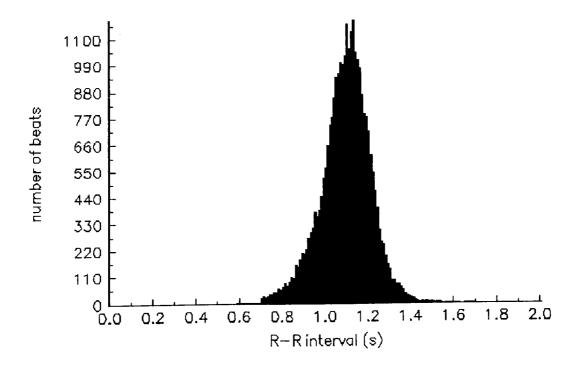

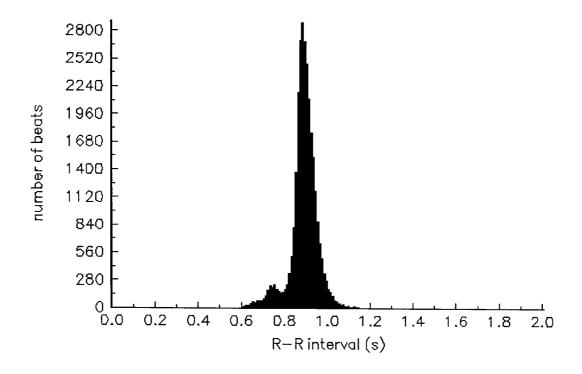

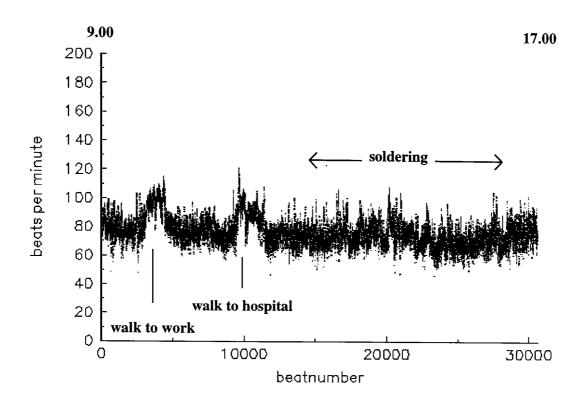

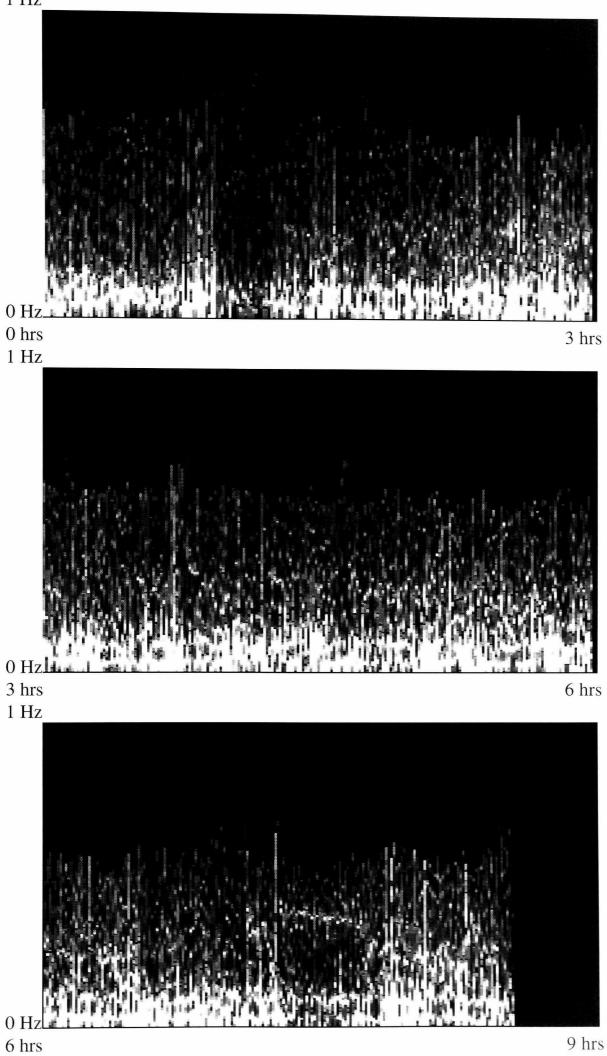

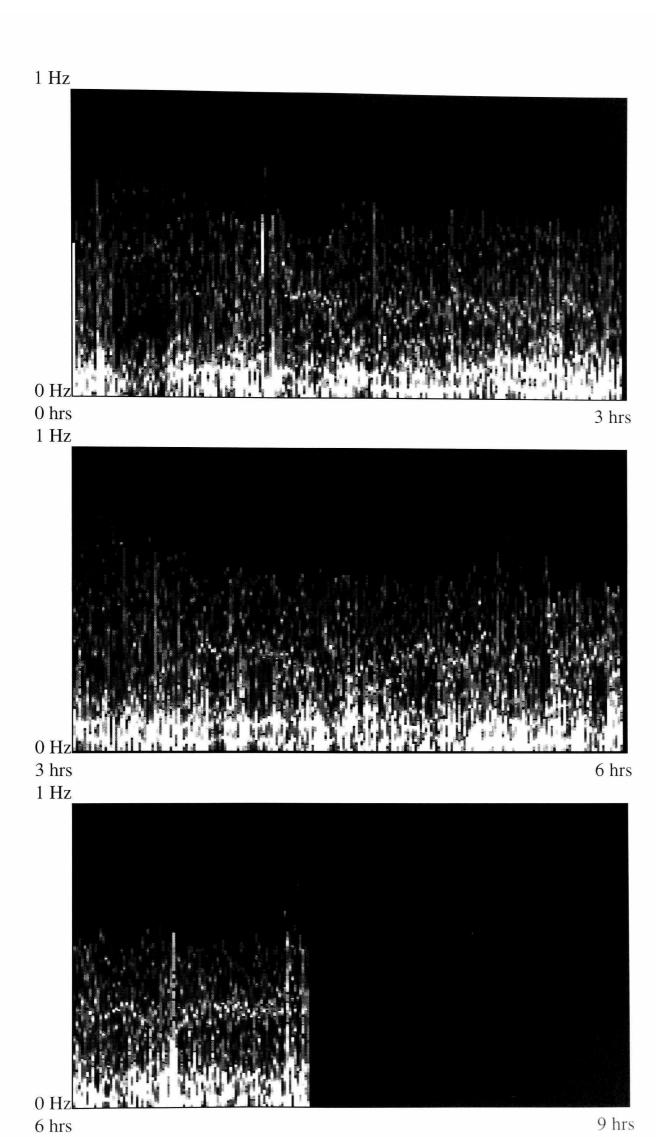

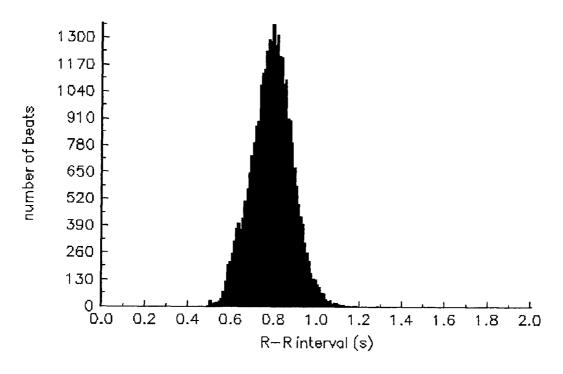

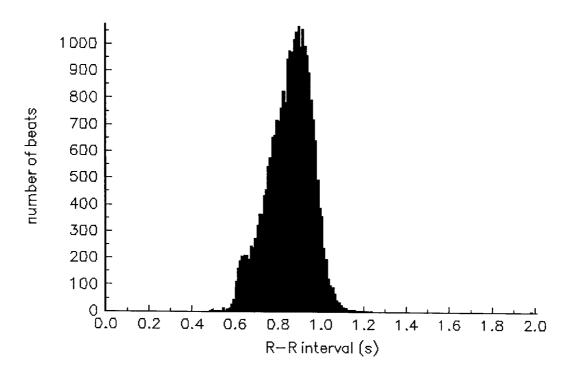

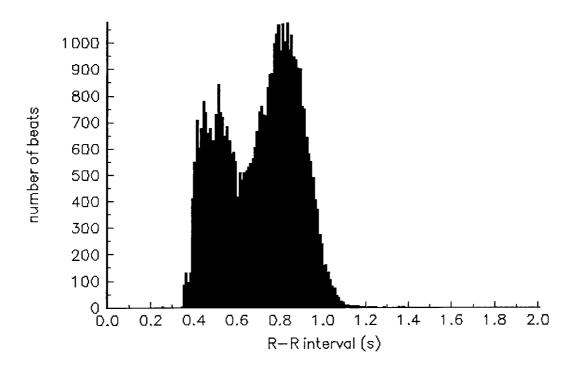

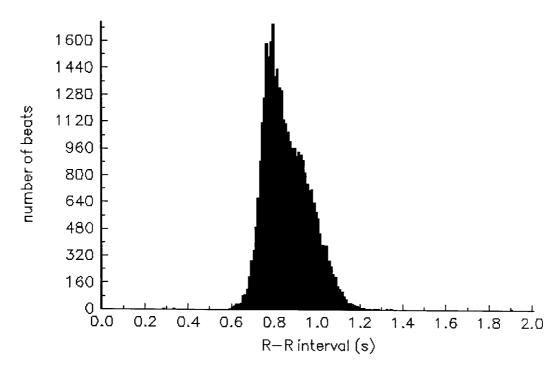

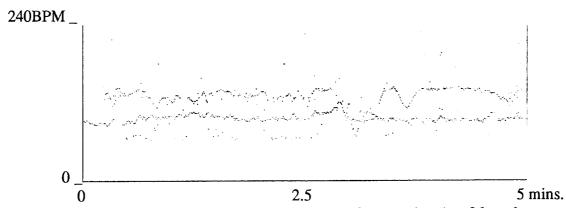

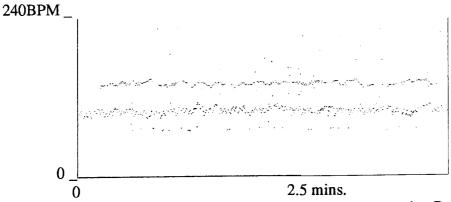

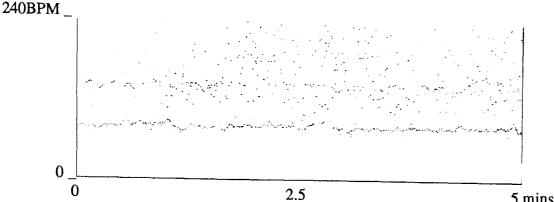

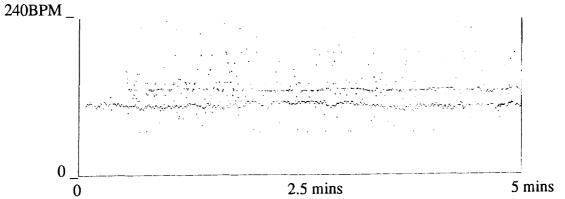

| 5.4.<br>5.5. | Results 5.4.1. Displaying the results 5.4.2. HR patterns at night 5.4.2.1. HR versus beatnumber scatter plots 5.4.2.2. R-R interval spectral plots 5.4.2.3. R-R interval histograms 5.4.3. HR patterns during the day 5.4.3.1. HR versus beatnumber scatter plots 5.4.3.2. R-R interval spectral plots 5.4.3.3. R-R interval histograms  Conclusions                     | 82<br>83<br>85<br>85<br>87<br>92<br>93<br>93<br>97<br>101 |

|              | 6: GENERAL ELECTROPHYSIOLOGICAL SIGNAL RECORDER AND FECG RECORDINGS                                                                                                                                                                                                                                                                                                      | 103                                                       |

| 6.1.         | Introduction                                                                                                                                                                                                                                                                                                                                                             | 106                                                       |

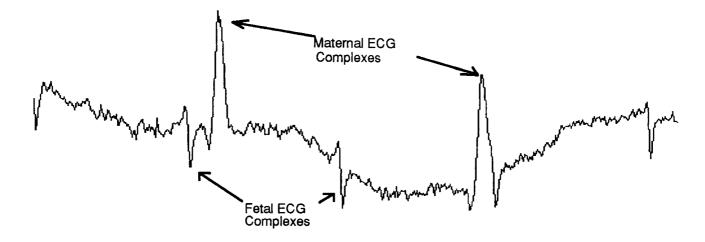

| 6.2.         | FHR Monitoring                                                                                                                                                                                                                                                                                                                                                           | 106                                                       |

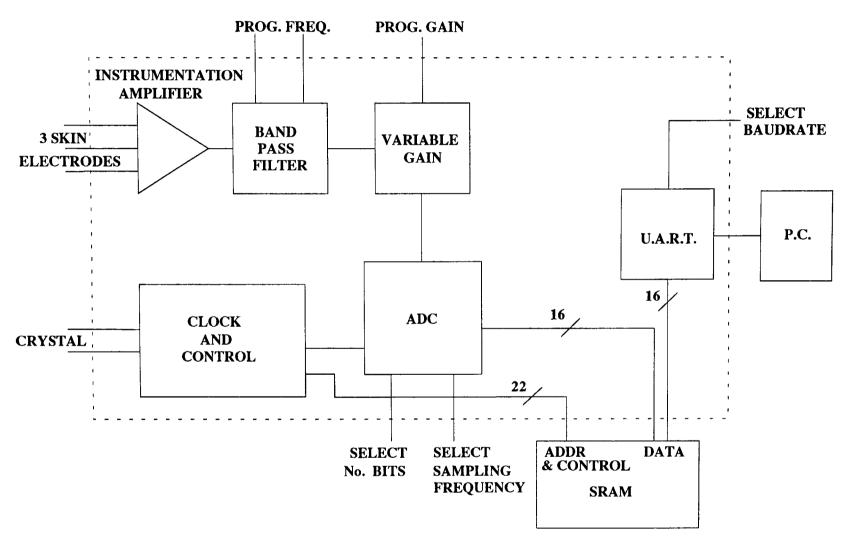

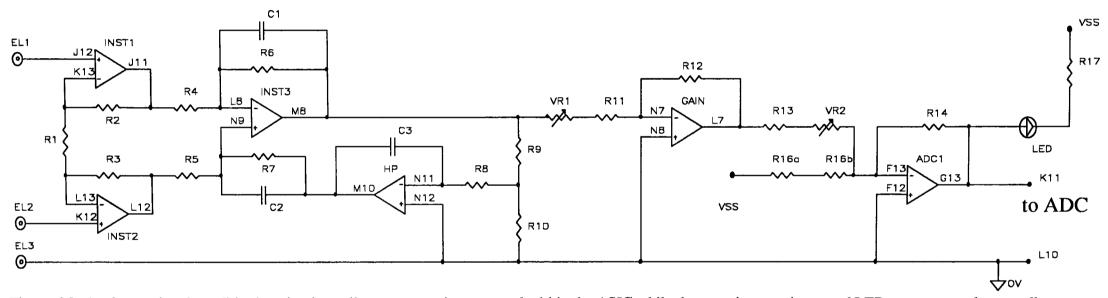

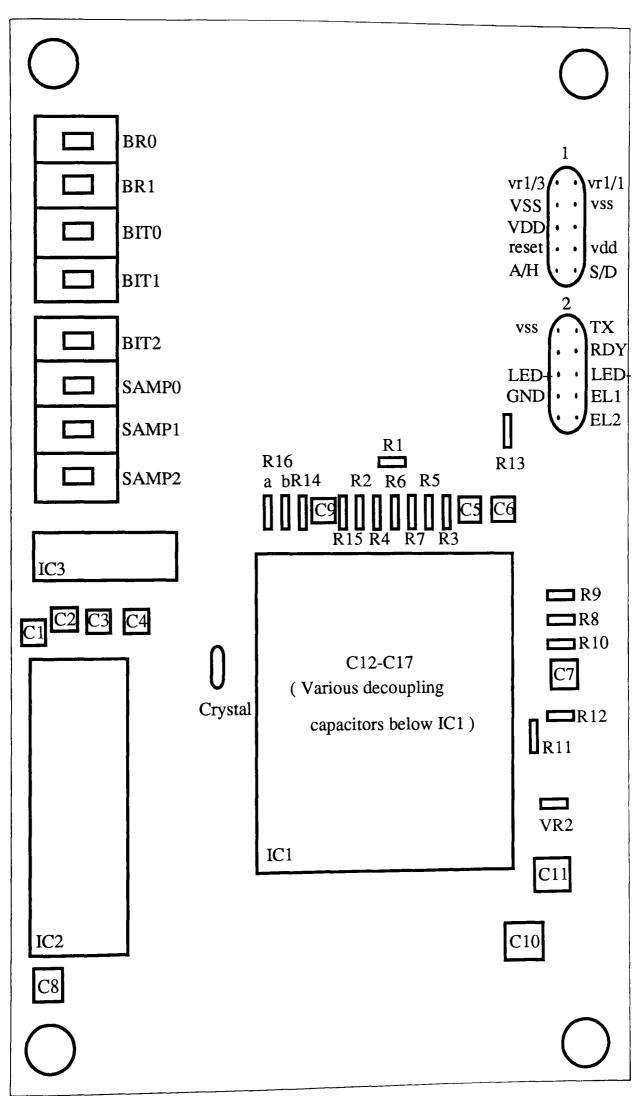

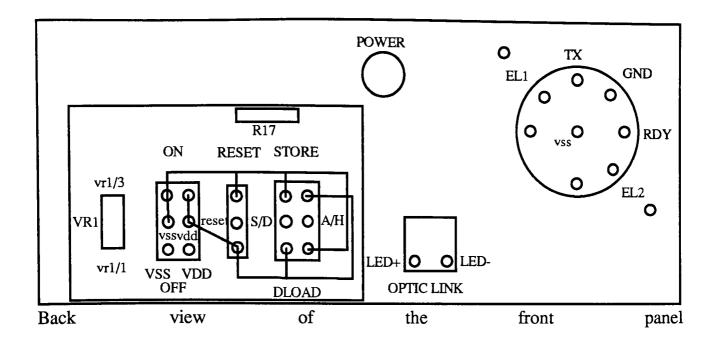

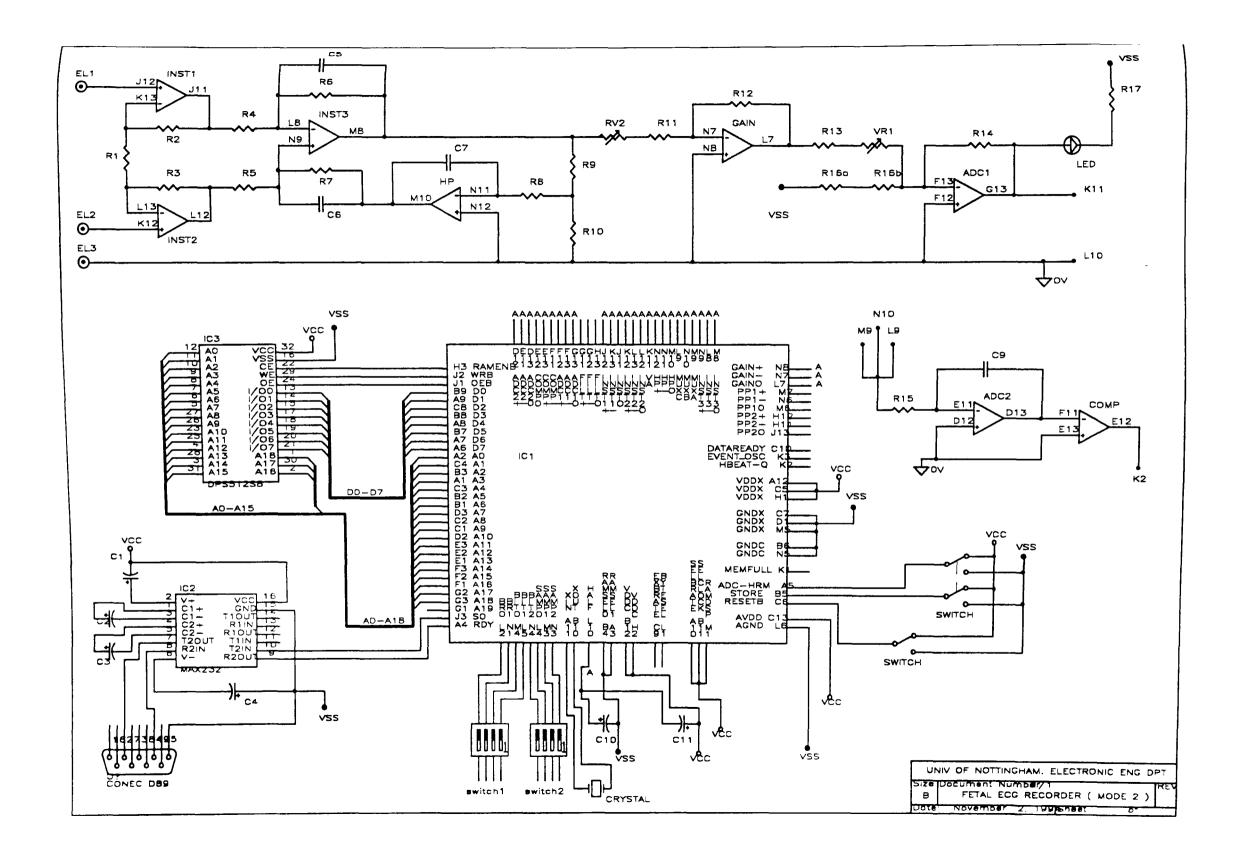

| 6.3.         | Circuit description 6.3.1. Variable bandwidth 6.3.2. Variable gain and the optical link 6.3.3. Programming the ADC and reducing aliasing                                                                                                                                                                                                                                 | 109<br>110<br>111<br>114                                  |

| 6.4.         | FECG recorder                                                                                                                                                                                                                                                                                                                                                            | 114                                                       |

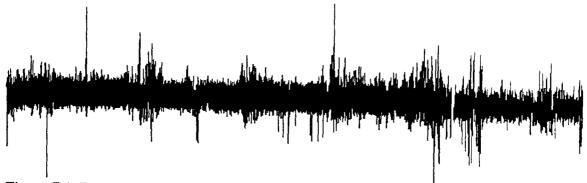

| 6.5.         | FECG results                                                                                                                                                                                                                                                                                                                                                             | 116                                                       |

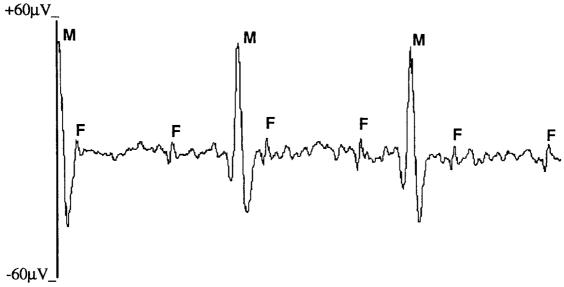

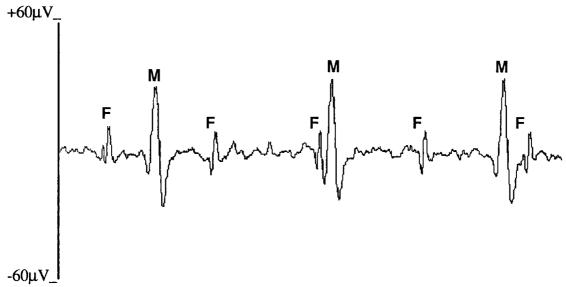

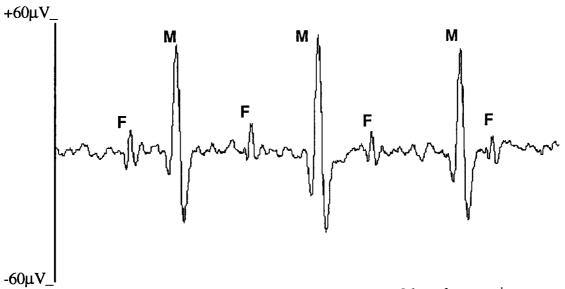

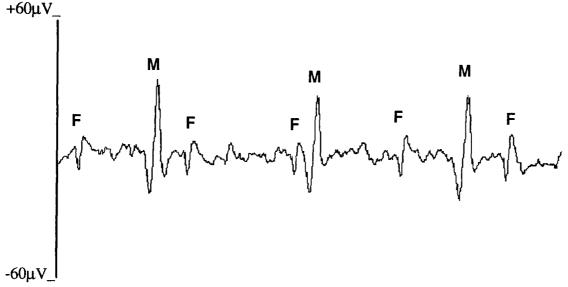

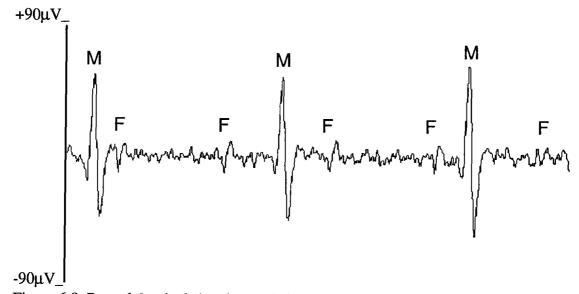

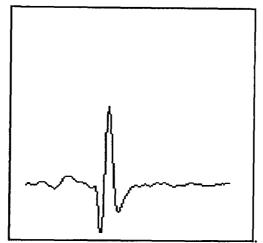

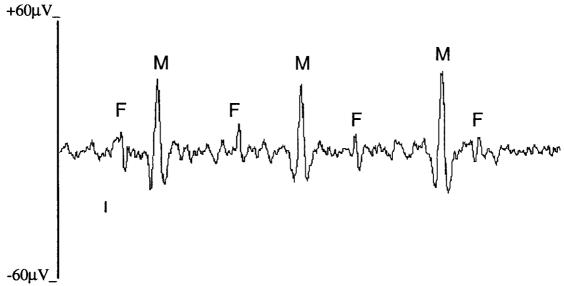

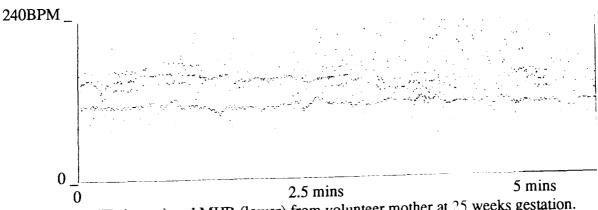

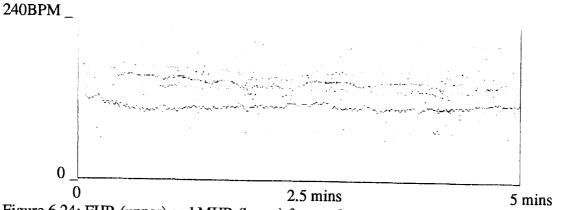

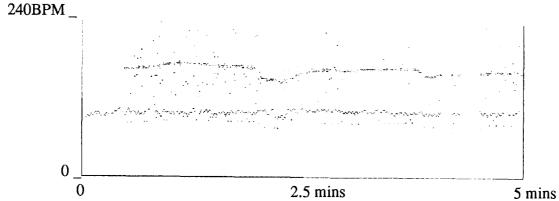

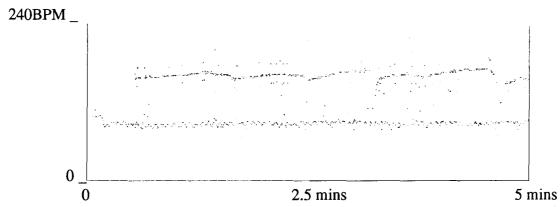

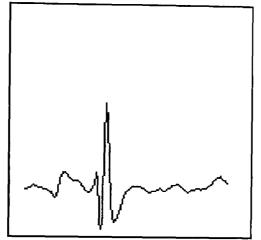

|         | 6.5.1. FECG traces                                                        | 117      |

|---------|---------------------------------------------------------------------------|----------|

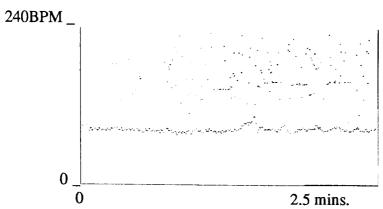

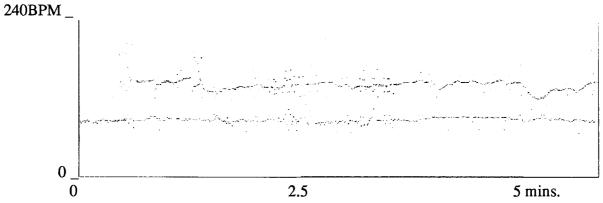

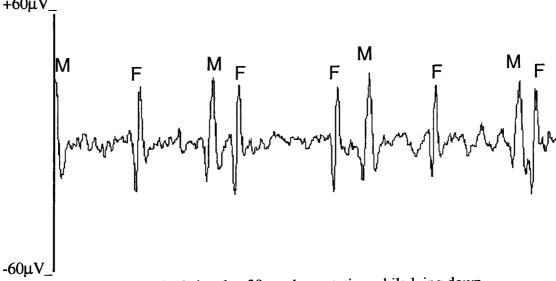

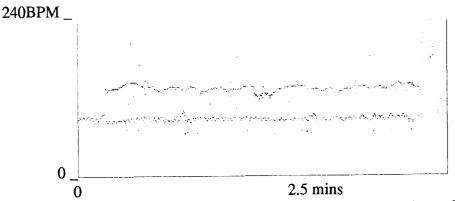

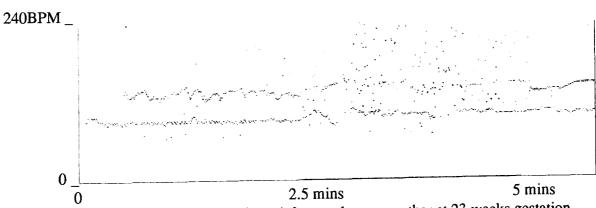

|         | 6.5.2. HR traces                                                          | 117      |

|         | 6.5.3. Averaged FECG complexes                                            | 118      |

|         | 6.5.4. Hospital recordings                                                | 119      |

|         | 6.5.4.1. Electrode type and position                                      | 120      |

|         | 6.5.4.2. Hospital FECG traces                                             | 120      |

|         | 6.5.4.3. Hospital HR traces                                               | 122      |

|         | 6.5.4.4. Hospital averaged FECG complexes                                 | 125      |

|         | 6.5.5. Longitudinal study                                                 | 125      |

|         | 6.5.5.1. Electrode type and position                                      | 126      |

|         | 6.5.5.2. Longitudinal study FECG traces                                   | 126      |

|         | 6.5.5.3. Longitudinal study HR traces                                     | 131      |

|         | 6.5.5.4. Longitudinal averaged FECG complex                               | 134      |

| 6.6.    | Conclusions                                                               | 134      |

| СНАРТЕБ | R 7: EHG RECORDINGS                                                       |          |

| 7.1.    | Introduction                                                              | 138      |

| 7.2.    | The Electrohysterogram                                                    | 138      |

| 7.3.    | EHG recorder                                                              | 140      |

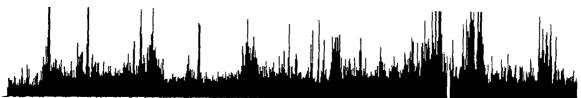

| 7.4.    | EHG results                                                               | 141      |

|         | 7.4.1. Electrode type and position                                        | 142      |

|         | 7.4.2. Processing of EHG signals                                          | 142      |

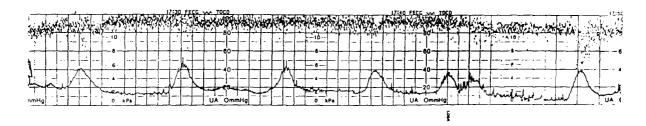

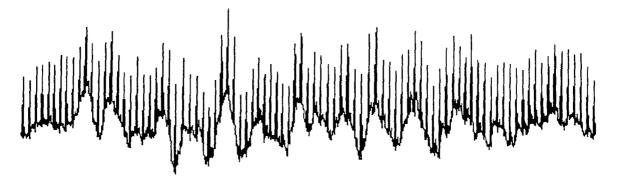

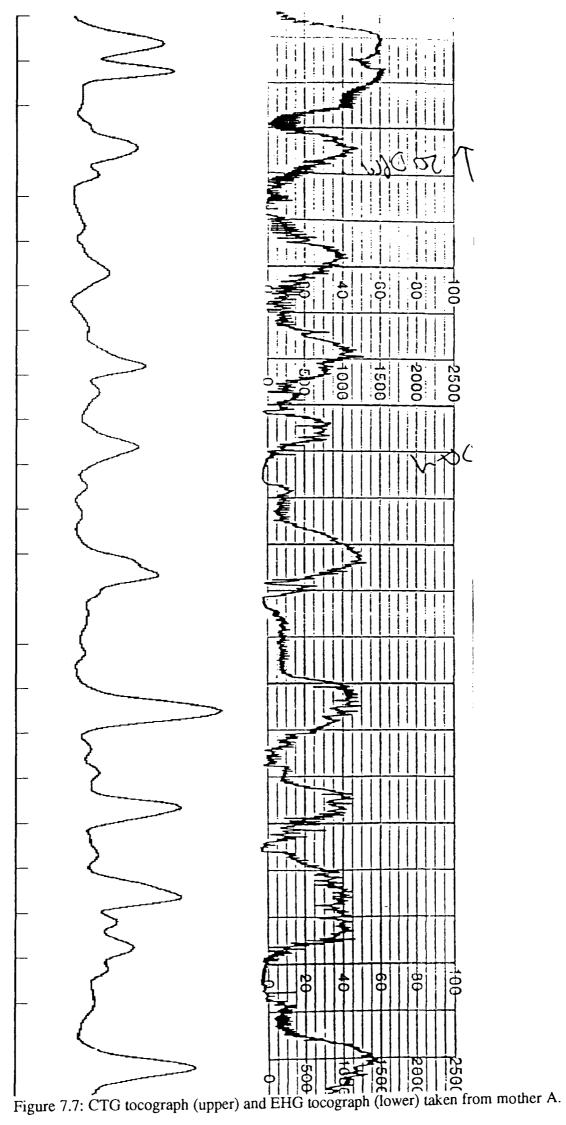

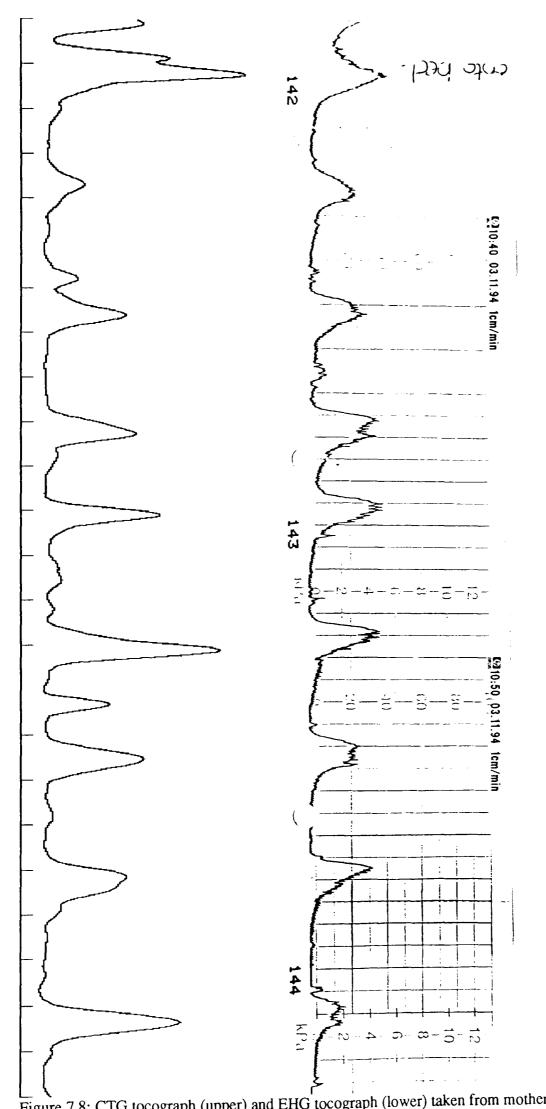

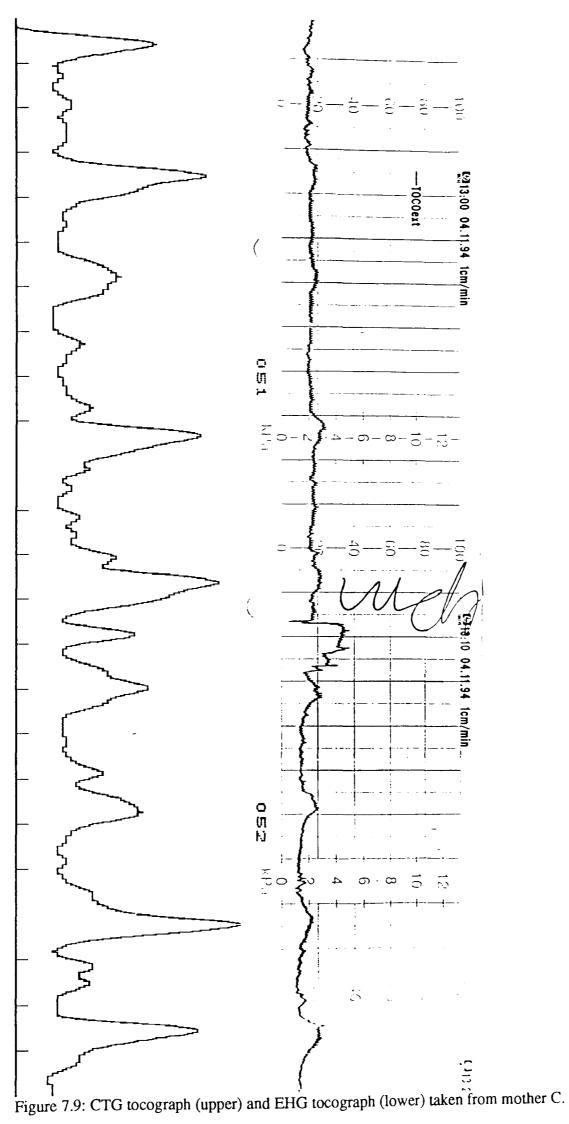

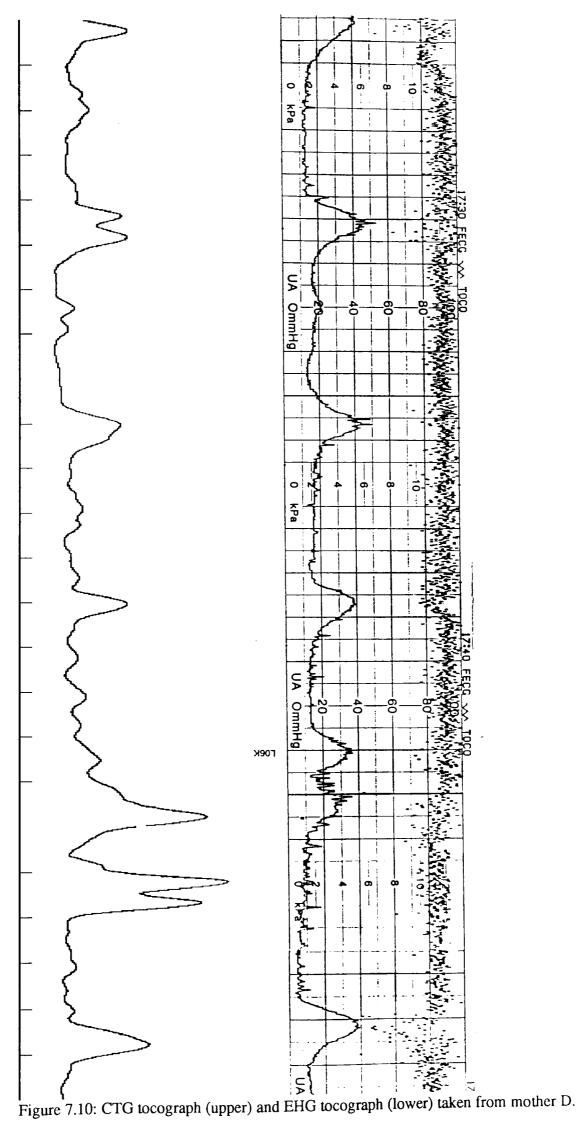

|         | 7.4.3. EHG and CTG tocographs                                             | 144      |

| 7.5.    | Conclusions                                                               | 149      |

| СНАРТЕК | 8: CONCLUSIONS AND FURTHER WORK                                           |          |

| 8.1.    | Conclusions                                                               | 152      |

| 8.2.    | Possible improvements to the ES2 ASIC design                              | 154      |

| 8.3.    | Possible improvements to adult HR recorder                                | 154      |

| 8.4.    | Possible improvements to the general electrophysiological signal recorder | l<br>158 |

| 8.5.    | Recent developments                                                       | 156      |

| REFEREN | CES                                                                       | 157      |

|         |                                                                           |          |

# APPENDIX A: ELECTRICAL SAFETY OF BATTERY OPERATED MEDICAL EQUIPMENT

- A.1. Terminology and definitions

- A.2. Equipment classification

- A.3. Identification, marking and documentation

- A.4. Protection against electric shock hazards

# APPENDIX B: REDUCTION OF NOISE AND 50 HZ INTERFERENCE IN BIOPOTENTIAL AMPLIFIERS

- B.1. Baseline drift (baseline wander)

- B.2. Muscle noise

- B.3. 50 Hz interference

- B.3.1. Magnetic induction into the patient leads

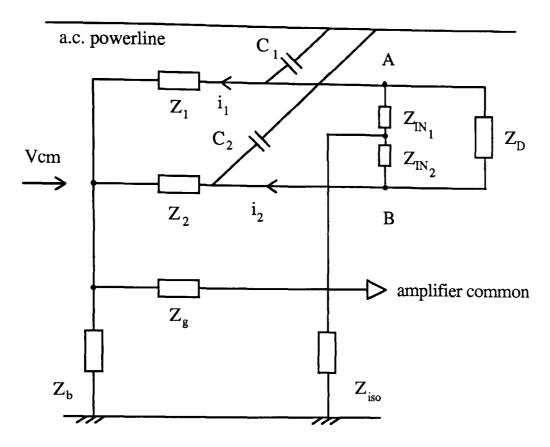

- B.3.2. Displacement current coupled into the patient leads

- B.3.3. Displacement current a.c. coupled into the patient leads

- B.4. Conclusions

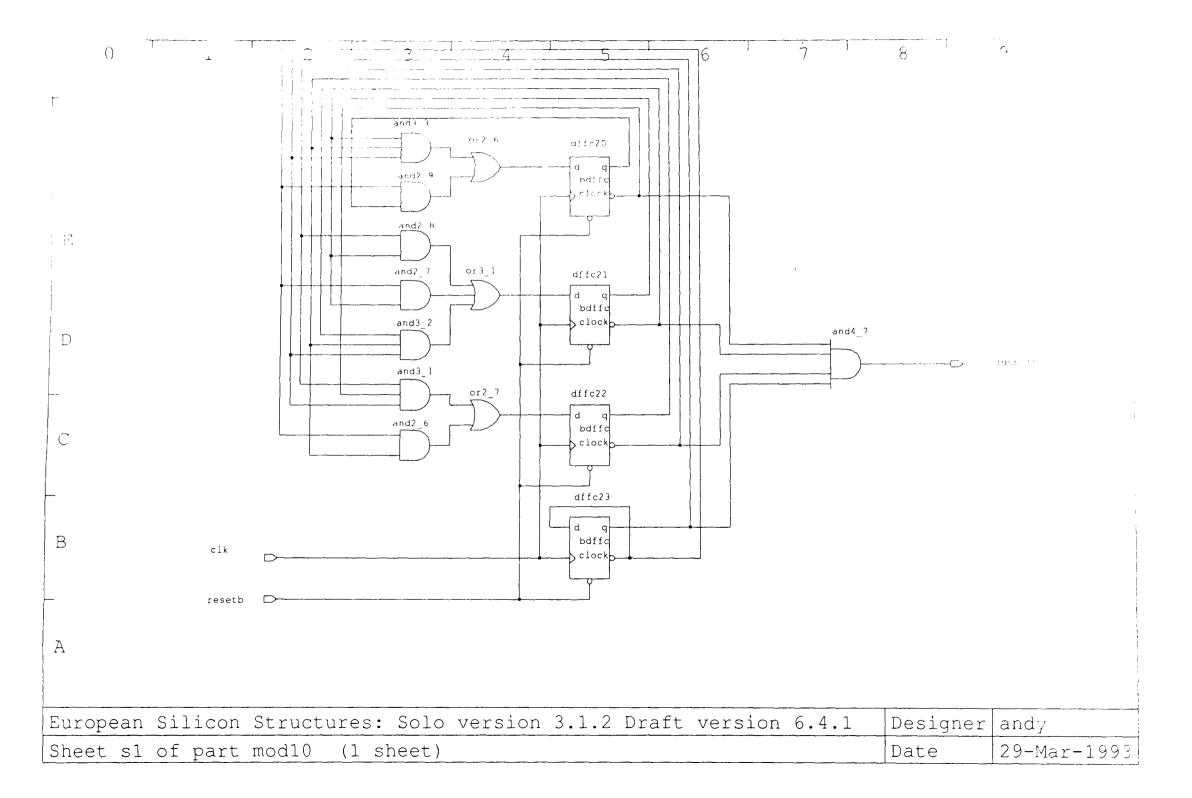

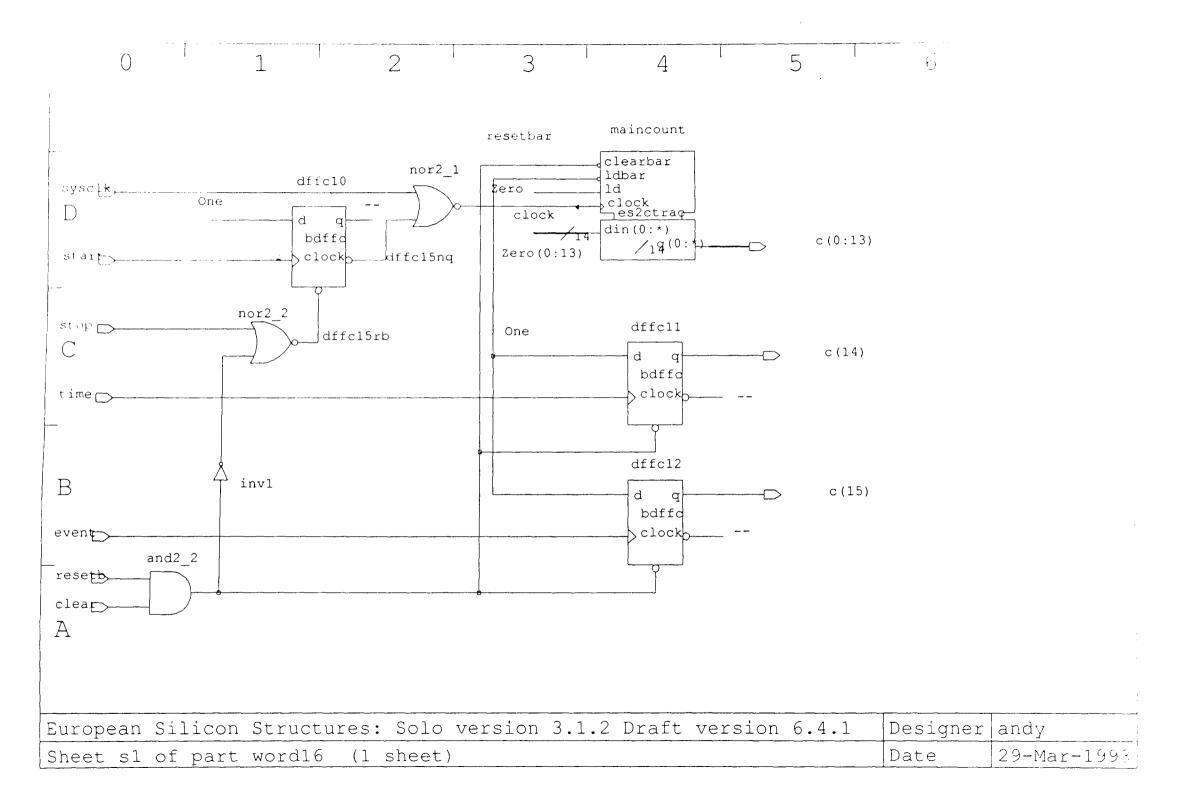

#### APPENDIX C: ASIC SCHEMATICS

#### APPENDIX D: PHOTOGRAPHS

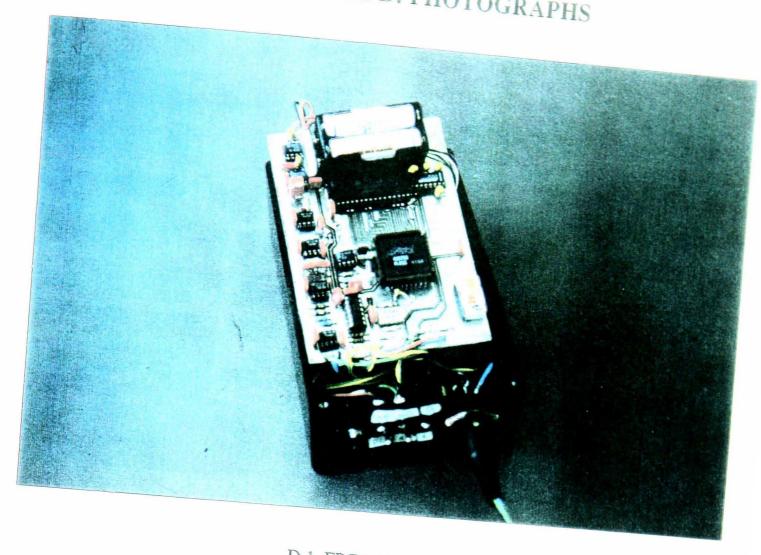

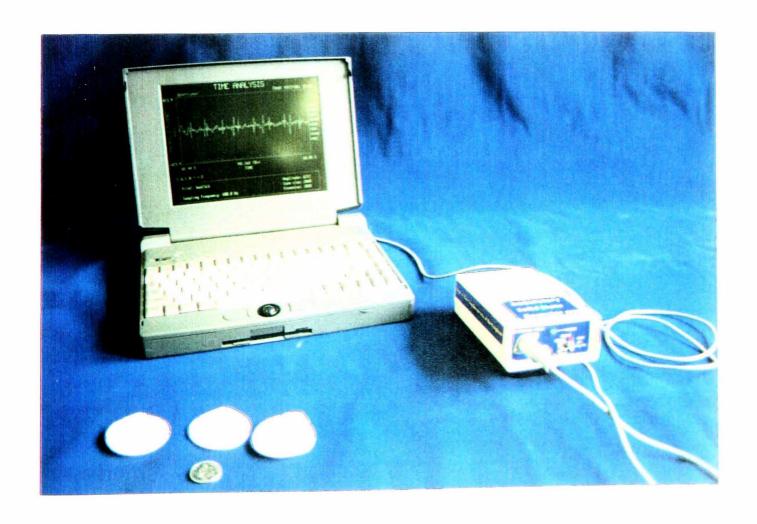

- D.1. FPGA HR recorder

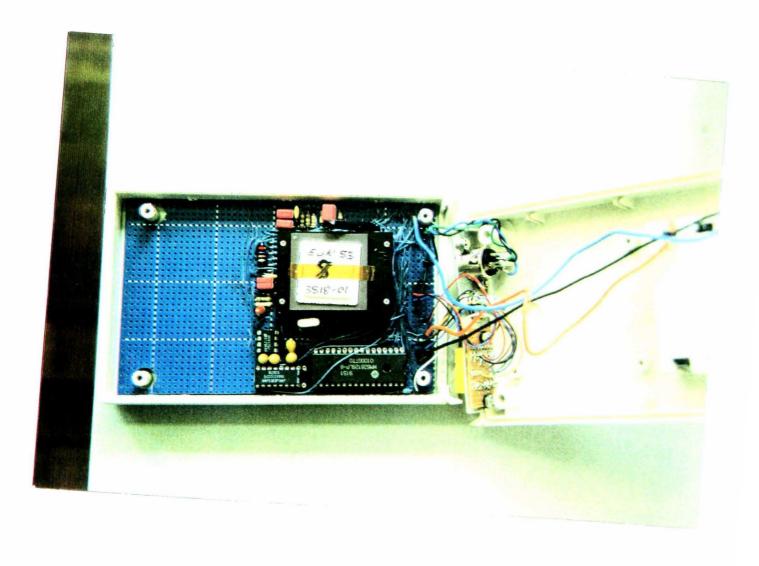

- D.2. ES2 ASIC HR recorder

- D.3. General electrophysiological signal recorder

- D.4. Downloading to the laptop

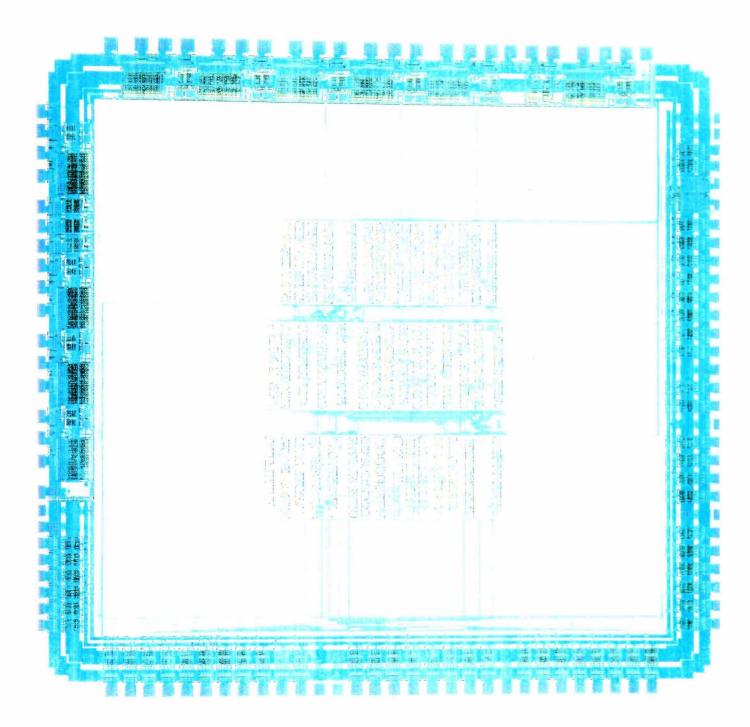

- D.5. ES2 ASIC layout plot

#### APPENDIX E: MESU DOCUMENTATION

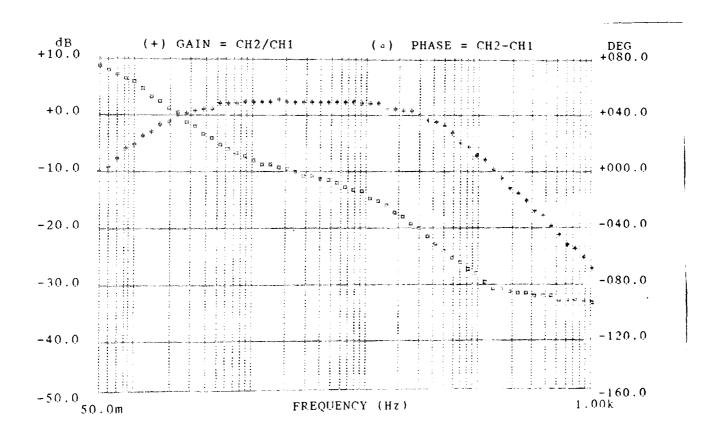

# APPENDIX F: FREQUENCY AND PHASE RESPONSE OF INSTRUMENTATION AMPLIFIER WITH FILTERING

#### **ABSTRACT**

The ability of application specific integrated circuits (ASICs) to minimise the size and power consumption of electronic circuitry, makes their application to the design of ambulatory monitoring equipment, an attractive option. To this end, a multi-purpose mixed analogue and digital ASIC has been fabricated and incorporated into both a long-term recorder of adult heart rate (HR) and a recorder of electrophysiological signals.

The adult HR recorder has been employed in a study of long-term daily HR patterns, which verified the ambulatory nature of this instrument, as well as its suitability for investigating HR variability.

The electrophysiological signal recorder uses the ASIC to amplify, filter and digitise signals, which are then stored directly into static RAM. The analogue front-end of this instrument is flexible in terms of gain, bandwidth and sampling frequency allowing it be applied to a whole range of signals.

This instrument has been used to record the antepartum fetal HR, as part of the development of an ambulatory, ASIC based recorder of fetal HR (FHR). These recordings have shown that a usable signal can be obtained from a mother in her home environment, whilst in various postures.

The electrophysiological signal recorder has also been used to record the electrohysterogram (EHG), which is the name given to the electrical activity of the uterus, from abdominal electrodes during labour. A strong correlation was found to exist between tocographs derived from the EHG and tocographs produced by conventional means.

#### **ACKNOWLEDGEMENTS**

This work was carried out in the Electrical and Electronic Engineering Department in collaboration with the Department of Obstetrics and Gynaecology at the University of Nottingham. I would like to thank all the members of staff of these Departments for their help and support. In particular, I would like to express my appreciation to both of my supervisors, Dr Barrie Hayes-Gill and Dr John Crowe for their valued guidance, encouragement and constant support.

I would especially like to thank Dr Wim van Wijndaarden, Hazel Mills and family, and all the volunteer mothers for their patient cooperation.

Thanks to all of my colleagues in the Medical Electronics group:

Jon for his biscuits, Jules for his jokes, Béatrice for her crips, Mark for being great, Nick for being funky and Richard for keeping me sane. Thanks also to Allaudin, William, Xia Bing, Simon, Jason and Artur.

Finally, special thanks to my parents and to Terena for their total support and encouragement throughout.

### **CHAPTER 1**

#### INTRODUCTION

#### 1.1. Long term ambulatory recording.

Long term ambulatory recording allows important medical variables, such as blood pressure or heart rate (HR) to be monitored over several hours or days. These recordings may be made in various environments, such as the home or at work, and during diverse activities, such as sleep or exercise. The information provided by such recordings is often unobtainable from short term monitoring, both because of the reduction in data and the fact that such studies are generally undertaken in the arguably artificial environment of a hospital or laboratory.

Ambulatory monitoring can be performed on any physiological parameter that is of an electrical nature or that can easily be transduced into an electrical signal. Commonly monitored parameters include: arterial blood pressure, respiration, posture and the electrical activity of the heart, brain, eyes and muscle [Olson, 1978]. Three examples of ambulatory monitors are presented below. The first type of monitor records an electrical signal direct from the skin; whereas the other two monitors require some type of electrical transducer.

Holter monitoring is the ambulatory recording of the electrical activity of the heart and is named after N.J. Holter who first published this technique in 1961 [Holter, 1961]. These monitors continuously record two channels of the electrocardiogram (ECG), taken from chest electrodes, over a 24 hour period.

Ambulatory beat-to-beat arterial blood pressure can be monitored indirectly using the Volume Compensation Technique. This method detects the variation in arterial volume using a transmission infra-red photoelectric plethysmograph (TIPP), together with a pneumatic finger cuff which is controlled by a servosystem in order to maintain a constant arterial volume [Kawarada et al., 1991].

The automatic measurement of physical activity and posture can be achieved by attaching either accelerometers or inclinometers to various positions on the body [Tanaka et al., 1994]. Ambulatory posture monitoring is usually performed in conjunction with blood pressure monitoring because the latter is posture dependent. Recording of physical activity is also used together with Holter monitoring in order to investigate the heart's reaction to exercise [Meijer et al., 1989].

Traditionally data is stored onto a miniature tape, but in recent years solid state recorders have become possible due to the ever increasing capacity of this type of memory device, together with the availability of low power microprocessors, capable of performing real time data compression.

In designing ambulatory monitoring equipment, it is important to produce an instrument which is both unobtrusive and comfortable enough to be worn over many hours or days. Therefore any means of reducing the overall size and power consumption of such equipment would seem to be of value. The ability of Application Specific Integrated Circuits (ASICs) to minimise the size and power consumption of electronic circuitry, makes their application to the design of long term ambulatory monitoring equipment an attractive option. The ability of ASICs to incorporate an element of real time processing could also be useful in extending recording times.

This thesis is concerned with the application of ASICs to ambulatory monitoring, and in particular, the development of long term ambulatory recorders of electrophysiological signals.

#### 1.2. Electrophysiological signals

Electrophysiological signals (also referred to as biopotentials or bioelectrical signals) are electrical signals produced by various parts of the normally functioning human, which appear on the surface of the body. It is possible to detect, amplify and record these signals with electronic instrumentation via cutaneous (skin) electrodes. Such instrumentation also usually incorporates an element of filtering which is required in order to suppress various types of noise and interference. The three most common types of noise and interference found in electrophysiological signals are baseline drift, muscle noise and 50 Hz interference. A more detailed description of these phenomena can be found in Appendix B.

Examples of electrophysiological signals include the electrocardiogram (ECG), electromyogram (EMG), electroencephalogram (EEG), electrooculogram (EOG) and electrogastrogram (EGG); all these signals are related to the operation of a particular part of the body i.e. heart, muscle, brain, eyes or stomach respectively. The normal operation of these organs can be investigated by analysing the related electrophysiological signal. This analysis has led to the use of electrophysiological signals as clinical tools in the detection and diagnosis of organ dysfunction.

#### 1.3. Initial application areas of ASIC based ambulatory monitors

Initially two areas of study were chosen as vehicles for investigating the value of ASICs to ambulatory monitors: long term heart rate variability (HRV) and monitoring in obstetrics. As well as investigating the suitability of ASICs for

ambulatory monitors, it was intended that by targeting these particular application areas, this work would interface well with other research work within the Medical Electronics group at Nottingham [Herbert, 93], [Gibson, 93].

#### 1.3.1. HRV studies

The standard method of collecting long-term HR data is to use a Holter monitor, but such systems are expensive in terms of both the price of the individual monitors and that of the analysing systems (both hardware and software). In addition, the suitability of these systems for producing accurate enough HR data for certain types of HRV studies has been questioned [Pinna et al., 1994]. This is because the requirement of Holter monitors to record two channels of raw ECG for 24 hours limits the sampling frequency that can be used (usually 128 Hz).

An instrument which just records HR should be able to increase both the accuracy of HR data obtained and the maximum record time. By designing the instrument such that recorded data can be downloaded to a general purpose PC, savings on the cost of analysing the data will also be made. However, it should be noted that recording just HR rather than the full ECG may limit the clinical use of such a recorder to subjects with predominantly normal ECGs. The ECG of cardiac patients generally contains many abnormal beats, which need to be eliminated before certain types of HRV analysis can be performed.

#### 1.3.2. Monitoring in obstetrics

Work on the development of a portable fetal and maternal heart rate (FHR + MHR) recorder [Mohd Ali et al., 1993] had reached a stage where the basic idea had been shown to be feasible using discrete components. By integrating

as much of this design as possible onto an ASIC, it should be possible to produce a truly ambulatory version.

During the development of this instrument it became apparent that a similar device capable of recording uterine contractions from abdominal electrodes would also be of value in the area of obstetrical monitoring [Marque, private communication]. Such an instrument could be useful in monitoring for premature contractions antenatally, as well as providing a more convenient means of monitoring uterine activity during labour. (Obviously the latter application does not necessarily require the monitoring equipment to be ambulatory.)

Therefore it was proposed that the existing FHR recorder design be modified so that it could also be configured to record uterine activity from the electrohysterogram (EHG), which is the name given to uterine EMG signals recorded on the abdomen.

#### 1.4. Initial recorder requirements

Two instruments were proposed: a long term recorder of adult HR for use in HRV studies and a general electrophysiological signal recorder for use in obstetrical monitoring. Although the primary application of the second instrument would be as a long term recorder of FHR, it would also be used as a means of investigating the potential for monitoring uterine activity from abdominal electrodes.

#### 1.4.1. Adult HR recorder

The adult HR recorder would need to be capable of storing HR data with an accuracy acceptable for HRV studies over a 24 hour period. The recorded HR information would then be downloaded to a standard PC for further analysis. It

was hoped that by integrating as much of the circuitry as possible onto a single ASIC, a small instrument could be constructed, using simply the ASIC, RAM and a PC interface IC.

#### 1.4.2. General electrophysiological signal recorder

By allowing the gain, bandwidth and sampling frequency of the existing FHR recorder design to be reconfigurable, a more general recorder would be realised. This flexibility would allow the instrument to be applied to many other electrophysiological signals, and in particular the recording of uterine activity from abdominal electrodes.

It was intended that ultimately a digital signal processor (DSP) would be used for the various real time processing procedures, such as extraction of FHR or detection of uterine contractions. After completion of the recording, data would need to be transferred to a standard PC for further analysis. The ASIC would thus be used for signal conditioning and digitising of the raw electrophysiological signal, as well as providing the glue-logic used in interfacing to the DSP. It was envisaged that such an instrument could be constructed using simply the ASIC, RAM, a DSP with external erasable programmable ROM (EPROM) and a PC interface IC.

Although the eventual aim is to produce a DSP based instrument, the initial instrument did not include a DSP. Instead raw electrophysiological signals were stored directly to RAM. This instrument was used to investigate the quality of raw signals obtainable using an ASIC based front end. Once downloaded to a PC these raw signals could be processed off-line. A collection of raw signal recordings will prove useful for developing algorithms which will eventually run in real time on the final DSP based instrument.

#### 1.5 Initial ASIC design

Initially a multipurpose ASIC was proposed having two modes of operation. It was intended that these modes would be used as the basis for one of two different ambulatory recorder designs:

- 1) Adult HR recorder (mode 1)

- 2) General electrophysiological signal recorder (mode 2)

As much of the circuitry as possible was to be integrated on to the ASIC in order to keep the final instruments as small as possible. By including the circuitry for both modes on a single ASIC, two different designs could be tried out for the cost of one design run, with minimal increase in overall ASIC size. This is because much of the circuitry is common to both designs, in particular the analogue front end circuitry needed for signal conditioning and the digital circuitry for interfacing with the serial port of a PC.

#### 1.5.1. Adult HR recorder (mode 1)

It was intended that all the circuitry required for an adult HR recorder with the exception of RAM and PC interface chip, could be included on the ASIC. This would consist of analogue signal conditioning and heart beat detection, followed by digital heart beat interval timing and RS-232 interface circuitry.

#### 1.5.2. General electrophysiological signal recorder (mode 2)

In mode 2 an on-chip analogue to digital converter (ADC) placed after the analogue signal conditioning circuitry would be used to digitise raw electrophysiological signals before being either stored directly in off chip RAM, or processed in real time by a DSP.

In order that the instrument could be used to record many different electrophysiological signals it should be made as flexible as possible in terms of gain, bandwidth, sampling frequency and ADC resolution. This flexibility would allow the instrument to be used to record signals of differing amplitude and frequency content. The simplest way to achieve maximum gain and bandwidth flexibility is to use off chip resistors and capacitors. Although this philosophy would lead to an increase in ASIC input/output (I/O) pins, the improvement in programmability and hence flexibility of the recorder warranted this.

When configured with a DSP, responsibility for writing and reading from RAM, as well as interfacing with the serial port of the PC during downloading would, be transferred from the ASIC to the DSP.

The flexibility of the ASIC front-end, together with the programmability of the DSP, will produce a general recording instrument which could have numerous applications within the field of ambulatory monitoring. It would, in fact, be possible to use mode 2 to record adult heart instead of mode 1. However the argument for developing mode 1 is still strong, as a mode 2 DSP based adult heart rate recorder would have the disadvantages of increased size and complexity, power consumption, and a higher cost.

A DSP based mode 2 instrument would also be able to overcome the problem of using a mode 1 instrument on cardiac patients. This would require algorithms, running on the DSP, to either detect and remove abnormal beats from HR data, or to compress the full ECG sufficiently well that a higher sampling frequency (than 128 Hz) could be used.

#### **1.6.** Development strategy

A major drawback in using ASIC technology to implement new circuit ideas, is the risk factors involved in going straight to silicon with an unproven design. As well as the cost of resubmitting an erroneous design, there is the time penalty induced in turning round the corrected design. It takes at least a month and more often three, from submitting a design to receiving the fabricated chips. To reduce these risk factors, certain parts of the design were initially prototyped in order to prove their validity.

The digital logic used in the 24 hour adult HR recorder design was first prototyped with an Actel field programmable gate array (FPGA). A printed circuit board (PCB) was then built, containing the FPGA together with discrete ICs for the analogue circuitry, in order to prove the complete mode 1 design. Once the decision had been made to fabricate the ASIC design using the European Silicon Structures (ES2) 1.5 µm process via Solo1400 CAD tool (ES2 computer aided design software package), various other parts of the design were prototyped using ES2 sample chips. Important analogue sections of the design, such as a sample and hold circuit and a dual slope ADC were tried out, as the ability of Solo1400 software package to simulate analogue circuitry is very limited.

The time and effort spent in proving much of the design in this manner, increased the confidence in the design and the ability to get the ASIC circuitry right first time.

#### 1.7. Structure of thesis

This thesis contains a total of 8 chapters together with several appendices, beginning with this chapter, which is a general introduction to the area of research.

An introduction to ASIC technology is presented in Chapter 2. This section briefly describes the advantages of using ASICs, together with the various types of ASICs that are currently available. Also included in this section is an introduction to FPGA technology, highlighting the relative merits of these devices in comparison to discrete ICs as well as more conventional mask ASICs.

Chapter 3 describes how the adult HR recorder design was prototyped by implementing all of the digital circuitry onto a single FPGA. Circuit diagrams of the FPGA based recorder are presented, together with a description of the instrument's operation. This is followed by a results section which includes HR recordings both at rest and during exercise.

The work involved in the design and realisation of a mixed analogue and digital ASIC for use in various long term ambulatory recorders of electrophysiological signals is contained in Chapter 4. Justification is given for selecting the ES2 foundry via the Solo1400 CAD tool, highlighting the importance of the Eurochip scheme in this decision. A description of the operation of the ASIC including the design of a dual slope integrating ADC is followed by a section on designing the ES2 ASIC using Solo1400.

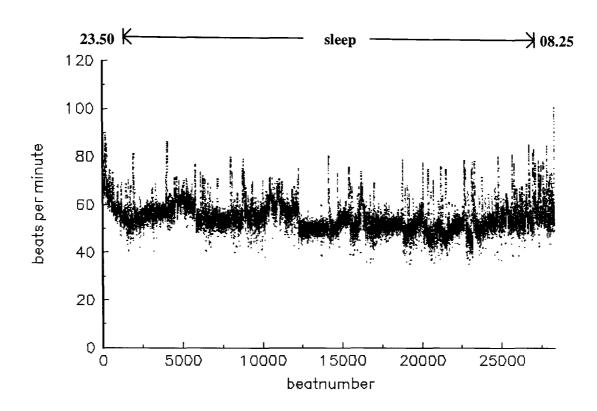

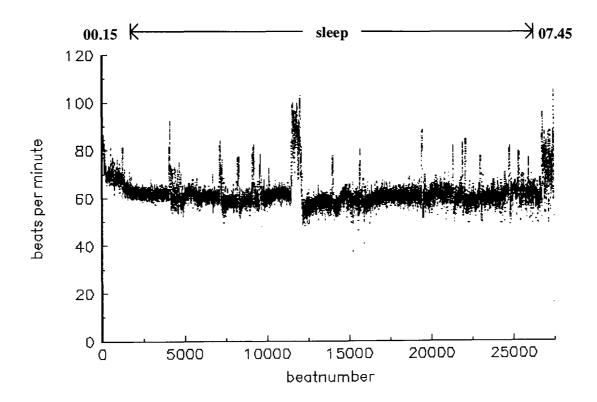

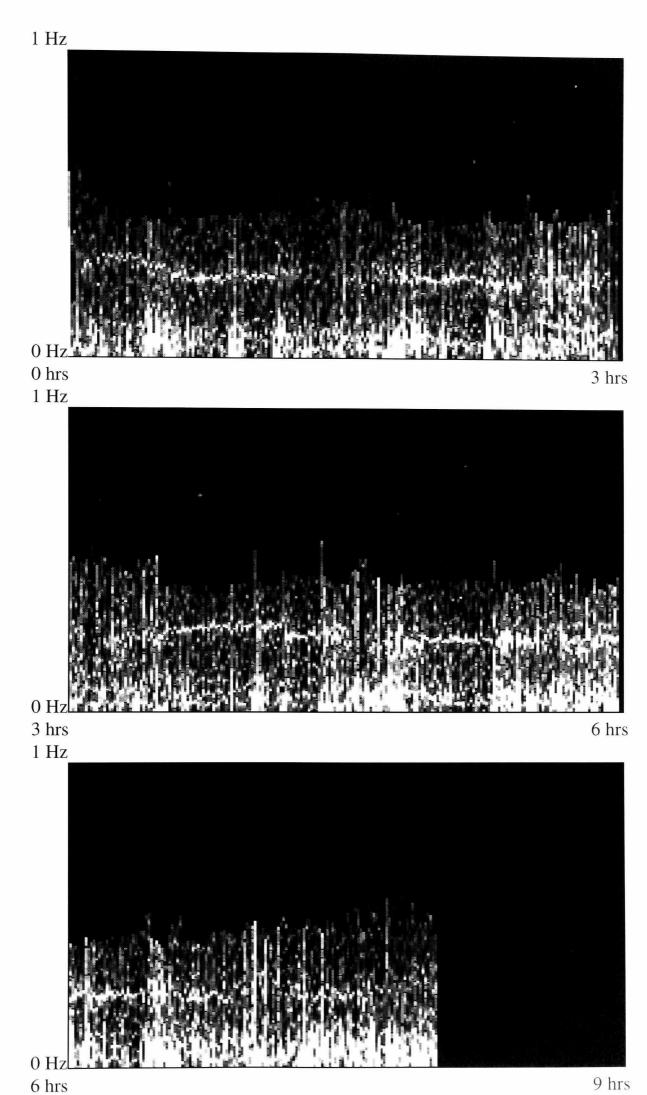

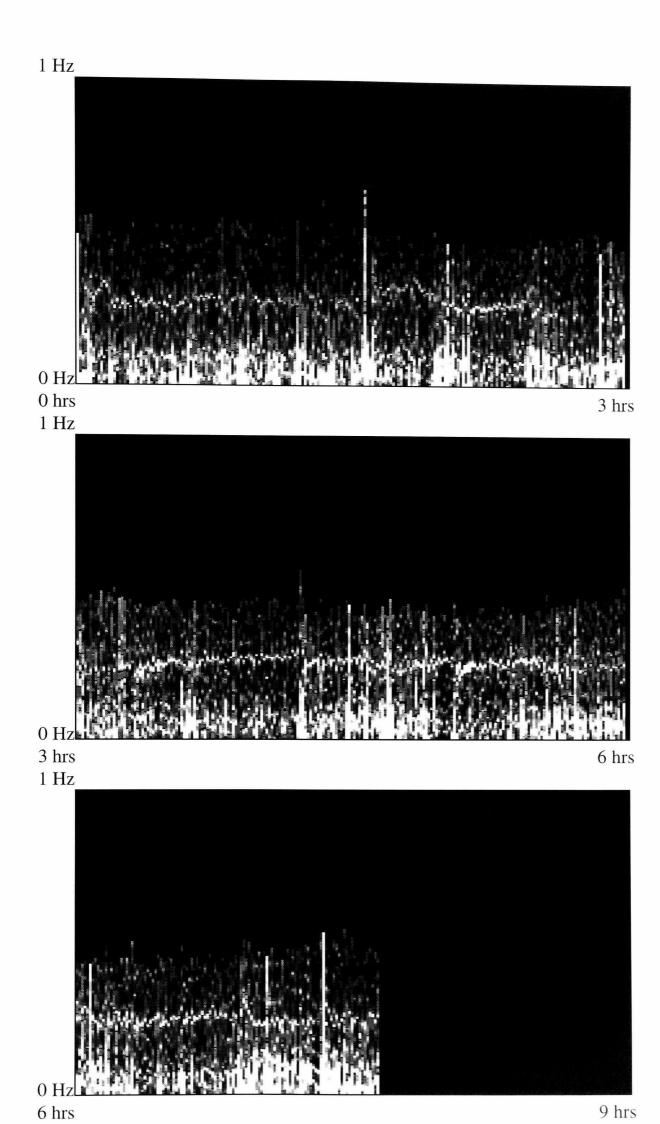

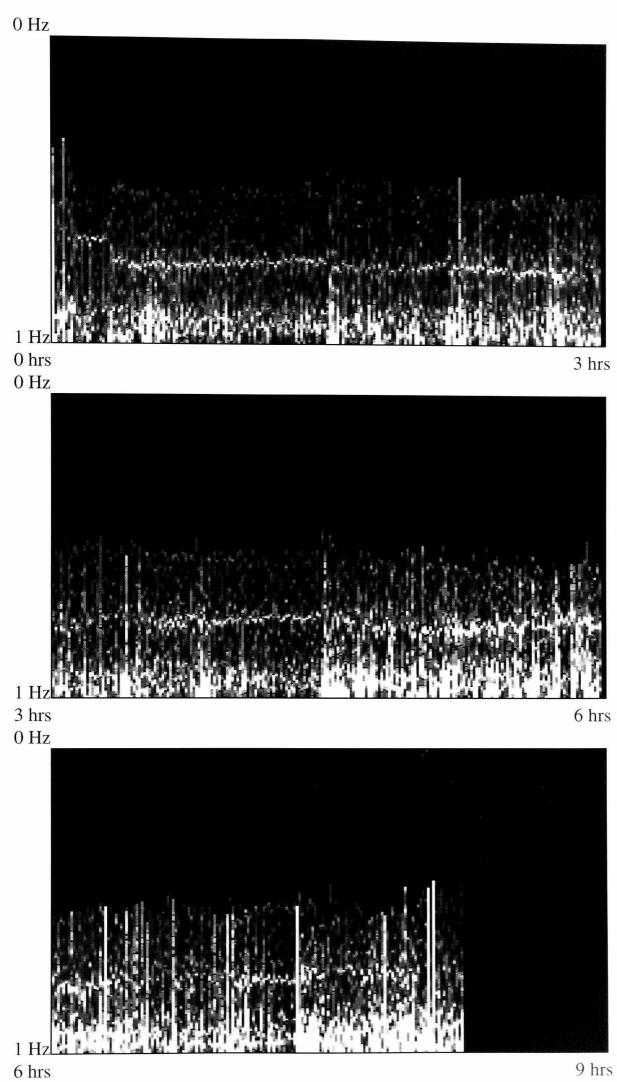

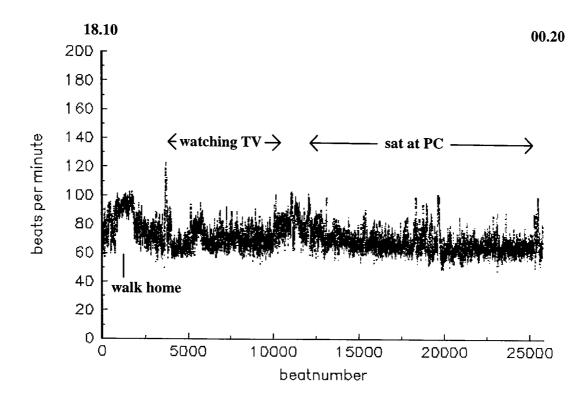

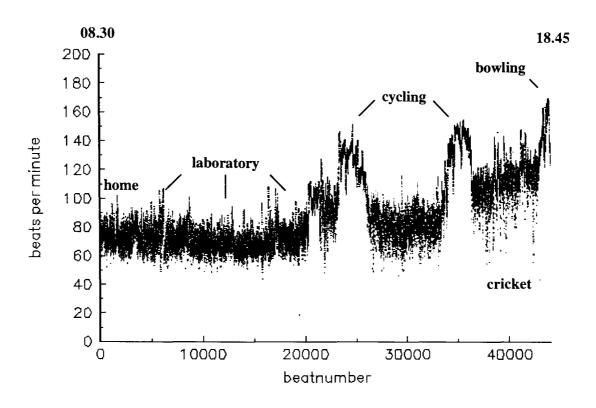

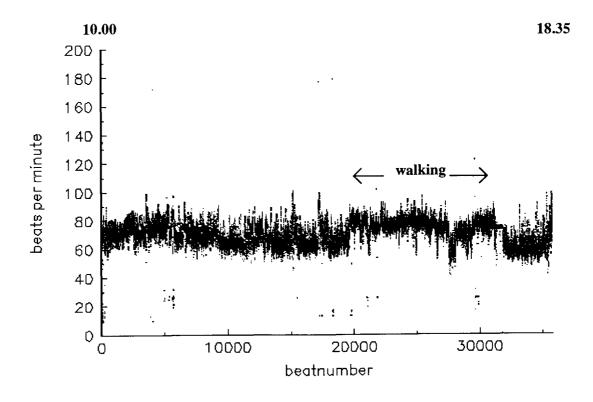

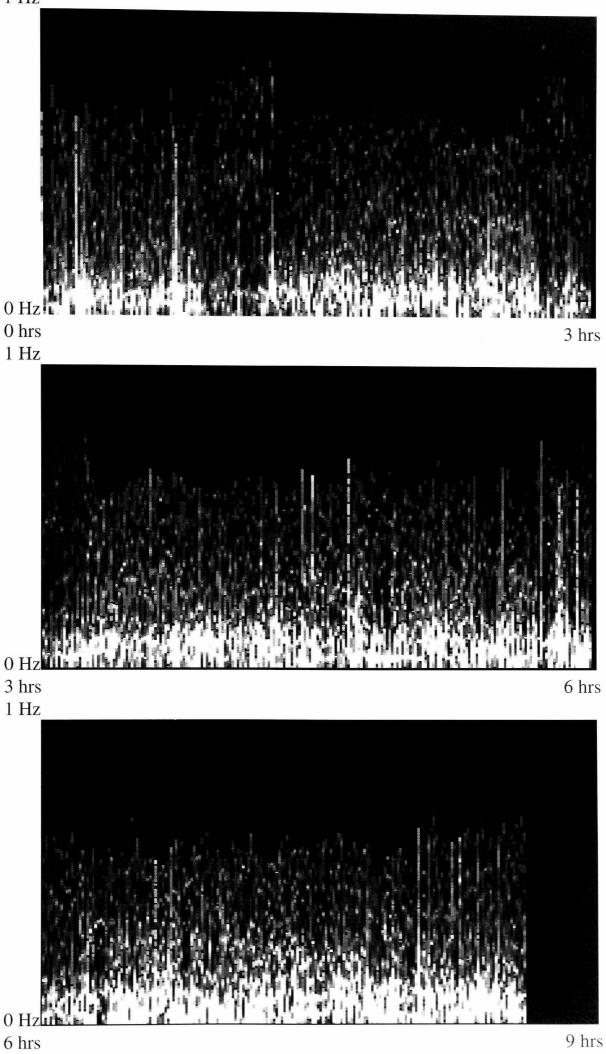

In Chapter 5 the design of an ambulatory adult HR recorder based on the ES2 ASIC is described (mode 1). Details of the improvements made to the FPGA version, which have been incorporated into the ASIC based instrument, are presented. Results obtained with this instrument include long term recording of daily beat-to-beat HR, HR during sleep and HR during exercise. The 0.3 Hz component of HRV which is associated with respiration [Sayers, 1973] is shown to be present in several recordings of HR during sleep.

Chapter 6 is concerned with the development of the general electrophysiological signal recorder based upon the ES2 ASIC (mode 2). A description of the recorder's operation is presented together with various circuits and system diagrams. Examples of some of the 119 abdominal FECG recordings made with this instrument are included, together with a selection of FHR and MHR traces extracted from these raw signals using a PC based software package.

Results of an initial investigation into the feasibility of monitoring uterine activity from abdominal electrodes are presented in Chapter 7. The signals obtained for this study were produced by the general electrophysiological signal recorder when configured as an EHG recorder.

Conclusions are contained in Chapter 8 together with suggestions for further work. Finally several appendices are included, giving guidelines on the electrical safety requirements of battery powered medical equipment, the reduction of noise and 50 Hz interference in biopotential amplifiers, plus a full set of ASIC schematic diagrams.

#### **CHAPTER 2**

# INTRODUCTION TO ASIC TECHNOLOGY

#### 2.1. Introduction

This chapter provides a brief introduction to application specific integrated circuit (ASIC) technology, including the advantages of ASICs and a description of the various types of ASICs that are currently available. An introduction to field programmable gate array (FPGA) technology is also included, highlighting the relative merits of these devices, in comparison to discrete ICs, as well as more conventional mask ASICs.

An ASIC is produced by the integration of an electronic circuit on to a single custom IC. The first generation of custom ICs became available around 1960 and were fabricated using small scale integration (SSI). These SSI devices were limited to a few simple logic gates requiring of the order of 10 transistors. By 1970, reductions in the minimum feature size and increasing silicon areas led to medium scale integration (MSI). MSI devices contain in the region of 1,000 transistors, enough to realise more complex circuitry such as adders and counters. The first large scale integration (LSI) circuits appeared around 1980 and were capable of integrating more than 10,000 transistors onto a single IC. The latest level of integration is referred to as very large scale integration (VLSI) and strictly refers to ICs containing over 100,000 transistors. VLSI processes capable of sub-micron feature sizes have facilitated the integration of whole microcomputer processors, containing millions of transistors, on to a single IC. It has now become common practice to refer to any ASIC design which is realised using state-of-the-art custom IC techniques as a VLSI design, even if it contains far fewer than 100,000 transistors.

#### 2.2. Advantages of ASICs

The advantages of applying VLSI technology to the design of a battery powered ambulatory recorder are a reduction in the overall size and power consumption of the instrument leading to a more portable design capable of longer recording times. ASIC technology can also lead to increased reliability, due to a reduction in the number of soldered joints and components needed. In addition, from a commercial viewpoint, a higher level of design security is achieved with an ASIC, since a VLSI design is virtually impossible to copy.

#### 2.3. Custom IC design

A custom IC or ASIC is simply an IC designed for a specific application. This may be an exclusively digital or analogue IC or alternatively a mixed ASIC, which will contain both. ASICs can be designed using any of the following methods. Full custom design, as the name implies, means the designer has the option of designing the whole chip, down to the transistor level, exactly as required. The next level, standard cell design, presents the designer with a clean slice of silicon but provides standard cells (e.g. gates, flip-flops, counters, opamps etc.) which can be automatically placed and routed (connected together) on the chip as required. Both of these levels of design complexity are used for analogue and digital design, and are characterised by long development times and high prototyping costs. One method of reducing prototyping costs involves the merging of designs to form a multi-project wafer (MPW) [Haskard, 1990]. This technique allows several different circuits to be implemented simultaneously on a single wafer, resulting in shared processing costs.

A less complex, and hence cheaper option is a gate array design. Here the designer has no input into the placing of gates on the IC, but is presented with a "sea" of universal logic gates, and has only to determine how these gates are

to be connected. Gate array design routes are at present only available for digital designs.

Until the late 1980s the cheapest route to a digital ASIC was via the use of a mask programmable gate array. The operation of these devices is determined by the final layer of the production mask which is provided by the designer. These mask programmable (gate array) ASICs are still available but since the late 1980s have had to face strong competition from field programmable digital ASICs or FPGAs as they are known.

#### 2.4. Introduction to FPGA technology

FPGAs allow digital circuitry to be integrated onto a single device without the long time penalty incurred with mask programmable ASICs. With FPGAs, the chip is not only designed on a PC or workstation but then also "fabricated" (i.e. programmed) using a device similar to an Erasable Programmable Read Only Memory (EPROM) programmer, connected via a card to the computer [Weste and Eshraghian, 1993]. The programming is achieved via either fuses or memory cells. In addition to this, the relatively low cost of FPGAs at low volume, compared to mask programmable ASICs make them an excellent prototyping option.

At present FPGA performance is still below that of certain mask programmable ASICs which continue to have an advantage when any of high performance (high speed, lower power consumption), high gate density or large volume runs are required. At the moment, all the FPGA devices on the market are of a purely digital nature.

#### **CHAPTER 3**

#### ADULT HR RECORDER USING AN FPGA

#### 3.1. Introduction

This chapter describes how the adult heart rate (HR) recorder design was prototyped by implementing all of the digital circuitry onto a single field programmable gate array (FPGA). Circuit diagrams of the FPGA based recorder are presented together with a description of the instrument's operation. This is followed by a results section which includes HR recordings both at rest and during exercise. The chapter begins by introducing the electrocardiogram (ECG), HR and commercially available instruments for measuring HR

#### **3.1.1. The ECG**

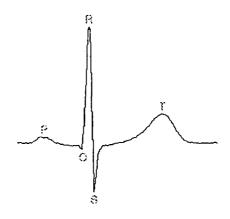

The ECG is the electrophysiological signal produced by the electrical activity of the heart, a small proportion of which propagates all the way to the surface of the body. This electrical activity results from a process of electrical depolarisation and repolarisation of the surface membrane of the cardiac muscle cells. Depolarisation begins in the sino atrial node of the right atrium and spreads via the A-V (atrial-ventricular) node through the A-V bundle to the ventricles. The normal ECG is composed of a P wave, a QRS complex and a T wave (Figure 3.1). The P wave is caused by the depolarisation of the atria, the QRS complex by the depolarisation of the ventricles and the T wave by the repolarisation of the ventricles.

Figure 3.1: The Electrocardiogram.

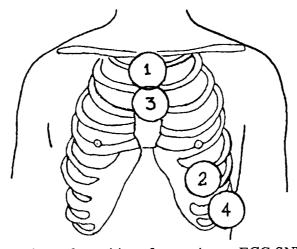

Analysis of the ECG is a standard procedure in the diagnosis of myocardial infarction and other cardiac diseases such as electrical conduction defects [Guyton, 1991]. The size and shape of the ECG is heavily dependent upon electrode position. For diagnostic applications ECG recordings are made from a standard 12 lead configuration [Thakor, 1988]. Most lead configurations will give an ECG amplitude of between 1 and 5 mV (R-peak height), provided the electrodes are placed on either side of the heart. Thakor and Webster (1985) investigated the optimum electrode position of a single channel ECG in terms of maximising the signal (QRS complex) to noise (artefact) ratio (SNR) and suggested two possible pairs of locations (Figure 3.2); manubrium-left midclavicular / 7<sup>th</sup> rib (1 and 2) and midsternum-left axillary / 9<sup>th</sup> rib (3 and 4), both of which are thoracic equivalents of the standard Einthoven lead II. Maximising the ECG SNR is of particularly importance in Holter monitoring due to the increased physiological interference caused by patient movements.

Figure 3.2: Optimum electrode positions for maximum ECG SNR [Thakor, 1984].

#### 3.1.2. Heart rate

Instantaneous beat-to-beat HR in beats per minute (BPM) can be determined easily from the ECG as it is the reciprocal of the time interval in seconds between two successive heart beats multiplied by 60. The reference point for a heart beat is generally taken to be the peak of the R-wave as this is the most distinguishable component of an ECG.

#### 3.1.2.1. Clinical importance of HR

Abnormal heart rhythms are known as cardiac arrhythmias. A fast HR (>100 BPM) is known as "tachycardia" and can be caused by increased body temperature, stimulation of the heart by the sympathetic nerves or toxic conditions of the heart. A slow heart rate (<60 BPM) is known as "bradycardia" and can be caused by stimulation of the parasympathetic nerves.

The amount of variability in beat-to-beat HR can be an indicator of the health of the heart. Decreased heart rate variability (HRV) can be a sign of severe coronary artery disease, heart failure, ageing or diabetic neuropathy [Kleiger et al., 1987], [Murray et al., 1975]. HRV, also known as sinus arrhythmia, can result from any one of many circulatory reflexes, or other nervous effects, that alter the strength of the sympathetic and parasympathetic nerve signals to the sinus node. Calculation of the P-P interval is the most direct method of investigating sinus arrhythmia. However, the relatively small P-wave can often be swamped by muscle noise, causing its detection to become unreliable. For this reason, the calculation of R-R interval is accepted as the standard method of investigating HRV. Any errors introduced by using R-R, rather than P-P interval tend to be minimal, as in general the P-R interval does not vary significantly from beat-to-beat [Kitney and Rompelman, 1987].

The study of HRV has also been shown to give information about various biological control functions of the body, such as respiration, thermoregulation and blood pressure [Sayers, 1973]. HRV has also been investigated as a predictor of long-term survival after Acute Myocardial Infarction (AMI) [Kleiger et al., 1987].

#### 3.1.2.2. HR in sports and exercise

The measurement of HR has also been applied to the field of sport and exercise. In recent years it has become common for athletes to monitor HR during training sessions. This is particularly true of long distance runners, cyclists and swimmers who wish to increase their aerobic efficiency, by exercising at just below their anaerobic threshold. Conconi et al., (1982) demonstrated the relationship between HR, running speed and blood lactate levels in runners showing how anaerobic activity may be monitored noninvasively by measuring HR, although the results of this work have since been challenged [Trowbridge, 1992].

#### 3.1.3. Commercially available HR monitors

The growing interest in measuring HR during exercise has lead to a large increase in commercially available HR monitors [Creative Health Products, commercial communication, 1991]. These instruments are usually worn on the wrist and display HR in BPM, with readings being updated approximately every 5 seconds. HR is obtained by either detecting the ECG in the chest or the hand area, or by detecting the pulse in the ear lobe or finger, using an infrared sensor [Creative Health Products, commercial communication, 1991]. The systems which detect the ECG from the chest area are the most accurate and reliable. This type of monitor detects the ECG using a chest band which contains two conductive electrode pads with a separation of around 150 mm. It

is recommended that these conductive pads are first wetted before the band is strapped horizontally around the chest, just below the nipples.

The HR information is either transmitted to the display using direct wires or with telemetry. A basic wrist watch style HR monitor can be purchased for less than £30. More advanced, and hence more expensive, monitors have the additional capability of storing HR at various intervals (5,30,60 secs), over several hours. Once the exercise session is complete the HR data can be downloaded via a computer interface to a PC for display and analysis. None of these sports orientated instruments either display or record HR on a beat-to-beat basis as athletes are not interested in HRV but rather in the underlying HR trends. Furthermore, it is desirable in sports applications, that HR readings remain constant for at least a couple of seconds, rather than being continuously updated.

Commercially available Holter monitors record 24 hours of continuous beat-to-beat HR. In these instruments R-R interval values are calculated digitally from ECG signals sampled at 128 Hz [Pinna et al., 1994]. This sampling frequency results in an R-R interval accuracy of +/- 3.9 ms, which relates to around +/- 0.25 BPM, at 60 BPM. This method is instantaneous, contains no averaging, and therefore does not smooth the results. The major disadvantage in using this method compared to averaging methods, is the increased amount of memory required to store HR continuously for 24 hours. Again, assuming an average HR of 60 BPM and an 8 bit R-R interval resolution, this would require 128 kbytes of RAM.

#### 3.2. Description of FPGA based HR recorder

An Actel FPGA [Actel, 1993] designed using the Viewlogic computer aided design (CAD) package [Viewlogic, 1991], was used to prototype the digital

circuitry of the adult HR recorder design. This design measures continuous beat-to-beat HR by calculating the R-R interval of the ECG.

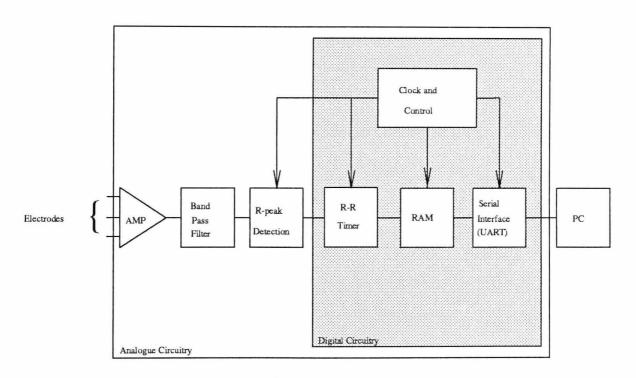

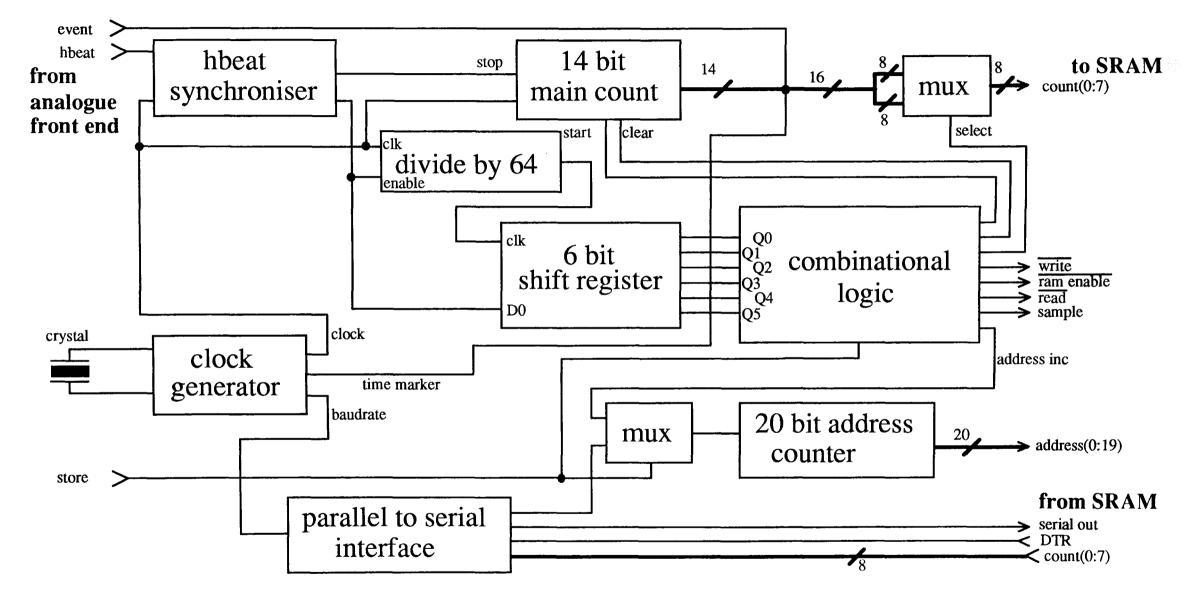

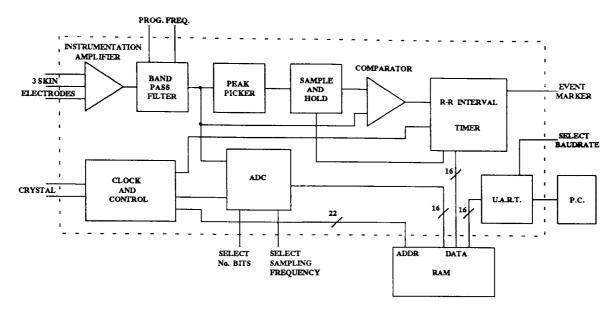

A block diagram of the FPGA based recorder is shown in Figure 3.3 which can be considered in two sections, namely analogue and digital. The analogue circuitry is used to detect the R-peak of the QRS complexes in the ECG, with the corresponding R-R intervals then timed and recorded by the digital section. This data, stored in static RAM (SRAM), can then be subsequently downloaded to a PC, via its serial port, over an RS-232 interface, for display and analysis. The analogue and digital circuits will now be described in more detail.

Figure 3.3: FPGA based HR recorder block diagram.

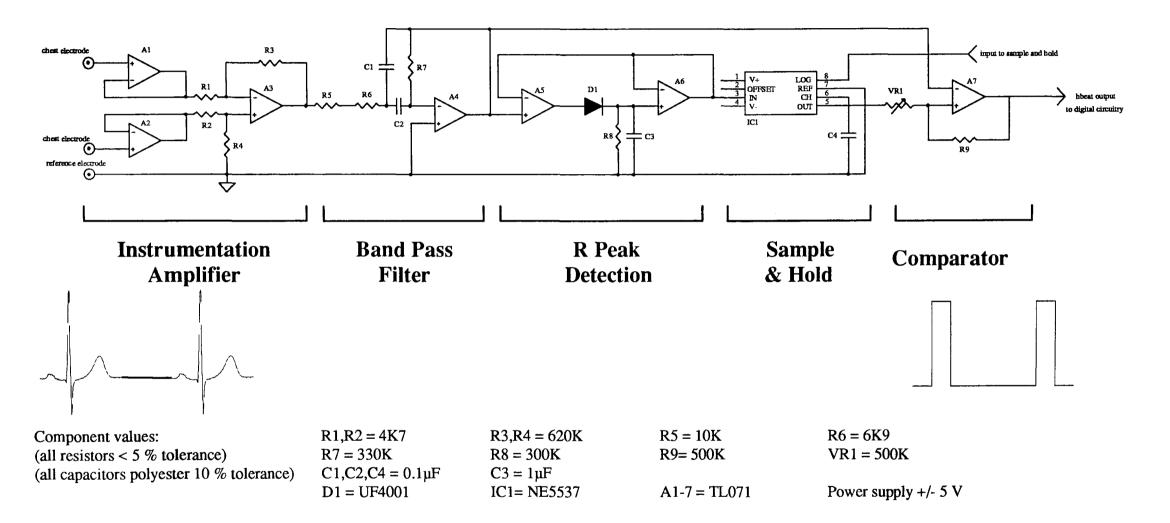

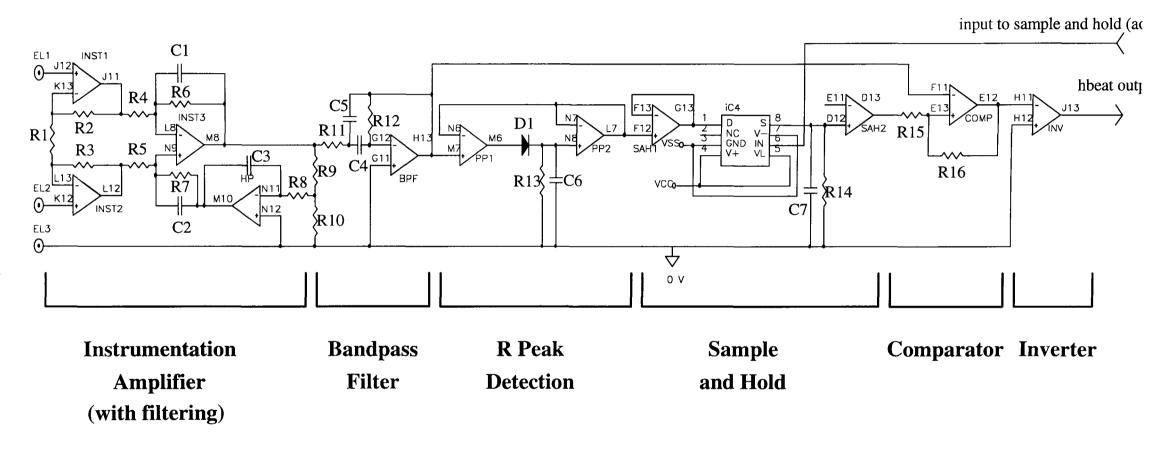

#### 3.2.1. Analogue front end circuitry

Figure 3.4 shows the analogue front end of the instrument. Two chest electrodes are used to detect the ECG which is amplified and band-pass filtered to reject baseline drift, 50 Hz interference and high frequency noise. R-peaks are then detected via an adaptive thresholding technique, in which the incoming signal is compared with approximately 70% of the last R-peak value. The

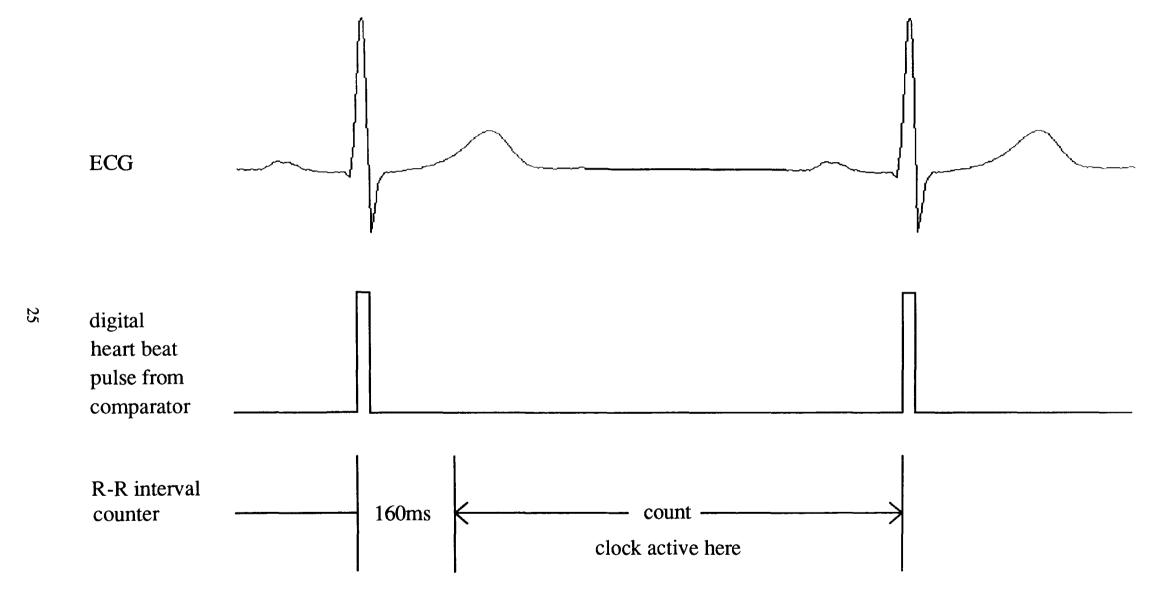

reference voltage used is obtained by sampling and holding the ECG signal, at a fixed time interval after the R-peak. This results in a reference signal being stored of about 70% of the last R-peak, which can then be used to threshold the incoming signal, and so determine the next R wave occurrence. This technique will result in a maximum error of around 4 ms, if the R-peak amplitude changes dramatically between successive beats. However, given that the R wave amplitude is usually constant, the error in the R-R interval will typically be about 1 ms. The comparator used to compare the threshold with the incoming signal serves to produce a pulse. This pulse is then used as the input to the digital circuitry, that is activated on the positive edge. Both the input ECG and the resulting output from the comparator are shown in Figure 3.5.

#### 3.2.2. Digital FPGA circuitry

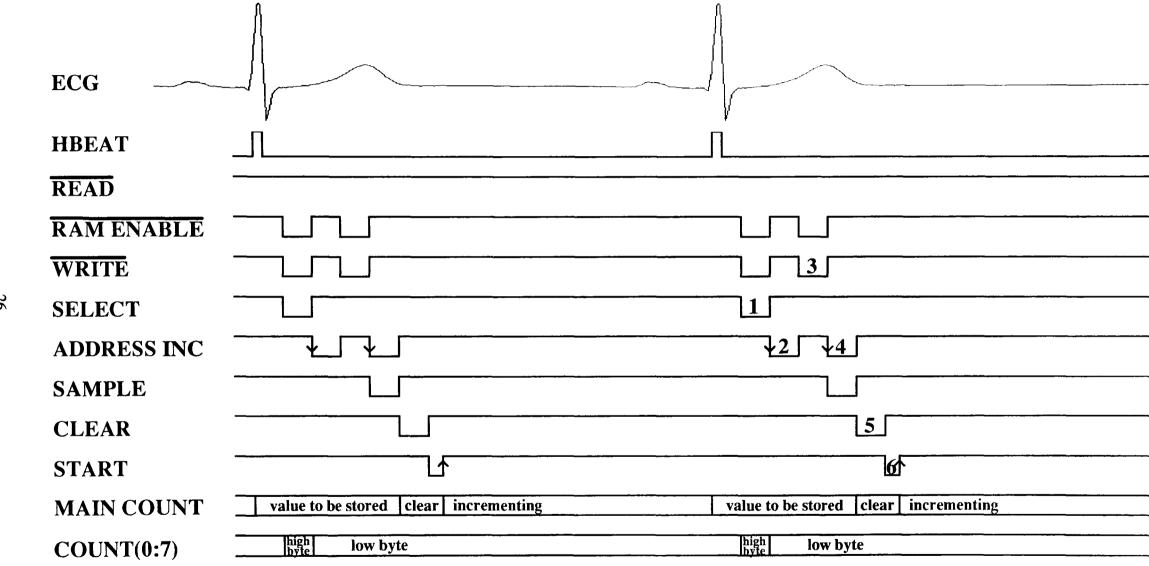

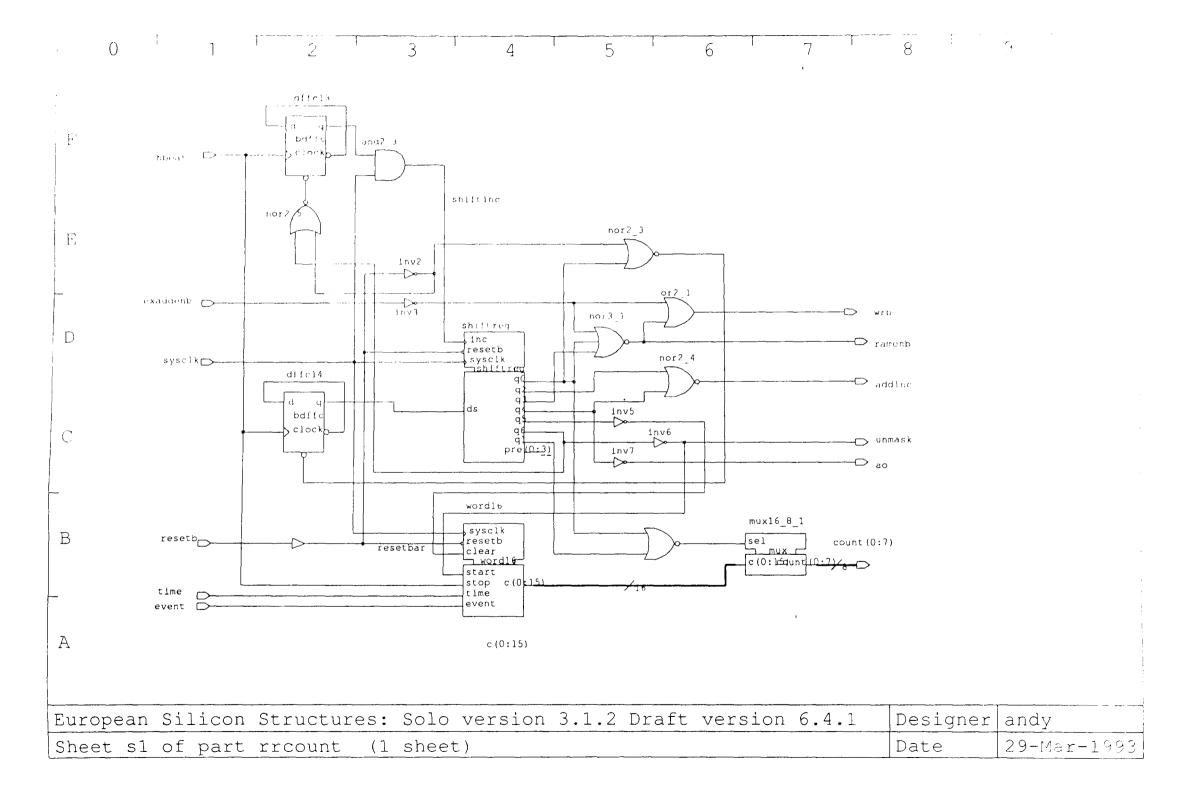

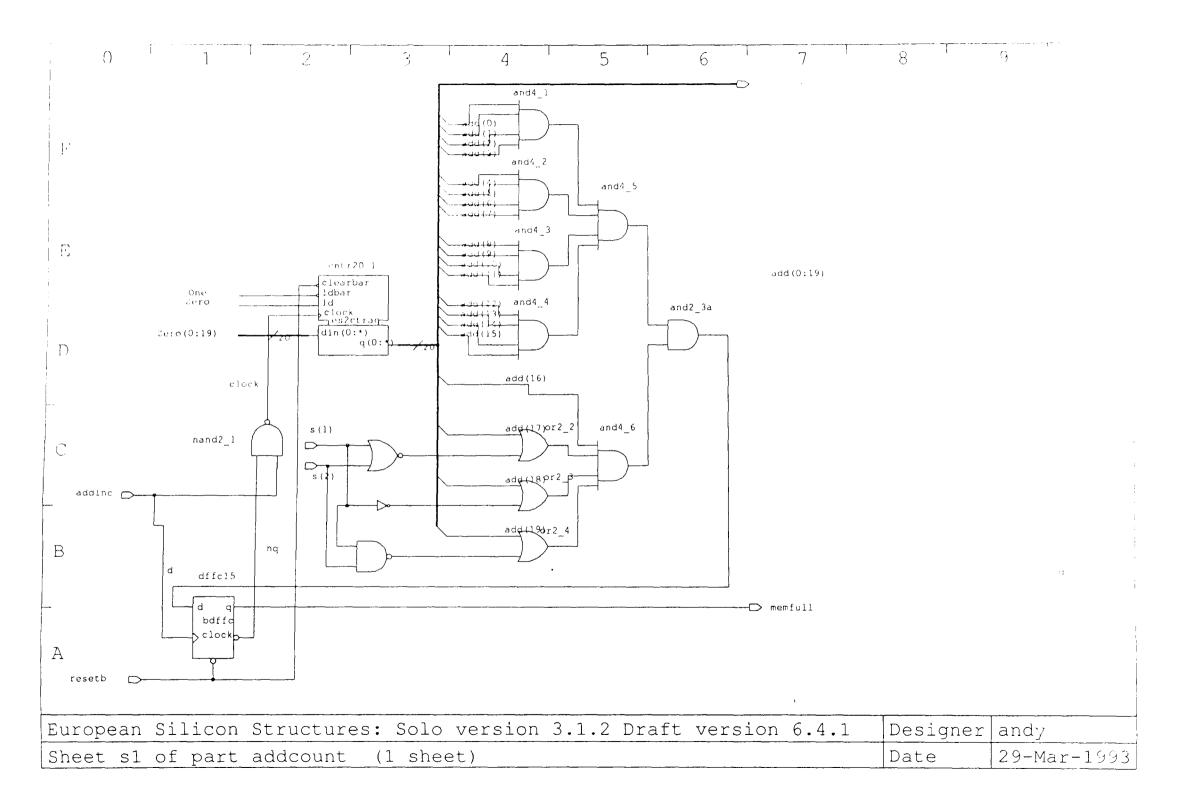

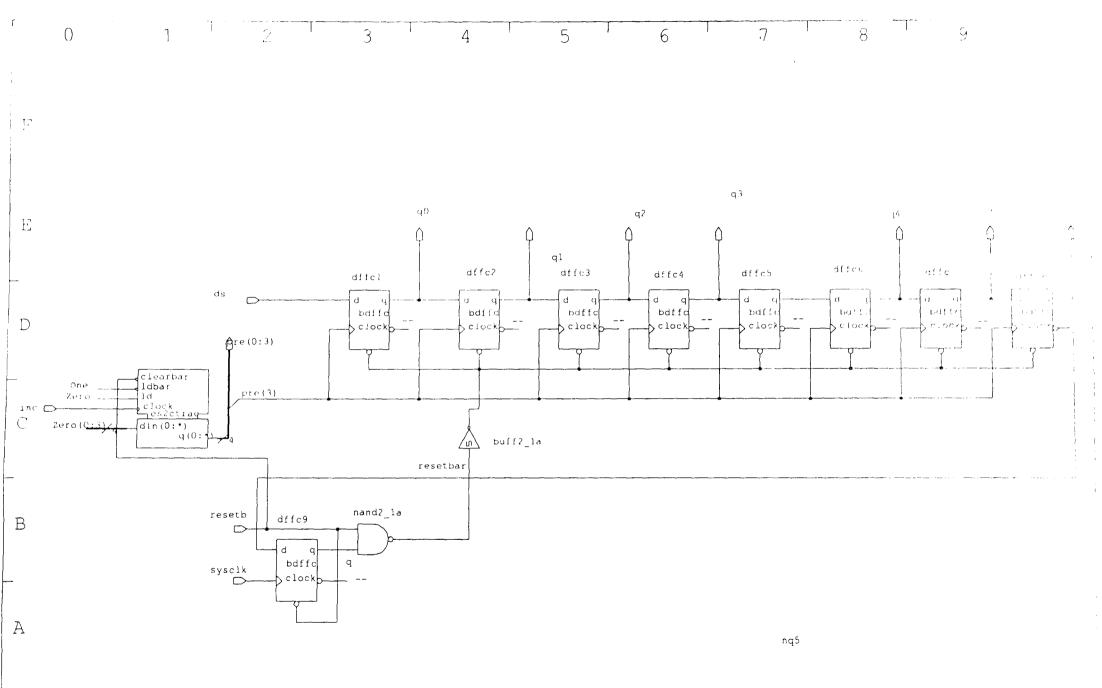

The R-R interval timer logic calculates the time between successive R-peaks and stores this value into a 128K by 8 bit SRAM. This is achieved by simply counting the number of system clock cycles within each R-R interval. The count is performed in two stages: firstly, a fixed period (i.e. a set number of clock cycles are counted) and secondly, the time between the end of this fixed period and the next R-wave (main count). It is the latter that is stored in memory. This technique allows a smaller counter to be used without compromising accuracy. The sequence of events are shown as a timing diagram in Figure 3.6 and the corresponding digital circuitry is shown in Figure 3.7. During the fixed count the previous variable count value is written to RAM and the main count is reset to zero.

A clock frequency of 2.4 kHz is used with the fixed count comprising 384 clock cycles (160 ms). A 14 bit counter is used to record the second variable count, giving a (theoretical) range of R-R intervals from 160 ms (i.e. a count of

zero) to 7 s, with a resolution of 0.42 ms (although this does not fix the overall accuracy of the recorder which will be primarily dependent on the analogue processing as described earlier). R-R intervals of 7 s are obviously not expected, but allowing for such values means the failure to detect several R-waves within otherwise valid data becomes clear upon inspection of the record. The R-R-interval data is stored in 16 bit memory as two bytes. The two bits not holding the count are used as timing and event markers.

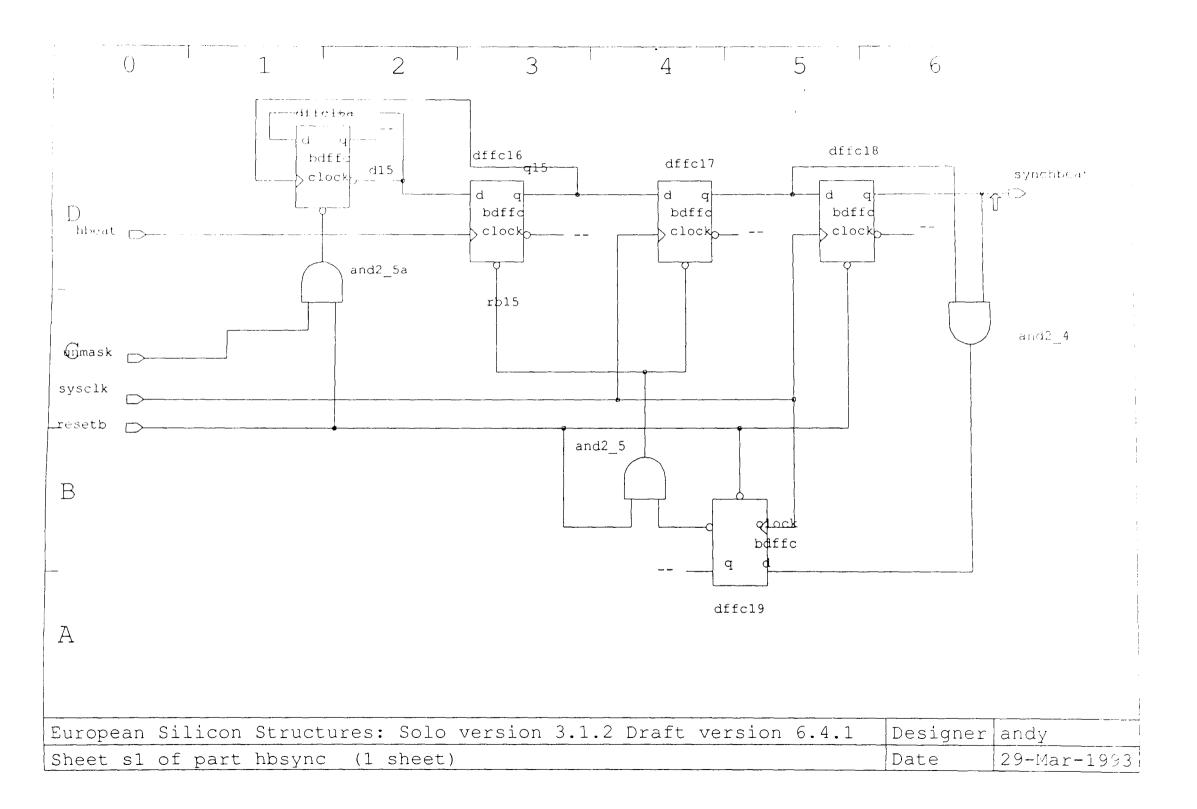

Since the pulses produced by the analogue circuit are asynchronous with the system clock, the first task is to achieve synchronisation, hence a heart beat synchroniser is shown in Figure 3.7. This signal is then used to stop the main 14 bit count and load a "1" into the 6 bit shift register. This shift register is clocked by the system clock, divided down by 64, during the 160 ms of the fixed count. The 6 outputs from this shift register, (Q0-Q5) which sequentially go high, are passed to a combinational logic circuit whose outputs are used to control:-

- 1. The resetting of the shift register input to zero and writing the high byte of the count to RAM

- 2. Incrementing of the RAM address

- 3. Writing the low byte (containing the remaining 6 bits of the count plus timing and event markers) to RAM.

- 4. Incrementing the RAM address and activating the sample and hold circuit used to record the R-peak amplitude.

- 5. Resetting the main 14 bit counter.

- 6. Halting the fixed count and initiating the variable main count.

The 14 bit output of the main count is tagged with time and event markers. If the event button has been pressed during the previous R-R interval a '1' is

latched into the 16th bit of the R-R interval count. Similarly a time marker is latched into the 15th bit every 14.56 minutes ( $2^{21}$  clock cycles).

Every time an R-peak is detected 14 bits of R-R interval data plus two bits for time and event markers are stored in two bytes of a 128 K x 8 bit SRAM. This memory capacity will allow almost 18 hours of continuous R-R data to be stored given an average heart rate of 60 BPM. Once recording is completed the stored data is transferred from SRAM to a PC for further analysis. This is achieved by reading in parallel R-R data from the SRAM to the FPGA, one byte at a time, converting it from parallel to serial RS-232 format, and then transmitting it serially to a PC via a MAX232 driver. This downloading process is controlled by a C program running on the PC. When the PC is ready to receive data the Data Terminal Ready (DTR) pin of the serial port is toggled and the FPGA begins transmitting data. Once all the data has been transmitted the information is saved on the hard disk of the PC for further analysis.

Figure 3.4: Analogue front end circuitry.

Figure 3.5: Two stages of the R-R interval count.

Figure 3.6: Timing diagram of R-R interval counter and interface to RAM.

Figure 3.7: Digital FPGA circuitry.

#### 3.3. Results

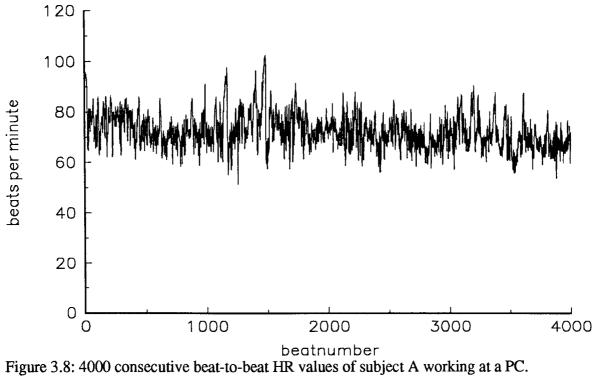

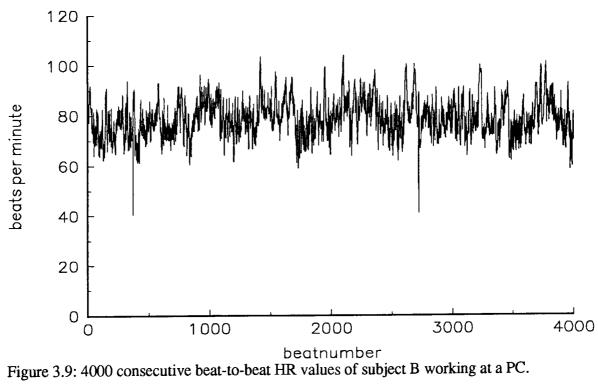

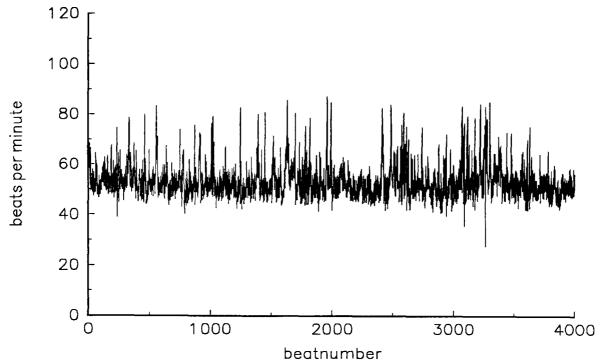

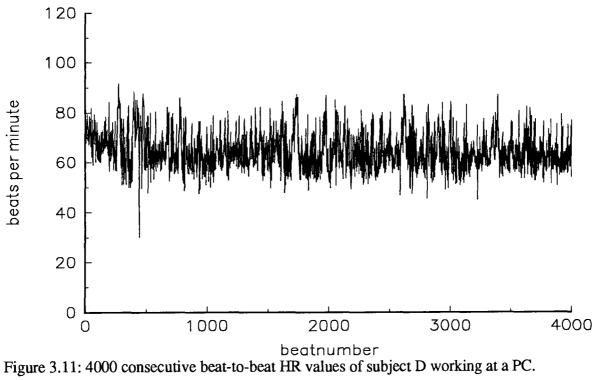

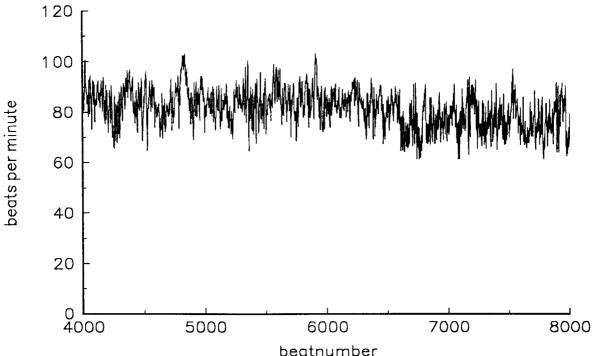

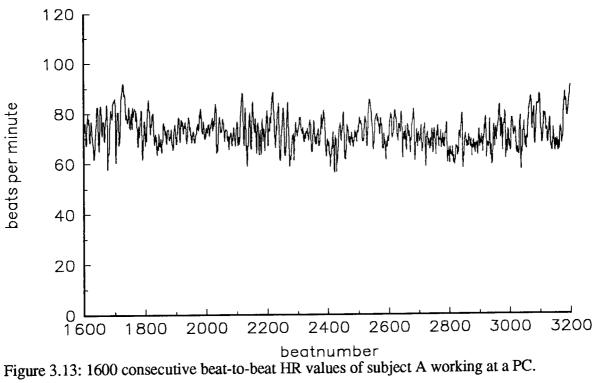

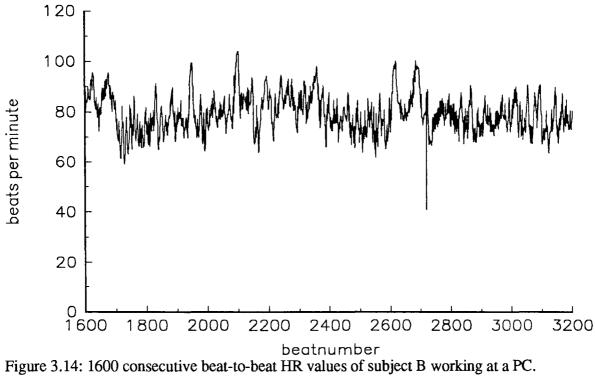

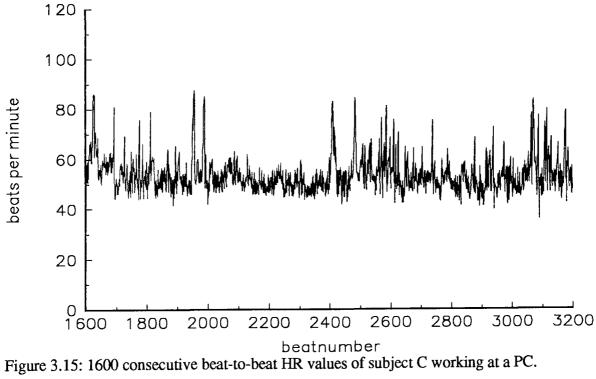

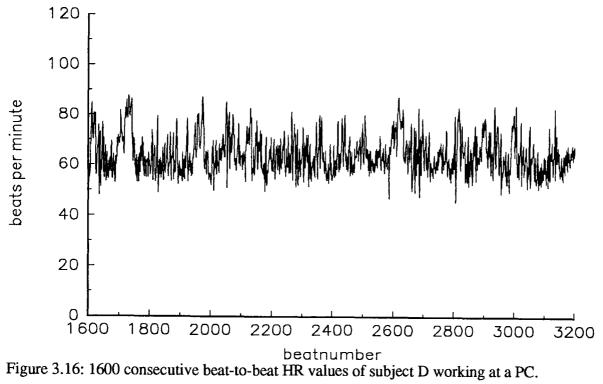

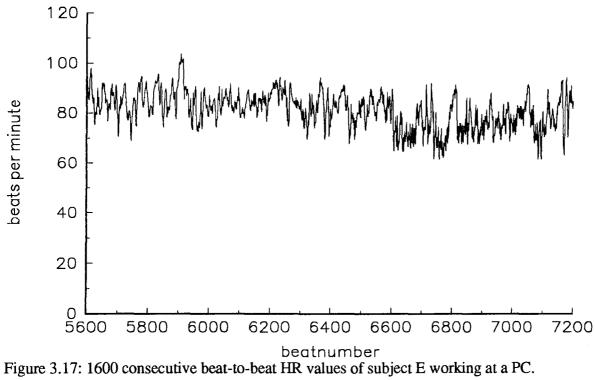

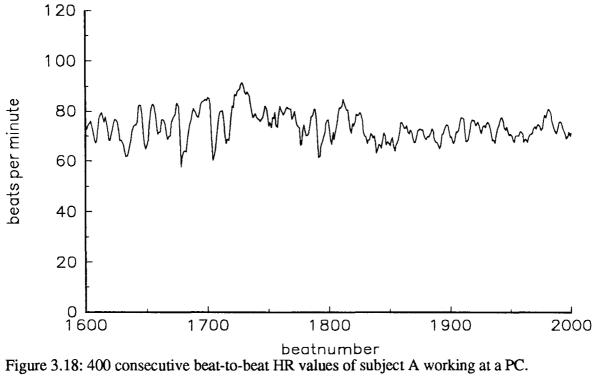

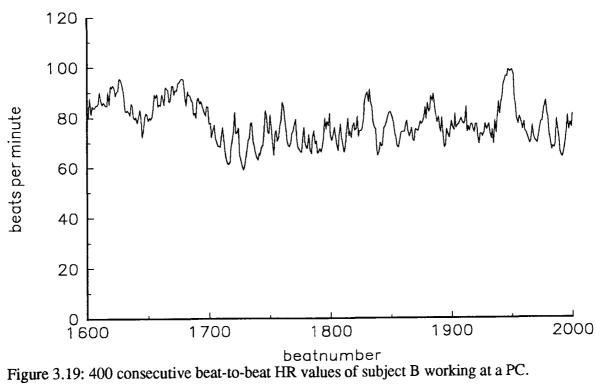

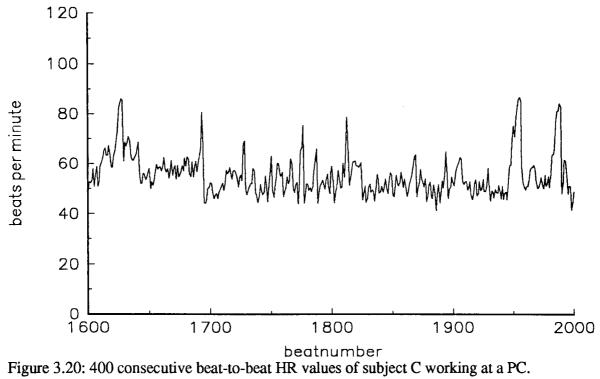

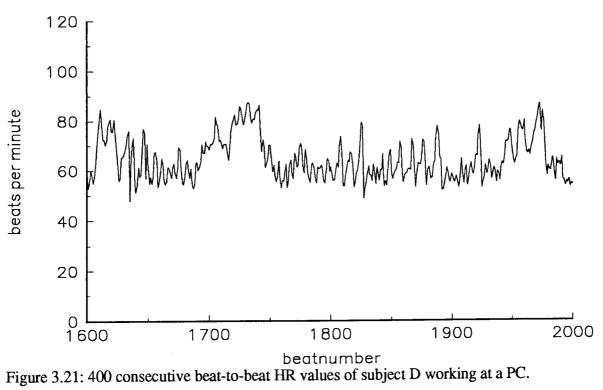

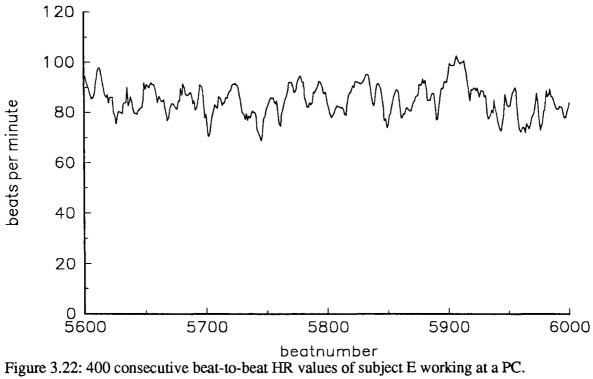

The FPGA based prototype of the adult HR recorder (see photograph in Appendix D) was used to record the HR of five different individuals (four males and one female aged 21 to 25). Each recording covers between 1 and 2 hours of the subject's typical daily working routine, which consists mainly of sitting at a computer terminal. Three disposable, foam-backed, silver-silver chloride, pre-gelled electrodes were used in all the HR recordings. Before attaching the electrodes, the subject's skin was prepared with an alcohol saturated swab and left to dry for around 5 minutes. The two differential input electrodes were positioned on the subject's chest as recommended by Thakor and Webster [Thakor and Webster, 1985]. The third 'common' electrode was placed on the subject's wrist. Extracts from the five recordings are shown below in Figures 3.8 to 3.12. In each case 4000 successive R-R intervals are displayed as beat-to-beat HR (in BPM) against beatnumber. Beatnumber can be converted into a true time axis by simply summing all the previous R-R intervals. However, problems can arise if the recording contains several successive missed beats or false detections leading to an apparent R-R interval which is less than 160 ms or greater than 7 s.

The five recordings shown below contain a total of four missed beats and no false detections. This consists of two missed beats in Figure 3.9 and one missed beat in both Figures 3.10 and 3.11. A single missed beat will cause the HR to halve and is therefore easily detected in HR data which has been calculated on a beat-to-beat basis. A single false detection will result in successive HR values which will have an average value that is twice the underlying HR. These errors can be corrected at the expense of beat-to-beat information (in the case of missed beats). Such corrections would be much more difficult to achieve if the HR data had been calculated using some element of averaging. Figures 3.13 to

3.22 contain the HR data from the same five recordings displayed on a variety of beatnumber scales.

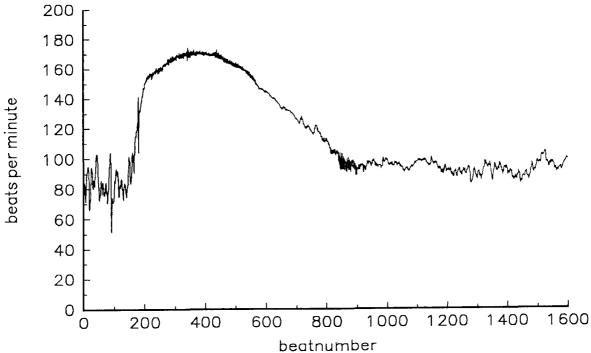

An example of a beat-to-beat HR trace during exercise is given in Figure 3.23. HR was recorded as the subject ran up 15 flights of stairs from the ground floor, stopped, caught the lift back to the 7<sup>th</sup> floor and then sat down to recover. The HR trace shows much variability in the form of accelerations and decelerations as the subject walked to the bottom of the stairs. As the subject begins to run up the stairs the HR accelerates sharply from around 80 BPM to 160 BPM and then slowly to a maximum of around 170 BPM. During this period the amount of variability in the HR is substantially reduced. Once the top of the stairs is reached, the HR begins to recover and more variability begins to appear in the HR trace. This reduction of HRV with exercise is a well known phenomena [Baselli et al., 1991].

beatnumber Figure 3.10: 4000 consecutive beat-to-beat HR values of subject C working at a PC.

beatnumber Figure 3.12: 4000 consecutive beat-to-beat HR values of subject E working at a PC.

beatnumber

Figure 3.23: 1600 consecutive beat-to-beat HR values of subject A running up 15 flights of stairs.

#### 3.4. Conclusions

The digital circuitry of the Adult HR recorder was successfully implemented using an Actel FPGA. This proved to be a neat and cost effective method of verifying the HR recorder design. The ability of the FPGA to integrate a large proportion of the circuitry onto a single device facilitated the development of a usable FPGA based prototype. This working prototype was used to successfully record the HR of several adults as well as to detect any design flaws. From these recordings it can be seen that the amount of HRV differs from individual to individual. Being able to test the HR design with a working prototype may have saved several design iterations which are an inevitable characteristic of an evolving design. The relative low cost of FPGAs and the ability of these devices to be programmed in the laboratory, allows design iterations to be made, without incurring the large financial and time penalties associated with resubmitting masked ASIC designs.

When the HR recorder design was migrated to the ES2 process (see Chapter 4), the success of the FPGA based prototype took the onus off the ASIC simulations. The HR recorder circuitry was transferred from the Actel FPGA design to the ES2 ASIC design, by simply re-entering the schematics. The successful operation of the FPGA based prototype HR recorder increased the likelihood of the ASIC based HR recorder circuitry being right first time.

The ability of FPGAs to implement the various circuits described in this thesis is limited by the purely digital nature of these devices. A mixed FPGA device containing a limited range of analogue components would prove to be a real alternative to masked ASICs for both circuit development and realisation of the final design, particularly if the power consumption could also be reduced.

# **CHAPTER 4**

# THE DESIGN OF A MIXED ANALOGUE AND DIGITAL ASIC

#### 4.1. Introduction

This chapter describes the work involved in the design and realisation of a mixed analogue and digital application specific integrated circuit (ASIC) for use in various ambulatory recorders of electrophysiological signals. Justification is given for selecting the European Silicon Structures (ES2) foundry via the Solo1400 computer aided design (CAD) tool, highlighting the importance of the Eurochip scheme in this decision

## 4.2. Overall ASIC design

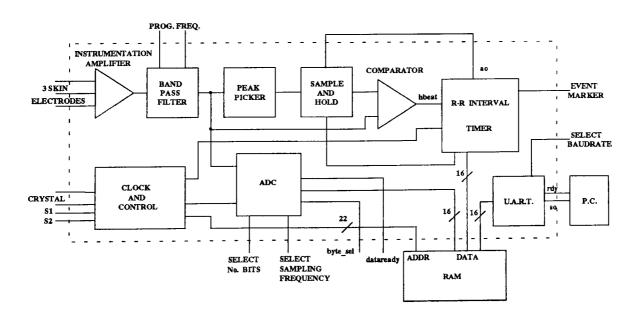

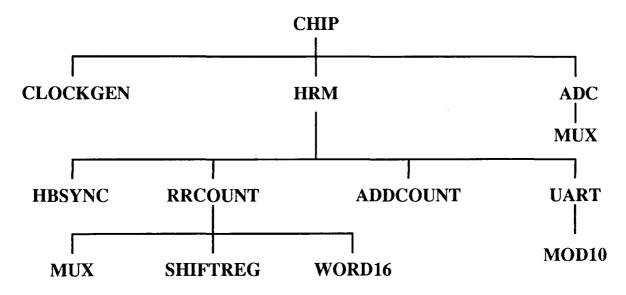

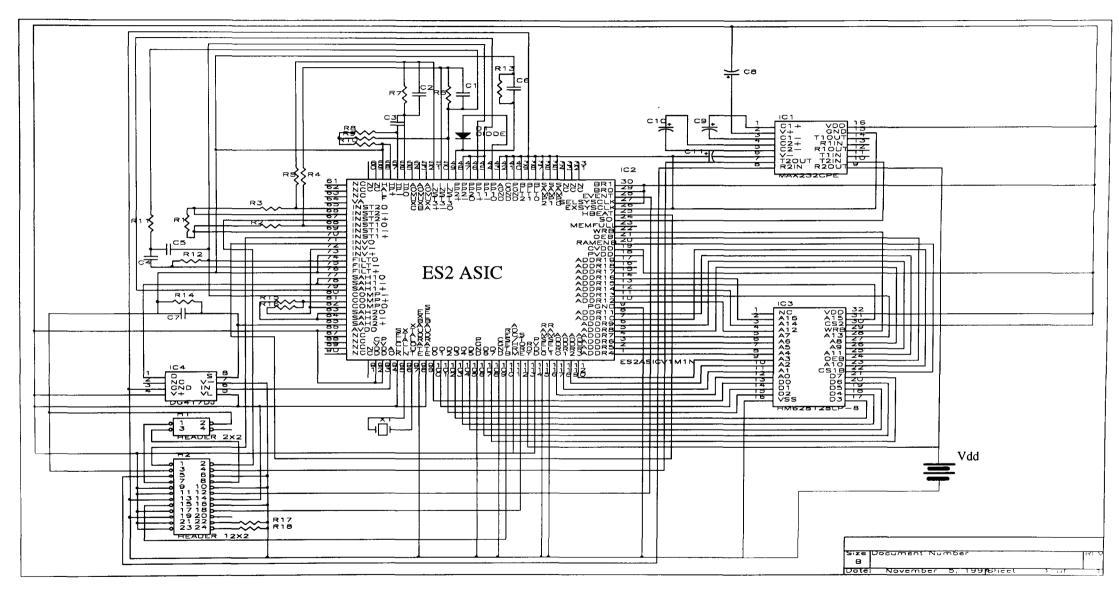

The final ASIC designed, contains all the components shown in Figure 4.1 apart from the RAM. The ASIC has two modes of operation, each mode being used as the basis for one of two different ambulatory recorder designs:

- 1) Adult heart rate (HR) recorder (Mode 1)

- 2) General electrophysiological signal recorder (Mode 2)

Similarities in the operation of these two recorder designs means that much of the ASIC circuitry is common to both instruments. This is particularly true for the analogue front end circuitry needed for signal conditioning and the digital circuitry used for interfacing with the serial port of a PC.

Figure 4.1: Overall ASIC design.

When configured as an adult HR recorder (Mode 1), the electrocardiogram (ECG), detected by skin electrodes on the chest, is amplified and filtered to enhance the R-wave, while suppressing baseline drift and high frequency noise. The combination of a peak picker, a sample and hold circuit and a comparator acts as an analogue R-peak detection scheme, which provides a digital rising edge to the R-R interval timer circuitry, every time an R-peak is detected. Successive R-R intervals are continuously stored in off-chip RAM until recording is complete, at which point the R-R interval data can be transferred, by the on-board universal asynchronous receiver transmitter (UART), to a PC, via its serial port.

When configured as a general electrophysiological signal recorder (Mode 2), the ASIC amplifies, filters and digitises the raw signal detected by the 3 skin electrodes. The gain and bandwidth of this signal conditioning circuitry is adjustable, as is the sampling frequency and resolution of the analogue to digital converter (ADC). This flexibility allows the instrument to be applied to a whole range of electrophysiological signals. The ASIC is designed so that the digitised signal can be either stored directly in off-chip RAM or first processed by an off-chip digital signal processor (DSP) (not shown in Figure 4.1.).

In the initial mode 2 recorder (without DSP), stored data is transferred to a PC, via its serial port, again using the on-board serial interface (UART). The clock and control circuitry controls the digital R-R interval timer circuitry, the sampling frequency of the ADC and the addressing of the external RAM. However, in the DSP based version of the mode 2 recorder both the addressing of the RAM and the downloading of data to a PC are controlled by the DSP.

# 4.3. Choosing a process and a CAD tool

Before the work on an ASIC design can begin it is important to choose an appropriate process and a suitable CAD tool. The process that is chosen will determine the method in which the circuit will be realised in silicon. Different process options have differing characteristics (full custom/standard cell/gate array, analogue/digital, on-chip resistors/capacitors), as well as different minimum feature sizes. The software packages (CAD tools) used to design ASICs vary greatly in complexity and capability. Some packages are generic, capable of full custom design and full analogue simulation, whereas others may be tied to a particular process and only be suitable for digital designs.

## 4.3.1. The Eurochip scheme

The cost of both CAD tools and fabrication can be expensive, often running into many thousands of pounds. One method of reducing the cost is to access the Eurochip scheme. Eurochip is a European initiative to provide low cost access to both processes and CAD tools, for academic institutions in the European Union. In addition, heavily discounted routes are also available to industry.

# **4.3.2. Process options**

The various process options available at the time were:

- 1. Mietec 2.4µm double metal, double poly, CMOS mixed analogue and digital Advantages:

- Analogue components in core of chip

- Double layer poly for accurate capacitors

- Full custom design possible

#### Disadvantages:

- Requires a more complex CAD tool (Mentor/Cadence)

- No accurate resistors

- No macros available for ADCs etc.

- No simulation models available for analogue cells (at the time)

- D-type flip flops with propagation delay less than hold time

- 2. ES2 1.5µm double metal, single poly, CMOS mainly digital standard cell Advantages

- Full custom design possible

- Macros available for ADCs(8 bit)

- Pseudo analogue simulation available in the digital environment

- Previous experience of using within the Department

- Analogue samples available

# Disadvantages

- Analogue components are located around the I/Os

- Unsure about the performance of the op-amps

- No resistors/capacitors available must be off chip

# 3. MCE 3µm mixed analogue and digital gate array

#### Advantages

- Small range of resistors and capacitors available

- Good range of analogue library (8 bit ADC)

- SPICE analogue models available

#### Disadvantages

- Gate array mainly

- No large digital macros i.e. multipliers

- Limited to less than 1000 digital gates

- Not part of Eurochip

## 4.3.3. CAD options

In addition to the selection of a suitable process, it is also necessary to chose a CAD package that is appropriate in terms of its complexity, capability and compatibility with the desired process. The various CAD package options available at the time were:

#### 1. Mentor Graphics

# Advantages:

- Good generic package

- Full custom capability

- Analogue simulation plus interface to SPICE

- Previous experience of using within the Department

#### Disadvantages

- Version 7 to version 8 transition bugs

- Poor Eurochip support

- Complex software package

#### 2. ES2 Solo1400

#### Advantages:

- Easy to learn, simple to use system

- Previous experience of using within the Department

- Good Eurochip support

- Designed specifically for the ES2 process

#### Disadvantages:

- Can only be used with the ES2 process

- No full custom design capability

- Only limited analogue simulations possible

#### 3. Cadence

# Advantages:

- Full custom design possible

- Good Eurochip support

## Disadvantages:

- No previous experience of using within Department

- Complex software package

# 4. MCE

#### Advantages:

- Good support from MCE

- Easy to learn, simple to use, PC based software

- Analogue simulation possible using SPICE

- Designed specifically for the MCE processes

#### Disadvantages:

- Can only be used with the MCE process

- No full custom CAD capability

# 4.3.4. Process and CAD selection

In choosing a suitable process and CAD tool, it is important to remember that for this project it was necessary to produce an ASIC as quickly and as cheaply as possible, which contained as much, if not all, of the analogue and digital circuitry required for both of the different recorder designs. Speed was important because sufficient time was needed for both laboratory based tests and clinical measurements to be taken.

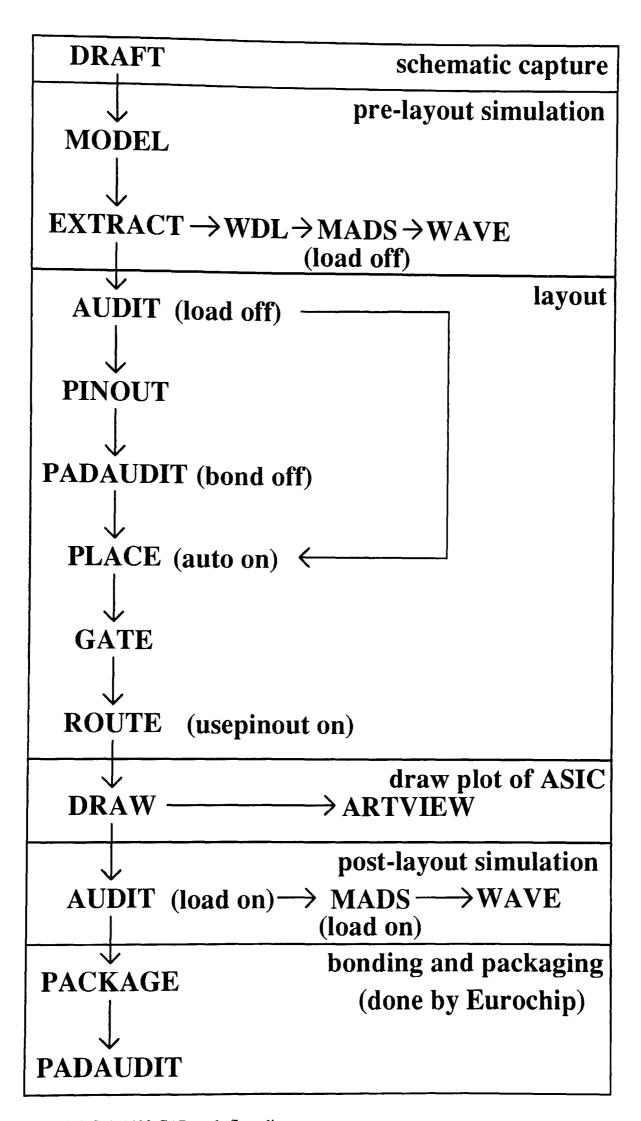

After considering all the options it was decided that the ASIC would be fabricated using the ES2 process via the Solo1400 CAD tool [ES2, 1991]. This tried and tested route uses an easy to learn, simple to use software package, with good Eurochip support, which has been specifically designed for use with the ES2 process. However, the lack of a full custom design capability (with Solo1400), restricts the ASIC circuitry to components which are available in the ES2 standard cell library, and the limited power of the analogue simulator, also restricts the complexity of any analogue simulations.

Although the ES2 1.5µm process is intended for purely digital designs, it does contain some analogue components in the standard cell library. Any analogue components which are used in a design are automatically placed by the software in the periphery of the ASIC, together with all the I/O pads. This has the disadvantage of increasing the periphery of the ASIC which tends to make designs which contain several analogue components, more likely to be pad limited. i.e. the area of silicon required for the design is determined by the number of I/O pads rather than the number of gates in the core of the chip. However, by keeping all the sensitive analogue components of the design together, in the periphery of the ASIC, away from "noisy" digital circuitry, the problem of switching noise is more likely to be reduced.

The ES2 standard cell library does not contain any resistors or capacitors, therefore all the resistors and capacitors required for the ASIC design have to be connected externally. This is not a major problem, as most of the resistors and capacitors needed for the design are required to be programmable, as their values determine the gain and bandwidth of the analogue front-end circuitry. Rather than having a series of selectable, potentially inaccurate resistors and capacitors on-chip, it is safer and more flexible to connect resistors and capacitors externally, even if this may require a few more I/O pins.

A major concern in using ES2 analogue components is the quality and performance of the ES2 op-amps. Although there have been hundreds of ES2 ASICs fabricated under the Eurochip scheme [Eurochip, 1993], virtually all of these designs have been purely digital. It is therefore difficult to obtain information regarding the quality of the ES2 op-amps, other than that which can be found in the ES2 data books. For a design which is intending to detect signals which are as small as the abdominal fetal electrocardiogram (FECG) (often less than 10  $\mu$ V), then information on the quality of the op-amps in terms of noise, offset voltage and linearity is obviously important.

Under Solo1400 analogue circuits can be simulated using a pseudo analogue simulator in the digital environment. All analogue signals are represented as 8 bit digital signals and are simulated, together with other digital signals, in a multi-level analogue and digital simulator (MADS). This simulator only works at a resolution of 8 bits which is not accurate enough to simulate the part of the ASIC design which includes a 16 bit ADC. Hence, an alternative strategy was employed.

# 4.4. Testing out the analogue circuitry with ES2 sample chips

In order to get over some of the problems faced by using ES2 analogue components, such as op-amp performance and the limited power of the ES2 analogue simulator, sample chips were obtained from ES2, which contained various analogue components from the standard cell library. By prototyping the desired analogue circuitry using the components on these sample chips, valuable information on the performance of the ES2 op-amps and the suitability of the ES2 analogue components in general, was obtained. In effect, bread-boarding the analogue parts of the design with sample chips, acted as an alternative to analogue simulation, and provided a great confidence boost that the mixed ES2 ASIC design would work first time.

The ES2 1.5 µm process is a 5 Volt process (a voltage that can be obtained by the use of 4 NiCd AA batteries - typically 1.25 V each). The analogue circuitry requires a bipolar power supply in order to amplify and filter electrophysiological signals that are of a bipolar nature. A bipolar supply is achieved by connecting the analogue common to the centre of the batteries i.e. 2.5 V of the full 5 V supply (again easily achieved with 4 individual AA cells). Before a description of the analogue circuitry can be given, it is important to employ a naming convention, to be used when referring to analogue voltages. From this point forward the analogue circuit common i.e. the centre point of the 4 AA cells will be referred to as 0 V. The positive analogue supply voltage i.e. the most positive end of the 4 AA cells will be referred to as +2.5 V (called avdd in ES2 terminology), with the corresponding negative analogue supply voltage referred to as -2.5 V (confusingly called agnd in ES2 terminology). Note, the ES2 digital supply pins are called vddc (core), vddx (periphery), gndc (core) and gndx (periphery).

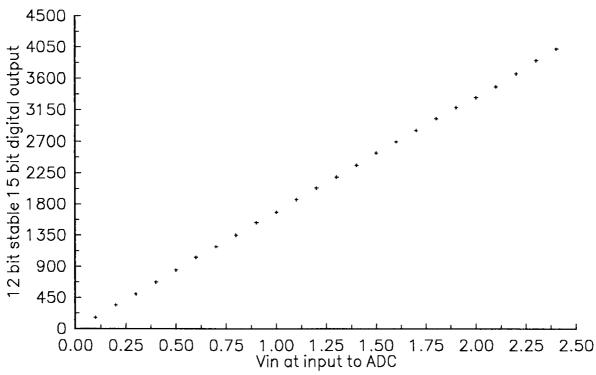

# 4.4.1. The dual slope integrating ADC

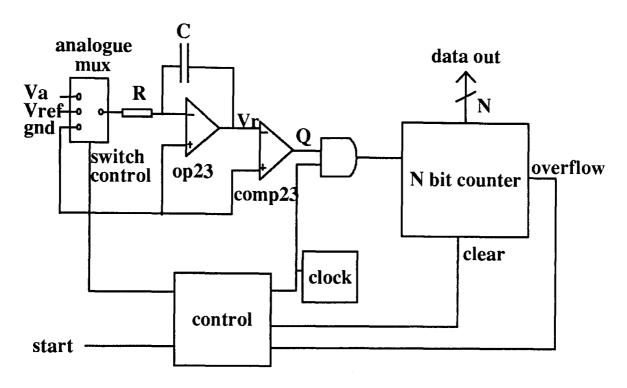

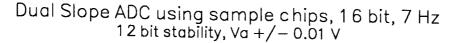

The ASIC designed for this thesis includes an ADC. This ADC is required in mode 2 and must be capable of digitising a variety of different electrophysiological signals. The ADC available in the ES2 1.5  $\mu$ m library is only 8-bit and is thus not accurate enough for recording fetal ECG signals, which require at least 12 bit resolution. It was therefore necessary to investigate the possibility of designing a more accurate ADC, using the existing ES2 1.5  $\mu$ m library components.

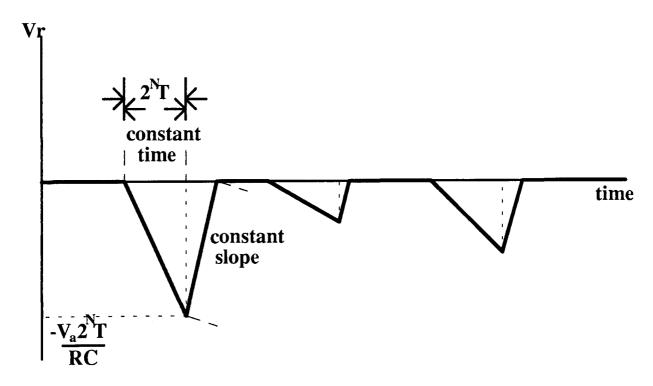

Various different types of ADCs were considered including successive approximation ADCs, flash ADCs and dual slope integrating ADCs [Horowitz and Hill, 1985]. Successive approximation ADCs require a digital to analogue converter (limited to 8 bit with ES2), flash ADCs require a large number of comparators (impractical with ES2), whereas a dual slope integrating ADC although frequency limited, has a reputed high accuracy and can be implemented relatively easily using components available in the ES2 1.5 µm library [Allen and Holberg, 1987]. It is also possible to change the resolution (i.e. number of bits) of a dual slope integrating ADC quite simply, allowing a programmable resolution ADC to be constructed. The analogue components needed for such an ADC consist of an op-amp (op 23), a comparator (comp23) and 3 analogue input multiplexers (as shown in Figure 4.2). The capacitor and resistor are connected externally since reproducible large values are difficult to achieve with integrated circuits. The resolution of the ADC is determined by the N bit counter. A maximum resolution of 16 bits was considered adequate for this application.

The operation of a dual slope integrating ADC is based around a simple integrating op-amp circuit, whose output Vr is used to control the clock of an N bit counter which outputs the result of the conversion. The overflow output

of the N bit counter is used to control a 3-to-1 analogue multiplexer which determines the voltage that is seen by the input of the integrator.

Figure 4.2: An N bit dual slope integrating ADC using ES2 sample chips.

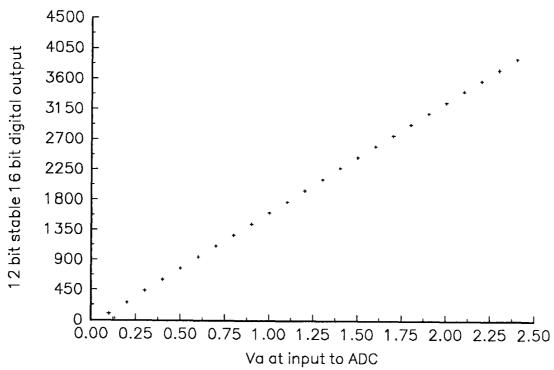

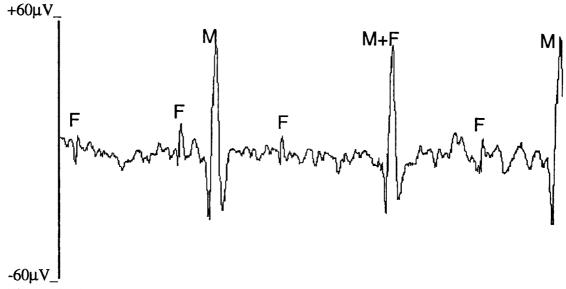

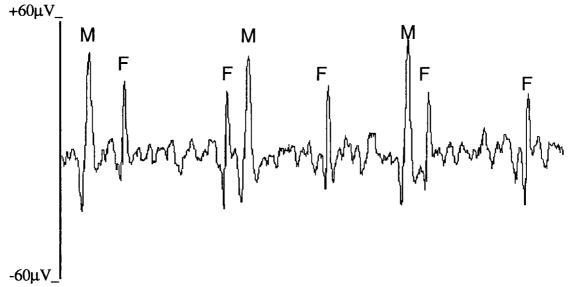

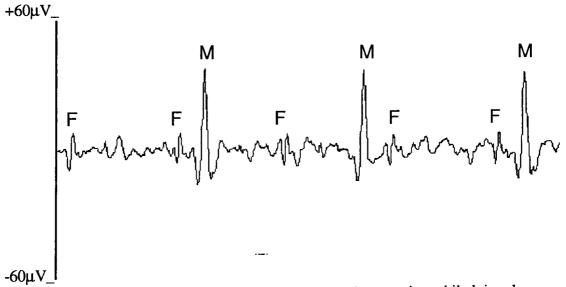

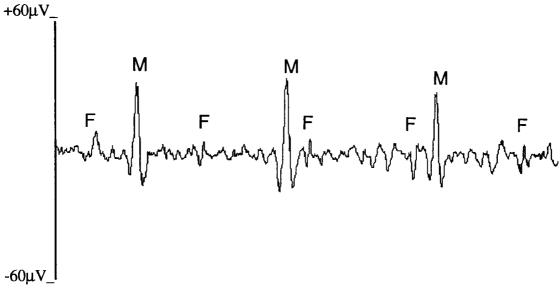

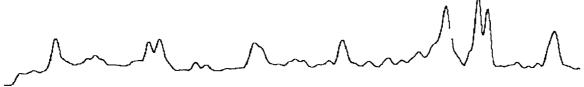

The operation of a dual slope integrating ADC requires a reference voltage, Vref, which is at least as negative as the maximum analogue input voltage is positive. As the power supply for the analogue circuitry is set at +/-2.5 V, the analogue input range of the ADC is therefore restricted to 0 to +2.5 V, with Vref set at -2.5 V. In order to prevent negative voltages being input to the ADC, a bias circuit is used to attenuate the output of the signal conditioning circuitry by a factor of two, as well as to bias the voltage up by 1.25 V. This circuit has the effect of converting a +/-2.5 V range to a 0 to 2.5 V range.