### Photong, Chonlatee (2013) A current source inverter with series AC capacitors for transformerless grid-tied photovoltaic applications. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/13128/1/Thesis\_Chonlatee.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

- Copyright and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners.

- To the extent reasonable and practicable the material made available in Nottingham ePrints has been checked for eligibility before being made available.

- Copies of full items can be used for personal research or study, educational, or notfor-profit purposes without prior permission or charge provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

- · Quotations or similar reproductions must be sufficiently acknowledged.

Please see our full end user licence at: <u>http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf</u>

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact eprints@nottingham.ac.uk

# A Current Source Inverter with Series AC Capacitors for Transformerless Grid-Tied Photovoltaic Applications

Chonlatee Photong, MSc

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

February 2013

#### Abstract

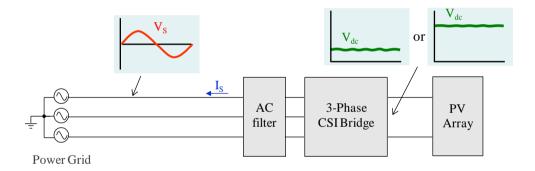

The Current Source Inverter (CSI) is one of the simplest power converter topologies that can convert DC to AC and feed power generated from photovoltaic (PV) cells into the AC grid with a single power conversion stage over the whole PV voltage range. The CSI also provides smooth DC current which is one of the requirements of the PV cells as well as preventing reverse current using unidirectional switches. However, the CSI operates with low efficiency at lower PV voltages, which is where the PV cells produce maximum output power. This low efficiency is caused by large differences in voltage levels between the PV side and the grid side across the converter.

This thesis presents an alternative topology to the three-phase CSI by connecting an AC capacitor in series with each AC phase line of the CSI circuit. The presence of the series AC capacitors in the CSI topology allows the AC voltage levels to be adjusted to match the voltage levels of the PV cells. Therefore, the CSI with series AC capacitors is able to operate with optimal DC-AC voltage levels.

Performance of the proposed topology is evaluated in comparison to the standard CSI and five other converter topologies based on transformerless circuit concepts selected from those already available in the market and suitable converters discussed in the literature. All converter topologies were modeled and simulated with the SABER simulation software package. The CSI with series AC capacitors prototype was constructed in order to validate the feasibility of the proposed topology and the performance of the proposed topology in comparison to the standard CSI. Simulation results show that the CSI with series AC capacitors provides improved efficiency and better input/output power quality in comparison to the standard CSI. The proposed topology also achieves the lowest output line current distortion, lowest voltage stress across the circuit components and lowest estimated cost of power semiconductors when compared to all considered topologies. Experimental results are also presented to validate the simulation results.

#### Acknowledgements

I would like to thank to my supervisors Dr. Christian Klumpner and Professor Patrick Wheeler for their support and patience over the duration of my study.

I would also like to thank Professor Mike Barnes and Dr. Zanchetta Paricle for their guidance and their time to examine me.

Special thanks to Dr. Liliana de Lillo, Dr. Lee Empringham, Dr. Alan James Watson, Dr. Edward Christopher for their kindness and support over the last few years. Thanks to the PEMC group at the University of Nottingham for providing a pleasant environment to work in. I would like to acknowledge to my friends Dr. Sudarat, Dr. Wanphut, Dr. Tanadon, P' Fon, P' Chris and N' Work who made my work and my stay in Nottingham more enjoyable.

With much love, I would like to thank to my parents P' Amphorn and M' Guan for their love and unconditional support. Thanks to my wife Pitinuch and my son Arpo for their love, patience and encouragement.

I would like to thank also to the Royal Thai Government for the financial support along my graduate studies.

Thank you.

# Contents

#### Chapter 1

| Introduction          | 1  |

|-----------------------|----|

| 1.1 Thesis Objectives | 11 |

| 1.2 Thesis Structure  |    |

#### Chapter 2

| C | Characteristics and Models of Photovoltaic Cells15                 |

|---|--------------------------------------------------------------------|

|   | 2.1 Structures of PV Cells                                         |

|   | 2.2 Materials of PV Cells 19                                       |

|   | 2.3 Operation Principle of PV Cells                                |

|   | 2.4 PV Equivalent Circuit Model and Equations                      |

|   | 2.5 Electrical Characteristics of PV Cells                         |

|   | 2.6 PV Modules                                                     |

|   | 2.7 PV Equivalent Circuit Modelling from the Datasheets            |

|   | 2.7.1 Typical PV Specification Parameters in the Datasheets        |

|   | 2.7.2 PV Equivalent Circuit Modelling Procedure                    |

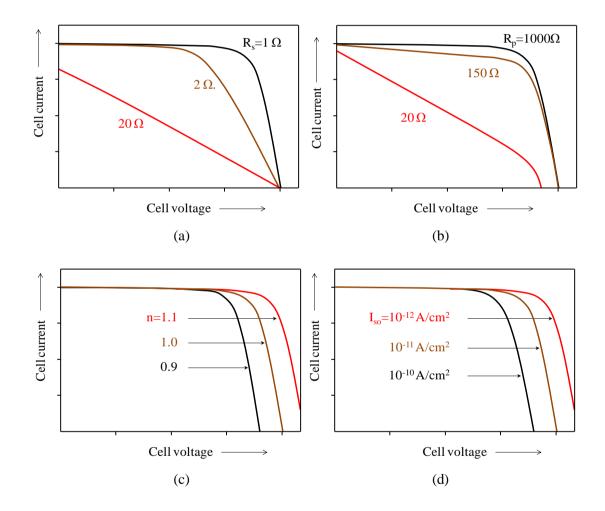

|   | 2.7.3 Effects of PV Equivalent Parameters on the PV Characteristic |

|   | Curves                                                             |

|   | 2.7.4 An Example of PV Equivalent Circuit Modelling                |

|   | 2.8 Summary                                                        |

|   |                                                                    |

| Characteristics of Grid-Tied PV Inverters | 40 |

|-------------------------------------------|----|

| 3.1 PV Side Characteristics               |    |

| 3.2 Grid Side Characteristics             |    |

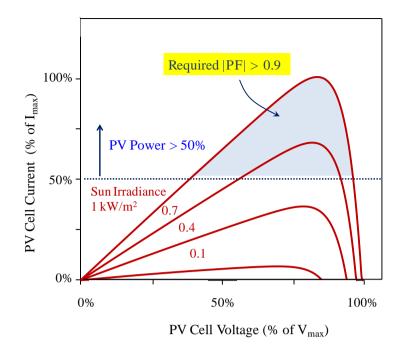

| 3.2.1 High Output Power Quality           | 43 |

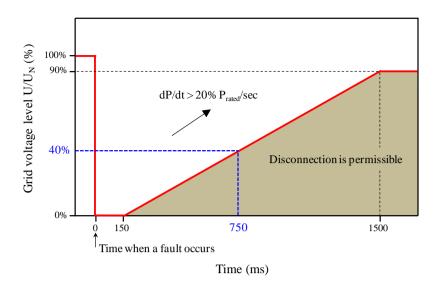

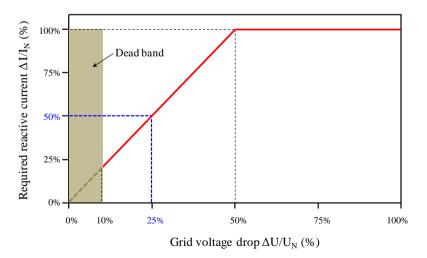

| 3.2.2 Grid Fault Ride-Through Capability | 45 |

|------------------------------------------|----|

| 3.2.3 Islanding Prevention               | 47 |

| 3.3 Other Characteristics                | 47 |

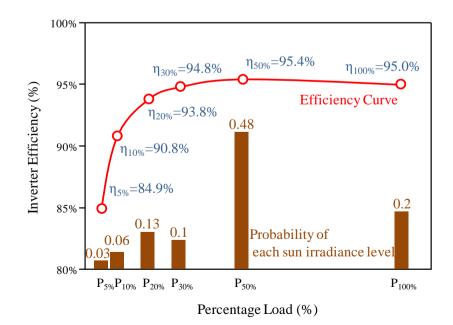

| 3.3.1 High Power Conversion Efficiency   | 47 |

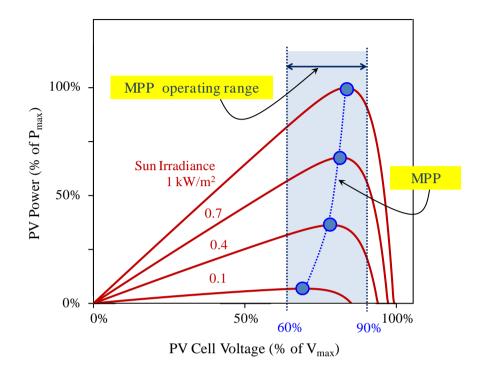

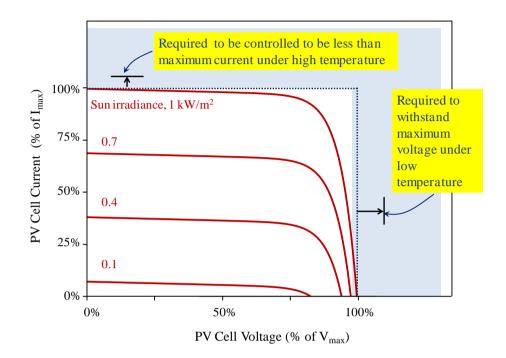

| 3.3.2 Accurate MPP Tracking              | 49 |

| 3.3.3 Minimum Costs                      | 51 |

| 3.4 Summary                              | 52 |

| Three-Phase    | Transformerless      | Grid-Tied      | PV     | Inverter | Topologies | under |

|----------------|----------------------|----------------|--------|----------|------------|-------|

| Investigation. | ••••••               | •••••          | •••••  | •••••    | •••••      | 53    |

| 4.1 Introduct  | tion                 |                |        |          |            | 53    |

| 4.2 Circuit C  | Configurations       |                |        |          |            | 55    |

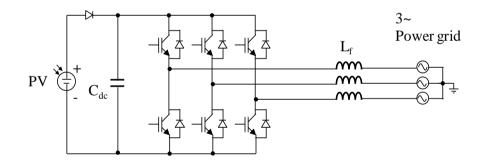

| 4.2.1 Volt     | tage Source Inverter |                | •••••  |          |            | 55    |

| 4.2.2 Curr     | rent Source Inverter |                | •••••  |          |            | 55    |

| 4.2.3 Two      | o-Stage VSI with a B | Boost Convert  | er     |          |            | 56    |

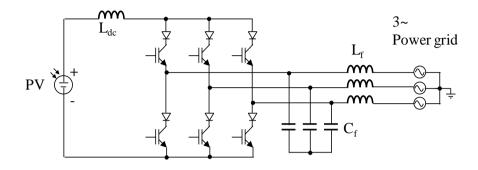

| 4.2.4 Two      | o-Stage CSI with a B | Buck Converte  | r      |          |            | 57    |

| 4.2.5 Volt     | tage Fed Z-Source In | nverter        | •••••  |          |            | 58    |

| 4.2.6 Curr     | rent Fed Z-Source Ir | nverter        | •••••  |          |            | 58    |

| 4.3 Modulat    | ion Strategies       |                | •••••  |          |            | 59    |

| 4.3.1 Prin     | ciple of the Space V | ector Modula   | tion   |          |            | 60    |

| 4.3.2 VSI      | Modulation           |                |        |          |            | 63    |

| 4.3.3 CSI      | Modulation           |                |        |          |            | 67    |

| 4.3.4 ZSI      | Modulation           |                |        |          |            | 72    |

| 4.4 Control S  | Strategies           |                |        |          |            | 76    |

| 4.4.1 VSI      | Control              |                | •••••  |          |            | 77    |

| 4.4.2 CSI      | Control              |                |        |          |            | 78    |

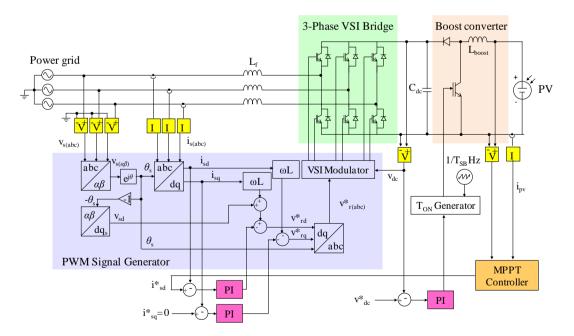

| 4.4.3 Two      | o-Stage VSI with a E | Boost Convert  | er Cor | ntrol    |            | 80    |

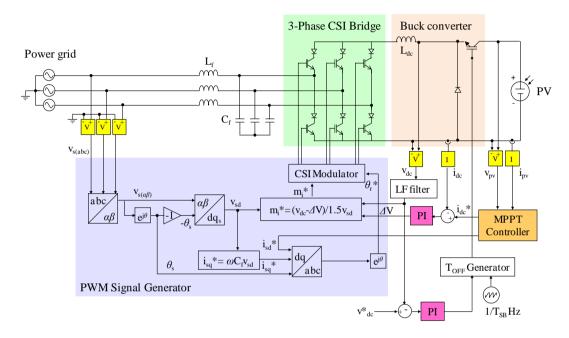

| 4.4.4 Two      | o-Stage CSI with a B | Buck Converte  | r Con  | trol     |            | 82    |

| 4.4.5 Volt     | tage Fed Z-Source In | nverter Contro | ol     |          |            | 83    |

| 4.4.6 Curr     | rent Fed Z-Source Ir | overter Contro | ol     |          |            | 86    |

| 4.5 Design N   | Methodology for the  | Passive Com    | ponen  | ts       |            | 88    |

| 4.5.1 Filte    | ering Component De   | esign          |        |          |            | 88    |

| 4.5.2 Additional Component Design |  |

|-----------------------------------|--|

| 4.6 Summary                       |  |

| The Current Source Inverter with Series AC Capacitors             |

|-------------------------------------------------------------------|

| 5.1 Fundamental Characteristics                                   |

| 5.2 Analytical Model and Equations                                |

| 5.3 Modulation and Control Methodologies 101                      |

| 5.3.1 Control Principle 101                                       |

| 5.3.3 DC-Link Current Control Design 107                          |

| 5.4 Design of the Series AC Capacitors 112                        |

| 5.5 Operating Results of the CSI with Series AC capacitors 115    |

| 5.5.1 Operating Results under Normal Grid Voltage Conditions      |

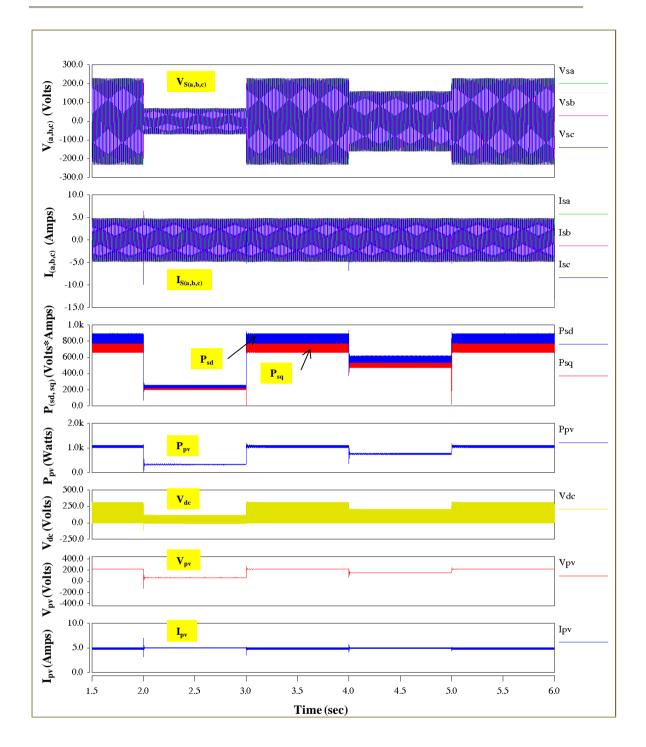

| 5.5.2 Operating Results under Low Grid Voltage Sag Conditions 125 |

| 5.6 Other Potential Applications 129                              |

| 5.6.1 Reduced Component Voltage Rating 129                        |

| 5.6.2 High Frequency Harmonics Reduction                          |

| 5.6.3 Reduced Size of the DC-link inductor                        |

| 5.7 Summary 135                                                   |

| Evaluation of the CSI with Series AC Capacitors in | Comparison to the Other |

|----------------------------------------------------|-------------------------|

| Inverter Topologies under Investigation            |                         |

| 6.1 Comparison of PV Voltage and Current Ratings   |                         |

| 6.2 Comparison of Operating Modulation Depths      |                         |

| 6.3 Comparison of Circuit Components               |                         |

| 6.3.1 Number of Active Components                  |                         |

| 6.3.2 Size of Passive Components                   |                         |

| 6.4 Comparison of Input Power Quality              |                         |

| 6.5 Comparison of Output Power Quality             | 154                     |

| 6.6 Comparison of Stress on Power Semiconductors   |                         |

| 6.7 Comparison of Estimated Cost of Power Semiconductors 1 | 166 |

|------------------------------------------------------------|-----|

| 6.8 Comparison of Estimated Semiconductor Power Losses 1   | 167 |

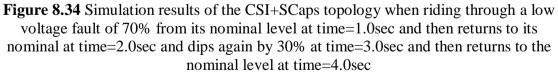

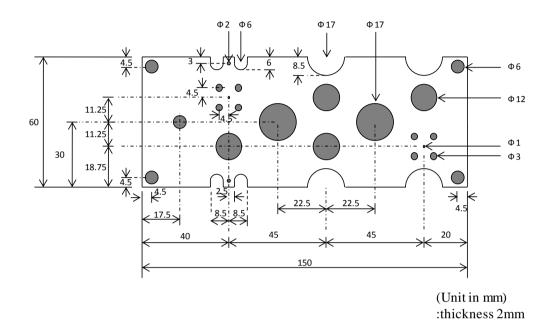

| 6.9 Comparison of Estimated Inverter Efficiency 1          | 174 |

| 6.10 Overall Performance Evaluation 1                      | 180 |

| 6.11 Summary 1                                             | 183 |

| Design and Construction of Experimental Test-Rig185                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------|

| 7.1 Overview of the Experimental Test-Rig 185                                                                                  |

| 7.2 PV Emulator                                                                                                                |

| 7.2.1 Overview of Hardware                                                                                                     |

| 7.2.2 Analogue Control Circuit                                                                                                 |

| 7.3 Prototype CSI+SCaps 194                                                                                                    |

| 7.3.2 CSI Power Module                                                                                                         |

| 7.3.3 Filtering Components                                                                                                     |

| 7.3.4 Series AC Capacitors                                                                                                     |

| 7.4 Interfacing Circuits 202                                                                                                   |

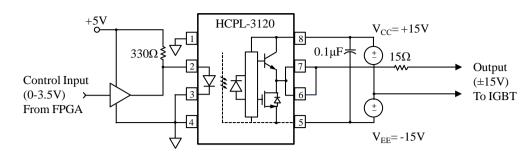

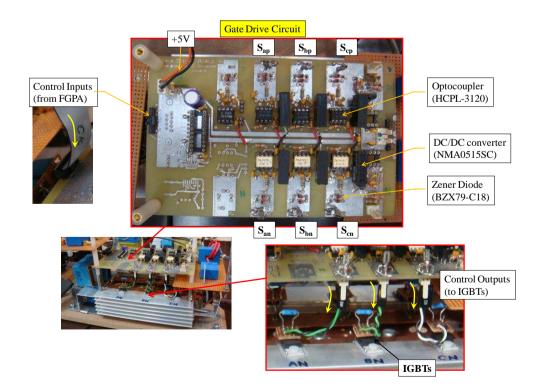

| 7.4.1 Gate Drive Circuit                                                                                                       |

| 7.4.2 Measurement Circuits                                                                                                     |

| 7. 1.2 Modstroment Chedus                                                                                                      |

| 7.5 Control Circuits   207                                                                                                     |

|                                                                                                                                |

| 7.5 Control Circuits                                                                                                           |

| 7.5 Control Circuits2077.5.1 Overview of the Control Platform207                                                               |

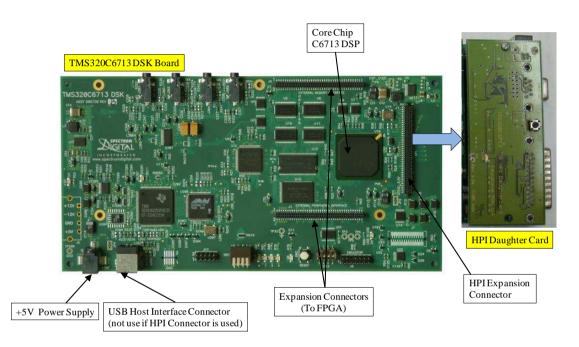

| 7.5 Control Circuits2077.5.1 Overview of the Control Platform2077.5.2 DSP Board208                                             |

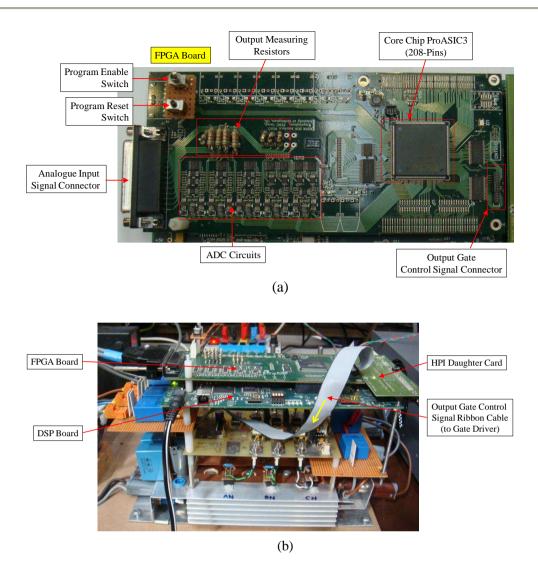

| 7.5 Control Circuits2077.5.1 Overview of the Control Platform2077.5.2 DSP Board2087.5.3 FPGA Board208                          |

| 7.5 Control Circuits2077.5.1 Overview of the Control Platform2077.5.2 DSP Board2087.5.3 FPGA Board2087.6 Protection Circuit211 |

| Experimental Results      |     |

|---------------------------|-----|

| 8.1 Test-Rig Verification |     |

| 8.1.1 PV Emulator         | 216 |

| 8.1.2 CSI with Series AC Capacitors Inverter Prototype    | 220 |

|-----------------------------------------------------------|-----|

| 8.2 Evaluation of the CSI with Series AC Capacitors       | 222 |

| 8.2.1 Performance during Start-Up and Shutdown Conditions | 223 |

| 8.2.2 Performance during Normal Grid Voltage Conditions   | 226 |

| 8.2.3 Performance during Low Voltage Grid Faults          | 245 |

| 8.2.4 Inverter Efficiency                                 | 255 |

| 8.3 Summary                                               | 257 |

|                                                           |     |

| Conclusions  |                                        | 258 |

|--------------|----------------------------------------|-----|

| 9.1 Summary  | of Achievements                        |     |

| 9.2 Future W | ork                                    |     |

| References   |                                        | 270 |

| Appendices   |                                        | 278 |

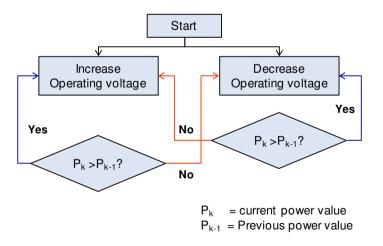

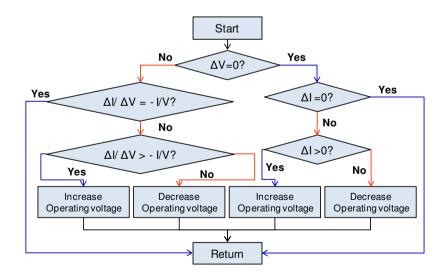

| Appendix A   | MPPT Techniques                        |     |

| Appendix B   | Drawings of Three-Phase Power Bus Bars |     |

# **List of Figures**

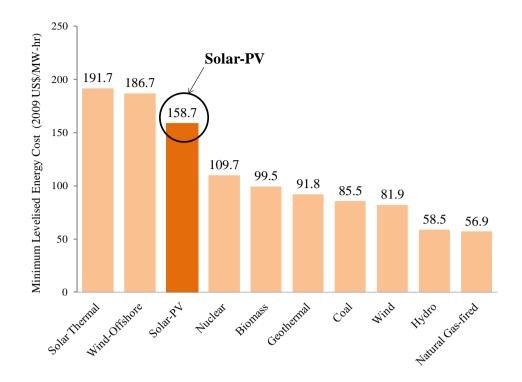

| Figure 1.1 Minimum cost of electricity production for different power plant typ | es [8] |

|---------------------------------------------------------------------------------|--------|

|                                                                                 | 3      |

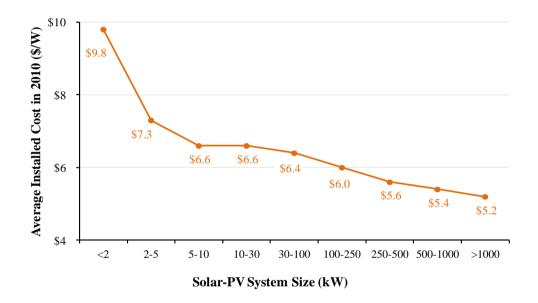

| Figure 1.2 Average installed cost for different solar-PV system size (kW) [29]  | 6      |

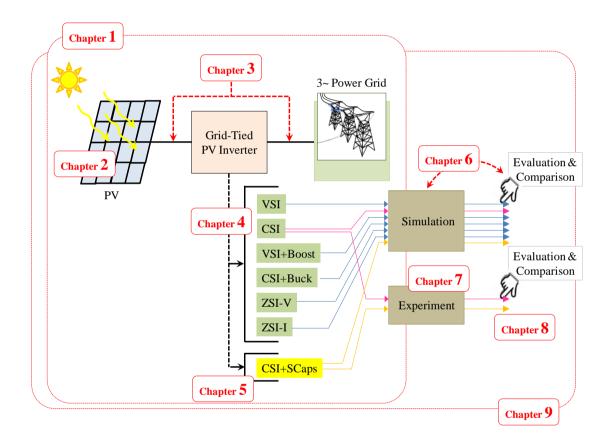

| Figure 1.3 Thesis structure                                                     | 12     |

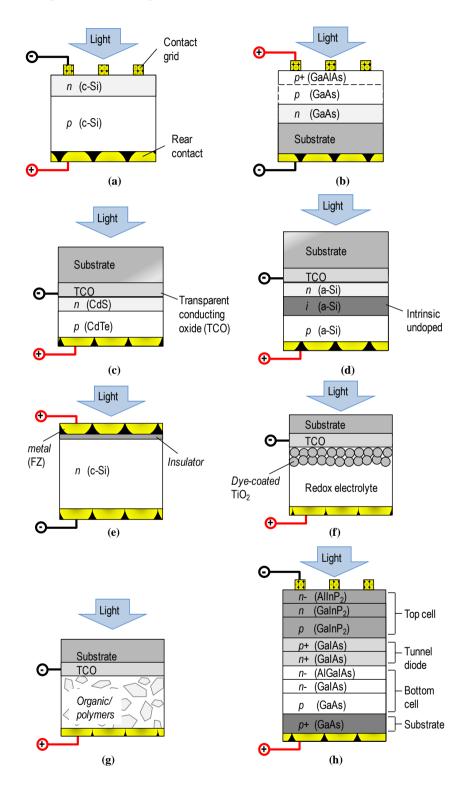

| Figure 2.1 Basic structures of a PV cell: (a) Homojunction, (b) Heteroface, (c)          |

|------------------------------------------------------------------------------------------|

| Heterojunction, (d) n-i-p (or p-i-n), (e) Schottky-Junction, (f) Dye-Sensitised, (g)     |

| Organic, and (h) Multijunction16                                                         |

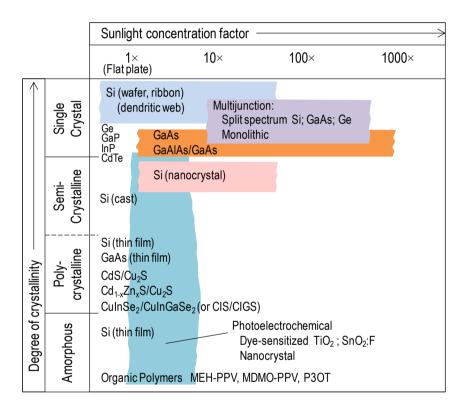

| Figure 2.2 Typical PV materials for different degrees of crystallinity and sunlight      |

| concentration factors [46] 19                                                            |

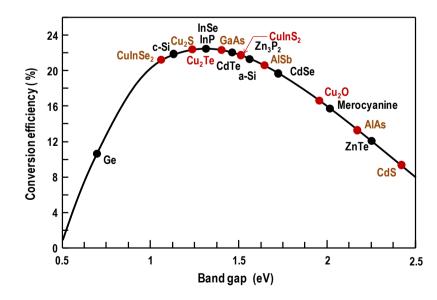

| Figure 2.3 Band-gaps of semiconductor materials and their maximum theoretical            |

| power conversion efficiencies at room temperature (298K)                                 |

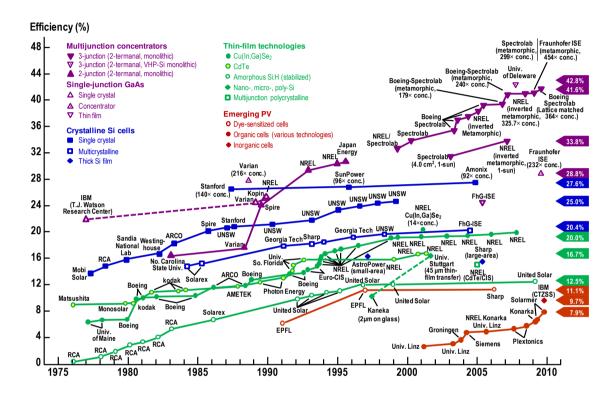

| Figure 2.4 Timelines of energy conversion efficiencies of different PV cell structures   |

| and materials with their developers [48], [49]21                                         |

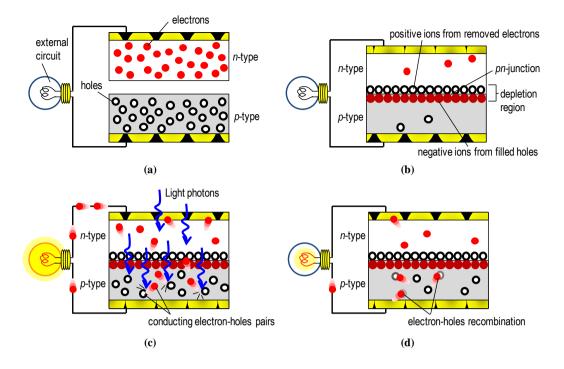

| Figure 2.5 Basic PV operations; (a) before contacting p-type and n-type layers, (b)      |

| after contacting p-type and n-type layers, (c) under activating light photons, and (d)   |

| after activating light photons                                                           |

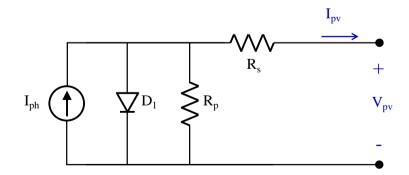

| Figure 2.6 PV equivalent circuit model                                                   |

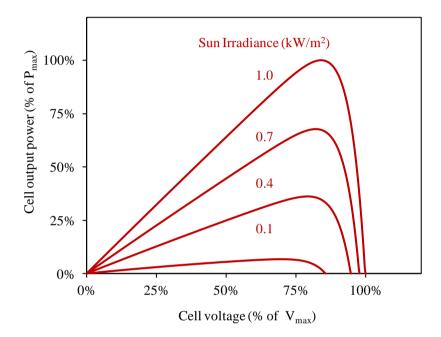

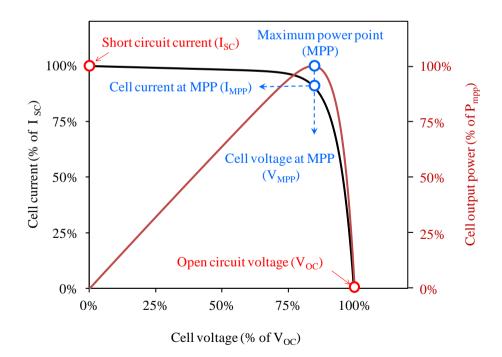

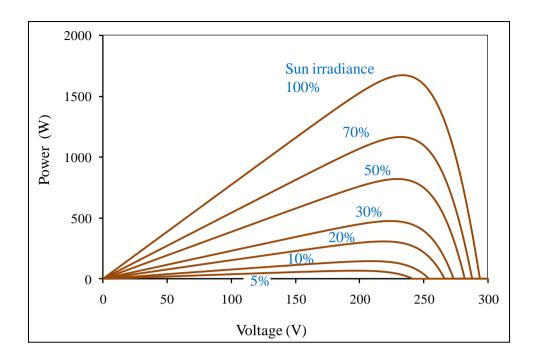

| Figure 2.7 Typical power-voltage (P-V) characteristic curves of the PV cells25           |

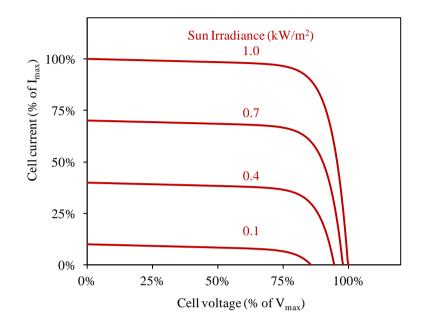

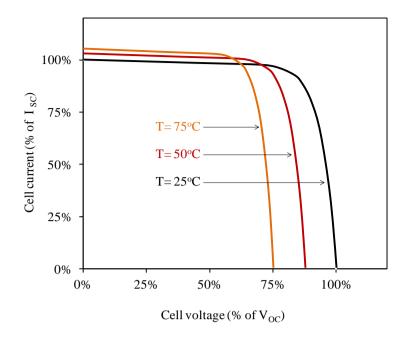

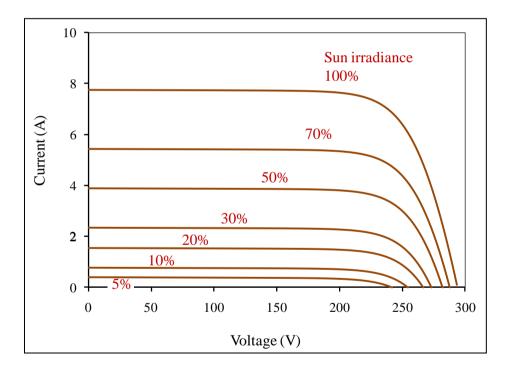

| Figure 2.8 Typical current-voltage (I-V) characteristic curves of the PV cells           |

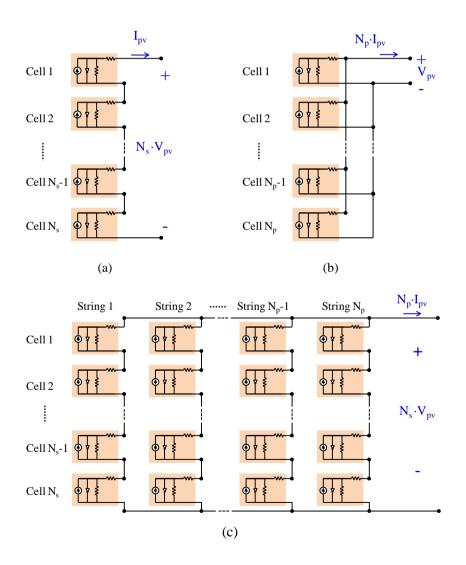

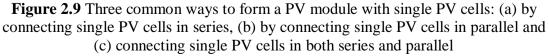

| Figure 2.9 Three common ways to form a PV module with single PV cells: (a) by            |

| connecting single PV cells in series, (b) by connecting single PV cells in parallel, and |

| (c) connecting single PV cells in both series and parallel                               |

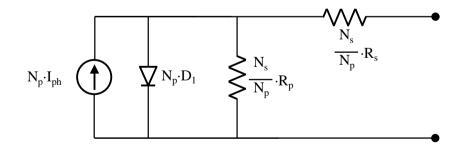

| Figure 2.10 An electrical PV equivalent circuit model of a PV module with $N_p$ strings  |

| of N <sub>s</sub> series connected cells                                                 |

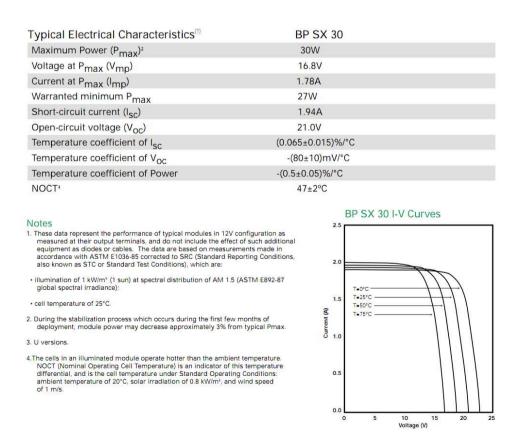

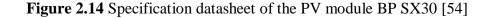

| Figure 2.11 Typical PV Specification parameters in the datasheets                        |

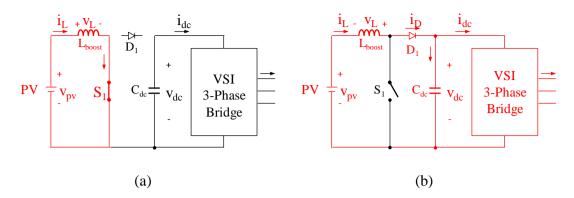

| Figure 4.1 Circuit configuration of a standard three-phase VSI          | 55        |

|-------------------------------------------------------------------------|-----------|

| Figure 4.2 Circuit configuration of a standard three-phase CSI          |           |

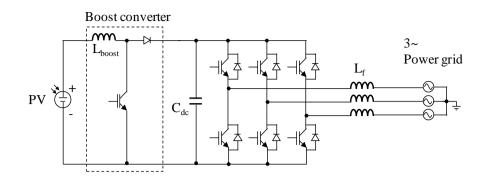

| Figure 4.3 Circuit configuration of the three-phase, two-stage VSI with | n a boost |

| converter                                                               | 57        |

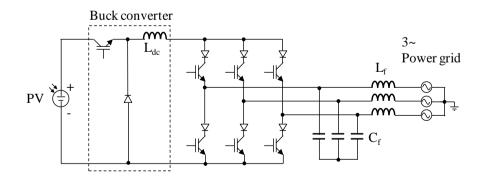

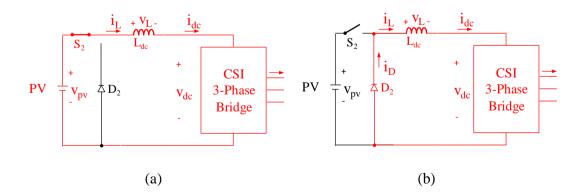

| Figure 4.4 Circuit configuration of the three-phase, two-stage CSI with | h a buck  |

| converter                                                               | 57        |

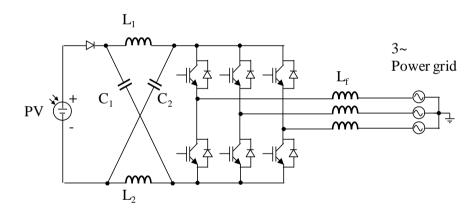

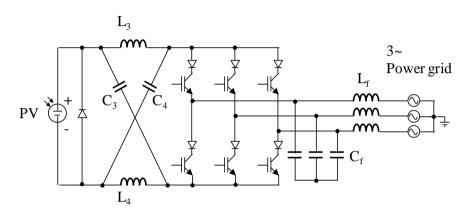

| Figure 4.5 Circuit configuration of the three-phase, voltage fed ZSI    | 58        |

| Figure 4.6 Circuit configuration of the three-phase, current fed ZSI    | 59        |

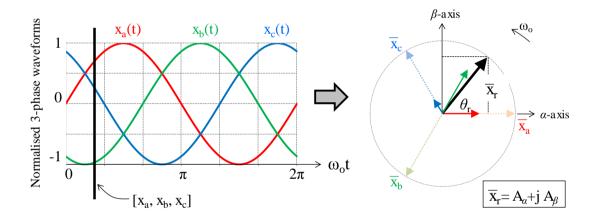

| Figure 4.7 Transformation process between the three-phase waveforms and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| representative vector rotating on the $\alpha$ - $\beta$ space vector plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

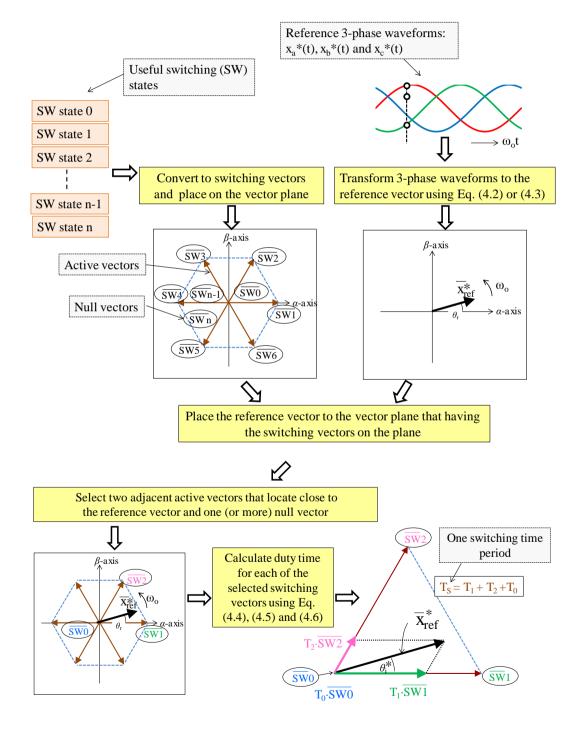

| Figure 4.8 Procedure to select the switching states and calculate the duty time for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| each of the selected switching states in the SVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

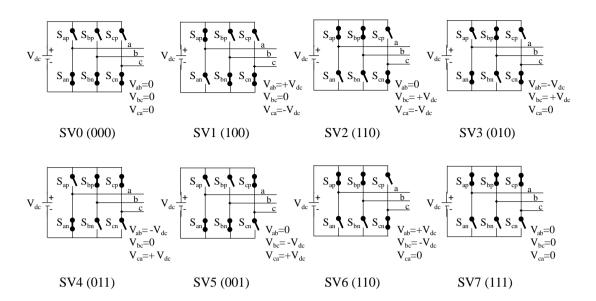

| Figure 4.9 Eight allowable switching states used in the VSI modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

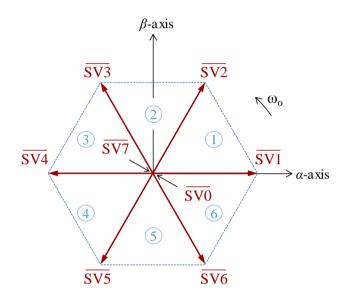

| Figure 4.10 Space vector plane for the SVM-VSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

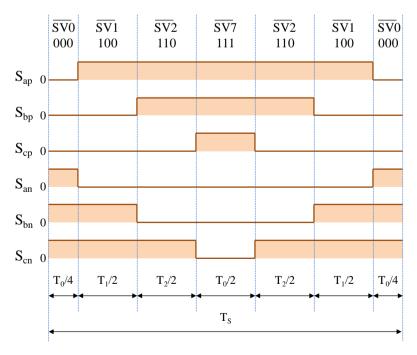

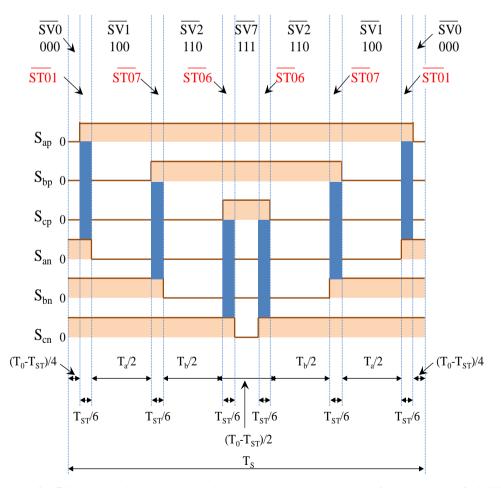

| Figure 4.11 Double-sided symmetrical switching sequence of the VSI modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| over one switching period when the reference vector is located in the Sector 1 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

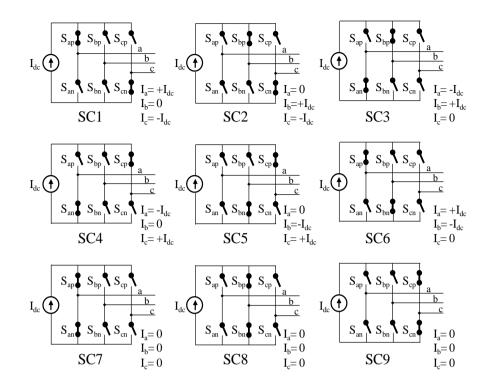

| Figure 4.12 Nine allowable switching states used in the CSI modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

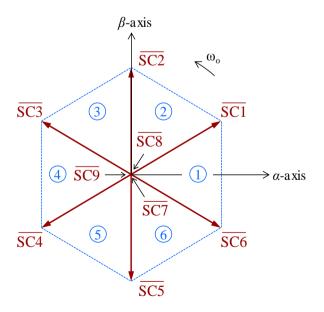

| Figure 4.13 Space vector plane for the SVM-CSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

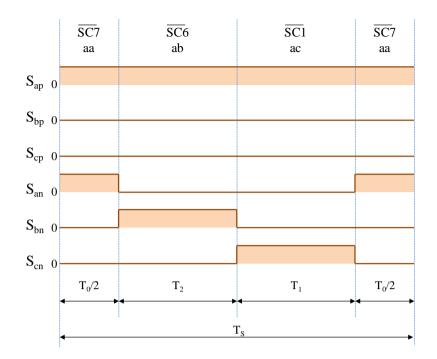

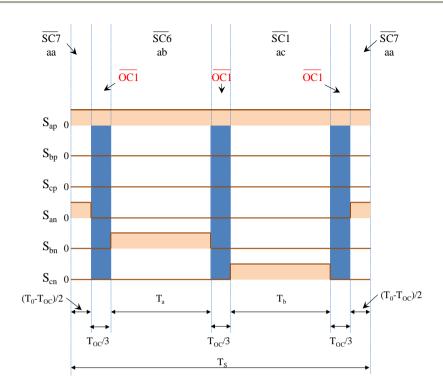

| Figure 4.14 Single-sided asymmetrical switching sequence of the CSI modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| over one switching period when the reference current vector is located in the Sector 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 4.15 Double-sided symmetrical switching sequence of the voltage fed ZSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| modulation for one switching period when the reference vector is located in Sector 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 4.16 Single-sided asymmetrical switching sequence of the current fed ZSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| modulation for one switching period when the reference vector is located in Sector 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| modulation for one switching period when the reference vector is located in Sector 1<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

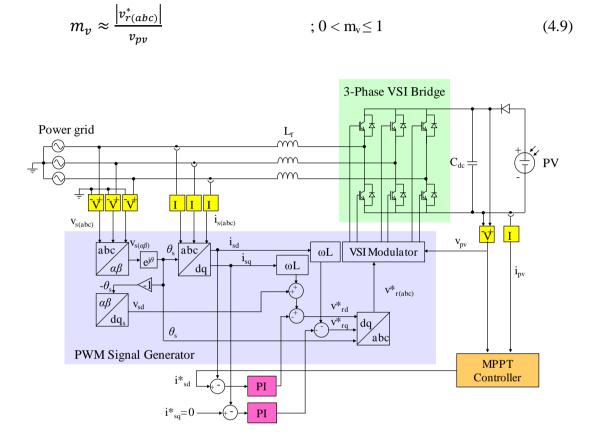

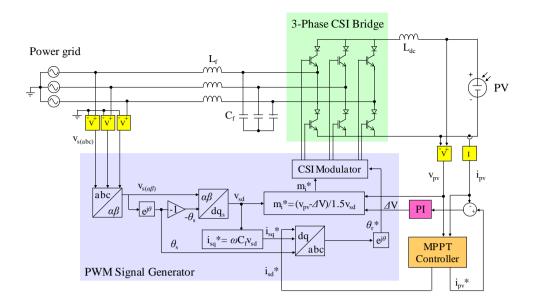

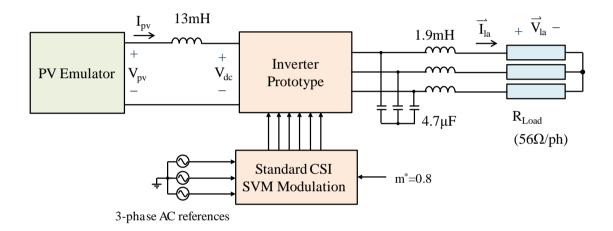

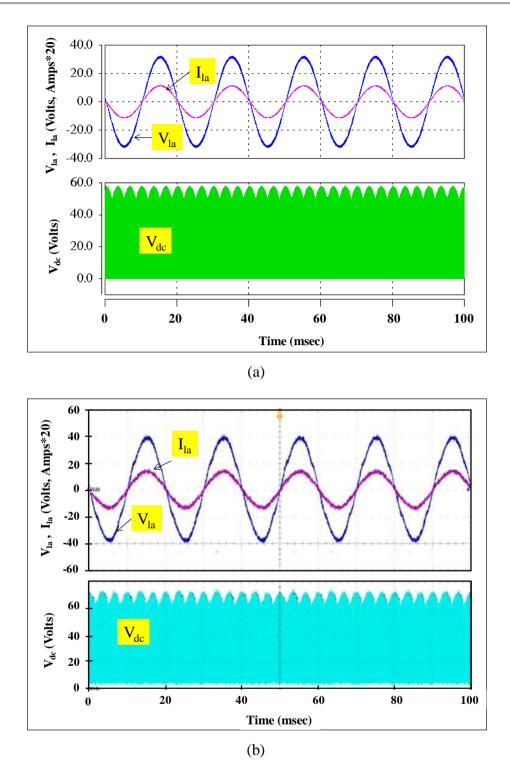

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost switch is (a) turned on and (b) turned off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost switch is (a) turned on and (b) turned off         81         Figure 4.20 Schematic for the two-stage VSI with a boost converter control                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost switch is (a) turned on and (b) turned off         81         Figure 4.20 Schematic for the two-stage VSI with a boost converter control         81         Figure 4.21 Diagrams of the two-stage CSI with a buck converter when the buck                                                                                                                                                                                                                                                                                                                              |

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost switch is (a) turned on and (b) turned off         81         Figure 4.20 Schematic for the two-stage VSI with a boost converter control         81         Figure 4.21 Diagrams of the two-stage CSI with a buck converter when the buck switch is (a) turned on and (b) turned off                                                                                                                                                                                                                                                                                   |

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost switch is (a) turned on and (b) turned off         81         Figure 4.20 Schematic for the two-stage VSI with a boost converter control         81         Figure 4.21 Diagrams of the two-stage CSI with a buck converter when the buck switch is (a) turned on and (b) turned off         82         Figure 4.22 Schematic for the two-stage CSI with a buck converter control         83                                                                                                                                                                           |

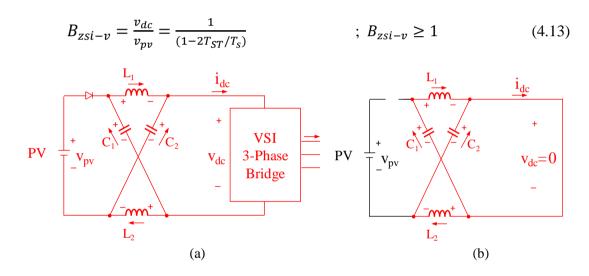

| 75         Figure 4.17 Schematic for the VSI control         78         Figure 4.18 Schematic for the CSI control         80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost switch is (a) turned on and (b) turned off         81         Figure 4.20 Schematic for the two-stage VSI with a boost converter control         81         Figure 4.21 Diagrams of the two-stage CSI with a buck converter when the buck switch is (a) turned on and (b) turned off         82         Figure 4.22 Schematic for the two-stage CSI with a buck converter control         83         Figure 4.23 Diagrams of the voltage fed ZSI when operating with (a) non shoot-                                                                                    |

| 75         Figure 4.17 Schematic for the VSI control       78         Figure 4.18 Schematic for the CSI control       80         Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boost switch is (a) turned on and (b) turned off       81         Figure 4.20 Schematic for the two-stage VSI with a boost converter control       81         Figure 4.21 Diagrams of the two-stage CSI with a buck converter when the buck switch is (a) turned on and (b) turned off       82         Figure 4.22 Schematic for the two-stage CSI with a buck converter control       83         Figure 4.23 Diagrams of the voltage fed ZSI when operating with (a) non shoot-through switching states and (b) shoot-through switching states.       84                       |

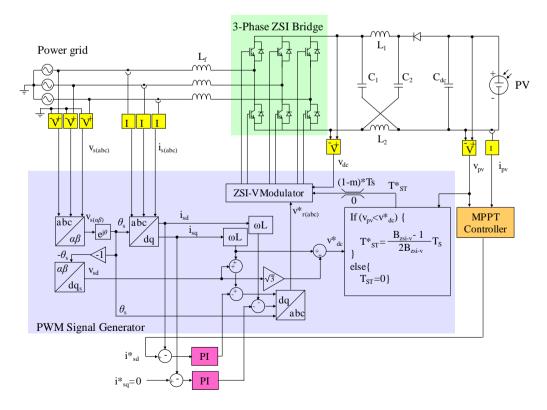

| 75Figure 4.17 Schematic for the VSI control78Figure 4.18 Schematic for the CSI control80Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boostswitch is (a) turned on and (b) turned off81Figure 4.20 Schematic for the two-stage VSI with a boost converter control81Figure 4.21 Diagrams of the two-stage CSI with a buck converter when the buckswitch is (a) turned on and (b) turned off82Figure 4.22 Schematic for the two-stage CSI with a buck converter control83Figure 4.23 Diagrams of the voltage fed ZSI when operating with (a) non shoot-through switching states and (b) shoot-through switching states84Figure 4.24 Schematic for the voltage fed ZSI Control                                                                                     |

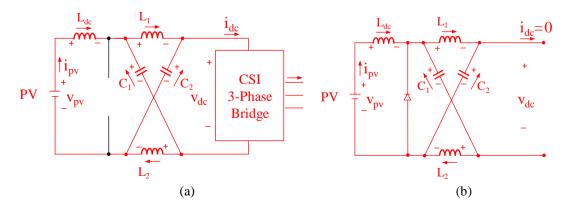

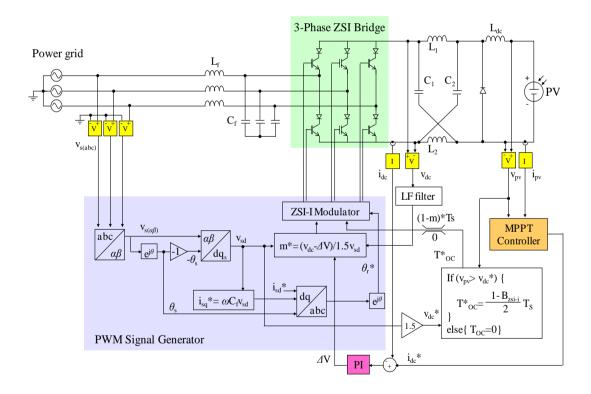

| 75Figure 4.17 Schematic for the VSI control78Figure 4.18 Schematic for the CSI control80Figure 4.19 Diagrams of the two-stage VSI with a boost converter when the boostswitch is (a) turned on and (b) turned off81Figure 4.20 Schematic for the two-stage VSI with a boost converter control81Figure 4.21 Diagrams of the two-stage CSI with a buck converter when the buckswitch is (a) turned on and (b) turned off82Figure 4.22 Schematic for the two-stage CSI with a buck converter control83Figure 4.23 Diagrams of the voltage fed ZSI when operating with (a) non shoot-through switching states and (b) shoot-through switching states84Figure 4.24 Schematic for the voltage fed ZSI Control85Figure 4.25 Diagrams of the current fed ZSI when operating in (a) non open-circuit |

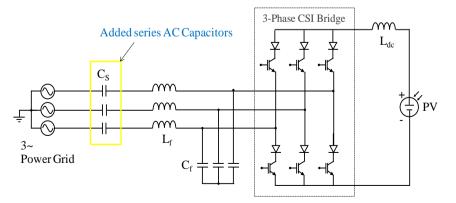

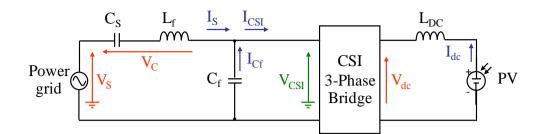

| Figure 5.1 Circuit configuration of the CSI with series AC capacitors (CSI+SCaps) 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.2 Standard CSI when operating with a low or high PV voltage level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 5.3 CSI+SCaps when operating with (a) a low PV voltage level and (b) high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PV voltage level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5.4 Per-phase equivalent circuit of the CSI+SCaps topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

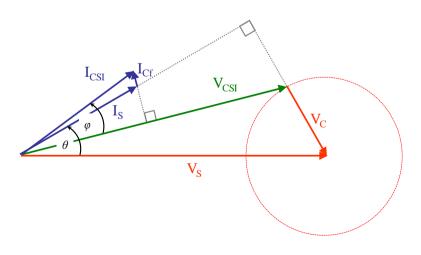

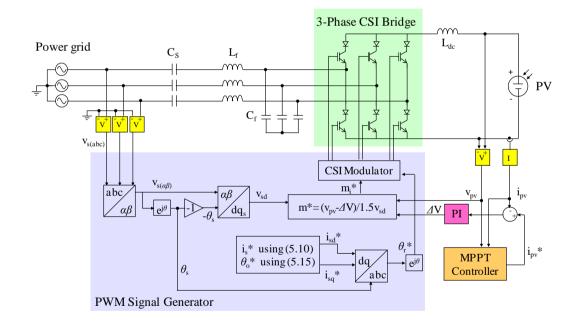

| Figure 5.5 Phasorial diagram representation of the analytical model of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CSI+SCaps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

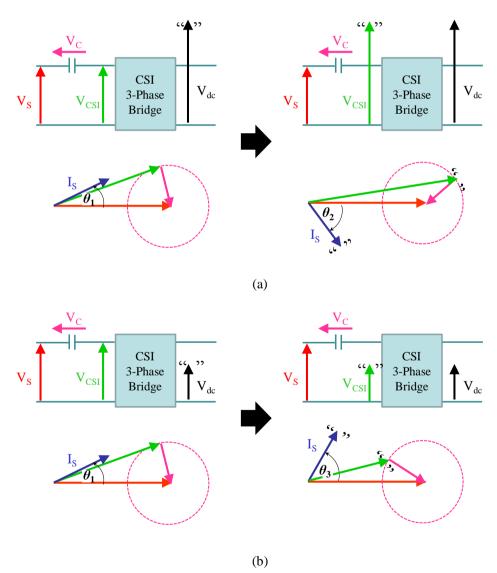

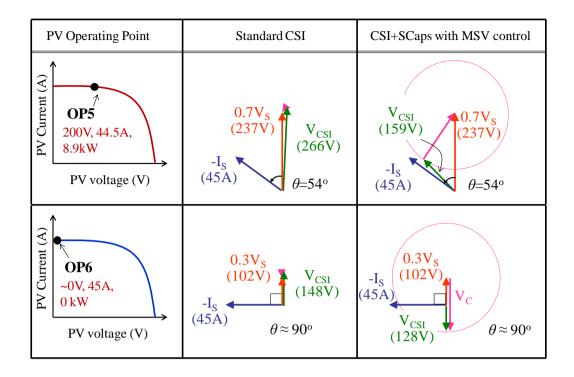

| Figure 5.6 Diagrams to show how the power factor angle can control the AC voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| level of the CSI+SCaps topology to match (a) a high DC voltage level and (b) a low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DC voltage level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 5.7 Diagrams to show how the magnitude of AC line current $(I_S)$ can affect the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| voltage level at the AC side of the inverter $(V_{CSI})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

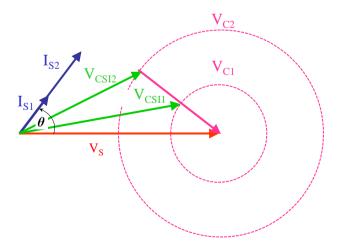

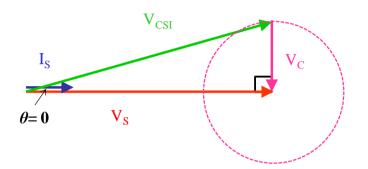

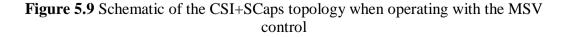

| Figure 5.8 Phasor diagrams when the CSI+SCaps operating with UPF control 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

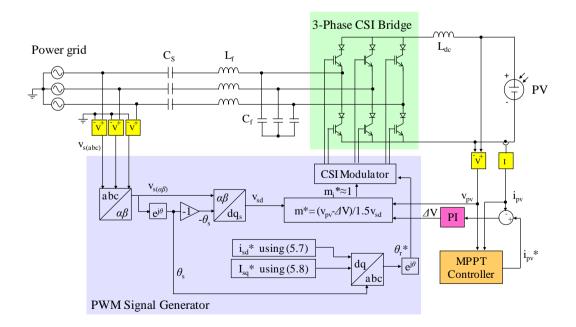

| Figure 5.9 Schematic of the CSI+SCaps topology when operating with the MSV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| control 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 5.10 Phasor diagram for the CSI+SCaps operating with the OPF control 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

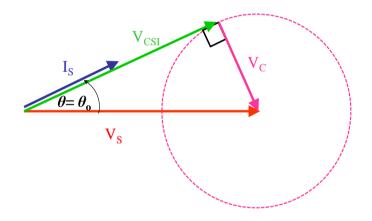

| Figure 5.11 Schematic of the CSI+SCaps topology operating with the OPF control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 5.11 Schematic of the CSI+SCaps topology operating with the OPF control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

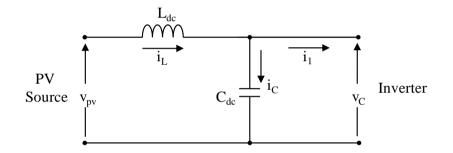

| 107         Figure 5.12 DC side equivalent circuit of the CSI-type topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 107         Figure 5.12 DC side equivalent circuit of the CSI-type topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 107Figure 5.12 DC side equivalent circuit of the CSI-type topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 107Figure 5.12 DC side equivalent circuit of the CSI-type topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

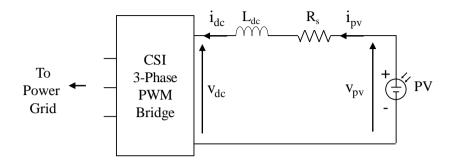

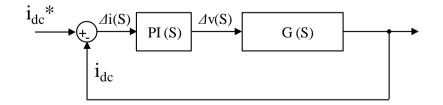

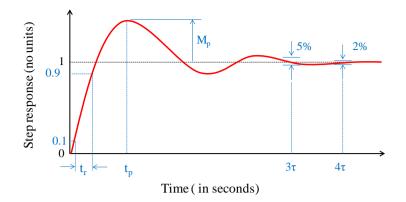

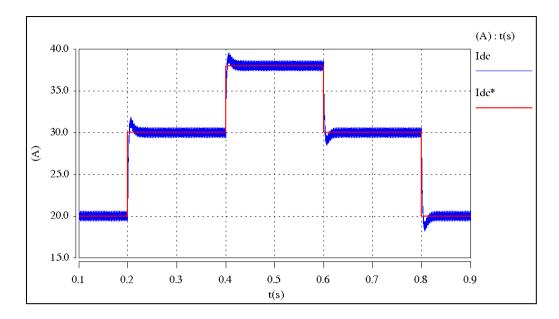

| 10 Figure 5.12 DC side equivalent circuit of the CSI-type topology108Figure 5.13 Diagram of the DC-link current control for the CSI-type topology108Figure 5.13 Diagram of the DC-link current control for the CSI-type topology108Figure 5.14 Specification parameters for the step response110Figure 5.15 Comparison of the DC-link current demand (Idc*) and the correspondingDC-link current (Idc) obtained from the CSI+SCaps when operating with the PI                                                                                                                                                                                      |

| 10 Figure 5.12 DC side equivalent circuit of the CSI-type topology108Figure 5.13 Diagram of the DC-link current control for the CSI-type topology108Figure 5.13 Diagram of the DC-link current control for the CSI-type topology108Figure 5.14 Specification parameters for the step response110Figure 5.15 Comparison of the DC-link current demand (Idc*) and the correspondingDC-link current (Idc) obtained from the CSI+SCaps when operating with the PIcontroller using the simulation parameters from Table 5.3                                                                                                                             |

| 10 Figure 5.12 DC side equivalent circuit of the CSI-type topology108Figure 5.13 Diagram of the DC-link current control for the CSI-type topology108Figure 5.13 Diagram of the DC-link current control for the CSI-type topology110Figure 5.14 Specification parameters for the step response110Figure 5.15 Comparison of the DC-link current demand (Idc*) and the correspondingDC-link current (Idc) obtained from the CSI+SCaps when operating with the PIcontroller using the simulation parameters from Table 5.3111Figure 5.16 Values of the series AC capacitors required for different (a) grid voltage                                    |

| 107Figure 5.12 DC side equivalent circuit of the CSI-type topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Figure 5.12</b> DC side equivalent circuit of the CSI-type topology 108<br><b>Figure 5.13</b> Diagram of the DC-link current control for the CSI-type topology 108<br><b>Figure 5.14</b> Specification parameters for the step response                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>Figure 5.12</b> DC side equivalent circuit of the CSI-type topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

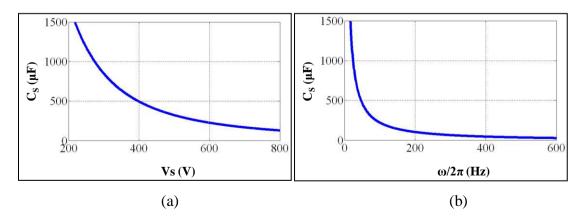

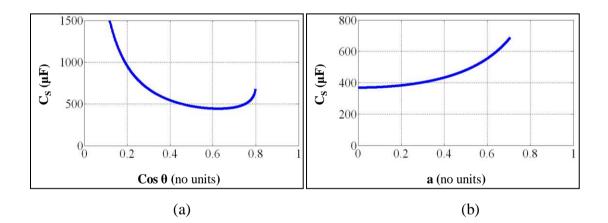

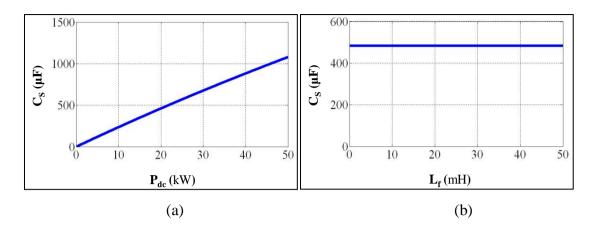

| 107Figure 5.12 DC side equivalent circuit of the CSI-type topology108Figure 5.13 Diagram of the DC-link current control for the CSI-type topology108Figure 5.14 Specification parameters for the step response110Figure 5.15 Comparison of the DC-link current demand ( $I_{dc}^*$ ) and the correspondingDC-link current ( $I_{dc}$ ) obtained from the CSI+SCaps when operating with the PIcontroller using the simulation parameters from Table 5.3111Figure 5.16 Values of the series AC capacitors required for different (a) grid voltageVs and (b) grid frequency ω; where $θ = π/4$ , a=0.8, P <sub>dc</sub> =20kW and L <sub>f</sub> =1mH |

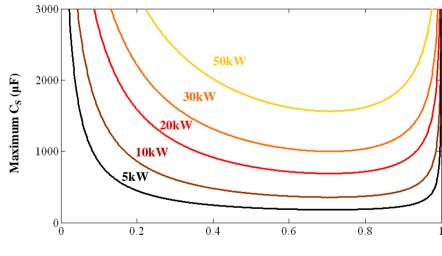

| Figure 5.19 Maximum values of the series AC capacitor required for different AC            |

|--------------------------------------------------------------------------------------------|

| side voltage of the inverter and different load power levels; $V_S$ =415V/50Hz, $L_f$ =1mH |

|                                                                                            |

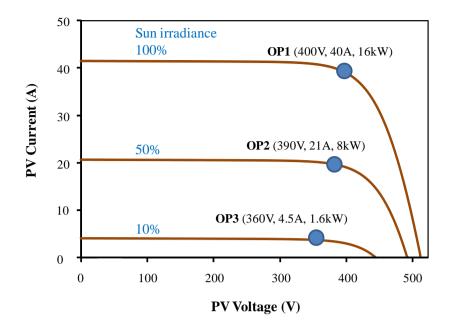

| Figure 5.20 Three operating points (OP1, OP2 and OP3) used to observe the                  |

| performance of the inverter topologies under investigation at different power levels       |

|                                                                                            |

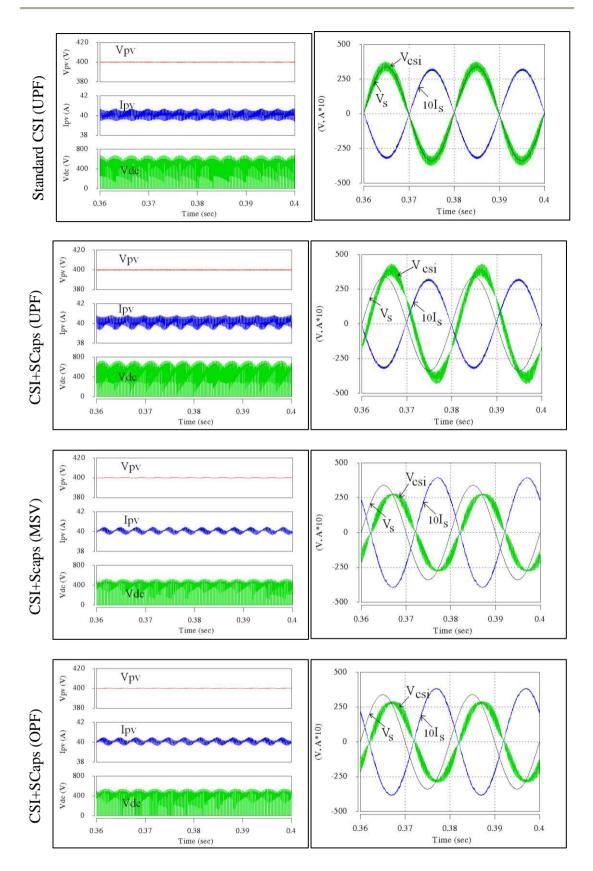

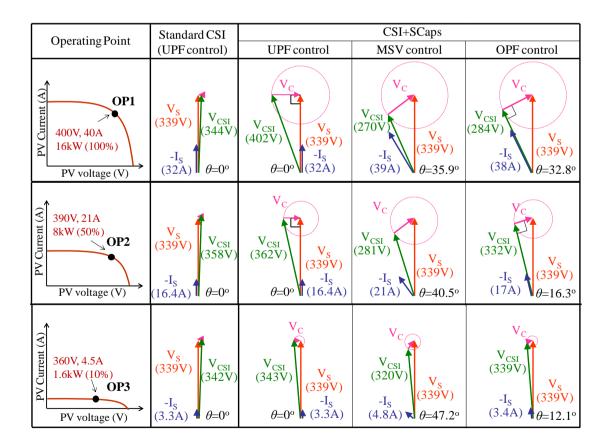

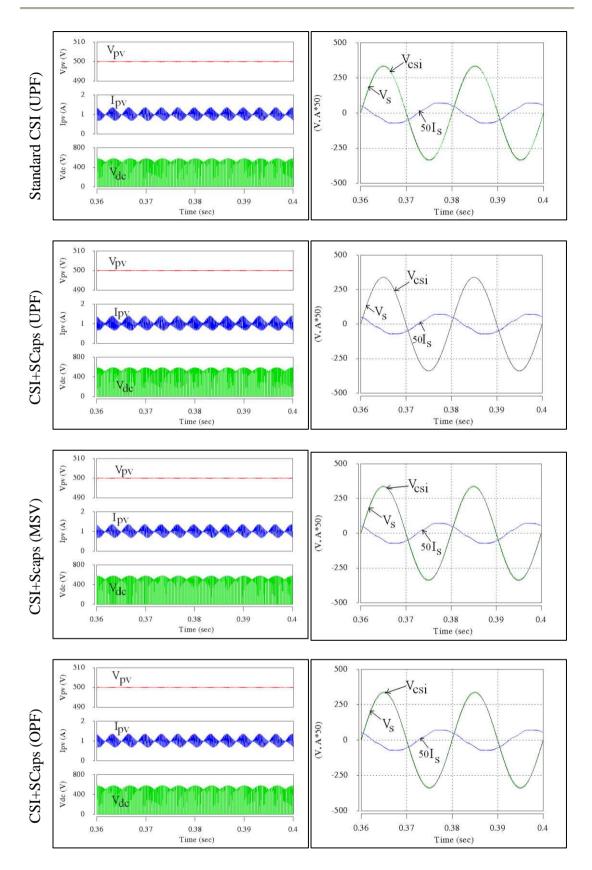

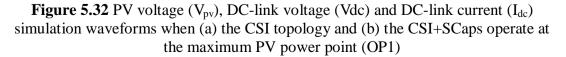

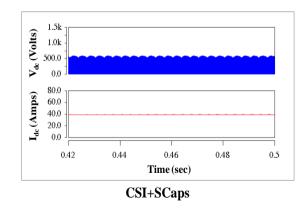

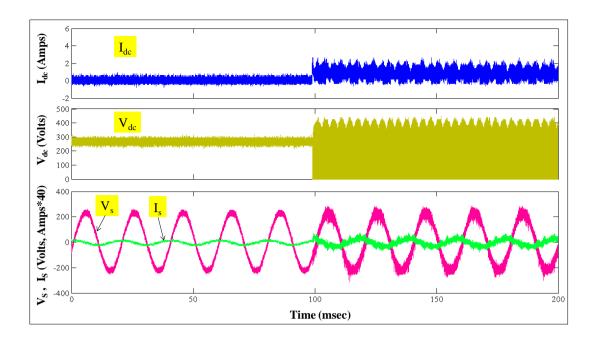

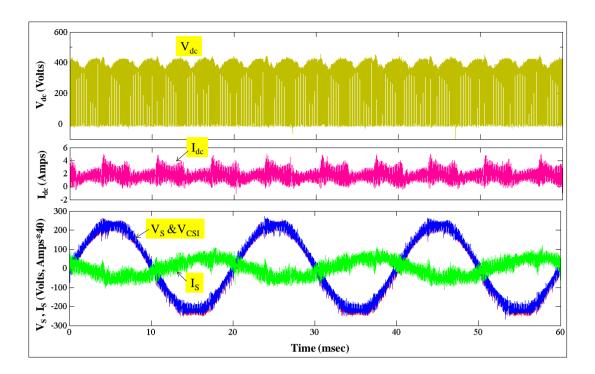

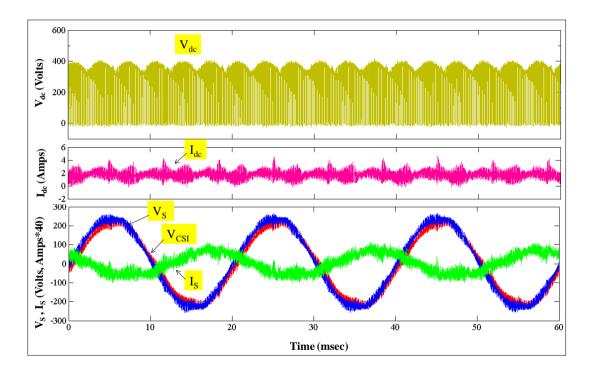

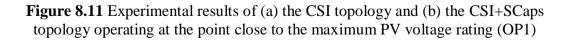

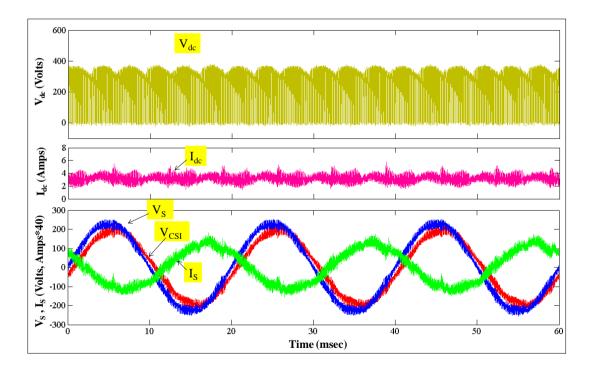

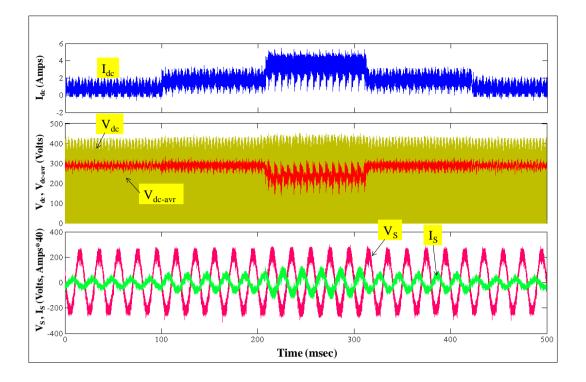

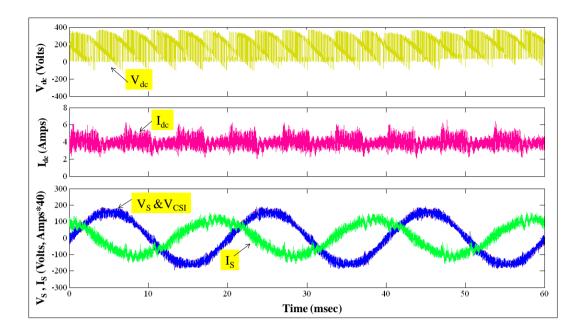

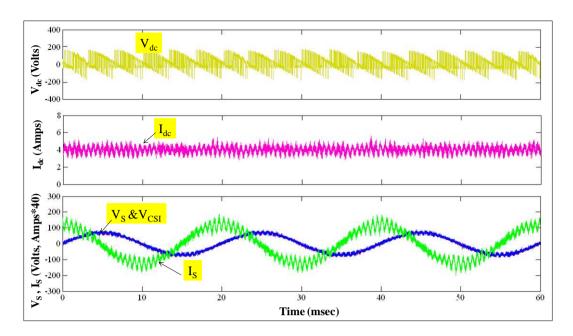

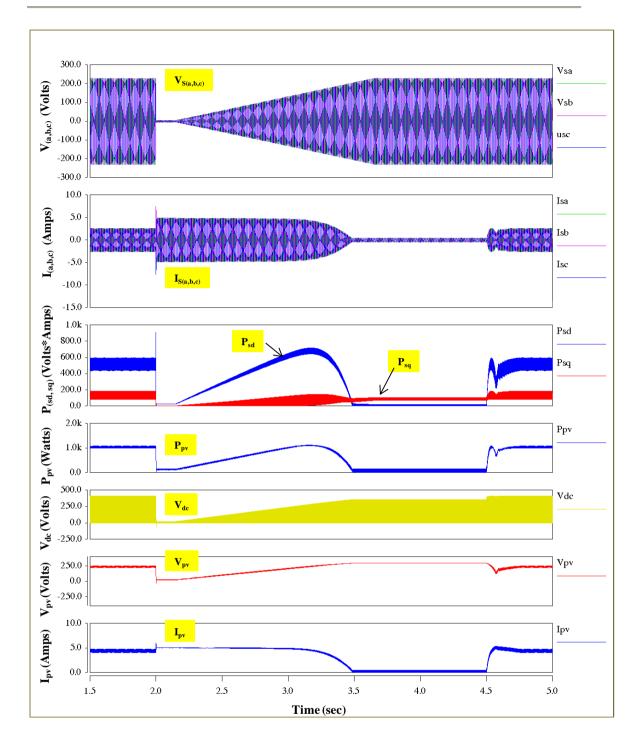

| Figure 5.21 DC side (left) and AC side (right) waveforms of the standard CSI with          |

| UPF control and the CSI+SCaps with UPF, MSV and OPF control when operating at              |

| 100% load power (OP1) 117                                                                  |

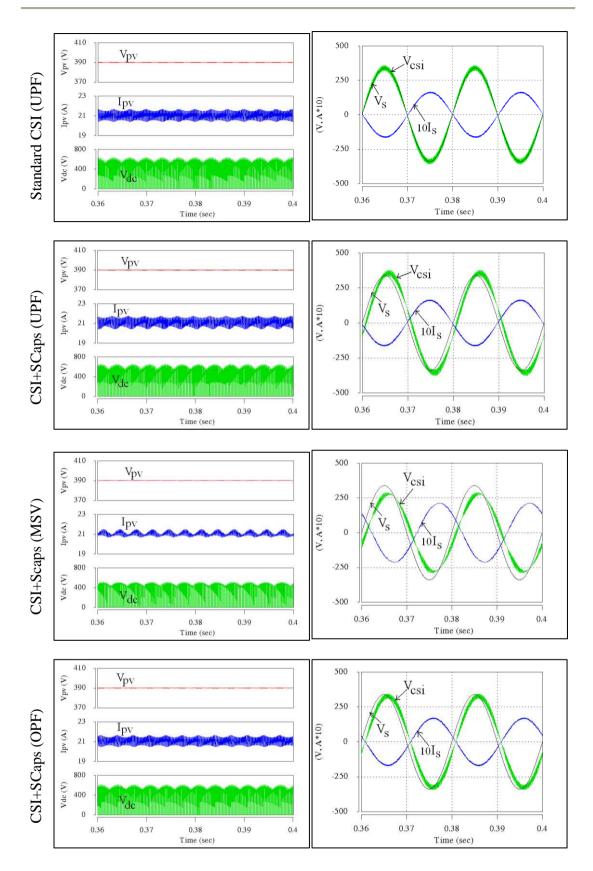

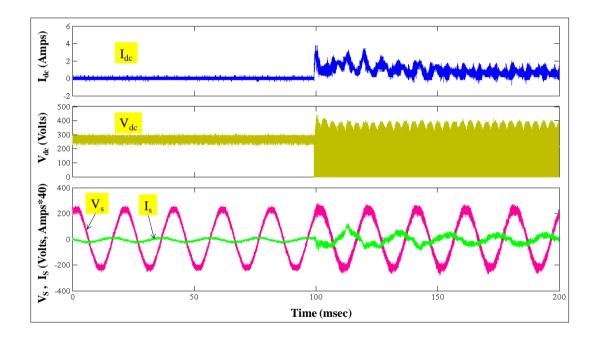

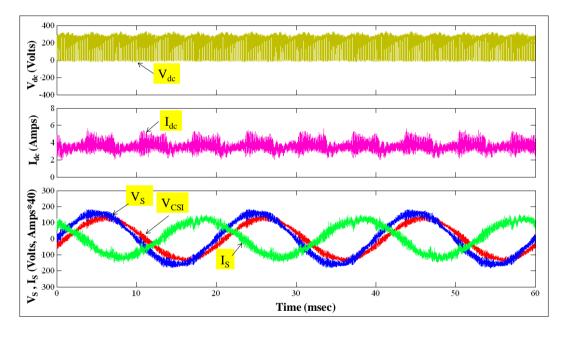

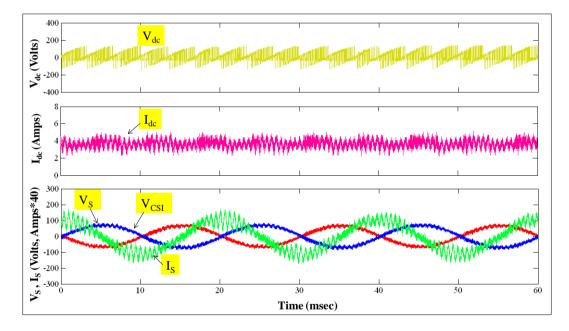

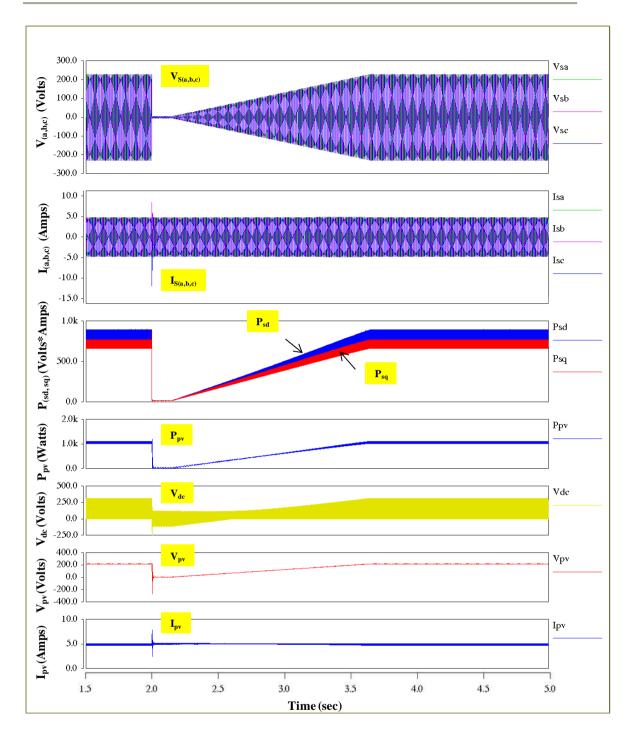

| Figure 5.22 DC side (left) and AC side (right) waveforms of the standard CSI with          |

| UPF control and the CSI+SCaps with UPF, MSV and OPF control when operating at              |

| 50% load power (OP2) 118                                                                   |

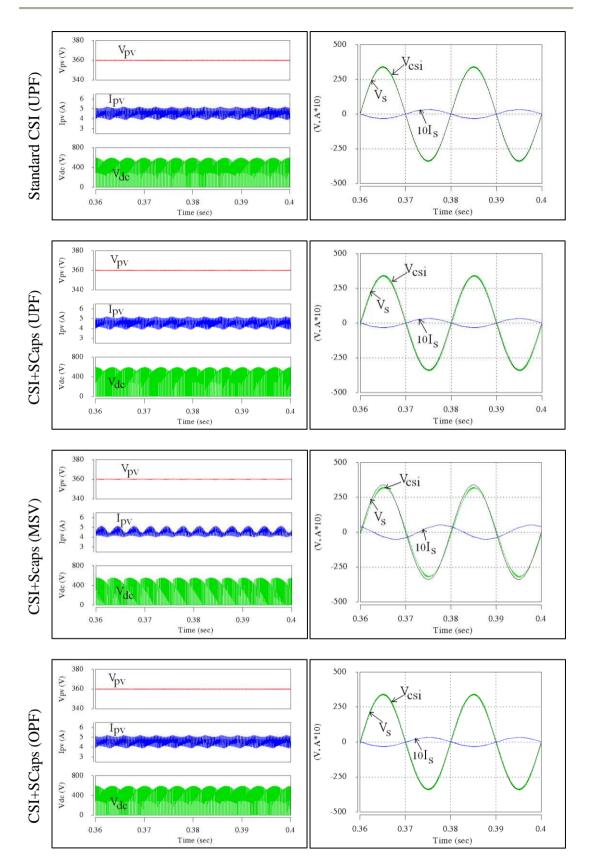

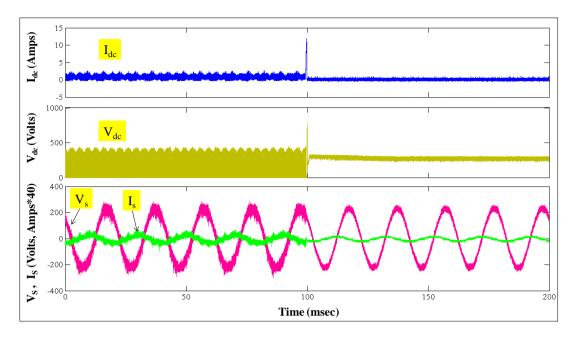

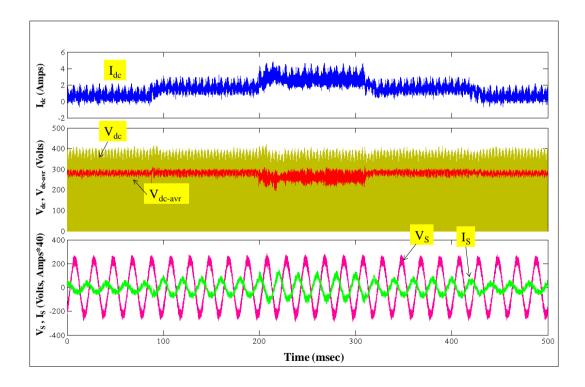

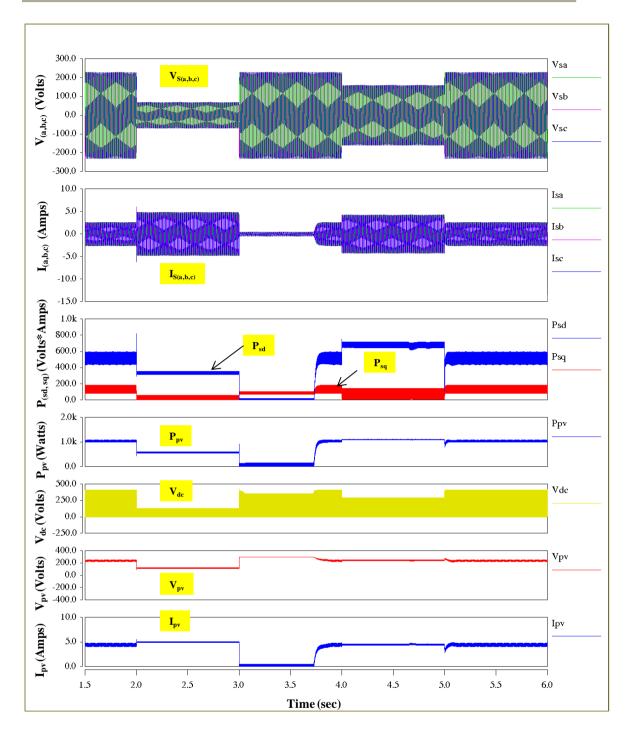

| Figure 5.23 DC side (left) and AC side (right) waveforms of the standard CSI with          |

| UPF control and the CSI+SCaps with UPF, MSV and OPF control when operating at              |

| 10% load power (OP3) 119                                                                   |

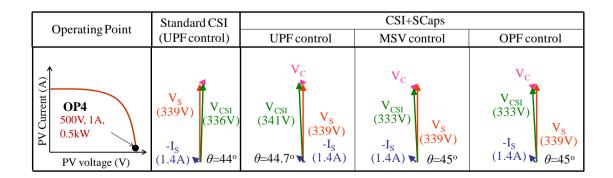

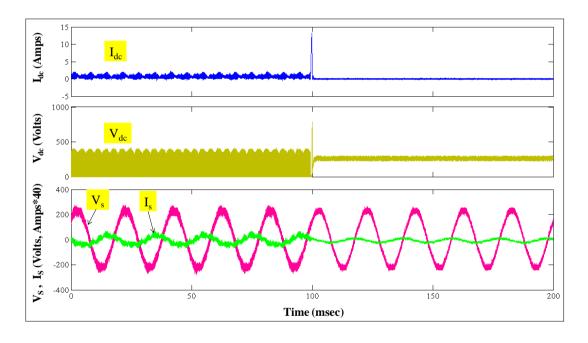

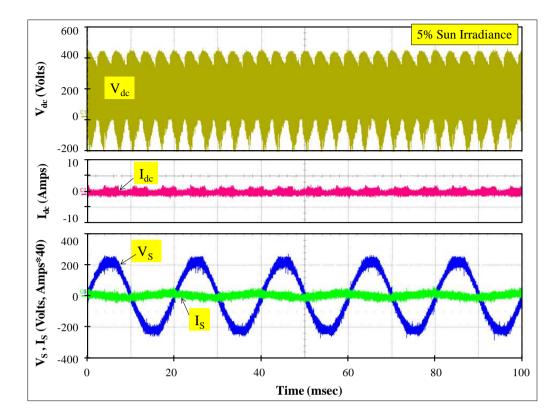

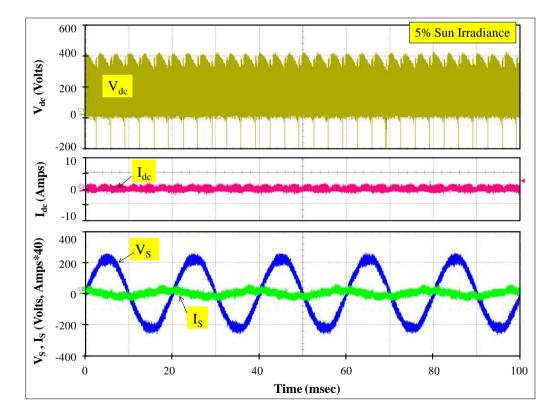

| Figure 5.24 DC side (left) and AC side (right) waveforms of the standard CSI with          |

| UPF control and the CSI+SCaps with UPF, MSV and OPF control when operating                 |

| near no load PV voltage (OP4) 124                                                          |

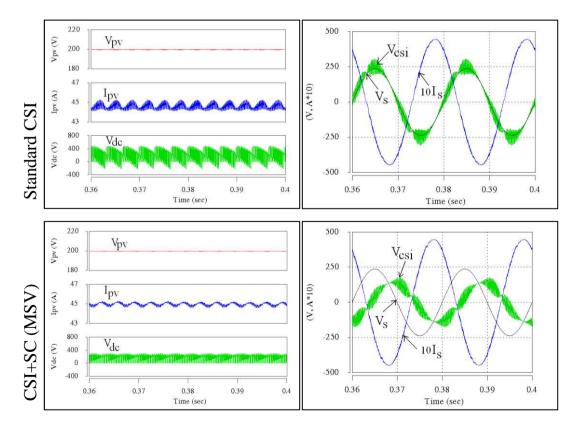

| Figure 5.25 DC side (left) and AC side (right) waveforms of the standard CSI and the       |

| CSI+SCaps when operating during 30% grid voltage dip (OP5) 126                             |

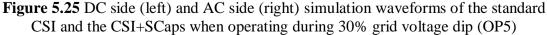

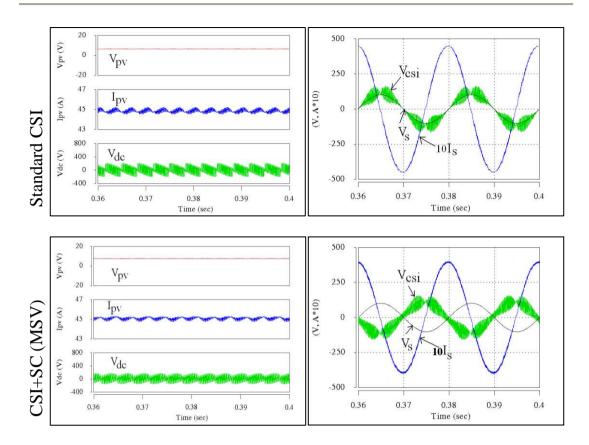

| Figure 5.26 DC side (left) and AC side (right) waveforms of the standard CSI and the       |

| CSI+SCaps when operating during 70% grid voltage dip (OP6) 127                             |

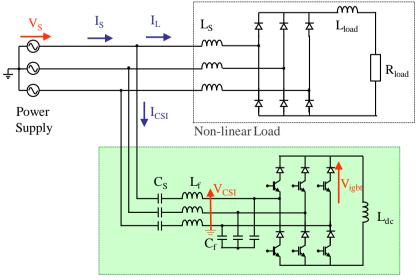

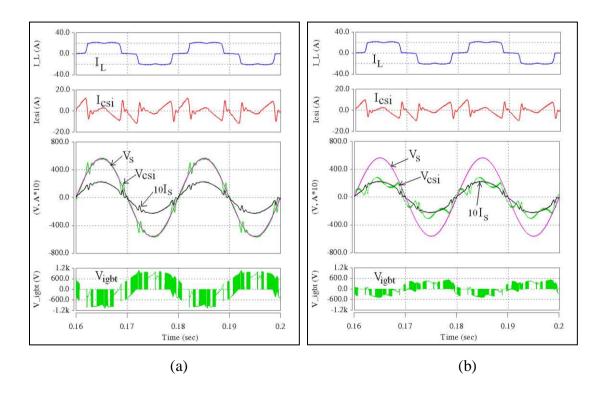

| Figure 5.27 The CSI+SCaps shunt active power filter                                        |

| Figure 5.28 Simulation waveforms when compensating 20kVA RL-type load in 690               |

| supply voltage with the harmonic generated from (a) the traditional CSI active power       |

| filter and (b) the CSI+SCaps active power filter                                           |

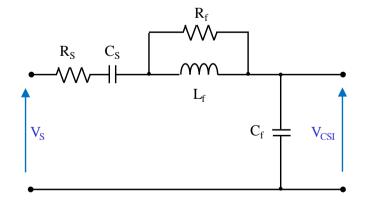

| Figure 5.29 Equivalent circuit of the AC filter of the CSI+SCaps topology                  |

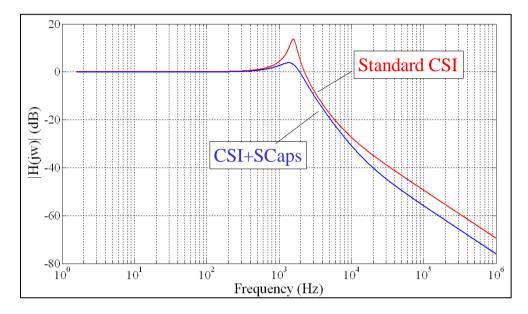

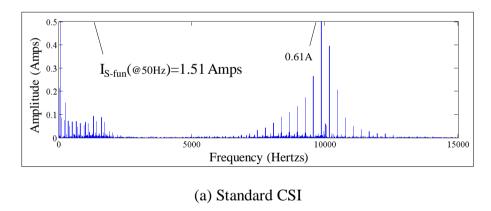

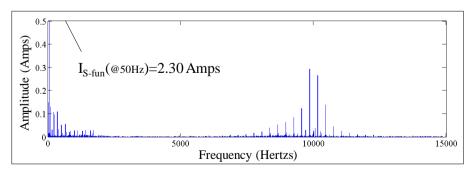

| Figure 5.30 Comparison of the harmonic amplitude attenuation performance of the            |

| AC filters used in the standard CSI topology versus the CSI+SCaps topology 132             |

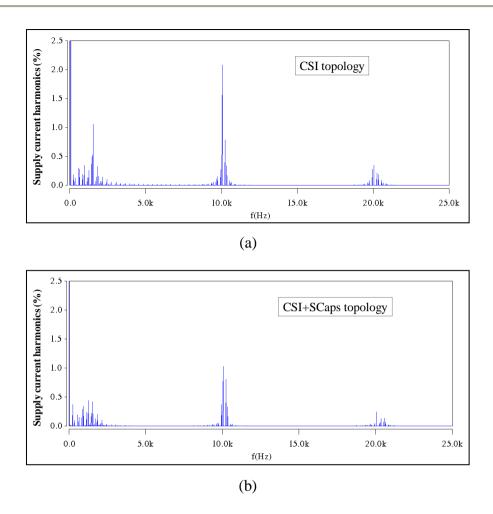

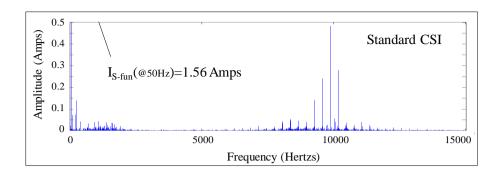

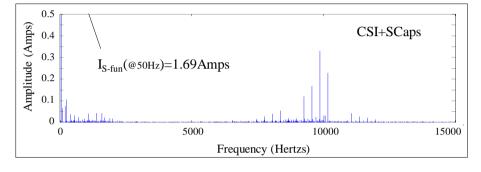

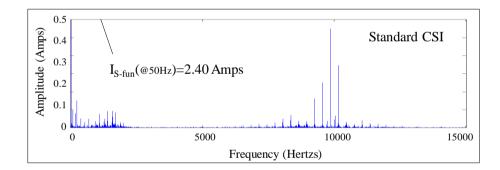

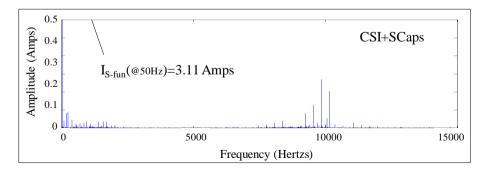

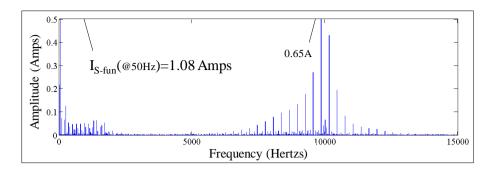

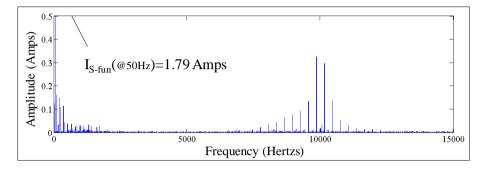

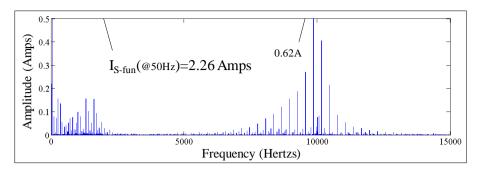

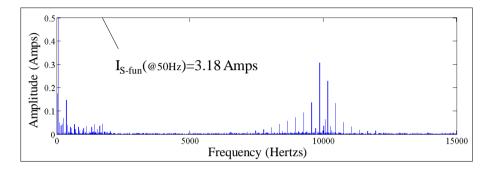

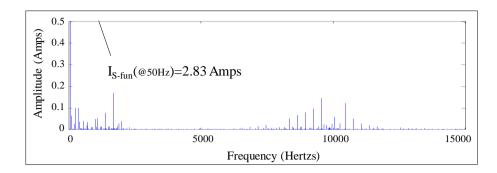

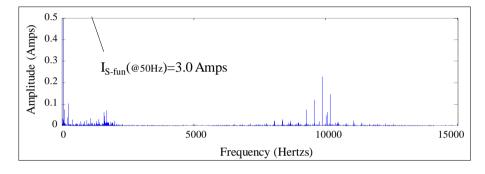

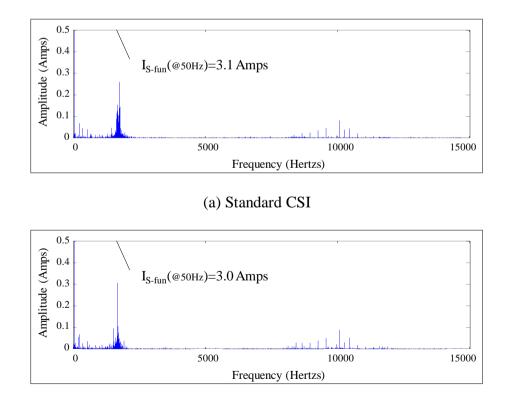

| Figure 5.31 Supply current harmonic amplitudes of (a) the standard CSI topology and        |

| (b) the CSI+SCaps topology when operating at the maximum PV power point (OP1)              |

| and using simulation parameter in Table 5.5 133                                            |

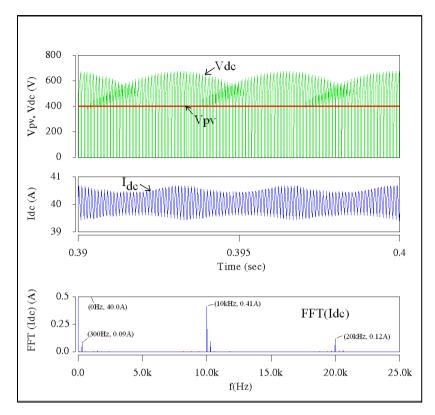

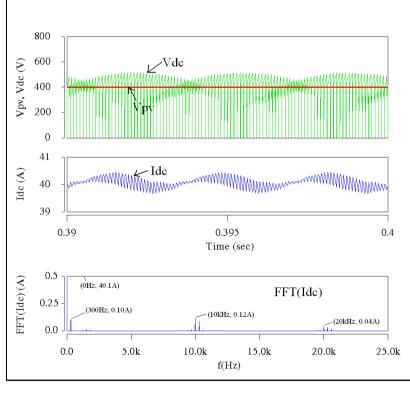

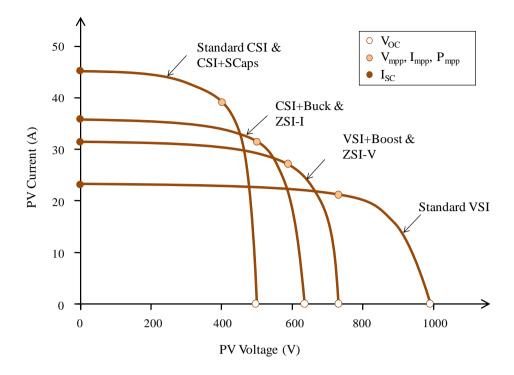

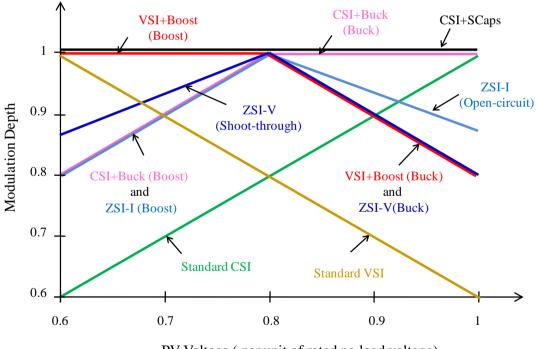

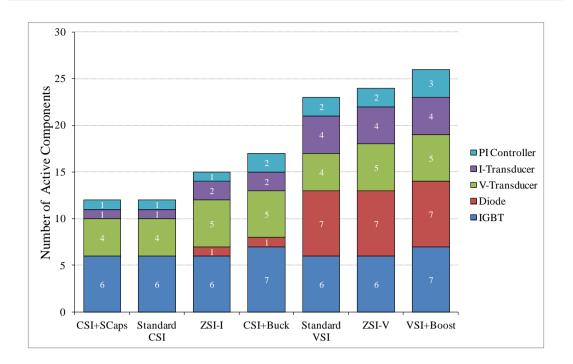

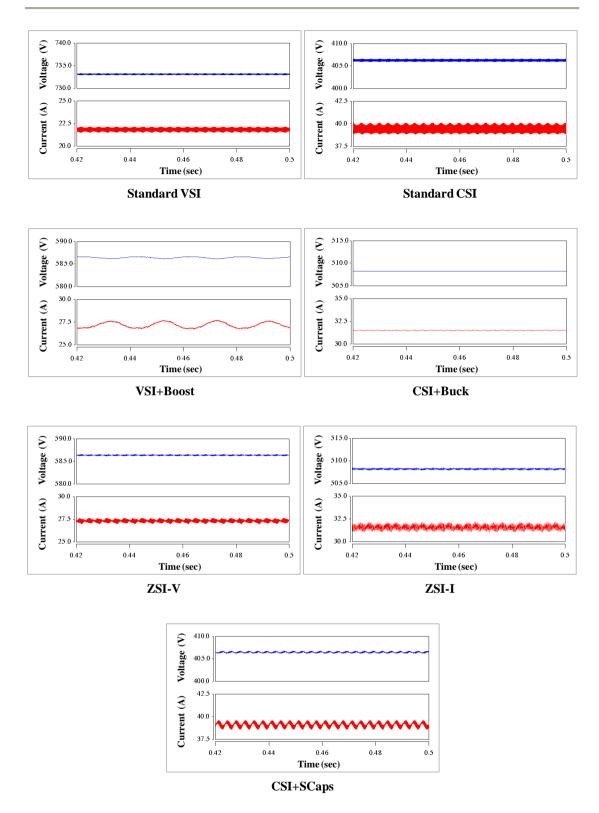

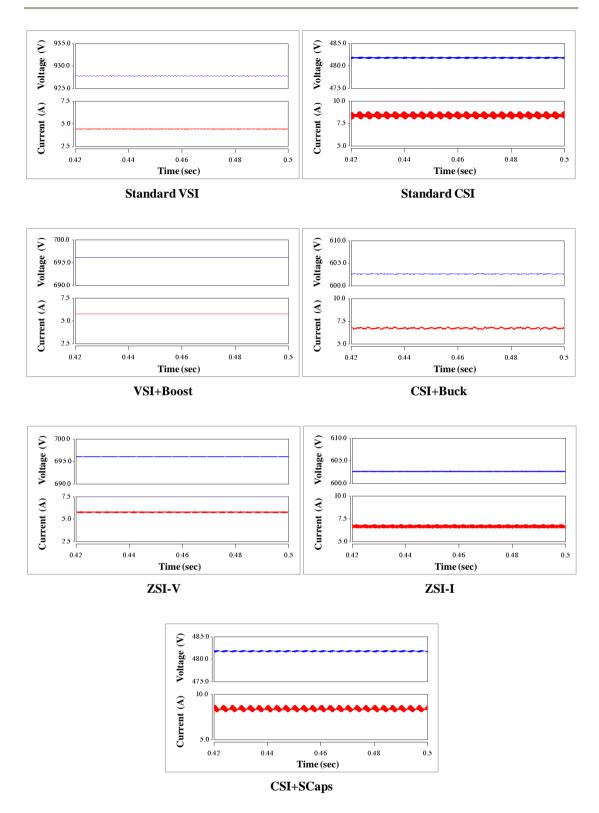

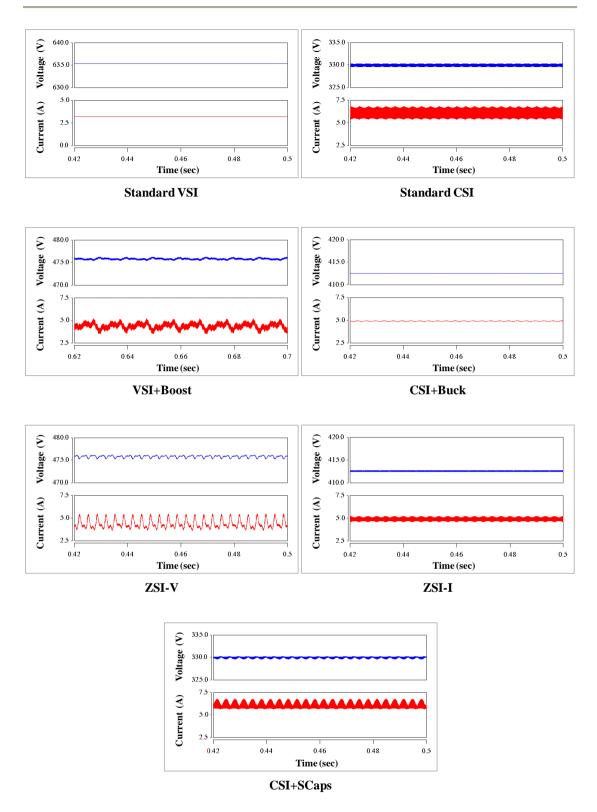

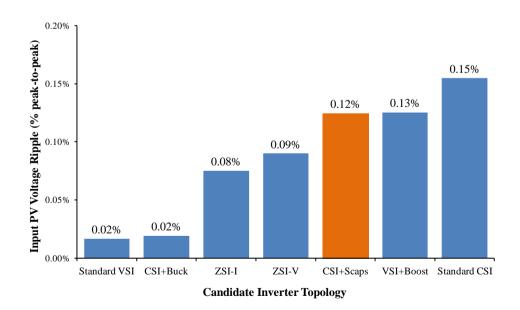

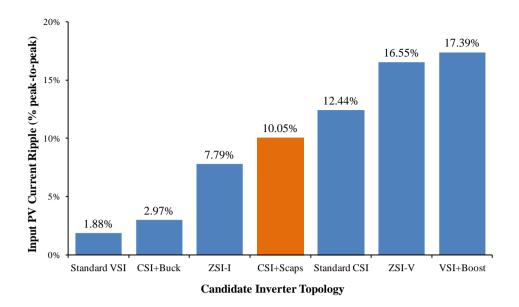

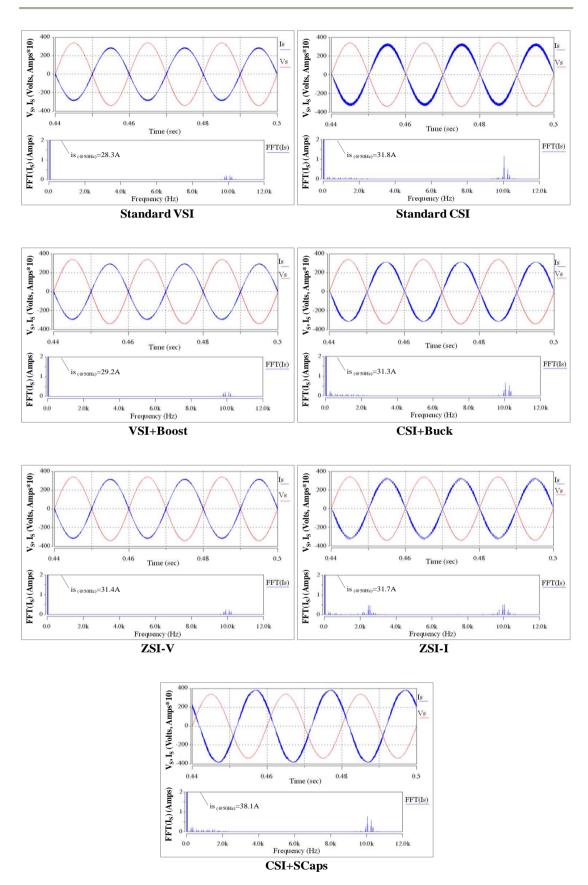

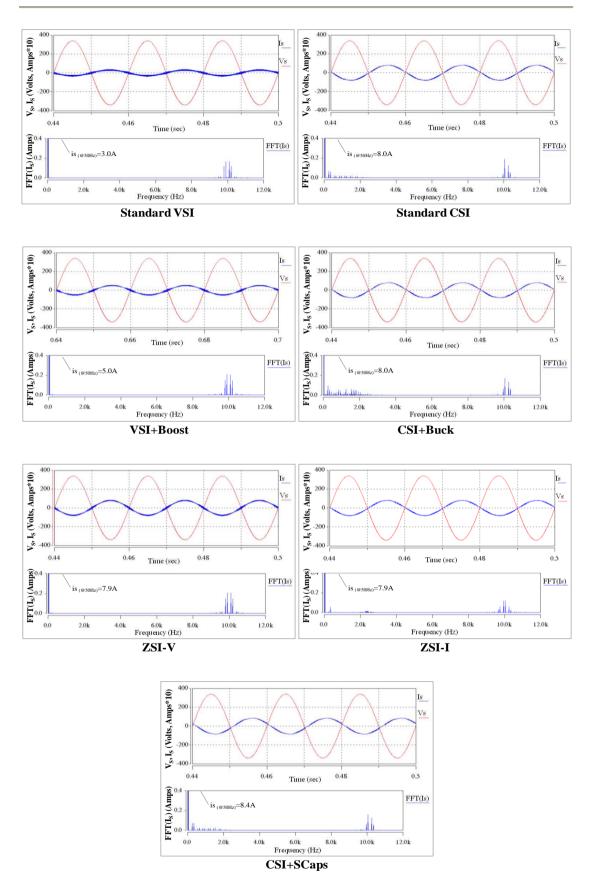

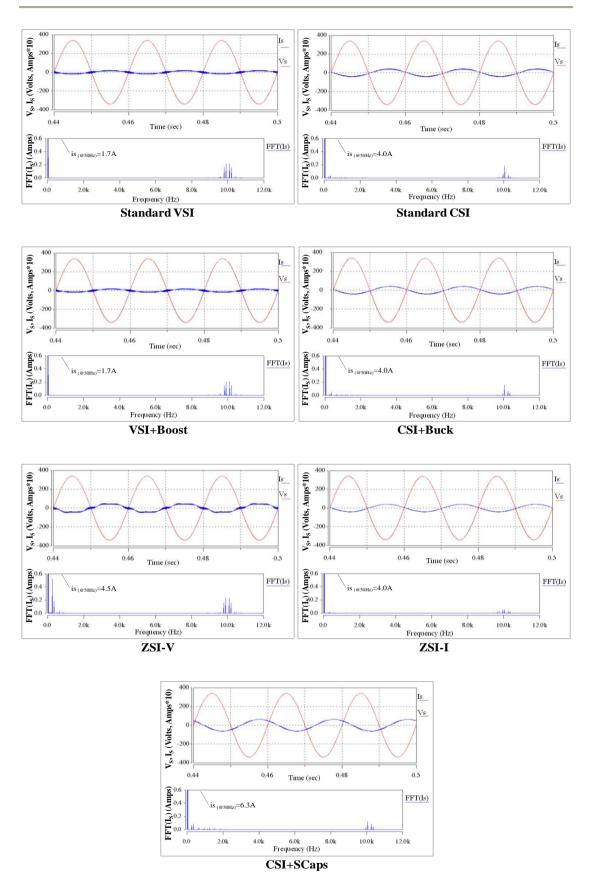

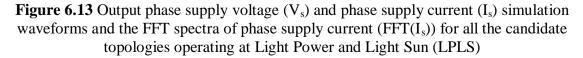

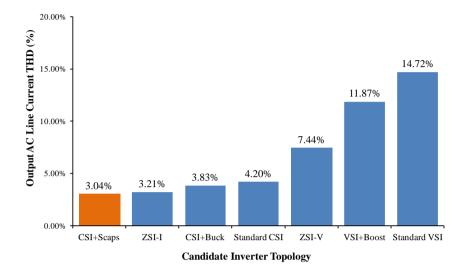

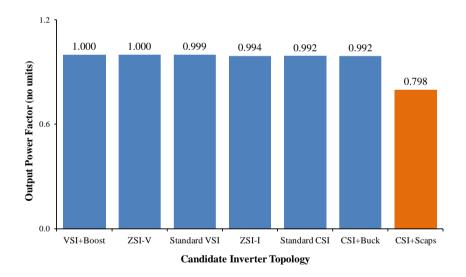

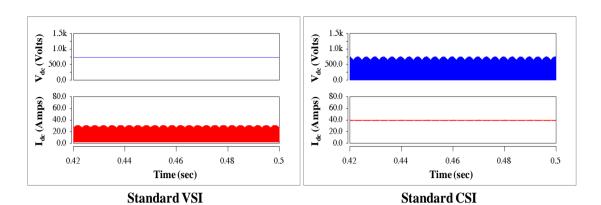

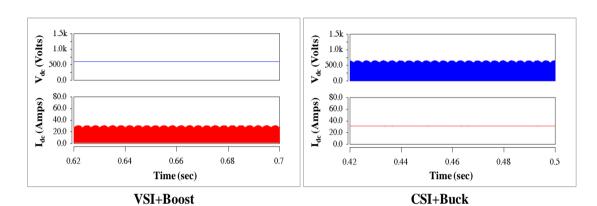

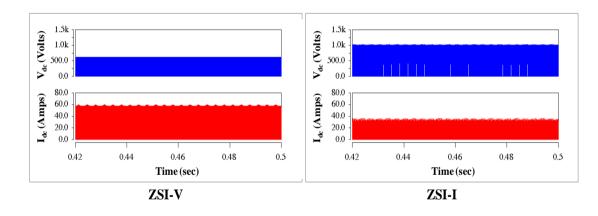

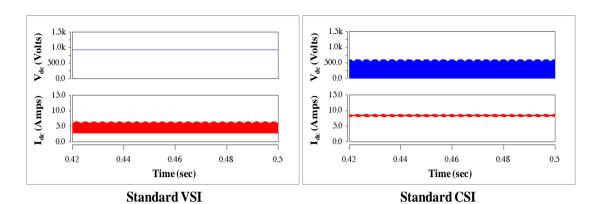

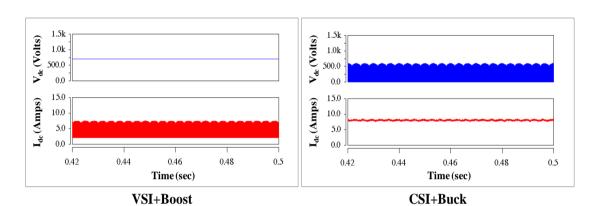

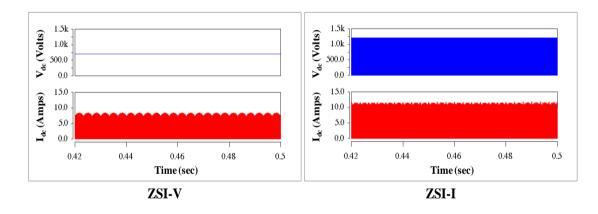

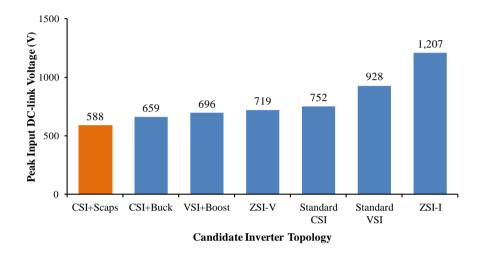

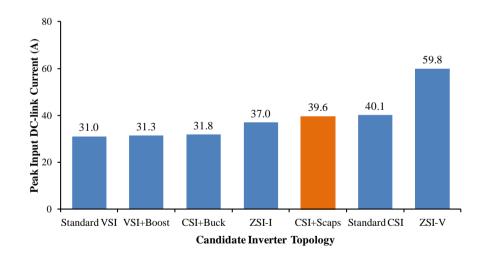

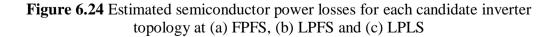

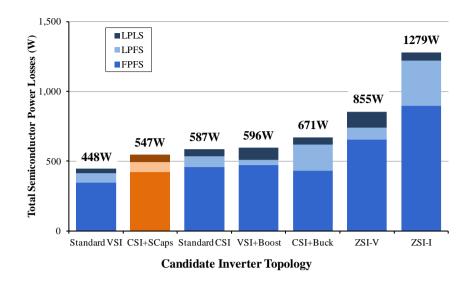

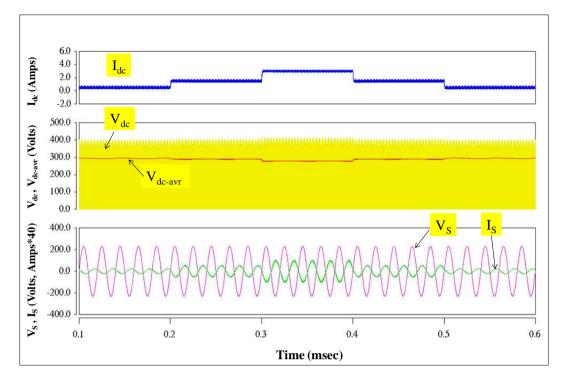

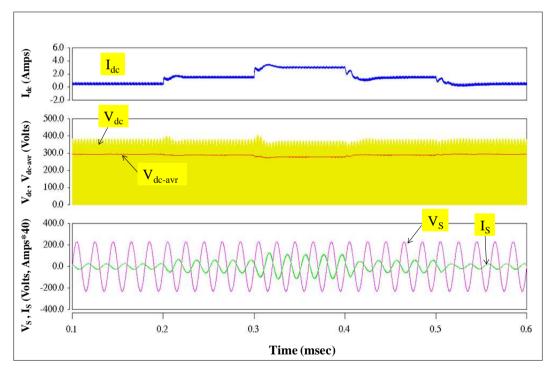

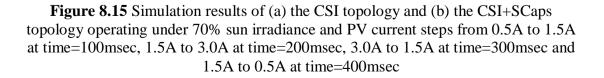

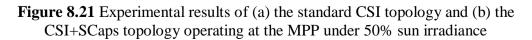

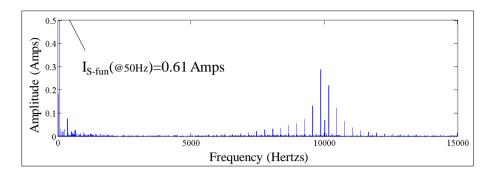

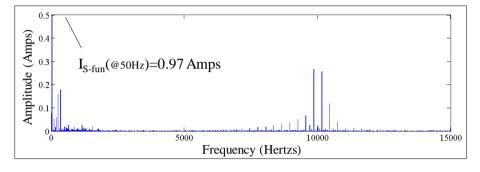

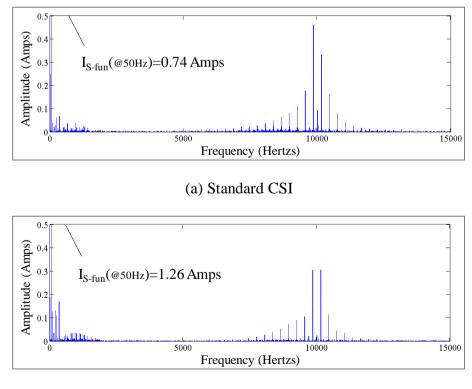

Figure 6.1 PV voltage and current ratings required for each candidate inverter Figure 6.2 Plot of modulation depth (m) curves as a function of operating PV voltages for each candidate inverter topology (according to Table 6.3) ...... 142 Figure 6.3 Required active components for each candidate inverter topology...... 144 Figure 6.4 Three different PV operating points for observing the size of passive components required for each candidate topology......145 Figure 6.5 Size of total required passive components of each candidate topology.. 147 Figure 6.6 Input voltage and current waveforms for all the candidate topologies operating at Full Power and Full Sun (FPFS) ...... 149 Figure 6.7 Input voltage and current waveforms for all the candidate topologies Figure 6.8 Input voltage and current waveforms for all the candidate topologies operating at Light Power and Light Sun (LPLS) ...... 151 Figure 6.10 Average input PV current ripple of each candidate topology ...... 154 **Figure 6.11** Output phase supply voltage  $(V_s)$  and phase supply current  $(I_s)$ waveforms and the FFT spectra of phase supply current (FFT(i<sub>s</sub>)) for all the candidate **Figure 6.12** Output phase supply voltage  $(V_s)$  and phase supply current  $(I_s)$ waveforms and the FFT spectra of phase supply current ( $FFT(I_s)$ ) for all the candidate topologies operating at Low Power and Full Sun (LPFS) ...... 157 Figure 6.13 Output phase supply voltage  $(V_s)$  and phase supply current  $(I_s)$ waveforms and the FFT spectra of phase supply current  $(FFT(I_s))$  for all the candidate Figure 6.14 Average output supply current THD of each candidate inverter topology

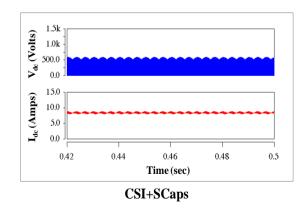

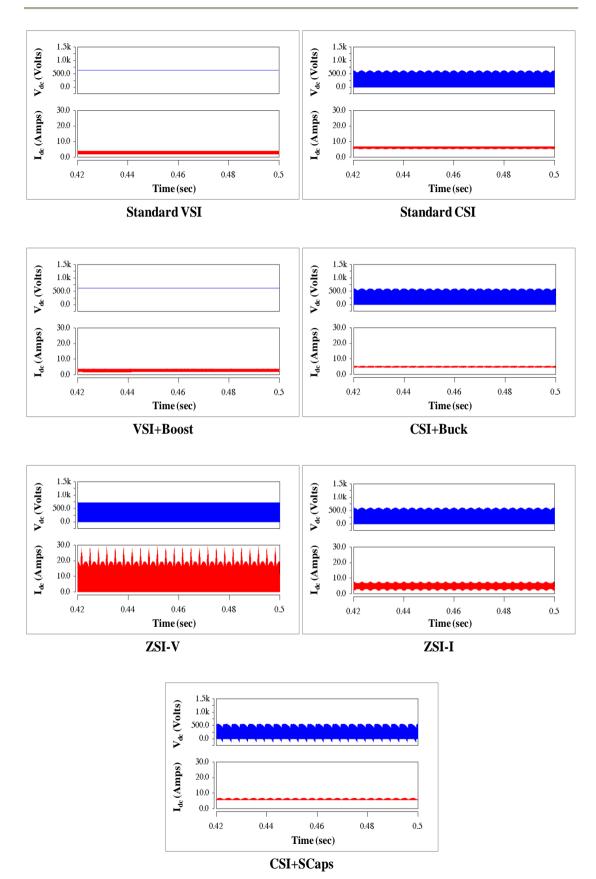

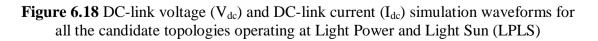

| Figure 6.17 DC-link voltage (V_dc) and DC-link current (I_dc) waveforms for all the               |

|---------------------------------------------------------------------------------------------------|

| candidate topologies operating at Low Power and Full Sun (LPFS) 162                               |

| Figure 6.18 DC-link voltage (V_dc) and DC-link current (I_dc) waveforms for all the               |

| candidate topologies operating at Light Power and Light Sun (LPLS) 163                            |

| Figure 6.19 Maximum voltage stress on power semiconductors for each candidate                     |

| topology                                                                                          |

| Figure 6.20 Maximum current stress on power semiconductors for each candidate                     |

| inverter topology                                                                                 |

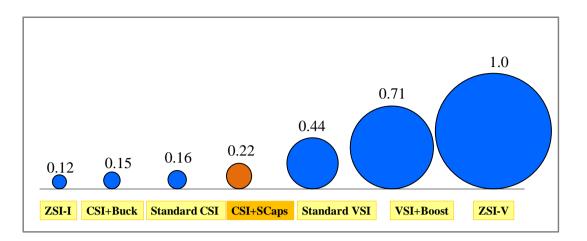

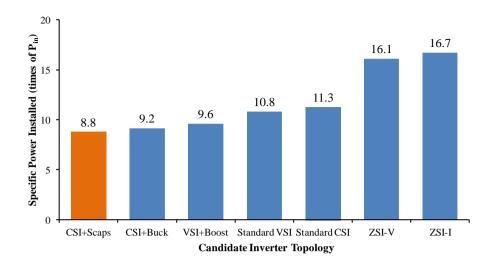

| Figure 6.21 Specific power installed in power semiconductors (Estimated cost of                   |

| power semiconductors) of each candidate inverter topology 167                                     |

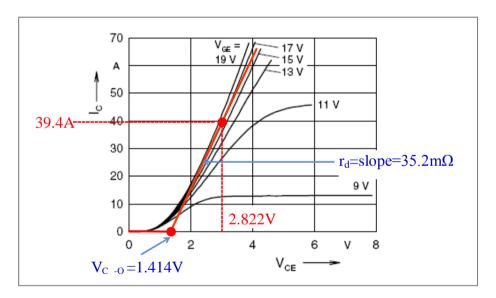

| Figure 6.22 Methods used to determine $V_{CE-O}$ and $r_d$ for the estimation of the              |

| semiconductor power losses                                                                        |

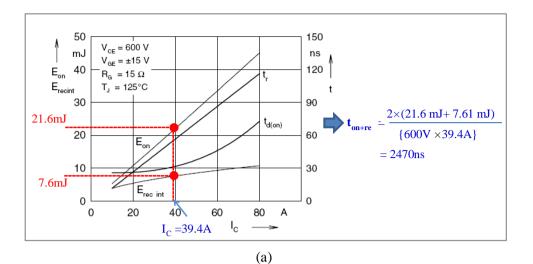

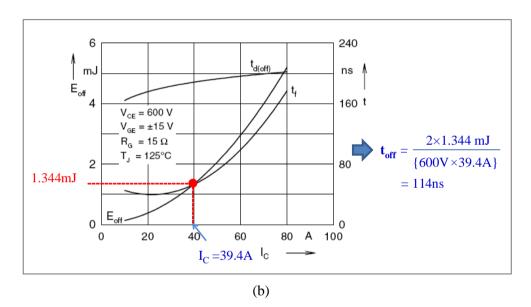

| Figure 6.23 Methods used to determine (a) $t_{on+rr}$ and (b) $t_{off}$ for the estimation of the |

| semiconductor power losses                                                                        |

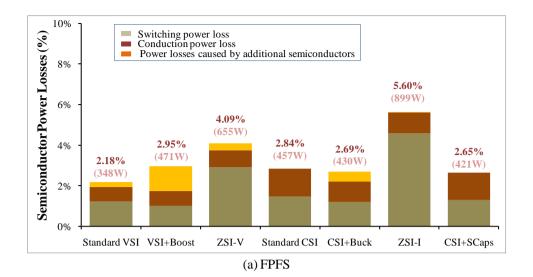

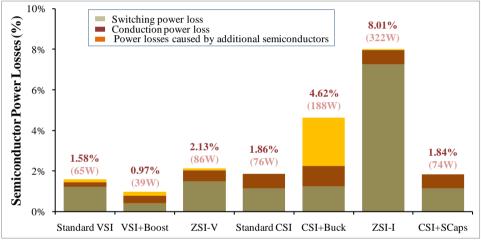

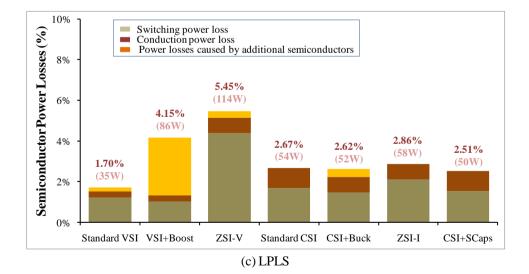

| Figure 6.24 Estimated semiconductor power losses for each candidate inverter                      |

| topology at (a) FPFS, (b) LPFS, and (c) LPLS                                                      |

| Figure 6.25 Total semiconductor power loss for each candidate inverter topology 174               |

| Figure 6.26 Efficiency curves and European efficiencies ( $\eta_{euro}$ ) for all the candidate   |

| topologies                                                                                        |

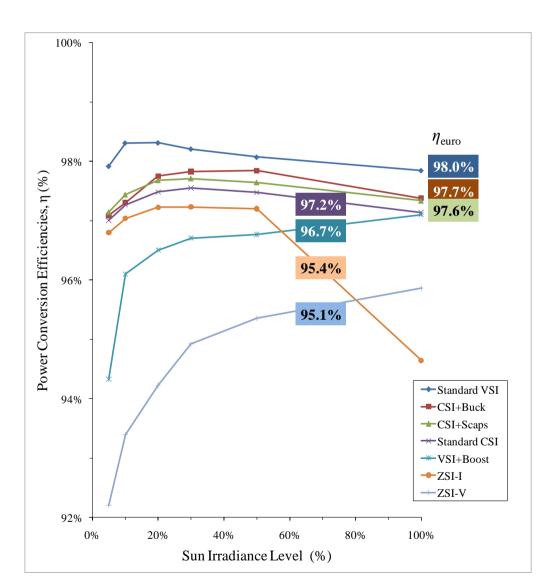

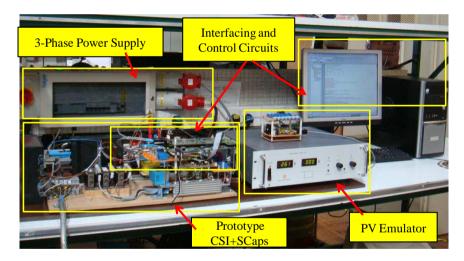

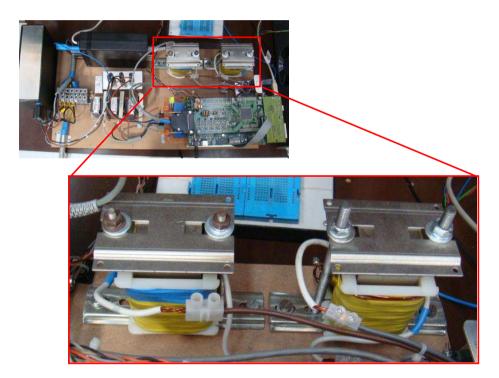

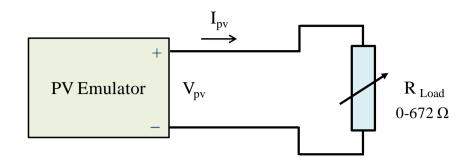

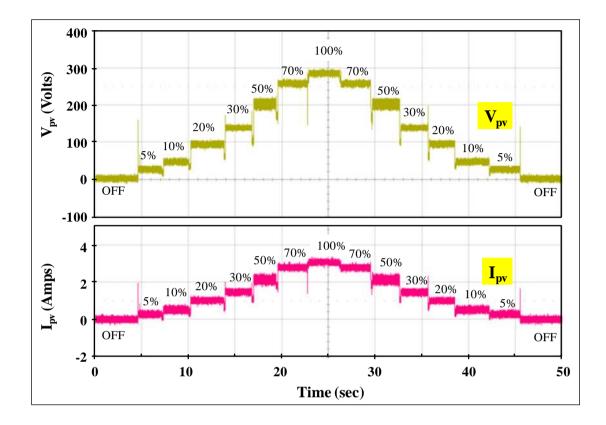

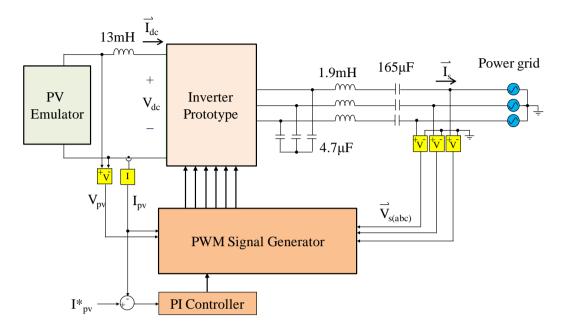

| Figure 7.1 Block diagram of the experimental test-rig                               |

|-------------------------------------------------------------------------------------|

| Figure 7.2 Photograph of the experimental test-rig                                  |

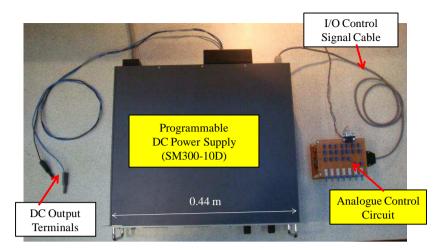

| Figure 7.3 Hardware configuration of the PV emulator                                |

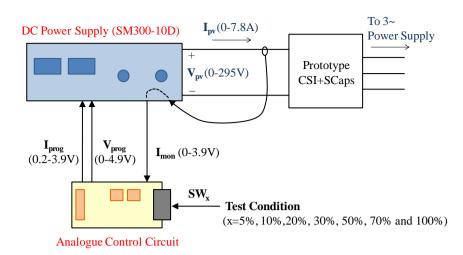

| Figure 7.4 Operational diagram for the PV emulator                                  |

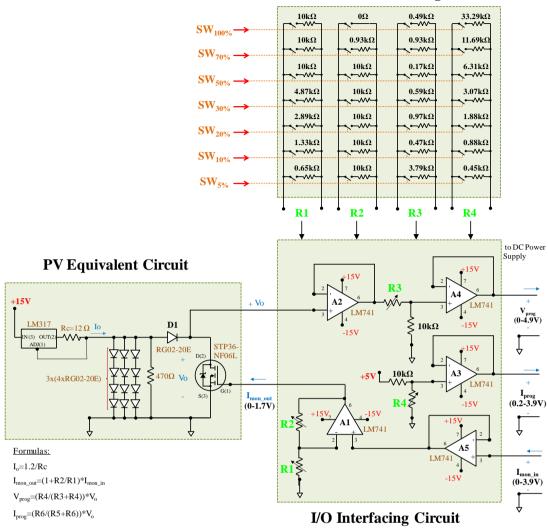

| Figure 7.5 Circuit diagram of the analogue control circuit                          |

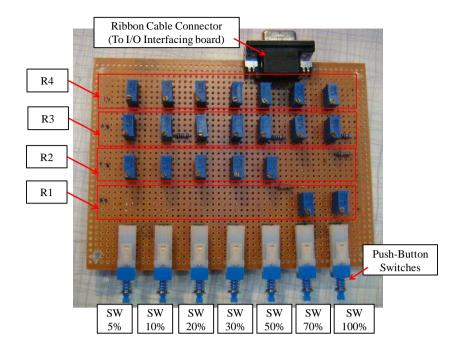

| Figure 7.6 Hardware configuration used for the test condition selecting circuit 191 |

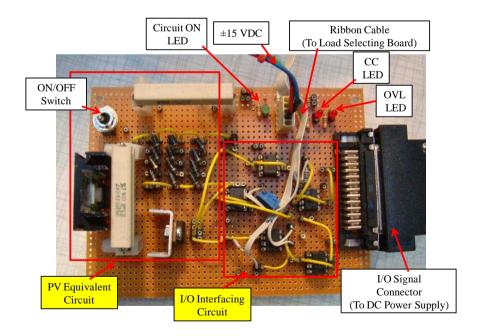

| Figure 7.7 Hardware configuration used for the I/O interfacing circuit and the PV   |

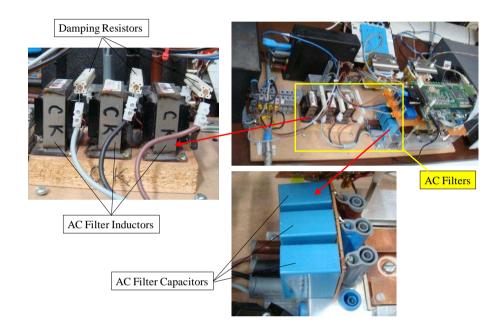

| equivalent circuit                                                                  |

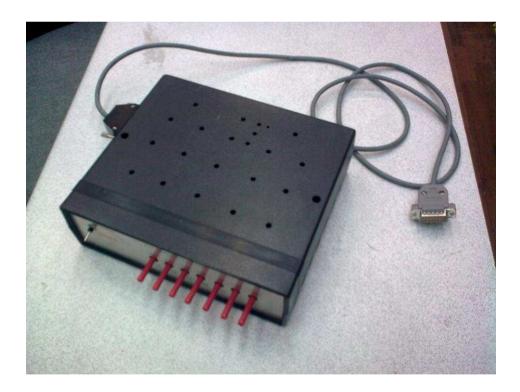

| Figure 7.8 Complete hardware for the analogue control circuit 193                   |

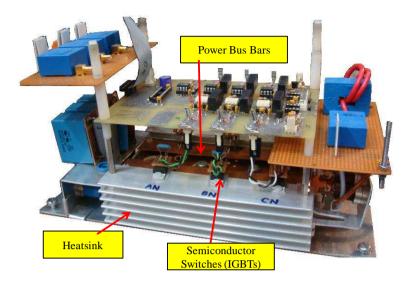

| Figure 7.9 Photograph of the prototype CSI+SCaps 194                                |

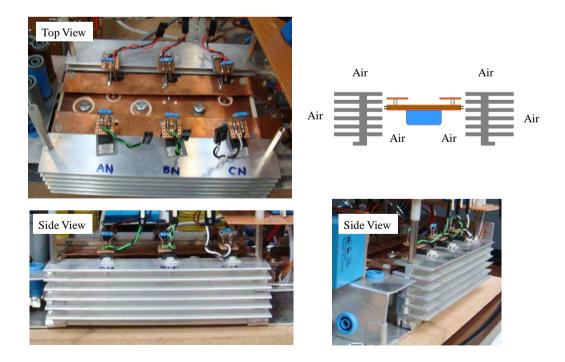

| Figure 7.10 Photograph of the CSI power module                                      |

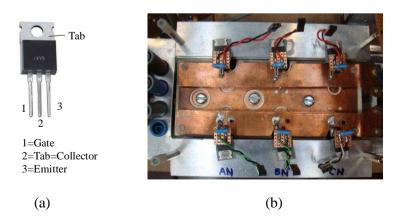

| Figure 7.11 Photographs of (a) the RB-IGBT model IXRA15N120 and (b) the             |

| mounting layout of the RB-IGBTs                                                     |

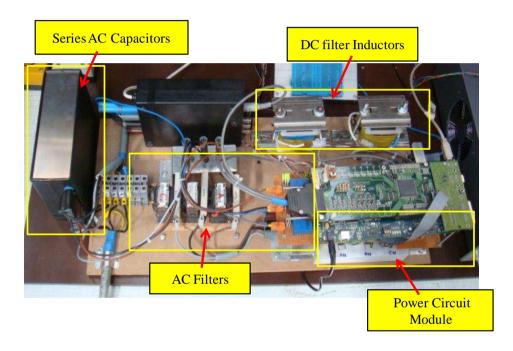

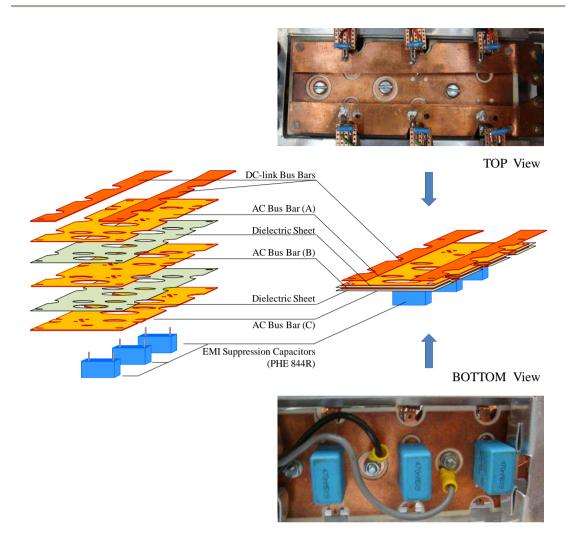

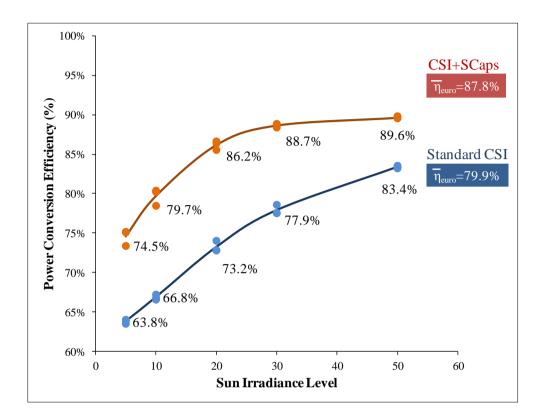

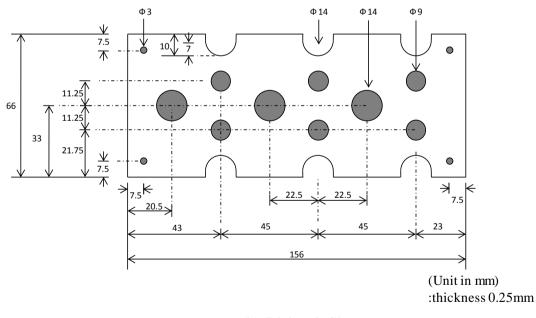

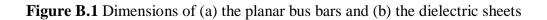

| Figure 7.12 Geometrical structure of the Power Bus Bars of the prototype CSI+SCaps     |

|----------------------------------------------------------------------------------------|

|                                                                                        |

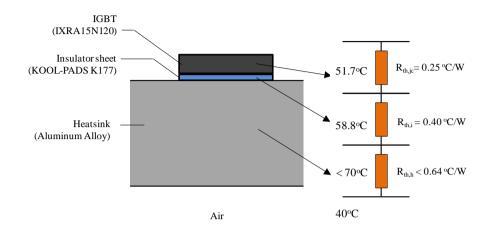

| Figure 7.13 Structure of the CSI power module and all relevant parameters when the     |

| converter prototype operates at PV output of 3 kW                                      |

| Figure 7.14 Photographs of the designed heatsink                                       |

| Figure 7.15 Photographs of the DC-link inductors                                       |

| Figure 7.16 Photographs of the AC filter components                                    |

| Figure 7.17 Photographs of the series AC capacitors                                    |

| Figure 7.18 Circuit diagram of the gate drive circuit for each single IGBT 203         |

| Figure 7.19 Photographs of the gate driver circuit board 203                           |

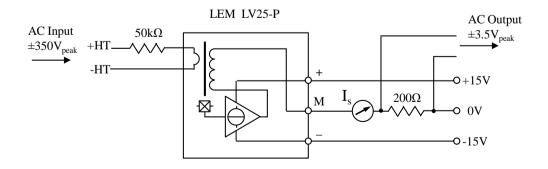

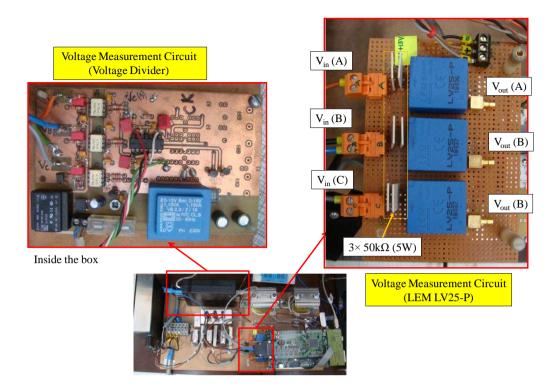

| Figure 7.20 Circuit diagram of the AC voltage measurement circuit using LEM            |

| LV25-P voltage transducers                                                             |

| Figure 7.21 Photographs of the AC voltage measurement circuits: (a) using voltage      |

| divider technology and (b) using the commercial LEM LV25-P voltage transducers         |

|                                                                                        |

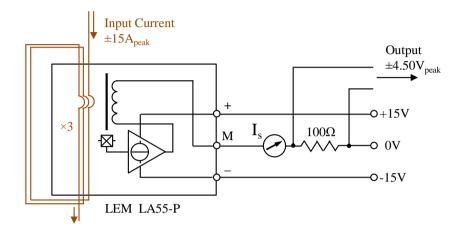

| Figure 7.22 Circuit diagram of the DC current measurement circuit 206                  |

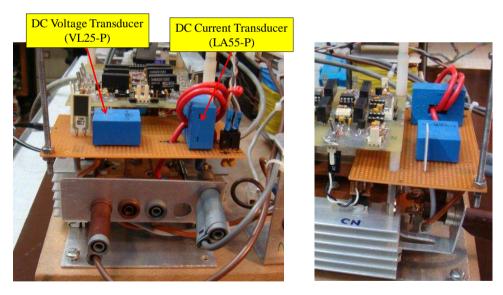

| Figure 7.23 Photographs of the DC voltage and current measurement circuit 206          |

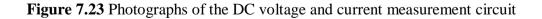

| Figure 7.24 Overview of the control platform of the prototype CSI+SCaps                |

| Figure 7.25 Photograph of the DSP board                                                |

| Figure 7.26 Photographs of (a) the FPGA board and (b) its connections 209              |

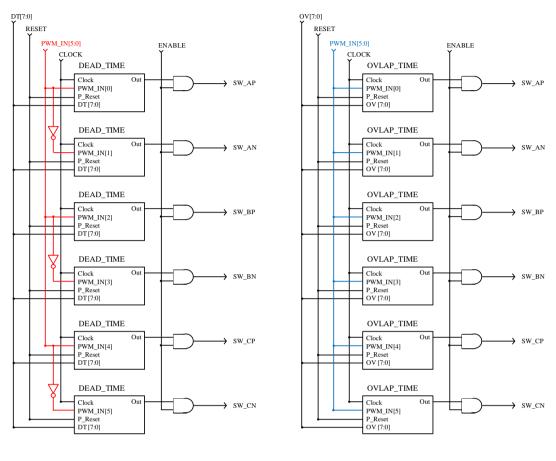

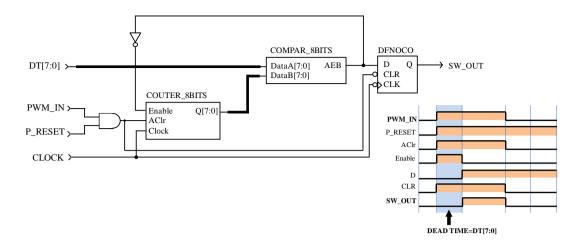

| Figure 7.27 Comparison of (a) original schematic and (b) modified schematic for the    |

| FPGA code in order to achieve independent gate control signals required for the CSI    |

|                                                                                        |

| Figure 7.28 Comparison of (a) original schematic and (b) modified schematic for the    |

| FPGA code in order to achieve the overlap time implementation for the CSI 211          |

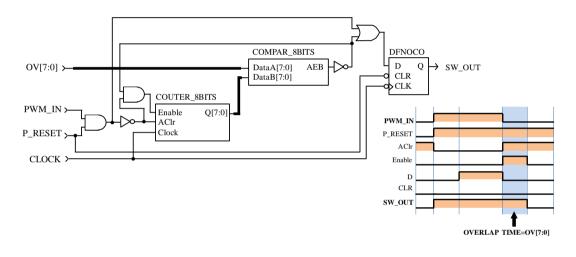

| Figure 7.29 DC-link clamp circuit: (a) the circuit diagram and (b) photographs of the  |

| DC-link clamp circuit shown the inside view (top right) and the outside (bottom right) |

| of the cover box                                                                       |

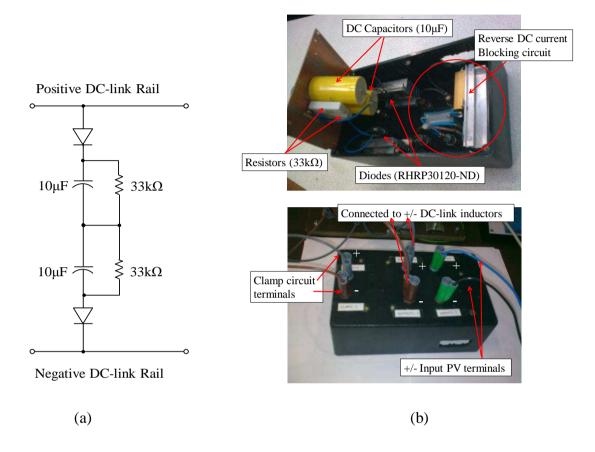

| Figure 7.30 Photographs of the three-phase AC electrical network                       |

|                                                                                        |

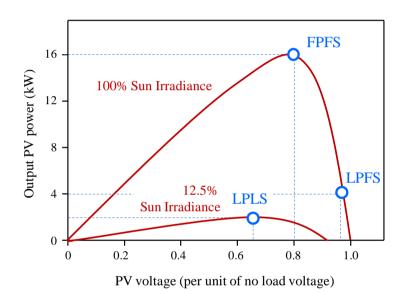

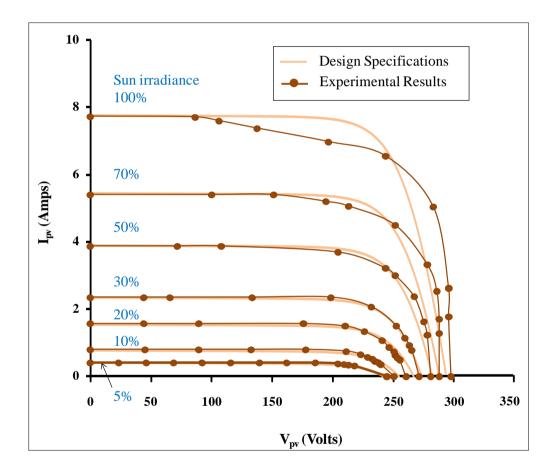

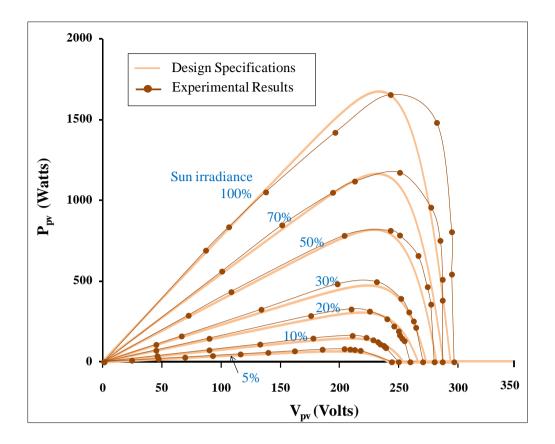

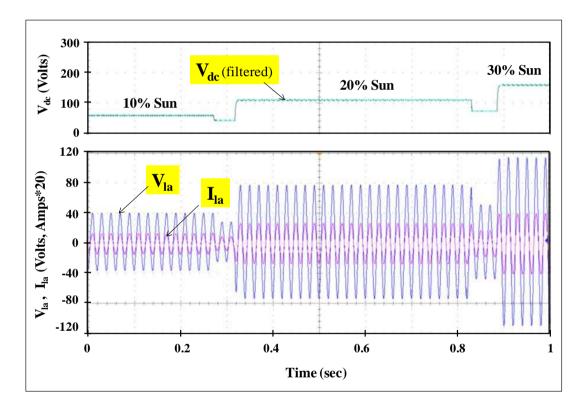

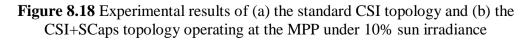

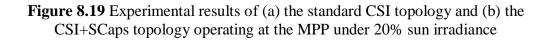

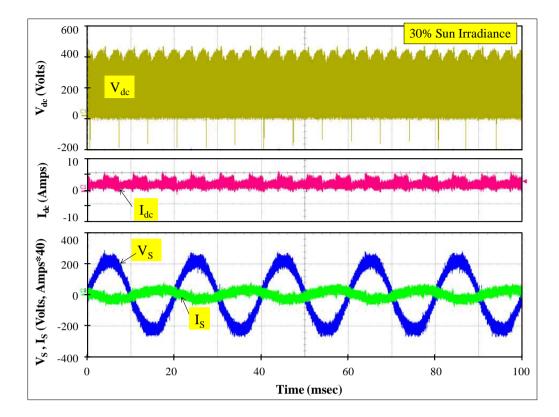

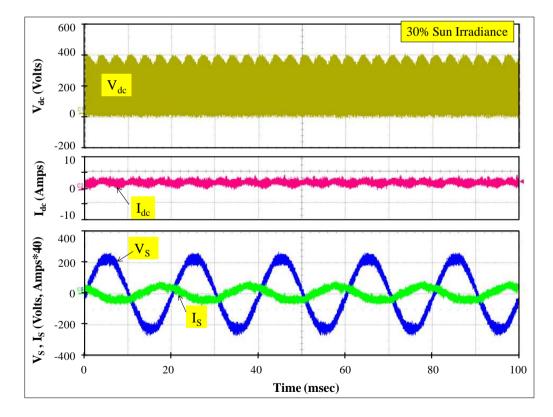

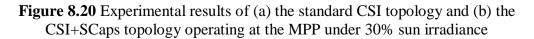

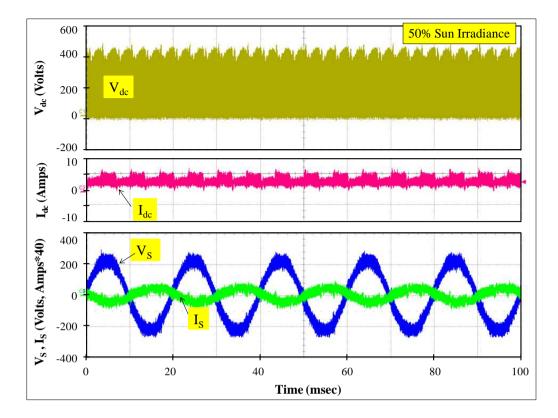

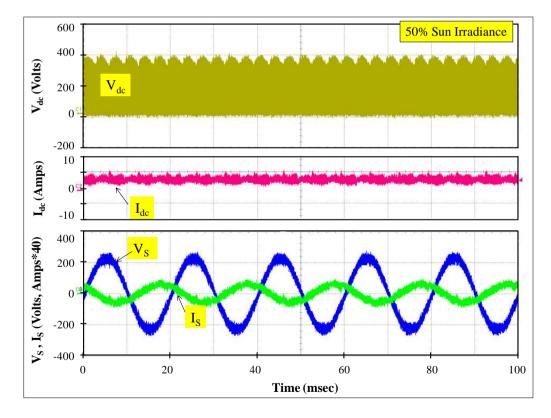

| Figure 8.3 Experimental results for the PV emulator and design specification P-V                         |

|----------------------------------------------------------------------------------------------------------|

| characteristic curves at varying sun irradiance levels; where $V_{\text{pv}}$ is the output PV           |

| voltage and $P_{pv}$ is the output PV power                                                              |