# Himsworth, John M. (2011) Linear array CMOS detectors for laser doppler blood flow imaging. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository: http://eprints.nottingham.ac.uk/12392/1/thesis-FINAL-05-11-2011.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

- Copyright and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners.

- To the extent reasonable and practicable the material made available in Nottingham ePrints has been checked for eligibility before being made available.

- Copies of full items can be used for personal research or study, educational, or notfor-profit purposes without prior permission or charge provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

- · Quotations or similar reproductions must be sufficiently acknowledged.

Please see our full end user licence at: <u>http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf</u>

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

# LINEAR ARRAY CMOS DETECTORS FOR LASER DOPPLER BLOOD FLOW IMAGING

John Michael Himsworth, M.Eng (Hons)

Thesis submitted to the University of Nottingham

for

the degree of Doctor of Philosophy December 2011

#### Abstract

Laser Doppler blood flow imaging is well established as a tool for clinical research. The technique has considerable potential as an aid to diagnosis and as a treatment aid in a number of situations. However, to make widespread clinical use of a blood flow imager feasible a number of refinements are required to make the device easy to use, accurate and safe.

Existing LDBF systems consist of 2D imaging systems, and single point scanning systems. Single point scanning systems can offer fast image acquisition time, and hence high frame rate. However, these require high laser power to illuminate the entire target area with sufficient power. Single point scanning systems allow lower laser power to be used, but building up an image of flow in skin requires mechanical scanning of the laser, which results in a high image acquisition time, making the system awkward to use.

A new approach developed here involves scanning a line along a target, and imaging the line with a 1D sensor array. This means that only one axis of mechanical scanning is required, reducing the scanning speed, and the laser power is vastly reduced from that required for a 2D system.

This approach lends itself well to the use of integrated CMOS detectors, as the smaller pixel number means that a linear sensor array can be implemented on an IC which has integrated processing while keeping overall IC size, and hence cost, lower than equivalent 2D imaging systems.

A number of front-end and processing circuits are investigated in terms of their suitability for this application. This is done by simulating a range of possible designs, including several logarithmic pixels, active pixel sensors and opamp-based linear front-ends. Where possible previously fabricated ICs using similar sensors were tested in a laser Doppler flowmetry system to verify simulation results.

A first prototype IC (known as BVIPS1) implements a 64x1 array of buffered logarithmic pixels, chosen for their combination of sufficient gain and bandwidth and compact size. The IC makes use of the space available to include two front-end circuits per pixel, allowing other circuits to be prototyped. This allows a linear front-end based on opamps to be tested. It is found that both designs can detect changes in blood flow despite significant discrepancies between simulated and measured IC performance. However, the signal-noise ratio for flux readings is high, and the logarithmic pixel array suffers from high fixed pattern noise, and noise and distortion that makes vein location impossible.

A second prototype IC (BVIPS2) consists of dual 64x1 arrays, and integrated processing. The sensor arrays are a logarithmic array, which addresses the problems of the first IC and uses alternative, individually selectable front-ends for each pixel to reduce fixed-pattern noise, and an array of opamp-based linear detectors. Simulation and initial testing is performed to show that this design operates as intended, and partially overcomes the problems found on the previous IC - the IC shows reduced fixed pattern noise and better spatial detection of blood flow changes, although there is still significant noise.

#### Acknowledgements

I would like to thank my supervisors Professor Barrie Hayes-Gill and Professor Stephen Morgan for their advice and support during this work. I would also like to thank my colleague Xianhong Xu, who designed the digital parts of the second prototype IC (BVIPS2), Hoang Nguyen and Diwei He for sharing their knowledge of Laser Doppler Flowmetry, Xiabing Huang and Martin Potter from Moor Instruments Ltd for their help with experimental equipment and LDF devices, and Roger Light for his guidance and assistance with all things chip related.

This work has been financially supported by the Engineering and Physical Sciences Research Council, and also through the UK Technology Strategy Board as part of the Blood Vessel Imaging for Venipuncture, Phlebotomy and Surgery project.

Finally I would like to thank my friends, family, and particularly Emma, for preserving my sanity throughout this project.

#### List of Abbreviations

- ADC Analog to Digital Converter

- AMS Austria Micro Systems

- BVIPS Blood Vessel Imaging for Phlebotomy, Veinipuncture and Surgery

- CCD Charge Coupled Device

- CMOS Complementary Metal Oxide Semiconductor

- CMRR Common Mode Rejection Ratio

- LDF Laser Doppler Flowmetry

- LDBF Laser Doppler Blood Flowmetry

- FFT Fast Fourier Transform

- FPN Fixed Pattern Noise

- FPGA Field Programmable Gate Array

- GMC Transimpedance-Capacitance Filter  $\left(g_m-C\right)$

- HDA Hysteretic Differentiator Amplifier

- IC Integrated Circuit

- LASCA Laser Speckle Contrast Analysis

- PCB Printed Circuit Board

- PSRR Power Supply Rejection Ratio

- SNR Signal-to-Noise Ratio

- SRAM Static Random Access Memory

- THD Total Harmonic Distortion

- TIA Transimpedance Amplifier

- VLSI Very Large Scale Integration

# Contents

| A            | bstra | lct                         |                                                                                         | i   |  |  |

|--------------|-------|-----------------------------|-----------------------------------------------------------------------------------------|-----|--|--|

| A            | ckno  | wledge                      | ements                                                                                  | iii |  |  |

| Li           | st of | Abbr                        | eviations                                                                               | iv  |  |  |

| $\mathbf{C}$ | onter | nts                         |                                                                                         | v   |  |  |

| 1            | Intr  | Introduction                |                                                                                         |     |  |  |

|              | 1.1   | Context of this Work        |                                                                                         |     |  |  |

|              |       | 1.1.1                       | DTI Project - Blood Vessel Imaging for Veinipuncture, Phlebotomy<br>and Surgery (BVIPS) | 2   |  |  |

|              |       | 1.1.2                       | Focus of this Work Within the BVIPS Project                                             | 2   |  |  |

|              |       | 1.1.3                       | Work Done by the Author                                                                 | 3   |  |  |

|              |       | 1.1.4                       | Other Aspects of the BVIPS project                                                      | 4   |  |  |

|              | 1.2   | Novel                       | ty of this Work                                                                         | 5   |  |  |

|              | 1.3   | Layou                       | t of the Thesis                                                                         | 6   |  |  |

|              | 1.4   | Syster                      | n to be Developed                                                                       | 8   |  |  |

|              | 1.5   | .5 The Doppler Effect       |                                                                                         |     |  |  |

|              | 1.6   | 1.6 Laser Doppler Flowmetry |                                                                                         |     |  |  |

|              |       | 1.6.1                       | Doppler Shift from Moving Cells                                                         | 10  |  |  |

|              |       | 1.6.2                       | Optical Mixing                                                                          | 12  |  |  |

|              |       | 1.6.3                       | Concentration and Flow Processing                                                       | 14  |  |  |

|              | 1.7   | Typic                       | al Laser Doppler Flowmetry System                                                       | 15  |  |  |

|              |       | 1.7.1                       | Typical LDBF System using Time-Domain Processing                                        | 15  |  |  |

|              |       | 1.7.2                       | Considerations for Frequency Domain Processing                                          | 17  |  |  |

|              | 1.8   | Expec                       | ted Doppler Signal                                                                      | 18  |  |  |

|              |       | 1.8.1                       | Light Levels and Photocurrents                                                          | 18  |  |  |

|              |       | 1.8.2                       | Large Photodiodes and Speckle Size                                                      | 19  |  |  |

|              |       | 1.8.3                       | Spectrum of the Doppler Signal                                                          | 21  |  |  |

| <b>2</b> | Rev | view of                 | Existing Laser Doppler and Vein Location Systems                    | <b>23</b> |

|----------|-----|-------------------------|---------------------------------------------------------------------|-----------|

|          | 2.1 | Introd                  | $\operatorname{luction}$                                            | 23        |

|          | 2.2 | Develo                  | opment of Laser Doppler Blood Flow Measurement Systems              | 24        |

|          |     | 2.2.1                   | Early Development of Laser Doppler Blood Flowmetry                  | 24        |

|          |     | 2.2.2                   | Single Point Measurement Systems                                    | 25        |

|          |     | 2.2.3                   | Scanning Systems                                                    | 25        |

|          |     | 2.2.4                   | 2D Doppler Flow Imaging Systems                                     | 26        |

|          |     | 2.2.5                   | 2D integrated CMOS LDBF Sensors                                     | 28        |

|          |     | 2.2.6                   | Choice of Sensor technology - CCD or CMOS                           | 30        |

|          | 2.3 | Develo                  | opment of LDBF for Medical Use                                      | 31        |

|          |     | 2.3.1                   | Research Use of Laser Doppler Flowmetry Systems                     | 31        |

|          |     | 2.3.2                   | Non-Imaging Applications of LDBF Techniques                         | 32        |

|          | 2.4 | Alterr                  | native Flow Assessment Methods                                      | 33        |

|          |     | 2.4.1                   | Laser Speckle Contrast Analysis                                     | 33        |

|          |     | 2.4.2                   | Laser Velocimetry                                                   | 34        |

|          | 2.5 | Alterr                  | ative Vein Location Technologies                                    | 35        |

|          |     | 2.5.1                   | Trans-Illumination                                                  | 35        |

|          |     | 2.5.2                   | Infra-Red Image Processing                                          | 36        |

|          |     | 2.5.3                   | Haptics                                                             | 37        |

|          |     | 2.5.4                   | Ultrasound                                                          | 38        |

|          | 2.6 | $\operatorname{Clinic}$ | al Use of Vein Location Systems                                     | 39        |

|          |     | 2.6.1                   | Laser Power against Acquisition Speed                               | 39        |

|          |     | 2.6.2                   | Location Marking on Patients                                        | 40        |

|          |     | 2.6.3                   | Confidence in Results                                               | 41        |

|          | 2.7 | $\operatorname{Comm}$   | nercially Available Imagers and Figures of Merit                    | 41        |

|          | 2.8 | Summ                    | nary                                                                | 42        |

| 3        |     | estigat<br>thods        | ion of Current to Voltage Converter Circuits and Processing         | g<br>44   |

|          | 3.1 | Introd                  | luction                                                             | 44        |

|          |     | 3.1.1                   | Pixel Elements for LDBF                                             | 44        |

|          |     | 3.1.2                   | Structure of the Chapter and Simulations Performed                  | 45        |

|          |     | 3.1.3                   | Simulator and Device Models                                         | 47        |

|          | 3.2 | Curre                   | nt to Voltage Converter Circuits                                    | 47        |

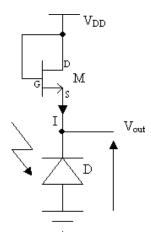

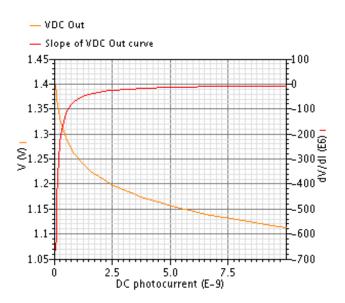

|          |     | 3.2.1                   | Logarithmic Current to Voltage Converters                           | 47        |

|          |     | 3.2.2                   | Buffered Pixel Design for Increased Bandwidth                       | 56        |

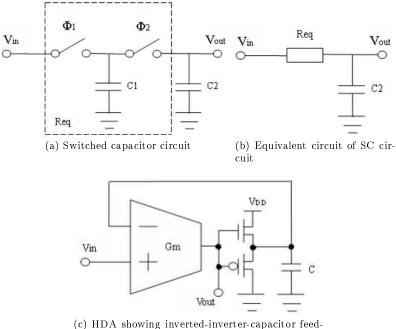

|          |     | 3.2.3                   | Current to Voltage Converter Circuit using CMOS inverter feedback . | 64        |

|          |     | 3.2.4                   | Simulation of Logarithmic Front-End Circuits                        | 66        |

|          |     |                         | -                                                                   |           |

|   |                 | 3.2.5  | Linear Front-End Circuit                                                                                                                      |

|---|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   |                 | 3.2.6  | Active Pixel Sensors                                                                                                                          |

|   |                 | 3.2.7  | Summary of Current to Voltage Converter Circuits                                                                                              |

|   | 3.3             | Ampli  | fier and High-pass Filter - Hysteretic Differentiator Amplifier $87$                                                                          |

|   |                 | 3.3.1  | HDA Using Inverted-Inverter Feedback                                                                                                          |

|   |                 | 3.3.2  | HDA Using $G_m C$ Feedback                                                                                                                    |

|   |                 | 3.3.3  | Simulation of HDA designs                                                                                                                     |

|   |                 | 3.3.4  | Summary of Amplifier Circuits                                                                                                                 |

|   | 3.4             | Low-p  | ass Filter - $G_m C$ Anti-Aliasing Filter                                                                                                     |

|   |                 | 3.4.1  | $G_m C$ Filter Schematic                                                                                                                      |

|   |                 | 3.4.2  | Simulation of $G_m C$ Circuit                                                                                                                 |

|   |                 | 3.4.3  | Summary of Low-pass Filter Circuits                                                                                                           |

|   | 3.5             | Summ   | ary                                                                                                                                           |

| 4 | $\mathbf{Desi}$ | ign an | d Testing of BVIPS1 IC 113                                                                                                                    |

|   | 4.1             | Introd | uction                                                                                                                                        |

|   |                 | 4.1.1  | Structure of the Chapter                                                                                                                      |

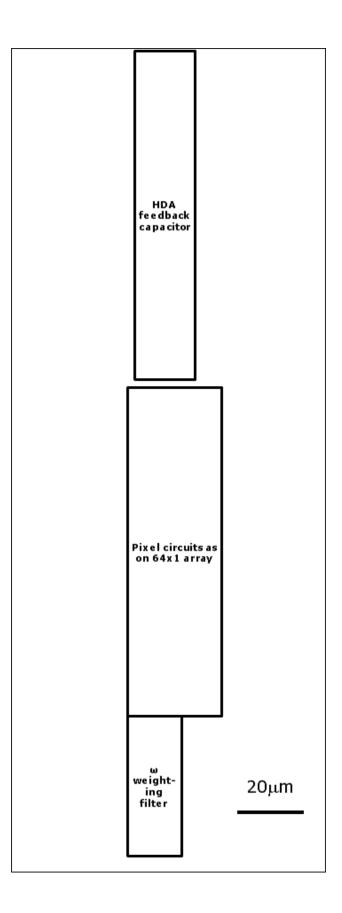

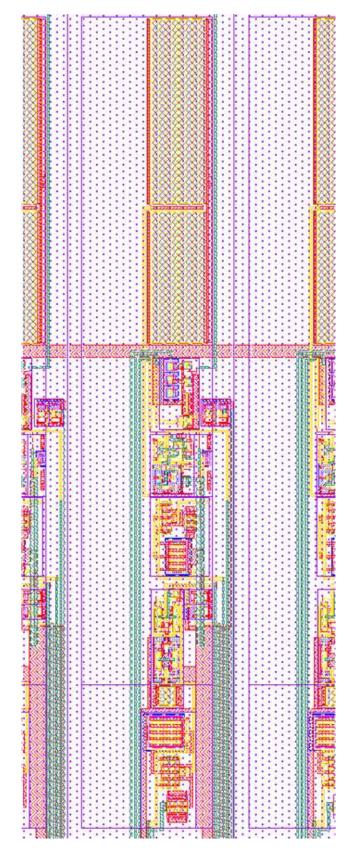

|   | 4.2             | BVIPS  | 51 IC Design Overview                                                                                                                         |

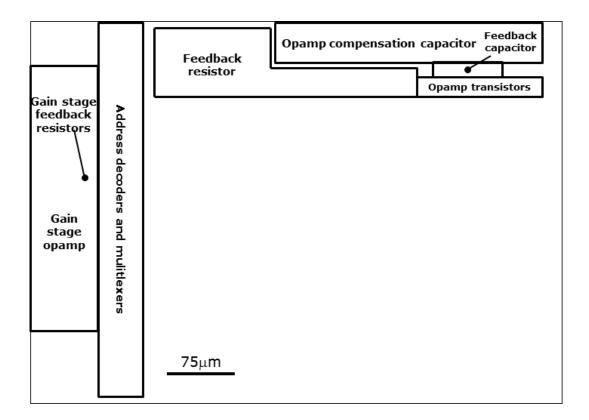

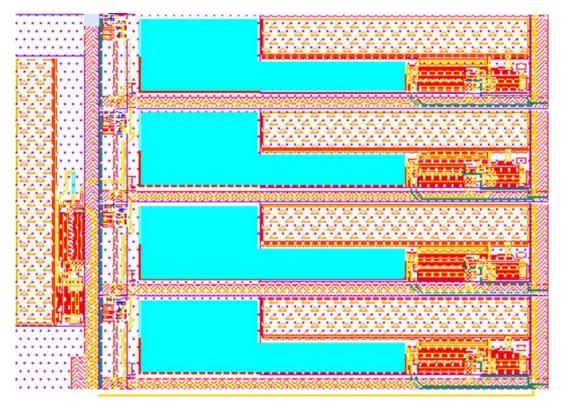

|   |                 | 4.2.1  | Layout of IC                                                                                                                                  |

|   |                 | 4.2.2  | RHS (64x1) Logarithmic Pixel Section                                                                                                          |

|   |                 | 4.2.3  | LHS (32x1) Logarithmic Pixel Section                                                                                                          |

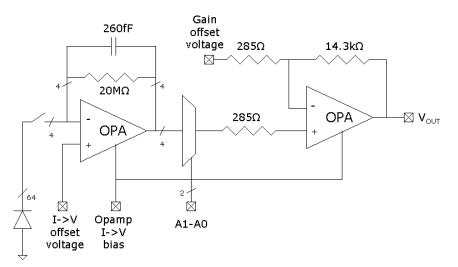

|   |                 | 4.2.4  | Opamp-Based Linear Front-end Section                                                                                                          |

|   | 4.3             | Chara  | cterisation of BVIPS1 IC $\ldots \ldots 132$                     |

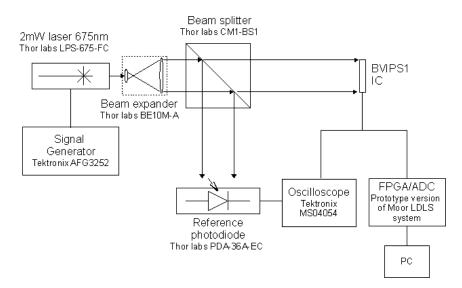

|   |                 | 4.3.1  | Characterisation Equipment                                                                                                                    |

|   |                 | 4.3.2  | Behaviour Tested                                                                                                                              |

|   |                 | 4.3.3  | Light Levels for Characterisation                                                                                                             |

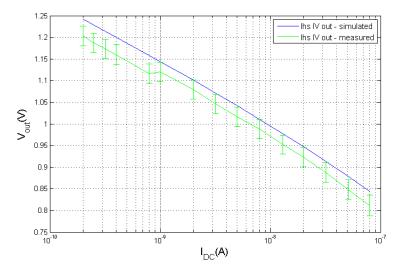

|   |                 | 4.3.4  | DC Response                                                                                                                                   |

|   |                 | 4.3.5  | AC Response                                                                                                                                   |

|   |                 | 4.3.6  | Noise Response                                                                                                                                |

|   |                 | 4.3.7  | Frequency Response                                                                                                                            |

|   | 4.4             | Noise  | Reduction $\ldots \ldots 159$ |

|   |                 | 4.4.1  | Original Configuration                                                                                                                        |

|   | 4.5             | Dopple | er Experiments                                                                                                                                |

|   |                 | 4.5.1  | Doppler Imaging Setup                                                                                                                         |

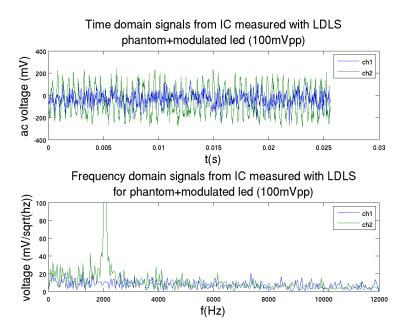

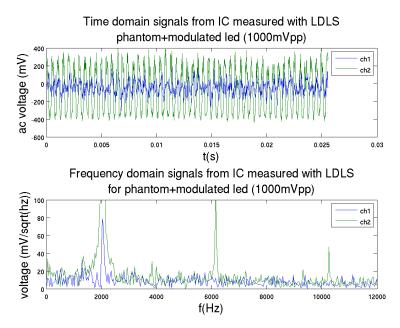

|   |                 | 4.5.2  | Raw Signals from Doppler Imaging                                                                                                              |

|   |                 | 4.5.3  | Processed Flux output from Doppler Imaging                                                                                                    |

|   |                 | 4.5.4  | Quantified Flux Measurements and SNR                                                                                                          |

|   |                | 4.5.5  | Flux Measurements using Opamp Pixels                 |

|---|----------------|--------|------------------------------------------------------|

|   | 4.6            | Discus | ssion and Fault Investigation 169                    |

|   |                | 4.6.1  | Discussion of Logarithmic Pixels                     |

|   |                | 4.6.2  | Discussion of Opamp Pixels                           |

|   |                | 4.6.3  | Spikes on Logarithmic Pixel AC amplifier Output      |

|   |                | 4.6.4  | Fixed Pattern Noise                                  |

|   | 4.7            | Summ   | ary                                                  |

| 5 | $\mathbf{Des}$ | ign an | d Characterisation of BVIPS2 IC 187                  |

|   | 5.1            | Introd | uction                                               |

|   |                | 5.1.1  | Structure of the Chapter                             |

|   | 5.2            | IC De  | sign                                                 |

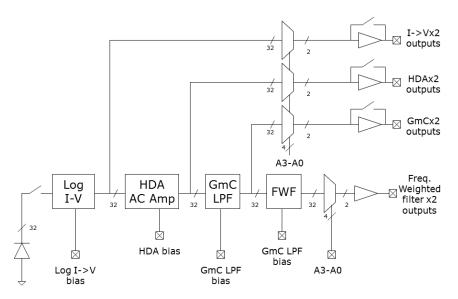

|   |                | 5.2.1  | IC Top Level Block Diagram                           |

|   | 5.3            | Logari | thmic Pixel Design                                   |

|   |                | 5.3.1  | Logarithmic Pixel Structure                          |

|   | 5.4            | Opam   | p Pixel Design                                       |

|   |                | 5.4.1  | Opamp Pixel Structure                                |

|   | 5.5            | Chang  | ges to Logarithmic Detector                          |

|   |                | 5.5.1  | HDA Alternative Design                               |

|   |                | 5.5.2  | Higher Order Filters                                 |

|   |                | 5.5.3  | Multiple Front-ends and Amplifiers for FPN Reduction |

|   | 5.6            | Chang  | ges to Opamp Pixel Design 214                        |

|   |                | 5.6.1  | Limitations of Opamp Pixel on BVIPS1                 |

|   |                | 5.6.2  | Compact Opamp Design                                 |

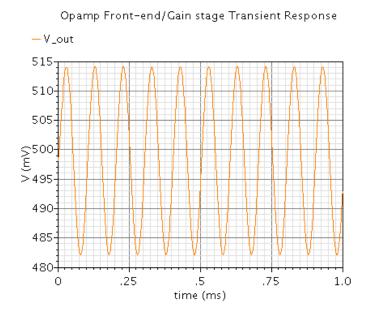

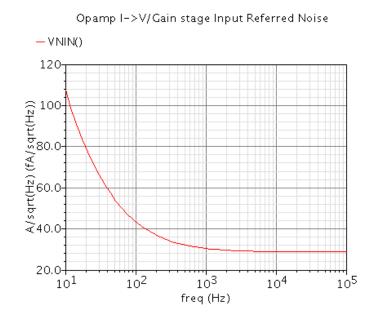

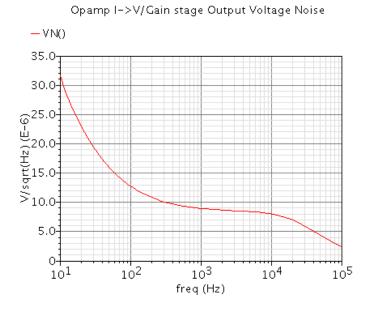

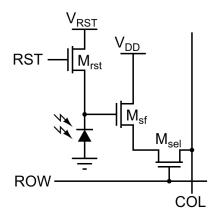

|   |                | 5.6.3  | Simulation of Compact Opamps 219                     |

|   |                | 5.6.4  | High-Pass Filter for AC Channel                      |

|   |                | 5.6.5  | HDA Amplifier AC Channel                             |

|   | 5.7            | On-Cl  | ip Processing                                        |

|   |                | 5.7.1  | Motivation for On-Chip Processing                    |

|   |                | 5.7.2  | Implementation of Processing                         |

|   |                | 5.7.3  | Flexibility of the Integrated System                 |

|   | 5.8            | Labor  | atory Characterisation                               |

|   |                | 5.8.1  | Characterisation Equipment and Procedure             |

|   |                | 5.8.2  | DC Response                                          |

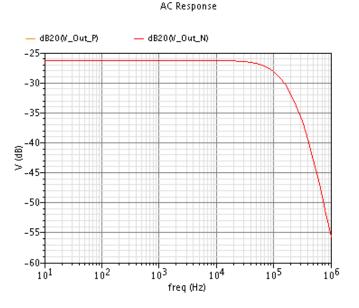

|   |                | 5.8.3  | AC Response                                          |

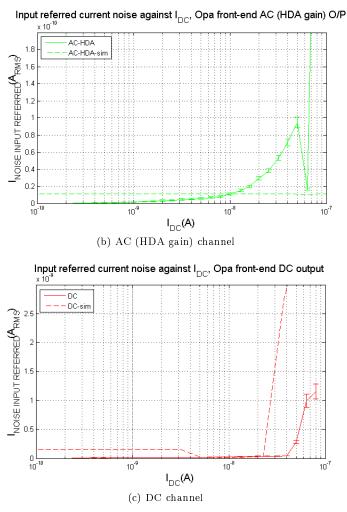

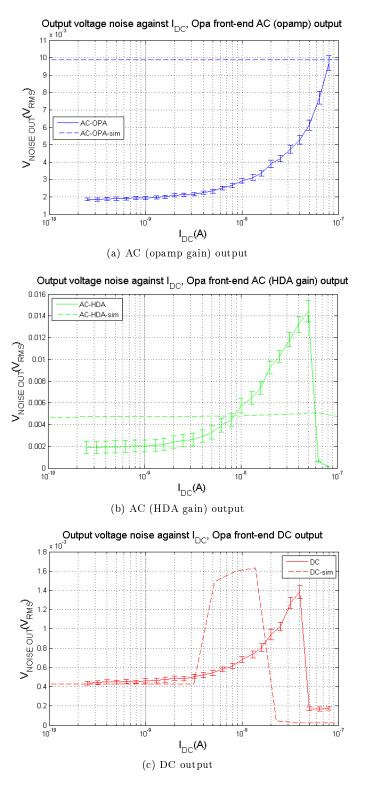

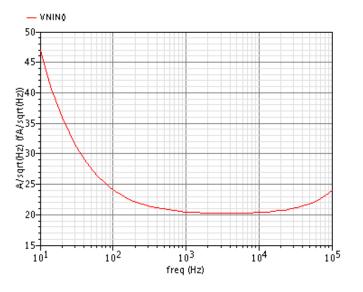

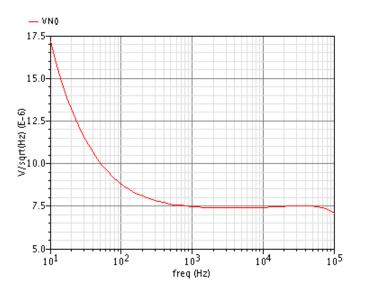

|   |                | 5.8.4  | Noise Response                                       |

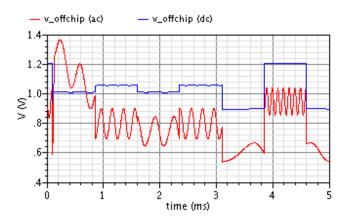

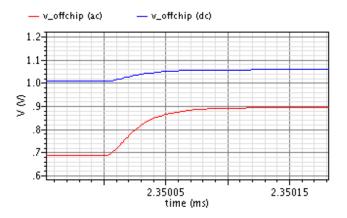

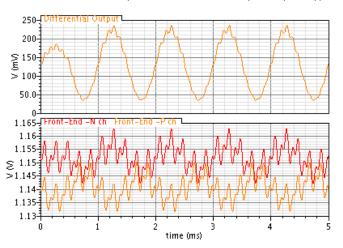

|   |                | 5.8.5  | Transient Response                                   |

|   |                |        |                                                      |

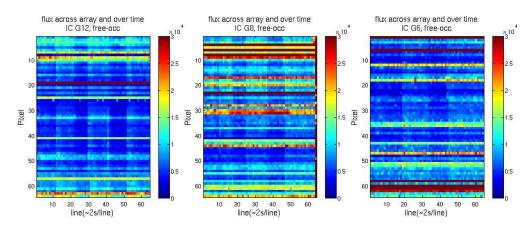

|                                                 | 5.9                                                             | Flow Images                                                    |                                                                                                                                                                                                                                                                                                           |                                                                                                       |  |  |

|-------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

|                                                 |                                                                 | 5.9.1                                                          | Doppler Imaging Setup                                                                                                                                                                                                                                                                                     | 261                                                                                                   |  |  |

|                                                 |                                                                 | 5.9.2                                                          | Logarithmic Pixel Section                                                                                                                                                                                                                                                                                 | 261                                                                                                   |  |  |

|                                                 |                                                                 | 5.9.3                                                          | Opamp Pixel Section                                                                                                                                                                                                                                                                                       | 265                                                                                                   |  |  |

|                                                 | 5.10                                                            | Summ                                                           | ary                                                                                                                                                                                                                                                                                                       | 267                                                                                                   |  |  |

| 6                                               | Con                                                             | clusio                                                         | ns and Summary                                                                                                                                                                                                                                                                                            | 270                                                                                                   |  |  |

|                                                 | 6.1                                                             | Introd                                                         | $\operatorname{uction}$                                                                                                                                                                                                                                                                                   | 270                                                                                                   |  |  |

|                                                 | 6.2                                                             | Thesis                                                         | Summary                                                                                                                                                                                                                                                                                                   | 270                                                                                                   |  |  |

|                                                 | 6.3                                                             | Furthe                                                         | er Discussion                                                                                                                                                                                                                                                                                             | 272                                                                                                   |  |  |

|                                                 |                                                                 | 6.3.1                                                          | Reduction in Size of 1D over 2D Integrated Sensors                                                                                                                                                                                                                                                        | 273                                                                                                   |  |  |

|                                                 |                                                                 | 6.3.2                                                          | Measurement of Flow Changes                                                                                                                                                                                                                                                                               | 274                                                                                                   |  |  |

|                                                 |                                                                 | 6.3.3                                                          | Discrepancies between Simulated and Measured Performance $\ldots$ .                                                                                                                                                                                                                                       | 280                                                                                                   |  |  |

|                                                 |                                                                 | 6.3.4                                                          | Large Photodiodes and Speckle Size                                                                                                                                                                                                                                                                        | 282                                                                                                   |  |  |

|                                                 |                                                                 | 6.3.5                                                          | Fixed Pattern Noise on Linear Arrays                                                                                                                                                                                                                                                                      | 283                                                                                                   |  |  |

|                                                 | 6.4                                                             | Furthe                                                         | er Work and Possible Alternatives                                                                                                                                                                                                                                                                         | 284                                                                                                   |  |  |

|                                                 |                                                                 | 6.4.1                                                          | Clinical Instrument Development                                                                                                                                                                                                                                                                           | 284                                                                                                   |  |  |

|                                                 |                                                                 | 6.4.2                                                          | Detection of Depth of Blood Flow                                                                                                                                                                                                                                                                          | 284                                                                                                   |  |  |

|                                                 |                                                                 | 6.4.3                                                          | Increase of Resolution                                                                                                                                                                                                                                                                                    | 285                                                                                                   |  |  |

|                                                 |                                                                 | 6.4.4                                                          | Limiting Factors to Further Development                                                                                                                                                                                                                                                                   | 285                                                                                                   |  |  |

| Bi                                              | bliog                                                           | raphy                                                          |                                                                                                                                                                                                                                                                                                           | 286                                                                                                   |  |  |

| A                                               | Mat                                                             | lab Co                                                         | ode Listing for Front-End Circuit Modelling                                                                                                                                                                                                                                                               | 295                                                                                                   |  |  |

|                                                 | A.1                                                             | 1 Modelling of Pixel Behaviour                                 |                                                                                                                                                                                                                                                                                                           |                                                                                                       |  |  |

|                                                 | A.2                                                             | A.2 Modelling of Noise                                         |                                                                                                                                                                                                                                                                                                           |                                                                                                       |  |  |

| B Tests of Existing Laser Doppler Flowmetry ICs |                                                                 |                                                                | mig of folice is a second s                                                                                                                                                                                           |                                                                                                       |  |  |

| в                                               | Test                                                            | s of E                                                         |                                                                                                                                                                                                                                                                                                           | 301                                                                                                   |  |  |

| в                                               | Test<br>B.1                                                     |                                                                |                                                                                                                                                                                                                                                                                                           |                                                                                                       |  |  |

| в                                               |                                                                 |                                                                | xisting Laser Doppler Flowmetry ICs                                                                                                                                                                                                                                                                       | 301                                                                                                   |  |  |

| в                                               |                                                                 | Tests 1                                                        | xisting Laser Doppler Flowmetry ICs                                                                                                                                                                                                                                                                       | 301<br>303                                                                                            |  |  |

| в                                               |                                                                 | Tests I<br>B.1.1                                               | xisting Laser Doppler Flowmetry ICs         Performed         Buffered Feedback Front-end Tests on DOP2 IC                                                                                                                                                                                                | 301<br>303<br>304                                                                                     |  |  |

| в                                               |                                                                 | Tests I<br>B.1.1<br>B.1.2<br>B.1.3                             | xisting Laser Doppler Flowmetry ICs         Performed         Buffered Feedback Front-end Tests on DOP2 IC         CMOS Inverter Front-end Tests in PC3 IC                                                                                                                                                | 301<br>303<br>304<br>305                                                                              |  |  |

| C<br>B                                          | B.1<br>B.2                                                      | Tests 1<br>B.1.1<br>B.1.2<br>B.1.3<br>Summ                     | xisting Laser Doppler Flowmetry ICs         Performed         Buffered Feedback Front-end Tests on DOP2 IC         CMOS Inverter Front-end Tests in PC3 IC         No-feedback Front-end Tests on DOP1 IC                                                                                                 | 301<br>303<br>304<br>305                                                                              |  |  |

|                                                 | B.1<br>B.2                                                      | Tests I<br>B.1.1<br>B.1.2<br>B.1.3<br>Summ<br>ign of           | xisting Laser Doppler Flowmetry ICs         Performed         Buffered Feedback Front-end Tests on DOP2 IC         CMOS Inverter Front-end Tests in PC3 IC         No-feedback Front-end Tests on DOP1 IC         ary                                                                                     | 301<br>303<br>304<br>305<br>307<br><b>308</b>                                                         |  |  |

|                                                 | B.1<br>B.2<br>Des                                               | Tests I<br>B.1.1<br>B.1.2<br>B.1.3<br>Summ<br>ign of<br>Introd | xisting Laser Doppler Flowmetry ICs         Performed         Buffered Feedback Front-end Tests on DOP2 IC         CMOS Inverter Front-end Tests in PC3 IC         No-feedback Front-end Tests on DOP1 IC         ary         ary         a Differential Pixel for Laser Doppler Flowmetry                | <ul> <li>301</li> <li>303</li> <li>304</li> <li>305</li> <li>307</li> <li>308</li> <li>308</li> </ul> |  |  |

|                                                 | <ul> <li>B.1</li> <li>B.2</li> <li>Dest</li> <li>C.1</li> </ul> | Tests I<br>B.1.1<br>B.1.2<br>B.1.3<br>Summ<br>ign of<br>Introd | xisting Laser Doppler Flowmetry ICs         Performed         Buffered Feedback Front-end Tests on DOP2 IC         CMOS Inverter Front-end Tests in PC3 IC         No-feedback Front-end Tests on DOP1 IC         ary         ary         a Differential Pixel for Laser Doppler Flowmetry         uction | 301<br>303<br>304<br>305<br>307<br><b>308</b><br>308<br>308                                           |  |  |

| C.3 | Differential Detection of a Doppler Signal |                                                                                                        |   |  |  |  |

|-----|--------------------------------------------|--------------------------------------------------------------------------------------------------------|---|--|--|--|

| C.4 | C.4 On-Chip Differential Pixel Design      |                                                                                                        |   |  |  |  |

|     | C.4.1                                      | Block Diagram of Pixel                                                                                 | 2 |  |  |  |

|     | C.4.2                                      | Differential Load Stage                                                                                | 2 |  |  |  |

|     | C.4.3                                      | Differential Amplifier                                                                                 | 3 |  |  |  |

|     | C.4.4                                      | Differential Buffer Stage                                                                              | 4 |  |  |  |

| C.5 | Layou                                      | t of the Differential Pixel $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 31$ | 4 |  |  |  |

| C.6 | Simula                                     | ation of the Differential Pixel                                                                        | 5 |  |  |  |

|     | C.6.1                                      | Transient Simulation                                                                                   | 5 |  |  |  |

|     | C.6.2                                      | DC Simulation                                                                                          | 9 |  |  |  |

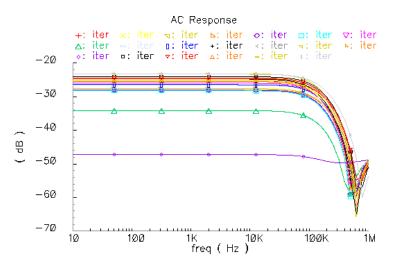

|     | C.6.3                                      | AC Simulation                                                                                          | 0 |  |  |  |

|     | C.6.4                                      | Noise Simulation                                                                                       | 1 |  |  |  |

| C.7 | Effect                                     | of Mismatch on a Differential Detector                                                                 | 2 |  |  |  |

|     | C.7.1                                      | Transient Simulation with $20\%$ Photocurrent Mismatch $\ldots \ldots 32$                              | 3 |  |  |  |

|     | C.7.2                                      | DC Simulation with 20% Photocurrent Mismatch                                                           | 3 |  |  |  |

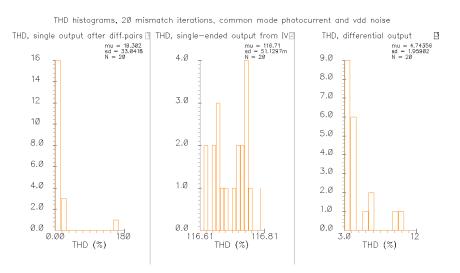

|     | C.7.3                                      | Monte-Carlo Simulation of Differential Pixel                                                           | 4 |  |  |  |

| C.8 | Testin                                     | g Methods for the Differential Detector $\ldots \ldots \ldots \ldots \ldots \ldots 32$                 | 8 |  |  |  |

|     | C.8.1                                      | Characterisation of Differential Detectors                                                             | 8 |  |  |  |

|     | C.8.2                                      | Doppler Testing                                                                                        | 9 |  |  |  |

| C.9 | Summ                                       | ary                                                                                                    | 9 |  |  |  |

|     |                                            |                                                                                                        |   |  |  |  |

### Chapter 1

# Introduction

This chapter will introduce the type of device developed during this work, along with the context of this work within a wider DTI research project, and the novelty of the work presented here. A summary of the thesis structure is also given.

The basic principle of Laser Doppler Flowmetry will then be discussed, along with related detection electronics. The physics of the Doppler effect will be introduced, and the way the effect applies to light reflecting from blood cells is discussed. The information available from this process is explained, and a generic electronic system for processing these signals is introduced. Possible processing methods are introduced, and the signal expected from the photosensors is estimated. Finally, the structure of the thesis is described.

#### 1.1 Context of this Work

This section introduces the wider DTI research project into Blood Flow Imaging, of which the work in this thesis forms a part. The intended work to be done as part of this project will be explained, including a description of exactly what parts of the presented work were performed by the author.

### 1.1.1 DTI Project - Blood Vessel Imaging for Veinipuncture, Phlebotomy and Surgery (BVIPS)

The aim of the project was to develop a line scanning blood flow imager for vein location, for use in a clinical setting. The project partners included Moor Instruments Ltd., a manufacturer of LDBF systems, Sifam Ltd (now Gooch & Housego), a manufacturer of Laser packages, Peninsular Medical School in Exeter, Nottingham City Hospital, and the University of Nottingham. The work presented here is based on the development of an integrated sensor array on a CMOS IC, intended to allow an improved imaging device to be produced.

#### 1.1.2 Focus of this Work Within the BVIPS Project

This section of the BVIPS project described within this thesis focused on the research and development of a custom integrated CMOS sensor for the imager. It was the intention at the outset of the project to fabricate two ICs during this project. This section describes the work required for this project and some of the constraints placed on this work by the wider project.

The first IC (referred to as 'BVIPS1'), was to include a 64x1 sensor array, which could be integrated into an existing imager. This IC was not intended to include digital processing, being focused on developing the analogue signal acquisition and conditioning stages. As no space on the IC was consumed by digital processing, a series of extra circuits could be included, allowing smaller arrays of alternative front-end and filtering circuits to be tested, with a view to inclusion on a second prototype IC. The additional circuits covered within this work include a 32x1 array which duplicated the pixel design used within the main array, with the addition of extra visibility of intermediate signals which was not available in the main array, and also an additional analogue processing stage which was not used in testing. Additionally, an opamp-based linear front-end circuit was fabricated, investigating the feasibility of using opamps as photodetector front-ends in 1D integrated arrays. The design and testing of this IC is shown in Chapter 4.

The second IC, BVIPS2, was to develop on the first IC by adding on-chip digital processing and analogue-digital conversion. This was intended to allow further refinements to an imaging instrument by minimising the size of the electronics elements. The IC consists of dual 64x1 arrays of two types of sensor (a technique developed for the first IC), and links these to on-chip analogue-digital conversion and digital processing. The design and testing of the analogue parts of this IC is shown in Chapter 5.

One significant constraint placed on the design of both ICs by other aspects of the project, and the line scanning technique, is the physical size of the photodiodes. As the ICs produced were to be built into an existing optical/mechanical system (the Moor LDLS imager), the IC had to address concerns about the line imaged onto the sensor 'wandering' across the sensors as the line is mechanically scanned. This is partly caused by imperfections in the mechanical components, and partly by the changing optical path as the scanning mirror moves causing the expected line location to move. This movement is not a problem in the imager using discrete components, as the discrete photodiodes used are considerable larger, at  $3.6 \text{ mm} \times 0.5 \text{ mm}$ .

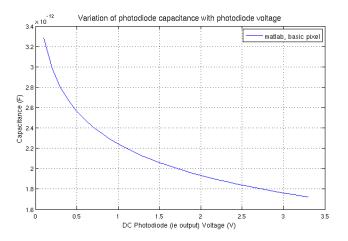

Intuitively, larger photodetectors would seem to be an advantage, with the larger area resulting in more light being gathered and hence higher photocurrent and easier current to voltage conversion. However, for LDBF applications the important photocurrent is the AC component rather than the overall intensity, and this does not increase linearly with area, and the modulation depth can actually decrease with larger photodiodes, as the AC component is linked to the size of the speckles produced by the light imaged onto the detector. This issue is discussed in more detail in Section 1.8.2.

#### 1.1.3 Work Done by the Author

As this work builds on previous research at the University of Nottingham, and involves external partners, this section clarifies which work was done by the author, and also where the work of others was used.

Overall IC design of both prototypes used was performed by the author. However, individual analogue circuits (the current to voltage converters, filters and amplifiers described in Chapter 3) were developed during previous work. Additionally, the first prototype includes an opamp-based front-end, which makes use of an opamp developed for use as an off-chip buffer for previous ICs developed at the University of Nottingham, although the front-end circuit itself is the authors work. The second version of this circuit, used on the second prototype IC, uses an opamp that was designed by the author for this project. The first IC also included two other prototype arrays designed by other researchers, but these circuits are not described within this thesis.

On the second prototype IC, described in Chapter 5, all analogue parts of the IC were designed by the author (excepting the individual circuit elements as described above). The digital parts of the IC were designed by other researchers, and are described in this thesis in order to demonstrate the suitability of these circuits as components for the overall system. Top level design of the IC including the analogue and digital elements was performed by the author.

All test results shown are from testing performed by the author.

#### 1.1.4 Other Aspects of the BVIPS project

Other parts of the project, not performed by the author, included:

- Work on processing hardware and algorithms, using FPGA based processing to increase frame rates, performed at the University of Nottingham by other researchers[Hoang et al., 2010]. The later stage of this work included developing processing techniques suitable for use on an ASIC. The digital processing block produced was included on the second prototype IC, integrating the processing techniques developed with the analogue sensors developed as part of this work. (However, this thesis is concerned with the analogue parts of the IC rather than the use of the digital processing also included.)

- Device development using discrete component front-ends, with the improved data acquisition/FPGA processing system developed here, by Moor Instruments Ltd. It was then intended to replace the discrete sensors here with the integrated CMOS sensors developed. Initial integration was performed to investigate the suitability of the IC produced, but this did not progress to producing a full imager with a CMOS array front-end.

- Production of either a stable visible red, fibre-coupled laser diode package of the required power level for this application (~40mW), or a combination of a stable, near infra-red laser with the required power along with a low power visible red laser as a 'guide' beam, allowing users to see where the laser is illuminating. The visible beam also improves laser safety, as it allows the blink response of the human eye to restrict

exposure time of the eye to the laser in the event that the laser shines into a user's or patient's eyes. This work was carried out by Sifam Ltd, up until this company was bought by Gooch & Housego.

• Clinical use of a prototype device, Peninsular Medical School, Exeter and City Hospital, Nottingham. This work was intended to investigate the clinical usefulness of an imager using the line scanning technique, and the user needs of such a device.

#### 1.2 Novelty of this Work

The work presented in this thesis has a number of novel aspects. The ICs produced are the first 1D array integrated sensors designed for use in laser Doppler blood flow imaging, with the second IC in particular showing the possibilities of CMOS integration, combining the photodetectors, analogue signal conditioning, data acquisition and blood flow processing on one IC.

Some of the novel aspects have wider application than blood flow imaging. The 1D array/line scanning imaging technique has two basic advantages:

- Reduced laser power as only one line of the imaging target has to be illuminated, the total illumination power required in a 1D system to give equivalent optical power density to a 2D system is reduced, to approximate the square root of the 2D illuminating power.

- Reduced area required for the 1D sensor array, due to reduced pixel count. This additional area can be used for any purpose the second IC fabricated here makes use of this area to implement an alternative, full-size, array of front-end circuits, as well as integrated ADCs and digital flow processing.

The reduction in illumination power has technical advantages, in terms of only requiring a lower power laser, and also safety advantages because of the reduced laser safety risks. For a system such as a blood flow imager, intended for use by non-specialists in an open setting (i.e. a normal hospital ward), this represents a significant advantage - a 2D imager could potentially be designed that has superior frame rate, larger imaging area and is simple to use, however if the high laser power required means the device is only considered safe when used by a specialist operator in a specific, private room, then the utility of the imaging device is greatly reduced.

The reduction in IC physical size applies to both pixel level and system level size. At the system level, the reduction in size from 2D to 1D sensors allows space for system-level components such as output-buffers, ADCs and the processing block, while keeping overall size and hence cost down. However, in the context of a full system the cost saving may not be a major advantage. However, the size advantage also applies at the pixel level - as the pixel count is reduced to the square root of the 2D equivalent pixel count, each pixel can be made much larger without having the severe impact that such changes would have on a 2D system. On the ICs produced here, this advantage is used by designing pixels that use large circuits such as opamps (where the front-end is generally too large for 2D integrated sensors), include higher order filters (which cannot be implemented at column level of a 2D array due to the settling time of the filters), and alternative signal paths (either alternative amplifier designs, or duplicate circuits to give redundancy). Similarly, the photodiode itself can be made larger if required by the application for increased light gathering, although at the expense of high input capacitance. The ICs produced here have large photodiodes  $(1 \text{ mm} \times 50 \,\mu\text{m})$ , although this is due to concerns about the mechanical line scanning causing the line imaged onto the sensor to wander, rather than for improved detection reasons.

#### **1.3** Layout of the Thesis

Chapter 1 introduces the type of device to be developed as part of this project. The Doppler effect and its application to measuring blood flow using reflected laser light is described. A generic Laser Doppler Flowmetry system architecture is presented, with the function of its various components discussed. Variations to this generic system due to the type of detection circuits and the processing methods that might be used here are considered.

The optical mixing process that produces an electronic signal in a photosensor is described, and based on previous experimental measurements, the signals that might be expected from the photodiodes to be used are calculated, allowing simulations on specific circuits to be performed using a known input current. The frequency component of this signal is also considered, allowing the bandwidth requirements of the system to be set. However, the light level measurements and calculations in that chapter were shown to be incorrect by later measurements (shown in chapter 4), potentially reducing the accuracy of some simulations for this specific application.

Chapter 2 reviews previous laser Doppler flowmetry systems, from initial development of the techniques through to modern systems in clinical use and current research trends in LDBF imagers. Applications of LDBF other than basic imaging are also introduced to show the potential of LDBF as a clinical tool.

As the system designed for this project is intended for vein location rather than general flow imaging, alternative technological methods of vein location are considered. This includes lowcost, simple devices intended as a minor aid to traditional clinical skills, as well as advanced vein imaging methods.

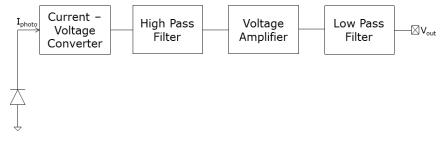

Chapter 3 investigates the circuits that can be used on ICs for laser Doppler detection, investigating each block of a generic LDBF system in turn. The general principles of the current-voltage converter circuits are introduced, along with several variations on the basic circuit that could be used in this application. Simulations are performed on these circuits to select the most suitable for this application. Various processing circuits (AC amplifiers and filters) are described to select other parts of the system, with simulations performed to show typical behaviour and the effect of manufacturing variations where necessary.

Chapter 4 describes the first IC designed for this project, known as BVIPS1. The system structure and pixel design are shown. Characterisation and simulation results from the IC are compared. Testing results from Doppler imaging with this IC are shown, and the implications of these results for vein imaging are discussed. Problems with the IC behaviour and their likely causes are described. Design options made possible by the use of a linear array (rather than a 2D array) are shown, such as dual front-end options, and physically larger front-end designs including opamp based linear detectors.

Chapter 5 shows the changes to be made to the BVIPS1 design for the 2nd IC fabricated for this project, known as BVIPS2. These changes are partly to solve issues found in testing the first IC, and also to develop the system to add on-chip analog-digital conversion and digital processing to find flux. A linear front-end using opamp based front-ends similar to those tested on BVIPS1 is also used as an alternative main circuit on this IC, which has two optional 64x1 detector arrays. Initial testing results from this IC in terms of characterisation and Doppler imaging are shown, although testing was limited by time. The tests show some improved performance, athough not all issues are fully resolved. Further work using this IC is considered.

The possibilities of a linear array sensor are further demonstrated on the BVIPS2 IC by the use of two full size sensor arrays along with the use of integrated processing circuitry on one IC. In particular, the linear array layout allows both sensor arrays to use novel features. One of the arrays is composed of opamp based front-using opamps ends, which has not been previously demonstrated on an IC for laser Doppler flowmetry, partly due to the large size of this type of pixel not being feasible on a 2D array sensor. The other array is composed of logarithmic pixels which combine the larger pixel area available with a compact front-end circuit design to allow redundant front-end circuits to be made available.

Finally, Chapter 6 presents conclusions from the project, summarising the work undertaken and its potential for use in clinical systems. Further work using the ICs and circuits developed is suggested, as well as developments to the systems designed. Possible limitations on the further development of this work are also considered.

#### 1.4 System to be Developed

This thesis discusses the research into and development of a line scanning blood flow imager intended for vein location, or more specifically the detector for such a system. The detector uses a 64x1 linear array of CMOS photodetectors. The use of CMOS technology for the detectors themselves allows processing circuitry to be integrated onto the same device. The work covers the selection and prototyping of detector circuits and analogue signal conditioning suited to this application, and also the integration of the analogue system produced into a system-on-chip with integrated data acquisition and digital processing.

Vein location will be performed by producing a 2D flow image of a target (tissue containing veins such as a hand or forearm), from which the high flow in a vein allows these structures to be identified. The 2D image will be formed by projecting a line onto the target, which will be imaged back onto the sensor array, allowing measurement of blood flow along this line. The line will then be mechanically scanned along the target, allowing a 2D image to be built up from successive lines.

#### 1.5 The Doppler Effect

The Doppler effected was first described by Christian Doppler in 1842 and demonstrated for sound waves shortly after [Houdas, 1991, Serway and Jewett, 2009]. It describes the nature of waves when the source is moving relative to the observer. This can most clearly be demonstrated for sound waves, such as the change in pitch of sound from a moving vehicle as it passes the observer.

As the source travels towards the observer, the apparent wavelength is shorter, as later wavefronts are produced nearer to the observer than the earlier fronts. As the wave velocity is constant, this means that frequency appears to be higher.

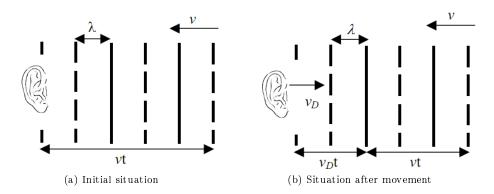

Figure 1.1: Wavefronts with wavelength  $\lambda$  travelling at velocity v, with an observer moving at  $v_D$  over time t

Figure 1.1 shows wavefronts travelling from a source to an observer, and the effect of movement on this situation. The Doppler effect can be considered in terms of wavelength or frequency, but as in electronics it is easier to measure frequency, this will be considered the main term. For the situation without movement (Figure 1.1a), the frequency, f, can be found as:

$$f = \frac{\text{oscillations received by observer}}{\text{total time}} = \frac{vt/\lambda}{t} = \frac{v}{\lambda}$$

(1.1)

In the case of a moving observer, the situation changes, as the observer passes a larger number of wavefronts than in the static case:

$$f' = \frac{\text{oscillations received by observer}}{\text{total time}} = \frac{(vt + v_D t)/\lambda}{t} = \frac{v + v_D}{\lambda}$$

(1.2)

The difference between these two frequencies is termed the Doppler shift frequency  $(f_d)$ , and is found by subtracting 1.1 from 1.2:

$$f_d = f' - f = \frac{v + v_D}{\lambda} - \frac{v}{\lambda} = \frac{v_D}{\lambda} = \frac{v_D f}{v}$$

(1.3)

$$v_D = \frac{f_d v}{f} \tag{1.4}$$

This means that if the Doppler frequency can be measured, for example by emitting a known wave (known f, v and  $\lambda$ ) and then measuring it in a different location, then  $v_D$  can be found as in equation 1.4, giving the relative velocity between the source and observer. This technique can be used for various situations including measuring speed of moving vehicles [Halliday et al., 2000] and astronomical measurements such as motion of stars, using the emitted light from the star as a source [Serway and Jewett, 2009, Cutnell and Johnson, 2006].

#### **1.6** Laser Doppler Flowmetry

#### **1.6.1** Doppler Shift from Moving Cells

Laser Doppler Blood Flowmetry involves illuminating the skin with coherent, monochrome light of constant intensity. As this light penetrates into the skin it interacts with cells by scattering and absorption. The absorbed light is lost, reducing the total reflected light. Some light scatters off static tissue, resulting in reflected light at the same wavelength as the incident light.

The Doppler shift applies to photons that are scattered by moving red blood cells. In this case the light is subject to a Doppler shift as described above. In this situation, where light is reflected back to the original source, the shift occurs twice, affecting the incident and reflected light. The first shift is the same as the situation described above - the light interacts with a blood cell that is moving relative to the source, so the light incident on the cell appears to have undergone a shift in frequency. When this light is scattered by the cell, the cell itself acts as a moving source relative to the static sensor, so undergoes another shift of the same frequency. This is referred to as a double Doppler shift [Shepherd and Oberg, 1990].

The situation is complicated by the complex movement of the cells. The flow being measured is that of a large number of blood cells flowing in a network of vessels. This means that cells are moving at a variety of speeds in a variety of directions, so the relative speed between the cell and the source is widely varying.

Similarly, the nature of the tissue means that incident photons can follow a variety of different paths, with variation in the number of scattering incidents with static tissue and with moving cells.

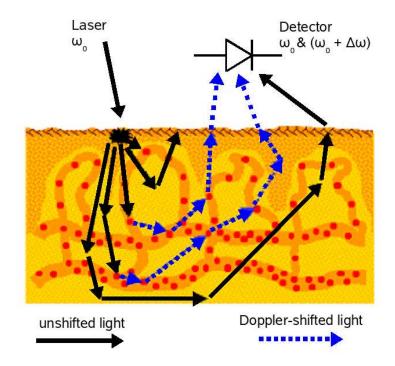

Figure 1.2 illustrates the interaction of incident light with tissue and the variety of paths that photons can take.

Figure 1.2: Path of incident light through the skin

For a single interaction, the Doppler frequency can be calculated as:

$$\Delta f = \frac{2v f_0 \cos \theta}{c_{tissue}} \tag{1.5}$$

where  $f_0$  is the frequency of transmitted light, v is the speed of a blood cell,  $c_{tissue}$  is the speed of light in tissue, and  $\cos \theta$  is the angle between the direction of cell movement and incident light (shift is highest if the cell is moving directly towards or directly away from the source). The factor of two represents the double Doppler shift.

For example, if the speed of light in tissue is  $2 \times 10^8 \text{ms}^{-1}$  (assuming refractive index of ~1.5 [Tuchin, 2007]), and  $f_0$  is that of 650 nm laser light then:

$$f = \frac{v}{\lambda} = \frac{2 \times 10^8}{650 \times 10^{-9}} \approx 3 \times 10^{14} \,\mathrm{Hz}$$

(1.6)

If we apply this to equation 1.5, with blood cells moving at roughly  $2 \,\mathrm{cms}^{-1}$ [Tanaka et al., 1974], we can find the Doppler shift frequency expected:

$$\Delta f = \frac{2v f_0 \cos\theta}{c_{tissue}} = \frac{2 \times 2 \times 10^{-2} \times 3 \times 10^{14}}{2 \times 10^8} = 60 \,\text{kHz}$$

(1.7)

In the real case this frequency would be considerably lower, as  $\theta$  will generally be less than 0, and the flow value used here is that in retinal blood vessels rather than capillaries.

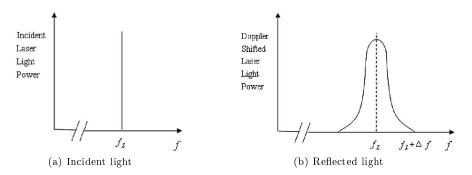

This gives the Doppler shift frequency for a single interaction. The overall received signal will be composed of many such interactions, including photons which have interacted with more than one moving cell and have therefore undergone several shifts. This results in the spectrum of the reflected light being spread around the original single wavelength, as shown in Figure 1.3. Section 1.8.3 shows the frequency spectrum from Doppler signals produced from moving blood cells in more detail.

Figure 1.3: (a) Spectrum of incident light and (b) reflected light after Doppler shifting and static reflection

#### 1.6.2 Optical Mixing

The frequency of the light cannot be directly measured by electronics, being of the order of  $10^{14}$  Hz [Albrecht et al., 2002]. The Doppler shift from equation 1.5 is considerably lower in magnitude than this, so the reflected light is still at a frequency of a similar order of magnitude.

However, the reflected light consists of static and shifted wavelengths. These components

mix in the detector giving an electrical signal at the difference frequency on a DC background. This mixing process can be expressed by the addition of the shifted and un-shifted components in equations 1.8 and 1.9.

$$E_1 = E_0 \cos(\omega_1 t + \phi) \tag{1.8}$$

$$E_2 = E_0 \cos(\omega_2 t + \phi) \tag{1.9}$$

where  $E_0$  is the amplitude of the wave,  $\omega_1$  and  $\omega_2$  are the angular frequencies of each wave and  $\phi$  is the phase of the wave. When both of these fields are incident upon a detector, the overall field is the sum of the individual fields:

$$E = E_0 \left[ \cos(\omega_1 t + \phi) + \cos(\omega_2 t + \phi) \right]$$

(1.10)

Using a trigonometric sum-to-product identity as in equation 1.11[Abramowitz, 1970], this can be seen as a mixing (i.e. multiplication) of signals at half of the sum and difference frequencies, shown in equation 1.12.

$$\cos(A) + \cos(B) = 2\cos(\frac{A+B}{2})\cos(\frac{A-B}{2}) \tag{1.11}$$

$$E = 2E_0 \cos\frac{1}{2}((\omega_1 + \omega_2)t + 2\phi)\cos\frac{1}{2}((\omega_1 - \omega_2)t + 2\phi)$$

(1.12)

Re-writing this as equation 1.13 shows the detected field, E, as a travelling wave at frequency  $\omega_1 + \omega_2$  and amplitude  $E_m$ :

$$E = E_m \cos \frac{1}{2} ((\omega_1 + \omega_2)t + 2\phi)$$

(1.13)

where:

$$E_m = 2E_0 \cos\left(\frac{1}{2}\left((\omega_1 - \omega_2)t + 2\phi\right)\right)$$

(1.14)

The sum frequency of the travelling wave,  $\omega_1 + \omega_2$  is still in the optical frequency range, so is undetectable by the electronics. The modulated amplitude  $E_m$  will be detected by the photosensor. The amount of the light illuminating the detector is known as the irradiance [Hecht, 2001], and is given by:

$$E_m^2 = 4E_0^2 \cos^2\left(\frac{1}{2}\left((\omega_1 - \omega_2)t + 2\phi\right)\right) = 2E_0^2\left[1 + \cos\left((\omega_1 - \omega_2)t + 2\phi\right)\right]$$

(1.15)

It can be seen from equation 1.15 that the DC level of the irradiance is  $2E_0^2$ , giving the DC photocurrent detected. The modulation frequency of the irradiance is  $\omega_1 - \omega_2$ , which is equal to the Doppler shift frequency. This means that measuring the frequency of the modulated signal gives the Doppler shift frequency, and hence the speed of the moving cells.

The amplitude in equation 1.15 assumes that the two frequency components have the same amplitude. In this application this is unlikely to be the case as more than half of the light incident on the skin will reflect off static tissue, mainly the top surface of the skin. This means the amplitude of the modulated component will be reduced. However, this gives us more information about the total blood flow. An increase in moving cells means that more of the reflected light will be from moving cells, and hence the amplitude of the Doppler shifted component will be higher. This will result in a higher modulation depth. From this, it is possible to measure the amount of moving cells, as well as the speed of cells. Combining this information gives an overall figure for flow.

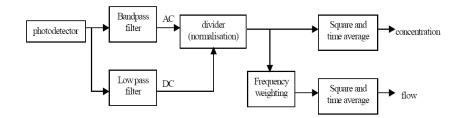

#### **1.6.3** Concentration and Flow Processing

The two values most commonly used as output from LDBF systems are concentration and flow. Concentration refers to blood volume rather than speed. Flow is found by weighting the concentration result according to frequency, as faster moving cells contribute to more overall movement of blood than a similar but slower moving blood volume.

Analytically, concentration is found from the total power in the Doppler signal [Belcaro et al., 1994]:

$$Concentration = \int_{\omega_1}^{\omega_2} P(\omega) d\omega$$

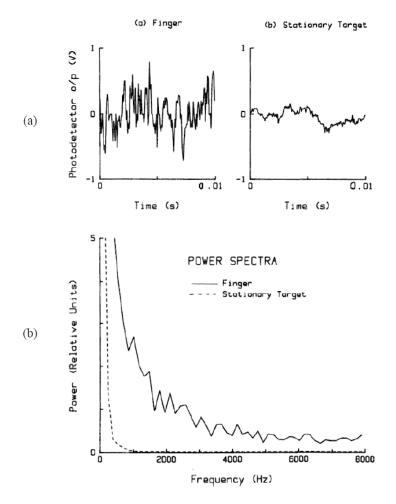

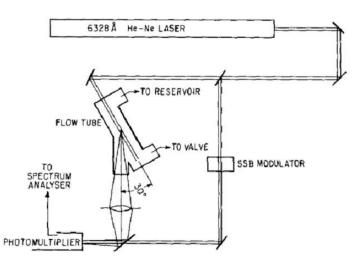

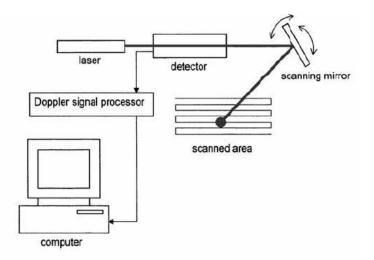

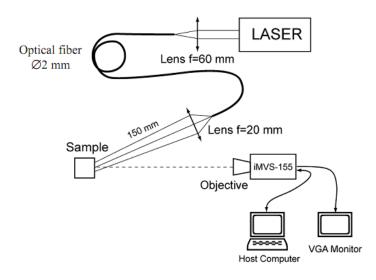

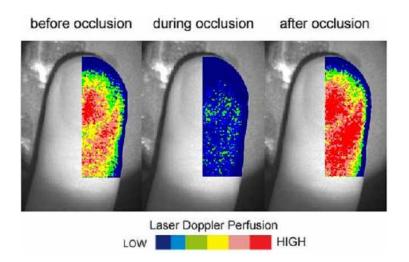

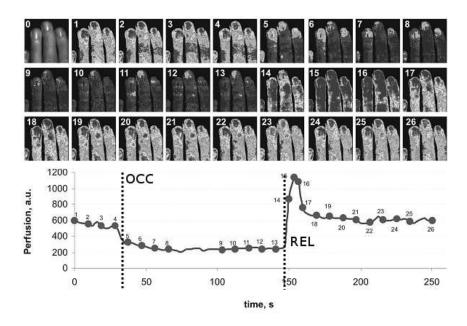

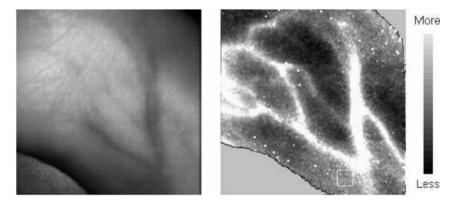

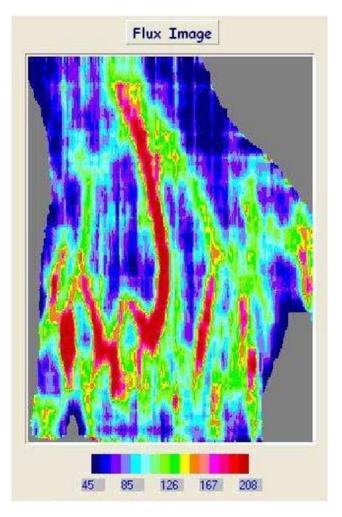

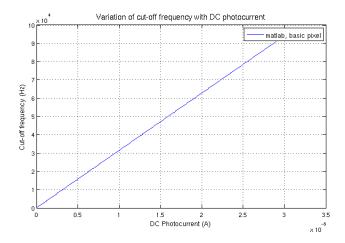

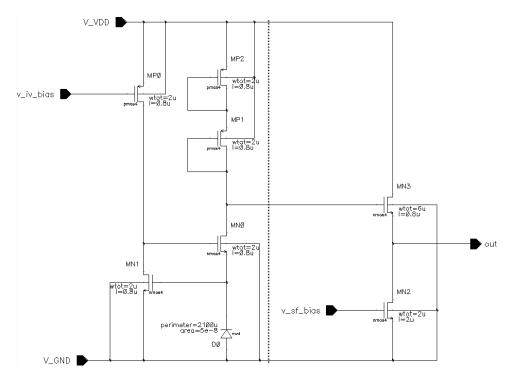

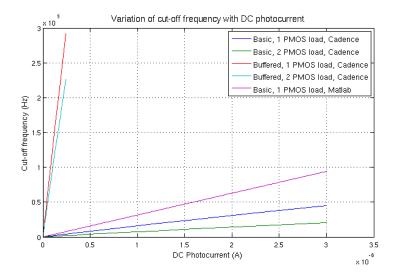

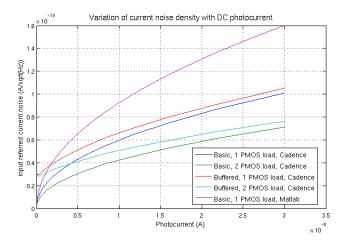

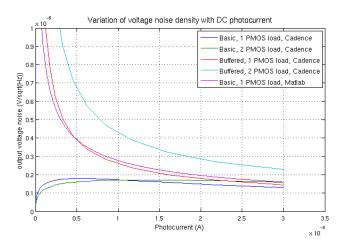

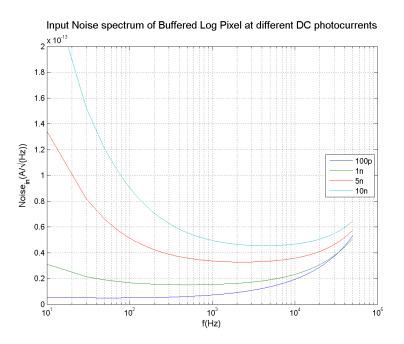

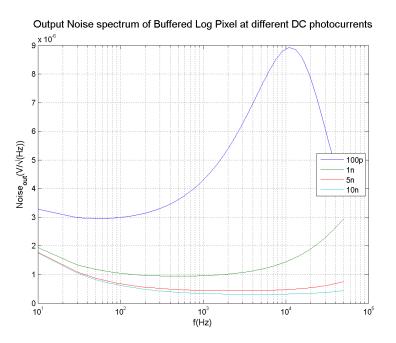

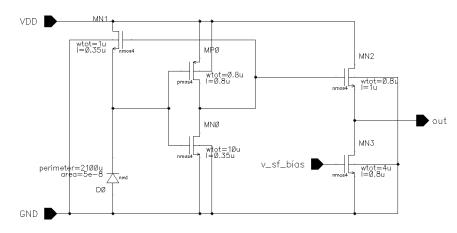

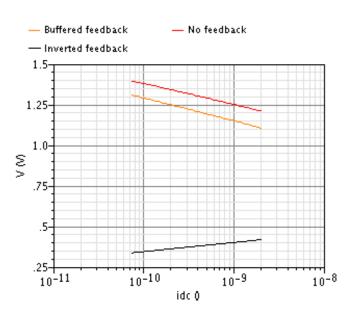

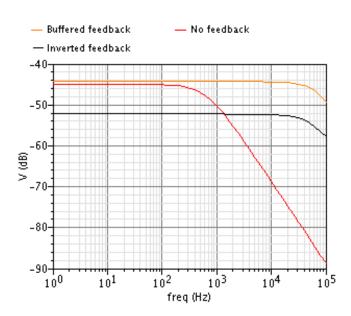

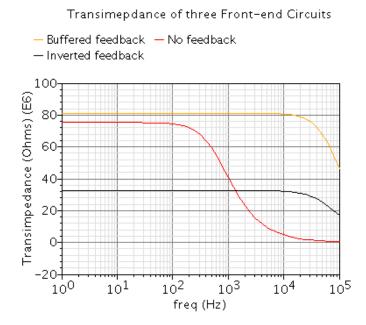

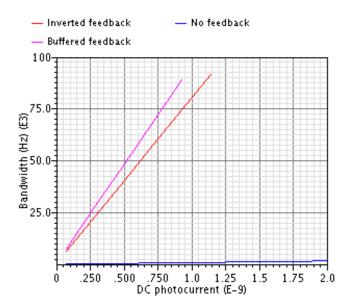

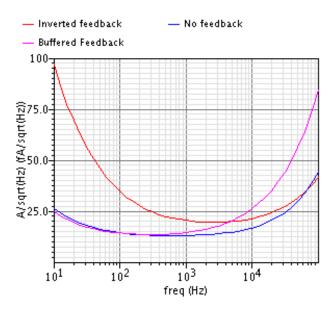

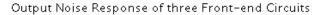

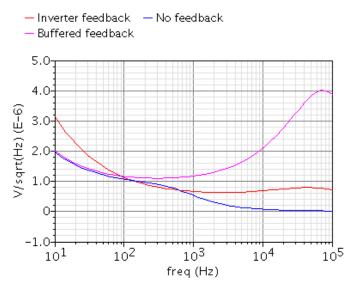

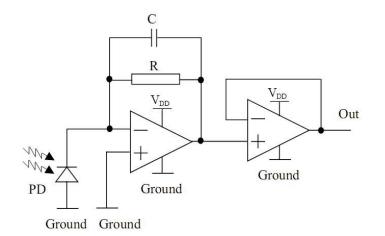

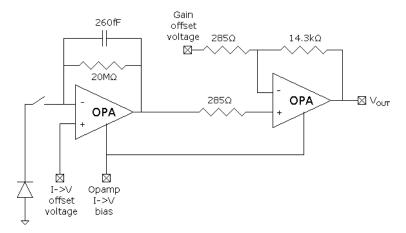

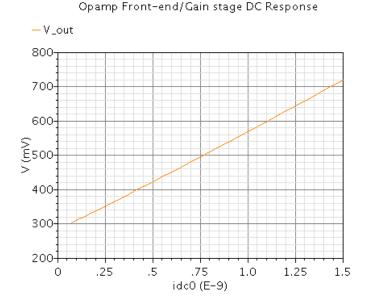

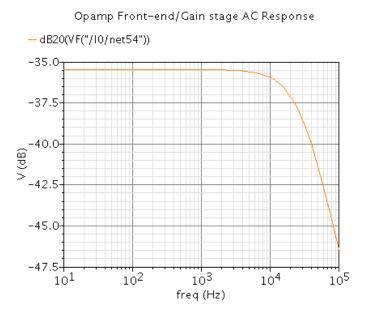

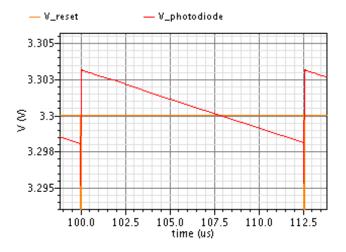

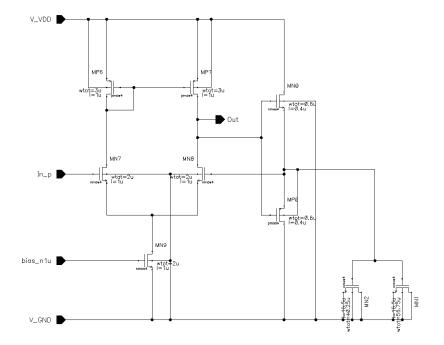

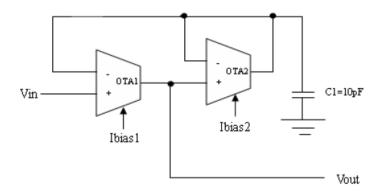

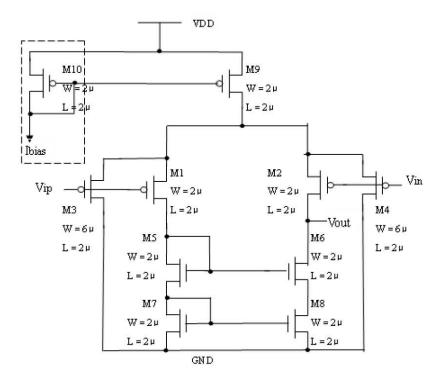

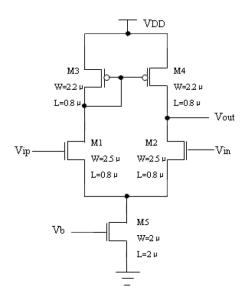

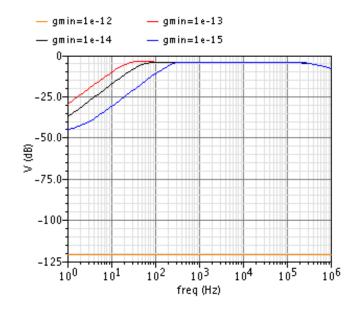

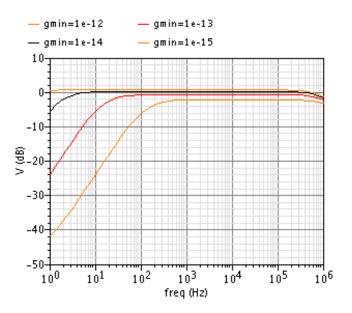

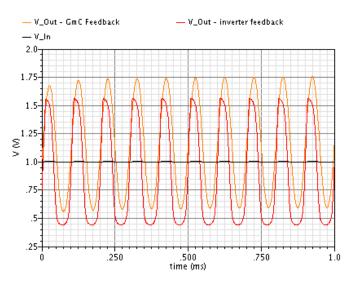

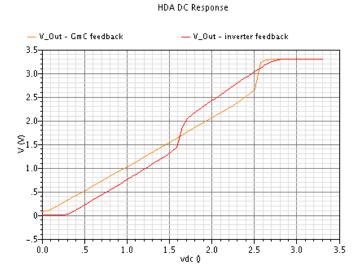

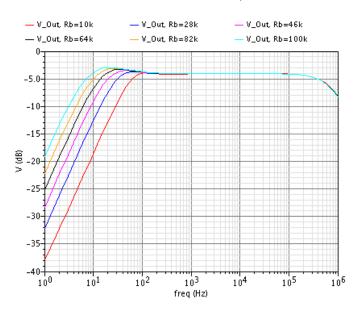

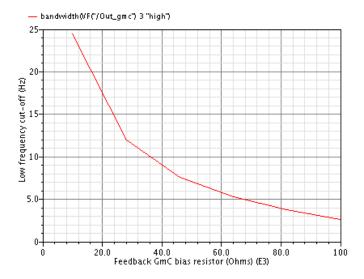

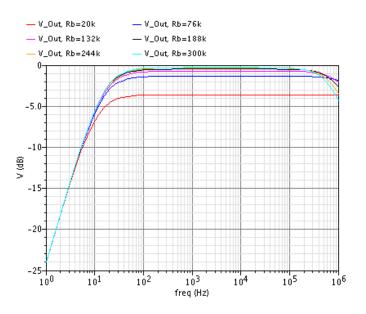

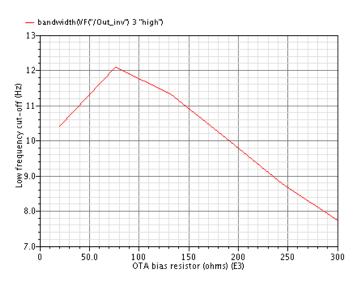

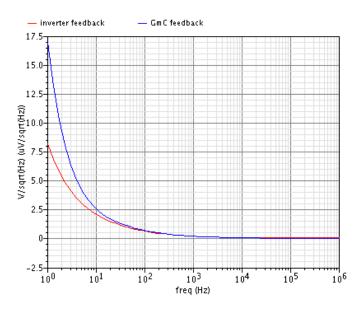

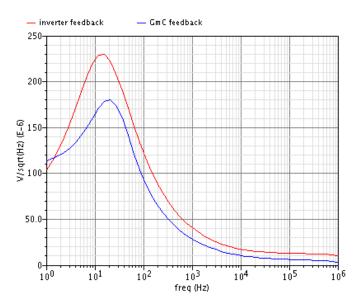

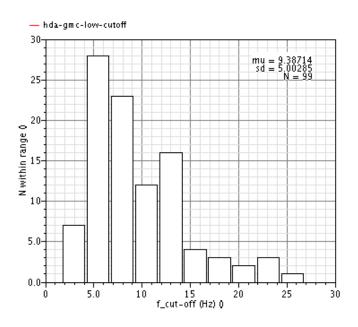

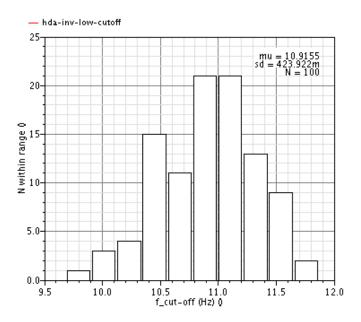

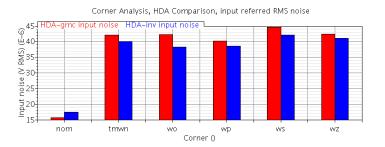

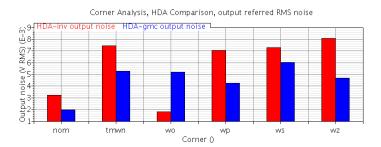

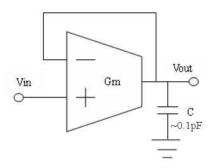

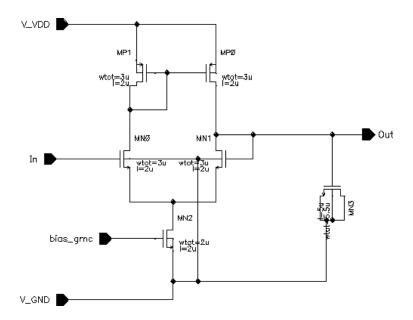

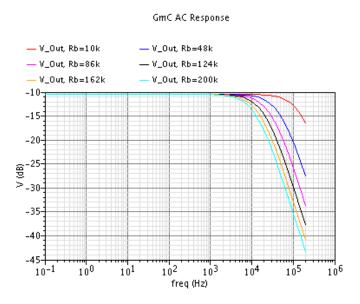

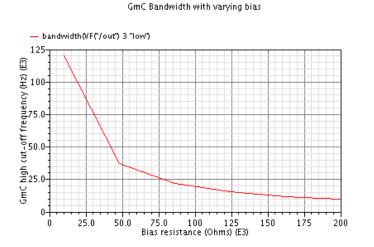

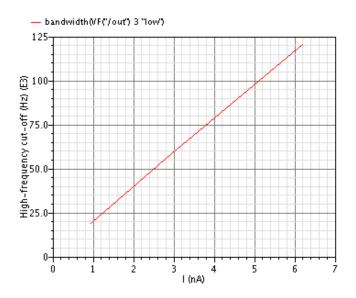

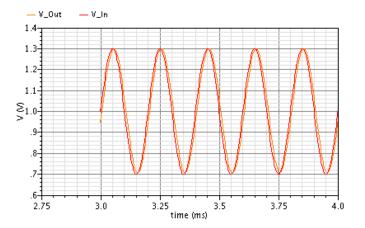

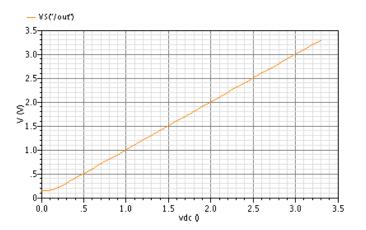

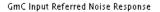

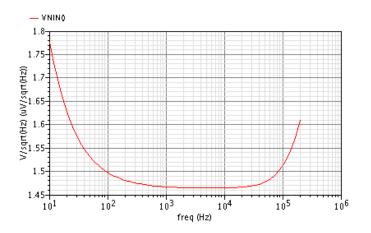

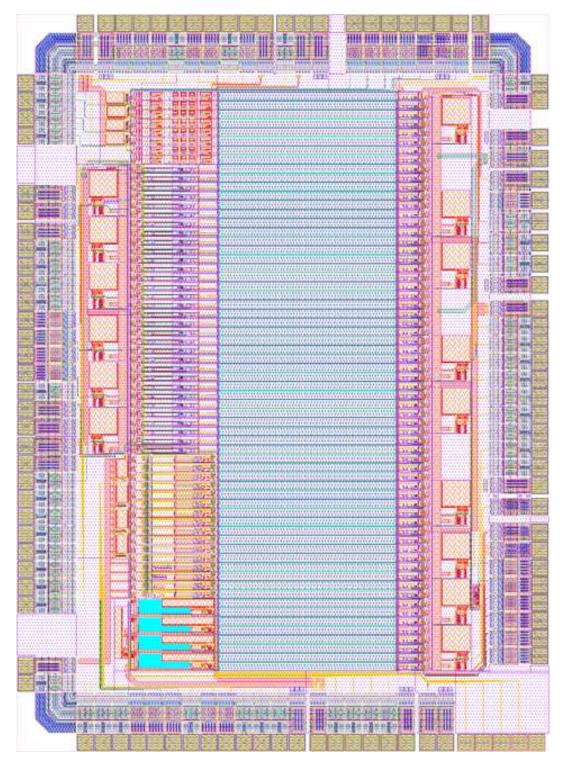

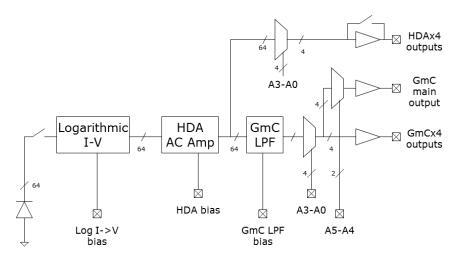

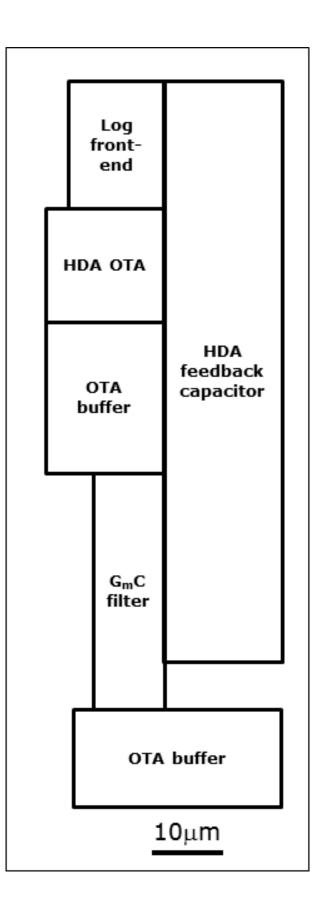

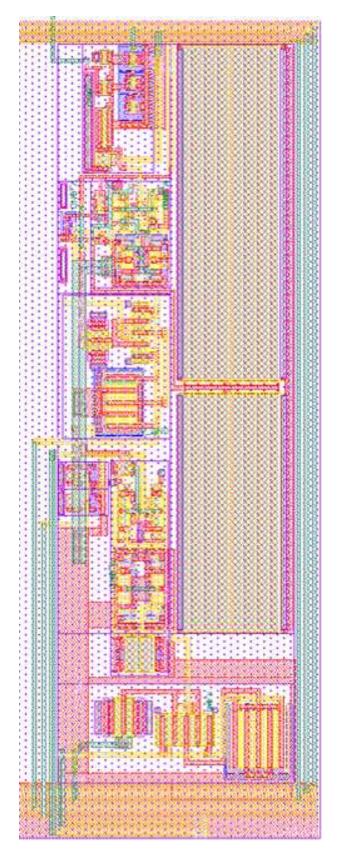

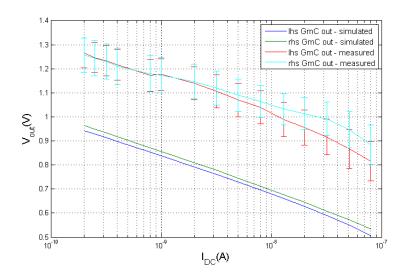

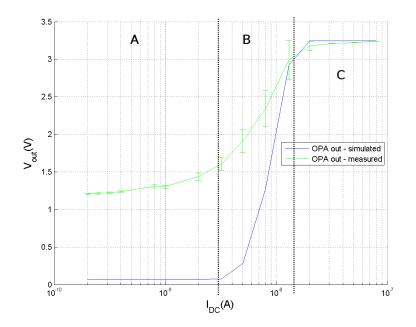

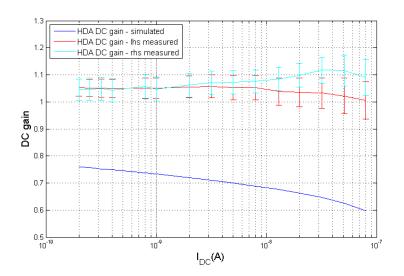

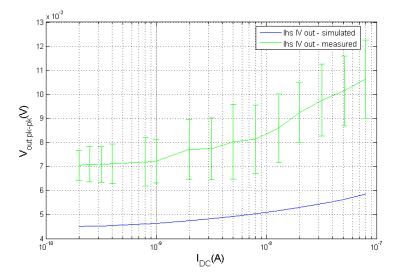

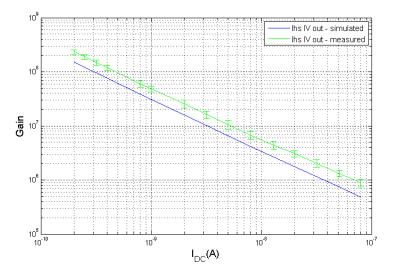

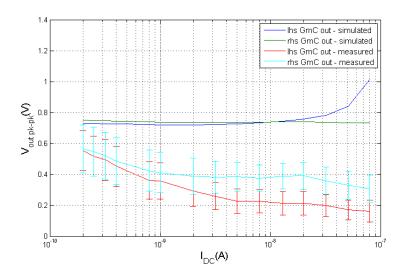

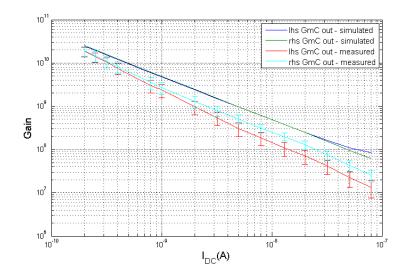

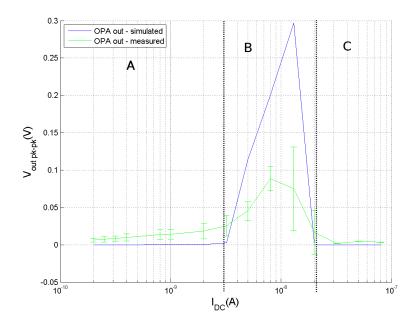

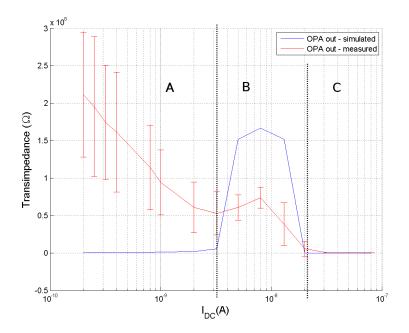

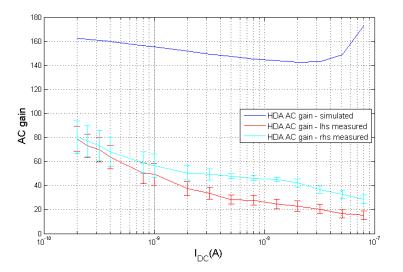

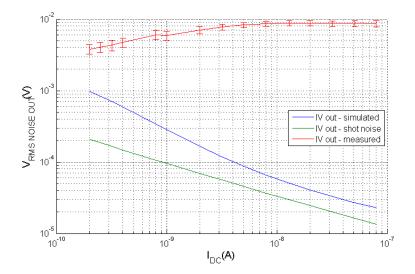

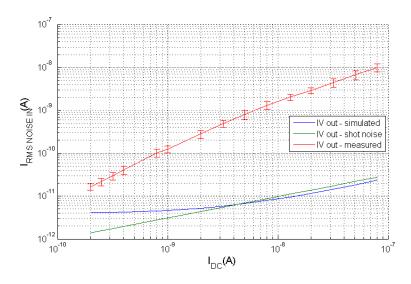

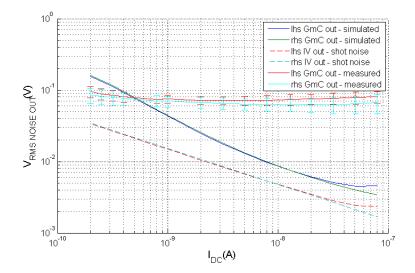

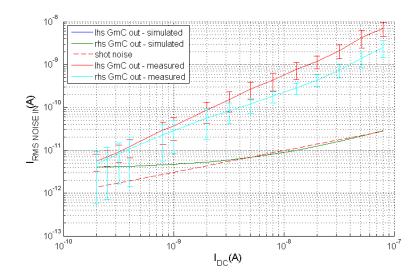

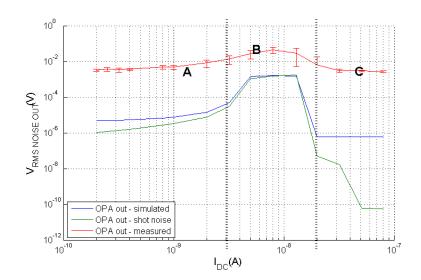

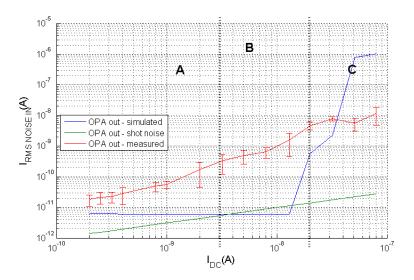

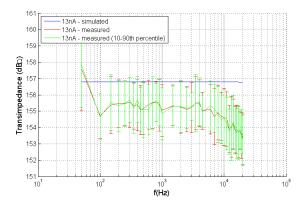

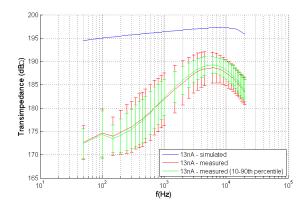

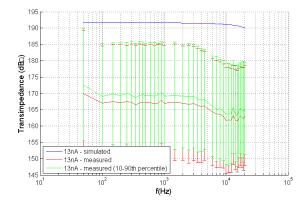

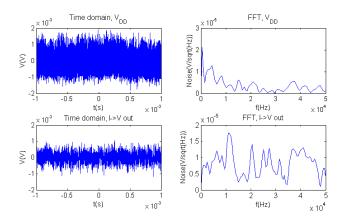

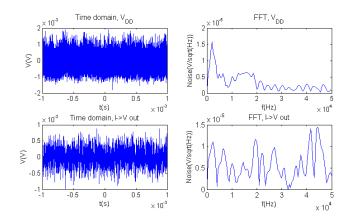

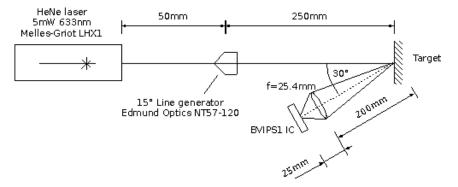

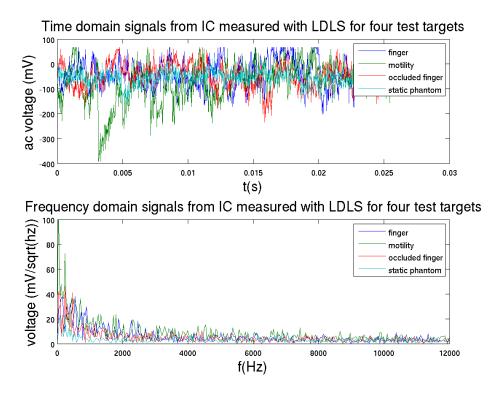

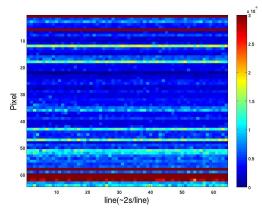

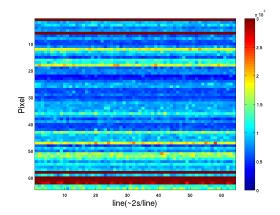

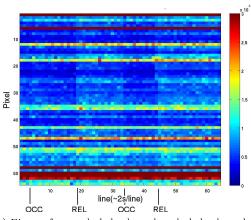

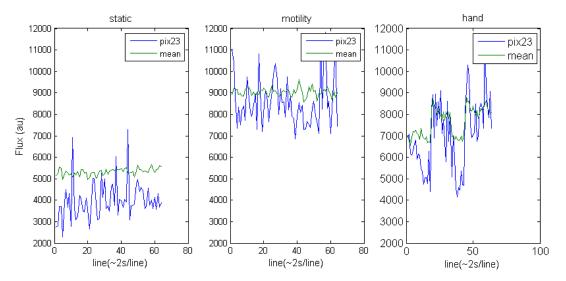

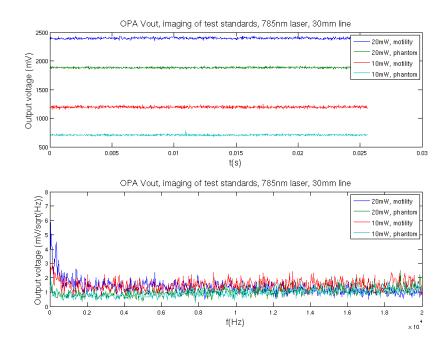

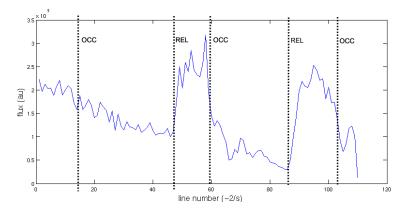

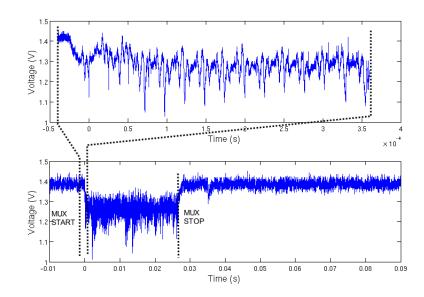

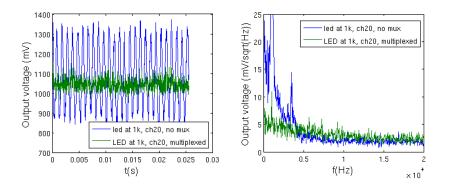

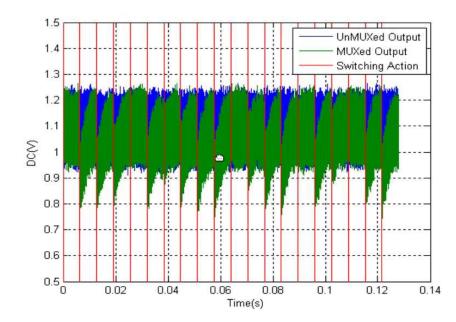

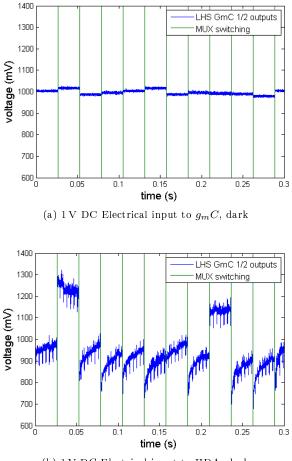

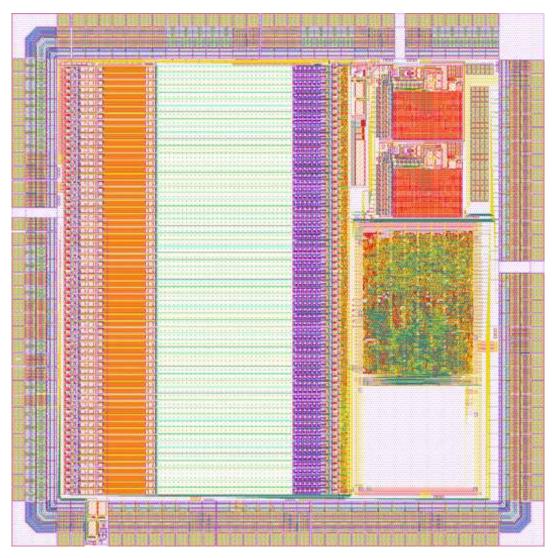

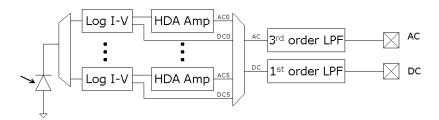

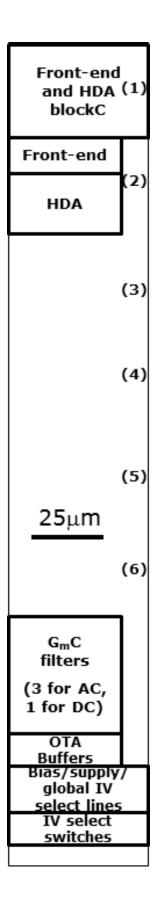

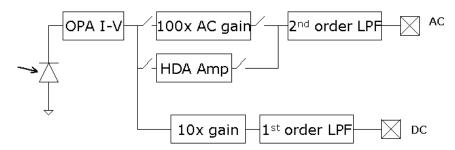

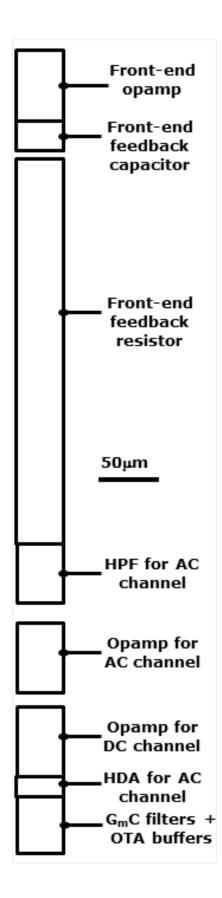

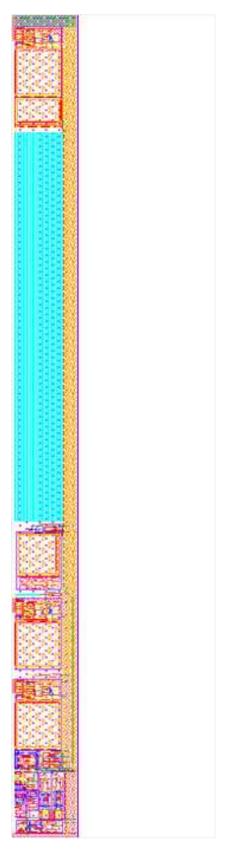

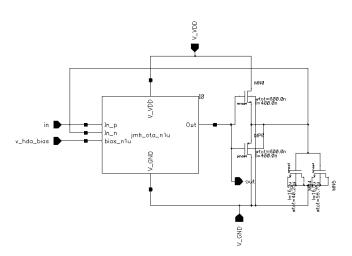

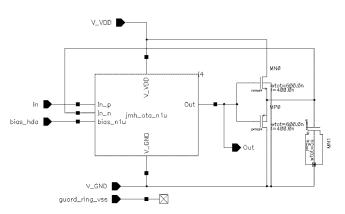

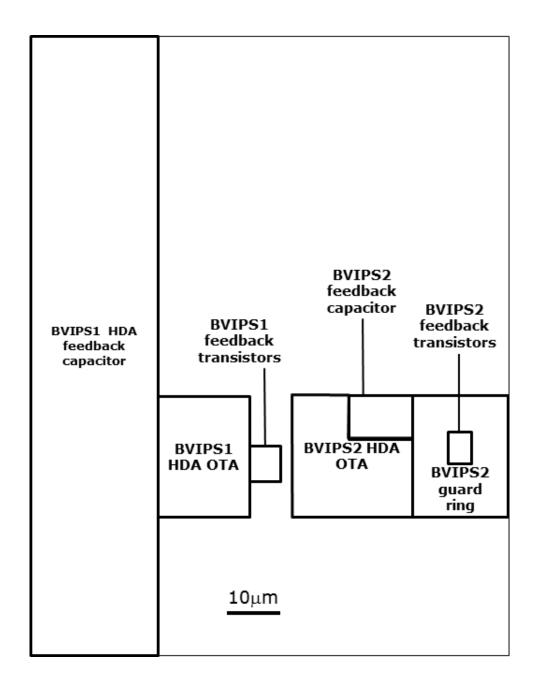

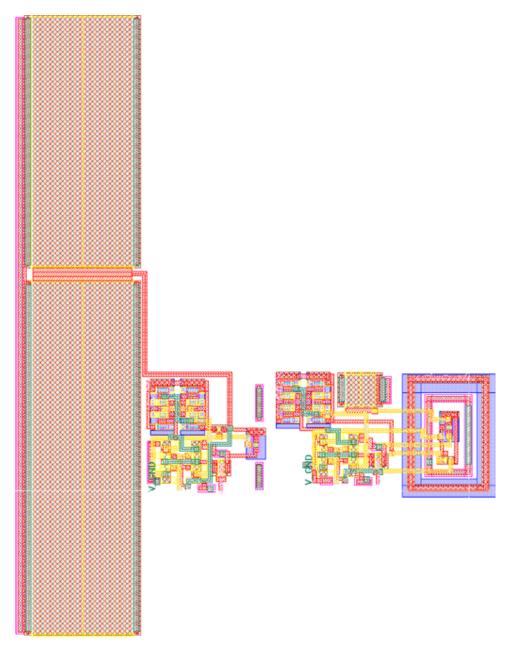

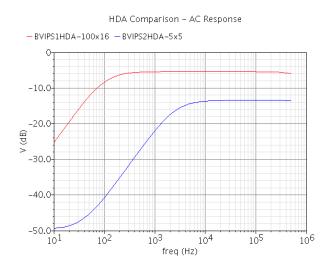

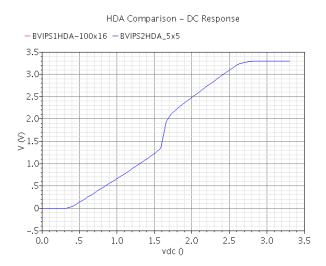

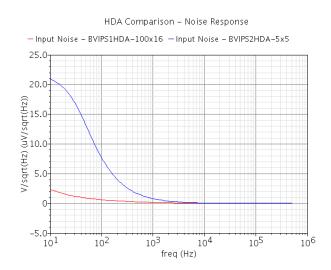

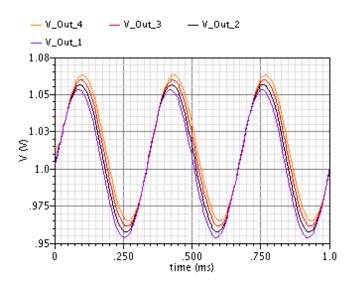

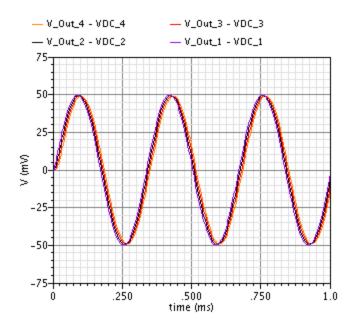

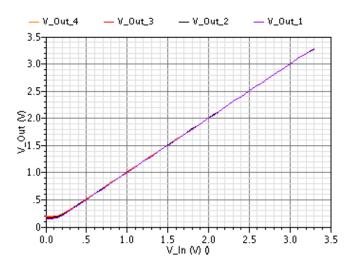

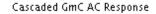

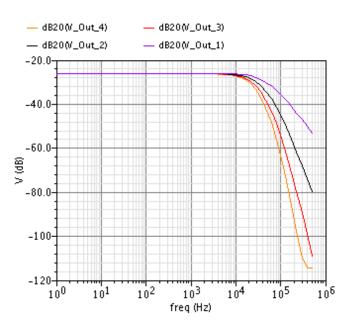

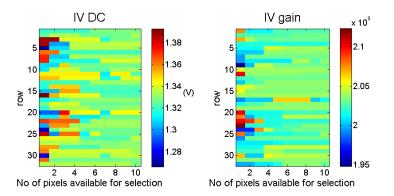

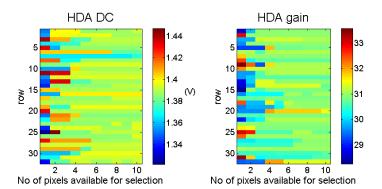

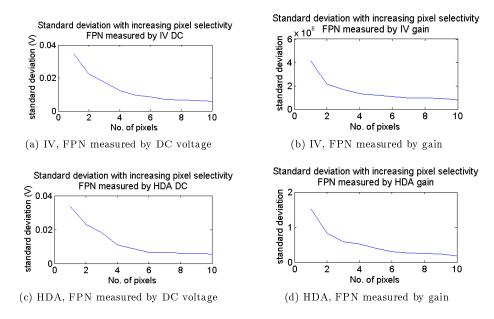

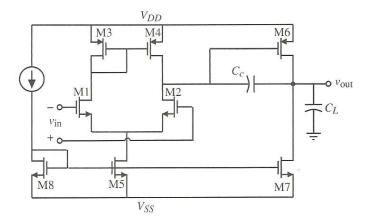

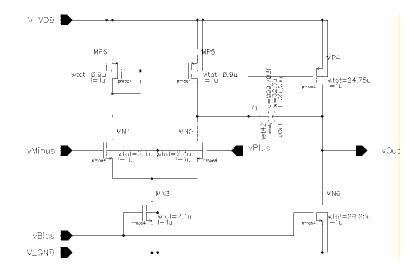

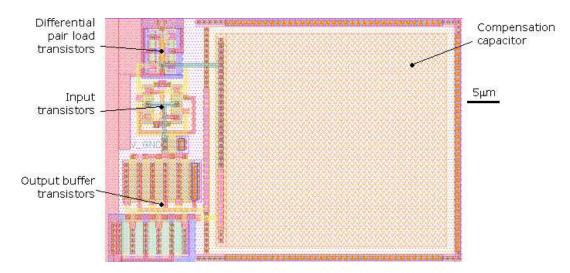

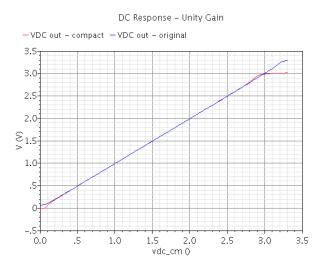

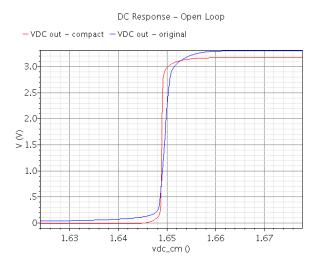

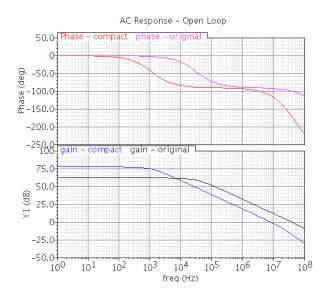

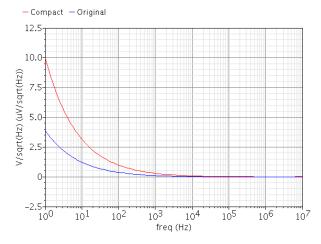

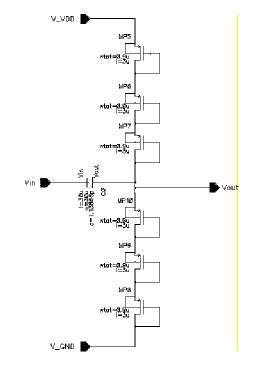

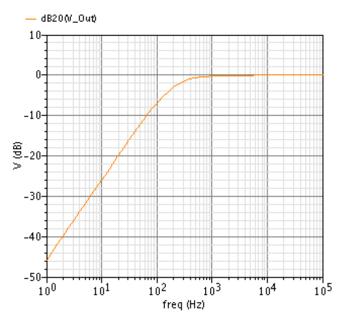

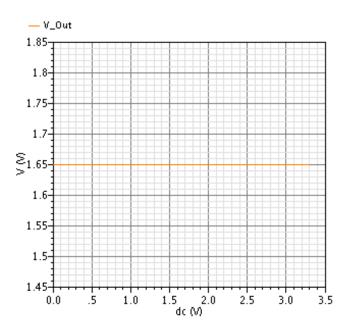

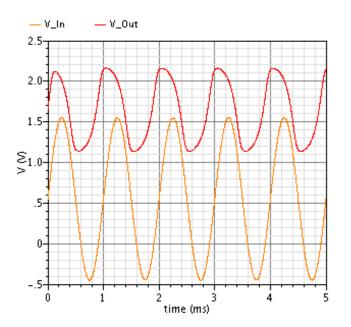

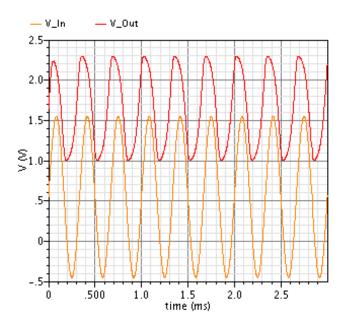

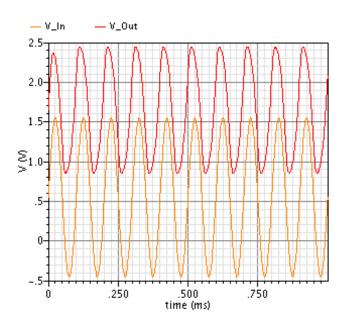

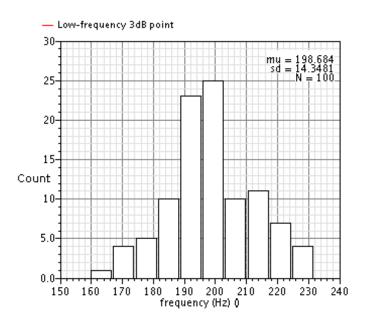

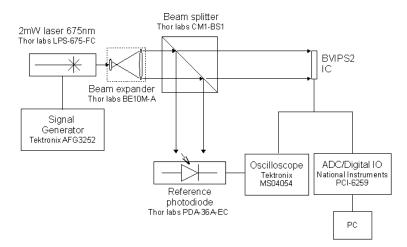

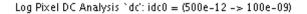

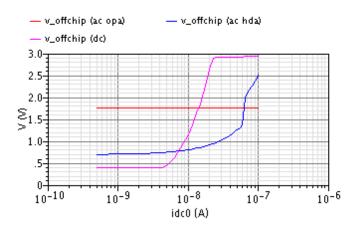

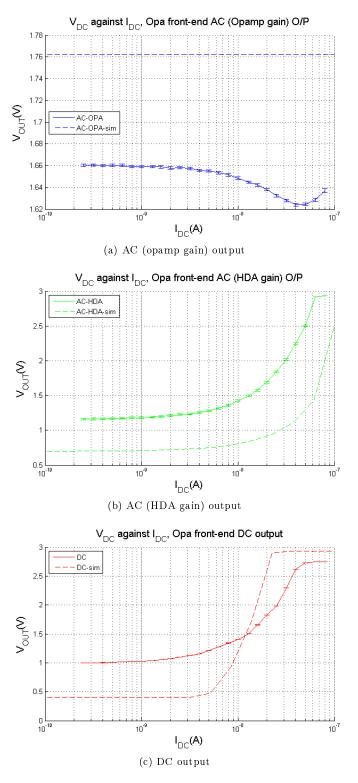

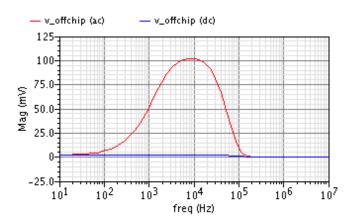

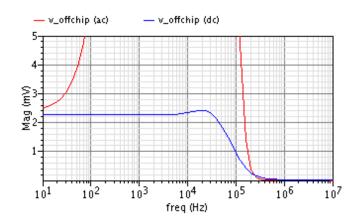

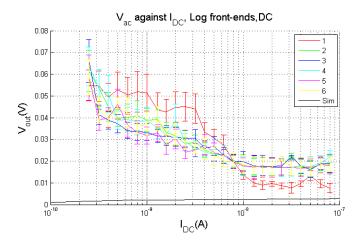

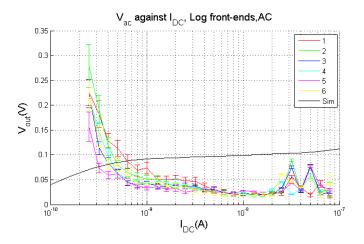

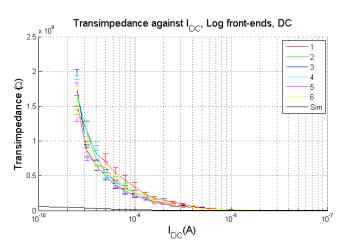

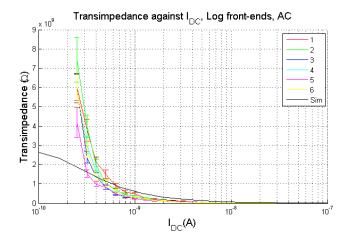

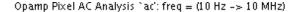

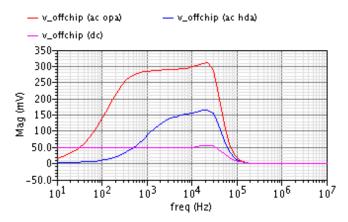

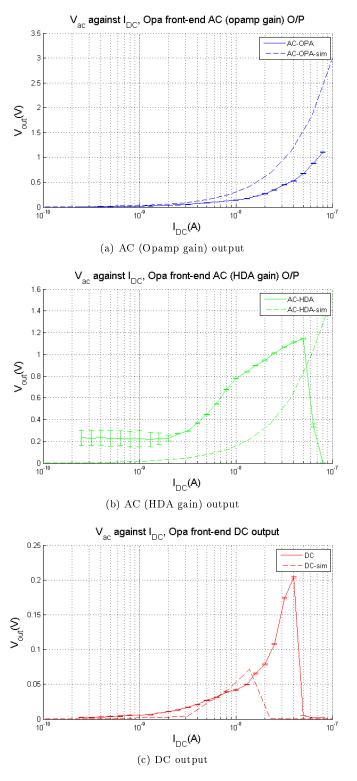

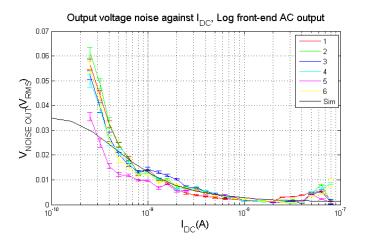

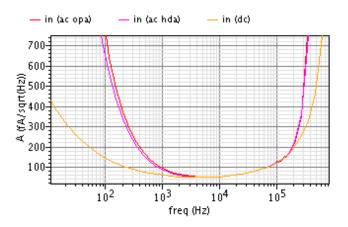

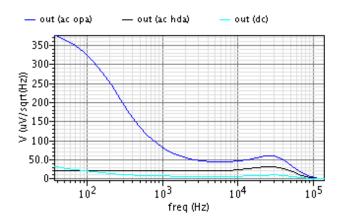

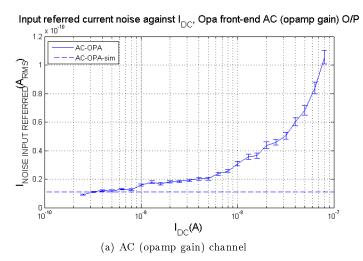

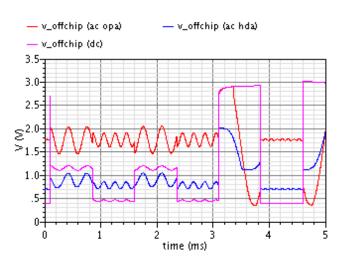

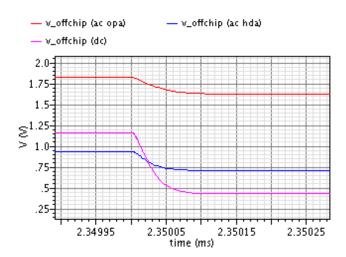

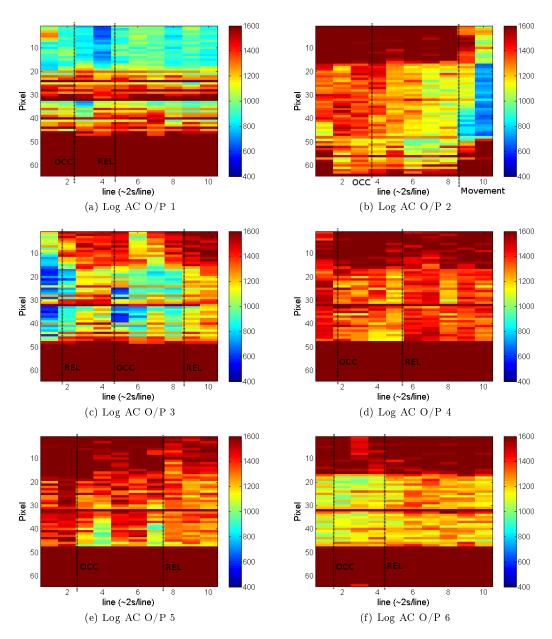

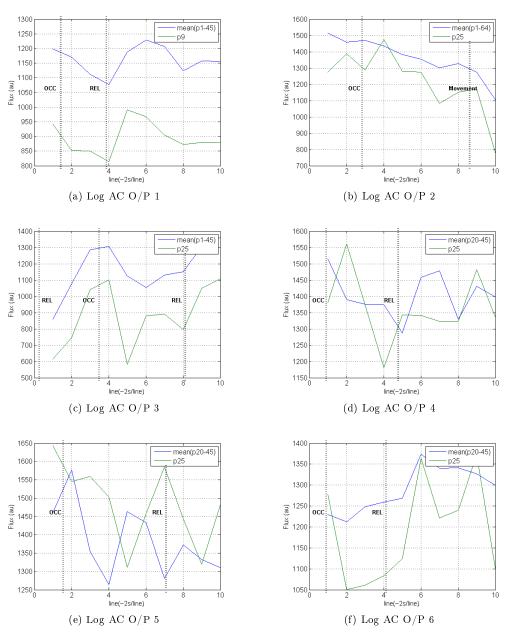

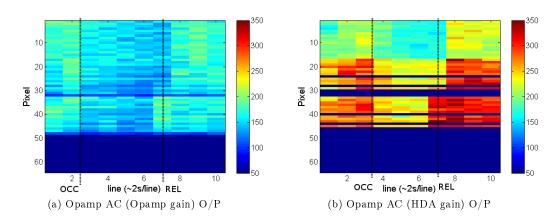

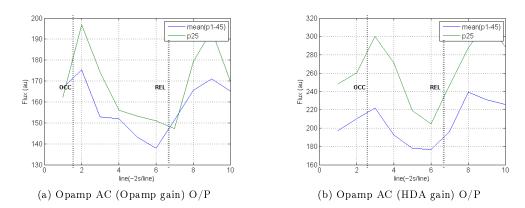

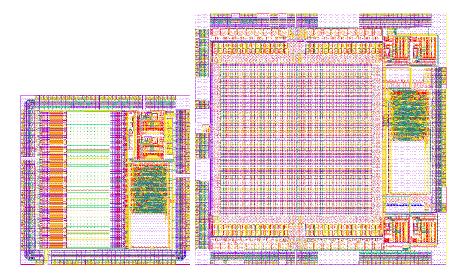

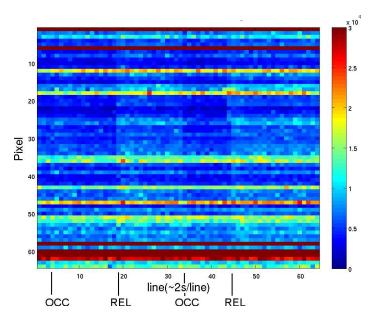

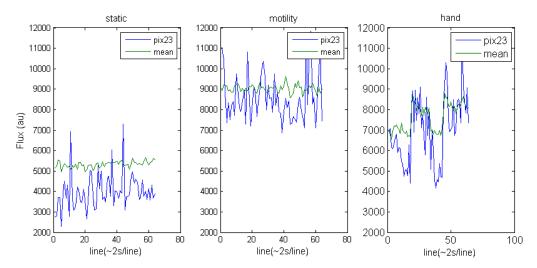

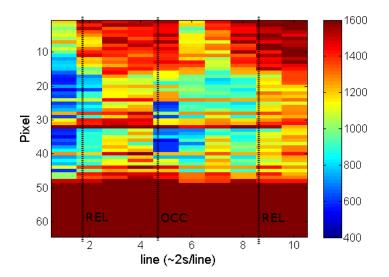

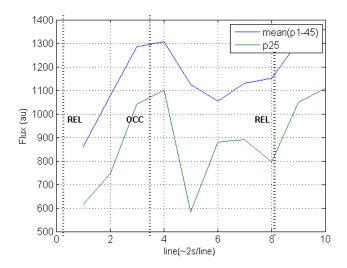

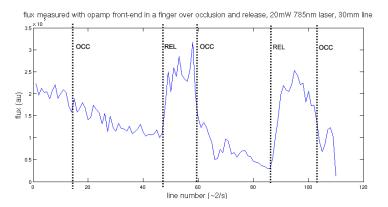

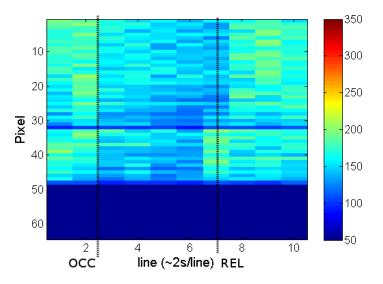

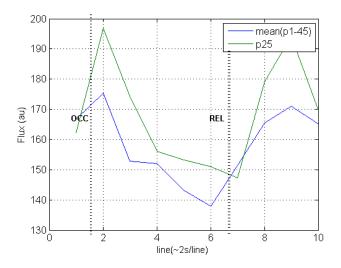

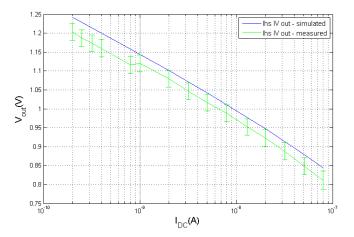

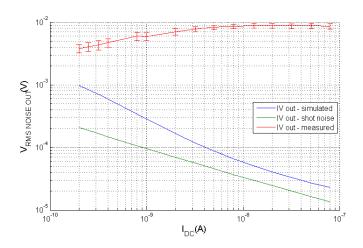

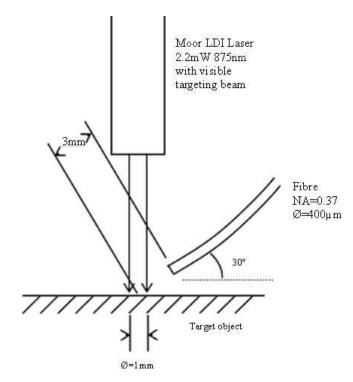

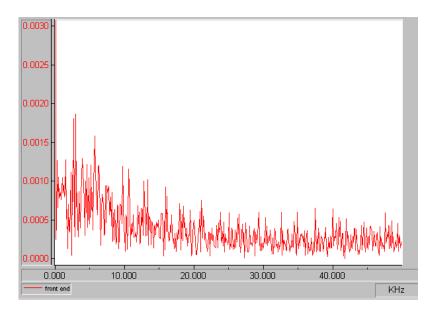

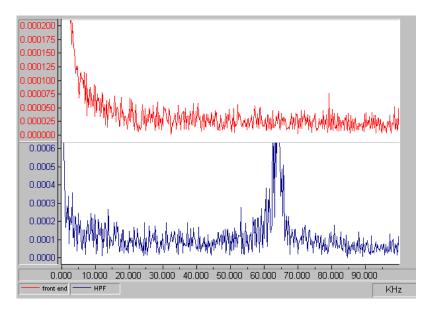

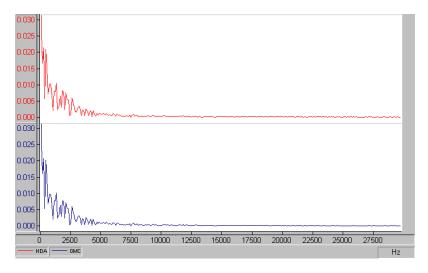

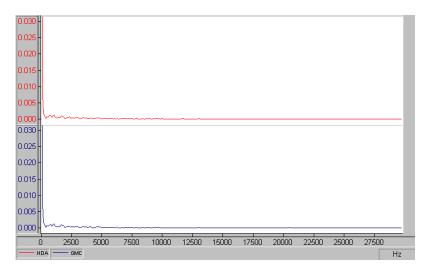

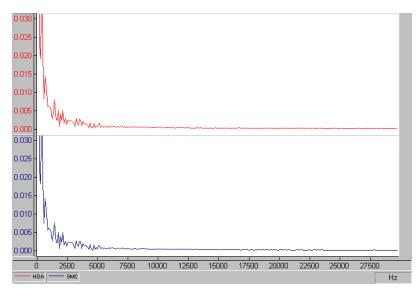

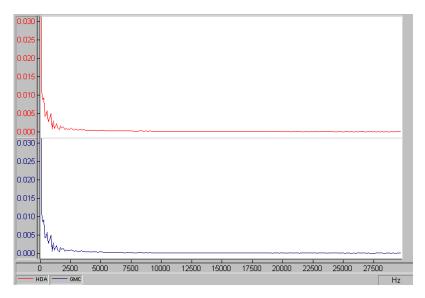

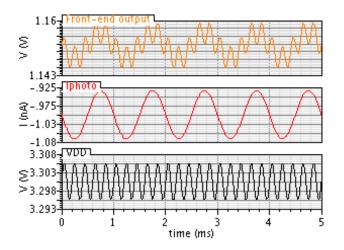

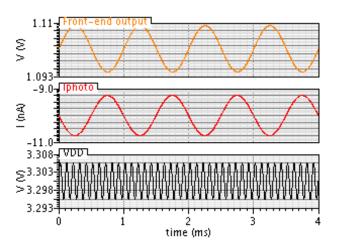

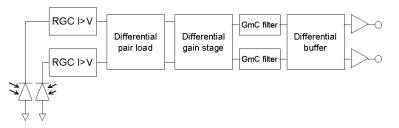

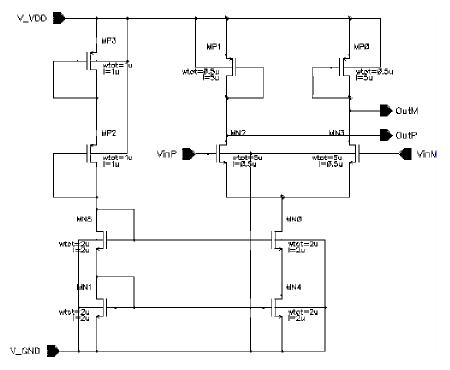

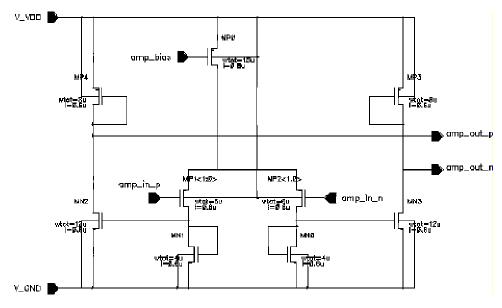

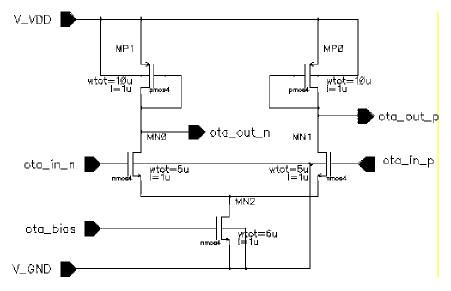

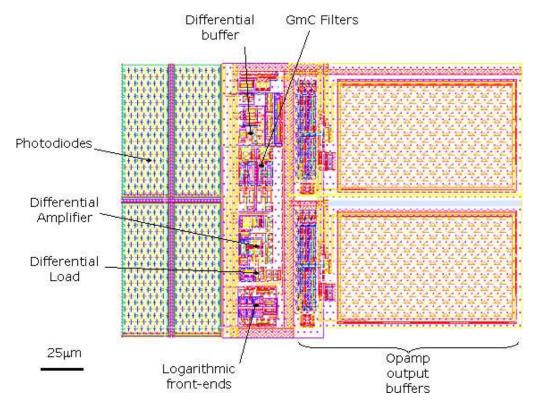

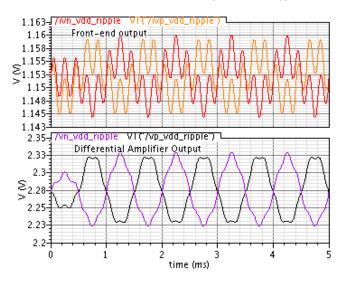

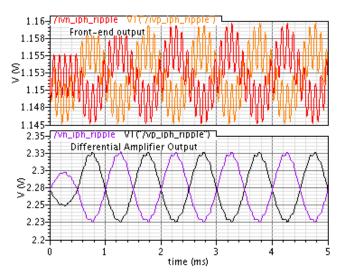

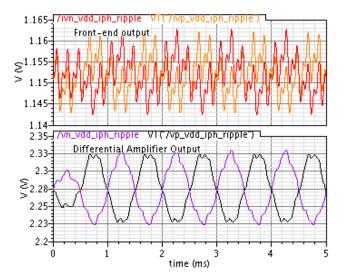

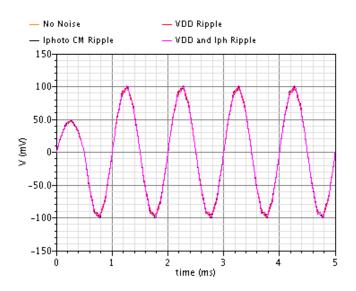

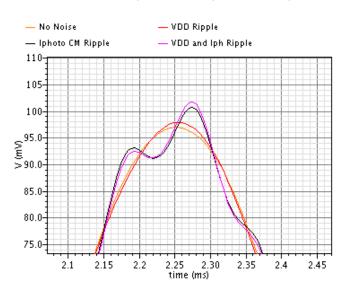

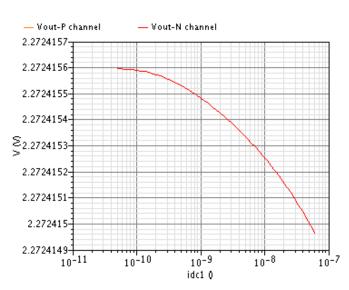

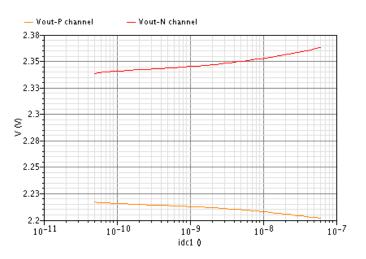

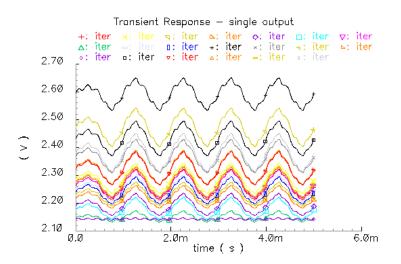

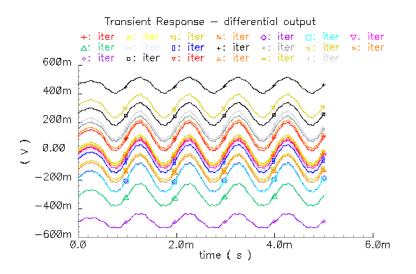

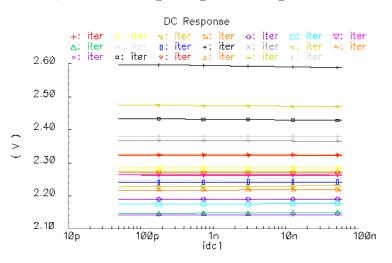

(1.16)