# Lopez Arevalo, Saul (2008) Matrix converter for frequency changing power supply applications. PhD thesis, University of Nottingham.

#### Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/10477/1/Saul Thesis.pdf

#### Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

- · Copyright and all moral rights to the version of the paper presented here belong to the individual author(s) and/or other copyright owners.

- To the extent reasonable and practicable the material made available in Nottingham ePrints has been checked for eligibility before being made available.

- Copies of full items can be used for personal research or study, educational, or notfor-profit purposes without prior permission or charge provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

- · Quotations or similar reproductions must be sufficiently acknowledged.

Please see our full end user licence at: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

#### A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact <a href="mailto:eprints@nottingham.ac.uk">eprints@nottingham.ac.uk</a>

# Matrix Converter for Frequency Changing Power Supply Applications

Saúl López Arévalo, MSc

Submitted to the University of Nottingham for the degree of Doctor of Philosophy, January 2008.

#### Abstract

The purpose of this work is to investigate the design and implementation of a 7.5kVA Matrix Converter-based power supply for aircraft applications (GPU Ground Power Unit). A Matlab/Simulink as well as SABER simulation analysis of the candidate Matrix Converter system is provided. The design and implementation of the Matrix Converter is described, with particular attention to the strict requirements of the given power supply application. This AC-AC system is proposed as an effective replacement for the conventional AC-DC-AC system which employs a two-step power conversion.

The Matrix Converter is an attractive topology of power converter for power supply applications where factors such as the absence of electrolytic capacitors, the potentiality of increasing power density, reducing size and weight and good input power quality are fundamental.

An improved control structure is proposed. This structure employs an ABC reference frame implementation comprising at the Repetitive Control strategy combined with a traditional tracking controller in order to attenuate or eliminate the unwanted harmonic distortion in the output voltage waveform of the Matrix Converter and to compensate for the steady-state error. The system with the proposed control was initially fully analyzed and verified by simulation. The analysis of the input and output waveforms identified the constraints that need to be satisfied to ensure successful operation of the converter. Finally, to demonstrate both the Matrix Converter concept and the control strategy proposed, a 7.5kVA prototype of the proposed system was constructed and tested in Nottingham PEMC laboratory. The experimental results obtained confirmed the expectations from the simulation study and the validity of the power converter and control design.

#### Acknowledgements

I would like to express my most sincere gratitude to my supervisors Prof Patrick W. Wheeler and Dr Pericle Zanchetta for their guidance and support over the course of this project and for believing in me. I would also like to express my sincere gratitude to Dr David Thomas for acting as internal examiner, and to Dr Nigel Schofield of the University of Manchester for acting as external examiner.

I would like especially to thanks Dr Lee Empringham, Dr Liliana de Lillo, Dr Si Dang, Dr Thiwanka Wijekoon and Edward Christopher for their friendship, their precious advise and technical support, without their help I could have never dreamt to reach the end of this project. I would like to thank the staff of the PEMC group at the University of Nottingham and all of the technicians of the ground floor workshop, for providing the necessary help, both theoretical and practical, to carry out this research.

I would like to thank my dear wife and my family for their infinite patience, support and love. They helped me to regain enthusiasm, strength and determination during the difficult times. Thanks for being there for me and believing in me, always. My deepest and sincere gratitude to M. en C. Jesús Reyes García for all the support I received and for believing that we can work hard with the hope of building a better country.

I gratefully acknowledge my sponsor, the Mexican Council of the Science and Technology (CONACYT), who have given me an opportunity to study abroad by granting me a scholarship. I owe them and promise that we will develop our lovely country together.

Thanks to the National Polytechnic Institute of Mexico for all the support I received to continue my studies.

Finally, I gratefully acknowledge the Public Education Ministry of Mexico for the complementary scholarship I received through my studies.

## Contents

| 1 | Inti | troduction                                      |    |  |

|---|------|-------------------------------------------------|----|--|

|   | 1.1  | The Matrix Converter                            | 1  |  |

|   | 1.2  | Control                                         | 4  |  |

|   | 1.3  | Modulation                                      | 5  |  |

|   | 1.4  | Research Outcomes                               | 8  |  |

|   | 1.5  | Project Objectives                              | 9  |  |

|   | 1.6  | Thesis Overview                                 | 10 |  |

| 2 | Mo   | dulation Techniques and Control                 | 12 |  |

|   | 2.1  | Introduction                                    | 12 |  |

|   | 2.2  | Matrix Converter Concept                        | 13 |  |

|   | 2.3  | Modulation Techniques                           | 17 |  |

|   |      | 2.3.1 Basic Solution for the Modulation Problem | 21 |  |

CONTENTS iv

|     | 2.3.2  | Venturini's Optimum Method                                 | 23 |

|-----|--------|------------------------------------------------------------|----|

|     | 2.3.3  | Scalar Method                                              | 26 |

|     | 2.3.4  | Space Vector Modulation (SVM) Method                       | 27 |

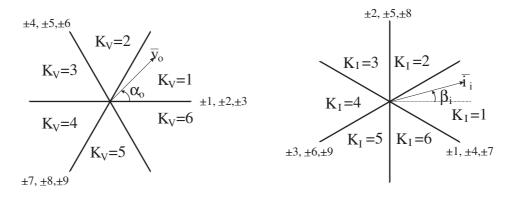

|     |        | 2.3.4.1 Space Vectors                                      | 27 |

|     |        | 2.3.4.2 Matrix Converter Switching States                  | 28 |

|     |        | 2.3.4.3 Selection of Switching States                      | 30 |

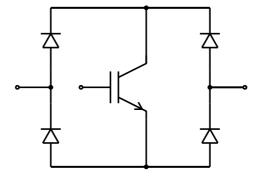

| 2.4 | Topolo | ogies of Bi-directional Switches                           | 33 |

|     | 2.4.1  | Diode Bridge Topology                                      | 34 |

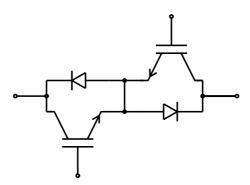

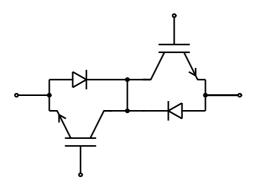

|     | 2.4.2  | IGBT with Anti-parallel Diode Topologies                   | 34 |

| 2.5 | Matrix | Converter Commutation Methods                              | 37 |

|     | 2.5.1  | Simple Commutation Methods                                 | 38 |

|     |        | 2.5.1.1 Deadtime Commutation Method                        | 38 |

|     |        | 2.5.1.2 Overlap Commutation Method                         | 39 |

|     | 2.5.2  | Advanced Commutation Methods                               | 39 |

|     |        | 2.5.2.1 The Current Direction Based Commutation Method     | 39 |

|     |        | 2.5.2.2 The Voltage Magnitude Based Commutation Method     | 42 |

|     |        | 2.5.2.3 The Voltage Magnitude and Current Direction Method | 44 |

| 2.6 | Input  | Filter                                                     | 45 |

CONTENTS v

|   | 2.7 | Outpu                         | at Filter                                          | 48                      |

|---|-----|-------------------------------|----------------------------------------------------|-------------------------|

|   | 2.8 | Contr                         | ol                                                 | 50                      |

|   |     | 2.8.1                         | Transformations                                    | 51                      |

|   |     | 2.8.2                         | Tracking Controller                                | 54                      |

|   |     | 2.8.3                         | Repetitive Controller                              | 58                      |

|   |     |                               | 2.8.3.1 Internal mode-based Repetitive Controller  | 59                      |

|   |     |                               | 2.8.3.2 External model-based Repetitive Controller | 60                      |

|   | 2.9 | Summ                          | ary                                                | 62                      |

| 3 | Mat | trix Co                       | onverter Power Supply Simulation                   | 64                      |

|   |     |                               |                                                    |                         |

|   | 3.1 | Introd                        | uction                                             | 64                      |

|   | 3.1 |                               | ical Specifications                                | 64<br>66                |

|   |     | Techn                         |                                                    |                         |

|   | 3.2 | Techn                         | ical Specifications                                | 66                      |

|   | 3.2 | Techn                         | ical Specifications                                | 66<br>67                |

|   | 3.2 | Techn Comp 3.3.1 3.3.2        | ical Specifications                                | 66<br>67<br>69          |

|   | 3.2 | Techn Comp 3.3.1 3.3.2        | ical Specifications                                | 66<br>67<br>69<br>73    |

|   | 3.2 | Techn Comp 3.3.1 3.3.2 Simula | ical Specifications                                | 666<br>677<br>699<br>73 |

CONTENTS vi

|   | 3.5 | Simulation with Tracking Controller                                     | 86 |

|---|-----|-------------------------------------------------------------------------|----|

|   |     | 3.5.1 Voltage Control in d-q Reference Frame                            | 88 |

|   |     | 3.5.2 Voltage Control in ABC Reference Frame                            | 91 |

|   | 3.6 | Voltage Control with Tracking Controller plus Repetitive Controller . 9 | 93 |

|   | 3.7 | Summary                                                                 | 00 |

| 4 | Mat | rix Converter Implementation 10                                         | )2 |

|   | 4.1 | Introduction                                                            | 02 |

|   | 4.2 | Overview of prototype converter                                         | 03 |

|   | 4.3 | Matrix Converter Power Circuit                                          | 05 |

|   |     | 4.3.1 Power Module                                                      | 06 |

|   |     | 4.3.2 Power Plane                                                       | 07 |

|   |     | 4.3.3 Gate Drive Circuit                                                | 08 |

|   |     | 4.3.4 Output Filter                                                     | 09 |

|   |     | 4.3.5 Input Filter                                                      | 12 |

|   |     | 4.3.6 Measurement Boards                                                | 15 |

|   | 4.4 | Matrix Converter Control Implementation                                 | 16 |

|   |     | 4.4.1 Digital Signal Processor                                          | 18 |

|   |     | 4.4.2 Field Programmable Gate Array                                     | 20 |

CONTENTS vii

|   |     | 4.4.3  | Host Po     | rt Interface                                                       | 124 |

|---|-----|--------|-------------|--------------------------------------------------------------------|-----|

|   |     | 4.4.4  | Second      | Order Controller                                                   | 126 |

|   |     |        | 4.4.4.1     | Implementation of Tracking Controller in the d-q Reference Frame   | 127 |

|   |     |        | 4.4.4.2     | Implementation of Tracking Controller in the ABC Reference Frame   | 128 |

|   |     |        | 4.4.4.3     | Implementation of Repetitive Controller in the ABC Reference Frame | 129 |

|   | 4.5 | Summ   | ary         |                                                                    | 131 |

| 5 | Exp | erime  | ntal Res    | ${ m ults}$                                                        | 132 |

|   | 5.1 | Introd | uction .    |                                                                    | 132 |

|   | 5.2 |        |             | Output Voltage with No Controller using ABC Reference              | 133 |

|   | 5.3 | Contro | ol of the ( | Output Voltage using Tracking Controller                           | 137 |

|   |     | 5.3.1  | Matrix (    | Converter connected to a Resistive Balanced Load                   | 137 |

|   |     | 5.3.2  | Matrix (    | Converter connected to a Resistive, Unbalanced Load                | 142 |

|   |     | 5.3.3  |             | Converter connected to a Resistive-Inductive Balanced              | 145 |

|   |     | 5.3.4  |             | Converter connected to a Resistive-Inductive Unbal-<br>oad         | 146 |

|   |     | 5.3.5  | Matrix (    | Converter with Load Disconnected                                   | 151 |

CONTENTS viii

|              | 5.4  |                  | ontroller                                                           | 154 |

|--------------|------|------------------|---------------------------------------------------------------------|-----|

|              |      | 5.4.1            | Matrix Converter connected to a Resistive Balanced Load             | 154 |

|              |      | 5.4.2            | Matrix Converter connected to a Resistive Unbalanced Load .         | 157 |

|              |      | 5.4.3            | Matrix Converter connected to a Resistive-Inductive Balanced Load   | 159 |

|              |      | 5.4.4            | Matrix Converter connected to a Resistive-Inductive Unbalanced Load | 162 |

|              |      | 5.4.5            | Matrix Converter with Load Disconnected                             | 167 |

|              |      |                  | 5.4.5.1 Output Voltage of the Matrix Converter                      | 167 |

|              |      |                  | 5.4.5.2 Input and Output Currents of the Matrix Converter           | 167 |

|              | 5.5  | Summ             | ary                                                                 | 171 |

| 6            | Con  | clusio           | ns                                                                  | 173 |

|              | 6.1  | Contro           | ol of output voltage under unbalanced conditions                    | 175 |

|              | 6.2  | Repeti           | itive control strategy                                              | 175 |

|              | 6.3  | $Furth \epsilon$ | er work                                                             | 176 |

|              | 6.4  | Public           | eations resulting from the work                                     | 178 |

| $\mathbf{A}$ | Pap  | er Pul           | blished                                                             | 190 |

| В            | Scho | $_{ m ematic}$   | Diagrams used in Saber                                              | 191 |

CONTENTS ix

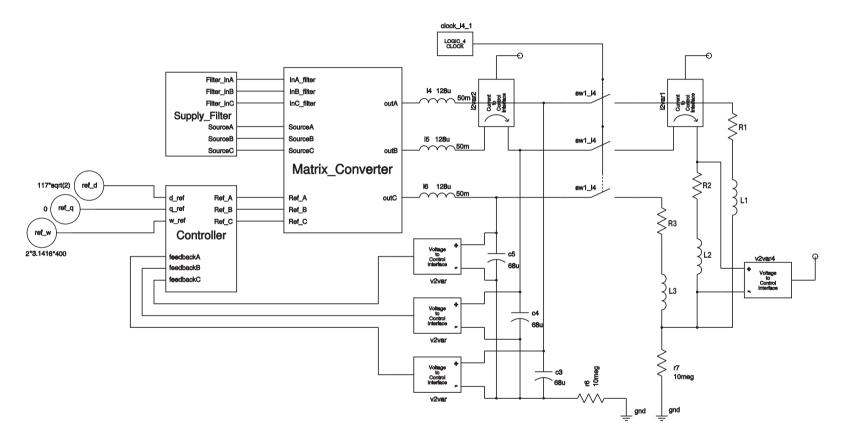

|              | B.1 | General Schematic Diagram of the System used in Saber Simulations   | 191 |

|--------------|-----|---------------------------------------------------------------------|-----|

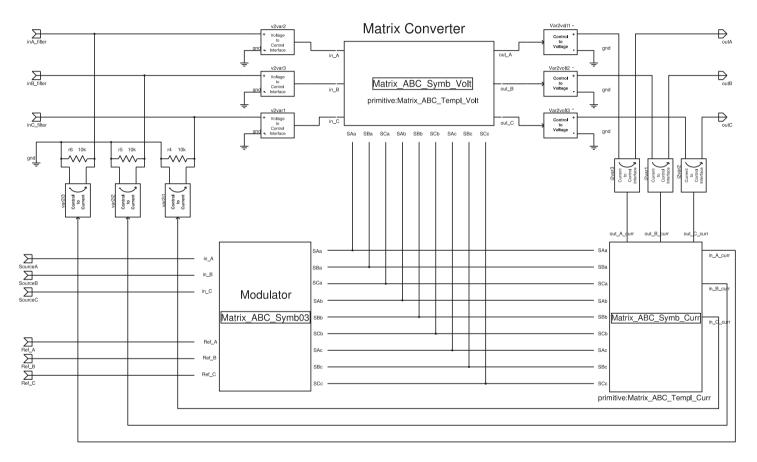

|              | B.2 | Schematic Diagram of the Matrix Converter used in Saber Simulations | 191 |

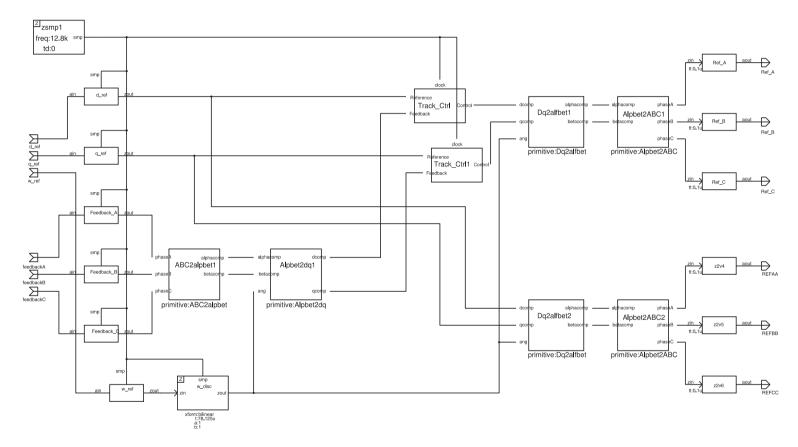

|              | В.3 | Schematic Diagram of the Controller used in Saber Simulations       | 193 |

| $\mathbf{C}$ | Sou | rce Code using MAST Language                                        | 196 |

|              | C.1 | MAST Code used in the Modulator                                     | 196 |

|              | C.2 | MAST Code used in for the Input Current Vector                      | 203 |

|              | C.3 | MAST Code used in for the Output Voltage Vector                     | 205 |

|              | C.4 | MAST Code used to model Bi-directional Switches                     | 208 |

| D            | Pro | grams Implemented in the DSP                                        | 209 |

|              | D.1 | Main Program Implemented in the DSP                                 | 209 |

|              | D.2 | Code of the Tracking Controller Implementation                      | 226 |

|              | D.3 | Code of the Repetitive Controller Implementation                    | 227 |

# List of Figures

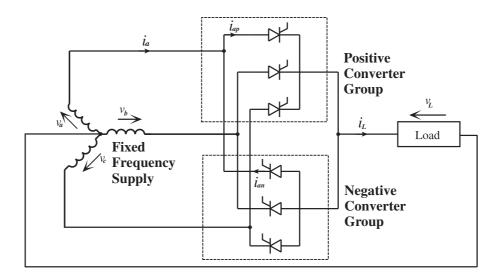

| 1.1 | Single-phase load fed from a three-pulse cycloconverter                                                                                              | 3  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

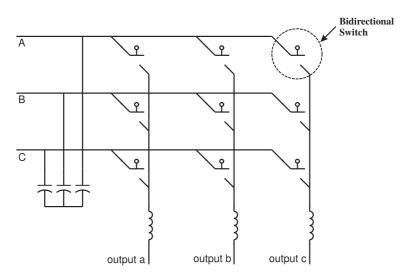

| 1.2 | Structure of Matrix Converter                                                                                                                        | 3  |

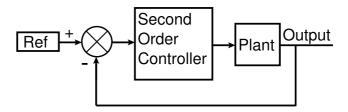

| 1.3 | Structure of plant with second order controller                                                                                                      | 4  |

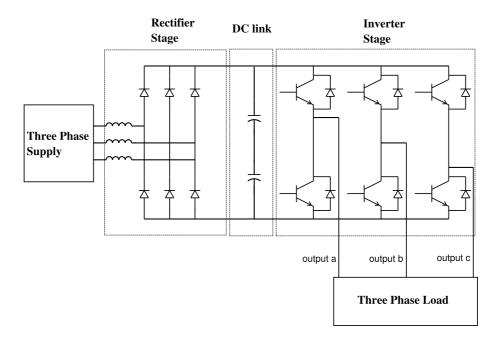

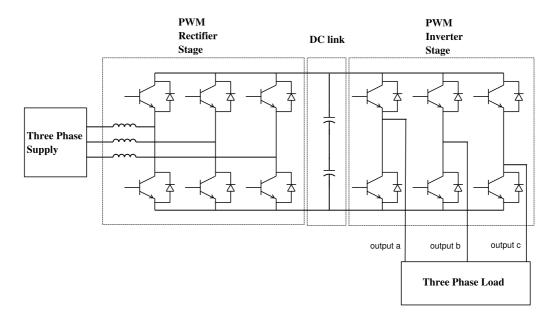

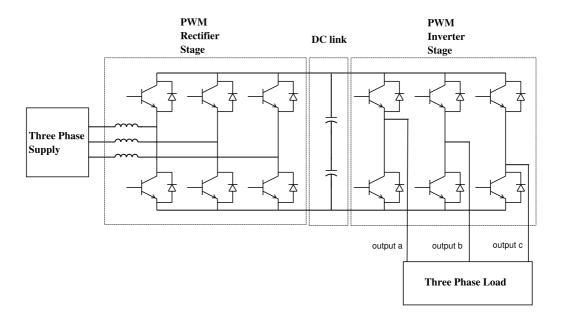

| 1.4 | Basic diagram of the Voltage Source Converter, power components                                                                                      | 6  |

| 1.5 | Schematic of the back to back converter                                                                                                              | 7  |

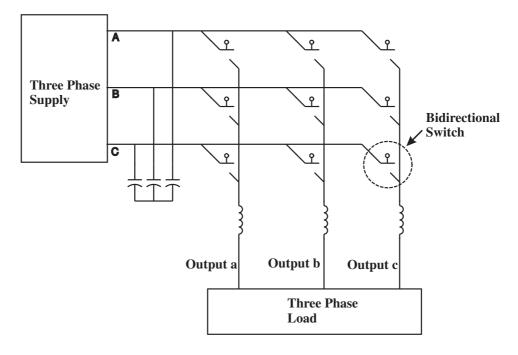

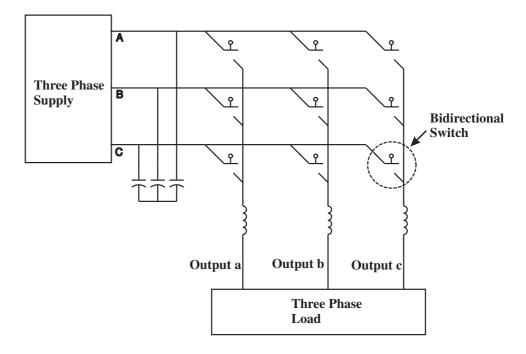

| 1.6 | Simplified representation of a Matrix Converter system                                                                                               | 7  |

| 2.1 | Schematic of AC to AC converter                                                                                                                      | 14 |

| 2.2 | Simplified representation of a Matrix Converter system                                                                                               | 15 |

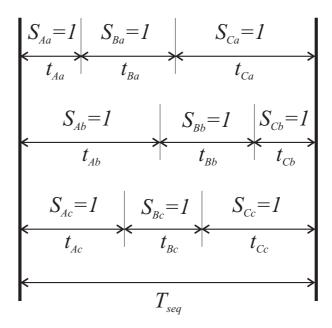

| 2.3 | General form of switching pattern                                                                                                                    | 20 |

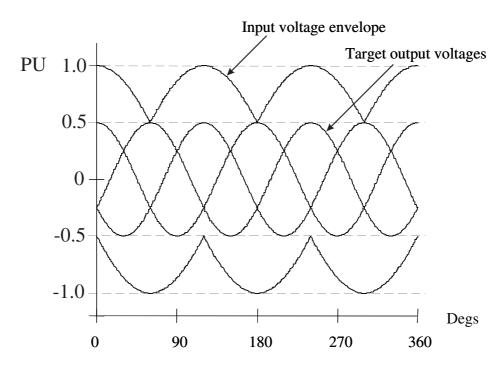

| 2.4 | Theoretical waveforms illustrating the $50\%$ voltage ratio limit                                                                                    | 24 |

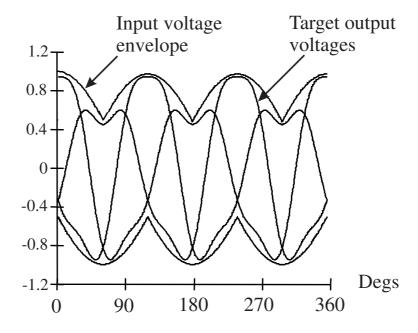

| 2.5 | Theoretical waveforms illustrating the third harmonic addition to obtain the 86% optimum voltage ratio limit. This is a rms value to rms value ratio | 24 |

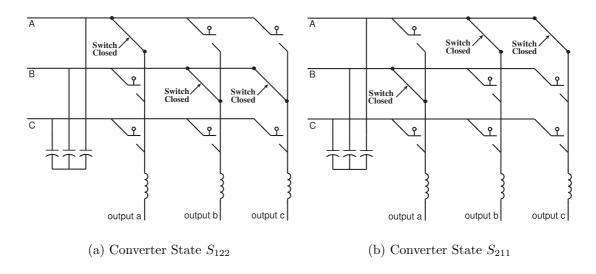

| 2.6  | States of the converter for switching configuration +1 and -1                                                    | 31 |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 2.7  | Synthesis of output voltage and input current space phasor                                                       | 31 |

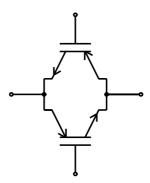

| 2.8  | Diode bridge bi-directional switch                                                                               | 34 |

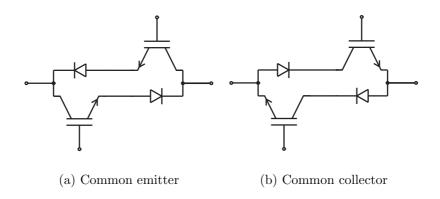

| 2.9  | Common emitter bi-directional switch                                                                             | 35 |

| 2.10 | Common collector bi-directional switch                                                                           | 36 |

| 2.11 | Back to back devices without central connection                                                                  | 36 |

| 2.12 | Reverse blocking IGBT bi-directional switch                                                                      | 37 |

| 2.13 | These conditions must be avoided for safe operation                                                              | 38 |

| 2.14 | Two-phase to single-phase converter                                                                              | 40 |

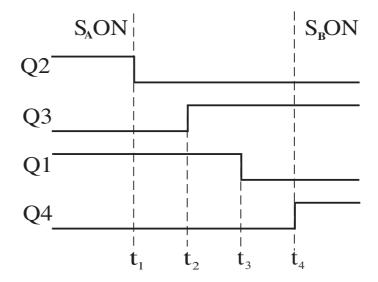

| 2.15 | Timing diagram for four-step current commutation between two switches.                                           | 41 |

| 2.16 | Timing diagram for two-step current commutation between two switches.                                            | 41 |

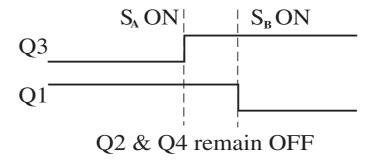

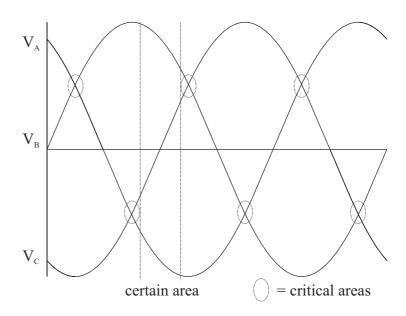

| 2.17 | Critical areas of commutation sequence selection                                                                 | 43 |

| 2.18 | Critical areas between phase A and B - Two additional sequences to phase C are inserted in the modulation period | 44 |

| 2.19 | Diagram to calculate transfer function of input filter                                                           | 47 |

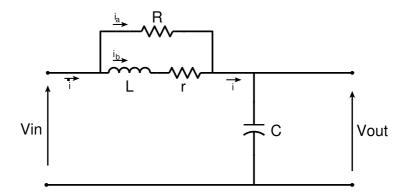

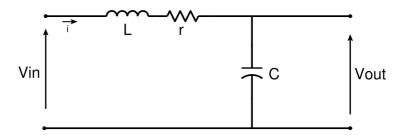

| 2.20 | Diagram to calculate transfer function of output filter                                                          | 49 |

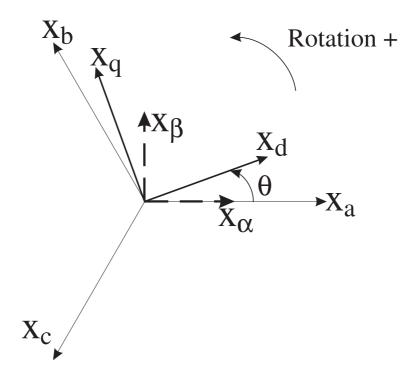

| 2.21 | d-q rotating reference frame and its relationship with the $abc$ stationary reference frame                      | 52 |

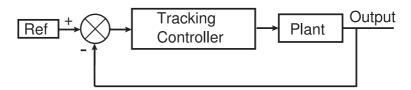

| 2.22 | Diagram of a control system                                                                                      | 55 |

LIST OF FIGURES xii

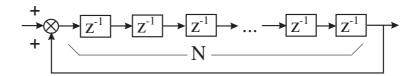

| 2.23 | Generation of repetitive signal                                                  | 60 |

|------|----------------------------------------------------------------------------------|----|

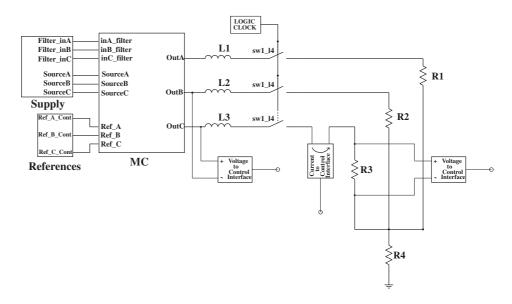

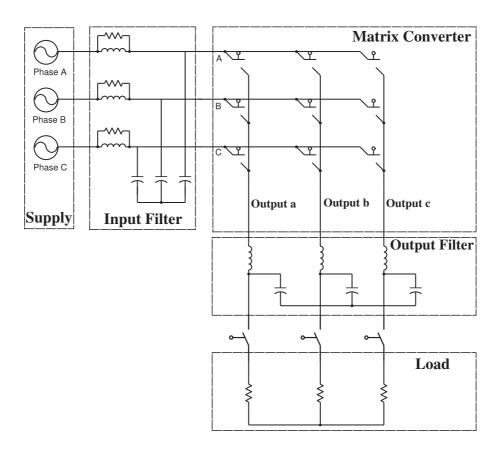

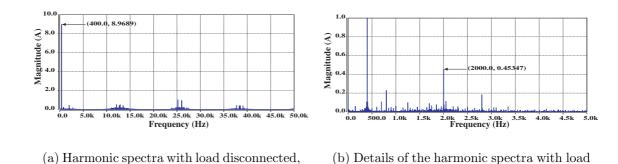

| 3.1  | Schematic of Matrix Converter used in Saber simulation                           | 72 |

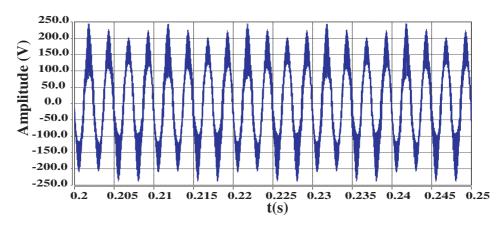

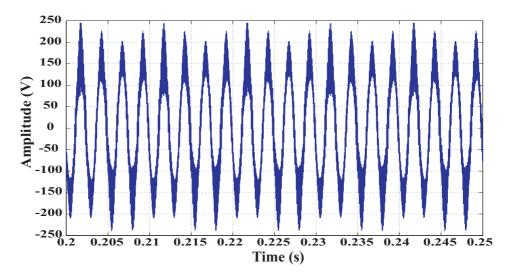

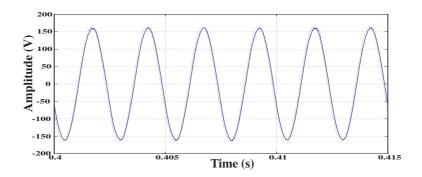

| 3.2  | Waveform of load voltage in phase c when simulated in Saber                      | 72 |

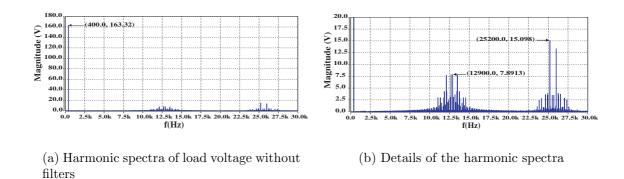

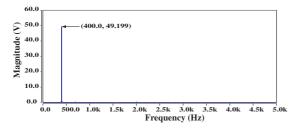

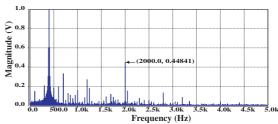

| 3.3  | Harmonic spectra of load voltage in phase c using Saber                          | 73 |

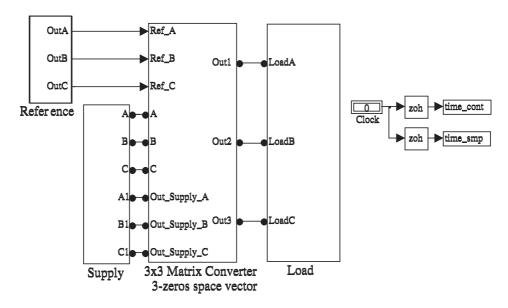

| 3.4  | Schematic of Matrix Converter used in Matlab/Simulink simulation                 | 73 |

| 3.5  | Load voltage in phase c when simulated in Matlab/Simulink                        | 74 |

| 3.6  | Harmonic spectra of load voltage in phase c using Matlab/Simulink                | 75 |

| 3.7  | Output voltage in phase c without filters                                        | 75 |

| 3.8  | Line-to-line voltage and load current of the Matrix Converter                    | 76 |

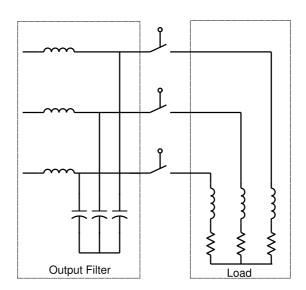

| 3.9  | Structure of output filter                                                       | 76 |

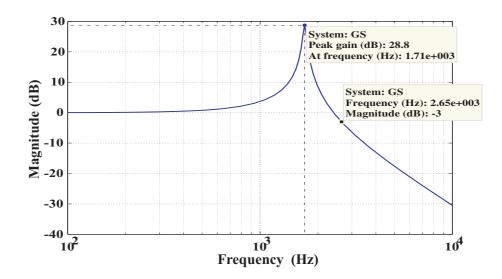

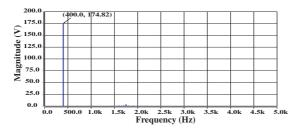

| 3.10 | Bode plot of the output filter transfer function in s domain                     | 79 |

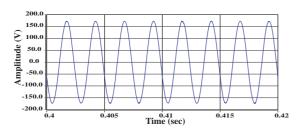

| 3.11 | Output voltage in phase c using the output LC low-pass filter                    | 80 |

| 3.12 | Harmonic spectra of output voltage in phase c                                    | 80 |

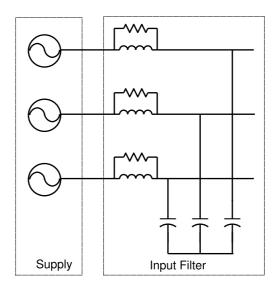

| 3.13 | Structure of input filter                                                        | 81 |

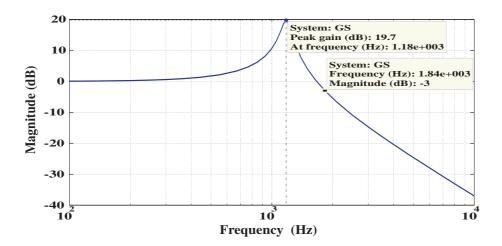

| 3.14 | Bode plot of the input filter transfer function in s domain                      | 84 |

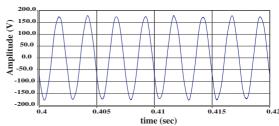

| 3.15 | Waveform of the output voltage in phase c using both the input and output filter | 85 |

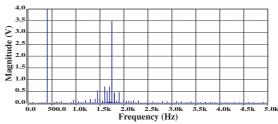

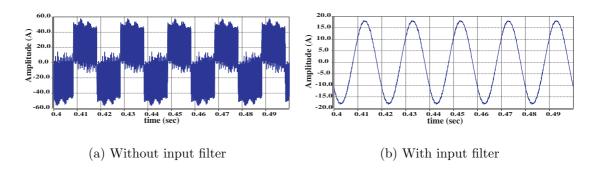

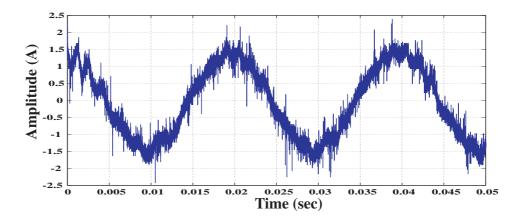

| 3.16 | Waveform of the input current in phase C                                         | 85 |

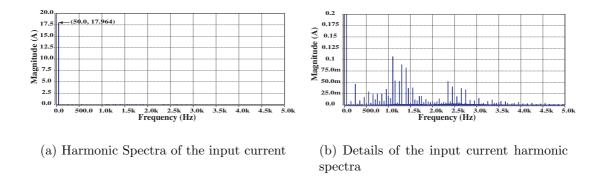

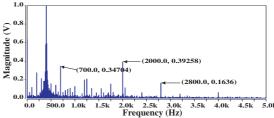

| 3.17 | Harmonic spectra of the input current in phase C                                 | 85 |

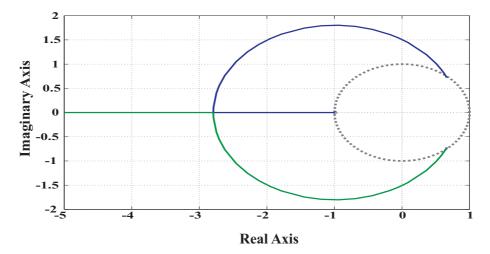

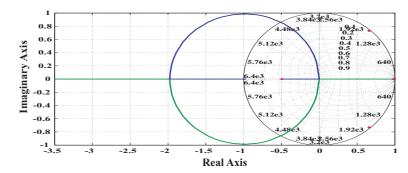

| 3.18 | Root locus of the input filter transfer function                                                                    | 86 |

|------|---------------------------------------------------------------------------------------------------------------------|----|

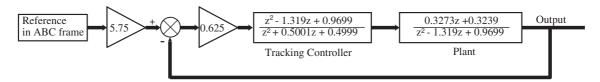

| 3.19 | Structure of the system using a second order controller as a tracking controller                                    | 88 |

| 3.20 | Root locus of the whole system shown in Figure 3.19                                                                 | 88 |

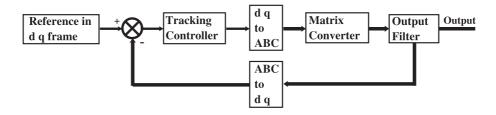

| 3.21 | Control strategy in d-q reference frame                                                                             | 88 |

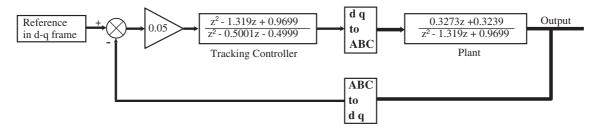

| 3.22 | Structure and final values of tracking controller when using control strategy in d-q reference frame                | 89 |

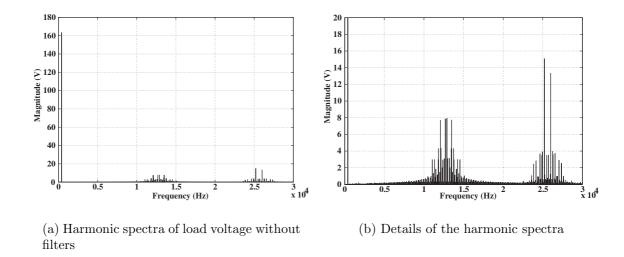

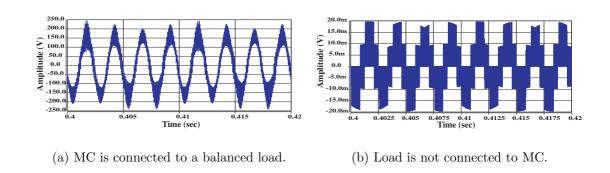

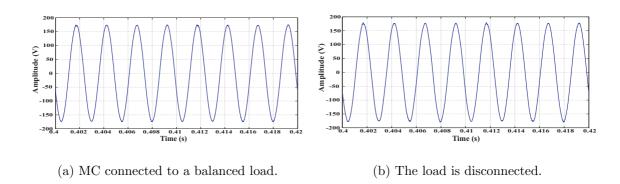

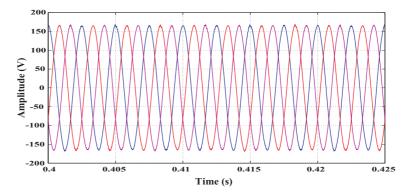

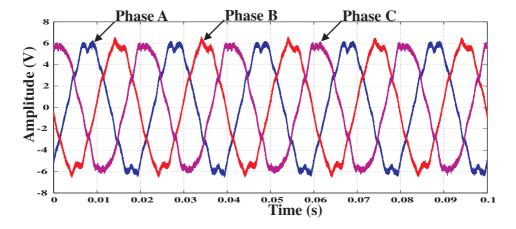

| 3.23 | Output voltage all phases using tracking controller when matrix Converter is connected to a perfectly balanced load | 89 |

| 3.24 | Output voltage in all phases using tracking controller when the Matrix Converter is not connected to a load         | 90 |

| 3.25 | Output voltage in all phases using tracking controller and connected to an unbalanced load                          | 90 |

| 3.26 | Control strategy in ABC reference frame                                                                             | 91 |

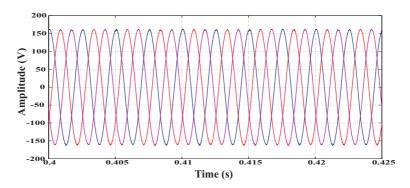

| 3.27 | Structure and final values of tracking controller when using control strategy in ABC reference frame                | 92 |

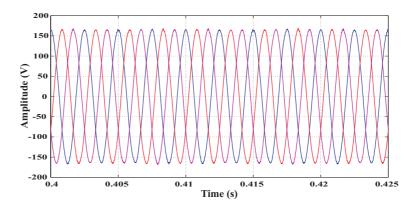

| 3.28 | Output voltage in phase c using tracking controller and connected to a balanced load                                | 92 |

| 3.29 | Output voltage in phase c using tracking controller and connected to an unbalanced load                             | 93 |

| 3.30 | Output voltage in phase c using tracking controller and load disconnected.                                          | 93 |

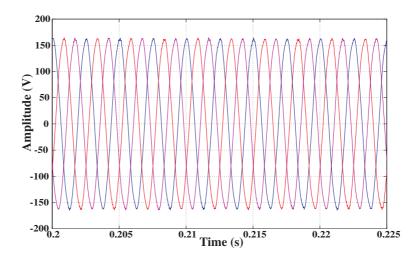

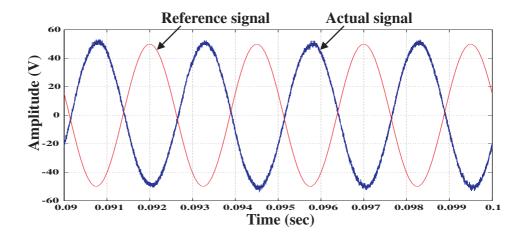

| 3.31 | Output voltage in phase c compared to the reference signal when tracking controller is used                               | 94  |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

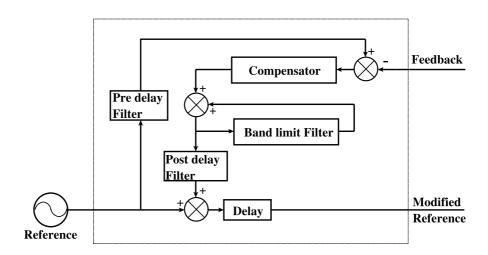

| 3.32 | Structure of Repetitive Controller                                                                                        | 95  |

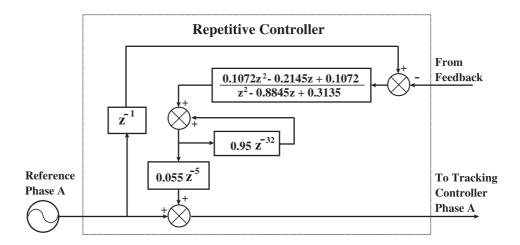

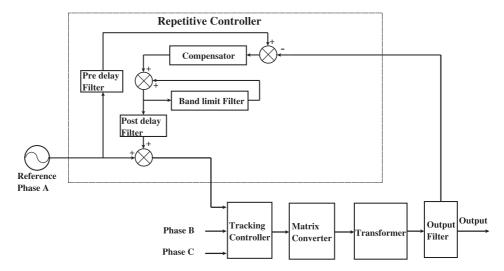

| 3.33 | Diagram of the Repetitive Controller proposed                                                                             | 98  |

| 3.34 | Overall diagram of the control structure proposed in ABC reference frame                                                  | 98  |

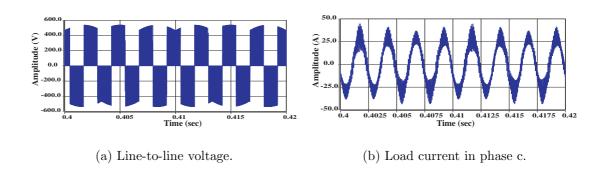

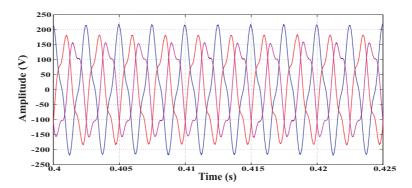

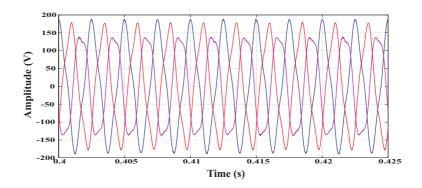

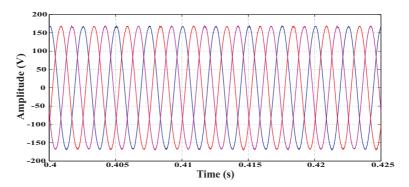

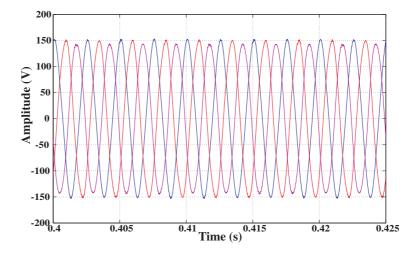

| 3.35 | Output voltage in all phases using tracking controller plus repetitive controller. A perfectly balanced load is connected | 99  |

| 3.36 | Output voltage in all phases using tracking controller plus repetitive controller. An unbalanced load is connected        | 99  |

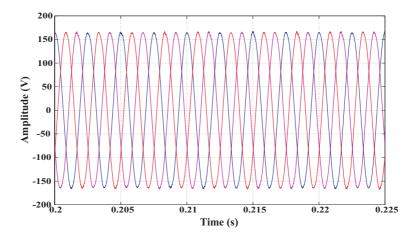

| 3.37 | Output voltage in all phases using tracking controller plus repetitive controller. Load is disconnected                   | 100 |

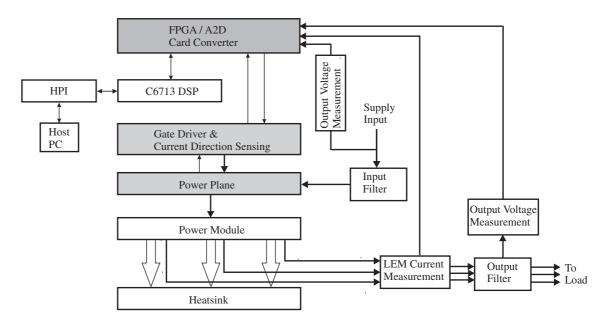

| 4.1  | Schematic of the rig                                                                                                      | 103 |

| 4.2  | Diagram of the Matrix Converter implementation                                                                            | 105 |

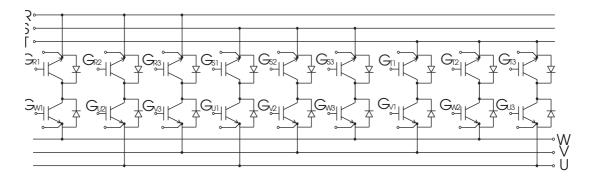

| 4.3  | Diagram of the power module                                                                                               | 106 |

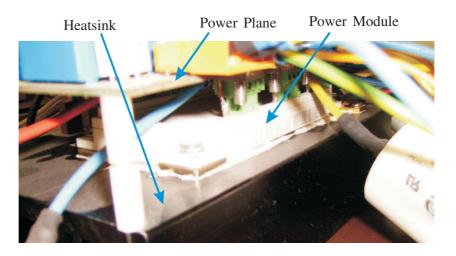

| 4.4  | Photograph of the power module                                                                                            | 107 |

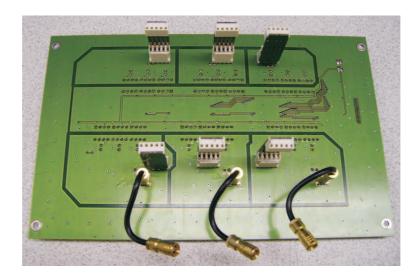

| 4.5  | Photograph of the gate driver, top view                                                                                   | 110 |

| 4.6  | Photograph of the gate driver, bottom view                                                                                | 110 |

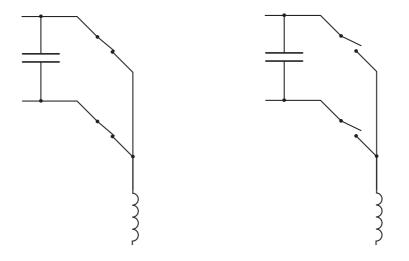

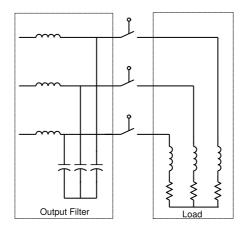

| 4.7  | Schematic diagram of the output filter                                                                                    | 111 |

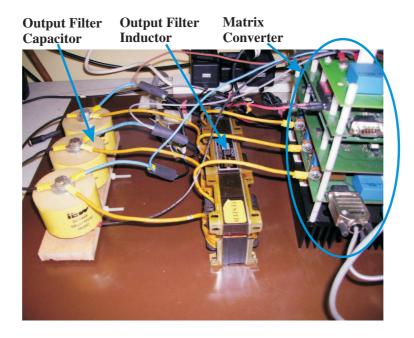

| 4.8  | Photograph of the output filter                                                                                           | 112 |

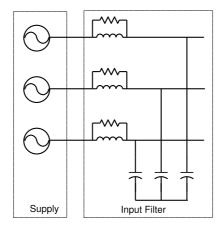

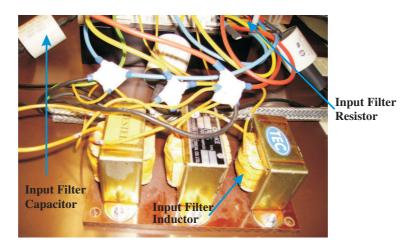

| 4.9  | Schematic diagram of the input filter                                         | 113 |

|------|-------------------------------------------------------------------------------|-----|

| 4.10 | Photograph of the input filter                                                | 114 |

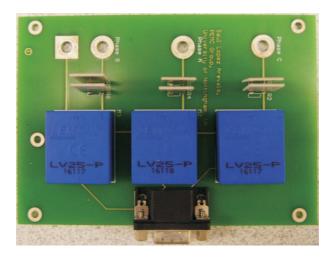

| 4.11 | Photograph of the voltage transducers                                         | 116 |

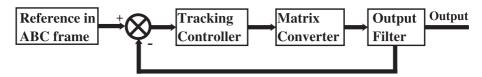

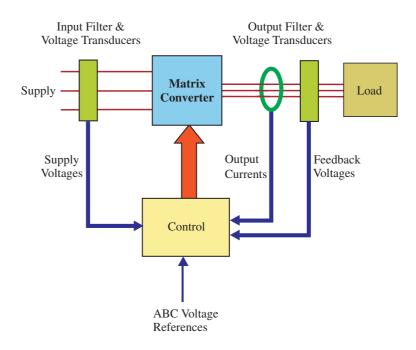

| 4.12 | Diagram to show the overall control structure                                 | 117 |

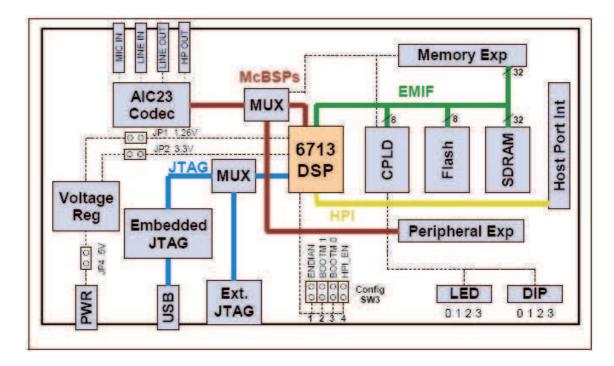

| 4.13 | Structure of the DSK C6713                                                    | 118 |

| 4.14 | Host port Interface (HPI) daughtercard                                        | 119 |

| 4.15 | Photograph of the Digital Signal Processor (DSP)                              | 120 |

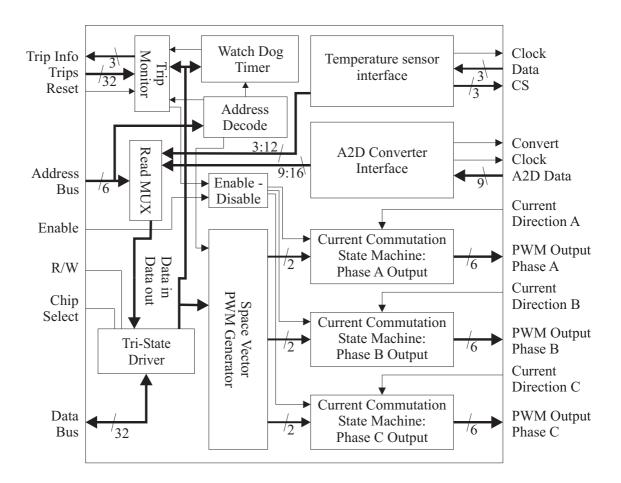

| 4.16 | FPGA block diagram                                                            | 121 |

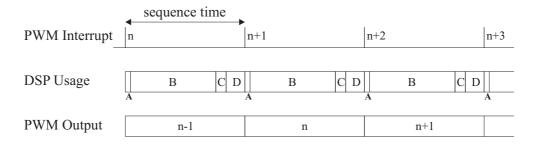

| 4.17 | Diagram to show PWM interrupt DSP usage                                       | 123 |

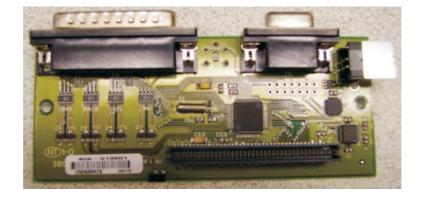

| 4.18 | Photograph of the FPGA board, top view                                        | 124 |

| 4.19 | Photograph of the HPI mounted on the DSP, top view                            | 125 |

| 4.20 | Screen from the HPI Interface in Matlab                                       | 126 |

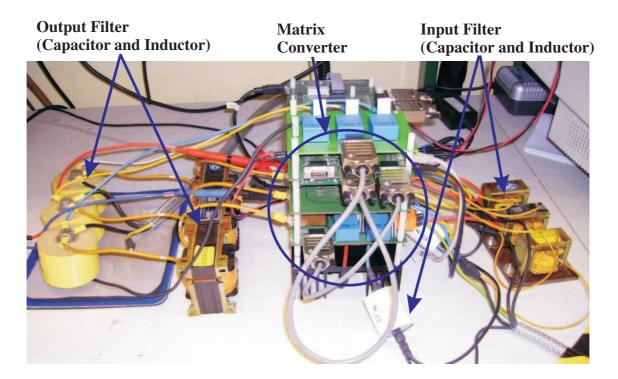

| 4.21 | Photograph of the final Matrix Converter prototype                            | 131 |

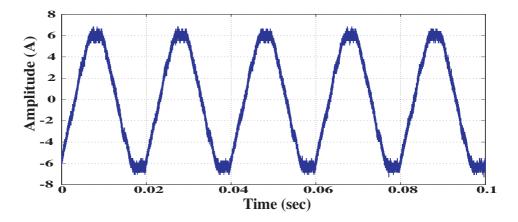

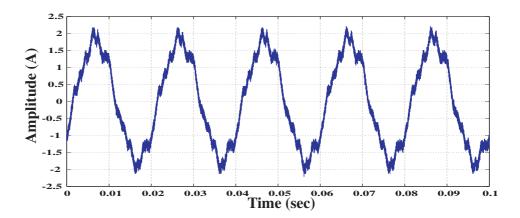

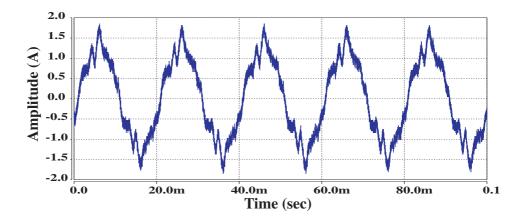

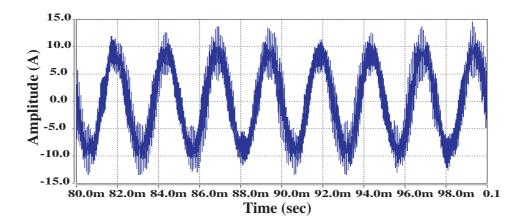

| 5.1  | Output voltage in phase c with a balanced RL load and no controller.          | 135 |

| 5.2  | Output line to line voltage with a balanced RL load and no controller.        | 135 |

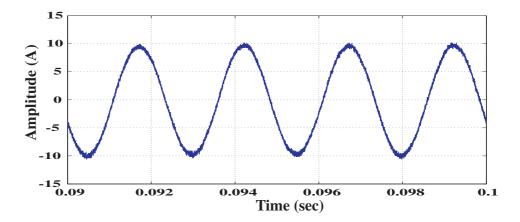

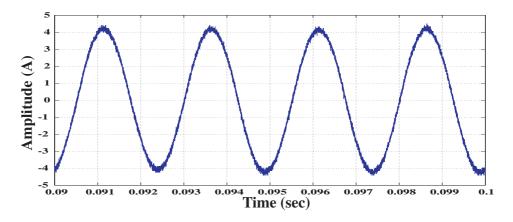

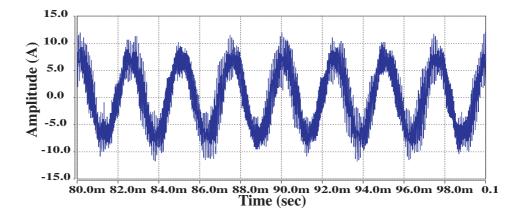

| 5.3  | Input current in phase c with a balanced RL load and no controller            | 136 |

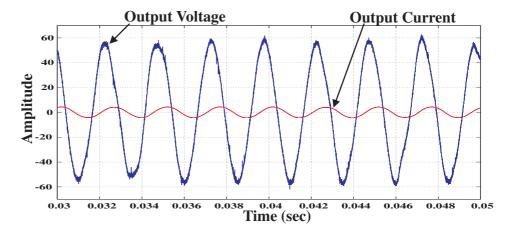

| 5.4  | Load voltage and current in phase c with a balanced RL load and no controller | 136 |

| 5.5  | Diagram of basic circuit used in the test                                     | 138 |

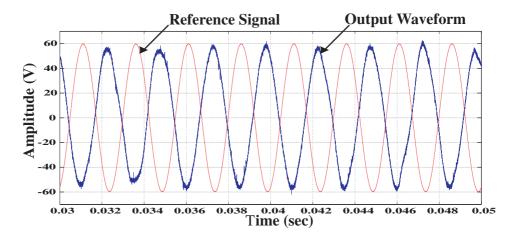

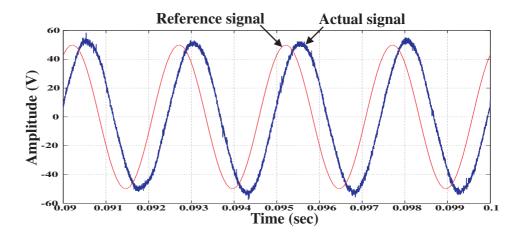

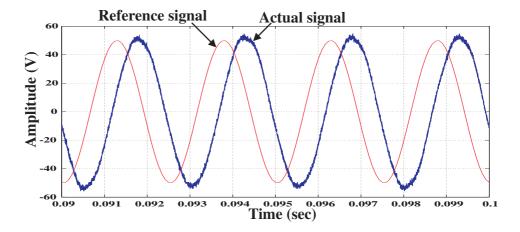

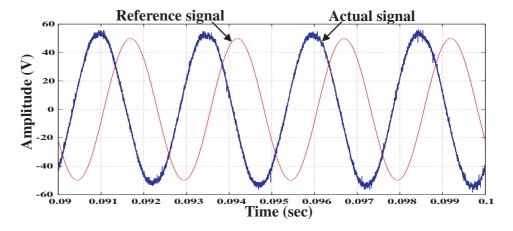

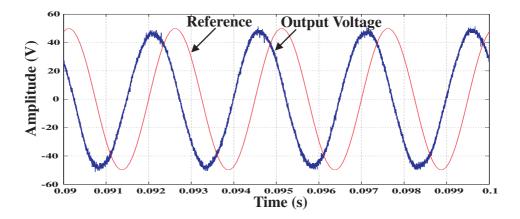

| 5.6  | Reference signal and output voltage in phase a with a pure resistive, balanced load and tracking controller                                                                                                                                        | 139 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

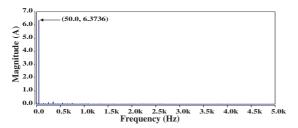

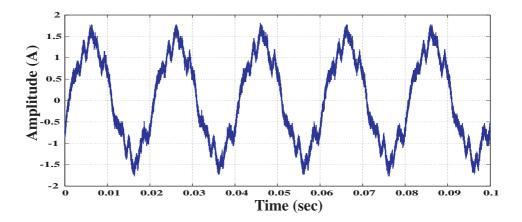

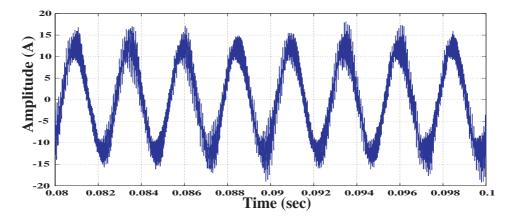

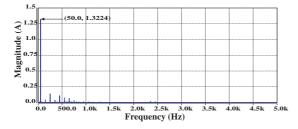

| 5.7  | Input current in phase a with a pure resistive, balanced load and tracking controller                                                                                                                                                              | 140 |

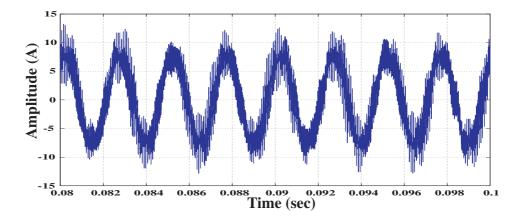

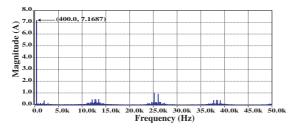

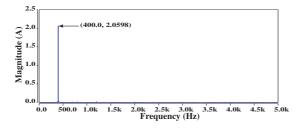

| 5.8  | Harmonic spectra of input current in phase A when tracking controller is used                                                                                                                                                                      | 140 |

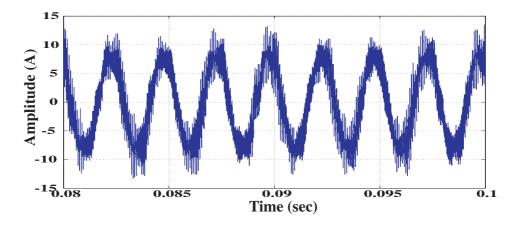

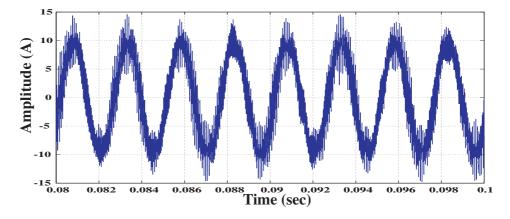

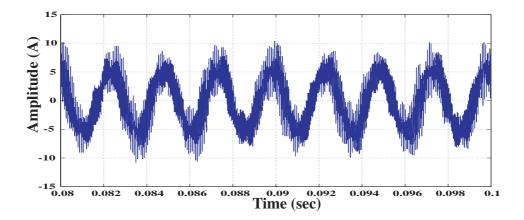

| 5.9  | MC Current in phase a with a pure resistive, balanced load and tracking controller                                                                                                                                                                 | 141 |

| 5.10 | Current in the load phase a with a pure resistive, balanced load and tracking controller                                                                                                                                                           | 141 |

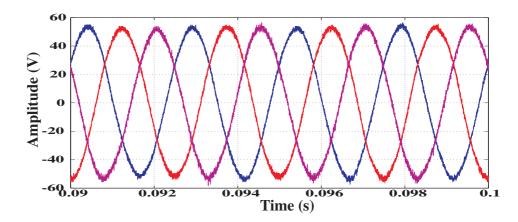

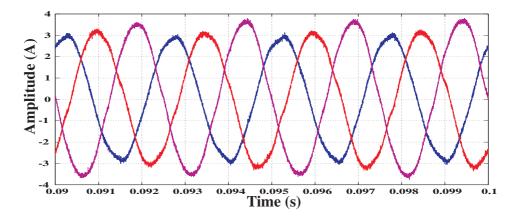

| 5.11 | Output voltages with a pure resistive, unbalanced load and tracking controller                                                                                                                                                                     | 143 |

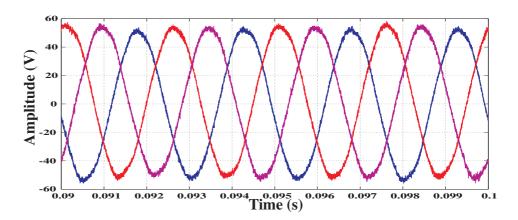

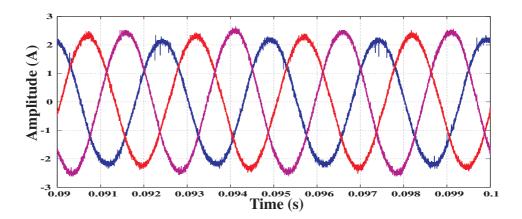

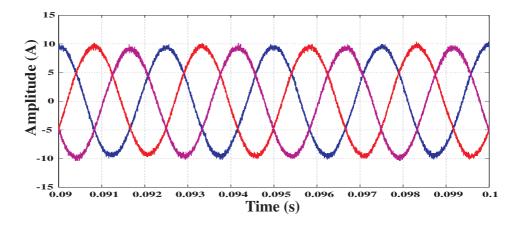

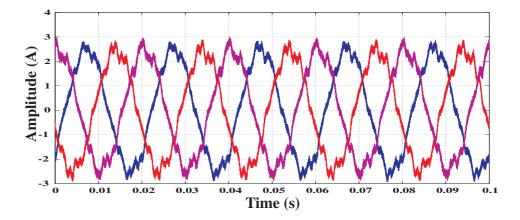

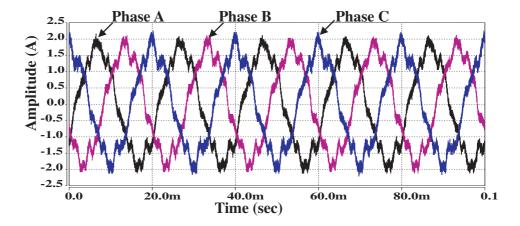

| 5.12 | Input currents with a pure resistive, unbalanced load and tracking controller                                                                                                                                                                      | 143 |

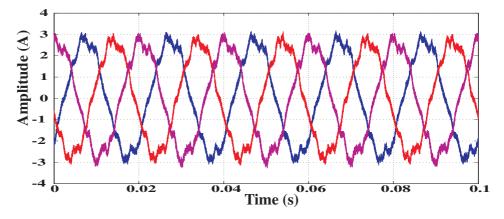

| 5.13 | Currents in the load with a pure resistive, unbalanced load and tracking controller                                                                                                                                                                | 144 |

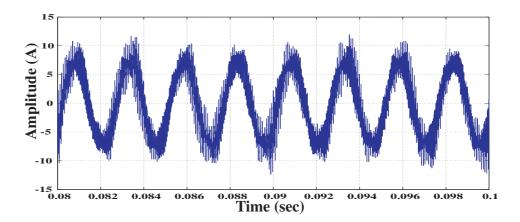

| 5.14 | Matrix Converter output current in phase a with a pure resistive, unbalanced load and tracking controller                                                                                                                                          | 144 |

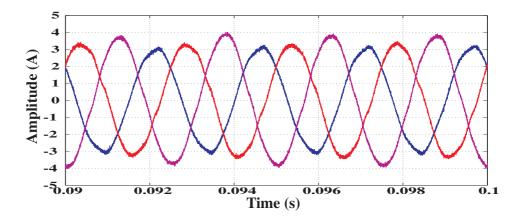

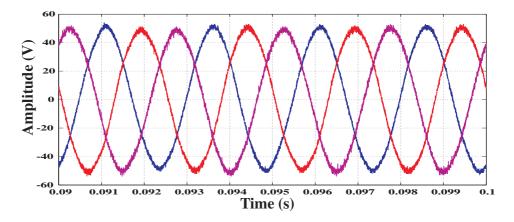

| 5.15 | Output voltage in phase a with a balanced RL load and tracking controller                                                                                                                                                                          | 146 |

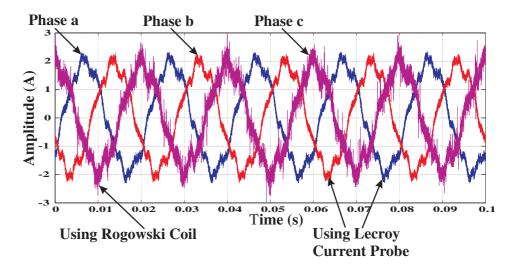

| 5.16 | Input currents with a balanced RL load and tracking controller. Note: the load current waveform in phase c looks more distorted than the other waveforms but this is due the use of a current probe with a different bandwidth range of operation. | 147 |

|      | different bandwidth range of operation                                                                                                                                                                                                             | 14/ |

| 5.17 | Matrix Converter current in phase a with a balanced RL load and tracking controller                  | 147  |

|------|------------------------------------------------------------------------------------------------------|------|

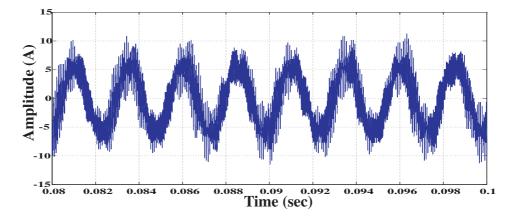

| 5.18 | Current in load phase a with a balanced RL load and tracking controller                              | .148 |

| 5.19 | Output voltages with an unbalanced RL load and tracking controller.                                  | 148  |

| 5.20 | Output voltage in phase a with an unbalanced RL load and tracking controller                         | 149  |

| 5.21 | Input currents with an unbalanced RL load and tracking controller                                    | 149  |

| 5.22 | Output current of the Matrix Converter in phase a with an unbalanced RL load and tracking controller | 150  |

| 5.23 | Currents in load with an unbalanced RL load and tracking controller.                                 | 150  |

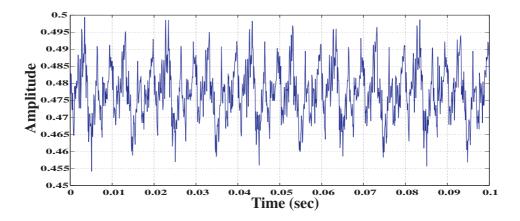

| 5.24 | Modulation index with load disconnected                                                              | 151  |

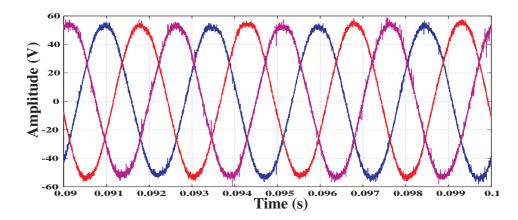

| 5.25 | Output voltages with load disconnected and using tracking controller.                                | 152  |

| 5.26 | Output voltage in phase a with load disconnected and using tracking controller                       | 152  |

| 5.27 | Input Current in phase a with load disconnected and using tracking controller                        | 153  |

| 5.28 | Current before output filter with load disconnected and using tracking controller                    | 153  |

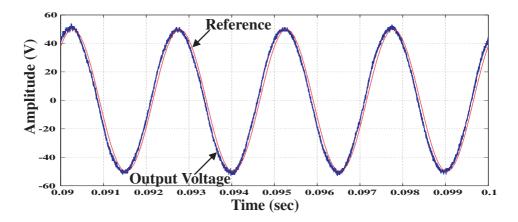

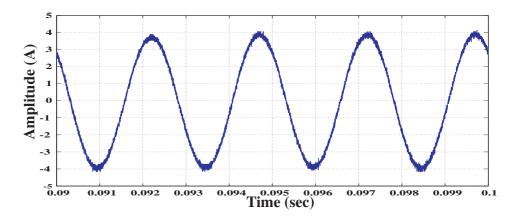

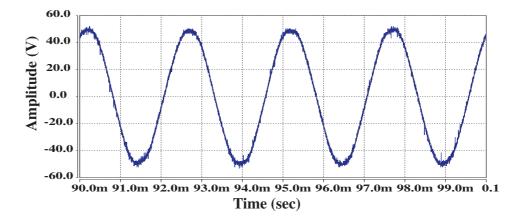

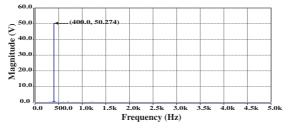

| 5.29 | Output voltage in phase a with a pure resistive, balanced load and Repetitive Controller             | 155  |

| 5.30 | Input currents with a pure resistive, balanced load and Repetitive Controller                        | 155  |

| 5.31 | Output current in phase a with a pure resistive, balanced load and Repetitive Controller             | 156  |

|------|------------------------------------------------------------------------------------------------------|------|

| 5.32 | Load currents with a pure resistive, balanced load and Repetitive Controller                         | 156  |

| 5.33 | Output voltages with a pure resistive, unbalanced load and Repetitive Controller                     | 157  |

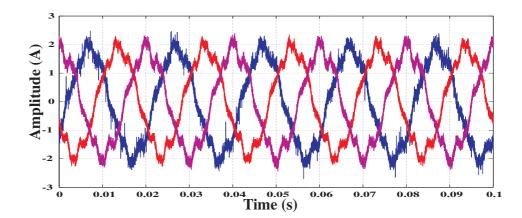

| 5.34 | Input currents whit a pure resistive, unbalanced load and Repetitive Controller                      | 158  |

| 5.35 | Matrix Converter current in phase a with a pure resistive, unbalanced load and Repetitive Controller | 158  |

| 5.36 | Load currents with a pure resistive, unbalanced load and Repetitive Controller                       | 159  |

| 5.37 | Output voltage in phase a with a balanced RL load and Repetitive Controller                          | 160  |

| 5.38 | Input current in phase A with a balanced RL load and Repetitive Controller                           | 160  |

| 5.39 | Matrix Converter output current in phase a with a balanced RL load and Repetitive Controller         | 161  |

| 5.40 | Load current in phase a with a balanced RL load and Repetitive Controller                            | 161  |

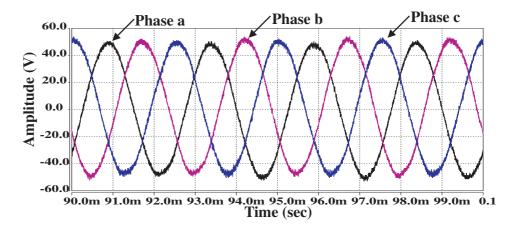

| 5.41 | Output voltages with an unbalanced RL load and Repetitive Controller                                 | .163 |

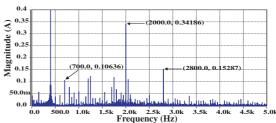

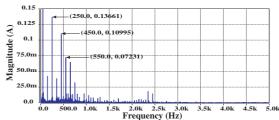

| 5.42 | Harmonic spectra of output voltage in phase a. THD = $2.1526\%$                                      | 163  |

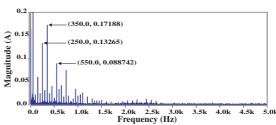

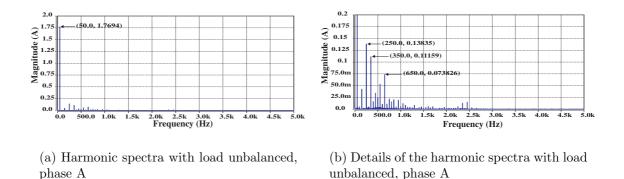

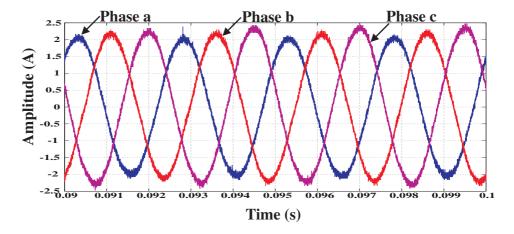

| 5.43 | Input currents with an unbalanced RL load and Repetitive Controller.                                 | 164  |

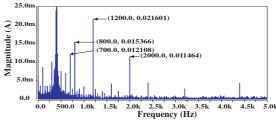

| 5.44 | Harmonic spectra of input current in phase A. THD = $6.15\%$                                      | 164 |

|------|---------------------------------------------------------------------------------------------------|-----|

| 5.45 | Matrix Converter output current in phase a with an unbalanced RL load and Repetitive Controller   | 165 |

| 5.46 | Harmonic spectra of Matrix Converter output current in phase a. THD = $0.61\%$                    | 165 |

| 5.47 | Load currents with an unbalanced RL load and Repetitive Controller.                               | 166 |

| 5.48 | Harmonic spectra of the load current in phase a. THD = $1.68\%$                                   | 166 |

| 5.49 | Output voltage in phase a with load disconnected and using Repetitive Controller                  | 168 |

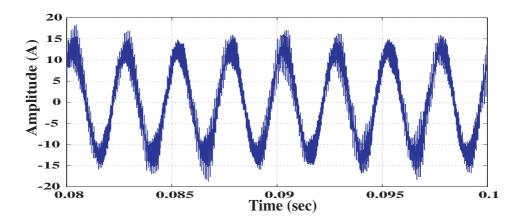

| 5.50 | Harmonic spectra of output voltage in phase a. THD = $1.93\%$                                     | 168 |

| 5.51 | Input current in phase a with load disconnected and using Repetitive Controller                   | 169 |

| 5.52 | Harmonic spectra of input current in phase A. THD = $5.56\%$                                      | 169 |

| 5.53 | Matrix Converter output current in phase a with load disconnected and using Repetitive Controller | 170 |

| 5.54 | Harmonic spectra of MC output current in phase a. THD = $0.83\%$ .                                | 170 |

| B.1  | Overall diagram of the whole Matrix Converter system used Saber. $\ .$                            | 192 |

| B.2  | Schematic diagram of the MC and modulator used in the power supply system                         | 194 |

| В.3  | Schematic diagram of the controller used in the power supply system.                              | 195 |

# List of Tables

| 2.1 | Switching States for a three-phase to three-phase Matrix Converter [1].                                                       | 29  |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Selection of switching configurations for each combination of $K_V$ and $K_I$ [1]                                             | 32  |

| 2.3 | Selection of switching configurations for each combination of $K_V$ and $K_I$ (continuation) [1]                              | 32  |

| 4.1 | Hardware and software trip usage                                                                                              | 122 |

| 5.1 | THD of practical results in phase $a$ with the tracking controller and the tracking controller plus the Repetitive Controller | 172 |

### Chapter 1

### Introduction

#### 1.1 The Matrix Converter

This thesis is concerned with the design and implementation of a Matrix Converter for Frequency Changing Power Supply Applications. Typically such units are used to convert between 50/60Hz supplies available in airports to a 400Hz one for aircraft supply when they are parked in their bays. This work will consider the design, simulation, practical construction and testing of a 7.5kVA system prototype. A Matrix Converter is a device used for converting directly AC energy into AC energy; the main feature of this device is to convert the magnitude as well as the frequency of the input into a desired magnitude and frequency of the output with an "all-silicon" solution. Mainly, a Matrix Converter consists of nine bi-directional switches, which are required to be commutated in the right way and sequence in order to minimize losses and produce the desired output with a high quality input and output waveforms.

After the controlled rectifiers were developed in the early 1930's, it was realized that this provided the possibility of generating alternating currents of variable frequency directly from a fixed frequency AC supply, the positive rectifier supplying the positive half cycles of current and the negative rectifier the negative half cycles. This

system was called cycloconverter at its early stage and this proved to be so appropriate that nowadays it is still used in some high power applications because of high power requirements and the Matrix Converter technology is still not available widely. Moreover, most of the industrial applications require frequencies in the range of 50Hz-60Hz, which is easily obtained by the cycloconverter. For a three-phase to three-phase cycloconverter, 36 thyristors are required. This makes that cycloconverter systems are large and complicated and tend to be used in applications where high power is required (1MW and up) [2]. Today, high power, multi-megawatts, thyristor based cycloconverters are very popular for driving induction and wound field synchronous motors. Some general applications of cycloconverters are [3]:

- Cement and ball mill drives

- Rolling mill drives

- Slip-power recovery Scherbius drives [4] [5]

- Variable-speed, constant-frequency (VSCF) power generation for aircraft 400Hz power supplies

Frequency conversion or modulation techniques can be used to take a fixed frequency or DC source and provide any load with a different or variable frequency supply. Cycloconversion is mostly concerned with converting directly a low-frequency waveform into a desired different frequency waveform. A cycloconverter is an arrangement of two converter connected back to back as shown in Figure 1.1 [6].

Matrix Converters were first mentioned in the early 1980's by Alesina and Venturini [7]. They proposed a general model and a relative mathematical theory for high-frequency synthesis converters. They stated that the maximum input-output transformation ratio possible for the new AC-AC converter is  $\sqrt{3}/2$  and also, they suggested a specific modulation and a feed-back-based control implementation of the proposed converter [8]. The AC-AC Matrix Converter is optimal in terms of minimum switch number and minimum filtering requirements. A three-phase AC-AC Matrix

Figure 1.1: Single-phase load fed from a three-pulse cycloconverter.

Converter consists basically of nine bidirectional voltage-blocking current-conducting switches. These switches are arranged in a matrix and by using this arrangement any input phase can be connected to any output phase at any time. Figure 1.2 shows such arrangement [9].

Figure 1.2: Structure of Matrix Converter.

1.2. CONTROL

#### 1.2 Control

There has been a gap between modern control theory and practice. However, a practicing engineer who knows a control system well, modifies, extends, and combines modern control theory with classical control theory. Successful results using developed control theory, especially to servo-motor and motion control, have been widely reported in the literature [10] [11] [12]. The theory may be given in s domain (continuous). However, using bilinear transformation or direct design the theory can be replaced by a discrete (digital) control method (which is needed when implementing the control with a DSP). Digital controllers can be considered sometimes as digital filters, they introduce delays. These delays depend on the order of the polynomial implemented as the controller. The control is defined as to manipulate an object (in this case the Matrix Converter) so as to serve a certain purpose (that is to make it work as required) [13].

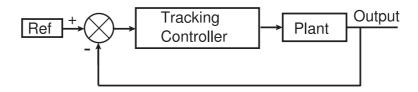

The term controller in a feedback control system is often associated with the elements of the forward path, between the error signal and the control variable. But it also sometimes includes the summing point, the feedback elements, or both, and some times the term controller or compensator is used synonymously [14]. Figure 1.3 shows a general structure of a plant with a second order controller.

Figure 1.3: Structure of plant with second order controller.

#### 1.3 Modulation

Applications areas of power converters still expand thanks to improvements in semiconductor technology, which offer higher voltage and current ratings as well as better switching characteristics. The main advantages of modern power electronic converters, such as high efficiency, low weight, small dimensions, fast operation, and high power densities, are being achieved though the use of the so-called switch mode operation, in which power semiconductor devices are controlled in ON/OFF fashion (no operation in the active region) [15]. This leads to different types of pulse width modulation (PWM), which is a basic energy processing technique applied in power converter systems. In modern converters, PWM is a high-speed process ranging from a few kiloHertz (motor control) [16] up to several megaHertz (resonant converters for power supply) depending on the rated power [17].

Figure 1.4 shows a Voltage Source Converter (VSC) which is used to provide ac variable voltage - variable frequency to a load from a fixed voltage - fixed frequency supply. This has been the traditional power converter employed for variable speed drive applications [3]. According to Figure 1.4, the input supply is first rectified then it is applied to the load by the inverter stage. The control of the output of this two stage converter is achieved by modulating the duty cycles of the devices in the inverter stage so as to produce near sinusoidal output currents in the inductive load machine, at a desired amplitude and frequency [18].

Figure 1.4 shows a large capacitor placed across the DC link to provide a constant DC voltage source with small variation and energy storage. This capacitor is considered large compared to the size of the rectifier and inverter semiconductor components. This means that a large capacitance is needed but within a reasonable volume, therefore electrolytic capacitors are normally used for the DC link components. Electrolytic capacitors typically occupy 30-50% of the total volume of the converter for power levels greater than a few kW and in addition to this they are temperature sensitive.

Due to the diode bridge front end, the inverter circuit shown in Figure 1.4 will draw

Figure 1.4: Basic diagram of the Voltage Source Converter, power components.

input currents that are rich in 5th and 7th harmonics, which can become a significant problem at increased power levels because the harmonic distortion injected to the mains and the power losses. This problem can be solved by employing an active PWM rectifier front end as shown in Figure 1.5, which can be modulated to draw near sinusoidal input currents. The active, or sinusoidal front end inverter, has the added advantage that the power flow can be bi-directional. However the DC link capacitors are still large (around 30-50% of the total volume) and so are the input inductors [19] [20].

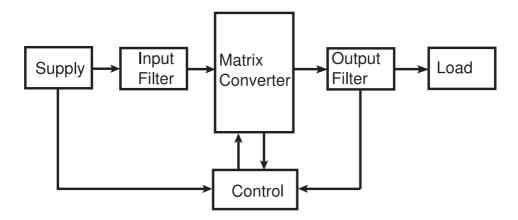

An alternative AC-AC power converter, the Matrix Converter, is discussed and used in this thesis. The Matrix Converter, shown in Figure 1.6, consists of an array of bi-directional switches where any input phase can be connected to any output phase. The duty cycle of the switches can be modulated to produce the desired output amplitude and frequency. The Matrix Converter is also described as a direct AC-AC converter because it requires no intermediate energy storage [21] [22].

Figure 1.5: Schematic of the back to back converter.

Figure 1.6: Simplified representation of a Matrix Converter system.

Much of the work on Matrix Converters over the past twenty years has been concentrated on modulation algorithms and, more recently, on the practical implementation issues such as the devices commutation, have largely been solved. One of the key benefits of the Matrix Converter technology is the possibility of greater power density due to the absence of a DC link. This is translated into a realistic advantage if the filter size is also optimized, by having a sufficiently high switching frequency of semiconductor devices. This means, though, a compromise between filter size and semiconductor losses must be found.

Factors such as the absence of electrolytic capacitors, the advantage for increasing power density, reducing size, reducing weight and obtaining good input power quality are fundamental to power supply applications [23] [24] [25].

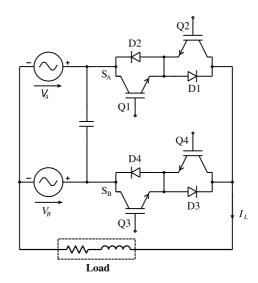

The purpose of this work is to investigate the design and implementation of a 7.5kVA Matrix Converter for frequency changing power supply applications. SABER and Matlab/Simulink simulations of the whole system (which includes the Matrix Converter, input and output filters) are provided. The design and implementation of the Matrix Converter is described, with particular attention to the strict requirements of the given power supply application. Finally, the Matrix Converter system using different types of load is assembled and tested.

#### 1.4 Research Outcomes

The system will have the following technical specifications:

- Rated input voltage: 415V (rms, line voltage). Three-phase, three-wire

- Input frequency: 50Hz.

- Input harmonics: relevant IEEE standards, IEEE 519 [26].

- Rated output voltage: 117V (rms, phase voltage). Three-phase, three-wires.

- Voltage tolerance: 114V to 120V

- Output frequency: 400Hz.

- Voltage total harmonic distortion: to be less than 4%.

- Voltage individual harmonic distortion: to be less than 2%.

- Voltage transients: not to exceed 10% of nominal voltage when switching the load between 0% and 100% and back.

- Rated output power: the Matrix Converter system is designed for a total power of 7.5kVA.

- Load conditions: unbalanced condition of 40%. Resistive-inductive load.

#### 1.5 Project Objectives

The research work presented in this thesis has generated the following novel achievements:

• A comparative study has been performed to ascertain the suitability of different Matrix Converter systems for power supply applications. A Matrix Converter control system was devised for each of the different load conditions. These include resistive load balanced, resistive load unbalanced, resistive-inductive load balanced, resistive-inductive load unbalanced and load disconnected. An improved control structure for the Matrix Converter system was introduced in simulation to control the output voltage. This structure which includes a Repetitive Control was simulated and the physical effects on the Matrix Converter system such as instability and harmonic distortion were investigated and results presented. Each of the control systems were then compared on the basis of the results of their analysis and their potential merits for power supply application in terms of power quality, harmonic content and power density determined.

- A 7.5kVA Matrix Converter has been designed and built to meet the requirements of power supplies driving different types of load. Issues which have previously prevented successful implementation such as device packaging, converter layout and protection have been addressed and solutions have been presented.

- The use of the overvoltage clamp circuit to improve the reliability of the Matrix Converter circuit by giving it the ability to withstand a circuit failure, such as current direction feedback failure has been investigated. No electrolytic capacitors were employed in the protection circuit or the input filter. In response to important issues such reliability requirements, polypropylene film capacitors were utilized to minimize the power converter volume.

#### 1.6 Thesis Overview

The remainder of this thesis is divided into the following Chapters:

In Chapter 1, the Matrix Converter research concept for power supply applications is introduced and discussed. Particular attention is given to the different load conditions driven by the Matrix Converter system and how these conditions influence the output voltage waveform quality.

In Chapter 2, the Matrix Converter concept is discussed and the mathematical model from which the modulation problem can be derived is introduced. A brief description of the Venturini and Space Vector Modulation methods are given. The practical implementation issues are introduced and the proposed solutions are discussed. A comparison between the conventional topology of power converters for AC-AC conversion and the Matrix Converter is provided in terms of a predicted reliability study.

SABER as well as Simulink simulation analysis of the Matrix Converter system, driving different types of load, is described in Chapter 3. The main differences between the control systems used are highlighted and the reason for the choice of the proposed

control structure for the given application, is discussed.

The design and construction of the 7.5kVA Matrix Converter is described in Chapter 4. The output voltage control of the power converter is also described and the used of the Repetitive Controller is proposed.

In Chapter 5, a full description is given of the different assembly and testing stages of the power converter first, the Matrix Converter system and, finally, the control strategy of the output voltage. The correspondent series of results is presented. The Chapter concludes with the description of the testing of the Matrix Converter based power supply.

In Chapter 6, conclusions are drawn from the work presented and the goals achieved. Also, areas of further research are highlighted.

### Chapter 2

# Modulation Techniques and Control

#### 2.1 Introduction

AC to AC power conversion can be realized by using a rectifier stage and an inverter stage or by using a Direct or Matrix Converter (MC). A Matrix Converter uses only one conversion stage compared to two stages for the rectifier/inverter solution. Each converter topology has particular advantages and disadvantages, the choice, therefore, depends on the requirements of the application.

The state of the art in Matrix Converter technology is presented in this chapter. The Matrix Converter concept is introduced with the mathematical model circuit operation and associated modulation techniques. Modulation techniques used in Matrix Converters have been considered by researches for many years [27]. These papers have proposed different modulation techniques. The modulation techniques section of this chapter presents the main modulation techniques used in Matrix Converters. The two Venturini modulation methods [28][8] and the scalar modulation scheme [29][30] are reviewed. A detailed analysis of Space Vector Modulation (SVM) algorithms for

Matrix Converters is then presented. The conventional SVM algorithm [1] usually generates both even and odd order harmonic voltages. The basic diagrams and the permitted switching states of the converter are included. Finally, this section presents the indirect modulation method [31][32].

The next two sections present the implementation of the required bi-directional switches and the techniques used for safe current commutation between these switches.

Issues regarding the design of both the output and input filters are included in the filters design section. Frequency response plots are also included in order to show the cut-off and resonant frequencies for both filters.

In order to control the output voltage of the converter a voltage control loop is used. The control section of this chapter focuses on the design of the second order controller required for this voltage control loop in both the s and z domain. The design of output filter described in the previous section is used to design the controller. In order to improve the output voltage waveform quality a Repetitive Controller (RC) is proposed. The design of this controller is included in the Repetitive Controller section. A structure of the proposed Repetitive Controller is given, as well as the values of parameters used in the implementation.

#### 2.2 Matrix Converter Concept

The power converter topologies used in industry can be grouped as follows:

- Inverters: used to change DC voltage or current to AC voltage or current.

Inverters are widely used in variable-speed drives and AC power supplies.

- Rectifiers: used to change AC voltage or current (usually from a grid supply of 50 or 60Hz) to DC voltage or current.

Rectifiers and inverters are often combined to form indirect AC to AC Converters, as shown in Figure 2.1.

Figure 2.1: Schematic of AC to AC converter.

Figure 2.2 shows a simplified block diagram of a 3-phase to 3-phase Matrix Converter drive system. As it can be seen in the figure, the Matrix Converter circuit consists of an array of nine bi-directional switches, constructed from unidirectional power devices, arranged in such a way as to enable any input line to be connected to any output line at any time. The switch duty cycles are modulated to generate the desired output waveform on the basis of the input supply voltages and the demanded output voltages. The demanded voltages are generally the output of a cascaded speed and current control loop. A Matrix Converter can be viewed as an "all-silicon solution" to the general AC-AC power conversion problem. Compared to the conventional rectifier/inverter topology, Matrix Converters have many advantages. No DC-link energy storage is required for the Matrix Converter topology. This removes the necessity for bulky electrolytic capacitors, which are intolerant to high temperatures and have a relatively short life time [33] [34] [35] [36]. As a result of the elimination of the DC-link a potentially compact converter system can be designed. Bi-directional power flow is straightforward with a Matrix Converter. By controlling the switching devices

appropriately both the output voltage and the input current are sinusoidal with harmonics only around or above the switching frequency of semiconductor devices. The displacement factor (df) is used to quantify the fact that not all of the fundamental current gives rise to power when there is a phase shift between voltage and current. Unity displacement factor can be achieved if an appropriate modulation strategy is used, and can be achieved irrespective of the load. The type of load for this case is resistive-inductive and the capacitive load has not been considered.

Figure 2.2: Simplified representation of a Matrix Converter system.

To understand the modulation problem and its solution, consider the arrangement shown in Figure 2.2. The fundamental requirement can be stated as follow; a balanced set of three-phase input voltages is expressed as,

$$[\mathbf{V_i(t)}] = \begin{pmatrix} V_{i1}(t) \\ V_{i2}(t) \\ V_{i3}(t) \end{pmatrix}$$

(2.1)

Where:

$$[\mathbf{V_i}(\mathbf{t})] = \begin{pmatrix} V_i cos(\omega_i t) \\ V_i cos(\omega_i t - 2\pi/3) \\ V_i cos(\omega_i t + 2\pi/3) \end{pmatrix}$$

(2.2)

With these input voltages the switching function M(t) that will produce a set of desired three-phase output voltages can be determined,

$$[\mathbf{V_o(t)}] = \begin{pmatrix} V_{o1}(t) \\ V_{o2}(t) \\ V_{o3}(t) \end{pmatrix}$$

(2.3)

Where:

$$[\mathbf{V_o(t)}] = [M(t)]. \begin{pmatrix} V_{i1}(t) \\ V_{i2}(t) \\ V_{i3}(t) \end{pmatrix}$$

(2.4)

$$[\mathbf{V_o}(\mathbf{t})] = \begin{pmatrix} V_o cos(\omega_o t + \theta_o) \\ V_o cos(\omega_o t + \theta_o - 2\pi/3) \\ V_o cos(\omega_o t + \theta_o + 2\pi/3) \end{pmatrix}$$

(2.5)

where  $\theta_o$  is an arbitrary output voltage phase angle [9]. The switching function, M(t), must satisfy the previous stated conditions. Several modulation strategies have been proposed [37] [38] [39]. These modulation strategies give different voltage conversion ratios and the number of commutations employed in each modulation strategies is different.

With the price of power semiconductors falling, Matrix Converters could become a more attractive alternative to the back-to-back converter in applications where sinusoidal input currents and true bi-directional power flow are required. The voltage transfer ration (q) is the relationship of the output voltage to the input voltage. The voltage transfer ratio limitation, which will be shown in Section 2.3.2, is a real problem if a standard machine and a standard supply are to be used. The voltage ratio limitation is not the main issue in the design of the Matrix Converter system when the application allows the specification of the output voltage. More important innovative and efficient strategies of implementing circuit protection [40] for the Matrix

Converter will ease the way for the commercialization of this converter in applications such as integrated motor drives, aerospace and marine propulsion applications where power density, space and weight play a fundamental role. This view is reinforced by the possibility that the Matrix Converter could be the ideal converter topology to employ future technologies such as high temperature silicon carbide devices because they can work a environments with a large range of temperatures. Adding to this, the absence of large electrolytic capacitors helps to overcome the problem of electronic equipment operating in difficult environmental conditions [41]. The electrolytic capacitors are limited in the range of temperature in what they can operate.

# 2.3 Modulation Techniques

In 1964 Schönung and Stemmler [42] proposed the triangular carried-based sinusoidal pulse width modulation (PWM) strategy for three-phase inverter modulation. The space vector modulation (SVM) strategy was proposed by Pfaff, Weschta and Wick [43] in 1982. They based the proposed SVM method on the development of new technology microprocessors. The SVM algorithm was improved by van der Broeck, Skudelny and Stanke [44]. This method become a basic modulation technique for three-phase PWM inverters. Pulse width modulated three-phase inverters can operate under voltage (open loop) or current (closed loop) control. Current-controlled systems have better performance and faster response than the voltage-controlled systems because the control of the current is done in the inner loop of the control system [15]. AC industrial drives normally employ cascade control structure. It consists of multiple loops: the inner most loop is the current loop (which is the fastest), followed by speed loop and position loop. Implementing cascade control structure requires the current to be controlled. Good current controlled schemes should produce low current ripple, good tracking capability with zero steady state error, and fast dynamic response. The faster the response of the loop, the faster the disturbance is taken into consideration. The inner current loop is a servo motor drive plays a more important role than just limiting the current incase of overload. This loop operates continuously to regulate the motor-developed torque so as to meet the load demand, and for meeting the speed trajectory specified by the motion controller. Motor drives of high dynamic response currently employ PWM current source [45]. Current-controlled systems connected to AC motors are used to reduce the dependence on stator parameters and also to allow fast action on the flux and torque developed by the controlled motor. Current is regulated to achieve the desired active and reactive power. It is also controlled to minimize or compensate the line power factor and current harmonics. A control structure comprising of an internal current feedback loop is a vital part of most applications of three-phase voltage-source power converters. Due to this fact, the quality of the applied current control strategy has an important role in the performance of the power converter system.

In principle, all modulation schemes aim to create trains of switched voltage or current pulses which have the same fundamental volt-second or amp-second average (i.e, the integral of the waveform over time) as a target reference waveform. The major difficulty with these trains of switched pulses is that they also contain unwanted harmonic components which should, ideally, be minimized since they are injected to the mains and degrade the quality of energy. This degradation of energy cause malfunction of other equipments.

The Matrix Converter control strategies were first mentioned by Alesina [7] and Venturini [28]. The block diagram of the Matrix Converter is represented in Figure 2.2. Various modulation techniques can be applied to the AC-AC matrix Converter to achieve sinusoidal output voltages and input currents. An optimal modulation strategy should minimize the input current and the output voltage harmonic distortion and device power loss [46]. The first modulator proposed for Matrix Converters, known as the Venturini modulation, employed a scalar model [7]. This model gives a maximum voltage transfer ratio of 0.5. An injection of a third harmonic of the input and output voltage was proposed in order to fit the reference output voltage in the input system envelope. This technique is used to achieve a voltage transfer ratio with a maximum value of 0.866.

In this analysis, a three-phase input, three-phase output converter is considered. Because the Matrix Converter is symmetrical, the designation of input and output ports is arbitrary. However, for any sensible mode of operation, one port should be considered to have a voltage stiff characteristic and the other port a current stiff characteristic. In this case stiff means that the voltage or current must be constant with no interruptions or sudden variations. For the following analysis it is assumed that the input port is voltage stiff and the output port is current stiff. In a practical Matrix Converter an input filter is included to circulate the high frequency switching harmonics and provide the voltage stiff characteristic. The output inductance is usually part of the load giving a current stiff characteristic. This study considers that upper case suffixes always denote the input phases and lower case suffixes denote the output phases as shown in Figure 2.2.

The concept of switching functions [47] is used to derive a mathematical model of the Matrix Converter. Ideal switching is assumed in this analysis. The switching function,  $S_{Kj}$ , is defined as the representation of the switch connecting input line Kto output line j. When the switch is ON, the switching function has a value of 1 and when the switch is OFF, the switching function has a value of 0. The instantaneous current and voltage relationships can then be written as given in Equations 2.6.

$$\begin{bmatrix} v_{a}(t) \\ v_{b}(t) \\ v_{c}(t) \end{bmatrix} = \begin{bmatrix} S_{Aa}(t) & S_{Ba}(t) & S_{Ca}(t) \\ S_{Ab}(t) & S_{Bb}(t) & S_{Cb}(t) \\ S_{Ac}(t) & S_{Bc}(t) & S_{Cc}(t) \end{bmatrix} \begin{bmatrix} v_{A}(t) \\ v_{B}(t) \\ v_{C}(t) \end{bmatrix}$$

$$\begin{bmatrix} i_{A}(t) \\ i_{B}(t) \\ i_{C}(t) \end{bmatrix} = \begin{bmatrix} S_{Aa}(t) & S_{Ab}(t) & S_{Ac}(t) \\ S_{Ba}(t) & S_{Ba}(t) & S_{Bc}(t) \\ S_{Ca}(t) & S_{Cb}(t) & S_{Cc}(t) \end{bmatrix} \begin{bmatrix} i_{a}(t) \\ i_{b}(t) \\ i_{c}(t) \end{bmatrix}$$

$$(2.6)$$

One of the most important rules that Matrix Converters must obey is the one expressed by Equation 2.7. This equation states that at any instant one and only one switch on each output phase must be closed. Analyzing the arrangement shown in Figure 2.2, which shows that there are no freewheeling diodes, this restriction means that the short circuit in the capacitive input as well as the open circuit in the inductive

output must be avoided.

$$\sum_{K=A,B,C} S_{Ka}(t) = \sum_{K=A,B,C} S_{Kb}(t) = \sum_{K=A,B,C} S_{Kc}(t) = 1$$

(2.7)

For the following analysis, it is assumed that Equation 2.7 is obeyed and, because ideal switches are used, the commutation between switches is instantaneous.

A typical switching pattern for Matrix Converter is shown in Figure 2.3. If conventional PWM is employed the switching sequence  $T_{seq}$  has a fixed period.

Figure 2.3: General form of switching pattern.

A modulation duty cycle should be defined for each switch in order to determine the average behavior of the Matrix Converter output voltage waveform. The modulation duty cycle is defined by,

$$m_{Aa}(t) = \frac{t_{Aa}}{T_{seq}} \tag{2.8}$$

where  $t_{Aa}$  represents the time when switch Aa is ON and  $T_{seq}$  represents the time of the complete sequence in the PWM pattern.

The modulation strategies are defined by using these continuous time functions. Equation 2.9 shows the use of these functions for the three-phase Matrix Converter.

$$\begin{bmatrix} v_{a}(t) \\ v_{b}(t) \\ v_{c}(t) \end{bmatrix} = \begin{bmatrix} m_{Aa}(t) & m_{Ba}(t) & m_{Ca}(t) \\ m_{Ab}(t) & m_{Bb}(t) & m_{Cb}(t) \\ m_{Ac}(t) & m_{Bc}(t) & m_{Cc}(t) \end{bmatrix} \begin{bmatrix} v_{A}(t) \\ v_{B}(t) \\ v_{C}(t) \end{bmatrix}$$

$$\begin{bmatrix} i_{a}(t) \\ i_{b}(t) \\ i_{c}(t) \end{bmatrix} = \begin{bmatrix} m_{Aa}(t) & m_{Ab}(t) & m_{Ac}(t) \\ m_{Ba}(t) & m_{Ba}(t) & m_{Bc}(t) \\ m_{Ca}(t) & m_{Cb}(t) & m_{Cc}(t) \end{bmatrix} \begin{bmatrix} i_{A}(t) \\ i_{B}(t) \\ i_{C}(t) \end{bmatrix}$$

$$(2.9)$$

Voltages  $v_a$ ,  $v_b$  &  $v_c$  and currents  $i_a$ ,  $i_b$  &  $i_c$  in Equation 2.9 are now values averaged over the sequence time. In Equation 2.10, which is a representation in a more compact notation of Equation 2.9, the matrix M(t) is known as the **modulation matrix**.

$$[v_o(t)] = [M(t)][v_i(t)]$$

$$[i_i(t)] = [M(t)]^T[i_o(t)]$$

(2.10)

Using this nomenclature, the constraint equation for Matrix Converters can now be written as,

$$\sum_{K=A,B,C} m_{Ka}(t) = \sum_{K=A,B,C} m_{Kb}(t) = \sum_{K=A,B,C} m_{Kc}(t) = 1$$

(2.11)

### 2.3.1 Basic Solution for the Modulation Problem

As stated in Section 2.2, the modulation problem assumes that a set of sinusoidal output voltages,  $v_o(t)$ , and input currents,  $i_i(t)$ , are required. These sets can be represented as,

$$[v_i(t)] = V_{im} \begin{bmatrix} \cos(\omega_i t) \\ \cos(\omega_i t + \frac{2\pi}{3}) \\ \cos(\omega_i t + \frac{4\pi}{3}) \end{bmatrix}$$

(2.12)

$$[i_o(t)] = I_{om} \begin{bmatrix} \cos(\omega_o t + \phi_o) \\ \cos(\omega_o t + \phi_o + \frac{2\pi}{3}) \\ \cos(\omega_o t + \phi_o + \frac{4\pi}{3}) \end{bmatrix}$$

(2.13)

The aim is to find a modulation matrix, M(t), such that Equations 2.14 and 2.15 are satisfied, as well as the constraint Equation 2.11.

$$[v_o(t)] = qV_{im} \begin{bmatrix} \cos(\omega_o t) \\ \cos(\omega_o t + \frac{2\pi}{3}) \\ \cos(\omega_o t + \frac{4\pi}{3}) \end{bmatrix}$$

(2.14)

$$[i_i(t)] = q \frac{\cos \phi_o}{\cos \phi_i} I_{om} \begin{bmatrix} \cos(\omega_i t + \phi_i) \\ \cos(\omega_i t + \phi_i + \frac{2\pi}{3}) \\ \cos(\omega_i t + \phi_i + \frac{4\pi}{3}) \end{bmatrix}$$

(2.15)

In Equations 2.14 and 2.15 q is the voltage transfer ratio,  $\omega_i$  and  $\omega_o$  are the input and output frequencies and  $\phi_i$  and  $\phi_o$  are the input and output phase displacement angles respectively. The problem was treated by Venturini, who found two solutions [28]. The solutions are expressed in Equations 2.16 and 2.17.

$$[M1(t)] = \frac{1}{3} \begin{bmatrix} 1 + 2q\cos(\omega_m t) & 1 + 2q\cos(\omega_m t - \frac{2\pi}{3}) & 1 + 2q\cos(\omega_m t - \frac{4\pi}{3}) \\ 1 + 2q\cos(\omega_m t - \frac{4\pi}{3}) & 1 + 2q\cos(\omega_m t) & 1 + 2q\cos(\omega_m t - \frac{2\pi}{3}) \\ 1 + 2q\cos(\omega_m t - \frac{2\pi}{3}) & 1 + 2q\cos(\omega_m t - \frac{4\pi}{3}) & 1 + 2q\cos(\omega_m t) \end{bmatrix}$$

$$(2.16)$$

with  $\omega_m = (\omega_o - \omega_i)$

$$[M2(t)] = \frac{1}{3} \begin{bmatrix} 1 + 2q\cos(\omega_m t) & 1 + 2q\cos(\omega_m t - \frac{2\pi}{3}) & 1 + 2q\cos(\omega_m t - \frac{4\pi}{3}) \\ 1 + 2q\cos(\omega_m t - \frac{2\pi}{3}) & 1 + 2q\cos(\omega_m t - \frac{4\pi}{3}) & 1 + 2q\cos(\omega_m t) \\ 1 + 2q\cos(\omega_m t - \frac{4\pi}{3}) & 1 + 2q\cos(\omega_m t) & 1 + 2q\cos(\omega_m t - \frac{2\pi}{3}) \end{bmatrix}$$

$$(2.17)$$

with  $\omega_m = (\omega_o + \omega_i)$ .

Considering the solution in Equation 2.16, the phase displacement at the input is the same as in the output because  $\phi_i = \phi_o$  whereas the solution in Equation 2.17 yields  $\phi_i = -\phi_o$  giving reversed phase displacement at the input. If both solutions are combined, the result provides the means for input displacement factor control,

$$[M(t)] = \alpha_1[M1(t)] + \alpha_2[M2(t)]$$

where  $\alpha_1 + \alpha_2 = 1$  (2.18)

Regardless of the load displacement factor, if  $\alpha_1$  is set to be equal to  $\alpha_2$  ( $\alpha_1 = \alpha_2$ ), the input displacement factor at the converter terminals is unity. Other possibilities exist, through the choice of  $\alpha_1$  and  $\alpha_2$ , to have any combination of leading or lagging displacement factor at the input with a lagging or leading power factor load at the output.

If  $\alpha_1 = \alpha_2$  is used, the modulation functions can be expressed in a compact equation:

$$m_{Kj} = \frac{t_{Kj}}{T_{seq}} = \frac{1}{3} \left( 1 + \frac{2v_K V_j}{V_{im}^2} \right) \quad \text{for } K = A, B, C \text{ and } j = a, b, c$$

(2.19)

Where  $V_{im}$  is the average input voltage.

Considering Equation 2.19, which represents the basic method, the average output voltages (taken over the switching sequence) are equal to the target output voltages  $[v_o(t)]$  during each switching sequence. This is only possible if the target output voltages must fit within the input voltage envelope for all operating conditions. Using this solution the maximum value of input to output voltage ratio, q, that the converter can achieve is 50%, as shown in Figure 2.4. The modulation algorithm represented by Equation 2.19 is suitable for real time implementation but in practice it is not used due to the 50% voltage transfer ratio limitation.

## 2.3.2 Venturini's Optimum Method

The method described in previous section can be improved. This improvement can be achieved by modifying the target output voltage matrix  $V_o(t)$  to include third harmonics of the input and output frequencies. This new strategy is known as Venturini's optimum method and employs the common-mode addition technique defined in [48]. The target output voltages in Equation 2.14 are modified in order to include the third harmonics. The maximum theoretical output to input voltage ratio, q, can be increased up to 86%, as shown in Equation 2.20. The complete use of the input voltage envelope is employed by the target output voltages as shown in Figure 2.5. The voltage transfer ratio may be defined as the output fundamental to

Figure 2.4: Theoretical waveforms illustrating the 50% voltage ratio limit.

Figure 2.5: Theoretical waveforms illustrating the third harmonic addition to obtain the 86% optimum voltage ratio limit. This is a rms value to rms value ratio.

the input fundamental ratio and its maximum value is 0.866.

$$[v_o(t)] = qV_{im} \begin{bmatrix} \cos(\omega_o t) - \frac{1}{6}\cos(3\omega_o t) + \frac{1}{2\sqrt{3}}\cos(3\omega_i t) \\ \cos(\omega_o t + \frac{2\pi}{3}) - \frac{1}{6}\cos(3\omega_o t) + \frac{1}{2\sqrt{3}}\cos(3\omega_i t) \\ \cos(\omega_o t + \frac{4\pi}{3}) - \frac{1}{6}\cos(3\omega_o t) + \frac{1}{2\sqrt{3}}\cos(3\omega_i t) \end{bmatrix}$$

(2.20)

Note that triple harmonics in the input frequency as well as in the output frequency are added. According to [8], when unity displacement factor is required the Equation 2.19 becomes,

$$m_{Kj} = \frac{1}{3} \left[ 1 + \frac{2v_k V_j}{V_{im}^2} + \frac{4q}{3\sqrt{3}} \sin(\omega_i t + \beta_K) \sin(3\omega_i t) \right]$$

(2.21)

for K=A,B,C and j=a,b,c

$$\beta_K = 0, \frac{2\pi}{3}, \frac{4\pi}{3}$$

for K=A,B,C respectively.

This implementation is readily handled by modern microprocessors up to switching frequencies of tens of kHz. Input displacement factor control can be introduced into the formulation in Equation 2.20 by inserting a phase shift between the actual input voltages and the input voltages,  $v_K$ . If the input displacement factor is different from unity, the output voltage limit will be reduced from  $0.86V_{im}(86\%)$  of the input voltage value) to a small value, which depends on the displacement factor achieved in the input. Therefore, the value of the output voltage must be lower than 86% of the input voltage.

### 2.3.3 Scalar Method

In 1987 G. Roy proposed a scalar control algorithm for [29]. The modulation duty cycle for this method is given by

$$m_{Lj} = \frac{(v_j - v_M)v_L}{1.5V_i m^2}$$

$$m_{Kj} = \frac{(v_j - v_M)v_K}{1.5V_i m^2}$$

$$m_{Mj} = 1 - (m_{Lj} + m_{Kj}) \quad \text{for } j = a, b, c \quad \text{respectively}$$

(2.22)

Here, the subscript M is assigned to the input voltage which has a different polarity to the other two inputs and the subscript L is assigned to to the smallest of the other two input voltage magnitudes. The third input voltage is assigned subscript K. As in the previous method, the common-mode addition is used in order to modify the target output voltages,  $v_j$ . This modification (by adding the third harmonics) is employed to achieve 86% voltage ratio capability. Although some differences can be observed, this method yields virtually identical switch timings to Venturini's optimum method. Using a similar expression to Equation 2.21, the modulation duty cycles for the scalar method can be represented by Equation 2.23.

$$m_{Kj} = \frac{t_{Kj}}{T_{seq}} = \frac{1}{3} \left[ 1 + \frac{2v_k V_j}{V_{im}^2} + \frac{2}{3} \sin(\omega_i t + \beta_K) \sin(3\omega_i t) \right]$$

(2.23)

for K=A,B,C and j=a,b,c

$$\beta_K = 0, \frac{2\pi}{3}, \frac{4\pi}{3}$$