# SHARED RESOURCE MANAGEMENT FOR NON-VOLATILE ASYMMETRIC MEMORY

by

# Miao Zhou

B.S., Huazhong University of Science and Technology, 2004M.S., Huazhong University of Science and Technology, 2007

Submitted to the Graduate Faculty of

the Dietrich School of Arts and Sciences in partial fulfillment

of the requirements for the degree of

# **Doctor of Philosophy**

University of Pittsburgh

2015

#### UNIVERSITY OF PITTSBURGH

#### DIETRICH SCHOOL OF ARTS AND SCIENCES

This dissertation was presented

by

Miao Zhou

It was defended on

April 30, 2015

and approved by

Rami Melhem, PhD, Computer Science Department

Bruce R. Childers, PhD, Computer Science Department

Daniel Mossé, PhD, Computer Science Department

Yiran Chen, PhD, Electrical and Computer Engineering Department

Dissertation Director: Rami Melhem, PhD, Computer Science Department

## SHARED RESOURCE MANAGEMENT FOR NON-VOLATILE ASYMMETRIC MEMORY

Miao Zhou, PhD

University of Pittsburgh, 2015

Non-volatile memory (NVM), such as Phase-Change Memory (PCM), is a promising energyefficient candidate to replace DRAM. It is desirable because of its non-volatility, good scalability and low idle power. NVM, nevertheless, faces important challenges. The main problems are: writes are much slower and more power hungry than reads and write bandwidth is much lower than read bandwidth. Hybrid main memory architecture, which consists of a large NVM and a small DRAM, may become a solution for architecting NVM as main memory. Adding an extra layer of cache mitigates the drawbacks of NVM writes. However, writebacks from the last-level cache (LLC) might still (a) overwhelm the limited NVM write bandwidth and stall the application, (b) shorten lifetime and (c) increase energy consumption.

Effectively utilizing shared resources, such as the last-level cache and the memory bandwidth, is crucial to achieving high performance for multi-core systems. No existing cache and bandwidth allocation scheme exploits the read/write asymmetry property, which is fundamental in NVM. This thesis tries to consider the asymmetry property in partitioning the cache and memory bandwidth for NVM systems.

The thesis proposes three writeback-aware schemes to manage the resources in NVM systems. First, a runtime mechanism, *Writeback-aware Cache Partitioning* (WCP), is proposed to partition the shared LLC among multiple applications. Unlike past partitioning schemes, WCP considers the reduction in cache misses as well as writebacks. Second, a new runtime mechanism, *Writebackaware Bandwidth Partitioning* (WBP), partitions NVM service cycles among applications. WBP uses a *bandwidth partitioning weight* to reflect the importance of writebacks (in addition to LLC misses) to bandwidth allocation. A companion *Dynamic Weight Adjustment* scheme dynamically selects the cache partitioning weight to maximize system performance. Third, *Unified Writeback-aware Partitioning* (UWP) partitions the last-level cache and the memory bandwidth cooperatively. UWP can further improve the system performance by considering the interaction of cache partitioning and bandwidth partitioning. The three proposed schemes improve system performance by considering the unique read/write asymmetry property of NVM.

### TABLE OF CONTENTS

| 1.0 | INTRODUCTION                                          | 1 |

|-----|-------------------------------------------------------|---|

|     | 1.1 Problem statement                                 | 3 |

|     | 1.2 Solution Overview                                 | 4 |

|     | 1.3 Contributions                                     | 4 |

| 2.0 | BACKGROUND AND RELATED WORK                           | 6 |

|     | 2.1 Phase Change Memory                               | 6 |

|     | 2.1.1 Phase Change Memory Background                  | 6 |

|     | 2.1.2 Architectural techniques for PCM                | 1 |

|     | 2.2 Management of Shared Caches                       | 6 |

|     | 2.2.1 Cache Replacement                               | 6 |

|     | 2.2.2 Cache Partitioning                              | 7 |

|     | 2.3 Bandwidth Partitioning                            | 8 |

|     | 2.4 Coordinated Cache and Bandwidth Partitioning      | 9 |

|     | 2.5 Non-volatile Main Memory Architectures            | 0 |

| 3.0 | CACHE PARTITIONING USING WRITEBACK INFORMATION        | 2 |

|     | 3.1 Motivation for Writeback-aware Cache Partitioning | 2 |

|     | 3.2 Writeback-aware Cache Partitioning                | 4 |

|     | 3.2.1 Monitoring of Writebacks                        | 4 |

|     | 3.2.2 Extended Utility Monitors (E-UMON)              | 6 |

|     | 3.2.3 Cache Partition Selection                       | 8 |

|     | 3.2.4 Weight Computation for Performance Optimization | 9 |

|     | 3.3 Write Buffer Balancing Replacement                |   |

|     | 3.4 | Experimental Methodology and Metrics                            | 33 |

|-----|-----|-----------------------------------------------------------------|----|

|     | 3.5 | Evaluation Results and Analysis                                 | 35 |

|     |     | 3.5.1 Dynamic Weight Adjustment for WCP                         | 35 |

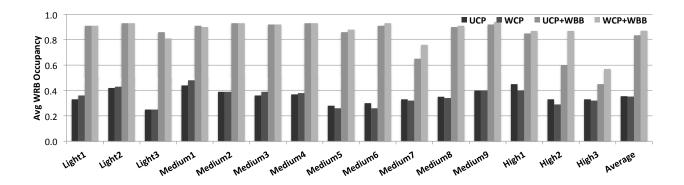

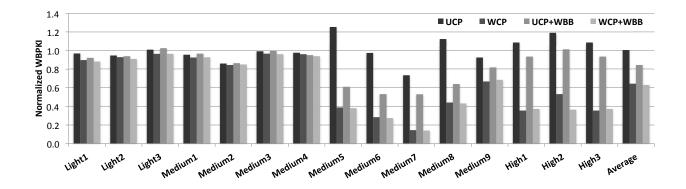

|     |     | 3.5.2 Unbalanced Write Buffers                                  | 37 |

|     |     | 3.5.3 Memory Lifetime                                           | 37 |

|     |     | 3.5.4 Energy Consumption                                        | 38 |

|     |     | 3.5.5 Performance                                               | 39 |

|     |     | 3.5.6 Sensitivity Study                                         | 41 |

|     |     | 3.5.7 Hardware Overhead                                         | 44 |

|     | 3.6 | Conclusion                                                      | 44 |

| 4.0 | BA  | NDWIDTH PARTITIONING USING WRITEBACK INFORMATION                | 45 |

|     | 4.1 | Limited Memory Device Bandwidth                                 | 45 |

|     | 4.2 | Architecture Support for Writeback-Aware Bandwidth Partitioning | 47 |

|     |     | 4.2.1 Bandwidth Partitioning                                    | 47 |

|     |     | 4.2.2 Architecture Overview                                     | 50 |

|     | 4.3 | Writeback-aware Bandwidth Partitioning                          | 52 |

|     |     | 4.3.1 CPI Formula Extension                                     | 53 |

|     |     | 4.3.2 Queuing Delay Derivation                                  | 54 |

|     |     | 4.3.3 Maximizing Weighted Speedup                               | 54 |

|     | 4.4 | Dynamic Weight Adjustment                                       | 56 |

|     | 4.5 | Evaluation Results                                              | 58 |

|     |     | 4.5.1 Performance                                               | 58 |

|     |     | 4.5.2 Effective Read Latency                                    | 61 |

|     |     | 4.5.3 Dynamic Weight Adaptation Granularity                     | 61 |

|     |     | 4.5.4 Sensitivity Study                                         | 62 |

|     | 4.6 | Conclusion                                                      | 64 |

| 5.0 | CO  | ORDINATING THE PARTITIONING OF CACHE AND BANDWIDTH              | 65 |

|     | 5.1 | Interaction of Cache and Bandwidth Partitioning                 | 65 |

|     | 5.2 | Coordinated Partitioning of Cache and Bandwidth                 | 68 |

|     |     | 5.2.1 Problem Definition                                        | 68 |

| 5.2.2 Search Driven Partitioning | 69 |

|----------------------------------|----|

| 5.2.3 Model Driven Partitioning  | 70 |

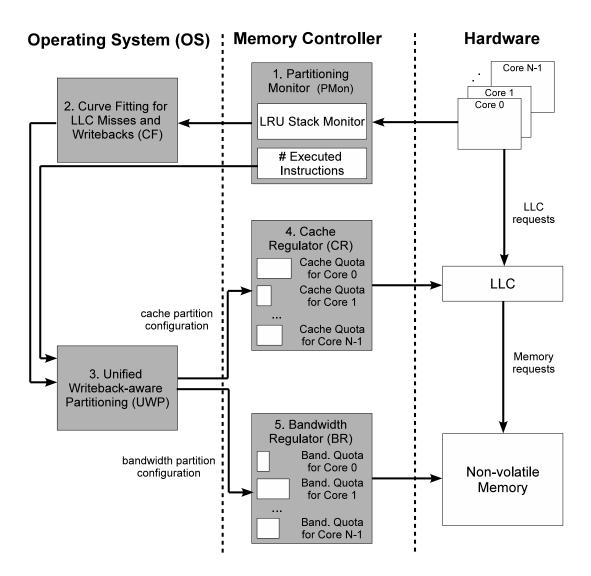

| 5.2.4 Architecture of UWP        | 75 |

| 5.3 Evaluation Results           | 76 |

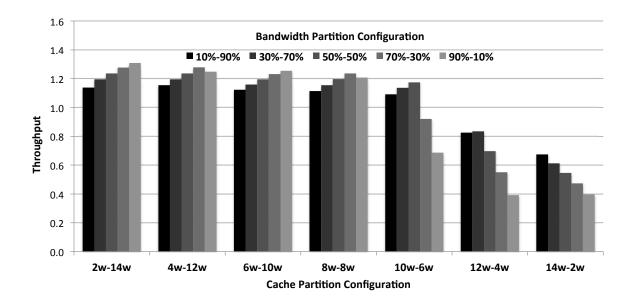

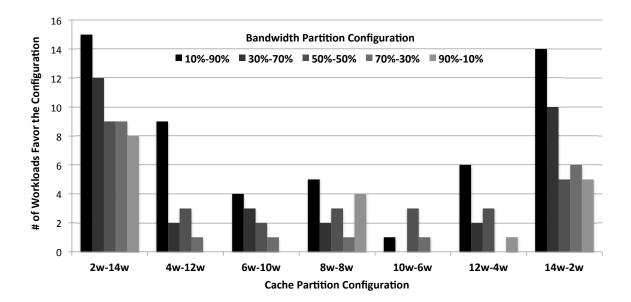

| 5.3.1 Search Driven Partitioning | 76 |

| 5.3.2 Performance                | 77 |

| 5.3.3 Memory Lifetime            | 80 |

| 5.3.4 Energy Consumption         | 81 |

| 5.3.5 Sensitivity Study          | 81 |

| 5.4 Conclusion                   | 84 |

| 6.0 CONCLUSION                   | 85 |

| BIBLIOGRAPHY                     | 87 |

### LIST OF TABLES

| 1 | Basic attributes of different memory technologies                  | 2  |

|---|--------------------------------------------------------------------|----|

| 2 | Partitioning weights for different optimization objectives         | 28 |

| 3 | Baseline configuration                                             | 33 |

| 4 | Benchmark classification based on writebacks per 1000 instructions | 34 |

| 5 | Multiprogrammed workloads of Light, Medium and High                | 34 |

| 6 | Storage overhead of WCP in a 8-core system                         | 44 |

| 7 | Parameters for the analytic model                                  | 49 |

| 8 | Latency overhead of search driven schemes and UWP                  | 77 |

### LIST OF FIGURES

| 1  | PCM cell structure                                                                   | 7  |

|----|--------------------------------------------------------------------------------------|----|

| 2  | The process of PCM write operations                                                  | 8  |

| 3  | Example current-voltage behavior of PCM cells                                        | 9  |

| 4  | Hybrid Main Memory Architecture                                                      | 20 |

| 5  | Architectural components to enable WCP                                               | 23 |

| 6  | An example of tracking writebacks from a cache                                       | 25 |

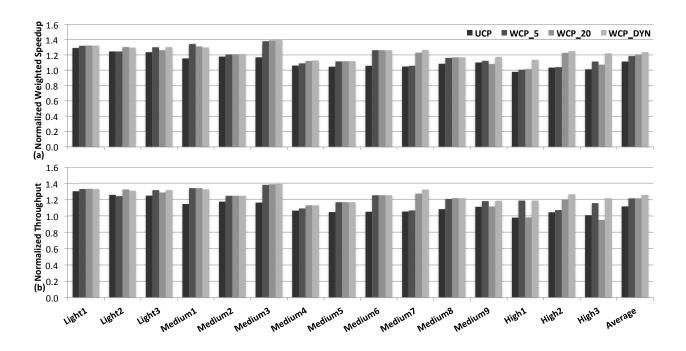

| 7  | Performance impact of cache partitioning weight                                      | 36 |

| 8  | Average occupancy of write buffers when there are congested write buffer(s) $\ldots$ | 37 |

| 9  | Impact on memory lifetime                                                            | 38 |

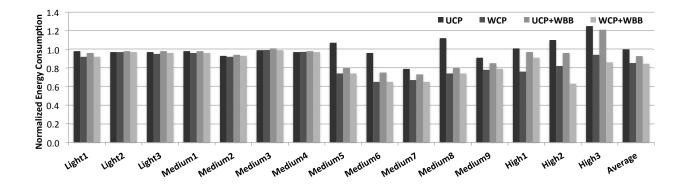

| 10 | Impact on memory energy consumption                                                  | 38 |

| 11 | Impact on weighted speedup                                                           | 39 |

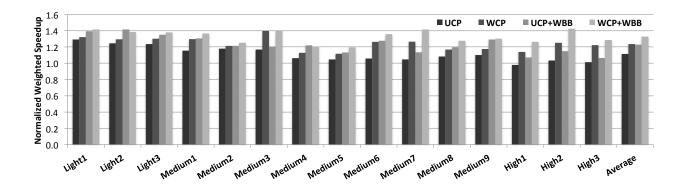

| 12 | Impact on system throughput                                                          | 40 |

| 13 | Impact on fairness                                                                   | 40 |

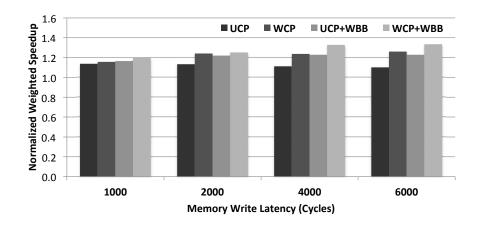

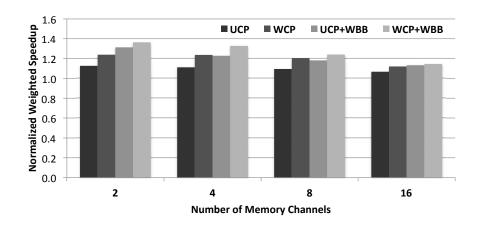

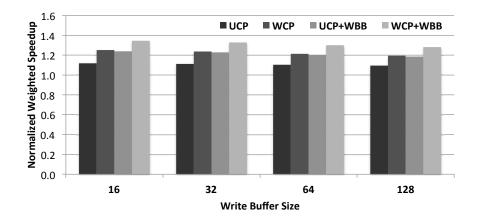

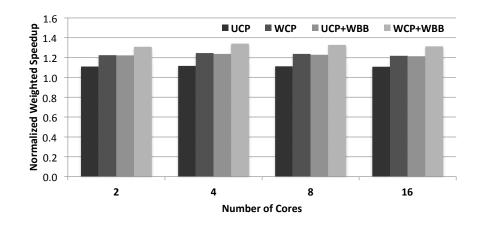

| 14 | Sensitivity of WCP and WBB to memory write latency                                   | 41 |

| 15 | Sensitivity of WCP and WBB to # of memory channels                                   | 42 |

| 16 | Sensitivity of WCP and WBB to write buffer size                                      | 42 |

| 17 | Sensitivity of WCP and WBB to # of cores                                             | 43 |

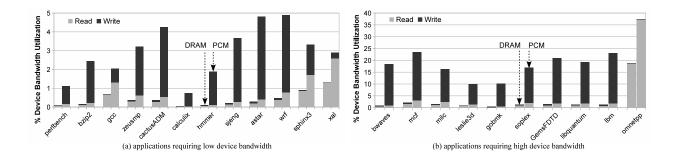

| 18 | Percentage of device bandwidth for DRAM and hybrid memory systems                    | 46 |

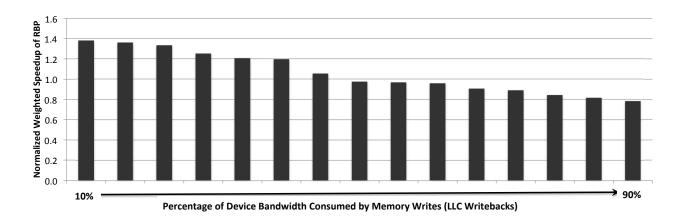

| 19 | Throughput of RBP normalized to SHARE                                                | 47 |

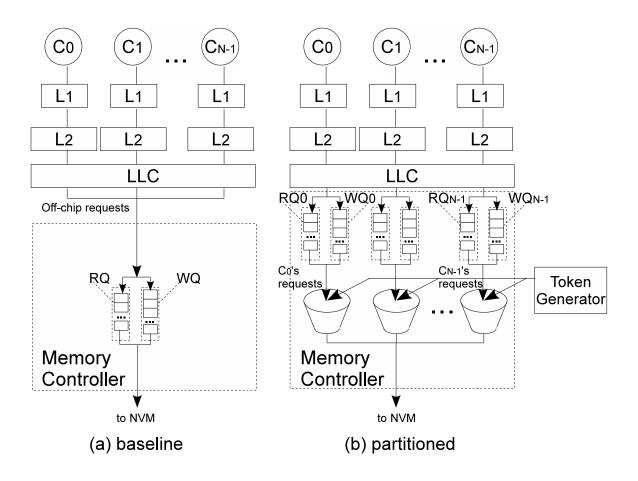

| 20 | Architecture abstractions for bandwidth partitioning                                 | 48 |

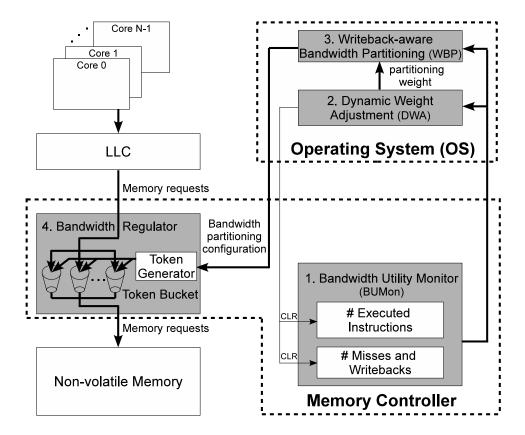

| 21 | Components added to memory controller and OS to support WBP                          | 51 |

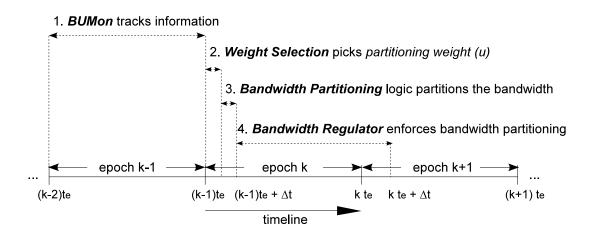

| 22 | Writeback-aware bandwidth partition steps/timeline                                   | 52 |

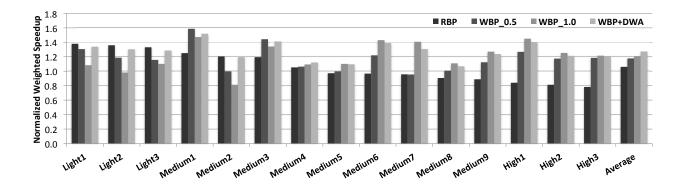

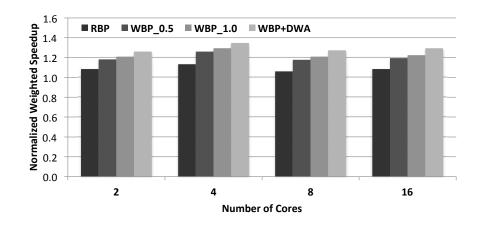

| 23 | Weighted speedup normalized to SHARE                                       | 59 |

|----|----------------------------------------------------------------------------|----|

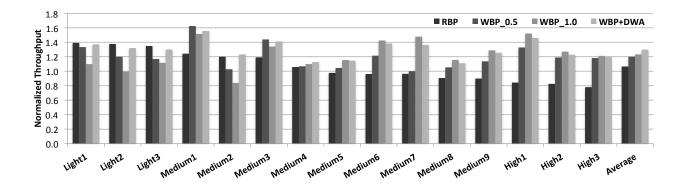

| 24 | Throughput normalized to SHARE                                             | 60 |

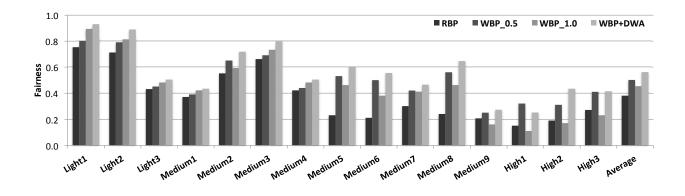

| 25 | Fairness normalized to SHARE                                               | 60 |

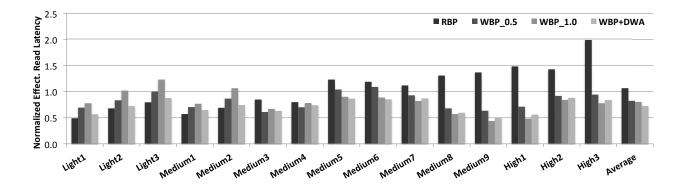

| 26 | Average effective read latency normalized to SHARE                         | 61 |

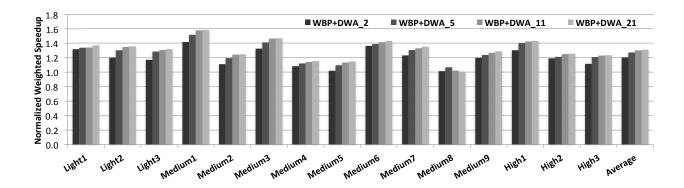

| 27 | Performance impact of dynamic weight adaptation granularity                | 62 |

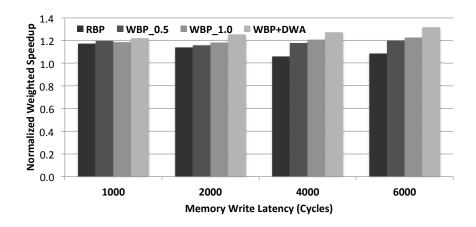

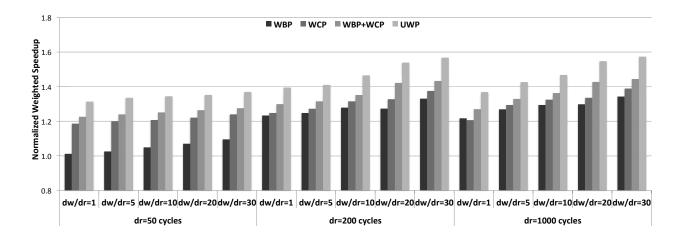

| 28 | Sensitivity of bandwidth partitioning schemes to memory write latency      | 63 |

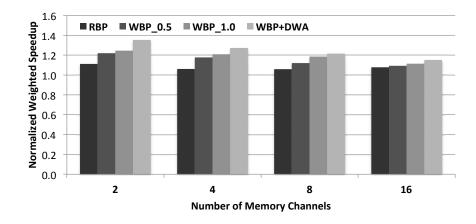

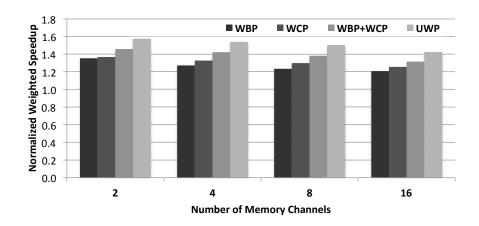

| 29 | Sensitivity of bandwidth partitioning schemes to # of memory channels      | 63 |

| 30 | Sensitivity of bandwidth partitioning schemes to # of cores                | 64 |

| 31 | Performance of <i>mcf-bzip2</i>                                            | 66 |

| 32 | Number of workloads favoring each static partitioning configuration        | 67 |

| 33 | Architectural components to support UWP                                    | 74 |

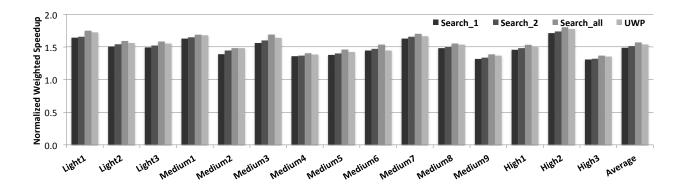

| 34 | Weighted speedup of search driven partitioning and UWP normalized to SHARE | 76 |

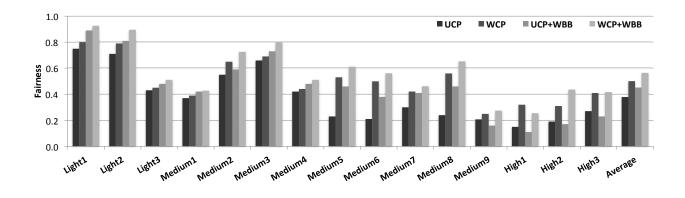

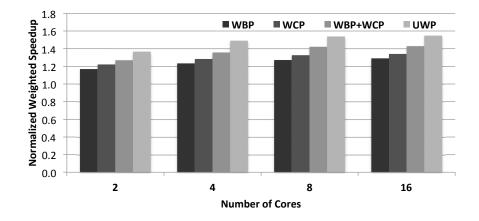

| 35 | Weighted speedup of WBP, WCP, WBP+WCP and UWP normalized to SHARE          | 78 |

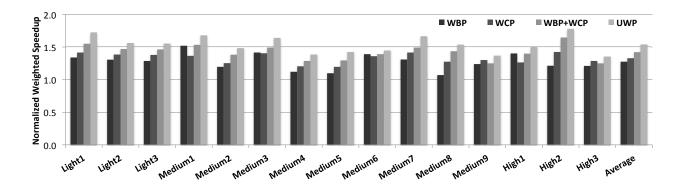

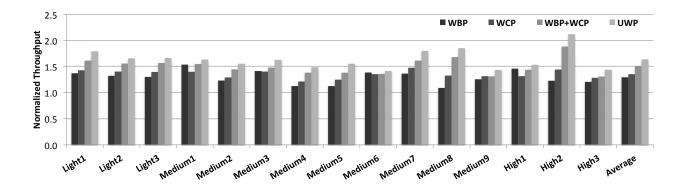

| 36 | Throughput of WBP, WCP, WBP+WCP and UWP normalized to SHARE                | 79 |

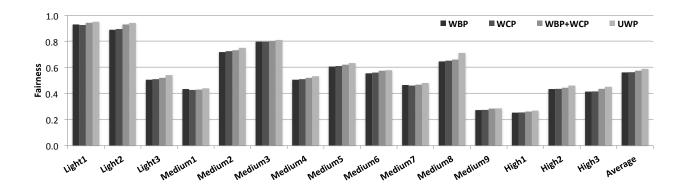

| 37 | Fairness of WBP, WCP, WBP+WCP and UWP normalized to SHARE                  | 79 |

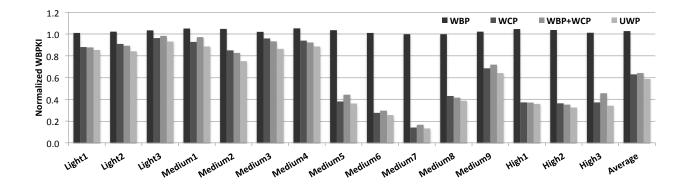

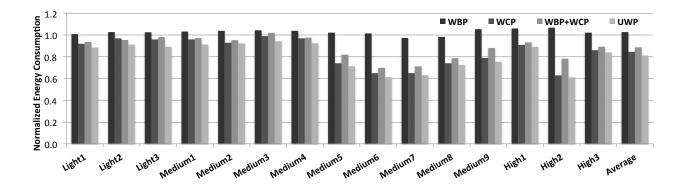

| 38 | WBPKI of WBP, WCP, WBP+WCP and UWP normalized to SHARE                     | 80 |

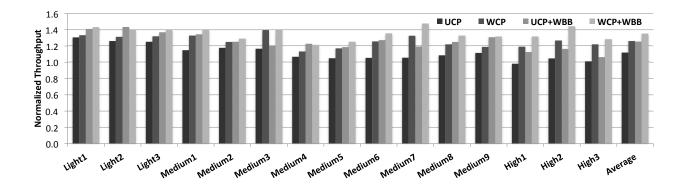

| 39 | Energy consumption of WBP, WCP, WBP+WCP and UWP normalized to SHARE .      | 81 |

| 40 | Sensitivity of UWP to memory write latency                                 | 82 |

| 41 | Sensitivity of UWP to number of memory channels                            | 83 |

| 42 | Scalability of UWP                                                         | 83 |

# LIST OF EQUATIONS

| 3.1  | Equation (3.1) . | • | • |     |   | • | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • |   | • |  | • | • | • |   | ••• | 28 |

|------|------------------|---|---|-----|---|---|---|-------|--|---|-------|---|---|---|---------|---|---|---|--|---|---|---|---|-----|----|

| 3.2  | Equation (3.2) . |   |   |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>• • | • |   | • |  |   | • |   |   |     | 28 |

| 3.3  | Equation (3.3) . |   |   |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>• • | • |   | • |  |   | • |   |   |     | 28 |

| 3.4  | Equation (3.4) . |   |   |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>• • | • |   | • |  |   | • |   |   |     | 28 |

| 3.5  | Equation (3.5) . |   |   |     |   |   |   |       |  | • | <br>• |   |   |   | <br>•   |   |   | • |  |   | • |   |   |     | 29 |

| 3.6  | Equation (3.6) . |   | • |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>•   | • |   | • |  |   | • |   |   | ••• | 35 |

| 3.7  | Equation (3.7) . |   | • |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>•   | • |   | • |  |   | • |   |   | ••• | 35 |

| 3.8  | Equation (3.8) . |   | • |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>•   | • |   | • |  |   | • |   |   | ••• | 35 |

| 4.1  | Equation (4.1) . |   | • |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>•   | • |   | • |  |   | • |   |   | ••• | 50 |

| 4.2  | Equation (4.2) . |   | • |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>•   | • |   | • |  |   | • |   |   | ••• | 53 |

| 4.3  | Equation (4.3) . |   | • |     |   |   | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • | • | • |  | • | • | • |   |     | 53 |

| 4.4  | Equation (4.4) . |   | • |     |   |   | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • | • | • |  | • | • | • |   |     | 53 |

| 4.5  | Equation (4.5) . |   | • |     |   |   | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • | • | • |  | • | • | • |   |     | 54 |

| 4.6  | Equation (4.6) . |   | • |     |   |   | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • | • | • |  | • | • | • |   |     | 54 |

| 4.7  | Equation (4.7) . |   | • |     |   |   | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • | • | • |  | • | • | • |   |     | 54 |

| 4.8  | Equation (4.8) . |   | • |     |   |   | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • | • | • |  | • | • | • |   |     | 54 |

| 4.9  | Equation (4.9) . |   | • | ••• | • |   |   | <br>• |  | • | <br>• |   | • | • | <br>• • | • |   | • |  |   | • |   | • |     | 55 |

| 4.10 | Equation (4.10)  |   | • | ••• | • |   |   | <br>• |  | • | <br>• |   | • | • | <br>• • | • |   | • |  |   | • |   | • |     | 55 |

| 4.11 | Equation (4.11)  |   | • | ••• | • |   |   | <br>• |  | • | <br>• |   | • | • | <br>• • | • |   | • |  |   | • |   | • |     | 55 |

| 4.12 | Equation (4.12)  |   | • |     |   |   | • | <br>• |  | • | <br>• |   |   | • | <br>•   | • | • | • |  | • | • | • |   |     | 55 |

| 4.13 | Equation (4.13)  | • |   | ••• |   | • | • | <br>• |  | • | <br>• | • | • | • | <br>• • |   | • | • |  |   | • |   |   |     | 56 |

| 4.14 | Equation (4.14)  |   |   |     |   |   |   | <br>• |  | • | <br>• |   |   | • | <br>•   |   |   | • |  |   | • |   |   |     | 57 |

| 4.15 | Equation (4.15)  | • |   | • | • |  | • |   | • |   | • |     | • |   |   |   | • | • |   | • |  |  |   |   |   |   | • |   | ••• | 4      | 57 |

|------|------------------|---|---|---|---|--|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|--|--|---|---|---|---|---|---|-----|--------|----|

| 4.16 | Equation (4.16)  |   |   | • | • |  |   | • |   | • | • |     | • |   |   |   |   |   | • | • |  |  |   |   |   |   | • |   |     | 4      | 57 |

| 4.17 | Equation (4.17)  | • | • | • | • |  |   |   | • |   | • |     |   |   |   | • |   | • |   | • |  |  |   | • |   |   | • |   |     | 4      | 58 |

| 5.1  | Equation (5.1) . | • |   | • | • |  |   | • | • | • | • | ••• | • | • | • |   | • |   | • | • |  |  | • |   | • | • | • | • |     | (      | 58 |

| 5.2  | Equation (5.2) . |   |   | • | • |  |   |   |   |   | • |     | • |   |   |   |   |   |   | • |  |  |   |   |   |   | • |   |     | (      | 59 |

| 5.3  | Equation (5.3) . |   |   | • | • |  |   |   |   |   | • |     | • |   |   |   |   |   |   | • |  |  |   |   |   |   | • |   |     | 7      | 71 |

| 5.4  | Equation (5.4) . |   |   | • | • |  |   |   |   |   | • |     | • |   |   |   |   |   |   | • |  |  |   |   |   |   | • |   |     | 7      | 71 |

| 5.5  | Equation (5.5) . | • |   | • | • |  |   | • | • | • | • | ••• | • | • | • |   | • |   | • | • |  |  | • | • | • | • | • | • |     | ,<br>, | 71 |

| 5.6  | Equation (5.6) . | • |   | • | • |  |   | • | • | • | • | ••• | • | • | • |   | • |   | • | • |  |  | • | • | • | • | • | • |     | ,<br>, | 71 |

| 5.7  | Equation (5.7) . | • |   | • | • |  |   | • | • | • | • | ••• | • | • | • |   | • |   | • | • |  |  | • | • | • | • | • | • |     | ,<br>, | 72 |

| 5.8  | Equation (5.8) . | • |   | • | • |  |   | • | • | • | • | ••• | • | • | • |   | • |   | • | • |  |  | • | • | • | • | • | • |     | ,<br>, | 72 |

| 5.9  | Equation (5.9) . |   |   | • | • |  |   |   |   |   | • |     | • |   |   |   |   |   |   | • |  |  |   |   |   |   | • |   |     | 7      | 72 |

| 5.10 | Equation (5.10)  | • |   | • | • |  |   | • | • | • | • | ••• | • | • | • |   | • |   | • | • |  |  | • | • | • | • | • | • |     | ,<br>, | 72 |

| 5.11 | Equation (5.11)  |   |   | • | • |  |   |   |   |   | • |     | • |   |   |   |   |   |   | • |  |  |   |   |   |   | • |   |     | 7      | 72 |

| 5.12 | Equation (5.12)  |   |   | • | • |  |   |   |   |   | • |     | • |   |   |   |   |   |   | • |  |  |   |   |   |   | • |   |     | 7      | 72 |

| 5.13 | Equation (5.13)  |   |   |   |   |  |   |   |   |   |   |     |   |   |   |   |   |   |   |   |  |  |   |   |   |   |   |   |     | 7      | 73 |

### LIST OF ALGORITHMS

| 3.1 | Monitoring Hits                                                                                     | 27 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 3.2 | Monitoring Writebacks                                                                               | 27 |

| 3.3 | Adjusting Cache Partitioning Weight $(w_c)$ Dynamically $\ldots \ldots \ldots \ldots \ldots \ldots$ | 30 |

| 3.4 | Write Buffer Balancing Replacement                                                                  | 32 |

| 5.1 | Search Driven Partitioning                                                                          | 70 |

| 5.2 | Lookahead Cache Partitioning Algorithm                                                              | 73 |

#### **1.0 INTRODUCTION**

Designing large capacity and energy-efficient memory systems becomes an increasingly important issue nowadays due to the high demands of modern data-intensive applications, the adoption of multicore processors and virtualization. Improving the energy efficiency of computing systems is a vital part towards a green society as the power consumed by computing systems is substantial. The U.S. Environmental Protection Agency estimated that the annual energy cost for data centers in 2011 was \$7.4 billion. The energy/power demand of modern processors has been lowered through numerous architectural and design techniques, such as dynamic voltage and frequency scaling (DVFS) [39]. With energy efficient processors and the increasing size of the memory systems, main memory becomes a significant system power consumer [44, 1].

In past decades, DRAM has been the best candidate for main memory due to its low cost per bit. However, the memory capacity of data centers and servers has increased tremendously due to the large footprints of modern applications and the advent of multi-core systems. In these systems, DRAM static power accounts for a substantial portion of energy. As a result, the memory sub-system has become a major consumer of power, which has fueled research in alternative memory technologies. Non-volatile memory (NVM) is proposed as a replacement for DRAM or in addition to DRAM (using a smaller DRAM as a cache for the larger NVM). NVM is a desirable technology because of its non-volatility, low power for reads and very low idle power. Some of the NVM technologies include NAND Flash, Change Memory (PCM) [33, 15] and Spin-Transfer Torque RAM (STT-RAM) [50, 78, 20, 8, 36, 10].

NAND Flash is not suitable for serving as the main memory. It has very limited number of write/erase cycles:  $10^5$  rewrites [19] as opposed to  $10^{16}$  for DRAM. NAND Flash also requires a block to be erased before writing into that block, which introduces considerably extra delay and energy. Moreover, NAND Flash can only be accessed in blocks and is not byte-addressable.

| Attribute        | DRAM      | NAND Flash     | PCM                 | STT-RAM     |

|------------------|-----------|----------------|---------------------|-------------|

| Non-Volatile     | No        | Yes            | Yes                 | Yes         |

| Byte-addressable | Yes       | No             | Yes                 | Yes         |

| Read Latency     | 20-50 ns  | $25~\mu{ m s}$ | 50 ns               | 2 ns        |

| Write Latency    | 20-50 ns  | 500 $\mu$ s    | $1 \ \mu s$         | 10 ns       |

| Endurance        | $10^{16}$ | $10^4 - 10^5$  | $10^{7}$ - $10^{8}$ | $10^{12}$   |

| Cell Area        | $6 F^2$   | $5 F^2$        | 5-8 $F^{2}$         | 37-40 $F^2$ |

Table 1: Basic attributes of different memory technologies

Therefore, NAND flash has been proposed as a disk cache [4, 35] or a replacement for disks [86] where writes are relatively infrequent, and happen mostly in blocks.

The other two NVM technologies, PCM and STT-RAM, are promising candidates for energyefficient memory technology. Both of them share the common advantages of non-volatility, byteaddressability and scalability [24, 32]. STT-RAM is faster than PCM, and has nearly the same endurance as DRAM [79]. PCM, on the other hand, is much denser than STT-RAM. The cell area for DRAM, PCM and STT-RAM are  $6F^2$  [81],  $5-8F^2$  [41], and  $37-40F^2$  [12] respectively, where F is the feature size. PCM also has excellent scalability within current CMOS fabrication methodology [71, 68, 41, 60, 70]. PCM's attributes, along with the common advantages of emerging memory technologies, make it a promising candidate of main memory [6, 42, 64].

Table 1 compares the basic attributes of NAND Flash, PCM and STT-RAM against DRAM [12, 22, 9, 41, 45, 79, 81, 96]. Unlike DRAM, NVM has a unique read/write asymmetry property (in terms of access latency, energy consumption and endurance).

In this dissertation, I explore using of PCM as main memory. Although PCM has many promising properties, it faces important challenges. It is wearable such that only 10<sup>7</sup> to 10<sup>8</sup> writes can be performed. A PCM device would fail in days or even hours without wear-leveling [96, 65, 7, 18]. Moreover, PCM is slower and consumes more energy on writes than DRAM. *Hybrid* main memory architectures [42, 17, 64] have been proposed to alleviate the problem. The hybrid architecture introduces a small DRAM as the *last-level cache* (LLC) before a large PCM, and is the baseline memory architecture in this thesis.

Last-level cache and memory bandwidth are two important resources impacting system performance. In a single-core system, cache reduces the average access latency and off-chip memory traffic, while the available memory bandwidth determines the processing rate of off-chip accesses. In a multi-core system, cores compete for these resources, drastically increasing their performance impact. Qureshi and Patt showed that cache partitioning improves the cache utility and system performance. They proposed to partition the LLC to minimize the total number of LLC misses to achieve better system performance, based on the observation that a reduction in LLC miss rate correlates with an improvement in IPC [63].

Bandwidth partitioning has also been shown to be beneficial for system performance. Liu et al. [47] proposed an analytic model to understand how off-chip bandwidth partitioning affects system performance. By allocating bandwidth according to the analytic model, they were able to improve the weighted speedup by up to 20% in a DRAM memory system.

The existing cache partitioning and bandwidth partitioning techniques [63, 47] do not consider the unique read/write asymmetry property of NVM. In this dissertation, we propose cache partitioning and bandwidth partitioning techniques that are tailored for NVM main memory systems by considering the read/write asymmetry property of NVM.

The rest of this dissertation is organized as follows: Chapters 1.1, 1.2 and 1.3 describe the problem we are solving, present our solution and contributions, respectively. Chapter 2 presents background information and related work. The proposed techniques are presented in Chapter 3 through Chapter 5. Chapter 6 concludes the thesis.

#### **1.1 PROBLEM STATEMENT**

Computing systems are part of our lives today, not only in a recognizable form but ranging from the large clusters in data centers to embedded systems in handy devices. Building energy-efficient and large capacity memory systems is very important. NVM technologies are promising candidates for energy-efficient memory. However, typical NVMs face certain challenges due to undesirable write

properties. It is our goal to propose techniques to better utilize the shared resources (last-level cache capacity, and memory bandwidth) to mitigate the undesirable impacts of memory writes by exploiting the unique read/write asymmetric property of NVM. This work is important for enabling energy-efficient NVM as the main memory.

#### **1.2 SOLUTION OVERVIEW**

In this dissertation, we propose three techniques to improve the shared resource utility and mitigate the negative effects of non-volatile memory's write operations. First, *writeback-aware cache partitioning* (WCP) is proposed to divide the last-level cache among competing applications such that the number of misses and writebacks are reduced. A companion scheme, *write buffer balancing* (WBB) replacement, spreads writeback traffic among memory banks to reduce the delay due to congested memory write requests. Second, *writeback-aware bandwidth partitioning* (WBP) splits memory device service cycles among competing applications to optimize the overall system performance. Finally, we study the interaction between cache partitioning and bandwidth partitioning. *Unified Writeback-aware Partitioning* (UWP) allocates the cache and memory bandwidth cooperatively to further improve the shared resource utility.

#### **1.3 CONTRIBUTIONS**

This dissertation makes the following contributions:

- It introduces the concept of writeback-aware partitioning which is suitable for shared resource management in NVM systems.

- It proposes *Writeback-aware Cache Partitioning* (WCP) to partition the LLC of NVM. WCP takes into account writeback information, and outperforms a seminal technique, UCP, in terms of system throughput, fairness, memory lifetime and energy efficiency. It also proposes WBB to manage the cache partition of each application to ensure that the writeback traffic to write buffers is balanced.

- It proposes *Writeback-aware Bandwidth Partitioning* (WBP) to account for writeback information to partition the memory bandwidth. A companion scheme, *Dynamic Weight Adjustment* (DWA), is proposed to find the best bandwidth partitioning weight at runtime based on workload behavior.

- It demonstrates the benefits of managing the last-level cache and memory bandwidth cooperatively. An analytic model is introduced to quantify the performance impact of cache partitioning coordinated with bandwidth partitioning. Based on the analytic model, *Unified Writebackaware Partitioning* (UWP) is proposed to partition cache and memory bandwidth cooperatively.

In conclusion, this thesis finds that LLC writeback information is important in managing the shared resources (e.g., LLC capacity and memory bandwidth) for systems with NVM due to the unique asymmetric property. By intelligently considering the LLC writeback information, we can improve the utility of the shared resources and achieve better system performance. The thesis also finds that coordinated management of the LLC capacity and memory bandwidth can further improve the overall shared resource utility and system performance. Although the thesis specifically considers PCM, most of the results can equally apply to other NVM technologies such as STT-RAM.

#### 2.0 BACKGROUND AND RELATED WORK

#### 2.1 PHASE CHANGE MEMORY

#### 2.1.1 Phase Change Memory Background

Phase Change Memory (PCM) is a non-volatile memory that exploits the unique behavior of phase change material to store information. Although the technology emerged recently, the theory of phase change material has its origins early in 1960s when Ovshinsky reported a reversible change in resistivity upon a change in phase in certain glasses [58]. The first Phase Change Memory device was announced in Electronics by Neale et al. [66]. In the following years, the advance of semiconductor manufacturing technology enabled the development and application of PCM. Phase change material is already widely used in rewritable CDs and DVDs, in which the same alloy is used as the PCM memory developed by Numonyx. By exploiting the electrical resistivity of phase change material, PCM is drawing increasing interest recently, as it can be used as a memory cell and organized into memory array similar to DRAM.

A conventional DRAM cell uses a capacitor to store a bit of information. Analogously, a PCM cell uses phase change material to remember a bit. The phase change material is one type of chalcogenide alloy, such as Ge2Sb2Te5 (GST), which has two stable physical states: amorphous and crystalline. In the amorphous state, the material is highly disordered and exhibits high resistivity. In the crystalline state, the material has a regular crystalline structure and exhibits low resistivity. PCM exploits the difference in resistivity between these two states of the material to

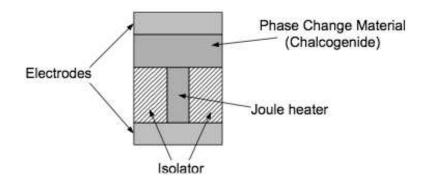

Figure 1: PCM cell structure

store data. Typically, a cell in the amorphous state (high resistance) is regarded as a logic "0" (RESET state), and a cell in crystalline state (low resistance) is regarded as a logic "1" (SET state). Unlike DRAM that relies on constant refresh to retain its data, the state of GST is preserved even after the cell is powered off, meaning that PCM is non-volatile.

A PCM cell is composed of several components (Figure 1). A layer of chalcogenide (GST) is sandwiched between two electrodes. A joule heater is placed between GST and the bottom electrode. The structure forms a PCM cell, which appears as a resistance in the circuit. Reading data from a PCM cell involves sensing the resistance level of the cell. This is done by applying a small voltage across the two electrodes so that the resistance of GST can be measured. This process is non-destructive and has negligible heat stress compared to write operations.

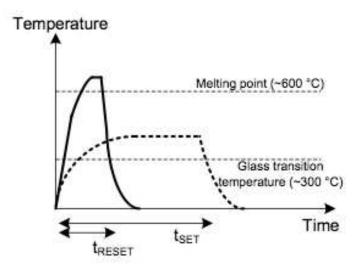

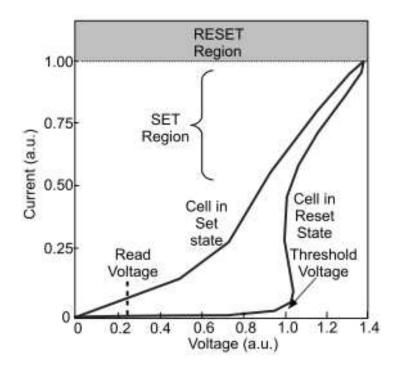

PCM write operations are done by changing the physical state of the GST material. The writing process requires controlling the temperature of the material to achieve the desired state. When heated above its crystallization temperature  $(-300^{\circ}C)$  but below its melting temperature  $(-600^{\circ}C)$  over a period of time, GST turns into a low-resistance crystalline state (which corresponds to logic "1" or SET state). When heated above its melting point and quenched quickly, GST turns into a high-resistance state (which corresponds to logic "0" or RESET state). Figure 2 illustrates the two process of PCM write operations. Figure 3 shows the example current-voltage behavior of PCM cells. Though writing a PCM cell incurs high operating temperature, the thermal cross-

Figure 2: The process of PCM write operations

talk between adjacent cells at 65nm is shown to be negligible even without thermal insulation material [60]. Similar to the multi-level flash memory, the phase change material can also be programmed into four or more distinct states, forming a multi-level PCM cell that can represent four or more values [60, 9].

Despite the differences with DRAM cells, PCM can still use a similar array structure as DRAM arrays. It can use the same peripheral logic such as decoders, row buffers, request/reply networks etc. as the DRAM array [43]. In a typical PCM cell array structure, each PCM cell is connected between an access transistor and a bitline (BL). The access transistor is controlled by the wordline (WL). In order to access a PCM cell, its wordline is selected to enable the access transistor, which forms a path between the cell's bitline and ground. Read or write operations on the PCM cell are then done by applying different voltage pulses on the bitline. Selecting a wordline enables the access transistor of a series ("row") of PCM cells. By controlling the bitlines using a column mux, read or write operations can be performed on selected cells in that row.

There are two main options for the access of the device in a PCM cell: a transistor or a diode. A diode has a simpler structure, and hence is good for cell density. However, a diode cannot satisfy the high write current requirement beyond sub-100nm technology [84]. Also the scaling rule for a

Figure 3: Example current-voltage behavior of PCM cells

diode is not as clear as in NMOS [60]. Lastly, the diode-based cell has been reported to be more vulnerable to errors induced by writing data to adjacent cells because of bipolar turn-on of the nearest-neighbor cells [29]. Taking all of the above, especially the scalability, into consideration, I assume transistor-based PCM cells in my experiments. My assumption was also confirmed by Li et al. [26].

**PCM's advantages.** Like DRAM, PCM memory is byte-addressable, giving it a big advantage over current NAND Flash technology that only supports block accesses. PCM offers comparable read latency as DRAM. Typical area size of PCM cell is  $5-8F^2$  [41], meaning that PCM has similar density to DRAM.

With shrinking feature size, DRAM is facing serious scaling problems as it is bounded by the limitation in cell-bitline capacitance ratio. DRAM has been found to be difficult to scale below 40nm [82]. PCM, on the other hand, offers much better scalability: When a PCM cell shrinks, the volume of the GST material shrinks as well, resulting in less write current. Hence PCM provides

a truly scalable solution compared to conventional DRAM. A recent prototype by Liang et al. demonstrated the viability of the PCM cell reaching 2.5nm technology node [26].

Like NAND Flash, PCM is non-volatile. In theory, a PCM cell only consumes energy when it is accessed (read or write). This makes it possible to build memory chips with low leakage, which is crucial to meet the low-power requirements of future memory systems. Moreover, PCM uses physical states instead of electrical charge to represent data, making it much less vulnerable to the soft errors caused by alpha particles or cosmic radiation.

**PCM's disadvantages.** Due to repeated heat stress applied to the phase change material, PCM has limited number of write cycles (i.e., write endurance). A single cell can typically sustain 10<sup>7</sup>-10<sup>9</sup> writes before a failure occurs [19, 9, 16]. While this is much better than NAND Flash, it could be a big concern if PCM is used in main memory. A PCM device without any lifetime improvement technique may last only about 100 days running a typical SPEC CPU program.

PCM's write operation is also slower than its read operation due to the heating/cooling process during a write. What makes things worse is that PCM write incurs high current injection (e.g., 0.6-1mA), resulting in high write power (2.88-4.8mW per bit) [43]. When PCM is used as memory, a multi-bit memory write (e.g., writing a 512-bit memory line) is usually completed in several rounds, with each round writing part of the line. This makes PCM's per-access write latency even longer. For example, Numonyx reported a 1us page write latency for its PCM prototype. This long per-access write latency and high write power have created some major issues when using PCM in main memory.

Another issue is the resistance drift in multi-level cells (MLC) [88, 23]. After a multi-level PCM cell is programmed, its resistance may increase and saturate over time, which is termed "resistance drift" [90]. Previous studies have indicated that the phenomena is caused by the structural relaxation of chalcogenide material, which is a thermally-activated, atomic rearrangement of the amorphous structure [88]. Resistance drift can cause a PCM cell to change to another state at runtime, causing a soft error. A study by Awasthi et al. has shown that the drift may occur as soon as 1.81 seconds after a cell is programmed [52]. In response to this problem, architectural techniques have been proposed to mitigate the issue without high overhead [52, 90]. In this thesis, I assume a single-level cell PCM which does not have the resistance drift issue. However, the techniques proposed in this thesis are independent of PCM cell technology. They can be extended to multi-level

cell (MLC) and are orthogonal to the drift-mitigating schemes.

While PCM is favored due to its non-volatility, high scalability and low power consumption, it suffers from the undesirable properties such as its slow, power hungry and destructive write operation. Next, we will described the existing architectural techniques to mitigate the endurance and performance problem of PCM.

#### 2.1.2 Architectural techniques for PCM

PCM has an endurance of  $10^7$  to  $10^9$  writes per cell [19, 9, 16]. If a specific cell is written once a second, it will take only 115 days for that cell to pass  $10^7$  writes. This shows that, even with a very low write rate per cell of one write per second, PCM endurance is not enough to sustain a lifetime of 7 to 8 years. which is the expected lifetime of a server assuming obsolescence and capacity limits.

A number of techniques have been proposed to increase lifetime of PCM devices and PCM memory systems. These techniques vary from write minimization (avoiding unnecessary writes), to various forms of wear-leveling, to changes in bit encoding. Some important techniques are presented in the following subsections.

The goal of the techniques presented below is to remove writes that are redundant or modify the value to be written to reduce the number of bits to be altered. This can be done at the cell, row or even at higher levels of aggregation.

**Read-before-write.** A read is executed before the write and only the cells that store values different from the values to be written are updated, and the cells that already have the final value are not modified. Many PCM devices [33, 37, 43] implement this scheme at the cell level.

**Partial writes.** In this technique [42], higher level caches (the one closest to the main memory) track dirty word or line and pass that information to the main memory. This additional information allows the PCM memory controller and devices to ignore the unmodified portions of the cache. In [64], a similar technique, called Line-Level Writes, is proposed that stores dirty information per cache line.

**Flip-N-Write.** Flip-N-Write uses an additional bit in each row to determine if the value is stored in a normal encoding or inverted [7]. The decision of which way to store is taken based

on the lowest number of changed bits between the already stored data and the new data. This technique reduces the number of bits to write, thus increasing write bandwidth to the memory. PCM write performance is power limited so more bits can be written simultaneously within the same power budget. Less energy is consumed per transaction increasing energy-efficiency of the memory.

In a system in which all the cells have the same endurance, an uneven distribution of wear can cause cells that have more wear to fail prematurely, causing the whole memory to fail even though most of the cells are still healthy. Wear-leveling has the objective of distributing the wear evenly over the cells, avoiding premature cell failures and consequently increasing the memory lifetime. The memory access pattern of applications does not normally follow a regular pattern of an even distribution of writes over the whole memory, but it is highly skewed (see Chapter 3) directing a higher number of writes to a small number of memory locations. The memory subsystem have to counteract that access pattern to avoid premature failures and achieve a higher lifetime. Wearleveling is applied to achieve this goal and can be implemented using different algorithms and granularities. A common implementation disconnects the physical address from a logical address using a mapping function that translates a logical address to the corresponding physical address. This mapping function allows the translation to be changed, pointing a logical address to different physical locations, throughout the lifetime of the memory effectively distributing the writes to the logical address over a larger number of physical addresses. Some of the wear-leveling algorithms use a configurable mapping function, while others implement a mapping table. Some of the algorithms require the physical memory to be larger than what is addressable by a logical address (excess capacity), while others do not require but support this implementation. The wear-leveling algorithms proposed to be used in PCM memories are described below.

**Row Shifting.** This technique implements wear-leveling at the row level [96]. The mapping of the physical cells and the logical cells in a row is shifted by a certain amount at each write, This technique is designed to mitigate the difference in wear of cells in a row. In [96], it is shown that writes to a specific row in general do not modify all bits in the row but tend to affect only a small subset (low order bits for example). By shifting the row, the physical location of a particular bit changes, hence distributing the writes to a single bit over a number of physical cells. It is proposed to use coarser shift instead of small ones (closer to 1bit shift), since modified bits tend to

cluster [96].

Segment Swapping. In segment swapping, each bank of memory is subdivided into fixed size segments. Each segment is composed of a number of rows. By using of a mapping table, the mapping of a logical segment and a physical segment can be made flexible, thus allowing any logical segment to map to any physical segment in that bank. Segment swapping exchanges both the mapping between logical segments and the data, preserving the information but exchanging the physical segment that now holds the data. Segment swapping is proposed in [96] to create a more coarse level wear-leveling. The key to the technique is the selection of the segments that are swapped. The segments chosen in [96] are the ones with the least number of writes since the last swap (above a threshold). Segments that are 1MByte in size are used to reduce the overhead in counters and the size of the mapping table. The memory is unable to respond to requests whenever a segment is being swapped, so even when the number of swaps is small (every  $2 \cdot 10^6$  writes) the latency of copying the data can be significant, since 2MBytes have to be transferred.

**Fine-Grained Wear-Leveling.** This technique is used to achieve intra-page wear-leveling [64]. Each page of 4KBytes is divided into 16 sub-pages and a shift number is added to the logical sub-page number to map to the corresponding physical sub-page. In [96], this shift number is changed only when the page is allocated by the operating system and it is not changed until the page is freed. The shift number is allocated randomly whenever it is changed.

**Start-Gap.** Start-gap is a low overhead wear-leveling technique [65]. The low overhead is achieved by using a programmable mapping function instead of a mapping table. The mapping function uses two counters, the start and gap counters. The start counter marks which physical address corresponds to the logical address 0 and the gap marks the start of the gap, a sequence of physical addresses that are not currently mapped to any logical address. The physical pages work as a circular buffer with the mapping determined by a start and gap counters. Periodically, based on number of writes, the gap counter is incremented and the information stored at the previous end of the gap is copied to the physical address pointed by the gap counter. This action remaps the logical address that corresponds to the gap entry to a new physical address. Since the physical memory is treated as a circular buffer, a particular logical address will point to all physical addresses during the lifetime of the memory.

Some memories utilize error correction, and in NAND Flash and PCM, ECC has been proposed

as a way to deal with cell failures. ECC reserves additional bits to store redundant information allowing errors to be detected and corrected. ECC is heavily used in servers DRAM main memory where memory errors cannot be tolerated. In a write, the error correcting code is generated and stored in addition to the original information. In a read, the stored error correcting code is compared to the one generated on the fly, if the original error correcting code and the newly generated code do not agree, an error has occurred. The ECC is capable of correcting errors up to a determined number of incorrect bits and detecting but not correcting a larger number of incorrect bits. The limits are determined by the number of additional bits used for ECC. In [69], ECC is determined to be detrimental to PCM and Error-Correcting Pointers (ECP) is proposed. ECC is detrimental to PCM because it requires more bits to be written for each write, increasing power consumption and decreasing write bandwidth. ECC also increases the number of bits modified in each write, because a single data bit changed will affect some or all bits in the error correcting code. ECC is used to detect bits that changed after writes which is useful in DRAM or flash, but not so useful in case of PCM since after a bit is successfully written it will not fail. ECP repurposes the excess bits to be used as pointers and replacements bits. When a write to a memory cell fails, a set of pointer and replacement bit is allocated and the correct value is stored in the replacement bit and the pointer contains the number of the failed bit. This removes the need of computing the error correcting code both in the write and the read, and reading the correct bit is a matter of swapping the incorrect bits pointed by the ECP code. ECP also avoids increasing the number of bits to be written by changing the pointer only when a new failure is detected otherwise the pointer and replacement bits are kept at 0. It is shown that ECP leads to a longer lifetime than ECC.

PCM write latency is one of the major limitations of the technology. Even though PCM reads are expected to be several times slower than DRAM reads, PCM writes are one or more orders of magnitude slower than PCM reads [42, 96]. Write bandwidth is also severely limited by power, since each cell written consumes a significant amount of power, limiting the total number of cells that can be written simultaneously. Read bandwidth does not suffer from that limitation and it is one to two orders of magnitude higher than write bandwidth. One of the simple solutions that has been adopted is write avoidance: to reduce the number of writes to PCM, by both reducing the total number of write operations and the number of bits that are written. Write avoidance has a significant energy and latency impact. Other performance improving techniques have been

proposed such as write cancellation and a improved PCM requests scheduler.

Write Avoidance. Flip-N-Write can reduce the write access traffic to the PCM devices by reducing the number of bits that are simultaneously written to the memory [7]. Partial writes and Read-before-write when used at a line/row level potentially can remove unnecessary writes [96]. The drawback of partial writes is the requirement of additional dirty bits to store the dirty status in a higher granularity. Read-before-write requires a read operation before a write and in worst case can have a small increase in latency since reads are much faster than writes.

**Request Preemption and Pausing.** PCM Request preemption is used to improve performance by reducing the impact of high latency operations. Both reads and writes can be preempted [61, 95]. The advantage of preemption is reduction of latency for higher priority requests even if another operation is already ongoing for that bank. Read preemption increases energy consumption since the operation has to be reexecuted in the future. Writes are the large latency offender in PCM, they are up to 10x slower than reads and are often not in the critical path. Write preemption (write cancellation) has the potential to improve latency at the cost of energy efficiency and memory lifetime [61]. The additional energy and wear are consequences of the reexecution of the write since the previous write was not completed and the stored value differs from the expected. These techniques try to limit the impact by not allowing preemptions to occur to the same request too many times [61, 95]. An alternative scheme, write pausing, is proposed to pause the write operation between steps in the loop (overprogramming) and resume the write later [61]. This operation does not incur in energy overhead, since the operation is not repeated but restarted from the point it was stopped. The request is paused so no additional latency is necessary beyond the delay caused by the requests interposed to the paused one.

Memory Request Scheduling. A new memory controller is proposed to implement a scheduling algorithm that is more amenable to PCM [95]. The scheduling algorithms proposed in [95] are a modification of PAR-BS [56], which is a fair scheduling algorithm designed for CMP systems and is modified to include write and read preemption in an effort to improve latency for higher priority requests. The preemption of requests that can be close to finishing does not improve latency significantly and can be detrimental to energy efficiency. Threshold limits are implemented to preclude preemption to requests that will take less than the threshold to finish. The advantage of specializing the memory controller to PCM is the ability to explore the difference in internal operations between PCM and DRAM. DRAM, contrary to PCM, requires that a read be followed by a write in a row, since reads are destructive while PCM reads are harmless. PCM can have preemptable reads or writes, while preemption in DRAM are not possible since that would provoke information loss in reads and a single write buffer prevents simultaneous operation (read with a write date buffered). This is possible in PCM since read data do not have to be stored to preserve information.

Zhou et al. [92] studied the memory scheduling algorithms suitable for embedded systems with PCM main memory. It is proposed to reorder PCM requests based on criticality of the requests to reduce latency and the number of missed deadlines.

#### 2.2 MANAGEMENT OF SHARED CACHES

Cache is an important resource that impacts the application/system performance. For an application, the cache replacement policy decides which cache block to evict to make room for an inserted cache block. An effective cache replacement policy can keep the highly reusable data in the cache longer to achieve better cache utility and application performance. In a CMP system with a shared cache, the allocation of the shared cache capacity on applications/cores can greatly influence the overall utility of the shared cache. In this dissertation, we consider both cache replacement and cache partitioning policies which are effective and suitable for asymmetric NVM memory systems by taking into consideration the LLC writeback information. This section discusses the existing cache replacement and cache partitioning techniques.

#### 2.2.1 Cache Replacement

TADIP [27] is a dynamic insertion policy (DIP) that dynamically identifies the application characteristic and inserts single-use blocks (dead on fill) in the LRU position to evict as early as possible. PIPP [87] pseudo partitions cache space to each application by having a different insert position for each application, which is determined using a utility monitor as in UCP. Upon hits, each block is promoted toward the MRU by one position. PIPP also considers the streaming behavior of an application. When an application shows streaming behavior, PIPP assigns only one way and allows promotion with a very small probability (1/128).

Pseudo-LIFO mechanisms are a new family of replacement policies based on the fill stack rather than the recency stack of the LRU [3]. The intuition of pseudo-LIFO is that most hits are from the top of the fill stack and the remaining hits are usually from the lower part of the stack. Pseudo-LIFO exploits this behavior by replacing blocks in the upper part of the stack, which are likely to be unused.

Jaleel et al. proposed re-reference interval prediction (RRIP) [28]. Cache replacement policies use some method of future reference prediction. For example, LRU predicts that all caches hits and misses will be re-referenced near-immediate. Dynamic insertion policies detect either a near-immediate or distance re-reference pattern in runtime, but not both at the same time. If an application shows a mixed pattern of temporal and non-temporal data, dynamic policies cannot hold near-immediate blocks in the cache. RRIP solves the problem of this mixed pattern by inserting incoming blocks in the not near-immediate position and promote blocks toward the near-immediate position upon hits. RRIP also uses a dynamic insertion policy to filter out non-temporal accesses. Wu et al. proposed prefetch-aware cache management [85], which is built on RRIP.

There is limited study on cache replacement for Non-volatile main memory systems. Ferreira et al. [18] proposed a clean-preferred page replacement algorithm named N-Chance for the DRAM cache in a PCM main memory system. N-Chance gives preference to evict clean pages, which reduces writebacks to PCM by coalescing writes in the DRAM cache.

#### 2.2.2 Cache Partitioning

In an associative cache, the cache capacity can be partitioned by allocating either the cache ways or the cache sets. Existing cache partitioning techniques can be classified into two categories: way partitioning [63, 93] and set partitioning [30, 46]. This thesis studies the way partitioning techniques that are effective for NVM memory systems.

Suh et al. first proposed dynamic cache partitioning schemes in chip multi-processors that consider the cache utility (number of cache hits) using a set of in-cache counters to estimate the cache-miss rate as a function of cache size [75, 74]. However, since the utility information is

acquired within a cache, information for an application cannot be isolated from other applications' intervention.

Utility-based cache partitioning (UCP) [63] addressed this problem by proposing a utility monitor (UMON) that uses separate structures, including ATD (auxiliary tag directory) and way counters. ATD maintains strict LRU-stack per application. Upon hits in ATD, the corresponding way counters will be incremented. The optimal partition for all applications is determined to maximize the overall number of cache hits.

Kim et al. considered the fairness problem from cache sharing such that slowdown due to the cache sharing is uniform to all applications [38]. Moreto et al. proposed MLP-aware cache partitioning, where the number of overlapped misses will decide the priority of each cache miss, so misses with less MLP will have a higher priority [55]. IPC-based cache partitioning [77] considered performance as the miss rate varies. Even though the cache miss rate is strongly related to performance, it does not always match the performance. However, since the baseline performance model is again based on the miss rate and its penalty, it cannot distinguish GPGPU-specific characteristics. Yu and Petrov considered bandwidth reduction through cache partitioning [89]. Srikantaiah et al. proposed the SHARP control architecture to provide QoS while achieving good cache space utilization [73]. Based on the cache performance model, each application estimates the cache requirement and central controllers collect this information and coordinate requirements from all applications.

#### 2.3 BANDWIDTH PARTITIONING

Similar to shared cache, memory bandwidth is also a critical shared resource for CMP systems. More specifically, memory bandwidth can be referred to as two different resources: the bus bandwidth and the bank bandwidth. In a DRAM system, the bus bandwidth is more likely to be the system bottleneck due to the fact that DRAM banks can process request at a relative high speed [47]. In contrast, the bank bandwidth becomes the system bottleneck for a system with NVM (e.g., PCM) [94]. An intelligent bandwidth partitioning policy should always target the system bottleneck. This thesis studies the partitioning of the bank bandwidth. This section discusses the existing memory bandwidth management techniques.

Past studies on bandwidth management took two directions. One direction focuses on memory request scheduling. Rixner et al. [59] proposed the FR-FCFS policy to favor requests that hit in the row buffer over other requests, and older over younger requests. Nesbit et al. [57] proposed Fair Queuing Memory Scheduler to prioritize requests according to the QoS objectives. Ipek et al. [25] proposed a reinforcement learning memory controller to adapt scheduling decisions. The other direction manages off-chip bandwidth allocation among applications. Liu et al. [47] used an analytic model to understand how off-chip bandwidth partitioning affects system performance. They also considered the impact of prefetching on bandwidth partitioning in [48]. Wang et al. [83] proposed a different model to reveal the relationship between various bandwidth partitioning schemes and system objectives. Kaseridis et al. [34] balanced bandwidth requirements among chips through workload migration. Ebrahimi et al. [13] proposed Fairness via Source Throttling (FST) to enable fair sharing of the memory. FST throttles cores causing unfairness by limiting the memory requests from the cores. FST is similar to WBP in certain ways. FST achieves fairness by throttling the most aggressive thread (with the smallest slowdown). WBP partitions memory bandwidth such that threads with higher bandwidth utility get more allocation, while threads with lower utility get less bandwidth share. FST throttles aggressive threads (with small slowdown), while WBP "throttles" less efficient threads (with small bandwidth utility). No existing research tries to incorporate writeback information in bandwidth partitioning decisions for non-volatile memory. The techniques proposed by Liu et al. [47] are the most related to ours. Our work differs in two aspects. First, we study partitioning of PCM device bandwidth which is the performance bottleneck in non-volatile memory. Second, our proposal takes into account writeback information which we show to be important to bandwidth partitioning.

#### 2.4 COORDINATED CACHE AND BANDWIDTH PARTITIONING

Bitirgen et al. [2] proposed a global resource manager that uses Artificial Neural Networks (ANNs) to manage the allocation of shared cache capacity and off-chip bandwidth. The study showed that coordinated cache and bandwidth partitioning can outperform unmanaged cache and bandwidth

Figure 4: Hybrid Main Memory Architecture

partitioning. As ANN is a black box optimizer, fundamental insights of how cache and bandwidth partitioning interact remain undiscovered. Also, Bitirgen et al. [2] did not consider the unique asymmetry property of non-volatile memory.

#### 2.5 NON-VOLATILE MAIN MEMORY ARCHITECTURES

To mitigate the shortcomings of non-volatile memory, many researchers propose to add an extra cache layer in front of the non-volatile memory [42, 17, 64]. This cache layer can be used in two ways. It can cache clean and dirty blocks for the memory. It could also be used as a write cache to store dirty blocks. The architecture that we study applies the first method because it benefits both read and write accesses, while the latter approach benefits only writes.

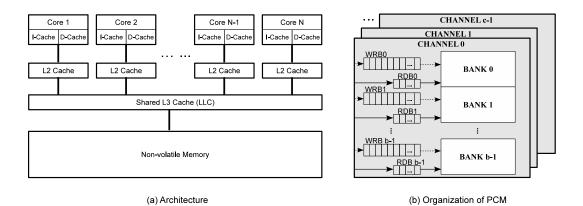

Figure 4(a) shows the main memory architecture that we consider throughout the thesis. Memory operations issued by the CPU are serviced by private L1 and L2 caches. Misses to the L2 cache, as well as writebacks from the L2 cache, are sent to the shared L3 cache, which is the lastlevel cache. The LLC works as a traditional write-allocate cache with a write-back policy (to the non-volatile memory). That is, when a modified cache line is evicted from the LLC, it must be written to the memory. The LLC is beneficial to PCM main memory: by coalescing a sequence of writes to the same line in the cache, the LLC partially mitigates the negative impacts of memory writes.

The hybrid main memory architecture can benefit non-volatile memory that suffers from the disadvantages of write operations. In this thesis, we study the hybrid memory architecture using Phase Change Memory as the main memory. Figure 4(b) presents the organization of PCM main memory with c channels of b banks each. Each bank has a r-entry read buffer (RDB) and a w-entry write buffer (WRB) for pending requests. When a writeback of a cache line from the LLC occurs, a write request is sent to the PCM, which is queued at a write buffer. The application progresses without delay if the write buffer has available entries since the writebacks are not on the critical path. However, the application stalls when the write buffer is full and cannot accept the request.

#### 3.0 CACHE PARTITIONING USING WRITEBACK INFORMATION

#### 3.1 MOTIVATION FOR WRITEBACK-AWARE CACHE PARTITIONING

Efficiently using the last-level cache (LLC) is crucial to improve system performance. For DRAM systems, Qureshi and Patt show that a reduction in LLC miss rate correlates with an improvement in IPC [63]. In their work, they classify applications as low utility, high utility and saturating utility depending on whether and how much an application benefits from a larger cache. A low-overhead circuit named UMON is introduced to monitor the utility information of each application. They propose Utility-based Cache Partitioning (UCP) to partition the LLC in a way that applications with high utility are given more cache quota, while applications with low utility get a small portion of the LLC. In this way, UCP outperforms LRU.

For hybrid main memory, however, reducing miss rate is insufficient to achieve high system performance. Reducing the number of LLC writebacks is also important due to the asymmetric property of non-volatile memory. In a hybrid memory architecture, memory writes are much slower than reads, and the memory write bandwidth is much lower than read bandwidth. These characteristics make it likely that the write buffers will become congested. Once the write buffers are full, the application stalls when a writeback from the LLC occurs. In this case, a writeback is more harmful than a cache miss because a memory write is much slower than a read.

Writebacks can also negatively affect memory lifetime and energy consumption. Non-volatile memory, such as NAND Flash, PCM and STT-RAM, has limited write endurance, and memory writes are more power hungry than reads. As a result, too many writebacks from the LLC shorten the memory lifetime and consume more energy.

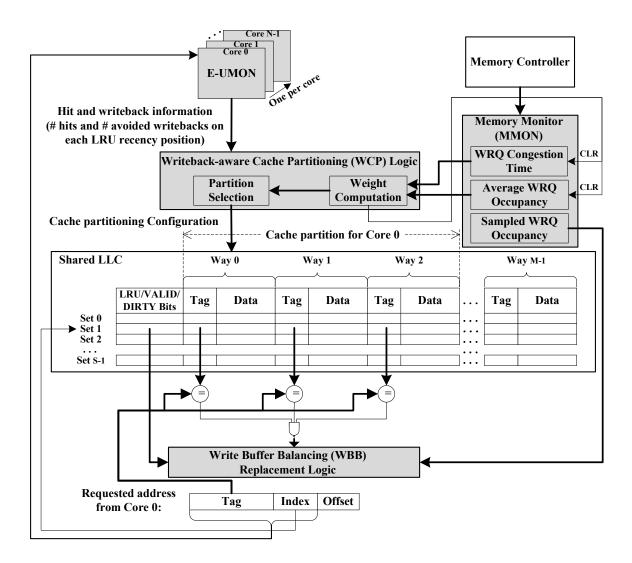

To the best of our knowledge, no existing cache partitioning and replacement scheme accounts for writeback information. Figure 5 shows the architectural overview of my approach to support

Figure 5: Architectural components to enable WCP

writeback-aware cache partitioning and replacement. It presents four major architectural components (gray colored in Figure 5), as follows. The *extended utility monitor* (E-UMON) is an extension of UMON that tracks hit and writeback information about an application. The *memory monitor* (MMON) tracks information about the write buffers of the memory devices. The *writeback-aware cache partitioning* logic uses information collected by E-UMON and MMON to select a cache partitioning configuration. It includes two modules: *partition selection* and *weight computation*. The *write buffer balancing replacement* logic uses information from MMON to pick a victim entry when a cache miss occurs. Chapter 3.2.2 describes E-UMON. Chapter 3.2.3 explains the cache partition selection scheme. Chapter 3.2.4 describes MMON and the weight computation. WBB replacement is described in Chapter 3.3.

# 3.2 WRITEBACK-AWARE CACHE PARTITIONING

Writeback information is important for efficient partitioning of the LLC in a hybrid main memory. This section describes the mechanism to track writeback information, and proposes writebackaware cache partitioning.

### 3.2.1 Monitoring of Writebacks

The writeback information that E-UMON monitors is based on the concepts of *stack distance* and *stack property*. Stack distance was introduced to study the behavior of storage hierarchies by Mattson et al. [53]. In a replacement policy that has the stack property, such as Least Recently Used (LRU) replacement, each set of a set-associative cache is viewed as a stack. All cache lines in the set are ordered by the last access time, where the top of the stack is the Most Recently Used (MRU) cache line, and the bottom is the LRU cache line. Stack distance is defined as the LRU recency position of a cache line when it is accessed again. It is critical for monitoring miss rate. An access is a hit if the cache associativity is no less than the stack distance.

Figure 6 shows a sequence of references to an M-way set-associative cache. The five accesses are to the same cache line X. Assume that a write-back policy is used by the cache. A dirty cache line X exists in the cache after time  $t_1$  when the first write access to X happens. Assume also that subsequent reads to the same cache line occur at  $t_2$ ,  $t_3$  and  $t_4$ , and another write access occurs at  $t_5$ . The stack distances for these five accesses are 4, 3, 5, 2 and 7. For instance, the cache line Xhas a LRU recency position of 3 before the read access happens at  $t_2$ , and is promoted to the top of the LRU stack after  $t_2$ . The following are some observations about the five references to the same cache line X:

If 1 ≤ M < 3, then the dirty cache line X is evicted from the cache. The eviction causes a writeback to the next level cache/memory between t₁ and t₂.</li>

| Time | Access  | LRU Stack | Stack<br>Distance | Writeback<br>Avoidance Distance |

|------|---------|-----------|-------------------|---------------------------------|

| t1   | Write X |           | 4                 | 0                               |

| t2   | Read X  |           | 3                 | 3                               |

| tз   | Read X  |           | 5                 | 5                               |

| t4   | Read X  |           | 2                 | 5                               |

| t5   | Write X |           | 7                 | 7                               |

Figure 6: An example of tracking writebacks from a cache

- If  $3 \le M < 5$ , then the writeback of cache line X happens between  $t_2$  and  $t_3$ .

- Finally, if 5 ≤ M < 7, then cache line X is written back to the next level cache/memory between t₄ and t₅.</li>

Hence, to avoid the writeback of cache line X between  $t_1$  and  $t_5$ , the cache associativity should be at least 7, which is the maximum value among 3, 5 and 7.

Here are two conclusions derived from the example. First, each write access leads to a potential writeback. A dirty line exists in the cache after a write access. The dirty line might eventually be evicted and cause a writeback. Second, a writeback is avoided if the dirty line stays in the cache until the next write access happens to the same line.

Consider a general example for an M-way set-associative cache. There is a sequence of accesses to the same cache line X,  $\{W_0, R_1, R_2, ..., R_n, W_{n+1}\}$ , including two write accesses  $(W_0$  and  $W_{n+1})$  and n read references  $(R_1, R_2, ..., R_n)$ . The stack distances for these accesses are

$SD_0, SD_1, SD_2, ..., SD_n, SD_{n+1}$ . Write access  $W_0$  causes a writeback when the dirty cache line X is evicted before the next write access  $W_1$  arrives. Cache line X will not be written back to the next level cache/memory between two write accesses  $W_0$  and  $W_1$  if and only if accesses  $R_1, R_2, ..., R_n$  and  $W_{n+1}$  are hits on the cache. In other words, a writeback of the cache line X could be saved if and only if  $M \ge max(SD_1, SD_2, ..., SD_n, SD_{n+1})$ .

The writeback avoidance distance of write access  $W_0$  to cache line X is defined as the maximum stack distance of all the accesses to cache line X which happens between  $W_0$  and the next write access to cache line X. A write access causes a writeback if the cache associativity is less than its writeback avoidance distance.

It is known that the LRU policy obeys the stack property, which means that an access that hits in a LRU managed cache containing M ways is guaranteed to also hit if the cache has more than M ways. The stack property also applies to writebacks: a write that does not cause a writeback in an M-way cache is guaranteed to also not cause a writeback in a cache with more than M ways. The reason is that all accesses between two consecutive writes are hits on a cache with more than M ways, if they are all hits on an M-way cache.

## **3.2.2** Extended Utility Monitors (E-UMON)

To make cache partitioning decisions among applications, the partitioning scheme needs to know the hit and writeback information of applications with different number of ways. Since LRU obeys the stack property, it is possible to track this information with a shadow tag array containing the same number of ways as the shared cache.

Mechanisms to monitor hit information have been described by many researchers [54, 63]. Similar to UMON [63], E-UMON monitors hit information of an application executing on core *c* through a shadow tag array and hit counters. The shadow tag array has the same associativity as the shared LLC. Each shadow tag entry has three fields: valid bit (V), tag address (TAG) and LRU bits (LRU) that track stack distance of each access. Dynamic set sampling [62] is applied to reduce the hardware overhead. Our evaluation shows that sampling 32 sets is sufficient for a cache with 2048 sets.

The shadow tag array is updated on every access to the LLC, using LRU replacement. Of

| A | lgorithm | 3.1 | Monitoring Hits |

|---|----------|-----|-----------------|

|---|----------|-----|-----------------|

parameters: i: Core id st: The accessed shadow tag entry addr: The accessed address

$\begin{array}{l} \text{if } st.TAG == GetTagAddress(addr) \text{ then} \\ st.SD \leftarrow GetLruRecencyPosition() \\ HIT^{i}_{st.SD} \leftarrow HIT^{i}_{st.SD} + 1 \\ \text{end if} \end{array}$

#### Algorithm 3.2 Monitoring Writebacks

parameters: *i*: Core id *st*: The accessed shadow tag entry *addr*: The accessed address

$\begin{array}{ll} \mbox{if $st.TAG == GetTagAddress(addr)$ then} \\ st.SD \leftarrow GetLruRecencyPosition() \\ \mbox{if $st.D == TRUE$ then} \\ st.WAD \leftarrow max(st.WAD, st.SD) \\ \mbox{end if} \\ \mbox{if the access is a write operation then} \\ AWB^i_{st.WAD} \leftarrow AWB^i_{st.WAD} + 1 \\ st.WAD \leftarrow 0 \\ \mbox{end if} \\ \mbox{else} \\ st.WAD \leftarrow 0 \\ \mbox{end if} \\ \mbox{else} \\ st.WAD \leftarrow 0 \\ \mbox{end if} \\ \end{array}$

course, E-UMON only updates the tag entries that belong to the sampled sets. E-UMON tracks the hit information through a set of counters, based on the information in the shadow tag array (see Algorithm 3.1). For an *M*-way cache, *M* counters  $HIT_0^i$ ,  $HIT_1^i$ , ...,  $HIT_{M-1}^i$  are used to get hit information.  $HIT_c^i$  is the number of additional hits when the  $c^{th}$  way is available for core *i*, where  $0 \le c \le M - 1$ . Counter  $HIT_{sd}^i$  is incremented on each hit on the shadow tag array, where sd is the stack distance.

To obtain writeback information, E-UMON adds two additional fields to each shadow tag entry: dirty bit (D) and the writeback avoidance distance (WAD). Writeback information is recorded through the avoidable writeback counters  $AWB_0^i$ ,  $AWB_1^i$ , ...,  $AWB_{M-1}^i$ , where  $AWB_c^i$  is the number of avoidable writebacks if the  $c^{th}$  way is available for  $0 \le c \le M - 1$  (see Algorithm 3.2). The writeback avoidance distance for each write access is tracked through the WAD field of the shadow tag entry. Initially, the WAD fields of all shadow tag entries are initialized to 0. Once the shadow tag entry is modified (i.e., the dirty bit D has been set), WAD records the maximum stack distance of the following accesses to the entry until the next write occurs. When a write hit happens, counter  $AWB_{wad}^i$  is incremented, where wad is the writeback avoidance distance. The WAD field is reset after each write hit, and starts tracking the writeback avoidance distance of the newly-arrived write access.

With the knowledge of hit and writeback information, the partitioning scheme can compute the

| Optimization Objective | Partitioning Weights                                                                                                  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Cache Miss Rate [63]   | $w_{Hit} = 1, w_{Awb} = 0$                                                                                            |

| Memory Dynamic Energy  | $w_{Hit}: w_{Awb} = E_R: E_W,$<br>where $E_R$ and $E_W$ are energy consumption of a<br>memory read and write request. |

| Memory Writes          | $w_{Hit} = 0, w_{Awb} = 1$                                                                                            |

Table 2: Partitioning weights for different optimization objectives

number of hits  $(hits_{M'})$  and avoidable writebacks  $(avoidablewritebacks_{M'})$  for an M'-way cache, where M' < M, as follows.

$$hits_{M'} = \sum_{c=0}^{M'-1} HIT_c^i$$

(3.1)

$$avoidable write backs_{M'} = \sum_{c=0}^{M'-1} AWB_c^i$$

(3.2)

## 3.2.3 Cache Partition Selection

Let  $\pi_i$  be the number of the ways used by core *i*. For cache way partitioning,  $\bar{\pi} = {\pi_0, ..., \pi_{N-1}}$  is a valid partition for a system with *N* cores and an *M*-way shared LLC, when it satisfies:

$$\sum_{i=0}^{N-1} \pi_i = M, \text{ where } 1 \le \pi_i \le M - N + 1.$$

(3.3)

Based on the hit and avoidable writeback counters in E-UMON, *Writeback-aware Cache Partitioning* (WCP) tries to select a valid partition that maximizes a weighted sum of the number of misses and the number of writebacks:

$$\sum_{i=0}^{N-1} \sum_{c=0}^{\pi_i - 1} (w_{Hit} \cdot HIT_c^i + w_{Awb} \cdot AWB_c^i)$$

(3.4)

Two parameters  $w_{Hit}$  and  $w_{Awb}$  are *partitioning weights* assigned to hit counters and writeback counters. These two parameters determine the relative importance of reducing misses and minimizing writebacks. The suitable partitioning weights differ for various system optimization objectives. Table 2 gives the partitioning weights for three optimization objectives. UCP was proposed to improve the system performance of a DRAM system by reducing the overall LLC miss rate [63]. UCP is a specific case of WCP with  $w_{Hit} = 1$  and  $w_{Awb} = 0$ . If the dynamic power efficiency of the memory is the criteria, then the partitioning weights should satisfy  $w_{Hit} : w_{Awb} = E_R : E_W$ , where  $E_R$  and  $E_W$  are energy consumption of a memory read and write request. The reason is that a memory read is avoided for a hit, while a memory write is saved for each avoided writeback. If reduction of memory writes is the objective, then  $w_{Hit} = 0$  and  $w_{Awb} = 1$  should be used.

## 3.2.4 Weight Computation for Performance Optimization