# A SELF-ORGANIZING WIRELESS SENSOR NETWORK AND DISTRIBUTED COMPUTING ENGINE FOR COMMODITY AND FUTURE PALMTOP COMPUTERS

by

## Haifeng Xu

B.S., Zhejiang University, 2009M.S., University of Pittsburgh, 2012

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Pittsburgh

2015

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Haifeng Xu

It was defended on

June 25th 2015

and approved by

Alex K. Jones, PhD, Associate Professor, Department of Electrical and Computer

Engineering

Hai Li, PhD, Assistant Professor, Department of Electrical and Computer Engineering

Yiran Chen, PhD, Associate Professor, Department of Electrical and Computer

Engineering

Ervin Sejdic, PhD, Assistant Professor, Department of Electrical and Computer

Engineering

Melissa M. Bilec, PhD, Associate Professor, Department of Civil Engineering

Dissertation Director: Alex K. Jones, PhD, Associate Professor, Department of Electrical and Computer Engineering

## A SELF-ORGANIZING WIRELESS SENSOR NETWORK AND DISTRIBUTED COMPUTING ENGINE FOR COMMODITY AND FUTURE PALMTOP COMPUTERS

Haifeng Xu, PhD

University of Pittsburgh, 2015

The embedded class processors found in commodity palmtop computers continue to become increasingly capable while retaining an energy-efficient footprint. Palmtop computers themselves, including smartphones and tablets, provide a small form factor system integrating wireless communication and non-volatile storage with these energy-efficient processors. Also, various wireless connectivity functions on mobile devices provide new opportunities in designing more flexible, smarter wireless sensor networks (WSNs), and utilizing the computation power in a way we could never imagine before. In this dissertation, I present a WSN concept for current and future generation tablet devices. My contributions include developments at the system level, architecture level, and collaborative design between different layers of the system. At the system level, I developed Ocelot, a grid-like computing environment for palmtop computers in place of traditional workstation or server class machines to compute highly parallel light to medium-weight tasks in an energy efficient manner. Additionally, I developed Lynx, a self-organizing wireless sensor network, which is a further step taken in exploiting the potential of palmtop computers. At the architecture level, to increase the storage capacity of future palmtop computers, I explore the use of a new storage class magnetic memory, Racetrack Memory (RM), throughout the memory hierarchy. Thus, I developed FusedCache, a naturally inclusive, dual-level private cache design for RM that provides fast uniform access at one level, and non-uniform access at the next, which allows RM to be effective as close to the processor as an L1 cache. For higher levels of the memory hierarchy such as the last level cache, I propose a Multilane Racetrack Cache (MRC), an RM last level cache design utilizing lightweight compression combined with independent shifting. MRCs allow cache lines mapped to the same Racetrack structure to be accessed in parallel when compressed, mitigating potential shifting stalls in an RM cache. Finally, leveraging the lightweight compression from MRC and the need for efficient communication in Lynx, I present a cross-level design combining memory-level lightweight compression with networklevel packet transfer, together with a technique called Source-Aware Layout Reorganization (SALR) to increase the compressibility of sensor data.

## TABLE OF CONTENTS

| PR  | PREFACE |                                                                             |    |

|-----|---------|-----------------------------------------------------------------------------|----|

| 1.0 | IN'     | TRODUCTION                                                                  | 1  |

|     | 1.1     | Motivations                                                                 | 1  |

|     | 1.2     | Problem Statement                                                           | 3  |

|     | 1.3     | Dissertation Overview                                                       | 4  |

|     |         | 1.3.1 Application Level: Distributed Computing in a Wireless Sensor Network | 4  |

|     |         | 1.3.2 Architecture Level: Cache Designs with Emerging Racetrack Memory      | 7  |

|     |         | 1.3.3 Cross-Level: A Memory Network Co-design with Compression              | 11 |

|     | 1.4     | Contributions                                                               | 12 |

|     | 1.5     | Dissertation Structure                                                      | 14 |

| 2.0 | PR      | IOR ART                                                                     | 16 |

|     | 2.1     | BOINC and Distributed Computing                                             | 16 |

|     | 2.2     | Wireless Sensor Networks and Mobile Connectivity                            | 17 |

|     |         | 2.2.1 Physical Layer Communication                                          | 18 |

|     |         | 2.2.2 System-level Management and Optimization                              | 18 |

|     |         | 2.2.3 Self-Organizing Network                                               | 19 |

|     | 2.3     | Architecting with Racetrack Memory                                          | 20 |

|     | 2.4     | Efficient data transfer in WSN                                              | 22 |

|     |         | 2.4.1 Data Compression                                                      | 22 |

|     |         | 2.4.2 Compression in WSN                                                    | 23 |

| 3.0 | 00      | ELOT: A WIRELESS SENSOR NETWORK AND COMPUTING                               |    |

|     | EN      | GINE WITH COMMODITY PALMTOP COMPUTERS                                       | 25 |

|     | 3.1                                                                                                  | Implementation Overview                                                                                                                                                                                                                                                                                                                                        | 25                                                                                                                                 |

|-----|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|     | 3.2                                                                                                  | Ocelot Basics                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                                                 |

|     | 3.3                                                                                                  | Ocelot Servers                                                                                                                                                                                                                                                                                                                                                 | 28                                                                                                                                 |

|     |                                                                                                      | 3.3.1 Database Server                                                                                                                                                                                                                                                                                                                                          | 28                                                                                                                                 |

|     |                                                                                                      | 3.3.2 Web Server                                                                                                                                                                                                                                                                                                                                               | 28                                                                                                                                 |

|     |                                                                                                      | 3.3.3 Scheduling Server                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                                 |

|     |                                                                                                      | 3.3.4 Push Server                                                                                                                                                                                                                                                                                                                                              | 29                                                                                                                                 |

|     |                                                                                                      | 3.3.5 Additional Servers                                                                                                                                                                                                                                                                                                                                       | 29                                                                                                                                 |

|     | 3.4                                                                                                  | Ocelot Client                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                                                                 |

|     | 3.5                                                                                                  | Ocelot Dashboard                                                                                                                                                                                                                                                                                                                                               | 34                                                                                                                                 |

|     | 3.6                                                                                                  | Security and Limitations                                                                                                                                                                                                                                                                                                                                       | 35                                                                                                                                 |

|     | 3.7                                                                                                  | Case Study: Dynamic Life Cycle Assessment of a LEED Silver Building                                                                                                                                                                                                                                                                                            | 36                                                                                                                                 |

|     |                                                                                                      | 3.7.1 Energy saving                                                                                                                                                                                                                                                                                                                                            | 38                                                                                                                                 |

|     |                                                                                                      | 3.7.2 Intra-device parallelism                                                                                                                                                                                                                                                                                                                                 | 41                                                                                                                                 |

|     |                                                                                                      | 3.7.3 Inter-device parallelism                                                                                                                                                                                                                                                                                                                                 | 43                                                                                                                                 |

|     |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                    |

| 4.0 | LY                                                                                                   | NX: A SELF-ORGANIZING WSN PLATFORM LEVERAGING                                                                                                                                                                                                                                                                                                                  |                                                                                                                                    |

| 4.0 |                                                                                                      | NX: A SELF-ORGANIZING WSN PLATFORM LEVERAGING<br>MMODITY HARDWARE                                                                                                                                                                                                                                                                                              | 44                                                                                                                                 |

| 4.0 | CO                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                | 44<br>44                                                                                                                           |

| 4.0 | <b>CO</b><br>4.1                                                                                     | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                    |

| 4.0 | CO<br>4.1<br>4.2                                                                                     | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | 44                                                                                                                                 |

| 4.0 | CO<br>4.1<br>4.2<br>4.3                                                                              | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | 44<br>44                                                                                                                           |

| 4.0 | CO<br>4.1<br>4.2<br>4.3<br>4.4                                                                       | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | 44<br>44<br>45                                                                                                                     |

| 4.0 | <ul> <li>CO</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>              | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | 44<br>44<br>45<br>46                                                                                                               |

| 4.0 | <ul> <li>CO</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | 44<br>44<br>45<br>46<br>48                                                                                                         |

| 4.0 | <ul> <li>CO</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | 44<br>45<br>46<br>48<br>51                                                                                                         |

| 4.0 | <ul> <li>CO</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | MMMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                              | 44<br>45<br>46<br>48<br>51<br>51                                                                                                   |

| 4.0 | <ul> <li>CO</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | <ul> <li>44</li> <li>44</li> <li>45</li> <li>46</li> <li>48</li> <li>51</li> <li>51</li> <li>52</li> </ul>                         |

| 4.0 | <ul> <li>CO</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | MMODITY HARDWARE                                                                                                                                                                                                                                                                                                                                               | <ul> <li>44</li> <li>44</li> <li>45</li> <li>46</li> <li>48</li> <li>51</li> <li>51</li> <li>52</li> <li>53</li> </ul>             |

| 4.0 | <ul> <li>CO</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul> | MMODITY HARDWARE         Lynx Basics         Connectivity Choice         Sensor Integration         Maintenance of Peer and Link States         Multi-hop Routing         Scalability and Limitations         Evaluation of Lynx         4.7.1 File Transfer Time         4.7.2 File Transfer Energy Consumption         4.7.3 Miscellaneous Energy Components | <ul> <li>44</li> <li>44</li> <li>45</li> <li>46</li> <li>48</li> <li>51</li> <li>51</li> <li>52</li> <li>53</li> <li>56</li> </ul> |

| 5.0 | FUSEDCACHE: A NATURALLY INCLUSIVE, RACETRACK MEM                                                     | -    |

|-----|------------------------------------------------------------------------------------------------------|------|

|     | ORY, DUAL-LEVEL PRIVATE CACHE                                                                        | . 64 |

|     | 5.1 FusedCache                                                                                       | . 64 |

|     | 5.1.1 Mapping and Addressing                                                                         | . 64 |

|     | 5.1.2 Handling cache hits/misses                                                                     | . 67 |

|     | 5.1.2.1 L1 hits                                                                                      | . 68 |

|     | 5.1.2.2 L1 misses - L2 hits                                                                          | . 68 |

|     | 5.1.2.3 L2 misses                                                                                    | . 70 |

|     | 5.1.3 Hybrid associativity                                                                           | . 72 |

|     | 5.2 Experimental Methodology                                                                         | . 73 |

|     | 5.3 Results                                                                                          | . 75 |

|     | 5.3.1 Performance                                                                                    | . 76 |

|     | 5.3.2 Energy                                                                                         | . 78 |

|     | 5.3.3 Sensitivity study                                                                              | . 78 |

|     | 5.3.3.1 L1 capacity                                                                                  | . 79 |

|     | 5.3.3.2 L2/L1 capacity ratio $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | . 81 |

|     | 5.3.3.3 Associativity                                                                                | . 82 |

| 6.0 | MULTILANE RACETRACK CACHES: IMPROVING EFFICIENCY                                                     | 7    |

|     | THROUGH COMPRESSION AND INDEPENDENT SHIFTING .                                                       | . 84 |

|     | 6.1 MRC Last Level Cache Design                                                                      | . 84 |

|     | 6.1.1 Fundamental Structure                                                                          | . 84 |

|     | 6.1.2 Memory In-place Compression                                                                    | . 87 |

|     | 6.1.3 Independent Shifting                                                                           | . 90 |

|     | 6.1.4 Skewed Alignment                                                                               | . 90 |

|     | 6.2 Experimental Methodology                                                                         | . 91 |

|     | 6.3 Results                                                                                          | . 93 |

|     | 6.3.1 Performance                                                                                    |      |

|     | 6.3.2 Energy                                                                                         | . 96 |

| 7.0 | IMPROVING EFFICIENCY OF WIRELESS SENSOR NETWORKS                                                     |      |

|     | THROUGH LIGHTWEIGHT IN-MEMORY COMPRESSION                                                            | . 98 |

| 7.1 WSN Memory and Network Co-Design for Low-Overhead Compressed Com- |     |

|-----------------------------------------------------------------------|-----|

| munication                                                            | 98  |

| 7.1.1 Lightweight In-place Compression                                | 98  |

| 7.1.2 Source-Aware Layout Reorganization (SALR)                       | 101 |

| 7.1.3 Memory Network Compression Co-Design                            | 104 |

| 7.2 Experiments and Results                                           | 107 |

| 7.2.1 Impact of SALR                                                  | 108 |

| 7.2.2 Compressed transfer in a WSN                                    | 110 |

| 8.0 CONCLUSION AND FUTURE WORK                                        | 113 |

| 8.1 Conclusion                                                        | 113 |

| 8.2 Future Work                                                       | 116 |

| 8.2.1 Future Work in Environmental Impact Evaluation                  | 116 |

| 8.2.2 Future Work in WSN System Improvements                          | 116 |

| BIBLIOGRAPHY                                                          | 118 |

### LIST OF TABLES

| 1  | Major specs of devices used in the experiments                                    | 37  |

|----|-----------------------------------------------------------------------------------|-----|

| 2  | Energy Consumption of Miscellaneous Processes                                     | 56  |

| 3  | Latency & energy parameters                                                       | 74  |

| 4  | Data array read latency breakdown                                                 | 75  |

| 5  | Benchmarks (L1 MPKI)                                                              | 76  |

| 6  | 14 compression schemes (including uncompressed) ordered by sizes after com-       |     |

|    | pressing a 64 byte cache line                                                     | 87  |

| 7  | Global architecture parameters                                                    | 92  |

| 8  | LLC parameters of different memory technologies                                   | 93  |

| 9  | 8 compression schemes (including uncompressed scheme) ordered by sizes after      |     |

|    | compressing a 64-byte data block (smaller compressed sizes have higher priories). | 101 |

| 10 | ZIP compression and decompression time on a Nexus 7 (2012) tablet $\ldots$        | 111 |

## LIST OF FIGURES

| 1  | Global Market Share of Personal Computing Platforms by Operating System          |    |

|----|----------------------------------------------------------------------------------|----|

|    | from 1975 to 2012                                                                | 2  |

| 2  | Overview of this dissertation work                                               | 4  |

| 3  | Overview of the Ocelot system                                                    | 5  |

| 4  | A Lynx wireless sensor network illustration.                                     | 7  |

| 5  | Planar Racetrack memory.                                                         | 8  |

| 6  | A schematic of Racetrack with three-dimensional structure                        | 10 |

| 7  | Five number summary of NOAA 1981-2010 wind speed normals of select eight         |    |

|    | U.S. stations: (a) hourly wind speed; (b) wind speed difference (absolute value) |    |

|    | between consecutive hours.                                                       | 12 |

| 8  | Ocelot client apps on both Android and iOS platforms.                            | 32 |

| 9  | Ocelot dashboard.                                                                | 34 |

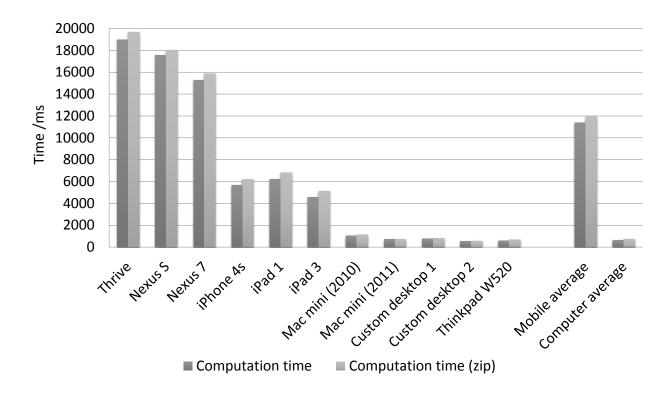

| 10 | Average computation time per task                                                | 38 |

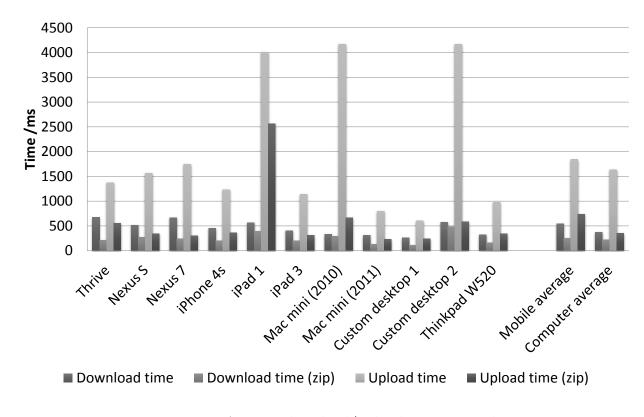

| 11 | Average download/upload time per task                                            | 39 |

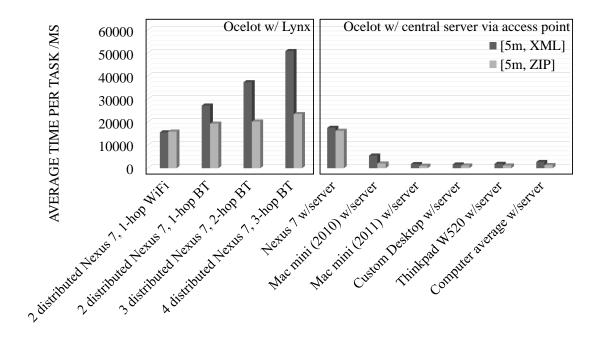

| 12 | Average total time per task                                                      | 40 |

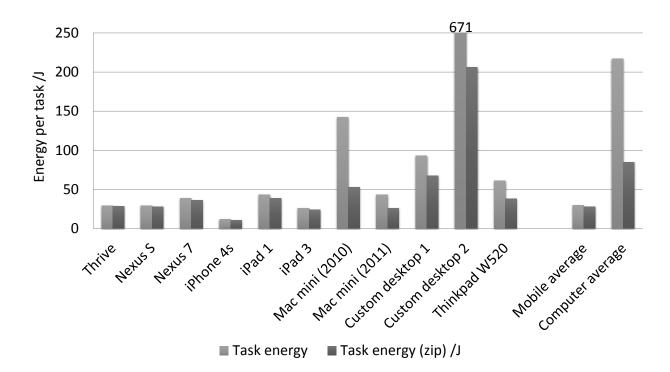

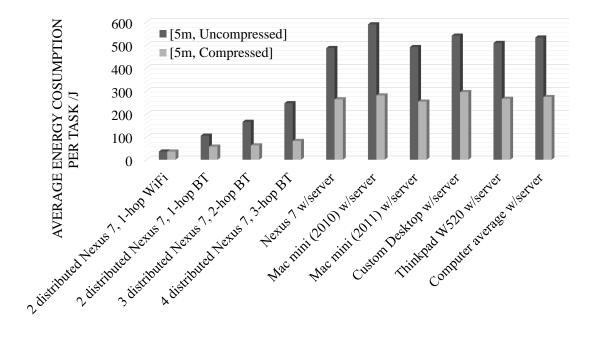

| 13 | Energy consumption per task                                                      | 41 |

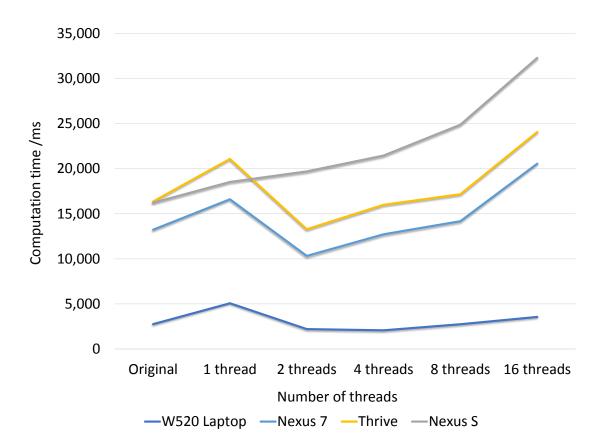

| 14 | Task computation time of intra-device multithreaded execution                    | 42 |

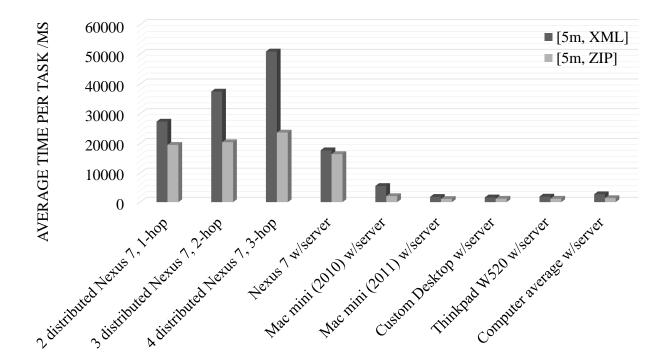

| 15 | Task completion speedups of inter-device parallel execution                      | 43 |

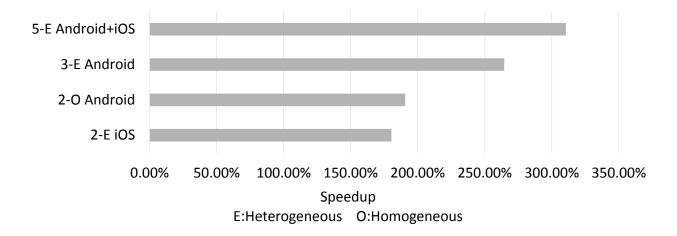

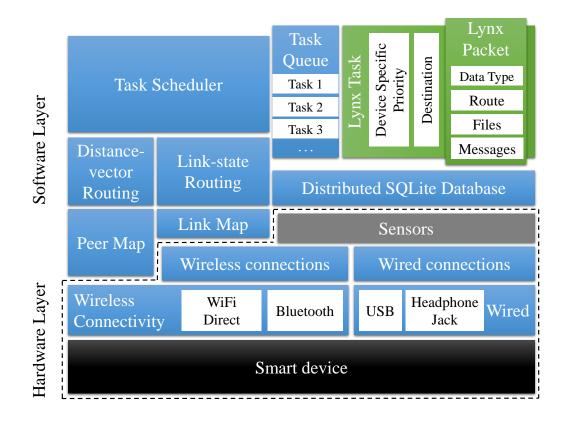

| 16 | The structure of a Lynx node                                                     | 45 |

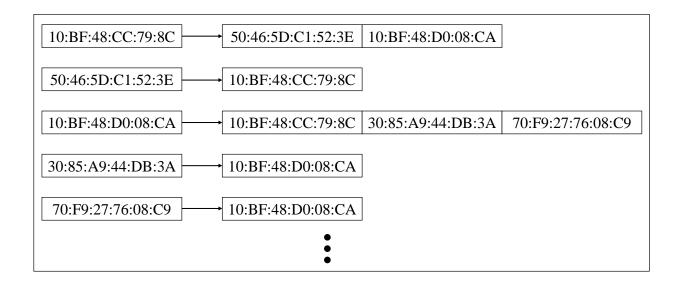

| 17 | A Lynx peer map illustration. MAC addresses are used in Lynx network to          |    |

|    | uniquely identify devices.                                                       | 47 |

| 18 | Sending a multi-hop message                                                      | 50 |

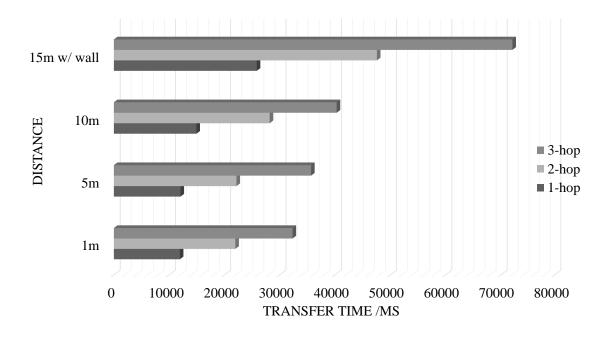

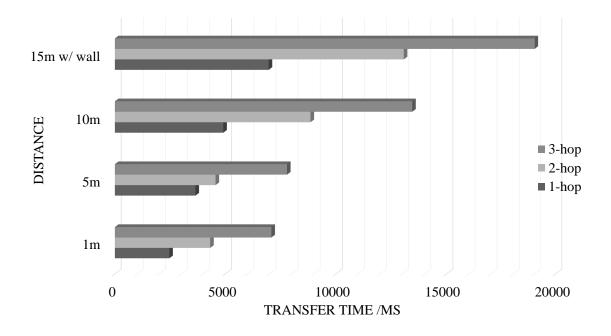

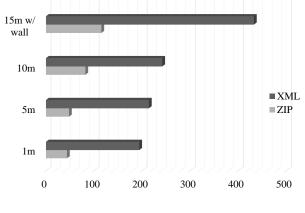

| 19 | Average XML file transfer time                                                       | 52 |

|----|--------------------------------------------------------------------------------------|----|

| 20 | Average Compressed ZIP file transfer time                                            | 53 |

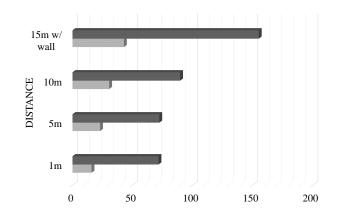

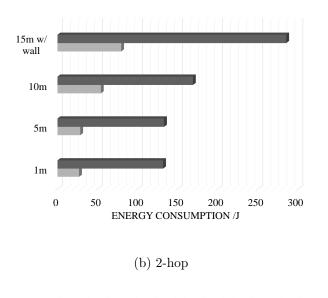

| 21 | Average energy consumption of transferring XML and ZIP files                         | 54 |

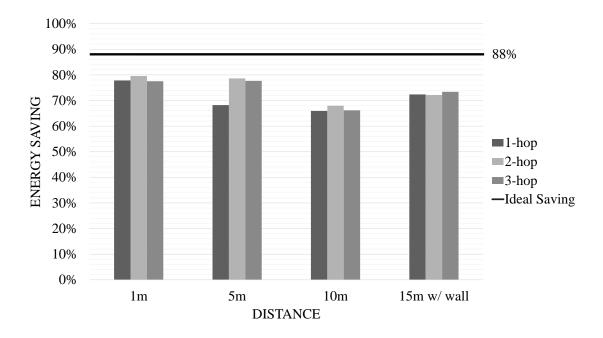

| 22 | Energy savings by data compression in different scenarios                            | 55 |

| 23 | Average time of transferring a 189,006 byte XML input file, with different           |    |

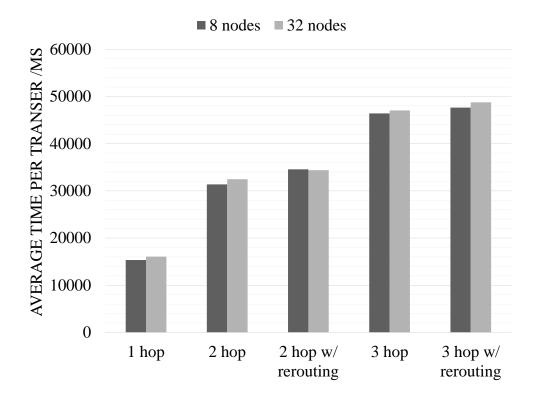

|    | numbers of hops per route, w/ and w/o rerouting. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 57 |

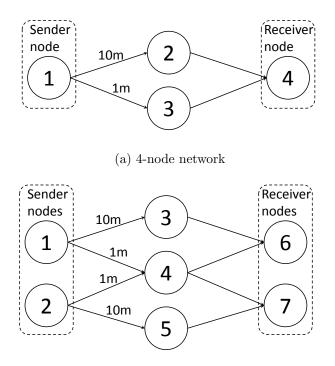

| 24 | Two network topologies used for testing the routing algorithm considering QoS.       |    |

|    | Edges indicate established connections; arrows indicate data transfer directions     | 59 |

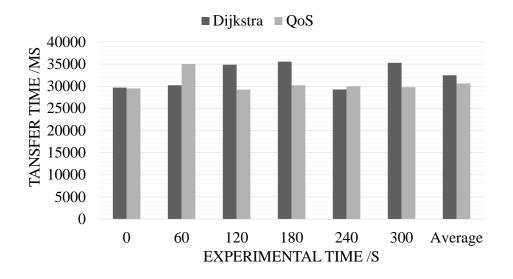

| 25 | Transfer time comparison of two routing algorithms in the 4-node network             | 60 |

| 26 | Transfer time comparison of two routing algorithms in the 7-node network             | 60 |

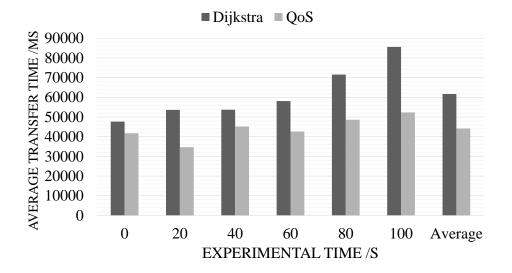

| 27 | Average execution time per task                                                      | 62 |

| 28 | Average energy consumption per task                                                  | 62 |

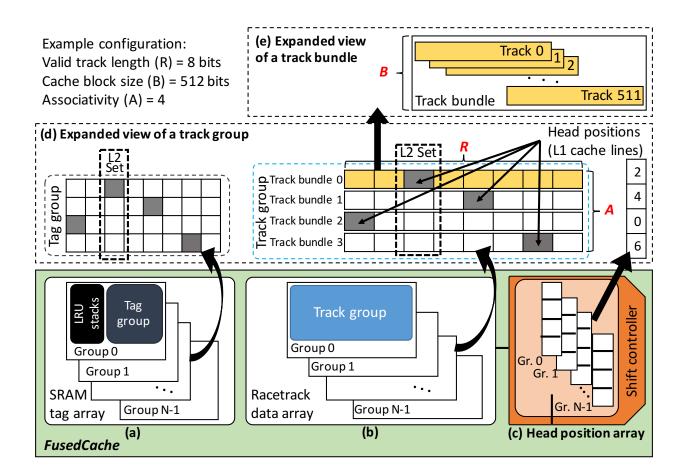

| 29 | Overview of the FusedCache structure including an example group with pa-             |    |

|    | rameters $R=8$ , $A=4$ . $B=512$                                                     | 65 |

| 30 | FusedCache addressing and indexing.                                                  | 66 |

| 31 | An L1 hit example.                                                                   | 68 |

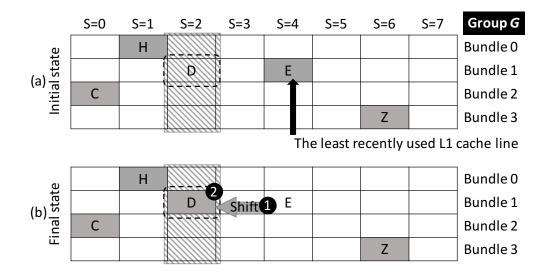

| 32 | An L2 hit example w/o swap. The "Shift" arrow illustrates the relative position      |    |

|    | change of the access port. In actual RM, domains shift to the access port, which     |    |

|    | is logically equivalent.                                                             | 69 |

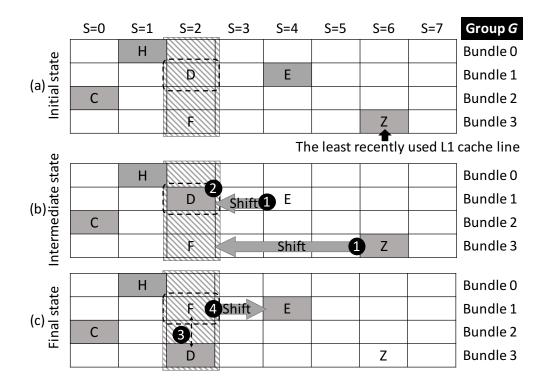

| 33 | An L2 hit example w/ swap.                                                           | 70 |

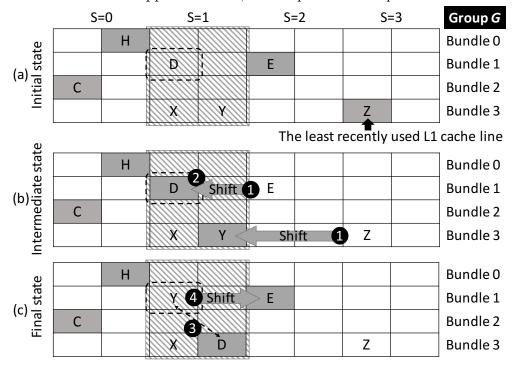

| 34 | An hybrid associativity mapping example                                              | 72 |

| 35 | An L2 hit example w/ swap in a hybrid associativity configuration                    | 73 |

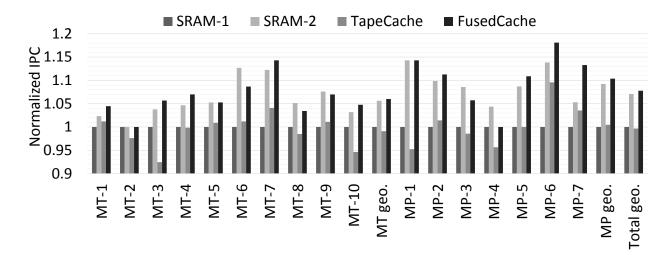

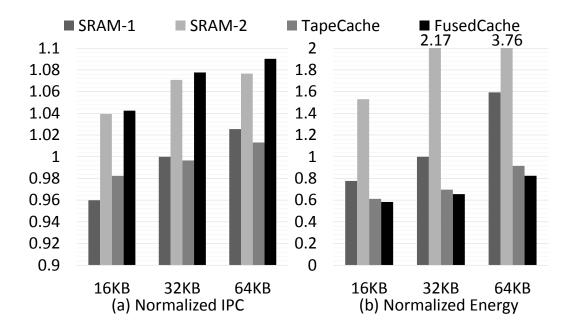

| 36 | Performance comparison of four cache schemes.                                        | 77 |

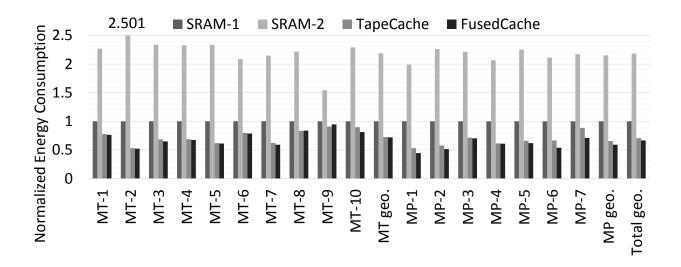

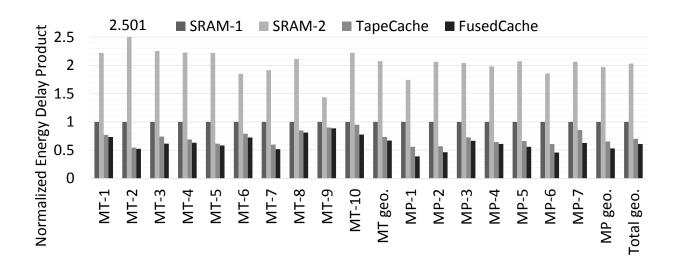

| 37 | Energy Consumption comparison of four cache schemes.                                 | 79 |

| 38 | Energy Delay Product (EDP) comparison of four cache schemes.                         | 79 |

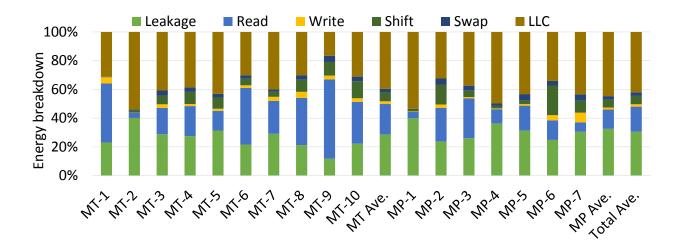

| 39 | Energy Breakdown of FusedCache scheme (LLC indicates overall energy con-             |    |

|    | sumption of the last level cache)                                                    | 80 |

| 40 | Average IPC and energy consumption: Constant $L2/L1$ capacity ratio with             |    |

|    | various L1 cache capacities.                                                         | 81 |

| 41 | Average IPC and energy consumption: constant L1 capacity and different                                                               |     |

|----|--------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | L2/L1 capacity ratios                                                                                                                | 82  |

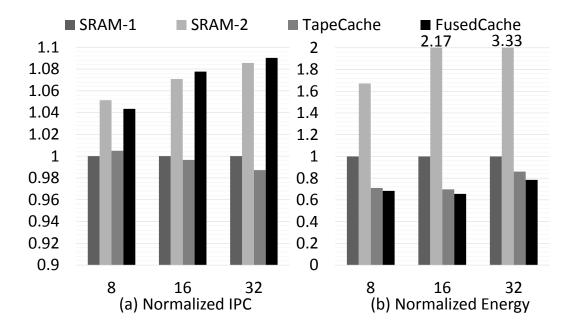

| 42 | Average IPC and energy consumption: constant L1 capacity and L2/L1 ca-                                                               |     |

|    | pacity ratios and different L1, L2 associativity combinations.                                                                       | 83  |

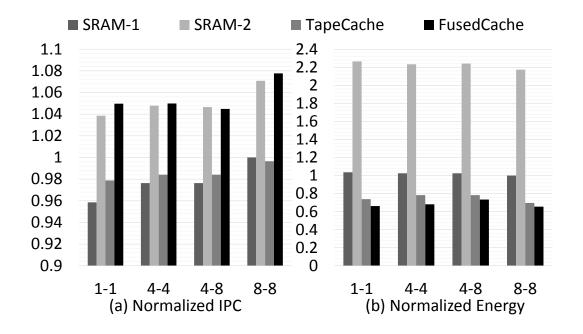

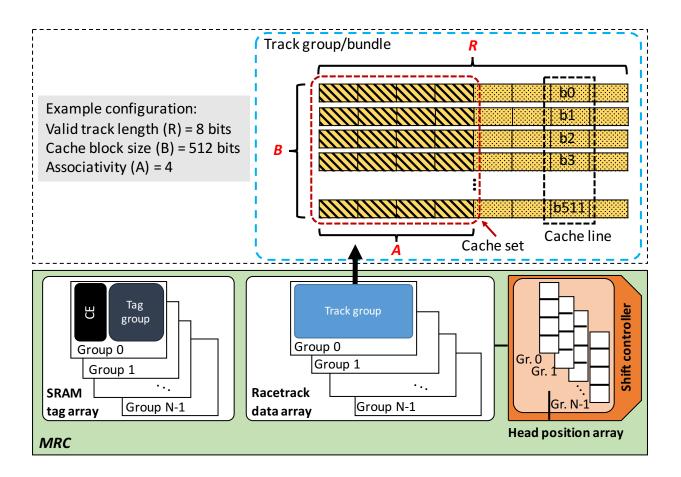

| 43 | Overview of the MRC structure including an example group with parameters                                                             |     |

|    | $R=8, A=4. B=512. \dots \dots$ | 85  |

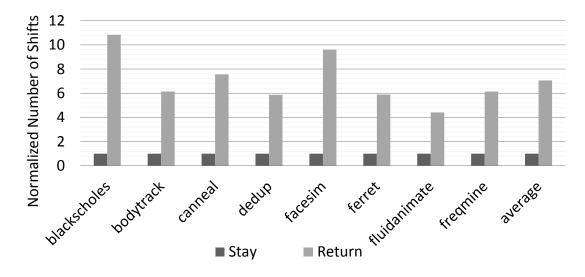

| 44 | Number of shifts for a 1MB 1P1T Racetrack LLC with track length of 16 (de-                                                           |     |

|    | tailed parameters from Tables 7 and 8) with <i>Return</i> shifting policy normalized                                                 |     |

|    | to the same design with <i>Stay</i> shifting policy.                                                                                 | 86  |

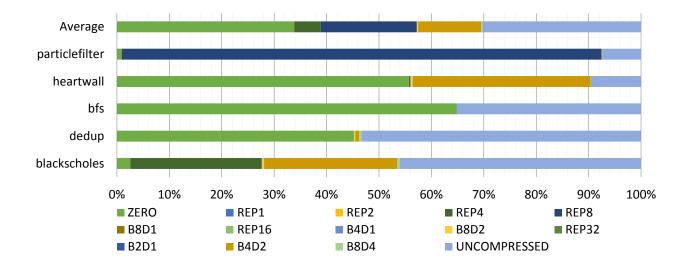

| 45 | Breakdown of occurrences of 14 compression schemes (including uncompressed)                                                          |     |

|    | in 5 applications with small input sets                                                                                              | 88  |

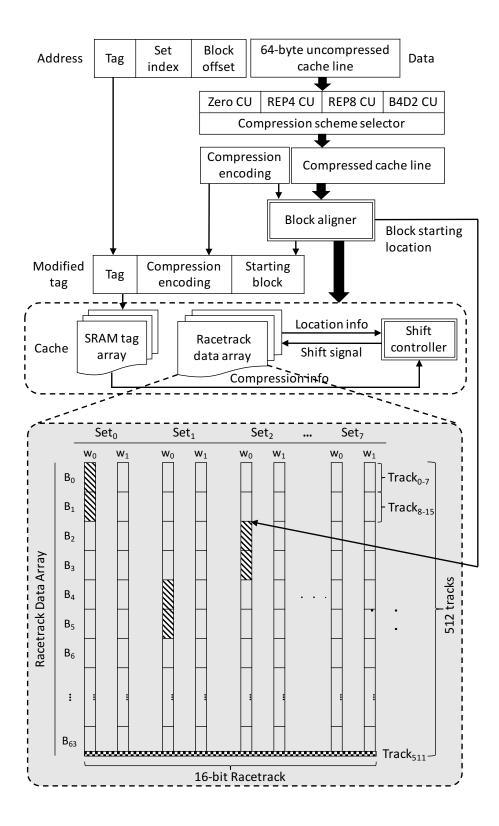

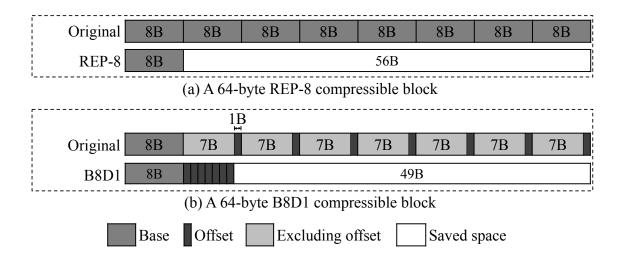

| 46 | Operational flow of a write access w/ compression to the Racetrack cache (top)                                                       |     |

|    | and logical view of a 1KB subarray of n-way (in this case, $n = 2$ ) set-associative                                                 |     |

|    | MRC cache data array with 64-byte block size (bottom)                                                                                | 89  |

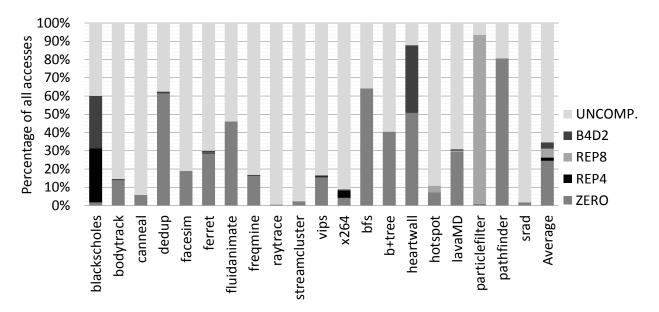

| 47 | Breakdown of occurrences of 5 compression schemes (including blocks that                                                             |     |

|    | cannot be compressed) in executing one billion instructions in 20 different                                                          |     |

|    | applications.                                                                                                                        | 94  |

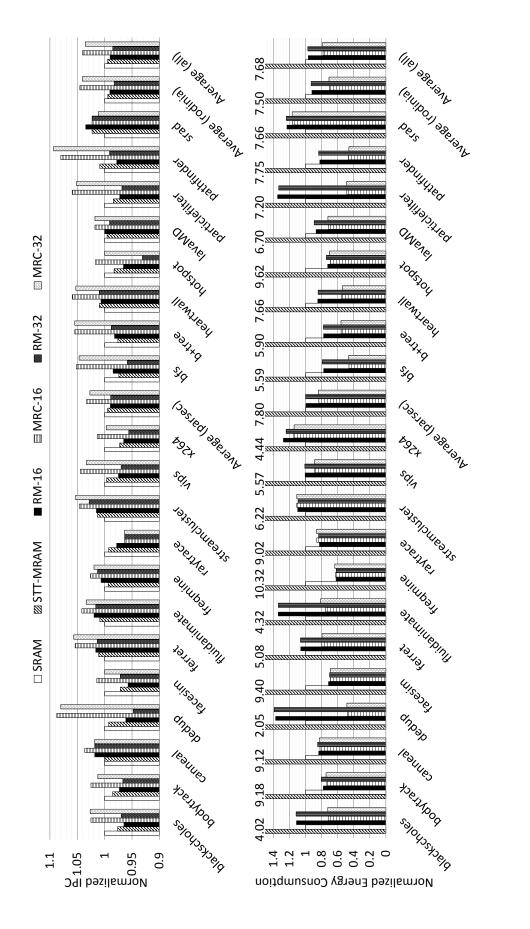

| 48 | Performance (top) and energy consumption (bottom) comparison of 6 LLC                                                                |     |

|    | schemes: SRAM, STT-MRAM, RM w/ 16-bit long track, MRC w/ 16-bit                                                                      |     |

|    | long track, RM w/ 32-bit long track, MRC w/ 32-bit long track. For each                                                              |     |

|    | application, IPCs are normalized the SRAM scheme, energy consumption is                                                              |     |

|    | normalized to the STT-MRAM scheme.                                                                                                   | 95  |

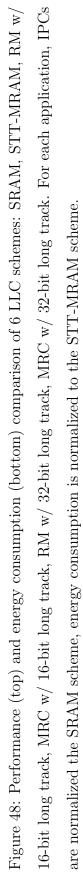

| 49 | Energy breakdown of a 1MB Racetrack LLC w/ compression (16-bit long track,                                                           |     |

|    | 64 program threads).                                                                                                                 | 96  |

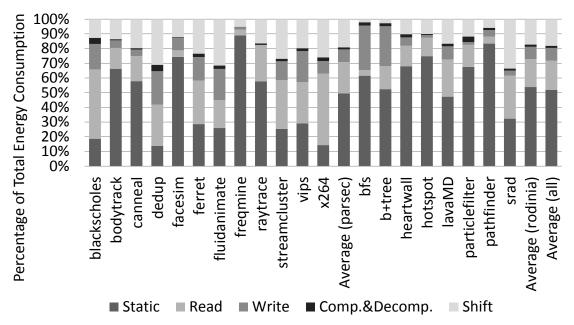

| 50 | Before and after comparison of compression schemes: (a) REP-8 (b) B8D1. $\ .$                                                        | 99  |

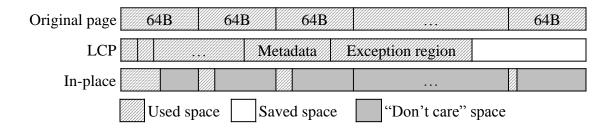

| 51 | Comparison of space saving compression with LCP with in-place compression                                                            |     |

|    | for a memory page.                                                                                                                   | 100 |

| 52 | Original structure of a 16 workunit structure                                                                                        | 103 |

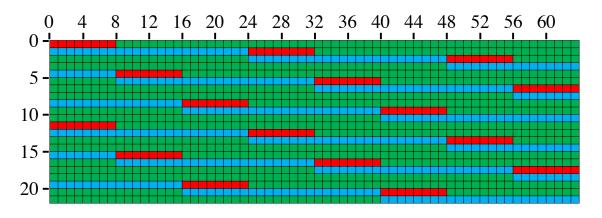

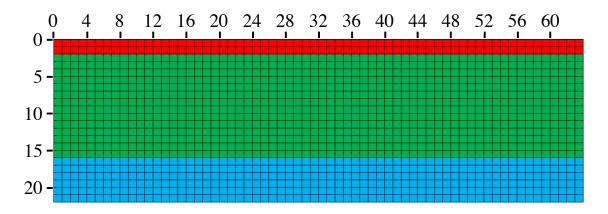

| 53 | Original layout (byte map) of a 16 workunit packet.                                                                                  | 103 |

| 54 | Reorganized structure of a 16 workunit structure                                                                                     | 104 |

| 55 | Reorganized layout (byte map) of a 16 workunit packet                             | 104 |

|----|-----------------------------------------------------------------------------------|-----|

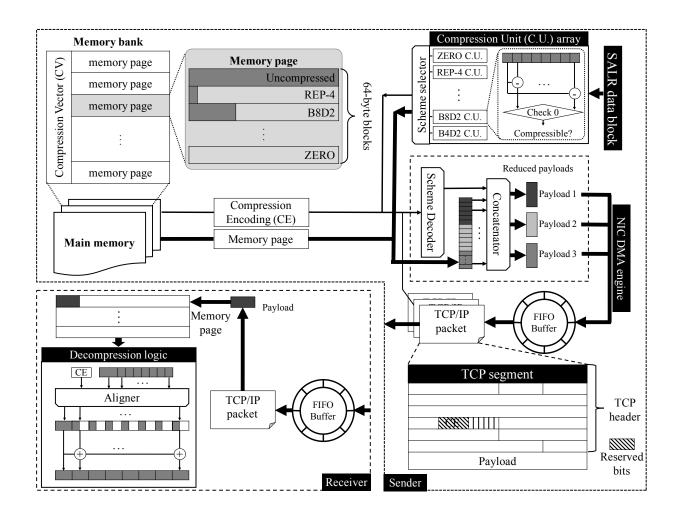

| 56 | Memory network co-design and work flow of compressed transfer in WSN              | 105 |

| 57 | Data formats.                                                                     | 108 |

| 58 | Breakdown of eight lightweight compression schemes                                | 109 |

| 59 | LCP, in-place (IP) and ZIP compression ratio for original and SALR data           |     |

|    | layouts. Compression ratio is $\frac{rawSize}{compressedSize}$ (higher is better) | 110 |

| 60 | Bluetooth transfer time of LCP, in-place (IP), and ZIP compression, with          |     |

|    | original and SALR layouts (normalized to LCP-original).                           | 112 |

| 61 | WiFi-Direct transfer time of LCP, in-place (IP), and ZIP compression, with        |     |

|    | original and SALR layouts (normalized to LCP-original).                           | 112 |

#### PREFACE

Earning a PhD is tough. Mine would have been a mission-impossible without help from some really important people. I would first thank my advisor, Dr. Alex Jones. Without the precious opportunity he provided to pursue my graduate study here at the University of Pittsburgh, I could never have gone so far geographically. I would never have reached so far in the field of advanced study and research without his relentless support, insightful instructions, and valuable advice. His attitude towards research steers me in the right direction for my PhD study and future work.

I want to thank Dr. Zhi-Hong Mao and Dr. Rami Melhem for their co-advising on my Master's thesis and my research work as a PhD candidate, respectively. Their outstanding experience in research and positive attitude towards work have always been inspiring and encouraging to me. I also thank Professor Hai Li, Professor Yiran Chen, Professor Ervin Sejdic and Professor Melissa Bilec for serving as my committee members and giving me valuable advice on my PhD proposal, defense and dissertation. I further thank my fellow researcher and good friend, Yong Li, for his help in my study and life in Pittsburgh. I am also very grateful to Dr. Michelle Jones for her help and advice in revising this dissertation.

Finally, I thank my wife and my parents for their invaluable care and support.

#### 1.0 INTRODUCTION

#### 1.1 MOTIVATIONS

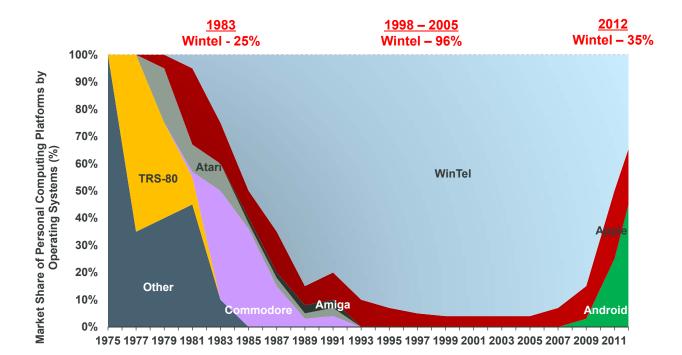

Over the last decade, there has been a dramatic shift in the computing market away from stationary computers to portable palmtop computers. Fig. 1 shows the global market share of personal computing devices by operating system from 1975 to 2012 [1]. Since the release of the first generation of iPhone in 2007 and Android operating system in 2008, the aggregate market share of these two major palmtop platforms has dramatically climbed, reaching 60% by the end of 2012, while the market share of desktop and laptop computers has dropped below 40%. One thing that remains constant is the continuous availability of computation resources that can be leveraged to solve problems. The popular distributed computing platform, BOINC [2], has gathered enormous processing from personal computers to help researchers in multiple areas, including astrophysics, physics, biology, and climatology. Utilizing the increasingly large processing power of palmtop computers to do lightweight distributed computing tasks is a promising, and even necessary approach. However, such a computing system on mobile computers has significantly different trade-offs, particularly related to energy/battery life.

Palmtop computers usually have smaller form factors and less processing power compared to traditional computing devices. However, they also consume less power thanks to energyoptimized components such as reduced instruction set computing (RISC) based low power embedded processors [3], Lower Power DDR (LPRRD) RAM [4], non-spinning eMMC (flash) storage, and Bluetooth Low-Energy [5], etc. Researchers have found in [6] that each core on an Atom chip (palmtop class) could handle web search queries at half the rate of a Xeon chip (workstation/server class) core but required just 20% of the energy per request. A

Figure 1: Global Market Share of Personal Computing Platforms by Operating System from 1975 to 2012.

better per-task energy efficiency is the main goal of this work, to be achieved by distributed computing on energy-efficient palmtop computing devices. However, the central server(s) providing services such as database storage, web query, and task scheduling, becomes the largest power component of the otherwise lightweight platform. Considerable benefit would be gained by conducting the distributed computing in a pure peer-to-peer (P2P) fashion without a server, which requires each computing node to be self-organizable in terms of data storage, data communication, and task management.

In addition to the processing capability of the palmtop devices, on-board storage is another limiter in processing and storing data. With the development of micro-electromechanical (MEMS) sensor technology, more on-board and external sensors can be integrated with the palmtop computers as sensor nodes to collect data at a finer granularity. However, issues such as higher power dissipation with CMOS technology scaling limit the growth of storage capacity of future palmtop computers. Emerging non-volatile memories (NVMs), such as phase change memory (PCM), spin-transfer torque MRAM (STT-MRAM), and Racetrack Memory (RM), are promising in addressing these issues with their near-zero static power and much higher density than traditional static random-access memory (SRAM). Among those NVMs, RM has the highest density thanks to its unique physical structure. However, drawbacks such as high dynamic write power and potential domain shift operations upon each access make it less competitive both performance- and energy-wise. Lightweight hardware compression is one method shown to be effective in mitigating these drawbacks.

Aside from data storage, data transfer is another important topic in palmtop computing. Software compression is effective in reducing data transfer time but requires nonnegligible compression and decompression overhead. A lightweight mechanism to increase the efficiency (latency and energy) is needed to address the data transfer problem. Since hardware algorithms leverage low dynamic ranges existing in the consecutive data blocks, it may be possible to better organize the data structures to increase the compressibility, thus further reducing the transfer time.

#### 1.2 PROBLEM STATEMENT

It is desirable to leverage the capabilities and ubiquity of commodity palmtop computing to build wireless sensor networks (WSNs) with on-board data processing capabilities. Fusion of a WSN node and a distributed computing client provides collaborative data collection and processing capability. Fusion of a distributed computing client and a server relaxes the restriction of a dedicated server for better energy efficiency and fits well in the context of P2P WSN. However, to accomplish these fusions effectively requires advancements at the system, memory architecture, and communication levels, as pressure on data storage as well as transmission becomes larger. The goal of this work is to create a WSN with decentralized distributed computing capability using palmtop devices, and explore the potential advancements in multiple levels of the palmtop system with emerging memory technologies and compression.

#### 1.3 DISSERTATION OVERVIEW

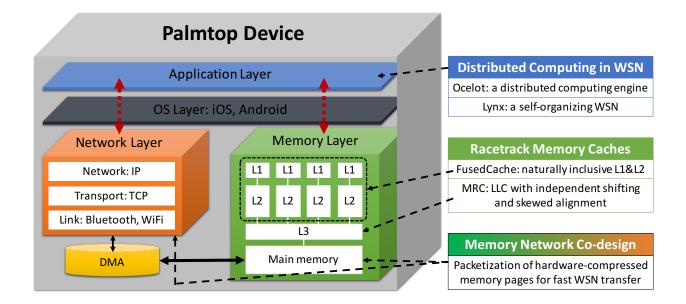

Figure 2: Overview of this dissertation work.

Fig. 2 illustrates different components of this dissertation, and relates these components to system components in existing and future palmtop computers. This work incorporates application level WSN platform implementations including Ocelot and Lynx for utilizing the processing power and rich connectivity of existing palmtop computers, architecture level cache designs including FusedCache and MRC for increased storage density with emerging Racetrack Memory, and cross-level memory network co-design for accelerated wireless transfers with seamless packetization of compressed memory pages. In the remainder of this section, I describe in detail how this work tackles the aforementioned challenges.

#### 1.3.1 Application Level: Distributed Computing in a Wireless Sensor Network

First, the initial steps for developing a distributed mobile computing platform named  $Ocelot^1$  are presented. Ocelot can be used in scenarios where highly parallel, lightweight computational tasks are required, saving the energy resources that would normally be required by

<sup>&</sup>lt;sup>1</sup>An ocelot is a small wild cat related to leopards. The name was selected for this system because the relationship between an ocelot and a leopard is similar to that of an embedded processor in a tablet with workstation-class processors.

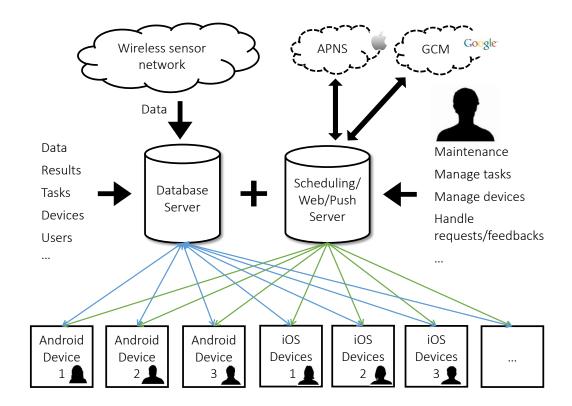

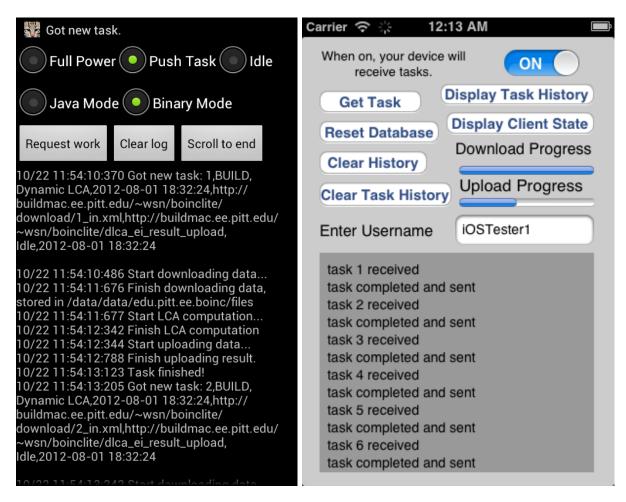

workstation or server machines. The Ocelot system working in such a scenario is shown in Fig. 3. Additionally, Ocelot can be used in an application specific WSN scenario in which it is difficult/impossible or undesirable to deploy a dedicated computational infrastructure. Conceptually, Ocelot is modeled after the Berkeley Open Infrastructure for Network Computing (BOINC) [2], an open source middle-ware system for volunteer and grid computing on PCs and servers. However, BOINC is complex, requiring a considerable amount of computational effort just to initiate and manage connections with the BOINC servers. On a workstation, this overhead is minimal, but on a mobile platform, this overhead becomes considerable. In contrast, Ocelot is a lightweight mechanism to deploy computation tasks on smartphones and tablets using the Android and iOS platforms. Though mobile devices come with embedded processing capabilities, their ubiquity can overcome this drawback through their flexibility in development and for lightweight tasks they can often provide much better power-efficiency.

Figure 3: Overview of the Ocelot system.

Of course, security features built into a system provides a challenge to task distribution over an open network. Smartphone and tablet platforms such as Android and iOS restrict the operating system features required to implement a grid style computing platform (such as receiving external data and code to process for a workunit). These security mechanisms are important given the nearly global access capability to avoid an attacker from using these devices to spy on their users or to steal sensitive information. This work principally describes the mechanism and performance of such a system with only a simple method to handle secure operations (e.g., registering devices and physical security).

In particular, an Ocelot dashboard is used for interactive project management to evaluate usage workloads and to monitor activity. Using a sustainable building-based study, use cases for managing sensor data and computing life-cycle assessment algorithms are shown. Palmtop devices with Ocelot are compared to dedicated workstations to demonstrate the energy benefits of my approach. On average, computations on a palmtop device require 67% less energy than on a workstation.

I also introduce  $Lynx^2$ , a self-organizing wireless sensor network research environment based on commodity hardware/software systems. Given the proliferation of tablets, smartphones, and music players, there is a continually expanding platform of devices that can be used to form a WSN. The typical smart-phone or tablet contains multiple communication mechanisms such as Global System for Mobile communication (GSM) [7], Code Division Multiple Access (CDMA) [8], Near Field Communication (NFC) [9], Bluetooth [10] and WiFi [11]. Further, these devices often provide a significant number of on-board sensors including light sensing, temperature sensors, etc., as well as the capability to connect to various types of external sensors. These devices are battery operated, making them highly portable and mobile.

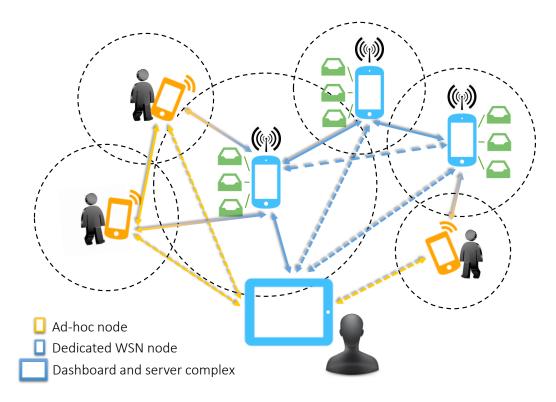

Fig. 4 provides an overview of how the Lynx system can construct a WSN from commodity tablet and palmtop computing platforms. A dedicated WSN node (fixed and preconfigured) consists of the palmtop computer running the Lynx client with one or more sensors monitoring certain physical or environmental conditions in an area. Sensing data can be stored locally and/or passed through wired (e.g. USB) or wireless connections (e.g.

<sup>&</sup>lt;sup>2</sup>The name Lynx was also selected because of its similarities to ocelots and leopards.

Figure 4: A Lynx wireless sensor network illustration.

WiFi or Bluetooth) on the Lynx node. Transient mobile devices (such as a smart-phone sitting in a pocket) can run the Lynx software and become an ad-hoc Lynx node. Though not required to gather sensor data, ad hoc nodes can serve as a bridge and help to relay data within their connection coverage and capacity. Ocelot and Lynx are then seamlessly integrated to provide the capability of distributed computing over self-organizing wireless sensor networks in a fully decentralized fashion.

#### 1.3.2 Architecture Level: Cache Designs with Emerging Racetrack Memory

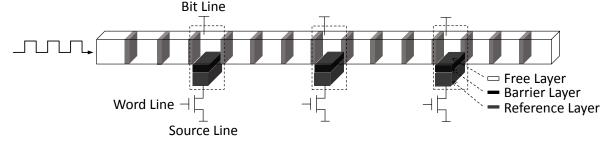

With the development of MEMS sensor technology, more on-board and external sensors can be integrated with palmtop computers as sensor hubs/nodes to collect data at a much finer granularity. Therefore, future palmtop computers may experience storage shortage at the current technology scaling speed. Emerging storage technologies must be leveraged to relax the storage restriction for future WSN applications. A modern consumer-grade hard disk drive (HDD) can accommodate terabytes of data with a single magnetic read/write head. The mechanical movement latency, including seek and rotation, measures in milliseconds, making HDDs at the very bottom of the memory hierarchy of computer systems. Spintronic domain-wall "Racetrack" memory (RM), recently proposed and demonstrated by IBM [12], is a promising candidate to overcome density limitations while retaining the static energy benefits of STT-MRAM. RM integrates several magnetic "domains" into one nanowire or track. In other words, each track can store multiple bits of non-volatile data with one or more discrete access points similar to a magnetic tunnel junction (MTJ) for reads/writes to the aligned domain as shown in Fig. 5. By applying spin-polarized current pulses, data bits can be shifted along the track to be aligned with these access points. In this fashion, RM resembles traditional hard disks with disk rotations aligning magnetic data with read/write heads. However, unlike mechanical disks, shifting speed is typically similar or faster to data access, making RM attractive for its density, speed, and non-volatility at higher memory hierarchies such as main memory and on-chip caches. RM demonstrations of memory array structures [13] and content addressable memories (CAMs) [14] show fabrication feasibility, as well as great potential for density, performance, and power consumption, suggesting that we have reached the appropriate time for circuit- and architecture-level design exploration.

Figure 5: Planar Racetrack memory.

By leveraging shift-based writing [15], racetrack writes become competitive with SRAM, eliminating a drawback of STT-MRAM for caches near the core (e.g. L1), due to their relatively large incidence of unfiltered writes. However, for dedicated memory structures, such as private L1 caches where timing predictability is crucial to maintain pipeline integrity, non-uniform access behavior is problematic. Further, I note that accesses closer to the core should minimize access latency while father accesses can tolerate longer latency. Therefore, I propose *FusedCache*, an RM cache that combines two logical levels of the cache hierarchy into a single physical storage array. Area-wise, an STT-MRAM cell can be considered equivalent to RM of length equal to one. By extending the length of the nanowire to hold more domains, the density of the storage is increased but the physical size of the array is not, as the CMOS access transistor still dominates a nanowire with ten or more domains. Moreover, the domain aligned to the access point has a deterministic access time (i.e., no shifting required). Thus, by replacing a STT-MRAM array with N-length RMs and enforcing the property that the domains aligned with the access point are the faster level cache (L1), the additional N-1 domains are treated as a next-level cache (L2) that tolerates longer non-uniform access latency due to shifting. Thus, I have *fused* together two levels of the memory hierarchy.

FusedCache has unique properties that make it valuable for use in the memory hierarchy as described. Beyond an obvious advantage that the cache retains a low-latency for L1 while removing the need for a dedicated separate L2 array thus saving area and power, the inclusion and eviction properties become naturally maintained in the structure. Consider a miss in L1. By shifting to access the data at an L2 location, the new data location becomes aligned with the access point and has automatically been promoted to L1, while the data formerly in L1 is automatically evicted to L2. Thus, the cache is *naturally* inclusive. Further, the tag array for both levels can be combined. In this L1/L2 case, the L2 tags are stored, but the L1 tags can be accessed by combining the L2 tag and the Racetrack shift position. To implement set-associativity in FusedCache, I present two designs. In the first design, the ways of each L1 set are matched to correspond to the same ways of the L2 set to which they belong through background swap operations. In the second design, I demonstrate a hybrid associativity organization where the L2 may have a larger number of ways than the L1.

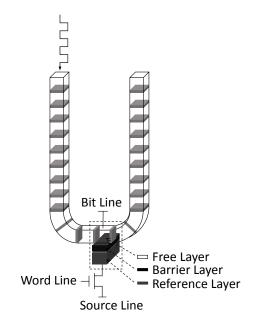

Fig. 6 shows a 3D Racetrack schematic with a single read/write port. Additional bits add only to the height of the vertical structure. Thus, a much larger storage density can be achieved over a planar structure (Figure 5). Spin-polarized current pulses are applied at one end of the nanowire to shift data from destination domains to the one at the access port. Including more domains on a single nanowire increases density, but without additional access ports, inevitably resulting in longer average shift distance and correspondingly higher shift latency and energy. Prior proposals for RM in caches [16, 17] focus on leveraging planar, multi-port-on-one-track (MP1T) Racetracks. However, planar structures considerably limit the density and static power advantages of RM over STT-MRAM. In contrast, a one-porton-one-track (1P1T) orientation can leverage the 3D structure to dramatically increase the density per area of RM while reducing design-time and run-time complexities at the cost of a larger shifting overhead. In terms of energy, like most non-volatile memories (NVMs) such as PCM and STT-MRAM, RM is dominated by dynamic power with an asymmetric energy of writes being larger than reads. Unlike other NVMs, shifting energy tends to be a significant, even dominant, component of the dynamic power.

Figure 6: A schematic of Racetrack with three-dimensional structure.

To address the aforementioned issues, I propose *multilane Racetrack caches* (MRC), a simple, energy efficient, RM-based last level cache (LLC) design using *in-place compression* and *independent shifting* to reduce data access and shifting overheads. In MRC, lightweight compression is used to reduce the cache line size in order to reduce the number of bits stored in the cache block. Further, by allowing independent shifting at a finer granularity than a line (e.g., byte-level), fewer tracks may require shifting to access compressed cache lines. Finally, using *skewed alignment* or adjusting the starting location of compressed lines within their cache blocks, contention for port resources may be alleviated by treating independent

shifting as *multiple Racetrack lanes* that allow concurrent data access. Energy consumed by reads, writes, and shifts can be reduced through all these methods and the reduced contention can also lead to performance benefits. While MRC can be applied effectively to both MP1T and 1P1T structures, compared to an isocapacity baseline 1P1T RM cache, MRC achieves 5% performance gain and 19% energy reduction.

#### 1.3.3 Cross-Level: A Memory Network Co-design with Compression

Compression turns out to be an effective and sometimes necessary approach to improve the usability and efficiency of both high level WSN applications and low level cache designs. I demonstrate in Lynx that software-based compression, although it requires extra time to compress and decompress, is able to significantly reduce data transfer time over the network. I also demonstrate that hardware-based lightweight compression is effective in saving dynamic write power and shifting energy of emerging Racetrack Memory, with minimal latency and energy overhead.

To leverage lightweight compression for reducing data communication latency, I propose a memory network co-design approach that compresses memory pages using low-latency hardware compression, and uses this compressed form to packetize payloads for communication over the wireless network links. While traditional software-based compression can outperform lightweight compression in terms of compression ratio, it requires a considerable runtime overhead to compress the transmitted data. And although traditional lightweight compression tends to work poorly on the traditional storage structure of sensor data across multiple sensors, I propose to better utilize the low dynamic range existing in most data tied to a single sensor. Thus, data storage layout is reorganized according to sensor source to improve the data compressibility, especially for lightweight compression but also benefiting traditional software compression approaches.

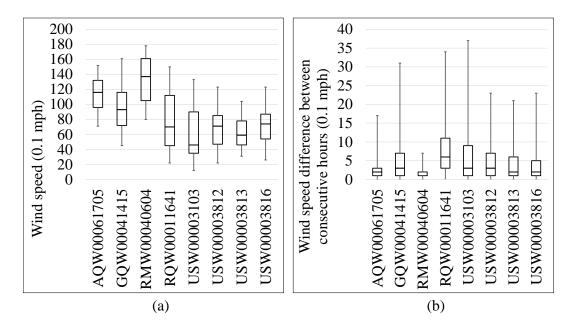

This approach is supported by the observation that sensor data from the same source tend to have a low dynamic range. Fig. 7 shows the five number summary<sup>3</sup> of NOAA 1981-

$<sup>^{3}\</sup>mathrm{A}$  five number summary consists of the minimum, first quartile, median, third quartile, and maximum of the dataset.

Figure 7: Five number summary of NOAA 1981-2010 wind speed normals of select eight U.S. stations: (a) hourly wind speed; (b) wind speed difference (absolute value) between consecutive hours.

2010 hourly wind speed normals<sup>4</sup> for eight arbitrarily selected U.S. stations [18]. The wind speeds at each station tend to vary within a reasonably small range, especially for consecutive timestamps. Similar patterns are observed in other types of data as well, including utility consumption, climatic, financial, and potentially many other datasets. This consistency provides an opportunity to optimize how this data is handled within WSNs with the goal of improving their performance and efficiency.

#### 1.4 CONTRIBUTIONS

The adoption of software and hardware compression techniques provides an opportunity to make contributions to the areas of both high level WSN systems and low level cache/memory architecture.

<sup>&</sup>lt;sup>4</sup>A "normal" of a particular variable is defined as the 30-year average.

To create a WSN system with commodity mobile hardware, I make the following contributions:

- Ocelot: I provide an energy-efficient distributed computing platform with commodity palmtop computers. Ocelot is the first attempt to utilize the growing processing power of mobile devices, and is a lightweight implementation of an energy-efficient distributed system, comprising clients, web/database servers, and assistive dashboards.

- Lynx: I simplify the creation of a WSN by leveraging existing infrastructure. Using Lynx, it is possible to quickly construct a sensor network from existing devices, many of which are already deployed by users for their more traditional purpose (e.g., smartphone, tablet function). Lynx can provide access to sensor data from on-board sensors and external sensors.

- Integration: I provide a smart, fully-distributed network for mobile computing. Lynx is designed as a platform for Ocelot. Integration of these two platforms creates a fully distributed computing engine without any central servers or infrastructure, as all the network communication utilizes peer-to-peer (P2P) connections. Moreover, by removing dedicated central servers in the Ocelot system, the overall energy consumption is further reduced.

# To advance the storage capacity of palmtop systems, I make the following architecture contributions:

• FusedCache: I demonstrate how a pseudo-sequential access structure (e.g., a Racetrack magnetic nanowire) can naturally integrate multiple memory storage levels in a single, highly dense storage array using the idea of *storage hierarchy driven* shifting, and describe a particular instantiation of storage hierarchy driven caching for various set-associativity parameters ranging from direct-mapped to hybrid set-associativity with different numbers of ways at each level, and support the value of the fused L1/L2 cache through a detailed power and energy evaluation, including sensitivity studies of different cache sizes and associativities, while also considering both iso-capacity and iso-area SRAM cache replacements. • MRC: I adopt lightweight in-place compression to reduce the number of bits stored, thus saving read and write energy of RM caches. Based on compression, I propose independent shifting to control Racetrack movements at a finer granularity than the cache line, to further save shift energy of compressed data in RM caches. Based on independent shifting, I propose skewed alignment to accelerate accesses to compressed cache lines in RM caches with independent shifting.

#### In the memory network co-design work, I make the following contributions:

- I propose a WSN system design that directly uses hardware/lightweight compression to compress memory pages in-place in order to natively compress data packets and avoid the need for software compression for improved efficiency in wireless communication.

- I propose the Source-Aware Layout Reorganization (SALR) approach to significantly increase compression ratios of sensor data for hardware/lightweight-based compression approaches, and integrate it with data communication using in-place hardware/lightweight compression and evaluate it using various types of data comparing the combined technique to using on-demand software-based compression for communication.

#### 1.5 DISSERTATION STRUCTURE

The rest of this dissertation is organized as follows. Chapter 2 provides a comprehensive list of prior work in related areas such as distributed computing, wireless sensor networks, data compression in both memory and networks, as well as emerging Racetrack Memory. Chapter 3 describes the features and implementation details of the Ocelot project, and a dynamic life cycle assessment case study to evaluate its feasibility and effectiveness. The Lynx project is discussed in Chapter 4, and evaluated using several approaches, including basic data transfer, scalability tests, tests as a hardware emulation platform by swapping the routing algorithm modules, and integration tests with Ocelot. Chapter 5 discusses Fused-Cache, a lower level cache design to ensure uniform accesses to the latency-critical L1 cache given RM's non-uniform access pattern. In Chapter 6, I explain how I extend the benefits of lightweight compression from saving energy to improving performance with emerging Racetrack Memory, which is a promising candidate as a high density memory technology on future palmtop computer. I explain in Chapter 7 a memory network co-design for improving the efficiency of wireless transfer with lightweight compression, as well as a data layout reorganization technique specially designed to improve the compressibility of sensor data from multiple sources. Finally, I conclude in Chapter 8.

#### 2.0 PRIOR ART

#### 2.1 BOINC AND DISTRIBUTED COMPUTING

The Berkeley Open Infrastructure for Network Computing (BOINC) is a middle-ware system connecting central servers and numerous distributed client computers for public-resource computing and storage. It was originally developed for the *SETI@home* [19] project before it became useful as a platform for other distributed applications in areas as diverse as mathematics, medicine, molecular biology, climatology, and astrophysics. BOINC makes it possible to accumulate the enormous processing power of the public volunteered personal computers (PCs) all around the world. For example, the pioneer project, *SETI@home*, performs digital signal processing of radio telescope data from the Arecibo radio observatory to help the *Search for Extraterrestrial Intelligence* (SETI). The *Climateprediction.net* [20] project tries to quantify and reduce the uncertainties in long-term climate prediction, based on large numbers of computer simulations with varying forcing scenarios and internal model parameters. PC owners participate in one or more of the BOINC projects as resource volunteers, and they can specify how their resources are allocated among these projects.

BOINC is designed to support applications that have either large computation requirements or storage requirements, or both. The main equirement of the application is that it be divisible into a large number (thousands or millions) of jobs that can be done independently. Thus, it is essentially a simple form of distributed computing platform without communications among the individual computers.

Ocelot uses principles similar to BOINC, except that it focuses on moving lightweight tasks from less power efficient workstations onto ubiquitous palmtop computers. The number of mobile phones per capita has reached nearly one per inhabitant worldwide [21], and smartphone penetration has reached over 50% in developed regions like EU5 [22] and U.S [23]. This resource can be utilized to reduce our need for workstation or server computers and reduce energy per computation.

#### 2.2 WIRELESS SENSOR NETWORKS AND MOBILE CONNECTIVITY

A WSN consists of spatially distributed nodes with capabilities such as sensing, wireless communication, or even lightweight data processing. Usage scenarios range from real-time tracking, to monitoring of environmental conditions, to ubiquitous computing environments, to monitoring of the health of structures or equipment. Nodes within the network can often self-organize, cooperatively passing their data through predefined protocols and providing paths to a center collector/storage. Often they also provide a distributed computational resource and local storage for sensor information. As such, WSNs have become an area of significant interest and research activity including a wide variety of academic and commercial research groups, product lines, etc.

The purpose of traditional WSN is to collect various kinds of sensor data, including temperature, pressure, and sound data at different locations (e.g., different labs in an engineering school building) through the interconnected network. Additionally, the processing power of modern mobile electronics has become powerful enough to take on sizable tasks. With large numbers of these devices connected, computationally complex algorithms such as signal and image processing tasks on sensor data can be efficiently completed by partitioning tasks onto independent mobile processors assigned from the mobile device pool.

A particular area of recent interest for WSNs is the tracking of environmental information and resource utilization by sensing local temperature or light levels or sensing energy usage. This interest has been accelerated by the increasing availability of palmtop computing, in particular, smartphone and tablet devices that are highly connected using various wireless protocols such as WiFi, Bluetooth, NFC, and optical communications such as infrared (IR). With the rapid development of *System-on-Chip* (SoC) technologies, these embedded systems continue to become more powerful computational engines while still remaining energy efficient. As a result, in-network data processing and low-to-medium effort computation has become possible in a WSN created with commodity devices as nodes. Just as in WSNs, performance is tempered with energy resources (e.g., battery life) as metrics to be considered. However, by deploying work wisely in such a system it may be possible to avoid the need to utilize heavy iron servers in many environments to process the sampled data in the system. Additionally, the global availability of these devices may create a network of computational resources that can be used much like grid computing has done in the past with idle personal computers or workstations.

#### 2.2.1 Physical Layer Communication

With the increasing popularity of mobile electronic devices including smartphones and tablet computers, connectivity technologies and computation capability are rapidly evolving. Commodity wireless protocols such as WiFi and Bluetooth are becoming more competitive with protocols typically designed to work with WSNs such as Zigbee [24]. For example, the development of WiFi 802.11n, with its multiple-input and multiple-output (MIMO) antennas, has led to support for new protocols such as WiFi-Direct [25] in tablets and smartphones. WiFi-Direct allows a device to find nearby WiFi-Direct capable devices and form a group to communicate over a peer-to-peer (P2P) link without wireless access points (base stations) in the infrastructure mode. This allows real world implementations of ad-hoc routing to be feasible and robust with commodity devices [26]. Bluetooth Low Energy (BLE) also shows good capability for short range data transmission. It represents a trade-off between energy consumption, latency, piconet size, and throughput [27].

#### 2.2.2 System-level Management and Optimization

Most hardware oriented studies in the WSN field focus on infrastructure [28, 29] or routing improvements [30, 31, 32, 33] in an attempt to improve network coverage area [34, 35] or reduce energy consumption for communication [36, 30, 37, 38, 39, 40, 41]. There is also a significant amount of theoretical work on improving routing algorithms and developing more efficient low-level communication protocols. Further, some efforts explore methods for distributing data across the network to maximize data availability when link connectivity is transient and unreliable, while minimizing other metrics such as system storage and energy overheads. The goal of such research include maximizing network lifespan under a fixed aggregate system energy storage capacity, maximizing system robustness, and to determine best practices for network self-organization and configuration [42, 43, 39, 44, 45].

#### 2.2.3 Self-Organizing Network

The Self-Organizing Network (SON) was originally proposed for the Long Term Evolution (LTE) mobile technology [46]. SON configures and optimizes the increasingly large and complex mobile networks automatically, so that manual interactions can be reduced and the efficiency of the network can be increased. A SON generally features functionalities such as self-configuration, self-optimization, and self-healing [47]. Adding or reducing network nodes should be configured and managed with the least possible human intervention, and communication workloads should also be dynamically balanced for better efficiency. When failure happens in any of the network nodes, the network structure should be reconfigured to reduce negative impacts.

The initial focus of SON development was to reduce operating costs in mobile radio networks [47], but the concept is now increasingly recognized as a method for any network to intelligently organize and manage its nodes at scale. The challenges of organizing a peer-to-peer network on small wireless sensors such as limited power, limited radio range, and potentially high geographical volatility, and all point to an adaptive and efficient selforganizing solution. For example, implementing the *Automatic Neighbor Relation* (ANR) detection feature in a SON helps to distributively establish the network map of a WSN. Nodes within the radio range of each other can communicate directly; nodes out of range are still able to communicate with the help of one or more "bridge" nodes, which sit in between.

#### 2.3 ARCHITECTING WITH RACETRACK MEMORY

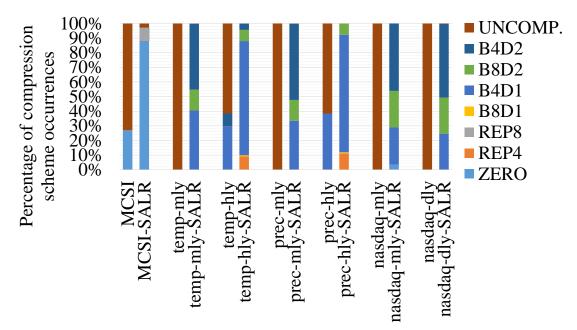

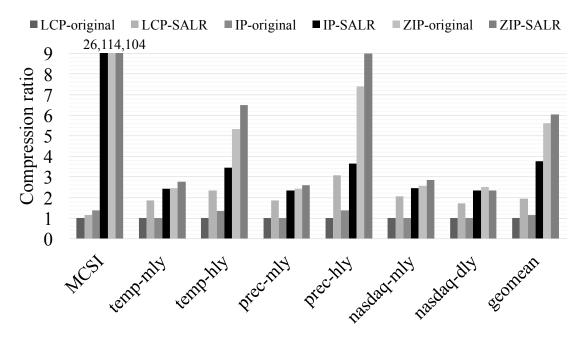

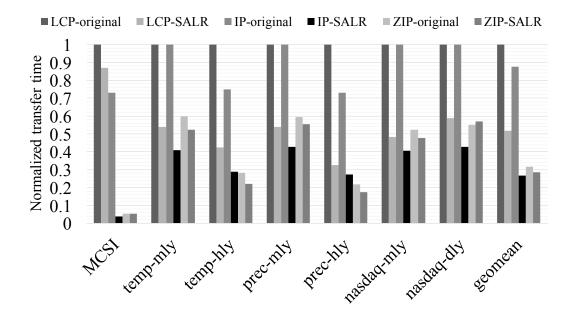

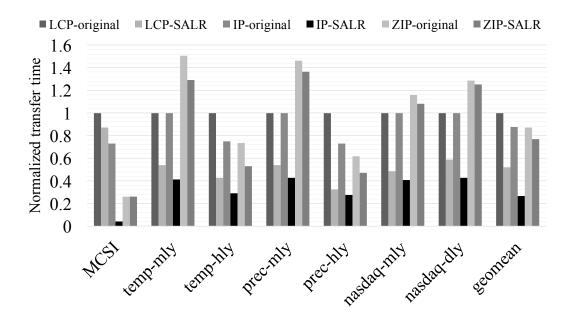

As a descendant of STT-MRAM, RM comprises an array of magnetic nanowires arranged vertically or horizontally on a silicon chip. A nanowire consists of many magnetic domains separated by *domain walls* (DWs). Each domain has its own magnetization direction. Similar to STT-MRAM, binary values can be represented by the magnetization direction of each domain. For a horizontally-arranged planar strip (Figure 5), several domains share one access point for read and write operations [48]. The DW motion is controlled by applying a short current pulse on the head or tail of the strip in order to align different domains with the access point. Since the storage elements and access devices in RM do not have a one-to-one correspondence, a random access requires two steps to complete: Step 1-shift the target magnetic domain and align it to an access transistor; Step 2-apply an appropriate voltage/current to read or write the target bit. Intrinsically, the operations in step 2 are the same as that used for accessing STT-MRAM. The DW motion, however, requires extra domains at both sides of a magnetic nanowire to prevent data loss.