# ENERGY-EFFICIENT CIRCUIT DESIGN

by

## Michael Nugent

B.S. Computer Science and Mathematics, University of Pittsburgh, 2007

### Submitted to the Graduate Faculty of

the Kenneth P. Dietrich School of Arts and Sciences in partial

fulfillment

of the requirements for the degree of

## Doctor of Philosophy

University of Pittsburgh

2015

# UNIVERSITY OF PITTSBURGH DIETRICH SCHOOL OF ARTS AND SCIENCES

This dissertation was presented

by

Michael Nugent

It was defended on

April 29, 2015

and approved by

Kirk Pruhs, Department of Computer Science

Daniel Mossé, Department of Computer Science

Adam Lee, Department of Computer Science

Anupam Gupta, Department of Computer Science, Carnegie Mellon University

Dissertation Director: Kirk Pruhs, Department of Computer Science

#### ENERGY-EFFICIENT CIRCUIT DESIGN

Michael Nugent, PhD

University of Pittsburgh, 2015

We initiate the theoretical investigation of energy-efficient circuit design. We assume that the circuit design specifies the circuit layout as well as the supply voltages for the gates. To obtain maximum energy efficiency, the circuit design must balance the conflicting demands of minimizing the energy used per gate, and minimizing the number of gates in the circuit; If the energy supplied to the gates is small, then functional failures are likely, necessitating a circuit layout that is more fault-tolerant, and thus that has more gates.

By leveraging previous work on fault-tolerant circuit design, we show general upper and lower bounds on the amount of energy required by a circuit to compute a given relation. We show that some circuits would be asymptotically more energy-efficient if heterogeneous supply voltages were allowed, and show that for some circuits the most energy-efficient supply voltages are homogeneous over all gates.

In the traditional approach to circuit design the supply voltages for each transistor/gate are set sufficiently high so that with sufficiently high probability no transistor fails. We show that if there is a better (in terms of worst-case relative error with respect to energy) method than the traditional approach then P = NP, and thus there is a complexity theoretic obstacle to achieving energy savings with Near-Threshold computing.

We show that almost all Boolean functions require circuits that use exponential energy. This is not an immediate consequence of Shannon's classic result that most functions require exponential sized circuits of faultless gates because, as we show, the same circuit layout can compute many different functions, depending on the value of the supply voltage.

If the error bound must vanish as the number of inputs increases, we show that a natural

class of functions can be computed with asymptotically less energy using heterogeneous supply voltages than is possible using homogeneous supply voltages. We also prove upper bounds on the asymptotic energy savings achieved by using heterogeneous supply voltages over homogeneous supply voltages for a class of functions, and also show a relation that can bypass this bound.

### TABLE OF CONTENTS

| PREFACE    |                                                                               |    |  |  |  |

|------------|-------------------------------------------------------------------------------|----|--|--|--|

| 1.0        | INTRODUCTION                                                                  | 1  |  |  |  |

|            | 1.1 Related Work                                                              | 5  |  |  |  |

|            | 1.2 Our Contributions                                                         | 7  |  |  |  |

|            | 1.2.1 General Bounds on Circuits With Constant Error                          | 7  |  |  |  |

|            | 1.2.2 Introduction to Heterogeneity                                           | 8  |  |  |  |

|            | 1.2.3 Hardness Results                                                        | 10 |  |  |  |

|            | 1.2.4 Almost All Functions Require Exponential Energy                         | 13 |  |  |  |

|            | 1.2.5 The Power of Heterogeneity to Reduce Energy                             | 15 |  |  |  |

| 2.0        | MODEL, DEFINITIONS, AND NOTATION                                              | 19 |  |  |  |

| 3.0        | GENERAL ENERGY UPPER AND LOWER BOUNDS                                         | 21 |  |  |  |

|            | 3.1 A General Energy Lower Bound                                              | 21 |  |  |  |

|            | 3.2 A General Energy Upper Bound                                              | 28 |  |  |  |

| <b>4.0</b> | INTRODUCTION TO SUPPLY VOLTAGE HETEROGENEITY                                  | 29 |  |  |  |

|            | 4.1 Supply Voltage Heterogeneity May Not Help                                 | 29 |  |  |  |

|            | 4.2 Supply Voltage Heterogeneity Can Help                                     | 30 |  |  |  |

| 5.0        | HARDNESS AND ALGORITHMIC RESULTS FOR CIRCUIT EN-                              |    |  |  |  |

|            | ERGY PROBLEMS                                                                 | 38 |  |  |  |

|            | 5.1 Polynomial-Time Approximation of the Minimum Circuit Energy Problem .     | 39 |  |  |  |

|            | 5.2 Hardness of Approximation for the Minimum Circuit Energy Problem          | 42 |  |  |  |

|            | 5.3 Hardness of Determining $(\epsilon, \delta)$ -reliability on Fixed Inputs | 48 |  |  |  |

|            | 5.4 Tree Circuits                                                             | 53 |  |  |  |

|     | 5.5  | Non-Monotonicity of $\delta$ in $\epsilon$                                     | 54 |

|-----|------|--------------------------------------------------------------------------------|----|

| 6.0 | AL   | MOST ALL FUNCTIONS REQUIRE EXPONENTIAL ENERGY                                  | 57 |

|     | 6.1  | A Lower Bound on the Number of Functions Computable by a Circuit               | 57 |

|     |      | 6.1.1 Homogeneous Supply Voltages                                              | 58 |

|     |      | 6.1.2 Heterogeneous Supply Voltages                                            | 62 |

|     | 6.2  | Almost all Functions Require Exponential Energy                                | 65 |

|     |      | 6.2.1 Adaptation of Shannon's Argument                                         | 66 |

|     |      | 6.2.2 Homogeneous Supply Voltages                                              | 66 |

|     |      | 6.2.3 Heterogeneous Supply Voltages                                            | 68 |

|     | 6.3  | Relating Energy and the Number of Noisy Gates                                  | 70 |

| 7.0 | TH   | IE POWER OF HETEROGENEITY TO REDUCE ENERGY                                     | 72 |

|     | 7.1  | Lower Bound for Functions                                                      | 72 |

|     | 7.2  | Upper Bound for Functions                                                      | 74 |

|     | 7.3  | Lower Bound for Relations                                                      | 76 |

|     | 7.4  | Generalizing the Failure-to-Energy Function                                    | 81 |

| 8.0 | CC   | NCLUSION                                                                       | 83 |

|     | 8.1  | Open Problems                                                                  | 84 |

|     |      | 8.1.1 Solving the Minimum Circuit Energy Problem for Restricted Classes        |    |

|     |      | of Circuits                                                                    | 85 |

|     |      | 8.1.2 Whether Heterogeneity Reduces Energy When $\delta$ is a Fixed Constant . | 85 |

|     |      | 8.1.3 Whether $\log n$ Energy Savings via Heterogeneity is the Maximum Pos-    |    |

|     |      | sible When $\delta$ Vanishes                                                   | 86 |

|     |      | 8.1.4 The Power of the Exact Failure Model                                     | 86 |

| BIE | BLIC | OGRAPHY                                                                        | 88 |

### LIST OF FIGURES

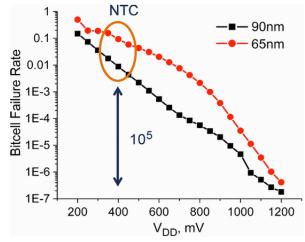

| 1  | Semi-log plot of voltage-to-failure for an SRAM cell from [16]                                                                                                                   | 2  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

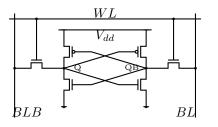

| 2  | Two SRAM circuits with the same functionality.                                                                                                                                   | 3  |

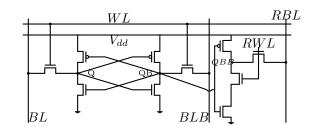

| 3  | (a) $\mathbf{Pr}[r \text{ outputs } 1] \ge 1 - p$ . (b) The path from b to g. The input gates $b_i$                                                                              |    |

|    | receive input 0                                                                                                                                                                  | 34 |

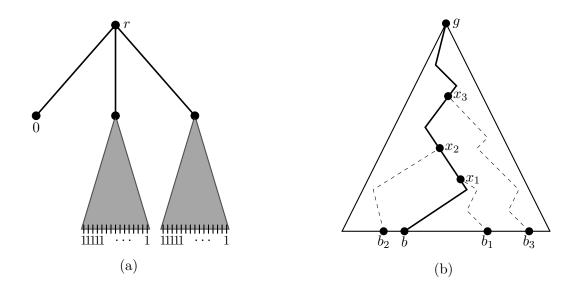

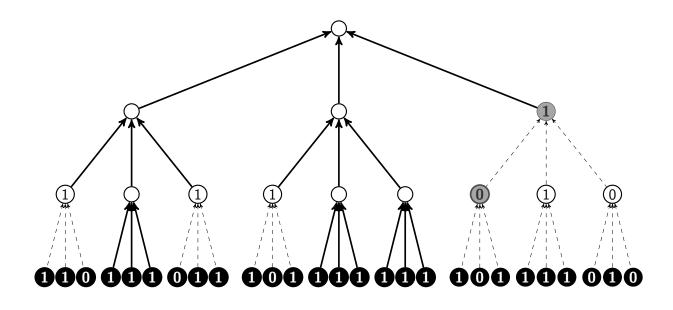

| 4  | A subtree B. The solid edges denote the full ternary subtree $T \in \Gamma$ . Note that                                                                                          |    |

|    | T has 1's as inputs on its leafs. The dashed edges denote the edges in $B \setminus T$ .                                                                                         |    |

|    | The gray nodes denote gates that failed                                                                                                                                          | 36 |

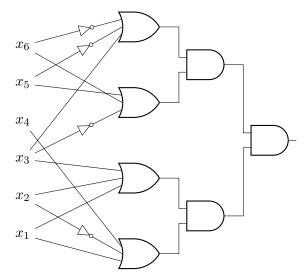

| 5  | The circuit $S_{\phi}$ where $\phi = (x_1 \lor \bar{x}_2 \lor x_4) \land (x_1 \lor x_2 \lor x_3) \land (\bar{x}_3 \lor x_6 \lor x_5) \land (x_3 \lor \bar{x}_5 \lor \bar{x}_6).$ | 43 |

| 6  | A simple circuit where $\delta^*(\epsilon)$ is not monotone in $\epsilon$ in the von Neumann failure                                                                             |    |

|    | model, consisting of two OR gates and one AND gate                                                                                                                               | 55 |

| 7  | A simple circuit where $\delta^*(\epsilon)$ is not monotone in $\epsilon$ in the 0-default failure model,                                                                        |    |

|    | consisting of an AND gate and two NOT gates                                                                                                                                      | 56 |

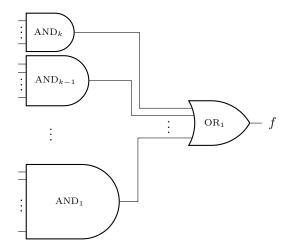

| 8  | The circuit used in the proof of Theorem 53.                                                                                                                                     | 59 |

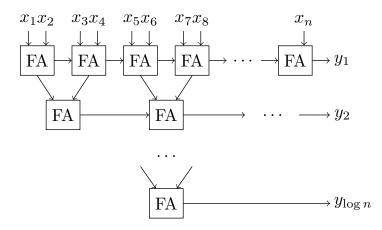

| 9  | A tree of adders. The majority of $x_1, \ldots, x_n$ is a function of $y_1, \ldots, y_{\log n}$ that                                                                             |    |

|    | is computable by a circuit of size $o(n)$                                                                                                                                        | 78 |

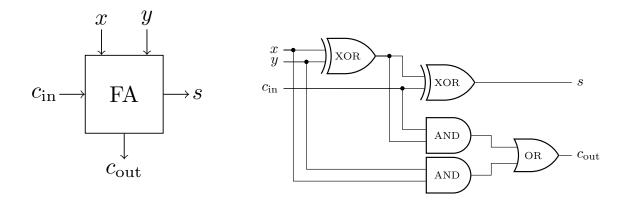

| 10 | A 1-bit full adder: logic block (left) and circuit realization (right).                                                                                                          | 79 |

#### PREFACE

The research within this dissertation was published in the following papers, and was a collaboration with the listed coauthors:

- Energy-Efficient Circuit Design, published in the 5th conference on Innovations in Theoretical Computer Science (ITCS), with Antonios Antoniadis, Neal Barcelo, Kirk Pruhs, and Michele Scquizzato [6].

- Complexity-Theoretic Obstacles to Achieving Energy Savings with Near-Threshold Computing, published in the 5th International Green Computing Conference (IGCC), with Antonios Antoniadis, Neal Barcelo, Kirk Pruhs, and Michele Scquizzato [5].

- Almost All Functions Require Exponential Energy, to appear in the 40th International Symposium on Mathematical Foundations of Computer Science (MFCS), with Neal Barcelo, Kirk Pruhs, and Michele Scquizzato [8].

- The Power of Heterogeneity in Near-Threshold Computing, in submission to the 6th International Green Computing Conference (IGCC), with Neal Barcelo, Kirk Pruhs, and Michele Scquizzato [9].

We thank Rami Melhem for insightful discussions about Near-Threshold Computing.

#### 1.0 INTRODUCTION

The number of transistors per unit volume on a chip continues to double about every two years. However, about a decade ago chip makers hit a thermal wall as the cost of cooling chips with these transistor densities became prohibitive. This has resulted in Moore's gap, namely that increased transistor density no longer directly translates into a similar increase in performance, and in energy becoming the first order design constraint in CMOS-based technologies.

One possible technique to attain more energy-efficient circuits is Near-Threshold Computing. The threshold voltage of a transistor is the minimum voltage at which the transistor starts to conduct current, around 0.2-0.3V for modern processors. Of course, even for identically-designed transistors, there can be variations in the actual threshold voltage due to manufacturing variations; And even for the same transistor, the actual threshold voltage will vary with environmental conditions. Further, actual supply voltages may differ from the designed voltage due to manufacturing and environmental variance. Thus if the designed supply voltage was exactly the ideal threshold voltage, some transistors would likely fail to conduct current as designed. For example, for a typical 65 nm SRAM circuit, halving the supply voltage from the nominal level to 0.5V typically increases the failure rate by about 5 orders of magnitude (see Figure 1 from [16]). Since the relationship between voltage and the log of the failure is approximately linear, the error as a function of supply voltage v is approximately of the form of  $\epsilon(v) = c^{-v}$ , for some positive constant c. Using the fact that the energy is proportional to the square of the supply voltage [10], the energy used by a 65nm SRAM with failure rate  $\epsilon$  is proportional to  $\Theta(\log^2(1/\epsilon))$ .

The traditional design approach to achieving fault tolerance is to set the supply voltage to be sufficiently high so that with sufficiently high probability no transistor fails. NearThreshold Computing simply means that the supply voltages are designed to be closer to the threshold voltage, which can potentially offer significant improvements in energy efficiency, provided another, more energy-efficient, solution for the fault-tolerance issue can be found.

Figure 1: Semi-log plot of voltage-to-failure for an SRAM cell from [16].

One strategy to achieve fault-tolerance is to design fault-tolerant circuits, namely circuits that correctly compute the desired output if the number of failures is not significantly higher than the expected number of failures. The study of fault-tolerant circuits is not new. Starting with the seminal paper by von Neumann [30], several papers [14, 15, 17, 18, 25–27] have considered the question of how many faulty gates, each (independently) having a (small) fixed probability of failure, are required to mimic the computation of an ideal circuit with some desired probability of correctness. In general, as the probability of gate failure increases, one would expect that more gates will be required to achieve a fixed probability of failure for the circuit. As an example from [16], the circuit shown in Figure 2a is the traditional 6-transistor design for an SRAM cell, while the circuit shown in Figure 2b is a more faulttolerant, and thus more suited for Near-Threshold Computing, 10-transistor design for an SRAM cell.

Our goal here is to initiate the theoretical study of the design of energy-efficient circuits. We assume that the design of the circuit specifies both the circuit layout as well as the supply voltages for the gates. To obtain maximum energy efficiency, the circuit design must balance the conflicting demands of minimizing the energy used per gate, and minimizing the

(a) Standard 6-transistor design.

(b) A more fault-tolerant 10-transistor design from [11].

Figure 2: Two SRAM circuits with the same functionality.

number of gates in the circuit; If the energy supplied to the gates is small, then functional failures are likely, necessitating a circuit layout that is more fault-tolerant, and thus has more gates. Thus the design should find a "sweet spot" for the supply voltages that balances the competing demands of small circuit size and low per-gate energy.

Perhaps the most natural question that arises within this context is the following: Given a function, what is the minimum energy required by a circuit to compute that function? Answering this involves finding the optimal tradeoff between reduced supply voltage and increased circuit size for that function, which is closely related to the problem of finding the smallest circuit to compute that function. Due to this relationship, coupled with the fact that the ability to determine the smallest circuit to compute an arbitrary function would have vast implications throughout theoretical computer science (for example, proving that an NP-complete problem requires circuits of super-polynomial size would show  $P \neq NP$ ), finding the optimal energy to compute an arbitrary function seems to be untouchable at this time; However, even conditional, approximate answers would provide useful insight, especially for the simpler classes of functions that circuits in computers are typically composed of. Additionally, one may be interested in optimizing the energy used by a specific circuit. In this case, the question is: Given a circuit, what is the lowest possible supply voltage such that the circuit still computes correctly (with sufficiently high probability)?

In order to begin to answer these questions, we formalize them as the following problems:

**Definition 1. Minimum Energy Circuit Problem (MEC):** Given a function (or relation) F, and an error bound  $\delta$ , output a circuit layout C and a setting v of the supply voltage, such that C uses minimal energy, subject to the constraint that C computes F with probability at least  $1 - \delta$ .

**Definition 2. Minimum Circuit Energy Problem (MCE):** Given a circuit layout C, and an error bound  $\delta$ , output a setting v of the supply voltage, such that C uses minimal energy, subject to the constraint that C computes correctly (what C would compute if there were no errors) with probability at least  $1 - \delta$ .

While it may not currently be practical, in principle the supply voltages need not be homogeneous over all gates of a circuit, that is, different gates could be supplied with different voltages. This naturally leads to the question of whether allowing heterogeneous supply voltages might yield lower-energy circuits than is possible if the supply voltages are required to be homogeneous. Intuitively, heterogeneous supply voltages should benefit a circuit where certain parts of the computation are more sensitive to failure than others. This naturally leads to the heterogeneous versions of the above two problems:

Definition 3. Heterogeneous Minimum Energy Circuit Problem (HMEC): Given a function (or relation) F, and an error bound  $\delta$ , output a circuit layout C and a setting  $v_g$ of the supply voltage for each gate  $g \in C$ , such that C uses minimal energy, subject to the constraint that C computes F with probability at least  $1 - \delta$ .

Definition 4. Heterogeneous Minimum Circuit Energy Problem (HMCE): Given a circuit layout C, and an error bound  $\delta$ , output a setting  $v_g$  of the supply voltage for each gate  $g \in C$ , such that C uses minimal energy, subject to the constraint that C computes correctly (what C would compute if there were no errors) with probability at least  $1 - \delta$ .

A variety of questions can be formulated around these problems. Perhaps most basically, for which functions can we solve MEC and HMEC (exactly or approximately)? As discussed, there are a number of functions for which solving this question seems to be beyond the reach of even state-of-the-art mathematics. However, even if it is infeasible to solve MEC and HMEC for most functions, it may be possible to say something about the minimum energy required to compute a randomly chosen function: If a function is chosen uniformly at random, how much energy does the solution to MEC or HMEC require (with high probability)? As these questions are formulated for both MCE and HMCE, it is natural to consider how much supply voltage heterogeneity effects the solutions: For which functions is the solution to HMEC significantly less than the solution to MEC? And for a function chosen uniformly at random, is the solution to HMEC significantly less than the solution to MEC? Switching to the problems for determining the minimum energy required by a fixed circuit, we can ask for which circuits can we solve MCE and HMCE (exactly or approximately)? In this case it is clear that HMCE can have a significantly smaller solution than MCE, as a fixed circuit may contain a large "useless" component that does not affect circuit computation, and thus heterogeneous supply voltages may be employed to spend little or no energy on that part of the circuit. However, it is still interesting to consider whether, for a very natural circuit that computes some function or relation, the solution to HMCE is significantly smaller than the solution to MCE.

#### 1.1 RELATED WORK

As far as we are aware, this is the first work to consider energy-efficient circuit design from a theoretical perspective; However, there has been a significant amount of related work in the area fault-tolerant circuit design, which we summarize here. Von Neumann [30] first introduced the model where each gate of the circuit fails with some independent, fixed probability  $\epsilon$ . Von Neumann also informally argued that any function that can be computed by a faultless circuit of size *s* can be computed by a faulty circuit of size  $O(s \log s)$ . Dobrushin and Ortyukov [15] proved this result formally. Subsequently, Pippenger [25] improved this result by giving explicit, rather than probabilistic, constructions of certain aspects of the proof, resulting in an explicit construction of a fault-tolerant circuit for some fixed values of  $\epsilon$ . Finally, Gács [17] proved this result in full generality for arbitrary values of  $\epsilon$ . Pippenger [25] also proved that any function can be computed by a network of  $O(2^n/n)$  faulty gates. When combined with Shannon's result that almost all functions require  $\Omega(2^n/n)$  faultless gates [28], this shows that almost all functions require only a constant factor increase in circuit size when the gates are faulty.

The remaining related work is in developing lower bounds on faulty circuit size. Dobrushin and Ortyukov [14] attempted to show that any function of sensitivity m requires at least  $\Omega(m \log m)$  faulty gates to compute, however their proof contains errors, which were first pointed out by Pippenger et al. [26]. Gács and Gál [18] proved the lower bound correctly, using a similar idea to [14] but proving new lemmas for the analysis. Reischuk and Schmeltz [27] independently gave another proof of the lower bound using decision trees.

The general idea of trading accuracy of a hardware circuit and computing architecture for energy savings dates back to at least [24]. The paper [16] gives an excellent survey on Near-Threshold Computing. According to [16], the three main barriers to the widespread use of Near-Threshold computing are:

- 1. **Performance Loss:** Circuits supplied a Near-Threshold voltage perform orders of magnitude slower than circuits supplied the nominal voltage.

- 2. Increased Performance Variation: Circuits supplied the nominal voltage experience a roughly 1.5X performance variation, while circuits supplied a Near-Threshold voltage experience up to a 20X performance variation.

- 3. Increased Functional Failure: Circuits experience an increased sensitivity to process, temperature, and voltage, resulting in an increased rate of functional failures.

While significant research has been performed to mitigate all of these barriers, the work presented in this dissertation is meant to provide the theoretical basis for solving the third problem, that of increased functional failure. From a system-design perspective, the problem of increased functional failures has been most pronounced in SRAM, and thus much of the research on this problem has been focused on making SRAM robust when supplied a Near-Threshold voltage [16]. As previously mentioned, some research has been in designing SRAM bitcells that are more fault tolerant, for example with 8 or 10 transistors, rather than the standard 6 transistor design [11, 12]. Other work has been in designing SRAM cache architectures using error-correcting codes, redundancy, and other methods to ensure cache reliability, at the cost of increased cache size or latency [1, 3, 13, 21, 22, 31, 32].

As an example of a technology that has at least the spirit of Near-Threshold Computing,

IBM's production POWER7 servers use a technique called *Guardband* to save energy by dynamically lowering operating voltage [4].

#### 1.2 OUR CONTRIBUTIONS

We discuss our main results in the following sections.

#### 1.2.1 General Bounds on Circuits With Constant Error

We begin in Chapter 3 by showing general lower and upper bounds on the amount of energy required by a circuit to compute a given relation, when the reliability parameter  $\delta$  is a fixed constant.

General lower bound on the energy to compute a function: We first show in Section 3.1 the following lower bound on the amount of energy required to compute any relation:

**Theorem 5.** Let  $\delta < 1/4$ , and let C be a circuit that computes a relation h of sensitivity m with probability at least  $1 - \delta$ . Then C requires  $\Omega\left(m \log\left(m \frac{1-2\sqrt{\delta}}{\delta}\right)\right)$  energy.

Gács and Gál [18], and independently Reischuk and Schmeltz [27], show that any Boolean function f with sensitivity m (roughly the number of input bits which affect the output) requires a circuit of size  $\Omega(m \log m)$  to be reliably computed when the gates of the circuit fail independently with a fixed positive probability. We modify the techniques in [18] to prove our lower bound on the energy required by any circuit that computes a relation with sensitivity m. The proof consists of two main parts. The first part is to consider a failure model that is equivalent in terms of the reliability of any part of the circuit, but where failures occur, and energy is consumed, on the wires of the circuit as well as at the gates. The second part considers the sensitive input bits to the circuit: If there are too few wires emanating from these input bits, then the probability that failures will cause the circuit to compute as if one of the sensitive bits were flipped is too large, and the output would be incorrect with too high a probability. An additional technical hurdle to obtaining our result is that supply voltages may be heterogeneous, so, unlike the setting of the previous work, different gates of the same circuit may use different amounts of energy, and thus fail with different probabilities.

General upper bound on the energy to compute a function: In Section 3.2, we extend the classic upper bound on circuit size from the fault-tolerant circuit literature to obtain the following upper bound on circuit energy consumption:

**Theorem 6.** Given a reliable circuit C of size s, and a fixed constant  $\delta > 0$ , it is possible to construct a circuit C' with homogeneous voltage supplies that uses  $O(s \log(s))$  energy and that computes the same function computed by C with probability at least  $1 - \delta$ .

Von Neumann [30] showed that given a Boolean function f and a circuit of size s which computes f, a circuit of size  $O(s \log s)$  is sufficient for computing f correctly with high probability when the gates of the circuit fail independently with a fixed positive probability. Using techniques from [30] and from [17, 25], we show that a relation h that is computable by a circuit of size s can, with probability at least  $1 - \delta$ , be computed by a circuit of faulty gates using  $O(s \log(s))$  energy. In our construction, the supply voltages are homogeneous. The construction works by introducing a  $\Theta(\log s)$  factor of redundancy in the circuit, and each gate of the circuit is replaced by a gadget. The input to each gadget is  $\Theta(\log s)$  wires per original gate input, most of which, with high probability, carry the same input bit as if the computation were being performed in the original, faultless circuit. The gadget contains  $\Theta(\log s)$  copies of the original gate, as well as a component of size  $\Theta(\log s)$  that ensures that the fraction of incorrect wires exiting the gadget is sufficiently low with high probability.

#### **1.2.2** Introduction to Heterogeneity

In Chapter 4, we consider simple cases in which allowing heterogeneous supply voltages both does and does not yield asymptotic decreases in energy.

Settings where heterogeneous supply voltages are not beneficial: In Section 4.1 we observe that, when  $\delta$  is restricted to a fixed constant, there are relations, namely the parity function, for which allowing heterogeneous supply voltages will not allow one to achieve a circuit design that uses asymptotically less energy than is achievable by a circuit design with

homogeneous supply voltages:

**Theorem 7.** Let  $\delta < 1/4$  be a fixed constant. The energy used by any circuit that computes the parity function with probability  $1 - \delta$  is  $\Omega(n \log(n))$ , and this is achievable by a circuit with homogeneous supply voltages.

Intuitively, the parity function has such high sensitivity that every gate in any reasonable circuit will be of equal importance, so nothing can be gained by heterogeneous supply voltages. This immediately implies that in the setting where  $\delta$  is a fixed constant, heterogeneity doesn't significantly benefit some functions. That is, for these functions the optimal solution to MEC and the optimal solution to HMEC use asymptotically the same energy (up to constants), which also implies that there are circuits for these functions such that the optimal solution to MCE and the optimal solution to HMCE use asymptotically the same energy. Formally, the proof is a corollary of our lower and upper bounds from Sections 3.1 and 3.2.

A setting where heterogeneous supply voltages is beneficial: In contrast, in Section 4.2 we give a natural example where allowing heterogeneous supply voltages allows one to use asymptotically less energy than would be achievable using homogeneous supply voltages. In particular, we consider a natural super-majority relation called LSR, which outputs the majority of the input bits if this majority is sufficiently large, and the most natural circuit that computes this relation, a balanced tree of majority gates, and obtain the following theorem:

**Theorem 8.** Let  $E_1(\delta)$  be the optimal energy consumption of the majority tree on n leaves with homogeneous supply voltages that computes LSR with probability  $1 - \delta$ , and  $E_2(\delta)$  be the optimal energy consumption of the same if supply voltages may be heterogeneous. Then, for  $\delta' = \frac{2}{\log_3 n}$ , it holds that  $\frac{E_1(\delta')}{E_2(\delta')} = \omega(1)$ .

We show that for homogeneous supply voltages the energy required by this circuit to compute LSR is  $\Omega(n \log^2(\delta))$ , where *n* is the number of input bits. We then show that if supply voltages can be heterogeneous, this circuit can compute LSR using energy  $O(n + 3^{1/\delta} \log^2(\delta/10))$ , which is asymptotically less than  $n \log^2(\delta)$  if  $\delta \to 0$  as  $n \to \infty$ . This implies that there are quite simple relations and circuits for which the optimal solution to HMCE uses asymptotically less energy than the optimal solution to MCE. The heterogeneous voltage setting is quite intuitive: Since we only care about a super-majority, the gates far from the output gate can sustain a small but constant fraction of failures without affecting the output, while the gates closer to the output, of which there are a comparatively small number, affect the output much more dramatically, so we use a large amount of energy to ensure they do not fail. For the proof, we lower bound the energy used by any homogeneous setting by observing that in any homogeneous setting, gates, and in particular the output gate, cannot fail with probability greater than  $\delta$ . We give an explicit setting of voltages for the heterogeneous upper bound, and use recurrence relations to bound the probabilities of "bad" failure profiles, to show that, with that heterogeneous setting, the circuit outputs correctly with probability at least  $1 - \delta$ .

#### 1.2.3 Hardness Results

Chapter 5 discusses complexity theoretic barriers to energy-efficient circuit design. Ideally, a circuit designer would like to solve MEC, but, for many functions, the ability to even approximately bound optimal circuit sizes is essentially at least as hard as the P vs. NP question,<sup>1</sup> and is untouchable with current mathematical knowledge. In order to avoid this mathematical barrier, we instead consider MCE. We show that this problem is NPhard. Thus if  $P \neq NP$  then there is no efficient method for computing the optimal supply voltage setting. The standard fallback approach for NP-hard optimization problems is to seek algorithms that are guaranteed to produce solutions with optimal/good relative error compared to the optimal solution. In our case, an algorithm A has approximation ratio c (or equivalently worst-case relative error c - 1) if for all inputs, the energy used by the circuit with the supply voltage setting given by A is at most c times the optimal minimum energy.

The approximation ratio of the traditional approach: We show in Section 5.1 that the approximation ratio of the traditional algorithm, which sets the supply voltages such that the probability that even a single gate fails is at most  $\delta$ , is  $O(\log^2 s)$ , where s is the number of gates in the circuit:

<sup>&</sup>lt;sup>1</sup>If one could prove that your favorite NP-complete problem required super-polynomially many gates to compute, this would prove  $P \neq NP$ .

**Theorem 9.** The traditional approach is an  $O(\log^2 s)$ -approximation for MCE.

Similar to the lower bound on the energy used by homogeneous voltage settings in Section 4.2, we can upper bound the failure probability of any homogeneous setting by  $\delta$ . The result follows by noting that setting the failure probability to  $\delta/s$  uses  $\Theta(\log^2 s)$  more energy, and that with this failure probability, the probability that even one gate fails is at most  $\delta$ .

Hardness of improving upon the traditional approach: In contrast, we show in Section 5.2 that it is NP-hard to approximate MCE to within a factor polynomially less than  $O(\log^2 s)$ :

# **Theorem 10.** It is NP-hard to $O(\log^{2-\gamma} s)$ -approximate MCE for any $\gamma > 0$ .

The circuit used in the reduction is the natural circuit for a 3SAT instance. The input bits represent the boolean settings of the variables, which are negated as appropriate and fed into OR gates, representing the clauses. The output to these OR gates is then fed into a tree of AND gates, and thus if the variable assignment satisfies the 3SAT formula, all of the inputs of the AND tree are 1's, and the circuit outputs 1; Otherwise, the circuit outputs 0. Intuitively, the AND tree is very prone to failures, and is very likely to output 0 if even a few gates of the AND tree fail, regardless of the input. Because of this, in the case that the 3SAT formula is satisfiable, the failure rate must be low enough such that every gate of the AND tree works correctly with sufficiently high probability, and so the energy must be high. On the other hand, if the 3SAT formula is not satisfiable, any input to the circuit should output 0, and thus a small number of failures in the AND tree do not significantly decrease the probability that it outputs 0. We also observe here that, using essentially the same proof as MCE, one can show HMCE is at least as hard in terms of approximation as MCE, as the ability to supply the gates of the AND tree of the 3SAT circuit different voltages yields no asymptotic benefit.

Generalization of hardness to other failure models: One might be concerned that this hardness is the result of how we specifically model functional failures in circuits, rather than due to the complexity of circuits; In order to provide evidence that the hardness does indeed come from the complexity of circuits, we prove that the same result holds in another model, the *0-default model*, that is somewhat different and, perhaps, closer to how failures occur in real circuits: In the 0-default model failures cause wires to carry a "default" 0 bit. In fact, we even show in Section 5.3 that it is NP-Hard in this model to even determine whether a circuit computes correctly on a fixed input.

**Theorem 11.** In the 0-default model, it is NP-hard to  $O(\log^{2-\gamma} s)$ -approximate MCE for any  $\gamma > 0$ . Additionally, it is NP-Hard to determine if a circuit computes correctly on a fixed input.

Bypassing hardness via specific families of circuits: Putting these results together, we see that there is a complexity theoretic obstacle to achieving more energy efficient circuits by using lower supply voltages than one obtains by the traditional high supply voltage approach. More precisely, if one could find a computationally efficient algorithm for setting supply voltages that has better worst-case relative error than the traditional approach, then P=NP. So, assuming  $P\neq NP$ , any proposed algorithm would either not have worst-case relative error better than the traditional approach, or would take super-polynomial time on some circuits. But of course the standard caveat applies here: as NP-hardness is a worstcase concept, this doesn't mean that one cannot beat the energy used by the traditional approach for particular circuits of interest. As a small step in the direction of showing that for circuits of interest MCE may be approachable, we show in Section 5.4 that there is an efficient algorithm to verify whether a particular setting of the supply voltage achieves the desired error bound if the circuit is a tree.

**Lemma 12.** Let C be a circuit with a tree as the underlying graph, and suppose each gate g of the circuit fails with probability  $\epsilon_g$ . Then there is a polynomial time algorithm to determine if C computes correctly with probability at least  $1 - \delta$ .

This result hints at the hardness of MCE coming from "cycles" in the circuit. In Section 5.5 we make the curious observation that there are circuits where the reliability of the output is not monotone in the reliability of the gates. Understanding this non-monotonicity seems to be the key to being able to solve MCE for circuits that are trees.

#### 1.2.4 Almost All Functions Require Exponential Energy

Chapter 6 discusses the minimum amount of energy required to compute almost all, i.e., a 1 - o(1) fraction of, functions. In principle, for every function f, MEC has some solution. Though for many functions finding the solution to MEC may be untouchable due to the previously discussed complexity-theoretic barriers, one might hope to determine the amount of energy required by an average Boolean function. Pippenger showed that all Boolean functions can be computed by circuit layouts with  $O(2^n/n)$  noisy gates [25]. Using that construction, it immediately follows that all Boolean functions can be computed by some circuit that uses  $O(2^n/n)$  energy assuming  $\delta$  is a fixed constant. We show in Chapter 6 that this result is tight for almost all functions, i.e.

**Theorem 13.** For any  $0 < \delta < 1/2$ , almost all Boolean functions on n variables require circuits that use  $\Omega(2^n/n)$  energy.

To develop intuition about this result, it is necessary to consider more precisely the relationship between the voltage supplied a gate and the probability that it actually fails. Let  $\epsilon$  be the function mapping voltage to error probability. In the *exact failure model*, when a gate is supplied a voltage v, it fails with probability *exactly*  $\epsilon(v)$ . On the other hand, in the *bounded failure model*, the gate fails with probability *at most*  $\epsilon(v)$ . The bounded failure model is arguably more realistic, in the sense that the circuit designer may not know exactly the probability that a gate will fail, and the failure probability may vary with time or environmental conditions. On the other hand, the exact failure model allows the circuit designer to use component failures as a source of randomness, and thus perhaps perform computations more efficiently. All of our results discussed thus far have held for both exact and bounded failure models.

Circuits that can compute many functions: The main component of the proof that almost all functions require exponential energy is to show that almost all functions require circuit layouts with exponentially many gates. In the bounded failure model, this directly follows from Shannon's result that almost all functions require circuits of exponential size [28], since in the bounded failure model a circuit must compute correctly even if no gates fail. The exact failure model is less straightforward, as, by modifying the voltage supplied to every gate, a single circuit layout may be able to compute a number of different functions. In fact, we have the following theorem for circuits with homogeneous supply voltages:

**Theorem 14.** For any  $0 < \delta < 1/2$  and  $n \in \mathbb{N}$ , there exists a circuit with n inputs of size O(n) that computes  $\Omega\left(\frac{\log n}{\log(\frac{1}{\delta}\log n)}\right)$  different functions with probability at least  $1 - \delta$ .

The circuit is composed of trees of AND gates of varying size, and one can see how this circuit computes multiple functions by observing that, as the failure rate increases, a tree of AND gates will switch from computing the AND function on its input bits, to computing the 0 function.

If supply voltages are allowed to be heterogeneous, we obtain the following theorem:

**Theorem 15.** For any  $0 < \delta < 1/2$  and  $n \in \mathbb{N}$ , there exists a circuit C with n inputs of size  $O(n^2)$  that computes  $\Omega(3^n)$  different functions with probability at least  $1 - \delta$ .

The circuit in this proof is a modification on the natural circuit for a 3CNF formula: Instead of connecting the literals in each clause directly to an input or its negation, for each literal, the output of a series of AND trees (each of which may output 1 or 0, depending on the voltage settings) specifies which input variable should be represented by that literal, and whether or not it should be negated. Thus, by modifying supply voltages, the circuit is able to compute any function on n inputs that can be represented by a 3CNF formula with a fixed number of fixed-sized clauses.

Upper bounds on the number of functions a circuit can compute: Despite the existence of circuits that can compute many functions, we are able to provide, both for homogeneous and heterogeneous supply voltages, a sufficiently small upper bound on the number of functions that a single circuit can compute:

**Lemma 16.** A circuit C on n inputs with s gates can compute at most  $s2^n + 1$  functions if supply voltages must be homogeneous, and at most  $(8e2^n)^s$  functions if supply voltages may be heterogeneous.

Though the proof for heterogeneous supply voltages is somewhat more complicated than the one for homogeneous supply voltages, both follow primarily from two observations: (1) The probability a fixed circuit outputs a 1 on a fixed input can be written as a polynomial in the failure rate of each gate of the circuit, and (2) A circuit with a fixed setting of supply voltages only computes a function when, on all inputs, it outputs either 1 or 0 with probability at least  $1-\delta$ . Combining these two, we observe that a circuit with a set of supply voltages only computes a function when, for each polynomial associated with the probability of outputting a 1 on an input, that polynomial is above  $1-\delta$  or below  $\delta$ . With this in hand, we can apply results from calculus and geometry to obtain the upper bound on the number of functions a single circuit can compute.

Equivalence of exponential energy and exponentially many noisy gates: These results leave open the possibility that some Boolean functions that do not require circuits with exponentially many gates still require exponential energy. For example it could be the case that for some function the energy optimal circuit has sub-exponentially many gates, with many of them requiring exponential energy. We show that this is not the case:

**Lemma 17.** A Boolean function f requires circuits that use exponential energy if and only if it requires circuits that contain exponentially many gates.

The proof follows by noting that, for any circuit, setting supply voltages such that the energy-per-gate is polynomial in the circuit size is sufficient for no gate in a circuit to fail, and thus using a higher energy-per-gate can provide no additional benefit.

#### 1.2.5 The Power of Heterogeneity to Reduce Energy

In Chapter 7, we explore the power of heterogeneous supply voltages to asymptotically save energy over any circuit using homogeneous supply voltages when computing certain functions or relations. In this chapter, we consider the case when the error parameter  $\delta$  vanishes as the number of the inputs to the function increases. Previously, in Chapter 3, we focused on the case when  $\delta$  is a fixed constant. This intuitively makes sense, as a circuit designer may calculate the requirements for  $\delta$ , and design the circuit based on that. However, it is also reasonable to consider the case when  $\delta$  must vanish as the number of inputs to the circuit increases: As the circuit size increases, circuit failures may become more expensive to recover from; Additionally, a single circuit may be a component of a larger system, and as this system grows, it will not function reliably enough if the the failure probability of the components it is made up of does not decrease. Many functions benefit from heterogeneous supply voltages: Perhaps surprisingly given the general upper and lower bounds in Chapter 3 when  $\delta$  is a fixed constant, which are tight for many natural functions (e.g., parity), we show that, if the circuit error probability must vanish as the number of inputs increases, there is a natural class of functions (that includes parity) which can be computed with asymptotically less energy if supply voltages are allowed to be heterogeneous.

**Theorem 18.** For any function f with minimum circuit size s, for any constant c > 0, if  $\delta = 1/s^c$ , then every circuit with homogeneous supply voltages computing f uses  $\Omega(s \log^2(s))$  energy, and there exists a circuit with heterogeneous supply voltages using  $O(s \log s)$  energy.

If we replace s by  $\Theta(n)$ , where n is the number of inputs to the function, then the above theorem applies to all functions with circuits of size linear in the number of inputs. Thus, for such functions, the solution to HMEC is asymptotically less than the solution to MEC by a factor of  $\Omega(\log n)$  when  $\delta$  is polynomial in 1/n. In order to show this, we first provide a  $\Omega(s \log^2 s)$  lower bound on the energy used by any circuit using homogeneous supply voltages, which can be obtained by noting that the voltage setting must be such that the output gate does not fail with probability more than  $\delta$ . On the other hand, we provide a general circuit construction and heterogeneous voltage setting for functions in this class that uses  $O(s \log s)$  energy. Intuitively, in a manner similar to the upper bound in Chapter 3, we replace each gate of a faultless circuit with a fault-tolerant gadget, and supply low voltages to these gates, with the result that the failure rate for each gate of each gadget is a constant. We are left at the end with a (relatively small) set of wires, such that, with high probability, the majority of these wires carry the correct output bit. We then use a majority circuit, with voltages set sufficiently high so that with high probability no gate fails, and thus obtain the correct output bit with high enough probability.

Limit for many functions on the energy savings via heterogeneous supply voltages: We then show that for functions that have circuits of linear size and obtain a  $\Omega(\log n)$  energy savings via heterogeneous supply voltages, this energy savings is tight, i.e., the solution to HMEC is only a factor of  $\Theta(\log n)$  less than the solution to MEC, as long as most input bits are non-degenerate. An input bit to a function is *non-degenerate* if, roughly, there is some input to the function where the value of that bit matters.

**Theorem 19.** Let f be a function with b non-degenerate input bits. Then, for any  $0 < \delta < 1/2$ , any circuit C that computes f with error at most  $\delta$  requires  $\Omega(b \log 1/\delta)$  energy.

We show that for any function, each input bit that is non-degenerate essentially must use  $\Theta(\log n)$  energy by itself, or else the output cannot possibly be correct with high enough probability. If the number of non-degenerate bits of a function is a constant fraction of n, then even circuits with heterogeneous supply voltages computing that function must use  $\Omega(n \log n)$  energy when  $\delta = 1/n$ .

Relations gaining greater energy savings via heterogeneous supply voltages: In principle, a circuit may compute a relation, rather than a function, as, for example, the proper functioning of the system may guarantee that the circuit does not receive certain inputs. This raises the question of whether heterogeneous supply voltages can provide a greater energy savings over homogeneous supply voltages when computing relations rather than functions, i.e., whether a circuit with heterogeneous supply voltages that computes a relation can save  $\omega(\log n)$  energy over any circuit with homogeneous supply voltages computing that relation. We answer this question in the positive.

**Theorem 20.** Suppose  $\delta = 1/n^c$  for some constant c > 0. Then there is a relation that can be computed by a heterogeneous circuit using O(n) energy, but for homogeneous circuits requires  $\Omega(n \log^2 n)$  energy.

The relation that obtains the  $\Theta(\log^2 n)$  energy savings by using heterogeneous supply voltages is a natural supermajority relation. This  $\Theta(\log^2 n)$  energy savings is the best savings possible for computing any relation that requires a faultless circuit of size O(n) that must access  $\Theta(n)$  of the input bits. Our lower bound on the energy used by any circuit with a homogeneous voltage setting is similar to our previous such lower bounds. The upper bound using a heterogeneous voltage setting modifies a standard majority circuit, and benefits from the fact that, in such a circuit, failures occuring closer to the inputs have only a small effect on the output of the circuit. As we traverse down the circuit, failures become more problematic, so we increase the redundancy linearly in order to make failures more rare, but since the number of gates decreases exponentially, adding this redundancy only increases the circuit size by a constant.

#### 2.0 MODEL, DEFINITIONS, AND NOTATION

We now make formal definitions. A Boolean relation h is a map from  $\{0,1\}^n$  to  $\{0,1\}^n$  to  $\{0,1\}^n$  where each input is mapped to 0, 1, or both 0 and 1. If  $x \in \{0,1\}^n$  is mapped to both 0 and 1, this can be thought of as "don't care" (for example because the input x should not occur in a correctly functioning system). A Boolean function f is a Boolean relation where each input is uniquely mapped to either 0 or 1. For any input  $x \in \{0,1\}^n$ , denote by  $x^{\ell}$  the input that has the same bits as x, except for the  $\ell$ -th bit, which is flipped. A Boolean relation h is sensitive on the  $\ell$ -th bit of x if neither h(x) nor  $h(x^{\ell})$  is mapped to both 0 and 1, and  $h(x) \neq h(x^{\ell})$ . The sensitivity of h on x is the number of bits of x that h is sensitive on. The sensitivity of h is the maximum over all x of the sensitivity of h on x.

A gate is a function  $g : \{0,1\}^{n_g} \to \{0,1\}$ , where  $n_g$  is the number of inputs (i.e., the fan-in) of the gate. We assume that the maximum fan-in is at most a constant. A Boolean circuit C with n inputs is a directed acyclic graph in which there are n nodes with no incoming edges that each output one of the input bits, and every other node is a gate. The size of a circuit, denoted by s, is the number of gates it contains. For any  $I \in \{0,1\}^n$ , we denote by C(I) the output of the Boolean function computed by Boolean circuit layout C.

In this paper we consider circuits  $(C, \bar{v})$  that consist of both a traditional circuit layout C as well as a vector of supply voltages  $\bar{v}$ , one for each gate of C. Every gate g is supplied with a voltage  $v_g$ . We say that the supply voltages (and, as shorthand, circuit) are homogeneous when every gate of the circuit is supplied with the same voltage, and heterogeneous otherwise. We say that a gate fails when it produces an incorrect output, that is, when given an input x it produces an output other than g(x).

The benefits of allowing the circuit designer to control the voltage depends both on the rate at which failures decrease as voltages increase as well as whether or not failure rates are

previously known. If the circuit designer knows exactly the probability that a component will fail when supplied a specific voltage, then this may be used as a source of randomness, which could in theory allow for more efficient computation. Because of this, we consider two different failure models. In the exact failure model, each non-input gate q fails independently with probability exactly  $\epsilon(v_g)$ . In contrast, in the bounded failure model, every non-input gate g fails with probability at most  $\epsilon(v_q)$  (we specify the failure model only for results that do not hold for both). While the bounded failure model perhaps more closely models reality, in the sense that the actual error rate of a circuit component may be unknown or may vary with time or environment, the exact failure model gives the circuit designer more power. In both models we assume  $\epsilon : \mathbb{R}^+ \to (0, 1/2)$  is a decreasing function. The voltage supplied to a gate determines both its energy usage and its failure probability, thus we define  $\epsilon_g := \epsilon(v_g)$  and drop all future formal reference to supply voltages. Finally we assume there is a decreasing, nonnegative failure-to-energy function  $E(\epsilon)$  that maps the failure probability  $\epsilon$  to the energy used by a gate. The energy required by a circuit C is simply the aggregate energy used by the gates,  $\sum_{g \in C} E(\epsilon_g)$  in our notation. Throughout the majority of this dissertation we assume  $E(\epsilon) = \Theta(\log^2(1/\epsilon))$ ; Throughout, in the appropriate locations, we discuss how to generalize our results to other failure-to-energy functions.

A gate that never fails is said to be *reliable* or *faultless*. Given a value  $\delta \in (0, 1/2)$ ( $\delta$  may not be constant), a circuit  $(C, \bar{\epsilon})$  that computes a Boolean relation h is said to be  $(1 - \delta)$ -*reliable* if for every input I on which h(I) is not both 0 and 1, C(I) equals h(I) with probability at least  $1 - \delta$ . We say that C can compute  $\ell$  different functions  $(1 - \delta)$ -reliably if there exists  $\bar{\epsilon}_1, \bar{\epsilon}_2, \ldots, \bar{\epsilon}_\ell \in (0, 1/2)^{|C|}$  and different functions  $f_1, f_2, \ldots, f_\ell$  such that  $(C, \bar{\epsilon}_i)$  is  $(1 - \delta)$ -reliable for function  $f_i$ . We say that a circuit is *reliable* or *faultless* if it is 1-reliable (for example, because all its gates are reliable). We say that the circuit is  $(\epsilon, \delta)$ -reliable if it is  $(1 - \delta)$ -reliable when gates fail with probability exactly  $\epsilon$ .

#### 3.0 GENERAL ENERGY UPPER AND LOWER BOUNDS

In this chapter, we prove a general lower bound, in terms of sensitivity, and a general upper bound, in terms of circuit size, on the amount of energy required to compute a function.

#### 3.1 A GENERAL ENERGY LOWER BOUND

Our main goal in this section is to prove Theorem 21, which roughly states that  $\Omega(m \log m)$ energy is necessary to compute a relation with sensitivity m.

**Theorem 21.** Let  $\delta < 1/4$ , and let C be a circuit that  $(1 - \delta)$ -reliably computes a relation h of sensitivity m. If each gate g of C fails independently with probability  $\epsilon_g$ , and incurs an energy consumption of  $E(\epsilon_g)$ , with E being a proper failure-to-energy function, then C requires

$$\Omega\left(m\log\left(m\frac{1-2\sqrt{\delta}}{\delta}\right)\right)$$

energy in order to  $(1 - \delta)$ -reliably compute h.

The outline of this section is as follows. First, we define proper failure-to-energy functions (Definition 22), and discuss why proper functions are natural. Then, similarly to [18], we show how to translate our problem to an equivalent problem where the failures occur not only on gates, but on wires as well. This is formalized in Statement 23, which is implied by the proof of Lemma 3.1 in [14], and is also used in [18]. Lemma 26 then gives a lower bound on the energy necessary for  $(1 - \delta)$ -reliable circuits within this new model with wire failures. The proof is based on the proof of Theorem 3.1 in [18], and uses a series of inequalities that relate the probability of an input being incorrectly transmitted to the probability of the

circuit being incorrect. Using this, we can write the problem as a single-variable optimization problem and use standard techniques to give the desired lower bound. Finally, to prove Theorem 21 we show that given a  $(1 - \delta)$ -reliable circuit C in our original model without wire failures, we can create a  $(1 - \delta)$ -reliable circuit C' in the new model with wire failures, where the energy consumptions of C and C' differ only by a constant.

**Definition 22.** A failure-to-energy function E is called proper when it satisfies the four following properties:

- 1. E is nonincreasing,

- 2.  $\lim_{\epsilon \to 0^+} E(\epsilon)/(\log 1/\epsilon) > 0$ ,

- 3.  $\lim_{\epsilon \to 1/2^{-}} E(\epsilon) > 0$ ,

- 4.  $E(\epsilon_1) + E(\epsilon_2) \ge 2E(\sqrt{\epsilon_1 \epsilon_2})$  for all  $\epsilon_1, \epsilon_2 \in (0, 1/2)$ .

The first and third restrictions are natural, since they just require that the energy used decreases, but never becomes zero, as the probability of failure of a gate increases. The second property states that the energy must increase "quickly enough" as the probability of a gate's failure tends to 0, which is necessary in order to have any energy saving over gates that never (or almost never) fail. The last property provides a convexity constraint on the function P. We point out that failure-to-energy functions typically observed in real gates fall within this class of proper failure-to-energy functions [16, 20].

Statement 23 ([14]). Let g be a gate with fan-in  $n_g$ , in a circuit C where both gates and wires may fail. Furthermore, let  $\epsilon \in (0, 1/2), \zeta_g \in [0, \epsilon/n_g]$  and let g(t) be the output of gate g assuming that its input-wires receive input t, and both g and g's input-wires are reliable. Then there exists a unique value  $\eta_g(y, \zeta_g) \in [0, 1]$  such that if

- the input wires of g fail independently with probability  $\zeta_g$ , and

- gate g fails with probability  $\eta_g(y, \zeta_g)$  when the gate receives input y,

then the probability that g does not output g(t) is equal to  $\epsilon$ .

Note that in Statement 23, since we can now have failures on wires, the input y received by a gate g may be different than the input t received by the corresponding wires.

We need the following definition and technical lemma.

**Definition 24.** Given  $x_{1,1}, x_{1,2}, \ldots, x_{1,n} \in \mathbb{R}$ , we recursively define a sequence of numbers as follows. Let  $m_j^u = \arg \max_i x_{j,i}$  and  $m_j^l = \arg \min_i x_{j,i}$ . Then, for all  $i \neq \{m_j^u, m_j^l\}$ , let  $x_{(j+1),i} = x_{j,i}$ , and let  $x_{(j+1),m_j^u} = x_{(j+1),m_j^l} = \sqrt{x_{j,m_j^u} x_{j,m_j^l}}$ .

**Lemma 25.** Let  $a_1, a_2, \ldots$  be a sequence of numbers such that  $a_j = x_{j,m_j^u} - x_{j,m_j^l}$ , with the terms  $x_{j,m_j^u}$  and  $x_{j,m_j^l}$  as defined above. Then,

$$\lim_{j \to \infty} a_j = 0$$

*Proof.* First note that within the n+1-th recursive step of the above construction there must be some index  $i^*$  that has been chosen as  $m_j^l$  twice. Let  $k_1$  and  $k_2$  denote the recursive step during which  $i^*$  is chosen for the first and second time, respectively. More formally, consider  $S_l = \bigcup_{j \leq l} \{m_j^l\}$ . Then,  $k_2$  is the minimum index  $j \leq n+1$  such that  $\{m_j^l\} \cap S_{j-1} \neq \emptyset$ , and  $k_1$  is the index  $j < k_2$  such that  $m_{k_2}^l \cap S_j \neq \emptyset$ .

For notational convenience, we denote  $x_{k_1,m_{k_1}^u}$  with  $x_h$  and  $x_{k_1,m_{k_1}^l}$  with  $x_l$ . Note that the sequence formed by  $x_{j,m_j^u}$  is monotonically decreasing in j, and similarly  $x_{j,m_j^2}$  is monotonically increasing in j. Then,

$$a_{k_2} = x_{k_2, m_{k_2}^u} - x_{k_2, m_{k_2}^l} = x_{k_2, m_{k_2}^u} - \sqrt{x_h x_l} \le x_h - \sqrt{x_h x_l}.$$

Therefore,

$$\frac{a_{k_2}}{a_{k_1}} \le \frac{x_h - \sqrt{x_h x_l}}{x_h - x_l} = \frac{\sqrt{x_h} \left(\sqrt{x_h} - \sqrt{x_l}\right)}{x_h - x_l} = \frac{\sqrt{x_h}}{\sqrt{x_h} + \sqrt{x_l}}$$

Rewriting this, we obtain  $a_{k_2} \leq a_{k_1}/(1 + \sqrt{x_l/x_h})$ . Then, by observing that the sequence of  $a_i$ 's is monotonically decreasing, because the sequence formed by  $x_{j,m_j^u}$  is monotonically decreasing and  $x_{j,m_j^2}$  is monotonically increasing in j, we conclude that

$$a_{k_2} \le \frac{a_1}{\left(1 + \sqrt{x_{m_1^l}/x_{m_1^u}}\right)}$$

It follows that, for any positive integer x,  $a_{xn+1} \leq a_1/(1 + \sqrt{x_{m_1^l}/x_{m_1^u}})^x$ , and therefore  $\lim_{j\to\infty} a_j = 0$ .

**Lemma 26.** Let *E* be a proper failure-to-energy function, and let *C* be a circuit that  $(1-\delta)$ reliably computes a relation *h* of sensitivity *m*. If (*i*) each gate *g* of *C* fails independently

with probability  $\eta_g(y, \zeta_g)$  when receiving input *y*, (*ii*) *g* incurs an energy consumption of zero,

and (*iii*) each wire *i* entering *g* fails independently with probability  $\zeta_g \in (0, 1/4)$  and incurs

an energy usage of  $f(\zeta_g)$ , then *C* requires

$$\Omega\left(m\log\left(m\frac{1-2\sqrt{\delta}}{\delta}\right)\right)$$

energy in order to  $(1 - \delta)$ -reliably compute h.

Proof. We start by rephrasing our problem after borrowing a constraint on the number of wires and some notation from [18]. Specifically, let z be an input such that h has maximum sensitivity on z. Let  $S \subset \{1, 2, ..., n\}$  be the set of indexes so that  $\ell \in S$  if and only if h is sensitive to the  $\ell$ -th bit on input z. Then |S| = m, where m is the sensitivity of h. For each  $\ell \in S$  denote by  $B_{\ell}$  the set of all wires originating from the  $\ell$ -th input of the circuit. Let  $w_{\ell} = |B_{\ell}|$ . For any set  $\beta \subset B_{\ell}$ , let  $H(\beta)$  be the event that the wires belonging to  $\beta$  fail and the other wires of  $B_{\ell}$  are correct. Denote by  $\beta_{\ell}$  the subset of  $B_{\ell}$  where

$$\max_{\beta \subset B_{\ell}} \Pr[C(z^{\ell}) = h(z^{\ell}) \text{ s.t. } H(\beta)]$$

is obtained, where  $C(z^{\ell})$  is a random variable for the output of the circuit given input  $z^{\ell}$ . Finally, let  $H_{\ell} = H(B_{\ell} \setminus \beta_{\ell})$ . Note that since wires can now fail with different probabilities, we have that,

$$\Pr[H_{\ell}] = \prod_{i \in \beta_{\ell}} (1 - \zeta_i) \prod_{i \notin \beta_{\ell}} \zeta_i \ge \prod_{i \in B_{\ell}} \zeta_i$$

It follows from Inequalities (5) and (6) of [18] that

$$\frac{\delta}{1 - 2\sqrt{\delta}} \ge \sum_{\ell \in S} \prod_{i \in B_{\ell}} \zeta_i$$

and as in [18], using the inequality of arithmetic and geometric means, we have

$$\frac{\delta}{1 - 2\sqrt{\delta}} \ge m \left(\prod_{\ell \in S, i \in B_{\ell}} \zeta_i\right)^{1/m}$$

Rewriting this to isolate the product term, we have

$$\prod_{\ell \in S, i \in B_{\ell}} \zeta_i \le \left(\frac{\delta}{m(1-2\sqrt{\delta})}\right)^m.$$

Therefore, minimizing the energy consumption, is equivalent to the following optimization problem,

minimize

$$\sum_{\ell \in S, i \in B_{\ell}} E(\zeta_i)$$

subject to

$$\prod_{\ell \in S, i \in B_{\ell}} \zeta_i \le \left(\frac{\delta}{m(1 - 2\sqrt{\delta})}\right)^m.$$

Now, take some feasible solution  $\zeta^*$  to the above optimization problem. Let  $\zeta_1^*$  and  $\zeta_2^*$  denote the minimum and maximum  $\zeta_i^*$  respectively, and M denote the total number of wires, i.e.,  $M = \sum_{\ell \in S} w_\ell$ . Note that since we assume that  $E(p_1) + E(p_2) \ge 2E(\sqrt{p_1p_2})$  for all  $p_1, p_2 \in (0, 1/2)$ , we can set  $\zeta_1^* = \zeta_2^* = \sqrt{\zeta_1^* \zeta_2^*}$ , without increasing the value of the objective, and further the constraint remains feasible. By Lemma 25 this process, if repeated, will converge to a solution where all  $\zeta_i$  are equal. Therefore, we can rewrite the optimization problem as

minimize

$$ME(x)$$

subject to  $x^M \le \left(\frac{\delta}{m(1-2\sqrt{\delta})}\right)^m$ .

Isolating M in the constraint above, the problem is equivalent to that of minimizing

$$\left(\frac{m}{\log 1/x} \log \left(m\frac{1-2\sqrt{\delta}}{\delta}\right)\right) E(x).$$

Since the function satisfies properties 1, 2, and 3 of Definition 22, the above expression will be minimized either at some constant  $x \in (0, 1/4)$ , in which case  $E(x)/\log(1/x) > 0$ , or in the limit as x approaches 0, in which case

$$\lim_{x \to 0^+} E(x) / \log(1/x) > 0,$$

or in the limit as x approaches 1/4, in which case

$$E(x)/\log(1/x) > 0.$$

The lemma follows.

We are now ready to prove Theorem 21.

of Theorem 21. We start by constructing a new circuit C' for computing h, which is identical to C except that both wires and gates may fail, wires of C' incur some non-zero energy consumption (as a function of their probability of failure), and the gates in C' do not consume energy. First we argue that this can be done such that C' is  $(1 - \delta)$ -reliable. Observe that if for each wire i entering gate g we set its probability of failure to  $\zeta_g = \epsilon_g/n_g$ , we can apply Statement 23 and set the failure probability on gate g when receiving input y to  $\eta_g(y, \zeta_g)$ . The result is that when the input wires of gate g in C' receive input t, the probability that g does not output g(t) is  $\epsilon_g$  (the same as the probability of failure of g in the original circuit C). Thus by setting these failure probabilities for each gate and wire in C' we have that, for any input x, C and C' output h(x) with the same probability, and so C' is  $(1 - \delta)$ -reliable.

Now we set the energy consumption of the wires such that the energy of C' is at most the energy of C. First observe that if for each gate g we set the failure-to-energy function of the wires that are inputs to g to be  $\tilde{E}_g(\zeta) = E(n_g \cdot \zeta)/n_g$ , then since  $\zeta_g = \epsilon_g/n_g$ , the total energy of the wires entering g would be  $n_g \tilde{E}_g(\zeta_g) = E(\epsilon_g)$  and the energy of C and C'would be equal. However, to apply Lemma 26, all wires must have the same failure-to-energy function. Therefore, let  $n_g^*$  be the maximum fan-in of any gate of C, i.e.,  $n_g^* = \max_{g \in C} n_g$ . We set the failure-to-energy function of all wires in C' to be

$$\tilde{E}(\zeta) = \begin{cases} E(n_g^* \cdot \zeta)/n_g^* & \text{if } \zeta < \frac{1}{2n_g^*} \\ \lim_{\epsilon \to 1/2^-} E(\epsilon)/n_g^* & \text{if } \zeta \ge \frac{1}{2n_g^*} \end{cases}$$

First observe that  $\tilde{E}_g(\zeta) \geq \tilde{E}(\zeta)$  for all  $\zeta \in (0, 1/2)$  since E is nonincreasing so  $E(n_g\zeta) \geq E(n_a^*\zeta)$ . This implies that the energy of C' is at most the energy of C.

In order to apply Lemma 26, we need to verify that  $\tilde{E}$  is a proper failure-to-energy function. The first property follows directly from the definition of  $\tilde{E}$ . For the second property, observe that

$$\lim_{\zeta \to 0^+} \frac{\tilde{E}(\zeta)}{\log\left(\frac{1}{\zeta}\right)} = \frac{1}{n_g^*} \lim_{\zeta \to 0^+} \frac{E(n_g^*\zeta)}{\log\left(\frac{1}{n_g^*\zeta}\right)} \cdot \lim_{\zeta \to 0^+} \frac{\log\left(\frac{1}{n_g^*\zeta}\right)}{\log\left(\frac{1}{\zeta}\right)}$$

$$= \lim_{\zeta \to 0^+} \frac{E(n_g^*\zeta)}{\log\left(\frac{1}{n_g^*\zeta}\right)} > 0.$$

The third property follows from the fact that

$$\lim_{\zeta \to 1/2^-} \tilde{E}(\zeta) = \lim_{\epsilon \to 1/2^-} E(\epsilon)/n_g^* > 0,$$

where we exploited the definition of  $\tilde{E}$  and the fact that, by hypothesis, E is a proper failureto-energy function. For the fourth property, let  $\zeta_1, \zeta_2 \in (0, 1/2)$ , and, w.l.o.g.,  $\zeta_1 < \zeta_2$ . There are four cases, depending on the relationship between  $\zeta_1, \zeta_2$ , and  $n_g^*$ . When  $\zeta_1 < \zeta_2 < 1/2n_g^*$ , by applying the definition of  $\tilde{E}$  and since E by hypothesis is a proper failure-to-energy function, we have

$$\tilde{E}(\zeta_1) + \tilde{E}(\zeta_2) = \frac{E(n_g^*\zeta_1)}{n_g^*} + \frac{E(n_g^*\zeta_2)}{n_g^*}$$

$$\geq 2\frac{E\left(\sqrt{n_g^*\zeta_1 n_g^*\zeta_2}\right)}{n_g^*}$$

$$= 2\tilde{E}\left(\sqrt{\zeta_1\zeta_2}\right).$$

When  $\zeta_1 < \zeta_2 = 1/2n_g^*$ , by the previous case we have that

$$\lim_{\zeta_2 \to (1/(2n_g^*))^-} \left( \tilde{E}(\zeta_1) + \tilde{E}(\zeta_2) - 2\tilde{E}\left(\sqrt{\zeta_1\zeta_2}\right) \right) \ge 0,$$

and so in this case the property holds. When  $\zeta_1 < 1/2n_g^* < \zeta_2$ , we have that

$$\tilde{E}(\zeta_1) + \tilde{E}(\zeta_2) = \tilde{E}(\zeta_1) + \tilde{E}\left(\frac{1}{2n_g^*}\right)$$

$$\geq 2\tilde{E}\left(\sqrt{\frac{\zeta_1}{2n_g^*}}\right)$$

$$\geq 2\tilde{E}\left(\sqrt{\zeta_1\zeta_2}\right),$$

where the first equality holds by definition of  $\tilde{E}$ , the first inequality follows by the preceding case, and the second inequality holds since  $\tilde{E}$  is nonincreasing and since, in this case,  $\sqrt{\zeta_1/2n_g^*} \leq \sqrt{\zeta_1\zeta_2}$ . Finally, when  $1/2n_g^* \leq \zeta_1 < \zeta_2$ ,  $\sqrt{\zeta_1\zeta_2} > \zeta_1$  and thus, by definition,  $\tilde{E}(\zeta_1) = \tilde{E}(\zeta_2) = \tilde{E}(\sqrt{\zeta_1\zeta_2})$ . We conclude that  $\tilde{E}$  is a proper failure-to-energy function. The theorem then directly follows by applying Lemma 26 to C' and  $\tilde{E}$ .

#### 3.2 A GENERAL ENERGY UPPER BOUND

Our main goal in this section is to prove Theorem 27, which roughly states that  $O(s \log s)$  energy is sufficient to simulate a circuit of size s.

**Theorem 27.** Given a reliable circuit C of size s, a non-trivial failure-to-energy function, and a fixed constant  $\delta > 0$ , it is possible to construct a circuit C' with homogeneous voltage supplies that uses  $O(s \log(s/\delta))$  units of energy and that  $(1 - \delta)$ -reliably computes the same function computed by C.

To prove Theorem 27 we use an upper bound on the number of gates for fault-tolerant circuits originally stated by Pippenger [25] and later proved in full generality by Gács [17]. This upper bound is stated in Theorem 28. The energy upper bound follows by choosing the voltage supply that minimizes the product of the total number of gates in the circuit constructed in Theorem 28, and the energy used by each gate. More specifically, we want to set the gate failure probability  $\epsilon$  so as to minimize  $E(\epsilon)/(\log(1/\epsilon) - r_0)$  for some constant  $r_0$ . As long as E is *non-trivial*, i.e., if for any  $p^* \in (0, 1/2)$  it holds that  $E(p^*) < +\infty$ , one can find an  $\epsilon$  such that  $E(\epsilon) = O(1)$ . This setting of  $\epsilon$  then implies the upper bound of  $O(s \log(s/\delta))$  on the energy used by this construction using homogeneous supply voltages.

**Theorem 28** ([17]). There are constants  $R_0, \epsilon_0, r_0 > 0$  such that for all  $\epsilon < \epsilon_0$  and  $\delta \ge 3\epsilon$ , for every reliable circuit C of size s there is a circuit of size  $R_0 \frac{s \log(s/\delta)}{\log(1/\epsilon^*) - r_0}$  that computes the same result as C with probability at least  $1 - \delta$  if gates fail independently with probability at most  $\epsilon$ , where  $\epsilon^* = \max{\epsilon, \delta/s}$ .

*Proof.* The main idea of this construction is to replace each gate of the reliable circuit with a gadget in the fault-tolerant circuit. A constant k is chosen as the level of redundancy for the circuit, meaning that each gadget has k outputs and each input to a gate in the reliable circuit is replaced by k inputs to a gadget. Another constant  $\theta \in (0, 1)$  is chosen such that, with high probability,  $\theta k$  wires exiting each gadget carry the same value as the corresponding gate in the reliable circuit. Each gadget contains k copies of the corresponding gate from the reliable circuit, as well as an additional circuit that ensures that at least a  $\theta$  fraction of the wires exiting the gadget are correct.

#### 4.0 INTRODUCTION TO SUPPLY VOLTAGE HETEROGENEITY

In this chapter, we show situations where allowing supply voltages to be heterogeneous rather than homogeneous both does and does not allow for asymptotic decreases in energy consumption. In Section 4.1, we show that, when  $\delta$  is a fixed constant, there are functions which do not use asymptotically less energy when supply voltages may be heterogeneous. In contrast, in Section 4.2, we show that for the natural circuit computing a supermajority relation, allowing supply voltages to be heterogeneous allows the relation to be computed with asymptotically less energy then if the supply voltages must be homogeneous.

### 4.1 SUPPLY VOLTAGE HETEROGENEITY MAY NOT HELP

In this section we observe in Theorem 29 that there are relations, namely the parity function, where heterogeneous supply voltages do not allow for an asymptotic reduction in energy.

**Theorem 29.** Let  $\delta < 1/4$  be a fixed constant. The energy used by any circuit to  $(1 - \delta)$ -reliably compute the parity function is  $\Omega(n \log(n/\delta))$ , and this is achievable by a circuit with homogeneous supply voltages.

*Proof.* The parity function can be reliably computed by a perfect binary tree of 2n - 1 XOR reliable gates. Thus, by Theorem 27 there exists a  $(1 - \delta)$ -reliable circuit for the parity function that uses homogeneous voltage supplies and that incurs  $O(n \log(n/\delta))$  energy consumption. Since the sensitivity of the parity function is n, by Theorem 21 this is the best possible to within a constant factor.

#### 4.2 SUPPLY VOLTAGE HETEROGENEITY CAN HELP

The goal of this section is to prove Theorem 33, which roughly states that heterogeneous supply voltages allow the natural majority circuit to compute a super-majority with asymptotically less energy than is possible with homogeneous supply voltages.

We start by defining the circuit and the logarithmic supermajority relation (LSR). Lemma 37 shows that  $\Omega(n \cdot E(\delta))$  energy is required to  $(1 - \delta)$ -reliably compute the LSR with homogeneous voltage supplies. The intuition behind the proof is that the output gate of any  $(1 - \delta)$ -reliable circuit cannot have a probability of failure greater than  $\delta$  and, since the voltage supplies are homogeneous, neither can any other gate. Then in Lemma 38 we show that there is a heterogeneous setting of the supply voltages so that this circuit  $(1 - \delta)$ -reliably computes LSR with energy  $O(n + 3^{1/\delta} E(\delta/10))$ . Intuitively, we split the circuit into an "upper" part consisting of gates close to the output gate, and a "lower" part consisting of gates close to the input gates: Each gate in the lower part has a constant probability of failure and thus a small energy consumption which results in non-constant savings compared to the optimal homogeneous setting. With the help of technical Lemmas 34 and 35, we are able to show that although there exist gates in the lower part of the circuit that fail with a probability higher than  $\delta$ , no such gate fails with a probability o(1). This preserves enough information for the upper part of the circuit to still  $(1 - \delta)$ -reliably compute LSR. In other words, in the upper part of the circuit we use a much smaller probability of failure for each gate in order to ensure that the circuit will "autocorrect" itself and output the correct result (see Lemma 36).

**Definition 30.** The Logarithmic Supermajority Relation (LSR) is the following Boolean relation: