# A DATA AWARE APPROACH TO SALVAGE THE ENDURANCE OF PHASE-CHANGE MEMORY

by

# Rakan Maddah

B.Sc. in Computer Science, Lebanese American University, 2007M.Sc. in Computer Science, Lebanese American University, 2009

Submitted to the Graduate Faculty of

the Kenneth P. Dietrich School of Arts and Sciences in partial

fulfillment

of the requirements for the degree of

**Doctor of Philosophy**

University of Pittsburgh

2015

#### UNIVERSITY OF PITTSBURGH

#### KENNETH P. DIETRICH SCHOOL OF ARTS AND SCIENCES

This dissertation was presented

by

Rakan Maddah

It was defended on

May 4<sup>th</sup>, 2015

and approved by

Dr. Rami Melhem, Department of Computer Science

Dr. Sangyeun Cho, Samsung Electronics Co.

Dr. Yiran Chen, Department of Electrical and Computer Engineering

Dr. Youtao Zhang, Department of Computer Science

Dr. Taieb Znati, Department of Computer Science

Dissertation Director: Dr. Rami Melhem, Department of Computer Science

Copyright © by Rakan Maddah 2015

# A DATA AWARE APPROACH TO SALVAGE THE ENDURANCE OF PHASE-CHANGE MEMORY

Rakan Maddah, PhD

University of Pittsburgh, 2015

Phase Change Memory (PCM) is an emerging non-volatile memory technology that could either replace or augment DRAM and NAND flash that are hindered by scalability challenges. PCM suffers from a limited endurance problem that needs to be alleviated before it can be endorsed into the memory stack. This thesis is based on the observation that the endurance problem and its ramification depend on the write data. Accordingly, a data-aware approach is applied to salvage the endurance of PCM at three different stages: pre-write fault avoidance, post-write fault tolerance and post-failure recovery.

The pre-write fault avoidance stage aims at reducing the endurance cost of servicing write requests. To this end, Cost Aware Flip Optimization (CAFO) is presented as an efficient technique to lessen the endurance degradation. Essentially, CAFO relies on a cost model that captures the endurance cost of programming memory cells based on their already stored values. Subsequently, the write data is encoded into a form that incurs a lower endurance cost than the original write data. Overall, CAFO is capable of reducing the endurance cost by up to 65% more than the existing schemes.

Worn out PCM cells exhibit a stuck-at fault model which makes the manifestation of errors dependent on the values that cells are stuck at. When a write fails, the data is rewritten inverted. This dissertation shows that applying data inversion at the post-write fault tolerance stage exploits the data dependent nature of errors which enables ECCs to tolerate faults up to double their nominal capability. Furthermore, extensions to RDIS which is an ECC designed specifically for the stuck-at fault model are presented.

At the post-failure recovery stage, Data Dependent Sparing is presented to manage bad blocks in PCM. Departing from the observation that defective blocks in the context of the stuck-at fault model still exhibit a low write failure probability due to the data dependent nature of errors, this thesis takes the approach of reusing blocks that are defective yet better-than-bad through a dynamic management of the reserve spare space. Data Dependent Sparing is capable of increasing the lifetime of PCM by up to 18%.

Keywords PCM, Endurance, Bit Flip Reduction, ECC, Bad Block Management.

## TABLE OF CONTENTS

| PR  | EFACE                                |

|-----|--------------------------------------|

| 1.0 | <b>INTRODUCTION</b> 1                |

|     | 1.1 Alternative Memory Technology    |

|     | 1.2 Challenges                       |

|     | 1.3 Data Aware Approach    3         |

|     | 1.4 Elements of a Good Solution      |

|     | 1.5 Thesis Contribution and Premise  |

|     | 1.6 Organization                     |

| 2.0 | <b>BACKGROUND AND RELATED WORK</b>   |

|     | 2.1 PCM Technology                   |

|     | 2.1.1 Write Operation                |

|     | 2.1.2 Read Operation                 |

|     | 2.1.3 Endurance                      |

|     | 2.1.4 Stored Levels                  |

|     | 2.2 Related Work                     |

|     | 2.2.1 Bit Flips Reduction Techniques |

|     | 2.2.2 Error Correction Schemes       |

|     | 2.2.3 Bad Block Management           |

|     | 2.3 Differences from Previous Work   |

| 3.0 | <b>PRE-WRITE FAULT AVOIDANCE</b>     |

|     | 3.1 CAFO Details                     |

|     | 3.1.1 Cost Model                     |

|     |     | 3.1.2 Cost Minimization Encoding Scheme                                      | 19 |

|-----|-----|------------------------------------------------------------------------------|----|

|     |     | 3.1.3 CAFO Encoding Example                                                  | 22 |

|     |     | 3.1.4 Encoding Scheme Optimization                                           | 24 |

|     |     | 3.1.5 Cost of Auxiliary Bits                                                 | 27 |

|     |     | 3.1.6 Decoding Process                                                       | 29 |

|     |     | 3.1.7 Design Considerations                                                  | 30 |

|     | 3.2 | evaluation                                                                   | 32 |

|     |     | 3.2.1 Random Input Streams                                                   | 33 |

|     |     | 3.2.1.1 Cost Reduction                                                       | 33 |

|     |     | 3.2.1.2 Cost Model Integration                                               | 35 |

|     |     | 3.2.1.3 Optimization Isolation                                               | 37 |

|     |     | 3.2.2 Benchmark Data                                                         | 38 |

|     | 3.3 | Conclusion                                                                   | 39 |

| 4.0 | PO  | ST-WRITE FAULT TOLERANCE                                                     | 40 |

|     | 4.1 | Power of One Bit: Increasing Error Correction Capability with Data Inversion | 41 |

|     |     | 4.1.1 Theoretical Foundation                                                 | 42 |

|     |     | 4.1.2 Integrated Protection                                                  | 42 |

|     |     | 4.1.3 Un-integrated Protection                                               | 45 |

|     |     | 4.1.4 Defectiveness Probability                                              | 46 |

|     |     | 4.1.5 Surviving Polarity Bit Defectiveness with Un-integrated Protection     | 48 |

|     |     | 4.1.6 Error Detection and Block Retirement                                   | 49 |

|     |     | 4.1.7 Evaluation                                                             | 50 |

|     |     | 4.1.7.1 Experimental Setup                                                   | 51 |

|     |     | 4.1.7.2 Main Memory Lifetime Improvement                                     | 52 |

|     |     | 4.1.7.3 Secondary Storage Lifetime Improvement                               | 53 |

|     |     | 4.1.7.4 Lifetime Variability                                                 | 54 |

|     |     | 4.1.7.5 Performance Overhead                                                 | 56 |

|     |     | 4.1.8 Summary                                                                | 57 |

|     | 4.2 | RDIS Extension                                                               | 60 |

|     |     | 4.2.1 Block Repair                                                           | 60 |

|     | 4.2.2 Multidimensional RDIS                                               | 62 |

|-----|---------------------------------------------------------------------------|----|

|     | 4.2.3 Block Repair Evaluation                                             | 63 |

|     | 4.2.4 Multidimensional RDIS Evaluation                                    | 64 |

|     | 4.2.5 Summary                                                             | 65 |

| 5.0 | POST-FAILURE RECOVERY                                                     | 67 |

|     | 5.1 Motivation                                                            | 67 |

|     | 5.2 Data Dependent Sparing                                                | 69 |

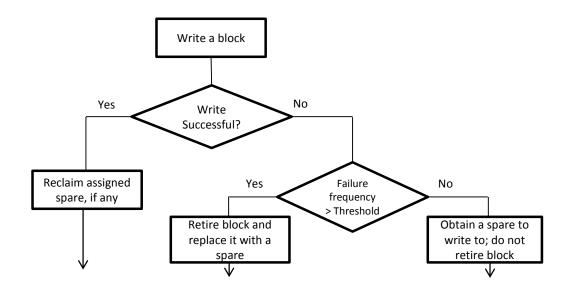

|     | 5.2.1 Mechanism of Block Reuse                                            | 69 |

|     | 5.2.2 Design Trade-Offs                                                   | 71 |

|     | 5.2.3 Overheads                                                           | 72 |

|     | 5.3 Evaluation                                                            | 72 |

|     | 5.3.1 Lifetime Improvement                                                | 73 |

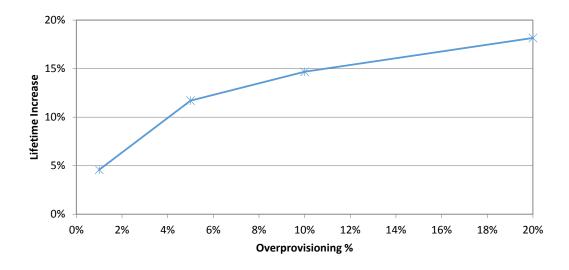

|     | 5.3.2 Sensitivity to Over-Provisioning                                    | 74 |

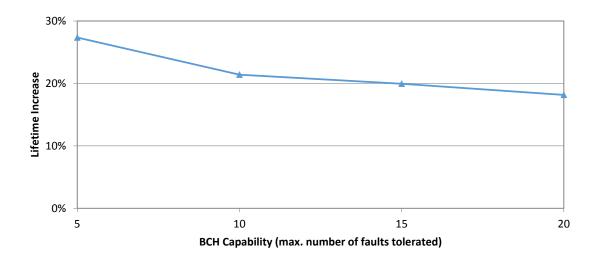

|     | 5.3.3 Sensitivity to BCH Capability                                       | 75 |

|     | 5.3.4 The Effect of Fail Frequency Threshold                              | 76 |

|     | 5.3.5 Sparing Overhead Reduction                                          | 76 |

|     | 5.4 Summary                                                               | 78 |

| 6.0 | EXTENSIONS TO MULTILEVEL CELLS                                            | 79 |

|     | 6.1 Symbol Shifting                                                       | 80 |

|     | 6.2 Multilevel CAFO                                                       | 81 |

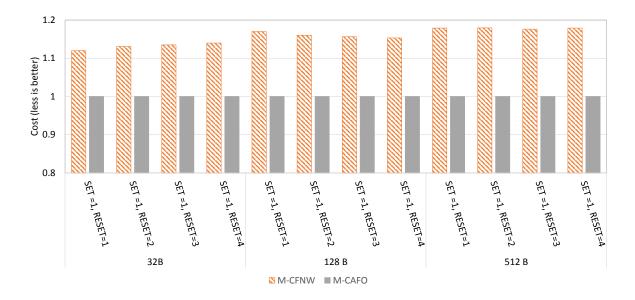

|     | 6.2.1 Evaluation                                                          | 84 |

|     | 6.3 Increasing Error Correcting Capabilities in MLC through Data Shifting | 85 |

|     | 6.3.1 Theoretical Foundation of Data Shifting                             | 86 |

|     | 6.3.2 Data Shifting effect on Block Defectiveness                         | 88 |

|     | 6.3.2.1 Integrated Protection                                             | 88 |

|     | 6.3.2.2 Un-integrated Protection                                          | 89 |

|     | 6.3.3 Execution Flow                                                      | 90 |

|     | 6.3.4 Dealing with Drift Errors                                           | 90 |

|     | 6.3.4.1 Reserved Capability                                               | 91 |

|     | 6.3.4.2 Composite Capability                                              | 92 |

|     | 6.3.5 Data Shifting Evaluation                     | 93  |

|-----|----------------------------------------------------|-----|

|     | 6.4 Multilevel Data Dependent Sparing              | 95  |

|     | 6.4.1 Multilevel Data Dependent Sparing Evaluation | 95  |

|     | 6.5 Summary                                        | 96  |

| 7.0 | SUMMARY AND FUTURE DIRECTIONS                      | 98  |

|     | 7.1 Future Directions                              | 99  |

| BIB | LIOGRAPHY                                          | 101 |

### LIST OF TABLES

| 1 | Probability of defectiveness for un-integrated protection because of a defective po-   |    |

|---|----------------------------------------------------------------------------------------|----|

|   | larity bit as a function of the number of faults within a 512 bit block protected by a |    |

|   | BCH-6 code                                                                             | 49 |

| 2 | Performance evaluation in terms of extra write operations required by data inver-      |    |

|   | sion to complete write requests successfully after the number of faults exceeds the    |    |

|   | nominal capability of the error correction code                                        | 58 |

| 3 | Required over-provisioning for data dependent sparing to match static sparing life-    |    |

|   | time                                                                                   | 77 |

| 4 | M-CAFO cost model for 3LC PCM cells                                                    | 82 |

### LIST OF FIGURES

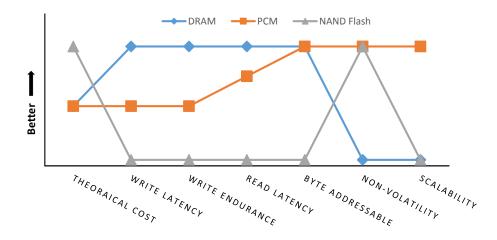

| 1  | A comparison among DRAM, PCM and NAND flash [69]                                                      | 3  |

|----|-------------------------------------------------------------------------------------------------------|----|

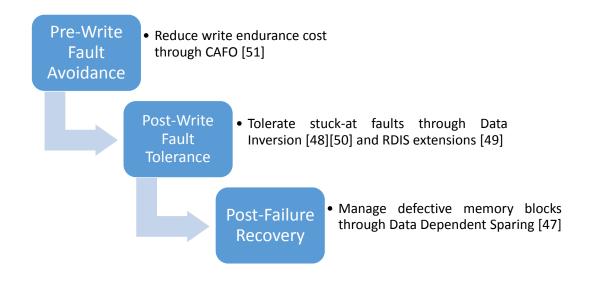

| 2  | Thesis Contributions                                                                                  | 5  |

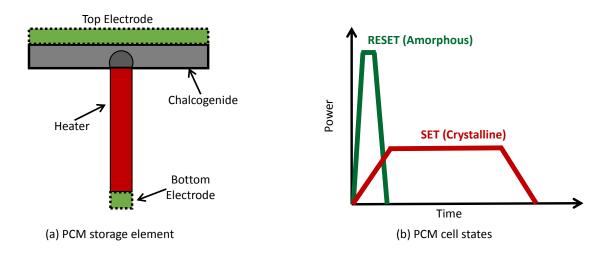

| 3  | An example of PCM storage elements (a) and the states it can take (b).                                | 8  |

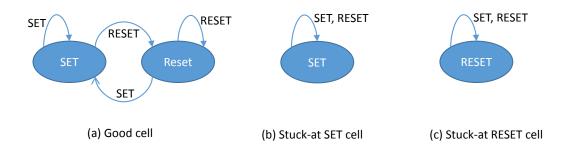

| 4  | Difference between a good and stuck cell.                                                             | 9  |

| 5  | The concept of multilevel PCM cell.                                                                   | 10 |

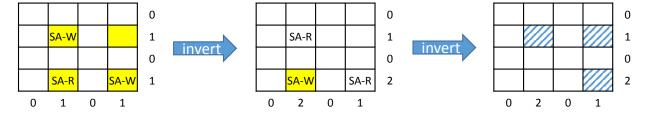

| 6  | RDIS encoding process. Highlighted cell(s) represent(s) the extracted sub-array at each               |    |

|    | step. Patterned cells represent the identified invertible set.                                        | 12 |

| 7  | A loop of faults that causes RDIS to halt. Highlighted cells represent the extracted sub-array        |    |

|    | at each inversion step.                                                                               | 13 |

| 8  | Cost model.                                                                                           | 18 |

| 9  | Gain calculation where the costs of a, b, c and d are 1, 2, 0 and 0 respectively                      | 19 |

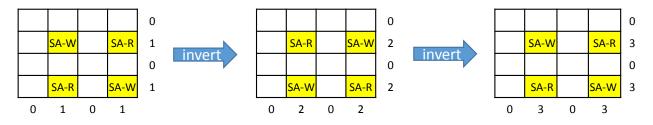

| 10 | CAFO encoding example where the number of bit flips is reduced from 33 to 21. A "0"                   |    |

|    | represents a matching cell ( $c = d = 0$ ), and a "1" represents a non-matching cell ( $a = b = 1$ ). |    |

|    | "Gain" is calculated as per Formula (3.2). Shaded cells represent rows and columns that are           |    |

|    | to be flipped                                                                                         | 23 |

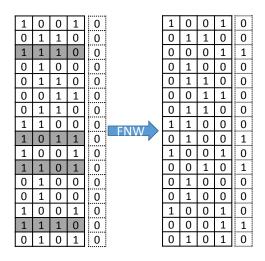

| 11 | An example of Flip-N-Write (FNW) encoding where the number of bit flips is reduced from               |    |

|    | 33 to 25. A data cell with "0" represents a match with the already written bit, "1" otherwise.        |    |

|    | Shaded cells represent a row that is to be flipped.                                                   | 25 |

| 12 | An example that shows that the cost of a write can still be reduced even when no row or               |    |

|    | column shows a positive gain. A data cell with "0" represents a match with the already                |    |

|    | written bit, "1" otherwise. Flipped rows and column are highlighted. The number of bit                |    |

|    | flips is reduced from 5 to 3                                                                          | 26 |

| 13 | An example of CAFO's optimization. A data cell with "0" represents a match with the                    |    |

|----|--------------------------------------------------------------------------------------------------------|----|

|    | already written bit, "1" otherwise. The cost of flipping an intersecting matching cell $c_{r,c}$ is    |    |

|    | -1. Flipped rows and column are highlighted in red. The number of bit flips is reduced from            |    |

|    | 6 to 4                                                                                                 | 27 |

| 14 | An example of taking the cost of the auxiliary bit into consideration when computing the               |    |

|    | gain. The costs of "a", "b", "c" and "d" are 1, 2, 0 and 0 respectively. Dotted cells represent        |    |

|    | auxiliary bits.                                                                                        | 28 |

| 15 | Write datapath logic for CAFO.                                                                         | 31 |

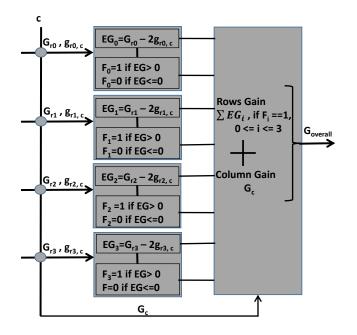

| 16 | Optimization logic. $EG$ is the expected gain of flipping a row. $G$ is the initial gain of rows       |    |

|    | or columns. $g_{r,c}$ is the gain of flipping the cell intersecting at row $r$ and column $c$ . $F$ is |    |

|    | a control signal to flag positive $EG$ . $G_{overall}$ is the overall gain of flipping the selected    |    |

|    | column with the rows with $EG > 0$                                                                     | 32 |

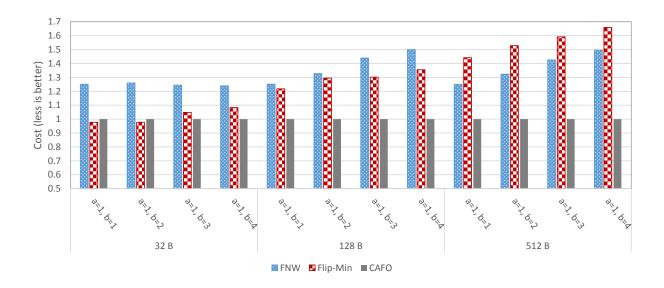

| 17 | Cost reduction achieved by CAFO over Flip-N-Write (FNW) and Flip-Min.                                  | 34 |

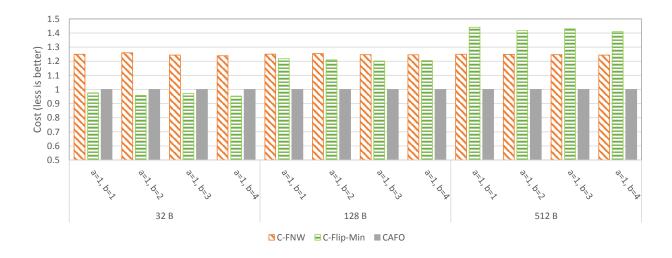

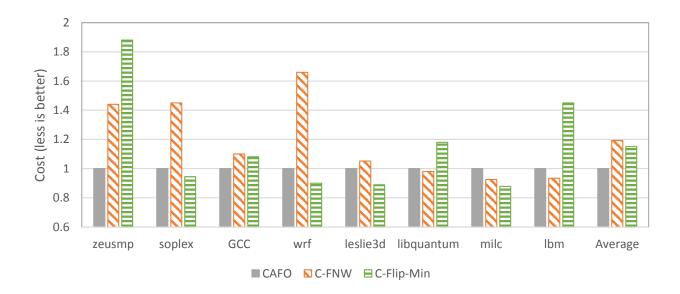

| 18 | Cost reduction achieved by CAFO over cost aware Flip-N-Write (C-FNW) and cost aware                    |    |

|    | Flip-Min (C-Flip-Min).                                                                                 | 35 |

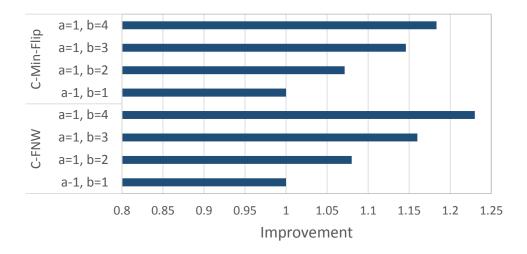

| 19 | Cost reduction improvement of cost aware Flip-N-Write (C-FNW) and Flip-Min (C-Flip-                    |    |

|    | Min) over cost oblivious Flip-N-Write and Flip-Min through the integration of CAFO's cost              |    |

|    | model                                                                                                  | 36 |

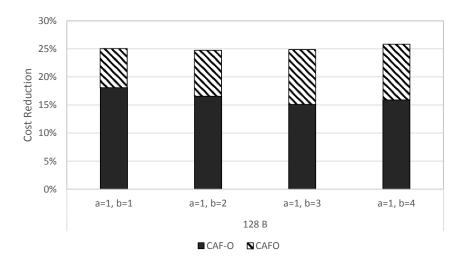

| 20 | Contribution of CAFO minus optimization (CAF-O) to the cost reduction over C-FNW for                   |    |

|    | a 128B block.                                                                                          | 37 |

| 21 | Cost reduction achieved by CAFO over cost aware Flip-N-Write (C-FNW) and Flip-Min                      |    |

|    | (C-Flip-Min).                                                                                          | 38 |

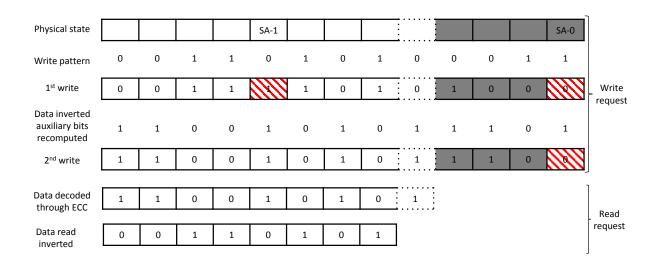

| 22 | An example of executing write and read requests with integrated protection comple-                     |    |

|    | menting an error correcting code of capability 1. Dotted cells represent the polarity                  |    |

|    | bit, grey cells represent the auxiliary bits and red patterned cells represent errors                  | 44 |

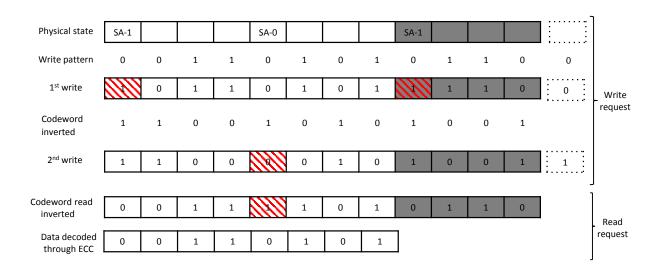

| 23 | An example of executing write and read requests with un-integrated protection com-                     |    |

|    | plementing an error correcting code of capability 1 protecting one byte of memory.                     |    |

|    | Dotted cells represent the polarity bit, grey cells represent the auxiliary bits and red               |    |

|    | patterned cells represent errors.                                                                      | 47 |

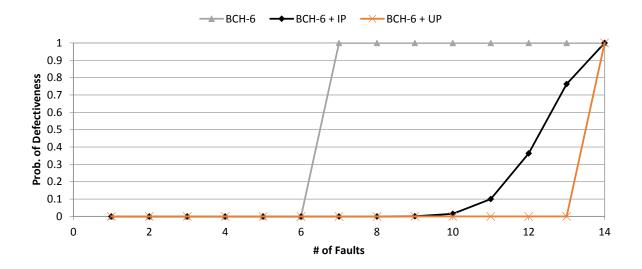

| 24 | Probability of defectiveness as a function of the number of stuck-at faults, where           |    |

|----|----------------------------------------------------------------------------------------------|----|

|    | a BCH-6 protects a block of size 512 bits. "IP" denotes integrated protection and            |    |

|    | "UP" denotes un-integrated protection.                                                       | 47 |

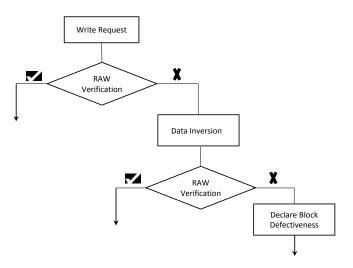

| 25 | Flow of executing a write request. "RAW" denotes read after write                            | 50 |

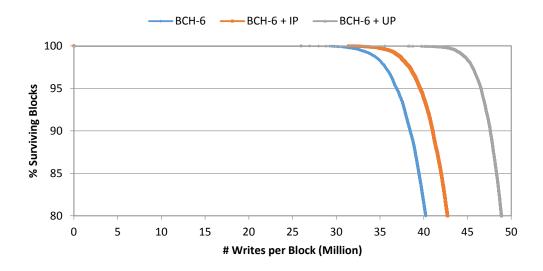

| 26 | Lifetime of PCM main memory blocks achieved with BCH-6 and BCH-6 comple-                     |    |

|    | mented by data inversion with integrated protection (IP) and un-integrated protec-           |    |

|    | tion (UP)                                                                                    | 52 |

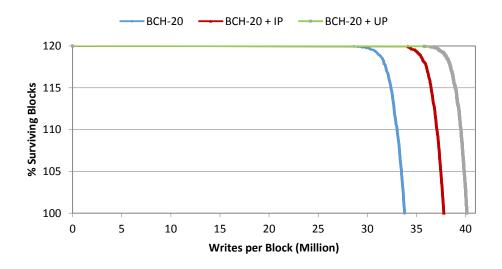

| 27 | Lifetime of PCM storage blocks achieved with BCH-20 and BCH-20 with inte-                    |    |

|    | grated protection (IP) and un-integrated protection (UP). This experiment assumed            |    |

|    | that 20% of spare storage capacity was provided                                              | 54 |

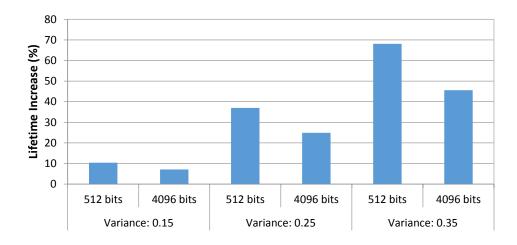

| 28 | Lifetime increase with BCH complemented with data inversion relative to regular              |    |

|    | BCH with various cell lifetime variance.                                                     | 55 |

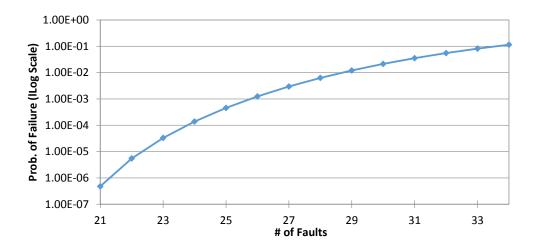

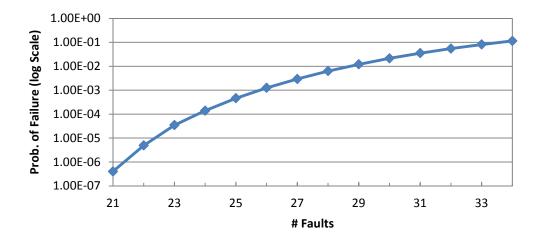

| 29 | Probability of the first write failure on a 512-bytes storage block protected by a           |    |

|    | BCH-20 code                                                                                  | 57 |

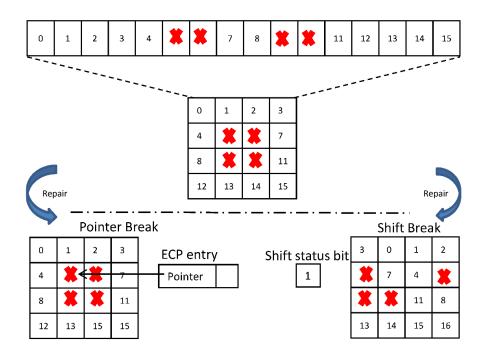

| 30 | Defective block fixing techniques.                                                           | 61 |

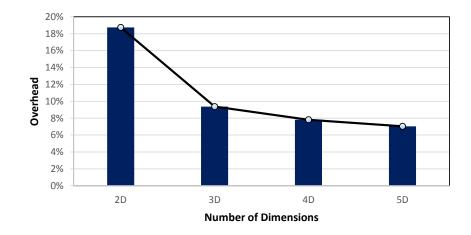

| 31 | Space overhead of RDIS for a 512-bit block with various dimensional arrangements             | 63 |

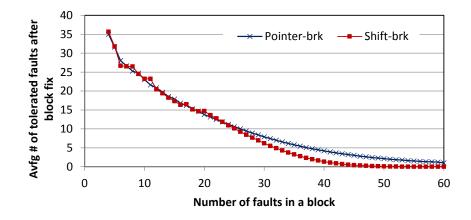

| 32 | Avg. number of additional tolerated faults after breaking a defective pattern in a 2048-bits |    |

|    | block size.                                                                                  | 64 |

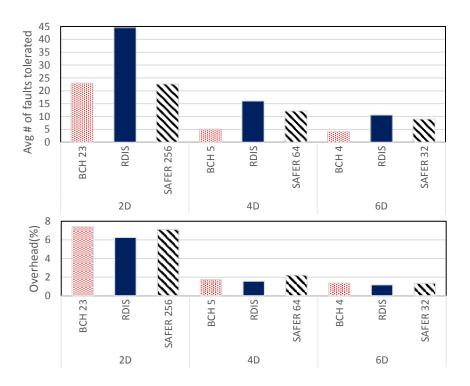

| 33 | Average number of faults that can be tolerated by RDIS with various dimensional arrange-     |    |

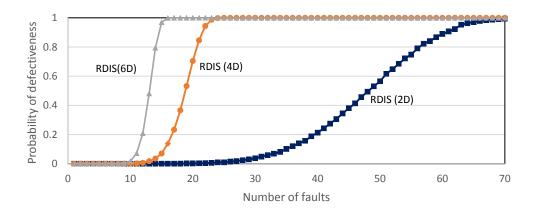

|    | ment compare to SAFER and BCH for 4096-bit block.                                            | 66 |

| 34 | Probability of defectiveness with different dimensional arrangements for a 4096-bit block    | 66 |

| 35 | Block write failure probability vs. # of faults within a 4KB storage block, when an error    |    |

|    | correction mechanism covers up to 20 errors.                                                 | 68 |

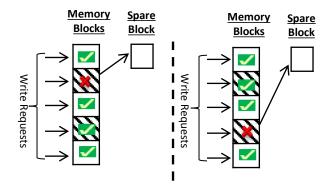

| 36 | Data-dependent Sparing. Shaded cells represent defective blocks.                             | 70 |

| 37 | Flow of execution in data dependent sparing.                                                 | 70 |

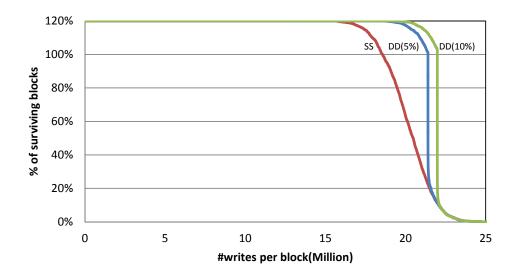

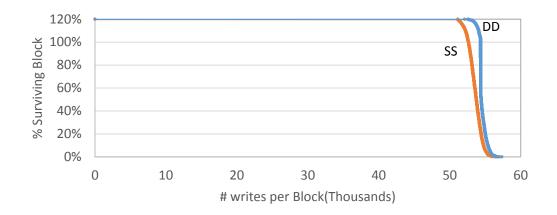

| 38 | Lifetime of PCM blocks with BCH-20 and 10% failure frequency threshold. "DD" denotes         |    |

|    | data dependent sparing and "SS" static sparing.                                              | 74 |

| 39 | Lifetime increase achieved by data dependent sparing at various levels of over-provisioning  |    |

|    | compared with static sparing with 20% over-provisioning.                                     | 75 |

| 40 | Lifetime increase achieved by data dependent sparing relative to static sparing for various |    |

|----|---------------------------------------------------------------------------------------------|----|

|    | BCH code capabilities.                                                                      | 76 |

| 41 | Lifetime of PCM blocks under two failure frequency threshold values: 5% vs. 10%. "DD"       |    |

|    | denotes data dependent sparing and "SS" static sparing.                                     | 77 |

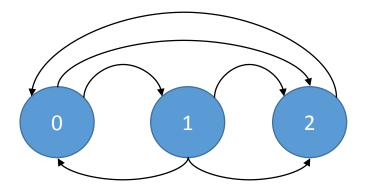

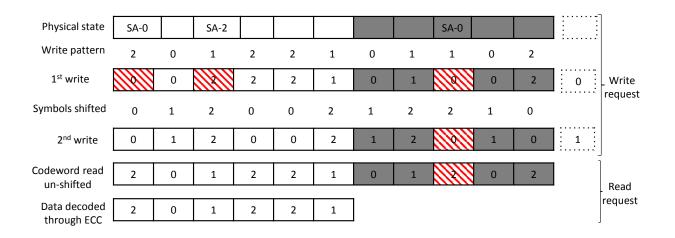

| 42 | A shift of symbols in the context of 3LC PCM cells                                          | 81 |

| 43 | 3LC programming model                                                                       | 82 |

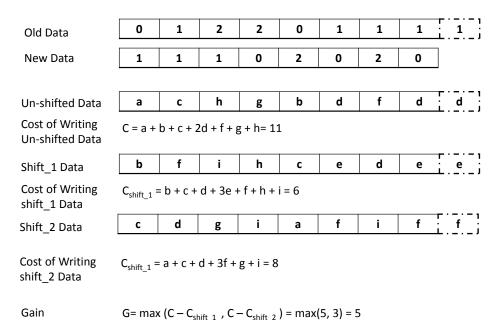

| 44 | Gain calculation in the context of 3LC PCM cells.                                           | 83 |

| 45 | Cost reduction of M-CAFO over M-CFNW in the context of 3LC PCM cells                        | 85 |

| 46 | An example of and (6, 11) LPDC code for ternary cells of capability 2 comple-               |    |

|    | mented by data shifting with un-integrated protection. Dotted cells represent the           |    |

|    | SSC, grey cells represent the auxiliary cells and red patterned cells represent sym-        |    |

|    | bol errors.                                                                                 | 91 |

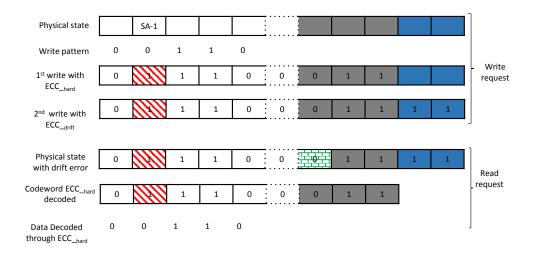

| 47 | An example of encoding/decoding with Composite Capability. Dotted Cell repre-               |    |

|    | sents the SSC. Grey cells represent $ECC_{hard}$ auxiliary bits. Blue cell represents       |    |

|    | $ECC_{drift}$ auxiliary bits. Red diagonal patterned cells represent stuck-at cell errors.  |    |

|    | Green brick patterned cells represent drift errors.                                         | 93 |

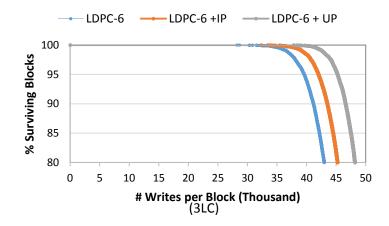

| 48 | Lifetime of PCM main memory blocks achieved with LDPC-6 and LDPC-6 com-                     |    |

|    | plemented by Symbol Shifting with integrated protection (IP) and un-integrated              |    |

|    | protection (UP).                                                                            | 94 |

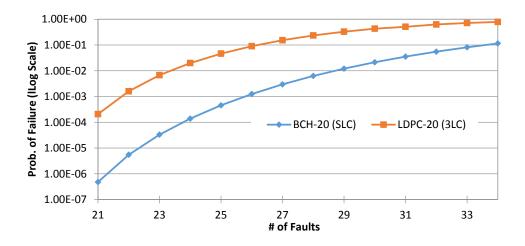

| 49 | Probability of failing to write on 4KB SLC and 3LC blocks protected by BCH-20               |    |

|    | and LDPC-20 respectively.                                                                   | 96 |

| 50 | Lifetime Improvement with Data Dependent Sparing (DD) in the context of 3LC in              |    |

|    | comparison to Static Sparing (SS).                                                          | 97 |

|    |                                                                                             |    |

### LIST OF ALGORITHMS

| 3.1 | CAFO Encoding | <br> | ••• | • | <br>• | ••• |  | <br>• | <br>• | • | • | • | ••• | • | • |  | 20 |

|-----|---------------|------|-----|---|-------|-----|--|-------|-------|---|---|---|-----|---|---|--|----|

| 3.2 | CAFO DECODING | <br> | ••• | • | <br>• | ••• |  | <br>• | <br>• | • |   | • |     | • | • |  | 29 |

# LIST OF EQUATIONS

| 3.1 | Equation (3.1) | • | • | • | • | • |  | • | • | • |   | • | • | <br>• |   | • | • |   | • | • | • |       |   | • | • | • |   | • | • |       | 18 |

|-----|----------------|---|---|---|---|---|--|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|-------|----|

| 3.2 | Equation (3.2) |   |   | • | • | • |  |   | • | • |   | • | • | <br>• |   |   | • |   | • | • | • |       |   |   |   | • |   | • |   |       | 19 |

| 3.3 | Equation (3.3) |   | • | • | • | • |  |   | • | • | • | • | • | <br>• |   |   | • | • | • | • | • |       | • | • |   | • | • | • |   |       | 25 |

| 3.4 | Equation (3.4) |   | • | • | • | • |  |   | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | <br>• | • | • |   | • | • | • | • | <br>4 | 26 |

| 3.5 | Equation (3.5) |   |   |   |   |   |  |   |   |   |   |   |   |       |   |   |   |   |   |   |   |       |   |   |   |   |   |   |   | <br>4 | 26 |

#### PREFACE

I am thankful to my adviser professor Rami Melhem for all the support and encouragement he provided during my Ph.D. journey. During my 5 years in the Ph.D. program, I do not recall a single instance where Rami shut his door against a discussion. Rami was always available to listen and give advice. I owe Rami for most of what I have learned during my Ph.D. years and he is and will always be a role model to me.

I would like to thank my thesis committee members professors Taieb Znati, Sangyeun Cho, Youtao Zhang and Yiran Chen for their support and constructive feedback during the materialization of my thesis. I am particularly grateful to professor Cho who co-advised me during the first 3 years of my Ph.D. and helped me set the path for my dissertation work.

I am grateful to all my friends that were always supportive throughout my graduate years. Particularly, I thank Deema Abdallah, Wissam Beaino, John Feghali, Iyad Batal, Jamal Alrifai, Shadi Halabi and Ohan Oumoudian.

I cannot but to express my gratitude to my wife's family for their support and their warm hospitality during my regular trips to the lovely city of Toronto.

I am eternally thankful to my brother Bacel and my sisters Wijdan and Dina for their unconditional love and support. You guys mean the world to me.

I am short of words that can truly describe my gratitude to my wife Zeina. This thesis would not have been achieved without your love, care, encouragement and patience. Thank you for being there for me in the good and bad times and for believing in us.

At last, I dedicate this thesis to my father Samih and my mother Souad. I would never have been the person I am without your guidance and support. Thank you for all what you have done to me. All I have and will accomplish are possible because of your sacrifices and love.

#### **1.0 INTRODUCTION**

Computer systems have integrated all aspects of human endeavors and activities. The enormous computational power gave researchers and scientists the ability to tackle and harness complex problems and mine enormous amount of data. This ability has led to unprecedented improvements in various fields, whether biological, economic or social. At the same time, these improvements shed light on new challenges and dimensions that require even more computational power than what is available. It is projected that every human being will produce more than 5000 gigabytes of data yearly which amounts to over 40 trillion gigabytes of memory [26, 2]. Clearly, the universe is turning digital. Therefore, computer scientists and engineers are faced with the challenge of offering exascale computing paradigms while sustaining the dependability and reliability of computer systems.

Among many elements that have contributed to the evolution of computer systems, the memory system is a defining component. DRAM as a main memory technology has scaled from memory chips that can hold few megabytes of data to memory chips that can hold gigabytes of data with improved performance. On the other hand, NAND flash solid state drives (SSD) replaced traditional hard disk drives while providing significantly faster access times. In the middle of this era of data explosion [26], it is of great importance to continue improving the performance and the density of main and secondary memories to meet the requirements of exascale computing power. Unfortunately, both DRAM and NAND flash are facing physical limitations putting their further scalability into jeopardy [30, 10, 12, 38]. Further scaling of DRAM's feature size makes the manufacturing process complex and costly with a decreased cell reliability and increased power consumption–30% of total system power is consumed by DRAM [42, 14, 1]. Similarly, scaling NAND flash to smaller technology nodes remarkably decreases the endurance of the storage cells and increases the number of transient and hard errors.

#### **1.1 ALTERNATIVE MEMORY TECHNOLOGY**

To circumvent the challenges faced by DRAM and NAND flash and sustain the evolution of the memory system, researchers and engineers are turning their attention to alternative memory technologies [44, 42, 37] that can either replace or augment existing technologies.

Amongst several memory candidates, phase-change memory (PCM) is emerging as one of the most promising technologies due to its desirable characteristics in terms of superior scalability, low access latency and negligible standby power [44, 43]. Initial Assessments and measurements show that PCM can compete with DRAM and NAND flash in terms of performance while providing improved scalability and density [44, 88]. PCM encodes bits in different physical states of chalcogenide alloy that consists of Ge, Sb and Te. Data is stored in PCM devices in the form of either a low resistance crystalline state (SET) or a high resistance amorphous state (RESET). Switching between the states happens through the application of different programming currents that cause the chalcogenide material to melt and then re-solidify the material into one of the SET/RESET states.

#### **1.2 CHALLENGES**

Figure 1 compares PCM against both DRAM and NAND flash [69]. While PCM could be perceived as a substantial improvement over NAND flash, it falls short to DRAM. Specifically, PCM suffers from slow writes and limited endurance. To make PCM a viable memory technology that can be endorsed within the memory stack, tackling the aforementioned shortcomings is key and essential. While addressing the slow write problem [21, 63, 86, 33] is important, salvaging the limited endurance is a must to prevent system failures due to worn out memory devices. In fact, each PCM cell can endure a limited number of SET/RESET cycles. The heating and cooling process to program a cell leads to frequent expansion and contraction of the chalcogenide material. Consequently, the heating element detaches from the chalcogenide material after sustaining  $10^6$ to  $10^8$  writes on average [22, 23]. Such a phenomenon results in a stuck-at hard fault that can be subsequently read but not reprogrammed [46, 74]. Accordingly, this thesis investigates techniques

Figure 1: A comparison among DRAM, PCM and NAND flash [69]

to preserve the endurance and mitigate the wear related failures in PCM.

#### 1.3 DATA AWARE APPROACH

A careful analysis of the characteristics of PCM would reveal that the data of write requests have a major impact on the endurance and its related problems. For instance, a submitted write request to a block with a data that has low resemblance to the already stored data would aggravate the endurance degradation rate. In fact, such a request results in a large number of cells that require programming as their intended values are different than the already stored values. Also, worn out cells are permanently stuck at a specific bit value. Thus, if a worn out cell gets written with a bit value identical to the bit value it is stuck at then no error would be manifested. Consequently, a submitted write request to a block classifies its worn out cells into two categories: (1) Stuck-at Wrong (SA-W) cells which are cells stuck at a bit value different than the intended value to be written and (2) Stuck-at Right (SA-R) which are cells stuck at a bit value identical the intended value to be written. Accordingly, a write request that would induce a large number of SA-W cells can lead to an unrecoverable write failure. Clearly, PCM's endurance problem and its ramifications depend on the data pattern to be written. Therefore, this thesis approaches the endurance problem by exploiting this dependency through proposing data-aware solutions.

#### **1.4 ELEMENTS OF A GOOD SOLUTION**

This thesis envisions that tackling the limited endurance problem of PCM can be accomplished at three different stages:(1) **the pre-write fault avoidance stage**, (2) **the post-write fault tolerance stage** and (3) **the post-failure recovery stage**. At the pre-write fault avoidance stage, a good solution would schedule the write on a block that has not been written extensively and try to service the write with the minimal possible degradation in endurance. While such a solution lessens the endurance degradation rate of PCM, cell wear-outs are unavoidable. A worn-out cell cannot be programmed reliably to the intended bit value. Accordingly, such a cell will often manifest errors in the post-write stage. Therefore, combating cell failures through proactive error correcting schemes is essential for the successful deployment of PCM within the memory system. Undoubtedly, error correcting schemes has to be limited for complexity concerns. Consequently, a memory block turns defective when the number of accumulated faults gets above the capability of the deployed error correcting scheme. Hence, managing defective block at the post-failure recovery stage is a necessity.

#### **1.5 THESIS CONTRIBUTION AND PREMISE**

This thesis presents techniques to salvage the endurance of PCM at each of the aforementioned stages as depicted in Figure 2. All the proposed techniques exploit the dependency of the endurance on the write data. Overall, the key contributions of this thesis are the following:

1. *CAFO*, a pre-write fault avoidance technique that services write requests while minimizing the wear out rate through taking the endurance cost of bit flips into consideration.

Figure 2: Thesis Contributions

- 2. *Data Inversion*, a post-write fault tolerance approach that increases the number of faults that error correcting codes can cover through exploiting the data dependent nature of errors. In addition, extensions to the PCM specific error correcting scheme *RDIS* are proposed to improve its error correcting capability.

- 3. *Data Dependent Sparing*, a post-failure recovery technique that delays the retirement of defective blocks by being aware of the data dependent nature of write failures.

The aforementioned techniques are effective in salvaging the endurance of PCM. *CAFO* is capable of reducing the endurance write cost by up to 65%. *Data Inversion* enables error correcting codes to tolerate a number of faults that is up to double their nominal capability which leads to up to 34.5% increase in lifetime. Similarly, the *extensions to RDIS* allow the correction scheme to effectively recover from detrimental fault patterns and reduce its space overhead. At a small management cost and with less than 1% spare over-provisioning, *Data Dependent Sparing* achieves the same lifetime as the conventional approach of managing defective blocks that assumes 20% spare over-provisioning.

Salvaging the endurance problem of PCM improves its reliability which paves the way for its integration within the memory stack. Accordingly, computer systems can benefit from a memory

technology that is dense and scalable.

#### **1.6 ORGANIZATION**

The remainder of this thesis is organized as follows. Chapter 2 presents a background on PCM and lists the related work. Chapter 3 presents and evaluates CAFO. Chapter 4 presents and evaluates Data Inversion and extensions to RDIS. Chapter 5 presents and evaluates Data Dependent Sparing. Chapter 6 presents the application of the proposed schemes in the context of multilevel cells. Finally, Chapter 7 summarizes the thesis and proposes future directions.

#### 2.0 BACKGROUND AND RELATED WORK

#### 2.1 PCM TECHNOLOGY

The concept of Phase Change Memory was envisioned by Dr. Stanford Ovshinsky back in 1960s [58]. PCM is a non-volatile memory that is amenable to process scaling [44]. The storage element of PCM, depicted in Figure 3(a), is composed of chalcogenide material sandwiched in between two electrodes and a heater (resistance). The chalcogenide material is characterized by its ability to switch into stable phases through the application of a heating current.

#### 2.1.1 Write Operation

A PCM cell can be in two states as illustrated in Figure 3(b). To put a cell into the RESET state, the heating element injects a high short current pulse. A short current increases resistivity by abruptly disconnecting the current quenching the heat generation and freezing the chalcogenide into the amorphous state [44, 43]. On the other hand, the SET state is reached by applying a long moderate current pulse. A long current ramps down gradually inducing crystal growth [44, 43].

#### 2.1.2 Read Operation

To read a PCM cell, a moderate read voltage is applied to sense the resistance of the cell. The sensed resistance is compared against a reference threshold value to differentiate between the SET and RESET states.

Figure 3: An example of PCM storage elements (a) and the states it can take (b).

#### 2.1.3 Endurance

The wear mechanism in PCM is associated with the write operation. The heating and cooling process to program a cell leads to frequent expansions and contractions of the material. Consequently, programming current cannot be injected reliably anymore to switch the state of a cell [9].

The endurance of a cell is determined by the number of writes that can be performed before that cell wears out. On average, PCM cells can endure  $10^6$  to  $10^8$  writes [22, 23]. When a cell reaches its endurance limit, the heating element detaches from the chalcogenide material resulting in a cell that is stuck at a specific state. While stuck-at cells cannot be reliably programmed, their stuck-at value can still be read [46, 74]. Generally, PCM cells can be classified intro three categories as illustrated in Figure 4: (a) good cell, (b) stuck-at SET cell, and (c) stuck-at RESET cell. Furthermore, stuck-at cells can be perceived as either stuck-at wrong (SA-W) or stuck-at right (SA-R) after a write operation. A SA-W is a stuck-at cell that exhibits an error as it is expected to store a value different than its stuck-at value. Conversely, a SA-R is an error free cell as it is stuck at a value that matches the expected value to be stored.

Both the SET and the RESET operations deteriorate the endurance of PCM cells. Since the programming current of the RESET state is significantly more intense than the SET state, studies

Figure 4: Difference between a good and stuck cell.

have shown that the endurance is mainly dependent on the RESET state [87, 39]. In fact, the RESET state could degrade the endurance by up to four times more than the SET state. This phenomenon creates a write endurance asymmetry in between the SET and the RESET states.

#### 2.1.4 Stored Levels

PCM cells can be used to store two or more states. A two states memory chip, also known as single level cell (SLC), stores binary data. Conventionally, a cell in the crystalline state is interpreted as a bit value of "1" while a cell in the amorphous state is interpreted as a bit value of "0". Never-theless, the resistances in the fully crystalline and amorphous states differ by two to three orders of magnitude. This difference in resistance can be exploited to store multi-bits per cells [60, 4]. Instead of representing the data in a cell using two states, the resistance range can be broken down into multiple states where each state represents a particular data pattern i.e. multi-level cell (MLC). Figure 5 shows a PCM cell arranged in two states (a) and 4 states (b) capable of storing 1 bit and 2 bits per cell respectively.

Obviously, the major advantage of MLC over SLC is density. However, a denser MLC PCM chip suffers from drift errors. As a matter of fact, PCM cells are susceptible to resistance drift over time. This drift in resistance is not large enough to cause SLC cells to switch levels, but it affects MLC cells leading to a high drift error rate that cannot be practically tolerated by error correcting codes [84]. Also, programming of MLC cells could require several iterations to make

Figure 5: The concept of multilevel PCM cell.

the cells attain the desired resistance level which could exacerbates the endurance degradation rate compared to SLC cells [4, 57]. Yet, the drift errors are the major challenge for MLC cells. One way of mitigating the drift errors is to store fewer states per cell. In [84, 34, 77], it was shown that storing 3 levels per cell instead of 4 would eliminate most of the drift errors.

#### 2.2 RELATED WORK

#### 2.2.1 Bit Flips Reduction Techniques

To tackle the endurance problem of PCM at the pre-write fault avoidance stage, several techniques have been proposed. The key concept of those techniques is to service write requests while reducing the number of cells that requires flipping as such a practice would decelerate the wear out rate. In this realm, Differential Writes [43] is a standard technique deployed in PCM. When a write to a block is submitted, differential write compares the data vector to be written to the already stored data vector within the block. Subsequently, only those cells with non-matching values are to be programmed.

Moreover, several techniques have been proposed to complement Differential Writes. The target of those technique is to service write requests while programming as few cells within a

block as possible. For instance, Flip-N-Write [15] encodes the data to be written into two different vectors, one in the regular form and the other in the inverted form. The vector that would yield in the least number of bit flips when paired with Differential Writes is chosen to be written. Flip-N-Write requires the introduction of one auxiliary bit to flag the inversion step, which makes the space overhead of Flip-N-Write depends on the granularity of the block it is applied to e.g. 8 : 1, 16 : 1, 32 : 1 etc.

In addition to Flip-N-Write, Flip-Min [31] has been proposed. Flip-Min is based on the concept of coset coding. An inverted (72, 64) Reed Muller code is used to encode each possible input data vector into 256 unique different vectors. Among those vectors, the vector that would yield in the least number of bit flips when paired with differential write is selected to be written. Flip-Min has been showed to achieve fewer bit flips than Flip-N-Write, while incurring a space overhead of 12.5%.

#### 2.2.2 Error Correction Schemes

For post-write fault tolerance, coding theory is an old and well established discipline in which several codes to tolerate errors have been proposed. For instance, SEC-DED [28] is a well known error correcting code deployed in DRAM modules to recover from bit errors. SEC-DED can cover one error and detect a second one. Given its low capability, SEC-DED does not provide enough coverage for memories expected to exhibit multiple simultaneous errors such as PCM. Accordingly, multi-bit error correcting codes such as *BCH* [7] are considered. Interestingly, the error correcting capability of multi-bit error correcting codes is tunable. Actually, setting the capability of the code depends on two factors. The first is the space overhead that can be incurred in terms of the number of added auxiliary bits as increasing the error correction capability requires increasing the number of auxiliary bits. The second is the complexity of the code as increasing its capability increases its complexity [82, 79]. Hence, there exists a trade-off between the capability of error correcting codes and their space and complexity overhead.

In addition to coding theory, several error correction schemes that were designed specifically for PCM's fault model have been proposed. Among those, *RDIS* [53] was proven to have a capability of tolerating a significantly large number of faults. RDIS' encoding process consists of

identifying a set containing all the SA-W cells. This set is dubbed the *invertible set* as it is enough to read its elements inverted to retrieve the intended data to be written. To identify this set, RDIS logically represents a memory block as a two-dimensional array and introduces a counter for each row and column. The value of each counter is incremented if the row or column it represents exhibits a SA-W cell. Subsequently, all the cells whose corresponding row and column counters share the same value are extracted as a sub-array. The latter is a candidate invertible set. Nevertheless, the sub-array could contain SA-R cells as they happen to be on the intersection of a row and a column both containing at least one SA-W cell. To take out the SA-R cells, the initial sub-array cells are inverted and the corresponding counters are incremented based on the newly revealed SA-W cells. Hence, a new sub-array that is smaller than the initial one is formed. This process is repeated recursively until the size of the initial sub-array is reduced to zero. Figure. 6.

Figure 6: RDIS encoding process. Highlighted cell(s) represent(s) the extracted sub-array at each step. Patterned cells represent the identified invertible set.

shows an example of RDIS's encoding process on a block that suffer from three stuck-at cells. After the completion of the first write operation, two of the stuck-at faults end up being SA-W and one cell ends up being SA-R leading to an initial sub-array of 4 cells (highlighted in yellow). To recover from the two SA-W cells, RDIS inverts the data to written within the initial sub-array. Consequently, one cell ends up being SA-W as the inversion step has the effect of exchanging the role of SA-W and SA-R cells. Subsequently, the corresponding flags and of the new SA-W cell are incremented and a second sub-array is formed. At last, RDIS inverts the data within the second sub-array rendering the remaining SA-W cell to be become SA-R. Thus, reducing the size of the initial sub-array to zero and forming an invertible set of 3 cells (blue pattern).

When it comes to the correction capability of RDIS, the recovery from three stuck-at faults is

guaranteed. Nevertheless, RDIS can recover from a higher number of faults with a significantly high probability. In fact, a specific pattern of faults has to form for RDIS to halt. For instance, if the rows and columns of an extracted sub-array each contains at least two stuck-at cells such that their location is adjacent to the location of the faults in another row or column then such a pattern causes RDIS to halt and is known as a loop of faults. In fact, such a pattern prevents an extracted sub-array from getting reduced to 0 when the faults happen to be alternatively stuck. Figure 7 shows an example of a loop of four faults. The size of the initial sub-array cannot be reduced as the example shows. Each inversion step will simply exchange the role of the faulty cells between SA-R and SA-W without being able to eliminate any cell.

Figure 7: A loop of faults that causes RDIS to halt. Highlighted cells represent the extracted sub-array at each inversion step.

In addition to RDIS, several other error correcting schemes designed specifically for PCM have been proposed. First, Error Correcting Pointer (ECP) [73] provides a preassigned number of programmable "correction entries". A correction entry holds a pointer (address) to a faulty cell within the protected block and a "patch" cell that replaces the faulty one. When a faulty cell is detected, a correction entry is allocated to cover the cell. A memory block is de-commissioned when the number of faulty cells exceeds that of the correction entries.

SAFER (Stuck-at-Fault Error Recovery) [76] When the value of the faulty cell is different from the intended value to be written, all cells in the group are written inverted. If the data block is to be partitioned into n groups, then SAFER allows  $\log_2 n$  "repartitions". Repartitioning is done whenever a new fault is detected. Therefore, SAFER guarantees the recovery from  $\log_2 n + 1$ faults. Any additional fault is tolerated only if it occurs in a fault-free group. Otherwise, the block has to be retired. PAYG (Pay-As-You-Go) [66] is a resilient architecture proposed to decrease the storage overhead of auxiliary bits information required by ECP and SAFER. Essentially, PAYG moves from a uniform allocation of auxiliary bits across the protected memory blocks to a dynamic on demand allocation. PAYG exploits the variability in lifetime that the memory blocks exhibit and assigns more auxiliary bits to memory blocks that suffer from a large number of faulty cells.

#### 2.2.3 Bad Block Management

When the number of hard faults within a protected block gets above the capability of the deployed error correction scheme, the block turns defective and write failures can start to occur. While this scenario is rare in DRAM where transient errors are dominant, it is a common practice in NAND flash SSDs [55] as several blocks turn defective due to limited endurance. After the first write failure is detected on a block, it is labelled bad and it is subsequently replaced by a healthy spare block; a practice commonly known as *bad block management* [56, 85, 32]. Bad block management is expected to remain integral for PCM due to its limited endurance.

#### 2.3 DIFFERENCES FROM PREVIOUS WORK

The work in this thesis has substantial differences to the previously proposed work. All the previous work at the pre-write fault avoidance stage focused on reducing the number of bit flips without exploiting the endurance degradation asymmetry in writing different bit values. CAFO introduces a model that assigns different endurance costs to each cell that requires programming; thus capturing the asymmetry in the write cost. In addition, CAFO introduces a new a 2D encoding scheme while previous work considered a 1D model. A 2D encoding allows for several modifications of the write data, which lead to a further reduction to the endurance cost of servicing write requests.

To increase the capability of an error correcting code, a number of auxiliary cells has to be added. In general, a block of size n requires  $t \times lgn$  auxiliary cells to recover from t errors [7]. Increasing the capability of an error correcting code does not only increase its space overhead, but also increases its encoding/decoding complexity. Data Inversion is capable of allowing an error correcting code of capability t to tolerate additional faults without the need of introducing a large number of auxiliary cells. In fact, Data Inversion introduces only one additional auxiliary cell. Tolerating the additional number of faults is accomplished through exploiting the data dependent nature of errors. Thus, Data Inversion enables tolerating an additional faults with a significantly decreased complexity and space overhead.

When it comes to bad block management, this thesis takes a completely different approach in managing defective blocks. Data Dependent Sparing builds on the observation that write failures on defective blocks are rare due to the data dependent nature of errors to delay the retirement of defective blocks and better utilizes the available spare blocks.

#### **3.0 PRE-WRITE FAULT AVOIDANCE**

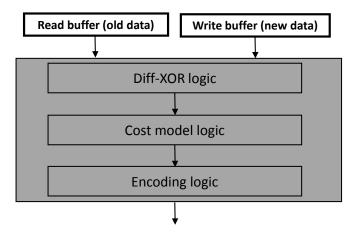

For endurance constrained memories such as PCM, it is of great importance to decelerate the wearout rate of storage cells. One way of achieving this goal is to service write requests while inducing as few bit flips as possible. In its simplest form, bit flip reduction can be achieved through a bit by bit comparison between the new data vector to be written and currently stored data vector. Subsequently, only those bit positions with non-matching bit values would be toggled. In this sequel, the similar the new data is to the old stored data, the fewer the number of bit flips. Accordingly, manipulating the new data vector to make it more similar to the old vector would yield in bit flips reduction. This manipulation consists of a well defined encoding of the new data vector to an intermediate vector that is similar to the old stored vector. It is to be noted that a well defined encoding is a requirement so that the data is properly decoded at retrieval time. While a number of bit flip reduction techniques have been proposed [15, 31], none of those techniques are aware of the write endurance asymmetry (refer to Section 2.1.3) manifested by the RESET state (binary "0") being more detrimental to endurance than the SET state (binary "1"). This chapter presents CAFO: Cost-Aware Flip Optimization [51]. CAFO is aware of the write endurance asymmetry. It introduces a cost model that captures the deterioration of endurance caused by each bit flip. Subsequently, CAFO encodes the data vector into a form that would require a lower overall endurance cost than the originally intended data vector to be written. Conceptually, CAFO makes the key contribution of moving from bit flip reduction to cost reduction.

#### 3.1 CAFO DETAILS

Minimizing the number of bit flips seems to be a good solution to tackle the endurance problem of PCM. Nonetheless, minimizing the number of bit flips in a manner that is oblivious to the asymmetry of writing different bit values could backfire. For example, let us assume that writing a bit value of "0" on a PCM cell has an endurance cost that is 4 times more than the endurance cost of writing a bit value of "1" [87, 39]. Furthermore, let us assume that the data vector of a submitted write request on a PCM block differs than the previously programmed vector on the same block by 3 cells that would need to be flipped from "0" to "1". If a bit flip minimization scheme encodes the data in such a way that brings the number of bit flips from 3 to 1, then the actual gain that is achieved depends on the bit value to be written by the single flip. While a single bit flip of " $0 \rightarrow 1$ " would be a significant improvement, a single bit flip of " $1 \rightarrow 0$ " would be harmful as writing a "0" is 4 times more detrimental to endurance than writing a "1".

Clearly, focusing solely on reducing the number of bit flips of a write operation does not capture all the dimensions affecting the endurance. This said, there is a need to associate a cost to write operations and to present schemes that aim at reducing the cost of servicing write requests.

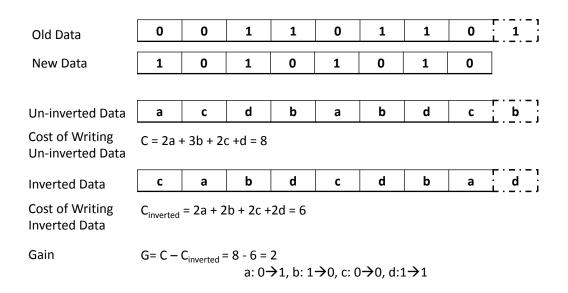

#### 3.1.1 Cost Model

When a write request to a block is submitted, its data vector is compared to the previously written data vector at the same block. Subsequently, the cells in the block can be classified into two categories: matching cells and non-matching cells. Accordingly, the proposed model labels the cost of matching cells with "c" and "d" for matching bit values of "0" and "1" respectively. Similarly, the cost of non-matching cells are labeled with "a" and "b" for bit flips of " $0 \rightarrow 1$ " and " $1 \rightarrow 0$ " respectively. Figure 8 shows an example for an 8 bit block where the stored data is compared to the new data to determine the endurance cost of programming each cell within the block.

Setting the cost for "a", "b", "c" and "d" depends on the memory technology being modeled and the objective function being optimized. For example, only non-matching cells would require programming in PCM. Hence, both "c" and "d" would be assigned a cost value of "0" as cells with such labels do not cause any endurance degradation. Moreover, the asymmetry of flipping

| Currently Stored Data Vector | 0 | 0    | 1      | 1                | 0      | 1              | 1 | 1 |

|------------------------------|---|------|--------|------------------|--------|----------------|---|---|

|                              |   |      |        |                  |        |                |   |   |

| New Data Vector              | 1 | 0    | 1      | 0                | 1      | 0              | 1 | 0 |

|                              |   |      |        |                  |        |                |   |   |

| Cost of Writing New Vector   | а | с    | d      | b                | а      | b              | d | b |

|                              |   | a: 0 | →1, b: | 1 <b>→</b> 0, c: | 0→0, 0 | d:1 <b>→</b> 1 |   |   |

Figure 8: Cost model.

" $0 \rightarrow 1$ " and " $1 \rightarrow 0$ " would be captured through assigning different cost values to "a" and "b" e.g. "a =1 ", "b = 3" if the endurance cost of writing a "0" is 3 times the endurance cost of writing a "1".

Adopting this cost model would give the ability to associate a cost to every write operation. As a matter of fact, the cost of a write operation, C, would be computed by the following formula:

$$C = n_{0 \to 1}a + n_{1 \to 0}b + n_{0 \to 0}c + n_{1 \to 1}d$$

(3.1)

where  $n_{0\to1}$ ,  $n_{1\to0}$ ,  $n_{0\to0}$  and  $n_{1\to1}$  are the total numbers of a, b, c and d flips respectively. Once the cost of a write operation has been computed, it is of great benefit to service write requests while minimizing the write cost, C. It is worth noting that the proposed cost model is general and can be applied to other objectives than calculating the endurance cost. For example, the cost model could be applied to capture the write energy cost. In addition, the model is not specific to PCM and can be applied to any memory technology that exhibits asymmetries such as STT-RAM. Nevertheless, this thesis focuses on salvaging the endurance of PCM. Hence, the next section presents CAFO's new encoding scheme that aims at servicing write requests while minimizing the overall endurance cost.

| Stored Data Vector                                             | 0                                      | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

|----------------------------------------------------------------|----------------------------------------|---|---|---|---|---|---|---|

| New Data Vector                                                | 1                                      | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

| Un-inverted Data                                               | а                                      | С | d | b | а | b | d | b |

| Cost of Writing<br>Un-inverted Data $C= 2a + 3b + 1c + 2d = 8$ |                                        |   |   |   |   |   |   |   |

| Inverted Data                                                  | С                                      | а | b | d | С | d | b | d |

| Cost of Writing<br>inverted Data                               | $C_{inverted} = 1a + 2b + 2c + 3d = 5$ |   |   |   |   |   |   |   |

|                                                                |                                        |   |   |   |   |   |   |   |

Figure 9: Gain calculation where the costs of a, b, c and d are 1, 2, 0 and 0 respectively.

#### 3.1.2 Cost Minimization Encoding Scheme

CAFO models an *N* bits memory block as a logical arrangement of an  $n \times m$  array. For each row and column, an additional auxiliary bit is added. When a write request is submitted, the new data is compared to the old written data in order to determine the cells that need to be updated as their bit values differ from previously programmed bit values. Subsequently, the cost of each bit flip is assigned in accordance with the cost model presented in the previous section.

Next, the gain of each row is determined as the difference between the costs of writing the data vector in two different forms. The first is the un-inverted form while the second is the inverted form. Specifically, the gain can be determined according to the following formula:

$$G = C - C_{inverted} \tag{3.2}$$

where G is the gain, C is the cost of writing the data in the un-inverted form and  $C_{inverted}$  is the cost of writing the data in the inverted form. Figure 9 shows an example of calculating the gain where the cost of writing the data is calculated in accordance to Formula (3.1). At first, the cost of writing the data un-inverted is determined. Then, the data is logically inverted and its writing cost

is determined. Subsequently, the gain (3) is calculated through subtracting the cost of writing the data un-inverted (8) from the cost of writing the data inverted (5).

A positive gain implies that inverting the data for a row has a lower overall cost than the uninverted data. Hence, every row with a positive gain is inverted and its corresponding auxiliary bit is toggled. After flipping the rows with positive gains, the same process is applied to the columns. Next, the gain of the rows is recalculated as flipping the columns may have turned the gain of certain rows to become positive. In practice, the process of flipping the rows and columns is repeated until the gain of every row and column is either zero or negative. Algorithm 3.1 shows the steps taken by CAFO's encoding scheme to reduce the cost of write operations.

| Algorithm 3.1 CAFO Encoding                            |  |  |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|--|--|

| 1: $Invert = True$                                     |  |  |  |  |  |  |  |

| 2: $ColumnCheck = False$                               |  |  |  |  |  |  |  |

| 3: while <i>Invert</i> do                              |  |  |  |  |  |  |  |

| 4: <b>if</b> <i>PositiveGainRows</i> () <b>then</b>    |  |  |  |  |  |  |  |

| 5: Flip Rows with Positive Gain                        |  |  |  |  |  |  |  |

| 6: else                                                |  |  |  |  |  |  |  |

| 7: <b>if</b> ColumnCheck <b>then</b>                   |  |  |  |  |  |  |  |

| 8: $Invert = False$                                    |  |  |  |  |  |  |  |

| 9: break                                               |  |  |  |  |  |  |  |

| 10: <b>end if</b>                                      |  |  |  |  |  |  |  |

| 11: end if                                             |  |  |  |  |  |  |  |

| 12: <b>if</b> <i>PositiveGainColumns()</i> <b>then</b> |  |  |  |  |  |  |  |

| 13: Flip Columns with Positive Gain                    |  |  |  |  |  |  |  |

| 14: $ColumnCheck = True$                               |  |  |  |  |  |  |  |

| 15: <b>else</b>                                        |  |  |  |  |  |  |  |

| 16: $Invert = False$                                   |  |  |  |  |  |  |  |

| 17: end if                                             |  |  |  |  |  |  |  |

| 18: end while                                          |  |  |  |  |  |  |  |

The *Invert* variable at line 1 serves as the loop invariant at line 3. In case the rows shows a negative gain, the *ColumnCheck* variable at line 2 serves as a flag to avoid calculating the gain of

the columns again if they have already been calculated. In fact, if the columns have already been flipped and the gain of the rows does not yield in a positive gain for any of the rows then the gain of the columns does not change and remains negative. The procedure at line 4, *PositiveGainRows()*, computes the gain of every row and return the list of rows that yields a positive gain in order to be flipped. If the list is empty and the gain of the columns have already been calculated, i.e. this is not the first iteration of the loop, then the algorithm terminates through setting the loop invariant to false at line 8 and discontinues the execution of the remaining of the statements within the body of the loop at line 9. In case any row got flipped or it is the first iteration of the loop, the *PositiveGainColumns()* procedure at line 12 returns a list of columns that have a positive gain. If the list in not empty, then the returned columns are flipped and the *ColumnCheck* flag is set at lines 13 and 14 respectively. If the list is empty, then the algorithm terminates through setting the loop invariant at line 16 to false. An empty list indicates no positive gain for any of the columns which is the same for the row as their gain has already been calculated and the rows with positive gain have already been flipped.

Applying a data flip to reduce the cost of write operations have been considered before e.g. Flip-N-Write. However, the flips are only considered at either the level of rows or columns without interleaving. The rationale behind the proposed encoding scheme is that allowing the interleaving of rows and columns data flips could allow more overall cost reduction as compared with inverting the rows or columns only. As a matter of fact, it can be shown that the interleaving could turn a row (column) that has had initially a negative gain into a positive gain. Hence, such a row (column) should be flipped resulting in an overall reduction in the write operation cost. It is to be noted that a flip is always guaranteed to reduce the overall cost as the decision to flip is based on a positive gain derived through Formula (3.2).

It is important to mention that CAFO's encoding algorithm is guaranteed to terminate. Stated differently, it is not possible for the alternation of the flips between the rows and the columns to continue infinitely. Consider any combination of one row and one column within the 2D block. They both intersect at one cell. If the row gets inverted then the intersecting cell could end up in the state of either a matching cell or a non-matching cell. Next, if the column gets flipped due to positive gain and the intersecting cell before the flip was in the non-matching state then the non-positive gain of the row increases (the row got flipped before so its gain is either negative or zero)

as the non-matching state of the intersecting cell turned matching i.e. the cell does not require programming which decreases the cost of writing the data un-inverted. Hence, the flip of the column will not lead to a second flip for the row. In the other case where the state of the intersecting cell before flipping the column was matching, the gain of the row could become positive as the state of the intersecting cell turns into non-matching which increases the cost of writing the data uninverted. Now, if the gain of row becomes positive then it will be flipped again which will increase the non-positive gain of the already flipped column as the state of the intersecting cell becomes non-matching after the second flip of the row. Accordingly, given any combination of a row and a column after two flips for the row (column) and one flip of the column (row) it is guaranteed that one of them will incur a negative gain which prevents an infinite alternation between the flips of the rows and the columns and guarantees termination.

Another point to note is concerning the optimality of CAFO's encoding algorithm. In theory, CAFO's encoding could be interpreted as the Gale-Berlekamp Switching Game[13]. This game considers an m by n grid of light bulbs and assigns and light switch for every row and for every column. Two players, A and B, alternate in turning the switches in order to achieve two different objectives. Player A tries to maximize the number of light bulbs that are "on" while player B tries to maximize the number of light bulbs that are "off". The Gale-Berlekamp game was proven to be NP-hard [72]. Without loss of generality, CAFO's encoding setting can be reduced to the Gale-Berlekamp game which makes an optimal encoding for CAFO NP-hard. Hence, Algorithm 3.1 is not optimal and uses the heuristic of alternating the flips between the rows and the columns until a non-positive gain is reached for every row and column. In fact, Section 3.1.4 presents an optimization to further improve the cost reduction capability of the encoding algorithm.

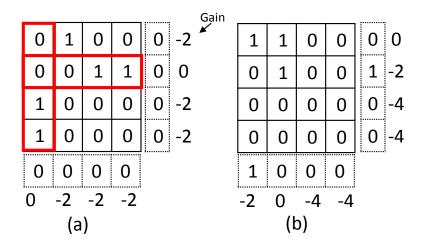

### 3.1.3 CAFO Encoding Example

To make the encoding process clear, Figure 10 shows an example where a 64 bits block is represented as an  $8\times8$  array. For ease of illustration, let us assume that the costs of the flips " $0\rightarrow1$ " and " $1\rightarrow0$ ", i.e. "a" and "b", are equal while the costs of the flips " $0\rightarrow0$ " and " $1\rightarrow1$ ", i.e. "c" and "d", are both zero. Accordingly, "1" represents a cell that needs to flipped while "0" otherwise. Since rows 5 and 8 both exhibit a positive gain as shown in Figure 10(a), those rows are flipped.

Figure 10: CAFO encoding example where the number of bit flips is reduced from 33 to 21. A "0" represents a matching cell (c = d = 0), and a "1" represents a non-matching cell (a = b = 1). "Gain" is calculated as per Formula (3.2). Shaded cells represent rows and columns that are to be flipped.

Subsequently, the gain of columns is computed as shown in Figure 10(b). Since columns 4 and 6 both show a positive gain, they are both flipped and the gain of the rows is recalculated as illustrated in Figure 10(c). Next, row 8, incurring a positive gain once again, gets flipped as shown in Figure 10(d). Now that all rows and columns incur a non-positive gain, the encoding process terminates. Overall, Figure 10 shows that the proposed encoding scheme reduces the cost (number of bit flips) from 33 to only 21. It is to be noted that the example does not take into consideration the cost of toggling the auxiliary bits. Nevertheless, our scheme can easily account for the cost of the auxiliary bits as shown in Section 3.1.5.

To illustrate the difference in the encoding process between CAFO and a row only flip scheme, Figure 11 shows that applying Flip-N-Write on the same data as in Figure 10(a) would reduce the number of bit flips from 33 to 25. Hence, CAFO reduces the cost of the same write operation by almost 20% more than Flip-N-Write. It is to be noted that a row is formed of 4 bits so that both schemes have the same level of space overhead (16 auxiliary bits).

In general, flipping a row (column) could increase the gain of the columns (rows). In turn, when those columns (rows) are flipped the overall cost would be reduced. For example, row 5 in Fig. 10(b) got flipped which increased the gain of column 2 as the intersection bit in between the row and the column flipped from bit value "0" to "1". When column 2 got flipped, the intersection bit with row 5 got reverted back to bit value "0". Thus, interleaving the flips of rows and columns allowed for the reduction of one additional bit for both the row and the column as opposed to flipping only the row or the column.

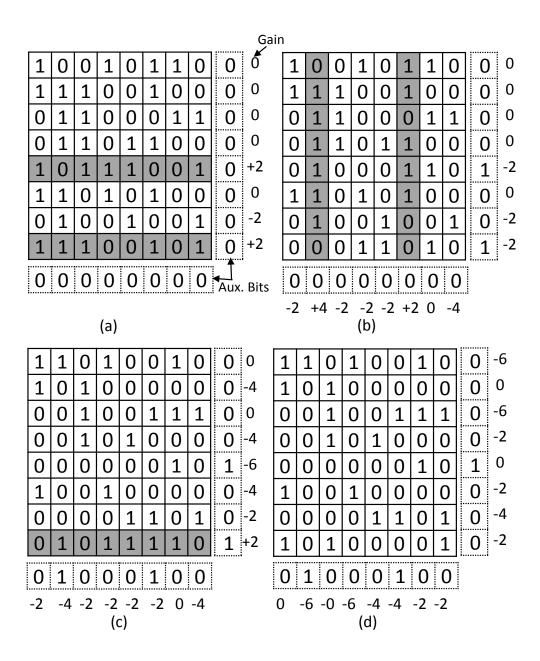

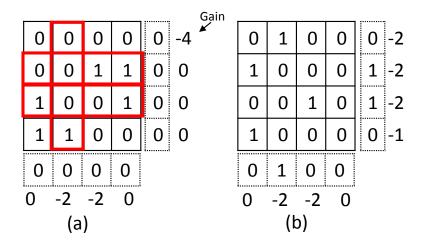

# 3.1.4 Encoding Scheme Optimization

Algorithm 3.1 assumes that the overall cost of a write operation cannot be further reduced once the gain of every row and column is non-positive. This section investigates the possibility of further reducing the cost of a write operation even when no row or column shows a positive gain. Consider the example in Figure 12 where a data cell with "1" represents a cell whose bit value differs from the current written value and "0" otherwise i.e. the costs of a, b, c and d flips are 1, 1, 0 and 0 respectively. Although all the rows and columns incur a non-positive gain, the example portrays that flipping row 2 and column 1 would reduce the cost of the write operation from 5 bit flips to 3.

Figure 11: An example of Flip-N-Write (FNW) encoding where the number of bit flips is reduced from 33 to 25. A data cell with "0" represents a match with the already written bit, "1" otherwise. Shaded cells represent a row that is to be flipped.

Motivated by the example in Figure 12, the conditions that have to be met in order for the cost to be reduced when flipping a row and a column with non-positive gains are next formulated.

Let us start by defining  $g_{r,c}$  as the gain of flipping the cell intersecting at row r and column c, which is determined by subtracting the cost of writing the intersecting cell un-inverted from the cost of writing the intersecting cell inverted. Furthermore, let  $G_r$  and  $G_c$  be the gains of row r and column c such that  $G_r \leq 0$  and  $G_c \leq 0$ . When row r and column c are both flipped together, the cell at their intersection does not get flipped. Accordingly, the gain of flipping the intersecting cell,  $g_{r,c}$ , has to be deducted from the overall gain of flipping both the row and the column. Hence, the total gain,  $G_{r+c}$ , of flipping row r and column c would be:

$$G_{r+c} = G_r + G_c - 2g_{r,c} \tag{3.3}$$

where  $g_{r,c}$  is multiplied by 2 as the local gain of the intersecting cell has to be deducted from the gains of both row r and column c.

Based on Formula (3.3), it is possible to incur gain for  $G_r \leq 0$  and  $G_c \leq 0$  if  $g_{r,c} < 0$ . In fact,  $g_{r,c}$  is less than zero when its bit value to be programmed matches the previously written bit value, i.e. a matching cell, as only such a cell would incur a negative gain in a flip operation. Accordingly,

Figure 12: An example that shows that the cost of a write can still be reduced even when no row or column shows a positive gain. A data cell with "0" represents a match with the already written bit, "1" otherwise. Flipped rows and column are highlighted. The number of bit flips is reduced from 5 to 3.

flipping a row and a column incurring a non-positive gain would yield in cost reduction if the following condition is met:

$$G_{r+c} = G_r + G_c - 2g_{r,c} > 0. ag{3.4}$$

Going back to the example in Figure 12,  $g_{2,1}$  is -1 as the cost of "a" and "b" flips is one. Thus, Formula (3.4) is satisfied as 0 + 0 - 2(-1) > 0.

The suggested optimization is not limited to one column and one row. As a matter of fact, the optimization works for one column with multiple rows as long as the overall cost is reduced. Generally, flipping one column, c, intersecting with a subset of rows, S, yields in overall cost reduction if the following formula is satisfied:

$$\sum_{r \in S} G_r + G_c - 2 \sum_{r \in S} g_{r,c} > 0.$$

(3.5)

Similarly, one row could be selected with multiple columns and Formula 3.5 can be equally applied.

Figure 13 illustrates an optimization example where one column is flipped with two rows. Initially, all columns and rows show a non-positive gain (Figure 13(a)). Nevertheless, column 2 intersects with rows 2 and 3 at two matching cells. Accordingly, the selected column and rows

Figure 13: An example of CAFO's optimization. A data cell with "0" represents a match with the already written bit, "1" otherwise. The cost of flipping an intersecting matching cell  $c_{r,c}$  is -1. Flipped rows and column are highlighted in red. The number of bit flips is reduced from 6 to 4.

would satisfy Formula (3.5), i.e. -2 + 0 + 4 > 0. Consequently, the overall cost of the write operation could be reduced from 6 bit flips to 4 after flipping the select column and rows as shown in Figure 13(b). This example does not consider the cost of auxiliary bits for simplicity. Taking the cost of writing the auxiliary bits is tackled in the next section.

At last, the proposed optimization can be theoretically generalized so that a subset of rows and a subset of columns are flipped simultaneously. Nevertheless, selecting multiple rows and columns is not feasible from an implementation point of view because of the combinatorial number of row/column combinations. Accordingly, this thesis only considers the case of selecting one row with multiple columns and one column with multiple rows. Moreover, applying the optimizations is a purely design choice. As a matter of fact, the evaluation section shows that CAFO outperforms the existing schemes even without applying any optimization.

### **3.1.5** Cost of Auxiliary Bits

So far, CAFO's encoding process did not consider the cost of writing the auxiliary bits. Taking the cost of the auxiliary bits into consideration is easy and simple. As stated before, the cost model of CAFO would compare the new data to be written on a block to the previously written data in order

Figure 14: An example of taking the cost of the auxiliary bit into consideration when computing the gain. The costs of "a", "b", "c" and "d" are 1, 2, 0 and 0 respectively. Dotted cells represent auxiliary bits.

to form the differential vector. Accordingly, the previously written auxiliary bits are read within the step of forming the differential vector. Subsequently, the cost of the new auxiliary bits to be written can be taken into consideration during the encoding step of CAFO.