# ARCHITECTURAL TECHNIQUES FOR MULTI-LEVEL CELL PHASE CHANGE MEMORY BASED MAIN MEMORY

by

# Lei Jiang

B.S., Shanghai Jiao Tong University, 2006

M.S., Shanghai Jiao Tong University, 2009

Submitted to the Graduate Faculty of the Swanson School of Engineering in partial fulfillment of the requirements for the degree of

Ph.D. in Computer Engineering

University of Pittsburgh

2014

# UNIVERSITY OF PITTSBURGH SWANSON SCHOOL OF ENGINEERING

This dissertation was presented

by

Lei Jiang

It was defended on

October 17th, 2014

and approved by

Jun Yang, Ph.D., Associate Professor, Department of Electrical and Computer Engineering Youtao Zhang, Ph.D., Associate Professor, Department of Computer Science Bruce R. Childers, Ph.D., Professor, Department of Computer Science Steven P. Levitan, Ph.D., John A. Jurenko Professor, Department of Electrical and Computer Engineering

Konstantinos Pelechrinis, Ph.D., Assistant Professor, School of Information Sciences

Dissertation Directors: Jun Yang, Ph.D., Associate Professor, Department of Electrical and

Computer Engineering,

Youtao Zhang, Ph.D., Associate Professor, Department of Computer Science

Copyright © by Lei Jiang 2014

# ARCHITECTURAL TECHNIQUES FOR MULTI-LEVEL CELL PHASE CHANGE MEMORY BASED MAIN MEMORY

Lei Jiang, Ph.D.

#### University of Pittsburgh, 2014

Phase change memory (PCM) recently has emerged as a promising technology to meet the fast growing demand for large capacity main memory in modern computing systems. Multi-level cell (MLC) PCM storing multiple bits in a single cell offers high density with low per-byte fabrication cost. However, PCM suffers from long write latency, short cell endurance, limited write throughput and high peak power, which makes it challenging to be integrated in the memory hierarchy.

To address the long write latency, I propose write truncation to reduce the number of write iterations with the assistance of an extra error correction code (ECC). I also propose form switch (FS) to reduce the storage overhead of the ECC. By storing highly compressible lines in single level cell (SLC) form, FS improves read latency as well.

To attack the short cell endurance and large peak power, I propose elastic RESET (ER) to construct triple-level cell PCM. By reducing RESET energy, ER significantly reduces peak power and prolongs PCM lifetime.

To improve the write concurrency, I propose fine-grained write power budgeting (FPB) observing a global power budget and regulates power across write iterations according to the step-down power demand of each iteration. A global charge pump is also integrated onto a DIMM to boost power for hot PCM chips while staying within the global power budget.

To further reduce the peak power, I propose intra-write RESET scheduling distributing cell RESET initializations in the whole write operation duration, so that the on-chip charge pump size can also be reduced.

## TABLE OF CONTENTS

| 1.0 | IN'           | TRODUCTION                                                          | 1  |

|-----|---------------|---------------------------------------------------------------------|----|

|     | 1.1           | THE CHALLENGES IN MLC PCM DEPLOYMENT                                | 5  |

|     |               | 1.1.1 Long write latency                                            | 5  |

|     |               | 1.1.2 Short cell endurance                                          | 5  |

|     |               | 1.1.3 Limited write throughput                                      | 6  |

|     |               | 1.1.4 Large peak power                                              | 7  |

|     | 1.2           | THESIS OVERVIEW                                                     | 7  |

|     | 1.3           | CONTRIBUTIONS                                                       | 9  |

|     |               | 1.3.1 R/W latency shorten technique                                 | 9  |

|     |               | 1.3.2 Cell endurance enhancement and write power reducing technique | 10 |

|     |               | 1.3.3 Write throughput improvement technique                        | 11 |

|     |               | 1.3.4 Peak power reduction technique                                | 12 |

|     | 1.4           | THESIS ORGANIZATION                                                 | 13 |

| 2.0 | BA            | SICS OF PHASE CHANGE MEMORY                                         | 14 |

|     | 2.1           | PCM FUNDAMENTALS                                                    | 14 |

|     | 2.2           | PCM WRITE                                                           | 14 |

|     | 2.3           | PCM READ                                                            | 18 |

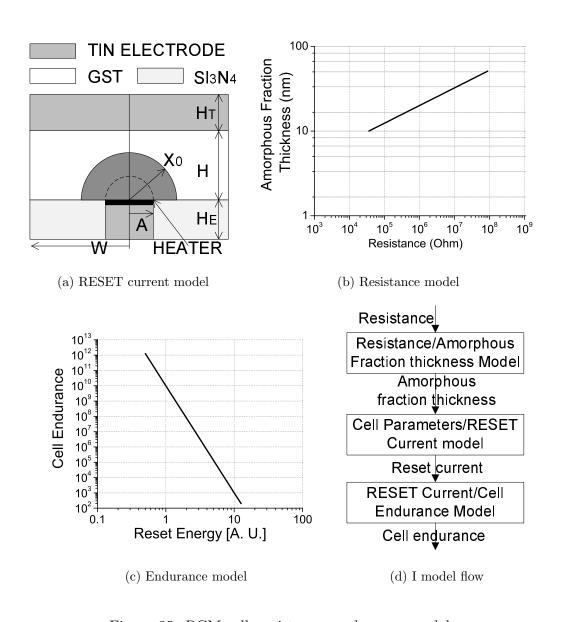

| 3.0 | $\mathbf{PR}$ | CIOR ART                                                            | 20 |

|     | 3.1           | ERROR CORRECTING AND SALVAGE                                        | 20 |

|     | 3.2           | REDUCING EFFECTIVE READ LATENCY                                     | 22 |

|     | 3.3           | COMPRESSION ON PCM                                                  | 22 |

|     | 3.4           | PROCESS VARIATION AND OVER-RESET                                    | 23 |

|            | 3.5           | PCM WRITE POWER MANAGEMENT                           | 23 |

|------------|---------------|------------------------------------------------------|----|

|            | 3.6           | MLC PCM                                              | 24 |

|            | 3.7           | ASYMMETRIC WRITE                                     | 24 |

|            | 3.8           | PCM CHARGE PUMP DESIGN                               | 25 |

| 4.0        | $\mathbf{MI}$ | C PCM WRITE LATENCY REDUCTION                        | 26 |

|            | 4.1           | MOTIVATION ON MLC PCM LONG WRITE LATENCY             | 26 |

|            | 4.2           | WRITE TRUNCATION                                     | 28 |

|            | 4.3           | FORM SWITCH                                          | 31 |

|            | 4.4           | MLC PCM WRITE LATENCY REDUCTION EXPERIMENTAL METHOD- |    |

|            |               | OLOGY                                                | 35 |

|            | 4.5           | MLC PCM WRITE LATENCY REDUCTION EVALUATION           | 38 |

|            |               | 4.5.1 WT and FS implementation overhead              | 38 |

|            |               | 4.5.2 Effective write latency                        | 39 |

|            |               | 4.5.3 Effective read latency                         | 39 |

|            |               | 4.5.4 Performance analysis                           | 40 |

|            |               | 4.5.5 WT section size                                | 41 |

|            |               | 4.5.6 Iteration latency                              | 43 |

|            |               | 4.5.7 Sensitivity to write model                     | 44 |

| <b>5.0</b> | MI            | C PCM ENDURANCE ENHANCEMENT                          | 47 |

|            | 5.1           | MOTIVATION ON MLC PCM SHORT CELL ENDURANCE           | 47 |

|            | 5.2           | MLC PCM RESISTANCE RANGES                            | 48 |

|            |               | 5.2.1 The PCM endurance model                        | 49 |

|            |               | 5.2.2 The work flow                                  | 49 |

|            | 5.3           | THE DETAILS OF ELASTIC RESET                         | 50 |

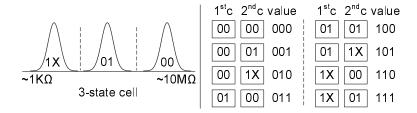

|            |               | 5.3.1 Constructing non- $2^n$ -state MLC cells       | 50 |

|            |               | 5.3.2 Elastic RESET                                  | 51 |

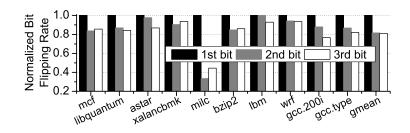

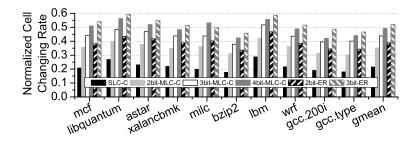

|            |               | 5.3.3 Fraction encoding                              | 52 |

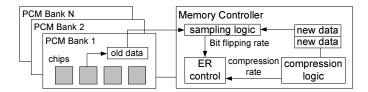

|            |               | 5.3.4 Architectural designs                          | 52 |

|            | 5.4           | MLC PCM ENDURANCE ENHANCEMENT EXPERIMENTAL METHOD-   |    |

|            |               | OLOCV                                                | 59 |

|     | 5.5 | MLC PCM ENDURANCE ENHANCEMENT EVALUATION                    | 54 |

|-----|-----|-------------------------------------------------------------|----|

|     |     | 5.5.1 Hardware overhead                                     | 55 |

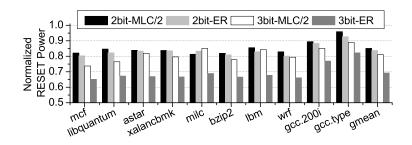

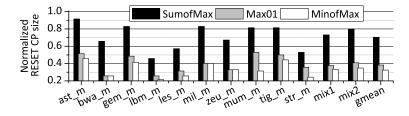

|     |     | 5.5.2 RESET power reduction                                 | 55 |

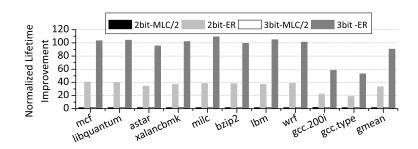

|     |     | 5.5.3 Lifetime improvement                                  | 55 |

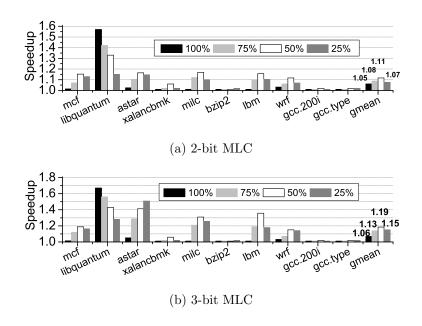

|     |     | 5.5.4 Exploiting low-power write for performance            | 55 |

|     |     | 5.5.5 Compression study                                     | 56 |

| 6.0 | MI  | C PCM WRITE POWER MANAGEMENT                                | 62 |

|     | 6.1 | MOTIVATION ON MLC PCM LARGE WRITE POWER                     | 62 |

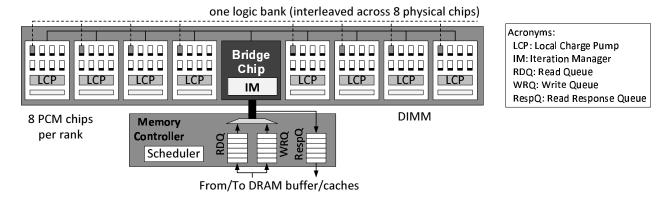

|     | 6.2 | MLC PCM MEMORY ARCHITECTURE                                 | 64 |

|     |     | 6.2.1 Non-deterministic MLC write                           | 65 |

|     |     | 6.2.2 DIMM power budget                                     | 66 |

|     |     | 6.2.3 Chip level power budget                               | 67 |

|     | 6.3 | THE POWER MODEL                                             | 68 |

|     | 6.4 | FPB-IPM: ITERATION POWER MANAGEMENT                         | 69 |

|     |     | 6.4.1 Architecture enhancement                              | 70 |

|     |     | 6.4.2 Multi-RESET                                           | 71 |

|     | 6.5 | FBP-GCP: MITIGATING CHIP POWER LIMITATION BY A GLOBAL       |    |

|     |     | CHARGE PUMP                                                 | 73 |

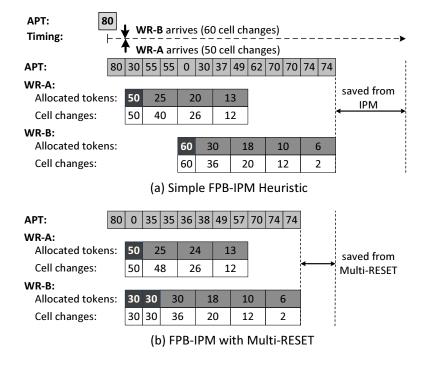

|     |     | 6.5.1 FBP-GCP scheme                                        | 73 |

|     |     | 6.5.2 Power efficiency                                      | 75 |

|     |     | 6.5.3 Cell mapping optimization                             | 76 |

|     | 6.6 | MLC PCM WRITE POWER MANAGEMENT EXPERIMENTAL METHOD-         |    |

|     |     | OLOGY                                                       | 78 |

|     |     | 6.6.1 MLC PCM write power management baseline configuration | 78 |

|     |     | 6.6.2 MLC PCM write power management simulated workloads    | 80 |

|     | 6.7 | MLC PCM WRITE POWER MANAGEMENT EXPERIMENTAL RESULTS         | 81 |

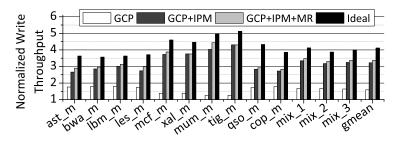

|     |     | 6.7.1 Effectiveness of FPB-GCP                              | 82 |

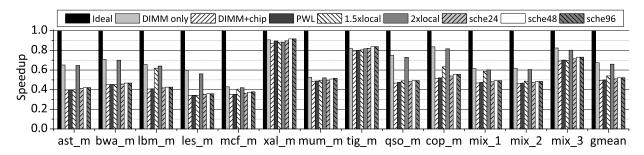

|     |     | 6.7.1.1 Performance improvement                             | 82 |

|     |     | 6.7.1.2 Cell mapping optimization                           | 83 |

|     |     | 6713 GCP area overhead                                      | 8/ |

|     |     |       | 6.7.1.4 Minimize wasted energy                         | 84  |

|-----|-----|-------|--------------------------------------------------------|-----|

|     |     |       | 6.7.1.5 BIM overall effectiveness                      | 86  |

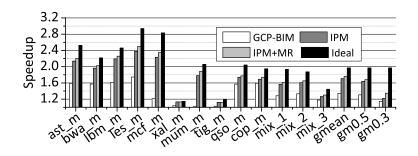

|     |     | 6.7.2 | Effectiveness of FPB-IPM                               | 86  |

|     |     |       | 6.7.2.1 Performance improvement                        | 86  |

|     |     |       | 6.7.2.2 Multi-RESET iteration count                    | 8   |

|     |     | 6.7.3 | Throughput improvement                                 | 88  |

|     |     | 6.7.4 | Design space exploration                               | 88  |

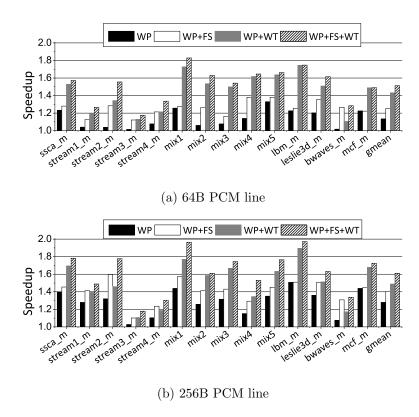

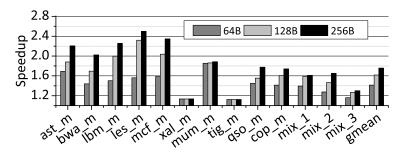

|     |     |       | 6.7.4.1 Cache/memory line size                         | 89  |

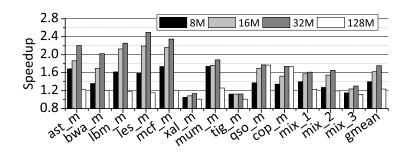

|     |     |       | 6.7.4.2 Last-level cache capacity                      | 89  |

|     |     |       | 6.7.4.3 Number of write queue entries                  | 90  |

|     |     |       | 6.7.4.4 Number of power tokens                         | 9   |

|     |     |       | 6.7.4.5 Integrating write pausing and write truncation | 9   |

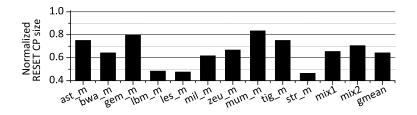

| 7.0 | PC  | M PE  | EAK POWER REDUCTION                                    | 93  |

|     | 7.1 | BACI  | KGROUND                                                | 9;  |

|     |     | 7.1.1 | High density PCM                                       | 93  |

|     |     | 7.1.2 | Multi-level cell (MLC) PCM                             | 94  |

|     |     | 7.1.3 | The baseline memory architecture                       | 96  |

|     | 7.2 | CHA   | RGE PUMP BASICS AND MODELING                           | 96  |

|     |     | 7.2.1 | CMOS-compatible on-chip charge pumps                   | 9   |

|     |     | 7.2.2 | Charge pump modeling                                   | 98  |

|     | 7.3 | PROI  | POSED DESIGNS                                          | 10  |

|     |     | 7.3.1 | Motivation                                             | 10  |

|     |     | 7.3.2 | Intra-write RESET Scheduling (Reset_Sch)               | 102 |

|     | 7.4 | PCM   | PEAK POWER REDUCTION EXPERIMENTAL METHODOLOGY          | 106 |

|     | 7.5 | RESU  | JLTS AND ANALYSIS                                      | 10' |

|     |     | 7.5.1 | Reset_Sch: Power Reduction and Performance             | 10' |

|     |     | 7.5.2 | Extending to other types of PCM                        | 11( |

| 8.0 | CO  | NCL   | USIONS                                                 | 11  |

|     | 8.1 | TECH  | HNIQUE CONCLUSIONS                                     | 11: |

|     | 8 2 | ARCI  | HITECTURE CONCLUSIONS                                  | 11' |

| 8.3    | IMPACTS . | <br> | <br> |  |  |  |  |  |  |  |  |  |  |  | 113 |

|--------|-----------|------|------|--|--|--|--|--|--|--|--|--|--|--|-----|

| BIBLIC | GRAPHY    | <br> | <br> |  |  |  |  |  |  |  |  |  |  |  | 115 |

## LIST OF TABLES

| 1  | Comparison of different memory technologies            | 3   |

|----|--------------------------------------------------------|-----|

| 2  | Proposed scheme summary                                | 9   |

| 3  | MLC PCM write latency reduction baseline configuration | 35  |

| 4  | MLC PCM write latency reduction simulated applications | 36  |

| 5  | The latency, energy and area overhead of WT and FS     | 38  |

| 6  | The comparison of different WT section sizes           | 43  |

| 7  | The resistance range of 2-bit MLC                      | 57  |

| 8  | MLC PCM endurance enhancement baseline configuration   | 59  |

| 9  | MLC PCM write power management baseline configuration  | 79  |

| 10 | MLC PCM write power management simulated applications  | 80  |

| 11 | Charge pump overhead as measured by power tokens       | 85  |

| 12 | Leakage power for all types of CPs                     | 101 |

| 13 | PCM peak power reduction baseline configuration        | 106 |

| 14 | 2-bit MLC PCM chip and main memory configuration       | 106 |

| 15 | Proposed technique application.                        | 114 |

## LIST OF FIGURES

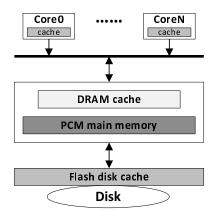

| 1  | System architecture with PCM main memory                         | 4  |

|----|------------------------------------------------------------------|----|

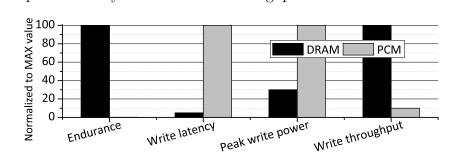

| 2  | Comparison between DRAM and PCM (not to scale)                   | 8  |

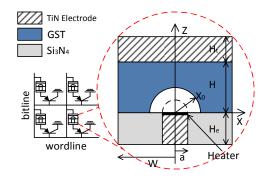

| 3  | PCM cell array.                                                  | 15 |

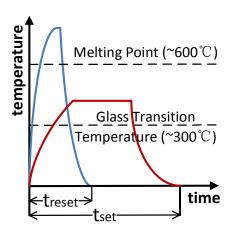

| 4  | PCM RESET and SET                                                | 15 |

| 5  | Non-deterministic PCM writes                                     | 17 |

| 6  | Single RESET multiple SETs staircase-up P&V scheme               | 18 |

| 7  | PCM read operation requires comparison to reference cells        | 19 |

| 8  | The distribution of the number of iterations.                    | 27 |

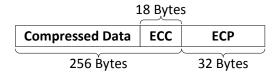

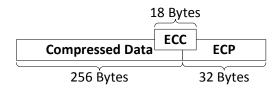

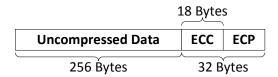

| 9  | Adding ECC to PCM lines for write truncation (WT)                | 29 |

| 10 | P&V programming with write truncation (WT)                       | 30 |

| 11 | Integrated form switch with write truncation                     | 32 |

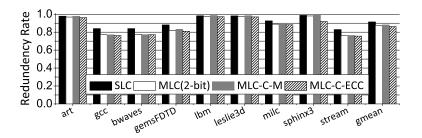

| 12 | Write redundancy comparison when storing data in different forms | 34 |

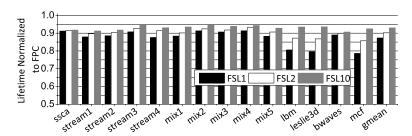

| 13 | Lifetime degradation due to storing extra ECC bits               | 34 |

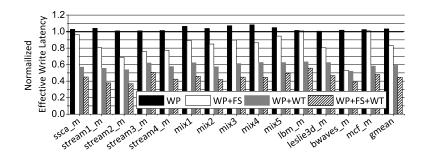

| 14 | Effective write latency (256B)                                   | 40 |

| 15 | Effective read latency (256B)                                    | 41 |

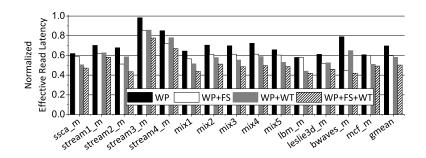

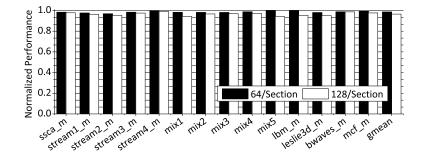

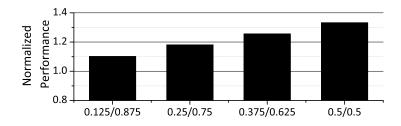

| 16 | The IPC comparison of different schemes                          | 42 |

| 17 | The comparison of IPC using different ECC codes                  | 43 |

| 18 | IPC comparison of WP+WT+FS with varying iteration latencies      | 44 |

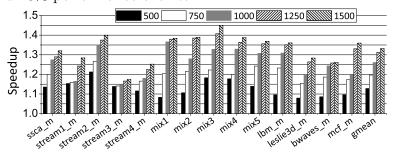

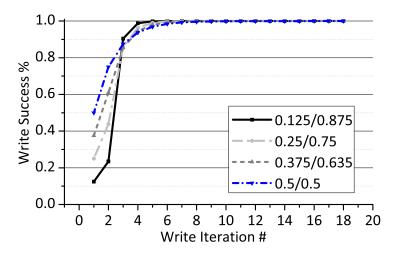

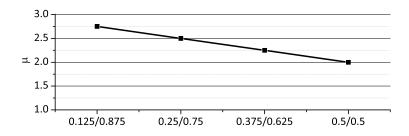

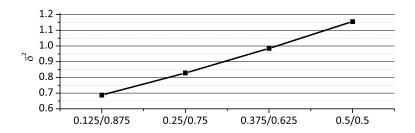

| 19 | Cell write iteration numbers with different $F_1/F_2$ s          | 45 |

| 20 | The average cell write iteration numbers per line write.         | 45 |

| 21 | The variance of cell write iteration numbers per line write      | 46 |

| 22 | IPC comparison with different $F_1/F_2$ s (normalized to WP)     | 46 |

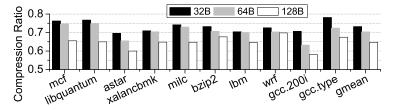

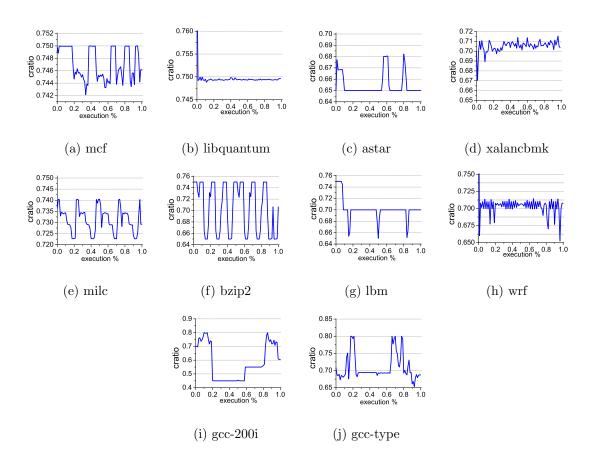

| 23 | Compression ratio of all line-level writes                 | 47 |

|----|------------------------------------------------------------|----|

| 24 | MLC has tighter resistance ranges                          | 47 |

| 25 | PCM cell, resistance, endurance models                     | 57 |

| 26 | 4/3 fraction encoding                                      | 58 |

| 27 | Flipping rate comparison among 3 bits                      | 58 |

| 28 | Optimized encoding for cell flipping (a) and energy (b)    | 58 |

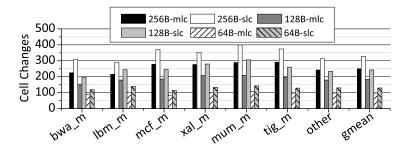

| 29 | Cell changes for different schemes with compression        | 59 |

| 30 | Dynamic sampling for ER.                                   | 59 |

| 31 | RESET power comparison (normalized to n-bit MLC/C)         | 60 |

| 32 | Lifetime improvement (normalized to n-bit MLC/C)           | 60 |

| 33 | Performance improvement under different power budgets      | 60 |

| 34 | Compression ratio of the whole execution                   | 61 |

| 35 | The performance under power restrictions for MLC PCM       | 62 |

| 36 | The baseline architecture (one DIMM)                       | 64 |

| 37 | The cell changes under different settings                  | 66 |

| 38 | Writes blocked by chip level power budget                  | 68 |

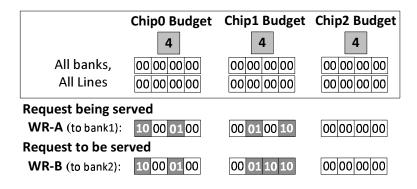

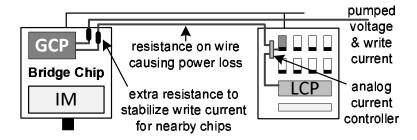

| 39 | FPB-IPM: iteration power management                        | 69 |

| 40 | Multi-RESET reduces maximum power demand                   | 72 |

| 41 | Integrating a global charge pump (GCP)                     | 73 |

| 42 | Schedule MLC PCM writes under FBP-GCP                      | 74 |

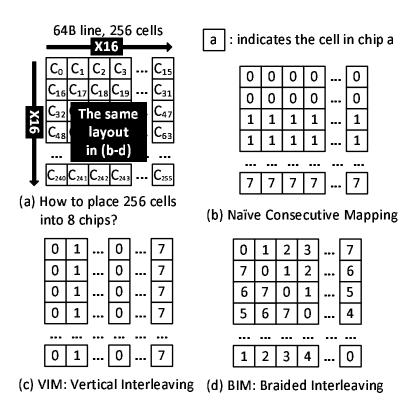

| 43 | Different cell mapping schemes                             | 77 |

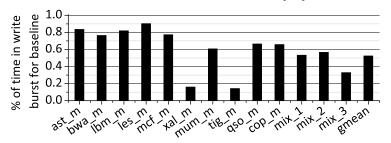

| 44 | Percentage of execution cycles in write burst for baseline | 81 |

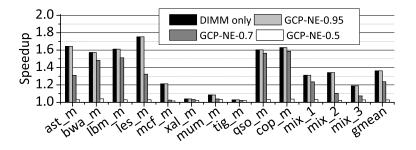

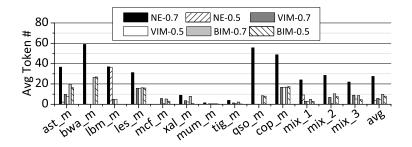

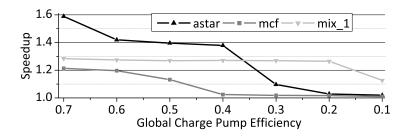

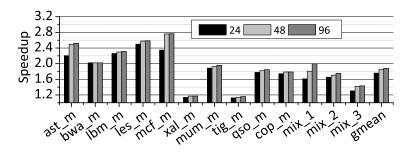

| 45 | Speedup with different GCP power efficiencies              | 82 |

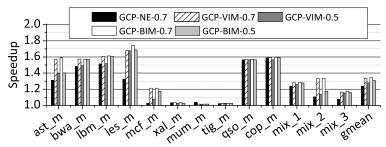

| 46 | Speedup of cell mapping optimizations                      | 83 |

| 47 | Maximum number of tokens requested by the GCP              | 84 |

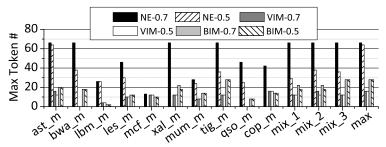

| 48 | Averge power tokens requested by NE, VIM and BIM           | 85 |

| 49 | Speedup with BIM as GCP efficiency is decreased            | 86 |

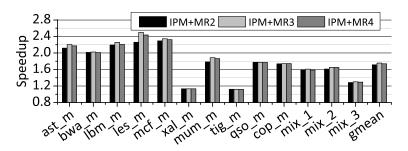

| 50 | Speedup achieved by IPM and Multi-RESET                    | 87 |

| 51 | Multi-RESET iteration split limit                          | 87 |

| 52 | Write throughput improvement.                              | 88 |

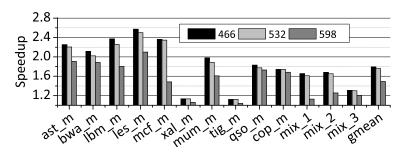

| 53 | Speedup of FPB for different line sizes                       | 86  |

|----|---------------------------------------------------------------|-----|

| 54 | Speedup of FPB for different LLC capacities                   | 90  |

| 55 | Speedup of FPB for different write queue sizes                | 90  |

| 56 | Speedup of FPM for different power token budgets              | 91  |

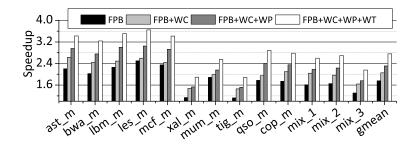

| 57 | FPB with WC, WP and WT.                                       | 92  |

| 58 | Trade-off between $V_{th}$ and chip density                   | 94  |

| 59 | PCM basics                                                    | 94  |

| 60 | Charge pump basics                                            | 98  |

| 61 | The RESET and READ CP modeling.                               | 101 |

| 62 | Power breakdown                                               | 101 |

| 63 | The power for writing a PCM line reaches its peak             | 103 |

| 64 | Scheduling RESETs without harming write latency.              | 104 |

| 65 | The potential of CP size reduction and wasted power reduction | 108 |

| 66 | Performance evaluation with reduced CP sizes                  | 109 |

| 67 | SLC RESET CP size reduction                                   | 109 |

| 68 | Future memory hierarchy.                                      | 112 |

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude to my advisor Prof. Jun Yang and my co-advisor Prof. Youtao Zhang for the continuous support of my Ph.D study and research. They taught me not only knowledge and skills to conduct research, but also the meaning of Ph.D. degree. I appreciate all their ideas, funding, patience, motivation, enthusiasm, and immense contributions to make my Ph.D. experience productive and stimulating. It has always been my honor and pleasure working with them. I would like to emphasize my special thanks to Prof. Zhang, who is an exceptionally versatile researcher, an unstoppable idea fountain and a great human being.

I also want to thank other members of my Ph.D. committee: Prof. Bruce R. Childers, Prof. Steven P. Levitan, and Prof. Konstantinos Pelechrinis, for their help on my research and my dissertation. They have provided me with discussions and comments on my thesis manuscript.

I owe a great debt of gratitude to my friends: Ping Zhou, Bo Zhao, Yu Du, Lin Li, Yi Xu, Wujie Wen and Mengjie Mao for helping me wholeheartedly on both my research and my life. I received lots of helps from them on setting up the experimental environment and discussing problems. Their help has been critical to my achievements. I am so grateful that I met Bo Zhao and his wife Di Wang. They always invited me for dinner to encourage me, when I was upset by my experimental results. I am particularly thankful to Prof. Li-tang Yan from Tsinghua University, who gave me a lot of help when I first came to USA.

I am deeply thankful to my father and my mother for their love and support. Without them, this thesis would never have been written. My hard-working parents have sacrificed their lives for myself and provided unconditional love and care. I know I always have my family to count on when times are rough.

#### 1.0 INTRODUCTION

Emerging big data [4] and cloud computing [32] benchmarks are designed for processing Yottabyte data imposing significant pressure on the traditional memory hierarchy. A single core processor executing these applications usually requires a large capacity memory hierarchy, including scalable caches and main memories, to contain their working sets. On the other hand, modern computing systems are increasingly built on chip-multiprocessors (CMPs). With the continuation of Moore's Law, the number of cores in a CMP is projected to increase from today's 4 to 10 cores to dozens, and perhaps even hundreds, of cores in the near future [11]. A large number of cores further enable more threads to run concurrently on one single chip. Therefore, to maintain scalable performance, the scale of memory will grow even larger, since the number of cores increases and applications become more data intensive. Unfortunately, this trend jeopardizes current DRAM main memory design. A large capacity DRAM faces power, leakage, and process variation problems at sub-micron scales. As an example, up to 40% of system power is consumed by main memory in a mid-range IBM eServer [63]. A more severe drawback for DRAM is its scalability. The recent ITRS report [45] indicates there is no path forward to scale DRAM below 22nm.

Therefore, device researchers have been studying new memory technologies that are more scalable than DRAM while still being competitive in terms of performance, cost and power. Many technologies that fulfill these criteria are NAND Flash [96], embedded DRAM (eDRAM) [99], Phase Change Memory [85] [116] [60], STT-MRAM [109] and Resistive RAM(RRAM) [102]. Table 1 compares different memory technologies, including emerging non-volatile memory technologies and traditional SRAM/DRAM/eDRAM.

In traditional memory hierarchy, SRAM serves as on-chip caches [26]; DRAM is deployed in main memory [41]; and NAND Flash is widely adopted in SSD disks [78]. SRAM has a

relatively standard cell size  $147F^2$  [26] over different process technology generations. The cell density of SRAM is low and the area overhead of SRAM is large, due to the large cell feature size. The leakage power of SRAM is huge, but the dynamic energy on SRAM is small [96]. SRAM also has reliability issues: for instance, it is vulnerable to NBTI [42], PBTI [7] and other physical problems [17]. The most effective solution to improve reliability on SRAM is to add more transistors into one single cell [7]. However, more transistors make SRAM cell size larger and SRAM leakage power more significant. DRAM is a high density random-access memory improving bandwidth by more advanced interfaces, like DDRx [62] and Buffer-on-Board [24]. The most common interface for DRAM is Double Data Rate (DDR) transferring data on both the rising and falling edges of the clock signal to lower the clock frequency and increase bandwidth. The most advanced DDR4 is able to supply 4266MT/s data transfer rate [41] in 2014. The advanced and fast DRAM interface is operated at a very high frequency, which makes the signal integrity worse. Delay Locked Loop (DLL) and on-die termination are added into DDR4 to ensure a good signal integrity [65]. However, power consumption also substantially increases with these complicated accessory circuitries. Furthermore, a single DRAM cell has to pay large power on refresh and face bad scalability problem beyond 22nm [45]. NAND Flash is a good solution to disk level storage because of its super high density [78]. In 2005, NAND Flash achieved 1GB chip size by multi-level cell [76]. By 3D stacking technique, vertical NAND Flash further enlarges the chip capacity to 16GB [78] in 2014. But the limited cell endurance, slow write operation and non-byte addressable access seriously impede the deployment of NAND Flash in main memory. A recent work [38] predicted that worse reliability and wore performance will happen on future NAND Flash system beyond 22nm. Despite these disadvantages, SRAM, DRAM and NAND Flash are basic components in traditional memory hierarchy.

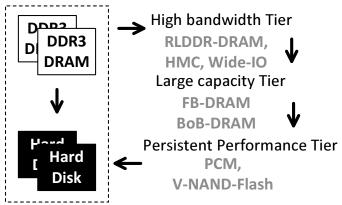

However, emerging applications [4, 32] and multi-core processors [11] mandate a large capacity main memory in Yottabyte scale, which is impossible to be implemented by traditional memory technologies. In order to build a large capacity memory hierarchy with low power consumption and low area overhead, recent works [96, 85, 109] started to investigate the possibility of fusing eDRAM, STT-MRAM, RRAM and PCM in Table 1 into the existing memory hierarchy.

Recently, eDRAM has been successfully integrated into the last level cache for IBM highend processors [108]. Compared to traditional SRAM, eDRAM reduces energy and leakage

power, but has a similar performance in last level caches [109, 19]. However, similar to

DRAM, eDRAM also faces poor scalability problem [77]: it is very challenging to fabricate

the capacitor of eDRAM beyond 32nm [100]. eDRAM wastes a lot of power to perform

refresh, whose frequency is much larger than traditional DRAM [105]. Therefore, eDRAM

is not an ideal candidate to implement future caches. On the contrary, STT-MRAM has

close read latency to SRAM, smaller cell size and leakage power than SRAM [109, 19, 96].

Perpendicular STT-MRAM even has a similar write latency to SRAM [35]. STT-MRAM

is also able to take advantage of multi-level cell to enlarge array density and reduce costper-bit [50]. Moreover, a recent work [59] shows STT-MRAM can be scaled well beyond

sub-20nm. Recent architectural works [109, 19, 96] believed STT-MRAM is one of the most

promising solutions to implement future on-chip caches.

Table 1: Comparison of different memory technologies.

| Metrics      | Flash <sup>a</sup> | SRAM           | eDRAM          | DRAM           | PCM          | $MRAM^{b}$     | RRAM           |

|--------------|--------------------|----------------|----------------|----------------|--------------|----------------|----------------|

| Read         | $\sim 25us$        | $\sim 2ns$     | $\sim 6ns$     | $\sim 20ns$    | $\sim 500ns$ | $\sim 2ns$     | $\sim 2ns$     |

| Write        | $\sim 2.5ms$       | $\sim 2ns$     | $\sim 6ns$     | $\sim 20ns$    | $\sim 1kns$  | $\sim 10ns$    | $\sim 7ns$     |

| Dyn. Power   | Large              | Tiny           | Small          | Small          | Medium       | Medium         | Medium         |

| Sta. Power   | Large              | Huge           | Large          | Large          | Small        | Small          | Small          |

| Cell Size    | $5F^2$             | $146F^{2}$     | $16F^{2}$      | $4F^2$         | $4F^2$       | $16F^{2}$      | $4F^2$         |

| Endurance    | $\sim 10^4$        | $\sim 10^{16}$ | $\sim 10^{15}$ | $\sim 10^{15}$ | $\sim 10^8$  | $\sim 10^{12}$ | $\sim 10^{11}$ |

| Volatility   | No                 | Yes            | Yes            | Yes            | No           | No             | No             |

| Byte-address | No                 | Yes            | Yes            | Yes            | Yes          | Yes            | Yes            |

<sup>&</sup>lt;sup>a</sup> NAND Flash is emphasized.

RRAM records data by changing the resistance across a dielectric solid-state material often referred to as a memristor [56]. The read latency of RRAM is close to STT-MRAM [109], while the write latency of RRAM can reach around 7ns in 2014 [18]. The cell size of RRAM can be minimized to  $4F^2$  [18]. The array of RRAM can be accessed by crossbar [56], so that the array size of RRAM can be also minimized, since there is no access transistor in each RRAM cell. RRAM also has a very good scalability, since a large capacity and a small cell size have been proved in 24nm node [64]. Similar to STT-MRAM, RRAM can also be

<sup>&</sup>lt;sup>b</sup> STT-MRAM is highlighted.

deployed in on-chip caches [103]. However, RRAM, as one type of memristor, presents very interesting characteristics in computing logics. For example, RRAM is natural predictor for branch prediction in modern CPUs [90]. The RRAM based branch predictor achieves high prediction accuracy with very low storage overhead. RRAM also can be used to implement synapses in a neuromorphic computing system [79]. Low power consumption makes RRAM appealing in neural network based computing system, since these computing platforms do not require high computing accuracy.

PCM utilizes phase change material, which is a chalcogenide alloy of multiple chemical elements, to record data. By the application of heat, PCM can switch the resistance states of phase change material. PCM has super high density and achieves  $4F^2$  cell size at 22nm [22]. Because of the non-volatility, PCM obtains zero cell leakage power. The read latency of PCM is comparable to traditional DRAM [85]. Recent computer architectural studies [85] [116] [60] have identified that PCM is one of the most promising memory technologies to substitute a portion of DRAM in main memory system. With emerging non-volatile memory technologies, like PCM, the traditional memory hierarchy should be revised. And the CMP system architecture with new memory hierarchy can be viewed as Figure 1.

Figure 1: System architecture with PCM main memory.

The largest advantage of PCM is the scalability. PCM has much better scalability [8] than DRAM: a PCM prototype with a feature size as small as 3nm has been fabricated [88].

By adjusting pulse height (i.e., voltage) and width (i.e., duration), it is possible to exploit partial crystallization states to record two or more bits of information in a single cell, which is called multi-level cell (MLC) PCM. MLC PCM further increases the capacity of main memory, while reduces the fabrication cost-per-bit [83].

#### 1.1 THE CHALLENGES IN MLC PCM DEPLOYMENT

#### 1.1.1 Long write latency

It is challenging to integrate MLC PCM in the memory hierarchy due to its longer access latencies than SLC PCM. Qureshi et al. modeled MLC PCM access, and proposed write cancellation (WC) [81] and write pausing (WP) [81] to let read operations preempt long latency write operations. These techniques reduce the effective read latency of MLC PCM. Qureshi et al. further proposed a morphable memory system [83] to improve the read latency of MLC PCM by converting one MLC PCM page into two SLC pages when there is sufficient memory. Sun et al. [97] proposed to compress data in MLCs for endurance and energy benefits.

MLC PCM usually adopts iterative program-and-verify (P&V) to achieve precise resistance control [83, 14]. However, most cells can be reliably written in a modest number of iterations, there are typically a small number of cells that require significantly more iterations. The cell that requires the largest number of iterations determines the completion time of one write operation.

Due to the non-deterministic material crystalline process, the same cell may require different number of iterations to complete from write to write. For example, given the same PCM line, the 1st cell may require the largest number of iterations in one write while the 3rd cell is the slowest in the next write. This non-determinism makes it impossible to adopt static designs such as finding and precluding these cells before the write operation.

#### 1.1.2 Short cell endurance

PCM is known for short endurance problem. A typical PCM SLC can be only reliably written for  $\sim \times 10^8$  times [84]. Recently, many architectural techniques have been proposed to attack this problem differential-write [116] extends PCM lifetime by removing redundant writes to cells. Wear leveling techniques [84] evenly distribute unbalanced write traffic among the entire chip. Salvaging schemes [91] were proposed to extend chip lifetime when non-negligible number of cells fail. Low power data encodings for MLC PCM were studied in [101]. By transforming MLC to SLC [83, 5], both a longer chip lifetime and a shorter read latency can be obtained on MLC PCM system.

#### 1.1.3 Limited write throughput

While past research has made significant strides, high PCM write power remains a major obstacle to improving throughput. For example, a recent study showed that the power provided by DDR3-1066×16 memory allows only 560 SLC PCM cells to be written in parallel [40], i.e., at most two 64B lines can be written simultaneously using Flip-n-Write [20]. Hay et al. proposed to track the available power budget and issue writes continuously as long as power demands can be satisfied [40]. This heuristic works well for SLC PCM.

Unfortunately, applying this heuristic to MLC PCM results in low write throughput and large performance degradation: On average, I observed a 51% performance degradation over an ideal baseline without a power limit. Through study of the PCM memory subsystem, I identify two major problems that limit throughput and performance.

The first problem is that allocating the same power budget for all iterations in a MLC line write is often too pessimistic. A MLC PCM write has one RESET pulse and a varying number of SET pulses. The RESET pulse is short and of large magnitude while the SET pulse is long and of low magnitude. In addition, when writing one PCM line, most cells in the line require only a small number of SET pulses [51]. Allocating power according to the RESET power request and for the duration of the longest cell write is power inefficient.

The second problem is that one heavily written (hot) PCM chip may block the memory subsystem even though most memory chips are idle. This phenomenon arises because the power that each chip can provide is restricted by the area of its charge pump. When multiple writes compete for a single chip, some writes have to wait to avoid exceeding the charge pump's capability. Otherwise, cell writes become unreliable.

#### 1.1.4 Large peak power

Comparing to SLC, MLC PCM suffers more severely from large RESET power and long read/write latency problems. In order to reliably represent the stored logic value, a PCM cell needs to have its resistance programmed within a tight resistance range. Since MLC has more resistance levels to represent, it often has tighter resistance range per level and/or higher maximum resistance. Given a PCM write circuit that has certain programming precision, MLC PCM requires a larger RESET current than SLC PCM to initialize its maximum resistance and contain more resistance levels. However, larger RESET energy significantly shortens cell endurance. As revealed by device studies [37, 58], 2× RESET energy results in  $100\times$  endurance degradation.

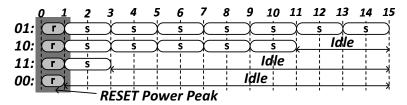

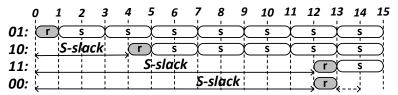

To control the cell resistance more precisely, MLC PCM usually adopts the P&V programming strategy to write an MLC PCM line starting with a RESET iteration followed by a non-deterministic number of SET iterations. In particular, the number of SET iterations is cell value dependent [51]. When writing a PCM line, all changed cells start with the high-power RESET, generating the largest power draw from the RESET charge pump. Hence, the power consumption reaches its peak in the first iteration and drops dramatically in the following iterations. Hence, it is crucial to reduce the peak power of a write.

#### 1.2 THESIS OVERVIEW

Figure 2 shows the comparison between DRAM and PCM. The endurance of DRAM is around  $\sim 10^{15}$  writes, while PCM only has  $\sim 10^8$  write cycling cell endurance. The significant cell endurance distinction exposes PCM vulnerable to intensive write application, especially malicious attacking program [94]. PCM also suffers from extremely long write latency.

Compared to DRAM, PCM has  $\times 20$  latency on write latency, but similar read latency [13, 106]. Such long write latency needs to be alleviated, even if PCM is in lower level memory hierarchy of DRAM. The RESET voltage of PCM is higher than Vdd. And the RESET current is larger than  $100\mu A$  [13]. Therefore, the write power of PCM is substantially higher than that of DRAM. Although previous work [116] adopted Differential Write to reduce the write activity on PCM. There are still a non-negligible number of cells which need to be written on PCM during the executions of typical benchmarks. Thus, the long write latency and high write power strictly limit the write throughput of PCM.

Figure 2: Comparison between DRAM and PCM (not to scale).

To fully integrate PCM into the entire memory hierarchy, I propose several architectural level techniques to address the weaknesses of PCM. A scheme summary can be viewed in Table 2. Write Truncation (WT) skips the redundant write iterations with the help of error correction code. Form Switching (FS) re-writes highly compressible memory line whose compressed size is less than 50% into SLC lines. Compared to MLC lines, SLC lines written by FS increase average MLC PCM chip lifetime and also enhance the read performance. Elastic RESET (ER) builds non-2<sup>n</sup>-state MLC PCM cell. Under the assistance of Fraction Encoding (FE), multiple non-2<sup>n</sup>-state cells can be re-organized to store multiple bits. By reducing the initial RESET energy, ER decreases write power and enlarges PCM chip lifetime. At last, I present fine-grained write power budgeting (FPB) including iteration based power management and global charge pump. FPB observes a global power budget and regulates power across write iterations according to the step-down power demand of each iteration. Global charge pump is used to balance the write power consumptions among different chips

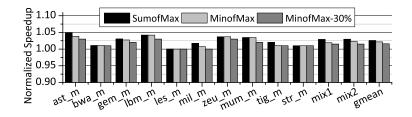

while staying within the global power budget. I also propose RESET scheduling, a scheme that significantly reduces the demand for large-sized RESET charge pumps. This is achieved through reducing the peak power in writing a memory line via scheduling the high-power RE-SET operations over the entire duration of the write, without prolonging the write latency. Such scheduling effectively diminishes the RESET charge pump area and wasted power by 70%.

Table 2: Proposed scheme summary.

| Proposed Scheme              | Problem and Challenges                   |  |  |  |  |  |

|------------------------------|------------------------------------------|--|--|--|--|--|

| Write Truncation             | Long Write Latency                       |  |  |  |  |  |

| Form Switching               | Long Read Latency, Short Cell Endurance  |  |  |  |  |  |

| Elastic RESET                | Large Write Power, Short Cell Endurance  |  |  |  |  |  |

| Fine-grained Power Budgeting | Large Write Power, Weak Power Management |  |  |  |  |  |

| Intra-write RESET Scheduling | Large Peak Power                         |  |  |  |  |  |

#### 1.3 CONTRIBUTIONS

#### 1.3.1 R/W latency shorten technique

First, due to cell process variation, composition fluctuation and the relatively small differences among resistance levels, MLC PCM typically employs an iterative write scheme to achieve precise control, which suffers from large write access latency. To address the MLC PCM write latency challenge, I make the following contributions:

- I propose Write Truncation (WT) to dynamically identify the cells that require more iterations to write, and truncate their last several iterations to finish a PCM write early. An extra error correction code (ECC) is introduced to cover the erroneous states of those cells. Through truncation, WT significantly reduces the number of iterations of a write operation.

- To mitigate the storage overhead of ECC, I propose Form Switch (FS) which uses frequent pattern compression [2] to compress a line to create storage space. If a PCM line can be

compressed to less than half of its size, it can be stored in SLC form rather than twobit MLC form. Since SLC PCM has shorter access latency and better write endurance than MLC PCM, accessing the line as SLC form accelerates performance critical read operations.

• I evaluate the designs in a hybrid DRAM-PCM main memory architecture, and compare them to state-of-the-art designs, such as write pausing [81] and MLC compression [97]. The results show that the designs reduce the effective write and read latencies by 57% and 28% respectively, and achieve 26% performance improvement over the state of the art.

#### 1.3.2 Cell endurance enhancement and write power reducing technique

Second, a larger PCM RESET energy significantly shortens cell endurance [37, 58]. To address this problem, I propose elastic RESET (ER) to construct non-2<sup>n</sup>-state MLC PCM. By reducing the RESET energy, RESET power is effectively reduced and PCM lifetime is prolonged. The existing work that is most close to my design is MLC-to-SLC transformation [5, 51] that compresses and stores highly compressible PCM lines in SLC format. MLC-to-SLC transformation is only applicable if a line is highly compressible, i.e., the compressed size is  $\leq$  half of the original size. Unfortunately, many applications have  $60\% \sim 75\%$  compression ratio and thus cannot benefit much from it. The contributions are summarized as follows.

- I propose *Elastic RESET* (ER) that reduces RESET current to construct non- $2^n$ -state MLC PCM. ER effectively reduces the RESET energy such that it can extend PCM endurance exponentially.

- I propose Fraction Encoding (FE) to store compressed data using non-2<sup>n</sup>-state MLC PCM cells. Instead of storing multiple bits in one cell, FE combines multiple cells to store multiple bits, e.g., 2 cells to store 3 bits, and thus can adaptively store compressed data with relaxed compression ratio.

• I evaluate my proposed designs and compare them to related works in the literature.

The experimental results show that ER improves PCM chip lifetime by ×32 and reduces

RESET power by 17% on average.

#### 1.3.3 Write throughput improvement technique

Previous power budget scheme [40] allocating the same power budget for all iterations in a MLC line write is often too pessimistic. A MLC PCM write has one RESET pulse and a varying number of SET pulses. The RESET pulse is short and of large magnitude while the SET pulse is long and of low magnitude. In addition, when writing one PCM line, most cells in the line require only a small number of SET pulses [51]. Allocating power according to the RESET power request and for the duration of the longest cell write is power inefficient.

Moreover, one heavily written (hot) PCM chip may block the memory subsystem even though most memory chips are idle. This phenomenon arises because the power that each chip can provide is restricted by the area of its charge pump. When multiple writes compete for a single chip, some writes have to wait to avoid exceeding the charge pump's capability. Otherwise, cell writes become unreliable. So, I propose two new fine-grained power budgeting (FPB) schemes to address these problems:

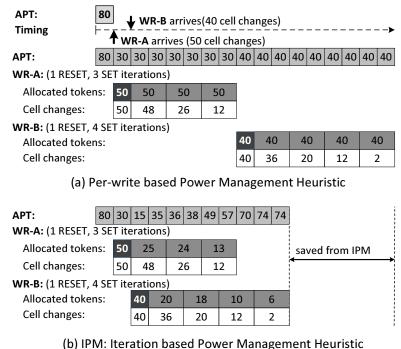

- FPB-IPM is a scheme that regulates write power on each write iteration in MLC PCM. Since writing one MLC line requires multiple iterations with step-down power requirements, FPB-IPM aims to (i) reclaim any unused write power after each iteration and (ii) reduce the maximum power requested in a write operation by splitting the first RESET iteration into several RESET iterations. By enabling more MLC line writes in parallel, FPB-IPM improves memory throughput.

- FPB-GCP is a scheme that mitigates power restrictions at the chip level. Instead of enlarging the charge pump in an individual PCM chip, FPB-GCP integrates a single global charge pump (GCP) on a DIMM. It dynamically pumps (boosts) extra power to hot chips in the DIMM. Since GCP has lower effective power efficiency (i.e., the percentage of power that can be utilized to write cells), I consider different cell layout optimizations to maximize throughput.

#### 1.3.4 Peak power reduction technique

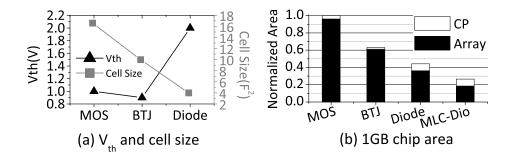

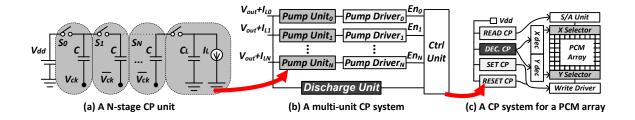

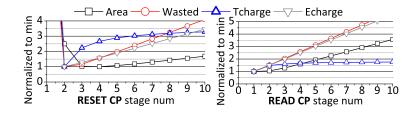

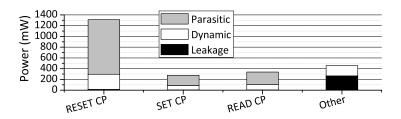

At last, high power consumption has become a major challenge in designing PCM based memory systems [40, 48]. The working voltage needs to be boosted from 1.8V  $(V_{dd})$  to 2.8V, 3.0V or even 5.0V for BJT, MOS- and diode-switched PCM respectively [8, 55, 61]. Those high voltages are provided by different types of CMOS-compatible on-chip charge pumps (CP) [73], which convert lower input voltage to higher output voltages. There are major limitations to CPs in PCM chips. First, a CP typically consists of cascaded stages of large capacitors and wide transistors, each stage elevating the voltage by a certain amount. Charging and discharging consume large parasitic power due to parasitic capacitance proportional to those large capacitors [73, 107]. In addition, the leakage power of CPs is usually quite large as a result of the wide, strong transistors and high voltages on internal nodes and the output [107]. Also, CPs dissipate significant power on its own peripheral circuits such as controls, drivers, clock generation and distribution. The parasitic, leakage and peripheral circuit power are significant sources of power loss of CP. They can be termed as wasted power in this work. This is also why the power conversion efficiency of CP, defined as the ratio between output and input power, is usually very low. As low as 20% of efficiency has been reported for a CP with current load in several PCM chips. To supply enough output current, either larger input current of a single CP is needed, or more CP units are necessary. As a result, CPs consume large chip area, e.g.  $\sim 20\%$  [61], as well. My evaluation shows that the total power dissipated by the CPs accounts for more than 81% of the total memory power. where 60\% is due to just the parasitic power. Hence, it becomes increasingly important to design effective schemes to reduce power loss of CPs. I propose one technique to tackle the aforementioned main limitations to PCM CPs. My contributions are as follows.

• I propose *RESET scheduling*, a scheme that significantly reduces the demand for large-sized RESET CPs. This is achieved through reducing the peak power in writing a memory line via scheduling the high-power RESET operations over the entire duration of the write, without prolonging the write latency. Such scheduling effectively diminishes the RESET CP area and wasted power by 70%.

• I provide detailed CP modeling, and simulated my proposed techniques on MOS-, BJT-, diode-switched PCMs. We also tested both SLC and MLC structures. The overall reduction in wasted power are observed to be between 37%~49% for different access devices or cell designs. These results prove that the proposed technique are effective and generally applicable to different PCM designs.

#### 1.4 THESIS ORGANIZATION

The rest of this thesis is organized as follows. Chapter 2 presents preliminary information of PCM. Chapter 3 discusses the related work. The MLC PCM latency reduction techniques are presented in Chapter 4. Chapter 5 illustrates the MLC PCM cell endurance enhancement schemes. The MLC PCM write power management techniques are summarized in Chapter 6. Chapter 7 elaborates the peak power reduction technique in PCM chips. Chapter 8 concludes the thesis.

#### 2.0 BASICS OF PHASE CHANGE MEMORY

#### 2.1 PCM FUNDAMENTALS

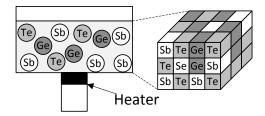

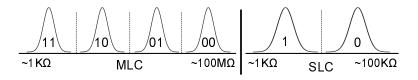

Phase change memory (PCM) is a type of non-volatile memory that stores information in a phase change material such as a chalcogenide alloy. Figure 3 shows one example of PCM array. A PCM cell usually consists of a thin layer of chalcogenide with two electrodes on each side. The chalcogenide, such as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST), has stable crystalline (logic "1") and amorphous states (logic "0"). Given the large resistance contrast between crystalline and amorphous states, it is possible to exploit partial crystallization states to store more than two bits per cell. This approach is referred to as multi-level cell (MLC) PCM. MLC PCM uses smaller resistance ranges to represent different digital levels, which demands more precise control to achieve reliable memory access.

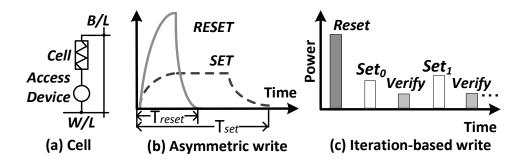

#### 2.2 PCM WRITE

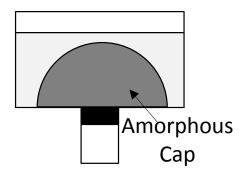

As shown in Figure 4, there are two kinds of PCM write (or programming) operations [46]. A SET operation heats the phase change material, GST, above the crystallization temperature (300 °C) but below the melting temperature (600 °C) using a long but small current. A SET operation writes the PCM cell into a logic '1' (crystalline state). In contrast, with a short and large current, the GST is melted and quenched quickly by a RESET operation, which writes the PCM cell into a logic '0' (amorphous state).

Writing MLC PCM cells exhibits significant non-determinism due to process variations and composition fluctuation in nano-scale devices. As shown in Figure 5(a), the composition

Figure 3: PCM cell array.

Figure 4: PCM RESET and SET.

of Ge, Sb, and Te in GST PCM has both inter- and intra- cell material fluctuations [10]. To change a cell's resistance level, a large RESET pulse is applied to form an amorphous cap in the GST. After this step, SET pulses are applied to build the crystalline filaments in the cap (Figure 5(b) and Figure 5(c)). The locations of filaments in GST are non-deterministic although the same amount of crystalline volume can be used to represent the same resistance levels. Studies have shown that the filament with slightly more Sb needs less crystallization time [10]. Therefore, given the same SET pulse, different PCM cells, or the same cell at different times, form different filaments in the cap. In addition, the heater size and peripheral circuits also introduce variations to a PCM write [112, 49]. Due to these reasons, it is very difficult for a single current pulse to precisely program a MLC to an intermediate state that has small resistance difference from neighboring states.

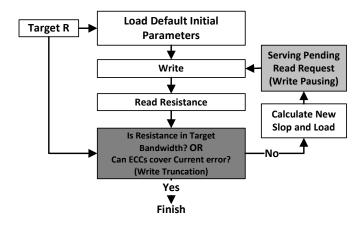

Because a single pulse is impractical, an iterative program-and-verify (P&V) strategy is widely adopted in both industrial prototypes [8, 69, 74] and academic research [14]. Given a target resistance range, the write circuit heuristically determines the initial current parameters to program the cell. After the programming pulse, the circuit reads the cell resistance and verifies whether the resistance falls in the target range. The write process completes when the target range is reached. Otherwise, the circuit re-calculates the write parameters and repeats the steps until the target range is reached or a predetermined maximum number of iterations has been attempted without success.

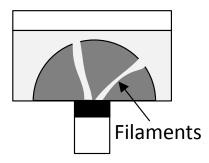

Figure 6 illustrates a staircase-up P&V MLC programming scheme. This design simplifies the hardware by using the same width for all current pulses, starting from an initial *RESET* pulse. An alternative programming scheme uses one SET pulse and multiple RESET pulses [52]. This scheme introduces reliability concerns, including resistance drift. It is also difficult to control the melting process. Therefore, industrial prototypes and most studies adopt the scheme in Figure 6. I also use the same mechanism, and assume that no write is performed if the value does not change, a.k.a., *Differential Write* [116].

The number of iterations required to complete a particular MLC PCM write depends on many factors, such as required programming precision, programming algorithm, and control circuit design. Qureshi *et al.* from IBM TJ Watson developed a two-phase model [82] to capture the P&V PCM programming strategy assuming the convergence probability of write

(a) Composition fluctuation.

(b) RESET pulse.

(c) SET pulse.

Figure 5: Non-deterministic PCM writes.

Figure 6: Single RESET multiple SETs staircase-up P&V scheme.

iterations follows the *Bernoulli distribution*. The model considers both the learning phase (the first several write iterations) and the practice phase, and computes the probability to finish a MLC PCM cell write at iteration k as

$$P(k) = \begin{cases} F_1 \cdot (1 - F_1)^{k-1} & \text{if } k \le i \\ F_2 \cdot (1 - F_2)^{k-i-1} (1 - F_1)^i & \text{if } k > i \end{cases}$$

(2.1)

where  $F_1$  and  $F_2$  indicate the expected probabilities of convergence at the k-th iteration during the learning phase and the practice phase, respectively; i is the number of iterations in the learning phase, and k is the count of write iterations. In the learning phase, the convergence probability is relatively small, which indicates more tries are necessary. After the learning phase, the write heuristic improves to have better convergence. This model was validated [82] and shown to match real-world experiments on write operations [69].

#### 2.3 PCM READ

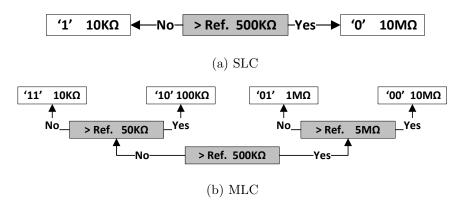

Reading a PCM cell involves sensing its resistance level and mapping the analog resistance to a corresponding digital value. For SLC PCM, this capability is achieved by comparing cell resistance to a reference cell. The reference cell's resistance is chosen as roughly the middle of the whole resistance range. In Figure 7(a), when compared with a  $500K\Omega$  reference cell, a larger resistance indicates the stored value is "0". Otherwise, the value is "1".

A read operation for a MLC commonly uses binary search. Figure 7(b) shows that, to read a 2-bit MLC, the circuit first compares the resistance to a reference cell at  $500K\Omega$ . Depending on the comparison outcome, the circuit next compares the resistance to  $50K\Omega$  or  $5M\Omega$ . It then determines the stored value. In general, a read operation for a n-bit MLC requires n iterations to complete.

Figure 7: PCM read operation requires comparison to reference cells.

Given that reads are on the critical path, an aggressive design could perform all comparisons in parallel and complete the read in one iteration. For n-bit MLC PCM, parallel sensing needs to duplicate the read circuit  $(2^n-1)$  times. This represents a trade-off between performance, increased sensing current and hardware overhead. As such, sequential sensing is widely adopted for MLC PCM read [83, 16].

#### 3.0 PRIOR ART

#### 3.1 ERROR CORRECTING AND SALVAGE

Resistance drift and cross-talk are neglected on traditional single level cell (SLC) PCM as described in [13]. For example, a SLC PCM cell, if it is written reliably, can retain data for more than 10 years at 85°C. As such, PCM failures considered in this paper can be immediately detected with read-after-write. Each line write is followed by a line read to confirm if the data was correctly written. Recent work [113] [6] noticed that resistance drifting may produce soft errors on multiple level cell (MLC) PCM. However, by applying anti-drifting encoding method and changing MLC pages to single level cell (SLC) pages, resistance drifting problem can be controlled in a trivial level [113].

Unlike traditional SRAM, PCM is resilient to radiation induced transient faults. However, because of the large area of periphery circuitry in a PCM chip, soft errors can still occur on the periphery, such as row buffers and interface logic. Free-P [111] deployed a 61-bit 6 bit-error correcting 7 bit-error detecting (6EC-7ED) BCH code for each 64-byte memory line to prevent potential soft errors. Device and circuit community have a more straightforward way to eliminate soft errors on periphery circuitry by ECC or parity before buffering the data, exchanging parity bits during bus transmissions [71] and reissuing requests in the case of a error. Therefore, no additional storage overhead within the PCM data array is required for protection against soft errors.

To change state, a bit cell is heated and cooled by applying different currents (RESET and SET current). Due to repeated heating, a PCM cell can be reliably written only a limited number of times, which is referred to as write endurance. While an individual PCM cell can handle  $10^{12}$  write cycles [58], experiments with PCM to arrays and chips have shown

much lower endurance in the range of  $10^7-10^9$  writes [13, 45]. Write endurance is significant obstacle that restricts PCM from serving as an immediate and widespread replacement for DRAM.

Wear-leveling aims to postpone the appearance of cell failures by spreading and balancing write operations [84, 93, 116, 34] among all usable cells/lines. Early table-driven wear-leveling techniques [116, 33] require OS management to periodically swap data stored in different regions based on write activity. To achieve better trade-offs, write frequencies are often recorded at a coarse-granularity in the table. Recently proposed wear-leveling techniques build a randomized mapping between physical address (PA) and PCM device address (DA) [84, 93]. In these designs, one PA may be mapped to different DAs at different times. The mapping is managed by simple hardware (including several registers and control circuit) and is hidden from the OS and user applications.

To accommodate relatively high cell failures, PCM devices include spare lines and use built-in hardware support to automatically remap failed lines to spares early in a chip's lifetime (i.e., with a small number of failures). Two types of hardware designs may be adopted. One design re-wires the address decoding logic (similar to a large capacity cache design [3]) and the other uses a small remapping table. Both designs incur large hardware overhead, and thus, can only support remapping a small number of failed lines. For example, Qureshi et al. [84] integrates a spare line buffer that can remap 5% of total lines. The benefits of built-in spare-line replacement are: it is transparent to upper level designs, user visible PCM space is contiguous, and access latency is little affected.

Salvaging techniques [91, 44, 94, 111] try to continue the duty cycle of PCM chips that have even a significant amount of failed cells, e.g., Ipek et al.[44] can tolerate up to one half of all pages failing. Salvaging techniques gracefully degrade in accordance with the number of failed cells, which is a significant difference to built-in spare line replacement that masks failures. To study the salvaging result in the later stage of lifetime of PCM chip, we adopt ECP [91] as our salvaging baseline. Given a 512-bit (64B) line, ECP saves six 9-bit pointers and corresponding 1-bit data in extra storage that was traditionally used to hold ECC information. Each pointer can fix any failed cell within a 64B line. ECP significantly improves PCM lifetime over ECC and other error correction techniques. SAFER [94] dynamically

divides broken bits into different groups within one 64-byte memory line. However, only 2% extra lifetime improvement over ECP was achieved by SAFER [94], therefore, we choose ECP as our baseline. We also compare LLS with FREE-p [111], which is memory line level remapping salvaging scheme.

#### 3.2 REDUCING EFFECTIVE READ LATENCY

There are different approaches to address the long latency write problem. By merging frequent writes within the DRAM cache, the number of writes issued to a PCM device can be greatly reduced [85]. Write pausing [82] allows performance critical read operations to preempt writes. Comparing to morphable memory system [83] that also converts MLC lines to SLC lines, FS is data-centric and transparent to higher system layers, including the operating system.

In a DRAM and PCM hybrid main memory system, cache replacement policy [114] and cache partition algorithm [115] are also proposed to move more write traffic to DRAM and read intensive lines to PCM. In this way, both short read latency and short write latency can be guaranteed.

#### 3.3 COMPRESSION ON PCM

Compression has been applied in PCM to reduce the total number of bits writing to the cells. Compressed data with a smaller size can be written into fewer PCM cells than original data. Comparing to compression-only designs [97, 112], FS stores highly compressible lines in SLC form using the same location such that it reduces the read accesses while [97] target at improving lifetime and energy only. Compression techniques [29] are also adopted to improve the small write bandwidth of PCM based or DRAM and PCM hybrid main memory system.

#### 3.4 PROCESS VARIATION AND OVER-RESET

For PCM chips with billions of cells, some cells tend to fail earlier than others. One variation source is the difficulty in controlling physical feature size in a nano-scale regime [112]. Due to these variations, different cells have different optimal RESET current values. A cell suffers from OVER-RESET if a current higher than its optimal value is used. An early report showed that every 10× increase in pulse energy results in 1000× lower endurance [58]. Recent measurements of failure rates on fabricated PCM chips showed similar results - 10× more failures were observed when a cell is 60% overheated [58]. While strong systematic process variations (PV) might be mitigated through circuit design, e.g., current provision [112, 49] or customized write circuit, there are still non-negligible variations at the chip level.

The impact of process variation on several parameters, such as gate length and Joule heater's radius, is analyzed in [112]. In [112], the distribution of *RESET* currents is generated by one dimensional heat model. This work selects the worst case in a 4MB block as the *RESET* current. Several other techniques, like Frequent Pattern Compression and page classification, are also adopted in [112] to increase PCM chip lifetime. However, too large systematic process variation is modeled in [112], while the latest works [44] [91] [94] observe no significant systematic process variation on PCM. Therefore, without the presence of large systematic process variation, employing the worst case *RESET* current in a 4MB size block may not be effective in increasing PCM lifetime.

#### 3.5 PCM WRITE POWER MANAGEMENT

High write power is known as a major disadvantage of PCM. Schemes have been proposed to change only the cells that need to be changed [116, 60]. Cho et al. proposed flip-n-write that can pack two line writes with the power budget of writing the number of one line cells [20]. It has limited benefit for MLC PCM due to the additional states used in MLC PCM. Hay et al. proposed to track/estimate bit changes in the last level cache and issue write operations as long as the DIMM level power budget can be satisfied [40]. Du et al. presented a novel

bit mapping scheme to distribute hot bits evenly into all PCM chips [30]. In this way, the chip level power constraint introduced by charge pump can be overcome, so that no hot chip will block the following writes [30]. These power management schemes focus mainly on SLC PCM. The FPB schemes proposed in this paper address MLC PCM write by exploiting its characteristics.

To address write power in MLC PCM, Joshi et al. proposed a novel programming method that decreases write energy and latency by switching between two write algorithms: single RESET multi-SET and single SET multi-RESET [52]. The latter is often less reliable. Wang et al. proposed to reduce write energy by adopting different mappings between data values and resistance levels [101].

#### 3.6 MLC PCM

MLC PCM can effectively reduce per bit fabrication cost. Schemes have been proposed to address its latency, write energy, and endurance issues [83, 81, 51]. MLC PCM differs from SLC PCM in that it has non-negligible resistance drift problem. Zhang *et al.* proposed different encoding schemes to mitigate drift [113]. Awasthi *et al.* proposed lightweight scrubbing operations to prevent soft errors [6].

#### 3.7 ASYMMETRIC WRITE

The RESET and SET operations have asymmetric characteristics in terms of latency and power [88]. Most previous work did a RESET followed by a sequence of SETs. Qureshi et al. proposed to perform SET operations before the memory line is evicted from last-level cache [80]. When a write operation comes, only the short-latency RESET needs to be performed. However, PRESET faces difficulty on MLC PCM as MLC uses more resistance levels, which prevents PRESET the line to one state.

# 3.8 PCM CHARGE PUMP DESIGN

Recent chip demonstration [22] proposed write charge pump *pre-emphasis* to accelerate the charging operation by providing a group of auxiliary RESET and SET CPs. In order to boost the write pumps faster, more area overhead and leakage for extra pumps have to be paid.

#### 4.0 MLC PCM WRITE LATENCY REDUCTION

#### 4.1 MOTIVATION ON MLC PCM LONG WRITE LATENCY

Observation: Uneven Distribution of MLC PCM Write Iterations: The staircase-up P&V MLC programming scheme uses multiple iterations to precisely program a PCM cell. Since each current pulse has the same width, the write latency is then determined by the number of iterations. When writing a PCM line, different cells require a different number of iterations. While the majority of cells likely finish in a modest number of iterations, some cells can take more iterations. Thus, the completion time of the whole line is determined by the cell that requires the largest number of iterations. In this section, I define the cells that require more iterations as a difficult-to-write cell set.

**Definition 4.1.1.** When writing a PCM line segment that has n cells, its **difficult-to-write** cell set is the subset of m cells that require the same or more iterations than the other cells. The cells in the difficult-to-write cell set require a certain number of iterations only for a particular write instance. Therefore, the difficult-to-write set membership may change from write to write.

**Definition 4.1.2.** When writing k PCM line segments (each has n cells), the difficult-to-write cell set is all m difficult-to-write cells in each segment, i.e., it consists of  $k \cdot m$  cells.

If n equals the number of cells in one PCM line, then the difficult-to-write cell set refers to the cells that globally require more iterations than other cells. If a PCM line is divided into k segments, then the difficult-to-write cell set refers to all m difficult-to-write cells in each segment. In this section, I choose n=64 and m=1; k varies depending on the size of the PCM line.

The completion time of the whole line is determined by the cell that requires the largest number of iterations. Moreover, the difficult-to-write cell set and the most difficult-to-write cell vary from one write to another due to non-determinism in changing device resistance, e.g., the growth of filaments, as explained in Section 2.2. Hence, such a set cannot be predicted and precluded before or during an early stage of the write. For example, for the same PCM line, its 1st and 2nd cells are difficult-to-write in one write, while its 3rd and 4th cells may become difficult-to-write in the next write. Similarly, the same MLC line may require only two iterations in one write instance, but then it requires eight iterations in another write instance.

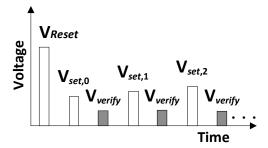

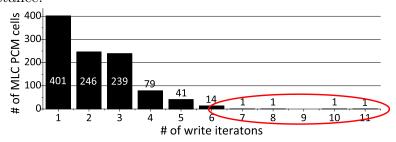

Figure 8: The distribution of the number of iterations.

Figure 8 plots the distribution of the number of iterations in writing a PCM line of 1024 2-bit MLCs, i.e., writing a 256-byte PCM line. This write finishes in 11 iterations. However, not all lines require this many iterations. Some may require fewer and others may require more. As discussed previously, a write to the same PCM line at different times may also require different number of iterations.

As Figure 8 shows, only one cell needs 11 iterations. The majority of cells finishes in less than 4 iterations. A few cells finish in 4-6 iterations. And only 4 cells require more than 6 iterations. When choosing (n=1024, m=4), these 4 cells form the difficult-to-write cell set for this write instance. If the excessive iterations can be avoided for the difficult-to-write cells, the line write latency can be reduced from 11 to 6 iterations, which is a 45% improvement for this line write instance<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>Choosing (n=1024, m=6) would include these 4 cells and 2 other cells that require 6 iterations. For this particular example, removing 6 difficult-to-write cells would have the same latency improvement as removing 4 cells.

It is challenging to integrate MLC PCM in the memory hierarchy due to its longer access latencies than SLC PCM. Qureshi et al. modeled MLC PCM access, and proposed write cancellation (WC) [82] and write pausing (WP) [82] to let read operations preempt long latency write operations. These techniques reduce the effective read latency of MLC PCM. Qureshi et al. further proposed a morphable memory system [83] to improve the read latency of MLC PCM by converting one MLC PCM page into two SLC pages when there is sufficient memory. Sun et al. [97] proposed to compress data in MLCs for endurance and energy benefits.

MLC PCM usually adopts iterative program-and-verify (P&V) to achieve precise resistance control [8, 83, 14]. However, I observed that most cells can be reliably written in a modest number of iterations, there are typically a small number of cells that require significantly more iterations. The cell that requires the largest number of iterations determines the completion time of one write operation.

#### 4.2 WRITE TRUNCATION

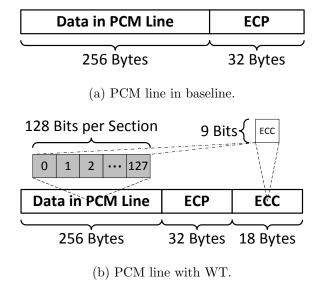

To prevent a few number of difficult-to-write cells from unnecessarily prolonging a write, I propose write truncation (WT) to truncate the trailing iterations of those cells. As a result, the difficult-to-write cells are temporarily failed since their writes did not finish. I apply single error correction, double error detection (SECDED) ECC to correct these soft errors. Note that the original line needs a mechanism to protect it from hard errors due to permanent cell damage. I assume error correction pointer (ECP) [91] is used, as illustrated in Figure 9(a). Hence, there are two sets of protection bits per PCM line: one for WT and the other for the baseline error protection.

Figure 9(b) illustrates a line in my WT design. I choose (n=64, m=1), i.e., the difficult-to-write cell set consists of the cell that requires the largest number of iterations in each 64 cell (128-bit) segment. For a 256B PCM line, there are 32B of ECP (64b per 512b block as in the original design [91]), and 18B of SECDED ECC (9b per 128b block). Hence, the extra space overhead of WT is 18B per 256B line.

Figure 9: Adding ECC to PCM lines for write truncation (WT).

The procedure of a write with WT is the following. When a line arrives, ECCs are computed, and written with the line using iterative P&V. At the end of each iteration, the write circuit checks in each 128-bit block (64 cells) how many cells are still being written. If there is only one cell left, the verification step tests if the current state is only one bit away from the target, such that ECC can cover this error. The write for this block is considered finished if the condition is true, and the full write can complete if all sub-writes are finished. Figure 10 summarizes my modifications to the existing P&V programming scheme. The SECDED ECC can rescue one bit per 128 bits (64 cells) and more write iterations are required if the condition is not satisfied. I adopt a gray code such that more write iterations bring the resistance closer to the target level without increasing the number of bit differences.

**Discussion**: One problem with WT is that if a hard fault occurred in a line, the faulty cell will become the dictating difficult-to-write cell since it can never be written no matter how many iterations are used. This will deplete the opportunity of WT. Typically, when a cell cannot be programmed to the target resistance range in a preset maximum number of iterations (MAX), then the cell is identified as a hard fault which is rescued by ECP. However, WT may terminate the write before MAX is reached, so that the hard fault is covered by

Figure 10: P&V programming with write truncation (WT).

ECC, rather than ECP. This problem can be solved through wear-leveling techniques such as start-gap [84]. Wear-leveling will guarantee that periodically, all lines are swapped within a region. WT can be disabled during wear-leveling to permit the writing of cells with hard faults to reach MAX. This process guarantees that cells with hard faults are discovered and marked by ECP bits. ECC will only cover non-faulty cells, continuing to provide short write latencies in the presence of hard faults.

Unlike ECC in DRAM, which corrects soft errors, ECC for WT is not intended to cover soft errors: PCM is naturally resilient to them. DRAM ECC is designed to achieve a certain reliability level. It may fail with a slim probability that there are more errors than it can handle, while my ECC guarantees to correct one "soft error" (from a difficult-to-write cell).

The advantage of using ECC over other error-correction mechanisms, such as ECP, is that ECC can be generated regardless of the positions of difficult-to-write cells. This property is desirable because ECC can be generated before a write operation starts, which enables writing the data and ECC simultaneously. As a comparison, ECP uses pointers to record the locations of the cells to rescue. Since these locations can only be known when a write operation almost completes, ECP can only be generated at that time. Using ECP would actually prolong the write operation. Therefore, ECC is adopted in my design.

Figure 10 also illustrates a recent write optimization for MLC PCM: write pausing [81]. This optimization allows reads to preempt long-latency write operations to avoid being blocked for a long time. WT is orthogonal to write pausing as the latter does not reduce the bank level service time for each write. WT allocates more service time for reads such that system performance is improved when memory accesses are intensive. With WT, MLC PCM write operations may have different programming iteration numbers and different write latencies. Without increasing the the complexity of memory controller, PCM chips can handle different write latencies with the new proposed framework and protocol in [31].

#### 4.3 FORM SWITCH

Although WT reduces the number of write iterations, it adds 9 bits per 128-bit PCM line segment, which corresponds to 7% storage overhead. In this section, I propose form switch (FS) to remove the storage overhead. FS compresses data to create space for storing ECC and transparently stores highly compressible lines in SLC form to reduce read latency.

FS employs frequent pattern compression [2] (FPC) to compress each MLC line. FPC examines every word and transforms frequently used patterns into fewer data bits and a prefix. A hardware compression unit is integrated in the memory controller to compress a line before it is stored in PCM. This compression unit also decompresses a line on a read. The experimental section shows that the compression unit's latency, area, and energy overhead are negligible.

I use the following configurations in FS with FPC. The baseline has 256 bytes of MLC, with 32 bytes of ECP and 18 bytes of ECC. When a line is compressed with FPC, the write circuit generates 9-bit ECC for every 128-bit block of a *compressed* line. For example, suppose a line is compressed to 64 bytes, only 36 bits  $(=(64\times8/128)\times9)$  of ECC are generated, instead of the full 18 bytes. This saves space. The ECP bits are not affected.

After compression, if the total number of bits of the compressed data, prefix tag, and ECC is 128 bytes or fewer, then FS treats MLC as SLC. That is, every cell stores only one bit of information. This form switch not only speeds up writes, but also improves reads as

(a) Data field with enough space

(b) Data field with not enough space

(c) Data field without any space

Figure 11: Integrated form switch with write truncation.

only one comparison round to the reference resistance is performed. In addition, FS also benefits endurance as SLC experiences much less stress during writes than MLC. I use 1 bit per line as a flag to indicate the line form. When the bit is set, the PCM line is used as an SLC line. Otherwise, it is an MLC line.