# REDUCED COMPLEXITY TURBO DECODERS

# CENTRE FOR NEWFOUNDLAND STUDIES

# TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

YASSIR NAWAZ

# **Reduced Complexity Turbo Decoders**

by

© Yassir Nawaz

A thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of Master of Engineering

Faculty of Engineering and Applied Science

Memorial University of Newfoundland

October, 2003

St John's

Newfoundland

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-99100-8 Our file Notre référence ISBN: 0-612-99100-8

## NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

## AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Canada

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant. To mama, abu, saman, and khala

## Abstract

Turbo codes are a class of forward error correction codes, which have outperformed all the previously known error coding schemes. The strength of this scheme lies in the parallel concatenation of component codes and their iterative decoding algorithm. Although turbo codes have found their way in a number of future wireless communications standards, their efficient implementation in hardware and software is still being actively researched. This study therefore focuses on the design of efficient turbo decoders. The dissertation begins with the description of encoding and decoding of turbo codes. Sliding window implementations of decoding algorithms, which are used to reduce the memory requirements in turbo decoders, are presented. The contribution of this work is the proposed modifications to the conventional sliding window implementations of SOVA, bi-directional SOVA and Max-Log-MAP based turbo decoders. The proposed modifications allow multiple bits to be released in a single decoding window thus reducing the computational complexity and increasing the decoding speed of turbo decoders. A performance and complexity comparison of these decoder implementations is also presented.

## Acknowledgements

I would like to acknowledge the excellent supervision of Dr. Ramachandran Venkatesan and Dr. Paul Gillard during this work. This thesis could not have been completed without Dr. Gillard's ideas and Dr. Venkatesan's advice. I would also like to thank the School of Graduate Studies at Memorial University for supporting me financially during my M.Eng. program.

Graduate study at the Faculty of Engineering has been a pleasant and valuable experience for me. I always found CERL (Computer Engineering Research Lab) to be a friendly and inviting place to work. I am especially thankful to my fellow students Atiq, Reza, Sainath and Li Cheng for the interesting academic discussions we had during the course of this work.

# **Table of Contents**

| List of Tabl             | esv                                                    | iii                        |

|--------------------------|--------------------------------------------------------|----------------------------|

| List of Figu             | res                                                    | ix                         |

| List of Abb              | reviations and Symbols                                 | xi                         |

| 1.1<br>1.2<br>1.3<br>1.4 | <ul> <li>1.1.1 Block Codes</li></ul>                   | 2<br>4<br>5<br>5<br>6<br>9 |

| 1.5<br>Chapter 2.4       | Organization of thesis1                                |                            |

| 2.1                      |                                                        |                            |

| 2.1                      |                                                        |                            |

| 2.2                      | 2.2.1 Encoding of Block Codes                          |                            |

|                          | -                                                      |                            |

| 0.0                      | 2.2.2 Cyclic Codes                                     |                            |

| 2.3                      | Convolutional Codes                                    |                            |

|                          | 2.3.1 Convolutional Encoder Structure                  |                            |

|                          | 2.3.2 Systematic Convolutional Encoder                 |                            |

|                          | 2.3.3 Recursive Systematic Convolutional (RSC) Encoder |                            |

|                          | 2.3.4 Convolutional Encoder Representations            |                            |

|                          | 2.3.4.1 Generator Representation                       |                            |

|                          | 2.3.4.2 State Diagram Representation                   |                            |

|                          | 2.3.4.3 Trellis Diagram Representation                 |                            |

| 2.4                      |                                                        |                            |

|                          | 2.4.1 Serial Concatenated Codes                        |                            |

|                          | 2.4.2 Parallel Concatenated Codes                      |                            |

| 2.5                      | Turbo Codes                                            |                            |

|                          | 2.5.1 A Turbo Encoder                                  |                            |

|                          | 2.5.2 Interleaving in Turbo Codes                      |                            |

|                          | 2.5.3 Trellis termination in Turbo Codes               |                            |

|                          | 2.5.4 Punctured turbo codes                            | 26                         |

| 2.6                      | Summary                                                | 27                         |

| Chanter 2 T              | terretive Deceding of Turks Codes                      | <b>7</b> 0                 |

|                          | terative Decoding of Turbo Codes                       |                            |

| 3.1                      | Introduction                                           | ۷ð                         |

| 3.2       | 2 System Model                                              | 29 |

|-----------|-------------------------------------------------------------|----|

|           | 3 Iterative Decoder Structure                               |    |

| 3.4       | 4 Component Decoders                                        |    |

|           | 3.4.1 The Maximum A Posteriori Algorithm (MAP)              | 33 |

|           | 3.4.1.1 Introduction and Mathematical Preliminaries         | 33 |

|           | 3.4.1.2 Forward Recursion and Calculation of $\alpha_k(s)$  | 35 |

|           | 3.4.1.3 Backward Recursion and Calculation of $\beta_k(s)$  | 38 |

|           | 3.4.1.4 Calculation of $\gamma_k(s, s)$                     | 38 |

|           | 3.4.1.5 Iterative Decoding Using MAP Algorithm              | 39 |

|           | 3.4.2 The Max-Log-MAP Algorithm                             | 42 |

|           | 3.4.3 The Log-MAP Algorithm                                 | 44 |

|           | 3.4.4 The Soft Output Viterbi Algorithm (SOVA)              | 45 |

|           | 3.4.4.1 Forward Recursion in SOVA                           |    |

|           | 3.4.4.2 SOVA Traceback                                      | 48 |

|           | 3.4.4.3 Iterative Decoding using SOVA Algorithm             | 51 |

|           | 3.4.5 Bi-directional SOVA                                   | 51 |

|           | 3.4.5.1 Rationale for Bi-directional SOVA                   | 52 |

|           | 3.4.5.2 Bi-directional SOVA Based Turbo Decoding            | 55 |

| 3.5       | 5 Summary                                                   | 56 |

|           |                                                             |    |

| Chapter 4 | Sliding Window Decoding of Turbo Codes                      | 58 |

| 4.1       | 1 Introduction                                              |    |

| 4.2       | 2 Sliding Window Component Decoders                         | 59 |

|           | 4.2.1 SOVA and Bi-directional SOVA                          |    |

|           | 4.2.2 MAP and Max-Log-MAP                                   | 61 |

|           | 4.2.3 Comparison of SOVA and MAP                            |    |

| 4.3       | 3 Multiple Bit Release Sliding Window Decoding              |    |

|           | 4.3.1 SOVA and Bi-directional SOVA                          | 63 |

|           | 4.3.2 The Effect of Modifications on Decoder Complexity and |    |

|           | Performance                                                 |    |

|           | 4.3.3 MAP and Max-Log-MAP                                   | 67 |

| 4.4       | 4 Summary                                                   | 68 |

|           |                                                             |    |

| Chapter 5 | Performance of Multiple Bit Release Turbo Decoders          |    |

| 5.1       | 1 Introduction                                              | 69 |

| 5.2       | F                                                           |    |

| 5.3       |                                                             |    |

| 5.4       | 1                                                           |    |

| 5.5       |                                                             |    |

| 5.6       | 6 Performance of Multiple Bit Release Bi-directional SOVA   | 77 |

| 5.7       | 7 Speedup from Multiple Bit Release Bi-directional SOVA     |    |

| 5.8       |                                                             |    |

| 5.9       |                                                             |    |

|           |                                                             |    |

| 5.10 Comparison of Bi-directional SOVA and Max-Log-MAP | 81 |

|--------------------------------------------------------|----|

| 5.11 Multiple Bit Release Punctured Turbo Codes        |    |

| 5.12 Turbo Codes with Higher State Encoders            |    |

| 5.13 Overall Speedup of the Turbo Decoder              |    |

| 5.13 Summary                                           | 89 |

| Chapter 6 Conclusions                                  | 91 |

| 6.1 Future Work                                        |    |

| References                                             | 94 |

# List of Tables

| Table 5.1 | Standard simulation parameters                                     | 71 |

|-----------|--------------------------------------------------------------------|----|

|           | Speedup from an 8 bit release implementation of SOVA               |    |

| Table 5.3 | Speedup from a 15 bit release implementation of bidirectional SOVA | 78 |

| Table 5.4 | Speedup from multiple bit release Max-Log-MAP                      | 81 |

# List of Figures

| Figure 2.1 | Cyclic encoder for $g(D) = 1 + D + D^2$                              | .14 |

|------------|----------------------------------------------------------------------|-----|

| Figure 2.2 | A (2, 1, 2) convolutional encoder                                    |     |

| Figure 2.3 | A (2, 1, 2) RSC convolutional encoder                                |     |

| Figure 2.4 | State diagram of a (2, 1, 2) RSC encoder                             |     |

| Figure 2.5 | Trellis diagram of a (2, 1, 2) RSC encoder                           |     |

| Figure 2.6 | Serial concatenated code                                             |     |

| Figure 2.7 | Parallel concatenated code                                           |     |

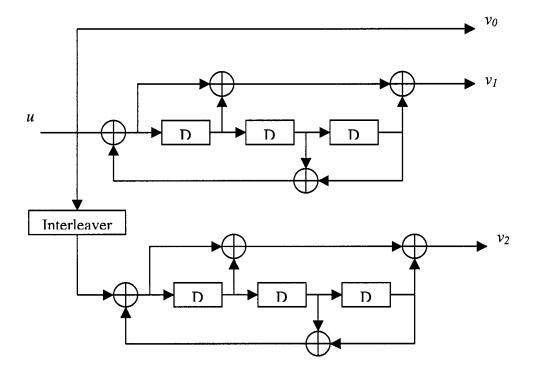

| Figure 2.8 | A rate 1/3 turbo encoder                                             |     |

| Figure 2.9 | Trellis termination strategies for RSC encoder                       |     |

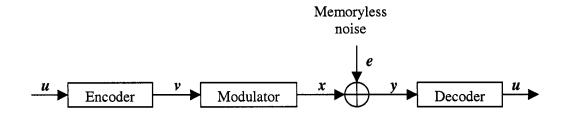

| Figure 3.1 | System model                                                         |     |

| Figure 3.2 | An iterative turbo decoder                                           | .32 |

| Figure 3.3 | MAP decoder trellis for a 4 state RSC code                           | .36 |

| Figure 3.4 | Recursive calculation of $\alpha_k(0)$ and $\beta_k(0)$              | 37  |

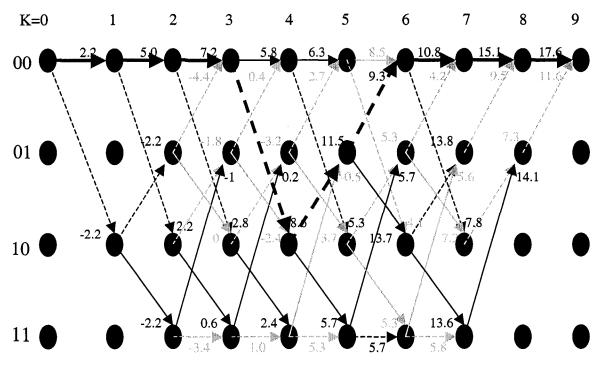

| Figure 3.5 | Forward recursion in SOVA decoding                                   |     |

| Figure 3.6 | Simplified trellis during SOVA traceback                             |     |

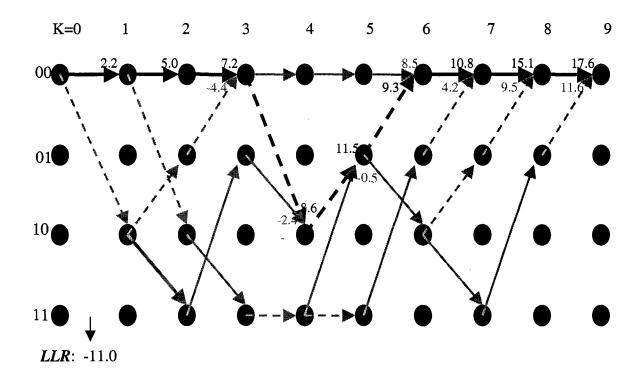

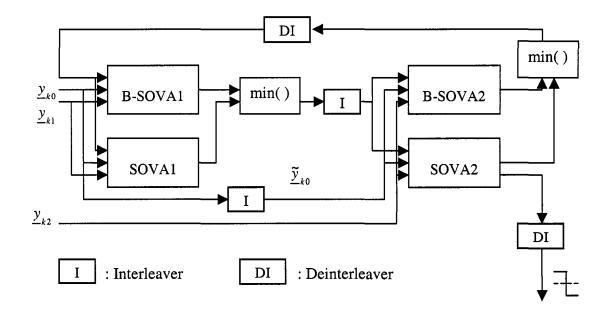

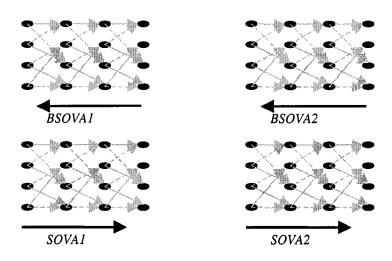

| Figure 3.7 | Bi-directional SOVA based turbo decoder                              |     |

| Figure 3.8 | Trellis formations in bi-directional SOVA                            | .53 |

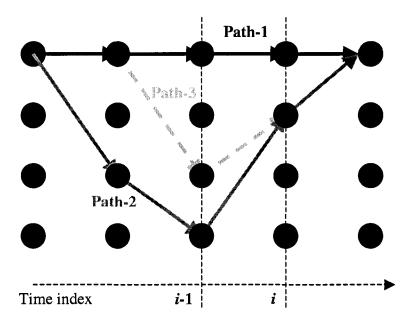

| Figure 3.9 | Path selections in SOVA decoding                                     |     |

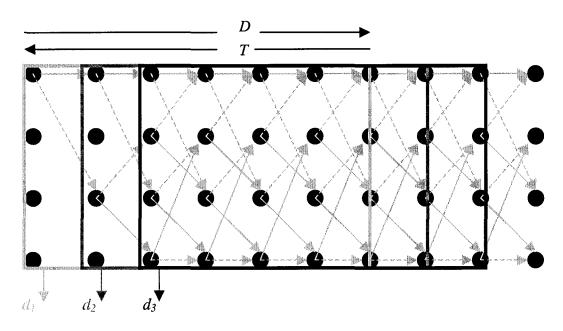

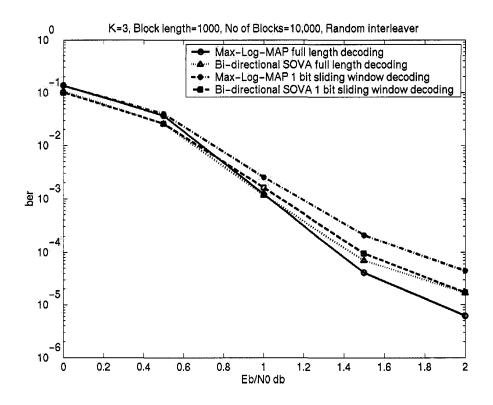

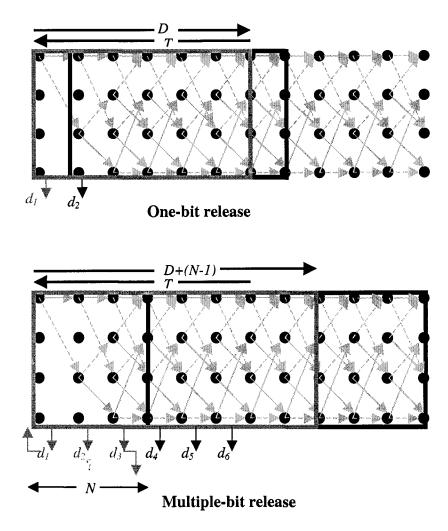

| Figure 4.1 | One bit release sliding window decoding                              | .60 |

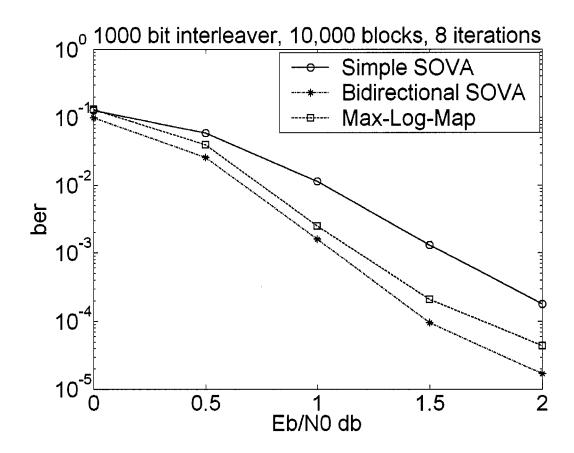

| Figure 4.2 | BER performance of one bit release sliding window decoding           |     |

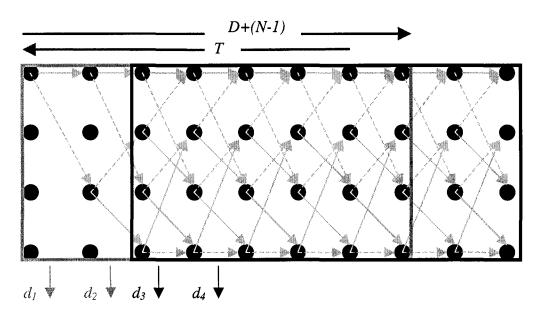

| Figure 4.3 | Multiple bit release sliding window decoding                         | 64  |

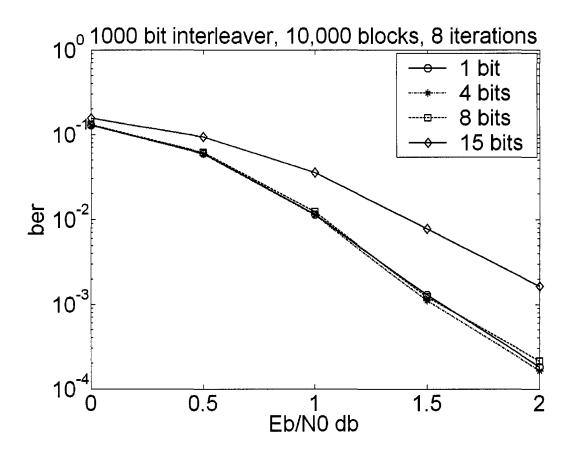

| Figure 4.4 | Performance analysis of multiple bit release sliding window decoding | 66  |

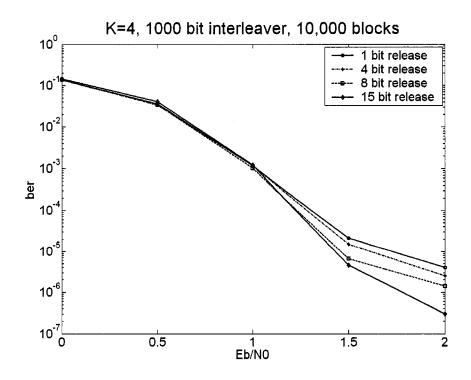

| Figure 5.1 | BER performance comparison of simple SOVA, bi-directional SOVA       |     |

|            | and Max-Log-MAP                                                      | 73  |

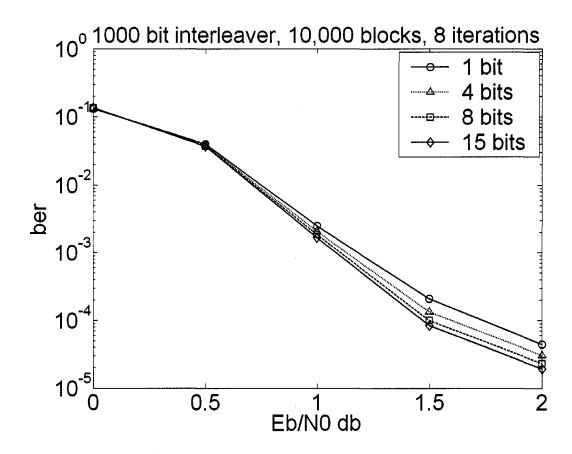

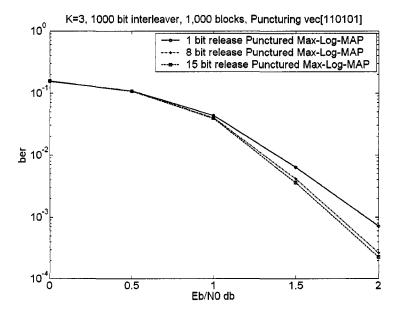

| Figure 5.2 | BER performance comparison of multiple bit release sliding window    |     |

|            | Simple SOVA                                                          | .74 |

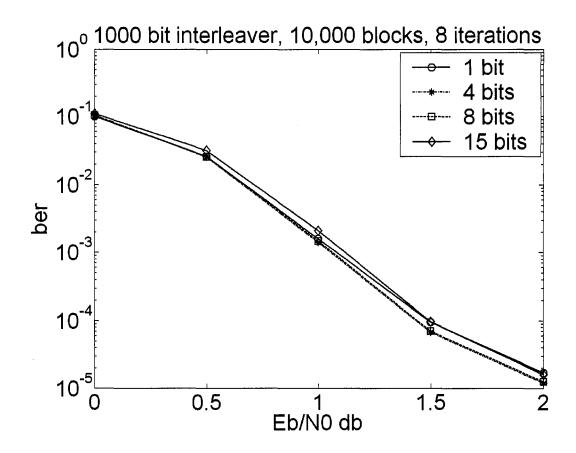

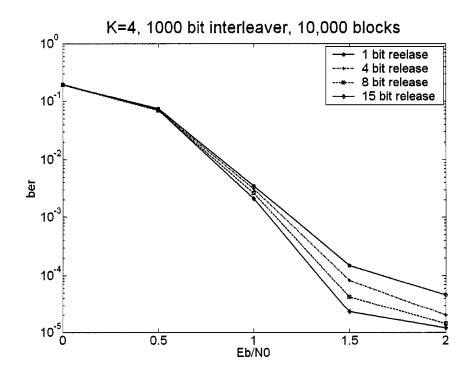

| Figure 5.3 | BER performance comparison of multiple bit release sliding window    |     |

|            | bi-directional SOVA                                                  | .77 |

| Figure 5.4 | BER performance comparison of multiple bit release sliding window    |     |

|            | Max-Log-MAP                                                          | 79  |

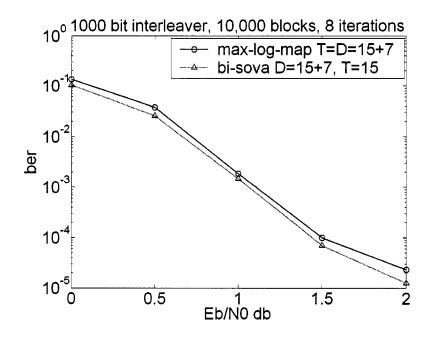

| Figure 5.5 | BER performance comparison of eight bit release sliding window bi-   |     |

|            | directional SOVA and Max-Log-MAP                                     | .82 |

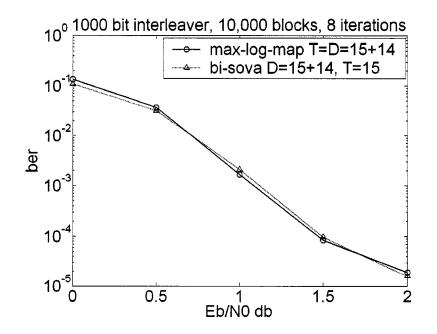

| Figure 5.6 | BER performance comparison of fifteen bit release sliding window bi- |     |

|            | directional SOVA and Max-Log-MAP                                     | .82 |

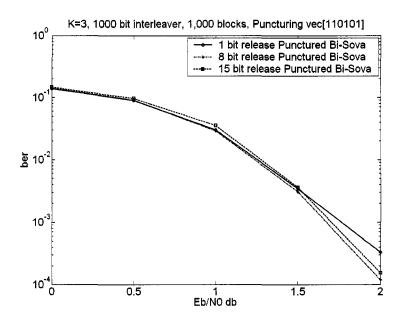

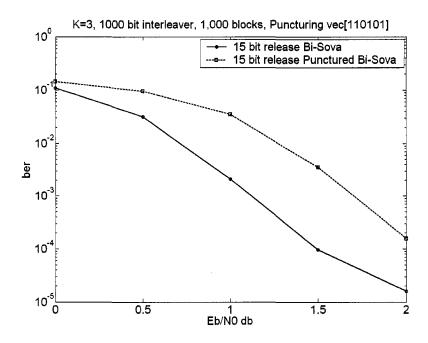

| Figure 5.7 | BER performance comparison of multiple bit release punctured bi-     | ~ ~ |

|            | directional SOVA                                                     | .85 |

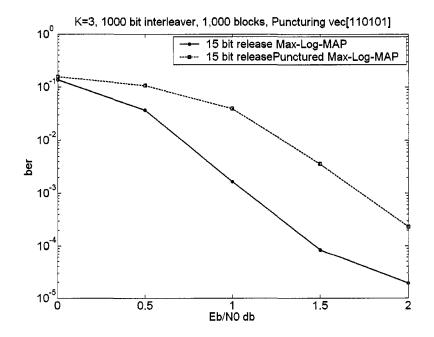

| Figure 5.8 | • • • •                                                              | 07  |

|            | Log-MAP.                                                             | .85 |

| Figure 5.9 | • • •                                                                | ~   |

|            | directional SOVA                                                     | 86  |

| Figure 5.10 | Performance degradation in multiple bit release punctured Max- |    |

|-------------|----------------------------------------------------------------|----|

| •           | Log-MAP                                                        | 86 |

| Figure 5.11 | 3G turbo encoder                                               | 87 |

| Figure 5.12 | BER performance comparison of 8-state bi-directional SOVA      | 88 |

| Figure 5.13 | BER performance comparison of 8-state Max-Log-MAP              | 88 |

# List of Abbreviations and Symbols

| 3G             | Third Generation                                                                                     |

|----------------|------------------------------------------------------------------------------------------------------|

| <b>3GPP</b>    | Third Generation Partnership Project                                                                 |

| ASIC           | Application Specific Integrated Circuit                                                              |

| AWGN           | Additive White Gaussian Noise                                                                        |

| BER            | Bit Error Rate                                                                                       |

| CCSDS          | Consultative Committee for Space Data Systems                                                        |

| CD             | Compact Disc                                                                                         |

| DVB            | Digital Video Broadcasting                                                                           |

| DVD            | Digital Versatile Disk                                                                               |

| ESA            | European Space Agency                                                                                |

| FPGA           | Field Programmable Gate Array                                                                        |

| IMT-2000       | International Mobile Telecommunications-2000                                                         |

| LLRs           | Log Likelihood Ratios                                                                                |

| MAP            | Maximum a Posteriori                                                                                 |

| ML             | Maximum Likelihood                                                                                   |

| NASA           | National Aeronautics and Space Agency                                                                |

| RSC            | Recursive Systematic Convolutional                                                                   |

| SOVA           | Soft Output Viterbi algorithm                                                                        |

| <b>Bi-SOVA</b> | Bidirectional Soft Output Viterbi algorithm                                                          |

| Α              | forward path metric for Max-Log-MAP                                                                  |

| В              | backward path metric for Max-Log-MAP                                                                 |

| $D_{MAP}$      | decision depth of trellis for MAP                                                                    |

| $D_{SOVA}$     | decision depth of trellis for SOVA                                                                   |

| $d_{min}$      | minimum code distance                                                                                |

| $E_b/N_0$      | energy per bit to noise density ratio                                                                |

| $E_{s}/N_{0}$  | energy per symbol to the noise density ratio                                                         |

| e              | memoryless noise                                                                                     |

| k              | number of inputs in a convolutional encoder                                                          |

| L(i)           | soft output expressed as log likelihood ratio                                                        |

| $L_c$          | channel reliability value                                                                            |

| $L_e$          | extrinsic value                                                                                      |

| M              | SOVA path metric                                                                                     |

| m<br>N         | number of memory elements in a convolutional encoder<br>number of bits released in a decoding window |

|                | number of outputs in a convolutional encoder                                                         |

| n<br>r         | code rate                                                                                            |

| $T_f$          | time to build one trellis stage in forward direction                                                 |

| $T_t$          | time to complete SOVA traceback                                                                      |

| $T_{MAP}$      | number of trellis stages in the backward recursion                                                   |

| $T_{SOVA}$     | traceback depth of trellis for SOVA                                                                  |

| u              | binary message sequence                                                                              |

| ν              | code sequence                                                                                        |

|                | -                                                                                                    |

- w weight of a codeword

- x modulated sequence

- y received sequence

- $\alpha$  forward path metric for MAP

- $\beta$  backward path metric for MAP

- $\gamma$  branch metric for MAP

- $\Gamma$  branch metric for Max-Log-MAP

- $\Delta$  metric difference

- $\sigma^2$  variance of zero-mean Gaussian noise

# **Chapter 1**

# Introduction

Turbo Codes introduced by Berrou and Glavix in 1993 have revolutionized the field of error correction coding [1]. This powerful error correction technique is ideal for communications systems where significant power saving is required or the operating signal to noise ratio is very low. Wireless communications, with its rapid growth and ever increasing demand for transmission bandwidth, is its foremost candidate. Turbo codes therefore have already been selected for a number of wireless communications standards.

This chapter begins by providing a brief history of the error correcting codes. Section 1.2 discusses the error correcting codes used in wireless communications. Section 1.3 focuses on the implementation of these codes. The remaining sections present the purpose and overview of this dissertation.

#### **1.1 A Brief History of Error Correcting Codes**

Information transmitted in a communications system is always liable to errors due to channel impairments. To preserve the accuracy of the information during transmission error correcting codes are used. These codes are also called channel codes. Error correcting codes add structural redundancy to the source information prior to its transmission. This redundancy is then exploited at the receiver to detect and correct transmission errors in the received information. All modern error correcting techniques can be traced back to the ground-breaking work of Shannon [2], Hamming [3] and Golay [4]. While Shannon's work laid the theoretical basis of coding, Hamming and Golay developed the first practical error control schemes.

Shannon, in his pioneering paper in 1948, [2] introduced the concept of source entropy and channel capacity. He mathematically defined source entropy as the average amount of information in a source message and channel capacity as the maximum rate at which the information can be transmitted over this channel. He then showed that it was possible to achieve reliable communications over a noisy channel if the source entropy is lower than that channel's capacity. This remarkable result proved that it is not the accuracy with which the information can be transmitted that is limited, but the rate at which it can be transmitted error free. While Shannon established the channel capacity as the upper limit on transmission rate, he never explicitly stated how it can be practically reached. His channel coding theorem only guaranteed the existence of codes which can be used to achieve transmissions at channel capacity. The history of error correcting codes since 1948 can therefore be characterized as the quest for this Holy Grail: The Shannon Limit. Hamming discovered the first error correcting code while he was working at the Bell Labs. His code called Hamming code was a great achievement; however it was inefficient and required three check bits to protect four data bits. The deficiencies in Hamming codes were addressed by Golay who discovered two more powerful and significant codes: Binary Golay codes and Tertiary Golay codes [5]. The work by Hamming and Golay laid the foundations of coding theory.

#### **1.1.1 Block Codes**

The codes discovered by both Hamming and Golay grouped information symbols into blocks of length k and then added n-k check symbols to each block to obtain n-symbol code words. These types of codes are referred to as block codes. Golay codes were soon replaced by more powerful Reed-Muller codes in 1954 [6]. While Hamming and Golay codes were specific in terms of n and k, Reed-Muller codes were a class of binary codes with flexible design parameters. National Aeronautics and Space Agency (NASA) extensively used Reed-Muller codes throughout 1960s and 1970s. Reed-Muller codes were followed by cyclic block codes that had the property that the cyclic shift of a codeword was also a code word [7]. The cyclic property of these codes enabled the design of encoders and decoders with reduced complexity. Bose Chaudhary and Hocquenghem discovered an important subclass of cyclic codes in 1960 [8]. These codes are known as BCH codes. BCH codes were binary codes; however, soon Reed and Solomon extended them to non binary codes [9]. Reed Solomon codes had superior burst error protection but the absence of an efficient decoder prevented their wide spread use in

practical applications. In 1967 Berlekamp introduced an efficient decoding algorithm for Reed Solomon codes [10]. Since then Reed Solomon codes have been extensively in a wide range of applications including Compact Disc (CD) and Digital Versatile Disk (DVD) players.

#### **1.1.2** Convolutional Codes

Block codes were successfully used for error correction however they suffered from certain drawbacks. Block codes required the entire code word to be received before the decoding process can be completed. This resulted in decoding delays. Another major drawback of block codes was their typical hard decision decoders. A hard decision decoder operates on binary channel output whereas a soft decision decoder operates on a continuous valued channel output. Soft decision decoding is more powerful than hard decision decoding because it does not suffer from the sub optimality that results from the quantization of the channel output. Therefore block codes with their hard decision decoders, although suitable for benign channels, were not ideal for noisy channels.

To address these drawbacks of block codes, Elias introduced a new coding approach called convolutional coding in 1955 [11]. Instead of segmenting the data in blocks and adding redundancy to each block, convolutional codes add redundancy to a continuous stream of data using linear shift registers. The data at the decoder can therefore be decoded continuously with low latency. Another advantage of convolutional codes is that they can be decoded using soft decision decoders. Convolutional codes were more powerful than block codes however it was only after the discovery of a practical and

optimal decoding algorithm by Viterbi in 1967 that they began to see extensive application in communications systems [12]. Convolutional codes were used by NASA in deep space probes such as Voyager and Pioneer [5]. They are also used in second generation digital cellular standards such as GSM and have also been incorporated in future standards such as Third Generation (3G) wireless systems [13].

#### **1.1.3 Concatenated Codes**

Concatenated codes are formed by the concatenation of two codes separated by an interleaver. The role of the interleaver is to rearrange the information to provide protection against burst errors. There are two types of concatenated codes: serial concatenated codes and parallel concatenated codes. In serial concatenated codes the output of one encoder is interleaved and then encoded by the second encoder. This technique allows the use of different codes that complement each other. For example Reed Solomon codes with good performance at low noise can be combined with convolutional codes, which have a better performance at high noise. This coding scheme was proposed by Forney in 1966 and is still used by NASA and European Space Agency (ESA) in deep space communications [14].

#### **1.1.4 Turbo Codes**

Parallel concatenation of two or more codes is called turbo coding. Berrou and Glavix introduced turbo codes in 1993. They decoded the code using an iterative decoding algorithm and achieved performance very close to the theoretical Shannon limit. Turbo

codes have outperformed all the previously known coding schemes and therefore are rapidly finding applications in future communications standards. Their superior performance actually comes from iterative decoding, in which component decoders share information to improve their individual decoded estimates. This sharing leads to an improvement in decoding performance with each decoding iteration. Although Berrou and Glavix used parallel concatenation of convolutional codes in their turbo coding scheme, it was soon realized that the iterative decoding technique can also be used to decode concatenated block codes. This led to the iterative soft decision decoding of concatenated block codes and several new decoding schemes based on this technique have been proposed recently [15]. Turbo codes, based on both block and convolutional codes, have finally provided us with the opportunity of designing practical communication systems that can operate very close to the channel capacity.

#### **1.2. Error Correcting Codes for Wireless Communications**

The choice of an error correcting scheme in a communications system is determined by the nature of the source information (i.e. type of application) and the type of communications channel. Sources of errors in wireless communications among others include low signal strength, shadowing and multipath fading. The problem of low signal strength is inherent to all the wireless channels. The strength of the received signal decreases as the distance between the receiver and transmitters increase. This is of significant importance in mobile wireless systems. The error correcting schemes for wireless communications must therefore, have good performance at low signal to noise

6

ratio. Convolutional codes generally outperform block codes at low signal to noise ratio and therefore were preferred for wireless communications. NASA's deep space probes, second generation cellular wireless standards and major commercial satellites used convolutional codes. Another source of errors in wireless communications is shadowing which results in the transmitted signal being completely blocked for a period of time. This causes burst errors in the transmitted information sequence. Convolutional codes, although efficient at low signal to noise ratio, are susceptible to burst errors. To address this problem concatenated codes were employed. NASA and ESA used them in Galileo and Giotto missions respectively. The Second generation GSM standard also uses concatenated codes.

Turbo codes formed by the parallel concatenation of convolutional codes also have the properties desirable in a wireless channel code. Moreover iterative decoding of these codes gives near Shannon limit performance at low signal to noise ratio. Therefore convolutional turbo codes are emerging as the foremost choice of future deep space communications, mobile satellite/cellular communications and microwave links. Some examples are

- Inmarsat's new multimedia service is based on turbo codes that allow the user to communicate with existing Inmarsat 3 spot-beam satellites from a notebook-sized terminal at 64 kbit/s.

- The Third Generation Partnership Project (3GPP) proposal for International Mobile Telecommunications-2000 (IMT-2000) includes turbo codes in the multiplexing and

channel coding specification. The IMT-2000 represents the third generation mobile radio systems worldwide standard. The 3GPP objective is to harmonize similar standards proposals from Europe, Japan, Korea and the United States.

- NASA's next-generation deep-space transponder will support turbo codes and implementation of turbo decoders in the Deep Space Network.

- The new standard of the Consultative Committee for Space Data Systems (CCSDS) is based on turbo codes. The new standard outperforms by 1.5 to 2.8 dB the old CCSDS standard based on concatenated convolutional code and Reed-Solomon code.

- The new European Digital Video Broadcasting (DVB) standard has also adopted turbo codes for the return channel over satellite applications.

#### **1.3.** Implementation of Error Correcting Codes

The real success of an error correction scheme depends not only on its power to correct errors but also on its ability of being incorporated into a practical communications system. For example scientists and engineers knew that they can achieve transmission rates close to channel capacity by increasing the length of the block codes, however due to the exponential increase in the decoder complexity it was not feasible to design a practical communications system with long block codes. Similarly several very powerful coding schemes did not find practical applications until decoding algorithms with reasonable complexity were found. Reed Solomon codes were proposed in 1960 but it was only after the discovery of Berlekamp decoder in 1967 that they were adopted in various communications and storage systems. Convolutional codes introduced in 1955 also had to wait for the arrival of Viterbi decoder in 1967 before they gained any practical significance.

The introduction of turbo codes in 1993 revolutionized error correction coding because it was the first scheme that performed close to Shannon limit and was also practical. The real breakthrough therefore was not the parallel concatenation of codes but the powerful iterative decoding technique that was also practical. The iterative decoding of turbo codes, although practical, is still considerably more complex than many decoding schemes used in existing error correction schemes. To decode a block, the turbo decoder must go through several decoding iterations (anywhere from two to fifteen). Therefore each component decoder operates on the block several times making the turbo decoder so much slower. Hence designing turbo decoders which are fast, have reduced complexity, and consume less power is crucial to the success of future wireless networks.

### **1.4.** Purpose of study

The purpose of this study is to investigate turbo coded systems for their implementation in wireless applications. The adoption of turbo codes as the standard channel codes for mobile satellite/cellular communications means their implementation in a range of wireless handheld devices. These devices must operate at fast link speeds, be small in size and weight, and consume little power. Since encoding in convolutional turbo codes is trivial, efficient implementations of turbo decoders are the key to the success of mobile networks. The nature of iterative decoding and the presence of interleavers prevent parallel computation by component decoders. Increasing the speed of the individual component decoders however, can increase the overall decoding speed of the turbo decoder. This study therefore focuses on increasing the speed of component decoders, and then analyzing its resulting effects on the performance of iterative decoding. The benefits of the techniques studied in this thesis are not limited to mobile systems. They can be used for the efficient implementation of any turbo-coded system.

### **1.5. Organization of thesis**

The rest of the thesis is organized as follows. Chapter 2 begins with an introduction to block codes followed by a detailed description of convolutional and turbo codes. Chapter 3 presents iterative decoding of turbo codes. This includes the description of component decoding algorithms and how they are used in an iterative decoding scheme. We restrict our discussion to convolutional turbo codes as they have better performance at low signal to noise ratio than block turbo codes. Chapter 4 introduces sliding window decoding of turbo codes. It is used to reduce the decoder memory requirements. In this chapter we also introduce multiple bit release sliding window implementations of various component decoders. The proposed multiple bit release implementations. Chapter 5 focuses on the performance and speed analysis of these implementations. Through extensive computer simulations we generate the performance curves and calculate the corresponding speed-ups for multiple bit release implementations of turbo codes. Chapter 6 provides conclusions and suggestions for the further extension of this work.

# Chapter 2

# **An Overview of Error Correcting Codes**

#### **2.1 Introduction**

In this chapter we provide a general overview of error correcting codes [16]. We shall divide these codes into three categories: block codes, convolutional codes and turbo codes. Block codes encode k bit information blocks into n bit coded blocks and are based rigorously on finite field arithmetic and abstract algebra. Some of the most commonly used block codes are Hamming codes, Golay codes, BCH codes and Reed Solomon codes. Convolutional codes, on the other hand, convert the entire data stream into a single codeword. The encoded bits depend not only on the current input bits but also on the previous input bits. They are widely used in real time communication. Finally we use the concepts and terminologies from the block and convolutional codes to explain turbo codes, which can be defined as a parallel concatenation of two component codes separated by a random interleaver.

#### **2.2 Block Codes**

A block code has *n* bit code words that contain *k* information bits and *r* parity bits, such that n = k + r. Such a code is referred to as an (n, k) block code where *n* and *k* are respectively the block length and information length of the code. The total number of code words in an (n, k) block code is  $2^k$  and the rate of the code is r = k/n.

#### **2.2.1 Encoding of Block Codes**

The encoding process consists of breaking up the data into message blocks m of length kand then performing a one to one mapping of each message  $m_i$  to a block of length ncalled a code word  $x_i$ . For linear codes this process can be described by a matrix multiplication

$$x = m G , (2.1)$$

where G has dimensions  $k \times n$  and is called the generator matrix. Linear codes have the property that sum of two code words is also a codeword and thus all linear code words must contain the all-zero codeword. Following are a few important definitions regarding block codes.

*Hamming distance:* The Hamming distance  $v(x_i, x_j)$  between the two code words  $x_i$  and  $x_j$  is the number of bit positions in which the two code words differ.

*Minimum distance:* The minimum distance  $d_{min}$  of a code is the minimum distance between any two code words.

$$d_{\min} = \min_{i \neq j} v(x_i, x_j).$$

(2.2)

A code with minimum distance  $d_{min}$  is capable of correcting all code words with t or less errors, where

$$t = \left\lfloor \frac{d_{\min} - 1}{2} \right\rfloor. \tag{2.3}$$

Hamming weight: Hamming weight w(x) of a code word x is the Hamming distance between itself and the all-zero codeword

$$w(x) = v(x,0),$$

(2.4)

where 0 or  $x_0$  represents the zero code word. The Hamming weight can be found by counting the number of ones in the codeword. For linear codes the minimum distance is the smallest Hamming weight of all code words except the all zero word.

$$d_{\min} = \min_{x \neq 0} w(x)$$

. (2.5)

## 2.2.2 Cyclic Codes

A code is cyclic if any cyclic shift of a code word produces another code word. A code *C* is cyclic if for every code word  $x = (x_0, x_1, \dots, x_{n-2}, x_{n-1}) \in C$  there is also a code word  $x' = (x_{n-1}, x_0, x_1, \dots, x_{n-2}) \in C$ . The generator matrix of a cyclic code can be expressed in the form

$$G = \begin{bmatrix} g_0 & g_1 & \dots & g_{n-k} & 0 & \dots & 0 \\ 0 & g_0 & g_1 & \dots & g_{n-k} & \dots & 0 \\ \vdots & & \dots & \ddots & \ddots & \ddots & \vdots \\ 0 & \dots & 0 & g_0 & g_1 & \dots & g_{n-k} \end{bmatrix}.$$

(2.6)

A cyclic code can also be represented by a generator polynomial

$$g(D) = g_0 + g_1 D + g_2 D^2 + \dots + g_{n-k} D^{n-k}.$$

(2.7)

Similarly the message *m* and the codeword *x* can also be represented by polynomials and the encoding process becomes the polynomial multiplication x(D) = m(D)g(D). The polynomial multiplication can be implemented by a linear shift register network and thus the encoders for cyclic codes are extremely simple. Figure 2.1 shows a cyclic encoder for generator polynomial  $g(D) = 1+D+D^2$ .

**Figure 2.1.** Cyclic encoder for  $g(D) = 1+D+D^2$

#### **2.3.** Convolutional Codes

Convolutional codes are one of the most widely used channel codes in practical communication systems such as satellite communications, cellular mobile, digital video broadcasting etc. A convolutional encoder operates on a source data stream using a sliding window and generates a continuous stream of encoded symbols. Unlike an (n, k) block code where the *n* bit output of an encoder depends solely on *k* input bits, the *n* bit output of a convolutional encoder is constructed from the *k* bit input as well as *m* previous inputs. A convolutional code that generates *n* outputs from *k* inputs and *m* previous inputs is referred to as an (n, k, m) convolutional code.

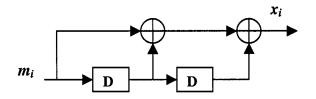

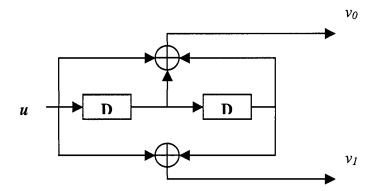

Figure 2.2. A (2, 1, 2) convolutional encoder

#### **2.3.1** Convolutional Encoder Structure

A convolutional code introduces redundant bits in the data stream through the use of linear shift registers. The encoder of an (n, k, m) convolutional code consists of a bank of k linear shift registers. Depending on the number of shift registers a convolutional code can become very complicated and therefore we shall restrict our discussion to convolutional encoders with only one shift register: binary convolutional codes. Figure 2.2 shows a (2, 1, 2) convolutional encoder.

The code rate r of a convolutional code is defined as

$$r = \frac{k}{n},\tag{2.8}$$

where k is the number of parallel input information bits and n is the number of parallel output encoded bits at any time interval. The constraint length K of a convolutional encoder is defined as

$$K = m + 1, \tag{2.9}$$

where m is the maximum number of stages in a shift register. The shift register stores the state of the convolutional encoder. The term constraint length refers to the number of previous bits on which the current output depends. The encoder shown in Figure 2.2 has a code rate of 1/2 and a constraint length of 3.

#### **2.3.2 Systematic Convolutional Encoder**

Systematic convolutional encoders encode in such a way that the unmodified input information stream is contained in the encoded output data sequence. This provides the systematic encoders with a significant advantage over nonsystematic encoders: the message is displayed in the encoded sequence and can be read directly from the received sequence thus eliminating the need for an inverter which is required if a nonsystematic encoder is used. Furthermore, the inverter for a nonsystematic code may not exist in which case a finite number of channel errors may cause an infinite number of decoding errors. Such codes are referred to as catastrophic codes. Systematic codes on the other hand do not require inverters and can never be catastrophic.

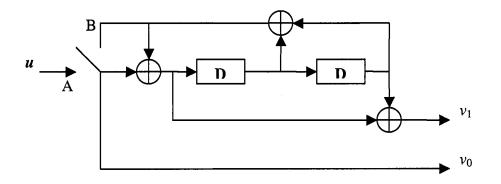

#### 2.3.3 Recursive Systematic Convolutional (RSC) Encoder

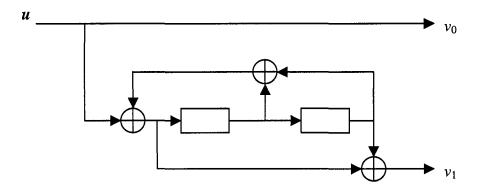

A recursive systematic convolutional encoder can be obtained from a nonrecursive nonsystematic encoder by feeding back one of its encoded outputs to its input. The RSC encoder shown in Figure 2.3 is obtained from the nonrecursive nonsystematic encoder of Figure 2.2 by feeding back one of its outputs.

Figure 2.3. A (2, 1, 2) RSC convolutional encoder

A recursive convolutional encoder tends to produce codewords with increased weight relative to a nonrecursive encoder. This results in fewer codewords with lower weights which leads to better error performance. For example consider an input sequence u=(...,0,1,0,0,0,0,0,0,0,0,...) containing a single 1 to a nonrecursive convolutional encoder. The encoder will emerge and then go back to an all-zero state within a finite number of transitions. The encoder output will contain finite number of 1s corresponding to the minimum distance of the code. However this input when given to a recursive encoder will result in a 1 eternally cycling through the encoder shift register. This will repeatedly produce 1s in the encoder output stream resulting in a codeword of increased weight. The recursive and systematic nature of RSC encoders thus provide significant advantages which justify use of RSC encoders in many communication systems.

### **2.3.4 Convolutional Encoder Representations**

A convolutional encoder can be represented in several different but equivalent ways:

- 1. Generator representation

- 2. State diagram representation

- 3. Trellis diagram representation.

#### **2.3.4.1 Generator Representation**

A Generator representation shows the hardware connection of the shift register taps to the modulo-2 adders. For an RSC encoder a feed-forward as well as a feedback polynomial is specified for each output. For example the RSC encoder of Figure 2.3 can be represented in generator form as

$$G(D) = \left[1, \frac{1+D^2}{1+D+D^2}\right],$$

(2.10)

where 1 corresponds to the systematic output  $v_0$  and  $1+D^2/1+D+D^2$  corresponds to the output  $v_1$  with  $1+D^2$  being its feed-forward and  $1+D+D^2$  the feedback polynomial.

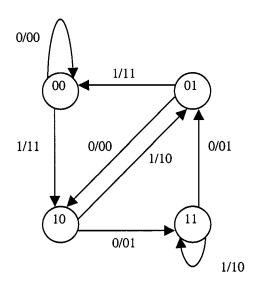

#### **2.3.4.2 State Diagram Representation**

The state diagram of a convolutional encoder is a graph that consists of nodes representing the encoder states, and directed lines representing the state transitions. Figure 2.4 shows the state diagram of the RSC encoder of Figure 2.3. The state of the encoder is defined as the contents of its shift register, and this is also referred to as encoder's memory contents. If m denotes the memory of the encoder then there are  $2^m$  possible states. Each directed line is labeled with an input/output pair. Given the current state of the encoder the information sequence at the input determines the path

Figure 2.4. State diagram of a (2, 1, 2) RSC encoder

through the state diagram and the output sequence. It is customary to begin the convolutional encoding from the all-zero state.

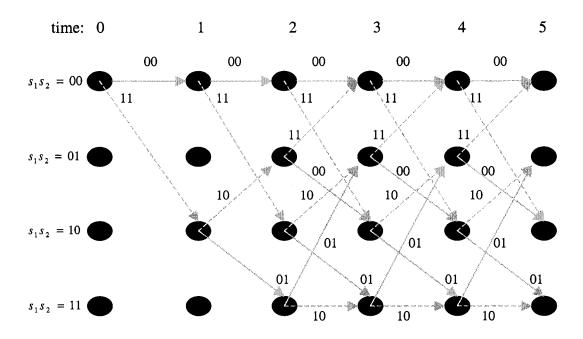

#### **2.3.4.3 Trellis Diagram Representation**

A trellis diagram is derived from a state diagram by tracing all the possible input/output sequences and state transitions. The Trellis diagram of the RSC convolutional encoder of Figure 2.3 is shown in Figure 2.5. The black circles at each stage of the trellis represent the four possible states of the encoder and the directed lines represent the transition from one state to the next. The solid lines represent the transition caused by the input symbol 0 and dotted lines represent the transition caused by input symbol 1. We shall assume that the encoder will start from all-zero state and therefore some states in the first two stages

Figure 2.5. Trellis diagram of a (2, 1, 2) RSC encoder

of the trellis are inaccessible. That is why certain transitions in the initial stages of the trellis are omitted in the trellis diagram. The output of the encoder at each transition is also labeled in the diagram.

# **2.4 Concatenated Codes**

A concatenated code is composed of two separate codes that are combined together to form a larger code. The primary reason for using a concatenated code is to achieve a low error rate with an overall decoder complexity which is less than that required for a single code of corresponding performance. There are two types of concatenated codes: serial concatenated codes and parallel concatenated codes.

Figure 2.6. Serial concatenated code

# 2.4.1 Serial Concatenated Codes

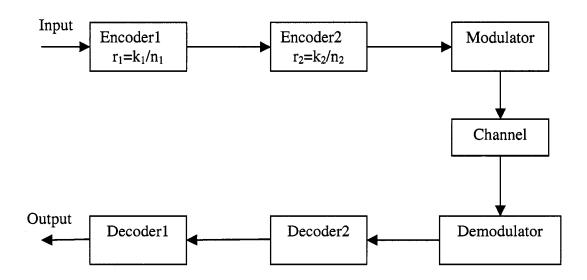

The transmission scheme for serially concatenated codes is shown in Figure 2.6. The total code rate for this serial concatenation is

$$r_{tot} = \frac{k_1 k_2}{n_1 n_2}.$$

(2.11)

Serial concatenated codes have been used in space communication, with convolutional codes as the inner code and low redundancy Reed Solomon codes as the outer code. Another application of concatenation codes is the concatenation of two convolutional codes where the inner decoder uses a soft-input/soft-output decoding algorithm to produce soft decisions for the outer decoder.

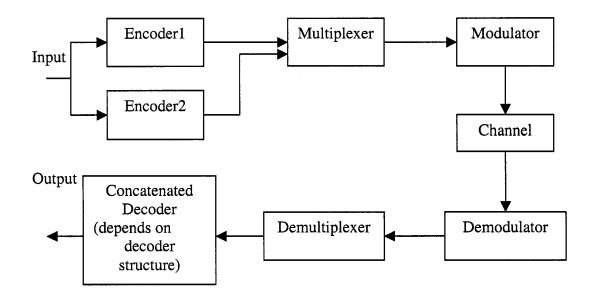

Figure 2.7. Parallel concatenated code

# **2.4.2 Parallel Concatenated Codes**

The transmission scheme for parallel concatenated codes is shown in Figure 2.7. The total code rate for this parallel concatenation is

$$r_{tot} = \frac{k}{n_1 n_2}$$

(2.12)

In both serial and parallel concatenation schemes an interleaver is incorporated between the two codes to decorrelate the received symbols thus increasing the burst error correction capability of the code.

## 2.5 Turbo Codes

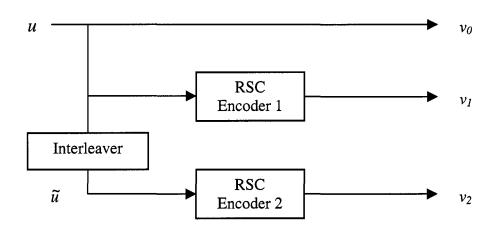

Turbo codes are formed by connecting two identical systematic codes in parallel. These component codes may either be block or convolutional codes and the turbo code formed by their concatenation is referred to as block or convolutional turbo code accordingly. The original turbo codes, presented by Berrou and Glavieux in 1993, used recursive systematic convolutional (RSC) encoders as component encoders and it is customary to refer to these convolutional turbo codes as simply turbo codes. From here onwards we shall also use the term turbo codes to refer to convolutional turbo codes.

## 2.5.1 A Turbo Encoder

A turbo encoder is formed by the parallel concatenation of two RSC encoders separated by an interleaver. Figure 2.8 shows the diagram of a rate 1/3 turbo encoder obtained through the parallel concatenation of two identical rate 1/2 RSC encoders. The first encoder (RSC Encoder 1) operates on the input sequence u directly. The output of this encoder consists of two sequences  $v_0$  and  $v_1$ . The sequence  $v_0$  is identical to the input usince the encoder is systematic. The second sequence  $v_1$  is the parity check sequence calculated by this encoder. The second encoder (RSC Encoder 2) receives an interleaved information sequence denoted by  $\tilde{u}$ . Only the parity check sequence from the second encoder, denoted by  $v_2$ , is transmitted. The information sequence  $v_0$  and the parity check sequences  $v_1$  and  $v_2$  are multiplexed to generate the output of the turbo encoder. This results in an overall code rate of 1/3.

Figure 2.8. A rate 1/3 turbo encoder

# 2.5.2 Interleaving in Turbo Codes

The interleaver used in turbo codes is a permuter or a scrambler defined by a permutation of L elements with no repetition. The interleaver plays two important roles in turbo codes.

- It is used to generate a long block code from small memory convolutional encoders.

The code block length depends on the interleaver length L.

- 2. It decorrelates the inputs to the two encoders. This helps in the decoding process, where iterative algorithms based on information exchange between the two component decoders are used. The decorrelated input ensures that there is a high probability that after the correction of some errors in the first decoder some of the remaining errors will be corrected in the second decoder.

In addition to the above two roles, interleavers are also designed to achieve tasks such as increasing the minimum weight of the codewords, termination of both encoders in the all zero state, and puncturing. We will discuss the trellis termination and puncturing in the following subsections.

## **2.5.3 Trellis Termination in Turbo Codes**

Trellis termination means driving the encoder to the all zero state. We drive the encoder to the all zero state at the end of a block to ensure that the initial encoder state for the next block is also the all zero state. For convolutional encoders we terminate the trellis by appending m zero bits, also known as tail bits, at the end of the information block, where *m* is the memory of the encoder. This strategy however does not work in RSC encoders due to the feedback. The tail bits required in this case depend on the state of the encoder after L information bits where L is the information block length. A simple solution to this problem is shown in Figure 2.9 [17]. After L information bits have been shifted in the encoder the switch is moved from position A to position B for m clock cycles. This drives the encoder to the all zero state. If a pseudorandom interleaver is used, it is highly unlikely that both component encoders in a turbo encoder will terminate in the all-zero state. Therefore only the first encoder is forced to return to the all-zero state and the second encoder is not forced to any particular state. The unknown state of the second encoder results in a performance degradation; however for large interleaver size this degradation is negligible. It is possible to drive both encoders to the all zero state by using a special interleaver such as Block Helical Simile interleaver [18].

Figure 2.9. Trellis termination strategy for RSC encoder

## 2.5.4 Punctured Turbo Codes

Puncturing is used in turbo codes to increase the code rate. For example the output of the rate 1/3 turbo encoder shown in Figure 2.8 can be punctured to obtain higher code rates such as 1/2, 2/3, 3/4, 5/6 and so on. During puncturing some output bits of  $v_0$ ,  $v_1$ , and  $v_2$  are deleted according to a chosen pattern defined by a puncturing matrix P. A rate 1/2 turbo code can be obtained from a rate 1/3 code by using the following puncturing pattern

$$P = \begin{bmatrix} 1 & 1 \\ 1 & 0 \\ 0 & 1 \end{bmatrix},$$

(2.13)

where the puncturing period is two. The position of zeros indicates the bits from the encoder output that are punctured. In the first cycle  $v_2$  is deleted by the zero in the third row of the first column and similarly in the second cycle  $v_1$  is deleted by the zero in the second row of the second column followed by the deletion of  $v_2$  in the next cycle and so on.

## 2.5.5 Summary

In this chapter we presented an overview of error correcting codes. We began by reviewing the most commonly used codes, i.e. block codes and convolutional codes. Block codes divide information bits into blocks and then map each information block to a unique code block. Convolutional codes encode the entire information stream into a single word through the use of shift registers. We further illustrated convolutional codes by introducing recursive systematic convolutional (RSC) encoders and various representations of convolutional encoders. This was followed by concatenated codes and finally, an introduction to turbo codes. We used the concepts and terminologies introduced in the preceding sections to define turbo codes and showed that a turbo encoder can be constructed from two RSC encoders separated by an interleaver.

# Chapter 3

# **Iterative Decoding of Turbo Codes**

## **3.1 Introduction**

In this chapter we describe the iterative decoding of turbo codes. Turbo codes are formed by the parallel concatenation of two RSC codes. The optimal decoding of such coding schemes is extremely complex. It has also been found that optimal decoding schemes used for turbo codes perform only marginally better than the iterative decoding schemes [19]. Furthermore, several turbo coding schemes, based on iterative decoding, have been found that approach the Shannon limit thus providing an almost optimal performance [20]. Hence, iterative decoding schemes are almost exclusively used in the decoding of turbo codes. We begin this chapter with the description of a communication system model. We then present the general structure of an iterative decoder followed by a detailed description of the component decoders used within this iterative decoder.

Figure 3.1. System model

# 3.2 System Model

We shall use the system model shown in Figure 3.1 to illustrate the decoding methods in this chapter. A binary message sequence, denoted by u is given by

$$\boldsymbol{u} = (u_1, u_2, u_3, \dots, u_t, \dots, u_L), \tag{3.1}$$

where  $u_t$  is the message symbol at time t and L is the sequence length. We will assume that all message symbols are generated independently and have equal a priori probabilities. The encoder encodes this binary message and produces a code sequence v. The code sequence is then modulated to produce a modulated sequence x. The code and modulated sequences are further explained as

$$\mathbf{v} = (\underline{v}_1, \underline{v}_2, \underline{v}_3, \dots, \underline{v}_t, \dots, \underline{v}_L), \tag{3.2}$$

where

$\underline{v}_t = (v_{t,0}, v_{t,1}, \dots, v_{t,n-1})$

is the codeword of length n.

The modulated sequence is represented as

$$\boldsymbol{x} = (\underline{x}_1, \underline{x}_2, \underline{x}_3, \dots, \underline{x}_t, \dots, \underline{x}_L), \qquad (3.3)$$

where

$$\underline{x}_{t} = (x_{t,0}, x_{t,1}, \dots, x_{t,n-1})$$

is the modulated codeword of length n and

$$x_{t,i} = 2v_{t,i} - 1, \qquad i = 0, 1, \dots, n - 1.$$

(3.4)

Equation (3.4) suggests a mapping of coded bit  $v_{t,i} = 1$  to  $x_{t,i} = +1$  and  $v_{t,i} = 0$  to  $x_{t,i} = -1$ .

The modulated sequence is corrupted by additive white Gaussian noise resulting in the received sequence

$$\mathbf{y} = (\underline{y}_1, \underline{y}_2, \underline{y}_3, \dots, \underline{y}_t, \dots, \underline{y}_L), \tag{3.5}$$

where

$$\underline{y}_{t} = (y_{t,0}, y_{t,1}, \dots, y_{t,n-1})$$

and

$$y_{t,i} = x_{t,i} + e_{t,i}, \qquad i = 0, 1, \dots, n-1,$$

(3.6)

where  $e_{t,i}$  is the zero-mean Gaussian noise random variable with zero mean variance  $\sigma^2$ . Each noise sample is independent from the others. The decoder receives the sequence y and after decoding provides an estimate of the input to the encoder. We shall represent the decoded bit at time unit k as  $u_{k}$ , in the description of the decoding methods.

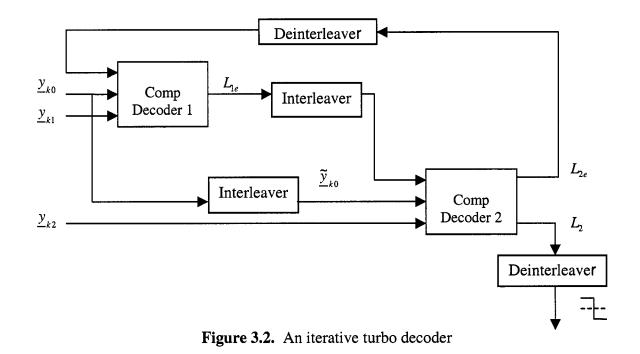

# **3.3 Iterative Decoder Structure**

The general structure of an iterative turbo decoder is shown in Figure 3.2. Two component decoders are linked by interleavers in a way similar to that of the turbo encoder. Each component decoder receives three inputs

1. The systematic channel output (information) bits,

- 2. The parity bits transmitted by its corresponding component encoder,

- 3. Information about the concerned bits from the other component decoder. This is also known as a priori information.

The component decoders use the inputs from the channel as well as the a priori information from the other decoder in the decoding process. They also provide the reliability information for each decoded bit. This reliability information, along with the bit estimate, is known as soft output of the component decoder. These soft outputs are typically represented as log likelihood ratios (LLRs). The magnitude of the ratio gives the reliability estimate and the sign, the bit estimate. For example LLR for the value of a decoded bit  $u_k$  is given by

$$L(u_k) = \ln\left(\frac{P(u_k = +1)}{P(u_k = -1)}\right)$$

(3.7)

where  $P(u_k = +1)$  is the probability that bit  $u_k = +1$ , and  $P(u_k = -1)$  is the probability that  $u_k = -1$ .

In the first iteration, the first component decoder takes channel output as its input and produces soft output. This soft output is the first decoder's estimate of the received data bits and is used as additional information by the second decoder. The second decoder uses this information along with the channel output to produce its own estimate of the data bits. This completes the first iteration. In the second iteration the first decoder again decodes the same channel output but this time it also uses the additional information provided by the output of the second decoder in the first iteration. This additional

information helps the first decoder improve its estimate and obtain more accurate soft outputs. These outputs are then used by the second decoder as a priori information and the cycle is repeated. After each iteration, the bit error rate (BER) of the decoded bits tends to fall, however the improvement in performance decreases with increasing iterations. For this reason the number of iterations is usually limited to a small number such as eight [23].

The iterative nature of decoding requires that the same information must not be reused more than once in each decoding step. Therefore, we must subtract any redundant information from the inputs of the component encoders. This leads us to the concept of extrinsic and intrinsic information which we shall consider later in this chapter.

# **3.4 Component Decoders**

The component encoders used in iterative decoding of turbo codes must have the ability to use a priori information as well as provide reliability information for each decoded bit. Two decoders that satisfy the above criteria are MAP (maximum a posteriori algorithm) proposed by Bahl et al. [21], and SOVA (soft output Viterbi algorithm) proposed by Hagenauer and Hoeher [22]. Let us now consider these component decoders in detail.

## **3.4.1** The Maximum A Posteriori Algorithm (MAP)

The MAP algorithm was introduced by Bahl et al. in 1974 to estimate the a posteriori probabilities of the states and the transitions of a Markov source observed in a memoryless noisy channel. When used to decode convolutional codes, the algorithm is optimal in terms of minimizing decoded BER. It examines every possible path through the convolutional decoder trellis, and was considered infeasibly complex in most applications. For this reason it was largely ignored before the discovery of turbo codes. However due to the iterative decoding used in turbo codes, Berrou et al. employed MAP decoding in their seminal paper on turbo codes.

#### **3.4.1.1 Introduction and Mathematical Preliminaries**

Let us now examine the theory behind the MAP algorithm. We shall assume binary coding. For each decoded bit  $u_k$ , the MAP algorithm gives the probability that this bit was +1 or -1, given the received symbol  $\underline{y}$ . This is equivalent to finding the a posteriori LLR  $L(u_k|\underline{y})$ , where

$$L(u_k \mid \underline{y}) = \ln\left(\frac{P(u_k = +1 \mid \underline{y})}{P(u_k = -1 \mid \underline{y})}\right).$$

(3.8)

If  $S_{k-1}=$ 's is the previous state and  $S_k=s$  is the present state in a trellis, then we can use Bayes' rule and the fact that only one transition between  $S_{k-1}$  and  $S_k$  could have occurred at the encoder to rewrite the above equation as

$$L(u_{k} \mid \underline{y}) = \ln \left( \frac{\sum_{\substack{u_{k}=+1 \\ u_{k}=+1}}^{(s,s) \Rightarrow} P(S_{k-1} = s \land S_{k} = s \land \underline{y})}{\sum_{\substack{u_{k}=-1 \\ u_{k}=-1}}^{(s,s) \Rightarrow} P(S_{k-1} = s \land S_{k} = s \land \underline{y})} \right),$$

(3.9)

where  $(s, s) \Rightarrow u_k = +1$  is the set of transitions from previous state's to present state s that can occur if the input bit  $u_k = +1$ , and similarly for  $(s, s) \Rightarrow u_k = -1$ . For brevity we shall write  $P(S_{k-1} = s \land S_k = s \land y)$  as  $P(s \land s \land y)$ .

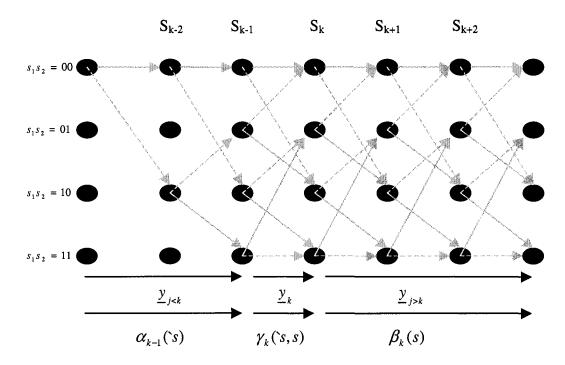

Let us now consider the individual probabilities in the above equation. We can split the received sequence  $\underline{y}$  into three sections: the received codeword associated with the present transition  $\underline{y}_k$ , the received sequence prior to the present transition  $\underline{y}_{j < k}$ , and the received sequence after the present transition  $\underline{y}_{j > k}$ . We can thus write

$$P(s \wedge s \wedge \underline{y}) = P(s \wedge s \wedge \underline{y}_{i < k} \wedge \underline{y}_{k} \wedge \underline{y}_{i > k}).$$

(3.10)

Let's assume that the channel is memoryless, i.e. the future received sequence will depend only on the present state and not on the previous state or the present and previous received channel sequences. Now we can use the Bayes' rule  $P(a \land b) = P(a|b)P(b)$  to rewrite the individual probabilities

$$P(s \land s \land \underline{y}) = P(s \land s \land \underline{y}_{j < k} \land \underline{y}_{k} \land \underline{y}_{j > k})$$

$$= P(\underline{y}_{j > k} \mid s) \cdot P(s \land s \land \underline{y}_{j < k} \land \underline{y}_{k})$$

$$= P(\underline{y}_{j>k} \mid s) \cdot P(\{\underline{y}_k \land s\} \mid s) \cdot P(s \land \underline{y}_{j

$$= \beta_k(s) \cdot \gamma_k(s, s) \cdot \alpha_{k-1}(s), \qquad (3.11)$$$$

where

- $\alpha_{k-1}(s) = P(s \land \underline{y}_{j < k})$  is the probability that trellis is in state 's at time k-1 and the received sequence up to this point is  $\underline{y}_{j < k}$ .

- $\beta_k(s) = P(\underline{y}_{j>k} | s)$  is the probability that trellis is in state s at time k and the future received sequence will be  $\underline{y}_{j>k}$ .

- $\gamma_k(s, s) = P(\{\underline{y}_k \land s\}|s)$  is the probability that at time k-1 trellis was in states, it moves to state s at time k and the channel sequence for this transition is  $\underline{y}_k$ .

Figure 3.3 shows a section of a four state trellis with this split of the received sequence. From Equations (3.10) and (3.11) we can finally write the conditional LLR for  $u_k$

$$L(u_{k} \mid \underline{y}) = \ln \left( \frac{\sum_{\substack{u_{k}=+1 \\ u_{k}=+1}}^{(s,s) \Rightarrow} \alpha_{k-1}(s) \cdot \gamma_{k}(s,s) \cdot \beta_{k}(s)}{\sum_{\substack{u_{k}=-1 \\ u_{k}=-1}}^{(s,s) \Rightarrow} \alpha_{k-1}(s) \cdot \gamma_{k}(s,s) \cdot \beta_{k}(s)} \right).$$

(3.12)

The MAP algorithm calculates the  $\alpha_k(s)$  and  $\beta_k(s)$  for all states throughout the trellis and uses Equation 3.12 to deliver the conditional LLRs. Let us see how the values of  $\alpha_k(s)$ ,  $\beta_k(s)$  and  $\gamma_k(s)$  are calculated.

#### **3.4.1.2** Forward Recursion and Calculation of $\alpha_k(s)$

From the definition of  $\alpha_{k-1}(s)$  in Equation 3.11, we can write

$$\alpha_k(s) = P(S_k = s \land y_{j < k+1})$$

Figure 3.3. MAP decoder trellis for a 4 state RSC code

$$= P(s \wedge \underline{y}_{j < k} \wedge \underline{y}_{k})$$

$$= \sum_{alts} P(s \wedge s \wedge \underline{y}_{j < k} \wedge \underline{y}_{k}), \qquad (3.13)$$

where in the last step we split the probability  $P(s \wedge \underline{y}_{j < k+1})$  into sum of joint probabilities  $P(s \wedge s \wedge \underline{y}_{j < k} \wedge \underline{y}_{k})$  over all possible previous states. Again using Bayes' rule and assuming a memoryless channel we can write

$$\alpha_{k}(s) = \sum_{alls} P(s \wedge s \wedge \underline{y}_{j < k} \wedge \underline{y}_{k})$$

$$= \sum_{alls} P(\{s \wedge \underline{y}_{k}\} | \{s \wedge \underline{y}_{j < k}\}) \cdot P(s \wedge \underline{y}_{j < k})$$

$$= \sum_{alls} P(\{s \wedge \underline{y}_{k}\} | s) \cdot P(s \wedge \underline{y}_{j < k})$$

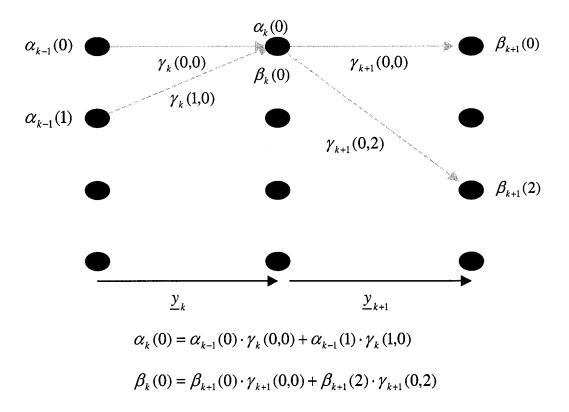

**Figure 3.4.** Recursive calculation of  $\alpha_k(0)$  and  $\beta_k(0)$

$$= \sum_{alls} \alpha_{k-l}(s) \cdot \gamma_k(s, s).$$

(3.14)

Thus the values for  $\alpha_k(s)$  can be calculated easily from the  $\gamma_k(s, s)$  values recursively. Figure 3.4 shows how  $\alpha_k(s)$  can be calculated recursively using  $\alpha_{k-1}(s)$  and  $\gamma_k(s, s)$  for a four state RSC code. Notice that because of the binary trellis we only have two previous states that can transit into a current state.

#### **3.4.1.3 Backward Recursion and Calculation of** $\beta_k(s)$

The values of  $\beta_k(s)$  can also be calculated recursively in a similar manner during a backward recursion. The backward recursion starts at the last stage of the trellis and moves in the reverse direction. Using a derivation similar to that of Equation 3.14 we can show

$$\beta_{k-1}(s) = \sum_{alls} \beta_k(s) \cdot \gamma_k(s, s).$$

(3.15)

Figure 3.4 again shows the calculation of one  $\beta_{k-1}(s)$  value from  $\beta_k(s)$  and  $\gamma_k(s, s)$  recursively.

### **3.4.1.4 Calculation of** $\gamma_k(s, s)$

Let's consider how we can calculate the transition probability values  $\gamma_k(s, s)$  in Equation 3.11 from the received channel sequence and the a priori information. From Equation 3.11 and Bayes' rule we have

$$\gamma_{k}(s, s) = P(\{\underline{y}_{k} \land s\} | s)$$

$$= P(\{\underline{y}_{k} | \{s \land s\}) \cdot P(s | s)$$

$$= P(\{\underline{y}_{k} | \{s \land s\}) \cdot P(u_{k})$$

$$= P(\underline{y}_{k} | \underline{x}_{k}) \cdot P(u_{k}), \qquad (3.16)$$

where  $u_k$  is the bit required for the transition from state 's to s and  $P(u_k)$  is the a priori probability of this bit.  $\underline{x}_k$  is the codeword associated with this transition. Thus the transition probability  $\gamma_k(s, s)$  is given by the product of the a priori probability of the bit required for this transition and the probability that, given the codeword associated with this transition  $\underline{x}_k$  was transmitted, we received sequence  $\underline{y}_k$ . Assuming a memoryless Gaussian channel with BPSK (binary phase shift keying) modulation,  $P(\underline{y}_k | \underline{x}_k)$  is given as [23]

$$P(\underline{y}_{k} \mid \underline{x}_{k}) = \prod_{l=1}^{n} P(y_{kl} \mid x_{kl}), \qquad (3.17)$$

where  $x_{kl}$  and  $y_{kl}$  are individual bits within the transmitted and received codewords  $\underline{y}_k$ and  $\underline{x}_k$  respectively and *n* is the number of these bits in each codeword.

#### **3.4.1.5 Iterative Decoding Using MAP Algorithm**

As the first MAP decoder receives the channel values  $y_{kl}$ , it uses these values and the a priori LLRs  $L(u_k)$  (which are provided by the other component decoder in iterative decoding) to calculate  $\gamma_k(`s, s)$  according to Equations 3.16 and 3.17. The  $\gamma_k(`s, s)$  are used to calculate  $\alpha_k(s)$  recursively from Equation 3.14. This constitutes the forward recursion of the MAP algorithm. Once all the channel values have been received and all  $\gamma_k(`s, s)$  have been calculated, backward recursion starts.  $\beta_k(s)$  are calculated in the backward recursion according to Equation 3.15. Finally all the calculated values of  $\alpha_k(s)$ ,  $\gamma_k(`s, s)$ , and  $\beta_k(s)$  are used in Equation 3.12 to calculate the values of a posteriori LLRs  $L(u_k \mid y)$ .

In iterative decoding the output of the first MAP decoder provides the a priori probabilities for the second MAP decoder. However these probabilities should come from an independent source. Recall that we calculated the a posteriori LLRs  $L(u_k \mid \underline{y})$  from a

priori LLRs  $L(u_k)$  and the received sequence  $y_{kl}$ .  $L(u_k)$  was provided by the other decoder and  $y_{kl}$  consisted of systematic bits  $y_{ks}$ , common to both MAP decoders. Therefore in order to provide the second decoder with independent a priori knowledge we must subtract the effect of the above two terms from the a posteriori LLRs of the first decoder. It can be shown [1] that, for a systematic code, output of the MAP decoder given by Equation 3.12 can be re-written as

$$L(u_{k} \mid \underline{y}) = \ln \left( \frac{\sum_{\substack{(s,s) \Rightarrow \\ u_{k}=+1}} \alpha_{k-1}(s) \cdot \gamma_{k}(s,s) \cdot \beta_{k}(s)}{\sum_{\substack{(s,s) \Rightarrow \\ u_{k}=-1}} \alpha_{k-1}(s) \cdot \gamma_{k}(s,s) \cdot \beta_{k}(s)} \right)$$

$$= L(u_{k}) + L_{c}(y_{ks}) + L_{e}(u_{k}), \qquad (3.18)$$

where  $L(u_k)$  is the a priori LLR given by(1), and  $L_c$  is the channel reliability value and  $y_{ks}$ is the received version of the transmitted systematic bit  $x_{ks} = u_k$ .  $L_c$  is further explained as

$$L_c = \frac{4a}{2\sigma^2},\tag{3.19}$$

where  $\sigma^2$  is the variance and *a* is the fading amplitude of the noise. For zero-mean Gaussian noise, *a*=1.

The final term  $L_e(u_k)$  is derived from the a priori information sequence  $L(u_n)$  and the received channel information sequence  $\underline{y}$  excluding the received systematic bit  $y_{ks}$  and the a priori information  $L(u_k)$  for the bit  $u_k$ . So it is called the extrinsic LLR of the bit  $u_k$ . It is this extrinsic LLR that is passed on to the second decoder as its a priori LLR.

Now we are ready to summarize the iterative decoding with MAP decoders. The first MAP decoder receives the channel sequence which consists of both the systematic and the parity bits. It uses this sequence and the a priori information available to calculate its

estimate of the conditional LLRs of data bits  $u_k$ , k=1,2..N. Note that in the first iteration of the first component decoder there is no a priori information available, and hence  $P(u_k)$ in Equation 3.16 will be 0.5. The extrinsic information  $L_e(u_k)$  is then calculated from Equation 3.18 which is then passed on to the second decoder. Next the second MAP decoder starts its operation. It receives the channel sequence containing the systematic bits and the interleaved parity bits from the second encoder. The second decoder uses this sequence and the a priori information (interleaved extrinsic information  $L_e(u_k)$  from the first decoder) supplied by the first decoder to calculate its own estimate of the conditional LLRs. This completes one iteration of the turbo decoder. In the second iteration the first decoder again processes its received channel sequence but this time its a priori information is provided by the extrinsic value of the second decoder calculated in the first iteration. This results in improved estimates of a posteriori LLRs by the first decoder. The second iteration continues with second decoder using a priori values derived from the improved a posteriori LLRs of the first decoder to improve its own estimates. The iterative process proceeds and with each iteration, BER of the decoded bits falls. However the improvement in performance diminishes with increasing number of iterations. Therefore for time and computational complexity reasons, the number of iterations is usually limited to a small number such as eight. At the end of the iterative process the a posteriori LLRs are taken from the second decoder and a hard decision is made on the received sequence.

# 3.4.2. The Max-Log-MAP Algorithm

The MAP algorithm as described above is extremely complex due to the multiplications involved in the recursive calculation for  $\alpha_k(s)$  in Equation 3.14 and  $\beta_{k-l}(s)$  in Equation 3.15. However its complexity can be dramatically reduced without affecting its performance. This is done by transferring the recursions in to the log domain and invoking an approximation to reduce its complexity. Max-Log-MAP was initially proposed by Koch and Baier [24]. It simplifies the MAP algorithm by transferring the calculation of  $\alpha_k(s)$ ,  $\beta_k(s)$ , and  $\gamma_k(s, s)$  into the log arithmetic domain and then using the approximation

$$\ln\left(\sum_{i} e^{x_{i}}\right) \approx \max_{i}(x_{i}).$$

(3.20)

Let us define  $A_k(s)$ ,  $B_k(s)$  and  $\Gamma_k(s, s)$  as

$$A_k(s) \underline{\Delta} \ln(\alpha_k(s)) \tag{3.21}$$

$$B_k(s) \triangleq \ln(\beta_k(s)) \tag{3.22}$$

$$\Gamma_k(s, s) \triangleq \ln(\gamma_k(s, s)). \tag{3.23}$$

Now we can re-write Equation 3.14 as

$$A_{k}(s) \triangleq \ln(\alpha_{k}(s))$$

$$= \ln\left(\sum_{all \cdot s} \alpha_{k-1}(s) \gamma_{k}(s,s)\right)$$

$$= \ln\left(\sum_{all \cdot s} \exp[A_{k-1}(s) + \Gamma_{k}(s,s)]\right)$$

$$\approx \max_{s}(A_{k-1}(s) + \Gamma_{k}(s,s)). \qquad (3.24)$$