# ANALYSIS AND HARDWARE IMPLEMENTATION OF SYNCHRONIZATION METHODS FOR STREAM CIPHERS

YAPING HUANG

## **Analysis and Hardware Implementation of Synchronization Methods for Stream Ciphers**

by

©Yaping Huang Master of Engineering

A thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of Master of Engineering.

Department of Electrical and Computer Engineering Memorial University of Newfoundland

April 12, 2010

## Contents

| List of Tables                                               | IV   |

|--------------------------------------------------------------|------|

| List of Figures                                              | V    |

| List of Abbreviations                                        | VIII |

| List of Symbols                                              | IX   |

| Abstract                                                     |      |

| Acknowledgements                                             | .XII |

| Chapter 1                                                    |      |

| Introduction                                                 |      |

| 1.1 Introduction to cryptography                             | 1    |

| 1.2 Objective of this Thesis                                 |      |

| 1.3 Outline of this Thesis                                   |      |

| Chapter 2                                                    | 7    |

| Background                                                   |      |

| 2.1 Classification of Stream Ciphers                         | 7    |

| 2.2 Stream Cipher Structures                                 |      |

| 2.2.1 FSR (Feedback Shift Register)                          |      |

| 2.2.2 Grain-128                                              |      |

| 2.3 Block Cipher Modes of Operation                          |      |

| 2.3.1 Output Feedback (OFB) Mode                             |      |

| 2.3.2 Cipher Feedback (CFB) Mode                             |      |

| 2.3.3 Statistical Cipher Feedback (SCFB) Mode                |      |

| 2.3.4 Optimized Cipher Feedback (OCFB) Mode                  |      |

| 2.4 Marker-based Mode                                        |      |

| 2.5 Characteristics of SCFB Mode                             | 24   |

| 2.5.1 OFB Block Size                                         |      |

| 2.5.2 Resynchronization.                                     | 26   |

| 2.5.3 Error Propagation                                      |      |

| 2.5.4 Comparison with Other Modes                            |      |

| 2.6 Digital Hardware Implementation Tools                    |      |

| 2.6.1 FPGA Implementation                                    |      |

| 2.6.2 Software Implementation                                | 34   |

| 2.7 Conclusion                                               |      |

| Chapter 3                                                    |      |

| Analysis of Characteristics of AES-based SCFB mode           | 36   |

| 3.1 SCFB Pseudocode                                          |      |

| 3.2 Synchronization Recovery Delay                           |      |

| 3.3 Error Propagation Factor                                 |      |

| 3.4 Conclusion                                               |      |

| Chapter 4                                                    |      |

| Analysis and Design of SCFB Mode Implementation of Grain-128 |      |

| 4.1 SCFB Mode Applied to a Synchronous Stream Cipher         |      |

| 4.2 System Design                                            |      |

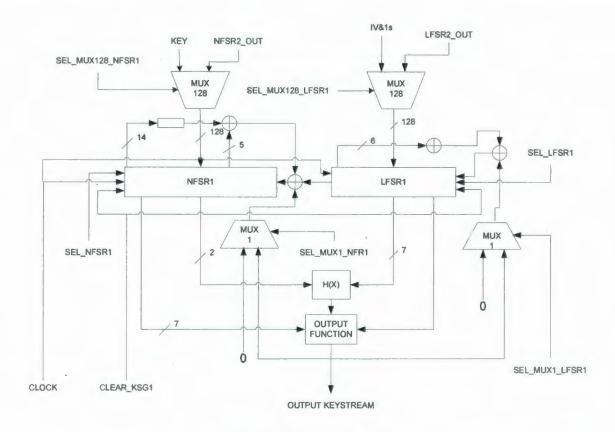

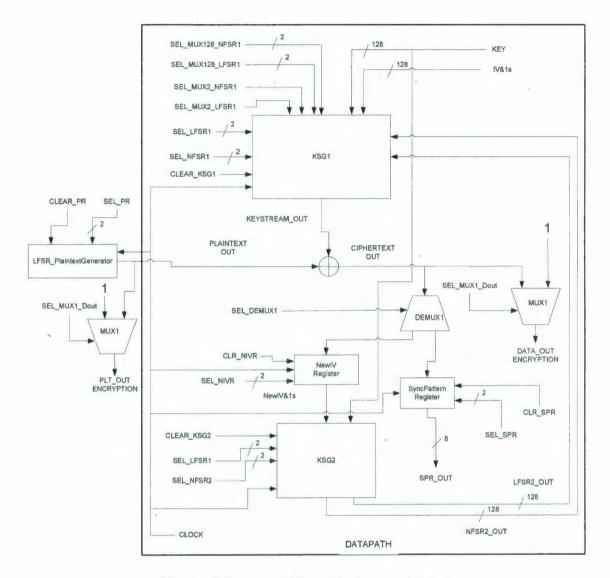

| 4.2.1 Primary Keystream Generator - KSG1                     |      |

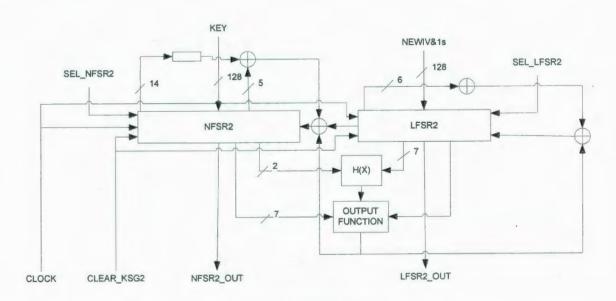

| 4.2.2 Setup Keystream Generator - KSG2                       |      |

| 4.2.3 Counters                                               | 62   |

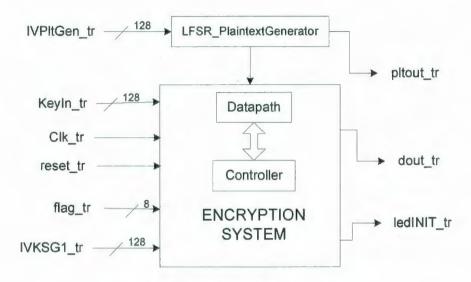

|     | 4.2.4 Datapath of Encryption System                                            | 63 |

|-----|--------------------------------------------------------------------------------|----|

|     | 4.2.5 Controller of Encryption System                                          | 68 |

|     | 4.2.6 Decryption System                                                        |    |

|     | 4.2.7 System Interface                                                         | 72 |

|     | 4.2.8 System on FPGA Board                                                     |    |

|     | 4.3 FPGA Implementation                                                        |    |

|     | 4.3.1 FPGA Board Configuration                                                 | 78 |

|     | 4.4 Testing and Synthesis Results                                              |    |

|     | 4.5 Analysis of SRD and EPF                                                    | 81 |

|     | 4.5.1 Synchronization Recovery Delay                                           |    |

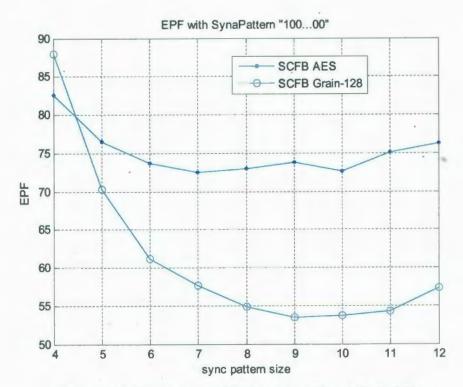

|     | 4.5.2 Error Propagation Factor                                                 | 84 |

|     | 4.6 Comparison of Characteristics of SCFB mode based on AES and Grain-128      | 86 |

|     | 4.6.1 Synchronization Recovery Delay                                           |    |

|     | 4.6.2 Error Propagation Factor                                                 |    |

|     | 4.7 Conclusion                                                                 |    |

| C   | hapter 5                                                                       | 91 |

|     | nalysis and Hardware Implementation of Marker-based Synchronous Stream Cipher. |    |

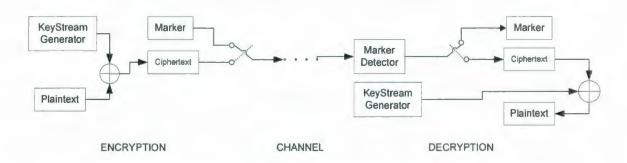

|     | 5.1 Description of Marker Concept                                              |    |

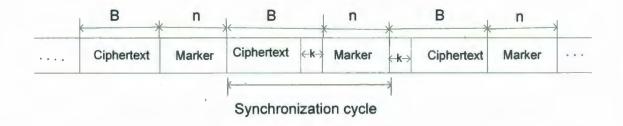

|     | 5.2 Description of Resynchronization                                           | 93 |

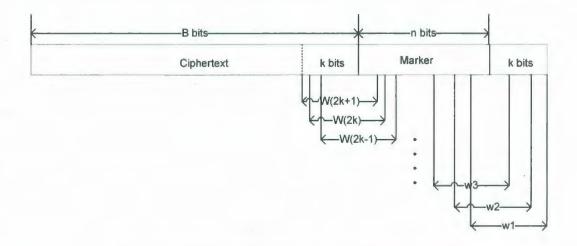

|     | 5.3 Description of Data Register at Decryption Side                            | 95 |

|     | 5.4 Description of System Design                                               |    |

|     | 5.4.1 Description of KeyStream Generator                                       |    |

|     | 5.4.2 Description of Encryption Datapath                                       | 99 |

|     | 5.4.3 Description of Encryption Controller                                     |    |

|     | 5.4.4 Description of Decryption Datapath                                       |    |

|     | 5.4.5 Description of Decryption Controller                                     |    |

|     | 5.5 Description of FPGA Implementation                                         | 10 |

|     | 5.6 Synthesis Results                                                          | 11 |

|     | 5.7 Characteristics of Marker-based Synchronization Implementation             | 12 |

|     | 5.8 Comparison of SCFB Mode and Marker-based Mode                              |    |

|     | 5.9 Comparison of FPGA implementation of AES and SCFB Mode and Marker-base     | ed |

|     | Mode                                                                           |    |

|     | 5.10 Conclusion                                                                | 18 |

|     | napter 6 1                                                                     |    |

| C   | onclusion and Future Work1                                                     |    |

|     | 6.1 Summary                                                                    |    |

|     | 6.2 Conclusions                                                                |    |

|     | 6.3 Future Work                                                                |    |

| A . | nnon div                                                                       | 20 |

## **List of Tables**

| Table 2.1. Summarize of SRD and EPF for OFB, CFB, and SCFB mode           | 3() |

|---------------------------------------------------------------------------|-----|

| Table 3.1. Best sync pattern format list for SRD                          | 41  |

| Table 3.2. Best sync pattern format list for EPF                          |     |

| Table 4.1. Input and output signals of structure of KSG1                  | 60  |

| Table 4.2. Input and output signals of structure of KSG2                  |     |

| Table 4.3. Input and output signals of block diagram of encryption system |     |

| Table 4.4 Control signals of transfer cycles of SCFB system interface     |     |

| Table 4.5. Mapping table of SCFB mode configured for Grain-128            |     |

| Table 4.6. Test vectors of Grain-128                                      |     |

| Table 4.7. Device utilization of SCFB configured by Stream Cipher         |     |

| Table 5.1. MSNum in terms of marker position                              | 109 |

| Table 5.2. Device utilization of marker-based mode                        |     |

# **List of Figures**

| Figure 2.1. General mode of a synchronous stream cipher                     | 9    |

|-----------------------------------------------------------------------------|------|

| Figure 2.2. General mode of a self-synchronizing stream cipher              | . 10 |

| Figure 2.3. Feedback shift register of length L [16]                        | . 11 |

| Figure 2.4. Linear feedback shift register of length L [16]                 | . 12 |

| Figure 2.5. Normal mode of onlinear combination generator                   | . 13 |

| Figure 2.6. the Geffe Generator                                             | . 14 |

| Figure 2.7. An overview of the Grain-128                                    | . 15 |

| Figure 2.8. Initialization mode of stream cipher Grain-128                  | . 16 |

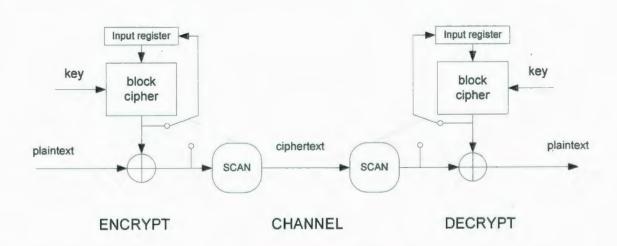

| Figure 2.9. Structure of OFB mode                                           | . 18 |

| Figure 2.10. Structure of CFB mode.                                         | . 19 |

| Figure 2.11. Structure of SCFB mode                                         | . 21 |

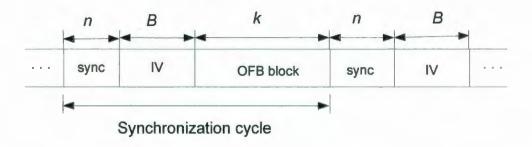

| Figure 2.12. Synchronization cycle of SCFB mode                             | . 22 |

| Figure 2.13. Picture of Digilent Nexys II board                             | . 34 |

|                                                                             |      |

| Figure 3.1. SCFB pseudocode [10]                                            | . 37 |

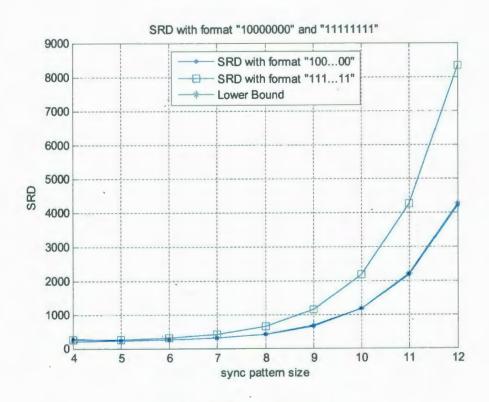

| Figure 3.2. SRD versus sync pattern size                                    | . 39 |

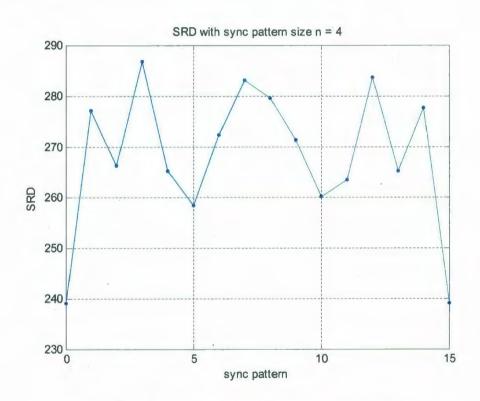

| Figure 3.3. SRD versus sync pattern with sync pattern size n = 4            |      |

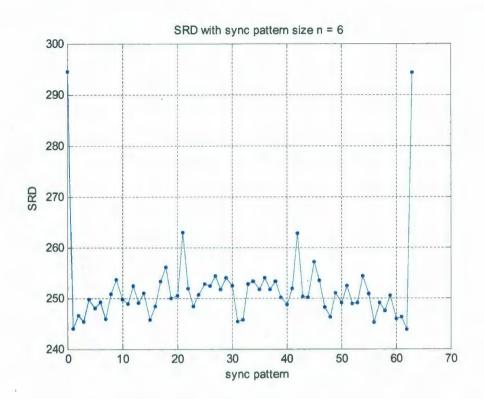

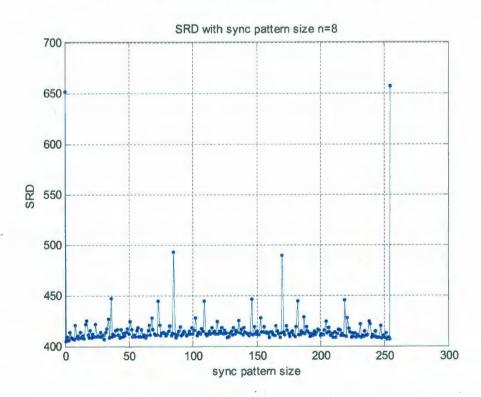

| Figure 3.4. SRD versus sync pattern with sync pattern size n = 6            | . 41 |

| Figure 3.5. SRD versus sync pattern with sync pattern size n = 8            | . 41 |

| Figure 3.6. EPF versus sync pattern size                                    |      |

| Figure 3.7. EPF versus sync pattern with sync pattern size n = 4            | . 48 |

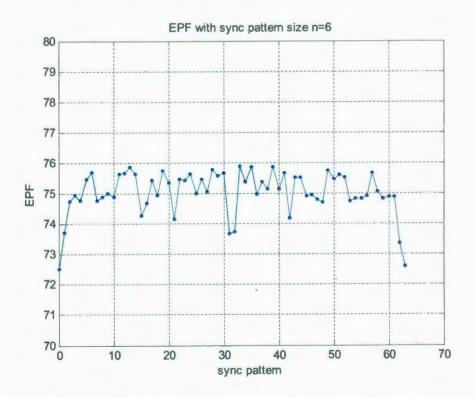

| Figure 3.8. EPF versus sync pattern with sync pattern size $n = 6$          | . 48 |

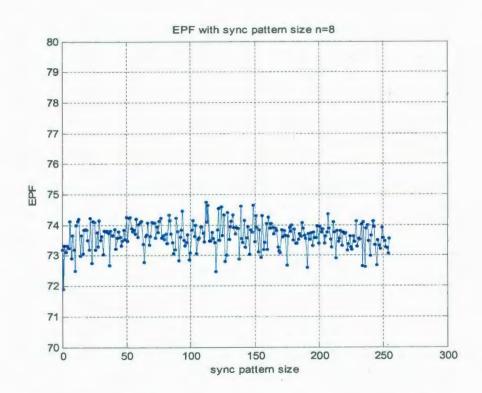

| Figure 3.9. EPF versus sync pattern with sync pattern size $n = 8$          | . 49 |

|                                                                             |      |

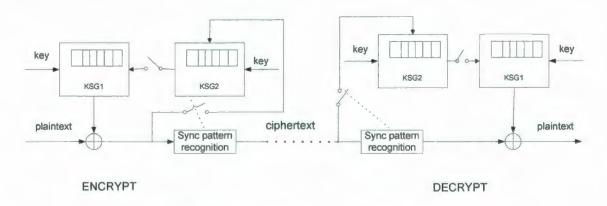

| Figure 4.1. Structure of SCFB mode configured for stream cipher             | . 55 |

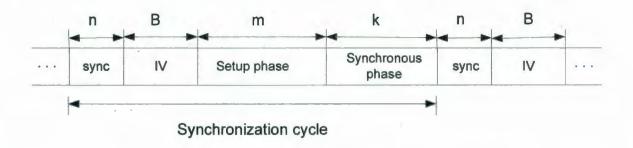

| Figure 4.2. Synchronization cycle of SCFB mode configured for stream cipher | . 56 |

| Figure 4.3. Structure of KSG1                                               | . 59 |

| Figure 4.4. Structure of KSG2                                               | 61   |

| Figure 4.5. Block Diagram of Encryption System                              | 65   |

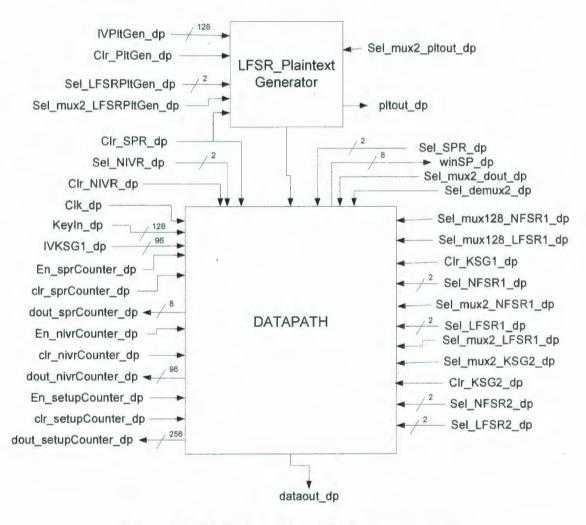

| Figure 4.6. Structure of datapath of encryption system                            | 66    |

|-----------------------------------------------------------------------------------|-------|

| Figure 4.7. Block diagram of datapath of encryption system                        | 67    |

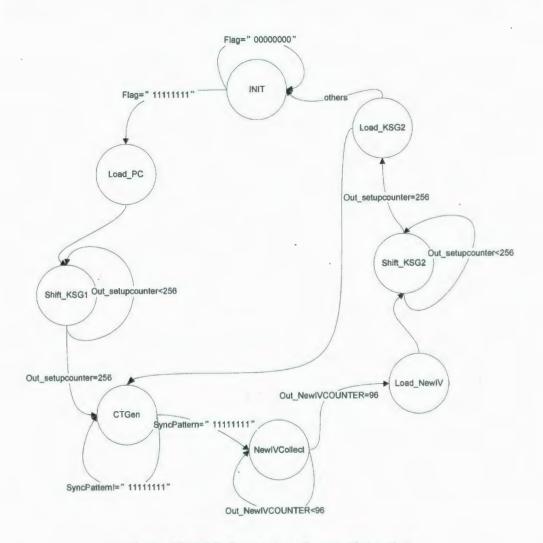

| Figure 4.8. FSM of controller of encryption system                                | 68    |

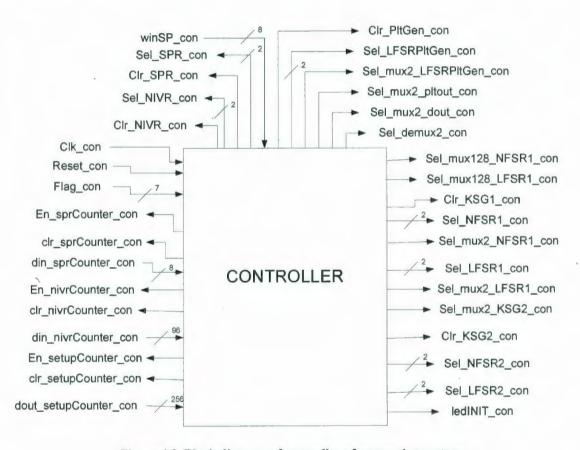

| Figure 4.9. Block diagram of controller of encryption system                      | 70    |

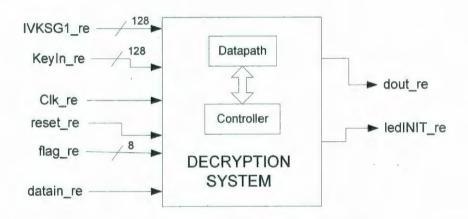

| Figure 4.10. Block diagram of decryption system                                   | 71    |

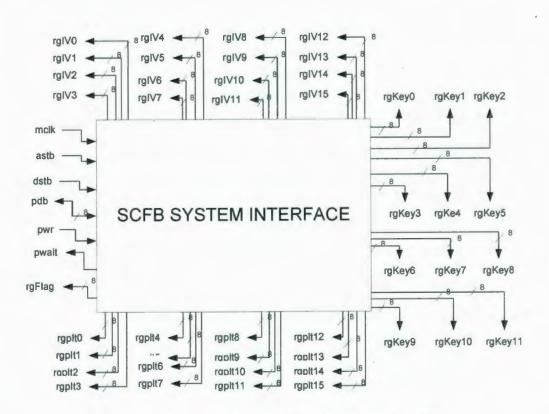

| Figure 4.11. Block diagram of SCFB system interface                               | 73    |

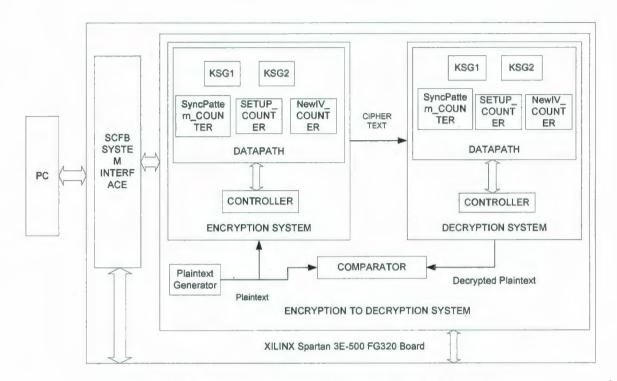

| Figure 4.12. Block diagram of the implementation of SCFB mode                     | 75    |

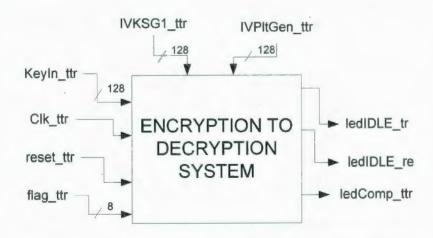

| Figure 4.13. Block diagram of encryption with decryption system                   |       |

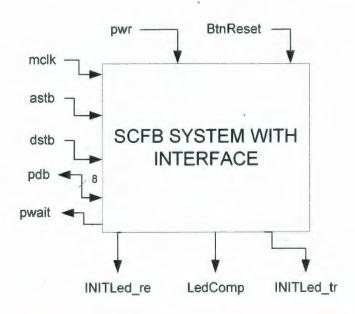

| Figure 4.14. Block diagram of SCFB system with interface                          | 77    |

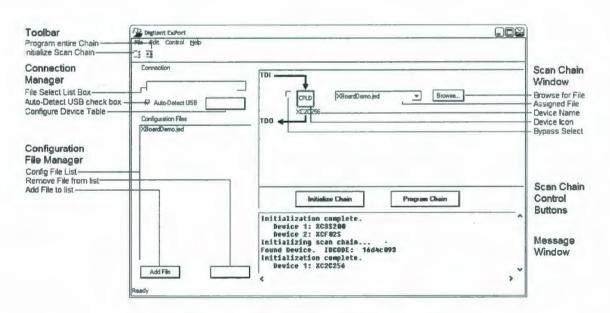

| Figure 4.15. Digilent Export main window [4]                                      | 78    |

| Figure 4.16. Digilent TransPort Register I/O window [4]                           | 79    |

| Figure 4.17. SRD versus sync pattern size with format "10000"                     | 83    |

| Figure 4.18. EPF versus sync pattern size with format "10000"                     | 85    |

| Figure 4.19. Comparison of SRD based on AES and Grain-128                         | 87    |

| Figure 4.20. Comparison of EPF based on AES and Grain-128                         |       |

|                                                                                   |       |

| Figure 5.1. Structure of marker-based synchronous stream cipher                   | 92    |

| Figure 5.2. Synchronization cycle of marker-based synchronous stream cipher       | 93    |

| Figure 5.3. Structure of data register of marker-based mode                       | 96    |

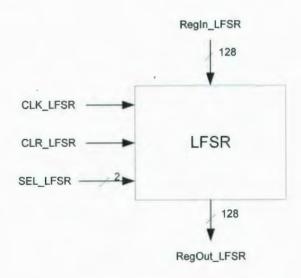

| Figure 5.4. Block diagram of LFSR.                                                | 99    |

| Figure 5.5. Structure of LFSR.                                                    | 99    |

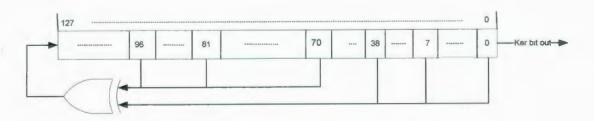

| Figure 5.6. Structure of datapath of encryption system                            | . 100 |

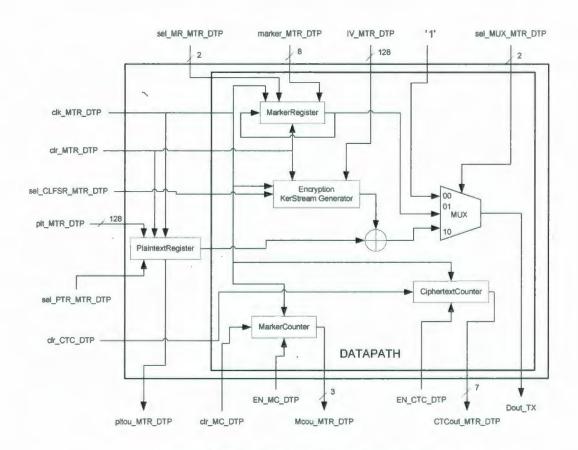

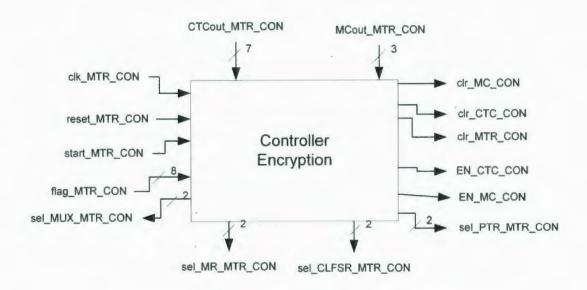

| Figure 5.7. Block diagram of controller of encryption system                      | . 102 |

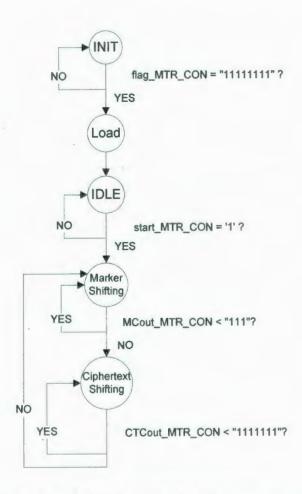

| Figure 5.8. Flow chart of controller of encryption system                         | . 103 |

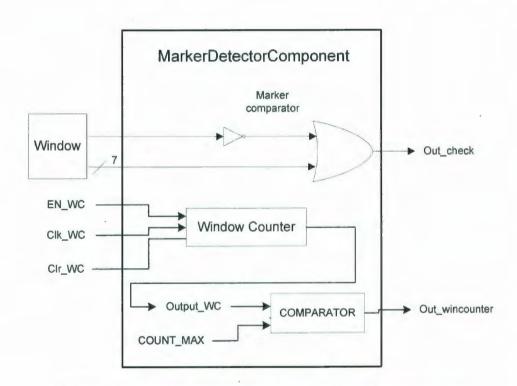

| Figure 5.9. Structure of marker detector component of decryption system           | . 104 |

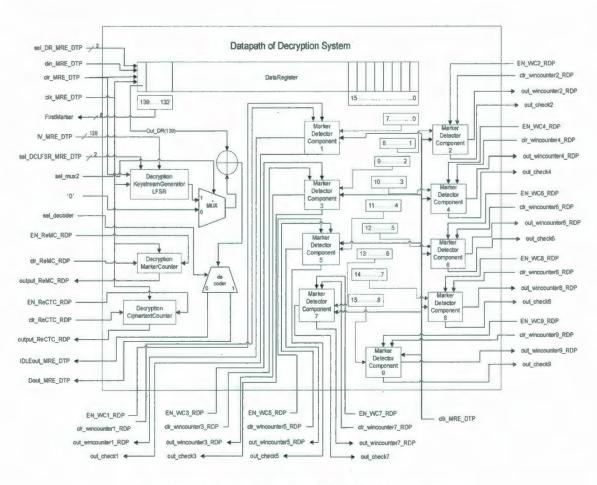

| Figure 5.10. Structure of datapath of decryption system                           | . 105 |

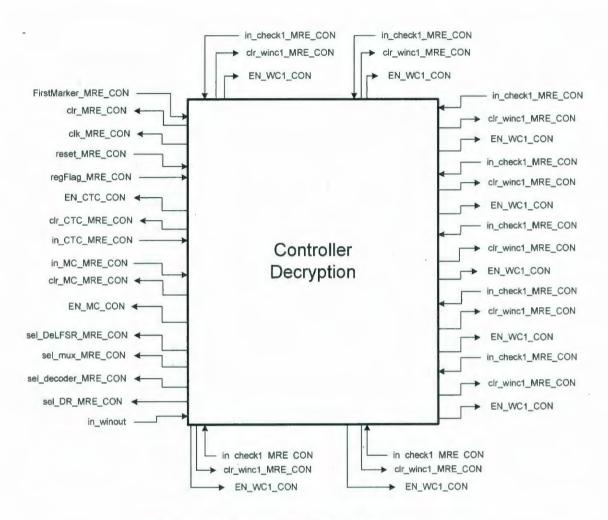

| Figure 5.11. Block diagram of controller of decryption system                     | . 107 |

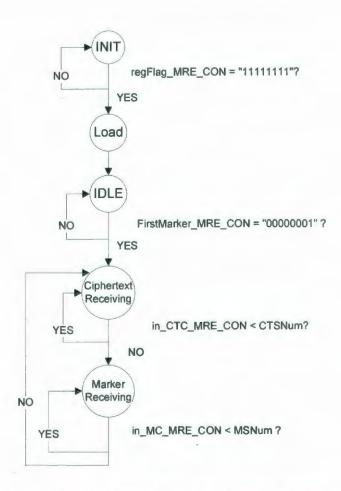

| Figure 5.12. Flow chart of controller of decryption system                        | . 108 |

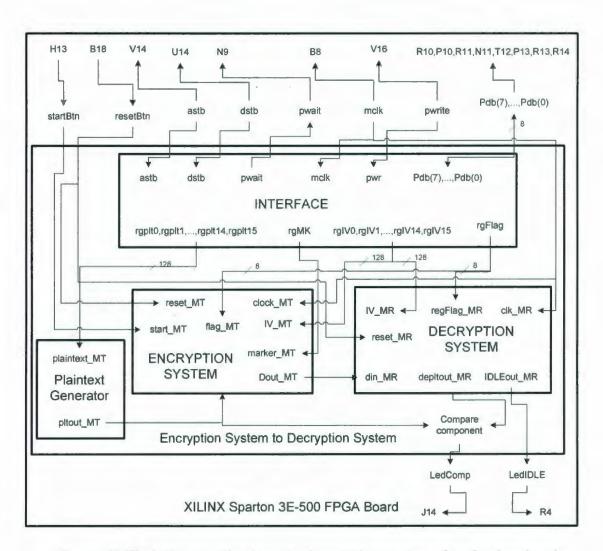

| Figure 5.13. Block diagram of hardware implementation structure of marker-based m | ode   |

|                                                                                   | 110   |

|                                                                                   | . 110 |

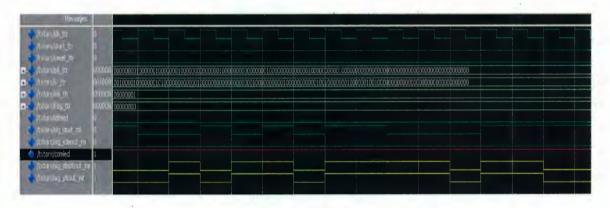

| Figure A1. Simulation result of marker-based stream cipher                  | 129 |

|-----------------------------------------------------------------------------|-----|

| Figure A2. Simulation result of Grain-128 with key1 and IV1                 | 130 |

| Figure A3. Simulation result of Grain-128 with key2 and IV2                 | 130 |

| Figure A4. Simulation result of Grain-128 based SCFB mode with key1 and IV1 | 131 |

| Figure A5. Simulation result of Grain-128 based SCFB mode with key2 and IV2 | 131 |

## List of Abbreviations

SCFB Statistical Cipher Feedback

OFB Output Feedback

CFB Cipher Feedback

OCFB Optimized Cipher Feedback

FPGA Field Programmable Gate Array

DES Data Encryption Standard

AES Advanced Encryption Standard

XOR Exclusive Or

FSR Feedback Shift Register

LFSR Linear Feedback Shift Register

NLFSR Non Linear Feedback Shift Register

SRD Synchronization Recovery Delay

EPF Error Propagation Factor

KSG Key Stream Generator

IV Initialization Vector

CTSNUM Ciphetext Shift Number

MSNUM Marker Shift Number

## **List of Symbols**

the state of the stream cipher for bit i $\sigma_i$ the i-th bit for keystream  $k_i$ the *i*-th bit for plaintext  $p_i$ the i-th bit for ciphertext  $C_i$ the next state function fthe function to produce the keystream g the function to produce ciphertext h C(D) the feedback polynomial of LFSR the feedback bit of LFSR  $S_j$ Lthe length of LFSR  $p(x_1, x_2, x_3)$ the combining function of Geffe Generator the feedback polynomial of NLFSR of Grain-128 q(x)m(x)the boolean function of Grain-128  $K_i$ the key of Grain-128 the size of synchronization pattern n the size of OFB block k P(k)the probability of the OFB block size k the expectation of the OFB block size k  $E\{k\}$ Bthe size of block cipher  $E_{k}(\cdot)$ the AES operation  $X_0...X_{B-1}$ the initial IV  $Q_0...Q_{n-1}$ the selected sync pattern  $W_0...W_{n-1}$ the n-bit window  $\alpha$ the size of the IV

## **Abstract**

In this thesis, we investigate two synchronization methods for stream ciphers. The first is statistical cipher feedback (SCFB) mode, which is a recently proposed mode of operation for block ciphers. The other is the marker-based mode, which is the synchronous stream cipher using "marker" to regain synchronization. SCFB mode is a hybrid of OFB mode and CFB mode; hence, it has a high throughput and the capability of self-synchronizing. The marker-based synchronous stream cipher is also able to obtain synchronization under limited circumstances.

In this thesis, SCFB mode and the marker-based mode are both implemented in digital hardware targeting the FPGA technology. The device we have used is the Xilinx Spartan-3E FPGA. Commonly, SCFB mode is implemented by using the block cipher, AES, as the keystream generator; however, in our research, we use the stream cipher, Grain-128, as the keystream generator for SCFB mode implementation. The designed system structure and synthesis results of the two modes are given in this thesis. Throughout our research, VHDL code and Modelsim PE Student Edition 6.5d are used to design and simulate the functionality of our systems. The behavior level description is synthesized by using Xilinx ISE Webpack 10.1 tool and the .bit stream which is used to configure FPGA board is generated. The designed system is run on the Digilent Nexys II FPGA board and tested. To download the .bit stream on to the FPGA board and transfer data between the computer and FPGA, the Digilent Adept Suite tool is used.

Through the FPGA hardware implementation, we obtain that SCFB mode configured for a stream cipher, Grain-128, can run at the speed of 89Mbps on a real FPGA and an efficiency of SCFB mode is 100%. The marker-based mode can reach the speed of 113

Mbps and has an efficiency of 94%. Although the system of marker-based mode is a little faster and has less hardware complexity than SCFB mode, it is limited in its synchronization recovery. In contrast, SCFB mode can regain synchronization for any number of bit slips. Hence, SCFB mode is more suitable for high speed physical layer security.

The performance analysis of SCFB mode and marker-based mode is also provided with respect to characteristics of synchronization recovery delay (SRD) and error propagation factor (EPF). In particular, through the simulation of SRD and EPF versus varying sync patterns, we have found the best sync pattern format for SCFB mode. The best sync patterns are uncorrelated, that is, the shifted version of the sync pattern do not match the bits from the original sync pattern. In our research, we have used the sequence "10000000" as the sync pattern for SCFB mode implementation and as the marker for marker-based synchronous stream cipher implementation.

## Acknowledgements

I would like to give my sincere gratitude to my supervisor, Dr. Howard Heys. During the past two years study, he has given me constant guidance, feedback, and encouragement to my research. He also gave me consistent trust and support to help me with my work and life in a foreign country. His two year's supervision will be the great asset in my future work.

I also want to take this opportunity to thank all the members of Computer Engineering Research Laboratory (CERL) in Memorial University of Newfoundland during the two years.

Thank you for all my friends for the precious friendship and generous support.

Thank you for my parents and my younger brother for their love and continuous encouragement during two years of my Master's study.

I also would like to thank my husband, Hao Chen, for his selfless support, great help and continuous encouragement in the pursing of my Master degree.

## Chapter 1

### Introduction

## 1.1 Introduction to cryptography

Cryptography, in Greek, literally means hidden writing or the art of changing the plain text message [20]. Generally, it consists of encryption and decryption, which are the two complementary processes. The encryption process is to transform the information into unreadable format except for the intended recipient; while the decryption process is to restore the encrypted message [20]. Cryptography was first used by the Egyptians some 4000 years ago. During World War I and World War II, cryptography played a vital role [6]. Nowadays, with the rapid development of information technology and the increasing usage of the Internet, network security has become a big concern; therefore, the study of cryptography is getting more necessary.

Based on the public availability of the key, cryptography algorithms can be classified into two types: asymmetric (or public key) ciphers and symmetric (or conventional or single-key) ciphers [20]. In the asymmetric key ciphers, there is a pair of keys, with one of them for encryption and the other for decryption. These two keys are related to each other; however, it is computationally infeasible to determine the decryption key given the only knowledge of encryption algorithm and encryption key. One of the most famous public key ciphers is RSA, which is widely used in digital signatures and message authentication [20]. In symmetric key cryptography, both the sender and recipient share

the same secret key. This secret key is known to both ends before the transmission starts and it must be securely kept. Usually, the decryption algorithm of the symmetric key cipher is similar to the encryption algorithm.

Symmetric key ciphers can be categorized as block ciphers and stream ciphers [6]. A block cipher performs transformation on blocks of input data and produces blocks of output data; while the stream cipher continuously deals with a single unit of data, typically one bit or one byte at a time. The typical block size for block ciphers is 64 or 128 bits, and the examples of modern block ciphers are DES (Data Encryption Standard) and AES (Advanced Encryption Standard) [18]. One interesting characteristic of block ciphers is that some modes of operation can perform as stream ciphers, such as output feedback (OFB) mode and cipher feedback (CFB) mode. Block ciphers are often applied to those applications which operate on blocks of data, such as file transfer, e-mail, and databases. On the other hand, stream ciphers are more appropriate for data communication channels or a browser/Web link, which requires encryption and decryption of a stream of data [6].

The stream cipher is very similar to the one-time pad cipher, both using the bitwise exclusive-OR (XOR) operation to combine the plaintext stream and the key stream [16]. In encryption, the plaintext and the keystream sequence are XORed to produce the corresponding ciphertext; while in decryption, the ciphertext stream and the same keystream sequence will be XORed to restore the original plaintext stream. The difference between the two ciphers is that a one-time pad cipher uses a genuine random number sequence for the keystream, whereas the stream cipher uses a pseudorandom number sequence for the keystream. In particular, the one-time pad cipher requires a key

length as long as the plaintext length, thus resulting in a huge problem of key management. However, the stream cipher uses a pseudorandom generator to produce the keystream and will require a much smaller secret key compared with that of the one-time pad cipher. Stream ciphers can be categorized as synchronous stream ciphers and self-synchronizing stream ciphers. Although the security of stream ciphers is not as well understood as block ciphers, stream ciphers are typically faster and more compact than block ciphers, particularly in hardware implementations. It is conjectured that with a properly designed pseudorandom generator, a stream cipher can be as secure as block cipher of comparable key length [19].

## 1.2 Objective of this Thesis

Many synchronous stream ciphers have recently been proposed in forums, such as the ESTREAM stream cipher project [7]. However, the number of self-synchronizing stream ciphers is small, and not many of them have been fully analyzed. Therefore, the self-synchronizing stream cipher still has great research potential. The main objective of this thesis is to analyze and implement two synchronization methods for stream ciphers. One of them is the self-synchronizing stream cipher mode referred to as statistical cipher feedback (SCFB) mode, which is a recently proposed mode of operation for block ciphers. The other is a self-synchronizing method for synchronous stream ciphers, referred to as the marker-based mode. These two modes will be implemented in FPGA based hardware.

The purpose for hardware implementation is to study the implementation issues and determine complexity and speed of the two modes for a real implementation. The reason for FPGA implementation is that FPGAs are common target technology and only a

simple FPGA will be required. Therefore, in this thesis, the two designed systems will finally be implemented on the targeted Xilinx Spartan-3E FPGA, utilizing the Digilent Nexys II development board.

However, first of all, we will examine the characteristics of SCFB mode, such as synchronization recovery delay (SRD) and error propagation factor (EPF). We will simulate the SCFB mode, which is configured for block cipher AES, through C code and gain the simulation results of SRD and EPF in terms of different sync pattern format in the same length as well as varying length. The purpose of these simulations is to find out the preferable sync patterns for SCFB mode.

The original proposal for SCFB mode uses the block cipher, AES, as the keystream generator. However, in this thesis, SCFB mode will be configured by the stream cipher, Grain-128, as the keystream generator. This will be the second part of our research topic. We will simulate this new approach and analyze the same characteristics, SRD and EPF. Moreover, we will implement this mode in digital hardware on a Xilinx Spartan-3E FPGA and test it, as well.

The original proposed hardware implementation of SCFB mode requires two queues to balance the speed of the AES operation and the whole system operation [10]. One of these two queues is the plaintext queue and the other is the ciphertext queue. While bits are being collected in the plaintext queue, bits will be removed from the head of the ciphertext queue at exactly the same rate [10]. This queuing implementation has high hardware complexity. In this thesis, we will implement the SCFB mode by using the stream cipher, Grain-128, as the keystream generator. Since there is no need of queues in this implementation, the hardware complexity is greatly reduced.

In the third part, we will discuss a newly designed self-synchronizing approach for synchronous stream ciphers, which is referred to as marker-based mode. This mode works by inserting an 8-bit marker every 128 bits ciphertext into the data leaving the transmitter. At the receiver, the incoming data is checked to see whether the marker is in the expected position in the data stream. If this 8-bit marker appears at the right position in every 136-bit data sequence, then both ends have maintained synchronization; otherwise, the synchronization is lost. Once the synchronization is lost, the receiver will be responsible for looking for the marker around the expected position, and adjust its synchronization to the new marker position. We will investigate the same characteristics, SRD and EPF of this marker-based synchronous stream cipher, and also implement this system on the Xilinx Spartan-3E FPGA.

In conclusion, this thesis will analyze and implement the self-synchronizing stream cipher based on SCFB mode and the synchronous stream cipher using a marker for synchronization. The characteristics, such as SRD and EPF, of these two modes will be simulated and analyzed; as well, these two systems will be implemented on the targeted Xilinx Spartan-3E FPGA and tested.

#### 1.3 Outline of this Thesis

The aim of this thesis is to analyze and perform FPGA hardware implementation of a self-synchronizing stream cipher based on SCFB mode and the marker-based synchronizing mode. There will be 6 chapters in total.

Chapter 2 will give the background knowledge. The main subject of this chapter will be stream ciphers. The topics will include the classification of stream ciphers, stream cipher design components, the self-synchronizing modes of operation, and the characteristics of stream ciphers. As well, it will introduce FPGA implementation tools. Among these topics, the modes of operation will be mainly discussed. It will consist of OFB mode, CFB mode, SCFB mode, Optimized Cipher Feedback (OCFB) mode, and the marker-based mode.

In Chapter 3, the characteristics of SCFB mode, which uses the block cipher, AES, as the keystream generator, will be discussed. This will include analyzing SRD and EPF versus different sync patterns with the same length and varying lengths. The purpose of this chapter is to find out the best sync pattern for this implementation approach of SCFB mode.

Chapter 4 will present the design structure of SCFB mode using the stream cipher, Grain-128, as the keystream generator. Moreover, this chapter will describe FPGA implementation details of this system, as well as the system testing process. As well, it will analyze SRD and EPF versus the sync pattern format "10000000".

Chapter 5 will be very similar to Chapter 4, except for the study object being the newly designed marker-based mode. It will also give the design details and FPGA implementation process of the marker-based mode. In addition, the analysis of characteristics of this mode, like SRD, will be covered.

Chapter 6 will draw a final conclusion of this thesis and provide directions for future work.

## Chapter 2

## Background

In this chapter, the background material for this thesis will be provided. The main subject will be stream ciphers. The topics of stream cipher will include the classification of stream ciphers, stream cipher design components, block cipher modes of operation, and the characteristics of stream ciphers. As well, FPGA implementation tools will be introduced. Among these topics, the block cipher modes of operation will be mainly discussed. It will consist of OFB mode, CFB mode, SCFB mode, and Optimized Cipher Feedback (OCFB) mode.

## 2.1 Classification of Stream Ciphers

Stream ciphers have memory to store the cipher state. Therefore, designers must consider the following two aspects when designing a stream cipher: how to describe the next state in terms of current state and how to express the ciphertext in terms of the state and the plaintext. The second concern is easy to solve because commonly stream ciphers use the XOR operation on the keystream and the plaintext to produce the ciphertext [14]. However, for the first issue, it is hard to choose the next state expression. Based on the next state function, stream ciphers may be divided into the categories of synchronous stream ciphers and self-synchronizing stream ciphers.

In a synchronous stream cipher, the keystream depends only on the key and the current state, but is independent of both plaintext and ciphertext. Such a stream cipher has no error propagation because one ciphertext bit modification does not affect the decryption of other ciphertext bits. However, the sender and the receiver must be synchronized in order to maintain the correct restoration of the plaintext. If one bit of ciphertext is lost, inserted, or deleted during the transmission, decryption will fail for the subsequent bits, and the system has to be resynchronized. Re-synchronization can be achieved by either periodically sending initialization vectors from transmitter to receiver through extra channel or including "marker positions" in the transmission and correct decryption of ciphertext will be reestablished after one of the marker positions is determined [17]. This is referred to as the marker-based stream cipher mode and will be fully discussed in Chapter 5.

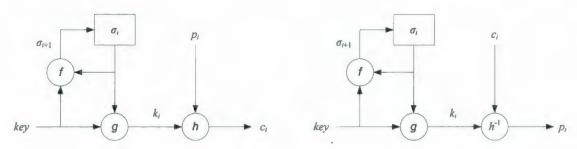

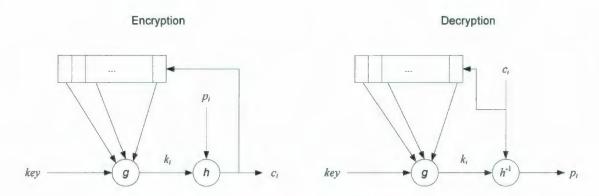

The encryption process of synchronous stream cipher can be defined as follows [16]:

$$\sigma_{i+1} = f(\sigma_i, key),$$

$k_i = g(\sigma_i, key),$  and

$c_i = h(k_i, p_i).$

Here,  $\sigma_i$  represents the state of the stream cipher for bit i with  $\sigma_0$  being the initial state of the stream cipher, and  $k_i$ ,  $p_i$ ,  $c_i$  represents the i-th bit for keystream, plaintext, and ciphertext, respectively. Function f is the next state function, g is the function to produce the keystream, and the ciphertext is produced by the function h. The encryption and decryption process for a synchronous stream ciphers is shown in Figure 2.1.

Figure 2.1. General mode of a synchronous stream cipher

On the other hand, the keystream of a self-synchronizing stream cipher depends on the key and a fixed amount of the previous ciphertext [17]. Therefore, the self-synchronizing stream cipher can resume correct decryption if the keystream generated by the decryption unit is not synchronized with the encryption keystream [17]. But unlike the synchronous stream cipher which has no error propagation, the self-synchronizing stream cipher has significant error propagation. Suppose that the next state depends on *t* previous ciphertext bits. If a single ciphertext bit is lost, inserted, deleted, or modified, the decryption of the following *t* ciphertext bits will be affected until the receiver side is resynchronized with the sender.

The encryption function of the self-synchronizing stream cipher can be described by the following equations [16]:

$$\sigma_i = (c_{i-t}, c_{i-t+1}, ..., c_{i-1}),$$

$$k_i = g(\sigma_i, key), \text{ and }$$

$$c_i = h(k_i, p_i).$$

Here,  $\sigma_i$  represents the state of the stream cipher for bit i with  $\sigma_0 = (c_{-t}, c_{-t+1}, ..., c_{-1})$  being the initial state, g is the function to produce the keystream, and h is the output

function which is used to produce the ciphertext. The encryption and decryption of selfsynchronizing stream ciphers can be shown in Figure 2.2.

Figure 2.2. General mode of a self-synchronizing stream cipher

## 2.2 Stream Cipher Structures

In this section, we will describe the feedback shift register (FSR), which is the common building block for stream ciphers. FSRs can be divided into LFSRs (linear feedback shift registers) and NLFSRs (nonlinear feedback shift registers). Moreover, we will introduce the stream cipher Grain-128, which will be used to configure SCFB mode in Chapter 4.

## 2.2.1 FSR (Feedback Shift Register)

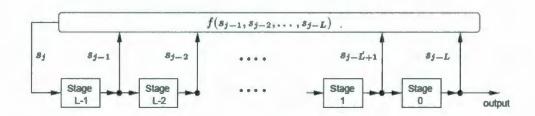

When designing stream ciphers, the main work is to design the keystream generator, which is used to generate the pseudorandom keystream. This requires that the period of the generated keystream to be large, and various sequence patterns of a given length must be uniformly distributed over the keystream as well [17]. There are many approaches to construct the keystream generator; however, the feedback shift register (FSR), in

particular, the linear feedback shift register (LFSR) is a basic building block often used when designing stream ciphers. The structure of a FSR of length L is given in Figure 2.3.

Figure 2.3. Feedback shift register of length L [16]

An FSR consists of L stages numbered from 0 to L-1. Each stage can store one bit and has one input and one output. The FSR is controlled by a clock. At each clock cycle, the content of stage i will be updated by that of the stage i+1 ( $0 \le i < L-1$ ). The content of stage 0, either "0" or "1", will be output to form the parts of the output sequence; the new content of the stage L-1 is the feedback bit  $s_j = f(s_{j-1}, s_{j-2}, ..., s_{j-L})$ , where f is the Boolean function, and  $s_{j-i}$  is the previous content of stage L-i ( $1 \le i \le L$ ) [16]. Based on the Boolean function f, a FSR can be classified as linear feedback shift register (LFSR) or nonlinear feedback shift register (NLFSR). If f is a linear function, then the register will be a LFSR; otherwise, if f is a nonlinear function, it will be a NLFSR.

An LFSR of length L is depicted in Figure 2.4. The feedback polynomial or connection polynomial of this LFSR is  $C(D)=1+c_1D+c_2D^2+...+c_LD^L$  with degree L [16], and the feedback bit can be uniquely determined by the following recursion:  $s_j=(c_1s_{j-1}+c_2s_{j-2}+...+c_Ls_{j-L})$  mod 2 for  $j \geq L$  [16]. In order to generate a keystream with large period, the LFSR must have a primitive feedback polynomial with degree L. The

maximum possible period of the sequence produced by each non-zero state of such an LFSR will be  $2^L - 1$ . Such a sequence is called an *m*-sequence, and the corresponding LFSR is called a maximum-length LFSR [16].

Figure 2.4. Linear feedback shift register of length L [16]

The LFSR is widely used when designing stream ciphers. The reason is that the LFSR can generate sequences with large period and good statistical properties; also, the LFSR is well-suited to hardware implementation. In this thesis, the marker-based synchronous stream cipher will use an LFSR as the keystream generator. This is just for the simplicity of hardware implementation. However, in a practical implementation, for security reasons, an LFSR itself cannot be directly used as the keystream generator because the Berlekamp-Massey algorithm can efficiently compute the feedback polynomial with only 2L successive sequences, and then recover the initial state[19]. Therefore, additional devices should be applied when using LFSRs in keystream generators.

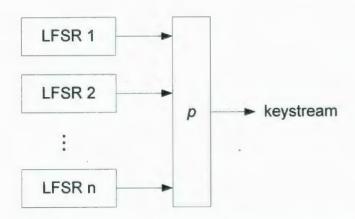

Commonly, three techniques are used to break the linearity of LFSR. First, combine the output sequence of several LFSRs using a nonlinear combining function. Second, use a filter function on the contents of a single LFSR. The last one is to control the clock of one or more LFSRs with the output sequence of another LFSR [16]. Therefore, stream

ciphers based on LFSRs can be classified as nonlinear combination generators, nonlinear filter generators, and clock controlled generators, respectively.

Figure 2.5 shows the normal mode of nonlinear combination generator. The notation p is the nonlinear combining function.

Figure 2.5. Normal mode of nonlinear combination generator

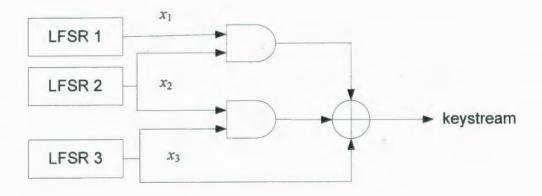

One example of nonlinear combination generators is the Geffe Generator. It is depicted in Figure 2.6. The Geffe Generator is constructed by three LFSRs with length  $L_1$ ,  $L_2$ , and  $L_3$ , respectively. Any two of these lengths are relatively prime. The combining function is as follows:

$$p(x_1, x_2, x_3) = x_1 x_2 \oplus x_2 x_3 \oplus x_3$$

.

The period of the Geffe Generator is  $(2^{L_1} - 1)(2^{L_2} - 1)(2^{L_3} - 1)$ . Although having large period and high linear complexity, the Geffe Generator is cryptographically weak because it can be broken by the correlation attack [16].

Figure 2.6. the Geffe Generator

#### 2.2.2 Grain-128

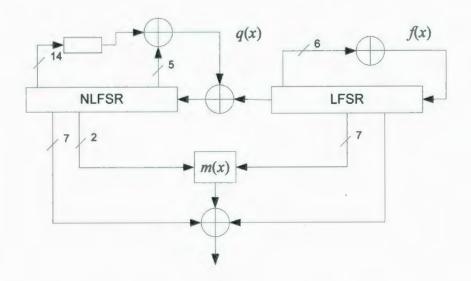

So far, we have discussed the basic building block for many stream ciphers, FSR. In this section, we will present one stream cipher, Grain-128, which targets hardware realization with limited resources in gate count, power consumption, and chip area [12]. In this thesis, the stream cipher Grain-128 will be used as the keystream generator in the SCFB mode implementation in Chapter 4. Grain-128 is a binary additive stream cipher with key size 128 bits and initialization vector (IV) size 96 bits. It consists of three components: an LFSR, an NLFSR, and an output function. The overview of Grain-128 is shown in Figure 2.7.

The content of the LFSR is denoted by  $s_i$ ,  $s_{i+1}$ , ...,  $s_{i+127}$ . The function f(x) is the feedback or connection polynomial of the LFSR, which is primitive with degree 128. It is defined as  $f(x)=1+x^{32}+x^{47}+x^{58}+x^{90}+x^{121}+x^{128}$  [13]. In Figure 2.7, the XOR gate has 2 or more inputs as indicated. Therefore, the corresponding update function or the feedback bit of this LFSR based on the primitive polynomial f(x) can be computed as  $s_{i+128}=s_i+s_{i+7}+s_{i+38}+s_{i+70}+s_{i+81}+s_{i+96}$  [13].

Figure 2.7. An overview of the Grain-128

Similarly, the content of the NLFSR is denoted by  $b_i, b_{i+1}, ..., b_{i+127}$ . The feedback polynomial q(x) is the sum of one linear and one bent function. The small rectangle with 14 inputs in Figure 2.7 represents  $x^{44}x^{60} + x^{61}x^{125} + x^{63}x^{67} + x^{69}x^{101} + x^{80}x^{88} + x^{110}x^{111} + x^{115}x^{117}$ .

It is defined as the following expression [13]:

$$q(x) = 1 + x^{32} + x^{37} + x^{72} + x^{102} + x^{128} + x^{44}x^{60} + x^{61}x^{125} + x^{63}x^{67} + x^{69}x^{101} + x^{80}x^{88} + x^{110}x^{111} + x^{115}x^{117}$$

Therefore, the update function or feedback bit of this NLFSR can be calculated as follows, where the notation  $s_i$  is the output bit of the LFSR [13]:

$$b_{i+128} = s_i + b_i + b_{i+26} + b_{i+56} + b_{i+91} + b_{i+96} + b_{i+3}b_{i+67} + b_{i+11}b_{i+13} + b_{i+17}b_{i+18} + b_{i+27}b_{i+59} + b_{i+40}b_{i+48} + b_{i+61}b_{i+65} + b_{i+68}b_{i+84}$$

The block m(x) is a Boolean function of 9 inputs, where 2 inputs are taken from the NLFSR, and 7 inputs are from the LFSR. This function is of degree 3 and defined as

$m(x) = x_0x_1 + x_2x_3 + x_4x_5 + x_6x_7 + x_0x_4x_8$ , where the variables  $x_0, x_1, x_2, x_3, x_4, x_5, x_6, x_7$  and  $x_8$  represent the state bits  $b_{i+12}$ ,  $s_{i+8}$ ,  $s_{i+13}$ ,  $s_{i+20}$ ,  $b_{i+95}$ ,  $s_{i+42}$ ,  $s_{i+79}$ , and  $s_{i+95}$ , respectively [13]. The keystream out of Grain-128 is computed as

$$k_i = \sum_{j \in A} b_{i+j} + m(x) + s_{i+93}$$

, where  $A = \{2,15,36,45,64,73,89\}$  [13].

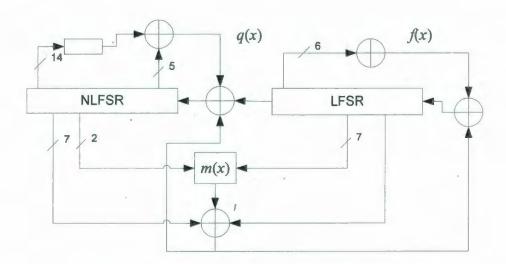

Like most stream ciphers, Grain-128 also needs to be initialized with the key and the IV before outputting any keystream. The initialization mode of Grain-128 is depicted in Figure 2.8. The difference between the initialization mode and the normal operating mode, which is shown in Figure 2.7, is that the output bit in the initialization mode is fed back to update the feedback bit of both NLFSR and LFSR, without outputting any keystream.

Figure 2.8. Initialization mode of stream cipher Grain-128

Let the key bit be denoted by  $K_i$  ( $0 \le i \le 127$ ), and the IV bit be denoted by  $IV_i$  ( $0 \le i \le 95$ ). In the initialization phase, at first, the 128 key bits will be loaded into the NLFSR,  $b_i = K_i$  ( $0 \le i \le 127$ ), and then the IV bits will be loaded into the first 96 states of

the LFSR,  $s_i = IV_i$  ( $0 \le i \le 95$ ). The last 32 states of the LFSR will be filled with ones,  $s_i = 1$  ( $96 \le i \le 127$ ). After the key and IV are loaded, the cipher will be clocked 256 times to mix the key and IV bits into the states of both NLFSR and LFSR.

### 2.3 Block Cipher Modes of Operation

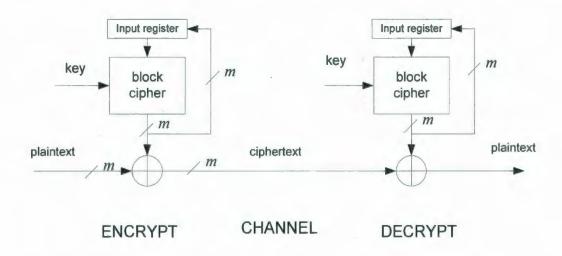

As mentioned before, one of the advantages of block ciphers is that they can perform as stream ciphers using various modes of operation. Block ciphers can be used to generate the keystream in these modes. There are several conventional modes of operation for block ciphers, but in this section, we are going to discuss four stream-oriented transmission application modes: OFB mode, CFB mode, SCFB mode, and OCFB mode. In the discussion, the notation B represents the block cipher size in bits: B = 64 for DES, and B = 128 for AES.

## 2.3.1 Output Feedback (OFB) Mode

In OFB mode, the block cipher output is not only used as the keystream to XOR the plaintext to produce the ciphertext, but also fed back to an input shift register of the system to generate the next data block. The general implementation structure of OFB mode is illustrated in Figure 2.9. Here, m could be any number from 1 to B. But to achieve high efficiency requirement, m will be equal to B. In this case, the whole output data block in every block cipher operation will be XORed with the plaintext block, and also fed back to the input register at the same time. Since the keystream of OFB mode is independent of the ciphertext, it falls into the category of synchronous stream cipher.

Figure 2.9. Structure of OFB mode

The primary advantage of OFB mode is that there is no error propagation delay, which means that one bit error in the ciphertext only affects the corresponding plaintext bit on the receiver side. However, once bit slips occur (one or more bits are erased or inserted) in the communication channel, the system will lose synchronization. Resynchronization can be achieved by periodically sending an initialization vector (IV) through the signaling channel from the transmitter to the receiver. This approach will result in extra messaging overhead and associated delays while synchronizing. Hence, the rate of sending IVs is critical. If they are sent frequently, the resulting overhead will greatly increase; but if they are sent too infrequently, the system will lose synchronization for a long period time [10].

In conclusion, OFB mode has high implementation efficiency and no error propagation delay, but does not have the ability of self-synchronizing. Typically, OFB mode is applied to the stream-oriented transmission over noisy channel (e.g. satellite communication) [6].

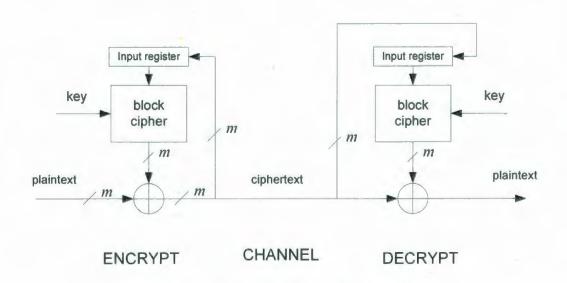

### 2.3.2 Cipher Feedback (CFB) Mode

The structure of CFB mode is very similar to that of OFB mode, except the bits that are fed back to the input register to produce the next data block come from the preceding ciphertext. The general structure of CFB mode is shown in Figure 2.10. From the figure, we can see that in each block cipher operation, m bits  $(1 \le m \le B)$  out of the B bits of block cipher output are selected to XOR with the plaintext to produce the corresponding ciphertext bits. Meanwhile, these m ciphertext bits are fed back to the input register to produce the next block cipher output.

Figure 2.10. Structure of CFB mode

Since the keystream depends on the ciphertext bits, CFB mode is capable of self-synchronizing. When a bit slip occurs, the system can regain synchronization once the affected bits are shifted out of the input register. In the typical application, m is equal to 1 to ensure that a loss or insertion of any number of bits can lead to resynchronization. That is to say, the slip event will eventually be shifted out of the input register at the receiver

side after B clock cycles. At this moment, both input registers at the transmitter and receiver sides are holding the same B ciphertext bits which are the following bits after the slip event; therefore, the system will be resynchronized.

The disadvantage of CFB mode is that a bit error in the ciphertext will not only affect the corresponding plaintext bit, but also results in corruption of the following B plaintext bits at the receiver side. Moreover, CFB mode is far less efficient than OFB mode. That is, one block of data from the block cipher only produces m bits of ciphertext, where m = 1 is commonly used to ensure recover from any number of lost or inserted bits [10].

In conclusion, CFB mode offers a huge benefit of self-synchronizing, but also has large error propagation and low efficiency.

### 2.3.3 Statistical Cipher Feedback (SCFB) Mode

In the last two sections, we have discussed two important block cipher modes of operation: OFB mode and CFB mode. Each mode has its own advantages and disadvantages. In this section, we are going to present another self-synchronizing mode of operation, which we refer to as statistical cipher feedback (SCFB) mode. SCFB mode is a hybrid of OFB mode and CFB mode; therefore, it has the advantage of self-synchronizing and disadvantage of significant error propagation [15]. However, SCFB mode has the major advantage of being highly efficient for hardware implementations.

The concept of SCFB mode is that initially it will work in OFB mode and scan the ciphertext bits. Once a certain data sequence, referred to as the sync pattern, is recognized, the cipher will switch to CFB mode, and the scan function will be turned off. During CFB mode, the following B ciphertext bits will be collected as the new IV, and then fed back

to the input register to re-initialize OFB mode. After this, the cipher will work in OFB mode again.

The general implementation structure of SCFB mode is given in Figure 2.11. From the figure, we can see that both the transmitter and receiver work in OFB mode initially. In this mode, each ciphertext bit goes into the n-bit scan window ( $4 \le n \le 12$  is proposed [10]). This window will regularly be compared to the previously selected n-bit sync pattern. If the content of the window matches the sync pattern, both the transmitter and the receiver will stop scanning and start to collect the following B ciphertext bits. Now the cipher is working in CFB mode. After the collection of the new IV is complete, it will be loaded into the input shift register and then the cipher will work in OFB mode. Since both sides have collected the same ciphertext bits as new IV, the following data out of the block cipher will be the same, thus the system has been resynchronized. This indicates that SCFB mode is capable of self-synchronizing.

Figure 2.11. Structure of SCFB mode

One of the important points of SCFB mode is that during the new IV collection, the ciphertext scanning function is suspended. That is to say, any bit patterns in the new IV which matches the sync pattern will be ignored.

Since SCFB mode works either in OFB mode or in CFB mode, the ciphertext bits of . SCFB mode can be categorized into three regions: the n-bit sync pattern, the B-bit IV, and the k-bit OFB block. The structure of this categorization is shown in Figure 2.12.

Figure 2.12. Synchronization cycle of SCFB mode

From the figure, we can see that the IV starts from the first bit following the sync pattern and lasts for B bits; the OFB block starts from the first bit following the IV, and ends at the first bit of the next sync pattern. Hence, the variable k is a random variable dependent on the location of the sync pattern appearing in the ciphertext. These three regions together form one synchronization cycle. That means one synchronization cycle consists of n + B + k bits. If an individual bit error occurs in the OFB block, then it will only affect the corresponding bit on the receiver side. However, if a bit error occurs in the sync pattern region, the correct sync pattern will be missed at the receiver side and if a bit error occurs in the IV region, an incorrect IV will be used at the receiver. In those two cases, the synchronization of the system will be lost until the next correct sync pattern is recognized. Thus many bits at the receiver side would possibly be corrupted because of

only one bit error in the communication channel. As a result, the error propagation characteristic of SCFB mode is much worse than that of OFB mode.

In conclusion, SCFB mixes OFB mode and CFB mode. It not only benefits from the capability of self-synchronizing, but also has high efficiency for hardware implementations.

## 2.3.4 Optimized Cipher Feedback (OCFB) Mode

Optimized cipher feedback (OCFB) mode is another self-synchronizing mode of operation. Since it works very similar to SCFB mode, we will not give details in this thesis. The description of OCFB mode can be found in [1] and the hardware implementation of OCFB mode can be found in [21]. It is much more efficient than CFB mode since it almost uses the whole block cipher output as the keystream.

### 2.4 Marker-based Mode

In Section 2.3, we have introduced four important block cipher modes of operation: OFB mode, CFB mode, SCFB mode, and OCFB mode. Except for OFB mode, these modes are all capable of self-synchronizing. For a synchronous stream cipher, another approach to regain synchronization is to include markers in the transmitted data; correct decryption of ciphertext will be established by synchronizing decryption based on the marker observed in the received data. This is referred to as the marker-based mode.

The concept of this mode is to add an *n*-bit marker preceding every *B* bits of ciphertext during the transmission. In the implementation, every 128 bits of ciphertext following an

8-bit marker will be sent out as the transmission ciphertext data block. At the receiver side, the incoming data sequence will be continuously scanned to determine the marker position. Once the marker is successfully recognized, the receiver will decrypt the ciphertext as the following 128 bits because it assumes that the bits following the marker position would be the ciphertext. However, when synchronization is lost due to bit slips in the communication channel, the receiver will not detect the marker in the expected position. In this case, it will search the area which is around the expected position, trying to find out the marker. If we assume that a limited number of bits can be lost or inserted, the marker will eventually be detected near the expected position. Hence, the new marker position will be adjusted and the receiver will be synchronized with the transmitter again. The detailed explanation and the hardware implementation of marker-based synchronous stream cipher mode will be given in Chapter 5.

## 2.5 Characteristics of SCFB Mode

SCFB mode has been discussed in Section 2.3.3. As mentioned, it is a hybrid of OFB mode and CFB mode, thus benefiting from high efficiency and self-synchronization. However, due to this mixed working modes, the bit slip and bit error effects of such mode are much more complex than that of OFB mode and CFB mode. In this section, we will review three characteristics of SCFB mode: OFB block size, synchronization recovery delay (SRD), and error propagation factor (EPF).

#### 2.5.1 OFB Block Size

From Figure 2.12, we can see that the OFB block is between the new IV and the next sync pattern. Its size k depends on the position where the next sync pattern will appear. The sync pattern is always scanned for in OFB operating mode. Basically, each n-bit ciphertext sequence is taken to compare with the selected sync pattern. Once it matches, the OFB block will end; however, it will not include the recognized sync pattern.

Because the keystream generator, AES, can produce a highly random data sequence, we assume that each ciphertext bit is equally likely to be "0" or "1", and each bit is independent. Assuming that the k-th n-bit sequence sample will match the sync pattern, the variable k will follow the geometric distribution if each n-bit sample is independent. Therefore, the probability of variable k is  $P(k)=(1-1/2^n)^k\cdot 1/2^n$ , the expected value of k is given by  $E\{k\}=2^n-1$ , and the second moment of k is given by  $E\{k\}=2^{2n+1}-3\cdot 2^n+1$  [10].

However, the *n*-bit sample of ciphertext is essentially sliding along a window, and this window will be compared to the sync pattern. Because there is an n-1 bit overlap of windows, the *n*-bit ciphertext sample windows are not independent of each other. Therefore, the OFB block size k does not exactly follow the geometric distribution; in particular, it is found that the distribution of the variable k is actually dependent on the sync pattern itself. In [10], the OFB block size k for sync pattern "100...00" and "111...11" is fully discussed. The probability of variable k for the sync pattern "100...00" is given as follows [10]:

$$P_a(k) = \begin{cases} \left[1 - \sum_{i=0}^{k-n} P_a(i)\right] \cdot \frac{1}{2^n}, k > 0 \\ \frac{1}{2^n}, k = 0 \\ 0, k < 0 \end{cases}$$

So the expected value of k based on this probability distribution can be computed as  $E\{k\} = 2^n - n$ , which is slightly different from the geometric distribution.

Also, for sync pattern "111...11", the probability distribution of variable k can be shown to be [10]:

$$P_b(k) = \begin{cases} \left[ 1 - \sum_{i=0}^{k-n-1} P_b(i) \right] \cdot \frac{1}{2^{n+1}}, k > 0 \\ \frac{1}{2^n}, k = 0 \\ 0, k < 0 \end{cases}$$

Therefore, the expected value of variable k is computed as  $E_b\{k\} = 2 \cdot (2^n - 1) - n$ , which has a significant difference from the geometric distribution.

## 2.5.2 Resynchronization

SCFB mode is capable of self-synchronizing. Once the sync pattern is recognized, the next ciphertext bits will be collected as the new IV. Since both the transmitter and the receiver are scanning for the sync pattern, synchronization will be regained. This is the ideal case where there is no slip or error occurrence in the ciphertext. However, in reality, the communication channel may be either slip prone or error prone and the synchronization may be delayed in these cases. Therefore, synchronization recovery delay (SRD) is used to characterize the re-synchronization properties of stream ciphers.

SRD is defined as the expected number of bits following a sync loss due to a slip before the synchronization is regained [10]. It is assumed that SRD starts from the termination of the slip event, thus it will not include the lost or inserted bits themselves.

So it is unnecessary to know how many bits will be lost or inserted in the communication channel. In order to minimize the corruption of data due to a sync lost condition, the synchronization of stream ciphers must be regained as quickly as possible [10]. That is, the smaller the SRD is, the better the re-synchronization properties will be.

In SCFB mode, SRD represents the number of bits following the slip until the next sync pattern is properly detected and the new IV is correctly collected. Because the occurrence of a single bit slip may possibly result in a false synchronization, the SRD has a lower bound and upper bound, which are fully explained in [10]. In [10], it is assumed that a slip will randomly occur and there are no other slips occurring in the synchronization cycle in which the slip terminates. Based on this assumption, the lower bound of SRD lies in the case that the receiver resynchronizes at the next sync pattern, i.e., at the end of the next IV. If the slip occurs at the average position within the synchronization cycle, the re-synchronization will take (n+B+k)/2 plus the n+B bits required at the beginning of the next cycle [10]. In [10], it is shown that for large n, the lower bound of the SRD is approximated by  $2^n$ .

However, in reality, a false synchronization is possible to occur due to a slip, thus resulting in longer delays in the re-synchronization process. This can happen in the case that slip occurs in the OFB block that results in a false sync pattern. If this false sync pattern is detected, the actual sync pattern might be ignored and collected as part of the false IV. Moreover, if the slip occurs in the sync/IV region, the sync pattern will be missed, thus the actual IV is mistakenly scanned for sync pattern. If it does contain the sync pattern, the receiver will detect it and collect the incorrect IV [10]. In those cases, the synchronization will be lost until the next sync pattern is properly detected. But if the

OFB block size k exceeds n + B, the synchronization must be regained since the OFB block will be at the end of the false IV. Then the next valid sync pattern will be properly detected. The upper bound of SRD is derived in [10] based on the probability that a synchronization cycle has  $k \ge n + B$ .

In reality, for small n, the re-synchronization is achieved very quickly since it is possible that the end of a false IV lies close to the end of the actual IV. In this case, it is likely that there is no sync pattern being detected before the OFB block starts. Hence, for small n, the upper bound of SRD is very loose. But for large n, the upper limit gets very tight and can reach  $2^n$  [10].

### 2.5.3 Error Propagation

Error propagation is also a very important characteristic for stream ciphers. For example, OFB mode does not have error propagation because a single bit error in the channel only affects the corresponding position of the decrypted plaintext at the receiver. However, in CFB mode, the effect of an individual bit error in the ciphertext is magnified at the receiver. That is, CFB mode has significant error propagation since the ciphertext bits will not only be used to restore the plaintext, but also serve as the input to the block cipher.

Error propagation is characterized by the error propagation factor (EPF), which is defined as the bit error rate at the output of the decryption divided by the probability of a bit error in the communication channel [10]. It is assumed that bit errors occur randomly and independently in the communication channel [10].

In Section 2.3.3, we have discussed the synchronization cycle of SCFB mode, which is shown in Figure 2.12. Based on the different regions of this cycle, where bit error could occur, five error scenarios are discussed in [10]. In this section, we will briefly introduce these five cases. In case 1, the error occurs in the n + B bits of sync/IV block, and then the sync will be lost in the entire cycle; therefore, half of the bits of the OFB block and the next sync/IV bits will be expected to be wrong. In case 2, the error occurs in the OFB block, but without generating any false sync pattern and then a single bit error will only result in one bit error at the output of the receiver. In cases 3 and 4, an error occurs in the OFB block and generates a false sync pattern. If the false sync pattern appears in the first k - (n + B) bits, then i/2 bits will be expected to have errors, where i represents the bits from the end of the false IV to the end of the actual IV. This is the case 3. In case 4, the false sync pattern appears in the last n + B bits of the OFB block and then the next sync pattern will be missed since it will be collected as part of the false IV. In this case, half of the bits will be in error until the next sync pattern is properly detected. The case 5 describes that errors occur while the sync has already been lost. It is assumed that the errors and slips occur infrequently enough that an error occurs in isolation, so the case 5 is ignored.

Moreover, it is given in [10] that the probability that a bit error results in a false sync pattern is less than  $n/(2^n-1)$ . So for small n, case 3 and case 4 becomes much more likely. But as n increases, this probability decreases dramatically; so case 1 and case 2 become more significant. For large n, most ciphertext bits will fall into the OFB block due to its larger size. Hence, case 2 is more likely than case 1. However, the number of the decrypted bit errors at the output in case 1 is much bigger than in case 2, thus resulting in

larger EPF. Therefore, for large n, case 1 is still the main scenario to determine the error propagation factor [10].

From the analysis of those 5 cases, the lower bound and upper bound of EPF for SCFB mode is shown in [10]. The lower bound is given by EPF > (n+B)/2. Since the upper bound is complex, we are not going to discuss it in detail in this thesis, but all can be found in [10]. Moreover, it is shown that as n gets larger, the upper bound of EPF approaches n + B/2 + 1.

## 2.5.4 Comparison with Other Modes

In Table 2.1, we summarize the resynchronization and error propagation characteristics of OFB mode, CFB mode, and SCFB mode.

| Resynchronization Delay (SRD)        | Error Propagation (EPF)                           |

|--------------------------------------|---------------------------------------------------|

| SRD = ∞                              | EPF = 1                                           |

| SRD = B                              | EPF = 1 + B/2                                     |

| SRD $\approx 2^n$ for large $n$ [10] | (n + B)/2 < EPF < n + B/2 + 1 [10] for larger $n$ |

|                                      | $SRD = \infty$ $SRD = B$                          |

Table 2.1. Summarize of SRD and EPF for OFB, CFB, and SCFB mode

In conclusion, the characteristics of SCFB mode have been discussed in this section.

Those included the re-synchronization property SRD and the error propagation EPF.

Moreover, these two metrics can also be applied to other stream ciphers which are able to resynchronize. As well, the OFB block size of SCFB mode was discussed.

# 2.6 Digital Hardware Implementation Tools

In this thesis, the characteristics of SCFB mode and the marker-based mode will be analyzed. Moreover, as mentioned before, in order to study the implementation issues and determine the complexity and speed of these two systems at a real implementation, the two modes will also be implemented in digital hardware. Since commonly, FPGAs are target technology and Digilent board is available for the device, these two modes will be implemented using an FPGA. In this section, we will briefly introduce the implementation tools.

## 2.6.1 FPGA Implementation

In this thesis, SCFB mode with stream cipher as the keystream generator and the marker-based synchronous stream cipher have both been realized through FPGA hardware implementation. Specifically, the target device is the Xilinx Spartan-3E, and the Digilent Nexys II board is used as a development platform. During this implementation process, three CAD tools were used. They are Modelsim PE Student Edition 6.5, Xilinx ISE Design Suite 10.1, and Digilent Adept Suite.

Modelsim was mainly used to functionally simulate the VHDL code of the designed system. Through analyzing the obtained simulation results, the system was verified to be functionally working. The behavior level VHDL code, which was simulated by

Modelsim, was synthesized by Xilinx ISE Project Navigator. This process includes synthesis, implementation, and generation of the bitstream. The implementation process consists of translate, map and place&route.

The synthesis process will convert VHDL or Verilog code into a gate-level netlist, i.e. a complete circuit with logical elements (gates, flip flops etc) for the design. The synthesis process will check code syntax and analyze the hierarchy of the design which ensures that the design is optimized for the design architecture. By default, the Xilinx ISE uses built-in synthesizer XST (Xilinx Synthesis Technology). Other synthesizers can also be used. XST output is stored in NGC (Native Generic Circuit) format [9].

The translate process merges all of the input netlists and design constraints and outputs a Xilinx NGD (Native Generic Database) file, which describes the logical design. This can be done by using NGD Build program. The design constraints include the assignment of the ports in the design to the physical elements (pins, switches, buttons) of the targeted device and the specified timing requirements of the design. This information is stored in a file named UCF (User Constraints File). Tools used to create or modify the UCF are PACE, Constraint Editor, and so on [9].

The map process divides the whole circuit with logical elements into sub blocks such that they can be fitted into the FPGA logic blocks. That is, the map process fits the logic defined by the NGD file into the targeted FPGA elements (Configurable Logic Blocks (CLB), Input Output Blocks (IOB)) and generates an NCD (Native Circuit Description) file which physically represents the design mapped to the components of FPGA. This can be done by using the MAP program [9].

The place&route process is done by using PAR program. This process places the sub blocks from the map process into logic blocks according to the constraints and connects the logic blocks. By taking all the constraints into account, the PAR tool takes the mapped NCD file as input and produces a completely routed NCD file as output, which consists of the routing information of the design [9].

After the synthesis and implementation process, the design must be downloaded on the FPGA. Therefore, the routed NCD file is given to the BITGEN program to generate a bit stream (a .BIT file) which is the acceptable format for the FPGA. This .BIT file will finally be used to configure the target FPGA device.

The Digilent Adept Suite was used to configure the FPGA board. It consists of four tools: Export, Transport, Ethernet Administrator, and USB Administrator [3]. In this research, only the first two of them have been used. The Export tool is used to load the bitstream onto the FPGA board and the Transport sends the data to the system on the FPGA board [3]. However, in order to use the Transport to send and collect data to and from the FPGA board, the designed system requires an interface, which will be responsible for writing and reading registers. This interface can also be described by VHDL code, and should be loaded onto the board, as well. The detailed information about the design of this interface can be found in [4] [5].

The FPGA device used in this thesis is the Xilinx Spartan-3E kit. It contains sufficient resources to study the implementation of our systems. A picture of the Digilent Nexys II FPGA board is given in Figure 2.13. This board is powered by the USB2 interface which is also used to transfer data between the board and the computer. In order to test the

designed system, the LEDs are used to indicate the testing results; as well, buttons are used to reset the system.

Figure 2.13. Picture of Digilent Nexys II board

# 2.6.2 Software Implementation

In this thesis, SCFB mode and the marker-based mode have been implemented in software. The characteristics of re-synchronization and error propagation are simulated by Microsoft Visual C++ 2008 Express Edition. As well, MATLAB 7.0.4 has been used to plot all the simulation data.

#### 2.7 Conclusion

In this chapter, we have discussed the fundamentals of stream ciphers, including the classification, the cipher structure, and the block cipher modes giving stream cipher operation. Stream ciphers are categorized as synchronous stream ciphers and selfsynchronizing stream ciphers. Synchronous stream ciphers have no error propagation, but require an extra signaling channel when re-synchronizing. Self-synchronizing stream ciphers are capable of self-synchronizing, but with significant error propagation. The main design component of stream cipher studied in this thesis are the linear feedback shift register (LFSR) and nonlinear feedback shift register (NLFSR). As well, the stream cipher Grain-128 was described, since it will be used as the keystream generator in Chapter 4. The main subject of this chapter was to talk about the block cipher modes of operation relevant to stream processing, which included output feedback mode (OFB), cipher feedback mode (CFB), statistical cipher feedback mode (SCFB), and optimized cipher feedback (OCFB) mode. In particular, the characteristics of SCFB mode, synchronization recovery delay (SRD), error propagation factor (EPF), and OFB block size, were fully explained. Moreover, the marker-based synchronous stream cipher mode was also introduced. In the end, the FPGA implementation CAD tools and software implementation tools were briefly discussed.

# **Chapter 3**

# Analysis of Characteristics of AES-based SCFB mode

In [10], the characteristics of SCFB mode, which uses block cipher, AES, as the keystream generator, are theoretically analyzed. In particular, the characteristics under the sync pattern formats "100...00" and "111...11" are explained in detail. It is clear that the characteristics of SCFB mode are affected by the sync pattern format.

In order to determine the best sync pattern, which can provide the best performance for SCFB mode, in terms of short re-synchronization delay, and limited error effect, the SRD and EPF of varying sync patterns were simulated using the C programming language. The simulation results will be presented and analyzed in this chapter.

## 3.1 SCFB Pseudocode

In the simulation, SCFB mode uses the block cipher, AES, as the keystream generator and the block size of AES is 128 bits. Since the structure of SCFB mode was discussed in Chapter 2, we will only present the pseudocode of SCFB mode here. The pseudocode describes the encryption operation in the transmitter. It is given in Figure 3.1.

In this pseudo code,  $E_k(\cdot)$  represents the AES operation, and  $X_0...X_{B-1}$  contains the initial IV, which is known to both transmitter and receiver. The notation  $Q_0...Q_{n-1}$  is used

to represent the selected sync pattern, and the notation  $W_0...W_{n-1}$  is the *n*-bit window which is currently compared to the sync pattern. The notation  $Z_0...Z_{B-1}$  is used to collect the new IV. In addition, the two flags loading\_IV and new\_IV indicate that the IV is currently being collected and the collection of IV has just finished, respectively. The C code is based on this pseudocode, but with a slight difference. In the pseudocode, the *n*-bit window is initialized to zero at the beginning of operation, in order to use the sync pattern "100...00"; in the simulation, since we need to use varying sync patterns, we start to compare the window with the sync pattern only after the window has collected *n* ciphertext bits of the OFB block.

```

loading_IV \leftarrow false

X_0 \dots X_{B-1} \leftarrow \text{initial value}

W_0 \dots W_{n-1} \leftarrow 0 \dots 0

i \leftarrow 0

Y_0 \ldots Y_{B-1} \leftarrow E_K(X_0 \ldots X_{B-1})

new_IV \leftarrow false

i \leftarrow 0

do

C_{j+i} \leftarrow P_{j+i} \oplus Y_i

if loading JV then

Z_k \leftarrow C_{l+k}

k \leftarrow k + 1

if k = B then

loading_JV \leftarrow false

new_IV \leftarrow true

X_0 \dots X_{B-1} \leftarrow Z_0 \dots Z_{B-1}

W_0 \dots W_{n-1} \leftarrow 0 \dots 0

W_0 \dots W_{n-2} W_{n-1} \leftarrow W_1 \dots W_{n-1} C_{j+i}

if W_0 \dots W_{n-1} = Q_0 \dots Q_{n-1} then

loading\_IV \leftarrow true

l \leftarrow j + i + 1

k \leftarrow 0

i \leftarrow i + 1

if i = B and not new IV then

X_0 \dots X_{B-1} \leftarrow Y_0 \dots Y_{B-1}

while i < B and not new_{-}IV

j \leftarrow j + i

while true

```

Figure 3.1. SCFB pseudocode [10]

In addition, the simulation was running under the following constraints:

- Simulation length: 10<sup>10</sup> plaintext / ciphertext bits.

- Bit slips occur every 10<sup>5</sup> bits after the effect of the last slip event is over; that is to say, a new slip event is generated at 10<sup>5</sup>-th bit after the synchronization is regained.

- Error events occur every 10<sup>5</sup> bits after the effect of the last error event is over. In order to make sure that the effect of an error is over, the decrypted plaintext at the receiver will be tracked after an error is generated. A counter is set up while tracking. The counter will be incremented when the decrypted plaintext is correct; otherwise, it will be cleared. When the output of the counter reaches the value "100", we can be confident that the effect is over as this indicates that 100 consecutive ciphertext bits have been received error free. Assuming the decrypted plaintext bit is equally likely to be "0" or "1", the probability of a random sequence of 100 bits having no error is 1/2<sup>100</sup> = 7.8886×10<sup>-31</sup>. This means it is highly improbable that corrupted ciphertext bits will result in 100 consecutive expected bits of plaintext.

In the following graphs, the horizontal axis labeled the "sync pattern" is representing the decimal equivalent of the binary representation of the sync pattern with most significant bit as the first bit transmitted in the sync pattern.

# 3.2 Synchronization Recovery Delay

In this section, we are going to present the simulation results of SRD versus varying sync patterns. Figure 3.2 shows the SRD in terms of sync pattern size n ( $4 \le n \le 12$ ) with sync pattern formats "100...00" and "111...11". The lower bound of SRD based on the geometric distribution of k can be obtained by the following expression [10]:

$$SRD > \frac{3}{2}(n+B) + \frac{1}{2\mu}[(n+B)E\{k\} + E\{k^2\}],$$

with

$$E\{k\} = 2^n - 1$$

,  $E\{k^2\} = 2^{2n+1} - 3 \cdot 2^n + 1$ , and  $\mu = n + B + 2^n - 1$  [10].

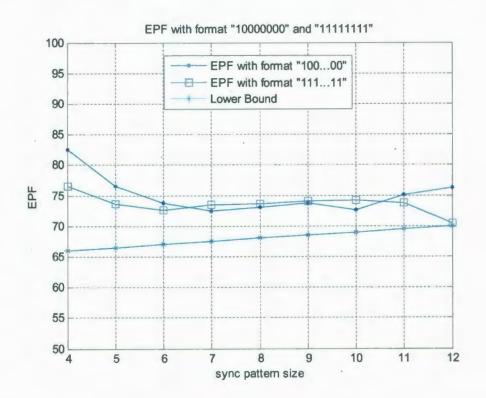

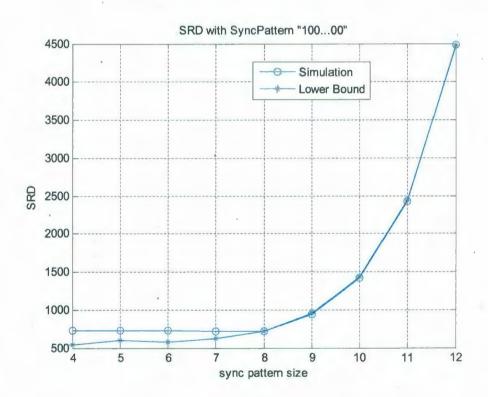

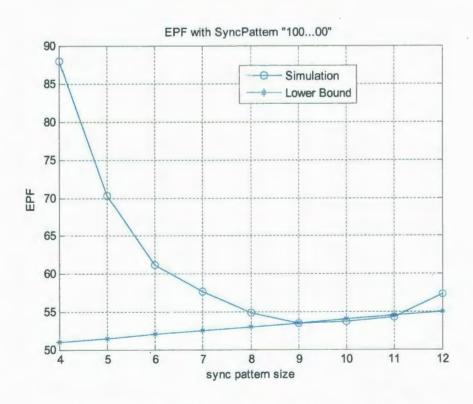

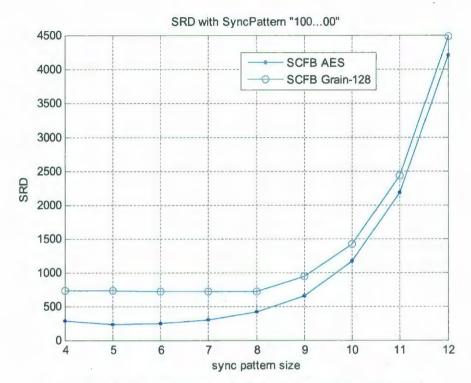

Figure 3.2. SRD versus sync pattern size

From this figure, we can see that as the sync pattern size n gets larger, SRD is also getting larger. Moreover, for larger size n ( $n \ge 8$ ), SRD increases very quickly as n increases. This is because for larger size n, the expected value of OFB block size k is very large, and it grows exponentially. Therefore, it will take much longer delay to regain

synchronization. Also, it is clear that the sync pattern format "100...00" results in smaller SRD than "111...11" for large sync pattern size n (n > 5), especially very large n ( $n \ge 9$ ). This will be explained later in this section. In addition, this figure confirms that the sync pattern format "100...00" is a better candidate than "111...11" with moderate sync pattern size n (n = 8, for example) since it leads to smaller SRD.

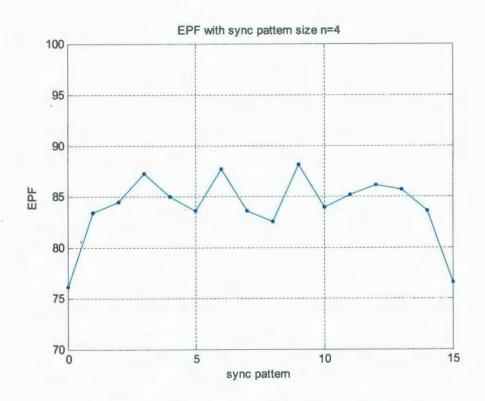

Figure 3.3, Figure 3.4, and Figure 3.5 show the SRD in terms of varying sync patterns with sync pattern size n = 4, 6, 8, respectively.

Figure 3.3. SRD versus sync pattern with sync pattern size n = 4

Figure 3.4. SRD versus sync pattern with sync pattern size n = 6

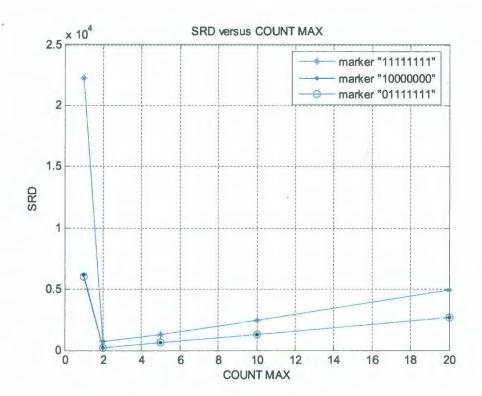

Figure 3.5. SRD versus sync pattern with sync pattern size n = 8