We are IntechOpen, the world's leading publisher of Open Access books Built by scientists, for scientists

125,000 International authors and editors 140M

Our authors are among the

TOP 1%

WEB OF SCIENCE

Selection of our books indexed in the Book Citation Index in Web of Science™ Core Collection (BKCI)

# Interested in publishing with us? Contact book.department@intechopen.com

Numbers displayed above are based on latest data collected. For more information visit www.intechopen.com

Chapter

# Development and Characterization of High-Quality HfO<sub>2</sub>/InGaAs MOS Interface

Sukeun Eom, Min-woo Kong and Kwang-seok Seo

## Abstract

The scope of this chapter is to introduce a highly efficient HfO<sub>2</sub> atomic layer deposition (ALD) process with superior interface defect characteristics that can be applied on high-mobility III-V substrates. For a long time, the major academic research of III-V metal-oxide-semiconductor (MOS) studies was mainly oriented on searching for the suitable high-k dielectric, and among the reported high-k/ III-V MOS studies, Al<sub>2</sub>O<sub>3</sub> and AlN have demonstrated the most promising results. However, usually, the dielectrics with higher dielectric constant suffered from more defective interface quality including the HfO<sub>2</sub>, which should be overcome to meet the intensive operation voltage scaling requirements. In order to protect the interface of the HfO<sub>2</sub>/III-V MOS, the exposed III-V surface has to be carefully treated before, while, and after the whole high-k deposition process. For this purpose, the effect of isopropyl alcohol precursor and in situ cyclic nitrogen plasma treatment on the HfO<sub>2</sub> ALD process at III-V substrates was thoroughly investigated. Remarkable interface state density levels with strong inversion behavior were achieved, which have not been observed at the previous HfO<sub>2</sub>/InGaAs studies. Also, detailed analysis of the interface characteristics was investigated to broaden the understanding of the improvement phenomenon.

**Keywords:** high-k oxides, hafnium oxide (HfO<sub>2</sub>), atomic layer deposition (ALD), III-V channel, indium gallium arsenide (InGaAs), metal-oxide-semiconductor (MOS)

## 1. Introduction

Over the past decades, the semiconductor foundry business has gone through a dynamic transformation. Recently, the foundries are leading the process development race at 10 nm [1, 2] and even to 7 nm [3, 4] and will continue to do so. However, the traditional physical scaling of advanced MOSFETs in conjunction with Dennard's scaling rules has become extremely challenging as to increase the drive currents for faster switching speeds at lower supply voltages is largely at the expense of large leakage current in extremely scaled device [5]. As a result, even with the huge R&D investments, the semiconductor firms gradually lagged the advertised on-chip feature sizes demonstrated in the scaling roadmap, and finally the end of Moore's law has been declared with the end of the 2016 International Technology Roadmap of Semiconductors (ITRS) [5, 6]. Also, the emergence of internet of things (IoT) and big data applications has driven a necessity of abundant computing and memory resources that requires always-on and high-performance ultralow-power devices to generate data instantly. Several device architectures and novel materials based on both analytical and experimental academic research were proposed in the metal-oxide-semiconductor field-effect transistor (MOSFET) technology. Among the viable technologies, the compound semiconductor especially the III-V materials have stood out to be a promising channel candidate for the future highly scaled CMOS application.

The light effective mass of III-V materials compared to the Si even in the highly strained case leads to a higher electron mobility and a higher injection velocity, which should translate into a great turn-on performance even at a lower operation voltage  $(V_{DD})$  level down to 0.5 V. Moreover, there is already a mature industry that uses III-V high electron mobility transistors (HEMTs) for high-frequency applications [7, 8], and it provides excellent techniques such as InGaAs and InAs quantum well (QW) FETs [9, 10]. However, most of these III-V compound semiconductors have smaller bandgaps, which have great impact on the band-to-band tunneling leakage currents. In addition, according to Yan's model [11], the higher permittivity of these materials may worsen the short channel effects (SCE). In spite of the demerits that may limit the scalability, the benefits are much more attractive which makes the III-V channel technology a powerful beyond CMOS solution. However, the use of III-V compound semiconductors has been reluctant to the industry because of its high-cost manufacturing process and CMOSincompatible process. Naturally, it brought out a strong motivation of research of III-V hetero-integration on a Si platform. The main obstacle of III-V on Si integration research is that as huge lattice constant mismatch exists between those two materials, growing epitaxial films directly on Si without defect is difficult [12]. Accordingly, different approaches have been developed, and among them, direct wafer bonding [13, 14] and aspect ratio trapping (ART) [15, 16] technologies have projected the most promising results.

Consequently, the remaining issue toward the practical realization of III-V materials is its defective interface quality which has been the major drawback compared to Si [17–21]. The poor native oxide quality compared with SiO2 is challenging even more with III-V materials. The III-V compound semiconductors are typically composed of binary, ternary, or even quaternary material by covalent bonding, and more complex elements mean a much richer population of possible oxides for the III-V materials [22]. These native oxides are not thermodynamically stable and very leaky that rise serious issues of creation of significant surface states on the oxidesemiconductor interface and huge trap-assisted gate leakage current [17, 19]. At the early stage of research, GaAs MOSFET suffered from high density of interface states (over 3 orders compared to Si) hindering inversion mode operation.

In order to overcome the defective interface problem, many research groups conducted extensive research effort with a search for a perfect gate dielectric that suits the III-V substrate [23, 24]. The study of atomic layer deposition (ALD) high-k dielectric led to a successful integration of high-k gate dielectrics on III-V substrate, and recent research is mainly focused on the development and interface character-ization of ALD high-k and III–V compound semiconductor. To evaluate the objective III-V metal-oxide-semiconductor (MOS) characteristics, it is important to understand the trapping mechanism and know what kind of measurement is required. For Si, the primary defects are the well-known P<sub>b</sub> centers, which are dangling bonds at the immediate interface with the dielectric [25]. However, for the III-V material, the anti-sites and interstitials are the critical defect centers [17], and the small DOS of the III-V materials is also a weak point [26]. These differences lead to different trapping mechanism, and unlike Si MOS, the III-V MOS gate stack often exhibits a particular C-V phenomenon typically known as the frequency dispersion effect [27].

The features of the frequency dispersion effect are threefold. First, large inversionlike hump occurs even at high measurement frequency, which could not be an actual inversion characteristic theoretically. Secondly, the C-V curve horizontally shifts to the negative direction as the measurement frequency decreases. Finally, the accumulation capacitance increases as the measurement frequency decreases.

The large interfacial trap densities  $(D_{it})$  that reside within high-k dielectric and III-V substrate are mostly responsible for the explained features [28]. The high  $D_{it}$ especially the near mid-gap states act as generation recombination centers that attribute to the inversion hump phenomenon in the weak inversion regime. In addition, the large donor-like D<sub>it</sub> near the conductance band (for n-type substrate) induces a substantial surface charge that needs to be compensated by larger gate biases resulting in a horizontal shift in the C-V curve. Detailed discussions are well explained through both theoretical and experimental research [27, 28]. The accumulation capacitance increase, however, is guite difficult to be explained only by the interface traps. There have been numerous publications on this particular accumulation dispersion behavior, and discussion led to an explanation of a carrier transport model from the crystalline semiconductor into the border traps, which are defects within the bulk of the dielectric [29]. The capture and emission process occur at border traps with the interaction of conduction band electrons resulting in discrepancy of accumulation capacitance, and the thermal barrier in capture process is responsible for the strong temperature dependency.

Among the reported high-quality insulator/InGaAs interface studies, the direct deposition of hafnium oxide (HfO<sub>2</sub>) on InGaAs substrate has generally led to poor electrical characteristics, and there are only few studies aimed at improving the intrinsic HfO<sub>2</sub>/InGaAs interface quality [30, 31]. These studies also target only in pretreatments, which is vulnerable during oxide deposition. Meanwhile, O<sub>3</sub> and H<sub>2</sub>O are the most common oxidants employed in HfO<sub>2</sub> ALD. However, one of the disadvantages of H<sub>2</sub>O-based ALD is high-concentration hydroxyl groups in the films, which degrades the dielectric interface during the post deposition annealing process [32]. In addition, sufficiently long purge time is needed because H<sub>2</sub>O tends to physisorb on the surface strongly, especially at low temperature. To solve this problem,  $O_3$  is used as one of the most promising alternative oxidants in ALD process, due to its strong oxidization and high volatility. However, O<sub>3</sub> is known to oxidize the III-V surface during the initial deposition cycles which will neglect the prior surface treatments that easily cause the formation of inferior native oxides [33]. The excess interfacial oxidation of the InGaAs surface initiated by the use of ozone is widely reported in the previous studies. H<sub>2</sub>O oxidant also is not totally free from surface oxidation [34]. Therefore, the research on alternative oxidation sources is necessary for the HfO<sub>2</sub>/InGaAs MOS studies to make the effort made in the pretreatment studies work.

### 2. Development of IPA-based ALD HfO<sub>2</sub> on n-type InGaAs substrates

Looking into the oxidant candidates, isopropyl alcohol (IPA) is known to be irresponsive to the semiconductor surface during the initial ALD cycles [35], and as most pretreatment studies are aimed at removing the native oxides of the III-V surface, the IPA oxidant will be able to efficiently suppress the surface oxidation after the pretreatment process.

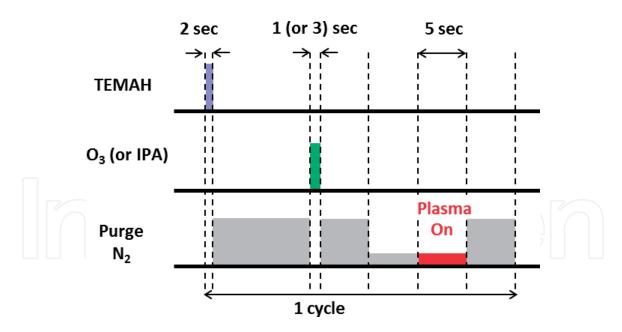

In order to study the effect of using IPA oxidant, O<sub>3</sub> was used as the reference to compare. The basic cycle of the HfO<sub>2</sub> deposition is consisted of a TEMAH precursor pulse and an oxidant (O<sub>3</sub> or IPA) exposure with N<sub>2</sub> purging process between the precursor injection and oxidant process. The temperature of the IPA precursor was

maintained at 4°C. The vapor pressure of IPA at 4°C is around 10 mmHg, which is four times smaller than that at the room temperature [36]. It is important to control the excessive vapor pressure because it leads to a longer purge time, which disables an efficient ALD cycle.

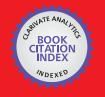

The ALD characteristics of  $HfO_2$  using  $O_3$  and IPA oxidants are shown in **Figure 1**. Oxidant pulse times were 1 and 3 s for  $O_3$  and IPA, respectively, which

Figure 1.

Comparison of the  $O_3$ - and IPA-based HfO2 ALD characteristics: (a) deposition rate vs. oxidant time, (b) deposition rate vs. deposition temperature, and (c) growth per cycle rate.

were chosen to meet the saturation requirement of ALD. Both oxidants had similar saturated deposition rate of 0.1 nm/cycle. Noticeable difference was observed in the temperature windows of oxidant type. While stable deposition rate of  $O_3$  oxidant was maintained in a large temperature range, saturated deposition rate of IPA oxidant was only observed in a small temperature range around 320°C. In low temperatures, low deposition rate is due to insufficient reaction which is originated from low reactivity of IPA. Also, in high temperatures above 320°C, thermal decomposition of Hf precursor occurs, and it hinders the self-limiting characteristics of ALD. Therefore, the deposition temperatures of HfO<sub>2</sub> ALD were chosen to be 230 and 320°C for  $O_3$  and IPA, respectively. Moreover, the film thickness per ALD cycles is presented. It is observed that the linear deposition rate per cycle is obtained for both oxidants and a thicker interface layer thickness appears to be existed for the  $O_3$  oxidant due to is strong reactivity (**Figure 2**).

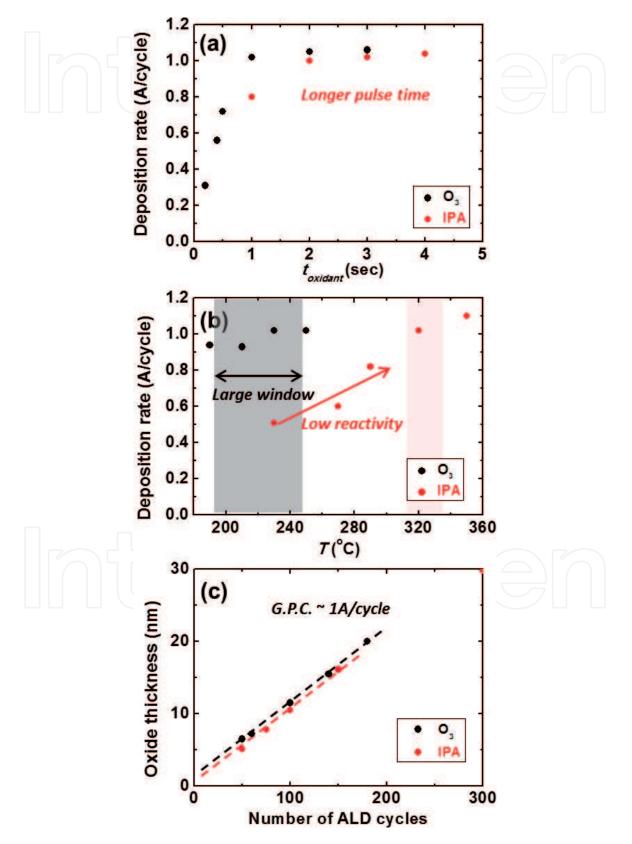

Based on the ALD characteristics, the HfO<sub>2</sub>/Si MOS capacitors are fabricated on the Si substrate. All samples underwent standard Si cleaning steps that consisted of SPM- and HF-based cleaning and 400°C 10 min annealing after the dielectric deposition. The C-V and forward gate leakage characteristics are measured and discussed. First of all, the C-V hysteresis difference is notable. As anticipated, the C-V hysteresis significantly decreases by employing the IPA oxidant. Powerful

oxidation ability of ozone may induce undesired interfacial oxide at the Si interface forming defective hafnium silicate leading to a large hysteresis, while IPA-based HfO<sub>2</sub> appears to be negligible on this effect [37]. The dielectric constants of IPAbased and O<sub>3</sub>-based HfO<sub>2</sub> extracted by the thickness series method are 19.4 and 17.6, respectively [38]. While the C-V results report promising potential of IPA oxidant in ALD HfO<sub>2</sub>, the leakage properties suggest a different aspect. Leaky forward gate leakage especially in the medium gate voltage range of the IPA-based HfO<sub>2</sub> is presented compared to the  $O_3$ -based HfO<sub>2</sub>. It is well known that at this gate bias range, the dominant leakage mechanism is by the Poole-Frenkel tunneling, which is a conduction method of electron tunneling from a metal electrode to traps in a nearby insulator layer, followed by detrapping of the electrons from the traps by virtue of a lowered potential well due to an applied electric field [39]. It usually implies the bulk quality of dielectric; in short, the larger the leakage in this E-field is, the more inferior the gate insulator is. It is speculated that by using the IPA oxidant, the bulk quality may be inferior than using the  $O_3$  oxidant in ALD HfO<sub>2</sub>. This might affect the further scaling down potential and the border trap density in ALD HfO<sub>2</sub> application on InGaAs substrate [40].

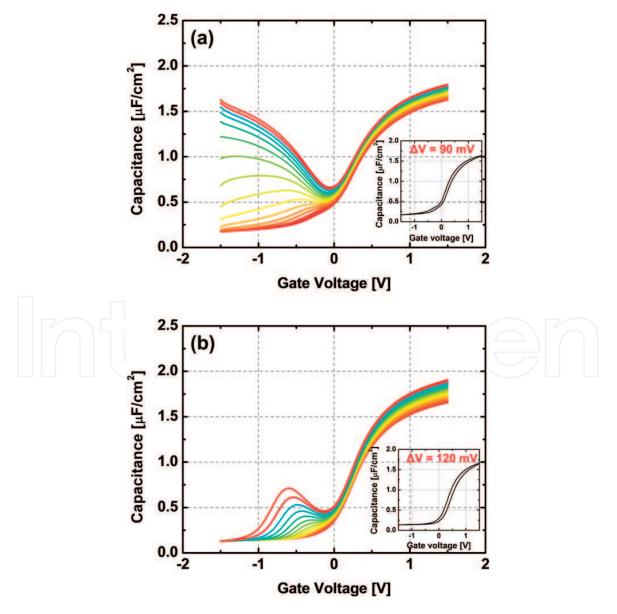

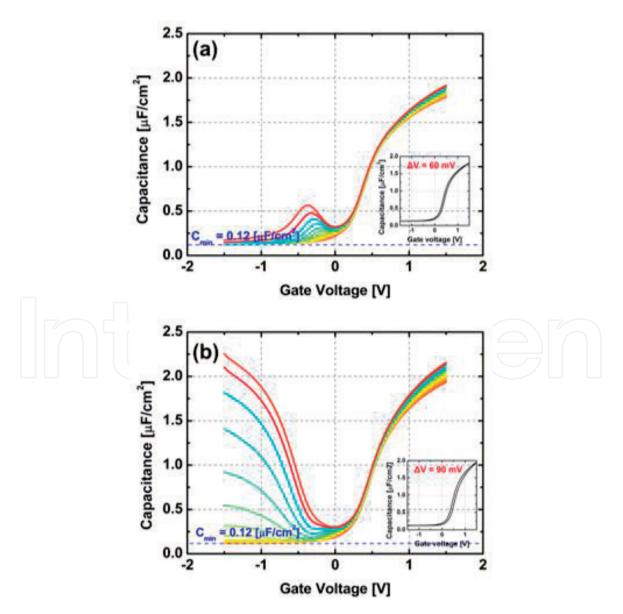

Figure 3.

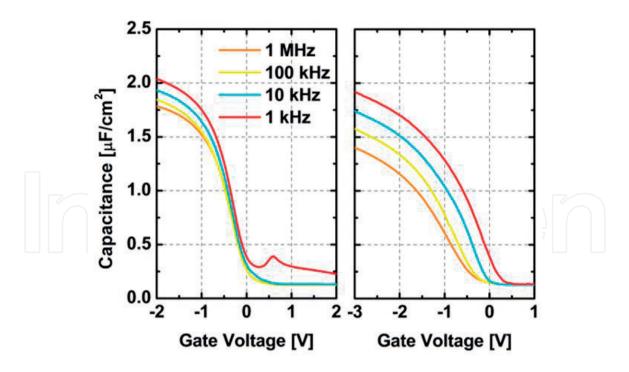

Multifrequency C-V responses of (a)  $O_3$ - and (b) IPA-based HfO<sub>2</sub>/In0.53Ga0.47As MOS capacitors; insets are the hysteresis at 1 MHz.

By using the developed  $O_{3}$ - and IPA-based HfO<sub>2</sub> dielectrics, HfO<sub>2</sub>/InGaAs MOS capacitors were successfully demonstrated [41]. The multifrequency (1 kHz–1 MHz) C-V characteristics of HfO<sub>2</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors using the O<sub>3</sub> and IPA oxidants are presented in **Figure 3**. The C-V curves of the O<sub>3</sub>-based HfO<sub>2</sub> ALD showed a large inversion hump in the negative bias range, which is attributed to the large density of interface defect states near the mid-gap trap level. In contrast, those of the IPA-based HfO<sub>2</sub> ALD showed a notable suppression of the inversion hump behavior. In addition, by employing the IPA oxidant, the effective oxide thickness (EOT) has decreased. We hypothesize that the reduced inversion hump and decrease of the EOT originate from the suppression of unintentional interfacial oxides by the use of the IPA oxidant. Detailed material characteristics analysis was conducted and proved the hypothesis to be convincing [41]. To our knowledge, it is the first successful demonstration of HfO<sub>2</sub> deposition using IPA at InGaAs substrate.

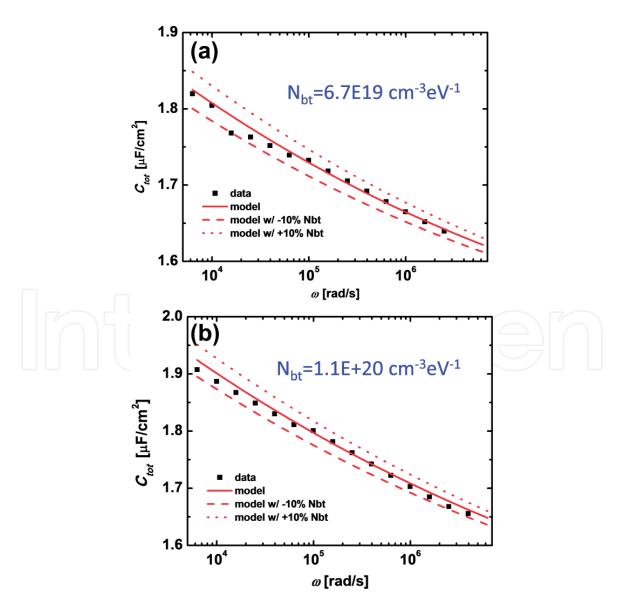

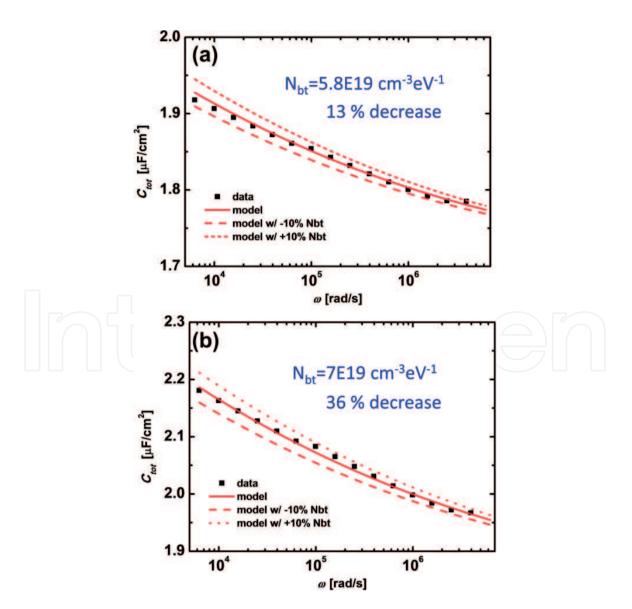

Despite the advantages of using the IPA oxidant, frequency dispersion at the accumulation region slightly increased from 3.3 to 4.7% per decade. In **Figure 4**, these values were used to estimate the border trap densities ( $N_{bt}$ ) by using a distributed bulk-oxide trap model, and increased  $N_{bt}$  of  $1.1 \times 10^{20}$  cm<sup>-3</sup> eV<sup>-1</sup> was extracted compared to  $6.7 \times 10^{19}$  cm<sup>-3</sup> eV<sup>-1</sup>. Also, larger C-V hysteresis and severely degraded

#### Figure 4.

Border trap estimation of  $HfO_2/InGaAs$  MOS capacitors by using the distributed oxide bulk trap model (a)  $O_3$ - $HfO_2$  and (b) IPA- $HfO_2$ .

leakage currents at positive bias are noticed. Based on these results, an inferior quality of the HfO<sub>2</sub> film for using IPA oxidant was predicted which should be resolved for reliable use of the IPA oxidant.

In order to improve the weak IPA-based HfO<sub>2</sub> bulk quality, the study of origin in HfO<sub>2</sub> defect is necessary. One of the main concerns in the replacement of SiO<sub>2</sub> to HfO<sub>2</sub> is that compared to SiO<sub>2</sub>, HfO<sub>2</sub> generally suffers from high defect densities leading to several issues such as large carrier trapping, mobility degradation due to coulombic scattering in the channel surface, and threshold voltage shifts in gate stress conditions [42]. To be specific, the threshold voltage shift issue was not a new phenomenon that suddenly happened with use of HfO<sub>2</sub>. In immature SiO<sub>2</sub> MOSFETs, it is widely known that the extrinsic contaminations in SiO<sub>2</sub> with alkali ions induce this similar phenomenon [43]. However, with HfO<sub>2</sub>, it appeared to be caused by the high defect concentrations, which originated from a more fundamental problem, not an extrinsic defect. Consequently, many researches were devoted to HfO<sub>2</sub> physical model simulation in order to identify the type of defects and their energy levels, and by these physical studies, researchers hoped to learn how the deposition and processing conditions can be optimized to minimize these defect origins [42, 44, 45].

Based on computational calculations, it is identified that oxygen vacancies in HfO<sub>2</sub> are both the principal trap and main cause of the discussed issues, and its formation energy and energy levels were also calculated [44]. Hence, in order to reduce the defect densities, experiments regarding deposition and post processing conditions were aimed to remove or passivate these defects, with an oxygen-rich ambient. However, in many cases, it only worked to some extent and led to new issues of excessive oxidation leaving oxygen interstitials and oxygen diffusion to the interface [46].

Additionally, due to the low density of states of III-V semiconductors, III-V substrates are heavily influenced to border traps that could severely worsen the device performance resulting in poor reliability properties. Therefore, not only the interface but also the bulk characteristics of HfO<sub>2</sub> should be considered in III-V MOS studies, and improvement in both qualities is definitely important.

One of the most effective methods to improve the inherent properties of  $HfO_2$  is the incorporation of nitrogen to passivate oxygen vacancies, and it has been extensively utilized in many recent studies [47–51]. Significant improvement in the electrical characteristics of various high-k gate dielectrics by nitrogen incorporation has been demonstrated, and it is found that interfacial layer growth is effectively suppressed [49] and there is lower boron penetration with nitrogen incorporation [51]. Also, lower leakage current density in HfO<sub>x</sub>N<sub>v</sub> is widely reported due to suppression of oxygen vacancy traps [50]. It has been reported that nitrogen incorporation in  $HfO_2$  can be achieved by several methods mostly by nitrogen ambient plasmabased nitridation [47, 50] or ammonia (NH<sub>3</sub>) ambient high-temperature annealing treatment [52, 53]. For Si-based MOS studies, the later approach is known to be very powerful for achieving good uniformity of nitrogen incorporation and excellent interface quality due to the absence of plasma damage. However, in order to successfully apply nitrogen incorporation technology on III-V substrate, the low thermal budget of III-V compound semiconductor always has to be considered, and high-temperature annealing treatment should be ruled out for nitrogen incorporation study in III-V MOS. In the other hand, although plasma-based nitridation technology offers low thermal budget capacity, most studies generally suffers from several issues such as nonuniform nitrogen distribution throughout dielectric, plasma-induced damage due to high-power plasma for dielectric penetration, and high energy potential nitrogen species substituting well-combined Hf-O bonds. Post deposition plasma treatments have recently been suggested for InGaAs MOS

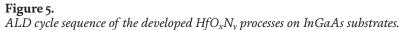

Figure 6.

Multifrequency C-V responses of (a)  $O_3$ - and (b) IPA-based HfON/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors; insets are the hysteresis at 1 MHz.

devices [54]; however, no effort was made to improve the nitridation technology regarding the discussed issues.

As a result, in order to improve the film quality of  $HfO_2$ , a cyclic nitrogen lowpower plasma step was added within the ALD cycles to passivate oxygen vacancies uniformly without causing damage or surface degradation. Through this technology with a combination of IPA oxidant, achievement of improvement in both interface and bulk quality of high-k/InGaAs MOS properties is expected. The detailed information of the ALD sequence is depicted in **Figure 5**. Every cycle consisted of sequential precursor pulse steps and a gas stabilization step followed by 5 s of 50 W N<sub>2</sub> plasma step with purge steps between pulse steps. It is discovered that there is a trade-off relationship of plasma condition. The plasma power should be enough for effective passivation although it may degrade the substrate by radiation damage. Through the developed ALD sequence, with adequate plasma condition, the HfO<sub>2</sub> layer is improved without having influence in the substrate.

By using the proposed nitridation technology, HfO<sub>x</sub>N<sub>y</sub>/InGaAs MOS capacitors are fabricated showing promising results as shown in **Figure 6** [41]. A significant suppression of the frequency dispersion was observed upon nitrogen incorporation in every gate bias range. The inversion humps and flat band voltage shift were effectively reduced for all samples, which imply that the defective interface states

#### Figure 7.

Border trap estimation of HfON/InGaAs MOS capacitors by using the distributed oxide bulk trap model (a)  $O_3$ -HfON and (b) IPA-HfON.

near the mid-gap level can be treated with nitrogen incorporation. It is hypothesized that oxygen diffusion through the oxygen vacancies of HfO<sub>2</sub>, which results in the formation of As-Ga anti-sites, was greatly reduced, as oxygen vacancies were effectively passivated with nitrogen [17]. Therefore, nitrogen may block further oxygen diffusion, thereby preventing surface oxidation, which could occur not only during but also after dielectric deposition. Furthermore, the frequency dispersion in the accumulation region greatly reduced to 2.1 and 3.2% per decade for O<sub>3</sub>- and IPA-based ALD, respectively. These values are comparable to suppressed dispersion values in low-EOT gate stacks, which imply excellent reliability quality of dielectric stacks on III-V substrate [55]. As the proposed nitridation technology is aimed to treat inferior bulk qualities of HfO<sub>2</sub>, it showed greater impact on IPA-based HfO<sub>2</sub>. The inversion behavior was observed for the IPA-based ALD HfO<sub>2</sub> which has not been reported from the former HfO<sub>2</sub>/InGaAs MOS studies, and it will be further discussed (**Figure 7**).

# 3. Characterization of IPA-based ALD HfO<sub>2</sub> on n- and p-type InGaAs substrates

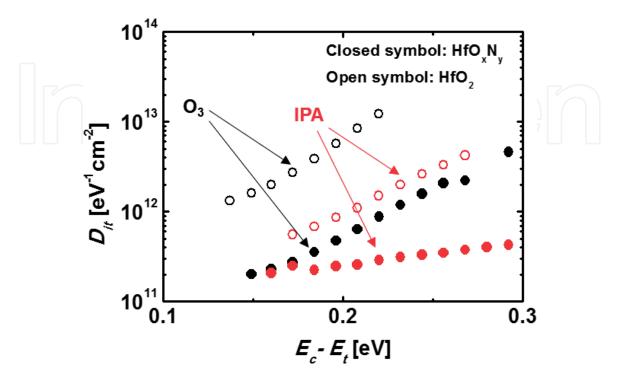

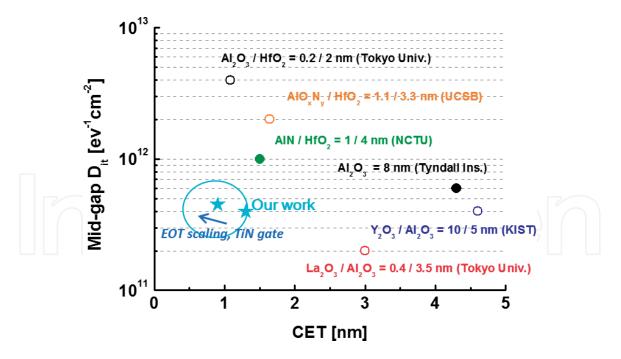

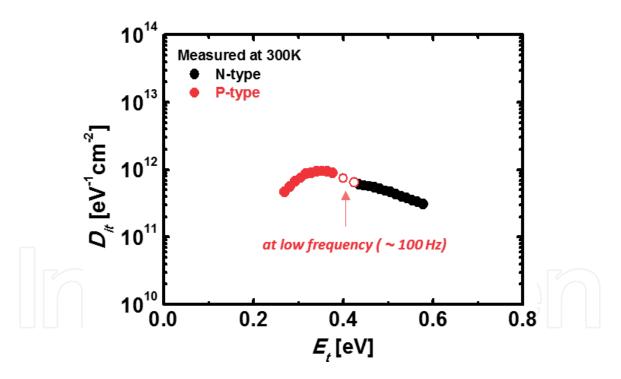

Based on the n-type MOS results, the  $D_{it}$  was extracted using the conductance method as shown in **Figure 8**. The combination of IPA oxidant and PA-ALD  $HfO_xN_y$  with standard interface treatments resulted in a reduced  $D_{it}$  level of  $4.5 \times 1011 \text{ eV}^{-1} \text{ cm}^{-2}$  at  $E_c - E_t = 0.3 \text{ eV}$ . Based on the  $D_{it}$  distribution, it is evident that the inversion behavior observed in the C-V curves is due to the significant midgap  $D_{it}$  decrease, which is consistent with the previously reported studies. As the mid-gap  $D_{it}$  is known to correlate to the As-Ga anti-site defect and the ozone-based  $HfO_xN_y$  lacked inversion characteristics with high mid-gap  $D_{it}$ , these defects might be the reason why the inversion behavior is difficult to be achieved in most studies. Also, these defects might be formed in the initial ALD steps through the oxidant exposure. Also, in **Figure 9**, we have benchmarked our results, comparing them

#### Figure 8.

The  $D_{it}$  distribution of the fabricated III-V MOS capacitors showing great reduction in the mid-gap  $D_{it}$  with the IPA-based HfO<sub>x</sub>N<sub>y</sub>.

#### Figure 9.

Benchmarking the mid-gap  $D_{it}$  values of the proposed high-k ALD compared to the best results in the field of III-V MOS. The filled circles represent C-V curves with inversion behavior.

to the best results ever reported in the field of III-V MOS device studies [56–61]. Extraordinary mid-gap  $D_{it}$  values are achieved with low CET values with the proposed technology. Especially, while other studies mostly suffer from insufficient dielectric constant of the IL, our work employs HfO<sub>2</sub> as an IL, which has merit in terms of the EOT scaling.

In addition, with conductance method in the measurement frequency range of 1 kHz-1 MHz, the n-type MOS capacitor results can only provide information of  $D_{it}$  distribution near the conduction band. In order to estimate the total  $D_{it}$  distribution throughout the bandgap in InGaAs, p-type InGaAs MOS was fabricated and analyzed. The p-type InGaAs MOS capacitors are fabricated in the same process flow of n-type MOS capacitors.

The multifrequency C-V measurements of IPA-based PA-ALD  $HfO_xN_y/n$ -In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors compared to the  $HfO_2$  (O<sub>3</sub>) sample is presented in **Figure 10**. Compared to the reference, the optimized HfON process exhibits significant frequency dispersion suppression with steeper C-V slope. This result is comparable to the previously reported high-quality p-type InGaAs MOS results. It is assumed that the interface improvement mechanism is similar to the previous n-type MOS analysis.

Based on the results, the  $D_{it}$  distribution within the InGaAs bandgap is extracted with the conductance method shown in **Figure 11**. The  $D_{it}$  level at the exact mid-gap energy level ( $E_g/2 = 0.375 \text{ eV}$ ) is around  $8 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$ . This value is still low for reported III-V MOS interface, and it is suggested that based on the  $D_{it}$  distribution, the accumulation mode n-channel III-V devices are favorable than the inversion mode p-substrate III-V devices because the overall  $D_{it}$  levels are much lower at the conduction band area.

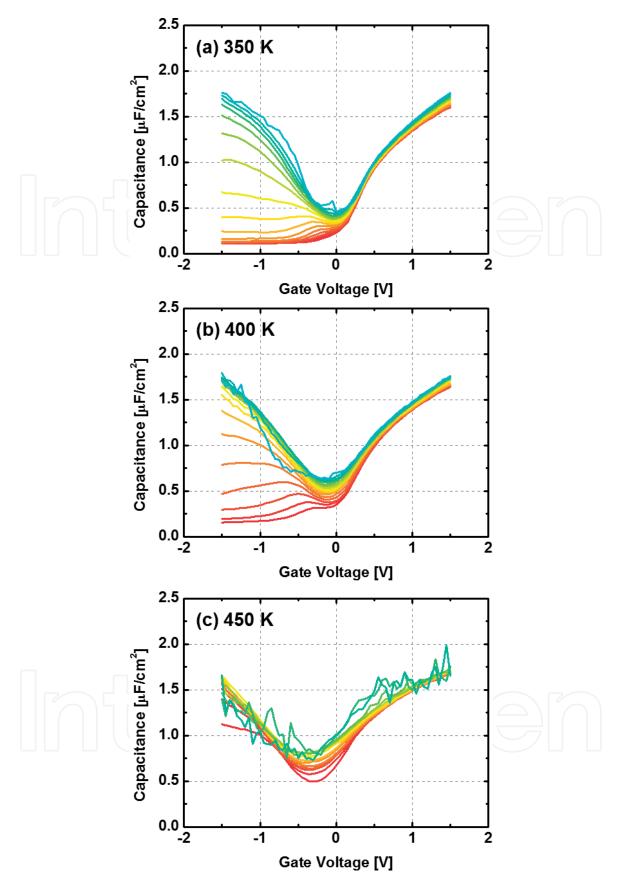

Moreover, temperature-dependent conductance method was performed in order to analyze the mid-gap D<sub>it</sub> level thoroughly. High-temperature (350, 400 and 450 K) multifrequency C-V analysis was conducted on HfON/InGaAs MOS capacitors. The C-V results of each measurement temperature are shown in **Figure 12**.

As the measurement temperature increases, the inversion response gets stronger at higher frequencies compared to the room temperature-measured results. Also,

Figure 10.

C-V characteristics of IPA-based PA-ALD HfO<sub>x</sub>N<sub>y</sub> (left) and O<sub>3</sub>-based HfO<sub>2</sub> (right) on p-type In<sub>0.53</sub>Ga<sub>0.47</sub>As substrates.

#### Figure 11.

The total  $D_{it}$  distribution within the  $In_{0.53}Ga_{0.47}As$  bandgap, which is extracted from the *n*- and *p*-type MOS capacitors.

while the dispersion at the accumulation region seems to be similar, there was a significant impact on the inversion hump phenomenon which is the interface trap characteristic. The measurement noise at higher temperature and lower frequencies was also noted. When the measurement temperature reaches around 450 K, the strong inversion response occurs even at 1 MHz, and it interferes with the interface trap-related conductance peak making the deconvolution process impossible.

The D<sub>it</sub> distribution was estimated from the temperature-dependent conductance technique as shown in **Figure 13**. As the measurement temperature increases, the

#### Figure 12.

C-V characteristics of IPA-based PA-ALD HfO<sub>x</sub>N<sub>y</sub> on n-type InGaAs substrate measured at (a) 350 K, (b) 400 K, and (c) 450 K.

deeper energy range could be measured. Similar  $D_{it}$  profile was observed showing a peak energy level around the exact mid-gap level (~0.375 eV). The peak  $D_{it}$  value is slightly higher than the previously estimated value which would be the effect of

Figure 13.

The total  $D_{it}$  distribution within the  $In_{0.53}Ga_{0.47}As$  bandgap, which is extracted from the temperaturedependent conductance method.

enhanced thermal broadening of trap response in higher temperatures. The differences between the D<sub>it</sub> profile estimation can be summarized as follows: While using p-MOS capacitors, a larger energy level range is observable with no thermal broadening of the trap response due to the fixed measurement temperature. On the other hand, using a temperature-dependent method has a thermal broadening issue but only requires one sample for characterization.

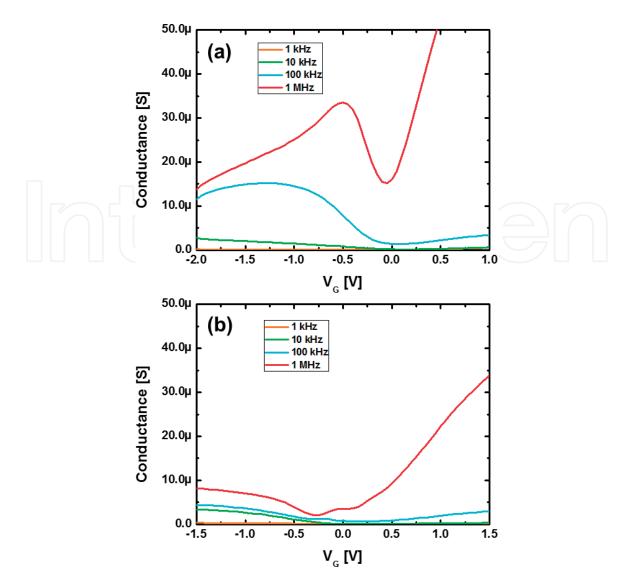

It was noted that the inversion behavior of IPA-based  $HfO_xN_y$  ALD is attributed to the mid-gap  $D_{it}$  level decrease. However, in order to verify true inversion characteristics, more analyses must be investigated. In **Figure 14**, the conductance profile of sample O<sub>3</sub>-based HfO<sub>2</sub> and IPA-based HfO<sub>x</sub>N<sub>y</sub> InGaAs MOS capacitors are depicted.

Both C-V profiles have shown inversion-like behavior in the negative bias region. However, clear difference is observed between the conductance profiles. While huge and Gaussian conductance profiles in the negative bias regions are observed for O<sub>3</sub>-based HfO<sub>2</sub>, smaller Gaussian conductance peaks are observed in depletion region, and distinct from these peaks, saturated conductance profiles are observed for IPA-based HfO<sub>x</sub>N<sub>y</sub>. Therefore, it is concluded that the inversion-like behavior in O<sub>3</sub>-based HfO<sub>2</sub> is attributed from the huge and broad conductance peaks that reflect high mid-gap D<sub>it</sub> levels, while inversion behavior in IPA-based HfO<sub>x</sub>N<sub>y</sub> might be attributed from real true minority carrier inversion.

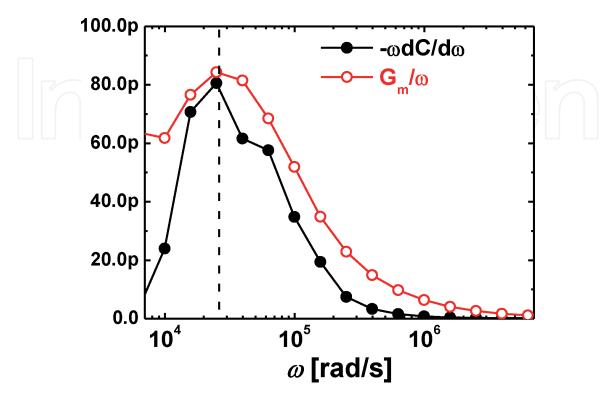

In **Figure 15**, to verify true inversion characteristics of IPA-based  $HfO_xN_y$ , the minority carrier response was investigated based on the extraction of the transition frequency,  $w_m$ , which is known to be a characteristic of a strong inverted surface for III-V MOS capacitors [62]. It is known that at the transition frequency, the –wdC/dw and  $G_m/w$  share the same peak magnitude in the strong inversion gate bias. Notably, –wdC/dw and  $G_m/w$  share the same peak magnitude at the same transition frequency of 4 kHz which suggests that IPA-based HfO<sub>x</sub>N<sub>y</sub> exhibits true inversion behavior. The true inversion behavior of hafnium oxide-based dielectrics on InGaAs substrate has not been reported yet which implies significant potential.

**Figure 14.** *The conductance profiles for (a)*  $O_3$ -*Hf* $O_2$  *and (b) IPA-HfON ALD.*

**Figure 15.** -wdC/dw and  $G_m/w$  profiles for IPA-HfON/InGaAs MOS.

## 4. Conclusions

In order to achieve both low EOT and low D<sub>it</sub>, a highly advanced gate stack, prepared by using an IPA oxidant in the PA-ALD of HfO<sub>x</sub>N<sub>v</sub> on In<sub>0.53</sub>Ga<sub>0.47</sub>As substrates, was proposed and showed the most outstanding results. A cyclic nitrogen low-power plasma step was added within the ALD cycles to passivate the oxygen vacancies uniformly without causing damage or surface degradation in comparison to the post deposition nitridation technology. Remarkable midgap D<sub>it</sub> levels with strong inversion characteristics were achieved which has not been reported in the previous HfO<sub>2</sub>/InGaAs interface studies. The improved interface characteristics can be attributed to both low surface oxidation ability of IPA and suppression of oxygen diffusion by effective nitrogen passivation to oxygen vacancies in HfO<sub>2</sub>. The proposed ALD HfO<sub>x</sub>N<sub>v</sub> was fully characterized by investigating different dopant types and measurement temperatures. The results show comprehensive understanding on the interface defect density distribution. It is suggested that not only surface treatments but also the development of an advanced HfO<sub>2</sub> ALD process has a great impact on the quality of the III-V MOS interface and the IPA-based HfON interfacial layer might have great potential in future technology node.

# IntechOpen

## **Author details**

Sukeun Eom<sup>\*</sup>, Min-woo Kong and Kwang-seok Seo Seoul National University, Seoul, Republic of Korea

\*Address all correspondence to: djatnrms90@snu.ac.kr

## **IntechOpen**

© 2020 The Author(s). Licensee IntechOpen. This chapter is distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

## References

[1] Cho H-J, Oh HS, Nam KJ, Kim YH, Yeo KH, Kim WD, et al. Si FinFET based 10nm technology with multi Vt gate stack for low power and high performance applications. In: 2016 IEEE Symposium on VLSI Technology. IEEE; 2016. DOI: 10.1109/VLSIT.2016.7573359

[2] Auth C, Aliyarukunju A, Asoro M, Bergstrom D, Bhagwat V, Birdsall J, et al. A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects. In: 2017 IEEE International Electron Devices Meeting (IEDM). IEEE; 2017. DOI: 10.1109/ IEDM.2017.8268472

[3] Tsai T-H, Sheen R-B, Chang C-H, Staszewski RB. A 0.2GHz to 4GHz Hybrid PLL (ADPLL/Charge-Pump-PLL) in 7NM FinFET CMOS Featuring 0.619PS Integrated Jitter and 0.6US Settling Time at 2.3MW. In: 2018 IEEE Symposium on VLSI Circuits. IEEE; 2018. DOI: 10.1109/VLSIC.2018.8502274

[4] Jeong WC, Kwon DJ, Nam KJ, Rim WJ, Jang MS, Kim HT, et al. True 7nm Platform Technology featuring Smallest FinFET and Smallest SRAM cell by EUV, Special Constructs and 3rd Generation Single Diffusion Break. In: 2018 IEEE Symposium on VLSI Technology. IEEE; 2018. DOI: 10.1109/ VLSIT.2018.8510682

[5] Bohr MT, Young IA. CMOS scaling trends and beyond. IEEE Micro.

2017;37(6):20-29. DOI: 10.1109/ MM.2017.4241347

[6] Theis TN, Wong H-SP. The end of Moore's Law: A new beginning for information technology. Computing in Science & Engineering. 2017;**19**(2): 41-50. DOI: 10.1109/MCSE.2017.29

[7] Duh KHG, Chao PC, Liu SMJ, Ho P, Kao MY, Ballingall JM. A super low-noise 0.1 mu m T-gate InAlAs-InGaAs-InP HEMT. IEEE Microwave and Guided Wave Letters. 1991;**1**(5): 114-116. DOI: 10.1109/75.89081

[8] Lai R, Mei XB, Deal WR, Yoshida W, Kim YM, Liu PH, et al. Sub 50 nm InP HEMT Device with Fmax Greater than 1 THz. In: 2007 IEEE International Electron Devices Meeting. IEEE; 2007. DOI: 10.1109/IEDM.2007.4419013

[9] Lin J, Antoniadis DA, del Alamo JA. Sub-30 nm InAs Quantum-Well MOSFETs with self-aligned metal contacts and Sub-1 nm EOT HfO<sub>2</sub> insulator. In: 2012 International Electron Devices Meeting. IEEE; 2012. DOI: 10.1109/IEDM.2012.6479149

[10] Kim D-H, del Alamo JA. Logic

Performance of 40 nm InAs HEMTs.

In: 2007 IEEE International Electron

Devices Meeting. IEEE; 2007. DOI:

10.1109/IEDM.2007.4419018

[11] Yan R-H, Ourmazd A, Lee KF. Scaling the Si MOSFET: From bulk to SOI to bulk. IEEE Transactions on Electron Devices. 1992 Jul;**39**(7): 1704-1710. DOI: 10.1109/16.141237

[12] Cirlin GE, Dubrovskii VG,

Soshnikov IP, Sibirev NV,

Samsonenko YB, Bouravleuv AD, et al.

Critical diameters and temperature domains for MBE growth of III-V

nanowires on lattice mismatched

substrates. Physica Status Solidi RRL:

Rapid Research Letters. 2009;3(4):

112-114. DOI: 10.1002/pssr.200903057

[13] Daix N, Uccelli E, Czornomaz L, Caimi D, Rossel C, Sousa M, et al. Towards large size substrates for

III-V co-integration made by direct wafer bonding on Si. APL Materials.

2014 Aug;2(8):086104. DOI: 10.1063/1.4893653

[14] Czornomaz L, Daix N, Caimi D, Sousa M, Erni R, Rossell MD, et al. An

integration path for gate-first UTB III-V-on-insulator MOSFETs with silicon, using direct wafer bonding and donor wafer recycling. In: 2012 International Electron Devices Meeting. IEEE; 2012. DOI: 10.1109/IEDM.2012.6479088

[15] Li JZ, Bai J, Park J-S, Adekore B, Fox K, Carroll M, et al. Defect reduction of GaAs epitaxy on Si (001) using selective aspect ratio trapping. Applied Physics Letters. 2007;**91**(2):021114. DOI: 10.1063/1.2756165

[16] Waldron N, Merckling C, Guo W, Ong P, Teugels L, Ansar S, et al. An InGaAs/InP quantum well finfet using the replacement fin process integrated in an RMG flow on 300mm Si substrates. In: 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers. IEEE; 2014. DOI: 10.1109/VLSIT.2014.6894349

[17] Robertson J, Guo Y, Lin L. Defect state passivation at III-V oxide interfaces for complementary metal–oxide– semiconductor devices. Journal of Applied Physics. 2015;**117**(11):112806. DOI: 10.1063/1.4913832

[18] Brammertz G, Lin HC, Martens K, Alian A-R, Merckling C, Penaud J, et al. Electrical properties of III-V/oxide interfaces. ECS Transactions. 2009;**19**(5):375-386. DOI: 10.1149/1.3119560

[19] Hinkle CL, Milojevic M, Brennan B, Sonnet AM, Aguirre-Tostado FS, Hughes GJ, et al. Detection of Ga suboxides and their impact on III-V passivation and Fermi-level pinning. Applied Physics Letters. 2009;**94**(16):162101. DOI: 10.1063/1.3120546

[20] Shahrjerdi D, Tutuc E, Banerjee SK. Impact of surface chemical treatment on capacitance-voltage characteristics of GaAs metal-oxidesemiconductor capacitors with Al<sub>2</sub>O<sub>3</sub> gate dielectric. Applied Physics Letters. 2007;**91**(6):063501. DOI: 10.1063/1.2764438

[21] He G, Chen X, Sun Z. Interface engineering and chemistry of Hf-based high-k dielectrics on III–V substrates. Surface Science Reports. 2013;**68**(1):68-107. DOI: 10.1016/j. surfrep.2013.01.002

[22] Hollinger G, Skheyta-Kabbani R, Gendry M. Oxides on GaAs and InAs surfaces: An x-ray-photoelectronspectroscopy study of reference compounds and thin oxide layers. Physical Review B. 1994;**49**(16):11159-11167. DOI: 10.1103/PhysRevB.49.11159

[23] Ye PD, Wilk GD, Kwo J, Yang B, Gossmann H-JL, Frei M, et al. GaAs MOSFET with oxide gate dielectric grown by atomic layer deposition. IEEE Electron Device Letters. 2003;**24**(4):209-211. DOI: 10.1109/ LED.2003.812144

[24] Huang YL, Chang P, Yang ZK, Lee YJ, Lee HY, Liu HJ, et al. Thermodynamic stability of Ga2O3(Gd2O3)/GaAs interface. Applied Physics Letters. 2005;**86**(19):191905. DOI: 10.1063/1.1923172

[25] Poindexter EH, Gerardi GJ, Rueckel ME, Caplan PJ, Johnson NM, Biegelsen DK. Electronic traps and Pb centers at the Si/SiO2interface: Bandgap energy distribution. Journal of Applied Physics. 1984;56(10): 2844-2849. DOI: 10.1063/1.333819

[26] Engel-Herbert R, Hwang Y, Stemmer S. Quantification of trap densities at dielectric/III–V semiconductor interfaces. Applied Physics Letters. 2010;**97**(6):062905. DOI: 10.1063/1.3479047

[27] Stemmer S, Chobpattana V, Rajan S. Frequency dispersion in III-V metal-oxide-semiconductor capacitors. Applied Physics Letters. 2012;**100**(23):233510. DOI: 10.1063/1.4724330 [28] Engel-Herbert R, Hwang Y, Stemmer S. Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces. Journal of Applied Physics. 2010;**108**(12):124101. DOI: 10.1063/1.3520431

[29] Yuan Y, Yu B, Ahn J, McIntyre PC, Asbeck PM, Rodwell MJW, et al. A distributed bulk-oxide trap model for Al<sub>2</sub>O<sub>3</sub> InGaAs MOS devices. IEEE Transactions on Electron Devices. 2012;**59**(8):2100-2106. DOI: 10.1109/ TED.2012.2197000

[30] Chobpattana V, Son J, Law JJM, Engel-Herbert R, Huang C-Y, Stemmer S. Nitrogen-passivated dielectric/InGaAs interfaces with sub-nm equivalent oxide thickness and low interface trap densities. Applied Physics Letters. 2013;**102**(2):022907. DOI: 10.1063/1.4776656

[31] Kent T, Tang K, Chobpattana V, Negara MA, Edmonds M, Mitchell W, et al. The influence of surface preparation on low temperature HfO<sub>2</sub> ALD on InGaAs (001) and (110) surfaces. The Journal of Chemical Physics. 2015;**143**(16):164711. DOI: 10.1063/1.4934656

[32] Rafí JM, Zabala M, Beldarrain O, Campabadal F. Effect of processing conditions on the electrical characteristics of atomic layer deposited Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> films. ECS Transactions. 2010;**28**(2):213. DOI: 10.1149/1.3372577

[33] García H, Castán H, Dueñas S, Bailón L, Campabadal F, Beldarrain O, et al. Electrical characterization of atomic-layer-deposited hafnium oxide films from hafnium tetrakis(dimethylamide) and water/ ozone: Effects of growth temperature, oxygen source, and postdeposition annealing. Journal of Vacuum Science & Technology, A: Vacuum, Surfaces, and Films. 2013;**31**(1):01A127. DOI: 10.1116/1.4768167 [34] Ahn J, McIntyre PC. Subcutaneous oxidation of In<sub>0.53</sub>Ga<sub>0.47</sub>As(100) through ultra-thin atomic layer deposited Al<sub>2</sub>O<sub>3</sub>. Applied Physics Letters. 2013;**103**(25):251602. DOI: 10.1063/1.4850520

[35] Cheng C-W, Fitzgerald EA. In situ metal-organic chemical vapor deposition atomic-layer deposition of aluminum oxide on GaAs using trimethyaluminum and isopropanol precursors. Applied Physics Letters. 2008;**93**(3):031902. DOI: 10.1063/1.2960574

[36] Parks GS, Barton B. Vapor pressure data for isopropyl alcohol and tertiary butyl alcohol. Journal of the American Chemical Society. 1928;**50**(1):24-26. DOI: 10.1021/ja01388a004

[37] Swerts J, Peys N, Nyns L, Delabie A, Franquet A, Maes JW, et al. Impact of precursor chemistry and process conditions on the scalability of ALD HfO[sub 2] gate dielectrics. Journal of the Electrochemical Society. 2010;**157**(1):G26. DOI: 10.1149/1.3258664

[38] Krylov I, Eizenberg M, Ritter D. Determination of the dielectric constant of InGaAs based gate stacks by a modified thickness series method. Applied Physics Letters. 2014;**105**(20):203506. DOI: 10.1063/1.4902114

[39] Harrell WR, Frey J. Observation of Poole–Frenkel effect saturation in SiO2 and other insulating films. Thin Solid Films. 1999;**352**(1-2):195-204. DOI: 10.1016/S0040-6090(99)00344-2

[40] Simoen E, Lin DH-C, Alian A, Brammertz G, Merckling C, Mitard J, et al. Border traps in Ge/III–V channel devices: Analysis and reliability aspects. IEEE Transactions on Device and Materials Reliability. 2013;**13**(4):444-455. DOI: 10.1109/ TDMR.2013.2275917

[41] Eom S-K, Kong M-W, Kang M-J, Lee J-G, Cha H-Y, Seo K-S. Enhanced interface characteristics of PA-ALD HfOxNy/InGaAs MOSCAPs using IPA oxygen reactant and cyclic N2 plasma. IEEE Electron Device Letters. 2018;**39**(11):1636-1639. DOI: 10.1109/ LED.2018.2870176

[42] Gavartin JL, Muñoz Ramo D,

Shluger AL, Bersuker G, Lee BH.

Negative oxygen vacancies in HfO<sub>2</sub> as charge traps in high-k stacks. Applied Physics Letters. 2006;89(8):082908.

DOI: 10.1063/1.2236466

[43] Greeuw G, Verwey JF. The mobility of Na+, Li+, and K+ ions in thermally grown SiO2 films. Journal of Applied Physics. 1984;**56**(8):2218-2224. DOI: 10.1063/1.334256

[44] Trivedi AR, Ando T, Singhee A, Kerber P, Acar E, Frank DJ, et al. A simulation study of oxygen vacancyinduced variability in HfO<sub>2</sub>/metal gated SOI FinFET. IEEE Transactions on Electron Devices. 2014;**61**(5):1262-1269. DOI: 10.1109/TED.2014.2313086

[45] Xiong K, Robertson J, Clark SJ. Passivation of oxygen vacancy states in HfO<sub>2</sub> by nitrogen. Journal of Applied Physics. 2006;**99**(4):044105. DOI: 10.1063/1.2173688

[46] Lee BH, Kang L, Nieh R, Qi W-J, Lee JC. Thermal stability and electrical characteristics of ultrathin hafnium oxide gate dielectric reoxidized with rapid thermal annealing. Applied Physics Letters. 2000;**76**(14):1926-1928. DOI: 10.1063/1.126214

[47] Dalapati GK, Sridhara A, Wong ASW, Chia CK, Chi DZ. HfOxNy gate dielectric on p-GaAs. Applied Physics Letters. 2009;**94**(7):073502. DOI: 10.1063/1.3079409

[48] Jin CG, Yang Y, Zhang HY, Huang TY, Wu MZ, Zhuge LJ, et al. Controllable nitrogen incorporation in HfO<sub>2</sub> films by modulating capacitivelycombined inductively-coupled plasmas. Journal of Physics D: Applied Physics. 2013;**46**(48):485206. DOI: 10.1088/0022-3727/46/48/485206

[49] Lee YB, Oh I-K, Cho EN, Moon P, Kim H, Yun I. Characterization of HfO N thin film formation by in-situ plasma enhanced atomic layer deposition using NH3 and N2 plasmas. Applied Surface Science. 2015;**349**:757-762. DOI: 10.1016/j.apsusc.2015.05.066

[50] Kang CS, Cho H-J, Choi R, Kim YH, Kang CY, Rhee SJ, et al. The electrical and material characterization of hafnium oxynitride gate dielectrics with TaN-gate electrode. IEEE Transactions on Electron Devices. 2004;**51**(2):220-227. DOI: 10.1109/ TED.2003.821707

[51] Yu X, Zhu C, Yu M. Impact of nitrogen in HfON gate dielectric with metal gate on electrical characteristics, with particular attention to threshold voltage instability. Applied Physics Letters. 2007;**90**(10):103502. DOI: 10.1063/1.2709948

[52] Dai M, Wang Y, Shepard J, Liu J, Brodsky M, Siddiqui S, et al. Effect of plasma N2 and thermal NH3 nitridation in HfO<sub>2</sub> for ultrathin equivalent oxide thickness. Journal of Applied Physics. 2013;**113**(4):044103. DOI: 10.1063/1.4775817

[53] Cheng C-C, Chien C-H, Chen C-W, Hsu S-L, Yang M-Y, Huang C-C, et al. Impact of post-deposition-annealing on the electrical characteristics of HfOxNy gate dielectric on Ge substrate. Microelectronic Engineering. 2005;**80**:30-33. DOI: 10.1016/j. mee.2005.04.033

[54] Chang P-C, Luc Q-H, Lin Y-C, Lin Y-K, Wu C-H, Sze SM, et al. InGaAs QW-MOSFET performance improvement using a PEALD-AlN passivation layer and an *In-situ* NH3Post remote-plasma treatment. IEEE Electron Device Letters. 2017;**38**(3): 310-313. DOI: 10.1109/LED. 2017.2656180

[55] Vais A, Franco J, Martens K, Lin D, Sioncke S, Putcha V, et al. A new quality metric for III–V/high-k MOS gate stacks based on the frequency dispersion of accumulation capacitance and the CET. IEEE Electron Device Letters. 2017;**38**(3):318-321. DOI: 10.1109/ LED.2017.2657794

[56] Hoshii T, Lee S, Suzuki R, Taoka N, Yokoyama M, Yamada H, et al. Reduction in interface state density of  $Al_2O_3/InGaAs$  metal-oxidesemiconductor interfaces by InGaAs surface nitridation. Journal of Applied Physics. 2012;**112**(7):073702. DOI: 10.1063/1.4755804

[57] Suzuki R, Taoka N, Yokoyama M, Lee S, Kim SH, Hoshii T, et al. 1-nm-capacitance-equivalent-thickness HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/InGaAs metal-oxidesemiconductor structure with low interface trap density and low gate leakage current density. Applied Physics Letters. 2012;**100**(13):132906. DOI: 10.1063/1.3698095

[58] Lee S, Chobpattana V, Huang C-Y, Thibeault BJ, Mitchell W, Stemmer S, et al. Record Ion (0.50 mA/um at VDD = 0.5 V and Ioff = 100 nA/um) 25 nm-gate-length ZrO2/InAs/InAlAs MOSFETs. In: 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers. IEEE; 2014. DOI: 10.1109/VLSIT.2014.6894363

[59] Chang C-Y, Ichikawa O, Osada T, Hata M, Yamada H, Takenaka M, et al. Impact of La<sub>2</sub>O<sub>3</sub> interfacial layers on InGaAs metal-oxide-semiconductor interface properties in Al<sub>2</sub>O<sub>3</sub>/La<sub>2</sub>O<sub>3</sub>/ InGaAs gate stacks deposited by atomiclayer-deposition. Journal of Applied Physics. 2015;**118**(8):085309. DOI: 10.1063/1.4929650 [60] Luc Q, Cheng S, Chang P, Do H, Chen J, Ha M, et al. Effects of in-situ plasma-enhanced atomic layer deposition treatment on the performance of HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As metal-oxide-semiconductor fieldeffect transistors. IEEE Electron Device Letters. 2016;**1**:1. DOI: 10.1109/ LED.2016.2581175

[61] Kim SK, Geum D-M, Shim J-P, Kim CZ, Kim H, Song JD, et al. Fabrication and characterization of Pt/ Al<sub>2</sub>O<sub>3</sub>/Y<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with low interface trap density. Applied Physics Letters. 2017;**110**(4):043501. DOI: 10.1063/1.4974893

[62] O'Connor É, Cherkaoui K, Monaghan S, Sheehan B, Povey IM, Hurley PK. Effect of forming gas annealing on the inversion response and minority carrier generation lifetime of n and p-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitors. Microelectronic Engineering. 2015;**147**:325-329. DOI: 10.1016/j. mee.2015.04.103