#### **ORIGINAL ARTICLE**

# Z-domain modeling of peak current mode control for full-bridge DC-DC buck converters

Xiaohong Wang<sup>1</sup> · Qisong Huang<sup>1</sup> · Bo Zhang<sup>1</sup> · Di Chen<sup>1</sup> · Quanxue Guan<sup>2</sup>

Received: 1 August 2020 / Revised: 8 September 2020 / Accepted: 11 September 2020  $\ensuremath{\textcircled{}}$  The Author(s) 2020

#### Abstract

Traditional local-averaged state-space modeling for peak current mode (PCM) controls fails to explain the subharmonic oscillation phenomenon when the spectrum is higher than half of the switching frequency. To address this problem, this paper presents a small-signal modeling method in the z-domain, and builds a discrete linear model for the current loop of a full-bridge DC-DC converter. This discrete model is converted into a second-order continuous model that is able to represent the system performance with a wider frequency range. A frequency-domain analysis shows that this model can be used to explain the subharmonic oscillations and unstable characteristics. This provides an engineering guideline for the practical design of slope compensation. The effectiveness of the proposed modeling method has been verified by simulation and experimental results with a prototype working in the Buck mode.

Keywords DC-DC converter  $\cdot$  Peak current mode control  $\cdot$  Slope compensation  $\cdot$  Subharmonic oscillation  $\cdot$  Z-domain modeling method

# 1 Introduction

Peak current mode (PCM) control has been widely used in power electronic converters due to its accuracy, fast dynamic response and software flexibility [1, 2]. Flying capacitor Buck converters [3], flyback converters [4] and Buck LED drivers [5] are some examples of this PCM control. In fullbridge DC-DC converter applications, PCM control has a simple structure and an inherent built-in overcurrent protection mechanism [6]. Implementation is easy due to the absence of a large inertia filtering link in the current feedback control loop [7]. This also results in the PCM control having a fast response.

In general, PCM control is implemented in cascaded double-loop control structures with the stability mainly depending on the inner current loop. However, when the steady-state duty ratio is higher than 50%, the converters have alternating wide pulses and narrow pulses, namely

Quanxue Guan quanxue.guan@gmail.com subharmonic oscillations. These oscillations result in poor system stability. Thus, it is necessary to have an appropriate control [8, 9].

The key to a good PCM control is to accurately model and analyze the characteristics of the current control loop. The numerical calculation in [10-12] uses a piecewise linear discrete model to iteratively calculate the circuit response. However, this method, which ignores the influence of parasitic parameters such as the dead-time, and the on-off voltage drop of the switches, is only suitable for simulations. The state space averaging method eases the parameter design for closed-loop controllers [13–17]. However, it is only valid for the low-frequency range below half of the switching frequency. Modeling methods in z-domain [18–20] are problematic in terms of high-frequency characteristics since they are based on the same local-averaged state space method. The describing function analysis method in [21] expresses non-linearity with the fundamental component and harmonic components using the Fourier series. However, since the sampling characteristics of the switches are not taken into account, this method cannot illustrate characteristics higher than half of the switching frequency, which are of special importance in the design of high bandwidth controllers. In addition, the aforementioned methods are relatively

<sup>&</sup>lt;sup>1</sup> School of Automation Science and Engineering, South China University of Technology, Guangzhou, China

<sup>&</sup>lt;sup>2</sup> Department of Electrical and Electronic Engineering, University of Nottingham, Nottingham, UK

complicated, which means they are not intuitive enough for practical engineers. Thus, they have limited applications.

The high-frequency characteristics and subharmonic oscillation phenomenon are still less-explored for PCM control in DC-DC converter applications. In this paper, a z-domain modeling method is proposed. By analyzing the small signal step response of the PCM current loop, the geometric constraint relationship between the inductance current and the setting current at each sampling instant is established. Then, the iterative equation of the current and duty cycle are obtained. As a result, the discrete transfer function of the system is derived, which can represent the frequency characteristics above half of the switching frequency. Afterward, the model is converted to the s-domain, so that it is possible to design an appropriate slope compensation to suppress the subharmonic oscillations.

The main contribution of this paper is to propose a z-domain modeling method describing the subharmonic oscillation in the high frequency band, which can explain the instability of the PCM current loop. On the basis of this model, an optimal coefficient adjustment method is provided for slope compensation, which is of great significance to engineering design.

## 2 Model analysis and current loop modeling

# 2.1 PCM control system description

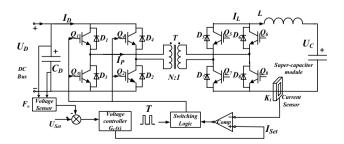

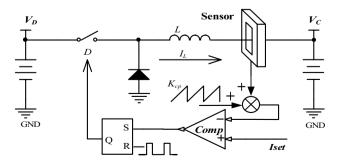

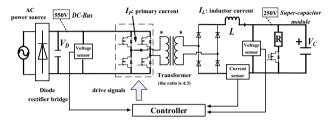

A circuit and control diagram of a full-bridge DC-DC converter is shown in Fig. 1. This converter is used for the charging and discharging of a supercapacitor. For the sake of brevity only the charging power flow in the Buck operation mode is investigated, which means the secondary side switches work as if in a synchronous rectifier.

A double closed-loop structure is adopted to control the converter, where PCM control regulates the inner current loop. The control loop includes a voltage feedback compensation network  $G_c(s)$ , a current comparator, a switching logic control unit, a voltage sensor and a current sensor, where  $F_v$  is the voltage feedback coefficient, and  $K_i$  is the current

Fig. 1 Full-bridge DC-DC converter with PCM control

sampling transfer function determined by the sensor and the conditioning circuit. The compensated voltage error signal is used to obtain the current loop setting value, and the current comparator is used to modulate the switching duty cycle signal. Then, the average voltage on the inductor is changed by adjusting the turn-on time of the switches.

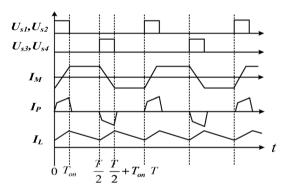

To simplify the analysis, it is assumed that the transformer is ideal and that the voltages of the DC-bus and the supercapacitor are constant during each switching period. During the steady-state, waveforms of the gate signals and inductance currents can be obtained as shown in Fig. 2.

$U_{S1}-U_{S4}$  are the driving gate signals for the switches  $Q_1-Q_4$ ,  $I_M$  is the magnetic current,  $I_P$  is the current of the transformer primary, and  $I_L$  is the output inductor current.

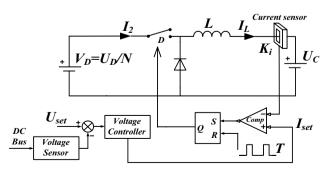

Once the closed loop controller becomes asymptoticly stable, the current loop model in Fig. 1 is equivalent to a simplified PCM circuit in a non-isolated topology as shown in Fig. 3.  $V_D = U_D/N$  is the referred voltage of the DC-bus voltage with respect to the supercapacitor side according to the turns ratio of the transformer,  $U_C$  is the supercapacitor voltage, L is the inductor, and  $I_2$  is the current flowing at the transformer secondary side.

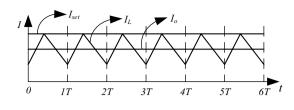

An ideal waveform of the inductor current is shown in Fig. 4, where  $I_{set}$  is the setting current,  $I_o$  is the average current, and T is a switching period.

Fig. 2 Steady-state waveforms of a converter in the Buck mode

Fig. 3 Simplified non-isolated PCM circuit in the Buck mode

Fig. 4 Inductor current according to volt-second balancing

The inductor current waveform is continuous. However, its derivative is not equal to 0, and the overall system is not at equilibrium. Therefore, it is a typical nonlinear system. To facilitate the design of the PI controllers, it is necessary to linearize the overall system around its steady-state operation point.

#### 2.2 Traditional linear approximation models

The local-averaging method in [22, 23] is a mainstream modeling method for power electronic converters. Based on the simplified structure diagram in Fig. 3, the first-order approximated current loop model with the inductor current  $I_L$  as the state variable is established as follows:

$$\dot{I}_L = \left(\frac{U_D}{NL} - \frac{U_C}{L}\right) \cdot D - \frac{U_C}{L} \cdot (1 - D) = \frac{D}{NL}U_D - \frac{U_C}{L} \quad (1)$$

Consider the small-signal model  $I_L$ , D,  $U_D$ , and  $U_C$  which are composed of an average value and ripple components:

$$I_L = \overline{I}_L + \hat{I}_L, D = \overline{D} + \hat{D}, U_D = \overline{U}_D + \hat{U}_D, U_C = \overline{U}_C + \hat{U}_C$$

(2)

After substituting (2) into (1) and removing the static values, the nonlinear state model can be established as:

$$\dot{I}_L = \frac{\overline{D}}{NL}\hat{U}_D + \frac{\overline{U}_D}{NL}\hat{D} - \frac{\hat{U}_C}{L}$$

(3)

Suppose  $K_1$  is the on-time slope of the inductor current. Then, the duty cycle reference in the current loop can be expressed below:

$$D = \frac{T_{on}}{T} = \frac{(I_{set} - I_L K_i)}{T \cdot K_1 K_i} = (I_{set} - I_L K_i) G_1$$

(4)

where  $G_1 = \frac{1}{T \cdot K_1 K_i}$ ,  $K_1 = \frac{V_D - V_C}{L}$ .

According to (2) and (4), the small signal of the duty cycle in the peak current mode can be the approximately expressed as:

$$\hat{D} \approx \left(\hat{I}_{set} - \hat{I}_L K_i\right) G_1 \tag{5}$$

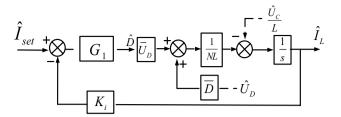

From Eqs. (1)–(5), a block diagram of the current loop can be drawn as shown in Fig. 5.

Fig. 5 Control block diagram based on the state-space averaging method

Therefore, the AC small signal transfer function is as follows:

$$G_{Buck}(s) = \left. \frac{\hat{I}_L(S)}{\hat{I}_{set}(S)} \right|_{\hat{U}_D(S) = \hat{U}_C(S) = 0} = \frac{1}{K_i} \frac{1}{\frac{NL}{\overline{U}_D G_1} s + 1}$$

(6)

It can be seen from the transfer function that the system has only one pole in the left half plane and that the system is stable at any duty cycle. However, in actual situations, the inductor current oscillates when D > 0.5. Obviously, Eq. (6) cannot describe this unstable phenomenon.

#### 2.3 Analysis of subharmonic oscillation

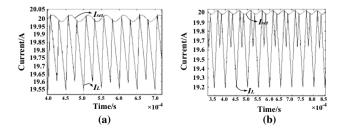

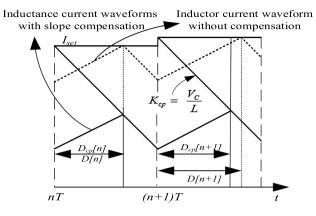

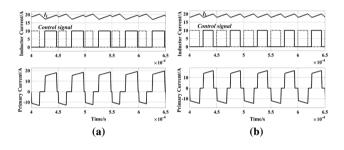

Subharmonic oscillation and instability are the two main problems of PCM control [5, 24, 25]. When  $V_C/V_D$  is close to 0.5, the angle between the rising curves of  $I_L$  and  $I_{set}$  is smaller than the angle between the falling curves of  $I_L$  and  $I_{set}$ . When there is a disturbance in the input, after a gradual accumulation of disturbances over several switching cycles, the duty cycle of two adjacent switching cycles has one large and one small response, which are asymmetric at the switching frequency [26]. The current loop causes subharmonic oscillation, as shown in Fig. 6.

Suppose the current loop input is added to a disturbance signal with an amplitude of one thousandth of the setting current and a frequency of one-half of the switching frequency. When  $V_C/V_D$  is close to 0.5, the current loop exhibits

Fig. 6 Time-domain response of a current loop under a sinusoidal disturbance input at half the switching frequency: **a**  $V_C/V_D = 0.25$ ; **b**  $V_C/V_D = 0.5$

an amplitude amplification at the selective frequency of  $\frac{1}{2}$  the switching frequency [27, 28].

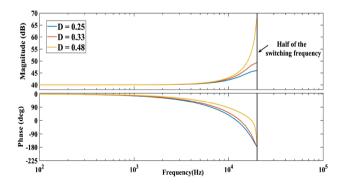

This amplification effect can weaken the disturbance suppression capability of the system, reduce the equivalent switching frequency by half, or even lead the system to instability. The results in Fig. 7 show that when the output voltage approaches half the input voltage, a low damping characteristic is exhibited by the signal in the band around the half the switching frequency. In addition, the amplification of the loop amplitude at this frequency increases sharply until it reaches the critical stability condition. In this process, the current loop gradually evolves into an oscillator at half the switching-frequency.

Phase lag information of the current loop under different input and output conditions is also obtained by frequencydomain analysis.

The bifurcation and oscillation phenomenon in the PCM current loop structure have been explained in [29]. During the process of a proportional increase between the output voltage and the input voltage of a full-bridge DC-DC converter, the steady state of the current loop enters the bifurcation state from the volt-second equilibrium state. Then, the oscillation phenomenon occurs.

# 3 Stability analysis and slope compensation

## 3.1 The proposed discrete modeling method

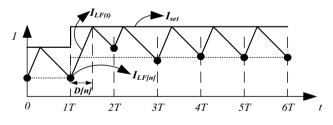

It can be seen from the steady-state operating waveforms of the full-bridge DC-DC converter in Fig. 4, that the rising and falling slopes of the inductor current, the setting current and the current of the starting points at two adjacent switching cycles form a geometric constraint relationship.

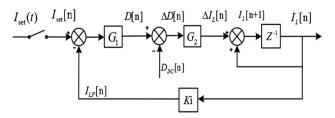

Let  $I_{set}[n]$ ,  $I_L[n]$ , and D[n] be the discretization values of the setting current  $I_{set}$ , the inductor current  $I_L$  at the start of the sampling period and the duty cycle D during the switching period in the current loop, respectively. Based on the geometric

**Fig. 7** Amplitude-frequency characteristics of  $G_I(Z)$  with various output-input voltage ratios

relationship of each variable under the step response, as shown in Fig. 8, a recurrence relationship can be created.

- (1) Using the tangent theorem of the triangle, the duty cycle D[n] can be calculated by  $I_{set}[n]$ ,  $I_L[n]$ , and the rising slope of the inductor current.

- (2) The increment of the inductor current  $\Delta I_L[n]$  during this period is determined by the difference between D[n] and the steady-state duty cycle  $D_{\text{DC}}[n]$ , which is determined by the volt-second balance.

- (3) By accumulating the values of  $I_L[n]$  and  $\Delta I_L[n]$  of the present cycle, the inductor current value  $I_L[n+1]$  of the next cycle can be derived.

A step response diagram of the current loop operating at a duty cycle of 0.33 is illustrated in Fig. 8. A dynamic structure diagram of this recurrence relation is shown in Fig. 9.  $K_i$  is the current feedback constant coefficient in the actual circuit shown in Fig. 1, and  $I_{IE}[n]$  is the current feedback signal.

From the geometric relationship of Fig. 8, the duty cycle of each sampling time is:

$$D[n] = (I_{set}[n] - I_{LF}[n]) \frac{1}{K_1 K_i T}$$

(7)

The incremental change in the inductor current between two sampling instants can be expressed as:

$$\Delta I_L[n] = (D[n] - D_{DC}[n]) \frac{V_D}{L} T$$

(8)

$D_{\rm DC}$  is the steady-state duty cycle determined by the voltsecond balancing principle, which results in:

Fig. 8 Typical small-signal step response of PCM current control

Fig. 9 Block diagram for the proposed PCM current control

$$K_{1} = \frac{V_{D} - V_{C}}{L}, D_{DC}[n] = \frac{V_{C}}{V_{D}}$$

(9)

The transfer functions of the overall dynamic structure diagram in Fig. 9 can be obtained according to (7)–(9):

$$G_{1} = \frac{L}{(V_{D} - V_{C})K_{i} \cdot T}, G_{2} = \frac{V_{D}}{L}T$$

(10)

Therefore, the system shown in Fig. 9 is a simple first-order discrete linear time-invariant system. With the current achieving volt-second balance, the steady-state duty cycle  $D_{DC}[n]$  in the structure diagram can be removed to sort out the z-domain small-signal model of the PCM current loop so that the transfer function of  $G_f(Z)$  can be obtained as follows:

$$G_{I}(Z) = \frac{G_{1}G_{2}}{Z + (G_{1}G_{2}K_{i} - 1)} = \frac{\frac{V_{D}}{(V_{D} - V_{C})K_{i}}}{Z + (\frac{V_{D}}{V_{D} - V_{C}} - 1)}$$

(11)

The pole position is used to determine the stability and frequency response characteristics of the current loop on the z-domain. In practice, it is necessary to further manipulate  $G_I(Z)$  in Eq. (11) by quantifying the frequency domain characteristics in a unit circle of the s-domain to provide a theoretical basis for system stability analysis and oscillation suppression. Therefore, by replacing Z in Eq. (11) with  $e^{sTs}$ , and multiplying the transfer function of the zero-order sample-hold effect [30], the continuation of the discrete model  $G_I(Z)$  can be obtained as follows:

$$G_{I}(S) = \frac{\frac{V_{D}}{(V_{D} - V_{C})K_{i}}}{e^{sT_{s}} + (\frac{V_{D}}{V_{D} - V_{C}} - 1)} \cdot \frac{1 - e^{-sT_{s}}}{s} \cdot f_{s}$$

(12)

According to the second-order Pade function,  $e^{sTs}$  can be approximately equal to:

$$e^{sT_s} \approx \frac{s^2 + 6f_s s + 12f_s^2}{s^2 - 6f_s s + 12f_s^2}, \quad \left(T_s = \frac{1}{f_s}\right)$$

(13)

Table 1

DC-DC converter parameters

| Parameter                                                                        | VALUE        |

|----------------------------------------------------------------------------------|--------------|

| Switching frequency $(f_s)$                                                      | 40 kHz       |

| Transformer turns ratio (N)                                                      | 4:3          |

| Inductance of L                                                                  | 1 mH         |

| Capacitance of supercapacitor module                                             | 20 F         |

| Voltage of DC-bus $(U_D)$                                                        | 550 V        |

| Voltage of supercapacitor module $(V_C)$<br>Current feedback coefficient $(K_i)$ | 250 V<br>0.1 |

Therefore, the s-domain transfer function of the discrete model can be obtained as follows:

$$G_I(S) = e^{-sT_s} \cdot \frac{k}{s^2 + 6f_s rs + 12f_s^2}$$

(14)

where  $k = 12f_s^2/K_i$ , and  $r = 1 - 2D_{DC}$ .

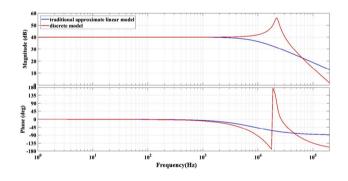

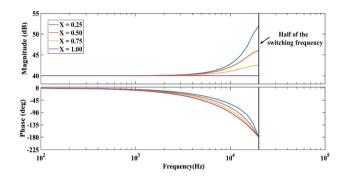

An example using the parameters listed in Table 1 is presented below to show the advantages of the proposed discrete model over the traditional state-space averaging model. Bode diagrams of both models are shown in Fig. 10. When compared with the traditional linear model, the proposed discrete model is more consistent with the actual performance of a system in the high-frequency band.

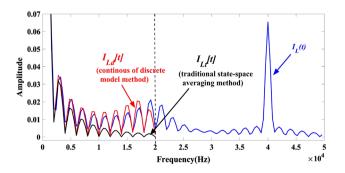

This can be seen more clearly from a spectrum comparison of three current signals after processing by the Chebyshev window as shown in Fig. 11. Among them,  $I_L(t)$  is the actual inductor current, while  $I_{Lt}(t)$  and  $I_{Ld}[t]$  are obtained by the traditional state-space averaging model and the discrete model, respectively.

The spectrum difference between  $I_{Ld}[t]$  and  $I_L(t)$  is small within a quarter of the switching frequency. The accuracy of the model is still acceptable when the frequency is close to half the switching frequency since the effect of the duty cycle on the inductor current can be correctly reflected. For practical engineering purposes, it is convenient to carry out

Fig. 10 Bode diagram of the traditional approximation linear model and the proposed discrete model

Fig. 11 Spectrum comparison of traditional and discrete methods

the analysis using the traditional approximation. However, the large discrepancy between  $I_L(t)$  and  $I_{Lt}(t)$  after half of the switching frequency shows the inherent disadvantages in the traditional state space average method. The spectrum of the inductor current is not well matched and cannot reflect the oscillation at  $\frac{1}{2}$  the switching frequency.

## 3.2 Slope compensation model mechanism

According to the analysis in Sect. 3.1, in order to stabilize the current loop of the system, feedback correction is usually considered to reconfigure the unstable pole of  $G_I(z)$ . For example, the average current mode control in [31] can be used. Slope compensation that superimposes a rising slope signal on the current feedback signal is used to stabilize the PCM current loop [32–35].

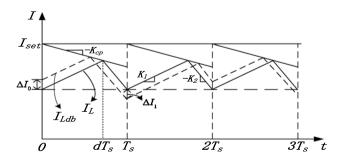

As shown in Fig. 12,  $I_{set}$  is the setting current,  $I_L$  is the inductor current without disturbances added,  $I_{Ldb}$  is the inductor current with disturbances added,  $\Delta I_0$  and  $\Delta I_1$  indicates the current error at the beginning and end of the period,  $K_1$  and  $K_2$  are the on-time and off-time slopes of the inductor current ( $K_1 = (V_D - V_C)/L$ ,  $K_2 = V_C/L$ ),  $K_{cp}$  is the compensation slope, and *Ts* is the switching period.

With the help of slope compensation, the disturbance influence on the current can be suppressed or even eliminated, as shown in Fig. 12. However, it is still not sufficient to explain and solve the problem of subharmonic oscillations.

To address this, it is interesting to analyze the effect of slope compensation. Then, the analytical optimal value of the compensation slope  $K_{cp}$  should be derived by analyzing the z-domain system model presented in Sect. 3.1.

According to Fig. 9 and Eq. (9), the pole of the current loop is:

$$1 - G_1 G_2 K_i = 1 - \frac{1}{K_1 K_i} \frac{V_D}{L} K_i = 1 - \frac{V_D}{V_D - V_C}$$

(15)

This indicates that instability only depends on the operating points of the input and output voltage, and that it has nothing to do with other parameters, which means that

Fig. 12 Current waveforms and slope compensation

changing the system internal parameters cannot eliminate instability. When the switching device is turned on, the lack of a rise rate causes the gain of the current loop to be too large. Therefore, the crux of the problem is to reduce the loop gain of the current loop without changing the input and output voltage conditions. The solution adopted in this paper is to superimpose a rising slope signal on the current feedback signal, as shown in Fig. 13. In this way, the error at the starting point of the switching cycle results in a lower duty cycle output, which is equivalent to a reduction in the loop gain.

The expressions of the compensated current open-loop gain are as follows:

$$G_1 G_2 K_i = \frac{1}{\left(K_1 + K_{cp}\right)K_i \cdot T} \cdot \frac{V_{\rm D}}{L} T \cdot K_i = \frac{1}{\frac{V_{\rm D} - V_{\rm C}}{L} + K_{cp}} \frac{V_{\rm D}}{L}$$

(16)

The condition for system stability is shown below:

$$\left|G_{1}G_{2}K_{i}-1\right|<1$$

(17)

or:

$$G_1 G_2 K_i = \frac{V_D}{V_D - V_C + L K_{cp}} < 2$$

(18)

Therefore, the inequality for the critical compensation condition is:

$$K_{cp} > \frac{V_C - 0.5V_D}{L} = \frac{(D_{DC} - 0.5)V_D}{L}$$

(19)

If the compensation slope increases to the critical value, the compensation slope is equal to the absolute value of the inductor current falling slope. At this time,  $K_{cp} = V_C/L$ and the pole of the current loop are pushed towards the origin of the Z-plane. Then, the current loop becomes a timedelayed first-order system. For step inputs in the range of the small signal, the subharmonic oscillation of the current loop is well suppressed. However, the adjusting time is as

Fig. 13 Slope compensation circuit

**Fig. 14** Current loop step responses with  $K_{cp} = V_C/L$

Fig. 15 Current loop amplitude-frequency characteristic with various compensation slopes

long as one switching period, as shown in Fig. 14, where  $D_{cp}[n]$  is the duty cycle with slope compensation.

Since the fixed slope rate is not suitable for all of the operating conditions, the compensation slope is parameterized for easy adjustments.

$$K_{cp} = \frac{\left(D_{DC} - 0.5 + 0.5X\right)V_D}{L} \tag{20}$$

where X is the normalized slope adjustment parameter with a value range of (0, 1]. Accordingly, the range of the slope  $K_{cp}$  is in the range of  $[(V_C - 0.5V_D)/L, V_C/L]$ . In these cases, the z-domain small signal transfer function of the PCM current loop can be expressed as follows:

$$G_d(Z) = \frac{G_1 G_2}{Z + (G_1 G_2 K_i - 1)} = \frac{\frac{V_D}{(V_D - V_C) + LK_{cp}} \cdot \frac{1}{K_i}}{Z + \left(\frac{V_D}{(V_D - V_C) + LK_{cp}} - 1\right)}$$

(21)

To observe the effect of slope compensation, the compensation coefficient X is increased in steps of 0.25. The current loop Bode diagram characteristics for different values of Xare shown in Fig. 15. It is important to note that with an increase of the coefficient X, the damping for the high-frequency signal gradually increases. In addition, the phase shift also increases. In other words, increasing the slope compensation  $K_{cp}$  can improve the stability of the system. However, it also affect the response speed of the system.

Following the analysis in Sect. 3.1, the s-domain expression of  $G_d(Z)$  can be obtained by Eqs. (20)-(21) as follows:

$$G_{d}(S) = e^{-sT_{s}} \cdot \frac{12f_{s}^{2}}{s^{2} + 6f_{s}r_{d}s + 12f_{s}^{2}} = e^{-sT_{s}} \cdot G_{k}(S)$$

$$r_{d} = 1 - \frac{2}{V_{D}} \cdot (V_{C} - LK_{cp}) = X$$

(22)

According to Eq. (22), the dynamic performance and the steady-state performance of the system are mainly determined by  $G_k(S)$ . Therefore, comparing this with a standard second-order system yields:

$$\omega_n = 2\sqrt{3}f_s$$

$$\xi = \frac{3f_s r_d}{\omega_n}$$

(23)

where  $\omega_n$  is the natural oscillation frequency, and  $\zeta$  is the damping of the system.

Substituting Eq. (23) into Eq. (22), the normalized slope adjustment parameter *X* can be calculated as:

$$X = \frac{\xi \omega_n}{3f_s} = \frac{2\sqrt{3}}{3} \cdot \xi \tag{24}$$

In engineering applications, while ensuring the stability of the system, the response speed of the system should be increased as much as possible. Therefore, the damping coefficient  $\zeta$  for the system is often set to 0.707, which is the optimal damping coefficient.

However, the introduction of the coefficient X brings peak inductor current errors. When X increases, the error increases. As can be seen from Fig. 14, when the slope compensation reaches its maximum value, the actual inductor current cannot approach its reference setting. Therefore, the current setting value needs to be modified according to the slope compensation  $K_{cp}$  together with the steady-state duty cycle D, as shown below:

$$I_{\text{set}}^* = I_{\text{set}} + K_{CP} \cdot D \cdot T \tag{25}$$

After modifying the setting value, the actual peak inductor current is equal to  $I_{set}^*$ . In an ideal case, the error caused by the peak current control can be eliminated.

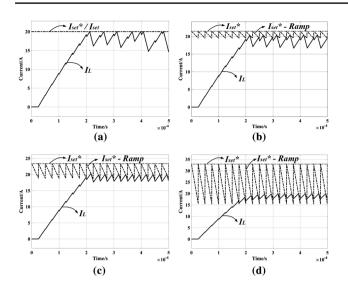

**Fig. 16** Current loop step responses under different slope compensation coefficients: **a** X = -0.38,  $K_{cp} = 0$ ; **b** X = 0,  $K_{cp} = 43,750$ ; **c** X = 0.8164,  $K_{cp} = 212,130$ ; **d** X = 3,  $K_{cp} = 662,500$

Fig. 17 Steady-state current waveforms with different slope compensation coefficients: **a** X=0,  $K_{cp}$ =43,750; **b** X=0.8164,  $K_{cp}$ =212,130

# 4 Simulation and experimental results

## 4.1 Simulation results

A current loop model is built in MATLAB/Simulink to control a full-bridge DC-DC converter working in the Buck mode. The specified parameters set according to an actual system are shown in Table 1. The target inductor current range of the current loop is 0-20A. In this subsection, the effects of the slope compensation on the dynamic and steady-state performances are analyzed by simulations.

In this example, X is chosen as 0.8164 to have the optimal damping coefficient of 0.707. Then, the slope compensation  $K_{cp}$  can be obtained by Eq. (20). The current setting value  $I_{set}$  is modified based on Eq. (25). When the current loop is suddenly set at 20A, the current of systems steps up, and the results are shown in Fig. 16 and Fig. 17.

With an increase of the slope compensation coefficient *X*, the subharmonic oscillation phenomenon is gradually

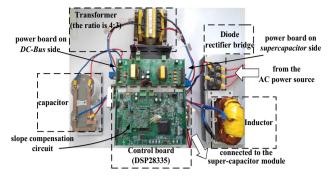

Fig. 18 Experimental prototype set-up

Fig. 19 Control structure of the experimental full-bridge DC-DC Buck converter

suppressed. However, if X is too large, the response speed of the current loop becomes slow, as shown in Fig. 16. When X is equal to 0.8164, the steady-state performance of the current loop is greatly improved. Meanwhile, it also ensures that the system has fast response. This validates the theoretical analysis in Sect. 3, where the system achieves good dynamic and steady-state performances by adding an appropriate slope compensation.

#### 4.2 Experimental results

Experiments were carried out to validate the discrete model and the slope compensation technique. The experimental set-up is shown in Fig. 18. The structure diagram and initial condition settings are shown in Fig. 19. Supercapacitor modular energy storage devices were used as loads at the low-voltage side with the rated voltage being 360 V. The DC-bus supply was used at the high-voltage side, which was made up of an AC power source and a diode rectifier bridge.

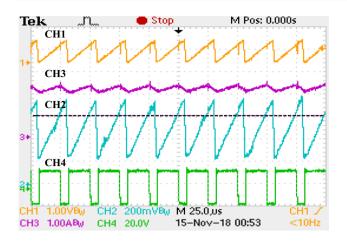

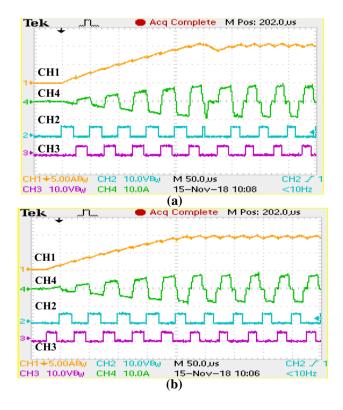

During the experiments, the sampled value of the inductor current was superimposed with a ramp signal, and compared with the setting value, which generates a duty cycle modulation signal. In Fig. 20, CH1 is the ramp signal generated by the ramp circuit according to  $K_{cp}$ , CH3 is the inductor current, CH2 represents the inductor current of the superimposed ramp signal after gain adjustment, and CH4 is the duty cycle signal. The dotted line in the figure indicates the simulated setting value of the inductor current.

Fig. 20 Ramp signal and duty cycle waveforms

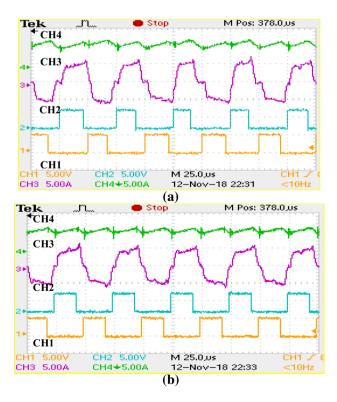

The system was set according to the initial conditions shown in Table 1. When the current loop was suddenly set to 10A, the current of the system steps up, and the experimental waveform is shown in Fig. 21. In this figure, CH1 is the inductor current waveform, CH4 is the primary current waveform, and CH2 and CH3 are the PWM drive signals of the full-bridge module. Due to the addition of the ramp

signal, a corresponding peak error was generated, which had been compensated by the correction formula (25).

Under the effect of the step response, the system worked in the maximum duty cycle, and the inductor current rose rapidly. However, the subharmonic oscillation phenomenon appeared as shown in Fig. 21a. The optimal value of the slope compensation can be calculated by Eqs. (20), (24), (25) and the corresponding current waveforms are shown in Fig. 21b. When compared with Fig. 21a, it can be seen that the subharmonic oscillation with the new slope compensation was well suppressed. Thus, the inductor current and the primary current were more stable.

Steady-state results are given in Fig. 22 with the same initial conditions. CH1 and CH2 are the PWM drive signals of the full-bridge switches, CH3 is the primary current, and CH4 is the inductor current.

The waveforms in Fig. 22 show that the duty cycles of two adjacent switching cycles have one large and one small response when no slope compensation is added. This is consistent with the analysis in Sect. 3. The presented inductor current and primary current waveforms exhibited subharmonic oscillations, and the transformer emitted significant noise. With the addition of appropriate slope compensation, all of the current waveforms remained stable and the subharmonic oscillations were eliminated.

**Fig. 21** Step response transient waveforms with different slope compensation coefficients when: **a** X=0,  $K_{cp}=43,750$ ; **b** X=0.8164,  $K_{cp}=212,130$

**Fig. 22** Steady-state waveforms with different slope compensation coefficients in experiments when: **a** X=0,  $K_{cp}=43,750$ ; **b** X=0.8164,  $K_{cp}=212,130$

# 5 Conclusion

In this paper, a small-signal discrete modeling method was presented and analyzed in the z-domain for the peak-current mode (PCM) control of full-bridge isolated DC-DC Buck converters. This new modeling method can improve the linear approximate accuracy of converters in the highfrequency band above half of the switching frequency when compared with existing local-averaged modeling methods. The new modeling method can be used to explain the instability problem of current control loops. Furthermore, an adjustable slope compensation coefficient has been provided based on the system model in the z-domain, which makes the slope compensation reliable and optimal. Simulation and experimental results have been shown to verify the accuracy of the modeling method, and the capability of the adjustable slope compensation in suppressing the subharmonic oscillations and improving dynamic and steady-state performance.

Acknowledgements This work was supported in part by the Science and Technology Major Project of Guangdong Province under Grant 2016B090911003, Science and Technology Major Project of Guangzhou under Grant 201902010066 and the National Natural Science Foundation of China under Grant 51707042.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

### References

- Abdelhamid, E., Bonanno, G., Corradini, L., Mattavelli, P., Agostinelli, M.: Stability properties of the 3-Level flying capacitor buck converter under peak or valley current programmed control. IEEE Trans. Power Electron. 34(8), 8031–8044 (2019)

- Kobayashi, N., Hayashi, Y., Iyasu, S., Handa, Y.: Fast current control of the single-phase DC-AC converter using digital peak current mode control. In: 2019 21st European Conference on Power Electronics and Applications, pp. 1–7, Genova (2019)

- Bao, B., Zhang, X., Bao, H., Wu, P., Wu, Z., Chen, M.: Dynamical effects of memristive load on peak current mode buck-boost switching converter. Chaos Solitons Fractals 122, 69–79 (2019)

- Cheng, C.-H., Chen, C.-J., Wang, S.-S.: Small-signal model of flyback converter in continuous-conduction mode with peak-current control at variable switching frequency. IEEE Trans. Power Electron. 33(5), 4145–4156 (2018)

- 5. Leng, M., Zhou, G., Zhou, S., Zhang, K., Xu, S.: Stability analysis for peak current-mode controlled buck LED driver based on

discrete-time modeling. IEEE J. Emerg. Sel. Topics Power Electron. **6**(3), 1567–1580 (2018)

- Taeed F., Nymand, M.: A new simple and high performance digital peak current mode controller for DC-DC converters. In: 2014 IEEE Applied Power Electronics Conference and Exposition, pp. 1213–1218 (2014)

- Sha, J., Xu, D., Chen, Y., Xu, J., Williams, B.W.: A peak-capacitor-current pulse-train-controlled buck converter with fast transient response and a wide load range. IEEE Trans. Ind. Electron. 63(3), 1528–1538 (2016)

- Kajiwara, K., Maruta, H., Shibata, Y., Matsui, N., Kurokawa F., Hirose, K.: Wide input digital peak current mode DC-DC converter for DC power feeding system. In: IEEE International Telecommunications Energy Conference, pp. 1–4 (2016)

- Ramya Chandranadhan V., Renjini G.: Comparison between peak and average current mode control of improved bridgeless flyback rectifier with bidirectional switch. In: International Conference on Technological Advancements in Power and Energy, pp. 254–259 (2015)

- Xie, G., Xu, H.: Modeling of current programmed mode nonideal buck converter systems. Proc. CSEE 32(24), 52–58 (2012)

- Nam, H., Ahn, Y., Roh, J.: 5-V buck converter using 3.3-V standard CMOS process with adaptive power transistor driver increasing efficiency and maximum load capacity. IEEE Trans. Power Electron. 27(1), 463–471 (2012)

- Liu, J., Wang, P., Kuo, T.: A current-mode DC–DC buck converter with efficiency-optimized frequency control and reconfigurable compensation. IEEE Trans. Power Electron. 27(2), 869–880 (2012)

- Salem, M., Jusoh, A., et al.: Steady state and generalized state space averaging analysis of the series resonant converter. In: 3rd IET International Conference, Clean Energy and Technology, pp. 1–5 (2014)

- Ridley, R.B.: A new, continuous-time model for current-mode control. IEEE Trans. Power Electron. 6(2), 271–280 (2002)

- Murthy, A., Badawy, M.: State space averaging model of a dual stage converter in discontinuous conduction mode. In: IEEE 18th Workshop on Control and Modeling for Power Electronics, pp. 1–7 (2017)

- Salem, M., Jusoh, A., Idris, N.R.N., Alhamrouni, I.: Modeling and simulation of generalized state space averaging for series resonant converter. In: Australasian Universities Power Engineering Conference, pp. 1–5 (2014)

- Budaes, M., Goras, L.: An averaging small-signal model for a DC-DC switched capacitor converter. In: International Semiconductor Conference, pp. 547–550 (2007)

- Mayer, E. A.: Using modified z-transforms to model the step response of the peak current-mode controlled buck converter. In: IEEE International Conference on Electro/Information Technology, pp. 193–196 (2008)

- Mayer, E.A., King, R.J.: An improved sampled-data currentmode-control model which explains the effects of control delay. IEEE Trans. Power Electron. 16(3), 369–374 (2001)

- VandeSype, D.M., DeGusseme, K., DeBelie, F.M.L.L., Vanden-Bossche, A.P., Melkebeek, J.A.: Small-signal z-domain analysis of digitally controlled converters. IEEE Trans. Power Electron. 21(2), 470–478 (2006)

- Suryanarayana, K., Prabhu, L.V., Anantha, S., Vishwas, K.: Analysis and modeling of digital peak current mode control. In: IEEE International Conference on Power Electronics, Drives and Energy Systems, pp. 1–6 (2012)

- 22. Wang, H., Wu, Y.: Modeling and simulation of FB ZVS-PWM converter. Telecom Power Technol. **25**(5), 41–45 (2008)

- Chen, S.: Small-signal model for a flyback converter with peak current mode control. IET Power Electron. 7(4), 805–810 (2014)

- 24. Fang, C., Chen, C.: Subharmonic instability limits for V2-controlled buck converter with outer loop closed/open. IEEE Trans. Power Electron. 31(2), 1657–1664 (2016)

- 25. Peng, C., Wu, M., Yue, D.: Working region and stability analysis of PV cells under the peak-current-mode Control. IEEE Trans. Control Syst. Technol. 26(1), 352-359 (2018)

- 26. Wei, L., Liu, Y., Zhang, Y.: Sub-harmonic oscillation of switching power supply with peak-current mode. Inf. Electron. Eng. 7(4), 330-334 (2009)

- 27. Basak, B., Parui, S.: Exploration of bifurcation and chaos in buck converter supplied from a rectifier. IEEE Trans. Power Electron. 25(6), 1556-1564 (2010)

- 28. Zhang, Y., Qin, H., Qu, Y., Wu, J.: Chaos phenomenon in the DC-DC switching converters. In: Proceedings of the 10th World Congress on Intelligent Control and Automation, pp. 2039-2043 (2012)

- 29. Gavagsaz-Ghoachani, R., et al.: Estimation of the bifurcation point of a modulated-hysteresis current-controlled DC-DC boost converter: stability analysis and experimental verification. IET Power Electron. 8(11), 2195–2203 (2015)

- 30. Zhu, D., Wang, Y., Duan J., Wang, R.: Modeling and bifurcation analysis of buck converters under peak current-mode control. In: Chinese Automation Congress, pp. 2563-2568 (2018)

- 31. Yan, Y., Lee, F.C., Mattavelli, P.: I^2 Average current mode control for switching converters. IEEE Trans. Power Electron. 29(4), 2027-2036 (2014)

- 32. Hallworth, M., Shirsavar, S.A.: Microcontroller-based peak current mode control using digital slope compensation. IEEE Trans. Power Electron. 27(7), 3340-3351 (2012)

- 33. Tian, F., Kasemsan, S., Batarseh, I.: An adaptive slope compensation for the single-stage inverter with peak current-mode control. IEEE Trans. Power Electron. 26(10), 2857-2862 (2011)

- 34. El Aroudi, A., Mandal, K., Giaouris, D., et al.: Self-compensation of DC-DC converters under peak current mode control. Electron. Lett. 53(5), 345-347 (2017)

- 35. Taeed, F., Nymand, M.: High-performance digital replica of analogue peak current mode control for DC-DC converter. IET Power Electron. 9(4), 809-816 (2016)

Science and Technology, Harbin, China, in 1999; his M.S. degree in Power Electronics and Power Drives from the Harbin Institute of Technology, Harbin, China, in 2003; and his Ph.D. degree in Control Theory and Control Engineering from the South China University of Technology, Guangzhou, China, in 2009. From 2009 to 2012, he was a Post-Doctoral Researcher at the Hitachi Elevator (China) Co., Ltd., Guangzhou, China. Since 2010, he has been an Associate Profes-

Xiaohong Wang received his B.S.

degree in Industrial Automation

from the Harbin University of

sor in the School of Automation, South China University of Technology. He has authored or co-authored over 80 papers in international journal and conference proceedings. His current research interests include power electronic topologies and applications in renewable energy generation and energy-saving systems, motion control, and servo and robot systems.

Qisong Huang received his B.S. degree in Automation from Shenzhen University, Shenzhen, China, in 2018. He is presently working towards his M.S. degree in Control Engineering at the South China University of Technology, Guangzhou, China. His current research interests include power electronics and motion control technology.

Bo Zhang received his B.S. degree in Automation from Hangzhou Electronic Science and Technology University, Hangzhou, China, in 2017; and his M.S. degree in Control Engineering at the South China University of Technology, Guangzhou, China, in 2020. His current research interests include power electronics technology and its application in renewable energy generation systems.

Nottingham, Nottingham, UK since 2017.

Quanxue Guan received his B.S. degree in Automation Engineering from the South China University of Technology, Guangzhou, China, in 2007. He started his combined M.Sc./Ph.D. program in Control Theory and Control Applications since 2009 and received his Ph.D. degree in Power Electronics and Motor Drives from the South China University of Technology, Guangzhou, China, in 2016. He has been a Research Fellow in the Power Electronics and Motor Control Group, University of