### Dynamic Dependability Analysis using HOL Theorem Proving with Application in Multiprocessor Systems

Yassmeen Elderhalli

A Thesis

in

The Department

of

Electrical and Computer Engineering

Presented in Partial Fulfillment of the Requirements

For the Degree of

Doctor of Philosophy (Electrical and Computer Engineering) at

Concordia University

Montréal, Québec, Canada

October 2019

© Yassmeen Elderhalli, 2019

#### **CONCORDIA UNIVERSITY**

#### SCHOOL OF GRADUATE STUDIES

This is to certify that the thesis prepared

Entitled: Dynamic Dependability Analysis using HOL Theorem Proving with Application in Multiprocessor Systems

and submitted in partial fulfillment of the requirements for the degree of

Doctor Of Philosophy (Electrical and Computer Engineering)

complies with the regulations of the University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

|                             | Chair               |

|-----------------------------|---------------------|

| Dr. Rene Witte              |                     |

|                             | External Examiner   |

| Dr. William M. Farmer       |                     |

|                             | External to Program |

| Dr. Rajagopalan Jayakumar   |                     |

|                             | Examiner            |

| Dr. Yan Liu                 |                     |

|                             | Examiner            |

| Dr. Mohammed Reza Soleymani |                     |

|                             | Thesis Supervisor   |

| Dr. Sofiène Tahar           | -                   |

Dr. Rastko Selmic, Graduate Program Director

December 9, 2019

Dr. Amir Asif, Dean Gina Cody School of Engineering & Computer Science

#### ABSTRACT

Dynamic Dependability Analysis using HOL Theorem Proving with Application in Multiprocessor Systems

Yassmeen Elderhalli, Ph.D.

Concordia University, 2019

Dynamic dependability analysis has become an essential step in the design process of safety-critical systems to ensure the delivery of a trusted service without failures. Dependability usually encompasses several attributes, such as reliability and availability. A dynamic dependability model is created using one of the dependability modeling techniques, such as Dynamic Fault Trees (DFTs) and Dynamic Reliability Block Diagrams (DRBDs). Several analysis methods, including paper-and-pencil or simulation, exist for analyzing these models to ascertain various dependability related parameters. However, their results cannot be always trusted since they may involve some approximations, truncations or even errors. Formal methods, such as model checking and theorem proving, can be used to overcome these inaccuracy limitations due to their inherent soundness and completeness. However, model checking suffers from state-space explosion if the state space is large. While, theorem proving was used only for the static dependability analysis without considering the system dynamics.

In order to conduct the formal dependability analysis of systems that exhibit dynamic failure behaviors within a theorem prover, these models need to be captured formally, where their structures, operators and properties are properly formalized. In this thesis, we provide a complete framework for the formal dependability analysis of systems modeled as DFTs and DRBDs in the HOL4 higher-order logic theorem prover. We provide the formalization of DFT gates and verify important simplification theorems based on well-known DFT algebra. In addition, our framework allows both qualitative and quantitative DFT analyses to be conducted using theorem proving. We use this formalization to formally verify the DFT rewrite rules, that are used by automated DFT analysis tools, to ascertain their correctness. Due to the lack of a DRBD algebra that allows the analysis using a theorem prover, in this thesis, we develop and formalize a novel algebra that includes operators and simplification theorems to formalize traditional RBD structures, such as the series and parallel, besides the DRBD spare construct. We formally verify their reliability expressions, which allows conducting both the qualitative and quantitative analyses of a given system. Leveraging upon the complementary nature of DFTs and DRBDs, our proposed framework provides the possibility of formally converting one model to the other, which allows reasoning about both the success and failure of a given system. Our framework provides generic expressions of probability of failure and reliability that are independent of the failure distribution of an arbitrary number of system components, which cannot be obtained using other formal tools, such as model checking. In order to demonstrate the usefulness of the proposed framework, we formally model and analyze the dependability of the terminal, broadcast and network reliability of shuffle-exchange networks, which are multistage interconnections networks that are used to connect the elements of multiprocessor systems. Conducting a sound analysis with generic expressions is essential in these systems, where it is required to accurately capture and analyze the failure behavior.

To my father, my mother, my sister and brothers

#### ACKNOWLEDGEMENTS

First of all, I am profoundly grateful to my supervisor, Dr. Sofiène Tahar, for his guidance, support and encouragement throughout my Ph.D. studies. His deep expertise in the field of formal methods has greatly boosted my Ph.D. He showed deep confidence in my work and never hesitated to travel and present it when I could not.

I am indebted to Dr. Osman Hasan for providing me with his support, technical feedback, encouragement and advice. I have learned a lot from his deep knowledge and immense experience. His valuable comments and our discussions have helped strengthen this work. Many thanks to Muhammed Qasim for his valuable comments about his HOL4 theories and Muhammad Umair Siddique for his suggestions.

I would like to express my gratitude to Dr. William Farmer for accepting to be my external Ph.D. thesis examiner. I am also grateful to Dr. Rajagopalan Jayakumar, Dr. Reza Soleymani and Dr. Yan Liu for serving on my advisory thesis committee.

I am very thankful to Dr. Asim Al-Khalili for his continuous encouragement and support. He was always available when I needed his advice. Many thanks to my friends and colleagues at the Hardware Verification Group (HVG), specially Hassnaa El-derhalli, Mbarka Soualhia, Mahmoud Masadeh and Saif Najmeddin, for being kind, supportive and helpful. Their company has made my journey at HVG unforgettable.

I am eternally grateful to my father, my sister, Hassnaa, my brothers, Omar and Mohamed, for their unconditional love and support. I would not have been able to reach this stage of my life without them.

### TABLE OF CONTENTS

| LI       | ST O | <b>DF TABLES x</b>                                  | ci |

|----------|------|-----------------------------------------------------|----|

| LI       | ST O | OF FIGURES                                          | v  |

| LI       | ST O | DF ACRONYMS                                         | 7i |

| 1        | Intr | roduction                                           | 1  |

|          | 1.1  | Motivation                                          | 1  |

|          | 1.2  | Dynamic Fault Trees                                 | 5  |

|          | 1.3  | Dynamic Reliability Block Diagrams                  | 9  |

|          | 1.4  | Framework for Formal Dynamic Dependability Analysis | 3  |

|          | 1.5  | Thesis Contributions                                | 6  |

|          | 1.6  | Thesis Organization                                 | 8  |

| <b>2</b> | Pre  | eliminaries 20                                      | 0  |

|          | 2.1  | HOL4 Theorem Proving                                | 0  |

|          | 2.2  | Probability Theory                                  | 1  |

|          | 2.3  | Lebesgue Integral                                   | 9  |

| 3        | For  | mal Qualitative Analysis of Dynamic Fault Trees 3   | 1  |

|          | 3.1  | Methodology                                         | 1  |

|          | 3.2  | Identity Elements and Temporal Operators            | 3  |

|          | 3.3  | Formalization of FT Gates                           | 5  |

|          |      | 3.3.1 AND and OR Gates                              | 6  |

|          |      | 3.3.2 Priority AND Gate (PAND)                      | 7  |

|          |      | 3.3.3 Functional DEPendency Gate (FDEP)             | 8  |

|          |      | 3.3.4 Spare Gates                                   | 9  |

|          | 3.4 | Forma  | l Verification of the Simplification Theorems        | 42 |

|----------|-----|--------|------------------------------------------------------|----|

|          | 3.5 | Forma  | l Qualitative Analysis of DFT Examples               | 43 |

|          | 3.6 | Forma  | l Qualitative Analysis Case Studies                  | 46 |

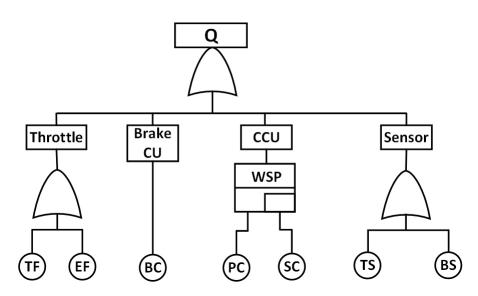

|          |     | 3.6.1  | Qualitative Analysis of DBW                          | 47 |

|          |     | 3.6.2  | Qualitative Analysis of CAS                          | 49 |

|          | 3.7 | Summ   | ary                                                  | 52 |

| 4        | For | mal Qı | antitative Analysis of Dynamic Fault Trees           | 53 |

|          | 4.1 | Metho  | dology                                               | 53 |

|          | 4.2 | Proba  | bilistic Model of DFT Gates                          | 55 |

|          |     | 4.2.1  | Probabilistic Model of AND Gate                      | 57 |

|          |     | 4.2.2  | Probabilistic Model of OR and FDEP Gates             | 58 |

|          |     | 4.2.3  | Probabilistic Model of PAND Gate and Before Operator | 60 |

|          |     | 4.2.4  | Probabilistic Model of Spare Gates                   | 69 |

|          |     |        | Cold Spare Gate                                      | 70 |

|          |     |        | Warm Spare Gate                                      | 75 |

|          |     |        | Spare Gates with a Shared Spare                      | 78 |

|          | 4.3 | Forma  | l Quantitative Analysis of DFT Examples              | 82 |

|          | 4.4 | Forma  | l Quantitative Analysis Case Studies                 | 84 |

|          |     | 4.4.1  | Formal Quantitative Analysis of DBW                  | 87 |

|          |     | 4.4.2  | Formal Quantitative Analysis of CAS                  | 90 |

|          | 4.5 | Summ   | ary                                                  | 94 |

| <b>5</b> | For | mal Ve | erification of DFT Rewrite Rules                     | 97 |

|          | 5.1 | DFT I  | Rewrite Rules                                        | 98 |

|          |     | 5.1.1  | Rewrite Framework                                    | 99 |

|   |                                                                                                                                 | 5.1.2 Rewrite Rules                                                      | 100                                                  |

|---|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------|

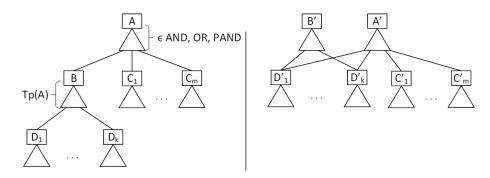

|   |                                                                                                                                 | General Rewrite Rules                                                    | 101                                                  |

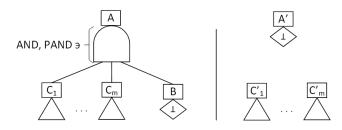

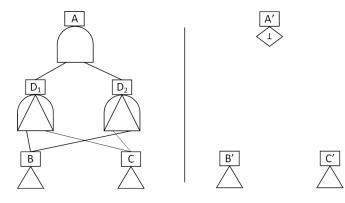

|   |                                                                                                                                 | Rewrite Rules for PAND gates                                             | 102                                                  |

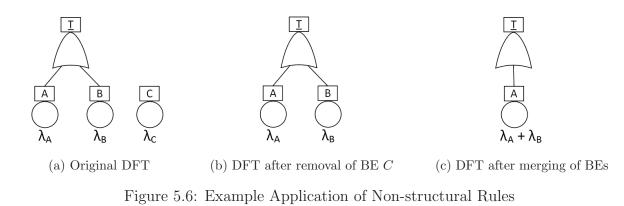

|   |                                                                                                                                 | 5.1.3 Non-structural Rules                                               | 103                                                  |

|   |                                                                                                                                 | Removing BEs                                                             | 103                                                  |

|   |                                                                                                                                 | Merging BEs                                                              | 104                                                  |

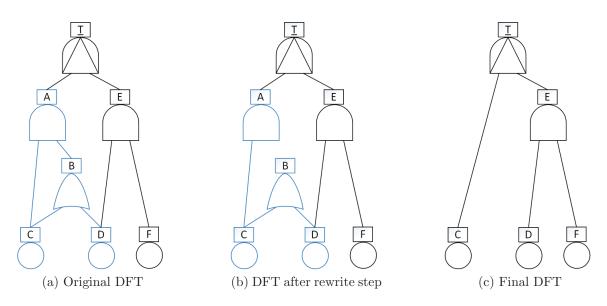

|   | 5.2                                                                                                                             | HOL Formalization of <i>n</i> -ary DFT Gates                             | 104                                                  |

|   | 5.3                                                                                                                             | Verification of Rewrite Rules                                            | 107                                                  |

|   |                                                                                                                                 | 5.3.1 General Rewrite Rules                                              | 107                                                  |

|   |                                                                                                                                 | 5.3.2 Rewrite Rules for PAND Gates                                       | 115                                                  |

|   |                                                                                                                                 | 5.3.3 Non-Structural Rules                                               | 118                                                  |

|   | 5.4                                                                                                                             | Summary                                                                  | 119                                                  |

|   |                                                                                                                                 |                                                                          |                                                      |

| 6 | For                                                                                                                             | rmal Analysis of Dynamic Reliability Block Diagrams                      | 120                                                  |

| 6 | <b>For</b> :<br>6.1                                                                                                             | Temal Analysis of Dynamic Reliability Block Diagrams         Methodology |                                                      |

| 6 |                                                                                                                                 |                                                                          | 121                                                  |

| 6 | 6.1                                                                                                                             | Methodology                                                              | 121<br>122                                           |

| 6 | 6.1<br>6.2                                                                                                                      | Methodology      DRBD Event                                              | 121<br>122<br>124                                    |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                   | Methodology          DRBD Event          Identity Elements and Operators | 121<br>122<br>124<br>131                             |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                                                       | Methodology                                                              | 121<br>122<br>124<br>131<br>131                      |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul>                                                     | Methodology                                                              | 121<br>122<br>124<br>131<br>131<br>136               |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>                                        | Methodology                                                              | 121<br>122<br>124<br>131<br>131<br>136<br>145        |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul>                           | Methodology                                                              | 121<br>122<br>124<br>131<br>131<br>136<br>145<br>146 |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> </ul> | Methodology                                                              | 121<br>122<br>124<br>131<br>131<br>136<br>145<br>146 |

|    | 7.2           | Terminal Reliability Analysis of Shuffle-exchange Networks 1 |                                                        |       |

|----|---------------|--------------------------------------------------------------|--------------------------------------------------------|-------|

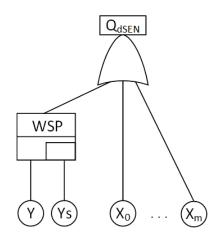

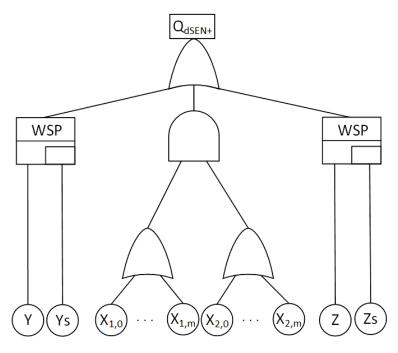

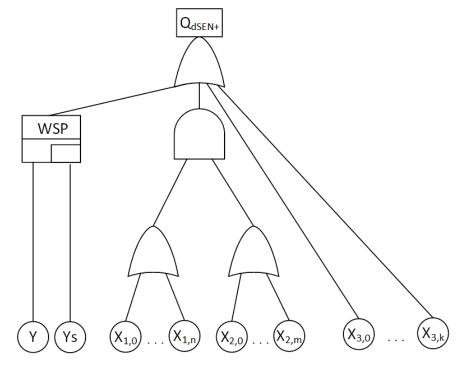

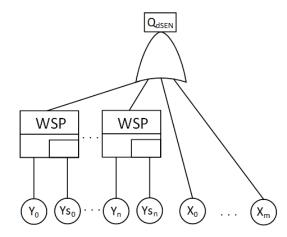

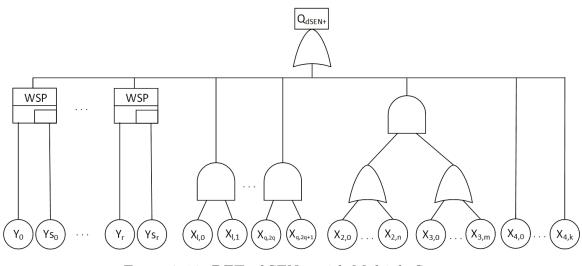

|    |               | 7.2.1                                                        | DFT Analysis of SEN and SEN+                           | . 158 |

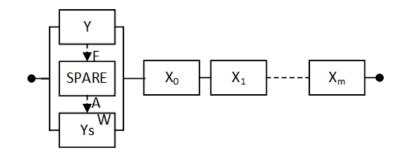

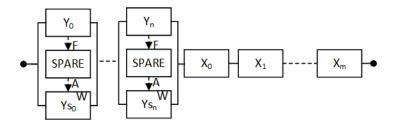

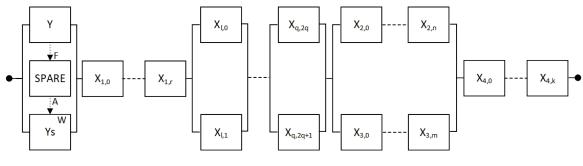

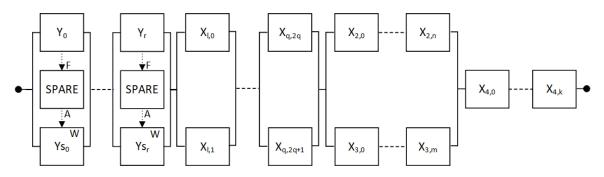

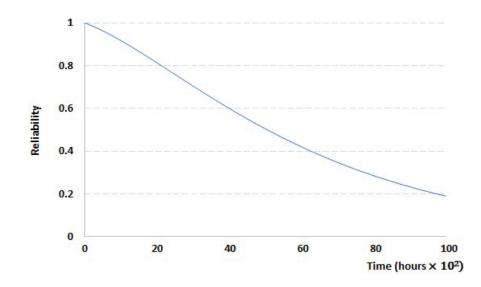

|    |               | 7.2.2                                                        | DRBD Analysis of SEN and SEN+                          | . 166 |

|    | 7.3           | Broad                                                        | cast Reliability Analysis of Shuffle-exchange Networks | . 171 |

|    |               | 7.3.1                                                        | DFT Analysis of SEN and SEN+                           | . 172 |

|    |               | 7.3.2                                                        | DRBD Analysis of SEN and SEN+                          | . 174 |

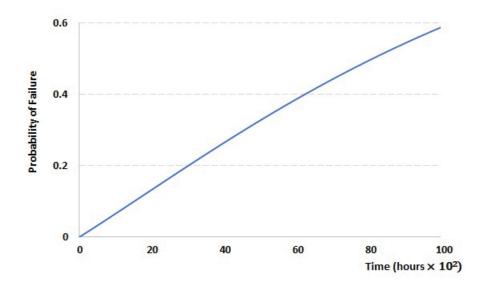

|    | 7.4           | Netwo                                                        | ork Reliability Analysis of Shuffle-exchange Networks  | . 177 |

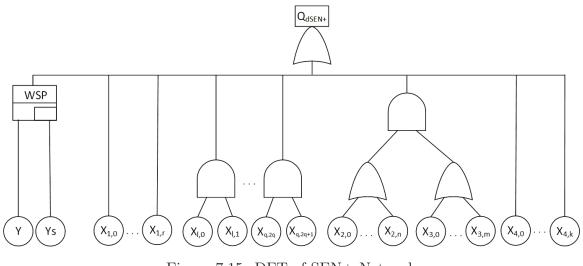

|    |               | 7.4.1                                                        | DFT Analysis of SEN and SEN+                           | . 178 |

|    |               | 7.4.2                                                        | DRBD Analysis of SEN and SEN+                          | . 187 |

|    | 7.5           | Equiva                                                       | alence of SEN DFT and DRBD Models                      | . 196 |

|    | 7.6           | Summ                                                         | nary                                                   | . 199 |

| 8  | Cor           | clusio                                                       | ns and Future Work                                     | 200   |

|    | 8.1           | Concl                                                        | usions                                                 | . 200 |

|    | 8.2           | Future                                                       | e Work                                                 | . 203 |

| Bi | bliog         | graphy                                                       |                                                        | 205   |

| Bi | Biography 215 |                                                              |                                                        |       |

# List of Tables

| 2.1 | Some HOL Symbols                                                |

|-----|-----------------------------------------------------------------|

| 3.1 | DFT Gates Mathematical Expressions                              |

| 3.2 | Examples of Formally Verified Simplification Theorems           |

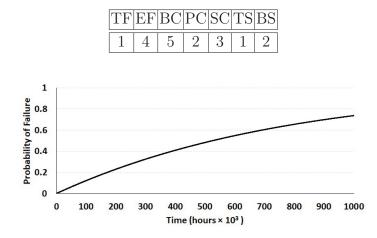

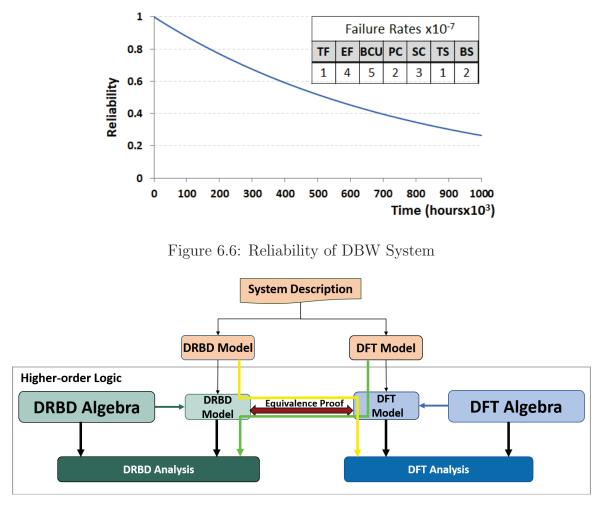

| 4.1 | Failure Rates for the DBW System $(\times 10^{-7})$             |

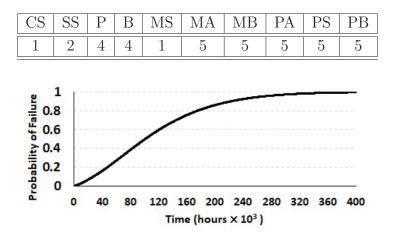

| 4.2 | Failure Rates of CAS $(\times 10^{-6})$                         |

| 6.1 | Formally Verified DRBD Simplification Theorems                  |

| 6.2 | Mathematical and Reliability Expressions of DRBD Structures 138 |

| 6.3 | Verified Equivalence of DFT and DRBD Algebras                   |

| 6.4 | Comparison of Formal Analysis Efforts of DBW                    |

# List of Figures

| 1.1 | Some DFT Elements                                                    |

|-----|----------------------------------------------------------------------|

| 1.2 | Dynamic DRBD Constructs                                              |

| 1.3 | Overview of the Proposed Framework                                   |

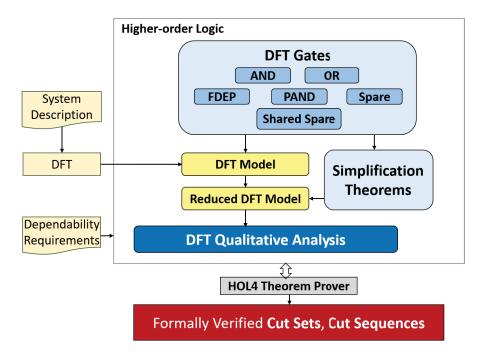

| 3.1 | Formal DFT Qualitative Analysis Methodology                          |

| 3.2 | DFT Examples                                                         |

| 3.3 | DFT of Drive-by-wire System                                          |

| 3.4 | DFT of Cardiac Assist System                                         |

| 4.1 | Formal DFT Quantitative Analysis Methodology                         |

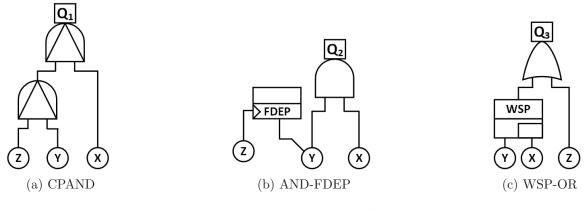

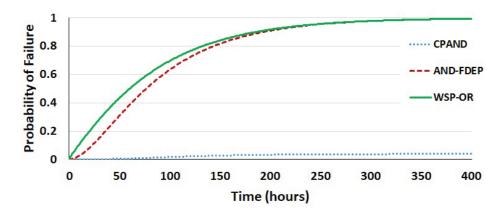

| 4.2 | Probability of Failure of CPAND, AND-FDEP and WSP-OR 85              |

| 4.3 | Probability of Failure of the Drive-by-wire System                   |

| 4.4 | Probability of Failure of the Cardiac Assist System                  |

| 5.1 | Subsumption of OR Gates by AND Gates [66, Rewrite Rule 8] 99         |

| 5.2 | Example Application of Rewrite Rule                                  |

| 5.3 | Left-flattening of Gates [66, Rewrite Rule 5]                        |

| 5.4 | AND/PAND Gate with $CONST(\bot)$ Successor [66, Rewrite Rule 13] 102 |

| 5.5 | Conflicting PAND Gates with Independent Successors [66, Rewrite      |

|     | Rule 19]                                                             |

| 5.6  | Example Application of Non-structural Rules                                   |

|------|-------------------------------------------------------------------------------|

| 6.1  | Formal DRBD Analysis Methodology                                              |

| 6.2  | Two-Block Series and Parallel DRBDs                                           |

| 6.3  | Spare Construct                                                               |

| 6.4  | DRBD Structures                                                               |

| 6.5  | DRBD of Drive-by-Wire System                                                  |

| 6.6  | Reliability of DBW System                                                     |

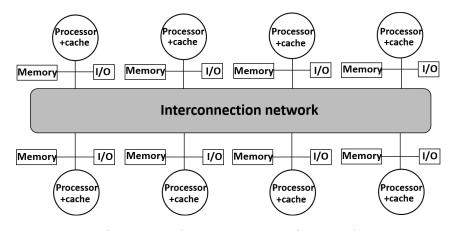

| 6.7  | Integrated Framework for Formal DFT-DRBD Analysis using HOL4 147              |

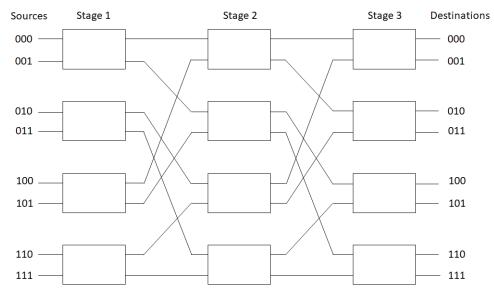

| 7.1  | Overview of Multiprocessor System Architecture                                |

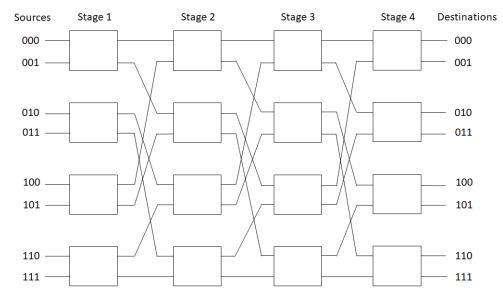

| 7.2  | An $8 \times 8$ SEN                                                           |

| 7.3  | An $8 \times 8$ SEN+                                                          |

| 7.4  | DFT of SEN                                                                    |

| 7.5  | DFT of SEN+ Terminal Connection                                               |

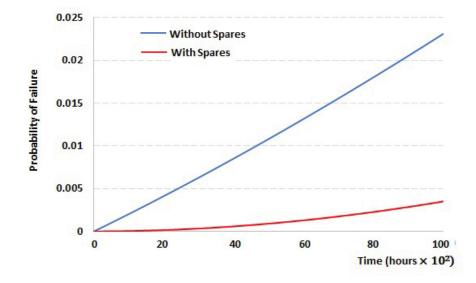

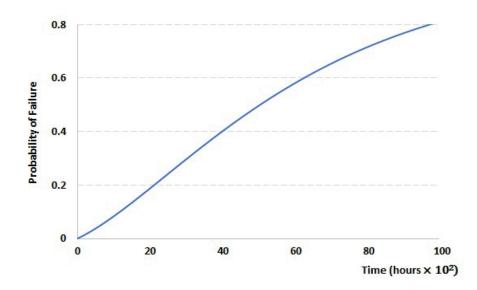

| 7.6  | Probability of Failure of the Terminal Connection of a $128\times128$ SEN+    |

|      | with and without Spares                                                       |

| 7.7  | DRBD of SEN                                                                   |

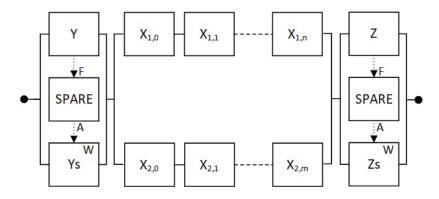

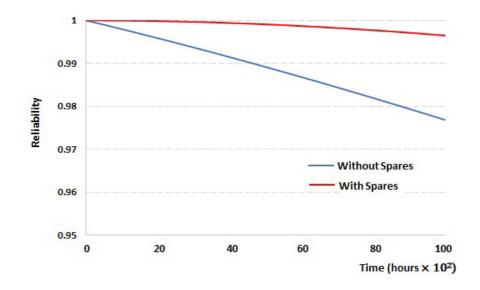

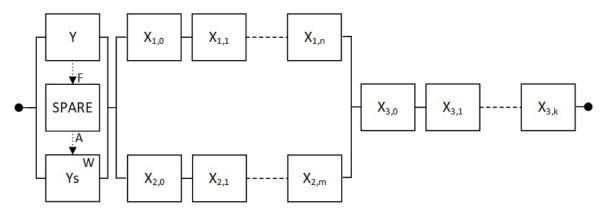

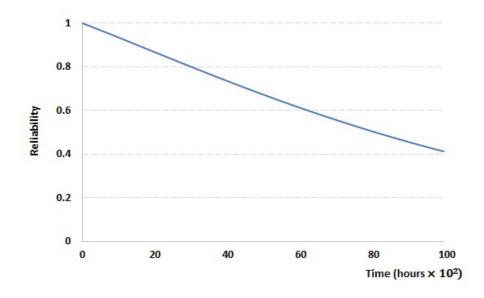

| 7.8  | Terminal Reliability DRBD of SEN+                                             |

| 7.9  | Terminal Reliability of $128 \times 128$ SEN+ with and without Spares $~$ 171 |

| 7.10 | DFT of Broadcast SEN+                                                         |

| 7.11 | Probability of Failure of the Broadcast of a $128 \times 128$ SEN+ 175        |

| 7.12 | Broadcast DRBD Model of SEN+                                                  |

| 7.13 | Broadcast Reliability of a $128 \times 128$ SEN+                              |

| 7.14 | DFT of SEN Network with Multiple Spares                                       |

| 7.15 | DFT of SEN+ Network                                                           |

| 7.16 | DFT of SEN+ with Multiple Spares                                              |

| 7.17 | The Probability of Failure of the Network of a $128\times128$ SEN+ $~$ 188 |

|------|----------------------------------------------------------------------------|

| 7.18 | DRBD of SEN Network                                                        |

| 7.19 | DRBD of SEN+ Network                                                       |

| 7.20 | DRBD of SEN+ Network with Multiple Spares                                  |

| 7.21 | The Network Reliability of a $128 \times 128$ SEN+                         |

### LIST OF ACRONYMS

| AE            | Almost Everywhere                 |

|---------------|-----------------------------------|

| BC            | Brake Control                     |

| BDD           | Binary Decision Diagram           |

| BE            | Basic Event                       |

| BS            | Brake Sensor                      |

| CAS           | Cardiac Assist System             |

| CDF           | Cumulative Distribution Function  |

| CPAND         | Cascaded PAND                     |

| CPN           | Colored Petri Nets                |

| CPU           | Central Processing Unit           |

| CS            | Crossbar Switch                   |

| CSP           | Cold SPare                        |

| CTMC          | Continuous Time Markov Chain      |

| DAG           | Directed Acyclic Graph            |

| DBW           | Drive-by-wire                     |

| DFT           | Dynamic Fault Tree                |

| DRBD          | Dynamic Reliability Block Diagram |

| EF            | Engine Failure                    |

| ET            | Event Tree                        |

| FDEP          | Functional DEPendency             |

| $\mathrm{FT}$ | Fault Tree                        |

| FTA           | Fault Tree Analysis               |

| HOL           | Higher-order Logic                |

| HSP  | Hot SPare                            |

|------|--------------------------------------|

| LSH  | Load SHaring                         |

| MC   | Markov Chain                         |

| MIN  | Multi-stage Interconnection Network  |

| MTTF | Mean-Time-To-Failure                 |

| PAND | Priority-AND                         |

| PDF  | Probability Density Function         |

| PIE  | Principle of Inclusion and Exclusion |

| PMC  | Probabilistic Model Checker          |

| RBD  | Reliability Block Diagram            |

| SDEP | State DEPendency                     |

| SEN  | Shuffle-exchange Network             |

| SFT  | Static Fault Tree                    |

| SS   | System Supervisor                    |

| SSD  | Solid State Drive                    |

| TF   | Throttle Failure                     |

| TS   | Throttle Sensor                      |

| VOT  | Voting                               |

| WSP  | Warm SPare                           |

# Chapter 1

# Introduction

### 1.1 Motivation

A man who lacks reliability is utterly useless.

- Confucius (551–479 BC)

The recent decades witnessed huge technological advancements, which took part in almost all aspects of our lives. While some of the applications that are related to technology can somehow tolerate errors in their results, there are other applications where errors can lead to financial losses, disasters and in the worst case losses in human lives. Crises such as the Toyota global recall [1] increased and necessitated the need to measure system dependability, which is the ability of a system to provide a trusted service [2]. Dependability analysis is also required in other types of systems, such as data centers, where the loss of financial or personal information cannot be tolerated. Dependability generally consists of several attributes such as reliability, availability, maintainability, safety and confidentiality. Some of these concepts can be quantified and measured such as reliability and availability. *Reliability* can be defined as the probability that a certain system when subject to specific conditions will deliver its correct function in a given period of time. This means that the probability that a system will not encounter any failure for a specific period can be calculated and analyzed based on certain requirements. On the other hand, *availability* is the probability that the system or a component of a system will provide its service at a certain moment of time [2]. Dependability is commonly modeled using combinatorial models, such as fault trees (FTs) [3], reliability block diagrams (RBDs) [4] and event trees (ETs) [5]. However, these traditional modeling techniques cannot capture the dynamic failure behavior of systems and thus cannot truly model many real-world systems that exhibit sequential failures and dependencies among system components.

A dynamic dependability, on the other hand, generally captures the dependent failure and repair sequences that the regular combinatorial dependability models cannot represent. Dynamic dependability analysis is considered as an important step in the design process of any system that possesses a dynamic behavior, especially safety-critical systems. The appropriate modeling technique is chosen to estimate the system dynamic dependability. These modeling techniques include Dynamic Fault Trees [3] and Dynamic Reliability Block Diagrams [6]. A Dynamic Fault Tree (DFT) is a graphical representation of the sources of faults that cause the failure of a system represented as the top event of the DFT. It utilizes dynamic gates to model the failure dependencies of the basic events. Dynamic Reliability Block Diagrams (DRBDs) have been introduced as an extension to traditional RBDs to capture the dynamic success paths of a given system. Traditionally, dependability models are analyzed using paper-and-pencil based proof methods or using simulation. The former provides a flexible way to model and analyze systems. However, it is prone to human error. On the other hand, simulation provides an easy and automated method to conduct the analysis, which justifies its common use in analyzing a wide range of applications. For example, in [7], the reliability of Solid State Drives (SSDs) of two different configurations are compared using simulation. However, due to the high computational cost of simulation, only part of the space could be analyzed, and thus the results cannot be termed as accurate or complete.

Formal methods, such as model checking [8] and theorem proving [9] have been used for the analysis of dependability models to overcome the inaccuracy limitations of the above-mentioned techniques. For example, the PRISM model checker [10] has been used in the reliability analysis of many applications, such as defect-tolerant systems [11]. More recently, the STORM model checker [12] has been used in the safety analysis of a vehicle guidance system [13] using DFTs. Although probabilistic model checkers provide an automatic way to conduct the analysis of dependability models, the state space explosion problem often limits its scope especially when analyzing complex systems. Moreover, the reduction algorithms embedded in these tools are usually not formally verified, which questions the accuracy of the reduced models. More importantly, probabilistic model checkers inherently assume the failures to be exponentially distributed for system components [14], and thus cannot capture, for example, the aging factor of these components.

Since the formalization of the probability theory in higher-order logic (HOL) [15,

16, 17, 18], theorem proving has also been used for dependability analysis. For example, some properties for continuous random variables were employed to formally reason about some system reliability properties, such as Mean-Time-To-Failure (MTTF) [19]. Moreover, some reliability theory elements were formally verified and used in the formal analysis of a reconfigurable memory array with stuck-at and coupling faults [20]. In [21] and [22], two frameworks for the analysis of FTs and RBDs, respectively, using theorem proving were proposed and used to formally analyze some real-world applications, like an air traffic management system [22] and a solar array for a satellite system [23]. However, this HOL formalization cannot handle or be extended to verify the dynamic properties of DFTs and DRBDs. Generally, using a theorem prover in the analysis allows having verified generic expressions of dependability that are independent of the distribution of system components. Accordingly, the results are not limited to exponential distributions.

Taking into account the concerns mentioned above about dynamic dependability analysis of systems, in particular safety-critical ones, there is a dire need to have an accurate framework for modeling and analysis of dynamic dependability models. In this thesis, we aim to provide a formal framework for the accurate dynamic dependability analysis of systems modeled as DFTs and DRBDs. Mainly, the idea is to build a mathematical model for the dynamic dependability of the system using either DFTs or DRBDs based on the system description and requirements, and then to utilize the expressiveness and sound nature of HOL theorem proving to perform the analysis of such models to provide generic expressions of dependability. It is worth mentioning that such generic expressions cannot be provided using model checking, which adds to the importance of the proposed framework as the first of its kind in providing sound generic expressions of dynamic dependability models that are formally verified. As an illustration of the usefulness of the proposed framework, we apply it in verifying some rewrite rules that are used in automatic DFT analysis tools, like the STORM model checker, to reduce DFT models, which demonstrates the soundness of these rules. Furthermore, we utilize this framework to conduct the formal dependability analysis of two safety-critical systems from the medical and automotive domains to reason about their dynamic failure behaviors. Furthermore, we apply our framework for the dependability analysis of real-world systems, namely multiprocessor networks, where the increased number of processing elements requires having a sophisticated interconnection network that must be on one hand efficient with low cost and on the other hand more reliable [24]. In particular, we propose to formally model and conduct the dynamic dependability analysis of shuffle-exchange networks (SENs) [25] using DFTs and DRBDs to reason about their behaviors. SENs are multistage interconnection networks (MINs) [26], which are widely used in multiprocessor systems to establish communication between system nodes, including processors, memories and I/O peripherals.

In this thesis, we use the HOL4 theorem prover [27] to formalize DFTs and DRBDs and perform the above-mentioned analysis. We choose HOL4 as we are using existing theories (libraries), such as probability [17] and Lebesgue integral [28], to build and verify the underlying foundations of these dependability models.

#### 1.2 Dynamic Fault Trees

Dynamic fault trees (DFTs) [3] are introduced to model the failure dependencies among system components that cannot be captured using traditional FTs, i.e., static fault tress (SFTs). A DFT is a graphical representation of the sources of failure of a given system. The modeling starts with an undesired top event that represents

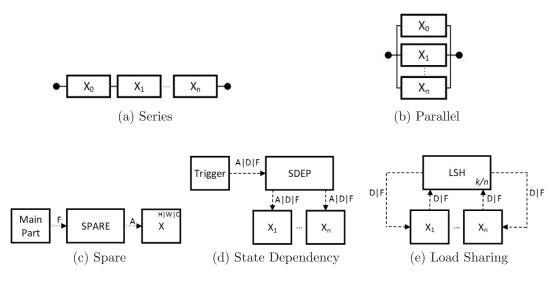

Figure 1.1: Some DFT Elements

the failure of the whole system or a subsystem. Inputs of the DFT represent basic events that contribute to the occurrence (failure) of the top event. The relationships and dependencies among these basic events are modeled using DFT gates, such as Priority-AND (PAND) gate.

DFTs are directed acyclic graphs (DAG) with typed nodes (AND, OR, etc.). Successors of a node v in the DAG are *inputs* of v. Some commonly used DFT elements are shown in Figure 1.1. Nodes without inputs are *basic events* (BE, Figure 1.1(a)) that represent atomic components, which can fail according to a failure distribution. Special cases of BEs are *constant failed* elements (CONST( $\top$ ), Figure 1.1(b)) that always fail and *constant fail-safe* elements (CONST( $\perp$ ), Figure 1.1(c)), that can never fail. DFT gates are nodes with inputs and are used to model the state dependencies and redundancies among system components. Some commonly used DFT gates include SFT gates (AND, OR) as well as the PAND DFT gate. The output event of the AND gate (Figure 1.1(d)) fails when both input events fail. The OR gate (Figure 1.1(e)) requires that at least one of its input events fails for the output event to fail. The PAND gate (Figure 1.1(f)) acts in a similar way to the AND gate, i.e., it requires that both input events fail. However, an additional condition is needed, where the inputs should fail in sequence, usually from left to right. There are also other DFT gates that are used to model the dynamic behavior in systems, like the Functional-DEPendency (FDEP) and spare gates.

Fault tree analysis (FTA) can be generally carried out qualitatively or quantitatively [29]. In the qualitative analysis, the combinations and sequences of basic events that contribute to the occurrence of the top event (failure of the system) are identified. The sets that include these combinations are called cut sets, while the cut sequences determine the required sequences of failure of the basic events. These combinations and sequences represent the cut sets and cut sequences [3], respectively. In the *quantitative* analysis, attributes, such as the MTTF and the probability of failure, can be evaluated based on the failure distribution of the basic events and their relationships. Dynamic FTA has been commonly conducted using a DFT algebra [30] or by analyzing the corresponding Continuous Time Markov Chain (CTMC) of the given DFT [29]. In the former method, an algebra similar to the ordinary Boolean algebra is defined with some temporal operators and simplification properties that allow the structure function of the top event to be reduced. Based on this structure function, both the qualitative and quantitative analyses can be carried out, where the probability of failure of the DFT's top event can be expressed based on the failure distribution of the basic events. On the other hand, the given DFT can be converted into its equivalent CTMC and then this CTMC is analyzed to find the probability of failure of the top event [29]. Complex systems can generate CTMCs with a large state space. This can be handled by applying a modularization approach, where the DFT is divided into static and dynamic parts. The static FT can be analyzed using one of the conventional methods, such as binary decision diagrams (BDDs) [3]. The dynamic part can then be analyzed by converting it to its corresponding CTMC. This kind of modulerization is implemented in the Galileo tool [31].

Dynamic FTA can be conducted analytically to manually generate probability of failure expressions. The cut sets and sequences are identified and then the probabilistic

principle of inclusion and exclusion (PIE) is applied to provide the probability of failure expression [30]. However, the results of this manual manipulation are prone to human error. Simulation, on the other hand, can provide a scalable and automated alternative to conduct the FTA. For example, in [32], DFT analysis is performed by combining the DFT algebra of [33] and Monte Carlo Simulation [34]. There also exist other tools for DFT analysis, such as BlockSim [35], Möbius [36] and isograph [37]; however, as mentioned earlier, their analysis results cannot be termed as complete nor accurate due to the sampling nature of their simulation method.

In order to overcome the limitations of simulation in terms of inaccuracies and completeness, formal methods can be used in the dynamic FTA. The DFTCalc tool [38] analyzes DFTs using an Input/Output Interactive Markov Chain, an extension of CTMCs, which is built based on a compositional aggregation technique [39]. Probabilistic model checking (PMCs) has been utilized to perform the analysis of DFTs. For example, the STORM model checker is used to conduct the quantitative analysis of DFTs in the form of probability of failure and MTTF [40]. However, generic expressions of probability of failure cannot be obtained based on this kind of analysis. Moreover, the failure distributions of the inputs are assumed to be exponential due to the state based nature of PMCs.

On the other hand, HOL theorem proving has been used in [21] to formalize SFTs and reason about their properties. However, this formalization cannot handle the dynamic aspects of real-world systems that are captured using DFTs. Furthermore, it cannot be extended to model and analyze the dynamic behavior of systems, and thus a new formalization is needed.

Due to the high expressive nature of HOL, in [41], we proposed a methodology to

conduct the DFT's qualitative analysis using the HOL theorem prover and the quantitative analysis using the STORM model checker. We provided the formalization of DFTs based on the algebraic approach [30]. In the algebraic approach, identity elements and temporal operators are defined to express the structure function of a DFT event. Several simplification properties are introduced that facilitate the reduction of this function. However, the arithmetic foundation of this approach was not formally verified, which puts a question mark on the soundness of the reported results. In [41], we provided the formalization of the DFT gates, operators and their simplification theorems. This allows the qualitative analysis to be performed within the sound core of a HOL theorem prover. In addition, we proposed to use the STORM model checker to find the probability of failure of the formally verified reduced DFT structure function. However, we cannot obtain generic expressions of probability of failure based on this methodology as a PMC is involved in the quantitative analysis. Moreover, our definitions in [41] cannot handle the DFT probabilistic analysis. Therefore, in this thesis, we propose new definitions of DFT gates and temporal operators, which allow us to conduct qualitative as well as quantitative analyses of DFTs in the form of generic expressions of probability of failure in a theorem prover.

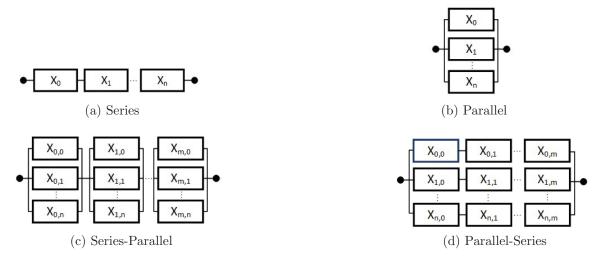

### 1.3 Dynamic Reliability Block Diagrams

A dynamic reliability block diagram (DRBD) models the paths of success in a given system using system components as blocks that are connected in the traditional series, parallel, series-parallel and parallel-series structures. The connections between system blocks are modeled using connectors (lines) to create one or more paths from the DRBD input to its output. These paths represent the required working blocks (system components) for the system to have a successful operation. The modeled system fails

Figure 1.2: Dynamic DRBD Constructs

when components fail in such a manner that leads to the disconnection of all the paths between the input and the output. Additional constructs are used to model the dynamic dependencies among system blocks.

The main dynamic DRBD structures and constructs are shown in Figure 1.2 [42]. In DRBDs, the blocks can be connected in series, parallel or deeper nested structures. For the series structure, shown in Figure 1.2(a), all system blocks should function properly in order to maintain a successful behavior. On the other hand, at least one of the blocks of the parallel structure in Figure 1.2(b) must work to have a successful system behavior. These two structures can be connected in a hierarchical manner to model complex systems. The *spare* construct (Figure 1.2(c)) is used to model spare parts in systems, similar to the DFT spare gate. The *state dependencies* (Figure 1.2(d)) are used to model the effect of activation(A)/deactivation(D)/failure(F) among system components. In Figure 1.2(d), the A/D/F of the trigger will cause the state dependency controller (SDEP) to signal the A/D/F of components  $X_1...X_n$ . Finally, the *load sharing* (LSH) construct is used to model the effect of sharing the same load among several components on the failure effect of the overall system. For example, the LSH in Figure 1.2(e) models a load that is shared among n components. It is required that at least k out of these n components to be working in order for the functionality of the system to be successful. Therefore, the D/F of some of these components may cause the D/F of the rest of the components. The last two constructs enable modeling more realistic scenarios in system reliability that include the effect of A/D of one component on the rest of the components. This behavior cannot be captured using DFTs [43] as they can only capture the failure effect of one system component on the rest of the components without considering the A/D effect.

Due to the dynamic nature of DRBDs, they can be analyzed by converting them into a state-space model, i.e., a Markov chain. Then, the resultant Markov chain can be analyzed using one the of the traditional techniques, including analytical methods or simulation, such as Monte Carlo simulation. There exist some tools that provide the DRBD analysis, such as Möbius [36], isograph [37] and BlockSim [35], which provide a graphical user interface to model DRBDs and conduct the analysis either analytically or using discrete event simulation. As mentioned previously, complex systems can generate Markov chains with a large number of states, which hinders the analysis process. Decomposition can be applied to divide the DRBD into a dynamic part that can be solved using Markov chains and a static part that can be analyzed using static RBD analysis techniques [44]. This decomposition would reduce the state space, but such simulation based analysis cannot provide accurate and complete results. The formal semantics of DRBDs have been introduced in [45] using the Object-Z formalism [46]. Then, this DRBD is converted into a Colored Petri net (CPN) [47], where it can be analyzed using existing Petri net tools. An algorithm to automatically convert a DRBD into a CPN is also proposed in [48]. However,

since the given DRBD is converted into a CPN, only state-based properties can be analyzed. In addition, generic expressions of reliability cannot be obtained, which represents our target in this thesis. HOL theorem proving has been used for the analysis of traditional RBDs [22]. However, there is no support for DRBD analysis using a HOL theorem prover that can handle the analysis of real-world systems that exhibit dynamic behavior.

In system engineering, it is important to be able to analyze DRBDs qualitatively in order to identify the sources of system vulnerability, and quantitatively in order to evaluate the system reliability. However, to the best of our knowledge, so far there exists no algebra that mathematically models a given DRBD and enables expressing its function based on basic components like the DFT algebra [30]. Using such algebra in the reliability analysis will result in simpler and fewer proof steps than the DFT-based algebraic analysis [30], since the probabilistic PIE will not be invoked. In this PhD thesis, we propose a new algebraic approach for DRBD analysis that allows a DRBD expression to be used for both qualitative and quantitative analyses. We introduce new operators to mathematically model the dynamic behavior in DRBD structures and constructs. In particular, we use these operators to model a DRBD spare construct as well as traditional series, parallel, series-parallel and parallel-series structures. Moreover, we provide simplification theorems that allow the structure of a given DRBD to be reduced. This DRBD structure can be then analyzed to obtain a generic expression of the system reliability. The reliability expressions obtained using this approach are generic and independent of the distribution and density functions that represent the system components. Although basic operators, such as OR and AND, were introduced in [44], they are only useful to model parallel and series constructs of dependent components. Moreover, there is no general mathematical

expression that would allow reasoning about the behavior of DRBDs. In addition, the DRBD constructs of [44] are quite complex, which complicates modeling large systems. Therefore, in this thesis, we use the constructs proposed in [45] as they are much simpler, which facilitates defining the new algebra to model various new DRBD constructs. Leveraging upon the expressive nature of HOL, we formally verify the soundness of the proposed DRBD algebra using HOL theorem proving. Although the formalization development can be conducted using many theorem provers, we choose the HOL4 theorem prover, as our existing formalization of DFT algebra can be useful since our proposed DRBD algebra is compatible with the DFT's.

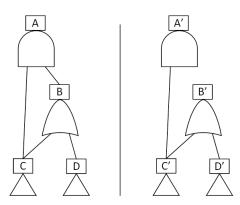

It is worth mentioning that a given DFT can be converted into its equivalent DRBD and vice-versa, which allows reasoning about both the success and failure of a given system using one model. This requires the conversion of each DFT gate into its equivalent DRBD construct or structure. For example, the DFT spare gate can be modeled using the DRBD spare construct [43].

#### **1.4** Framework for Formal Dynamic

### **Dependability Analysis**

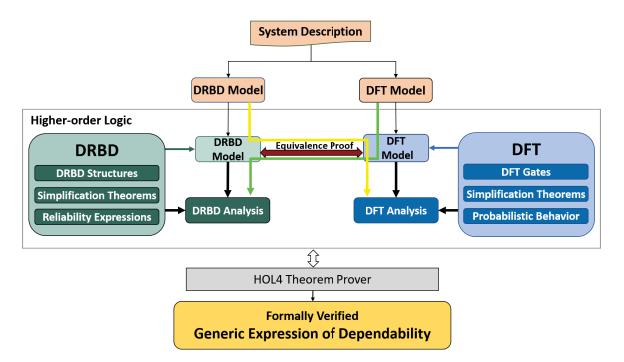

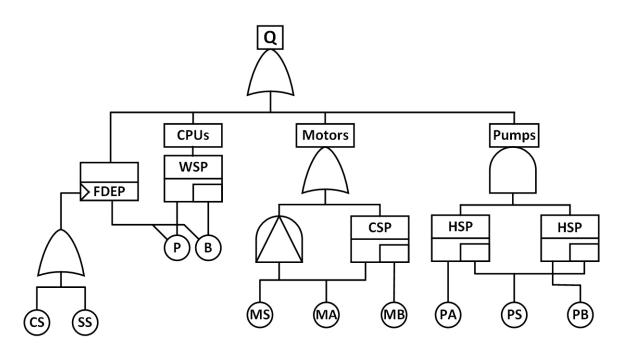

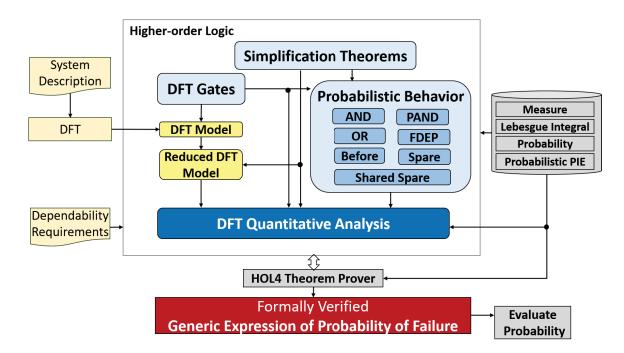

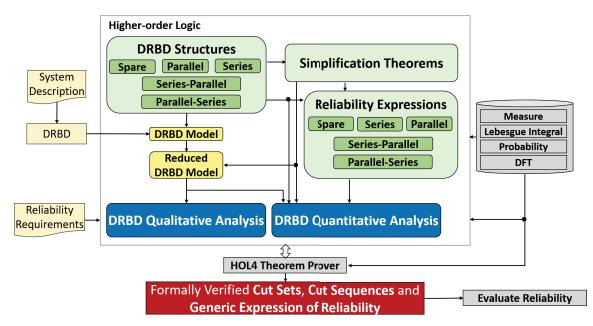

As mentioned earlier, there exist many techniques that can be invoked to analyze the dynamic dependability of systems. However, none of them provides an accurate, scalable and expressive framework for dynamic dependability modeling and analysis, which represents important features in analyzing the dynamic failure behavior of systems, specially safety critical ones. Therefore, the objective of this thesis is to provide a framework for the dynamic dependability analysis of systems modeled as DFTs and DRBDs. The proposed framework is depicted in Figure 1.3.

Figure 1.3: Overview of the Proposed Framework

This framework provides verified generic expressions of dependability using HOL4 theorem prover of DFTs and DRBDs. The analysis starts by having a system description, which is assumed to be correct, with some dependability requirements, such as a certain expression of reliability. This system can be modeled either using a DFT or DRBD model according to its description. We create formal DFT or DRBD models utilizing our library of formalized DFT gates and DRBD constructs. This library also includes the DFT and DRBD simplification theorems and verified probabilistic behavior as well as the reliability expressions. The formal DFT and DRBD models can then be analyzed qualitatively or quantitatively. In the former, the sources of vulnerabilities of the system are verified by identifying the cut sets and cut sequences. In the latter, we prove generic failure and reliability expressions

of DFT and DRBD based systems, respectively. It is worth mentioning that unlike model checking approaches, the formally verified generic expressions of DFT and DRBD are independent of the probability distributions of the system components. HOL4 was used in the development of the formalization of static dependability models, i.e., FTs [21] and RBDs [22]. Therefore, in this thesis, we choose to follow the same path and use HOL4 as this would facilitate using some of the developed work, such as the probabilistic PIE theory [23]. In addition, we build our theories utilizing some of the existing theories in HOL4 such as the theories on measure, Lebesgue integral [49] and probability [28]. This proposed framework allows conducting the dynamic dependability analysis of many real-world systems to provide generic expressions. It is important to note that the DFT part of the proposed framework is primarily based on the formalization of the algebraic approach presented in [30]. However, a distinguishing feature of our formalization is that it allows us to conduct computer based proofs of the probability of failure expressions for DFT gates within the sound environment of a theorem prover software. These proofs are either unavailable in [30], or we are able to conduct them in a simpler manner. In addition, we explicitly define DFT events that are used to provide the set of time to perform the probabilistic analysis. Moreover, as we are providing the formalization in a theorem prover, datatypes should be carefully handled to capture both the behavior of DFT gates and the probability of their failure. These details are not provided in [30], which signifies the importance of the proposed methodology. Since this framework integrates both DFT and DRBD algebras, it provides the capability of formally converting one dependability model to another based on the equivalence proof of both algebras. This means that the DRBD model can be converted to a DFT to model the failure instead of the success, then this model is analyzed using the DFT algebra. Similarly, the DFT model can be analyzed

by converting it to its counterpart DRBD model. It is worth noting that based on the system description, the analysis can be conducted at different levels of abstraction in a hierarchical (modular) manner.

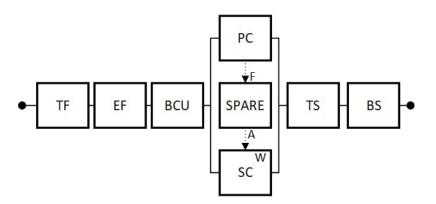

As an application of the formalized DFT algebra, we formally verify within HOL the DFT rewrite rules that are used in other DFT analysis tool, such as STORM. This demonstrates the applicability and generality of our DFT formalization. Furthermore, we apply our framework in the formal DFT analysis of two safety-critical systems: a cardiac assist system (CAS), and a drive-by-wire (DBW) system. Similarly, we perform the analysis of the DRBD of the DBW. Finally, we illustrate the usefulness of the entire framework by conducting the formal dependability analysis of shuffleexchange networks, which are widely used in multiprocessor systems. We use both DFT and DRBD models to perform the analysis and utilize their equivalence to show the possibility of conducting the analysis in both directions.

### 1.5 Thesis Contributions

The main contribution of this thesis is to develop a framework for the formal dynamic dependability analysis of DFT and DRBD models using HOL theorem proving. This framework represents an alternative approach to other less rigorous ones, such as simulation and paper-and-pencil. To accomplish this objective, we develop libraries for each dependability model. Each library has the formalized mathematical foundations for each algebra, including the DFT gates definitions and the DRBD structures. In addition, these libraries include the formally verified probabilistic behavior of each model besides the equivalence proof of both algebras. Below, we provide the list of contributions of this work along with the related publications available in the Biography section at the end of the thesis:

- Formalization of a DFT algebra in HOL, which includes operators and gates definitions in addition to the verification of the simplification theorems. The gates and operators are defined based on the time-of-failure of the inputs and the outputs, which are modeled as random variables of failure that return extended-real numbers. We verify the simplification theorems based on these definitions and using the properties of extended-real numbers [Bio-Jr2, Bio-Tr3].

- Formal qualitative analysis of DFTs in HOL. We use the simplification theorems to reduce the structure function of a given DFT. Then, using the HOL4 theorem prover, we formally verify the cut sets and cut sequences. Moreover, we formally conduct the qualitative analysis of the DBW and CAS systems [Bio-Jr1].

- Formal verification of the probabilistic failure behavior of the DFT gates using HOL theorem proving, which allows conducting the formal quantitative analysis of a given DFT in HOL. Building this theory requires using the properties of the Lebesgue integral and the probability theory. We perform the probabilistic analysis of the DBW and CAS systems to provide generic expressions of probability of failure that are independent of the failure distributions of the input events [Bio-Jr2, Bio-Tr4].

- Formal verification of DFT rewrite rules that are useful in reducing a given DFT. These rewrite rules are used in automated DFT analysis tools, such as the STORM model checker, which represents the first step towards the formal verification of these tools. We extend the definitions of DFT gates to n-ary gates, which are required to formalize these rewrite rules [Bio-Cf2].

- Development of a novel DRBD algebra that allows expressing the structure of a DRBD with spare constructs. We introduce DRBD operators and simplification

theorems, similar to the DFT algebra, to enable reducing a given DRBD [Bio-Cf1, Bio-Tr3].

- The formalization of the new DRBD algebra besides modeling the spare construct and several DRBD structures, such as series and parallel structures. We formally verify the reliability expressions of the DRBD structures and the spare construct to allow conducting the reliability analysis of a given DRBD in a theorem prover [Bio-Cf1, Bio-Tr3].

- Formal verification of the equivalence of DFT and DRBD that allows the bidirectional path between both models. This enables formally analyzing the success and failure behaviors of systems modeled using either model [Bio-Tr2].

- Formal verification of the terminal, broadcast and network reliability analysis of several versions of generic shuffle-exchange networks, which are widely used in the interconnection of multiprocessor systems. We perform the formal analysis using both DFT and DRBD dependability models and illustrate the utilization of their equivalence [Bio-Tr1].

### **1.6** Thesis Organization

The rest of the thesis is structured as follows: In Chapter 2, we provide some preliminaries that are required for the understanding of the rest of this thesis. This includes an overview of theorem proving and the HOL4 theorem prover. In addition, we provide a summary of the required theories that are needed to develop the proposed framework.

In Chapter 3, we present the formalization of DFT operators and gates based on the algebraic approach. Then, we formally verify a set of simplification theorems that are used to conduct the formal qualitative analysis.

In Chapter 4, we provide the verification details of the probabilistic failure analysis of each DFT gate. Furthermore, we present the formal quantitative analysis of the CAS and DBW systems in the form of generic expressions of probability of failure.

As an application to our DFT formalization, in Chapter 5, we provide the formalization of the rewrite rules of DFTs, which enable the reduction of DFT models in automated DFT analysis tools. Moreover, we present the HOL formalization of n-ary gates that are required to model the rewrite rules.

In Chapter 6, we introduce the proposed DRBD algebra including DRBD operators, spare construct and structures. Furthermore, we provide the simplification theorems that are used to simplify the structure of a given DRBD. We present the formalization details of the DRBD algebra and the verified reliability expressions. Finally, we verify the equivalence of the DFT and DRBD algebras, which enables the analysis of a given system using both models.

We use the proposed framework in Chapter 7 to provide the dynamic dependability analysis of MINs of multiprocessor systems, particularly the terminal, broadcast and network reliability of shuffle-exchange networks. We provide DFT and DRBD models of these systems and verify generic expressions of probability of failure and reliability for different system scenarios. Finally, we conclude the thesis in Chapter 8 and provide some future work directions.

# Chapter 2

# Preliminaries

In this chapter, we provide some preliminaries that are required for the understanding of the rest of the thesis. We describe the HOL4 theorem prover and its probability and Lebesgue integral theories. In addition, we introduce some definitions in HOL4 that are required for the formalization of DFTs and DRBDs.

#### 2.1 HOL4 Theorem Proving

Theorem proving is one of the formal methods techniques that uses a computerized program, i.e., a theorem prover, to carry out mathematical proofs of theorems based on deductive reasoning. The level of expressiveness of these theorems depends on the type of logic used, like first-order logic and higher-order logic (HOL). There are several HOL theorem provers that are available, such as HOL4 [27], Isabelle [50] and Coq [51], which vary in the availability of the supported libraries.

HOL4 is an interactive theorem prover, which is capable of verifying a wide range of hardware and software systems as well as mathematical expressions constructed in HOL. Being an interactive tool, HOL4 requires the guidance of the verification engineer to complete the verification process. In order to verify certain properties of a system, a mathematical model for this system should be created first, then based on this model, HOL4 can be used to verify several system properties in the form of theorems. This makes HOL4 an expressive platform for the verification of any system that can be described mathematically. The main characteristic of HOL theorem proving is its soundness, i.e., only valid proof goals can be proved. The core of HOL4 consists only of four axioms and eight inference rules. Soundness is assured as any new theorem should be verified based on these axioms and rules, or based on previously proven theorems. In addition, no approximation is involved in the models, as their behavior, such as the failure in the case of DFTs, is captured in mathematical terms. These features make HOL4 suitable for carrying out the DFT based analysis of safetycritical systems that require sound verification results. The term *formalization* means to mathematically model the behavior of a system in an appropriate logic. A proof goal consists of a list of assumptions of type Boolean and a conclusion. For example, " $\forall$  (x:real). 0 < x  $\Rightarrow$  0 < x<sup>-1</sup>" is a proof goal, which can be formally verified as a theorem in HOL4. A *theory* in HOL4 is a collection of definitions, constants and theorems that can be included in the working environment to be used in verifying other proof goals. Table 2.1, lists some of the used symbols in HOL.

## 2.2 Probability Theory

The probability theory is formalized based on the measure theory in HOL4 [28]. A measurable space is represented as a pair  $(\mathcal{X}, \mathcal{A})$ , where  $\mathcal{X}$  represents a space and  $\mathcal{A}$  a set of measurable sets. The functions **space** and **subsets** are defined in HOL to return the  $\mathcal{X}$  and  $\mathcal{A}$ , respectively, of a measurable space  $(\mathcal{X}, \mathcal{A})$ . A measure is

| HOL Symbol            | Meaning                                       |  |  |

|-----------------------|-----------------------------------------------|--|--|

| $\land$               | Logical and                                   |  |  |

| V                     | Logical or                                    |  |  |

|                       | Appends a new element to a list               |  |  |

| ++                    | Joins two lists                               |  |  |

| HD L                  | Head of a list $L$                            |  |  |

| TL L                  | Tail of list $L$                              |  |  |

| (a,b)                 | A pair with elements $a$ and $b$              |  |  |

| FST                   | First element of a pair                       |  |  |

| SND                   | Second element of a pair                      |  |  |

| $\lambda$ x. f x      | Lamda abstracted function $f$                 |  |  |

| $\{x \mid P \mid x\}$ | Set of elements $x$ that satisfy $P(x)$       |  |  |

| FINITE s              | set $s$ is finite                             |  |  |

| A DIFF B              | A - B                                         |  |  |

| e INSERT s            | <b>INSERT s</b> insert element $e$ in set $s$ |  |  |

| s DELETE e            | A set that has all elements of $s$ except $e$ |  |  |

| DISJOINT A B          | sets $A$ and $B$ are disjoint                 |  |  |

Table 2.1: Some HOL Symbols

generally a function that designates a certain number to a set, which represents the size of this set [17]. It is defined as the triplet  $(\mathcal{X}, \mathcal{A}, \mu)$ , where  $\mathcal{X}$  represents the space,  $\mathcal{A}$  represents the measurable sets and finally  $\mu$  represents the measure. Three functions, m\_space, measurable\_sets and measure, are defined in HOL to return the space  $(\mathcal{X})$ , measurable sets  $(\mathcal{A})$  and measure  $(\mu)$  of a measure space, respectively [52]. A probability space is defined as a measure space, with the added condition that the probability measure for the entire space is equal to 1.

Random variables are formalized as measurable functions that map events from the probability space to some other  $\sigma$ - algebra space s. For a collection of subsets of a space  $(\mathcal{X})$ ,  $(\mathcal{A})$  is a  $\sigma$ - algebra on  $(\mathcal{X})$  if it contains the empty set, and is closed under countable unions and complements within the space  $(\mathcal{X})$  [17]. Random variables are defined in HOL4 as in [17]:

#### Definition 2.1.

#### $\vdash \forall X p s.$ random\_variable X p s $\Leftrightarrow$

prob\_space p  $\land$  X  $\in$  measurable (p\_space p, events p) s

where prob\_space p ensures that p is a probability space with p\_space as its space and events as its measurable sets.  $X \in$  measurable (p\_space p, events p) s ensures that X belongs to the set of measurable functions from the probability space p to the  $\sigma$ -algebra space s [52]. Measurable spaces s and (p\_space p, events p) are ensured to be  $\sigma$ -algebra spaces using the measurable function.

The probability distribution of a random variable X represents the probability that the random variable X belongs to a set A. This is equivalent to finding the probability of the event  $\{X \in A\}$ , which can also be represented using the preimage as  $X^{-1}(A)$ . The probability distribution is defined in HOL4 as in [17]:

#### Definition 2.2.

$\vdash$   $\forall$  p X. distribution p X = ( $\lambda \texttt{s}.$  prob p (PREIMAGE X s  $\cap$  p\_space p))

where  $\mathbf{s}$  is a set of elements of the space that the random variable X maps to. For a random variable that maps the probability space (p) into another measurable space, the push forward measure is a measure that uses the space and subsets of the measurable space as its space and measurable sets and uses the distribution of the random variable as its measure part [18]. In general, the push forward measure for any measurable function X from measure M to measure N can be expressed as:

## Definition 2.3.

```

\vdash \forall M N f. distr M N f =

(m_space N, measurable_sets N,

\lambda A. measure M (PREIMAGE f A \cap m_space M))

```

A density measure is used to define a density function, f, over the measure space M as in [53]:

#### Definition 2.4.

```

\vdash \forall M f. density M f =

(m_space M, measurable_sets M,

\lambda A. pos_fn_integral M (\lambda x. f x * indicator_fn A x))

```

where **pos\_fn\_integral** represents the Lebesgue integral of positive functions as will be described in the following section.

The cumulative distribution function (CDF) of a random variable X is usually used when we are interested in finding the probability that the random variable is less than or equal to a certain value. It is formally defined for real values as in [23]:

## Definition 2.5.

```

\vdash \forall p X t. CDF p X t = distribution p X {y | y \leq (t:real)}

```

It is worth mentioning that the CDF can be defined for extended-real (extreal) random variables as well, where extreal is a HOL data-type containing the real numbers plus  $\pm \infty$ . However, in our formalization we will use the CDF of real random variables, as it is required to integrate their density functions over the real line.

When dealing with multiple random variables, the probabilistic *Principle of Inclusion and Exclusion* (PIE) provides a very interesting relationship between the probability of the union of different events. It can be expressed as:

$$Pr(\bigcup_{i=1}^{n} A_i) = \sum_{t \neq \{\}, t \subseteq \{1, 2, \dots, m\}} (-1)^{|t|+1} Pr(\bigcap_{j \in t} A_j)$$

(2.1)

It has been formally verified in HOL4 as follows [23]:

Theorem 2.1.

$\vdash \forall p L.$

prob\_space p  $\land$  ( $\forall$  x. MEM x L  $\Rightarrow$  x  $\in$  events p)  $\Rightarrow$

(prob p (union\_list L = sum\_set {t | t

$$\subseteq$$

set L  $\land$  t  $\neq$  {}}

$(\lambda t. -1 \text{ pow (CARD } t+1) * \text{ prob p (BIGINTER } t))$

where L is the list of events that we are interested in expressing the probability of their union.

In order to be able to handle multiple random variables, a pair measure (often called binary product measure) is required to be able to model joint distribution measures. This pair measure can be also used in a nested way to model the joint distribution measure of multiple random variables. The pair measure is defined as the product of two measures. It was initially formalized in Isabelle/HOL [18] and was then ported to HOL4 [53]. The space and the measurable sets of this pair measure are generated using the Cartesian product of the spaces and the measurable sets of the participating measures, while the measure part is defined using the Lebesgue integral.

Since there are real and extended-real data-types in HOL4, there exist two Borel spaces, one over the real line (borel) [54] and the second over the extended-real line (Borel) [49]. The Lebesgue-Borel measure is required to integrate over the real line. In particular, we need the Lebesgue-Borel measure in this work to integrate the density functions of the random variables over the real line. The Lebesgue-Borel measure is a measure defined over the real line, which uses the real line as its space and the Borel sets as its measurable sets. The Lebesgue-Borel measure is defined in HOL4 as lborel, which uses the real borel sigma algebra (borel) generated by the open sets of the real line as well as the Lebesgue measure [54]. The independence of random variables is an important property when dealing with multiple random variables. In general, for any two random variables X and Y, the probability of the intersection of their events is equal to the multiplication of the probability of the individual events. The independence of random variables is defined as indep\_vars [53]:

### Definition 2.6.

```

\vdash indep_vars p M X ii =

(∀ i. i ∈ ii ⇒

random_variable (X i) p

(m_space (M i), measurable_sets (M i))) ∧

indep_sets p

(λi. {PREIMAGE f A ∩ p_space p |

(f = X i) ∧ A ∈ measurable_sets (M i)}) ii

```

where **p** is the probability space and **M** is the measure space that the random variable **X** maps to. In this case, **M** and **X** are indexed by a number from the set of numbers ii, which gives the possibility of defining the independence for multiple random variables that map from the probability space to different spaces. The function indep\_vars defines the independence by first ensuring that the group of input functions **X** are random variables and that their event sets are independent using indep\_sets. Using indep\_sets, the probability of the intersection of any sub-group of events of the random variables is equal to the multiplication of the probability of the individual events.

Using indep\_vars, the independence of two random variables is defined as in [53]:

Definition 2.7.

```

\vdash indep_var p M_x X M_y Y =

```

indep\_vars p ( $\lambda$ i. if i = 0 then M\_x else M\_y) ( $\lambda$ i. if i = 0 then X else Y) {x | (x = 0)  $\lor$  (x = 1)}

We define several functions that facilitate handling our formalization. The first function is measurable\_CDF, which is defined as:

#### Definition 2.8.

```

\vdash \forall p X. measurable_CDF p X =

```

( $\lambda$ x. CDF p X x)  $\in$  measurable borel Borel

This function ensures that the CDF of random variable X is measurable from the **borel** space to the **Borel** space. In other words, it ensures that the CDF is measurable from the real line to the extended-real line. This implies that the domain for this CDF is the real line and the range is the extended-real line.

We define another function, cont\_CDF, which ensures that the CDF is continuous. It is formally defined as:

## Definition 2.9.

$\vdash$   $\forall$  p X. cont\_CDF p X =  $\forall$  z. ( $\lambda$ x. real (CDF p X x)) contl z

where the function real typecasts the value of CDF from extended-real to real datatype, and contl ascertains that the function is continuous over all values in its domain. It is worth mentioning that X is a real valued random variable. However, the CDF returns extended-real. As the continuity of functions is defined in HOL4 for real valued functions, it is required to typecast the value of the CDF from extended-real to real. In addition, since the values of the CDF range from 0 to 1, as it represents a probability, this function is the same in both cases but with different datatypes. Therefore, if the function is continuous in the extended-real, then it is continuous using the real data-type. Furthermore, later we will use extended-real random variables, therefore, it is required to typecast their values using the **real** function.

Next, we define a function,  $rv_gt0_ninfinity$ , to ensure that the input random variables of a DFT can only have the range  $[0, +\infty)$ :

## Definition 2.10.

```

⊢ (rv_gt0_ninfinity [] = T) ∧

(rv_gt0_ninfinity (h::t) = (∀ s. 0 ≤ h s ∧ h s ≠ PosInf) ∧

(rv_gt0_ninfinity t))

```

Finally, we define a function, den\_gt0\_ninfinity to ensure the proper values for the marginal, joint and conditional density functions:

## Definition 2.11.

```

\begin{array}{l} \vdash \forall \ f\_xy \ f\_y \ f\_cond.\\ \\ den\_gt0\_ninfinity \ f\_xy \ f\_y \ f\_cond \Leftrightarrow\\ \\ \forall \ x \ y.\\ \\ 0 \ \leq \ f\_xy \ (x,y) \ \land \ 0 \ < \ f\_y \ y \ \land \ f\_y \ y \ \neq \ \texttt{PosInf} \ \land \ 0 \ \leq \ f\_cond \ y \ x \end{array}

```

where  $f_xy$  is the joint density function,  $f_y$  is the marginal density function, and finally  $f_cond$  is the conditional density function of X given Y. This function can be used to assign the mentioned conditions to other functions and not necessarily only the density functions.

## 2.3 Lebesgue Integral

The Lebesgue integral is defined in HOL4 using positive simple functions, which are measurable functions defined as a linear combinations of indicator functions of measurable sets representing a partition of the space X [28]. A positive simple function, g, can be represented using the triplet (s, a, x) as [28]:

$$\forall t \in X, \ g(t) = \sum_{i \in s} x_i \mathbf{1}_{a_i}(t), \quad x_i \ge 0$$

(2.2)

where s is a finite set of partition tags,  $x_i$  is a sequence of positive extreal numbers,  $a_i$  is a sequence of measurable sets and  $\mathbf{1}_{a_i}$  is the indicator function of measurable set  $a_i$  and is defined as in [28]:

#### Definition 2.12.

$$\vdash$$

$\forall$  A. indicator\_fn A = ( $\lambda$ x. if x  $\in$  A then 1 else 0)

The Lebesgue integral is first defined for positive simple functions and then extended for positive functions for measure M as pos\_fn\_integral M ( $\lambda x$ . f x) [28], where f is the positive function that we are integrating. In this work, we are integrating the density functions over the real line. Therefore, we will use the Lebesgue-Borel measure with the Lebesgue integral. The Lebesgue-Borel (lborel) measure is a measure defined over the real line. As with any measure, lborel should have a space and measurable sets. For lborel, the real line represents its space and the borel sets represent the lborel measurable sets [54]. For example, the Lebesgue integral of the positive function f from 0 to t ( $\int_0^t f(x) dx$ ) can be expressed formally as: pos\_fn\_integral lborel ( $\lambda x$ . f x \* indicator\_fn {x'| 0 \le x' \land x' \le t} x), where the indicator function is used here to set the interval that we are integrating over. Throughout this thesis, we will use a mix of standard and HOL math notation to facilitate the readability of the text.

It is usually required that the probability of an event for a random variable to be expressed using the integration of the random variable's distribution. This is verified in HOL4 as [17]:

Theorem 2.2.

```

⊢ ∀ X p s A.

random_variable X p s ∧ A ∈ subsets s ⇒

(distribution p X A =

integral (space s, subsets s, distribution p X)(indicator_fn A))

```

In the above theorem, X can be a continuous or a discrete random variable. However, in our DFT formalization, we are only interested in continuous random variables as they represent the time of failure of system components.