# Modular DC/DC Converter Topologies for Off-shore DC Collection Point

He Liu

B.Sc., M.Sc.

A thesis submitted for the degree of Doctor of Philosophy

August 2018

School of Electrical and Electronic Engineering

Newcastle University

United Kingdom

#### **Abstract**

With the development of the economy, the demand for energy has been substantially growing. Wind power, particularly from offshore wind farms, is one of the best solutions. In Europe, installed capacity had exceeded 8GW by 2105 and will probably reach 40GW in 2020. These ambitious plans require the establishment of large-scale wind farms with more efficient transmission systems. The high voltage direct current (HVDC) transmission system is an effective way to deliver large-scale energy over long distances with lower power losses. However, due to the growth of large-scale offshore wind energy system, the connection between the farms and HVDC transmission lines is more challenging. Medium-voltage DC (MVDC) collection networks are a promising technology for such integration, aiming to eliminate voltage difference. High-voltage high-power DC/DC converters are the key enabler for MVDC grids. But the present lack of suitable high-voltage high-power DC/DC converter topologies is preventing the development of DC networks. Several high-voltage high-power topologies have proposed in previous studies, but most such topologies involve design compromises in terms of switching losses, limited conversion ratios, and lack of modular design, lack of electrical isolation features.

This thesis presents three novel modular DC/DC topologies, which are developed based on the conventional modular multilevel converter (MMC), to enable the integration of off-shore wind farms with high voltage direct current (HVDC) transmission systems. The first topology is a unidirectional single-phase modular DC/DC converter, and the second is a unidirectional three-phase modular DC/DC converter consisting of a windfarm-side three-phase modular multilevel (MMC) inverter and a series-connected diode rectifier module linked by a special decoupled medium frequency transformer. The third topology is a bidirectional three-phase modular DC/DC converter where a three-phase MMC inverter produces a controllable AC voltage connected at the primary side of a three-phase decoupled medium frequency transformer. The secondary output voltages decoupled into three identical but 120-degree phase-shifted voltages. Simulations using MATLAB/Simulink are reported to demonstrate the effectiveness of the proposed converters. Moreover, a low voltage scaled-down prototype of the unidirectional

single-phase modular DC/DC converter is developed to validate its feasibility experimentally.

**Keywords:** Modular multilevel converter, offshore wind farm, unidirectional/bidirectional modular DC/DC converters, HVDC system.

# **Dedication**

I dedicate this thesis to my grandparents, parents, and girlfriend.

## Acknowledgements

Firstly, I am very grateful to my tutor, Dr Mohamed Dahidah, for giving me a lot of encouragement and great help. His guidance enabled me to complete this project. His hard work has deeply influenced my attitude toward academics.

I am very grateful for James Yu, R. T. Naayagi, and Matthew Armstrong for their financial support, valuable comments, and encouragement, which are important for me to overcome different challenges during the process of my research.

I am very grateful for my parents, Liu Bo and Liu Wei Dong, as well as my girlfriend, Liang Yuan Lin, for their support and encouragement during my study in the UK.

I am grateful for all my friends who gave me precious memory, valuable comments, and encouragement.

Finally, I am grateful for Scottish Energy for their financial support to this project.

# **Table of Contents**

| Abstract                                                             | I    |

|----------------------------------------------------------------------|------|

| Dedication                                                           | III  |

| Acknowledgements                                                     | IV   |

| Table of Contents                                                    | V    |

| List of Figures                                                      | VIII |

| List of Symbols                                                      | XV   |

| List of Abbreviations                                                | XVII |

| Chapter 1. Introduction                                              | 1    |

| 1.1 Historical Development of HVDC Systems                           | 1    |

| 1.2 Comparison Between HVDC and HVAC Transmission Systems            | 2    |

| 1.3 Offshore Wind Farm System                                        | 3    |

| 1.4 Real Examples of Offshore HVDC Systems                           | 8    |

| 1.5 Objectives of the Thesis                                         | 10   |

| 1.6 Thesis Contributions and Publications                            | 10   |

| 1.7 Dissertation Outline                                             | 12   |

| Chapter 2. Conventional High-Voltage High-Power DC/DC Converters     | 14   |

| 2.1 Introduction                                                     | 14   |

| 2.2 Cascaded Modular DC/DC Converters                                | 14   |

| 2.3 Modular Multilevel DC/DC Converters                              | 17   |

| 2.4 Research Prospects for High-Voltage High-Power DC/DC Converters  | 19   |

| 2.5 Summary                                                          | 20   |

| Chapter 3. Basic Theory and Analysis of MMC                          | 21   |

| 3.1 Introduction                                                     | 21   |

| 3.2 The Configuration of the MMC and its Basic Operating Principles  | 21   |

| 3.3 Mathematical Model of MMC                                        | 23   |

| 3.3.1 Switching model of MMC                                         | 24   |

| 3.3.2 Average model of MMC                                           | 26   |

| 3.3.3 dq rotating average model of MMC                               | 30   |

| 3.4 Power Fluctuation Characteristics in the Arms of MMC             | 31   |

| 3.5 Switching Modulation of the MMC                                  | 35   |

| 3.6 SM Voltage Balance Control of the MMC                            | 36   |

| 3.6.1 PI controller-based capacitor voltage balance control strategy | 36   |

| 3.6.2 Sorting algorithm                                                   | 39 |

|---------------------------------------------------------------------------|----|

| 3.7 Summary                                                               | 40 |

| Chapter 4. Unidirectional Single-Phase DC/DC Modular Multilevel Converter | 41 |

| 4.1 Introduction                                                          | 41 |

| 4.2 Configuration of the Proposed Converter                               | 41 |

| 4.3 Mathematical Model                                                    | 43 |

| 4.4 Output Power Characteristics                                          | 46 |

| 4.4.1 The typical voltage waveform                                        | 46 |

| 4.4.2 Derivation of output power                                          | 47 |

| 4.4.3 Output power characteristics                                        | 49 |

| 4.5 Control Strategy of the Proposed Converter                            | 50 |

| 4.6 Simulation Results                                                    | 50 |

| 4.7 Summary                                                               | 58 |

| Chapter 5. Unidirectional Three-Phase DC/DC Modular Multilevel Converter  | 59 |

| 5.1 Introduction                                                          | 59 |

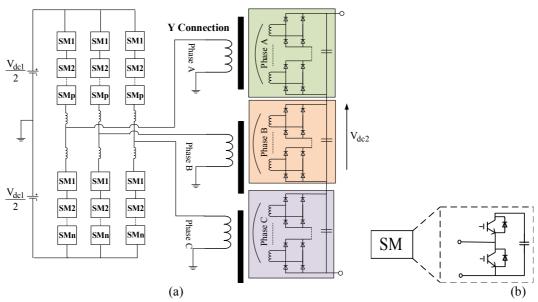

| 5.2 Configuration of the Proposed Converter                               | 59 |

| 5.3 Mathematical Model                                                    | 61 |

| 5.4 Output Power Characteristics                                          | 63 |

| 5.4.1 Typical voltage waveforms                                           | 63 |

| 5.4.2 Derivation of the output power                                      | 65 |

| 5.4.3 Output power characteristics                                        | 67 |

| 5.5 Control Strategy of the Proposed Converter                            | 68 |

| 5.6 Simulation Results                                                    | 70 |

| 5.7 Summary                                                               | 76 |

| Chapter 6. Bidirectional Three-Phase DC/DC Modular Multilevel Converter   | 77 |

| 6.1 Introduction                                                          | 77 |

| 6.2 Configuration of the Proposed Converter                               | 77 |

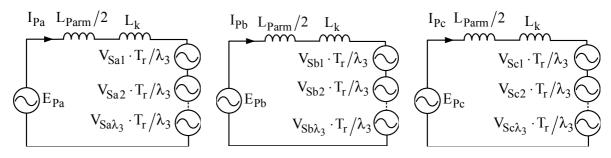

| 6.3 Mathematical Model                                                    | 78 |

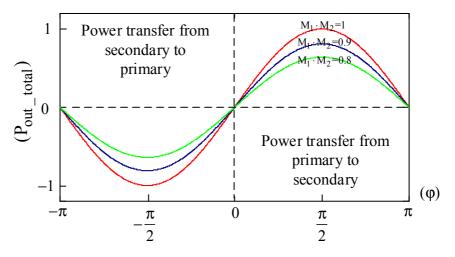

| 6.4 Output Power Characteristics                                          | 82 |

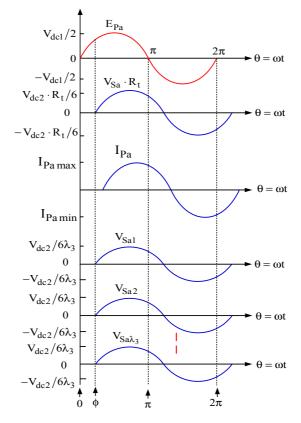

| 6.4.1 Typical voltage waveforms                                           | 82 |

| 6.4.2 Derivation of the output power                                      | 82 |

| 6.4.3 Output power characteristics                                        | 84 |

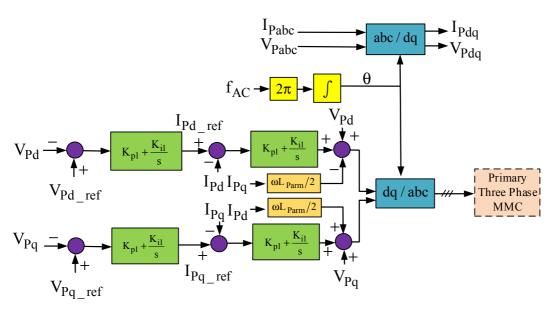

| 6.5 Control Strategies of the Proposed Converter                          | 85 |

| 6.6 Simulation Results                                                    | 91 |

| 6.7 Summary                                                                                                           | 100 |

|-----------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 7. Calculation of Losses and Comparison of Topologies                                                         | 101 |

| 7.1 Introduction                                                                                                      | 101 |

| 7.2 Calculation of Losses in the IGBT Modules of the MMC                                                              | 101 |

| 7.3 Calculation of Losses in the Medium Frequency Transformer                                                         | 106 |

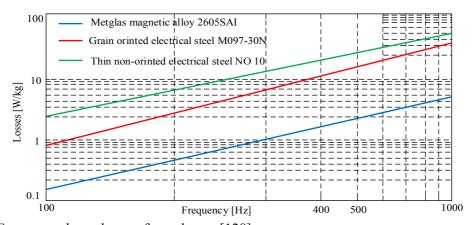

| 7.3.1 Medium frequency transformer design considerations                                                              | 106 |

| 7.3.2 Calculation of losses in the transformer                                                                        | 108 |

| 7.4 Evaluation of the Efficiency of the Converters                                                                    | 109 |

| 7.5 Comparison of Topologies                                                                                          | 110 |

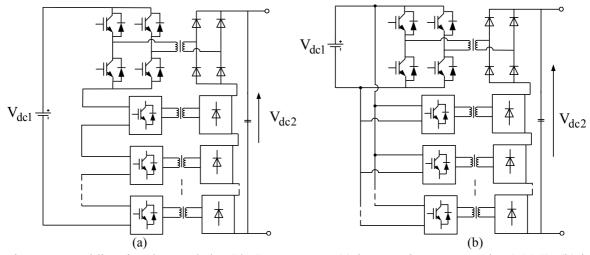

| 7.5.1 Comparison of topologies of the unidirectional DC/DC converters                                                 | 110 |

| 7.5.2 Comparison of topologies of the bidirectional DC/DC converters                                                  | 117 |

| 7.6 Summary                                                                                                           | 122 |

| Chapter 8. Components Design and Experimental results of the Unidirectional Sin<br>Modular Multilevel DC/DC Converter | _   |

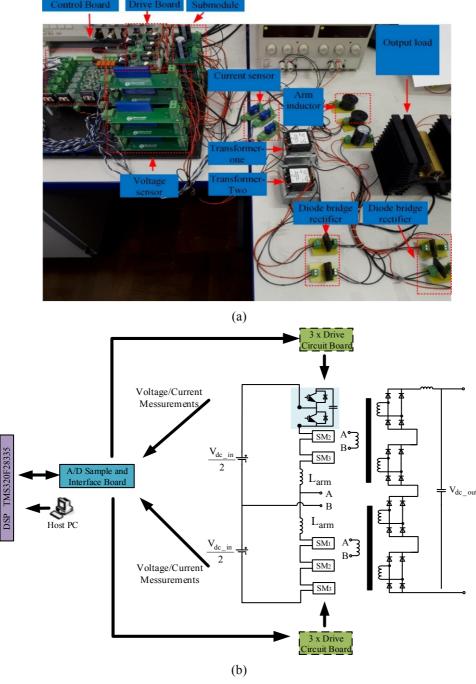

| 8.1 Introduction                                                                                                      | 123 |

| 8.2 Design Considerations for the Laboratory Prototype                                                                | 123 |

| 8.2.1 Submodule capacitor selection                                                                                   | 123 |

| 8.2.2 Arm inductor selection                                                                                          | 123 |

| 8.2.3 Consideration of the output filter                                                                              | 127 |

| 8.3 Transformer Design Example                                                                                        | 130 |

| 8.4 Control System                                                                                                    | 133 |

| 8.5 Experimental Results                                                                                              | 136 |

| 8.5.1 Experimental results of laboratory prototype with single transformer                                            | 138 |

| 8.5.2 Experimental results of laboratory prototype with two transformers                                              | 144 |

| 8.6 Summary                                                                                                           | 151 |

| Chapter 9. Conclusion and Future Work                                                                                 | 152 |

| 9.1 Conclusions                                                                                                       | 152 |

| 9.2 Further work                                                                                                      | 154 |

| References                                                                                                            | 156 |

# **List of Figures**

| Figure 1.1 A basic offshore transmission system [2].                                               | 4     |

|----------------------------------------------------------------------------------------------------|-------|

| Figure 1.2Wind turbine connection mode: (a) radial connection; (b) loop connection [2]             | 5     |

| Figure 1.3 General offshore HVAC transmission system with AC collection network [2]                | 6     |

| Figure 1.4 General offshore windfarm HVDC transmission system with mixed AC/                       | /DC   |

| collection network [2].                                                                            | 6     |

| Figure 1.5 General offshore HVDC transmission system with a DC collection (paral                   | llel- |

| connected wind turbines) network [2].                                                              | 7     |

| Figure 1.6 General offshore HVDC transmission system with a DC collection (series-connec           | cted  |

| wind turbines) network [2]                                                                         | 7     |

| Figure 2.1 Schematic diagrams of unidirectional cascaded DC/DC converters: (a) input-para          | ıllel |

| output-series (IPOS); (b) input-parallel output-parallel (IPOP); (c) input-series output-parallel  | ıllel |

| (ISOP); (d) input-series output-series (ISOS).                                                     | . 15  |

| Figure 2.2 Schematic diagram of unidirectional cascaded input-series-input-parallel outp           | put-  |

| series (ISIPOS) DC/DC converter                                                                    | . 15  |

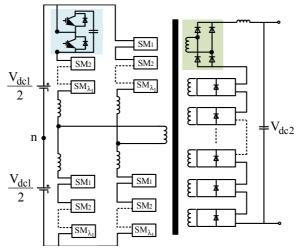

| Figure 2.3 Two MMCs based DC/DC converter: (a) single-phase; (b) three-phase; (c) the              | heir  |

| possible half-bridge and full-bridge submodules.                                                   | . 18  |

| Figure 3. 1 Commercialized MMC-based HVDC project: (a) submodule of the MMC; (b) MI                | MC    |

| arm; (c) complete structure of the MMC [107]                                                       | . 21  |

| Figure 3. 2 Configuration of: (a) three-phase MMC; (b) its possible half-bridge and full-bri       | dge   |

| SMs.                                                                                               | . 22  |

| Figure 3. 3 Operating states of half-bridge SM: (a) state: $V_{SM} = V_C$ ; (b) sate: $V_{SM} = 0$ | . 22  |

| Figure 3. 4 Derivation process of simplified mathematical model of MMC                             | . 24  |

| Figure 3. 5 (a) Schematic diagram of the one-leg MMC and (b) its equivalent circuit                | . 24  |

| Figure 3. 6 Equivalent circuit of the final simplified average model of the MMC.                   | . 30  |

| Figure 3. 7 Equivalent circuits of the dq rotating average model of the MMC                        | . 31  |

| Figure 3. 8 Equivalent circuits of one-leg MMC: (a) balanced energy condition; (b) unbalan         | iced  |

| energy condition.                                                                                  | . 32  |

| Figure 3. 9 Different modulation strategies for the MMC.                                           | . 35  |

| Figure 3. 10 Carrier phase shift modulation (CPS-PWM): (a) upper arm modulation; (b) lower                     |

|----------------------------------------------------------------------------------------------------------------|

| arm modulation. 36                                                                                             |

| Figure 3. 11 Schematic diagrams of the voltage balancing controllers, including SM voltage                     |

| (red dotted line) control and arm average voltage control (blue dotted line)                                   |

| Figure 3. 12 The process of the sorting algorithm.                                                             |

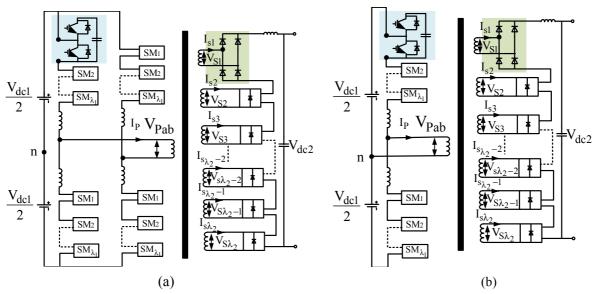

| Figure 4. 1 Proposed modular DC/DC converter with single transformer: (a) single-phase (two-                   |

| leg) MMC-based DC/DC converter; (b) one-leg MMC-based DC/DC converter42                                        |

| Figure 4. 2 Proposed modular DC/DC converter with multiple transformers: (a) single-phase                      |

| (two-leg) MMC-based DC/DC converter; (b) one-leg MMC-based DC/DC converter42                                   |

| Figure 4. 3 One-leg MMC: (a) Schematic diagram of the one-leg MMC; (b) equivalent circuit.                     |

| 43                                                                                                             |

| Figure 4. 4 Equivalent circuit of the proposed converter referred to the primary side45                        |

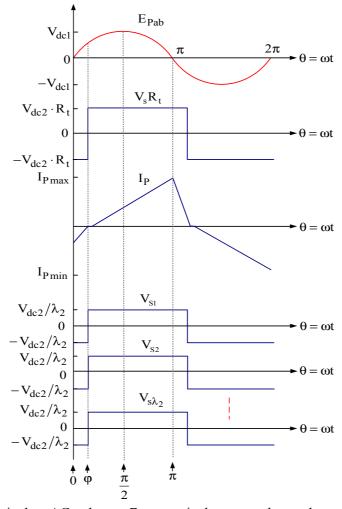

| Figure 4. 5 Primary equivalent AC voltage, $E_{Pab}$ ; equivalent secondary voltage refer to the               |

| primary side, $V_SRt$ ; secondary AC voltages of each winding of the transformer,                              |

| $V_{S1}, V_{S2}, \dots, V_{S\lambda 2}$ 46                                                                     |

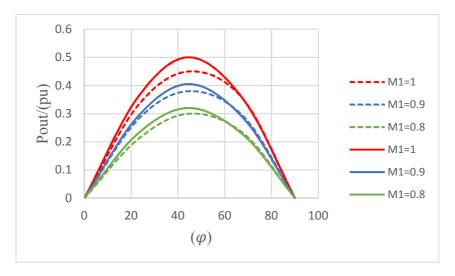

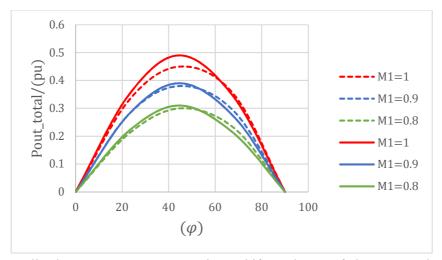

| Figure 4. 6 Normalized output power versus phase shift angle $\phi$ of the proposed converter                  |

| with different values of modulation index $(M_1)$ ; the solid line represents theoretical results and          |

| the dashed line represents simulation results. 49                                                              |

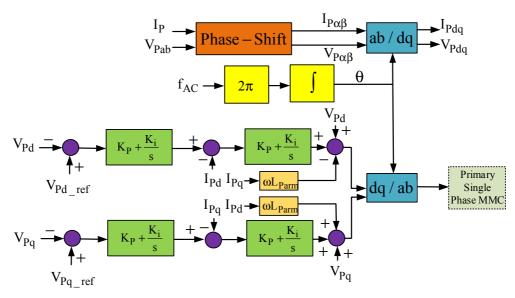

| Figure 4. 7 Schematic diagram of the proposed control strategy based on the d-q rotating                       |

| reference frame. 51                                                                                            |

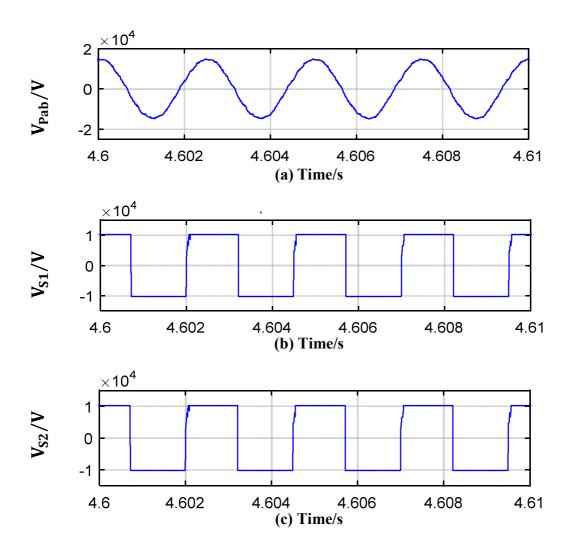

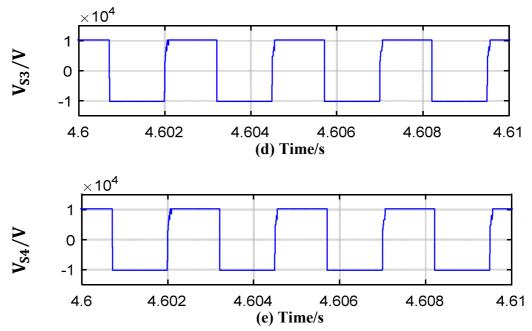

| Figure 4. 8 Transformer voltage waveforms: (a) primary terminal voltage $V_{Pab}$ ; (b) secondary              |

| winding-one voltage $V_{S1}$ ; (c) secondary winding-two voltage $V_{S2}$ ; (d) secondary winding-three        |

| voltage $V_{S3}$ ; (e) secondary winding-four voltage $V_{S4}$ .                                               |

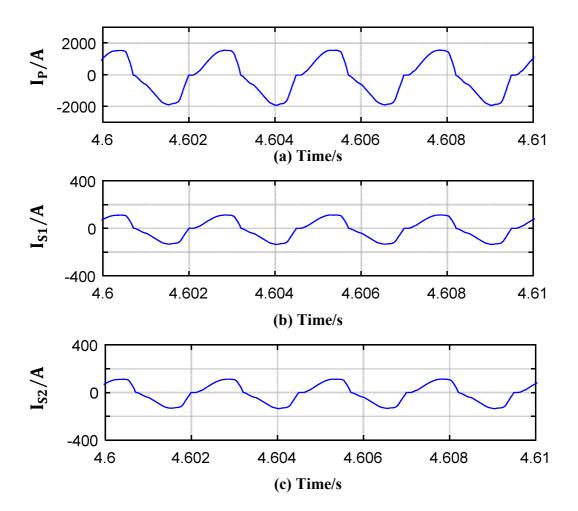

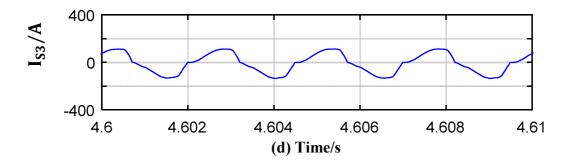

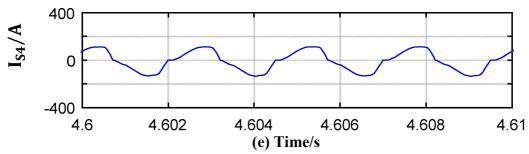

| Figure 4. 9 Transformer current waveforms: (a) primary current $I_P$ ; (b) secondary winding-one               |

| current $I_{S1}$ ; (c) secondary winding-two current $I_{S2}$ ; (d) secondary winding-three current $I_{S3}$ ; |

| (e) secondary winding-four current $I_{S4}$                                                                    |

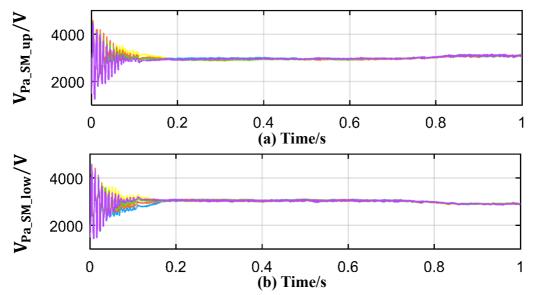

| Figure 4. 10 Upper and lower SM voltages. 56                                                                   |

| Figure 4. 11 Output waveforms of the proposed converter under steady-state operation: (a)                      |

| output DC voltage; (b) output DC current; (c) output power                                                     |

| Figure 4. 12 The output waveforms of the proposed converter under a step change at 2.5s: (a)                   |

| transformer primary terminal voltage waveform; (b) output DC voltage, (c) output DC current            |

|--------------------------------------------------------------------------------------------------------|

| (d) output power. 58                                                                                   |

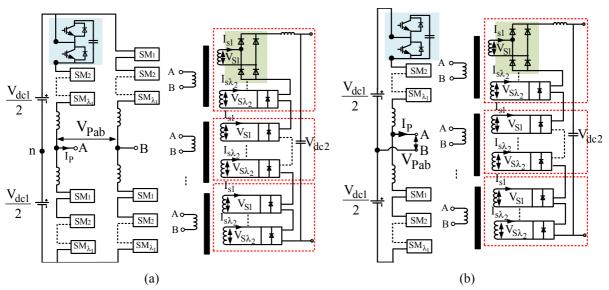

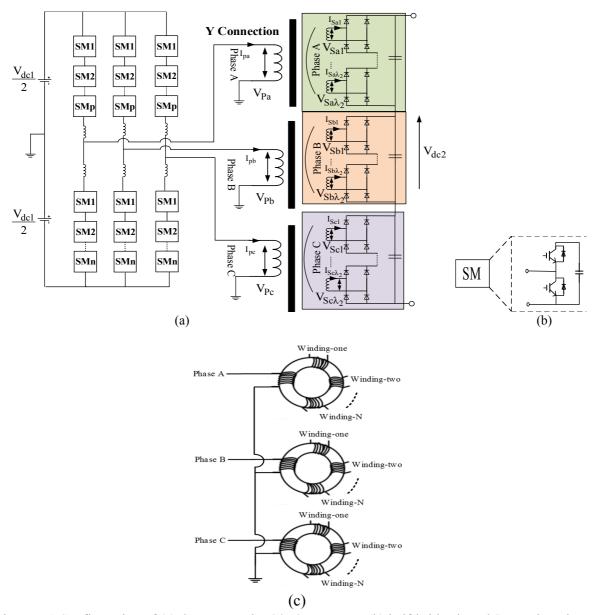

| Figure 5. 1 Configuration of the (a) proposed DC/DC converter; (b) half-bridge-based SM a              |

| the primary side of the proposed converter; and (c) configuration of decoupled transformer. 60         |

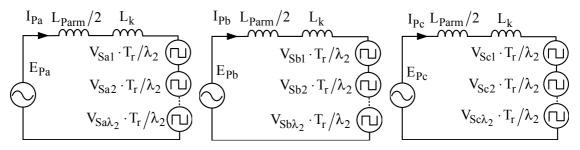

| Figure 5. 2 Phase-a: (a) schematic diagram; (b) equivalent circuit                                     |

| Figure 5. 3 Equivalent circuit of the proposed converter referred to the primary side 63               |

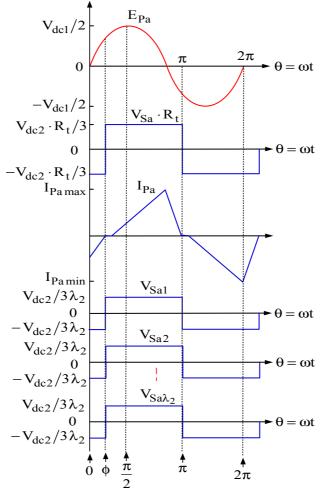

| Figure 5. 4 Phase-a: primary equivalent AC voltage, $E_{Pa}$ ; equivalent secondary voltage references |

| to the primary side, $V_{Sa}Rt$ ; secondary AC voltages of each winding of the transformer             |

| $V_{Sa1}, V_{Sa2}, \dots, V_{Sa\lambda 2}$                                                             |

| Figure 5. 5 Normalized output power versus phase shift angle $\phi$ of the proposed converted          |

| with different values of modulation index $(M_1)$ ; the solid line represents theoretical results and  |

| the dashed line simulation results                                                                     |

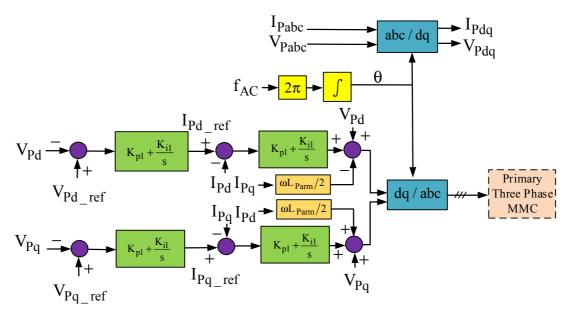

| Figure 5. 6 Control system for the primary three-phase MMC-based inverter                              |

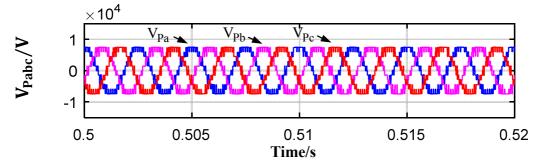

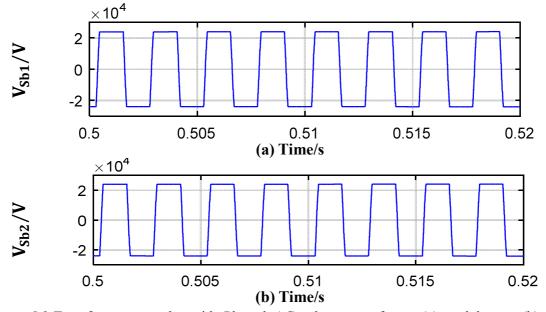

| Figure 5. 7 Transformer primary three-phase AC voltages                                                |

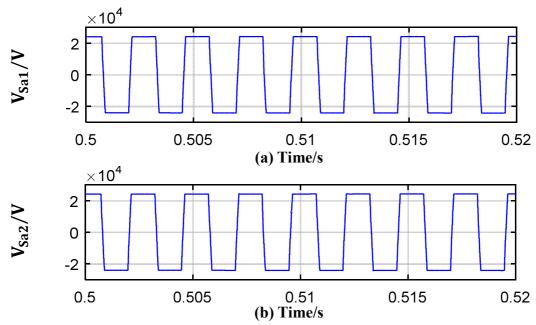

| Figure 5. 8 Transformer secondary side Phase-a AC voltage waveforms: (a) module-one; (b)               |

| module-two. 72                                                                                         |

| Figure 5. 9 Transformer secondary side Phase-b AC voltage waveforms: (a) module-one; (b)               |

| module-two. 72                                                                                         |

| Figure 5. 10 Transformer secondary side Phase-c AC voltage waveforms: (a) module-one; (b)              |

| module-two. 73                                                                                         |

| Figure 5. 11 Transformer primary three-phase AC currents.                                              |

| Figure 5. 12 Transformer current waveforms: (a) secondary side Phase-a module-one and                  |

| module-two AC current. (b) secondary side Phase-b module-one and module-two AC current                 |

| (c) secondary side Phase-c module-one and module-two AC current                                        |

| Figure 5. 13 Primary Phase-a: (a) upper SM voltages and (b) lower SM voltages                          |

| Figure 5. 14 Output waveforms of the proposed converter under steady-state operation: (a)              |

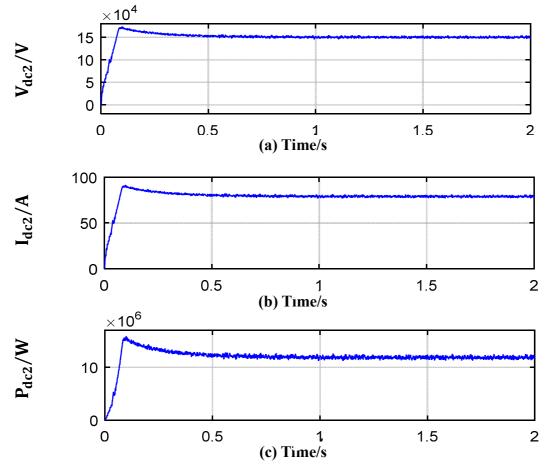

| output DC voltage; (b) output DC current; (c) output power                                             |

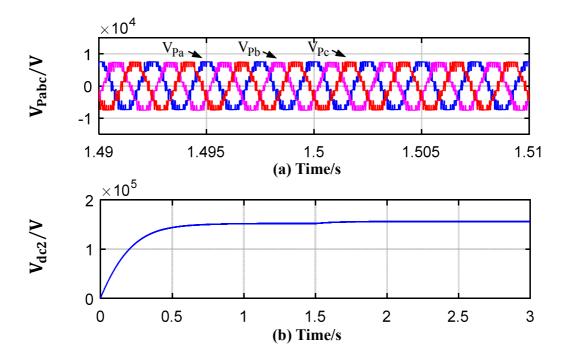

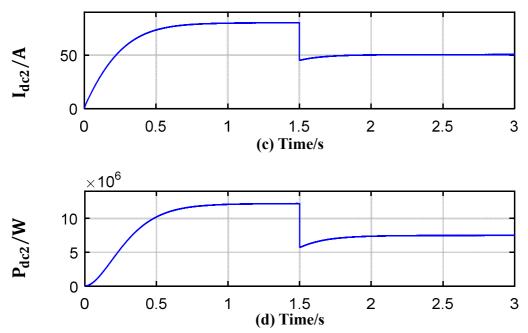

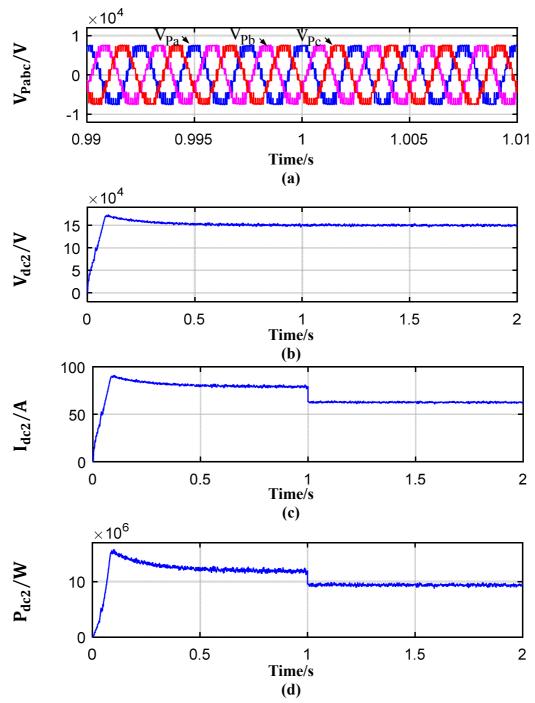

| Figure 5. 15 Output waveforms of the proposed converter under a step change at 1.5s:(a)                |

| transformer primary three-phase AC voltages; (b) output DC voltage; (c) output DC current; (d)         |

| output power                                                                                           |

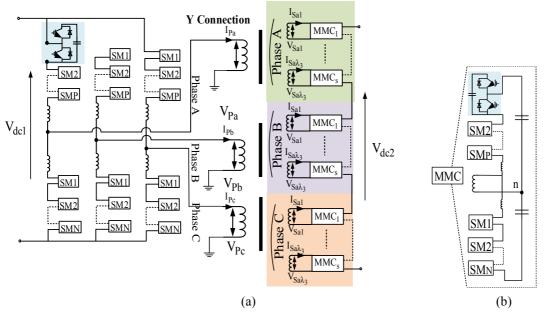

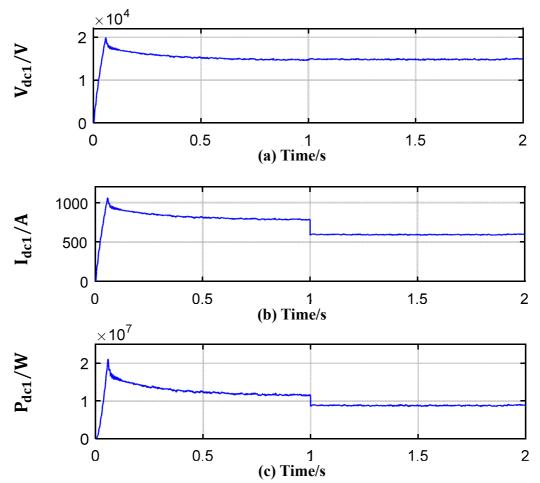

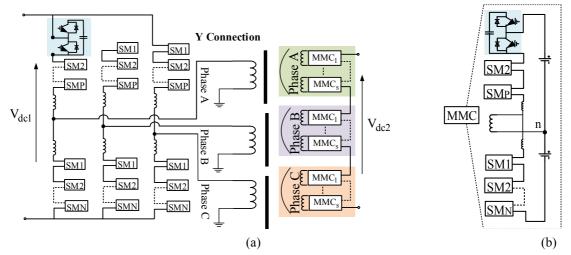

| Figure 6.1 (a) The proposed DC/DC converter configuration; (b) one-leg MMC based                    |

|-----------------------------------------------------------------------------------------------------|

| submodule at the secondary side of the proposed converter                                           |

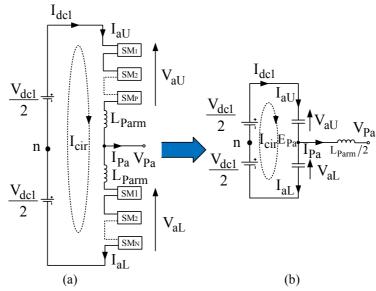

| Figure 6.2 The one-leg MMC: (a) schematic diagram; (b) equivalent circuit79                         |

| Figure 6.3 Equivalent circuit of the proposed converter referred to the primary side81              |

| Figure 6.4 Phase-a: primary equivalent AC voltage, $E_{Pa}$ ; equivalent secondary volatge refer to |

| the primary side, $V_{Sa}Rt$ ; secondary AC voltages of each winding of the transformer,            |

| $V_{Sa1}, V_{Sa2}, \dots, V_{Sa\lambda 3}$                                                          |

| Figure 6.5 Normalized output power versus phase shift angle $\varphi$ of the proposed converter. 85 |

| Figure 6.6 Control system for the primary three-phase MMC-based inverter                            |

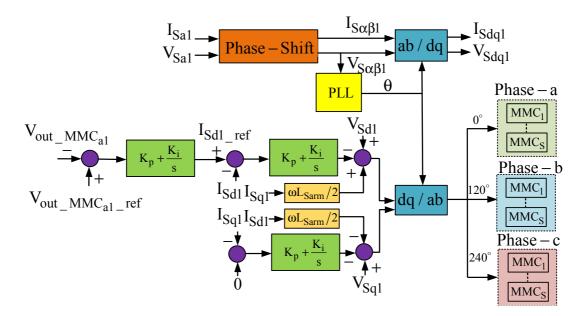

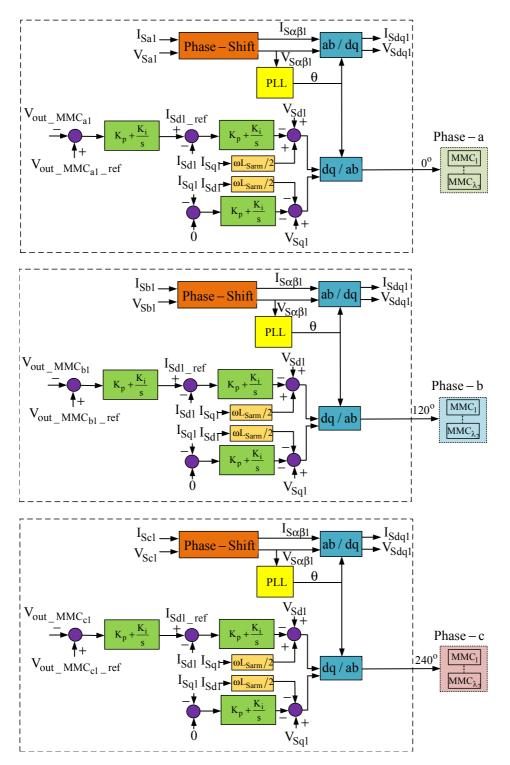

| Figure 6.7 Control system for the secondary one-leg MMC-based rectifiers87                          |

| Figure 6.8 Individual control system for the secondary decoupled phases at the secondary side.      |

| 90                                                                                                  |

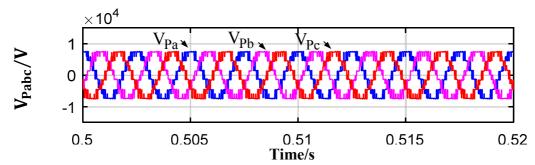

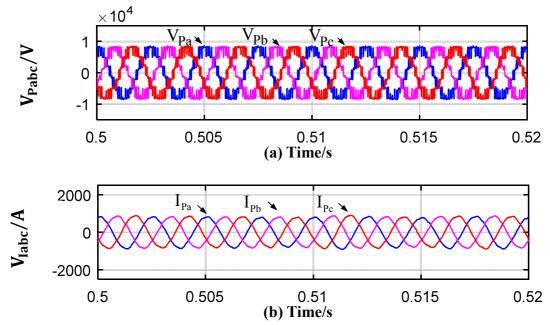

| Figure 6. 9 Transformer primary three-phase AC voltages                                             |

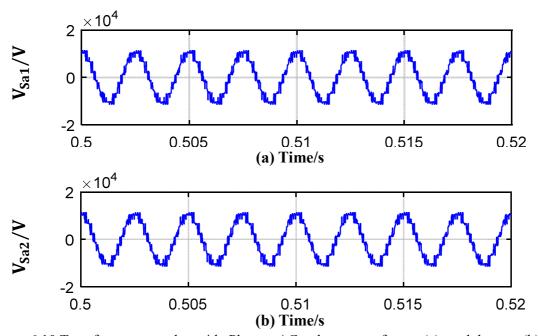

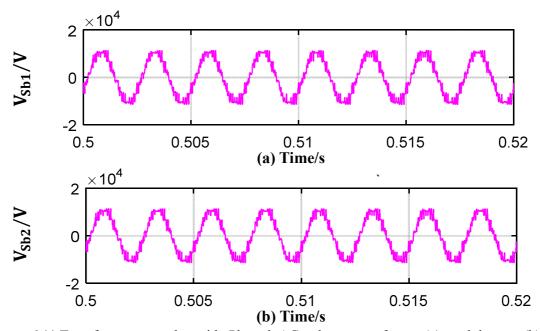

| Figure 6. 10 Transformer secondary side Phase-a AC voltage waveforms: (a) module-one; (b)           |

| module-two92                                                                                        |

| Figure 6. 11 Transformer secondary side Phase-b AC voltage waveforms: (a) module-one; (b)           |

| module-two93                                                                                        |

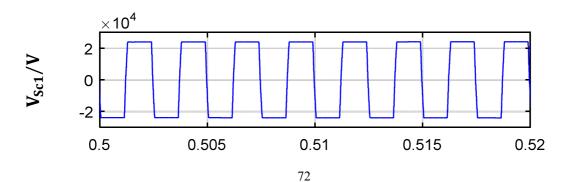

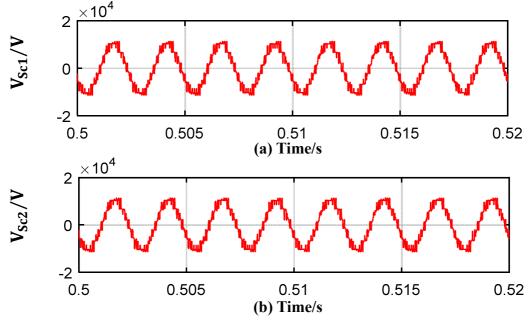

| Figure 6. 12 Transformer secondary side Phase-c AC voltage waveforms: (a) module-one; (b)           |

| module-two93                                                                                        |

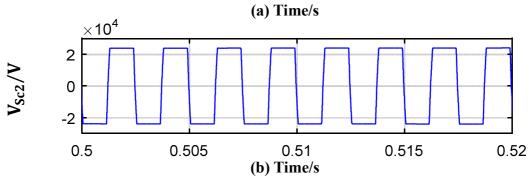

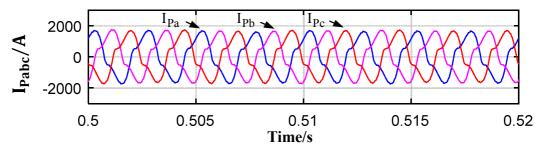

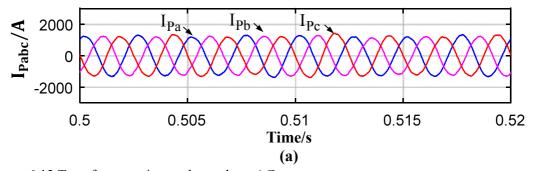

| Figure 6. 13 Transformer primary three-phase AC currents                                            |

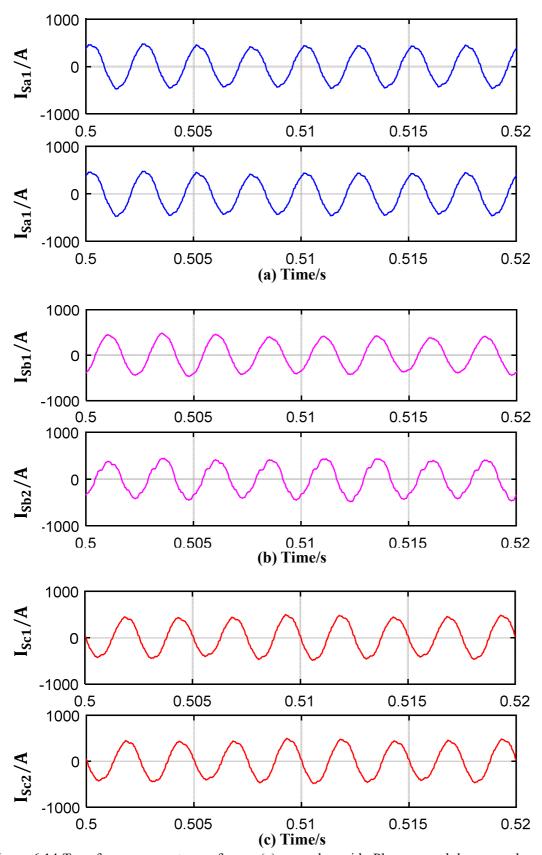

| Figure 6. 14 Transformer current waveforms: (a) secondary side Phase-a module-one and               |

| module-two AC current. (b) secondary side Phase-b module-one and module-two AC current.             |

| (c) secondary side Phase-c module-one and module-two AC current                                     |

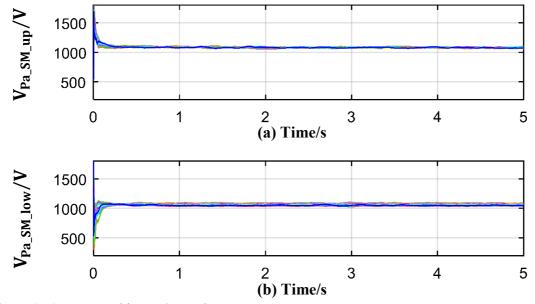

| Figure 6. 15 Primary Phase-a: (a) upper arm SM voltages; (b) lower arm SM voltages95                |

| Figure 6. 16 Secondary decoupled Phase-a one-leg MMC rectifier module-one: (a) upper arm            |

| SM voltages; (b) lower arm SM voltages96                                                            |

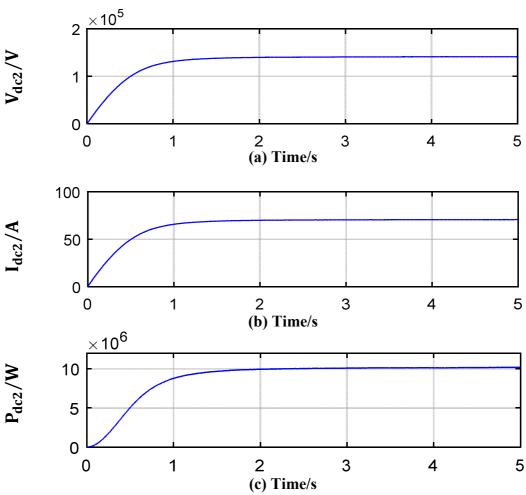

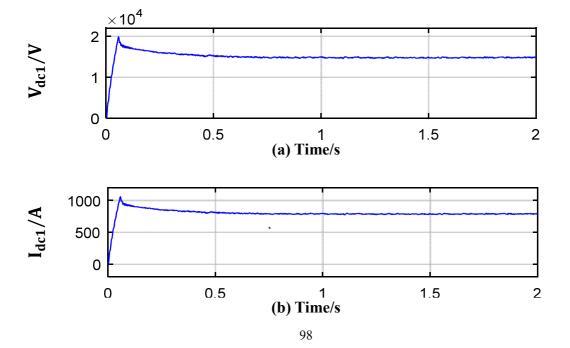

| Figure 6. 17 Output waveforms of the proposed converter under steady-state operation: (a)           |

| output DC voltage; (b) output DC current; (c) output power                                          |

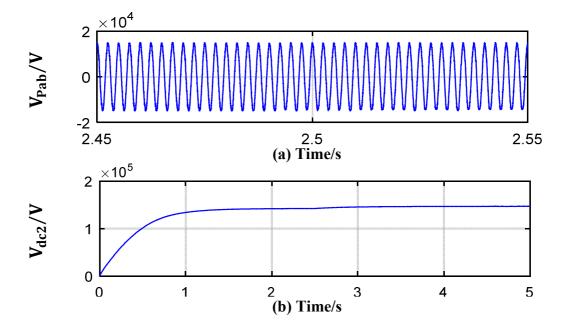

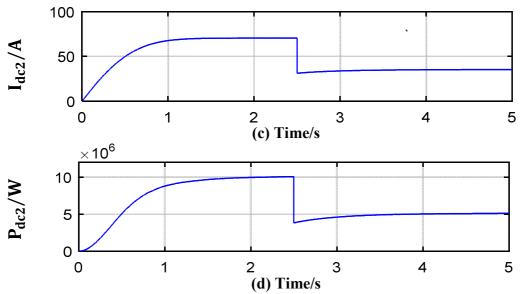

| Figure 6. 18 Output waveforms of the proposed converter under a step change at 1s: (a)              |

| transformer primary three-phase AC voltages; (b) output DC voltage; (b) output DC current; (d)      |

| output power9                                                                                 | ) / |

|-----------------------------------------------------------------------------------------------|-----|

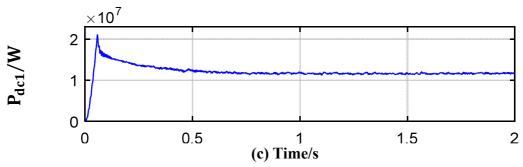

| Figure 6. 19 Transformer primary side three-phase waveforms: (a) voltage (b) current          | 8(  |

| Figure 6. 20 Output waveforms of the proposed converter under steady-state operation: (       | a)  |

| primary output DC voltage; (b) primary output DC current; (c) primary output power9           | )9  |

| Figure 6. 21 The output waveforms of the proposed converter under a step change at 1s: (      | a)  |

| primary output DC voltage; (b) primary output DC current; (c) primary output power9           | 9   |

| Figure 7. 1 Three-phase MMC: (a) Current distribution in the arms of the three-phase MMC      | Ξ;  |

| (b) current directions in the half-bridge SM                                                  | )2  |

| Figure 7.2 Frequency dependency of core losses [128]                                          | )7  |

| Figure 7.3 Proposed unidirectional single-phase DC/DC converter                               | 0   |

| Figure 7.4 Configuration of (a) the proposed unidirectional three-phase DC/DC converter; (    | b)  |

| half-bridge based submodule at the primary side of the proposed converter11                   | 1   |

| Figure 7.5 Unidirectional cascaded DC/DC converters: (a) input series output series (ISOS); ( | b)  |

| input parallel output series (IPOS)                                                           | 1   |

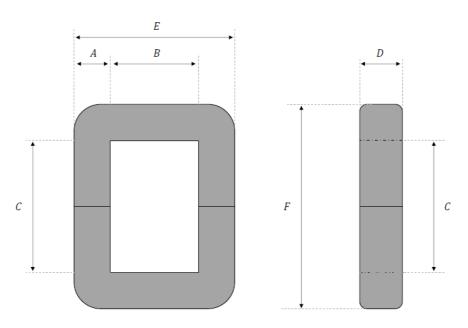

| Figure 7.6 C-core structure dimensions                                                        | 13  |

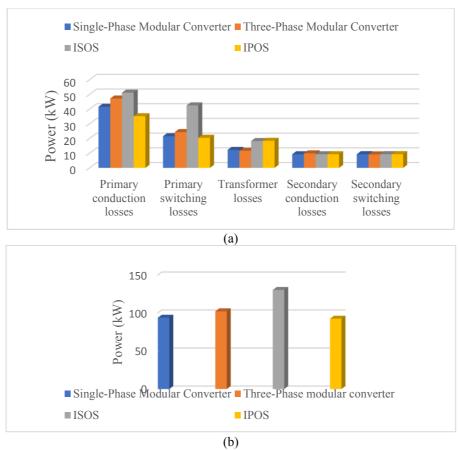

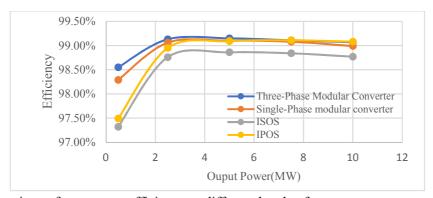

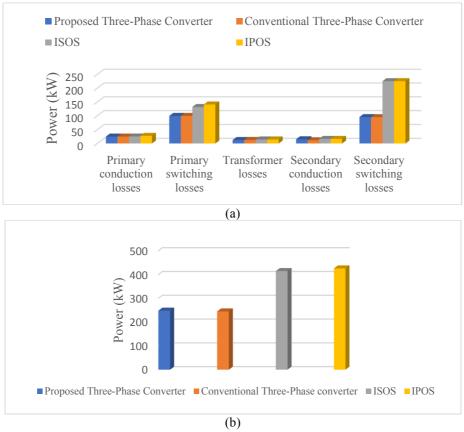

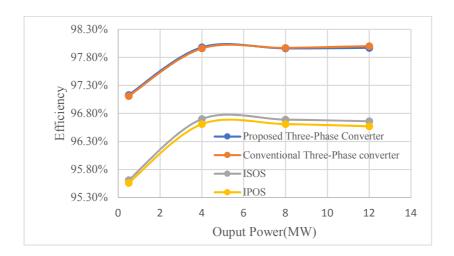

| Figure 7.7 Distribution of the power losses of the proposed unidirectional single and thre    | e-  |

| phase converters and ISOS and IPOS converters for operation at a rated power of 10MW (        | a)  |

| breakdown of losses; (b) total losses                                                         | 6   |

| Figure 7.8 Efficiency comparison at different levels of output power.                         | 6   |

| Figure 7.9 Configuration of (a) proposed DC/DC converter; (b) one-leg MMC based submodu       | le  |

| at the secondary side of the proposed converter.                                              | 17  |

| Figure 7.10 Two three-phase MMC-based DC/DC converter.                                        | 17  |

| Figure 7.11 Bidirectional cascaded DC/DC converters: (a) input series output series (ISOS); ( | b)  |

| input parallel output series (IPOS)                                                           | 8   |

| Figure 7.12 Distribution of power losses in the proposed and conventional bidirectional thre  | e-  |

| phase converters, and bidirectional cascaded ISOS and IPOS converters at 12MW output pow      | er  |

| (a) breakdown of losses; (b) total losses.                                                    | 21  |

| Figure 7.13 Efficiency comparison at different output power levels                            | 21  |

| Figure 8.1 Schematic diagram of the control platform13                                        | 34  |

| Figure 8.2 TMS320F28335 DSP controller board                                                  | 35  |

| Figure 8.3 Interface board: (a) schematic diagram (b) photograph                              | 35  |

| Figure 8.4 Drive circuit board                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------|

| Figure 8.5 Unidirectional single-phase modular multilevel DC/DC converter with single transformer: (a)                       |

| scaled down laboratory prototype; and (b) schematic diagram                                                                  |

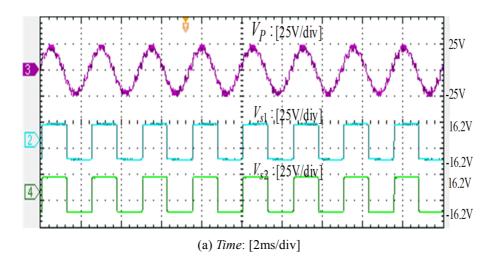

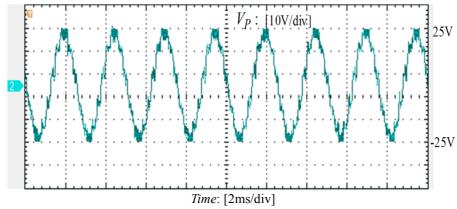

| Figure 8.6 Performance at steady state: (a) transformer primary terminal voltage VP and secondary                            |

| winding-one voltage $Vs1$ and winding-two voltage $Vs2$ ; (b) transformer primary current $IP$ and                           |

| secondary winding-one current Is1 and winding-two current Is2; (c) output DC current Idc_out and                             |

| voltage Vdc_out                                                                                                              |

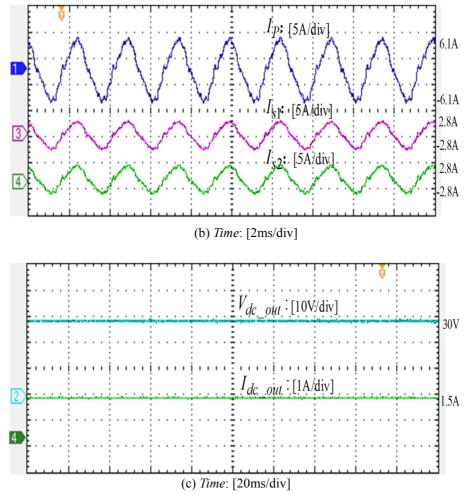

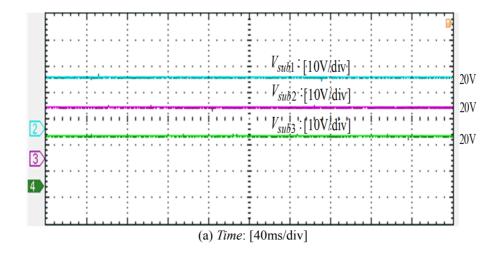

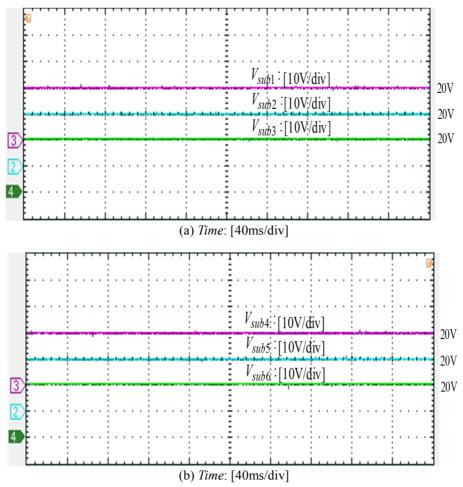

| Figure 8.7 Performance at steady state, (a) upper arm SM voltages <i>Vsub</i> 1, <i>Vsub</i> 2 and <i>Vsub</i> 3; (b) lower  |

| arm SM voltages <i>Vsub</i> 4, <i>Vsub</i> 5 and <i>Vsub</i> 6                                                               |

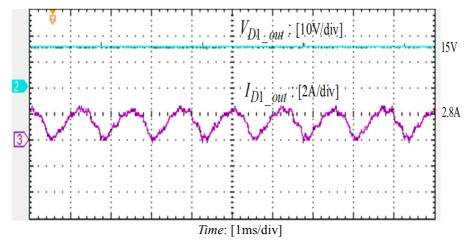

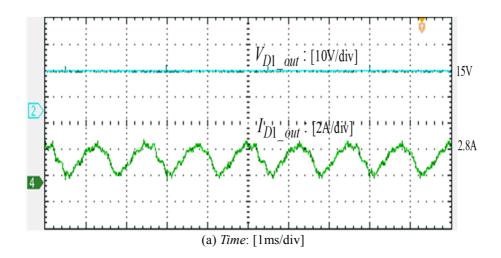

| Figure 8.8 Performance at steady state: output voltage and current waveforms: secondary diode-bridge-                        |

| rectifier module-one. 142                                                                                                    |

| Figure 8.9 Performance at steady state: output voltage and current waveforms: secondary diode-bridge-                        |

| rectifier module-two                                                                                                         |

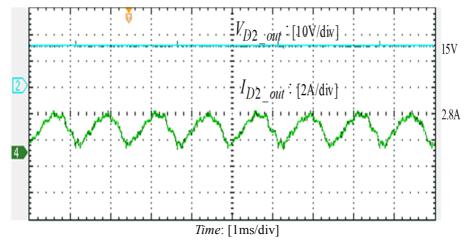

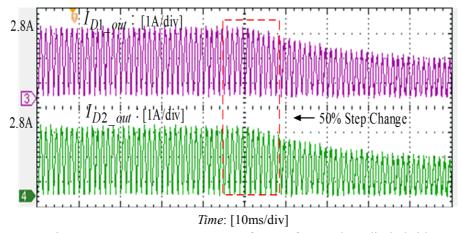

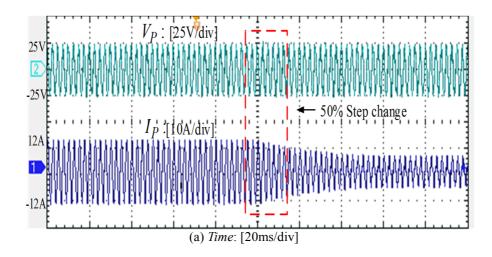

| Figure 8.10 Dynamic response: (a) output current waveforms of secondary diode-bridge-rectifiers module-                      |

| one ID1_out, and module-two ID2_out; (b) transformer primary terminal voltage VP and current IP.                             |

|                                                                                                                              |

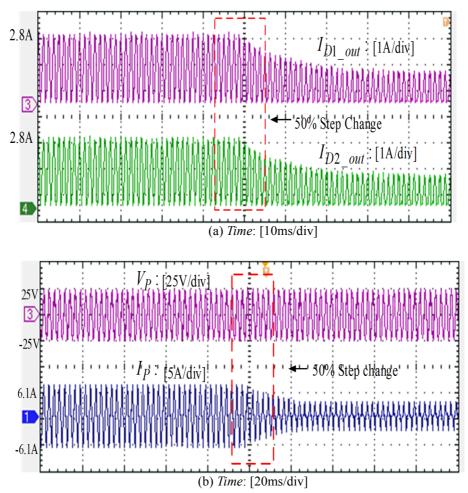

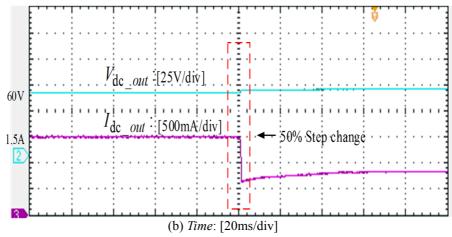

| Figure 8.11 Dynamic response: output DC voltage <i>Vdc_out</i> and current <i>Idc_out</i>                                    |

| Figure 8.12 Unidirectional single-phase modular multilevel DC/DC converter with two transformers: (a)                        |

| scaled down laboratory prototype; and (b) schematic diagram                                                                  |

| Figure 8.13 Performance at steady state: primary terminal voltage <i>VP</i>                                                  |

| Figure 8.14 Performance at steady state: (a) transformer-one secondary winding-one voltage Vs1 and                           |

| winding-two voltage $Vs2$ . (b) transformer-two secondary winding-one voltage $Vs3$ and winding-two                          |

| voltage <i>Vs</i> 4                                                                                                          |

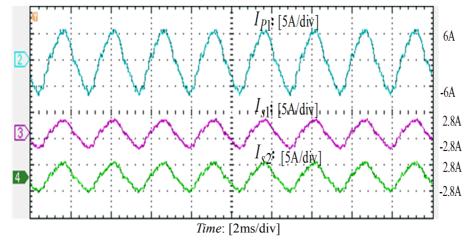

| Figure 8.15 Performance at steady state: transformer-one primary current <i>IP</i> 1and secondary winding-one                |

| current Is1 and winding-two current Is2                                                                                      |

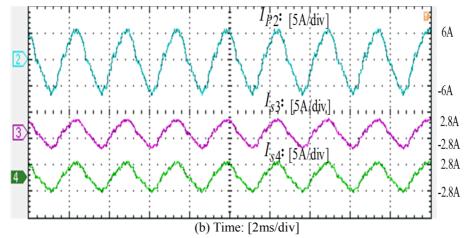

| Figure 8.16 Performance at steady state: transformer-two primary current <i>IP</i> 2 and secondary winding-three             |

| current Is3 and winding-four current Is4.                                                                                    |

| Figure 8.17 Performance at steady state: proposed converter output DC current <i>Idc_out</i> and voltage                     |

| <i>Vdc_out</i>                                                                                                               |

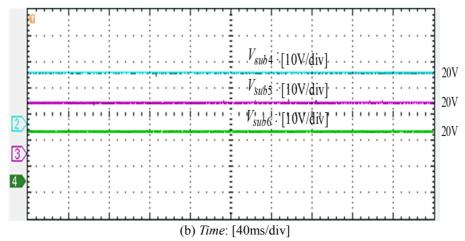

| Figure 8.18 Performance at steady state: (a) upper arm SM voltages <i>Vsub</i> 1, <i>Vsub</i> 2 and <i>Vsub</i> 3; (b) lower |

| arm SM voltages Vsub4, Vsub5 and Vsub6                                                                       |

|--------------------------------------------------------------------------------------------------------------|

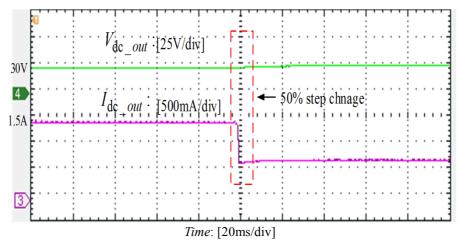

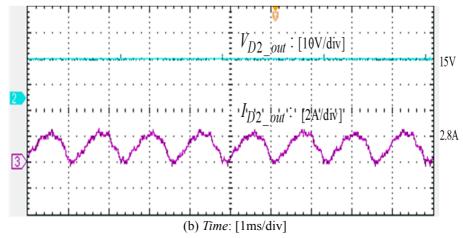

| Figure 8.19 Performance at steady state: output voltage and current waveforms of (a) secondary diode-bridge- |

| rectifier module-one; (b) secondary diode-bridge-rectifier module-two.                                       |

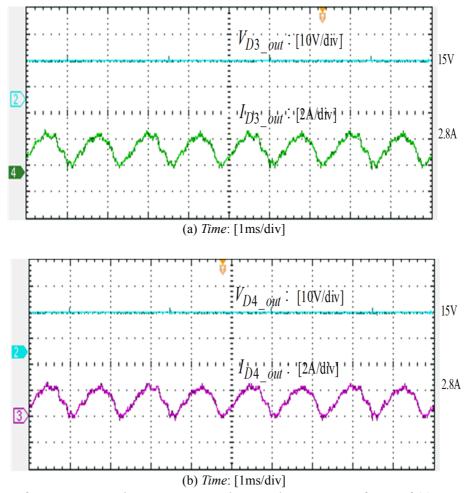

| Figure 8.20 Performance at steady state: output voltage and current waveforms of (a) secondary diode-bridge- |

| rectifier module-three; (b) secondary diode-bridge-rectifier module-four149                                  |

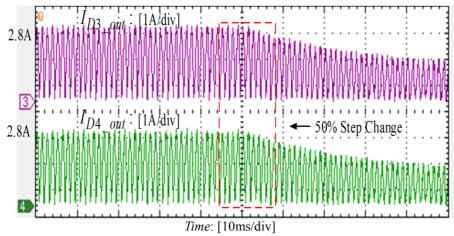

| Figure 8.21 Dynamic response: output current waveforms of secondary diode-bridge-rectifier module-one        |

| ID1_out, and module-two ID2_out150                                                                           |

| Figure 8.22 Dynamic response: output current waveforms of secondary diode-bridge-rectifier module-one        |

| ID3_out, and module-two ID4_out150                                                                           |

| Figure 8.23 Dynamic response: (a) transformer primary terminal voltage VP and current IP; (b) output DC      |

| voltage Vdc_out and current Idc_out151                                                                       |

# **List of Symbols**

$B_{pk}$ : Maximum allowable core flux density

$f_{AC}$ : Fundamental AC frequency

$f_c$  : Carrier frequency

$I_{cir}$ : Circulating current

$I_{Px}$  : AC output current

$I_{xU}$ : Upper arm current

$I_{xL}$ : Lower arm current

$I_{dc1}$ : Input DC current

$I_{dc2}$ : Output DC current

$I_{P\alpha\beta}$ : Orthogonal pair of the primary AC current

$I_{Pda}$ : D-axis and q-axis components of the primary AC current

*J* : Current density

$k_p$ : Proportional constant

$k_i$ : Integral constant

*k* : Unbalanced factor

$K_{v}$ : Voltage waveform factor

$K_u$ : Window utilization ratio

$L_{Parm}$ : Primary arm inductance

$L_{Sarm}$ : Secondary arm inductance

$L_o$ : Output inductance

$P_{copper}$  : Copper losses

$P_{dc2}$ : Output power

$P_{core}$ : Core losses

$P_d$ : Dielectric losses

$P_T$ : Transformer losses

$P_{IGBT x}$ : IGBT losses

$R_c$ : Carrier-reference frequency ratio

$T_1$ : Upper Switch

$T_2$ : Lower Switch

$V_c$ : Submodule capacitor voltage

$V_{SM}$ : Submodule output voltage

$V_{dc1}$ : Input DC voltage

$V_{dc2}$ : Output DC voltage

$V_{Px}$ : Primary output AC voltage

$V_{xU}$ : Upper arm voltage

$V_{xL}$ : Lower arm voltage

V<sub>s</sub> : Secondary equivalent voltage

$V_{P\alpha\beta}$ : Orthogonal pair of the primary AC voltage

$V_{Pdq}$ : D-axis and q-axis components of the primary AC voltage

$V_{core}$ : Core volume

$\lambda_1$  : Submodule number of primary MMC per arm

$\lambda_2$ : Module number of secondary diode bridge rectifiers

$\lambda_3$ : Module number of secondary one-leg MMC modules

η : Efficiency

#### List of Abbreviations

AC : Alternating current

CPS : Carrier phase shift

DC : Direct current

DSP : Digital signal processor

DAB : Dual active bridge

GTO : Gate turn-off thyristor

HVDC : High voltage direct current

HVAC : High voltage alternating current

IGBT : Insulated gate bipolar transistor

IPOS : Input parallel output series

ISOS : Input series output series

IPOP : Input parallel output parallel

ISOP : Input series output parallel

ISIPOS : Input series input parallel output series

KVL : Kirchhoff voltage laws

MMC : Modular multilevel converter

MFT : Medium frequency transformer

PD : Phase deposition

SPWM : Sinusoidal pulse width modulation

SM : Submodule

SAB : Single active bridge

VSC : Voltage source converter

## **Chapter 1. Introduction**

#### 1.1 Historical Development of HVDC Systems

In 1882, the French physicist Marcel Deprez used a DC generator installed in the Miesbach coal mine to send electricity at 2kV to an international exhibition in Munich via 57 km of telegraph line, completing the first ever test [1]. With the development of the modern economy, the demand for electricity in society has been rapidly increasing. However, due to the lower voltage in early versions of transmission systems, a huge power loss resulted. This problem becomes worse over longer distances, thus hindering the development of DC transmission systems.

In the 1880s and 1890s, the principle of multi-phase AC circuits was gradually mastered, and transformers and induction motors were created which greatly enhanced voltage levels, transmission capacity and power system reliability. As a result, AC has almost completely replaced DC and has developed into today's massive power systems. However, DC transmission still has advantages, such as delivering large-scale energy over long distances with less power loss, and no capacitive AC current for long-distance transmission [2]. Therefore, many countries, including the United States, Sweden, and Germany, continued to investigate HVDC technology and developed pilot projects. However, after the successful development of the controllable mercury arc rectifier in 1928, HVDC transmission systems began to develop rapidly [3].

Since the 1950s, the demand for electricity has been growing considerably, and the scale of power systems has further expanded. Meanwhile, the the AC system has encountered a series of insurmountable technical difficulties. On the other hand, successful research into high-power converters has overcome the technical obstacles to HVDC transmission. All of these factors have contributed to the development of current HVDC systems.

In 1970, the American company GE developed the first thyristor. This overcame the

shortcomings of the mercury arc valve, such as high reverse-arc failure rates, low reliability and the inconvenience of operation and maintenance [4]. The operational performance and reliability of HVDC transmission can be improved, and this promotes the development of HVDC transmission technology.

In recent years, developers of HVDC technology have accomplished a historical breakthrough based on voltage source converter (VSC) technology and fully-controlled power electronic power devices, such as the gate turn-off thyristor (GTO) and insulation gate bipolar transistors (IGBTs) [5-7]. This technology introduces fully-controlled power electronics into the field of DC transmission systems and significantly improve the controllability and flexibility of DC transmission technology.

#### 1.2 Comparison of HVDC and HVAC Transmission Systems

Two kinds of transmission system coexist in modern transmission engineering: high voltage AC (HVAC) transmission and high voltage DC (HVDC) transmission [8]. Both of these two transmission methods have advantages and disadvantages. The following comparison of HVDC and HVAC transmission systems illustrates their respective value in applications.

The advantages of HVAC transmission are mainly manifested in the areas of power generation and distribution. According to the principle of electromagnetic induction, the alternator can economically and easily convert other forms of mechanical energy and chemical energy into electricity [9]. The cost of AC sources and substations is lower than for a DC power supply and DC converter stations with the same power. Meanwhile, AC can be easily boosted and stepped down using transformers, which is very convenient when delivering power.

The advantages of HVDC transmission are mainly manifested in the processes of power transmission, as described below:

1) Compared with three-wire three-phase HVAC transmission, only two wires are required for DC transmission. Therefore, based on the same cross-sectional area of the transmission line and current density when transferring the same power, a one-third saving in DC transmission lines and insulation materials can be achieved even without considering skin effects [10-12]. If

skin effects and other types of losses, such as dielectric loss in insulating material and eddy current loss from magnetic induction, are taken into consideration, the cross-sectional area of AC transmission lines will be 1.33 times bigger when compared with DC transmission lines transmitting the same level of power [10-12]. Therefore, the amount of wire used in DC transmission is almost half that in AC transmission. Meanwhile, the structure of the DC transmission tower is simpler than for three-phase AC transmission, and the area occupied by the line corridor is also smaller [10-12].

2) In some special cases, underground and submarine cables are necessary when high-voltage transmission lines pass cities and narrow seaways respectively. Due to the presence of coaxial capacitors between the cable core and the earth, no-load capacitor current is significant in HVAC transmission lines [13]. For instance, a 200kV cable has a capacitance of about 0.2μF per kilometre, requiring about 3×103kVar of reactive power [13]. Whereas in DC transmission, there is essentially no capacitive current applied to the cable due to the small voltage fluctuations. It is worth noting that the consumption of this reactive power of the transmission lines per kilometre can be calculated by the following equation:

$$Q_{c\_loss} = 2 \cdot \pi \cdot f_{AC} \cdot C_{equivalent} \cdot V_{line}^{2}$$

(1.1)

Where  $f_{AC}$  is the fundamental frequency of the transmission system ( $f_{AC} = 50$ Hz);  $V_{line}$  and  $C_{equivalent}$  are the voltage and equivalent capacitance of the transmission lines.

3) When using AC for long-distance transmission, a significant phase shift in the voltage will occur at both ends of the power transmission system [10], which requires complex compensation. Otherwise, a large circulating current may form in the power transmission system which would damage equipment or cause outage accidents.

#### 1.3 Offshore Wind Farm System

Due to topographic factors, wind speeds at different altitudes on land vary greatly, which leads to large changes in wind speed in the vertical direction. As a result, imbalances in the forces acting on the top and bottom of the wind turbines cause the transmission system to be

easily damaged [14-17]. However, there is no such problem at sea, where the surface is very flat with almost no resistance, and the average wind speed is high with less variation compared to that on land. Moreover, changes in wind direction at sea are also smaller than on land, and so the wind energy at sea is more stable. It is well known that the power generated by a wind turbine is proportional to the cube of the wind speed, and the wind speed at sea is about 20% higher than that on land [14-17]. Therefore, the annual generating capacity of an offshore wind turbine can be 70% higher than that on land.

A larger power generation capacity means larger wind turbine blades, which leads to restrictions on their transport on land. However, this would be much easier at sea. Furthermore, onshore wind farms possess other restrictions such as the availability of land resources and other environmental and operational constraints. Moreover, most major developed cities in the world are situated on the coast, which means that offshore wind energy is the most attractive source of energy. Therefore, it can be concluded that offshore wind power will have broader prospects in future global energy supply systems.

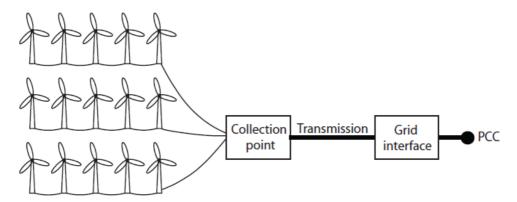

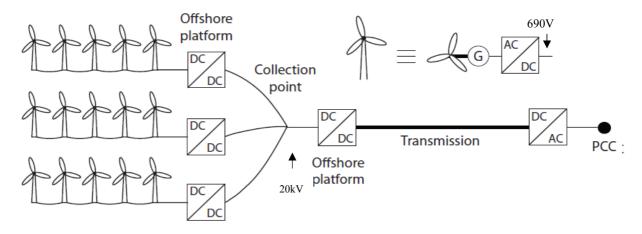

Figure 1.1 A basic offshore transmission system [2].

Offshore wind power systems usually consist of offshore wind farms, power transmission cables, and distribution lines, as shown in figure 1.1 [2] [18] [19]. Many wind turbines are grouped and connected to a local AC or DC grid to form an offshore wind farm. This local grid is then connected to the power transmission cable via a converter or transformer, and eventually, the energy is transmitted to the onshore power distribution system.

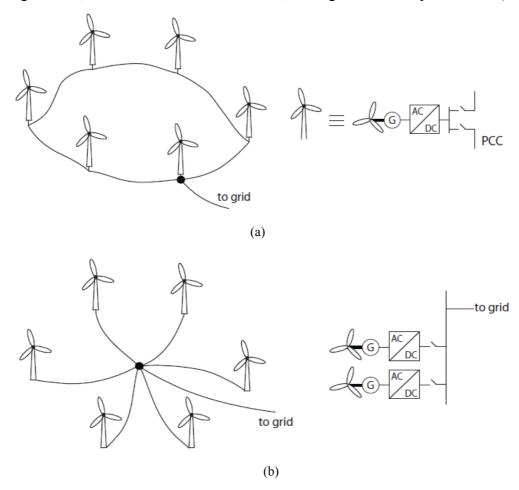

In a wind farm, there are generally two types of wind turbine connection, which are star and

loop connections as shown in figure 1.2. The different layouts of offshore wind farm transmission systems are also shown below [2]. (It is worth noting that the layouts of offshore shown in figures 1.3, 1.4 and 1.5 are star connection, and figure 1.6 is loop connection).

Figure 1.2 Wind turbine connection mode: (a) loop connection (b) star connection[2].

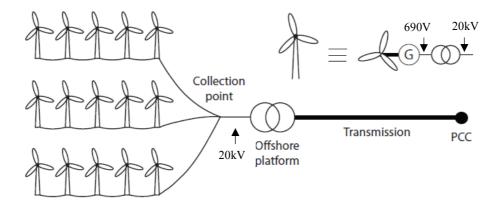

#### 1) AC collection for wind farms:

Figure 1.3 shows a typical schematic diagram of the AC collection of a wind farm, where the output voltage of each wind turbine is generally about 690V [2] [18]. However, for a wind power system with AC collection mode, the voltage level of the AC connection network for the wind turbines is between 20kV and 35kV [18], which requires the output terminal of each wind turbine to be connected to a medium voltage transformer in order to raise the voltage level and render it suitable for connection to the AC network. Then another high voltage transformer is employed on the offshore platform, as shown in figure 1.3, and this boosts the voltage to facilitate the employment of HVAC transmission lines.

<u>Chapter 1</u> <u>Introduction</u>

Figure 1.3 General offshore HVAC transmission system with AC collection network [2].

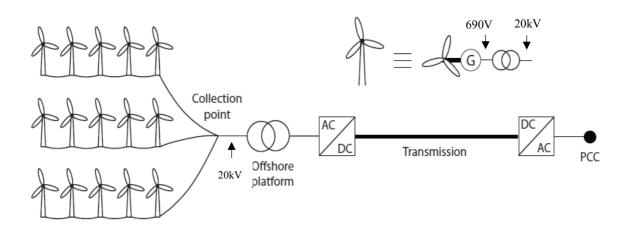

#### 2) Mixed AC/DC collection for wind farm:

Similarly to the AC collection arrangement described above, power is here collected using an AC medium voltage network. Transformers are again employed to raise the voltage produced by the wind turbines, and then another high voltage transformer is employed between the AC collection point and the rectifier side of the HVDC transmission lines, as illustrated in figure 1.4 [2] [18].

Figure 1.4 General offshore windfarm HVDC transmission system with mixed AC/DC collection network [2].

#### 3) DC collection: parallel-connected wind turbines

Unlike the previous collection scenario, each wind turbine, in this case, is equipped with an AC/DC rectifier with an output voltage of about 690V. However, the typical voltage of the DC

collection network for an offshore system is between 20kV to 40kV, and therefore a medium voltage DC/DC converter is required to raise the voltage [2] [18]. The output of the medium voltage DC/DC converters will then serve as input to the high voltage DC/DC converter that facilitates the connection with the HVDC transmission lines.

Figure 1.5 General offshore HVDC transmission system with a DC collection (parallel-connected wind turbines) network [2].

#### 4) DC collection: series-connected wind turbines

In this case, all wind turbines in the same cluster are connected in series as shown in figure 1.6. This enables the achievement of high voltage without additional DC/DC boost converters. However, if one wind turbine is out of service, then the other wind turbines need to compensate for the voltage loss, which results in increased voltage stress and energy loss [2] [18].

Figure 1.6 General offshore HVDC transmission system with DC collection (series-connected wind turbines) network [2].

#### 1.4 Real Examples of Offshore HVDC Systems

At present, many offshore HVDC systems have been built by large companies such as Siemens, ABB, C-EPRI, and Alstom. Table 1.1 shows the detailed parameters of some typical offshore HVDC projects.

| Wind Park | Power | Voltage | Cable      | Manufacturer | Commissioning    |

|-----------|-------|---------|------------|--------------|------------------|

|           | (MW)  | (kV)    | Length(km) |              |                  |

| BorWin1   | 400   | ±150    | 200        | ABB          | 2009             |

| DolWin1   | 800   | ±320    | 165        | ABB          | 2015             |

| DolWin2   | 900   | ±320    | 135        | ABB          | 2017             |

| HelWin1   | 576   | ±250    | 130        | Siemens      | 2015             |

| HelWin2   | 690   | ±320    | 130        | Siemens      | 2015             |

| SylWin1   | 864   | ±320    | 210        | Siemens      | 2015             |

| BorWin2   | 800   | ±300    | 200        | Siemens      | 2015             |

| BorWin3   | 900   | ±320    | 160        | Siemens      | Expected in 2019 |

| DolWin6   | 900   | ±320    | 90         | Siemens      | Expected in 2023 |

| DolWin3   | 800   | ±320    | 160        | Alstom       | 2017             |

| DolWin5   | 900   | _       | 115        | Tennet       | (To be built by  |

|           |       |         |            |              | 2025)            |

| BorWin5   | 900   | _       | 125        | Tennet       | (To be built by  |

| 1         |       |         |            |              | 2025)            |

Table 1.1 Detailed parameters of some typical offshore HVDC projects [19].

#### *Projects developed by ABB* [19]:

- 1) **BorWin1 offshore HVDC project (2009):** BorWin1 was the first offshore HVDC project in Germany. This project is used to connect Park BARD Offshore1 and other wind farms near Borkum to the European power grid, where the cable length is 200km, and the rated voltage and power are  $\pm 150$ kV and 400MW respectively.

- 2) **DolWin1 offshore HVDC project (2015)**: This HVDC project was designed to provide the grid connection of offshore wind farms off the coast of Germany and to transmit power to the German power grid, where the cable length is 165km, and the rated voltage and power are ±320kV and 800MW respectively.

- 3) **DolWin2 offshore HVDC project (2017)**: This project has a similar function to the above DolWin1 project and is also employed to transmit offshore wind power to the German power

grid, where the cable length is 135km, and the rated voltage and power are ±320kV and 900MW respectively.

Projects developed by Siemens [19]:

- 1) **HelWin1 offshore HVDC project (2015)**: HelWin1 is part of the German Energy Transition program. It was built to connect two offshore wind farms, Nordsee and Meerwind, to the German power grid, where the cable length is 130km, and the rated voltage and power are ±250kV and 576MW respectively.

- 2) **HelWin2 offshore HVDC project (2015)**: This project was built to transmit the offshore wind energy to the German power grid, where the cable length is 130km, and the rated voltage and power are ±320kV and 690MW respectively.

- 3) **SylWin1 offshore HVDC project** (2015): This project was used to connect the offshore wind farm Dan Tysk to the power grid of Germany. The cable length is 210km, and the rated voltage and power are ±320kV and 864MW respectively.

- 4) **BorWin2 offshore HVDC project (2015):** This project is used to connect two offshore wind farms, Veja Mate and Global Tech 1, to Germany power grid, where the cable length is 200km, and the rated voltage and power are ±300kV and 800MW respectively.

- 5) **BorWin3 offshore HVDC project (2015):** This project is the most recent offshore HVDC project in Germany. It is expected to be finished in 2019. The cable length of this project is 200 km, and the rated voltage and power are  $\pm 300 \text{kV}$  and 800 MW respectively.

The project developed by Dong Alstom: [19]

1) **DolWin3 offshore HVDC project (2017)**: This project is used to transport offshore wind power to the German power grid, where the cable length is 160km, and the rated voltage and power are ±320kV and 800MW respectively.

## 1.5 Objectives of the Thesis

The main objectives of the thesis are:

To conduct a comprehensive literature review that can contribute to the development of modular multi-level DC/DC converters.

- To propose novel step-up modular multi-level DC/DC converters which are highly modular and where the voltage stress of the submodules is considerably reduced compared to the conventional DC/DC converters.

- To develop detailed analytical models for each proposed converter to identify and understand the various parameters that define their operating characteristics.

- To conduct a comparison with conventional DC/DC converters that demonstrates the superiority of the proposed converters.

- To develop a low-voltage scaled-down laboratory prototype to validate the feasibility of the proposed converter experimentally.

#### 1.6 Thesis Contributions and Publications

The main original contributions of this research work are as follows:

- A novel unidirectional single-phase modular DC/DC converter is developed (Chapter 4).

- A control method based on a rotating reference frame is developed for the proposed unidirectional single-phase modular DC/DC converter (Chapter 4).

- A novel unidirectional three-phase modular DC/DC converter is proposed (Chapter 5).

- A control strategy based on the d-q rotating reference frame for the proposed unidirectional three-phase modular DC/DC converter is developed (Chapter 5).

- A novel bidirectional three-phase modular DC/DC converter is developed (Chapter 6).

• Two different d-q vector control strategies are developed for the primary and secondary sides of the proposed bidirectional three-phase modular DC/DC converter (Chapter 6).

• A comparison of the proposed DC/DC converters and their existing counterparts is conducted to demonstrate the superiority of the proposed converters (Chapter 7).

Reports of most of the above outcomes have been published in the following papers:

#### Journals:

- [1] **He Liu**, Mohamed Dahidah, James Yu, R.T. Naayagi, and Matthew Armstrong "Design and control unidirectional DC/DC modular multilevel converter for offshore DC collection point: theoretical analysis and experimental validation," *IEEE Transactions on Power Electronics*, August 2018. (Accepted).

- [2] **He Liu**, Mohamed Dahidah, James Yu, R.T. Naayagi, and Matthew Armstrong "Unidirectional DC/DC modular multilevel converter for offshore wind farm with the control strategy based on stationary frame," *IET Journal of engineering*, July 2018. (Accepted)

#### **Conferences:**

- [3] **He Liu**, Mohamed Dahidah, Matthew Armstrong, and R.T. Naayagi "High voltage high power DC/DC modular multilevel converter for offshore windfarm DC collection point," in *Proceedings of the Power Electronics Machines and Drives 8<sup>th</sup> IET International Conference*, April 2016, pp.1-6.

- [4] **He Liu**, Mohamed Dahidah, James Yu, R.T. Naayagi, and Matthew Armstrong "A novel modular multilevel step-up DC/DC converter for offshore systems," in *Proceeding of the Industrial Electronics 2017 IEEE 26<sup>th</sup> International Symposium*, June 2017, pp.576-581.

- [5] **He Liu**, Mohamed Dahidah, James Yu, R.T. Naayagi, and Matthew Armstrong "Unidirectional DC/DC modular multilevel converter for offshore wind farm with the control strategy based on stationary frame," in *Proceedings of the Power Electronics Machines and Drives 9<sup>th</sup> IET International Conference*, June 2018.

- [6] Mohamed Dahidah, **He Liu**, and Vassilios Agelidis "Reconfigurable converter with multiple-voltage multiple-power for E-mobility charging," in *Proceeding of the Power Electronics International Conference*, May 2018.

#### 1.7 Dissertation Outline

The rest of the thesis is organised as follows:

Chapter 2 provides a literature review of conventional high-voltage high-power DC/DC converters which can be employed to build medium-voltage DC (MVDC) collection networks to eliminate extra conversion stages and improve system reliability.

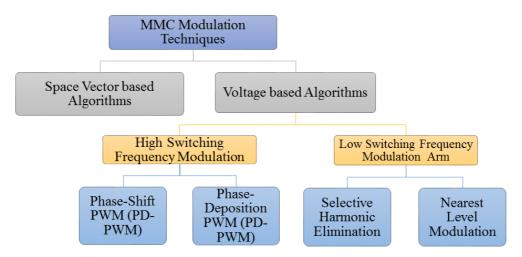

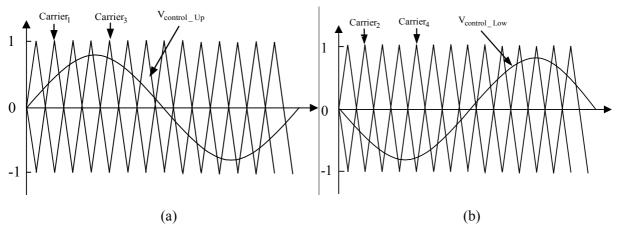

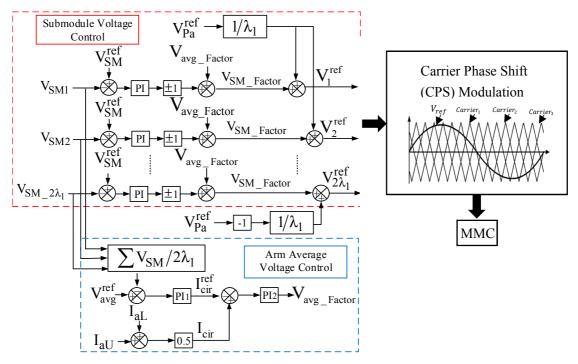

Chapter 3 introduces the basic theoretical analysis of MMCs in terms of the configuration, operational principles, switching modulation methods, submodule voltage control strategies, and arm power fluctuation characteristics. Moreover, a simplified mathematical model of the MMC is also derived in this chapter, which establishes the theoretical basis for the proposed control strategy and modular DC/DC converters developed later.

Chapter 4 proposes a unidirectional single-phase modular DC/DC converter. Detailed theoretical design analysis is presented, and parameters that affect the operation of the proposed converter are defined and thoroughly discussed. This includes configuration, mathematical modelling, and power transfer capability. A control method for the proposed converter based on a rotating reference frame is also developed in this chapter. The performance of the proposed converter is validated through simulation.

Chapter 5 proposes a unidirectional three-phase modular DC/DC converter. As in Chapter 4, the proposed converter in this chapter is also analysed in detail in terms of configuration, mathematical modelling, and power transfer capability. A control strategy based on the d-q rotating reference frame for the proposed converter is derived. Simulation studies under different operating conditions are discussed.

Chapter 6 presents a bidirectional three-phase modular DC/DC converter. The detailed theoretical design process of the proposed converter is also presented. Two different kinds of d-q vector control strategy are developed for the primary and secondary side of the proposed converter. The proposed converter and its control strategy are validated through various simulations.

Chapter 7 analyses and calculates in detail the different losses in the proposed converter and compares them with losses in corresponding competitive topologies. Also, the structure of the

circuit topologies and the overall efficiency and component utilization are compared as well.

Chapter 8 introduces a low-voltage scaled-down laboratory prototype. It details the theoretical design process of the submodule capacitor, arm inductor, and output filter. A case study of a medium frequency transformer is also presented in this chapter. Moreover, the development of a control platform is also briefly introduced. Experimentally validated results are then discussed and analyzed.

Chapter 9 concludes this thesis. Further work is also recommended.

# Chapter 2. Conventional High-Voltage High-Power DC/DC Converters

#### 2.1 Introduction

The HVDC transmission system is an effective way to deliver large-scale energy over a long distance with lower power losses [20-22]. Large-scale offshore wind energy systems are increasingly common, and the connection between multiple farms is becoming more challenging. Medium-voltage DC collection networks are a promising technology for such integration, aiming to eliminate extra conversion stages and improve system reliability [36-39]. High-voltage high-power DC/DC converters, and especially modular multilevel DC/DC converters have gradually become key enablers for the DC grid. In this chapter, various high-voltage high-power DC/DC converters are investigated and reviewed. These can be broadly classified as cascaded, consisting of multiple converter modules [23-25], and modular multilevel topologies [26-27].

#### 2.2 Cascaded Modular DC/DC Converters

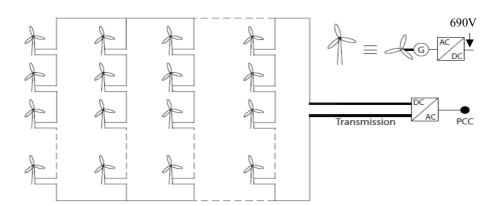

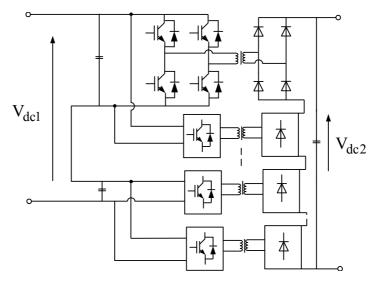

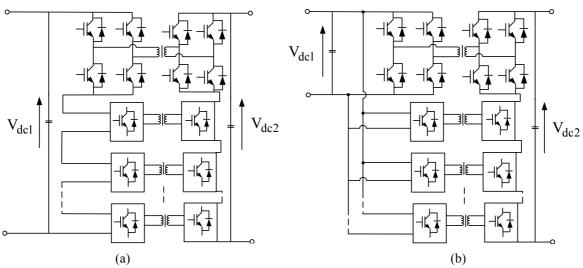

Most notably, dual active bridge (DAB) or single active bridge (SAB) converters have received a great deal of attention from researchers due to their distinctive features, such as galvanic isolation and the ability to operate at the high switching frequency. However, the high-voltage and high-power requirements of DC/DC converter-based HVDC systems necessitate series and parallel combinations at both the power semiconductor devices and converter module levels [28]. Such systems are commonly referred to as cascaded modular DC/DC converters. According to the different connection modes, cascaded modular DC/DC converters can be divided into four basic types as shown in figure 2.1: 1) input-parallel output-series (IPOS) [29-40]; 2) input-parallel output-parallel (IPOP) [41-48]; 3) input-series output-parallel (ISOP) [49-65]; 4) input-series output-series (ISOS) [66-74]. Furthermore, the inputs

Figure 2.1 Schematic diagrams of unidirectional cascaded DC/DC converters: (a) input-parallel output-series (IPOS); (b) input-parallel output-parallel (IPOP); (c) input-series output-parallel (ISOP); (d) input-series output-series (ISOS).

Figure 2.2 Schematic diagram of unidirectional cascaded input-series-input-parallel output-series (ISIPOS) DC/DC converter.

and outputs of these four types of series-parallel configurations can be further combined [28], thereby obtaining enhanced hybrid series-parallel combined topologies, as shown in figure 2.2 [28]. An input-series-input-parallel configuration can effectively decrease the voltage and current stress of the power devices at the primary side. The output-series configuration at the secondary side makes the converter more suitable for high voltage applications. At present, cascaded modular DC/DC converters are widely employed in many engineering applications due to their specific advantages, which include highly modular design, lower voltage and current stress, redundancy characteristics, and higher power density. According to the characteristics of different configurations, each type of cascade modular DC/DC converter has particular applications. For example, the ISOS configuration is suitable for applications where input and output voltages are higher, while the IPOP configuration is suitable for applications where the input and output currents are higher. The IPOS configuration is always employed for applications with high input current and high output voltage, whereas the ISOP configuration is found in applications involving high input voltage and high output current.

Several studies have investigated SAB/DAB submodule-based cascaded DC/DC converters as a DC collection point for HVDC systems [28] [75]. However, for such a converter, the soft switching operation is required when operating with high switching frequency. But due to the operational characteristics of SAB/DAB, full soft switching can only be achieved with limited ranges of load and input voltage, which substantially limits the efficiency and the performance of the converter due to increased switching losses [76]. To address this problem, an external large resonant inductor is usually connected in series with the transformer so as to extend the soft switching range, but the large inductance has a detrimental effect on the performance of the converter since it results in increased duty cycle losses as well as severe voltage ringing due to the resonance between the inductance and junction capacitance [77]. The concept of using a saturation inductor instead of a linear inductor has been discussed [78], and this effectively extends the soft switching range with lower conduction losses and without significant duty cycle loss. However, a large core is required for thermal dissipation, limiting the whole system's power density and large-scale application. Also, more recently an improved soft switching range with conduction losses eliminated was achieved using additional active switches [79-81].

However, the added switches complicate control and increase switching losses, especially in a larger-scale system.

In addition to the methods described above, there is a simpler way to reduce losses. This involves making the converters operate at low frequency. However, it is rare to find a cascaded modular DC/DC converter operating at low or medium frequency (e.g. <500Hz), because the power density of the whole system will be substantially reduced due to the need for large numbers of low or medium frequency transformers and corresponding heat dissipation systems. This would seriously restrict the large-scale engineering applications of cascaded topologies, especially for the offshore platforms with limited space [28] [75].

#### 2.3 Modular Multilevel DC/DC Converters

Modular multilevel converters (MMC) as a DC collection point for HVDC systems have also received close attention in recent years, due to the following distinct advantages in the applications with HVDC systems [82-95]:

- The number of submodules (SMs) in modular multilevel DC/DC converters can be changed to meet different input/output voltage level requirements in the HVDC system.

- Redundancy in modular multilevel DC/DC converters could effectively improve the reliability of the whole HVDC system.

- Low harmonics waveforms can easily be achieved since a large number of SMs is required when modular multilevel DC/DC converters operate in an HVDC system.

- Due to the highly modular design of modular multilevel DC/DC converters, the development cycle and cost of the whole HVDC system are significantly reduced.

- Generally, most modular multilevel DC/DC converters operate at the low/medium frequency in the HVDC system, hence decreasing switching losses.

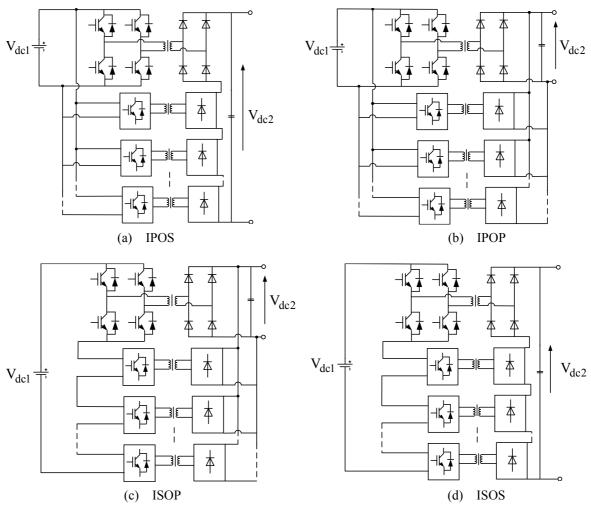

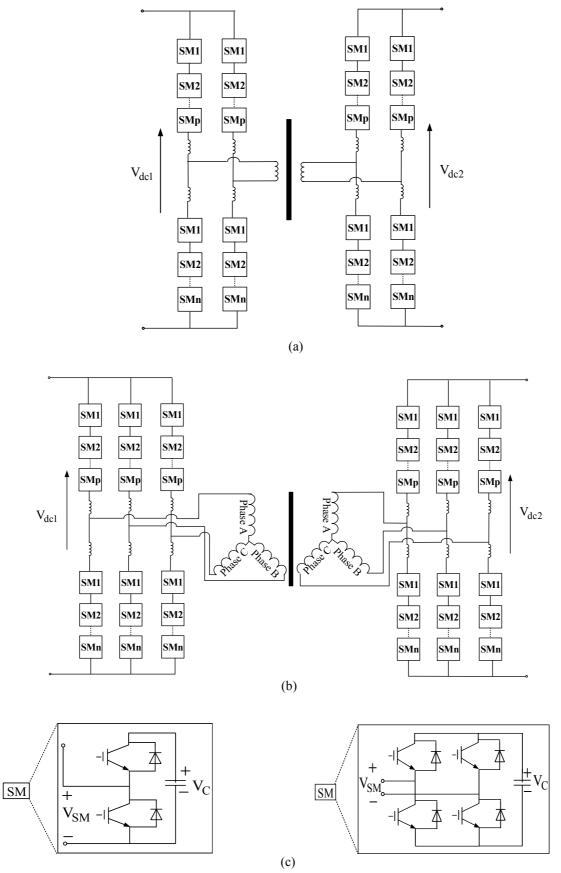

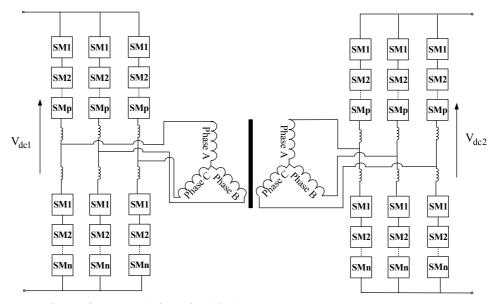

Figure 2.3 Two MMC-based DC/DC converters: (a) single-phase; (b) three-phase; (c) their possible half-bridge and full-bridge submodules.

Although modular multilevel DC/DC converters have many advantages in applications of HVDC systems, there are also some challenges. It is well known that when modular multilevel DC/DC converters are used in an HVDC system, large numbers of SMs are required. This not only increases costs but also complicates the control system. Also, a large number of SMs requires an additional control system to balance their voltages, which would be a big challenge associated with modular multilevel DC/DC converters in real engineering applications of HVDC systems.

Different studies [82-95] have proposed a series of MMC-based DC/DC converters as shown in figure 2.3, functioning as a DC collection point for HVDC systems. At present, most MMC-HVDC projects that are put into operation use the half-bridge-based SM, since it has distinct advantages which include the need for fewer power devices, lower system costs, and higher operational efficiency. However, when a DC fault occurs, the MMC itself does not have the capability of active protection, and so the fault needs to be isolated with additional relay protection equipment. To handle DC faults through the action of the MMC itself, many researchers have conducted extensive investigations and proposed various SM configurations with the capability of protection against faults. The most representative configurations of this kind of MMC consist of full-bridge SMs [96-100]. However, the number of power devices required for a full-bridge SM-based MMC is twice that of a half-bridge SM based MMC, which would not only increase costs but also decrease the efficiency of the whole system [101-105]. Also, a hybrid MMC that consists of full-bridge and half-bridge SMs can also provide a DC fault blocking capability, but without a significant increase in the number of power devices compared with a full-bridge SM-based MMC [101-105].

## 2.4 Research Prospects for High-Voltage High-Power DC/DC Converters

At present, HVDC systems based on modular multilevel DC/DC converters have gradually become the main focus of research, compared to cascaded modular multilevel converters or any other conventional two-level DC/DC converters. However, current research on modular

multilevel DC/DC converters mainly considers mathematical models [92] [98] [101], switching modulation [83] [88] [91] [93] [97] [99], voltage balance control [89] [95], DC-fault blocking [94] [96], SM pre-charging [106], and circulating current suppression [95]. The development of modular multilevel DC/DC converter topologies is still at an early stage. In real engineering applications, the topologies of the modular multilevel DC/DC converters available are very limited. To address this problem, some efforts have been made by researchers to develop more topologies, but many of these involve design compromises in terms of switching losses, limited conversion ratios, and the lack of electrical isolation features. Therefore, in this thesis, an offshore HVDC system will be taken as the application background for modular multilevel DC/DC converters to develop different topologies that can function as DC collection points.

#### 2.5 Summary

This chapter has reviewed the most popular high-voltage high-power DC/DC converters proposed in recent years, including cascaded modular and modular multilevel DC/DC converters. The basic structural characteristics and advantages and disadvantages of these converters have been briefly introduced. Also, the likely directions of further research into high-voltage high-power DC/DC converters have also been considered.

# Chapter 3. Basic Theory and Analysis of MMC

#### 3.1 Introduction

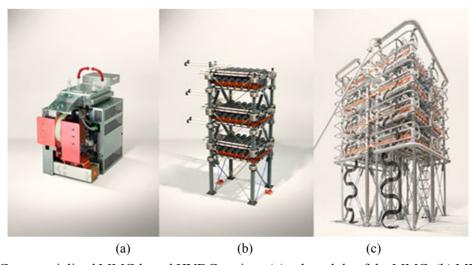

The use of the modular multilevel converter (MMC) in high-voltage high-power (HVDC) systems has several advantages, such as low voltage and current stress, feature modularity, high-quality output waveforms, and fault tolerance operation [93]. Hence that has been an increased interest in this topology in the industry and among researchers. Nowadays, more and more HVDC projects have been built based on the MMC topology, as indicated in figure 3.1 which shows a commercial MMC topology developed by Siemens in August 2013 [107]. This chapter focuses on the basic theory of MMC and puts forward the theoretical basis for the proposed control strategies and MMC-based DC/DC converters discussed in the following Chapters 4, 5, and 6.

Figure 3.1 Commercialized MMC-based HVDC project: (a) submodule of the MMC; (b) MMC arm; (c) complete structure of the MMC [107].

#### 3.2 The Configuration of the MMC and its Basic Operating Principles

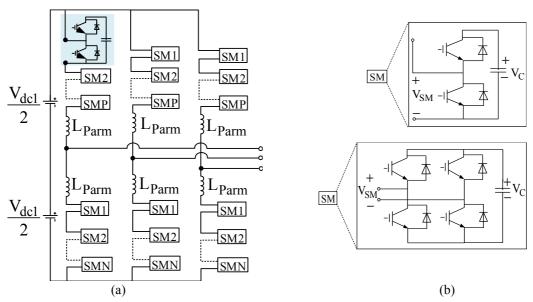

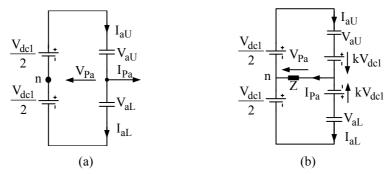

Figure 3.2 shows a simplified schematic diagram of a three-phase MMC, where each phase

Figure 3.2 Configuration of: (a) three-phase MMC; (b) its possible half-bridge and full-bridge SMs.

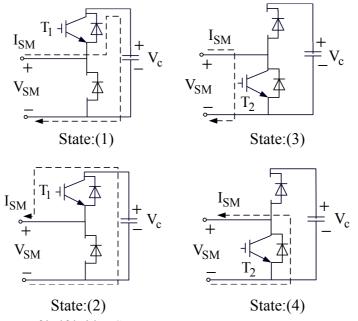

Figure 3.3 Operating states of half-bridge SM.

Table 3.1 Half-bridge SM states of MMC

| States | $T_1$ | $T_2$ | $I_{SM}$ | $V_{SM}$ | Submodule   |

|--------|-------|-------|----------|----------|-------------|

| 1      | ON    | OFF   | > 0      | $V_c$    | charging    |

| 2      | ON    | OFF   | < 0      | $V_c$    | discharging |

| 3      | OFF   | ON    | > 0      | 0        | By-passed   |

| 4      | OFF   | ON    | < 0      | 0        | By-passed   |

consists of half-bridge/full bridge-based submodules (SMs). It is worth noting that the design is fully modular and can be easily expanded as required by simply adding more modules. Each

phase includes two arm inductors which function as reactors to limit the arm current ripple. The DC voltage source is connected at the DC side of the MMC and three-phase AC voltages can be obtained at the output AC side. Because the half-bridge SM-based MMC is used in the following topology design, the operating modes of the half-bridge SM are described below.

Table 3.1 lists the possible operating modes of the half-bridge-based-SM, where the current directions are schematically presented in figure 3.3 [108]. Taking the upper arm of Phase-a as an example, each SM is either inserted or bypassed, leading the voltage of Phase-a to be either increased or decreased by an SM capacitor voltage,  $V_c$  respectively.

When  $T_2$  is turned on and  $T_1$  is turned off, if the current flowing to the SM,  $I_{SM} > 0$ , the SM is by-passed. Similarly, when  $T_2$  is turned on and  $T_1$  is turned off, if the current flowing to the SM,  $I_{SM} < 0$ , the SM is also by-passed. Conversely, when  $T_2$  is turned off and  $T_1$  is turned on, if the current flowing to the SM,  $I_{SM} > 0$ , the SM is in the charging state. Similarly, when  $T_2$  is turned off and  $T_1$  is turned on, if the current flowing to the SM,  $I_{SM} < 0$ , the SM is in the discharging state.

#### 3.3 Mathematical Model of MMC

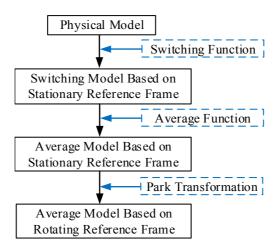

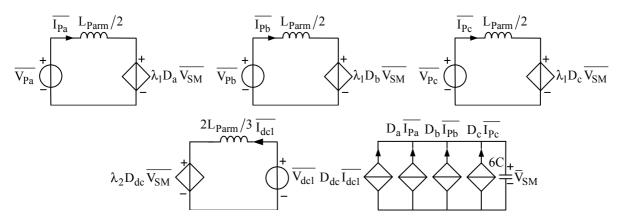

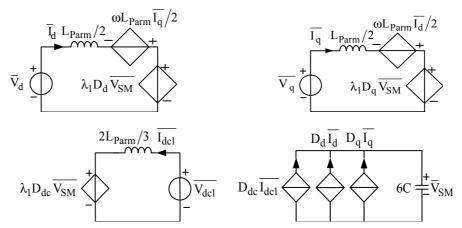

It is well known that there are many switches and energy storage components such as arm inductors and SM capacitors, in the circuit of the MMC, which leads to the need for a high-order, discrete mathematical model. Therefore, to simplify the process of analysis, a simplified model of the MMC is required. This can be obtained by a series of transformations as shown in figure 3.4. From figure 3.4, it can be seen that, based on the circuit configuration of the MMC, the physical model of the MMC is given and simplified to an average model through three steps of simplification and coordinate transformation. Finally, the desired low-order and continuous model is achieved, which can substantially decrease the complexity of the analysis of the MMC.

Figure 3.4 Derivation process of a simplified mathematical model of MMC.

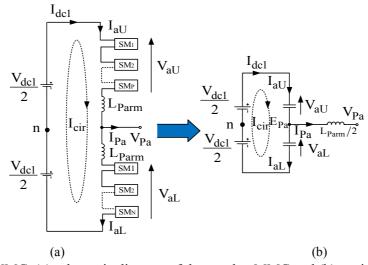

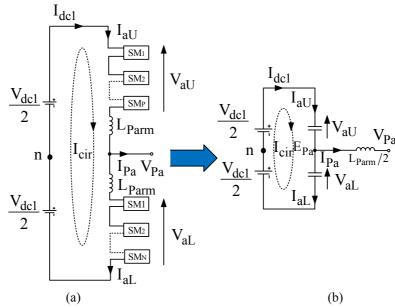

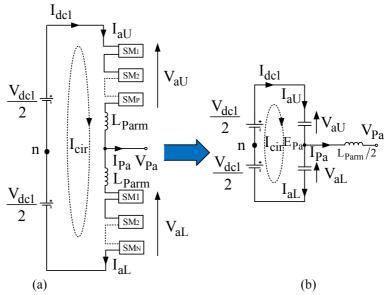

# 3.3.1 Switching model of MMC

Figure 3.5 shows the equivalent circuit of one-leg (Phase-a) of the MMC, where  $V_{dc1}$  and  $I_{dc1}$  are its DC input voltage and current respectively,  $V_{aU}$  and  $V_{aL}$  are the voltages of the upper and lower arm of Phase-a respectively,  $I_{aU}$  and  $I_{aL}$  are the currents of the upper and lower arms of Phase-a respectively,  $E_{Pa}$  is the equivalent output phase voltage as shown in figure 3.5(b) and  $V_{Pa}$  is the output AC voltage, and  $I_{cir}$  and  $I_{Pa}$  are the circulating and ouput AC currents respectively.

Figure 3.5 One-leg MMC, (a) schematic diagram of the one-leg MMC and (b) equivalent circuit. From figure 3.5, the upper and lower arm currents of the Phase-a leg can be expressed by:

$$I_{aU} = I_{Pa}/2 + I_{cir} (3.1)$$

$$I_{aL} = -I_{Pa}/2 + I_{cir} (3.2)$$

where the circulating current,  $I_{cir}$ , flows through both the upper and lower arms.

It should be noted that the circulating current has no effect on the output phase current and can be expressed as:

$$I_{cir} = (I_{all} + I_{aL})/2 (3.3)$$

Concerning (3.1) and (3.2), the equation for output AC current  $I_{Pa}$  can be expressed in terms of upper and lower arm currents as:

$$I_{Pa} = I_{aU} - I_{aL} \tag{3.4}$$

If *n* is a neutral point, applying the Kirchhoff voltage laws (KVL) to the one-leg MMC shown in figure 3.5(a) allows the upper and lower voltages to be derived as:

$$V_{aU} = \frac{V_{dc1}}{2} - V_{Pa} - L_{Parm} \frac{dI_{aU}}{dt}$$

(3.5)

$$V_{aL} = \frac{V_{dc1}}{2} + V_{Pa} - L_{Parm} \frac{dI_{aL}}{dt}$$

(3.6)

Combining (3.5) and (3.6), the output phase voltage  $V_{Pa}$  can be expressed as:

$$V_{Pa} = \frac{1}{2} (V_{aL} - V_{aU}) - \frac{1}{2} L_{Parm} \frac{d(I_{aL} - I_{aU})}{dt}$$

(3.7)

Substituting (3.4) into (3.7), the equivalent output phase voltage  $E_{Pa}$  can be given by:

$$E_{Pa} = \frac{1}{2} (V_{aL} - V_{aU}) = V_{Pa} + \frac{1}{2} L_{Parm} \frac{dI_{Pa}}{dt}$$

(3.8)

Therefore, the mathematical model of the one-leg MMC can be derived by rearranging (4.8) as:

$$\frac{1}{2}L_{Parm}\frac{dI_{Pa}}{dt} = E_{Pa} - V_{Pa} \tag{3.9}$$

Therefore, the equivalent circuit of one-leg MMC can be obtained as shown in figure 3.5(b) based on the equation (3.9).

Then, by introducing the switching function into (3.5) and (3.6), the upper and lower arm voltages can be expressed as:

$$V_{aU} = \frac{V_{dc1}}{2} - V_{Pa} - L_{Parm} \frac{dI_{aU}}{dt} = \sum_{i=1}^{\lambda_1} S_{aU_i} V_{SM\_aU\_i}$$

(3.10)

$$V_{aL} = \frac{V_{dc1}}{2} + V_{Pa} - L_{Parm} \frac{dI_{aL}}{dt} = \sum_{i=1}^{\lambda_1} S_{aL_i} V_{SM\_aL\_i}$$

(3.11)

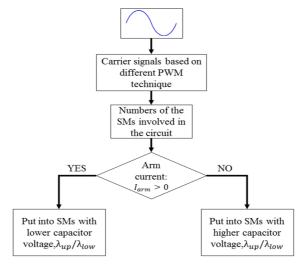

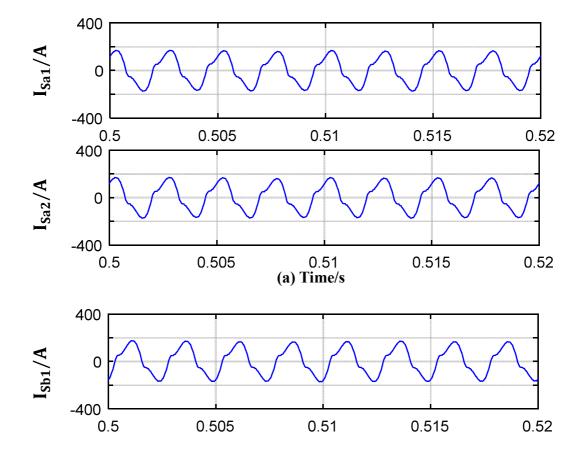

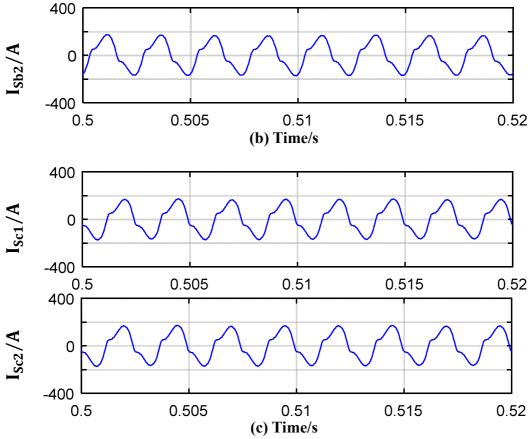

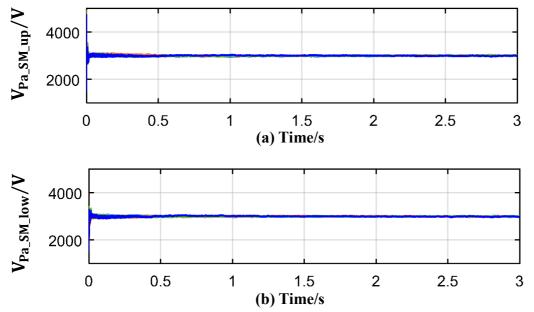

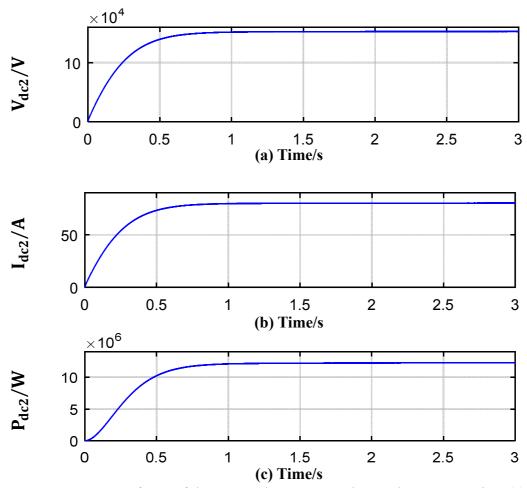

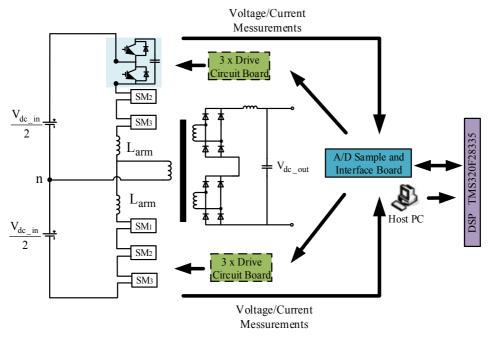

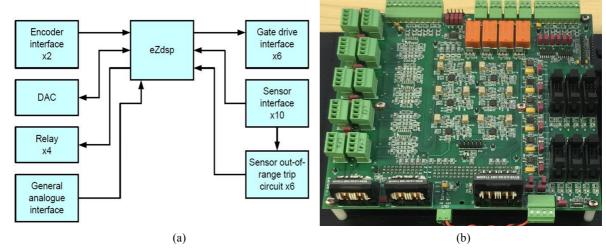

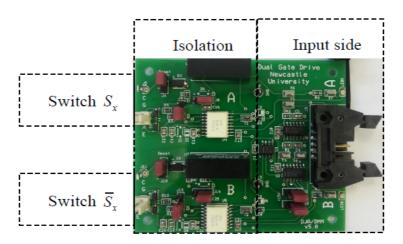

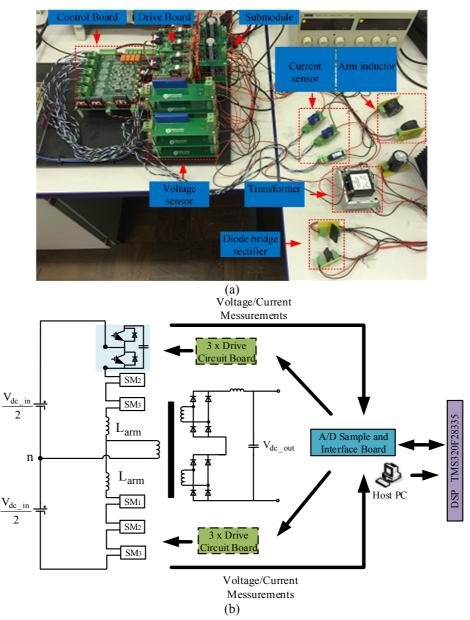

where  $\lambda_1$  is the number of SMs per arm of the MMC,  $V_{SM\_aU\_i}$  and  $V_{SM\_aL\_i}$  are the  $i^{th}$  SM voltages of the upper and lower arm in Phase-a respectively, and  $S_{aU_i}$  and  $S_{aL_i}$  are the  $i^{th}$  SM switching function of the upper and lower arms in Phase-a respectively.