# EMBRACING VISUAL EXPERIENCE AND DATA KNOWLEDGE: EFFICIENT EMBEDDED MEMORY DESIGN FOR BIG VIDEOS AND DEEP LEARNING

A Thesis Submitted to the Graduate Faculty of the North Dakota State University of Agriculture and Applied Science

By

Jonathon David Edstrom

# In Partial Fulfillment of the Requirements for the Degree of DOCTOR OF PHILOSOPHY

Major Department: Electrical and Computer Engineering

May 2019

Fargo, North Dakota

# North Dakota State University Graduate School

# Title EMBRACING VISUAL EXPERIENCE AND DATA KNOWLEDGE: EFFICIENT EMBEDDED MEMORY DESIGN FOR BIG VIDEOS AND DEEP LEARNING

By

Jonathon David Edstrom

The Supervisory Committee certifies that this disquisition complies with North Dakota

State University's regulations and meets the accepted standards for the degree of

# DOCTOR OF PHILOSOPHY

SUPERVISORY COMMITTEE:

Scott Smith

Chair

Na Gong

Sudarshan Srinivasan

Yiwen Xu

Mijia Yang

Approved:

5/3/19 Date Benjamin D. Braaten

Department Chair

# ABSTRACT

Energy efficient memory designs are becoming increasingly important, especially for applications related to mobile video technology and machine learning. The growing popularity of smart phones, tablets and other mobile devices has created an exponential demand for video applications in today's society. When mobile devices display video, the embedded video memory within the device consumes a large amount of the total system power. This issue has created the need to introduce power-quality tradeoff techniques for enabling good quality video output, while simultaneously enabling power consumption reduction. Similarly, power efficiency issues have arisen within the area of machine learning, especially with applications requiring large and fast computation, such as neural networks. Using the accumulated data knowledge from various machine learning applications, there is now the potential to create more intelligent memory with the capability for optimized trade-off between energy efficiency, area overhead, and classification accuracy on the learning systems. In this dissertation, a review of recently completed works involving video and machine learning memories will be covered. Based on the collected results from a variety of different methods, including: subjective trials, discovered datamining patterns, software simulations, and hardware power and performance tests, the presented memories provide novel ways to significantly enhance power efficiency for future memory devices. An overview of related works, especially the relevant state-of-the-art research, will be referenced for comparison in order to produce memory design methodologies that exhibit optimal quality, low implementation overhead, and maximum power efficiency.

#### ACKNOWLEDGEMENTS

I would like to thank Dr. Na Gong for her time, guidance, and knowledge in completing all the works presented in this dissertation. I would also like to thank my other committee members, Dr. Scott Smith, Dr. Yiwen Xu, Dr. Sudarshan Srinivasan, and Dr. Mijia Yang for their feedback and assistance in presentations, papers and other advice given during my doctoral study. I am thankful for all the help provided by the other members of my lab, especially Yifu Gong, Dongliang Chen, and Hritom Das. Their help with preparing experiments, calculating simulation results, and verifying designs was paramount in completing the necessary work for conferences, journals, and the completion of my doctoral requirements.

I am grateful to Dr. Mark McCourt and the Department of Psychology at NDSU for allowing us to use their facility for psychophysical tests. I would specifically like to thank Ganesh Padmanabhan and Enrique Alvarez Vazquez for the assistance in analyzing video samples, preparing a mobile application testing environment for subjective trials, and preparing results for further discussion. Without their help, the process for obtaining results would have taken much longer and been much more difficult.

Last, I would like to recognize and thank the National Science Foundation and ND EPSCoR for the financial support that made the included research possible. I am grateful to NDSU's Center for Computationally Assisted Science and Technology (CCAST) for allowing me access to their high power computing servers for computing simulation results; without this, a lot of my research relating to data-mining and machine learning would not have been possible.

In reference to IEEE copyrighted material, which is used with permission in this dissertation, the IEEE do not endorse any of North Dakota State University's products or services. Internal or personal use of this material is permitted.

iv

# DEDICATION

To my parents, Fred and Terri, who have always been there to support me in everything I do.

| ABSTRACT                                                                                     | iii  |

|----------------------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                                             | iv   |

| DEDICATION                                                                                   | v    |

| LIST OF TABLES                                                                               | x    |

| LIST OF FIGURES                                                                              | xi   |

| LIST OF ABBREVIATIONS                                                                        | xiii |

| CHAPTER 1. INTRODUCTION                                                                      | 1    |

| Motivation for Video and Machine Learning Memory Optimization                                | 1    |

| Memory Design for Video Applications                                                         |      |

| Memory Design for Deep Learning Applications                                                 | 5    |

| Design Trade-offs and Evaluation                                                             | 6    |

| CHAPTER 2. DATA-PATTERN ENABLED SELF-RECOVERY LOW-POWER<br>STORAGE SYSTEM FOR BIG VIDEO DATA |      |

| Embedded Memory Failure Analysis at Near-Threshold Voltage                                   | 8    |

| Data Pattern Investigation for Self-Recovery                                                 | 10   |

| Rule Mining Enabled Horizontal Association                                                   | 10   |

| Vertical Correlation                                                                         |      |

| Optimal Data Patterns for Self-Recovery                                                      |      |

| Recovery Failure Caused by Double Faults in Data Patterns                                    |      |

| DPSR Hardware Implementation                                                                 |      |

| Evaluation Methodology and Results                                                           |      |

| Performance                                                                                  |      |

| Layout                                                                                       |      |

| Power Efficiency                                                                             |      |

| Video Output Quality Analysis                                                                |      |

# **TABLE OF CONTENTS**

| Comparison with Prior Work                                                                           | 26 |

|------------------------------------------------------------------------------------------------------|----|

| DPSR Concluding Remarks                                                                              | 27 |

| CHAPTER 3. CONTENT-ADAPTIVE MEMORY FOR VIEWER-AWARE ENERGY-<br>QUALITY SCALABLE MOBILE VIDEO SYSTEMS | 28 |

| Influence of Video Content on Viewer Experience                                                      | 28 |

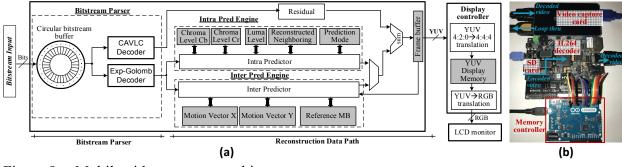

| Mobile Video Memory System                                                                           | 28 |

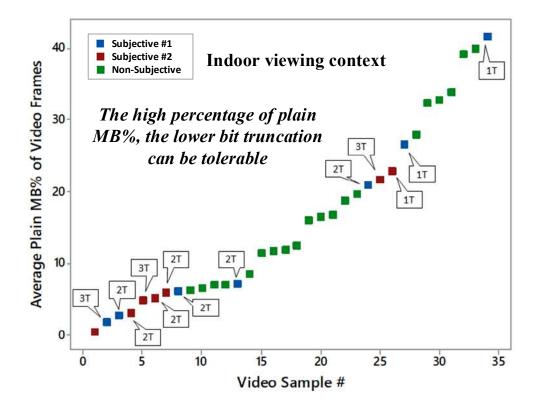

| Influence of Video Content on Viewer Experience in the Presence of Hardware Noise                    | 30 |

| Modeling Process                                                                                     | 35 |

| Subjective Testing Procedure for Data Collection                                                     | 36 |

| Modeling Process                                                                                     | 36 |

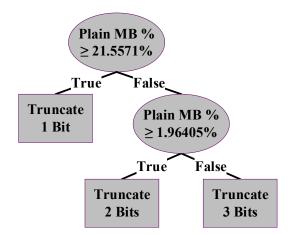

| Quality Optimized Bit Truncation Design                                                              | 40 |

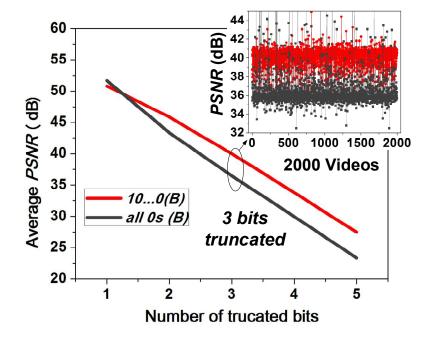

| Quality Optimized Bit Truncation                                                                     | 40 |

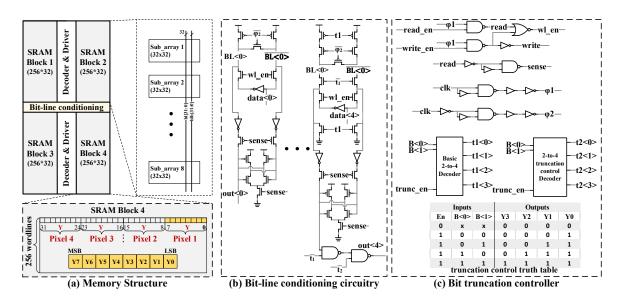

| Content-Adaptation Video Memory Design                                                               | 42 |

| Experimental Results                                                                                 | 43 |

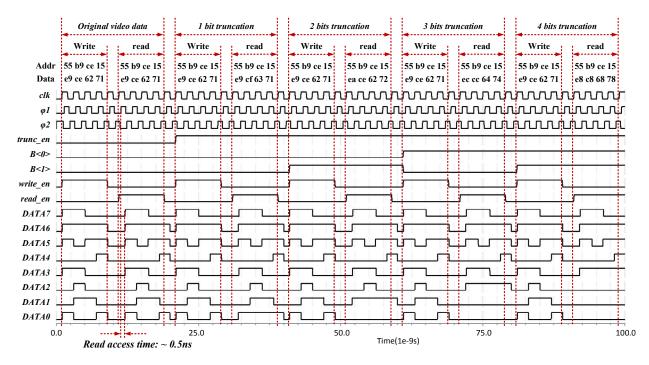

| Speed                                                                                                | 44 |

| Layout                                                                                               | 44 |

| Power Savings                                                                                        | 45 |

| Video Quality                                                                                        | 46 |

| Context-Aware Memory Concluding Remarks                                                              | 51 |

| CHAPTER 4. DATA-DRIVEN INTELLIGENT EFFICIENT SYNAPTIC STORAGE<br>FOR DEEP LEARNING                   | 52 |

| Synaptic Storage and Memory Failure Overview                                                         | 52 |

| Synaptic Storage in Artificial Neural Networks                                                       | 53 |

| Impact of Synaptic Memory Failures on ANN Classification Accuracy                                    | 54 |

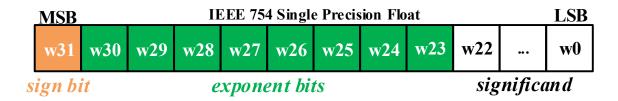

| Data Characteristics of Synaptic Storage                                                             | 57 |

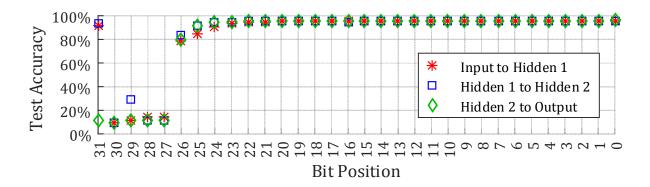

| Data Contribution Characteristics                                                               | 57 |

|-------------------------------------------------------------------------------------------------|----|

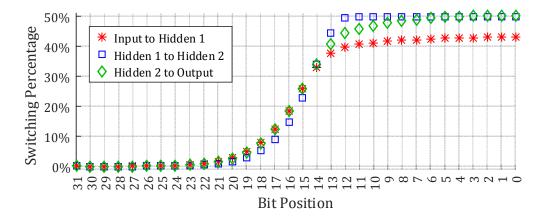

| Data Switching Characteristics                                                                  | 59 |

| Data Association / Correlation Characteristics                                                  | 60 |

| Proposed Data-Driven Synaptic Memory                                                            | 61 |

| Implementation                                                                                  | 61 |

| Results                                                                                         | 62 |

| Data-Driven Synaptic Memory Concluding Remarks                                                  | 64 |

| CHAPTER 5. ENABLING ENERGY-EFFICIENT DIFFERENTIALLY PRIVATE<br>EDGE INFERENCE FOR DEEP LEARNING | 66 |

| Learning with Differential Privacy                                                              | 66 |

| Why do we need Deep Learning with Privacy?                                                      | 66 |

| Differentially Private Deep Learning and State of the Art                                       | 68 |

| Impact of Memory Failures in Differentially Private Deep Learning Systems                       |    |

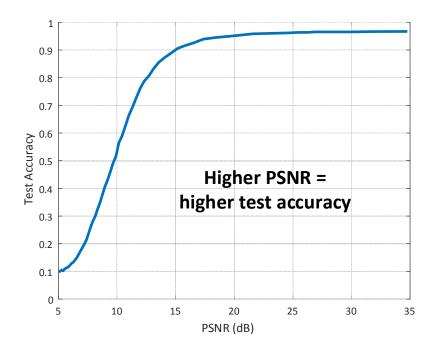

| Impact of Image Quality on Classification Accuracy                                              |    |

| Impact of Dataset Memory in Edge Devices                                                        |    |

| Impact of Hardware on Privacy/Accuracy Trade-off                                                |    |

| Optimization Model based Memory Design                                                          |    |

| Embedded Memory Design for Deep Learning                                                        |    |

| Optimized Memory Design                                                                         |    |

| Power Consumption                                                                               |    |

| Dataset Quality and Accuracy                                                                    |    |

| Accuracy at Different Privacy Levels                                                            |    |

| Differential Private Edge Inference Memory Concluding Remarks                                   | 82 |

| CHAPTER 6. CONCLUSIONS AND FUTURE WORK                                                          |    |

| REFERENCES                                                                                      | 85 |

| APPENDIX A. YOUTUBE-8M VIDEO DOWNLOAD SCRIPT                                                    |    |

| APPENDIX B. YOUTUBE-8M VIDEO CLIPPED TIMING SCRIPT        | 95  |

|-----------------------------------------------------------|-----|

| APPENDIX C. MACROBLOCK ANALYSIS AND TRUNCATION PROGRAM    | 96  |

| APPENDIX D. SYNAPTIC STORAGE FOR DEEP LEARNING MODEL CODE | 104 |

| APPENDIX E. MNIST BIT FAULT INJECTION PROGRAM             | 108 |

# LIST OF TABLES

| Table                                                                                | Page |

|--------------------------------------------------------------------------------------|------|

| 1. Fault probability in a 32-bit SRAM word (10 <sup>9</sup> Monte Carlo simulations) |      |

| 2. Discovered association rules. Bit 1 (i.e. Y1, Cb1, Cr1) is the MSB                |      |

| 3. Vertical correlation probabilities                                                | 14   |

| 4. Optimal data patterns from 25 YouTube-8M videos                                   | 16   |

| 5. DPSR recovery failure rates                                                       | 17   |

| 6. Video PSNR metric comparison                                                      |      |

| 7. Video SSIM metric comparison                                                      |      |

| 8. DPSR comparison with prior works on low power SRAM                                |      |

| 9. Video memories and their functionality                                            |      |

| 10. Results of videos with different LSBs truncated in different memories            |      |

| 11. PSNR of different videos with bit truncated applied                              |      |

| 12. Results of ordinal logistic regression                                           |      |

| 13. Probability mass function for random variable <i>Y</i>                           |      |

| 14. ANN architecture and configurations                                              |      |

| 15. Synaptic storage comparison with existing 8T+6T hybrid design                    |      |

| 16. 6T and 8T bit cell design options for 45nm technology at 0.5V                    |      |

| 17. Optimal design results and comparison                                            |      |

| 18. Power consumption of optimized 45nm memory design at 0.5V                        | 79   |

| 19. Dataset quality and accuracy for MNIST and Fashion                               | 80   |

| 20. Impact of privacy level on test accuracy                                         |      |

# LIST OF FIGURES

| Figure                                                                 | Page                         |

|------------------------------------------------------------------------|------------------------------|

| 1. Trade-off between hardware evaluation metrics                       | 7                            |

| 2. Error maps in SRAM array at 0.5V. (a) Error rate: $10^{-3}$ and (b) | error rate: 10 <sup>-2</sup> |

| 3. 2D data-pattern enabled self-correction and data pattern analys     | is dataset11                 |

| 4. Proposed DPSR with data self-recovery ability                       |                              |

| 5. DPSR layout design                                                  |                              |

| 6. Power consumption of different memory operations                    |                              |

| 7. Video output using different video storage techniques               |                              |

| 8. Mobile video memory architecture.                                   |                              |

| 9. Plain macroblock visualization and video output comparison (v       | white = plain)               |

| 10. Acceptable truncated bits based on subjective feedback             |                              |

| 11. Developed decision tree model for bit truncation                   |                              |

| 12. Average PSNR values using two different truncation technique       | es 42                        |

| 13. Content-adaptive video memory                                      |                              |

| 14. Timing diagram (DATA7: MSB; DATA0: LSB)                            |                              |

| 15. Physical layout design                                             |                              |

| 16. Power Savings                                                      |                              |

| 17. Psychological experiment setup                                     |                              |

| 18. Video quality testing results using the decision tree model        |                              |

| 19. Output quality of video with tag <i>wF6lvdXXwc4</i>                |                              |

| 20. (a) ANN architecture; (b) Single neuron with synaptic weights      |                              |

| 21. (a) Schematic and (b) layout design of 6T and 8T SRAM bit ce       | ells 55                      |

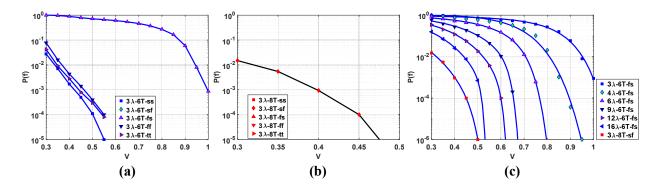

| 22. 45nm SRAM bit cell failure rates based on $V_{dd}$ voltage scaling |                              |

| 23. IEEE 754 Single Precision Floating Point Representation            |                              |

| 24. Influence of synaptic weight bit position on ANN classification accuracy   | 59 |

|--------------------------------------------------------------------------------|----|

| 25. MNIST average bit switching percentage of each bit position                | 59 |

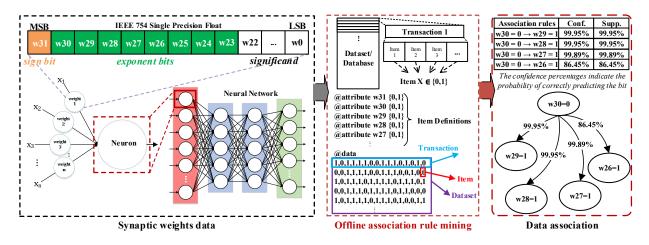

| 26. Offline data-mining assisted synaptic data relationships study             | 60 |

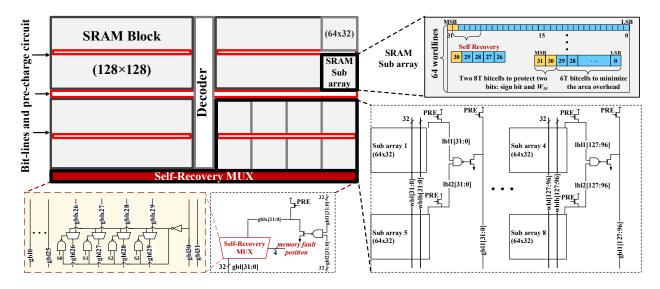

| 27. Data-driven efficient synaptic storage                                     | 62 |

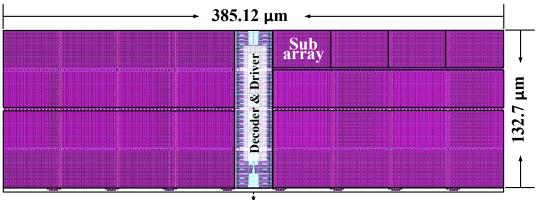

| 28. Layout of the proposed synaptic memory in 45 nm technology                 | 63 |

| 29. Power consumption of synaptic storage                                      | 64 |

| 30. Proposed deep learning system with energy-efficiency/privacy/accuracy      |    |

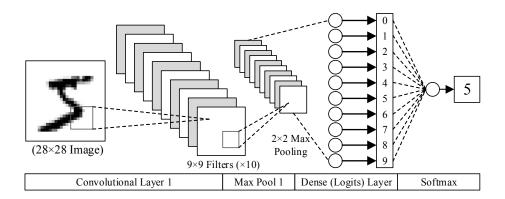

| 31. Differentially private convolutional neural network used for analysis      | 71 |

| 32. Influence of dataset quality on test accuracy (MNIST dataset results)      |    |

| 33. Impact of errors on privacy/accuracy. MSBs protected: (a) None (b) 2       |    |

| 34. Impact of memory failure rate on the accuracy of the learning system       | 74 |

| 35. SRAM bit cells. Minimum sized 45nm schematic and layout: (a) 6T (b) 8T     | 77 |

| 36. Verification of errors on privacy/accuracy. MSBs protected: (a) None (b) 2 |    |

# LIST OF ABBREVIATIONS

| CMOS            | Complementary Metal-Oxide-Semiconductor |

|-----------------|-----------------------------------------|

| SRAM            | Static Random Access Memory             |

| ECC             | Error Correcting Code                   |

| BIST            | Built-In Self-Test                      |

| LSB             | Least Significant Bit                   |

| MSB             | Most Significant Bit                    |

| IoT             | Internet of Things                      |

| PSNR            | Peak Signal-To-Noise Ratio              |

| NMOS            | N-Type Metal-Oxide-Semiconductor        |

| PMOS            | P-Type Metal-Oxide-Semiconductor        |

| V <sub>dd</sub> | Supply Voltage                          |

| RBL             | Readout Bit Line                        |

| MUX             | Multiplexer                             |

| POST            | Power-On Self-Test                      |

| RDF             | Random Dopant Fluctuation               |

| URL             | Uniform Resource Locator                |

| DPSR            | Data Pattern Self-Recovery              |

| MSE             | Mean Squared Error                      |

| SSIM            | Structural Similarity                   |

| ANN             | Artificial Neural Network               |

| CNN             | Convolutional Neural Network            |

### **CHAPTER 1. INTRODUCTION**

Recently, research and development of energy-efficient memory for general use or application specific designs has become of great interest [1]. The need for devices that are capable of saving power intrinsically, while maintaining a robust, minimal failure operation is becoming more and more necessary with the growing use of portable electronics [2]. The detailed description of multiple techniques to allow for power savings, including partially disabling circuitry or minimizing supply voltage and the use of self-correction techniques to mitigate errors and provide a high quality output, will be introduced in the different chapters within this dissertation. This chapter contains a brief introduction describing the importance of the presented designs and related works. The main two topics that will be described in detail in this dissertation involve video and deep learning applications.

# Motivation for Video and Machine Learning Memory Optimization

According to market research, by the year 2020, the total amount of data that will have been created, transmitted, and replicated, will be as large as 40ZB (Zettabyte, or 10<sup>21</sup> bytes) [3, 4]; and more than half of that data will be video data [5]. Video streaming is currently one of the most energy-intensive applications on mobile devices, with frequent memory accesses contributing to over 30% of the total power consumption [6, 7]. The frequent memory accesses required for these types of streaming applications lead to shorter battery life, which is becoming one of the largest contributors to user dissatisfaction [5]. One other notable concern is the increased memory footprint in mobile video systems. With recent advances to high definition video formats, the video decoder memory can occupy more than 65% of the total silicon area [8, 9]. As the silicon area increases, the total cost to manufacture the memory increases; therefore, designing memory with minimal area overhead is of paramount importance to the end user.

Similar to video memory design, the growing demand for computing and memory resources in machine learning applications has created a need for efficient hardware schemes to enable real-time adaptation. For example, deep learning systems such as neural networks require extensive computational time and dissipate a large amount of power to calculate a high accuracy trained model [10]. In particular, the training process needs continuous model updating and requires intensive memory access. For these types of designs, the on-chip SRAM occupies more than 56% of the silicon area and contributes to over 60% of the power consumption of the entire system [11]. Consequently, improving the energy efficiency of SRAM with low area overhead is vital to support future deep learning systems.

## **Memory Design for Video Applications**

Video applications have been shown to inherently possess error resiliency to some extent [12]. This error resiliency enables video applications to be redesigned using approximate computing methods for power savings. The video memory designs described within the chapters of this dissertation deal with mobile video applications in particular; but these designs can be adapted for use in devices that are a part of other application types as well. The designed memories use CMOS SRAM technology, but the methodologies used to incorporate power savings and data correction may prove useful in future technologies as well.

Voltage scaling techniques have been widely applied to reduce the power consumption of memory systems. Researchers have shown that SRAM achieves maximum efficiency at near-threshold voltage [13]. However, as voltage scales, SRAMs are susceptible to failure due to significant process variation. Various techniques have been developed to correct or eliminate these memory failures as voltage is scaled. Traditional low power memory techniques can be divided into three general categories: (i) assist schemes, such as adjustment of cell voltage [14]

and boosted word-line voltage [15]; (ii) large bit cells, such as upsized 6T cell [16], asymmetric 7T cell [17], single-ended read-decoupled 8T cells [18], read-disturb-free 9T [19], and bitinterleaving 12T cells [20]; and (iii) error correction techniques spanning from the use of error correction codes [21] to data remapping [22]. Unfortunately, almost all existing solutions require considerable implementation overhead, as high as 50-100% of the original memory design.

Recently, a new branch of low voltage embedded memory techniques have been developed to embrace the memory faults, instead of avoiding the faults (i.e. assist schemes or more than 6T bit cells) or correcting the faults (e.g. ECC). Those techniques aim to mitigate the impact of memory faults by minimizing the magnitude of the error due to a faulty cell, based on the determined memory fault positions from runtime testing (e.g. BIST). Those techniques are referred to as fault-position aware mitigation techniques. For example, in [23], a shifting technique was developed to store the LSBs in faulty bit cells, which may lead to a tolerable output quality. In [13], a squeezing technique was presented to compress zeros and store them in less memory space, thereby avoiding memory failures at low voltages. However, based on the predetermined memory fault positions, the existing techniques still involve complex operation (e.g. shifting value calculations and storage) and the overhead incurred is still significant (e.g. 65% in [23]). Several recent efforts have also investigated application resilience of videos to approximations with "good enough" output and additional power savings. [24] presented a hybrid 6T+8T SRAM to achieve quality-power optimization. In [16], a heterogeneous sizing scheme is presented to reduce the failure probability of conventional 6T bit cells. In [25], the correlation between the MSBs of video data was utilized to design a hybrid 8T+10T memory for power savings.

To address the storage challenge of videos as well as other big data, leveraging the assets of big data to extract useful knowledge and actionable information for hardware design is proposed in chapter 2. Today's big data applications, including videos, have three common data characteristics [26]: redundant inputs, multiple acceptable outputs, and statistical computations. Those intrinsic characteristics provide substantial opportunities for data relationship discovery and pattern identification. This is turn will enable a new dimension for hardware design space and bring exciting innovation opportunities for multi-dimensional innovations in circuits and systems. Based on this, an extension of the work done in [27] proposes an efficient SRAM design technique for big video data. The design is presented in chapter 2 with negligible area overhead (7.94%) and performance penalty.

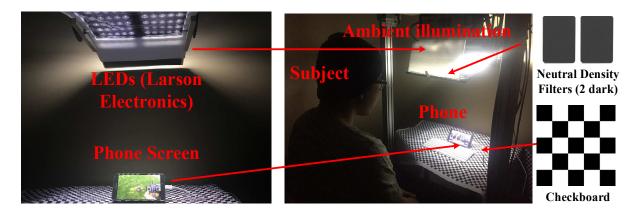

Viewer's experience is one other important design concern that hardware engineers need to consider when designing circuitry such as the memory used for storing video. Various studies have displayed the impact of contextual influences such as illuminance levels, where an increased amount of ambient luminance allows for a larger amount of error to be introduced by voltage reduction techniques without noticeable degradation to the viewers. Two low power techniques in particular, voltage scaling and bit truncation, have been explored [28, 29, 30] and achieve similar PSNR values. However, the video quality degradation caused by bit truncation is much less noticeable than that of the voltage scaling technique for viewers.

Based on previous works [28, 29, 30] and the novel introduction of video content characteristics, chapter 3 proposes a video memory design that uses the viewer's experience to enable video content-adaptive functionality with dynamic energy-quality trade-off.

#### Memory Design for Deep Learning Applications

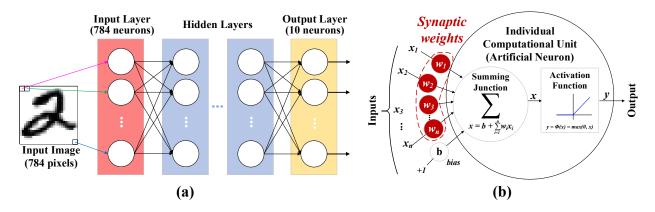

Traditional low power memories are implemented to accommodate a large amount of data utilizing more than 6T bit cells or assist schemes which usually come with significant implementation cost (e.g. silicon area, performance overhead). Although such overhead might be acceptable in general-purpose systems, they are not sufficient to satisfy the storage need for deep learning applications. Recently in [31], a deep learning specific hybrid 8T-6T synaptic storage was presented where varying number of 8T bit cells replace the traditional 6T bit cells to store the MSBs because 8T bit cells are more robust at scaled voltages with decoupled read and write paths.

In chapter 4, a systematic data-mining framework that enables a comprehensive understanding of synaptic data characteristics is used to develop a low-power synaptic memory for deep learning. Using an offline data-mining assisted synaptic relationships study, discovered synaptic characteristics including contribution, switching, and association/correlation were used to optimize the memory design. A novel data-driven memory design technique is proposed that can store synaptic weights efficiently and with the ability for self-recovery under memory failures. A 64kbit SRAM is designed that enables considerable power savings of up to 83.2% and with negligible area overhead (3.17%) with minimal loss to classification accuracy (0.72%).

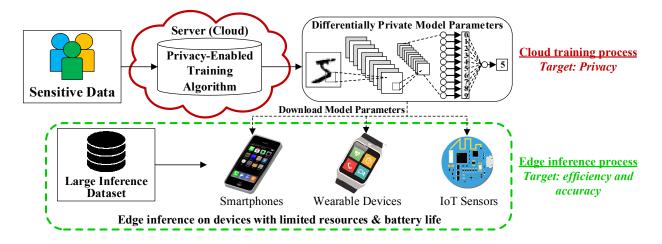

With deep learning becoming popular for developments in artificial intelligence in modern applications such as facial identification, automatic translation, computer vision, selfdriving cars, healthcare and education, the need for data privacy is becoming increasingly important. For example, collected health care data can be used in deep learning models to provide personalized methods of prevention, treatment and care, ultimately aiding people who are aging or those with disabilities to address health issues. These learning enabled benefits do

however come at a cost, which partially involves the issue of a serious privacy concern. Sharing personal data carries inherent risk to the individual.

To protect the privacy of an individual's data that are used to train these deep learning models, one technique that has recently been proposed is differentially private deep learning algorithms. This approach adds random noise to the computation while learning so that the output of the model does not significantly depend on any particular training sample. In addition to privacy, as deep learning models grow, the energy and resources needed during the inference process, particularly the memories, have become a major constraint to resource-limited IoT devices. Existing low-power memory design techniques, such as voltage scaling, usually come with large memory failures under low power conditions, which further reduce the accuracy of deep learning systems. Therefore, new memory hardware techniques are needed to consider the trade-off between power efficiency, accuracy, and privacy in order to meet the increasing demands of the edge inference storage in these devices.

In chapter 5, a memory-based technique to enable a suitable accuracy/privacy trade-off that will meet the requirement of different AI applications is presented. The proposed technique will allow for low power operation to enable power savings, thereby enabling an energy-efficient edge inference on edge devices such as IoT sensors.

#### **Design Trade-offs and Evaluation**

In order to evaluate how well each of the designed memories perform, simulations were performed to calculate values for power, quality, and area overhead. The relationship between the main three hardware design metrics is shown in Figure 1. By constraining two of the three metrics and improving the third, while also comparing against recent research, it is possible to clearly show improvements of each work against the state of the art. The following chapters

describe the design process for four unique works, each using novel memory optimization techniques, including comparison against the state of the art.

Figure 1. Trade-off between hardware evaluation metrics

All information, tables, and figures in chapters 2, 3, 4, and 5 are either directly taken or adapted, with permission to re-use, from [32], [33], [34], and [35], respectively. The final chapter discusses the comparison of these techniques with state of the art designs in other recent works.

# CHAPTER 2. DATA-PATTERN ENABLED SELF-RECOVERY LOW-POWER STORAGE SYSTEM FOR BIG VIDEO DATA<sup>1</sup>

The growing popularity of powerful mobile devices such as smart phones and tablet devices has resulted in the exponential growth of demand for video applications. However, due to the large video data size and intensive computation, mobile video applications require frequent embedded memory access, which consumes a large amount of power and limits battery life. In this chapter, a low-cost self-recovery video storage system is presented by investigating meaningful data patterns hidden in big video data through introducing data mining techniques to the hardware design process. A two-dimensional data-pattern approach is proposed in order to explore horizontal data-association and vertical data-correlation characteristics. Such data relationship discovery and pattern identification enable a new dimension for the hardware design space and bring self-recovery ability to memories in the presence of bit cell failures. Based on the identified optimal data patterns, a low-cost and efficient SRAM design to enable data self-recovery at low voltages is presented. A 45nm 32kb SRAM is implemented that delivers good video quality at near-threshold voltage (0.5 V) with negligible area overhead (7.94%).

# **Embedded Memory Failure Analysis at Near-Threshold Voltage**

It has been shown that the computing efficiency is maximized when a circuit is operating at near-threshold voltage [13]. However, at 0.5V (the target near-threshold voltage for this design), SRAM failures become more severe with the increasing process variation. In particular, the RDF effect leads to threshold voltage ( $V_{th}$ ) variation and SRAM cell failures [36]. For the current manufacturing technologies, the failure probability of an SRAM cell ( $P_{fail}$ ) typically

<sup>&</sup>lt;sup>1</sup> The material in this chapter was co-authored by Jonathon Edstrom, Dongliang Chen, and Yifu Gong. Jonathon Edstrom was in charge of all pattern discovery, data analysis, and video quality metric and simulation results. Dongliang Chen and Yifu Gong, provided the presented SRAM hardware design with power simulation results based on the discovered patterns.

ranges between 10<sup>-3</sup> and 10<sup>-2</sup>, depending on the bit cell area [13, 37]. The minimum-sized SRAM has highest failure rate of 10<sup>-2</sup> and larger bit cells have a lower failure probability. With 58% area overhead, the failure rate can be reduced from 10<sup>-2</sup> to 10<sup>-3</sup> [37]. Both 10<sup>-2</sup> (minimum-sized SRAM) and 10<sup>-3</sup> (upsized SRAM) conditions are considered in the design analysis. It should be noted that, the failure rate can be further optimized using a recently developed priority based sizing technique [38].

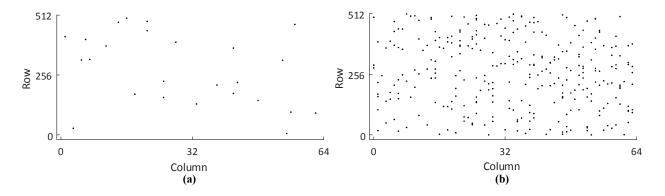

To further study the SRAM failure characteristics at low voltage, errors maps for 512 word × 64 bit SRAM were investigated for  $P_{fail}$  equal to  $10^{-2}$  and  $10^{-3}$ . During the fault injection process, the bits that failed were assumed to be located across the memory cells based on the failure probabilities according to a uniform distribution, introducing embedded memory failures to the decoding process. Using a uniform distribution for simulating the errors is confirmed by memory failure measurements in [39]. The results are shown in Figure 2. SRAM faults are uniformly distributed in the array.

Figure 2. Error maps in SRAM array at 0.5V. (a) Error rate:  $10^{-3}$  and (b) error rate:  $10^{-2}$

The probability of different faults in the same word line (32-bit word) were also analyzed and the results are listed in Table 1. It can be seen that a word line has a low number of faulty cells. The probability of two faults existing in the same word line is only 3.6% when the SRAM bit cell failure rate is 10<sup>-2</sup>. Accordingly, in the presence of a memory fault, SRAM may achieve self-recovery based on other bits in the same word line if meaningful bit-level data patterns exist.

| Number of faults<br>per word-line | SRAM failure<br>rate: 10 <sup>-3</sup> (0.001) | SRAM failure<br>rate: 10 <sup>-2</sup> (0.01) |

|-----------------------------------|------------------------------------------------|-----------------------------------------------|

| 0                                 | 96.8523477%                                    | 72.7279953%                                   |

| 1                                 | 3.0992274%                                     | 23.2812509%                                   |

| 2                                 | 0.0479198%                                     | 3.6012385%                                    |

| 3                                 | 0.0005023%                                     | 0.3611914%                                    |

| 4                                 | 0.0000028%                                     | 0.0267011%                                    |

| 5                                 | 0%                                             | 0.0015432%                                    |

| 6                                 | 0%                                             | 0.0000756%                                    |

| 7                                 | 0%                                             | 0.000004%                                     |

Table 1.

Fault probability in a 32-bit SRAM word (10<sup>9</sup> Monte Carlo simulations)

#### **Data Pattern Investigation for Self-Recovery**

This section presents the data-mining methodology to discover data patterns hidden in video data to enable reliable self-recovery. Specifically, a new two-dimensional (2D) data pattern approach is proposed to explore horizontal data-association and vertical data-correlation characteristics, thereby achieving optimal data patterns.

# **Rule Mining Enabled Horizontal Association**

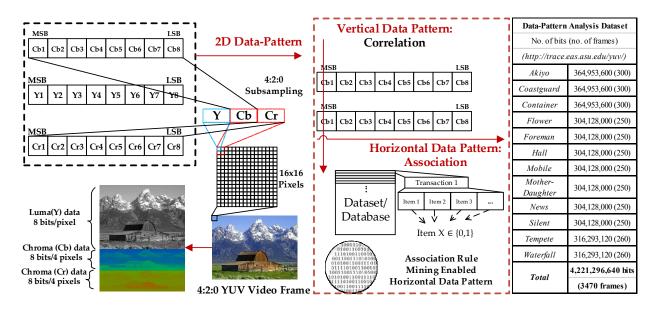

Today's mobile video frames are typically stored and processed in YUV format. The YUV format includes one luma (Y) component, which contains the brightness information of the image, and two chroma components, which contain the blue-difference (Cb) and red-difference (Cr) color information. Figure 3 shows a typical frame of video data stored in embedded memory using a  $352 \times 288$  resolution YUV 4:2:0 video as an example. As shown, each pixel has 8-bit luma data and 8-bit subsampled chroma data. Since video data is stored in on-chip memory as

binary bits, using an association data mining technique to identify horizontal bit-level data patterns is possible.

Figure 3. 2D data-pattern enabled self-correction and data pattern analysis dataset

Association rule mining was introduced in 1993 to discover relationships between different variables, called items, in a dataset or database [40]. A complete dataset is made up of many transactions where each transaction contains a set of items. Each item can be associated with a binary attribute, 0 or 1, that is used to distinguish if that item is present or not in its corresponding transaction. This type of data organization is illustrated in Figure 3. Each resulting rule, generated from the association rule mining process, is an implication of the form  $X \rightarrow Y$ , where X and Y are disjoint sets of, or individual items. Each rule is also accompanied by collected statistics from the dataset called support and confidence values. The support value for a set of items is the proportion of transactions in the dataset that contains such set of items. The confidence value for an association rule  $X \rightarrow Y$ , is the proportion of transactions that contain X which also contain Y, or the conditional probability  $P(Y \mid X)$ . To enable association data mining, 12 different video benchmarks were used to build a dataset [41, 42]. In total, the video data size used was 4,221,296,640 bits from 3470 video frames, as shown in Figure 3. Each video data bit was defined as an individual item and Weka [43] was used to perform the well-known Apriori association rule mining algorithm on the large video dataset. Table 2 lists the horizontal data patterns that were discovered for both luma and chroma data based on the video benchmarks.

| From 12 video benchmarks [41, 42]                                       |            |         | From 10,000 Youtube-8M videos [44] |                                                                         |            |         |                         |

|-------------------------------------------------------------------------|------------|---------|------------------------------------|-------------------------------------------------------------------------|------------|---------|-------------------------|

| Association<br>Rules                                                    | Confidence | Support | Confidence<br>× Support            | Association<br>Rules                                                    | Confidence | Support | Confidence<br>× Support |

| Y2=1 →<br><b>Y1=0</b>                                                   | 74.16%     | 57.15%  | 42.38%                             | $\begin{array}{c} Y2=1 \rightarrow \\ Y1=0 \end{array}$                 | 76.92%     | 50.57%  | 38.90%                  |

| Y3=1 →<br>Y1=0                                                          | 74.28%     | 52.23%  | 38.04%                             | $\begin{array}{c} Y3=1 \rightarrow \\ Y1=0 \end{array}$                 | 72.17%     | 51.52%  | 37.18%                  |

| $\begin{array}{c} Y2=0 \rightarrow \\ Y1=1 \end{array}$                 | 22.65%     | 42.85%  | 9.71%                              | $\begin{array}{c} Y2=0 \rightarrow \\ Y1=1 \end{array}$                 | 41.51%     | 71.18%  | 29.55%                  |

| Y1=1 →<br><b>Y2=0</b>                                                   | 39.85%     | 24.22%  | 9.65%                              | Y1=1 →<br><b>Y2=0</b>                                                   | 71.18%     | 41.51%  | 29.55%                  |

| Y1=1 →<br><b>Y3=0</b>                                                   | 42.86%     | 24.22%  | 10.38%                             | Y1=1 →<br><b>Y3=0</b>                                                   | 61.82%     | 37.01%  | 22.88%                  |

| $\begin{array}{c} \text{Cb2=0} \rightarrow \\ \text{Cb1=1} \end{array}$ | 94.75%     | 23.23%  | 22.01%                             | $\begin{array}{c} \text{Cb2=0} \rightarrow \\ \text{Cb1=1} \end{array}$ | 98.56%     | 46.53%  | 45.86%                  |

| $\begin{array}{c} \text{Cb2=1} \rightarrow \\ \text{Cb1=0} \end{array}$ | 97.56%     | 73.64%  | 71.84%                             | $\begin{array}{c} \text{Cb2=1} \rightarrow \\ \text{Cb1=0} \end{array}$ | 98.20%     | 52.65%  | 51.71%                  |

| $\begin{array}{c} \text{Cb1=0} \rightarrow \\ \text{Cb2=1} \end{array}$ | 98.28%     | 73.64%  | 72.38%                             | $Cb1=0 \rightarrow Cb2=1$                                               | 99.26%     | 52.69%  | 52.30%                  |

| $\begin{array}{c} \text{Cb1=1} \rightarrow \\ \text{Cb2=0} \end{array}$ | 92.65%     | 23.23%  | 21.52%                             | $Cb1=1 \rightarrow Cb2=0$                                               | 99.42%     | 46.56%  | 46.29%                  |

| $Cr2=1 \rightarrow Cr1=0$                                               | 97.51%     | 23.52%  | 22.93%                             | $Cr2=1 \rightarrow Cr1=0$                                               | 95.75%     | 33.66%  | 32.23%                  |

| $Cr2=0 \rightarrow Cr1=1$                                               | 100.00%    | 75.88%  | 75.88%                             | $Cr2=0 \rightarrow Cr1=1$                                               | 99.34%     | 65.38%  | 64.95%                  |

| $Cr1=1 \rightarrow Cr2=0$                                               | 99.22%     | 75.88%  | 75.29%                             | $Cr1=1 \rightarrow Cr2=0$                                               | 99.01%     | 65.43%  | 64.78%                  |

| $Cr1=0 \rightarrow Cr2=1$                                               | 99.99%     | 23.52%  | 23.51%                             | $Cr1=0 \rightarrow Cr2=1$                                               | 99.44%     | 33.71%  | 33.52%                  |

| $Cr1=1 \rightarrow Cr3=0$                                               | 97.80%     | 74.80%  | 73.16%                             | $Cr1=1 \rightarrow Cr3=0$                                               | 95.21%     | 62.61%  | 59.61%                  |

| $Cr1=0 \rightarrow Cr3=1$                                               | 92.23%     | 21.69%  | 20.01%                             | $Cr1=0 \rightarrow Cr3=1$                                               | 97.04%     | 32.62%  | 31.65%                  |

Table 2. Discovered association rules. Bit 1 (i.e. Y1, Cb1, Cr1) is the MSB

The video data used for determining optimal rules was further expanded to larger-scale and real video datasets beyond typical benchmarks in order to emulate the use of mobile devices in the environment of big data. Google's YouTube-8M dataset [44], one of the largest video databases to date, was used for this purpose. Specifically, 10,000 unique videos from the YouTube-8M dataset, with a total data size of 57.6 gigabytes, representing 500,000 individual frames, was analyzed using data mining methods. A script was written that would download the 10,000 videos from the approximately 7 million available URLs provided in the YouTube-8M dataset. After each video was downloaded, 50 contiguous frames were randomly selected from the video and were converted from the .mp4 file format to the raw .yuv format using the FFmpeg decoder [45] for data mining analysis. In order to support large-scale video data processing, these data mining calculations were performed on the Thunder cluster at the Center for Computationally Assisted Science and Technology (CCAST) at North Dakota State University, which consists of approximately 100 compute nodes with a theoretical peak performance of around 150 teraflops. As illustrated in Figure 3, each video data bit is defined as an individual item and the well-known Apriori algorithm was used on the video datasets to gather both confidence and support metric calculations. The average results obtained for the horizontal data patterns are also listed in Table 2. It can be seen that the association rules obtained from the video benchmarks are very general and also exist within the large-scale video dataset.

#### **Vertical Correlation**

Vertical data correlation characteristics of multimedia applications have been studied by many researchers [25, 46]. These works have shown that the MSBs of the video data have a strong correlation with neighboring pixels, and their switching probabilities are very low. Based on the video benchmarks, Table 3 lists the correlation probability of the MSBs (Y1, Cb1, Cr1) in

neighboring pixels is over 93%, while the LSBs have around 53% correlation probability in the worst case (i.e. Cb8). A similar trend in probabilities can be seen for the YouTube-8M videos. The MSBs in neighboring pixels have a very strong correlation (with probability over 90%), but LSBs display more of a random behavior and have little correlation with neighboring pixels.

|    | Correlation                                             | 1 probabiliti | es from 12 video | benchmarks |        |

|----|---------------------------------------------------------|---------------|------------------|------------|--------|

| Y1 | 96.72%                                                  | Cb1           | 93.79%           | Cr1        | 93.78% |

| Y2 | 93.22%                                                  | Cb2           | 92.87%           | Cr2        | 93.58% |

| Y3 | 87.79%                                                  | Cb3           | 90.77%           | Cr3        | 92.34% |

| Y4 | 80.86%                                                  | Cb4           | 85.45%           | Cr4        | 88.35% |

| Y5 | 73.97%                                                  | Cb5           | 77.95%           | Cr5        | 81.56% |

| Y6 | 67.42%                                                  | Cb6           | 69.30%           | Cr6        | 73.18% |

| Y7 | 61.78%                                                  | Cb7           | 59.99%           | Cr7        | 63.50% |

| Y8 | 58.52%                                                  | Cb8           | 53.25%           | Cr8        | 55.16% |

|    | Correlation probabilities from 10,000 YouTube-8M videos |               |                  |            |        |

| Y1 | 91.55%                                                  | Cb1           | 90.10%           | Crl        | 90.41% |

| Y2 | 84.64%                                                  | Cb2           | 89.87%           | Cr2        | 90.12% |

| Y3 | 77.23%                                                  | Cb3           | 88.67%           | Cr3        | 88.75% |

| Y4 | 68.87%                                                  | Cb4           | 84.86%           | Cr4        | 85.11% |

| Y5 | 60.05%                                                  | Cb5           | 78.11%           | Cr5        | 78.72% |

| Y6 | 51.49%                                                  | Cb6           | 68.87%           | Cr6        | 70.11% |

| Y7 | 44.14%                                                  | Cb7           | 58.81%           | Cr7        | 60.56% |

| Y8 | 38.78%                                                  | Cb8           | 50.84%           | Cr8        | 52.62% |

| Table 3. | Vertical correlation probabilities |

|----------|------------------------------------|

| 14010 5. | vertieur eenteration probabilities |

Power saving techniques involving the correlation have been used in previous works for bit prediction where no transistor switching results in power savings [9] and attempting to load the same value (i.e. reading continuous 0s or 1s) from memory bit cells in order to eliminate the cost of pre-charging if the correct value is read out from the previous bit-line read [25]. This work uses the correlation property of YUV data through the use of a novel bit correction technique that attempts to correct memory faults with high precision. By comparing the correlation percentages and the association rules that have been identified, the best combination of association rules and correlation between bits can be constructed for an optimal pattern for data self-recovery.

### **Optimal Data Patterns for Self-Recovery**

In order to select an optimal data pattern from association and correlation, the *Weighted Confidence*, based on the support and confidence of a particular rule, is defined as follows:

For example, the *Weighted Confidence* of the association rule  $\overline{Cr1} \rightarrow Cr2$  can be expressed as:

Weighted Confidence of  $(\overline{Cr1} \rightarrow Cr2)$

$$= Confidence(\overline{Cr1} = 0 \rightarrow Cr2 = 1) \times Support(\overline{Cr1} = 0 \rightarrow Cr2 = 1)$$

$$+ Confidence(Cr1 = 1 \rightarrow Cr2 = 0) \times Support(Cr1 = 1 \rightarrow Cr2 = 0)$$

$$= 0.9999 \times 0.2352 + 0.9922 \times 0.7588 = 0.9880$$

(2)

This parameter is then used to compare to the sum of the correlation values for 0 and 1 nonswitching, which is equal to the correlation. This is equivalent to the *Weight Confidence* calculation, but instead uses the individual bit value (0 or 1) correlation percentages and is calculated as follows:

$$Correlation = Confidence(Bit_{previous} = 0 \rightarrow Bit_{current} = 0) + Confidence(Bit_{previous} = 1 \rightarrow Bit_{current} = 1)$$

(3)

where *Bit*<sub>previous</sub> and *Bit*<sub>current</sub> represent the video data bits in the same position of two neighboring pixels.

As an example, the correlation of Cr2 can be calculated as follows:

*Correlation of Cr2* = *Confidence*( $Cr2_{previous} = 0 \rightarrow Cr2_{current} = 0$ ) +

$$Confidence(Cr2_{previous} = 1 \rightarrow Cr2_{current} = 1)$$

= 0.2091 + 0.726 = 0.935 (4)

Accordingly, the optimal bit-level data patterns with high prediction rate to enable selfrecovery were calculated. 25 videos from the YouTube-8M dataset, separate from the 10,000 videos used in the training dataset, were used to verify the correction prediction percentage shown in Table 4. These videos are obtained using the same method as previously used, but are unique from the previous 10,000 videos to ensure the rules that are employed work properly for correction. An analysis of the different portions of the image show that luma data is more random and has less association with other bits in the same pixel, and the optimal data patterns are all from correlation.

| Y<br>bits | Optimal<br>Data<br>Patterns             | Correct<br>Prediction | Cb<br>bits | Optimal<br>Data<br>Patterns                                                           | Correct<br>Prediction | Cr<br>bits | Optimal<br>Data<br>Patterns                                                                             | Correct<br>Prediction |

|-----------|-----------------------------------------|-----------------------|------------|---------------------------------------------------------------------------------------|-----------------------|------------|---------------------------------------------------------------------------------------------------------|-----------------------|

| Y1        | Correlation<br>(Y1 <sub>previous)</sub> | 91.53%                | Cb1        | $\begin{array}{c} \text{Association} \\ (\overline{Cb2} \rightarrow Cb1) \end{array}$ | 98.60%                | Cr1        | $\begin{array}{c} \text{Association} \\ (\overline{\textit{Cr2}} \rightarrow \textit{Cr1}) \end{array}$ | 96.72%                |

| Y2        | Correlation<br>(Y2 <sub>previous)</sub> | 82.67%                | Cb2        | $\begin{array}{c} \text{Association} \\ (\overline{Cb1} \rightarrow Cb2) \end{array}$ | 99.79%                | Cr2        | $\begin{array}{c} \text{Association} \\ (\overline{Cr1} \rightarrow Cr2) \end{array}$                   | 97.77%                |

| Y3        | Correlation<br>(Y3 <sub>previous)</sub> | 76.27%                | Cb3        | Correlation<br>(Cb3 <sub>previous)</sub>                                              | 88.46%                | Cr3        | $\begin{array}{c} \text{Association} \\ (\overline{Cr1} \rightarrow Cr3) \end{array}$                   | 93.86%                |

| Y4        | Correlation<br>(Y4 <sub>previous)</sub> | 67.64%                | Cb4        | Correlation<br>(Cb4 <sub>previous)</sub>                                              | 84.31%                | Cr4        | Correlation<br>(Cr4 <sub>previous)</sub>                                                                | 83.64%                |

| Y5        | Correlation<br>(Y5 <sub>previous)</sub> | 59.24%                | Cb5        | Correlation<br>(Cb5 <sub>previous)</sub>                                              | 78.53%                | Cr5        | Correlation<br>(Cr5 <sub>previous)</sub>                                                                | 78.35%                |

| Y6        | Correlation<br>(Y6 <sub>previous)</sub> | 51.75%                | Cb6        | Correlation<br>(Cb6 <sub>previous)</sub>                                              | 69.40%                | Cr6        | Correlation<br>(Cr6 <sub>previous)</sub>                                                                | 68.80%                |

| Y7        | Correlation<br>(Y7 <sub>previous)</sub> | 44.47%                | Cb7        | Correlation<br>(Cb7 <sub>previous)</sub>                                              | 59.40%                | Cr7        | Correlation<br>(Cr7 <sub>previous)</sub>                                                                | 59.73%                |

| Y8        | Correlation<br>(Y8 <sub>previous)</sub> | 38.41%                | Cb8        | Correlation<br>(Cb8 <sub>previous)</sub>                                              | 51.13%                | Cr8        | Correlation<br>(Cr8 <sub>previous)</sub>                                                                | 52.96%                |

Table 4.Optimal data patterns from 25 YouTube-8M videos

#### **Recovery Failure Caused by Double Faults in Data Patterns**

Since the discovered optimal data patterns used for self-recovery exist between two bits in the same word line, it may cause recovery failures if both of the two bits in a pattern fail simultaneously. Table 5 lists the recovery failure rate. It shows that DPSR has good reliability with extremely low self-recovery rates (less than 0.2%). This is due to the fact that there is low probability of having multiple faults in the same word line, as discussed earlier.

Table 5.DPSR recovery failure rates

| Double Word Line Faults | SRAM P <sub>fail</sub> : 10 <sup>-3</sup> (0.001) | SRAM P <sub>fail</sub> : 10 <sup>-2</sup> (0.01) |  |

|-------------------------|---------------------------------------------------|--------------------------------------------------|--|

| Correlation Faults      | 0.0010899%                                        | 0.1077362%                                       |  |

| Association Faults      | 0.0005957%                                        | 0.0587964%                                       |  |

| DPSR Recovery Failure   | 0.0016856%                                        | 0.1665326%                                       |  |

# **DPSR Hardware Implementation**

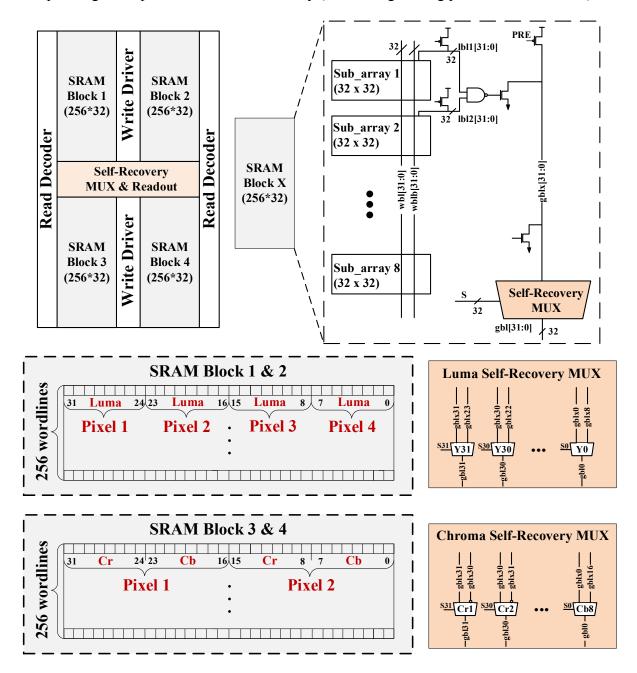

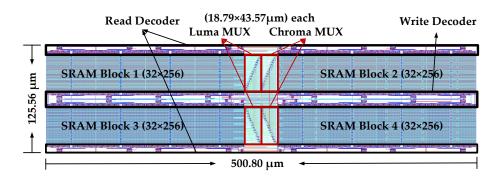

Utilizing the obtained optimal bit-level data patterns, a simple but efficient DPSR hardware design with low implementation cost is presented. Figure 4 shows the array architecture of the proposed DPSR SRAM, where the total array size is 32 kbits and there are four blocks with 256 words  $\times$  32 bits. In the design, both luma data and chroma data will be stored in the same SRAM but in different blocks. Block 1 and block 2 will be used to store the luma data and each word line will store the luma data of 4 pixels. Block 3 and block 4 will be used to store the chroma data and each word line will store the chroma data of 2 pixels.

Regarding the luma data stored in blocks 1 and 2, based on the optimal luma patterns obtained previously, vertical correlation rules (i.e. luma data of the previous pixel) will be used for recovering the data of the current pixel. Since SRAM read operations are row-wise, reading two physical rows will cause a considerable performance penalty. Accordingly, the vertical

correlation based luma self-recovery is adapted to a hardware-friendly design scheme. Each word line stores the luma data of 4 pixels and uses its neighboring pixel in the same row for data correction in the current pixel. As an example, if a data bit in pixel 1 has a failure (see Figure 4), the corresponding bit in pixel 2 is used for recovery; if a bit in pixel 4 has a failure, the corresponding bit in pixel 3 is used for recovery (i.e the neighboring pixel in the same row).

Figure 4. Proposed DPSR with data self-recovery ability

To verify the DPSR design will maximize the correct bit predictions, calculations were performed for the correct prediction percentage for predicting each bit using both the previous and next pixel's corresponding bit. These calculations showed that they were approximately equal values, with both having ~79.4% average correct prediction for all luma bits based on calculations from all samples in the training and verification testing video benchmarks [41, 42].

Chroma data self-recovery is implemented in SRAM block 3 and block 4 using the optimal chroma patterns. As shown in Figure 4, each word line stores two pixels of chroma data with both Cr and Cb. Both vertical correlation rules and horizontal data pattern rules are used for the chroma data self-recovery (see Table 4). Similarly, for vertical correction based recovery rules, the neighboring pixel stored in the same row for data corrections are used to avoid a penalty to performance. For example, if Cb1 in pixel 1 has a failure (see Figure 4), the inverted value of Cb2 in the same pixel will be used for recovery. If Cr4 in pixel 1 fails, Cr4 in pixel 2, which is stored in the same row, will be used for recovery.

As shown in Figure 4, a hierarchical RBL scheme (i.e. local RBL and global RBL) is applied to reduce the access time of the memory. The self-recovery logic of DPSR can be simply implemented by connecting MUXs to RBLs of the conventional SRAM design. Each global bitline (i.e. gbl in Figure 4) is connected to a MUX which is controlled by the received fault positions. If a fault is indicated, self-recovery is enabled by selecting the data pattern. The fault position information is used as the select signal of the MUX in order to control which bit value will be output. Similar to other existing fault position aware mitigation techniques, DPSR receives pre-determined locations of the faulty bits in the SRAM array, which is usually executed during post fabrication testing or Power-On Self-Test (POST) [13, 47, 48]. This testing process can also be used to track temporal degradation caused by memory failures such as the

aging effect. The evaluation results in the following sections show that the DPSR SRAM design also achieves smaller silicon area overhead, while delivering good output quality at near threshold voltage.

# **Evaluation Methodology and Results**

To evaluate the effectiveness of the proposed technique, a 32kb SRAM was implemented using a high-performance 45nm FreePDK CMOS process [49] to meet the multi-megahertz performance requirement of today's mobile video decoders.

# Performance

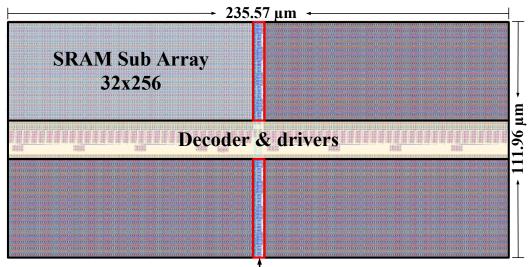

The performance of the proposed DPSR design was first evaluated. Due to the added MUXs, the read access time of DPSR increases from 0.27ns to 0.31ns, which is fast enough to deliver high-quality video formats including 4K and 8K ultra high-definition applications [50]. **Layout**

As discussed before, embedded SRAMs typically occupy a large portion of silicon area within a video chip, and therefore the cost of the embedded SRAM is an important design concern. Figure 5 shows the layout of DPSR. Each added self-recovery logic MUX occupies an area of  $18.79\mu m \times 43.47\mu m$ , resulting in 7.94% area overhead. It should also be noted that, the self-recovery logic is added to the RBLs and increasing the number of words in a memory is beneficial in reducing the overall area overhead.

Figure 5. DPSR layout design

# **Power Efficiency**

In order to evaluate the power efficiency of the proposed technique, the power consumption of the memory is modeled as follows:

$$P_{Dynamic} = \frac{\sum_{j=0}^{31} \sum_{i=0,1} \left[ P_j(i) \cdot (R(i) + W(i)) \right]}{2}$$

(5)

$$P_{Leak} = \sum_{d=0}^{1023} \sum_{j=0}^{31} \sum_{i=0,1} L_j(i)$$

(6)

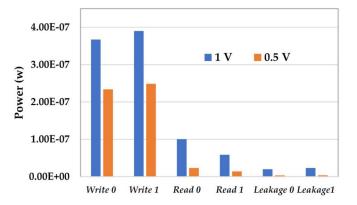

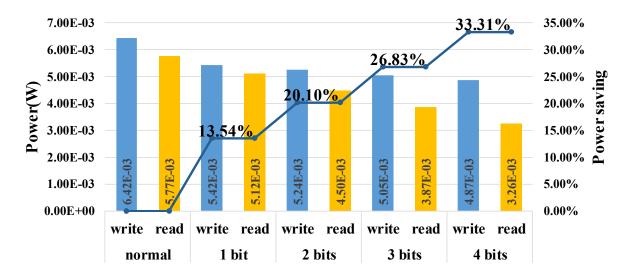

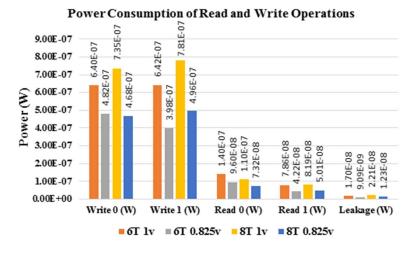

where  $P_{Dynamic}$  and  $P_{Leak}$  are the dynamic and leakage power consumption, respectively. *i* is the value stored in SRAM, *j* is the bit number in a word, which is from 0 to 31.  $P_j(i)$  is the probability of a data bit *j* to be 0 or 1, which is extracted from various video benchmarks. R(i), W(i), and L(i) are the read power, write power, and leakage power consumption for a single SRAM bit cell, respectively, that stores a particular data bit value *i*. Figure 6 compares the power consumption in different memory operations. As expected, all power components decrease as the voltage scales from 1.0V to 0.5V. It should be noted that the power consumption overhead caused by the self-correction logic in the proposed technique is negligible as compared to the power reduction enabled by reducing voltage to near-threshold voltage, since the dynamic and leakage power consumption scale at a quadratic and linear rate with the voltage, respectively.

Figure 6. Power consumption of different memory operations

The proposed memory at 0.5V consumes 219µW dynamic power and 193µW leakage power. As compared to the conventional memory design at 1.0V, the proposed design has 81.52% dynamic power savings and 82.45% leakage power savings.

### Video Output Quality Analysis

Different from the video benchmark datasets used previously for this design, a new video benchmark dataset is organized for verification: 3 videos from [41] and 5 videos from [42]. To evaluate the video quality, the well-known PSNR metric is adopted, which is defined as [25]:

$$PSNR = 10 \cdot log_{10} \left(\frac{255^2}{MSE}\right) \tag{7}$$

where MSE is the mean squared error between the original videos (*Org*) and the degraded videos (*Deg*), expressed as:

$$MSE = \frac{1}{mn} \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} [Org(i,j) - Deg(i,j)]^2$$

(8)

Researchers have shown that a PSNR of 30dB or higher for a video are considered to be acceptable [13]. Table 6 compares the PSNR values using different techniques with a  $P_{fail}$  (i.e. the failure probability) of  $10^{-2}$  for minimum-sized SRAM designs and  $10^{-3}$  for upsized SRAM with 58% area overhead [37]. In addition to video benchmarks, 10 YouTube-8M videos from the 25 videos used for verification earlier in Table 4 (separate from the 10,000 videos used in the training dataset) are used for calculating the video metrics presented. Due to the limited space, Figure 7 shows six video output images with a memory failure rate of  $10^{-2}$  when failures are injected. It can be seen that DPSR has good recovery precision and can deliver good video quality with a PSNR over 35dB, even for minimum sized SRAM. Accordingly, DPSR achieves good video output quality at near-threshold voltages.

| Video              | Original Video             | Conventional ( $P_{fail} = 0.01$ ) | DPSR ( $P_{fail} = 0.01$ ) | Shift ( <i>P<sub>fail</sub></i> = 0.01) [23] |

|--------------------|----------------------------|------------------------------------|----------------------------|----------------------------------------------|

| city               | PSNR: 36.8039 SSIM: 0.9306 | PSNR: 24.5045 SSIM: 0.5739         | PSNR: 33.7729 SSIM: 0.9095 | PSNR: 36.7801 SSIM: 0.9290                   |

| crew               |                            |                                    |                            |                                              |

| football           |                            | PSNR: 24.5212 SSIM: 0.5142         |                            |                                              |

| Concert            | PSNR: 36.5037 SSIM: 0.9163 | PSNR: 24.4878 SSIM: 0.5542         | PSNR: 34.6731 SSIM: 0.9046 | PSNR: 36.4816 SSIM: 0.9148                   |

| Game               |                            | PSNR: 24.7593 SSIM: 0.5834         | PSNR: 39.6992 SSIM: 0.9839 | PSNR: 59.4008 SSIM: 0.9987                   |

| Electric<br>Guitar |                            | <i>PSNR</i> : 24.7528 SSIM: 0.5580 | PSNR: 42.5844 SSIM: 0.9884 | PSNR: 59.4008 SSIM: 0.9985                   |

Figure 7. Video output using different video storage techniques

The PSNR metric has been used extensively to describe video output quality in a quantitative way, but recent efforts to capture the true human perception show that it may not accurately describe the actual video quality a human perceives [51]. This is due to the fact that PSNR is based on the summation of error for every pixel's luminance and chrominance component values, and this alone is not necessarily a good estimate to the user's perception of the video. Analyzing the video quality using SSIM is a method that is more aware of the user's perception since it includes calculations for luminance, contrast, and structural changes in the video. The general form of the SSIM equation is defined as [51]:

$$SSIM(x,y) = [l(x,y)]^{\alpha} \cdot [c(x,y)]^{\beta} \cdot [s(x,y)]^{\gamma} = \frac{(2\mu_x\mu_y + c_1)(2\sigma_{xy} + c_2)}{(\mu_x^2 + \mu_y^2 + c_1)(\sigma_x^2 + \sigma_y^2 + c_2)}$$

(9)

where l(x,y), the luminance comparison, is a function of the mean intensities,  $\mu_x$  and  $\mu_y$ , c(x,y), the contrast comparison is a function of the standard deviations,  $\sigma_x$  and  $\sigma_y$ , and s(x,y), the structural comparison, is a function of the correlation between x and y, or  $\sigma_{xy}$ . Setting the values of  $\alpha = \beta = \gamma = 1$  in the original equation results in the second equation.  $C_1$  ( $C_2$ ) is a constant that is included to avoid instabilities when the sum of the means (standard deviations) squared is equal to the values near zero. The value of the SSIM is in the range 0 to 1. As the value of SSIM(x,y) gets closer to 1, the quality of the video y more closely matches the quality of video x. For our testing purposes, video x is the raw, uncompressed YUV video, before the decoding process, and video y is the post decoded YUV video that may or may not have other bit shifting or correction changes performed on it.

The results of these SSIM calculations for conventional and DPSR are listed in Table 7. The video output quality of the proposed DPSR method has a significant increase in SSIM over the no failure, conventional memory at scaled voltages.

| Dataset    | Videos          | conventional<br>( <i>P<sub>fail</sub></i> = 0.001) | $DPSR \\ (P_{fail} = 0.001)$ | conventional<br>( <i>P<sub>fail</sub></i> = 0.01) | $DPSR \\ (P_{fail} = 0.01)$ | <b>Ref.</b> [23]<br>( <i>P<sub>fail</sub></i> =0.001) | <b>Ref.</b> [23] ( <i>P<sub>fail</sub></i> = 0.01) |

|------------|-----------------|----------------------------------------------------|------------------------------|---------------------------------------------------|-----------------------------|-------------------------------------------------------|----------------------------------------------------|

|            | akiyo           | 33.762219                                          | 40.641272                    | 24.676287                                         | 36.639433                   | 41.248639                                             | 41.185088                                          |

|            | bus             | 32.102969                                          | 35.405863                    | 24.410622                                         | 33.373556                   | 35.706569                                             | 35.689801                                          |

|            | city            | 32.550805                                          | 36.360825                    | 24.426879                                         | 33.772872                   | 36.801408                                             | 36.780126                                          |

| Video      | coastguard      | 32.090258                                          | 35.489524                    | 24.426879                                         | 34.265358                   | 35.667736                                             | 35.650842                                          |

| Benchmarks | crew            | 32.680147                                          | 36.928508                    | 24.521212                                         | 35.563219                   | 37.142670                                             | 37.119667                                          |

| 201101111  | football        | 32.439115                                          | 36.255904                    | 24.487795                                         | 34.673071                   | 36.501345                                             | 36.481558                                          |

|            | foreman         | 32.71063                                           | 36.878115                    | 24.529656                                         | 35.022773                   | 37.211848                                             | 37.188112                                          |

|            | sign_irene      | 33.253495                                          | 38.980559                    | 24.590776                                         | 36.573802                   | 38.976183                                             | 38.940649                                          |

|            | Running         | 34.843802                                          | 47.751093                    | 27.751663                                         | 37.896356                   | 69.178843                                             | 59.400849                                          |

|            | Concert         | 34.843123                                          | 50.617823                    | 24.745933                                         | 39.835772                   | 69.178843                                             | 59.400849                                          |

|            | Music Video     | 34.842942                                          | 48.993861                    | 24.765553                                         | 37.908828                   | 69.178843                                             | 59.400849                                          |

|            | Festival        | 34.843240                                          | 45.838237                    | 24.892104                                         | 35.958557                   | 69.178843                                             | 59.400849                                          |

| YouTube 8M | Game            | 34.843259                                          | 49.286247                    | 24.759353                                         | 39.699233                   | 69.178843                                             | 59.400849                                          |

| Dataset    | Electric Guitar | 34.843014                                          | 51.566521                    | 24.752845                                         | 42.584377                   | 69.178843                                             | 59.400849                                          |

|            | Snow            | 34.844445                                          | 50.725480                    | 24.761392                                         | 40.861991                   | 69.178843                                             | 59.400849                                          |

|            | Flute           | 34.842227                                          | 53.769387                    | 24.755972                                         | 44.158630                   | 69.178843                                             | 59.400849                                          |

|            | Vehicle         | 34.843032                                          | 50.015065                    | 24.741031                                         | 42.251862                   | 69.178843                                             | 59.400849                                          |

|            | Planet          | 34.843295                                          | 53.306924                    | 24.760113                                         | 44.022668                   | 69.178843                                             | 59.400849                                          |

Table 6. Video PSNR metric comparison

Table 7. Video SSIM metric comparison

| Dataset    | Videos          | Conventional $(P_{fail} = 0.001)$ | $DPSR$ $(P_{fail} = 0.001)$ | conventional $(P_{fail} = 0.01)$ | $DPSR$ $(P_{fail} = 0.01)$ | Ref. [13]<br>( <i>P</i> <sub>fail</sub> =0.001) | Ref. [13]<br>( <i>P</i> <sub>fail</sub> = 0.01) |

|------------|-----------------|-----------------------------------|-----------------------------|----------------------------------|----------------------------|-------------------------------------------------|-------------------------------------------------|

|            | akiyo           | 0.895568                          | 0.960037                    | 0.524455                         | 0.943273                   | 0.961509                                        | 0.959164                                        |

|            | bus             | 0.884369                          | 0.928646                    | 0.615363                         | 0.917352                   | 0.929814                                        | 0.928514                                        |

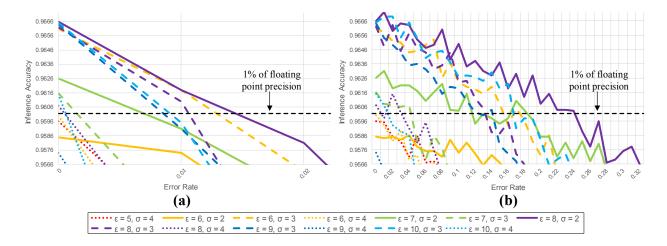

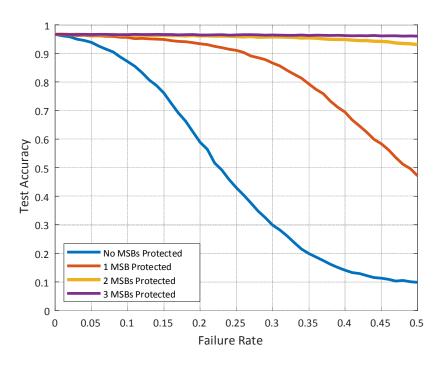

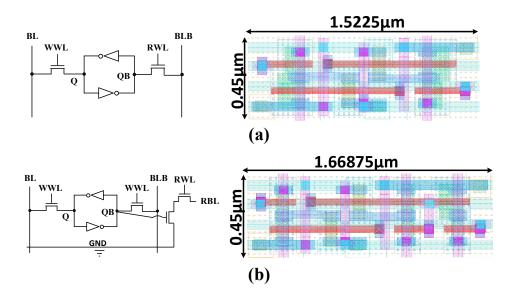

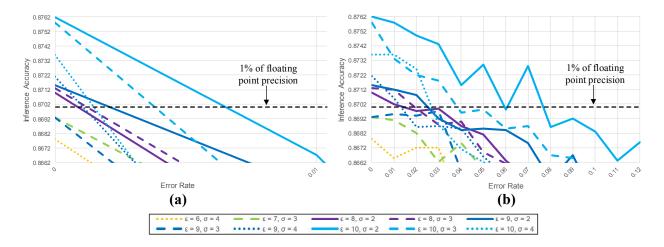

|            | city            | 0.879284                          | 0.928319                    | 0.573905                         | 0.909453                   | 0.93045                                         | 0.929045                                        |