University of Massachusetts Amherst ScholarWorks@UMass Amherst

**Doctoral Dissertations**

**Dissertations and Theses**

July 2020

# Formal Verification of Divider and Square-root Arithmetic Circuits Using Computer Algebra Methods

Atif Yasin

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Digital Circuits Commons, Hardware Systems Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Yasin, Atif, "Formal Verification of Divider and Square-root Arithmetic Circuits Using Computer Algebra Methods" (2020). *Doctoral Dissertations*. 1910. https://scholarworks.umass.edu/dissertations\_2/1910

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

## FORMAL VERIFICATION OF DIVIDER AND SQUARE-ROOT ARITHMETIC CIRCUITS USING COMPUTER ALGEBRA METHODS

A Dissertation Presented

by

ATIF YASIN

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

May 2020

Electrical and Computer Engineering

© Copyright by Atif Yasin 2020 All Rights Reserved

## FORMAL VERIFICATION OF DIVIDER AND SQUARE-ROOT ARITHMETIC CIRCUITS USING COMPUTER ALGEBRA METHODS

A Dissertation Presented

by

ATIF YASIN

Approved as to style and content by:

Maciej Ciesielski, Chair

Wayne Burleson, Member

Daniel Holcomb, Member

Namrata Shekhar, Member

Christopher V. Hollot, Department Head Electrical and Computer Engineering

## ABSTRACT

## FORMAL VERIFICATION OF DIVIDER AND SQUARE-ROOT ARITHMETIC CIRCUITS USING COMPUTER ALGEBRA METHODS

MAY 2020

#### ATIF YASIN

# B.S., LAHORE UNIVERSITY OF MANAGEMENT SCIENCES M.S., UTAH STATE UNIVERSITY Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Maciej Ciesielski

A considerable progress has been made in recent years in verification of arithmetic circuits such as multipliers, fused multiply-adders, multiply-accumulate, and other components of arithmetic datapaths, both in integer and finite field domain. However, the verification of hardware dividers and square-root functions have received only a limited attention from the verification community, with a notable exception for theorem provers and other inductive, non-automated systems. Division, square root, and transcendental functions are all tied to the basic Intel architecture and proving correctness of such algorithms is of grave importance. Although belonging to the same iterative-subtract class of architectures, they widely differ from each other. IEEE floating point standard specifies square-rooting and division as basic arithmetic operation alongside the usual three basic operations. The difficulty of formally verifying hardware implementation of a divider/square-root can be attributed mostly to the modeling of its characteristic function and the high memory complexity required by standard algebraic approach.

The work proposed in this thesis discusses formal verification of combinational divider and square-root circuits. Specifically, it addresses the problem of formally verifying gate-level circuits using an algebraic model. In contrast to standard verification approaches using satisfiability (SAT) or equivalence checking, the proposed method verifies whether the gate-level circuit actually performs the intended function or not, without a need for a reference design. Firstly, we present a verification methodology for a constant divider, where the divisor value is fixed to a constant integer. Albeit simpler case of verification, it provides us with the basic understanding of verification techniques and the underlying issues applicable to divider verification. Secondly, a layered verification approach is proposed for the verification of generic array dividers. Finally, the work proposed in this thesis will further analyze the divider and square-root circuits and aim to curb the memory explosion issue experienced by computer algebra based verification methods in order to successfully verify large bitwidth divider-type arithmetic circuits. More specifically, a novel idea of "hardware rewriting" is introduced, which avoids the high memory complexity. The mentioned technique verifies a 256-bit gate-level square-root circuit with around 260,000 gates in just under 18 minutes and 127-bit gate-level divider circuit in under one minute.

## TABLE OF CONTENTS

| ABSTRACT        | iv           |

|-----------------|--------------|

| LIST OF TABLES  | ix           |

| LIST OF FIGURES | $\mathbf{x}$ |

## CHAPTER

| 1. | INT                             | NTRODUCTION 1                                                                                                                                                   |  |

|----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | $1.1 \\ 1.2$                    | VLSI Design Flow                                                                                                                                                |  |

|    |                                 | 1.2.1Canonical Diagrams31.2.2SAT: Satisfiability Problem41.2.3Theorem Proving5                                                                                  |  |

| 2. | TE                              | CHNICAL BACKGROUND 6                                                                                                                                            |  |

|    | 2.1                             | Fields, Polynomials, Ideals and Varieties                                                                                                                       |  |

|    |                                 | 2.1.1       Fields                                                                                                                                              |  |

|    | $2.2 \\ 2.3 \\ 2.4$             | Ideal Membership Test.9Gröbner basis.11Related Work.12                                                                                                          |  |

| 3. | AL                              | GEBRAIC REWRITING AND DIVIDER MODEL 16                                                                                                                          |  |

|    | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Algebraic Model of Electronic Circuits16Gröbner Basis Polynomial Reduction19Algebraic Rewriting23AIG Rewriting26Comparison between GB Reduction and Rewriting28 |  |

| 4. |              |                                                                          | VERIFICATION OF INTEGER DIVIDERS:                                                                                                              |

|----|--------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 4.1<br>4.2   | Introd                                                                   | luction                                                                                                                                        |

|    |              | 4.2.1                                                                    | Divider Circuit Implementation                                                                                                                 |

|    | 4.3          | Verific                                                                  | eation                                                                                                                                         |

|    |              | $\begin{array}{c} 4.3.1 \\ 4.3.2 \\ 4.3.3 \\ 4.3.4 \\ 4.3.5 \end{array}$ | Verification of the Constant Divider                                                                                                           |

|    | 4.4          | Result                                                                   | ts and Analysis                                                                                                                                |

|    |              | $\begin{array}{c} 4.4.1 \\ 4.4.2 \\ 4.4.3 \\ 4.4.4 \\ 4.4.5 \end{array}$ | Modular Architecture44Flat Unroll Architecture45The Restoring Constant Divider45Simulation Based Verification47The Restoring Generic Divider48 |

| 5. |              |                                                                          | VERIFICATION OF HARDWARE DIVIDERS<br>G LAYERED VERIFICATION STRATEGY 50                                                                        |

|    | $5.1 \\ 5.2$ |                                                                          | luction                                                                                                                                        |

|    |              | 5.2.1<br>5.2.2<br>5.2.3                                                  | Functional Verification Model51Fractional vs. Integer Divider52Layered Rewriting55                                                             |

|    | $5.3 \\ 5.4$ |                                                                          | ts                                                                                                                                             |

| G  |              |                                                                          |                                                                                                                                                |

| 0. | -            |                                                                          | -ROOT AND DIVIDER CIRCUIT VERIFICATION<br>G HARDWARE REWRITING                                                                                 |

| υ. | -            | U <b>SINC</b><br>Chara                                                   |                                                                                                                                                |

| υ. | 6.1          | U <b>SINC</b><br>Chara                                                   | G HARDWARE REWRITING    61      acteristic Function of Square-Root    61                                                                       |

|    |     | $6.4.1 \\ 6.4.2$ | Remainder Generation    6      Hardware Rewriting    7                                                                                                          |    |

|----|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | 6.5 | Divide           | er Verification                                                                                                                                                 | 72 |

|    |     | 6.5.1            | Verification Model: SAT-based vs Algebraic Rewriting                                                                                                            |    |

|    |     | 6.5.2            | Layered Algebraic Rewriting                                                                                                                                     |    |

|    |     | 6.5.3            | Layered Hardware Rewriting $\dots$ 7                                                                                                                            |    |

|    |     | $6.5.4 \\ 6.5.5$ | Verifying Output Constraint, $R < D$                                                                                                                            |    |

|    |     | 6.5.6            | Constraint Verification for Layered Divider $\dots \dots \dots$ |    |

|    |     | 0.0.0            |                                                                                                                                                                 | )1 |

|    | 6.6 | Result           | s٤                                                                                                                                                              | 32 |

|    |     | 6.6.1            | SQRT Circuits                                                                                                                                                   | 32 |

|    |     | 6.6.2            | Divider Circuits                                                                                                                                                | 34 |

| 7. | SUN | MMAF             | RY, CONTRIBUTION, AND PUBLICATIONS 8                                                                                                                            | 37 |

|    | 7.1 | Contri           | bution                                                                                                                                                          | 37 |

|    |     | 7.1.1            | Future Directions                                                                                                                                               | 38 |

|    | 7.2 | Public           | ations                                                                                                                                                          | 39 |

|    |     |                  |                                                                                                                                                                 |    |

| BI | BLI | OGRA             | PHY                                                                                                                                                             | )1 |

## LIST OF TABLES

## Table

## Page

| 4.1 | <ul> <li>Verification results for the divide-by-constant divider circuit using our technique for: (1) Modular 1-bit block, 2-bit block; and 2) 4-bit block architecture with a 32-bit dividend X (Figure 4.2).</li> <li>Time-out TO = 1200 s, Memory-out MO = 16 GB44</li> </ul> |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2 | Verification results for the divide-by-constant divider circuit using our technique for Flat-Unroll architecture with a 9-bit dividend $X$ (Figure 4.2). Time-out TO = 1200 s, Memory-out MO = 16 GB;                                                                            |

| 4.3 | Verification results for the divide-by-constant divider circuit using our technique for Restoring Constant Divider with a 22-bit dividend $X$ . TO = 1200s, MO = 24GB. SF = Segmentation Fault                                                                                   |

| 4.4 | Verification run time for the Restoring generic Divider. #Bits show<br>the bit-width of dividend. SF = segmentation fault49                                                                                                                                                      |

| 5.1 | Verification results for a bug-free restoring divider. #Bits = Dividend<br>bit-width. MO = Memory-out 20 GB, TO = Time-out 3600 s59                                                                                                                                              |

| 6.1 | Square Root verification results using standard-Style rewriting67                                                                                                                                                                                                                |

| 6.2 | Verification run times for SQRT circuits. #Bits = Radicand<br>bit-width; MO = Memory-out 20GB; TO = Time-out 3600s82                                                                                                                                                             |

| 6.3 | Verification of a bug-free restoring divider. MO = Memory-out 20<br>GB, TO = Time-out 3600 s                                                                                                                                                                                     |

| 6.4 | Detailed analysis of verification of a bug-free restoring divider using<br>Hardware-based rewriting for Full vs. Layered strategies. MO =<br>Memory-out 20 GB, TO = Time-out 3600 s85                                                                                            |

## LIST OF FIGURES

| Figure | Page                                                                                                                                                                                                    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1    | VLSI design flow1                                                                                                                                                                                       |

| 3.1    | Gate-level arithmetic circuit (Full Adder)                                                                                                                                                              |

| 3.2    | Half-Adder gate-level arithmetic circuit                                                                                                                                                                |

| 3.3    | AIG rewriting of a full adder circuit from Figure 3.1                                                                                                                                                   |

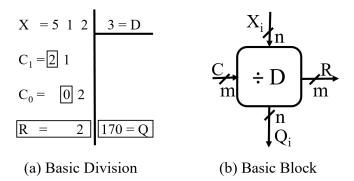

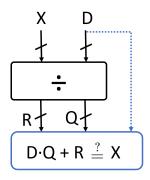

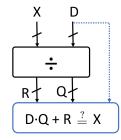

| 4.1    | Pencil and Paper division operation and the basic divider block                                                                                                                                         |

| 4.2    | Generic divider block for X divided by const. $d = 3 \dots 34$                                                                                                                                          |

| 4.3    | Divide-by-3 block specification tables                                                                                                                                                                  |

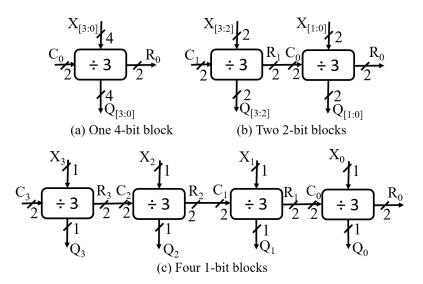

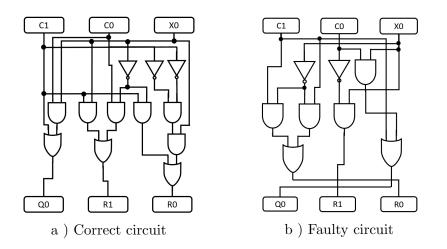

| 4.4    | Gate level implementation of a single-block, one-bit architecture of a $X/3$ divider. Output signature $Sig_{out} = 3Q_0 + 2R_1 + R_0$ ; the expected input signature is $Sig_{in} = 4C_1 + 2C_0 + X_0$ |

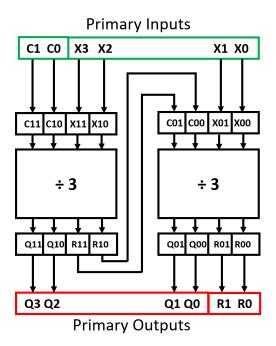

| 4.5    | Division of a 4-bit divide-by-3 in a two-bit block divider circuit. Rewriting is applied in the opposite direction to the flow of the data                                                              |

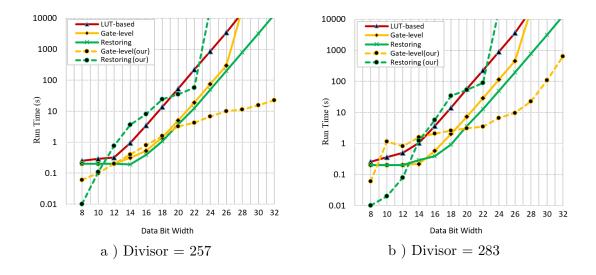

| 4.6    | Exhaustive simulation run time for divisors D=257 and D=283 for<br>different implementations, as a function of the dividend bit-width.<br>Dotted Lines show equivalent for our rewriting technique      |

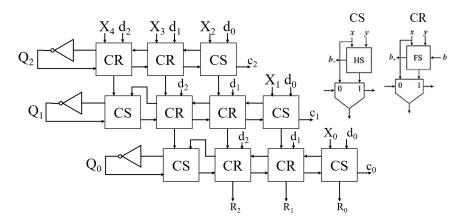

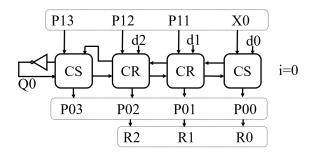

| 4.7    | Restoring Generic 3-bit Divider [40]                                                                                                                                                                    |

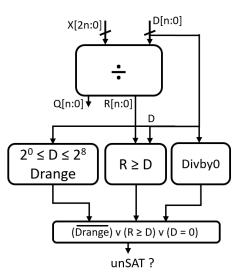

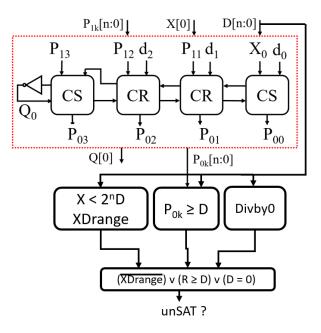

| 5.1    | Functional verification model of the divider                                                                                                                                                            |

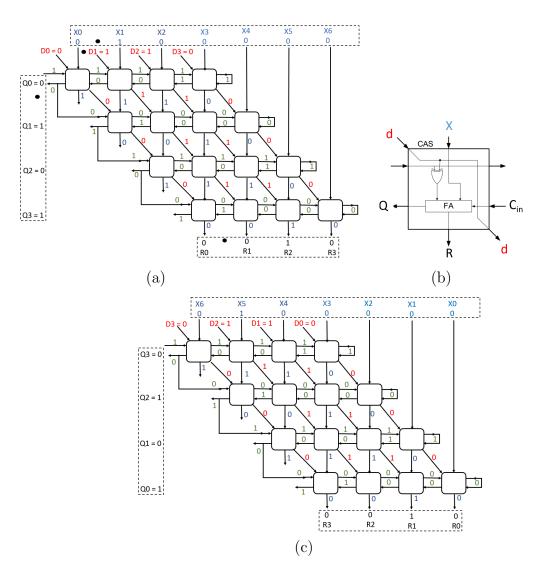

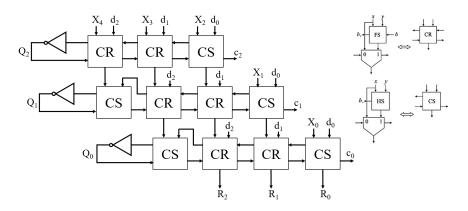

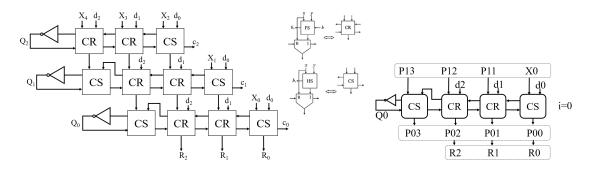

| 5.2    | Nonrestoring 7-4 divider $(n = 3)$ : a) Fractional divider; b) Controlled Add/Subtract (CAS) block; c) Integer divider                                                                                  |

| 5.3    | Single layer of the restoring divider used in rewriting                                                                                                                                                 |

| 5.4    | Restoring integer divider [40]                                                                                                                                                                          |

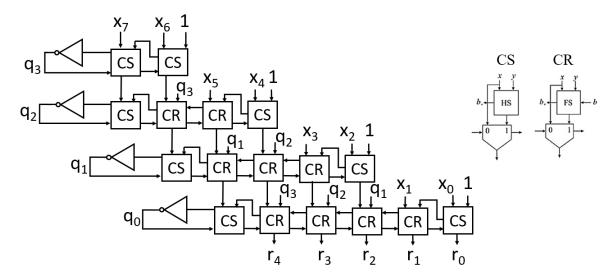

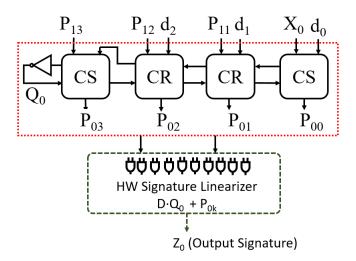

| 6.1  | A restoring SQRT circuit with a 7-bit radicand, 4-bit quotient, and a 5-bit remainder                       |

|------|-------------------------------------------------------------------------------------------------------------|

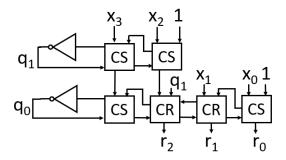

| 6.2  | A restoring SQRT circuit with a 4-bit radicand, 2-bit quotient, and a 3-bit remainder                       |

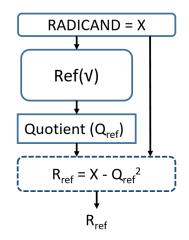

| 6.3  | Residue generation using a Reference Design                                                                 |

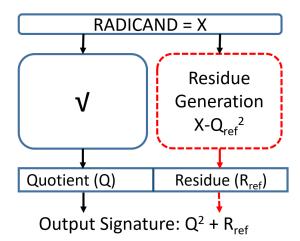

| 6.4  | Conceptual standard rewriting                                                                               |

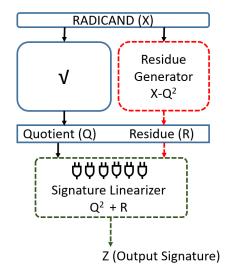

| 6.5  | Hardware rewriting                                                                                          |

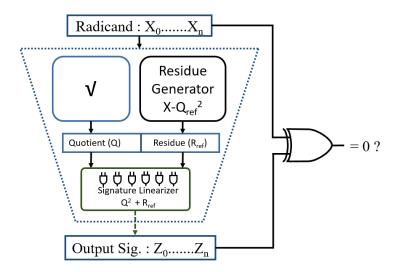

| 6.6  | Final verification using SAT: check if $\forall i, X_i = Z_i$                                               |

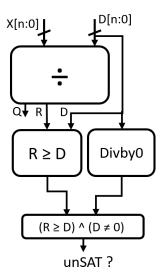

| 6.7  | Divider verification model                                                                                  |

| 6.8  | Restoring integer: divider [40]; a) Layered architecture b) Single layer<br>used in rewriting [48]74        |

| 6.9  | Layered hardware rewriting for dividers                                                                     |

| 6.10 | Verifying condition $R < D$ of a complete divider                                                           |

| 6.11 | Verifying condition $R < D$ of a complete divider using case-splitting<br>strategy for a given range of $D$ |

| 6.12 | Verifying condition $R < D$ for the layered verification strategy, layer<br>0, using case-splitting         |

## CHAPTER 1

## INTRODUCTION

## 1.1 VLSI Design Flow

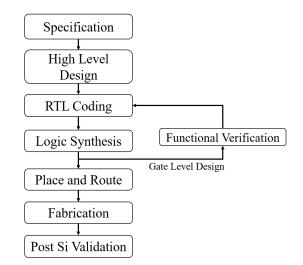

What is hardware verification and more specifically, why is it important? Before we answer these questions, we need to understand the basic design flow of Very Large Scale Integrated circuits. Figure 1.1 shows the VLSI design flow, with the functional verification stage shown.

Figure 1.1: VLSI design flow

The design flow begins with an initial system-level specification written using a programming language, which can either be software (C, C++) or hardware language (Verilog, VHDL, etc.). This specification entails the functional behavior of the design, which is then converted into a register-transfer-level (RTL) description and translated

into Boolean expression for individual logic blocks and the interconnections logic by a process called synthesis. Synthesis is a process that maps the logic expressions of the design/circuit onto a gate-level netlist. Different optimization goals can be considered at this point to optimize the design for parameters, such as area, delay or power minimization, depending upon the target application and technology (ASIC or FPGA). Finally, the layout design tools, such as Cadence Encounter are used to perform physical synthesis, also known as place and route. Final sign-off of the design includes an extensively thorough verification before the circuit is sent out for fabrication. Many Electronic Design Automaton (EDA) tools provide seamless integration between all these steps and verify the functional correctness of the design between consecutive steps.

## **1.2** Hardware Verification

The main idea of these verification checks is to make sure that the specification of the design gets properly and accurately translated from previous state to the next and, ultimately, into a physical design without any errors. With contemporary processors containing over two billion transistors, it is imminent to employ design verification strategies to catch and correct the errors before the circuit gets fabricated on a physical chip. These multi-billion transistor chips can be generally sub-divided into datapath operators, memory unit, control unit, and other special purpose modules. Datapath operators are the main workhorses of computer systems, doing all the computations; they include arithmetic operations such as adders, subtractors, multipliers, dividers, square-rooters, etc. With an ongoing quest for minimum-area, high-speed and power-efficient design of these operators, these circuits/designs undergo several periodic improvements and optimizations. This consistent evolution demands a need for an efficient and consistent verification. Given the large input bit-width of these operators, enumerating the solution space by performing exhaustive simulation is simply infeasible. Hence, modern symbolic verification techniques (formal verification) are used to reason about the solution-sets without actually enumerating them. In this work, we use computer algebra techniques, which can reason about the solution space at both, the bit- and word-level, and naturally possess the required power of abstraction. Specifically, we target the functional verification of gate-level arithmetic designs (net-lists), and more specifically, dividers and square-rooters. Other kinds of hardware verification, such as model/property checking, physical verification, timing verification, clock domain crossing (CDC) verification, etc., are not subject of this work.

#### **1.2.1** Canonical Diagrams

Binary decision diagrams (BDDs) [4] and all other variants BMDs [3], TEDs [8] etc. are data structures for representing Boolean functions, i.e., functions that take Boolean variables as input and produce Boolean outputs. Truth tables have been used to enumerate the logic described by a boolean function. However, truth tables require exhaustive enumeration, and are not memory efficient. Whereas, canonical diagrams, evolving from the Shannon expression, are compact graphs, where logic functions are encoded in graph paths efficiently, and some variants of BDDs are actually very efficient in crawling through the solution space of a Boolean function, addressing functional verification and equivalence checking of different arithmetic designs. These canonical diagrams are efficient to some degree in solving also arithmetic circuits, such as adders, subtractors, and multipliers. However, this representation has its limitations. Since the size of these diagrams increases exponentially with the size of bit-width, BDDs become prohibitive for larger designs and specifically for arithmetic circuits. Even though BDDs have been used to verify adders/subtractors [52] and to some extent multipliers [7], [23], the literature is rather scarce on verification of divider circuits. A notable exception in this domain is the work of Bryant [5]. Although, effective and being able to catch the infamous Pentium 4 floating point division bug, it requires generating a checker circuit, which itself needs to be proved. However, no reliable means were offered for the verification of the checker circuit itself.

### 1.2.2 SAT: Satisfiability Problem

In order to overcome the shortcomings of canonical diagram based verification, SAT (short for satisfiability) has emerged as a leading technique in Formal Verification. The main goal of SAT based verification is to find satisfying assignments to a formula, hence the name SAT. Typically, the formula is in the form of Cunjunctive Normal Form (CNF), a conjunction of one or more clauses, where a clause is a disjunction of literals. For example, the Boolean formula  $\varphi = (a + \neg b)(\neg a + \neg b + c)$ can be satisfied by choosing a = 1; b = 1; c = 1, which makes  $\varphi = 1$ , and hence provides a satisfiable solution. If the assignment of variables that makes the Boolean formula  $\varphi = 1$  does not exist, the problem is called unsatisfiable or unSAT.

Since the seminal 1962 paper of Davis, Putnam, Logemann and Loveland [12], their DPLL algorithm has become a predominant algorithm to solve SAT instances. It is based on an intelligent space searching with a basic backtracking capability. Variables are selected according to some heuristic and assigned value 0 or 1. The newly assigned constants are propagated to the unsatisfied clauses by the process called Boolean Constraint Propagation (BCP) to identify implications, conflicts, and the satisfied clauses. An important enhancement to the basic DPLL algorithm is a Conflict-Driven Clause Learning (CDCL), which provides ability to learn new clauses that prevents the space search process from ending in an unsatisfying assignment. It also adds non-chronological backtracking from which a new search continues. Modern software SAT solvers are equipped with an efficient BCP, conflict resolution strategies, and an improved decision heuristic that can rapidly and efficiently prune the search space.

However, regardless of all these innovations and developments, the SAT-based methods have a low scalability in verifying arithmetic circuits. For example, a state-of-art SAT solver, miniSAT [44], takes up to an hour to verify a 16-bit multiplier. Furthermore, it takes several hours to verify a 17-bit divider circuit. This is not an effective verification methodology since the current multiplication and divider units in core datapath are usually 32-bit or 64-bit wide. Hence, we need an effective and efficient methodology to verify these essential datapath operators.

#### 1.2.3 Theorem Proving

The technique that received most attention in industry in arithmetic circuit verification is Theorem Proving. In this technique, the circuit is characterized by a set of rules, which are used to make complex formulas to represent the circuit [39][27][24][25][26]. However, the process of converting a circuit into a predefined set of rules to be applied sequentially requires a significant human effort and an intimate knowledge of the domain. The success of the proof relies on the choice of, and on the order in which the rules are applied, with no guarantee of a successful conclusion. Rager et al. [36] report that proving that the divider implemented by ORACLE is formally proven as equivalent of the SPARC ISA and IEEE 754 specifications, required "a sizable effort". Furthermore, these approaches cannot be fully automated or generalized. Regardless of these techniques, there is still a need to formally verify the actual hardware (typically, gate-level) implementation, which is addressed in this work.

# CHAPTER 2 TECHNICAL BACKGROUND

This chapter provides a mathematical background of computer algebra method presented in this work and reviews the related work in the literature. This and the next chapter is written in collaboration with my colleague Tiankai Su [45] and is presented as a joint work to serve as a brief summary of computer algebraic background. Specifically, in order to build an algebraic model for an arithmetic circuit in the context of computer algebra, the following concepts are need to be revised: fields, polynomials, ideals, varieties and ideal membership, and Gröbner basis.

### 2.1 Fields, Polynomials, Ideals and Varieties

#### 2.1.1 Fields

In mathematics, a field is a set F, containing at least two elements, on which two operations + and  $\cdot$  (called addition and multiplication, respectively) are defined, so that for each pair of elements  $x, y \in F$  there are unique elements x + y and  $x \cdot y$  in F. A field is thus a fundamental algebraic structure, which is widely used in algebra, number theory, and many other areas of mathematics. To learn about fields, we start with the *commutative ring*, since field is a special class of ring. A commutative ring consists of a set R and two binary operations " $\cdot$ " and "+" defined on R, for which the following conditions are satisfied:

(i) Associativity: (a+b) + c = a + (b+c) and  $(a \cdot b) \cdot c = a \cdot (b \cdot c)$  for all  $a, b, c, \in \mathbb{R}$ .

(ii) Commutativity: a + b = b + a and  $a \cdot b = b \cdot a$  for all  $a, b \in R$ .

(iii) Distributivity:  $a \cdot (b + c) = a \cdot b + a \cdot c$  for all  $a, b, c \in R$ .

(iv) *Identities*: There are elements  $0, 1 \in R$  such that a + 0 = a and  $a \cdot 1 = a$  for all  $a \in R$ .

(v) Additive inverse: Given  $a \in R$ , there is  $b \in R$  such that a + b = 0.

Two examples of commutative rings are the integers  $\mathbb{Z}$  and the polynomial ring  $k[x_1,...,x_n]$ , with coefficients in an arbitrary field k. A field  $\mathbb{F}$  is a commutative ring with unity, where every element in  $\mathbb{F}$ , except 0, has a *multiplicative inverse*:  $\forall$  a  $\in (\mathbb{F} - \{0\}), \exists \ \hat{a} \in \mathbb{F}$  such that  $a \cdot \hat{a} = 1$ . The most commonly used fields are  $\mathbb{Q}$ ,  $\mathbb{R}$  and  $\mathbb{C}$ . The set  $\mathbb{Z}$ , which is of particular interest to us, is a ring but not a field, since it does not have the attribution of a multiplicative inverse.

#### 2.1.2 Polynomials

A polynomial is an expression consisting of variables and coefficients that involves the operations of addition, multiplication, and non-negative integer exponents of variables. In general, a **polynomial** f in variables  $x_1,...,x_n$  is a finite linear combination of monomials, with coefficients in some field k. A polynomial can always be written in a sum-of-product form  $f = \sum a_i x_i^{\alpha_i}$ , where each product  $x_i^{\alpha_i}$  is called *monomial* and  $a_i$  is the coefficient. A monomial in variables  $x_1,...,x_n$  is a product of the form  $x_1^{\alpha_1} \cdot x_2^{\alpha_2} \cdots x_n^{\alpha_n}$ , where all of the exponents  $\alpha_1,...,\alpha_n$  are nonnegative integers. The *degree* of this monomial is the sum  $\alpha_1 + \cdots + \alpha_n$ . The total degree of polynomial f, denoted deg(f), is the maximum degree among all the monomials. A *term* of f is the product of a nonzero coefficient and its monomial. As an example, polynomial  $f = 2x^3y^2z + \frac{2}{3}y^3z^3 - 3xyz + y^2$  has four terms and total degree six. Note that there are two terms of maximal total degree, which is something that cannot happen for polynomials in one variable.

There are several ways to order monomials (referred to as *term order*), such as *lexicographic order* (LEX), *Degree reverse lexicographic order* (DEGREVLEX), and others. For instance, in LEX order,  $2x^3y^2z > \frac{2}{3}y^3z^3$ . The first, or greatest term of f (in terms of the adapted term order), is called the *leading term* lt(f) of the polynomial f. In the above example, the leading term is  $2x^3y^2z$ .

Leading terms play an important role in the proposed verification method, where logic gates of a circuit are described as polynomials. Specifically, the polynomial terms are ordered such that the leading term is a variable representing an output of a gate. This ordering makes a profound impact on the efficiency of the proposed verification technique. This issue will be discussed in detail in Chapter 3.

In this work, since all variables representing in the circuits are Boolean, we are particularly interested in polynomials with variables of degree 1. Such a polynomial is called *Pseudo-Boolean* polynomial. Formally, a Pseudo-Boolean function is a function  $f: B^n \to \mathbb{R}$ , where  $B = \{0, 1\}$  is a Boolean domain and n is a nonnegative integer called the arity of the function. It can be written as a multi-linear polynomial

$$f = a + \sum a_i x_i + \sum_{i < j} a_{ij} x_i x_j + \sum_{i < j < k} a_{ijk} x_i x_j x_k + \dots$$

with constant coefficients  $a, a_i, \dots$  in the given field.

### 2.1.3 Ideals and Varieties

Given a polynomial ring  $R = k[x_1,...,x_n]$  with coefficients in some field k, a subset  $I \subset R$  is an *ideal* if it satisfies:

(i)

$$0 \in I$$

. (ii) If  $f, g \in I$ , then  $f + g \in I$ . (iii) If  $f \in I$  and  $h \in R$ , then  $hf \in I$ .

In general, if  $I \in k[x_1,...,x_n]$  consists of all the linear combinations of a set of polynomials  $\{f_1, ..., f_s\} \in k[x_1,...,x_n]$ , then I is an ideal of the set  $\{f_1, ..., f_s\}$ , and the set of  $\{f_i\}$  is called *generator* or *basis*.

$$J = \langle f_1, ..., f_s \rangle = h_1 f_1 + ... + h_s f_s : h_i \in R$$

(2.1)

We call  $\langle f_1, ..., f_s \rangle$  the ideal generated by the basis  $\{f_1, ..., f_s\}$ .

Given an ideal  $J = \langle f_1, ..., f_s \rangle$  generated by  $f_1, ..., f_s, \in k[x_1, ..., x_d]$ , the set of all solutions to:  $f_1 = f_2 = \cdots = f_s = 0$  is called **variety**  $V(f_1, ..., f_s)$  of J. While an ideal may have different bases, the variety depends only on the ideal and not on the basis (generator). That is, different bases that produce the same ideal will have exactly the same variety. In Section 2.3, we will introduce an especially useful basis for our verification, called Gröbner basis.

Let  $\{f_1, ..., f_s\}$  and  $\{g_1, ..., g_t\}$  be the bases of the same ideal in  $k[x_1, ..., x_n]$ , i.e.  $\langle f_1, ..., f_s \rangle = \langle g_1, ..., g_t \rangle$ ; then  $V(f_1, ..., f_s) = V(g_1, ..., g_t)$ . In the next section, we will show how the concept of ideal and variety is applied to circuit verification.

### 2.2 Ideal Membership Test

The symbolic algebra theories about polynomial rings, ideals and varieties we use in this work are all defined over a field, typically  $\mathbb{Q}$ . However, as described next and fully developed in the next section, the polynomials introduced in our work represent logic gates and are defined over ring  $\mathbb{Z}$ . However, these polynomials have a special structure, namely their leading term  $lt(f_i)$  that represents a variable associated with a logic gate  $g_i$  has coefficient 1. Subsequently, the process of polynomial division, which is an essential element of the verification process (to be described in detail later), will never introduce any coefficient outside of  $\mathbb{Z}$ . Consequently, this allows us to treat the polynomials as if they were in  $\mathbb{Q}$ .

Let  $B = \{f_1, ..., f_s\}$ , with  $f_i \in \mathbb{Z}[X]$ , be a set of polynomials representing the circuit elements and let the ideal  $J = \langle f_1, ..., f_s \rangle$  be generated by basis  $\{f_1, ..., f_s\}$ . In our case, each generator is a polynomial model of a circuit module (logic gate), and the set of generators can be viewed as the *implementation* of the circuit. Then, from the circuit perspective, the variety V(J) of J, which is the set of all simultaneous solutions to a system of equations  $f_1(x_1, ..., x_n) = 0; ..., f_s(x_1, ..., x_n) = 0$ , contains all signal values of the circuit for all possible input valuations  $\{x_i\}$ .

Similarly, functional specification of the circuit is also defined as a polynomial in  $\mathbb{Z}[X]$ , where X is a set of input and output variables. For example, the specification of a multiplier circuit,  $Z = A \cdot B$ , can then be written as a polynomial  $F : Z - A \cdot B$ . Here, A, B, and Z are symbolic, word-level variables, each represented as a polynomial in their respective bit-level variables, e.g.,  $A = \sum_{i=0}^{n-1} 2^i a_i$ , and similarly for B and Z. In terms of computer algebra, the arithmetic circuit verification problem is then formulated as follows [34][30][41][38]:

Given a circuit represented by a set of generators (implementation),  $B = \{f_1, ..., f_s\}$ , and the specification F, the goal of functional verification is to prove that the implementation (B) satisfies the specification (F). Here, B have the same notation as in the previous example, but it represents a set of gate polynomials. This means that for a functionally correct circuit, the solution to F = 0 agrees with V(J), or, equivalently, that F vanishes on  $V(J)^1$ . Consequently, this problem has been termed as an *ideal membership test*, which decides whether the specification polynomial F is a member of the ideal J generated by B, i.e., if  $F \in J$  [18][34][30].

Given an ideal  $J = \langle f_1, ..., f_s \rangle$ , in order to test if  $F \in J$ , polynomial F is divided consecutively by  $f_1, ..., f_s$ . The goal of each division is to cancel the leading term of F(with respect to a chosen term order) using one of the leading terms of  $f_1, ..., f_s$ . Such a reduction results in a polynomial remainder  $r = F - \frac{lt(F)}{lt(f_i)} \cdot f_i$ , in which the leading term lt(F) has been canceled. If the remainder r reduces to zero, the implementation satisfies the specification. However, if  $r \neq 0$ , such a conclusion cannot be drawn: rcan still be in J but it is not divisible by any of the polynomials in  $B = \{f_1, ..., f_s\}$ . That is, the basis  $B = \{f_1, ..., f_s\}$  may not be sufficient to reduce  $F \longrightarrow 0$ , and yet the circuit may be correct. To check if F is reducible to zero for the given ideal J, one must compute a *canonical* set of generators,  $G = \{p_1, ..., p_t\}$ , called the *Gröbner basis*,

<sup>&</sup>lt;sup>1</sup>Polynomial f is said to vanish on a set V if  $\forall a \in V \ f(a) = 0$ . Or,  $V(f) \subseteq V(J)$ .

with the same ideal  $\langle p_1, ..., p_t \rangle = \langle f_1, ..., f_s \rangle$ , the set  $G = \{p_1, ..., p_t\}$  be the Gröbner basis for ideal J, then F belongs to J if and only if the remainder of the division of F by the elements of G is zero, denoted as  $\forall F \in J, F \xrightarrow{G} + 0$  [1]. The sign + means that the division/reduction is done consecutively by using the elements of G one by one. In short, the Gröbner basis is necessary to unequivocally answer the question whether  $F \in J$ .

### 2.3 Gröbner basis

A basis  $\{p_1, ..., p_t\}$  of an ideal  $J\langle p_1, ..., p_t \rangle$  is called a **Gröbner basis** (w.r.t. the monomial order >) if the leading term of every nonzero element of J is a multiple of (at least) one of the leading term  $lt(p_1), ..., lt(p_t)$ . A known algorithmic procedure for computing a Gröbner basis is called Buchberger's algorithm [6]. Given some basis  $B = \{f_1, ..., f_s\}$ , it produces another basis  $G = \{p_1, ..., p_t\}$ , such that the ideals  $\langle p_1, ..., p_t \rangle = \langle f_1, ..., f_t \rangle$  and hence have the same variety  $V(\langle G \rangle) = V(\langle B \rangle)$ . Buchberger's algorithm is computationally expensive, since it computes the so-called *S*-polynomials (*SPoly*) by performing reduction operations on all pairs of polynomials in *B*. The S-polynomial of polynomials p and g in a polynomial set P, is the combination Spoly $(p, g) = \frac{L}{lt(g)}p - \frac{L}{lt(g)}g$ , where L is the least common multiple LCM(lm(p), lm(g)). Note that Spoly(p, g)  $F \xrightarrow{P}_+ r$  gives a new leading term.

The basic purpose of computing SPoly pairs is to compute polynomials with new leading terms, which can be used in the reduction step of the ideal-membership testing. These newly generated polynomials belong to the ideal G which completely defines the system. To compute Gröbner basis  $G = \{g_1, ..., g_l\}$  for an ideal  $\langle p_1, ..., p_t \rangle$ , Buchberger's algorithm computes G in some finite number of steps by performing the Spoly $(p,g) \xrightarrow{P}_+ r$  iteratively. The algorithm determines if Spoly $(p,g) \xrightarrow{P}_+ 0$ . In this case, we also conclude that all polynomials are relatively prime to each other, with a distinct leading term.

This establishes that the generating set (generator) whose polynomials are relatively prime to each other is in fact a *Grobner* basis. This important fact will be used in developing the verification method in the upcoming sections. A number of other algorithms have been developed for computing a *Gröbner* basis, such as F4 [17], which in contrast to the basic Buchberger's algorithm, compute multiple SPoly pairs in each iteration. However, in general, the process of generating a *Gröbner* remains computationally expensive.

### 2.4 Related Work

The work in arithmetic circuit verification was pioneered by Shekhar et al. [43] and Wienand et al. [47], where some important concepts from computer algebra and algebraic geometry were applied to model the core verification problem. In [47]an arithmetic circuit is modeled as a network of arithmetic operators, such as halfand full-adders, comparators, and product generators, extracted from the gate-level implementation. These operators are modeled using *arithmetic bit-level* (ABL) expressions,  $B = \{B_j\}$ . The authors of [47] (and also of [30]) show that for an arbitrary combinational circuit, if the terms of the gate equations B are ordered in reverse topological order,  $\{\text{outputs}\} > \{\text{inputs}\}, \text{ then all leading monomials of the polynomials}$ in B are relatively prime. As a result, the corresponding set B already constitutes a Gröbner basis (GB), obviating the computation of the complete canonical Gröbner basis. The verification problem is solved by reducing the specification F modulo Bto the normal form and testing if it vanishes over  $\mathbb{Z}_{2^n}$ . The restriction to binary variables is achieved by imposing Boolean constraints,  $\langle x^2 - x \rangle$  for all the variable x [34], and the problem is solved over quotient ring  $Q = \mathbb{Z}_{2^n}[X]/\langle x^2 - x \rangle$  (for all variable x) using a popular computer algebra system, Singular [15]. This approach,

however, is limited to circuits composed entirely of half adders and full adders, which must first be extracted from the gate-level implementation. In practice, this is the most expensive part of the process, and it is not always possible to perform such extraction, especially in highly bit-optimized implementations.

In [30] the verification problem was similarly formulated as an *ideal membership* test but applied to Galois Field (GF or  $\mathbb{F}_{2^q}$ ) arithmetic circuits. It has been shown that in GF, when the specification F and the ideal J of the circuit implementation are in  $\mathbb{F}_{2^q}$ , the problem can be reduced to testing if  $F \in (J + J_0)$ , over a larger ideal  $(J + J_0)$  where  $J_0 = \langle x^2 - x \rangle$  is an ideal of the field polynomials. Adding  $J_0$  basically restricts the variety V to solutions in  $\mathbb{F}_2$ , i.e. to  $V(J) \cap V(J_0)$  [11]. The polynomials of  $J_0$  are referred to as field polynomials. Similarly to [47], the authors of [30] derive the term order from the topological structure of the circuit, which renders the set of polynomials B (circuit implementation) a Gröbner basis (GB), thus obviating the need to perform the expensive GB computation. The method uses a customized, F4-style polynomial reduction using a modified Gaussian elimination algorithm [17] under this term order.

A different approach to that of defined earlier has been proposed in [51], whereby the expensive polynomial reduction process has been replaced by a computationally simpler *algebraic rewriting* technique. The method introduces the concept of an *input signature*, a polynomial in the primary inputs, and an *output signature*, a polynomial derived from the encoding of the primary outputs. The verification is accomplished by rewriting the output signature, using algebraic expressions of the internal gates, into an input signature. This process de facto performs *function extraction*. Several ordering techniques have been described to make this method applicable to large arithmetic circuits, but the method still cannot handle the heavily optimized circuits.

A similar approach to arithmetic circuit verification, called *backward construction*, was proposed in 1995 in [23]. It uses BMDs to reconstruct functional, high level representation from the gate-level structure of arithmetic circuits such as adders and multipliers. Experimental results show that time complexity of the tested circuits is in the order of  $n^4$  for multipliers with n bit operands. There is no clear indication if the BMD is an efficient data structure for this problem, and our experiments could not confirm its efficiency.

The basic approach of the ideal membership testing and Gröbner basis (GB) reduction has also been used in the works of [41][38], where it was applied to integer circuits. In [41] the following features have been added to make the reduction more efficient:

- Logic reduction with an AND-XOR vanishing rule, which analyzes the structure of the circuit to identify and remove vanishing monomials that correspond to the product of XOR, AND signals with shared input variables;

- An XOR rewriting scheme, which reduces the model of the circuit to consider only primary inputs, outputs, and fan-out points/XOR gates; and

- Common rewriting, which eliminates the nodes with a single parent. These techniques simplify the task of GB reduction by eliminating all the nodes which have exactly one parent, thus increasing the chance for early term cancellation during the rewriting process.

Another work [38] revisits the techniques from [51] and [41] and provides the proof of correctness for these approaches. It uses a column-wise technique to model and verify basic multiplier structures by computing the Gröbner basis incrementally for each column of the output bit, rather than for the entire circuit. The work is concluded by showing the efficacy of the technique by applying it to clean and "dirty", i.e., heavily optimized, multipliers. The paper justifies the use of the theory of ideal membership (in principle applicable to  $\mathbb{Q}[X]$ ) to prove properties of integer arithmetic circuits in  $\mathbb{Z}$ . It points out that, since the leading coefficients of the gate polynomials forming the Gröbner basis are +1 or -1, polynomial reduction never introduces fractional coefficients and their computation remains in  $\mathbb{Z}$ . This also explains why the dedicated implementations in [51] and [41] can rely on computation in  $\mathbb{Z}$  only, while remaining sound and complete [38]. A follow-up paper [37] describes an enhancement to this column-wise technique by extracting half- and full-adder constraints to further reduce the size of Gröbner basis to speed up the reduction process.

In general, the problem of formally verifying complex integer arithmetic circuits (not just multipliers) remains open, and new solutions are being proposed. In the next chapter, an efficient and scalable approach, called *algebraic rewriting*, is introduced to address this issue. This approach has already been proposed by our group earlier, but it is further refined and formalized in this dissertation to be adequately applied to Divider and Square-root circuits. In addition, a *bit-flow* model is proposed to support the proof of the correctness of algebraic rewriting, and to offer a new insight into the problem of arithmetic circuit verification [9].

## CHAPTER 3

## ALGEBRAIC REWRITING AND DIVIDER MODEL

This chapter introduces the algebraic model used in circuit verification, which is the key to solve the verification problem in algebraic domain. Two flavors of computer algebra techniques that use this model will be discussed in detail: 1) Gröbner basis reduction techniques [34][41][38] and 2) algebraic rewriting [51]. Detailed algorithms for the reduction and the rewriting are given. We analyze the relation between these two computer algebra techniques and provide a comparison from the efficiency point of view.

### 3.1 Algebraic Model of Electronic Circuits

The arithmetic circuits considered in this dissertation are the ones which can be expressed as a polynomial in the input variables. These include adders, subtractors, multipliers, fused add-multiply circuits, dividers, and square-root. In this Section, we provide examples of existing solutions for multiplier verification. Later, we provide a detailed analysis of a divider verification methodology. Such arithmetic circuits are modeled as a network of interconnected bit-level components, each with a finite set of binary inputs with one or more binary outputs. In this work, we will focus on *gate-level* integer arithmetic circuits with single-output logic gates. However, the model can be extended to other, more complex, multiple-output circuit components such as dividers and square-rooters.

Each gate is modeled by a *pseudo-Boolean* polynomial  $f_i \in \mathbb{Z}[X]$ , with Boolean variables X representing circuit signals associated with a logic gate. A pseudo-

Boolean polynomial is an integer-valued function  $f : \{0,1\}^n \to \mathbb{Z}$ . It is an algebraic expression with usual multiplication and addition operators over Boolean variables. The following expressions summarize the algebraic representation of basic Boolean operators NOT, AND, OR and XOR.

$$\neg a = 1 - a$$

$$a \wedge b = a \cdot b$$

$$a \vee b = a + b - a \cdot b$$

$$a \oplus b = a + b - 2a \cdot b$$

(3.1)

By construction, each expression evaluates to a binary value  $\{0,1\}$  and hence correctly models the Boolean function of a logic gate. Models for more complex AOI (And-Or-Invert) gates, used in standard cell technology, are readily obtained from these basic logic expressions. For example, the algebraic model for the logic gate

- $g = a \lor (b \land c) \Longrightarrow g = a + bc abc$

- $OR3 (a \lor b) => z = a + b + c ab ac bc + abc$

- $XOR3 \ (a \oplus b \oplus c) => z = a + b + c 2ab 2ac 2bc + 4abc$

- $MAJ3 (a \land b \lor a \land c \lor b \land c) => ab + bc + ac 2abc$

Multiple output modules, such as single-bit adders, with binary inputs can be expressed similarly. For example, a half-adder (HA) and a full-adder (FA), can be expressed by the following expressions:

HA:

$$2C + S = a + b$$

FA:  $2C + S = a + b + c_{in}$  (3.2)

where  $a, b, c_{in}$  are binary inputs and C, S are binary outputs.

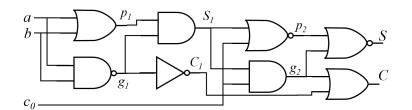

The function computed by an arithmetic circuit is represented as a specification polynomial in the primary input variables, denoted  $F_{spec}$ . For example, the specification of an *n*-bit unsigned integer multiplier,  $Z = A \cdot B$  with inputs  $A = [a_0, \dots, a_{n-1}]$ and  $B = [b_0, \dots, b_{n-1}]$ , is described by  $F_{spec} = \sum_{i=0}^{n-1} \sum_{j=0}^{n-1} 2^{i+j} a_i b_j$ . The result of the computation, stored in the primary output bits, is also expressed as a polynomial, called *output signature*,  $S_{out}$ . Typically, such a polynomial is linear, uniquely determined by the *m*-bit encoding of the output, provided by the designer. For example, for a signed 2's complement arithmetic circuit with *m* output bits,  $S_{out} =$  $-2^{m-1}z_{m-1} + \sum_{i=0}^{m-2} 2^i z_i$ . The circuit is implemented as a network of logic gates G, each modeled as a polynomial  $g_i$  derived from Eqn.(3.1). The polynomial representing a given gate evaluates to zero for all the input and output combinations satisfied by this gate. As an example, a non-standard gate-level implementation of a full adder, is shown in Fig. 3.1.

Figure 3.1: Gate-level arithmetic circuit (Full Adder)

The set of polynomials  $G = \{f_i\}$  in Eqn. 3.3 represents the gate-level implementation of the full adder circuit. We refer to this set as G to indicate that it is a Gröbner basis (or GB for short). It has been shown that if the polynomials in G are ordered such that the leading term is the output of the gate, and the leading term of all the polynomials are relatively prime, the set G forms Gröbner basis [35].

The set G consists of two parts: gate polynomials  $(f_1, ..., f_8)$  and field polynomials  $(f_9, ..., f_{17})$ . Each polynomial satisfies the relation  $f_i = 0$ . The gate polynomials have the form  $f_i = v_i - tail(f_i)$ , where the leading term  $lt(f_i) = v_i$  is the output of

gate  $f_i$ , and  $tail(f_i)$  is the logic specification of the gate in terms of its inputs. The leading terms under such ordering are relatively prime, which renders G a Gröbner basis [34][30][38]. This feature is essential for both the GB reduction and algebraic rewriting, which will be discussed in the next sections.

$$f_{1} = p_{1} - (-ab + a + b)$$

$$f_{2} = g_{1} - (-ab + 1)$$

$$f_{3} = S_{1} - p_{1}g_{1}$$

$$f_{4} = C_{1} - (-g_{1} + 1)$$

$$f_{5} = p_{2} - (S_{1}c_{0} - S_{1} - c_{0} + 1)$$

$$f_{6} = g_{2} - S_{1}c_{0}$$

$$f_{7} = S - (p_{2}g_{2} - p_{2} - g_{2} + +1)$$

$$f_{8} = C - (-C_{1}g_{2} + C_{1} + g_{2})$$

$$f_{9} = (a^{2} - a)$$

$$f_{10} = (b^{2} - b)$$

$$\dots$$

$$f_{17} = (g_{2}^{2} - g_{2})$$

$$(3.3)$$

Each field polynomials,  $f_9, ..., f_{17}$ , has the form  $J_0 = \langle x^2 - x \rangle$ , where x is one of the signals  $\{a, b, c_0, p_1, g_1, S_1, C_1, p_2, g_2\}$ . These field polynomials play an important role in polynomial reduction to maintain the Boolean property of each variable. However, they are handled differently in the GB reduction than in the algebraic rewriting approach, as discussed in the next sections.

### 3.2 Gröbner Basis Polynomial Reduction

In this method the reduction of F modulo G is accomplished by successively eliminating terms of F, one by one, by a leading term of some polynomial  $f_i \in G$ , using Gaussian elimination. The reduction is performed over a Gröbner basis derived from G and the field polynomials  $J_0$ . From the mathematical point of view, this means that the computation will be performed in the quotient ring,  $\mathbb{Z}[X]/\langle x^2 - x \rangle : x \in X$ , the set of all variables (signals) of the circuit. The Gröbner basis (GB) reduction algorithm is given in Algorithm 1. First, the polynomial base  $G=\{f_1, ..., f_m\}$  is derived from  $\mathcal{N}$  using Equations (3.1), where m is the number of logic components in  $\mathcal{N}$ . Each polynomial in G has the form  $f_i = v + tail(f_i)$ , where v is the the leading monomial  $lm(f_i)$ . All the variables in the circuit are ordered in reverse-topological order, from primary outputs to primary inputs, and for each gate polynomial from the gate output to its inputs.

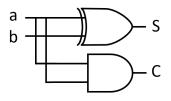

Figure 3.2: Half-Adder gate-level arithmetic circuit

Furthermore, the output signals of the gates that depend on common variables (fanins) should be ordered next to each other, as this will maximize the chance for a potential term cancellation and minimize the size of intermediate polynomials. For example, consider the reduction of a polynomial F = 2C + S + ... in a circuit containing a half adder composed of an AND gate C = ab and an XOR gate S = a+b-2ab, shown in Figure 3.2. Since both C and S depend on common variables, a, b, reducing them one immediately after the other will eliminate the product term ab from the polynomial, resulting in F = a + b + .... This is beneficial from the complexity point of view, and should be performed before the reduction of the remaining terms of the polynomial.

Considering these two basic ordering rules, one possible term order for the polynomial ring of the circuit in Figure 3.1 is shown below, where variables in curly brackets can assume any relative order.

$$\{S, C\} > \{p_2, g_2\} > \{S_1, C_1\} > \{p_1, g_1\} > \{a, b, c_0\}$$

$$(3.4)$$

The expression F to be reduced is initialized with the difference between the output signature  $S_{out}$  and  $F_{spec}$ . In this case  $F = 2C + S - (a + b + c_0)$ . The goal is to reduce F to 0 by G.

| Algorithm 1 Gröebner Basis Polynomial Reduction                                          |

|------------------------------------------------------------------------------------------|

| <b>Input:</b> Specification polynomial $F_{spec}$ ; and Gate-level netlist $\mathcal{N}$ |

| Output: Remainder Rem                                                                    |

|                                                                                          |

| 1: Create base $G = \{f_1, \dots, f_m\}$ of $\mathcal{N}$ using Eq.(3.1)                 |

| 2: Generate $S_{out}$ from $\mathcal{N}$                                                 |

| 3: Define ring and specify term order                                                    |

| 4: Initialize $F \leftarrow S_{out} - F_{spec}$                                          |

| 5: while $F \neq 0$ do                                                                   |

| 6: <b>if</b> $\exists f_i \in G : \frac{lt(F)}{lt(f_i)} \neq 0$ <b>then</b>              |

| 7: /* there exists $f_i$ such that its leading term is divisible by $lt(F)$ */           |

| 8: $F \leftarrow F - \frac{lt(F)}{lt(f_i)} \cdot f_i // $ polynomial division            |

| 9: else                                                                                  |

| 10: /* no leading term of $f_i$ divides $F$ , move $lt(F)$ to $Rem */$                   |

| 11: $F \leftarrow F - lt(F)$                                                             |

| 12: $Rem \leftarrow Rem + lt(F)$                                                         |

| 13: end if                                                                               |

| 14: Maintain the term order imposed on the ring                                          |

| 15: end while                                                                            |

| 16: return Rem                                                                           |

|                                                                                          |

The main part of the GB reduction is given in lines 5-15. The algorithm searches for a polynomial  $f_i$  in G such that the leading term of  $f_i$  divides the current leading term lt(F) of F. If such a polynomial exists, it will be used to reduce F, as shown in line 8. Otherwise, the lt(F) will be moved to the remainder *Rem* (lines 11 - 12). At any point, when new terms (containing new intermediate variables introduced by division) are added to polynomial F (line 8), the procedure must maintain the term order imposed on the ring. The reduction process terminates when F becomes empty, either by being reduced or moved to *Rem*. The zero remainder is the evidence of a correct implementation, as discussed in Chapter 2.2.

We illustrate the GB reduction process with the example in Fig. 3.1. The initial polynomial for this circuit is:

$$F = 2C + S - (a + b + c_0) \tag{3.5}$$

Equation (3.6) gives the sequence of steps that reduces F with the gate polynomials  $f_i \in G$  for the circuit in Figure 3.1. At each step, F represents the polynomial reduced by the previous reduction step. For brevity, the substitution is shown for a pair of variables at once. For example, F/(C, S) means reducing variables C and S with polynomial  $f_8$  followed by  $f_7$ . The term order given in Eqn. (3.4), imposed on the ring, is maintained throughout the entire reduction process.

$$F = 2C + S - (a + b + c_0)$$

1)  $F/(S, C) = 2(-C_1g_2 + g_2 + C_1) + (p_2g_2 - p_2 - g_2 + 1) - (a + b + c_0)$

$= p_2g_2 - p_2 - 2g_2C_1 + g_2 + 2C_1 - (a + b + c_0) + 1$

2)  $F/(p_2, g_2) = (S_1c_0 - S_1 - c_0 + 1)S_1c_0 - (S_1c_0 - S_1 - c_0 + 1) - 2S_1C_1c_0$

$+ S_1c_0 + 2C_1 - (a + b + c_0) + 1$

$= \mathbf{S_1^2c_0^2 - S_1^2c_0 - S_1c_0^2 + S_1c_0 - 2S_1C_1c_0 + S_1 + 2C_1 - (a + b)$

3)  $F/(S_1^2 - S_1) = -2S_1C_1c_0 + S_1 + 2C_1 - (a + b)$

4)  $F/(S_1, C_1) = -2(p_1g_1)(-g_1 + 1)c_0 + p_1g_1 + 2(-g_1 + 1) - (a + b)$

$= -2(-\mathbf{p_1g_1^2} + \mathbf{p_1g_1})\mathbf{c_0} + p_1g_1 - 2g_1 - (a + b) + 2$

5)  $F/(g_1^2 - g_1) = p_1g_1 - 2g_1 - (a + b) + 2$

6)  $F/(p_1, g_1) = (-ab + a + b)(-ab + 1) - 2(-ab + 1) - (a + b) + 2$

$= \mathbf{a}^2\mathbf{b}^2 - \mathbf{a}^2\mathbf{b} - \mathbf{ab}^2 + \mathbf{ab}$

7)  $F/(a^2 - a) = 0$

The effect of field polynomials  $J_0 = \langle x^2 - x \rangle$ , responsible for keeping each variable Boolean, can be observed during steps 2, 4, 6 and 7, shown in bold. The reduction terminates in Rem = 0, indicating that the circuit implements the function indicated by the specification, a full adder.

### 3.3 Algebraic Rewriting

Algebraic rewriting is the process of transforming the output signature  $S_{out}$  into an input signature  $S_{in}$  using algebraic models of the internal components (logic gates) of the circuit. The rewriting is done in reverse topological order: from the primary outputs (PO) to the primary inputs (PI); for this reason it is also referred to as a *backward rewriting* [51]. Intermediate expressions obtained during rewriting are also represented as polynomials, referred to as *signatures*, over the variables representing the internal signals of the circuit. By construction, each variable in a given signature (starting with  $S_{out}$ ) represents an output of some logic gate.

The rewriting transformation simply replaces each variable with the corresponding algebraic expression of the logic gate. If the variable is part of a monomial involving other variables, the expression is multiplied by the remaining terms and expanded to a disjunctive normal form. This is followed by a standard polynomial simplification by combining terms with same monomials.

#### Algorithm 2 Algebraic Rewriting

**Input:** Specification polynomial  $F_{spec}$ ; and Gate-level netlist  $\mathcal{N}$ **Output:**  $(S_{in} = F_{spec})$ , or the computed signature  $S_{in}$

- 1: Derive  $G = \{f_1, ..., f_m\}$  from  $\mathcal{N}$  using Eqn.(3.1) 2: Sort G to maximize the cancellations // proproce

- 2: Sort G to maximize the cancellations // pre-processing

- 3: Generate  $S_{out}$  from  $\mathcal{N}$

- 4: Initialize  $Sig \leftarrow S_{out}$

- 5: for  $f_i$  in G do

- 6:  $v \leftarrow \ln(f_i) //$  leading monomial of  $f_i$  is output of a gate

- 7: **if**  $v \in Sig$  then

- 8: /\* replace v with  $tail(f_i)$  in Sig \*/

- 9:  $Sig \leftarrow Sig(v \leftarrow tail(f_i))$

- 10:  $x \leftarrow x^2 // \text{ for all } x \text{ in } Sig$

- 11: **end if**

- 12: **end for**

- 13: /\* upon termination, Sig is composed of PIs only \*/

- 14: if  $Sig == F_{spec}$  return True

- 15: else return  $S_{in} = Sig$

Algebraic Rewriting procedure is summarized in Algorithm 2. First, the polynomial base  $G = \{f_1, ..., f_m\}$  is derived from  $\mathcal{N}$  using Eq.(3.1), as in the GB reduction. Then, the polynomials in G are sorted in reverse-topological order (lines 1-2). Among several possible topological orders the one that maximizes the number of early cancellations during rewriting is sought. This has an effect of minimizing the size of the intermediate polynomials during rewriting (the "fat belly" effect) [51]. It is accomplished by keeping together the polynomials whose leading terms (gate outputs) depend on common variables, as in the GB reduction. The expression to be rewritten, Sig, is initialized with the given output signature  $S_{out}$  of  $\mathcal{N}$  (lines 3-4).

The main part of the rewriting, lines 5-12, iterates over the polynomials  $f_i \in G$ and performs the required substitutions. Specifically, all occurrences of  $v = lt(f_i)$ in Sig are replaced by  $tail(f_i)$ , followed by possible expansion of the resulting term. To maintain Boolean values of the variables during rewriting, the degree of each variable in Sig is reduced to 1 (line 10). This step is equivalent to dividing Sig by a field polynomial  $\langle x^2 - x \rangle$ , but it is achieved in a more efficient way. At the end, the algorithm returns  $S_{in}$  as the derived signature of the circuit. If the terms of polynomials in G are sorted in a reversed topological order, the returned polynomial  $S_{in}$  contains only the primary input (PI) variables, so it can be compared with  $F_{spec}$ .

While the main goal of algebraic rewriting, as described by Algorithm 2, is to determine the arithmetic function implemented by the circuit, it can also be used to verify it against the known specification. This can be simply done by rewriting  $F = S_{out} - F_{spec}$  and checking if it produces a zero. We will use this rewriting mode in order to compare it against the GB reduction method in Chapter 3.2.

We illustrate the rewriting process using the example of the gate-level full-adder circuit in Figure 3.1. The output signature of the circuit is  $S_{out} = 2C + S$ , determined by the binary encoding of the output. The specification for this circuit  $F_{spec} =$  $a+b+c_0$ . Following the ordering rules described in [51], the best rewriting order which

$$F = 2C + S - (a + b + c_{0})$$

1)  $F/(S, C) = 2(C_{1} + g_{2} - C_{1}g_{2}) + (1 - (p_{2} + g_{2} - p_{2}g_{2})) - (a + b + c_{0})$

$$= 2C_{1} + g_{2} - 2C_{1}g_{2} - p_{2} + p_{2}g_{2} + 1 - (a + b + c_{0})$$

2)  $F/(p_{2}, g_{2}) = 2C_{1} + S_{1}c_{0} - 2S_{1}C_{1}c_{0} - (1 - (S_{1} + c_{0} - S_{1}c_{0}))$

$$+ (1 - (S_{1} + c_{0} - S_{1}c_{0}))S_{1}c_{0} + 1 - (a + b + c_{0})$$

$$= 2C_{1} - 2S_{1}C_{1}c_{0} + S_{1} + \mathbf{S}_{1}\mathbf{c}_{0} - \mathbf{S}_{1}^{2}\mathbf{c}_{0} - \mathbf{S}_{1}\mathbf{c}_{0}^{2} + \mathbf{S}_{1}^{2}\mathbf{c}_{0}^{2} - (a + b)$$

$$= 2C_{1} - 2S_{1}C_{1}c_{0} + S_{1} + \mathbf{S}_{1}\mathbf{c}_{0} - \mathbf{S}_{1}^{2}\mathbf{c}_{0} - \mathbf{S}_{1}\mathbf{c}_{0}^{2} + \mathbf{S}_{1}^{2}\mathbf{c}_{0}^{2} - (a + b)$$

$$= 2C_{1} - 2S_{1}C_{1} + S_{1} - (a + b)$$

3)  $F/(S_{1}, C_{1}) = 2(1 - g_{1}) - 2(1 - g_{1})(p_{1}g_{1})c_{0} + p_{1}g_{1} - (a + b)$

$$= 2 - 2g_{1} - 2(\mathbf{p}_{1}\mathbf{g}_{1} - \mathbf{p}_{1}\mathbf{g}_{1}^{2}) + p_{1}g_{1} - (a + b)$$

$$= 2 - 2g_{1} + p_{1}g_{1} - (a + b)$$

4)  $F/(p_{1}, g_{1}) = 2 - 2(1 - ab) + (a + b - ab)(1 - ab) - (a + b)$

$$= \mathbf{ab} - \mathbf{a}^{2}\mathbf{b} - \mathbf{ab}^{2} + \mathbf{a}^{2}\mathbf{b}^{2} = 0$$

minimizes the size of intermediate polynomials is  $\{(S, C), (p_2, g_2), (S_1, C_1), (p_1, g_1)\}$ , as in the GB reduction. The signals shown in brackets can be rewritten in any order as they depend on common inputs. Equation (3.7) shows the rewriting steps for the circuit. The terms shown in bold face indicate those that are reduced to zero during polynomial simplification. For brevity, the substitution is shown for each pair of variables applied at once. For example: F/(C, S) means rewriting of F using Cand S variables of polynomials  $f_8, f_7$ .

During the rewriting, two types of simplifications can be observed:

- Simplification of the terms with same monomials; for example,  $2g_2 g_2 = g_2$ , in Step 1. In the process, some polynomial terms are reduced to 0. This is a common simplification applied in GB reduction as well.

- Lowering the term x<sup>2</sup> to x, since the signal variables are binary. This can be seen in Steps 2, 3, and 4, shown in bold face. For example, in step 2 we have: S<sub>1</sub>c<sub>0</sub> − S<sub>1</sub><sup>2</sup>c<sub>0</sub> − S<sub>1</sub>c<sub>0</sub><sup>2</sup> + S<sub>1</sub><sup>2</sup>c<sub>0</sub><sup>2</sup> = S<sub>1</sub>c<sub>0</sub> − S<sub>1</sub>c<sub>0</sub> − S<sub>1</sub>c<sub>0</sub> + S<sub>1</sub>c<sub>0</sub> = 0. Similarly, in step 3: (p<sub>1</sub>g<sub>1</sub> − p<sub>1</sub>g<sub>1</sub><sup>2</sup>) = p<sub>1</sub>g<sub>1</sub> − p<sub>1</sub>g<sub>1</sub> = 0, etc. This simplification is simpler and can be executed faster than dividing the polynomials by the respective field

polynomials  $(x^2 - x)$ , as it is done in computer algebra approach. This is one of the main reasons for greater efficiency of the algebraic rewriting compared to GB reduction.

Subsequently, the final result reduces  $F = S_{out} - F_{spec}$  to zero, indicating that the circuit correctly implements a full adder.

It should be noted that in addition to the two basic simplification rules mentioned above (rewriting the gates with common inputs, and the  $x^2 \rightarrow x$  reduction), more sophisticated simplifications can be applied to the running polynomial *Sig* during rewriting by analyzing the structure of the gate-level network. For example, recognizing that some signal g is a product of XOR and AND signals with the same fanin inputs will reduce signal g to zero. This simplification, called an *XOR-AND vanishing rule* has been used by [41], but for clarity of the illustration, it has not been taken into account here.

# 3.4 AIG Rewriting

The algebraic rewriting technique described in the previous section can be further improved by performing rewriting using the functional AIG (Add-Inverter Graph) representation of the circuit instead of its gate level structure. This section provides a brief overview how this is accomplished, with details provided in [50].

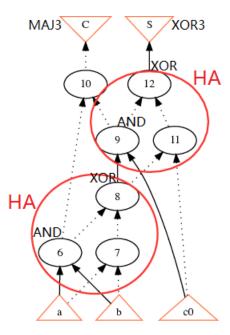

AIG (And-Inverter Graph) is a combinational Boolean network composed of twoinput AND gates and inverters [2]. Each internal node of the AIG represents a two-input AND function; the graph edges are labeled to indicate a possible inversion of the signal. We use the *cut-enumeration* approach of ABC [2] to detect XOR and Majority (MAJ) functions with a common set of variables; they are essential components of adder trees that are present in most arithmetic circuits in some form [50]. After detecting the XOR and MAJ components of the adder's AIG, rewriting skips over the detected adders, significantly speeding up the rewriting process. Figure 3.3 illustrates the process for the full adder (FA) circuit from Figure 3.1. In Figure 3.3 the groups of nodes (6,7,8) and (9,11,12) correspond to half adders (HA). The functions rooted at nodes 6 and 9 are majority (AND) functions, and those at nodes 12 and 8 are XORs. Subsequently, the functions at node 12 (S) and node 10 (C) are identified as XOR3 and MAJ3, respectively, on the shared inputs,  $a, b, c_0$ . The AIG rewriting of  $S_{out} = 2C + S$  over the extracted XOR3 and MAJ3 nodes is trivial, with the nonlinear monomials automatically cancelled, as shown in Eqn. 3.8.

$$2C + S = 2(ab + ac_0 + bc_0 - 2abc_0) + (a + b + c_o - 2ab - 2ac_0 - 2bc_0 + 4abc_0) = a + b + c_o$$

(3.8)

The resulting signature matches the specification, which clearly indicates that the circuit is a full adder. As illustrated with this example, the AIG rewriting requires considerably fewer terms than the standard algebraic rewriting.

Figure 3.3: AIG rewriting of a full adder circuit from Figure 3.1.

**Data structure**: AIG rewriting is implemented in ABC with the polynomial data structure, type Pln\_Man\_t. Its main components include: 1) the AIG manager

(Gia\_Man) that represents the input design; and 2) two vector hash tables using type  $Hsh_VecMan_t$  are used for storing the constants and monomials. The hash tables of monomials include coefficient vectors and monomial vectors. When substitution is applied to the leading term, new monomials are created and the substituted one removed. For example, when ab + c + bd is substituted by a = b + d, the monomial ab is removed first, and b and bd are added to Pln\_Man\_t. During the process of adding the new monomials, the program will first check if these monomials already exist in Pln\_Man\_t; in this case only the coefficient of these monomials will be changed accordingly. In this example, two new monomials are generated by the substitution, namely  $b^2$ , reduced to b, and bd. Since bd already exists in the expression, the coefficient 1 of bd is replaced by 2, resulting in b + c + 2bd.

# 3.5 Comparison between GB Reduction and Rewriting

It should be clear from the above discussion that both methods, the GB reduction and the algebraic rewriting, are equivalent in the sense that they both perform polynomial reduction. The GB reduction scheme achieves polynomial reduction by division, in fact, performing Gaussian elimination. In contrast, algebraic rewriting does it by substituting the gate output variable by the polynomial expression of the gate's function. While the goal of GB reduction scheme is to reduce  $F = S_{out} - F_{spec}$ modulo the set of implementation polynomials G to 0, it can also be used to extract the arithmetic function by reducing  $S_{out}$  modulo G, and interpret the result as the functional specification of the circuit  $F_{spec}$ . In the algebraic rewriting scheme, the goal is to rewrite the output signature  $S_{out}$  to  $S_{in}$ , the expression in the primary inputs, and check if it matches the expected specification  $F_{spec}$ . If  $S_{in} = F_{spec}$ , the circuit is correct; otherwise it is faulty. Alternatively, as illustrated above, algebraic rewriting can be also applied to  $F = S_{out} - F_{spec}$ , as in the GB approach. Variable substitution of algebraic rewriting (line 9 of Algorithm 2) seems simpler than the main step of polynomial division of the GB reduction (line 8 of Algorithm 1). On the other hand, it requires additional multiplication of the terms and expansion into a sum of products. Hence, the complexity of these steps is comparable. Both methods avoid explicit computation of the Gröbner basis, but achieve it by different means. In the GB reduction it is done by setting the variable order in the ring so that all variables are in reverse topological order, which makes the implementation set G a Gröbner basis. In the algebraic rewriting scheme on the other hand, the polynomials  $f_i \in G$  are sorted in reverse topological order to effect the rewriting. As a result, both methods ensure that the polynomial base is a Gröbner basis. However, there are some essential differences between the two methods that affect their efficiency.

- The GB reduction scheme requires the *field polynomials J<sub>0</sub> =< x<sup>2</sup> − x >* to be added to the base G in order to keep the variables Boolean. This increases the size of the Gröbner basis and results in a larger search space in each iteration. Whereas in the rewriting scheme, the reduction by < x<sup>2</sup> − x > is solved in a simpler way, namely by lowering x<sup>2</sup> to x via a simple data structure (line 10 in Algorithm 2).