# Overcome the Limitations of Performance Parameters of On-Chip Antennas Based on Metasurface and Coupled Feeding Approaches for Applications in System-on-Chip for THz Integrated-Circuits

Mohammad Alibakhshikenari<sup>1</sup>\*, Bal S. Virdee<sup>2</sup>, Chan H. See<sup>3,4</sup>, Raed A. Abd-Alhameed<sup>5</sup>, Francisco Falcone<sup>6</sup>, and Ernesto Limiti<sup>1</sup>

<sup>1</sup> Electronic Engineering Department, University of Rome "Tor Vergata", Via del Politecnico 1, 00133, Rome, ITALY

<sup>2</sup> London Metropolitan University, Center for Communications Technology & Mathematics, School of Computing & Digital Media, London N7 8DB, UK

<sup>3</sup> School of Eng. and the Built Environment, Edinburgh Napier University, 10 Colinton Rd., Edinburgh, EH10 5DT, UK

<sup>4</sup> School of Engineering, University of Bolton, Deane Road, Bolton, BL3 5AB, UK

<sup>5</sup> Faculty of Engineering & Informatics, University of Bradford, Bradford, BD7 1DP, UK

<sup>6</sup> Electrical and Electronic Engineering Department, Public University of Navarre, 31006 Pamplona, SPAIN

# \*alibakhshikenari@ing.uniroma2.it

Abstract: This paper proposes a new solution to improve the performance parameters of on-chip antenna designs on standard CMOS silicon (Si.) technology. The proposed method is based on applying the metasurface technique and exciting the radiating elements through coupled feed mechanism. The on-chip antenna is constructed from three layers comprising Si.-GND-Si. layers, so that the ground (GND) plane is sandwiched between two Si. layers. The silicon and ground-plane layers have thicknesses of 20µm and  $5\mu m$ , respectively. The 3×3 array consisting of the asterisk-shaped radiating elements has implemented on the top silicon layer by applying the metasurface approach. Three slot lines in the ground-plane are modelled and located directly under the radiating elements. The radiating elements are excited through the slot-lines using an opencircuited microstrip-line constructed on the bottom silicon layer. The proposed method to excite the structure is based on the coupled feeding mechanism. In addition, by the proposed feeding method the on-chip antenna configuration suppresses the substrate losses and surface-waves. The antenna exhibits a large impedance bandwidth of 60GHz from 0.5THz to 0.56THz with an average radiation gain and efficiency of 4.58dBi and 25.37%, respectively. The proposed structure has compact dimensions of  $200 \times 200 \times 45 \mu m^3$ . The results shows that, the proposed technique is therefore suitable for on-chip antennas for applications in system-onchip for terahertz (THz) integrated circuits.

*Keywords:* On-chip antennas, metasurface, coupled feeding mechanism, terahertz (THz) systems-on-chip applications, CMOS silicon (Si.) technology, THz integrated circuits, ground (GND).

#### I. INTRODUCTION

With the recent development in mobile communications and silicon technology, interest in new advancement of radio frequency integrated circuits (RFICs) has enhanced, containing the representation of antennas for system on-chip (SoC) applications [1, 2]. On-chip antennas are an integral part of wireless sensor networks, in low-cost silicon IC sensors, and for data communication between ICs [3]. Integrated antennas eliminate the need for external transmission line connections, sophisticated packaging and therefore make feasible manufacture of cost-effective and compact microwave and millimeter-wave devices.

On-chip antenna is the last barrier for the true Systemon-Chip (SoC) solution, especially applying the Si. process [4-8]. The high permittivity and low resistivity of Si. substrate result in narrow bandwidth, low gain and low radiation efficiency of antenna. Various approaches have been presented to improve the performance of the on-chip antenna [9-12]. However, these techniques are costly as the designs are complex to implement or the antenna performance falls short of practical applications.

Proposed in this paper is a new but simple method to improve the performance parameters of on-chip antennas working on terahertz area. The antenna design is based on metasurface technology. In addition, the proposed structure is low profile, cost effective, and easy to manufacture.

## II. HIGH PERFORMANCE ON-CHIP ANTENNA

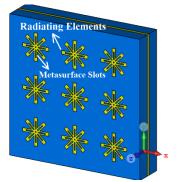

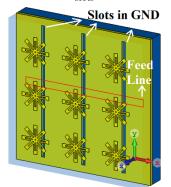

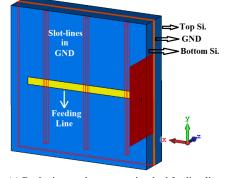

The proposed on-chip antenna design is constructed from three layers comprising silicon-ground-silicon layers, as shown in Fig.1. The two silicon layers that sandwich the ground-plane have a thickness of  $20\mu m$ , and the ground-plane has a thickness of  $5\mu m$ . On the top silicon layer, a  $3\times3$  array of asterisk-shaped radiating elements is implemented, as exhibited in Figs. 1 (a) and (b). Realized in the middle ground-plane layer are three slot lines that are aligned under the asterisk-shaped elements, as shown in Figs. 1 (b) and (c), which supress the surface waves and substrate losses.

To improve the antenna's performance parameters such as the impedance bandwidth and the radiation behaviour, the metasurface slots in optimized dimensions are etched on the asterisk-shaped elements, which enlarge the antenna's effective aperture area without affecting its dimensions. Therefore, the proposed configuration acts like a metasurface that essentially have positive effects on the radiation characteristics of the antenna.

To improve impedance matching and bandwidth a simple and novel feeding mechanism to excite the antenna was employed. This consisted of an open-circuited microstrip-line implemented under the bottom silicon layer. Electromagnetic signal applied to the opencircuited line is coupled to the asterisk-shaped elements on the top substrate via the slot-lines on the GND.

(a) Top view to show asterisk-shaped elements including metasurface slots

(b) Isometric view showing asterisk-shaped elements on the top Si. substrate, slot-lines in the GND layer, and open-ended microstrip feed line on the bottom silicon layer.

(c) Back view to show open-circuited feeding line Fig.1. On-chip antenna configuration.

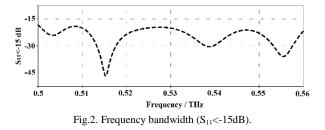

The reflection-coefficient of the proposed on-chip antenna in Fig.2 indicates that the on-chip antenna operates over the frequency band from 0.5-0.56 THz for  $S_{11}$ <-15dB, that corresponds to the fractional bandwidth of ~11.3%.

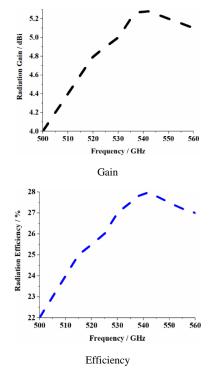

Gain and radiation efficiency responses of the proposed on-chip antenna structure are indicated in Fig.3. It demonstrates that the maximum gain and radiation efficiency are 5.3dBi and 28.15%, respectively, that are occurred at 540 GHz. The radiation characteristics over frequency are listed in details in the table I.

Fig.3. Radiation properties of the proposed on-chip antenna structure.

TABLE I. ON-CHIP ANTENNA RADIATION PROPERTIES

| Frequency (GHz) | Gain (dBi)    | Efficiency (%)  |

|-----------------|---------------|-----------------|

| 500             | 4 (minimum)   | 22 (minimum)    |

| 540             | 5.3 (maximum) | 28.15 (maximum) |

| 560             | 5.11          | 27.05           |

To enhance the validity of the proposed model, it is compared with the various publications. Table II lists the results. Obviously, the proposed structure exhibits higher performance parameters in comparison with the literature.

## III. CONCLUSION

A novel and simple technique is described that enhances the performance parameters of on-chip antennas implemented on CMOS Silicon substrate. The proposed technique utilizes the metasurface technology to increase the effective aperture of the antenna, which leads to improve its radiation properties. The antenna is excited by the coupling electromagnetic energy through slots in the middle ground-plane layer, which is sandwiched between the two silicon layers. This type of feeding suppresses the surface waves and substrate losses, which has caused to improve the antenna's impedance matching and its impedance bandwidth. It is shown that, the proposed technique overcomes the common drawbacks of narrow bandwidth and poor radiation specifications of on-chip antennas. The proposed technique is therefore suitable for on-chip antennas for applications in system-on-chip for terahertz integrated circuits.

| Ref.         | Antenna<br>Type                                         | Freq.<br>(GHz)/<br>BW<br>(%) | Gain<br>(dBi) | Eff.<br>% | Process              | Size<br>(mm <sup>2</sup> ) | Height<br>(mm) |

|--------------|---------------------------------------------------------|------------------------------|---------------|-----------|----------------------|----------------------------|----------------|

| [13]         | Patch Fed<br>Higher<br>Order<br>Mode DRA                | 341/7                        | 7.9           | 74        | 0.18-µm<br>SiGe      | 0.2                        | 0.5            |

| [14]         | On-chip 3D<br>(Yagi like<br>concept)                    | 340/12                       | 10            | 80        | 0.13-µm<br>SiGe      | 0.49                       | 0.11           |

| [15]         | Slot-Loaded<br>Magnetic<br>Loop<br>on SIW               | 340/7                        | 3.3           | 45        | 0.13-μm<br>SMOS      | 0.49                       | -              |

| [16]         | Patch                                                   | 280/2.<br>5                  | -1.6          | 21        | 0.13-μm<br>CMOS      | 0.2                        | -              |

| [17]         | Ring<br>Antenna                                         | 296/-                        | 4.2           | -         | 65-nm<br>CMOS        | 0.3                        | -              |

| [18]         | Slot Ring<br>Antenna +<br>Superstrate                   | 375/8                        | 1.6           | 35        | 45-nm<br>CMOS<br>SOI | 0.05                       | -              |

| [19]         | Ring<br>Antenna<br>with Silicon<br>Lens                 | 288/N<br>A                   | 18.3          | 65        | 65-nm<br>CMOS        | 12.56                      | 2.55           |

| [20] -<br>a  | Half-Mode<br>Cavity Fed<br>DRA                          | 135/13                       | 3.7           | 62        | 0.18-μm<br>CMOS      | 0.63                       | 0.25           |

| [20] -<br>b  | Half-Mode<br>Cavity<br>Fed Higher<br>Order<br>Mode DRA  | 135/7                        | 6.2/7.5       | 46/<br>42 | 0.18-μm<br>CMOS      | 0.72                       | 1.3/2.2        |

| [21]         | Slot Fed<br>Stacked<br>DRA (Two<br>DRAs +<br>Supporter) | 130/11                       | 4.7           | 43        | 0.18-μm<br>CMOS      | 0.72                       | 1.28           |

| [22]         | DRA                                                     | 135/11                       | 2.7           | 43        | 0.18-µm<br>CMOS      | 0.72                       | 0.6            |

| This<br>Work | Metasurface                                             | 540/11<br>.3                 | 5.3           | 28.<br>15 | CMOS                 | 0.04                       | 0.045          |

TABLE II. COMPARISON TABLE

#### ACKNOWLEDGEMENTS

This work is partially supported by innovation programme under grant agreement H2020-MSCA-ITN-2016 SECRET-722424 and the financial support from the UK Engineering and Physical Sciences Research Council (EPSRC) under grant EP/E0/22936/1.

#### REFERENCES

[1] P. V. Bijumon, Y. M. M. Antar, A. P. Freundorfer, and M. Sayer, "Dielectric Resonator Antenna on Silicon Substrate for System On-Chip Applications", IEEE Transactions on Antennas and Propagation, vol.56, no.11, pp.3404-3410, November 2008.

[2] M. Pons, F. Touati, and P. Senn, "Study of on-chip integrated antennas using standard silicon technology for short distance communication," in Proc. Eur. Conf. Wireless Technol., Oct. 2005, pp. 273–276.

[3] K. K. O et al., "On-chip antennas in silicon ICs and their application," IEEE Trans. Electron Devices, vol. 52, no. 7, pp. 1312–1323, Jul. 2005.

[4] D. Hou, Y. Xiong, W. Hong, W. Goh, and J. Chen, "Silicon-based On-chip Antenna Design for Millimeter-wave/THz Applications", IEEE Electrical Design of Advanced Packaging and Systems Symposium, pp.1-4, 12-14 Dec. 2011, Hanzhou, China.

[5] Kenneth K. O, K. Kim, B. A. Floyd, J. L. Mehta, H. Yoon, C. Hung, D. Bravo, T. O. Dickson, X. Guo, R. Li, N. Trichy, J. Caserta, W. R. Bomstad, J. Branch, D. Yang, J. Bohorquez, E. Seok, L. Gao, A. Sugavanam, J.-J. Lin, J. Chen, and J. E. Brewer, "On-Chip Antennas in Silicon ICs and Their Application", IEEE Trans. on Elec. Devices, vol. 52, no. 7, pp.1312-1323, July 2005.

[6] Houssemeddine Ben Elhaj Moussa, Bruno Barelaud, Georges Zakka El Nashef, and Edouard Ngoya, "Integrated On-Chip Antenna on Silicon for Millimeter-wave Applications", 2013 13th Mediterranean Microwave Symposium (MMS), 2-5 Sept. 2013, Saida, Lebanon.

[7] Y. P. Zhang, M. Sun, and L. H. Guo, "On-Chip Antennas for 60-GHz Radios in Silicon Technology", IEEE Trans. on Elect. Devices, vol. 52, no. 7, pp.1664-1668, July 2005.

[8] C. R. Trent and T. M. Weller, "Design and tolerance analysis of a 21GHz CPW-fed, slot-coupled, microstrip antenna on etched silicon," in IEEE AP-S Dig., vol. 1, 2002, pp. 402–405.

[9] A. B. M. H. Rashid, S.Watanabe, and T. Kikkawa, "High transmission gain integrated antenna on extremely high resistivity Si for ULSI wireless interconnect," IEEE Electron Devices, vol. 23, no. 12, pp. 731–733, Dec. 2002.

[10] K. T. Chan, "Integrated antennas on Si with over 100 GHz performance, fabricated using on optimized proton implantation process," IEEE Microw. Wireless Compon. Lett., vol. 13, no. 11, pp. 487–489, Nov. 2003.

[11] I. K. Itotia and R. F. Drayton, "Aperture coupled patch antenna chip performance on lossy silicon substrates," in Proc. IEEE Antennas Propag. Symp., Jul. 2005, vol. 1B, pp. 377–380.

[12] P. V. Bijumon, A. P. Freundorfer, and Y. M. M. Antar, "High gain on-chip dielectric resonator antennas using silicon technology for millimeter wave wireless links," in Proc. IEEE Canad. Conf. Elect. Comput. Eng., Vancouver, Canada, Apr. 2007, pp. 804–807.

[13] C.-H. Li and T.-Y. Chiu, "340-GHz low-cost and high-gain on-chip higher order mode dielectric resonator antenna for THz applications," IEEE Trans. THz Sci. Technol., vol. 7, no. 3, pp. 284–294, May. 2017.

[14] X.-D. Deng, Y. Li, C. Liu, W. Wu and Y. -Z. Xiong, "340 GHz on-chip 3-D antenna with 10 dBi gain and 80% radiation efficiency," IEEE Trans. THz Sci. Technol., vol. 5, no. 4, pp. 619–627, July. 2015.

[15] X.-D. Deng, Y. Li, W. Wu and Y. -Z. Xiong, "340-GHz SIW cavity-backed magnetic rectangular slot loop antennas and arrays in silicon technology," IEEE Trans. Ant. Propag., vol. 63, no. 12, pp. 5272-5279, Dec. 2015.

[16] R. Han et al., "A 280-GHz Schottky diode detector in 130-nm digital CMOS," IEEE J. Solid-State Circuits, vol. 46, no. 11, pp. 564–580, Nov. 2011.

[17] S. Jameson, E. Halpern, and E. Socher, "A 300 GHz wirelessly locked 2×3 array radiating 5.4 dBm with 5.1% DC-to-RF efficiency in 65 nm CMOS," in Proc. IEEE Int. Solid-State Circuits Conf. Tech. Dig., Feb. 2016, pp. 348–349.

[18] F. Golcuk, O. D. Gurbuz, and G. M. Rebeiz, "A 0.39-0.44 THz 2×4 amplifier-quadrupler array with peak EIRP of 3-4 dBm," IEEE Trans. Microw. Theory Techn., vol. 61, no. 12, pp. 4483–4491, Dec. 2013.

[19] J. Grzyb, Y. Zhao, and U. R. Pfeiffer, "A 288-GHz lens-integrated balanced triple-push source in a 65-nm CMOS technology," IEEE J. Solid-State Circuits, vol. 48, no. 7, pp. 1751–1761, Jul. 2013.

[20] D. Hou et al., "D-band on-chip higher-order-mode dielectricresonator antennas fed by half-mode cavity in CMOS technology," IEEE Antennas Propag. Mag., vol. 56, no. 3, pp. 80–89, Jun. 2014.

[21] D. Hou, Y.-Z. Xiong, W.-L. Goh, S. Hu, W. Hong, and M. Madihian, "130-GHz on-chip meander slot antennas with stacked dielectric resonators in standard CMOS technology," IEEE Trans. Antennas Propag., vol. 60, no. 9, pp. 4102–4109, Sep. 2012.

[22] D. Hou, Y.-Z. Xiong, W. Hong, W.-L. Goh, and J. Chen, "Silicon based on-chip antenna design for millimeter-wave/THz applications," in Elect. Design of Adv. Pkg. and Syst. Symp. (EDAPS), 2011, pp. 1–4.