# Alexoudi, T., Kanellos, G. T., & Pleros, N. (2020). Optical RAM and integrated optical memories: a survey. *Light, science & applications, 9*, 91. https://doi.org/10.1038/s41377-020-0325-9

Publisher's PDF, also known as Version of record License (if available): CC BY Link to published version (if available): 10.1038/s41377-020-0325-9

Link to publication record in Explore Bristol Research PDF-document

This is the final published version of the article (version of record). It first appeared online via Nature at https://doi.org/10.1038/s41377-020-0325-9 . Please refer to any applicable terms of use of the publisher.

### University of Bristol - Explore Bristol Research General rights

This document is made available in accordance with publisher policies. Please cite only the published version using the reference above. Full terms of use are available: http://www.bristol.ac.uk/red/research-policy/pure/user-guides/ebr-terms/

### **REVIEW ARTICLE**

### Open Access

# Optical RAM and integrated optical memories: a survey

Theoni Alexoudi<sup>1</sup>, George Theodore Kanellos<sup>2</sup> and Nikos Pleros<sup>1</sup>

### Abstract

The remarkable achievements in the area of integrated optical memories and optical random access memories (RAMs) together with the rapid adoption of optical interconnects in the Datacom and Computercom industries introduce a new perspective for information storage directly in the optical domain, enabling fast access times, increased bandwidth and transparent cooperation with optical interconnect lines. This article reviews state-of-the-art integrated optical memory technologies and optical RAM cell demonstrations describing the physical mechanisms of several key devices along with their performance metrics in terms of their energy, speed and footprint. Novel applications are outlined, concluding with the scaling challenges to be addressed toward allowing light to serve as both a data-carrying and data-storage medium.

### Introduction

Over the past decades, "storing light" has appeared as a rather controversial statement, given that a photon's inherent nature hinders its spatial confinement. The first research efforts in demonstrating optical memory functionality started as a fascinating experimental exercise, with the first optical memory being reported by means of a folded optical delay line<sup>1</sup> back in 1965. Two decades later, the first optical set-reset flip-flop (SR-FF) mechanism was launched in 1985, achieving response times of <1 ns<sup>2</sup>, while in the next few years, research efforts mainly focused on temporarily confining light to a continuous loop inside a medium<sup>1,3-5</sup>. As fiber optics gradually turned into a mainstream telecom transmission platform, the research interest in optical memories experienced a significant boost in view of the possible high-speed optical signal processing applications, with a variety of schemes such as optical delay lines<sup>6–9</sup>, fiber-loop-based and slowlight optical buffers<sup>10,11</sup> and, more recently, all-optical flip-flop (AOFF) devices being introduced for packet-level contention resolution purposes<sup>12,13</sup>.

Following the initial attempts to store light for packetlevel processing, optical memories have made significant progress during the last decade and managed to penetrate the area of bit-level storage, significantly expanding along the performance metrics, functionality and application perspectives. This progress has been greatly facilitated by the rapid advances in photonic integration<sup>14</sup> and the massive penetration of optics at interconnect segments closer to the CPU level<sup>15,16</sup>. At the same time, the wellknown memory-related bottlenecks in the fields of computing<sup>17-20</sup> and routing have served as the main motivating use-cases for transferring the speed and energy advantages of light technology to the memory domain, with the CPU-memory bandwidth bottleneck<sup>20</sup> and the more recent decline of Koomey's law<sup>21</sup> comprising just two indicative examples driving research toward optical random access memories (RAMs) and optical memories for non-Von-Neumann computing paradigms, respectively.

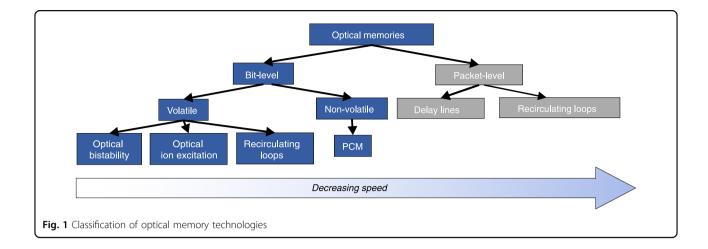

Figure 1 presents an overview of the most important categories into which current optical memories can be classified. Based on the size of the data information that is stored, i.e., a data bit or a complete data packet, optical

Correspondence: Theoni Alexoudi (theonial@csd.auth.gr)

<sup>&</sup>lt;sup>1</sup>Department of Informatics, Aristotle University of Thessaloniki, Thessaloniki, Greece

<sup>&</sup>lt;sup>2</sup>Department of Electrical & Electronic Engineering, University of Bristol, Bristol, UK

<sup>©</sup> The Author(s) 2020

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

memories can be categorized in (a) bit-level and (b) packet-level configurations, with packet-level buffering performed by more conventional and older delay line and recirculating loop technologies and as such not fitting into the scope of the current review article. Similar to electronic technology, optical bit-level memories can in turn be classified as either volatile or non-volatile structures, depending on whether the stored data are lost or maintained, respectively, when the power supply is switched off. Optical volatile memories can typically offer faster access times and higher speed operation compared to their non-volatile counterparts and form the core memory mechanism in the optical versions of the well-known and highly useful RAM cell architectures, again discriminated into two main categories: (a) the optical dynamic (DRAM) and (b) the optical static (SRAM) RAM, with their main difference lying in their requirement for refreshing (DRAM) or not (SRAM) the stored bit value. Optical SRAM layouts have thus far been implemented mainly by means of bistable optical devices 22-43, whereas the optical DRAM cells that have been reported rely on either lowspeed optical physical mechanisms such as ion excitation<sup>44–47</sup> or recirculating loop arrangements<sup>48,49</sup>. Optical non-volatile memories are a more recent addition to lightenabled memory technology, mainly taking advantage of the rapid progress experienced in the field of phasechange material (PCM) structures<sup>50-55</sup>, which have been shown to allow for permanent light storage in a continuously growing field of diverse applications.

In this article, we review the substantial progress witnessed in the field of integrated optical memory technologies, mainly focusing on bit-level volatile and nonvolatile optical structures and on roadmaps for transforming these elementary optical memory modules into practical optical RAM cell layouts. The paper is organized as follows: First, the basic approaches and principles applied to achieve light-based storage in general are presented, and the main technical system requirements in terms of memory are discussed. Then, the state-of-the-art optical memory technologies and concepts are reviewed, and their benefits in terms of energy, bandwidth and footprint are summarized. Following this, advanced memory functionality i.e., true optical RAM operation, is explained, and recent advancements are reported. Finally, an analysis is presented for the next steps that optical memory technologies must undertake to release a viable and practical alternative memory roadmap.

### How to store information with light

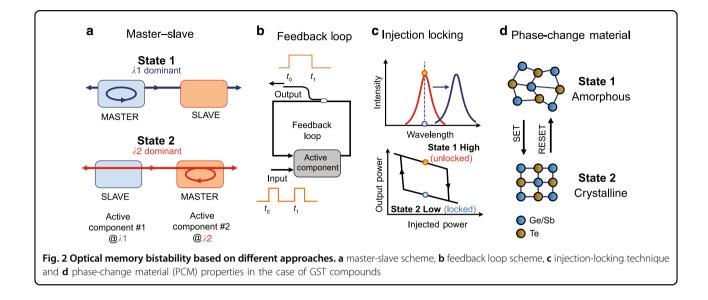

Although light has inherent disadvantages when considering buffering functionalities, as the neutral charge of photons makes it impossible to mimic the respective capacitor-based electronic memory layouts, the research community has devised several methods to enable lightbased storage. The most common approaches to achieving this rely on either the bistability of engineered optical resonances (artificial cavities), such as in refs.  $2^{2-36}$ , or the inherent bistable characteristics of devices stemming from their material properties<sup>37-43</sup>. Two main conditions should be applied to achieve optical bistability and consequently memory operation: the system should (a) provide at least two discrete, stable states that represent the logical one and logical zero and (b) allow switching between the two states under certain conditions. Figure 2 summarizes the four most popular categories of bistable memory devices, which rely on (a) the master-slave configuration, (b) the feedback loop scheme, (c) the injectionlocking technique and (d) phase-change materials. In the master-slave configuration (Fig. 2a), two active components that are usually either switches<sup>22,24,30</sup> or lasers<sup>30</sup> are placed in a coupled arrangement, forming an artificial cavity. In this case, the discrete memory states (i.e., logical value "1" or logical value "0") are represented by two different states of a certain light beam characteristic, such as the polarization or wavelength of the light beams emitted by the respective active components.

Figure 2a depicts the case where two different wavelengths are used to denote the different binary states. Each time, only one of the two available wavelengths can be dominant in the cavity, whereas the other remains suppressed. Assuming that wavelength  $\lambda_1$  corresponds to the logical value of "1" and wavelength  $\lambda_2$  represents the logical value "0" emitted by active component #1, State 1 refers to the cavity situation where light at  $\lambda_1$  dominates the cavity and suppresses wavelength  $\lambda_2$  emitted by active component #2. As long as State 1 is dominant, active component #1 serves as the "master", whereas active component #2 is the "slave", with the memory output signal obtained at wavelength  $\lambda_1$ . Conversely, in State 2, wavelength  $\lambda_2$  suppresses wavelength  $\lambda_1$ , and the memory output emits a signal at wavelength  $\lambda_2$ . Changing between the two states is accomplished by injecting external light at the appropriate amount of power and wavelength into the "master" component, suppressing its operation and allowing sufficient time for the "slave" device to recover to its equilibrium state. In this case, the wavelength emitted by the "slave" device can then reach the "master" device, acting as a holding signal that retains the suppression of the former "master" wavelength even if the external light injection stops. This type of scheme is usually employed for set-reset flip-flops (SR-FFs), which have also been employed in optical SRAM cells<sup>22,23</sup>. To date, theoretical studies on coupled schemes<sup>56</sup> have revealed that the switching time between two states is inversely proportional to the length of the cavity formed between the two active components, suggesting that an integrated solution has to be adopted to enable switching times in the picosecond regime.

Optical memories based on feedback loops, shown in Fig. 2b, require a single active component along with an external cavity usually implemented by loop configurations that feed the output signal back to the active element either through a fiber<sup>26,27,48,49</sup> or by using an integrated bent waveguide<sup>36</sup>. The cavity acts as the memory element, enabling bit storage, and a tap of the cavity allows for monitoring the logical state of the feedback loop, i.e., the memory content. The active element employed so far is a  $1 \times 2$  optical switch<sup>26,27,31</sup> that either feeds the loop with the switched signal supporting its recirculation or blocks the recirculation by switching the signal out of the loop. This type of optical memory has been demonstrated in SR-FF schemes<sup>33</sup> using independent and discrete set and reset externally injected signals but has also been employed to build toggle flip-flops (T- $(FFs)^{26,27,31}$  by applying a single external pulsed signal, as depicted in Fig. 2b. The demonstrated T-FFs<sup>26,27,31,32</sup> follow an electronics-borrowed approach where two options are available: (a) either maintain the current state's value for another cycle in the case of a logical zero or (b) toggle the value (negate it) at the next clock edge in the case of a logical one at each input. In that case, the loop retains its state when the incoming signal is blocked; otherwise, the memory content is changed, yielding a T-FF functionality that is highly useful for shift registers and counters<sup>32,57</sup>.

On the other hand, the injection-locking technique widely used in lasers can provide optical memory bistability<sup>37,42,43</sup> by forcing specific light characteristics of the lasing device to lock to the respective characteristics of an externally injected optical beam. The light characteristics that can be applied through the locking mechanism are usually the (a) wavelength<sup>37–39,42,43</sup>, (b) polarization state<sup>40,41</sup>, and (c) propagation direction<sup>30,33,35</sup>. In this case, memory bistability is observed as the interchange of the laser emission states between a free-running mode (unlocked/high state) and an injection-controlled mode

(injection-locked/low state). The principle of operation in the case of wavelength bistability is graphically represented in Fig. 2c. Initially, the laser emits at its freerunning state signal, shown in red in Fig. 2c. In the presence of a wavelength-detuned input injection signal, called the control signal, the laser starts emitting at the injection wavelength (blue in Fig. 2c) and not at its freerunning mode wavelength when the control power increases above a specific threshold. As the optical power of the control signal decreases to a certain value at this state, the device enters a hysteresis loop retaining this emission state even when the control signal optical power is decreased to a certain cut-off level. Figure 2c illustrates an indicative hysteresis loop formed by a laser device assuming a given wavelength detuning. As is evident, when the optical power of the injected signal falls below this cut-off level, the laser emission returns to its freerunning "unlocked" state. Consequently, the laser emission output has two states, i.e., locked (low) and unlocked (high), which depend on the ascending or descending direction of the injection signal power, and the memory operation can be achieved when operating within the bistable range of the laser device. Similarly, memory bistability can be achieved by means of polarization  $^{40,41}$  by interchanging the polarization state (orthogonal or vertical polarization) of the injected optical signal, while in the case of the propagation direction, the light in the device can be forced to circulate either to the clockwise (CW) or to the anticlockwise (ACW) propagation mode<sup>30,33,35</sup> by setting the injected external signal in the appropriate direction.

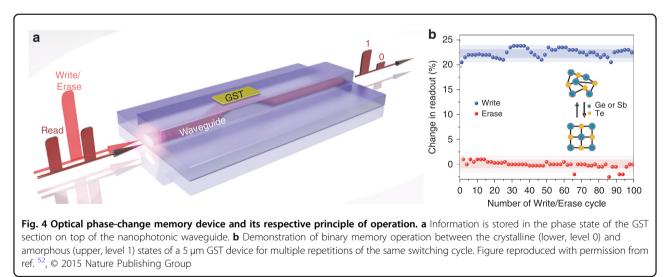

Another approach to enabling optical memory bistability relies on the exploitation of the physical properties of the optical phase-change materials (O-PCMs)<sup>52-55</sup>. O-PCMs have emerged as a unique class of materials that can exhibit large changes in their optical properties (index change  $\Delta n > 1$ ,  $\Delta \kappa \sim$  order of magnitude) in response to an external stimulus (i.e., temperature, applied voltage or ultra-fast optical excitation). Most established O-PCMs for optical memories are chalcogen-based alloys such as Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (commonly known as GST), in which the material undergoes transitions between its amorphous and crystalline states. An example of the principle of operation of a PCM-based optical memory is shown in Fig. 2d. In this recently introduced all-optical PCM memory<sup>52</sup>, a small patch of GST loaded on top of a silicon-nitride waveguide is used, and memory bistability is triggered by injecting optical pulses that can lead the thin film to adopt either an ordered crystalline or disordered amorphous state. In Fig. 2d, different colors represent different atoms, such as Ge, Sb, and Te, in the GeSbTe compound<sup>52</sup>. The phase of the GST element affects the optical properties of the underlying waveguide such that the specific phase and subsequently the memory content can be concluded by monitoring the intensity of the propagating light at the output. In the crystalline state, the GST is more absorptive, inducing strong attenuation to the propagating light, which results in low intensity at the output that corresponds to the logical "0". On the other hand, in the amorphous state, the absorption is reduced, allowing for high-intensity pulses at the output and yielding a logical value of "1" at the memory output. Switching between the two phase states occurs when high-intensity optical pulses are injected and, based on their total energy, can initiate either amorphization (write) or crystallization (erase). It is important to note that this type of memory element can also be configured to support multiple intermediate absorption levels between its two extreme states, allowing for multi-level operation and multi-bit storage properties.

### State-of-the-art optical memory technologies

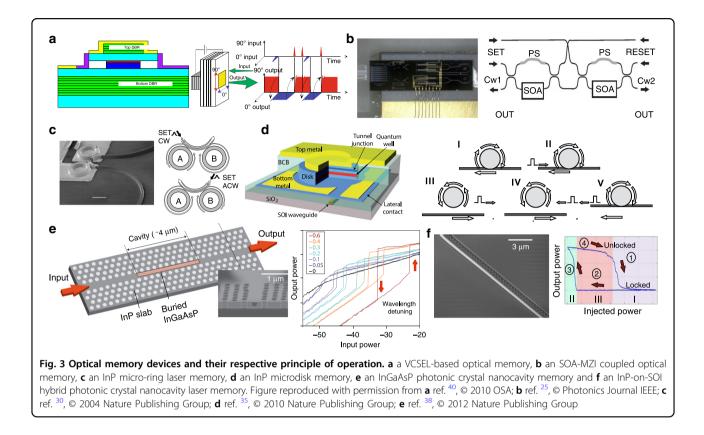

In this section, we review the current state-of-the-art optical memory technologies. Figure 3 summarizes the most popular optical volatile memory technologies that have been successfully pursued toward delivering light-based storage, relying mainly on (a) VCSELs, (b) semi-conductor optical amplifiers (SOAs), (c) InP coupled ring lasers, (d) an InP microdisk laser, (e) InP buried hetero-structure (BH)-PhC nanocavity switches, and (f) hybrid InP-on-SOI PhC lasers. Figure 4 presents the non-volatile PCM optical memory technology platform and its main principle of operation.

### Vertical cavity surface emitting lasers (VCSELs)

The first optical memory demonstration based on a bistable vertical cavity surface emitting laser (VCSEL) was reported in 1991 58. Since then, significant research efforts have been invested toward achieving VCSEL-based memories<sup>40,41,58-61</sup>. The VCSEL structure for polarization bistability at the 1.55 µm wavelength region and its respective principle of operation are shown in Fig. 3a. It exploits the polarization bistability, which is controlled through the injection of an external signal with an appropriate power and polarization direction (orthogonal or vertical), such that the polarization state of the VCSEL output signal follows the polarization state of the injected optical pulse. In this way, the memory content (i.e., logical state "0" or "1") of the VCSEL optical memory is identified based on the polarization state of the output signal. Polarization bistable 980 nm VCSEL-based memories have been demonstrated with 20-Gb/s RZ and 40-Gb/s NRZ optical pulses 40 at slower repetition periods. enabling multi-bit memory implementations<sup>61</sup>. The main advantages of polarization-bistable VCSELs include (a) their potential for high-speed memory operation<sup>62</sup>, being able to handle up to 40 Gb/s optical pulses, (b) their attractive properties for logic gate functionalities<sup>63</sup>, (c)

their low-energy consumption requirements (~105 fJ for 40 GHz operation<sup>40,41</sup>) compared to other types of bistable laser diodes, stemming from their lower bias current requirements<sup>63</sup>, and (d) their established and mature laser technology platform, which can form the basis of a reliable optical memory solution. Among their main limitations are certainly the relatively increased footprint requirements, as only the active square mesa corresponds to ~36  $\mu$ m<sup>262</sup>, and the need for a carefully controlled polarization state and alignment, especially when targeting multi-bit integrated modules.

### Semiconductor optical amplifier (SOA)-based schemes

In the early 2000s, several AOFF demonstrations were introduced relying on semiconductor optical amplifier (SOA)-based lasers or switches performing in master-slave configurations and exploiting well-known non-linear physical phenomena such as gain saturation<sup>64,65</sup> and

polarization-dependent gain saturation in SOA-based switches<sup>66,67</sup>. These demonstrations were implemented with discrete fiber-pigtailed components, with the first integrated AOFF appearing in 2006<sup>68</sup>. This AOFF utilized hybrid silica-on-silicon integration technology and a coupled SOA-MZI-based architecture 68 and mainly targeted all-optical packet switching applications to facilitate routing and forwarding directly in the optical domain<sup>12,13</sup>. Bit-level optical memory implementations were demonstrated shortly after utilizing cross-phase modulation (XPM) phenomena in SOA-MZIs<sup>22</sup>, crossgain modulation (XGM) in coupled SOAs<sup>23,24</sup> or SOAbased coupled ring lasers<sup>32,69</sup>. The transfer of this AOFF scheme into its InP-based monolithically integrated version, which was then also employed in true optical RAM cell setups, was only recently demonstrated<sup>25,70</sup>, reporting 10 Gb/s operation and a drastic footprint reduction of 97.8%% compared to its hybrid-integrated predecessor<sup>68</sup>. A photo of the monolithic integrated device and its principle of operation are shown in Fig. 3b, illustrating that it follows a master-slave configuration, with the two coupled SOA-MZIs being powered by two external continuous-wave (CW) input signals CW1 and CW2 and the logical value of the memory cell being determined by the wavelength of the dominant CW signal. Other AOFF schemes based on SOA-based DFBs<sup>71</sup>, SOAs in combination with DFB laser diodes<sup>72</sup>, loop mirror setups<sup>73</sup>, and feedback loops<sup>34,36</sup> have also been presented. Among the main benefits of SOA-based technologies in optical memory implementations  $^{22-27,34,36,49,64-73}$  are (a) their enhanced maturity level and flexibility characteristics that, in many cases<sup>22-24</sup>, allowed for the proof-of-concept demonstration of novel memory concepts prior to proceeding to their more compact and integrated versions<sup>25,36</sup> and (b) their high-speed potential, having already resulted in 10 Gb/s memory line rates<sup>70</sup> and being theoretically predicted to allow up to 40 Gb/s operating speeds even in optical SRAM cell arrangements<sup>56</sup>. However, their energy and footprint drawbacks probably critically affect its practical perspectives: SOA-based AOFFs require very large amounts of energy for both SOA biasing  $(\sim 120 \text{ pJ}^{25} \text{ and } \sim 180 \text{ pJ}^{70})$  and for optically switching between set and reset states ( $\sim 3 \text{ pJ}^{25}$ ,  $\sim 0.5 \text{ pJ}^{70}$ ), with the current footprint requirements hardly going below a few mm<sup>2</sup>.

### (Micro) ring lasers

A fast, low-power AOFF-integrated memory based on coupled micro-ring lasers exploiting the injection-locking technique was reported 30 in 2004, with its principle of operation shown in Fig. 3c. By connecting two ring lasers together via a waveguide, as depicted in Fig. 3c, two inherent lasing modes can be exploited to create a system where the master micro-laser injection locks the slave laser under certain conditions and defines the direction of the propagating light, dictating in this way two possible stable states: (a) laser light traveling in the clockwise (CW) direction and (b) laser light in the anticlockwise (ACW) direction. To switch states, light close to the lasing characteristics in terms of the wavelength and polarization needs to be injected into the waveguide connecting the lasers to set both lasers to lase simultaneously in either the CW or ACW direction. Alternative AOFFs and optical memory demonstrations relying on semiconductor ring lasers have also been suggested<sup>33,74,75</sup> following the rationale that the cavity should support two counter-propagating directional modes. The first demonstration was a novel single semiconductor microring laser employing a retro-reflector cavity to enable 2bit optical storage while achieving fast ON/OFF switching times<sup>74</sup>. Another semiconductor ring laser was also proposed by CNIT in 2013, who reported high-speed operation at 10 Gb/s and an improvement in the switch-ON times up to 10 ps<sup>33</sup>. The proposed micro-ring lasers<sup>30</sup> can provide electrically pumped optical memory implementations, also requiring, however, an additional DC current bias to tune the resonant frequencies of two lasers close to each other<sup>30</sup>. Although integrated ring laser schemes can offer some attractive advantages such as (a) multi-Gb/s operational speeds (10 Gb/s 33) and fast switching times of 20 ps<sup>28,30</sup> and (b) high-output-signal extinction ratio values that can reach almost 40 dB<sup>74</sup>, their main drawbacks remain (a) the total energy consumption accounting for several pJ ( $\sim 1.2 \text{ pJ}^{30}$  and 54 pJ<sup>33</sup>) and being mainly dominated by the bias current  $(30 \text{ mA}^{30})$ ,  $\sim$ 200 mA<sup>33</sup>) and (b) their large footprint, occupying more than  $1000 \,\mu\text{m}^2$  <sup>74</sup> and reaching, in some cases<sup>33</sup>, even several mm<sup>2</sup>.

### Microdisk laser

An ultrasmall, low-power, electrically pumped AOFF memory on a silicon chip was introduced by IMEC in 2010<sup>35</sup>. The AOFF relied on a single microdisk laser with a diameter of 7.5 µm coupled to a silicon-on-insulator (SOI) wire waveguide. Figure 3d shows a schematic of the microdisk laser and its principle of operation, which again exploits the propagating light direction to designate an AOFF state, relying on the interchange between the clockwise (CW) and anticlockwise (ACW) propagation directions of the whispering gallery modes (WGMs) supported by the microdisk. Assuming that the microdisk laser works initially in the CW dominant state (Fig. 3d–I), the ACW mode is suppressed, and the optical power measured at the left side of the SOI bus waveguide is high. When an optical reset pulse is injected (Fig. 3d–II), it will invoke the ACW mode, which will be retained even after the reset pulse has passed through the microdisk laser, as shown in Fig. 3d–III. In this case, the power monitored at

the left side of the SOI waveguide becomes low. Switching back to the CW dominant state can be achieved by injecting an optical set pulse from the right side of the SOI waveguide, as shown in Fig. 3d-IV,V<sup>35</sup>. Microdisk-laser-based memories comprise a highly compact integrated memory scheme that has low switching power requirements (1.8 fl<sup>35</sup>) and fast switching times (~60 ps<sup>35</sup>) but requires additional power for thermal tuning (~0.8 mW/ bit<sup>35</sup>) that increases the total energy consumption.

### InP buried heterostructure (BH) photonic crystal (PhC) laser/ nanocavity

Significant research efforts have been invested in recent years in investigating (a) InP BH-PhC lasers<sup>37</sup> targeting all-optical signal processing and next-generation optical packet switching systems and (b) nanocavities<sup>38,39</sup> toward achieving successful optical memory operation for various types of optical processing, including network routing. In 2011, the first optically pumped PhC laser-based AOFF was introduced relying on a wavelength injection-locking technique in an InGaAsP/InP BH-PhC laser that exhibited fast switching times of 60 ps and switching powers in the range of ~20–70  $\mu W^{37}.$  A significant step in the advancement of optical memory was performed in 2012, when a BH-PhC nanocavity again integrated in InGaAsP platform material was used to demonstrate optical memory bistability with a record-low static energy consumption on the order of 30 nW<sup>38</sup>. Figure 3e shows a cross-sectional electron micrograph image of a fabricated sample, the respective hysteresis response when the laser wavelength was detuned by an offset *d* from its resonance, and the output power  $(P_{out})$  versus the input power  $(P_{in})$ for different wavelengths. The proposed BH-PhC nanocavity memory was tested with short pulses that can, in principle, lead to attractive memory speeds of 40 Gb/s<sup>38</sup>; however, the switch-OFF time reported was on the order of 7 ns owing to the slow carrier relaxation time in the cavity. This technology was also the first to demonstrate high-integration-density memory setups exploiting wavelength-division-multiplexing<sup>39</sup> and yielding a 128-bit storage capacity<sup>39</sup>. Recently, an InP photonic crystal nanocavity with an embedded InGaAsP active region demonstrated an all-optical memory with only 2.3 nW operating power requirements<sup>76,77</sup> and unlimited storage time. Among the most important advantages of the InP BH-PhC nanocavity-based memory technology are certainly (a) the ultra-low-energy consumption and (b) the proven capability to produce multi-bit photonic memory chips and high integration, with the main drawback thus far being the rather long switch-OFF time, which has most likely restricted their application to high-speed data traffic.

### Hybrid InP-on-SOI photonic crystal (PhC) laser

Photonic crystals (PhCs) represent a disruptive solution toward low-power nanophotonic circuitry, with the heterogeneous integration of PhC lasers having also been successfully employed for optical memory operation<sup>42,43,78</sup>. The first InP-on-SOI PhC laser-based memory setup was demonstrated for the first time in 2013 using an optical pumping scheme and reporting on the >2 s storage capability<sup>78,79</sup>. More recently, this laser structure was shown to perform successfully even with true pseudorandom bit sequence (PRBS) data patterns in both fundamental logic functionalities, i.e., gating<sup>77</sup> and latching<sup>42</sup>. Figure 3f shows the PhC nanocavity laser device and its principle of operation when relying on wavelength bistability through injection locking, depicting an indicative hysteresis loop formed for a given wavelength detuning. The device requires a constant optical bias signal and operates as a set-reset AOFF, taking advantage of the three discrete areas of injection signal optical power levels, as shown in Fig. 3f: Area I, where the injection power levels allow for the set operation, as the laser output is changed from a free-running (unlocked) to an injection-controlled (locked) state; Area II, where the injection power levels are below a certain threshold, enabling the reset operation, i.e., the laser output returns to its free-running (unlocked) state, and Area III, where the injection power levels cover the bistable range and enable the storing operation, because the laser emission retains its previous state. Hybrid InP-on-SOI PhCs combine some important advantages for memory applications as they can satisfy at the same time three critical requirements: (a) low footprint (6.4  $\mu$ m<sup>2</sup>), (b) low-energy consumption (13 fJ) and (c) high-speed bit-level operation, which have all been already verified experimentally at up to 10 Gb/s with the true data traffic<sup>43</sup>. Considering that this memory technology can, in principle, be migrated to an electrically pumped scheme similar to the respective electrically pumped PhC laser nanocavities demonstrated more recently<sup>80</sup>. This platform seems to hold all the necessary credentials toward promising optical memories for real application needs.

### Other optical bistable memory technologies

Several optical memory demonstrations employing bistable laser diodes<sup>81–84</sup> and injection locking in Fabry–Perot (FP)<sup>85,86</sup>, DFB<sup>87</sup> or DBR lasers<sup>88</sup> have also been presented. Memory schemes with V cavity<sup>89</sup> and modulated-grating Y branch<sup>90</sup> lasers as well as symmetric Mach–Zehnder switches with 2D photonic crystals were also exhibited<sup>91</sup>. Nevertheless, the majority of these designs are relatively complex or require difficult activepassive integration techniques or high currents.

### Ion excitation and recirculation loops

In addition to the volatile optical memory schemes that have been analyzed thus far and rely on some type of bistability-induced latching mechanism, there have also been alternative volatile optical memory layouts demonstrating the exploitation of a storage mechanism closer to the principle of electronic capacitor-based memories. Erbium-doped<sup>47,92</sup> or erbium-ytterbium-doped<sup>45</sup> fiber absorption and fluorescence properties take advantage of the optically induced Er ion excitation to store information in the form of an excited state, which, however, decays after a few milliseconds, resembling the behavior of the electronic capacitor discharge. Identifying this correlation, these schemes have been successfully proposed for mimicking electrical dynamic random access memory (DRAM) circuitry and demonstrating respective optical DRAM cell layouts<sup>44-47</sup>. Similarly, alternative volatile optical memories for optical DRAM setups were demonstrated using SOA-based fiber loops<sup>48,49,93</sup>, where again a memory refresh operation had to take place by rewriting the bit that circulates in the loop and inevitably had its quality degraded after a certain amount of recirculation. Although these layouts comprise scientifically interesting attempts to transfer electronic DRAM functions directly in the optical domain, their fiber-based implementation thus far comprises a significant limiting factor in their practical application perspectives, revealing a rather limited maturity and increased power consumption requirements.

### Optical phase-change material (O-PCM) memories

Optical phase-change materials (PCMs) have emerged in recent years as a unique class of material platforms with great promise for non-volatile integrated photonic memory applications 50-55. PCMs can switch between the amorphous and crystalline phases by applying only short optical pulses with very low energy, being able to retain their new state for very long times. At the same time, their amorphous or crystalline state is associated with different light absorption levels, allowing their translation into optical memory functions by simply encoding the stored material phase into the power level of propagating light. The transition between the two phases can be performed on a picosecond to sub-nanosecond timescale for amorphization and on a sub-nanosecond to nanosecond timescale for crystallization. In 2015<sup>50</sup>, an all-photonic, non-volatile memory based on Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) phasechange material was proposed for the first time, performing at 1 GHz optical clock frequencies and allowing for all-optical multi-level and multi-bit memory capabilities. As illustrated in more detail in Fig. 4a, information is stored in the phase state of the GST section that is placed on top of the nanophotonic waveguide. Both reading and writing of the memory can be performed with ultrashort optical pulses, utilizing the interaction between the evanescent field of the guided light and the GST material. During the read operation, a weak optical probe pulse is employed to obtain the material phase encoded onto the power level of the probe pulse, while the write and erase operations require the use of intense optical pulses that are responsible for enforcing a phase transition within the GST. As shown in Fig. 4b, the crystalline state of GST (level 0) results in higher absorption levels and, as such, increased attenuation compared to its amorphous state (level 1). As such, the data are stored in different material phases, finally translating into a different attenuation factor, allowing its content to be finally read at the amount of probe light transmitted through the waveguide. This principle has been utilized in ref.<sup>51</sup> to demonstrate a fast non-volatile GST-based PCM memory with a capacity of 5 bits, occupying an area of only  $4 \times$  $1.3 \,\mu\text{m}^2$ , while the speed was pushed close to 1 GHz in the all-optical memory cell presented in ref.<sup>52</sup> using only 13.4 pJ. As such, PCM-based optical memories offer some highly attractive benefits, which include (a) their small footprint<sup>51</sup>, (b) the broadband optical transparency<sup>53</sup>, (c) their ability to carry out the multi-bit and multi-level memory operation 52-54, (d) their compatibility with silicon processing  $5^{5}$ , (e) the ultra-low energy requirements and, obviously, (f) their non-volatile nature, which has triggered a series of new and highly interesting applications, including their use as synaptic elements for neuromorphic computing architectures<sup>94,95</sup>. Their rather limited operational speed can be considered as among their drawbacks, although its non-volatile characteristics direct its employment in application fields where multi-GHz operation is not necessarily considered as a prerequisite.

Of all the above proposed solutions, the VCSEL-based and SOA-based memory schemes present the most mature volatile optical memory implementations, as both have been well-established commercial optical technologies for more than two decades. With this taken into account and with consideration of the fact that the ultimate target for non-volatile memories is to reach the functional level of SRAM and DRAM circuitry, it is no surprise that the first demonstration of optical SRAMs<sup>22</sup> was indeed accomplished with the mature SOA-based technology. Silicon- and PhC-based memory technologies have shown great potential to significantly improve the footprint, speed and energy consumption over VCSELand SOA-based memories and form the dominant volatile optical memory scheme of the future; however, they are both more recent technological platforms necessitating a few more steps to reaching the maturity level required by multi-bit optical RAM prototypes. When non-volatile optical memory setups are considered, this seems to be the stronghold of PCM-based optical structures, as they

feature ultra-low footprint and multi-level memory capabilities that have already been successfully employed in several novel application fields<sup>94–98</sup>.

## From elementary optical memory cells to optical random access memories (RAMs)

The main performance metrics related to memory functionality and characteristics are summarized in Box 1, whereas Box 2 provides a brief overview of the different application segments that have been addressed thus far by optical memory technologies. Although non-volatile optical memories seem capable of penetrating their respective application targets without requiring any additional circuitry, most of the volatile memory application areas necessitate the employment of more advanced memory schemes with random access functionality on top of the simple storage mechanism. The random access operation goes beyond the simple latching operation offered by elementary volatile optical memories and is typically provided by SRAM<sup>22-25,70,99</sup> and DRAM<sup>48,93</sup> circuits, suggesting that volatile optical memory layouts have to proceed along their migration from elementary AOFFs toward complete optical RAMs with controllable access at any random time to form reliable alternatives for practical use in real application cases. This section provides a brief analysis of how elementary volatile memories can scale into RAM cell layouts by simply enriching their design with optical access gating functions.

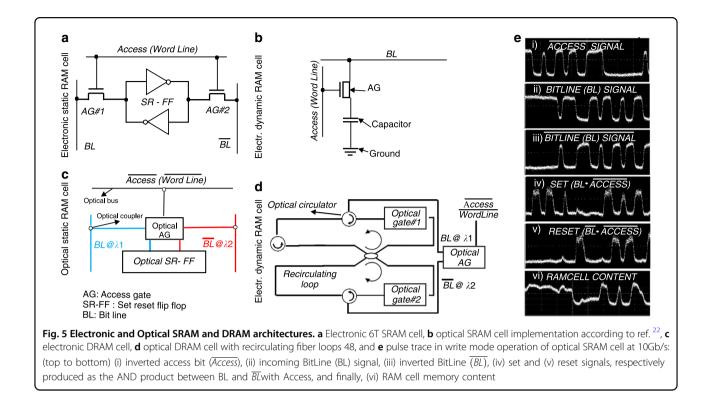

The first attempts toward deploying optical RAM cells were inspired by the architectural layouts of the respective electronic SRAM and DRAM cells. Figure 5a depicts the standard 6T electronic SRAM cell that comprises a bistable transistor-based structure typically made of two back-to-back connected CMOS inverters. These crosscoupled inverters form the AOFF mechanism, i.e., the SR-FF, and comprise the main memory cell used for bit storage. An AOFF, as the basic storage circuit, has two stable states ("logical zero" or "logical one") that alternate through external input signals (i.e., set/reset in the case of SR-FF). However, to migrate to advanced RAM functionalities, additional gating circuitry is required apart from the AOFF to enable communication between a memory and its environment through the read/write functions. The random access operation is provided by two access transistors that are additionally employed as access gates (AGs), controlling the communication of the memory cell with the "outer world" depending on the applied access (word line) signal<sup>100</sup>, which designates whether the memory cell has been selected to perform the write or read functionality. Figure 5b depicts the standard electronic DRAM cell, which employs a simple capacitor instead of a latch as its main memory cell and one additional transistor that acts as an AG to activate the data.

### Page 9 of 16

### Box 1 Basic performance parameters of memory units

The long-term experience obtained from using electronic memory devices outlines the following parameters as the most critical performance indicators for the practical perspectives of any optical memory technology:

### Memory bandwidth

This parameter is defined as the rate at which data words can be retrieved from or stored in an optical memory. Today, state-of-the-art chip multiprocessors (CMPs) exhibit limited bandwidths of 20 GB/s<sup>122</sup> and 8.5 GB/s that correspond to 160 Gb/s and 64 Gb/s for cache and DRAM access, respectively. At the same time, high-performance state-of-the-art SRAM line rates do not exceed  $4-4.6 \text{ GHz}^{101,123}$ . Photonic solutions seem to hold the potential for higher bandwidth values but have thus far been restricted solely to interconnect implementations<sup>124–126</sup>.

#### Energy efficiency

This parameter is usually expressed in mW/Gb/s or pJ/bit at a certain operating frequency and emerges as a key factor toward developing multi-bit optical memories. Unlike electronic memories that require more energy to reach higher bit rates, optics offer bit-rate transparency, as their operating frequency is irrespective of the required energy.

### Integration density

This parameter appears to be the most important factor when moving to high-capacity multi-bit memory banks and is also associated with the footprint of the device. Footprint is defined as the area occupied by a device, calculated as width  $\times$  height in the case of a 1-bit memory cell. In electronics, the scaling of CMOS transistors has led to modern IC chips with more than one billion transistors, allowing for high-density SRAMs. For example, in state-ofthe-art 22 nm technology<sup>101</sup>, a bit cell footprint of  $0.092 \,\mu\text{m}^2$  can enable high array densities up to 6.7 Mb/mm<sup>2</sup>. High-density electronic SRAM bit cells have already been reported, achieving 0.027  $\mu$ m<sup>2</sup> and 0.031  $\mu$ m<sup>2</sup> bit cell sizes in 7 nm<sup>119</sup> and 10 nm<sup>12</sup> processes, respectively, corresponding to 23.6 Mb/mm<sup>2</sup>. The integration density in the case of optical memories is tightly related to the fabrication technology employed, but obviously, the miniaturization of photonics has not yet reached the maturity level of electronics, whereas the simultaneous optimization of the performance and footprint in optical memory layouts has just begun. Thus far, the highest integration density in optical memory cells reported is 128 b/mm<sup>39</sup>. Recently, PCM memories with a capacity up to 5 bits<sup>5</sup> have been presented, occupying  $4 \times 1.3 \,\mu\text{m}^2$ , corresponding to a potential integration density of 8 kb/mm<sup>2</sup>, whereas a plasmonic photonic memory<sup>112</sup> has presented an unprecedented low footprint of  $0.0025 \,\mu\text{m}^2$ , holding the potential for even higher integration densities in the future.

### Access time

This term is defined as the time delay between a request to access a data bit and the successful completion of that attempt. On an electronic memory cell basis, this time is dominated by the RC delay of the transistor employed in the memory architecture and can also be expressed as 1/(bit rate), representing the actual time required to switch-on the transistor. State-of-the-art high-performance 6T SRAM cells based on Tri-Gate technology exhibit an access time of ~200 ps. Moving to more complex systems (i.e. array level, system level), the access time increases to several ns as the access time accumulates delays due to different resistances and capacitances present in the memory system. Optical bit-level memory implementations already demonstrate access time of the optical memory cell unit without including, of course, any propagation time or any latency associated with additional functions.

### Box 2 Applications of optical memory technologies

Drawing from the vast experience with the diverse applications of electronic memory technologies, optical memories have gradually penetrated into multiple application sectors that include processing, routing, and computing, as follows:

Optical digital signal processing and optical Boolean logic This area involves the deployment of the necessary optical building blocks for realizing the complete toolkit of elementary digital processing electronic circuitry directly in the optical domain, including among others of all different types of flip-flops, shift registers and counters. Set-reset flip-flops (SR-FFs) have been implemented by a great variety of bit-level optical memory technologies<sup>22–36</sup>, while more advanced D-type<sup>32</sup> and toggling AOFFs<sup>26,27,31,32</sup> have also been realized. Shift register and bit counter configurations that require the cascaded employment of multiple AOFFs have been demonstrated, mainly relying on VCSEL-<sup>40,63</sup> and SOA-based<sup>32,57</sup> memory setups. This application area primarily aims to replicate well-known functions and layouts at much higher operational speeds toward enabling true processing via optics. In addition to the performance parameters described in Box 1, this application segment requires a solid cascadability potential of the AOFF technology.

## Contention resolution and buffering in optical packet switches (OPSs)

Contention resolution refers to the procedure carried out in packet switched networks to avoid a collision between incoming data packets that require, at the same time, the same router output port, which would result in non-recoverable signal degradation and subsequently in the loss of information. The most typical way to resolve contention relies on the use of buffers to delay one of the two contending packets until the desired outgoing port again has an available timeslot. Realizing optical buffers for storing optical packets in OPS fabric demonstrations was widely researched in the early 2000 s, often residing in the areas of recirculating fiber loops<sup>3-5</sup> or fiber delay lines<sup>6-9</sup> to circumvent the absence of true optical RAM buffers. However, these setups can offer only a limited buffering time; hence, the quest toward real optical RAM buffers soon became a necessity and was pioneered in a big R&D initiative in Japan<sup>36-39,11</sup> promoting for the first time the use of InP photonic crystal nanocavities for packet buffering purposes in OPS fabrics. Alternative contention resolution methods have used optical FFs to provide alternative wavelengths toward triggering wavelength conversion circuits and resolution in the wavelength domain<sup>12,13</sup>

### Address look-up table and forwarding

These functions usually take place at a router to identify the destination address of the incoming data and to force the data to leave through the correct router outgoing port. Address look-up involves a procedure where the incoming address is compared with a set of possible addresses stored locally in the router, while forwarding indicates the procedure where the address matching is associated with the router outgoing port that has to be activated. Address look-up is typically performed by means of content addressable memories (CAMs) that comprise a special type of memory performing simultaneously memory and comparison operations within a single clock cycle<sup>129</sup>. Optical look-up tables have not yet been realized, but the recent demonstrations of optical binary<sup>130</sup> and ternary<sup>107</sup> CAM cells using coupled SOA-MZI-based FFs might release new perspectives for all-optical look-up table deployments. Forwarding is usually implemented by a 2-dimensional RAM bank, where every RAM row stores the address of a router output port and is activated by the look-up CAM-based table.

### Cache memories

Caching is typically used in computing systems to store a small but often accessible amount of data close to the CPU to allow for ultra-fast fetching, avoiding the increased latency times of remote DRAM accesses. They exploit static RAM cells surrounded by certain peripheral circuitry for read/write control, row/column decoding and tag comparison purposes. The first all-optical cache design was proposed recently in refs. <sup>102,103</sup>, while all its constituent building blocks were demonstrated experimentally<sup>22–25,104,105</sup>.

The capacitor is either charged or discharged, corresponding to the two possible data values (logical "1" or logical "0").

Transferring these principles into the optical domain can result in the respective optical SRAM and DRAM cells, as shown in Fig. 5c, d, respectively. The optical SRAM cell utilizes an optical AOFF circuit (i.e., an SR-FF) as its main memory cell, which can be any of the volatile latching memories analyzed in the previous section, whereas the optical DRAM cell employs two coupled recirculating loops as its main memory element, as shown in ref. <sup>48</sup>. In both RAM cells, the optical AGs are realized by ON-OFF optical switches controlled by the access (word line) bit, typically operating in inverted logic and necessitating their control by the inverted access signal in the thus far reported optical SRAM<sup>22-25,70,99</sup> and DRAM<sup>48,49,93</sup> implementations. This means that an access bit of logical "0" value blocks the transition of the optical BitLine (BL) and its inverted  $\overline{BL}$  signal through these AGs, prohibiting communication between the memory cell and the outer world and allowing the optical RAM cell to retain its previous logical content. Access to the memory cell for the read/write operation is enabled only when the optical access bit becomes "1" and the respective  $\overline{Access}$ signal becomes "0". Read mode operation is accomplished when  $\overline{Access}$  is set to "0" and no new bit values are carried by the BL and  $\overline{BL}$  lines, allowing the memory content and its complementary value to reach the BL and  $\overline{BL}$  buses, respectively. When the  $\overline{Access}$  signal has a logical value of "0" and the write operation is targeted, a logical bit stream and its complementary signal are applied at the BL and  $\overline{BL}$ lines, respectively. These signals enter the SRAM or DRAM cell through an AG and are inserted into the memory cell, acting as the corresponding set and reset signals. One of the main advantages of optical SRAM implementation over its electronic counterparts is the potential to employ different wavelengths for the optical BL and  $\overline{BL}$  signals, which can allow the use of a single multi-wavelength AG element instead of the two AGs typically required in electronic SRAMs, as illustrated in Fig. 5c.

An example of the write operation at 10 Gb/s can be observed in Fig. 5e, which depicts the respective results of the recently successfully demonstrated optical static RAM cell<sup>70</sup>, which utilizes a monolithically integrated SOAbased SR-FF and an SOA-MZI-based dual-wavelength AG element. Figure 5e-i presents the pulse sequence of the optical Access signal, whereas Fig. 5e-ii, iii illustrate the optical BL and  $\overline{BL}$  signal sequences, respectively. Figure 5e-iv, v reveal the set and reset signals, respectively, obtained after the AND operation between the BL and  $\overline{BL}$ with the access bit and entering the memory cell. In the absence of an  $\overline{Access}$  bit (logical state equal to "0"), successful write functionality can be confirmed by the SRAM cell content shown in Fig. 5e-vi, the logical value of which exactly follows the content of the incoming BL sequence. When the logical value of the Access becomes high (i.e., logical state equal to "1"), both the set and reset signals become zero, and the memory content preserves its previous state, remaining unchanged.

Although the transition from elementary memory units to complete optical SRAM and DRAM cells relies on the rather simple addition of optical AG elements, so far, only a few volatile AOFF structures, including coupled SOAbased modules<sup>22–25,70</sup> and bistable semiconductor ring lasers<sup>99</sup>, have managed to scale to fully functional optical SRAM<sup>22,23,70,99</sup> and DRAM<sup>48,49</sup> layouts. Optical DRAM cell demonstrations<sup>48,49</sup> have still not managed to escape the fiber-based landscape, but optical SRAM cell implementations<sup>22,23,70,99</sup> are constantly adopting higher integration-density AOFF technology moving from hybrid-integrated<sup>22</sup> to monolithically integrated<sup>25,70</sup> configurations, reducing their footprint by 99.8% within the last ten years. They have also recently managed to break the electronic SRAM speed<sup>101</sup>, releasing the fastest SRAM cell reported thus far at 10 Gb/s<sup>70</sup>, whereas the demonstration of WDM-enabled SRAM circuitry<sup>25</sup>, together with the complete optical cache memory design<sup>102,103</sup> and the experimental verification of the required optical cache memory peripheral circuits<sup>104,105</sup>, suggests a strong potential for fabricating complete optical cache memory prototypes in the near future and enabling completely new computing architectures, such as disintegrated computing with macrochips<sup>106</sup>. Moreover, the recent employment of monolithic InP-based AOFF technology for novel optical content addressable memories (CAMs)<sup>107-109</sup> that were demonstrated to reach operational speeds almost 10× higher than those of the respective electronic CAMs implies that optical SRAMs could also form a viable vehicle with which to penetrate the routing look-up table application area when combined with the respective optical CAM technology  $^{107-109}$ .

### **Opportunities and challenges**

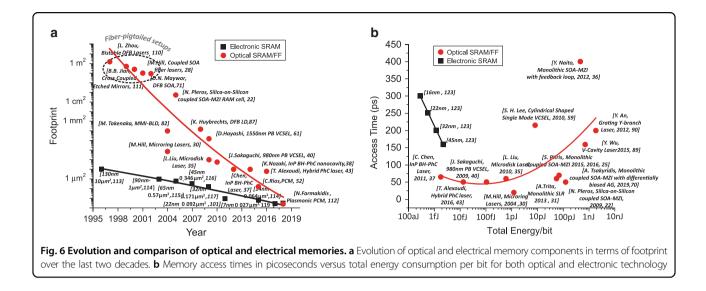

The significant progress witnessed in elementary optical FF memory and optical RAM layouts in comparison with the respective evolutions in electronic SRAMs can be clearly overviewed in Fig. 6. Figure 6a depicts the size scaling over the last 25 years, indicating that the

emergence of reliable photonic integration around early 2000 triggered some rapid footprint improvements in optical memory setups. Optical memory cells rapidly evolved from m<sup>2</sup>-scale layouts constructed with fiberpigtailed bulk components<sup>28,71,110,111</sup> until the early 2000s, reaching down to mm<sup>2</sup>-scale hybrid-integrated configurations when employing planar lightwave circuit (PLC) technology<sup>22,68</sup> and then to the more compact  $\mu$ m<sup>2</sup>scale monolithically integrated memory cells<sup>25,70</sup> recently developed, promising sizes of sub-µm<sup>2</sup> offered by volatile photonic crystal nanocavities<sup>38,39</sup>, nanolasers<sup>37,43</sup> and the non-volatile PCM-based memory cells<sup>52,112</sup>. This implies a 12-orders-of-magnitude improvement in footprint scaling for optical memory devices during the last 20 years. Over the same period, electronic technology<sup>113–119</sup> gradually moved from the 130 nm<sup>2</sup> processing node<sup>113</sup> down to the  $7 \text{ nm}^2$  node size over the same time period, reducing the SRAM cell size by 3 orders of magnitude and featuring an SRAM cell size of 0.027  $\mu$ m<sup>2</sup><sup>119</sup>. Despite this comparison being carried out while considering both smaller-size and simpler elementary memory elements together with complete SRAM cells for the optics with only SRAM cells being taken into account for electronics where the size is slightly higher compared to the incorporated electronic latch, it is still revealed that all-optical memory technology has made radical progress that continues to exhibit a steep improvement slope.

Figure 6b compares the relevant progress experienced by optical memories with respect to the memory access time and energy efficiency, again being compared with several generations of electronic SRAMs that typically comprise the fastest electronic memory layout. The optical memory setups again include the elementary volatile optical latching elements as well as more advanced optical SRAM cells reported thus far, without encompassing the non-volatile optical memories that are well known to support lower operational data rates compared to their volatile counterparts. In this graph, the power efficiency is expressed as energy/bit, taking into account both the required optical/electrical bias energy and the optical switching energy for the optical components, as reported in Table 1. For the electronics, the power efficiency has been deduced as the cell-level write energy including the energy of charging the storage node plus the energy of opening the two access transistors<sup>100</sup>. This graph clearly reveals that the power efficiency of optical memories has been drastically reduced by 5 orders of magnitude from the value of ref. <sup>99</sup> pJ/bit down to 1 fJ/ bit as optical memory technology has moved from mmlong SOA to µm-long InP micro-rings, microdisks, and VCSELS and then further to III-V photonic crystal cavities. It is important to note that this energy efficiency improvement has occurred with a simultaneous reduction in the memory access time, highlighting the fact that optics can take advantage of their bit-rate transparent power consumption to offer high bit-rate capabilities simultaneously with improvements in the energy efficiency. On the other hand, electronic setups can hardly cope with simultaneous advances in both memory access times and energy efficiency. The speed-up of electronic gates comes at the cost of increased energy and heat dissipation requirements, finally restricting clock speeds to a few GHz to remain within a reasonable energy envelope<sup>120</sup>. Today's electronic SRAM cells are severely challenged by the increasing standby leakage induced by the increased gate, sub-threshold, and junction leakage of the minimum-sized FETs<sup>100,121</sup>. To cope with the leakageinduced energy burden while keeping in line with Moore's law, memory designers have resorted to sub-threshold voltage techniques in SRAM circuits that are accompanied by severe reliability issues during read/write operations; thus, the energy reduction comes at the cost

| Switching<br>time (ps) |                 | Freq. (GHz)        | Energy efficiency (pJ/bit) |                     |         |                     | Footprint             | Capacity (bits) | Technology/refs.                                                                         |

|------------------------|-----------------|--------------------|----------------------------|---------------------|---------|---------------------|-----------------------|-----------------|------------------------------------------------------------------------------------------|

|                        |                 |                    | Switching <sup>a</sup>     | Static <sup>b</sup> |         | Total               | (µm²)/cell            |                 |                                                                                          |

| On                     | Off             | _                  |                            | Electr.             | Opt     |                     |                       |                 |                                                                                          |

| 20                     | 20              | 50 <sup>c</sup>    | 0.0055                     | 2.16 <sup>d</sup>   | -       | 2.16                | 720 <sup>30</sup>     | 1               | Micro-ring lasers <sup>30</sup>                                                          |

| <50                    | <50             | 5 <sup>e</sup>     | ~0.6                       | 120                 | -       | 120.6               | 540×106 <sup>68</sup> | 1               | Silica on silicon coupled SOA-MZIs <sup>22,60</sup>                                      |

| 50 <sup>f</sup>        | 50 <sup>f</sup> | 40 <sup>e</sup>    | 0.00475                    | 0.1 <sup>f</sup>    | -       | ~0.105              | 36                    | 4               | 1550-/980 nm PB VCSEL <sup>40,41</sup>                                                   |

| 60                     | ~100            | 10 <sup>g</sup>    | 0.0018                     | 0.6 <sup>f</sup>    | -       | 0.6                 | 56.25 <sup>35</sup>   | 1               | Microdisk laser <sup>35</sup>                                                            |

| 58                     | 65              | ~15 <sup>c</sup>   | 0.00031                    | _                   | 0.0017  | ~0.002 <sup>h</sup> | <10                   | 1               | BH-InP PhC nanolaser <sup>37</sup>                                                       |

| 44                     | 7×103           | 0.142 <sup>i</sup> | 0.0025                     | _                   | 0.00021 | ~0.0027             | <10                   | 104/128         | BH-PhC nanocavity <sup>38,39</sup>                                                       |

| 200                    | 200             | 5 <sup>c</sup>     | ~0.6                       | ~450                | -       | ~450.6              | $40 \times 10^{6}$    | 1               | Monolithic SOA-MZI with feedback loop <sup>36</sup>                                      |

| 10                     | 60              | 10 <sup>e</sup>    | ~18                        | 36                  | _       | ~54                 | $0.03 \times 10^{6}$  | 1               | Semiconductor ring laser <sup>33</sup>                                                   |

| 70                     | 70              | 10 <sup>e</sup>    | 3                          | ~120                |         | ~123                | $12 \times 10^{6}$    | 1               | Monolithic coupled SOA-MZIs <sup>25</sup>                                                |

| 25                     | 75              | 10                 | 0.5                        | ~180                |         | ~180.3              | 12 × 10 <sup>6</sup>  | 1               | Monolithic coupled SOA-MZIs with differentially biased push-pull technique <sup>70</sup> |

| 50                     | 50              | 10 <sup>e</sup>    | 0.0032                     | -                   | 0.01    | 0.013 <sup>h</sup>  | 6.2                   | 1               | III–V on SOI PhC nanocavity laser <sup>43</sup>                                          |

| 10×103                 | $10 \times 103$ | 1 <sup>g</sup>     | 5.3                        | _                   | -       | 5.3                 | 0.16-0.25             | 3               | PCM <sup>52</sup>                                                                        |

Table 1 Summary of optical memory technologies

<sup>a</sup>Based on the reported switching energy or calculated as the product of the switching power and the pulse duration

<sup>b</sup>Calculated as the product of the electrical/optical power and frequency (pulse duration). Electrical static power is noted for electrically pumped memories, whereas optical static power refers to the bias power required in the case of optically pumped memories

<sup>c</sup>Frequency estimated by the authors of the current work based on the reported response time

<sup>d</sup>Based on the calculation provided in ref. <sup>35</sup>, we estimated the electrical consumption for both micro-ring lasers (2  $\times$  30 mA assuming 1.8 V with 20 ps pulses) excluding wavelength tuning

<sup>°</sup>Frequency demonstrated by the authors in their respective papers <sup>f</sup>Based on the performance table of ref. <sup>38</sup>. The total energy excludes the wavelength tuning energy consumption

<sup>9</sup>Frequency reported by the authors in their respective papers

<sup>h</sup>Excluding wavelength tuning energy consumption

Frequency estimated based on the switch-OFF time, which equals 7 ns according to refs. 38,39

<sup>9</sup>Based on the performance table of ref. <sup>38</sup> and including the wavelength tuning energy consumption. The overall power consumption according to ref. <sup>53</sup> is estimated to be 6 mW (3.5 mA  $\times$  1.5 V + 0.8 mW for wavelength tuning)

of lower speed operation<sup>121</sup>. This is clearly captured in Fig. 6b, as the electronic power efficiency evolution line moves from the fJ regime of the 45 nm technology with access times of ~160 ps to the aJ regime enabled by the 16 nm technology, where, however, the access times increase to 300 ps<sup>100</sup>. This practice reveals that the race for lower-energy electronic SRAMs comes at the loss of access time improvements, whereas optics have proven their bit-rate-transparent power consumption even in the memory domain, reaching 50 ps access times and close to 1 fJ/bit energy efficiencies<sup>37</sup>, canceling in this way the trade-off between access time and energy efficiency. The fitting among the optical memory technology bullets in Fig. 6b forms an evolution line that points toward the desired target specifications for both low energy and low access times, whereas the respective electronic line seems to deviate from the low access time requirement to reach the low-energy target.

These evolution trends highlight the future perspectives of optical memory technology to meet the complete framework of performance requirements along a broad field of volatile memory applications: high integration densities and, as such, high-capacity modules, low memory access times and low-energy consumption. Turning this promise into a tangible reality has, however, still to overcome some pressing challenges to confirm the use of this lightenabled memory roadmap in real computing, signal processing, routing, datacom and telecom applications:

- Theoretical predictions about the volatile memory a. line-rate operation up to or even beyond 40 Gb/s<sup>56</sup> have to be experimentally confirmed through a lowfootprint, low-energy and fast-access-time photonic integrated circuit technology, concluding with speed-optimized integrated memory layouts.

- Ь. The potential for high-integration density and small-footprint setups has to be validated in

high-memory-capacity configurations, elevating current optical memory capacity metrics from just a few bytes to kB or even Mb implementations. This obviously requires an intense effort to improve the yield of photonic integrated memory circuits while optimizing the architectural layout to reduce possible undesired thermal stability and crosstalk effects.

- c. Low-footprint, low-energy and high-speedcredible integrated optical memories have to take the next step in evolving from simple memory elements into highly functional and practical optical SRAM, DRAM and CAM cells, which have been reported thus far only via the use of SOA-based technologies.

- d. Low-footprint and energy-efficient non-volatile PCM-based optical memories need to (a) overcome materials science issues related to the stability of the amorphous phase that defines the data retention in memory devices and (b) improve the crystallization time to achieve faster operation in excess of a few GHz.

- e. Finally, their integration roadmap has to be shaped around a high-yield and low-cost fabrication technology allowing for dense optical memory architectures to arrive at scales, complexities and cost-efficiencies similar to those of their electronic counterparts.

### Acknowledgements

This work has received funding from the Hellenic Foundation for Research and Innovation (HFRI) and the General Secretariat for Research and Technology (GSRT) through the ORION project under Grant Agreement No. 585.

#### Conflict of interest

The authors declare that they have no conflict of interest.

# Received: 18 November 2019 Revised: 22 February 2020 Accepted: 28 April 2020

Published online: 25 May 2020

#### References

- Schulte, H. & Rack, A. Optical delay line memory. *IEEE J. Quantum Electron.* 3, 246 (1967).

- 2. Liu, J. M. & Chen, Y. C. Optical flip-flop. Electron. Lett. 21, 236-238 (1985).

- Koffman, I. et al. A fiber optic recirculating memory loop for radar applications. *Microw. Optical Technol. Lett.* 1, 232–235 (1988).

- Dietrich, E. et al. BER measurements in random access fibre loop optical memory. *Electron. Lett.* 27, 1585–1586 (1991).

- Avramopoulos, H. & Whitaker, N. A. Addressable fiber-loop memory. *Opt. Lett.* 18, 22–24 (1993).

- Hunter, D. K., Chia, M. C. & Andonovic, I. Buffering in optical packet switches. J. Lightwave Technol. 16, 2081–2091 (1998).

- Yamada, Y., Sasayama, K. & Habara K. Proc. 22nd European Conference on Optical Communication (IEEE, Oslo, Norway, 1996).

- Bowers, J., Burmeister, E. & Blumenthal, D. Proc. 2006 International Conference on Photonics in Switching (IEEE, Heraklion, Greece, 2006).

Page 14 of 16

- Burmeister, E. F., Blumenthal, D. J. & Bowers, J. E. A comparison of optical buffering technologies. *Optical Switching Netw.* 5, 10–18 (2008).

- Sedgwick, F. G. et al. Storage-bit-rate product in slow-light optical buffers. Electron. Lett. 41, 1347–1348 (2005).

- Tucker, R. S., Ku, P. C. & Chang-Hasnain, C. J. Slow-light optical buffers: capabilities and fundamental limitations. *J. Lightwave Technol.* 23, 4046–4066 (2005).

- Apostolopoulos, D. et al. Contention resolution for burst-mode traffic using integrated SOA-MZI gate arrays and self-resetting optical flip-flops. *IEEE Photonics Technol. Lett.* **20**, 2024–2026 (2008).

- Zakynthinos, P. et al. Proc. 2008 34th European Conference on Optical Communication (IEEE, Brussels, Belgium, 2008).

- Stojanović, V. et al. Monolithic silicon-photonic platforms in state-of-the-art CMOS SOI processes [Invited]. Opt. Express 26, 13106–13121 (2018).

- Booth, B. et al. On-board optical interconnection. CTR III TWG Report #3, MIT Microphotonics Center, April 2013 IEEE/OSA J. Opt. Commun. Netw. https:// mphotonics.mit.edu/docman/ctr/ctr-3/short-reach-interconnect-twg/722-onboard-optical-interconnection-digest-1/file.

- Bohn, M. et al. Proc. OSA Optical Fiber Communication Conference (OSA, San Diego, CA, USA, 2019).

- Zhao, L. et al. Proc. IEEE Symposium on High-Performance Computer Architecture (HPCA), Workshop on Chip Multiprocessor Memory Systems and Interconnects 2007 (IEEE, Phoenix, AZ, USA, 2007).

- Oracle's SPARC T5-2, SPARC T5-4, SPARC T5-8, and SPARC T5-1B Server Architecture. White Paper, Feb 2014. http://www.oracle.com/technetwork/ server-storage/sun-sparc-enterprise/documentation/o13-024-sparc-t5architecture-1920540.pdf.

- Borkar, S. & Chien, A. A. The future of microprocessors. Commun. ACM 54, 67–77 (2011).

- McKee, S. A. Proc. 1st Conference on Computing Frontiers (ACM, Ischia, Italy, 2004).

- Hasler, J. & Marr, B. Finding a roadmap to achieve large neuromorphic hardware systems. *Front. Neurosci.* 7, 118 (2013).

- Pleros, N. et al. Optical static RAM cell. *IEEE Photonics Technol. Lett.* 21, 73–75 (2009).

- Fitsios, D. et al. Dual-wavelength bit input optical RAM with three SOA-XGM switches. *IEEE Photonics Technol. Lett.* 24, 1142–1144 (2012).

- Vagionas, C. et al. Optical RAM and flip-flops using bit-input wavelength diversity and SOA-XGM switches. J. Lightwave Technol. **30**, 3003–3009 (2012).

- Pitris, S. et al. WDM-enabled optical RAM at 5 Gb/s using a monolithic InP flip-flop chip. IEEE Photonics. *Journal* 8, 0600207 (2016).

- Vyrsokinos, K. et al. Proc. 37th European Conference and Exposition on Optical Communications (OSA, Geneva, Switzerland, 2011).

- Bakopoulos, P. et al. All-optical T-flip-flop using a single SOA-MZI-based latching element. *IEEE Photonics Technol. Lett.* 24, 748–750 (2012).

- Hill, M. T. et al. All-optical flip-flop based on coupled laser diodes. *IEEE J. Quantum Electron.* 37, 405–413 (2001).

- Zhang, S. X. et al. Ring-laser optical flip-flop memory with single active element. *IEEE J. Sel. Top. Quantum Electron.* 10, 1093–1100 (2004).

- Hill, M. T. et al. A fast low-power optical memory based on coupled microring lasers. *Nature* 432, 206–209 (2004).

- Trita, A. et al. All-optical toggle flip-flop based on monolithic semiconductor ring laser. *IEEE Photonics Technol. Lett.* 26, 96–99 (2014).

- Wang, J. et al. All-optical clocked flip-flops and binary counting operation using SOA-based SR latch and logic gates. *IEEE J. Sel. Top. Quantum Electron.* 16, 1486–1494 (2010).

- Trita, A. et al. Monolithic all-optical set-reset flip-flop operating at 10 Gb/s. IEEE Photonics Technol. Lett. 25, 2408–2411 (2013).

- Clavero, R. et al. All-optical flip-flop based on a single SOA-MZI. *IEEE Photonics Technol. Lett.* 17, 843–845 (2005).

- Liu, L. et al. An ultra-small, low-power, all-optical flip-flop memory on a silicon chip. *Nat. Photonics* 4, 182–187 (2010).

- Naito, Y. et al. Investigation of all-optical latching operation of a monolithically integrated SOA-MZI with a feedback loop. *Opt. Express* 20, B339–B349 (2012).

- Chen, C. H. et al. All-optical memory based on injection-locking bistability in photonic crystal lasers. *Opt. Express* 19, 3387–3395 (2011).

- Nozaki, K et al. Ultralow-power all-optical RAM based on nanocavities. Nat. Photonics 6, 248–252 (2012).

- Kuramochi, E. et al. Large-scale integration of wavelength-addressable alloptical memories on a photonic crystal chip. *Nat. Photonics* 8, 474–481 (2014).

- Sakaguchi, J., Katayama, T. & Kawaguchi, H. All-optical memory operation of 980-nm polarization bistable VCSEL for 20-Gb/s PRBS RZ and 40-Gb/s NRZ data signals. *Opt. Express* 18, 12362–12370 (2010).

- Katayama, T., Ooi, T. & Kawaguchi, H. Experimental demonstration of multi-bit optical buffer memory using 1.55-µm polarization bistable vertical-cavity surface-emitting lasers. *IEEE J. Quantum Electron.* 45, 1495–1504 (2009).

- Fitsios, D. et al. ultra-compact III–V-on-Si photonic crystal memory for flip-flop operation at 5 Gb/s. Opt. Express 24, 4270–4277 (2016).

- Alexoudi, T. et al. III–V-on-Si photonic crystal nanocavity laser technology for optical static random access memories. *IEEE J. Sel. Top. Quantum Electron.* 22, 4901410 (2016).

- 44. Ponzini, F. et al. Proc. 2005 IEEE/LEOS Workshop on Fibres and Optical Passive Components (IEEE, Palermo, Italy, 2005).

- Malacarne, A., Bogoni, A. & Poti, L. Erbium–ytterbium-doped fiber-based optical flip-flop. *IEEE Photonics Technol. Lett.* 19, 904–906 (2007).

- Poti, L. Erbium-based photonic flip-flop memories: model and experimental validation. *IEEE J. Quantum Electron.* 44, 473–479 (2008).

- Gregorkiewicz, T. et al. Er-doped electro-optical memory element for 1.5μm silicon photonics. *IEEE J. Sel. Top. Quantum Electron.* 12, 1539–1544 (2006).

- Berrettini, G., Potì, L. & Bogoni, A. Optical dynamic RAM for all-optical digital processing. *IEEE Photonics Technol. Lett.* 23, 685–687 (2011).

- Berrettini, G. et al. All-optical digital circuits exploiting SOA-based loop memories. *IEEE J. Sel. Top. Quantum Electron.* 18, 847–858 (2012).

- Pernice, W. H. P. & Bhaskaran, H. Photonic non-volatile memories using phase change materials. *Appl. Phys. Lett.* **101**, 171101 (2012).

- 51. Li, X. et al. Fast and reliable storage using a 5 bit, nonvolatile photonic memory cell. *Optica* **6**, 1–6 (2019).

- Ríos, C. et al. Integrated all-photonic non-volatile multi-level memory. Nat. Photonics 9, 725–732 (2015).

- Zhang, Y. F. et al. Proc. Conference on Lasers and Electro-Optics (OSA, San Jose, CA, USA, 2017).

- 54. Cheng, Z. G. et al. Device-level photonic memories and logic applications using phase-change materials. *Adv. Mater.* **30**, 1802435 (2018).

- Miller, K. J., Haglund, R. F. & Weiss, S. M. Optical phase change materials in integrated silicon photonic devices: review. *Optical Mater. Express* 8, 2415–2429 (2018).

- Fitsios, D. et al. Memory speed analysis of optical RAM and optical flip-flop circuits based on coupled SOA-MZI gates. *IEEE J. Sel. Top. Quantum Electron.* 18, 1006–1015 (2012).

- Fitsios, D. et al. Proc. IEEE Photonic Society 24th Annual Meeting (IEEE, Arlington, VA, USA, 2011).

- Huffaker, D. L. et al. Optical memory using a vertical-cavity surface emitting laser. *IEEE Photonics Technol. Lett.* 3, 1064–1066 (1991).

- Lee, S. H. et al. 1-GHz all-optical flip-flop operation of conventional cylindricalshaped single-mode VCSELs under low-power optical injection. *IEEE Photo*nics Technol. Lett. 22, 1759–1761 (2010).

- Marconi, M., Barland, S. & Giudici, M. Nonvolatile polarization control of a bistable VCSEL. Opt. Express 20, B299–B22305 (2012).

- Hayashi, D. et al. Bit error rate measurements of all-optical flip-flop operations of a 1.55-µm polarization bistable VCSEL. J. Lightwave Technol. 32, 2671–2677 (2014).

- Sakaguchi, J., Katayama, T. & Kawaguchi, H. High switching-speed operation of optical memory based on polarization bistable vertical-cavity surfaceemitting laser. *IEEE J. Quantum Electron.* 46, 1526–1534 (2010).

- Kawaguchi, H. in Advanced Lasers (eds Shulika, O. & Sukhoivanov, I.) 1–17 (Springer, Dordrecht, 2015).

- Hill, M. T. et al. Fast optical flip-flop by use of Mach-Zehnder interferometers. *Microw. Optical Technol. Lett.* 31, 411–415 (2001).