# **MASTER THESIS**

TITLE: Automatic Transmit Power Control for Power Efficient Communications in UAS

MASTER DEGREE: Master's degree in Applications and Technologies for Unmanned Aircraft Systems (Drones) (MED)

**AUTHOR: Wantao Li**

ADVISOR: Pere L. Gilabert

**DATE: June 7th, 2020**

#### Abstract

Nowadays, unmanned aerial systems (UAS) have become one of the most popular tools that can be used in commercial, scientific, agricultural and military applications. As drones become faster, smaller and cheaper, with the ability to add payloads, the usage of the drone can be versatile. In most of the cases, unmanned aerials systems are equipped with a wireless communication system to establish a link with the ground control station to transfer the control commands, video stream, and payload data. However, with the limited onboard calculation resources in the UAS, and the growing size and volume of the payload data, computational complex signal processing such as deep learning cannot be easily done on the drone. Hence, in many drone applications, the UAS is just a tool for capturing and storing data, and then the data is post-processed off-line in a more powerful computing device. The other solution is to stream payload data to the ground control station (GCS) and let the powerful computer on the ground station to handle these data in real-time. With the development of communication techniques such as orthogonal frequency-division multiplexing (OFDM) and multiple-input multiple-output (MIMO) transmissions, it is possible to increase the spectral efficiency over large bandwidths and consequently achieve high transmission rates. However, the drone and the communication system are usually being designed separately, which means that regardless of the situation of the drone, the communication system is working independently to provide the data link. Consequently, by taking into account the position of the drone, the communication system has some room to optimize the link budget efficiency.

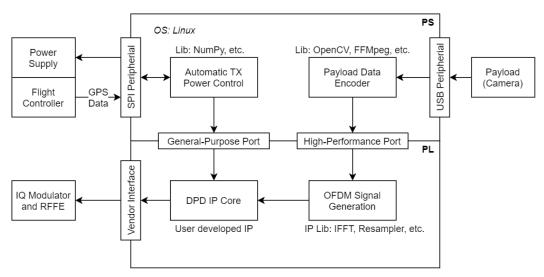

In this master thesis, a power-efficient wireless communication downlink for UAS has been designed. It is achieved by developing an automatic transmit power control system and a custom OFDM communication system. The work has been divided into three parts: research of the drone communication system, an optimized communication system design and finally, FPGA implementation.

In the first part, an overview on commercial drone communication schemes is presented and discussed. The advantages and disadvantages shown are the source of inspiration for improvement. With these ideas, an optimized scheme is presented. In the second part, an automatic transmit power control system for UAS wireless communication and a power-efficient OFDM downlink scheme are proposed. The automatic transmit power control system can estimate the required power level by the relative position between the drone and the GCS and then inform the system to adjust the power amplifier (PA) gain and power supply settings. To obtain high power efficiency for different output power levels, a searching strategy has been applied to the PA testbed to find out the best voltage supply and gain configurations. Besides, the OFDM signal generation developed in Python can encode data bytes to the baseband signal for testing purpose. Digital predistortion (DPD) linearization has been included in the transmitter's design to guarantee the signal linearity. In the third part, two core algorithms: IFFT and LUT-based DPD, have been implemented

in the FPGA platform to meet the real-time and high-speed I/O requirements. By using the high-level synthesis design process provided by Xilinx Corp, the algorithms are implemented as reusable IP blocks. The conclusion of the project is given in the end, including the summary of the proposed drone communication system and envisioning possible future lines of research.

## **CONTENTS**

| CHA    | APTER 1. IN    | FRODUCTION                                           | 1  |

|--------|----------------|------------------------------------------------------|----|

| Moti   | vation         |                                                      | 1  |

| Obje   | ctives         |                                                      | 2  |

| Tech   | nologies invol | ved                                                  | 2  |

| Plan   | ning           |                                                      | 3  |

| CHA    | APTER 2. DR    | ONE COMMUNICATION SYSTEM                             | 4  |

| 2.1.   | Targeting UA   | S                                                    | 4  |

| 2.2.   | Existing solu  | tions                                                | 5  |

| 2.3.   | Optimized tra  | nsmitter architecture                                | 7  |

| CHA    | APTER 3. SY    | STEM DESIGN                                          | 9  |

| 3.1.   | Automatic tra  | nsmit power control                                  | 9  |

|        |                | n filter for estimating the RX power                 |    |

|        |                | ation of the power and distance estimation in Python |    |

|        | 3.1.3. TX po   | wer control logic                                    | 15 |

| 3.2.   | Design of an   | OFDM system                                          | 16 |

|        |                | ler                                                  |    |

|        | 3.2.2. QAM     | mapper                                               | 17 |

|        |                | and serial to parallel conversion                    |    |

|        |                |                                                      |    |

|        |                | prefix                                               |    |

|        |                | 1 baseband data samples                              |    |

|        |                | nel simulation                                       |    |

|        |                | ronizationnel estimation                             |    |

| 3.3.   | Tochniques t   | o improve power efficiency                           | 30 |

| J.J.   | 3.3.1. PA bia  | as point selection and operating classes             | 32 |

|        |                | iew of commercial power amplifiers                   |    |

|        |                | I predistortion techniques                           |    |

|        |                | ower amplification testbed                           |    |

|        |                | hing for the optimal PA configuration                |    |

|        | 3.3.6. Perfor  | m DPD with the optimal settings                      | 42 |

| СН     | DTFR / FD      | GA IMPLEMENTATION                                    | 44 |

| ~ I I/ | \              | ~~ LLIVILIVI I ~ I I V ( )                           | ~~ |

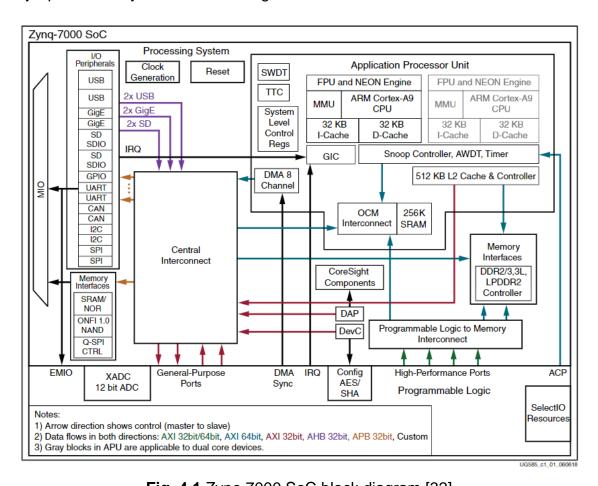

| 4.1. | <b>FPGA</b> | and Zynq SoC introduction                  | . 44       |

|------|-------------|--------------------------------------------|------------|

|      | 4.1.1.      | Zyng APSoC architecture                    | . 45       |

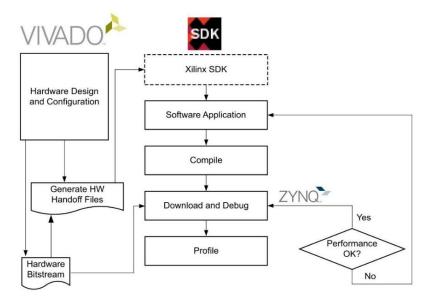

|      | 4.1.2.      | Zynq-based design methodology and practice | . 46       |

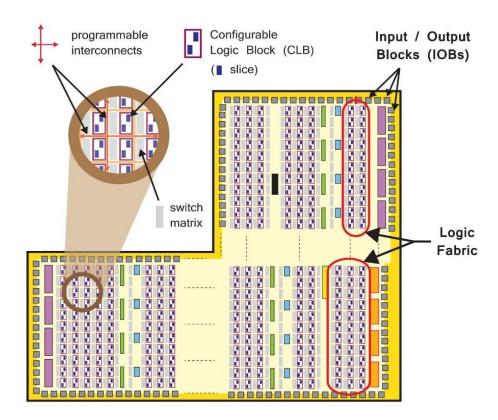

|      |             | Useful PL resources                        |            |

|      | 4.1.4.      | The Zedboard for experimental validation   | . 52       |

| 4.2. | Hiah-L      | evel synthesis                             | . 53       |

|      | 4.2.1.      |                                            | . 53       |

|      | 4.2.2       | Directives for optimization                |            |

|      |             | Generating in-chip interfaces              |            |

| 4.0  | IEET :      | and an autotic a                           | <b>-</b> - |

| 4.3. |             | nplementation                              |            |

|      |             | FFT IP from the HLS library                |            |

|      | 4.3.2.      | Evaluate the IFFT IP                       | .5/        |

| 4.4. | DPD ir      | nplementation                              | . 58       |

|      |             | Architectures of implementing DPD in FPGA  |            |

|      |             | LUTs extraction                            |            |

|      | 4.4.3.      | Indexing logic and simulation              | . 61       |

|      | 4.4.4.      | Synthesis and performance analysis         |            |

|      | 4.4.5.      | Final implementation                       |            |

|      |             |                                            |            |

| CHA  | APTER       | 5. CONCLUSIONS AND FUTURE WORK             | 66         |

|      |             |                                            |            |

| REF  | EREN        | CES                                        | 68         |

## **LIST OF FIGURES**

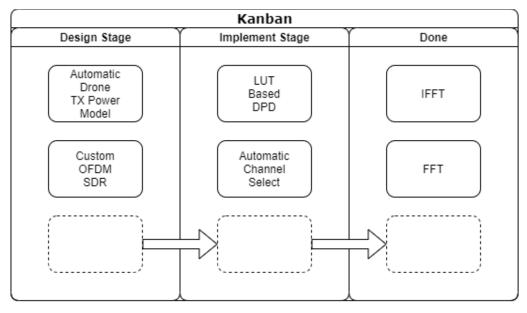

| Fig. | 1.1 Kanban board schedule                                             | . 3 |

|------|-----------------------------------------------------------------------|-----|

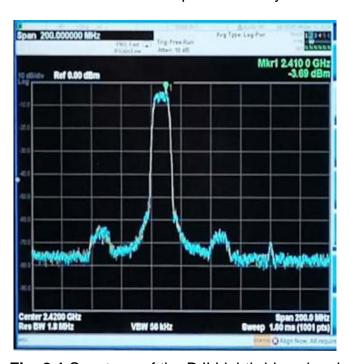

| Fig. | 2.1 Spectrum of the DJI Lightbridge signal                            | . 6 |

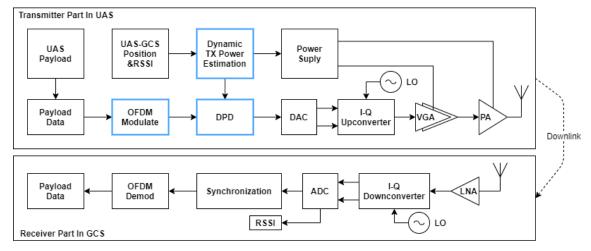

| Fig. | 2.2 Block diagram of the drone transmitter and GCS receiver           | . 7 |

|      | 2.3 Static TX power vs dynamic TX power                               |     |

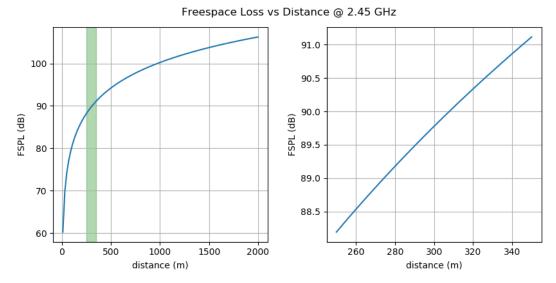

|      | 3.1 FSPL vs distance                                                  |     |

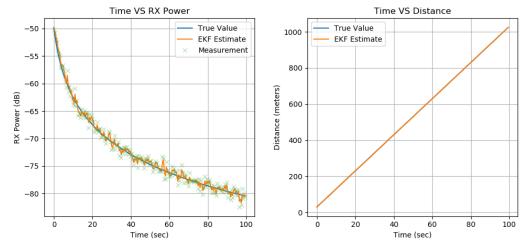

|      | 3.2 EKF RX power and distance vs time                                 |     |

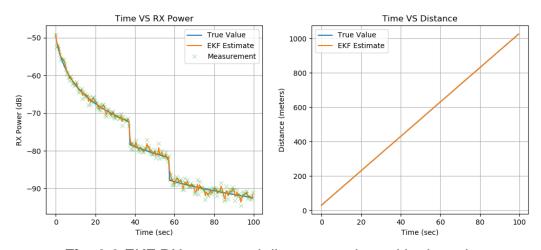

|      | 3.3 EKF RX power and distance vs time with obstacles                  |     |

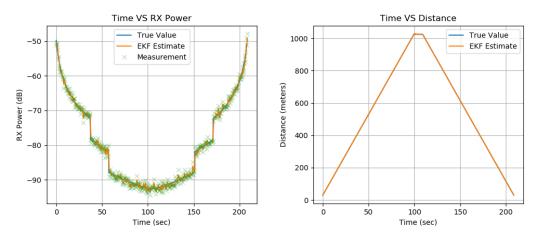

| _    | 3.4 EKF RX power and distance vs time with obstacle and go back       |     |

|      | 3.5 Automatic power control logic                                     |     |

|      | 3.6 The simulated control of TX power                                 |     |

|      | 3.7 OFDM full implementation diagram [10]                             |     |

|      | 3.8 OFDM baseband generator                                           |     |

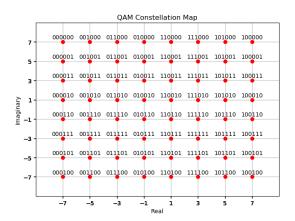

|      | 3.9 QAM-64 gray coding constellation                                  |     |

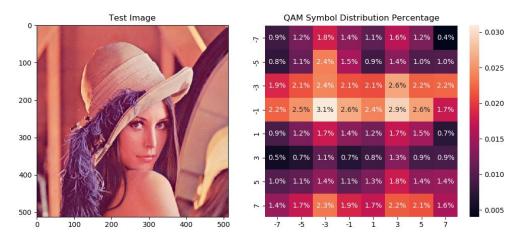

| _    | 3.10 Sample image and QAM symbol distribution                         |     |

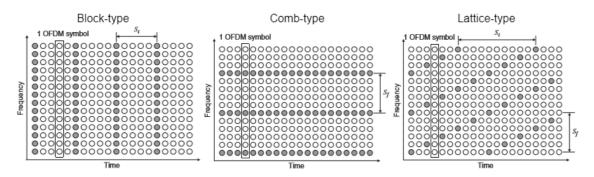

|      | 3.11 Comparison of three pilot structures [10]                        |     |

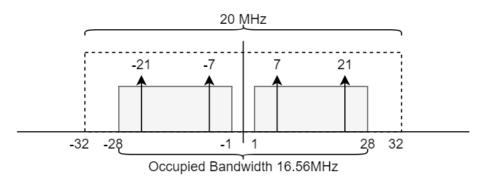

|      | 3.12 Pilots location and the OFDM subcarriers scheme                  |     |

|      | 3.13 OFDM cyclic prefix                                               |     |

|      | 3.14 Power spectrum of the samples                                    |     |

|      | 3.15 Diagram of peak cancellation CFR technique [13]                  |     |

|      | 3.16 Distribution of generated signal amplitude                       |     |

|      | 3.17 Spectrum and Amplitude comparison on CFR signal                  |     |

|      | 3.18 CCDF & PDF of PAPR with or without cliping and filtering         |     |

| _    | 3.19 Constellation decode without synchronization and equalization    |     |

| _    | 3.20 STO Estimation using CP minimum difference method                |     |

|      | 3.21 CP-based CFO estimation with simulation data                     |     |

| _    | 3.22 Procedure for pilots extraction                                  |     |

|      | 3.23 Channel estimation results                                       |     |

|      | 3.24 Constellation and decoded image with pilot equalization          |     |

|      | 3.25 General power amplifier scheme                                   |     |

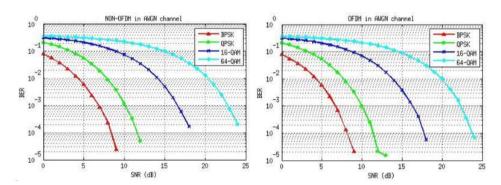

|      | 3.26 SNR vs BER in different modulation schemes [18]                  |     |

|      | 3.27 Power vs frequency of different transistor technologies [21]     |     |

| _    | 3.28 Direct learning approach DPD diagram                             |     |

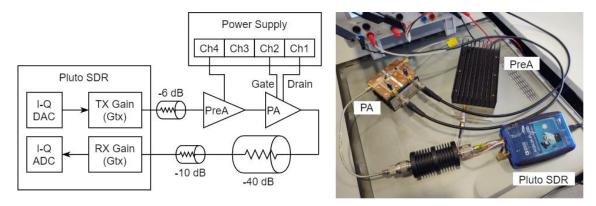

|      | 3.29 Block diagram and photograph of the testbed                      |     |

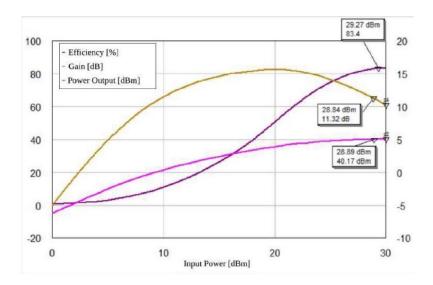

|      | 3.30 Input power sweep simulation of the PA [28]                      |     |

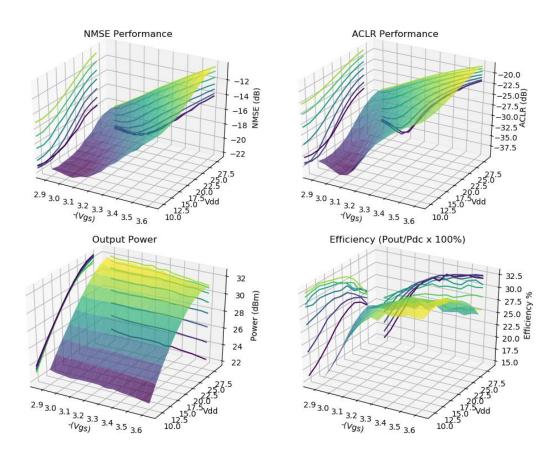

|      | 3.31 PA performance with different supply settings without DPD        |     |

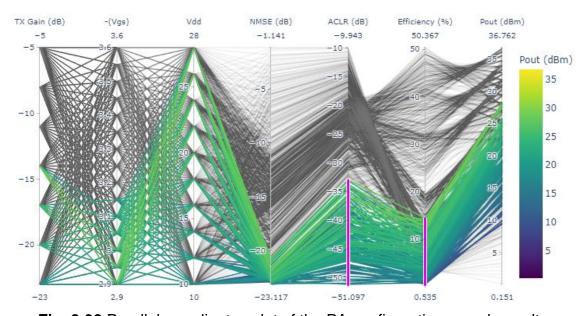

|      | 3.32 Parallel coordinates plot of the PA configuration search results |     |

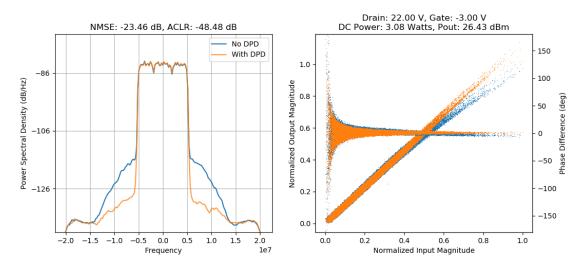

|      | 3.33 DPD Result of the fifth optimal configuration                    |     |

|      | 4.1 Zync-7000 SoC block diagram [32]                                  |     |

|      | 4.2 Implementation considerations of the proposed drone communicati   |     |

| 3    | system                                                                |     |

| Fia. | 4.3 Hardware and software development flow [33]                       | 49  |

|      | 4.4 The logic fabric and its consitiuent elements [34]                |     |

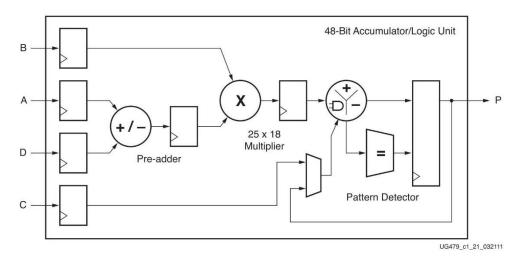

|      | 4.5 Simplified DSP48E1 slice functionality [35]                       |     |

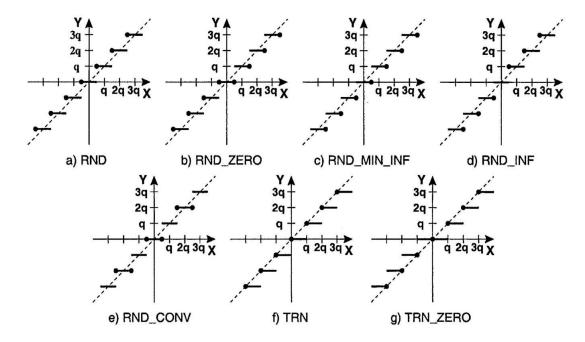

| Fig. | 4.6 Different quantization modes [40]                                 | 54  |

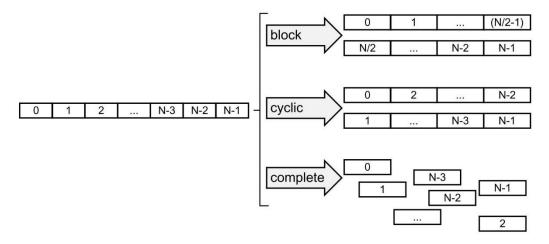

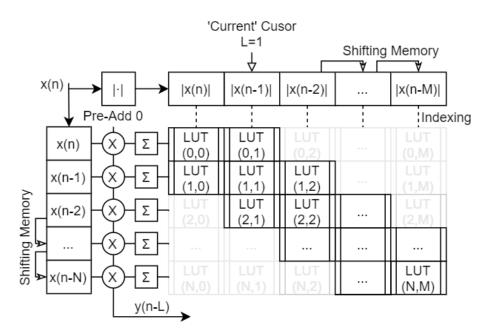

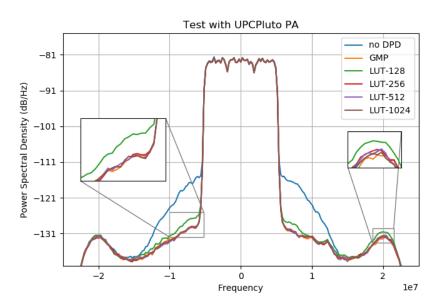

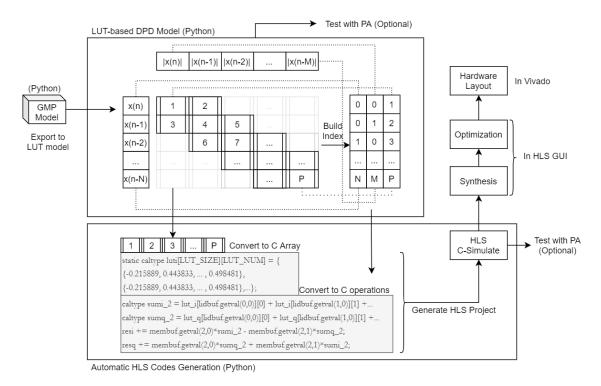

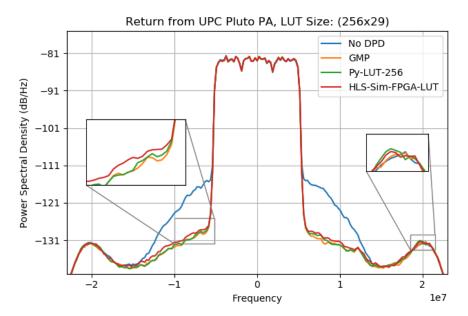

| Fig. 4.7 Different types of array partitioning [38]                        | . 59<br>. 60<br>. 61<br>. 62<br>. 64<br>. 65 |

|----------------------------------------------------------------------------|----------------------------------------------|

| LIST OF TABLES                                                             |                                              |

|                                                                            |                                              |

| Table 1.1. Typical ISM transceiver ICs [1]                                 |                                              |

| Table 2.1 Three levels of flexibility to custom drone communication system |                                              |

| Table 2.2. Telemetry link scheme for drone [4]                             | 5                                            |

| Table 3.1. Gain and loss factors                                           |                                              |

| Table 3.2. Kalman filter procedure of the problem                          |                                              |

| Table 3.3. Discrete time EKF                                               |                                              |

| Table 3.4. Comparison of different OFDM protocols                          |                                              |

| Table 3.5. SNR for BER at 0.1% in AWGN channel [18]                        |                                              |

| Table 3.6. Amplifier classes and properties                                |                                              |

| Table 3.7. The optimal configuration without DPD                           | . 41                                         |

| Table 3.8. DPD results with optimal and fixed configurations               |                                              |

| Table 4.1. Implementation considerations                                   |                                              |

| Table 4.2. Key features of the Zedboard                                    |                                              |

| Table 4.3. Overflow and quantization modes                                 | . 54                                         |

| Table 4.4. IFFT performance and resources of different architecture        |                                              |

| Table 4.5. DPD performance comparison                                      |                                              |

| Table 4.6. Synthesised DPD performance and resources usage                 | . 63                                         |

### **ACRONYMS**

ARM Advanced RISC Machine

APSoC All-Programmable SoC

APU Application Processor Unit

AWGN Additive White Gaussian Noise

AXI Advanced eXtensible Interface

BER Bits Error Rate

CAN Controller Area Network

CFO Carrier Frequency Offset

CFR Crest Factor Reduction

CLB Configurable Logic Block

CP Cyclic Prefix

CPU Central Processing Unit

CPWL Canonical Piecewise-Linear

CRC Cyclic Redundancy Check

DAC Digital-to-Analog Converter

DDR Double Data Rate

DFT Discrete Fourier transform

DPD Digital Predistorsion

DSC Drone Small Cells

DSP Digital Signal Processing

DSSS Direct Sequence Spread Spectrum

DVR Decomposed Vector Rotation

EASA European Union Aviation Safety Agency

EKF Extended Kalman filter

FF Flip Flop

FFT Fast Fourit Transform

FHSS Frequency-hopping spread spectrum

FIR Finite Impulse Response

FPGA Field-Programmable Gate Array

FSBL First Stage Boot Loader FSK Frequency-Shift Keying FSPL Free-Space Path Loss

GaAs Gallium Arsenide

GaN Gallium Nitride

GCS Ground Control Station

GMP Gemeralized Memory Polynomial

GP General-Purpose port

GPS Global Positioning System

HLS High-Level Synthesis

HP High-Performance port

ICI Inter-Carrier Interference

IDE Integrated Development Environment

IDFT Inverse Discrete Fourier transform

IFFT Inverse Fast Fourit Transform

II Initiation Interval

IP Intellectual Property

ISI Inter-Symbol Interference

ISM Industrial, Scientific and Medical LDMOS Laterally Diffused MOSFET LiDAR Light Detection and Ranging

LNA Low-Noise Amplifier

LO Local Oscillator

LUT Look-Up Table

LWIP Lightweight IP

MP Memory Polynomial

MPU Microprocessing Unit

OFDM Orthogonal frequency-division multiplexing

PA Power Amplifier

PAPR Peak to Average Power Ratio

PL Programmable Logic

POSIX Portable Operating System Interface

PS Processing System

PSK Phase-Shift Keying

QAM Quadrature Amplitude Modulation

QoS Quality of Service

QSPI Queued Serial Peripheral Interface

RAM Random Access Memory

RC Radio control RF Radio Frequency

RSSI Received Signal Strength Indicator

RTL Register Transfer Level

RX Receiver

SDK Software Development Kit SDR Software Define Radio

SiC Silicon Carbide

SNR Signal to Noise Ratio SoC System on a Chip

SPI Serial Peripheral Interface

STO Symbol Time Offset

TX Transmiter

UART Universal Asynchronous Receiver/Transmitter

UAS Unmanned Aircraft System VGA Variable Gain Amplifiers

Introduction

### CHAPTER 1. INTRODUCTION

#### Motivation

Drones are devices flying in the air, far away from the operator. The most common way to send and receive data/commands is by using the wireless communication system. Usually, when selecting the transceiver for drones, one will first consider the data rate and the distance. For example, to send control commands, one possibility is the use of general transceiver ICs or modules that operate under low-frequency ISM band. These transceivers are easy to use, they provide serial interfaces like SPI, I2C with a user manual to help set up their communication, with the advantages of low power consumption and long coverage range. However, these transceivers offer low data rate that might be enough for sending control data, like mission waypoints and inertial states, but not sufficient for large-volume data such as video and LiDAR data. Table 1.1 lists some typical transceivers that operate in the ISM band.

Table 1.1. Typical ISM transceiver ICs [1]

| Name     | Frequency                                     | Modulation                                        | Data Rate<br>(Max) | Power<br>Output | Sensitivity |

|----------|-----------------------------------------------|---------------------------------------------------|--------------------|-----------------|-------------|

| CC2500   | 2.4 GHz                                       | 2FSK, GFSK,<br>MSK, OOK                           | 500 kbps           | 1 dBm           | -104 dBm    |

| CC1121   | 410 MHz ~<br>480 MHz,<br>820 MHz ~<br>960 MHz | 2FSK, 2GFSK,<br>4FSK, 4GFSK,<br>MSK, OOK          | 200 kbps           | 16 dBm          | -120 dBm    |

| NRF24L01 | 2.4 GHz                                       | GFSK                                              | 2 Mbps             | 20 dBm          | -94 dBm     |

| SI4461   | 142 MHz ~<br>1.05 GHz                         | 4GFSK,<br>GFSK, GMSK,<br>OOK                      | 1 Mbps             | 16 dBm          | -129 dBm    |

| ADF7021  | 80 MHz ~<br>650 MHz,<br>862 MHz ~<br>950 MHz  | 2FSK, 2GFSK,<br>3FSK, 4FSK,<br>FHSS, GMSK,<br>MSK | 32.8 kbps          | 13 dBm          | -130 dBm    |

In some drone applications, for example, drone small cells (DSC) [2], the drone is used as a base station. The communication system itself has the major role and it is supposed to transmit large volumes of data. For these special cases, the communication system needs to cover a large range, with the permission to transmit high power signal levels and occupy large bandwidths. The need to have a high-efficiency RF-frontend is of crucial interest, because the drone power supply system nowadays, apart from supplying the motors to maintain the drone position, few rooms remain to support a power-hungry wireless base station.

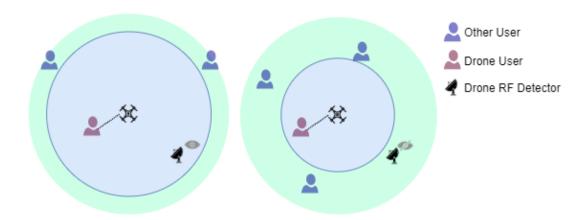

Furthermore, most drone communication systems are independent of the drone context. The communication system only involves the wireless data link and the flight controller only cares about how to fly. The communication system uses its maximum ability to have the best QoS (quality of service), conventionally sends signals with the same power, even though if the drone is fairly close to the GCS. Sending signals with a certain power level leads to unnecessary power consumption and is a kind of vulnerability that a third-party may utilize to estimate the location of the drone. Therefore, one of the objectives of this master thesis is to design a flexible and efficient communication system optimized for the UAS.

## **Objectives**

Below listed the goals of this master thesis:

- 1. Provide an overview on the drone communication system.

- Discuss current existing solutions on some popular drone platforms.

- Identify the most used modulation, typical output power levels, bandwidth, data rates, power efficiency, coverage and operating frequencies.

- 2. Design a communication system architecture optimized for drones

- Propose a scheme to adjust the TX power automatically.

- Design an OFDM downlink communication system.

- Include a DPD linearization system that in combination with the proposed TX power control scheme, significantly improves the overall power efficiency while maintaining the required linearity levels.

- 3. Implementation of core algorithms in a FPGA

- Implement the main algorithms (IFFT and DPD) to IP cores for Xilinx FPGA by using the high-level synthesis (HLS) methodology to prove their feasibility.

- Optimize the design by reducing the hardware resources usage and increasing the throughput to meet the required data rate.

## **Technologies involved**

This thesis relies heavily on digital signal processing for RF communications. For example, IFFT is used in the OFDM signal generation. In order to have a better performance in linearity, DPD linearization is used to predistored the baseband signal. In the scheme design part, Python programming language is used to build the mathematical models and perform the theory validation.

The FPGA programming is also part of the technologies involved in this thesis. To implement an IP core, techniques on in-chip interfaces, FPGA resources, and the hardware architectures have to be taken into account. The implemented IP core should give similar results as Python, so the cross-validation method is used to guarantee it. High-level-synthesis is used to develop and simulate an IP core. C++ is the selected language for the HLS development. Moreover, to reduce the validation time and avoid redundant coding in HLS, the template engine

Introduction 3

technique is introduced. In short, this thesis widely covers both software development and FPGA hardware development.

## **Planning**

A complete wireless communication system requires a huge amount of development for every specific detail and follows many industrial specifications. This thesis, however, will simplify many details and focus the new design strategies on the specific parts that can have an impact in the drone context. The project is therefore divided into three stages: design stage, implement stage and done stage. In time planning, general consideration will be done in advance to initiate some plan tasks as separate goals in the design stage. Then some tasks will be moved to the implement stage and focusing on these tasks, once a task is finished, it will be moved to the done stage. Each task can be considered independent and parallel, which means that there is no need to wait for a specific task. In this way, when encountering some difficulties, it is possible to switch to another task and maximize the final outputs within the project period. This is eventually following the Kanban scheduling system. The Kanban was designed to have three process stages: "design", "implement" and "done". Each task is a card in the Kanban board, initialized in the design stage and will be pushed to the next stage once been finished.

Fig. 1.1 Kanban board schedule

### CHAPTER 2. DRONE COMMUNICATION SYSTEM

In this chapter, an overview on the drone communication system will be presented and discussed. Details on the transceiver type, modulation method, data rate, and power consumption of the existing commercial solutions will be analysed. According to these characteristics, we will analyse their design motivation, identify their advantages and try to minimize their disadvantages. Finally, we will come up with an optimized scheme for the drone communication system.

## 2.1. Targeting UAS

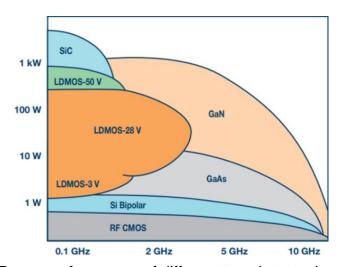

Before exploring the existing transmitting solutions, we will specify the UAS selected to apply the optimization on the communications system. Since drones are vehicles that fly at the altitude of tens and hundreds of meters, in order to perform data exchange, it is natural to think about using wireless solutions. UAS can be used for different purposes and have different levels of complexity. It can be as simple as a toy for kids or can be as complicated as a military weapon. For the simplest cases, the communication system is a trivial remote controller with only an uplink, so no data will return from the drone. Apparently, it is not worth spending efforts to perform optimization. According to the regulation from EASA [3], drones were classified into 5 classes, C0-C5. Each class follows with some limitations on the features such as maximum take-off mass (MOTM), height and speed. For example, C0 operates in the open category, only allows flying a low altitude (≤120 m) with MOTM of 250 g and air speed of 19 m/s. Although EASA does not explicitly regulate the communication system of UAS, some limitations on certain characteristics indirectly affects the communication system. For example, the maximum power voltage for C0 and C1 is 24 V, for C2 and C3 is 48 V. Since high-power power amplifiers require a supply voltage of 28 V, it is not possible to equip it on the C0 or C1 UAS. For those who can get permission to fly C4 drones, they are also more likely to gain special permission on the use of RF, to send higher power signals and to occupy a larger bandwidth. Table 2.1 shows the level of flexibility to perform modification on the drone communication system.

Table 2.1 Three levels of flexibility to custom drone communication system

|                   | Low    | Medium | High        |

|-------------------|--------|--------|-------------|

| Possible Class    | C0,C1  | C2,C3  | C4          |

| Data Rate         | Low    | High   | Even Higher |

| Max Altitude      | 120 m  | 120 m  | N/A         |

| Weight            | ≤900 g | ≤25 kg | N/A         |

| Power Voltage     | ≤24 V  | ≤48 V  | N/A         |

| Worth to optimize | No     | Yes    | Yes         |

C2, C3 covers most of the cases, because it allows a drone weight up to 25kg, so it is possible to mount payloads such as LiDAR and cameras. With granted permission, it is possible to fly beyond the visual line of sight (BVLOS). In the view of communication system, it means both uplink and downlink are included. The transceivers must have enough bandwidth to transmit/receive video data, and must send them with enough power to cover a certain range. When the required TX power is getting higher, it makes more sense to give optimization on power efficiency. For the most special cases like C4 and sometimes the military drones that are granted with the highest permission, the flight altitude can be much higher and the TX power is much higher, there is more payload data to send and higher signal bandwidths can be used. The PA power efficiency versus linearity trade-off becomes more important and the proposed communications architecture would be much more useful.

## 2.2. Existing solutions

With considerations of robustness and range for telemetry, and the large throughput requirement for video transmission, most of the existing drones detach the communication affairs to the telemetry link and video link. According to the research of drone communication protocols in [4], popular modulation schemes have been proposed, as shown in the Table 2.2, spread spectrum techniques of frequency hopping spread spectrum (FHSS) and direct sequence spread spectrum (DSSS) are widely used in the telemetry link.

Table 2.2. Telemetry link scheme for drone [4]

| Brand       | Frequency   | Modulation | Technology  |

|-------------|-------------|------------|-------------|

| DJI Phantom | 2.4/5.8 GHz | FHSS/ DSSS | FASST/      |

|             |             |            | Lightbridge |

| Futaba      | 2.4 GHz     | FHSS/ DSSS | FASST       |

| Spektrum    | 2.4 GHz     | FHSS/ DSSS | DSM2/ DSMX  |

| JR          | 2.4 GHz     | FHSS/ DSSS | DMSS        |

| Hitec       | 2.4 GHz     | FHSS/ DSSS | AFHSS       |

| Graupner    | 2.4 GHz     | FHSS/ DSSS | HOTT        |

| Yuneec      | 2.4 GHz     | DSSS       | ZigBee      |

| Parrot AR2  | 2.4 GHz     | OFDM       | Wi-Fi       |

| Immersion   | 433 MHz     | FHSS       | EZUHF       |

The telemetry link is used to send essential status information like battery voltage, position, and commands. These data are important for the operator but might not necessary for the application. On the other hand, these low-speed data need to be reliable and secure, hence spread spectrum techniques are extremely fit with them. According to the specification of DJI Phantom [5], when running in the RC and FCC mode (only enable the telemetry), without obstacles and free of interference, it is possible to fly at a distance of 7000 meters. It is enough for most drone applications.

Things are different when considering video streaming. The video stream contains much more data and requires more bandwidth than the telemetry link. Advanced modulation techniques such as OFDM is more likely to be used. The following table (Table 2.3) shows that FM and OFDM are popular choices.

| Brand     | Frequency | Modulation | Technology        |

|-----------|-----------|------------|-------------------|

| DJI       | 2.4 GHz   | OFDM       | Lightbridge/Wi-Fi |

| Immersion | 2.4 GHz   | FM         | -                 |

| Yuneec    | 5.8 GHz   | OFDM       | Wi-Fi             |

| Connex    | 5.8 GHz   | OFDM       | -                 |

| Boscam    | 5.8 GHz   | FM         | -                 |

The RF signal of the Video link occupies a large bandwidth, spread spectrum is no longer suitable because it will make the spectrum wider and difficult to meet the ISM regulations. The DJI phantoms radio link with the video stream enabled downgrades the maximum distance to 2000 meters. To find out more characteristics of the drone video link, a simple experiment was done with the DJI Lightbridge and a spectrum analyser. The Lightbridge can transmit both the video stream and the control commands. After the booting sequence, the signal from the Lightbridge can be monitored in the spectrum analyzer as shown in Fig. 2.1.

Fig. 2.1 Spectrum of the DJI Lightbridge signal

The spectrum analyzer received the signal through an antenna at a 2.4 GHz with a 10 dB attenuator. From the spectrum plot, the feature of the video signal can be clearly seen, it occupies 20 MHz in the 2.4 GHz band. If the drone position stays the same, the signal spectrum will always have the same shape and the

same power, as specified in Table 2.3, this is a 20 MHz OFDM signal. If the drone moves away from the receiver antenna, the signal power will decrease following a linear-like pattern. It means that the feature of the video link is possible to recognise and the fixed output power makes it possible for estimating the drone distance. Some drone detection projects [6, 7] were made based on these assumptions. Furthermore, the Lightbridge specs [8] shows that it transmits 100 mW at 2.4 GHz and the air system operating current is 650 mA at 12 V, so the overall system power efficiency for transmitting is very low, approximately 100mW/(650mA\*12V) \* 100% = 1.28%. (It is not the PA efficiency alone, the PA efficiency must be higher, but we do not have the detailed information to know the specific PA efficiency)

The camera is a type of payload equipped on the drone, so the video link can also be considered as the payload link responsible for transferring payload data in real-time. So far, the conclusion on the conventional video link is listed below:

- Video (payload) link uses OFDM for sending a large amount of data with high spectral efficiency (i.e., bits/s/Hz).

- The output power is fixed regardless of the drone position.

- The wireless traffic is asymmetric and it is more relevant in the downlink.

- The RF system efficiency (defined as the RF transmit power/consumed DC power x100%) is low.

Inspired from the above conclusions, the following subchapter will give a scheme to optimize the communication system for UAS.

## 2.3. Optimized transmitter architecture

The proposed architecture is an OFDM communication system optimized for drone communications. All the modifications were performed in the drone transmitter side. Fig. 2.2 shows the block diagram of the proposed scheme.

Fig. 2.2 Block diagram of the drone transmitter and GCS receiver.

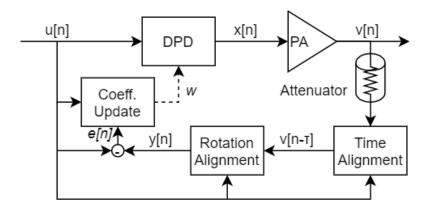

Fig. 2.2 shows the three subsystems (highlighted in blue) specifically designed in this thesis, which took the most of our efforts and resources. First, because of the wide use of OFDM in drone video links, it deserves to remain in the scheme. Second, the dynamic TX power estimation block estimates the required TX power, based on the distance between UAS and GCS, and the RSSI from the GCS receiver. With the estimated TX power level, the power supply can adjust the gain of the VGA and the supply voltage of the power amplifier in order to improve the PA power efficiency. Finally, the DPD is used to guarantee the PA linearity. The change of the PA supply voltage will lead to a change of the PA behaviour. So, the DPD needs to be able to track these changes and adapt its coefficients.

The automatic TX power control system can add some advantages to the drone communication system. For example, if multiple drones are flying at the same time and operating at the same radio channel, each user will have to keep a distance to avoid interference. The power control system can automatically lower the TX power and make it possible to fly more drones within an area. On the other hand, a fixed output power makes it possible for a third party to detect the existence of drone and locate the position. The dynamic TX power can at least hide the drone distance information. When the drone is closer to the operator than the RF detector, the drone detector has more difficulties to detect the drone's existence.

**Fig. 2.3** Static TX power vs dynamic TX power.

In summary, the proposed scheme can improve the UAS downlink with the following advantages:

- It can save the unnecessary TX power.

- It makes the drone hard to be detected by a third party.

- More drones could be used within a large area.

- It can improve PA efficiency by using optimized supply settings and DPD.

### CHAPTER 3. SYSTEM DESIGN

This chapter will present the design details of the communication system. First, for estimating the required TX power, a Kalman filter will be designed. Then the OFDM signal generation and recovery will be designed and simulate. Finally, the DPD algorithms will be presented and tested together with the OFDM signal in a customized testbed built for the occasion.

## 3.1. Automatic transmit power control

Link budget is a general method to calculate the required TX power. In the link budget calculation, the received power is estimated by adding all gains and subtracting all losses. Note that the unit of power in this thesis is always expressed in the logarithmic scale (i.e., dBW or dBm). The equation of the link budget is shown below.

$$P_{rx} = P_{tx} + \sum_{i} Gain_i - \sum_{j} Loss_j$$

(3,1)

In the proposed drone communication system, the gain items include the TX and RX antennas gain, and the gains from RX LNA and the TX PA. The loss items are the free space propagation loss (FSPL) and the pointing loss due to the moving behaviour, and the antenna polarization. Some of these items are constant, for example, the RX LNA gain is always fixed, while other items change according to the situation, for example, the free space loss changes with the distance. Table 3.1 shows detail of the loss and gain factors taken into account in this master thesis.

Table 3.1. Gain and loss factors

| Factors                     | Fixed |

|-----------------------------|-------|

| GCS antenna gain            | Yes   |

| GCS LNA gain                | Yes   |

| GCS cabling loss            | Yes   |

| GCS pointing loss           | No    |

| UAS antenna gain            | Yes   |

| UAS cabling loss            | Yes   |

| UAS pointing loss           | No    |

| UAS PA gain                 | No    |

| Free space propagation loss | No    |

Although the UAS pointing angle can be obtained from the IMU data, the GCS can be a hand-held device whose angular position is unpredictable, hence the pointing loss cannot be calculated. For simplicity, assuming the use of bipolar antennas, a constant pointing loss budget of 6 dB (the worst case) is reserved. As a result, the remaining variables are the TX PA gain and the FSPL. Denote  $P_c$

as the sum of all the constant losses and gains, the received power  $P_{rx}$  can be derived as follows.

$$P_c = P_{tx} + \sum G_{const} - \sum L_{const}$$

(3,2)

$$P_{rx} = P_c + G_{PA} - L_{freespace}$$

(3,3)

The objective is to estimate the required TX power and then derive the PA gain. The OFDM system sensitivity and the receiver performance decide the required received power, which is also a constant. In the actual practices, an extra link margin will be preserved to the system. By moving the PA gain to left side, the equation of the required PA gain is shown below, where  $P_{cc}$  denotes the sum of all constants.

$$P_{cc} = P_{rx,required} - P_c + ExtraLinkMargin$$

(3,4)

$$G_{PA,required} = P_{cc} + L_{freespace}$$

(3,5)

$P_{cc}$  can be obtained by some rough experimental tests. Now that the only variable left is the FSPL, which is the loss between two isotropic radiators in the free space, expressed as a power ratio. In the log scale, it is a function of distance and center frequency. The equation of FSPL is shown below, the unit of distance is meter and the unit of frequency is Megahertz.

$$FSPL(dB) = 20\log_{10}(d) + 20\log_{10}(f) - 27.55$$

(3,6)

In an ideal case, given the accurate GPS position of GCS and the UAS, the distance can be calculated and the required TX power can be indicated. The position of GCS can be sent to the UAS through the telemetry link, and the automatic power regulation takes place on the UAS. However, in a realistic case we also have noise and unwanted obstacles, and thus this simple method is not reliable. The following subchapter describes the efforts of using a Kalman filter to make it more reliable and robust.

#### 3.1.1. Kalman filter for estimating the RX power

There are several reasons for not having an accurate estimation. For example, the constant  $P_{cc}$  is a rough approximation, and the GPS location can have some meters of error. Apart from these numerical errors, obstacles such as buildings, mountains, and trees can randomly appear in the path of the wireless communication link. If the link margin is small, the UAS may lose communication for a moment. On the contrary, if a big link margin is introduced to the transmitter, then the TX power is significantly higher than the minimum required power, which is clearly against our objective of saving power. What's more, the GCS can also be a moving object such as a car, and its GPS location may be missing, so the distance measurement is not always available. Fortunately, the receiver on the

GCS can calculate the RSSI and send it to the UAS to improve the required TX power estimation.

The problem now becomes: Knowing the previous received signal power, predict the next RX power. The derived equation is shown below, where  $\hat{P}_{rx}$  represents the estimated RX power  $\Delta$  represents the difference.

$$\hat{P}_{rx} = P_{rx} + \Delta G_{PA} - \Delta L_{freespace}$$

(3,7)

The difference between TX power ( $\Delta G_{PA}$ ) is a variable which can be controlled by the automatic power control system. The difference of the FSPL ( $\Delta L_{freespace}$ ) can be derived from the distance. The current distance is denoted as  $d_t$ , and the former distance as  $d_{t-1}$ , the difference of FSPL can be derived as follows,

$$\Delta L_{freespace} = L(d_t) - L(d_{t-1})$$

(3,8)

$$\Delta L_{freespace} = 20\log_{10}(d_t) - 20\log_{10}(d_{t-1})$$

(3,9)

To be more specific, the distance can be measured by calculating the Euclidean distance from the UAS to the GCS by using the GPS data. By denoting the longitude as X, the latitude as Y and the height as Z (all the units are in meters), the distance, d, is given by

$$d = \sqrt{(X_{gcs} - X_{uas})^2 + (Y_{gcs} - Y_{uas})^2 + (Z_{gcs} - Z_{uas})^2}$$

(3,10)

The linear velocity v along the line of GCS and UAS can also be estimated from the distance difference over time. Finally, the prediction of RX power is a function over time, given by

$$\hat{P} = P + 20log_{10}(\frac{d + v\Delta t}{d}) + \Delta G_{PA}$$

(3,11)

In short, the system keeps tracking the RX power P, distance d and velocity v between GCS and UAS. The next state can be predicted by equation (3,11), and the measurement of distance and RX power can be obtained from the GCS through the telemetry link to improve the estimation. It can be described as a typical Kalman filter process as shown in the Table 3.2.

Table 3.2. Kalman filter procedure of the problem

| State       | p, d, v                                            |

|-------------|----------------------------------------------------|

| Predict     | $\hat{p}, \hat{d}, \hat{v} = f(p, d, v, \Delta t)$ |

| Measurement | $gps \rightarrow d, rssi \rightarrow p$            |

The basic Kalman filter requires linear equations for state propagation, however, the logarithmic operation is not linear. Fortunately, the speed between GCS and UAS is not very high, extended Kalman filter can be used to linearize the problem.

As shown in Fig. 3.1, the relationship between FSPL and distance at 2.45 GHz, from 10 to 2000 meters is a log curve, but when zoom in and have a closer look of 100 meters range from 240 to 340 meters, it is nearly a straight line.

Fig. 3.1 FSPL vs distance

The discrete-time Extended Kalman filter process is shown in Table 3.3.

Table 3.3. Discrete time EKF

| Predict                     |                                                     |

|-----------------------------|-----------------------------------------------------|

| State estimate              | $\hat{x}_{k k-1} = f(\hat{x}_{k-1 k-1}, u_k)$       |

| Covariance estimate         | $P_{k k-1} = F_k P_{k-1 k-1} F_k^T + Q_k$           |

| Update                      |                                                     |

| Measurement residual        | $\tilde{y}_k = z_k - h(\hat{x}_{k,k-1})$            |

| Residual covariance         | $S_k = H_k P_{k,k-1} H_k^T + R_k$                   |

| Kalman gain                 | $K_k = P_{k k-1} H_k^T S_k^{-1}$                    |

| Updated state estimate      | $\hat{x}_{k k} = \hat{x}_{k k-1} + K_k \tilde{y}_k$ |

| Updated covariance estimate | $P_{k k} = (I - K_k H_k) P_{k k-1}$                 |

The state prediction function f contains three individual functions for this model, one for predicting the RX power, one for the distance and one for the velocity.

$$\begin{bmatrix} \hat{p} \\ \hat{d} \\ \hat{v} \end{bmatrix} = f \begin{pmatrix} p \\ d \\ v \end{pmatrix} = \begin{bmatrix} p + 20log_{10}(\frac{d + v\Delta t}{d}) + \Delta G_{PA} \\ d + v\Delta t \\ v \end{bmatrix}$$

(3,12)

The F in the Extended Kalman filter is the Jacobians of f, given as

$$\mathbf{F} = \frac{\partial f}{\partial x} = \begin{bmatrix} \frac{\partial f_1}{\partial p} & \frac{\partial f_1}{\partial d} & \frac{\partial f_1}{\partial v} \\ \frac{\partial f_2}{\partial p} & \frac{\partial f_2}{\partial d} & \frac{\partial f_2}{\partial v} \\ \frac{\partial f_3}{\partial p} & \frac{\partial f_3}{\partial d} & \frac{\partial f_3}{\partial v} \end{bmatrix}$$

$$= \begin{bmatrix} 1 & \frac{20d(\frac{1}{d} - \frac{1}{d^2}(d + \Delta tv))}{(d + \Delta tv)ln(10)} & \frac{20\Delta t}{(d + \Delta tv)ln(10)} \\ 0 & 1 & \Delta t \\ 0 & 0 & 1 \end{bmatrix}$$

(3,13)

Similarly, to calculate the Jacobians of the measurement function h, the measurement matrix H is given by

$$h\begin{pmatrix} p \\ d \\ y \end{pmatrix} = \begin{bmatrix} p \\ d \end{bmatrix}, H = \frac{\partial h}{\partial x} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \end{bmatrix}$$

(3,14)

The EKF also requires the process noise matrix  $\mathbf{Q}$  and the measurement noise matrix  $\mathbf{R}$ . The processing noise of RX power is independent of the position, and the processing noise of velocity and distance can use the discrete white noise model in [9],  $\mathbf{Q}$  is given below and  $\sigma_{rx}$  represents the RX power variance and  $\sigma_d$  is the distance variance.

$$\mathbf{Q} = \begin{bmatrix} \sigma_{rx}^2 / \sigma_d^2 & 0 & 0 \\ 0 & T^4 / 4 & T^3 / 2 \\ 0 & T^3 / 2 & T^2 \end{bmatrix} \sigma_d^2$$

(3,15)

For the measurement noise, the noise from the receiver of GCS is independent of the GPS. The measurement noise matrix R can be defined by doing some experimental measurements.

$$\mathbf{R} = \begin{bmatrix} \sigma_{receiver}^2 & 0\\ 0 & \sigma_{gps}^2 \end{bmatrix}$$

(3,16)

The proposed EKF design has been coded in Python, and numerical simulation was conducted to validate the correctness of the theory. The simulation results are presented in the following subchapter.

## 3.1.2. Simulation of the power and distance estimation in Python

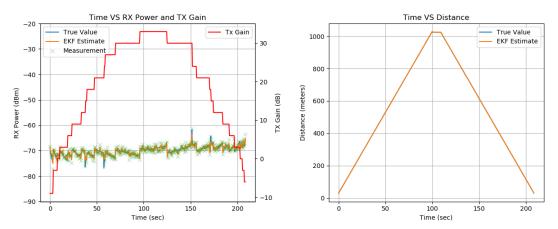

The first simulation assumed a UAS flying away from the GCS without any obstacle, the distance and RSSI data were generated according to the mathematical model as the "true value". Gaussian noise was added to the "true value" to emulate the sensor measurement. The proposed EKF filter was used to predict and update the states. Fig. 3.2 shows the drone moving away with a

speed of 10 m/s, the EKF can work fine to follow the true line of RX power. The distance in the following simulation are the Euclidean distance between the drone and the GCS.

Fig. 3.2 EKF RX power and distance vs time

The second simulation in Fig. 3.3 takes the obstacles into account. Let's assume that the UAS signal is blocked by some object (e.g., buildings, trees, mountains, etc.) at 400 meters and 600 meters, and each obstacle can cause 6 dB of loss. The same EKF was applied to the emulated data, as shown in Fig. 3.3, the filter can match the line of true value, which validates the robustness of the Kalman filter for predicting the RX power and distance.

Fig. 3.3 EKF RX power and distance vs time with obstacles

A last simulation has been considered to complete some of the typical scenarios. Let's assume that the UAS will hold the position for 10 seconds (maybe executing some missions) and then fly back to GCS. As shown in Fig. 3.4, the change of velocity does not affect the quality of the EKF estimation.

Fig. 3.4 EKF RX power and distance vs time with obstacle and go back

### 3.1.3. TX power control logic

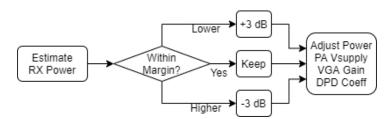

Taking into account the good estimation of the RX power obtained with the EKF, it is possible to calculate the required PA gain by using equation (3,5) and adjust the TX power. In this work, we used a simple strategy of increasing/decreasing the TX power when the prediction exceeds a certain margin. For example, given the margin of 6 dB and the required RX power of -70 dBm, when the estimated RX power is lower than -73 dBm or higher than -67 dBm, the output power will increase or decrease 3 dB. To adjust the output power, the VGA gain and the power supply of PA need to be set. In the meantime, the DPD linearizer needs to be informed and adapt its coefficients. With this method (summarized in Fig. 3.5), it is possible to pre-define a set of output power levels, which is helpful for the DPD to have a limited number of pre-calculated coefficient configurations.

Fig. 3.5 Automatic power control logic

In combination with the third simulation from the last subchapter, let's assume that the UAS flew away from the GCS and then waited 10 seconds and came back. The behaviour of the automatic TX power control was simulated and the results are shown in Fig. 3.6. In Fig. 3.6-left, the orange line shows that the RX power was well controlled at the level of -70 dBm. The red line shows the TX PA gain increase and decrease with a similar shape to the distance plot.

Fig. 3.6 The simulated control of TX power

With the proposed automatic TX power control logic, the TX power can change according to the specific needs and thus saving unnecessary power consumption. To improve the PA efficiency while guaranteeing its linearity, DPD linearization will be included, it will be described later in subchapter 3.3. Before that, the OFDM system needs to be designed for signal generation. Next subchapter will discuss the design of a simple OFDM downlink system.

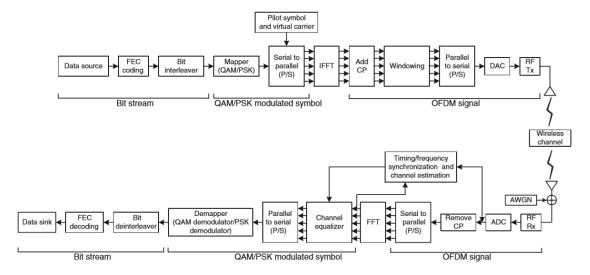

## 3.2. Design of an OFDM system

Orthogonal frequency division multiplexing (OFDM) is a suitable multicarrier access technique for the drone video link, since it allows achieving high data throughput in the downlink. As shown in Fig. 3.7, full implementation of an OFDM system involves the design of a bit interleaver, mapper, synchronizer, etc., which is not the objective of this thesis. However, generating a decent OFDM signal is necessary for demonstrating the application. In this work, the OFDM was simplified, most of the efforts were put in the signal generation.

Fig. 3.7 OFDM full implementation diagram [10]

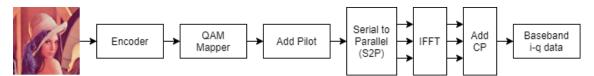

As the UAS downlink usually contains a video stream, an image was selected as representative of the payload data. The image data bytes will go through the encoder, QAM mapper and other function blocks to generate the baseband I-Q signals. The baseband data will then be upconverted to the RF signal and transmitted through the air. The block diagram in Fig. 3.8 shows the simplified OFDM generator used in this thesis.

Fig. 3.8 OFDM baseband generator

#### 3.2.1. Encoder

The encoder converts the RGB image bytes to bits array follows the order of bigendian. To lower the design complexity, compression methods are not used, so the length of bits has a direct relationship with the size of the image, and the frame rate is low. Besides, retransmissions and CRC methods are not included. The received image could have lots of distortion depending on the transmission quality.

## 3.2.2. QAM mapper

Typically, the OFDM transmitter requires the bits mapped into PSK or QAM symbols which will be subsequently converted into N parallel streams. The modulation scheme 64-QAM was used in this work, with a square-like constellation and Gray coding as shown in Fig. 3.9.

Fig. 3.9 QAM-64 gray coding constellation

Each 64-QAM symbol contains six bits of information, so the number of payload data in bits should be an integer multiple of six. As the encoder directly converts the 3-channel (RGB) image from bytes to bits, it is possible to group the data into 6 bits per batch. The equations below show the relationship between RGB image

size and the number of bits and symbols, where w and h denote the image width and height respectively, and h denotes number of symbols per image.

$$ImageBits = w \times h \times 3(rgb) \times 8(bits/byte) = n \times 6$$

(3,17)

$$SymbolsPerImage = n = w \times h \times 4$$

(3,18)

In short, the QAM mapper converts every 6 bits to a complex symbol according to the constellation map in Fig. 3.9 and then passes it to the next procedure. The QAM mapping was done in Python and Fig. 3.10 shows the symbol distribution of the "lenna.jpg". The heat map on the right shows the distribution of symbols in percentage. All QAM symbols are used with the minimal distribution of 0.4% and the maximal of 3.1%, over 1,048,576 symbols.

Fig. 3.10 Sample image and QAM symbol distribution

## 3.2.3. Pilots and serial to parallel conversion

OFDM time-domain signals consist of a set of data subcarriers that deliver the information and pilot subcarriers that help to estimate the radio channel. In the frequency-domain, data carriers are the QAM symbols, which have been generated in the previous subchapter by the mapper. Pilot carriers are inserted between data carriers or OFDM symbols depending on the arrangement. Three different types of pilot structures are considered: block type, comb type, and lattice type. Fig. 3.11 shows the three aforementioned arrangements.

Fig. 3.11 Comparison of three pilot structures [10]

In the block-type, the OFDM symbols with pilots at all subcarriers are transmitted periodically. Time-domain interpolation is performed to estimate the channel along the time axis, it is suitable for frequency-selective channels. For the Combtype, every OFDM symbol has pilot tones that are periodically-located between subcarriers. Frequency-domain interpolation is performed to estimate the channel along the frequency axis, it is suitable for fast-fading channels. In Lattice-type, pilot tones are inserted along both the time and the frequency axes with certain periodicity. Both time and frequency domain interpolations are required to estimate the channel, it can work for both frequency-selective and fast-fading channels, however, it is complicated to implement. According to the study of the UAS communication channel [11, 12], for the air to ground communication during the take-off, en-route and landing phases is more justified to use the fast-fading channel, hence, the comb-type has been selected in this thesis.

Each OFDM symbol contains several QAM symbols, these symbols have to be parallelized before sending them to the IFFT block. The number of QAM symbols per spectrum shot depends on the number of OFDM subcarriers and the number of pilot subcarriers. For example, in the WLAN 802.11n/ac protocol, 20 MHz bandwidth is divided by 64 for each subcarrier, the space between each subcarrier is 312.5 KHz. Only 56 subcarriers near the low frequency are used with 52 subcarriers for data and 4 for pilots. In LTE, typically 2048 subcarriers are used, but only 1200 subcarriers are active, with subcarrier spacing of 15 kHz and sampling frequency of 30.72 MHz, the occupied bandwidth is approximately 18 MHz. The following table shows a comparison of different standards using OFDM-based communications.

Table 3.4. Comparison of different OFDM protocols

|                               | LTE<br>(BW=20MHz) | WIFI<br>802.11g/a | WIFI<br>802.11n/ac |

|-------------------------------|-------------------|-------------------|--------------------|

| Total Subcarriers (NIFFT)     | 2048              | 64                | 64                 |

| Active Subcarriers            | 1200              | 52                | 56                 |

| Subcarrier spacing $\Delta f$ | 15 kHz            | 312.5 kHz         | 312.5 kHz          |

| Sampling frequency (Fs)       | 30.72 MHz         | 20 MHz            | 20 MHz             |

| Occupied Bandwidth            | 18 MHz            | 16.25 MHz         | 17.5 MHz           |

In this work, we considered the 802.11n/ac as the OFDM design reference. So, 64 IDFT with 56 activated subcarriers are used. The pilot and subcarriers allocation are shown in Fig. 3.12.

Fig. 3.12 Pilots location and the OFDM subcarriers scheme

The serial to parallel conversion requires grouping every 52 QAM symbols to a batch. However, the number of QAM symbols of an image cannot fit with the size of integer multiple of 52, redundant random symbols were added at the end to address the lack of OFDM symbols.

#### 3.2.4. IFFT

Time-domain OFDM baseband signals were given by applying the IDFT (Inverse Discrete Fourier Transform) of the frequency-domain OFDM symbols. It can be computed efficiently by using the IFFT (Inverse Fast Fourier Transform) algorithm.

$$x_{l}[n] = \frac{1}{N} \sum_{k=0}^{N-1} X_{l}[k] e^{j2\pi kn/N}$$

(3,19)

With the IFFT functions from the Python library of *NumPy*, this procedure can be easily done with one line of code. IFFT should apply to every OFDM symbol individually and ensure that the same IFFT size was used.

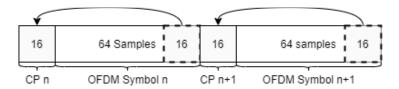

## 3.2.5. Cyclic prefix

The OFDM needs guard intervals to mitigate the ISI (Inter Symbol Interference). The length of the guard interval should be set not shorter than the maximum delay (i.e., delay spread) of the channel. Cyclic prefix (CP) consists in extending the OFDM symbol by copying the last samples of the time-domain symbol at the beginning. Taking a quarter of the 64 IFFT size signal as the CP, the last 16 samples will be copied at the beginning, as shown in Fig. 3.13.

Fig. 3.13 OFDM cyclic prefix

### 3.2.6. OFDM baseband data samples

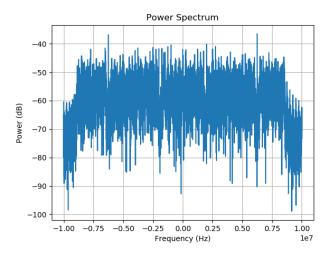

After adding the CP, the original 512x512 RGB image has been converted to baseband data with 1,613,200 samples. The samples are then divided into 10 batches (this would not break an OFDM symbol); each batch has 161,320 samples that can be directly sent to the I-Q upconverter after digital to analog conversion. In the following chapter, we will use these data samples for training the DPD to guarantee the required linearity levels at the output of the RF power amplifier and enhance its power efficiency. To better describe the generated data, Fig. 3.14 shows the power spectrum of the I-Q baseband signals, samples were normalized to 1 before the FFT.

Fig. 3.14 Power spectrum of the samples

One unwanted characteristic of OFDM signal is that it can present high peak to average power ratios (PAPRs). The transmit signals can have high peak values since many subcarrier components can be added constructively (in-phase) after the IFFT operation. The calculation of PAPR is given as below.

$$PAPR(dB) = 10log\left(\frac{P_{max}}{P_{avg}}\right) = 10log\left(\frac{max(|x[n]|^2)}{avg(|x[n]|^2)}\right)$$

(3,20)

The PAPR can degrade a wireless transmission chain since it can put most of those systems operating in a large-signal nonlinear zone. The DAC and the PA of the transmitter require large dynamic ranges to avoid amplitude clipping. Crest factor reduction (CFR) techniques are therefore used to reduce the PAPR of the OFDM-based signals. Several CFR techniques for OFDM-based signals have been published in literature, for example:

- **Coding**, that consists in using custom coding schemes to reduce the occurrence probability of the same phase of signals by selecting the codewords that minimize the PAPR in the transmission.

- Partial Transmit Sequence (PTS), that partition the input data into disjoint sub-blocks. Then, the sub-carriers in each sub-block are IFFT transformed into time-domain partial sequences and independently weighted by phase factors.

- **Selected Mapping (SLM)**, that use the transmit sequence and multiply it by a codeword (vector of phase-shifts) that will change it in order to decrease the PAPR.

- Interleaving Technique, similar to the SLM, uses a set of interleavers instead of phase sequences to generate new data blocks to reduce PAPR of OFDM-based signals.

- Clipping and Filtering, that is used for abruptly reduce the peaks on the envelope signal. Nonlinear distortion of spectral regrowth will occur due to the peak cut-off, following a band-pass filter is used to compensate for the out-of-band distortion, however residual in-band distortion remains.

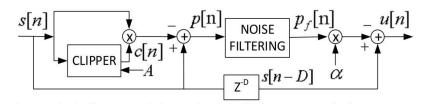

As explained in [13], the peak cancellation (PC) technique can reduce the signal PAPR and properly combined with DPD can enhance the PA power efficiency while guaranteeing the overall linearity. The PC method belongs to the clipping and filtering branch of CFR techniques. The block diagram of scaled peak cancellation (SPC) technique is shown in the figure below.

Fig. 3.15 Diagram of peak cancellation CFR technique [13]

The clipper output c[n] can be written as (3,21) where A is the clipping threshold.

$$c[n] = \begin{cases} A/|s[n]| & \text{if } |x[n]| > A \\ 1 & \text{if } |x[n]| \le A \end{cases}$$

(3,21)

The clipped pulse p[n] is written as follows.

$$p[n] = s[n] - s[n] \cdot c[n]$$

(3,22)

After applying low pass filter to the clipped pulse to remove the high frequency discontinuity, and scaling by a factor  $\alpha$ , the final PAPR reduced signal u[n] can be obtain by subtracting a delay version of the input s[n], the output u[n] is described as follows, where h[n] is the low pass filter.

$$p_f[n] = p[n] * h[n]$$

$u[n] = s[n-d] - \alpha \cdot p_f[n]$  (3,23)

Scaled repeated peak cancellation (SRPC) method in [14] is an improved version of the scaled peak cancellation (SPC). The SRPC increases convergence rate to the desire threshold level by using several stages of the SPC technique, which is helpful to limit the peak re-growth caused by the filter. Let the  $\boldsymbol{u}$  in (3,23) be the input signal of next stage, the  $i^{th}$  stage SRPC can be described as follows.

$$u_1 = u - \alpha_1 \cdot p_{f1}$$

$$u_2 = u_1 - \alpha_2 \cdot p_{f2}$$

...

$$u_i = u_{i-1} - \alpha_i \cdot p_{fi}$$

(3,24)

The scale factors  $\alpha_i$  is given by

$$\alpha_i = \frac{\max(|\boldsymbol{p_i}|)}{\max(|\boldsymbol{p_{fi}}|)}$$

(3,25)

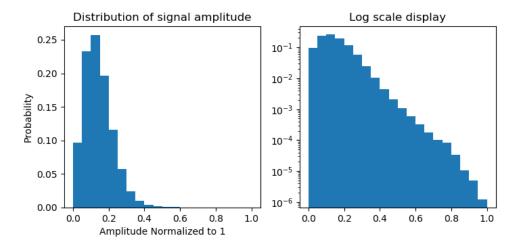

The SRPC technique will be used later in this thesis to reduce the PAPR of the generated OFDM signal. The clipping threshold need to be decided before applying the SRPC. By observing the distribution on the absolute value of the normalized OFDM baseband data, as shown in Fig. 3.16, most of the sample amplitude is below 0.5, so it is justified to set the clipping threshold to a little bit higher than 0.5 which is 0.6 in this work.

Fig. 3.16 Distribution of generated signal amplitude

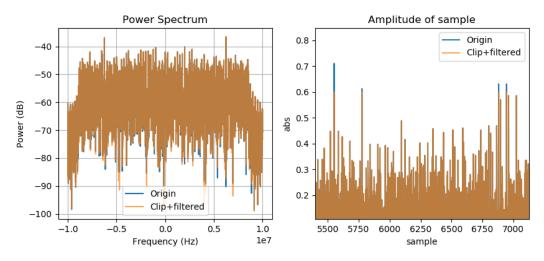

Low-pass filtering is required by the SRPC, so a FIR filter was designed. In the proposed OFDM system, the lower 56 subcarriers of 64-IFFT are used, the low pass filter should pass the lower part of 87.5% of the bandwidth. Besides, three iterations (i=3) are specified for the SRPC. Fig. 3.17 shows the comparison of the original signal and the signal after applying the clipping and filtering SRPC CFR method. It can be observed that the power spectrum is not significantly affected, and the amplitude after clipping and filtering is adequately controlled at the threshold of 0.6.

Fig. 3.17 Spectrum and Amplitude comparison on CFR signal

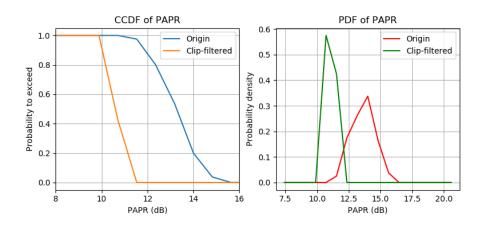

From the spectrum/time perspective, it is hard to tell the improvement regarding the PAPR. In order to know the improvement of the overall PAPR performance, the PAPR for every symbol sample signal is calculated individually, and the probability distribution function (PDF) and the cumulative density function (CCDF) of both the original signal and the signal after clipping and filtering were calculated. As shown in Fig. 3.18, the PAPR of the original baseband data is around 11-16 dB and approximately following the Gaussian distribution, with around 60% of the possibility to exceed 13 dB. The overall PAPR level is lower after the clipping and filtering. The mean PAPR has been moved left to about 11 dB. The peak probability is higher, and the shape is narrower, which means more likely to send the signal at the average level.

Fig. 3.18 CCDF & PDF of PAPR with or without cliping and filtering

#### 3.2.7. Channel simulation

The UAS communication system has the same characteristic of a mobile wireless system, i.e., both operate in a time-variant communication channel. The output signal after the communications channel is described by

$$y(t) = \int_{-\infty}^{\infty} x(t-\tau)h(\tau,t)d\tau$$

(3,26)

where h(t) is the time-variant impulse response of the channel. The large-scale attenuation model and the small-scale fading model can be used to simulate the UAS communication channels [12]. The large-scale attenuation model is suitable for UAS in the open environment where the attenuation of the signal in free space and the transmit path attenuation are considered, while multipath fading situation are not included. The impulse response h(t) for the large-scale attenuation model can be finally determined by the distance between the receiver and the kinematic position such as the angle of the UAS. The observed impact when considering a small burst of signal in our simulations are a constant phase shift, a small delay and the power loss on the whole original signal. The small-scale fading model is mainly for cities or mountain environments, since it takes into account the multipath fading factors. The impact of the multipath channel is that the received signal will be the sum of several signals coming with different amplitudes and delays (resulting from the different paths), which can be simulated by performing the convolution of the input signals with the impulse response h(t)of a multipath fading system. This will cause the signal to have different phaseshifts and magnitude changes on different frequencies. At the end, the channel simulation was simplified and we used a fixed impulse response with additive white Gaussian noise to meet a certain level of signal to noise ratio (SNR). In addition, a constant time shift  $\tau$  was added to represent the delay.

$$y[n] = \sum_{m=-\infty}^{\infty} x[n-m-\tau]h[m] + AWGN(SNR)$$

(3,27)

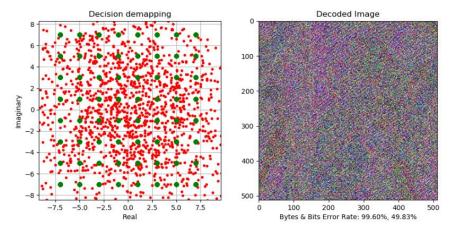

Without any kind of compensation, the received signal will be significantly distorted and thus, the demapped QAM constellation will be blurry and will introduce a huge amount of bit errors. As shown in Fig. 3.19, the demapped constellation is tremendously distorted and the image can be hardly recognized with a byte error rate of 99.6% and a bit error rate of 49.83%.

Fig. 3.19 Constellation decode without synchronization and equalization

### 3.2.8. Synchronization

Synchronization techniques are essential for OFDM-based communications to compensate for the symbol time offset (STO) and the carrier frequency offset (CFO) of the received signal. The STO is caused by the signal transferring time in the space and the processing time on both the transceiver and the receiver. If the FFT window begins in the cyclic prefix or the window begins after the starting point of the data part, inter-symbol interference (ISI) will be introduced and it cannot be compensated by using equalization. The CFO can be caused by the Doppler effect as the UAS is moving or by the slight frequency difference of the local oscillator (LO) between the receiver down-converter and the transmitter upconverter. Depending on the relative velocity of the UAS to the GCS, and the precision of the LO frequency, the impact of the CFO is different. The OFDM system relies on the orthogonality of subcarriers to avoid inter-carrier interference (ICI), however, the CFO misleads the receiver to calculate the FFT and generates a shifted spectrum which favours the appearance of ICI. Usually, the synchronization will first compensate the STO to find out the beginning of an OFDM symbol and then it will correct the CFO with the time-aligned signal.

The starting point of OFDM symbols can be accurately determined by estimating the STO with a synchronization technique at the receiver. The estimation of STO can be implemented in both time-domain and frequency domain. In the time-domain, STO can be estimated by using the cyclic prefix. For example, using the sliding windows method and considering two windows spaced N samples apart (where N is the length of the data symbol), where each has the same width as the CP. The sliding windows move through the received signal and calculating the similarity by summing the difference of both signals for different delays. Since the CP is a copy of a part of the data signal, the index of the minimum distance results at the starting point of an OFDM symbol. Taking into account the received signal y, the STO can be found by searching the point where the difference between two blocks of M samples within two sliding windows is minimum [10], as shown below.

$$\hat{\delta} = \underset{\delta}{\operatorname{argmin}} \left( \sum_{i=\delta}^{M-1+\delta} |y[n+i] - y[n+N+i]| \right)$$

(3,28)

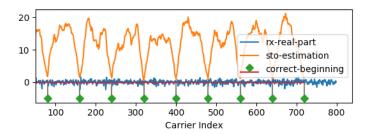

By applying this CP-based sliding windows method to the simulation signal distorted by the multipath channel model, the STO compensation result is shown in Fig. 3.20. The starting point can be well estimated, located in the valley of the "STO-estimation" axis.

Fig. 3.20 STO Estimation using CP minimum difference method

The other time-domain STO estimation method is achieved by adding a training symbol before a set of symbols. The training symbols, also known as the preamble [15], are special symbols that are known by the receiver. The beginning of the symbol can be estimated by a single sliding window that calculates the correlation. It differs from the former method because involves preambles, which will downgrade the maximum data throughput. However, it does not suffer from the effect of the multi-path channel and it only requires one sliding window. Apart from the time-domain methods, frequency-domain based STO estimation methods [16] are also available since the phase rotation is proportional to subcarrier frequency.

For CFO estimation, like the STO, methods can also be based on the time-domain or frequency-domain and make use of the CP or the preamble. For example, the time-domain method that uses the CP, assuming a good enough symbol synchronization, and the location of CP in the data symbol is already known, the CFO can be found from the phase angle of the product of CP and the corresponding part of the data symbol. Denoting  $N_{cp}$  as the length of CP, N the OFDM IFFT length and  $y^*$  is the complex conjugate of the received signal y, the CFO can be estimated as below.

$$\hat{\varepsilon} = \frac{1}{2\pi} \arg\left(\sum_{n=1}^{N_{cp}} y^*[n] y[n+N]\right)$$

(3,29)

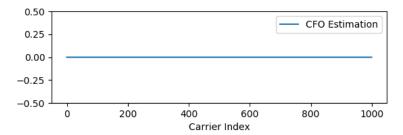

The argument operation results to the angle from  $[-\pi,\pi)$ , hence the estimated  $|\hat{\varepsilon}| < 0.5$ . It means that a big CFO ( $|\hat{\varepsilon}| \ge 0.5$ ) cannot be estimated by this CP-based technique. Other CFO estimation techniques based on the training symbol can be used to increase the CFO estimation range. For example, the frequency-domain approach by Moose in [17], first creates a training symbol and repeats it K times and then inserts it into the data symbols. This technique can increase the CFO estimation range by K times, but at the price of sacrificing the MSE. We tested the CP-based CFO estimation with the generated simulation data, as shown in Fig. 3.21, but since no deliberated frequency offset was added, the values were all close to 0.

Fig. 3.21 CP-based CFO estimation with simulation data

#### 3.2.9. Channel estimation

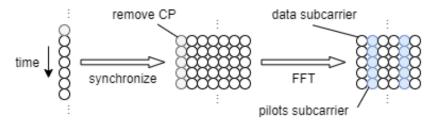

With the help of pilot subcarriers, the receiver can estimate the channel by comparing the received signal with the known pilot value. Comb-type pilots were used in the signal generation in order to be able to estimate the fast fading channel. As shown in Fig. 3.22, before the channel estimation, the receiver should have done synchronization, find out the start of the symbol and have removed the CP. After applying FFT to every OFDM symbol batch, according to the Comb-type arrangement, the pilots can be identified.

Fig. 3.22 Procedure for pilots extraction

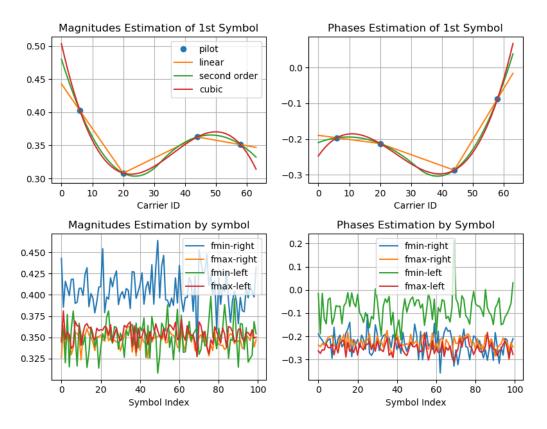

The effect of the channel can be estimated for each frequency component by performing interpolation to the pilot subcarriers extracted after the FFT operation at the receiver. Popular interpolation methods include linear interpolation, second-order polynomial interpolation, and cubic spline interpolation. High order interpolation introduces unnecessary complexity to the estimation, while linear interpolation is enough and thus more suitable since is less computational complex for this simulated scenario. In Fig. 3.23, the two plots on the top show the interpolated result of the first OFDM symbol using different interpolation orders; the two plots on the bottom are the magnitudes and phases of the first 100 symbols at the frequency of the four pilot carriers. The multipath channel simulation fairly changed the phases and amplitudes with the same scale, the pilot value should not change over time. However, the FIR filtering after the peak cancellation made the equalization scales different between samples.

Fig. 3.23 Channel estimation results

Let's denote the channel estimation made with an OFDM symbol  $\widehat{H}$ , while  $R_t$  is the received OFDM symbol after FFT, then, the equalized signal  $\widehat{Y}_t$  is obtained after a simple division [10]. In the real-time implementation, the OFDM symbol at moment (t) is calculated by the estimation at moment (t-1) to reduce the lagging.

$$\hat{Y}_{t}[k] = \frac{R_{t}[k]}{\hat{H}_{t-1}[k]} = \frac{X_{t}[k]H_{t}[k]}{\hat{H}_{t-1}[k]} \approx X_{t}[k]$$

(3,30)

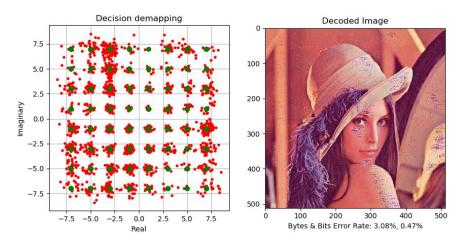

After the channel equalization, most constellation points were equalized and reallocated to the right position in the constellation. The recovered image in Fig. 3.24 is pretty accurate with only 3.08% of bytes error. By comparing it with Fig. 3.19 that showed 99.6% of bytes error, we can conclude that the equalization made a significant improvement. Inserting more pilot subcarriers or considering higher-order interpolation methods could improve the channel estimation and thus the equalization.

Fig. 3.24 Constellation and decoded image with pilot equalization

# 3.3. Techniques to improve power efficiency

As discussed in subchapter 3.1.3, the proposed communication system automatically changes the TX power according to the distance and the received signal strength. To adjust the output power, there are some options in the RF power amplifier circuit that are available.

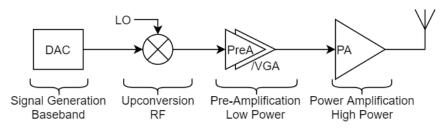

Before looking at the options, it is necessary to introduce and discuss the topic of RF power amplifiers to know the basic principles of amplification and some interesting properties. Fig. 3.25 shows a simplified block diagram for an amplification system for communications: from the analog-to-digital converter to the PA, passing through the upconversion to RF and pre-amplification. Thus, it requires at least four stages to generate the RF signals and send through the air with a certain output power. Since the PA cannot directly amplify the small signal to high power, one or more pre-amplifiers are required to increase the power step by step. Sometimes, the variable gain amplifier (VGA) might exist in the preamplify stage in order to give the flexibility to set the power. In this general scheme, it is assumed that both the pre-amplifier and the PA are ideally linear and thus the gain value can be added without considering any gain compression. For example, the DAC outputs a signal with 0 dBm mean power, the VGA together with the Pre-amplifier can add a gain between 10 to 20 dB, and the PA can add 13 dB of gain. The system can finally present a signal with 23 to 33 dBm of mean output power.

Fig. 3.25 General power amplifier scheme

Apart from using the VGA in the pre-amplification stage to control the output power, every stage can have its way to affect the output power. The DAC can control the power by giving small digital numbers, which is easy to handle and low-cost, however in a communication system, this will decrease the DAC dynamic range and thus degrade the quality of the generated signal due to the quantization noise. Another possibility is to tune the output power by changing the PA supply, by varying the drain voltage or the gate bias, which affects the Q-point of the transistor. By setting the position of the transistor Q-point, the amplifier will operate in different classes that have differences in efficiency and linearity.