Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier XXX

## A Program Logic for Reasoning about C11 Programs with Release-Sequences

MENGDA HE<sup>1</sup>, SHENGCHAO QIN<sup>1</sup> (Senior Member, IEEE & ACM), ZHIWU XU<sup>2</sup>

<sup>1</sup>School of Computing, Engineering and Digital Technologies, Teesside University <sup>2</sup>College of Computer Science and Software Engineering, Shenzhen University

Corresponding author: Shengchao Qin (e-mail: s.qin@tees.ac.uk).

#### ABSTRACT

With the popularity of weak/relaxed memory models widely used in modern hardware architectures, the C11 standard introduced a language level weak memory model, A.K.A the C11 memory model, that allows C/C++ programs to exploit the optimisation provided by the hardware platform in memory ordering and gain benefits in efficiency. On the other hand, with the weakened memory ordering allowed, more program behaviours are introduced, among which some are counterintuitive and make it even more challenging for programmers to understand or to formally reason about C11 multithread programs. To support the formal verification of the C11 weak memory programs, several program logics, e.g. RSL, GPS, FSL, and GPS+, have been developed during the last few years. However, due to the complexity of the weakened memory model, some intricate C11 features still cannot be handled in these logics. A notable example is the lack of supporting to the reasoning about a highly flexible C11 synchronisation mechanism, the release-sequence. Recently, the FSL++ logic proposed by Doko and Vafeiadis moves one step forward to address this problem, but FSL++ only considers the scenarios with atomic update operations in a release-sequence. In this article, we propose a new program logic, GPS++, that supports the reasoning about C11 programs with fully featured release-sequences. We also introduce fractional read permissions to GPS++, which are essential to the reasoning about a large number of real-world concurrent programs. GPS++ is a successor of our previous program logic GPS+, but it comes with much finer control over the resource transmission with the newly introduced restricted-shareable assertions and an enhanced protocol system. A more sophisticated resource model is devised to support the soundness proof of our new program logic. We also demonstrate GPS++ in action by verifying C11 programs with release-sequences that could not be handled by existing program logics.

• INDEX TERMS program logic, formal semantics, program verification, C11 weak memory model, releasesequence

#### I. INTRODUCTION

To discuss the behaviours of shared-memory concurrent programs, a memory model must be assumed, as it fundamentally defines how the threads communicate with each other. The traditional strong memory model, i.e., the sequentialconsistency (SC) [1] model, assumes a single global memory that is accessed by all threads in an interleaving manner while the instructions in each thread are executed strictly following their program orders. However, this model is abandoned by most of the modern hardware architectures, as it leaves very little room for optimisation. Modern hardware architectures embrace more relaxed memory models, which allow memory accessing operations to be reordered and threads to have their

VOLUME x, 202x

own observations about the memory states. For instance, the memory model used for the x86 architecture is the total-storeorder (TSO) model instead of the SC model, as with write buffers facilitated, the x86 architecture allows some store operations to be reordered after the following load operations as long as a total order for all store operations is preserved. Other platforms like ARM and PowerPC adopt even weaker memory models.

With the various levels of memory weakening allowed by different hardware platforms, a unified interface is essential to help programmers to compose programs that have best performance regardless the underlying platforms. Therefore, in the C11 standard [2], [3], a language-level weak memory

model, i.e., the C11 memory model, is introduced and has later been formalised by Batty et al. [4]. However, it remains challenging to understand or to reason about the counterintuitive behaviours introduced by this weakened memory model. Several program logics (RSL [5], GPS [6], [7] FSL [8], GPS+ [9], [10], and FSL++ [11]) focusing on C11 programs have been proposed during the last few years, but the reasoning about some highly intricate features of the C11 memory model is still not supported. A notable example is that the support to a highly flexible C11 synchronisation mechanism, i.e., the release-sequences, is usually left out. As shown in Table 1, there are four commonly used paradigms to establish C11 synchronisations. From the most straightforward way that only uses release write and acquire read pairs to the ones with fully featured release-sequences involved, the complexity increases along with its flexibility, as more program commands' interactions need to be taken under consideration. The formal reasoning about the most flexible paradigm facilitating with fully featured release-sequences is not supported until this work.

Beside the memory optimisations, another approach to maximising the benefits of multiprocessing is to reduce the fractions of tasks that could not be parallelised. For instance, instead of enforcing all the accesses to a shared resource to be mutually exclusive, a readers-writer-lock allows multiple readers (or a single writer) to exist at a time. The readers-writer-lock is widely adopted by real-world programs (e.g. the Linux kernel, pthread library, etc.). However, to formally verify a sophisticated algorithm like the readers-writer-lock, fractional permissions [12], [13] will be a necessary ingredient, which is not yet supported in the GPS family.

In this article, we propose GPS++, a program logic that supports the reasoning about C11 programs with fully featured release-sequences. To achieve this, our logic is facilitated with an enhanced per-location protocol system, a new type of assertions, i.e., the restricted shareable assertion, and a set of new reasoning rules to deal with C11 release-sequences related operations. We also introduce the support to fractional permissions, which enables us to use the proposed logic against sophisticated real-world concurrent algorithms such as the readers-writer-lock.

This article extends the earlier conference version [14] significantly with the following additional contributions: 1. The support for fractional read permissions in the new logic, that allows it to reason about real-world concurrent algorithms that otherwise would not be possible; 2. The proof in the new logic of the correctness of a non-trivial concurrent program, i.e. readers-write-lock (which cannot be handled by previous logics in the GPS family) that illustrates the applicability of GPS++; 3. A more sophisticated resource-map-based instrumented semantic model that help characterise the subtle new features in GPS++; 4. The formulation of the soundness of the GPS++ logic, together with proof sketches for lemmas and theorems.

In the rest of the article, we first introduce our core language that captures most essential C11 features and the C11 memory model in §II. Then we discuss this work's foundation, the GPS+ logic, in §III, before presenting our new logic in §IV. We demonstrate the power of our new program logic by using it to verify example programs including a variant of the readers-writer-lock in §V. After that, we present the formal foundation of GPS++ in Section VI and illustrate its soundness in §VII. Finally, related work is discussed in §VIII and the article is concluded in §IX.

#### **II. THE LANGUAGE AND THE MEMORY MODEL**

#### A. THE LANGUAGE

| Val     | v | ::= | $x \mid V$ where $V \in \mathbb{N}$                                   |

|---------|---|-----|-----------------------------------------------------------------------|

| Exp     | e | ::= | $v \mid v + v \mid v - v \mid v == v \mid v \operatorname{mod} v$     |

|         |   |     | $	ext{let} x = e 	ext{in} e \mid 	ext{repeat} e 	ext{ end} \mid$      |

|         |   |     | $	t if v 	t then e 	t else e \mid 	t fork e \mid 	t alloc(V)$         |

|         |   |     | $[v]_O \mid [v]_O := v \mid CAS_{O,O}(v, v, v) \mid \texttt{fence}_O$ |

| MO      | O | ::= | rel   acq   rlx   na                                                  |

| EvalCtx | K | ::= | $[] \mid \texttt{let} \ x = K \texttt{in} \ e$                        |

We use the expression-oriented language presented in Fig. 1 as our core language. It is used to capture the essential features of the C11 memory model. With the support to atomic read/write (load/store), fences, and compare-and-swap (CAS) our language can express C11 programs using various kinds of inter-thread synchronisation mechanisms, including the powerful release-sequence.

Our language has variable names (represented by metavariable x) and integer values (represented by metavariable V) as values (Val). The pointer arithmetic, letbinding, loop command repeat e, conditional statement if ... then ... else, thread forking fork e, memory allocation alloc(V), memory load (read)  $[v]_O$  and store (write)  $[v]_O := v$ , atomic update operation  $CAS_{O,O}(v, v, v)$ , and fence operations fence<sub>O</sub> are supported as our expressions (e). Specifically, in the loop command repeat e the loop body e will be repeatedly executed until a non-zero value is returned.

Note that a memory order O needs to be specified for some expressions indicating which degree of memory relaxation can be applied to the annotated operation. Following the C11 language, we require a memory location is either atomic or non-atomic and this cannot be changed once defined. For an atomic location  $v_1$ , the memory order O used in a load operation  $[v_1]_O$  can be acquire (acq) or relaxed (rlx); the memory order O in a store operation  $[v_1]_O := v$  can be either release (rel) or relaxed (rlx). Meanwhile, memory accesses to nonatomic locations can only be annotated as non-atomic (na). The compare-and-swap expression  $CAS_{O_1,O_2}(v_1, v_2, v_3)$  requires  $v_1$  to be the address of an atomic location and performs the following steps in a single atomic move: firstly, the value of  $v_1$  is loaded with the memory order  $O_1$  (which can be either acq or rlx), then the value is used to "compare" with the expected value  $v_2$ ; if they are the same, the value  $v_3$ is stored to location  $v_1$  with the memory order  $O_2$  (which can be rel or rlx) (the "swapping") and a numerical value

TABLE 1: Program Logics' Support to C11 Synchronisations

| Synchronisation Paradigms                       | RSL          | GPS          | FSL          | GPS+         | FSL++        | GPS++        |

|-------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|

| With Release Store & Acquire Load Pairs         | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| With Fences                                     |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| With Release-sequences with only Atomic Updates |              |              |              |              | $\checkmark$ | $\checkmark$ |

| With Fully Featured Release-sequences           |              |              |              |              |              | $\checkmark$ |

1 is returned indicating its success; otherwise 0 is returned indicating the failure of the compare-and-swap process.

#### B. THE GRAPH SEMANTICS

The C11 memory model resides at language-level aiming at abstracting away the differences of underlying hardware memory models. Therefore, it is not straightforward to express it in an operational manner. The axiomatic approach is often used instead to formalise the C11 memory model, where execution graphs are used to represent candidate executions (with the program actions/events as vertices and their relations represented by the edges) and a set of axioms decide if an execution is legal or not. This is the approach adopted by Batty et al. [4] to give the first formalisation of the C11 memory model. The memory models used in the C11 program logics [5], [6], [8]–[11] are defined in a similar manner but with certain simplifications, e.g., only accepting synchronisations created using a simple way without releasesequences involved. This work follows the graph based axiomatic semantics, with extra information added for threads (highlighted in Fig. 2), and supports synchronisations with fully featured release-sequences.

As shown in Fig. 2, the event graph  $\mathcal{G}(A, T, sb, mo, rf)$  concerns a set of events, and records their action type information in A (the action types will be further discussed shortly), their thread identities in T (i.e. to which threads they belong), as well as their relations in sb, mo, and rf. The sequenced-before relation (sb) represents the non-transitive program order. All store operations accessing a same location form a strict-total order, which we record in the modification-order (mo). When a load operation reads from a store operation, this relation is tracked in the reads-from map (rf). We formalise the thread pool as  $\mathcal{T}$  which tracks each numerically indexed thread's last event and the expressions to be executed.

| Action                                                              | $\alpha$      | ::=   | $ \mathbb{S} \mid \mathbb{A}(\ell\ell') \mid \mathbb{W}(\ell, V, O) \mid \mathbb{R}(\ell, V, O) \mid \\ \mathbb{U}(\ell, V, V, O, O) \mid \mathbb{F}(O) $ |  |  |

|---------------------------------------------------------------------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EventName                                                           | a             |       | (from an infinite set)                                                                                                                                    |  |  |

| ActMap                                                              | A             | $\in$ | $EventName \stackrel{fin}{\rightharpoonup} Action$                                                                                                        |  |  |

| ThreadID                                                            | T             | $\in$ | $EventName \stackrel{fin}{\rightharpoonup} \mathbb{N}$                                                                                                    |  |  |

|                                                                     |               |       | (A, T, sb, mo, rf) where                                                                                                                                  |  |  |

| $sb,mo\subseteqdom(A)\timesdom(A),rf\indom(A)\rightharpoonupdom(A)$ |               |       |                                                                                                                                                           |  |  |

| ThreadMap                                                           | $\mathcal{T}$ | $\in$ | $\mathbb{N} \stackrel{fin}{\rightharpoonup} (EventName \times Exp)$                                                                                       |  |  |

| FIGURE 2: Syntax of event graph                                     |               |       |                                                                                                                                                           |  |  |

As shown in Fig. 3 and Fig. 4, we adopt a two-layer semantics, namely, event-step and machine-step, following GPS and GPS+. An event-step  $(e \xrightarrow{\alpha} e')$  is the execution of e, resulting in a return value or a remainder expression (e') and an action ( $\alpha$ ) to be added to the execution graph in the machinesteps. The executions of arithmetic, let-banding, repeat, and conditional expressions returns different values or remainder expressions but they only generates skip actions (S) as they do not involve memory accesses. The allocation expression alloc(n) generates an allocation action  $\mathbb{A}(\ell .. \ell + n - 1)$ , which indicates n fresh memory location ranging from  $\ell$  to  $\ell + n - 1$  are allocated and  $\ell$  is returned. Store and fence expresses generate corresponding write  $(\mathbb{W})$  and fence  $(\mathbb{F})$ actions with specified memory orders; and we let them always return 0 as they should not be used to change the program control flow. Note that the event-step rule for read action  $\mathbb{R}$  only specifies that it should return some numerical value V. The actual value can be read is constrained by the memory model axioms (consistentC11) in the machinesteps (which will be discussed shortly in this section) with the global execution taken under consideration. There are two rules for CAS expressions to correspondingly capture the successful and failure cases. In the case of success, an update action  $\mathbb{U}(\ell, V_o, V_n, O_r, O_w)$  is generated, where the current value  $V_o$  stored at location  $\ell$  is required to be the same as specified in the expression; otherwise, the CAS should be considered as failed and is treated as an atomic read action which reads some value other than  $V_{\alpha}$ .

We use the machine configuration  $\langle \mathcal{T}; \mathcal{G} \rangle$  to represent the execution states, where the thread pool  $\mathcal{T}$  contains the expressions to be executed in each thread and the execution graph  $\mathcal{G}$  is a record of the execution history. Machine-step rules are used to update the machine configurations. The first rule states that an arbitrary thread from  $\mathcal{T}$  can take a move  $(e \xrightarrow{\alpha} e')$  and generate a new machine configuration  $(\langle \mathcal{T}'; \mathcal{G}' \rangle)$  based on the current one  $(\langle \mathcal{T}; \mathcal{G} \rangle)$  with the new event (a') and the corresponding relations added to the event graph given that the C11 memory model axioms are preserved in the extended graph (consistent  $C11(\mathcal{G}')$ ). More specifically, assume the thread i in the thread pool  $\mathcal{T}$  is chosen to execute, its last event is a and the expression to be executed is e. Then e is reduced to e' following the corresponding event-step semantics rule, yielding a new action  $\alpha$ with a new event name a'. We update *i* in the thread pool with this information (a', e'), then add the newly generated event to the event graph as the following, yielding a new graph  $\mathcal{G}'$ . Firstly, the mapping  $a' \mapsto \alpha$  and  $a' \mapsto i$  are added to the action map ( $\mathcal{G}'.A$ ) and the thread map ( $\mathcal{G}'.T$ ), respectively. This information will be crucial for reasoning about programs with C11 release-sequences, as we will need to know if different writes are from a same thread or not. Secondly, we know that a' comes after a, so we record it in the sequenced-

FIGURE 3: Event-steps semantic rules:  $e \xrightarrow{\alpha} e'$

$$\begin{array}{ccc} e \xrightarrow{\alpha} e' & \texttt{consistentC11}(\mathcal{G}') & \mathcal{G}'.A = \mathcal{G}.A \uplus [a' \mapsto \alpha] & \mathcal{G}'.T = \mathcal{G}.T \uplus [a' \mapsto i] \\ & \mathcal{G}'.\mathsf{sb} = \mathcal{G}.\mathsf{sb} \uplus (a,a') & \mathcal{G}'.\mathsf{mo} \supseteq \mathcal{G}.\mathsf{mo} & \mathcal{G}'.\mathsf{rf} \in \{\mathcal{G}.\mathsf{rf}, \mathcal{G}.\mathsf{rf} \uplus [a' \mapsto b]\} \\ & & \langle \mathcal{T} \uplus [i \mapsto (a,e)]; \mathcal{G} \rangle \longrightarrow \langle \mathcal{T} \uplus [i \mapsto (a',e')]; \mathcal{G}' \rangle \end{array}$$

$\langle \mathcal{T} \uplus [i \mapsto (a, K[\texttt{fork}\,(e)])]; \mathcal{G} \rangle \longrightarrow \langle \mathcal{T} \uplus [i \mapsto (a, K[0]) \uplus [j \mapsto (a, e)]; \mathcal{G} \rangle$

FIGURE 4: Machine-step semantics:  $\langle \mathcal{T}; \mathcal{G} \rangle \longrightarrow \langle \mathcal{T}'; \mathcal{G}' \rangle$

before relation ( $\mathcal{G}'$ .sb). Finally, the modification-order only gets updated if a' is a write ( $\mathbb{W}$ ) or a success update action ( $\mathbb{U}$ ), so we have  $\mathcal{G}'.mo \supseteq \mathcal{G}.mo$ . Similarly, the read-from relation only gets updated if a' is a read ( $\mathbb{R}$ ) or an update action ( $\mathbb{U}$ ) which reads from a write/update action b. The exact way these two relations to be updated is restricted by the C11 memory model axioms consistentC11 that to be presented in the next subsection.

The second machine-step rule indicates that the fork e command creates a new thread (i.e. j) that will be added to the thread pool. The expression e is waiting to be executed in the new thread while the parent thread (i) has whatever left in the evaluation context K[0].

A thread terminates if its expression is reduced to be a pure value and the program terminates when all its threads terminate.

#### C. THE MEMORY MODEL

A memory model defines how different CPU cores can access a shared memory, and thus controls how multithread programs should behave. As a language-level memory model that must be sufficiently generalised, the C11 memory model regulates the program behaviours by using a group of axioms based on the event graph. We have discussed the event graph; now we first introduce several derived relations before we can formally introduce the C11 memory model axioms. 1) Happens-before Relation

The happens-before relation is the cornerstone of the causality in C11 programs. That is, for two events a and b, unless we can establish that a happens before b  $(a \xrightarrow{hb} b)$ , there is no guarantee that a's effect will be observed by b. The happens-before relation is derived from the sequenced-before and the synchronised-with relations (to be discussed shortly in §II-C2), i.e.,  $hb \triangleq (sb \cup sw)^+$ . Intuitively, the happensbefore relation preserves the program order for events within the same thread; however, for the events from different threads can by ordered in hb only if their threads are synchronised at appropriate locations.

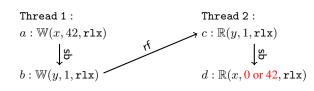

This idea is demonstrated in Fig. 5 with an unsuccessful message passing program. In this example, we assume both x and y are initialised as 0. In the first thread, the flag y is changed to 1 (event b) after the message x is set to be 42 (event a); the second thread first reads y to be 1 (event c) then reads x (event d). Though a chain of relations can be established as  $a \stackrel{\text{sb}}{\rightarrow} b \stackrel{\text{rf}}{\rightarrow} c \stackrel{\text{sb}}{\rightarrow} d$ , the stale value 0 can still be read by d as the read-from relation between b and c is not strong enough to form a synchronisation, thus the happensbefore relation  $a \stackrel{\text{hb}}{\rightarrow} d$  could not be derived and a's effect is not guaranteed to be seen by d.

FIGURE 5: A failed message passing example

#### 2) Release-sequence and Synchronisation

As a weak memory model, the C11 memory model allows threads to have different observations about the memory<sup>1</sup>. But when necessary, one thread's observation can be passed to another if they are synchronised. To form a synchronisation and share its observation, the sharer's thread must first perform a release action. Intuitively, the release action would label its up-to-date memory observation as ready to be shared. Then a sequence of store operations, i.e. a releasesequence, work like messengers notifying their readers that some information can be acquired. However, the acquisition is only successful after an acquire action is performed in the reader's thread. In this way, the acquire action is synchronised with the release action and is obliged to acknowledge the memory modifications happened before the release action.

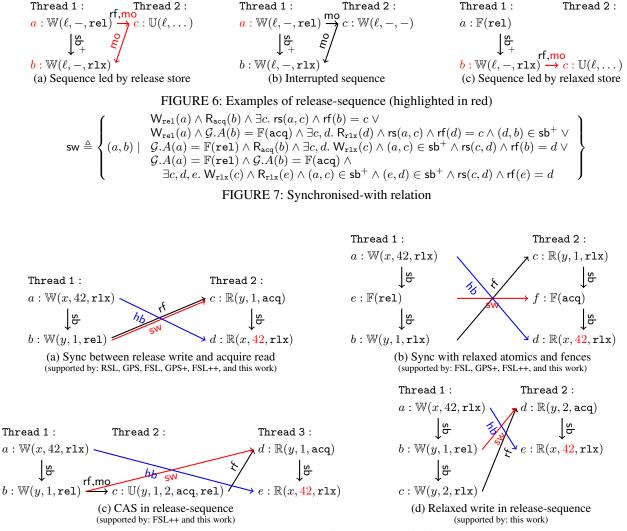

The release-sequence plays the crucial role in this process. It is led by an action with the release memory order, i.e., the release head, which can either be a release fence or a release store, and is followed by the longest sub-sequence of store operations from the modification order (mo) where these store operations are either in the same thread as the release head or atomic update operations (i.e.,  $\mathbb{U}$ ).

As the example shown in Fig. 6a the release write event a is the release head; and the release-sequence also contains b and c as they follow a in the mo order and is either in a's thread (b) or is an atomic update (c). Another thread can acquire a's observation by reading from any event from this sequence. Fig. 6b shows that a release-sequence can be interrupted if a non-update store operation (c in this case) from a different thread is positioned in the chain of mo order. In the case shown in Fig. 6b, the release-sequence only contains the head a. As shown in Fig. 6c, a relaxed write can lead a hypothetical release head. If an operation acquires from this sequence, it is synchronised with a release fence prior to the hypothetical release head if there is any.

To formally define the synchronised-with relation, we first define a predicate (along with some shorthand definitions) that indicates if an action b is qualified to be a member of the release-sequence led by action a:

**IEEE**Access

$$rs\_element(a, b) \triangleq sameThread^{\mathcal{G}}(a, b) \lor isCAS^{\mathcal{G}}(b)$$

$$sameThread^{\mathcal{G}}(a, b) \triangleq \mathcal{G}.T(a) = \mathcal{G}.T(b)$$

$$isCAS^{\mathcal{G}}(b) \triangleq \mathcal{G}.A(b) = \mathbb{U}(-, -, -, -, -)$$

$$W_{O}(a) \triangleq \mathcal{G}.A(a) = \mathbb{W}(-, -, O) \lor \mathbb{U}(-, -, -, -, O)$$

$$R_{O}(a) \triangleq \mathcal{G}.A(a) = \mathbb{R}(-, -, O) \lor \mathbb{U}(-, -, -, -, -, -)$$

For a store action a, we say that event b is in a's releasesequence,  $a \stackrel{rs}{\rightarrow} b$  or rs(a, b), if and only if:

$$\mathsf{W}_{O}(a) \land \begin{pmatrix} a = b \lor \mathsf{rs\_element}(a, b) \land a \xrightarrow{\mathsf{mo}} b \land \\ \forall c. \ a \xrightarrow{\mathsf{mo}} c \xrightarrow{\mathsf{mo}} b \Rightarrow \mathsf{rs\_element}(a, c) \end{pmatrix}$$

Then we can formally define the synchronised-with relation as that shown in Fig. 7:

#### D. DEMONSTRATING C11 SYNCHRONISATIONS

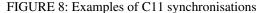

We have introduced the highly flexible release-sequence based C11 synchronisation mechanism. In Fig. 8, we demonstrate how C11 synchronisations can be formed in different manners by restoring the message passing protocol discussed in Fig. 5 in various ways. Recall that, as summarised in Table 1, existing C11 program logics usually support simplified versions of the C11 synchronisation mechanism, due to its complicity, with limited scenarios allowed to from synchronisations. These demonstrations are also used to illustrate which types of C11 synchronisations can be supported by existing C11 program logics.

The first C11 program logics, RSL and GPS, can only be used to reason about C11 programs with synchronisations formed between release write and acquire read pairs as that is shown in Fig. 8a. With C11 fences supported, FSL and GPS+ can also reason about programs like that is shown in Fig. 8b. Still, they do not accept release-sequences with more than one element. FSL++ overcomes this limitation, but expect the release head, it only accepts atomic update operations to be in a release-sequence (Fig. 8c). To the best of our knowledge, only this work supports the reasoning about C11 programs with synchronisations based on fully-featured release-sequences, including the scenario shown in Fig. 8d.

#### E. THE AXIOMATIC MODEL

With the preparations that have been made about synchronisations, happens-before relations and etc., in this subsection, we present the axiomatic definitions for the C11 memory model in Fig. 9 following a similar approach used by [4]. Intuitively, the axioms are regulations that rule out illegal executions, e.g., "no one can read from an event that happens after itself" or "an update action cannot be interrupted", and etc. These axiomatic rules also leave us enough room to ensure the aforementioned principle: no guarantee of observation without happens-before relations.

Specifically, ConsistentMO1 states that mo is a binary relation over writing actions. ConsistentMO2 requires all writing actions in mo to follow a strict total order. ConsistentRF1

<sup>&</sup>lt;sup>1</sup>For instance, in the example shown in Fig. 5, thread 2 can observe a state where  $x = 0 \land y = 1$ , which is infeasible from the perspective of thread 1.

indicates there always is at least one writing action before a reading on the same location, that is, all locations are initialised before reading. ConsistentRF2 says that a reading action cannot read from a writing that happens after itself. For a non-atomic reading action, ConsistentRFNA requires it must read from a writing action that happens before it. Coherence puts restrictions on happens-before relations and the modification orders, e.g. a reading actions should not read older value than its happens-before ancestors. AtomicCAS enforces no interruption could happen to an atomic update action. ConsistentAlloc states the sets of locations allocated by two allocation actions will not intersect, that is, no location will be allocated more than once. Acyclic is introduced to rule out the thin-air-read problem following [6], [9].

Note that while atomic locations are meant to be accessed concurrently, concurrent accesses (accesses that are not ordered in hb) to non-atomic locations with at least one write action lead to a hazardous situation called data-race, in which the program behaviour is undefined. The memory error is another hazardous situation, which involves accessing a location before it is allocated. Definitions for these two hazardous situations are needed to complete our semantical model as we need them to rule out executions with undefined results.

$$\begin{split} \mathsf{dataRace}(\mathcal{G}) &\triangleq \exists \ell. \exists a, b \in \mathsf{dom}(\mathcal{G}.A). \\ & \left( \begin{array}{c} \mathcal{G}.A(a) = \mathbb{W}(\ell, -, \mathtt{na}) \land \mathcal{G}.A(b) = \mathbb{W}(\ell, -, \mathtt{na}) \lor \\ \mathcal{G}.A(a) = \mathbb{W}(\ell, -, \mathtt{na}) \land \mathcal{G}.A(b) = \mathbb{R}(\ell, -, \mathtt{na}) \lor \\ \mathcal{G}.A(a) = \mathbb{R}(\ell, -, \mathtt{na}) \land \mathcal{G}.A(b) = \mathbb{W}(\ell, -, \mathtt{na}) \end{matrix} \right) \\ & \land \neg ((a, b) \in \mathtt{hb} \lor (b, a) \in \mathtt{hb}) \end{split}$$

$$\begin{split} \mathsf{memErr}(\mathcal{G}) &\triangleq \exists l.\exists b \in \mathsf{dom}(\mathcal{G}.A). \ (\mathcal{G}.A(b) = \mathbb{W}(\ell, -, -) \\ &\vee \mathcal{G}.A(b) = \mathbb{R}(\ell, -, -) \lor \mathcal{G}.A(b) = \mathbb{U}(\ell, -, -, -, -)) \\ &\wedge \nexists a \in \mathsf{dom}(\mathcal{G}.A).A(a) = \mathbb{A}(\vec{\ell}) \land \ell \in \vec{\ell} \land (a, b) \in \mathsf{hb} \end{split}$$

#### **III. RECAP OF GPS+**

Verifying concurrent programs is difficult. To reason about C11 concurrent programs with weak memory behaviours is even harder. To do this, GPS-like logics amalgamate three techniques from state-of-the-art concurrent program logics

## IEEE Access

$consistentC11((A, T, sb, mo, rf)) \triangleq$  $\forall a, b. \ \mathsf{mo}(a, b) \Rightarrow \exists \ell. \ \mathsf{writes}(a, \ell, -), \ \mathsf{writes}(b, \ell, -)$ (ConsistentMO1)  $\land \forall \ell.$ strictTotalOrder({ $a \mid$ writes( $a, \ell, -$ )}, mo) (ConsistentMO2)  $\land \forall b. \mathsf{rf}(b) \neq \bot \Leftrightarrow \exists \ell, a. \mathsf{writes}(a, \ell, -) \land \mathsf{reads}(b, \ell, -) \land \mathsf{hb}(a, b)$ (ConsistentRF1)  $\land \forall a, b. \mathsf{rf}(b) = a \Rightarrow \exists \ell, V. \mathsf{writes}(a, \ell, V) \land \mathsf{reads}(b, \ell, V) \land \neg \mathsf{hb}(b, a)$ (ConsistentRF2)  $\land \forall a, b. \mathsf{rf}(b) = a \land (\mathsf{isNonatomic}(a) \lor \mathsf{isNonatomic}(b)) \Rightarrow \mathsf{hb}(a, b)$ (ConsistentRFNA)  $\land \ \forall a, b. \ \mathsf{hb}(a, b) \Rightarrow a \neq b \land \neg \mathsf{mo}(\mathsf{rf}(b), \mathsf{rf}(a)) \land \neg \mathsf{mo}(\mathsf{rf}(b), a) \land \neg \mathsf{mo}(b, \mathsf{rf}(a)) \land \neg \mathsf{mo}(b, a)$ (Coherence)  $\land \forall a, c. isUpd(c) \land rf(c) = a \Rightarrow mo(a, c) \land \nexists b. mo(a, b) \land mo(b, c)$ (AtomicCAS)  $\wedge \ \forall a \neq b, \vec{\ell}, \vec{\ell'}. \ A(a) = \mathbb{A}(\vec{\ell}) \land A(b) = \mathbb{A}(\vec{\ell'}) \Rightarrow \vec{\ell} \cap \vec{\ell'} = \emptyset$ (ConsistentAlloc)  $\land$  acyclic(hb  $\cup$  rf) (Acyclic) where strictTotalOrder $(S, R) \triangleq (\not\exists a. R(a, a)) \land (\forall a, b, c. R(a, b) \land R(b, c) \Rightarrow R(a, c))$  $\land \ (\forall a, b \in S. \ a \neq b \Rightarrow R(a, b) \lor R(b, a))$  $\operatorname{acyclic}(R) \triangleq \exists x. R^+(x, x)$  $\operatorname{reads}(a, \ell, V) \triangleq A(a) \in \mathbb{R}(\ell, V, -), \mathbb{U}(\ell, V, -)$ writes $(a, \ell, V) \triangleq A(a) \in \mathbb{W}(\ell, V, -), \mathbb{U}(\ell, -, V)$

FIGURE 9: The C11 axioms

(e.g. [15]–[28]), namely ghost states, protocols and separation logic. Our proposed program logic, GPS++, follows the line of GPS works. In this section, we lay the foundation for the discussion of our program logic by briefly introducing its closest predecessor GPS+.

#### A. PROTOCOLS FOR ATOMIC LOCATIONS

As illustrated in previous sections, in C11 concurrent programs threads communicate with each other by writing and reading atomic locations. As updates may happen in other threads, it is difficult to determine the precise value of an atomic location. Therefore, GPS/GPS+ employs the concept of per-location protocols and each atomic location has its own protocol depicting how its states can evolve along with the program execution. The possible states for an atomic location are partially ordered, and the state assertion is used to describe the lower-bound state an atomic location can be in. That is, assuming an atomic location  $\ell$ 's protocol is  $\tau$ , the state assertion  $\overline{\ell : s | \tau |}$  says that  $\ell$  is at least at state *s*.

Atomic locations can be concurrently accessed by different threads, therefore their state assertions should be able to be duplicated and shared between different threads. These assertions that do not require exclusive ownership are called knowledge in GPS logics. A knowledge assertion is decorated with the notation  $\Box$  and the following rules applied:

$$\fbox{\ell:s|\tau} \Rightarrow \Box \fbox{\ell:s|\tau} \quad \Box P \Leftrightarrow \Box P * \Box P \quad \Box P \Rightarrow P$$

The first rule states that a state assertion is knowledge. The second rule says that copies can be made out of a knowledge assertion. When necessary a knowledge assertion can also be transformed back to its normal form using the third rule.

To complete the protocol definition  $\tau$  for its atomic location  $\ell$ , a partial order  $\sqsubseteq_{\tau}$  must be provided to depict all  $\ell$ 's possible state transitions. That is, assuming  $\ell$  is currently in state *s* and a write command moves it to state *s'*, this is valid if and only if  $s \sqsubseteq_{\tau} s'$  is defined in the protocol. In addition, state interpretations need to be specified for all states. A state interpretation  $\tau(s, z)$  describes the conditions that must be satisfied for a write command to be permitted to write value *z* to  $\ell$  and transfer  $\ell$  to state *s*. On the other hand, when a reader reads  $\ell$  at state *s*, it knows some conditions have been established in the writer's thread. Therefore, they can reach agreement about these facts, i.e., they are synchronised. The following rules formally capture this process.

$$\frac{[\text{GPS+-RELEASE-STORE}]}{P \Rightarrow \tau(s'', v) * Q} \quad \forall s' \sqsupseteq_{\tau} s. \tau(s', -) * P \Rightarrow s'' \sqsupseteq_{\tau} s'}{\{[\ell:s]\tau] * P\} [\ell]_{\text{rel}} := v \{[\ell:s'']\tau] * Q\}}$$

The [<u>GPS+-RELEASE-STORE</u>] rule states that to move  $\ell$  to the target state s'', the state interpretation  $\tau(s'', v)$  must be derivable from the resource P currently possessed in its precondition (the first premise). Note that the *ghost move*  $\Rightarrow$ used to imply the state interpretation refers to a transition that only affects auxiliary states leaving physical states unchanged. Note also that due to the possible moves from the environment, the actual state of  $\ell$  before the writing may be different from the lower-bond state s in the triple's precondition. Therefore, the second premise is introduced requiring that the target state s'' is reachable from any possible state s'that  $\ell$  might be currently in.

$$\begin{array}{c} [ \underline{\text{GPS+-ACQUIRE-LOAD}} ] \\ \forall s' \sqsupseteq_{\tau} s. \forall z. \tau(s', z) * P \Rightarrow \Box Q \\ \hline \{ \boxed{\ell:s|\tau} * P \} \ [\ell]_{\mathtt{acq}} \ \{ z. \exists s'. \boxed{\ell:s'|\tau} * P * \Box Q \} \end{array}$$

The [GPS+-ACQUIRE-LOAD] states that some knowledge  $\Box Q$  can be added to an acquire read's postcondition if

the knowledge can be derived from the candidate states' interpretations. Note that only knowledge assertions can be retrieved, as the read operations from different threads may observe a same state and try to retrieve the same information. If the information to be retrieved is not duplicable, conflicts will raise. The assertion P included in this rule enables *rely-guarantee* style of reasoning and reduces the possible states that can be read [6].

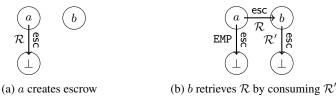

#### B. ESCROWS FOR NON-ATOMIC LOCATIONS

The [<u>GPS+-ACQUIRE-LOAD</u>] rule only retrieve knowledge assertions from state interpretations. However, the ownership of some exclusive resource is also often needed to be transmitted across threads. This can be done by using *escrows* in GPS/GPS+. Intuitively, an escrow  $\sigma : P \rightsquigarrow Q$  is a safe protecting Q with a non-duplicable resource P as the key. Following ghost move rules are used to put some resource (Q) under escrow and retrieve it:

$$\frac{\sigma: P \rightsquigarrow Q}{Q \Rrightarrow [\sigma]} \qquad \frac{\sigma: P \rightsquigarrow Q}{P \land [\sigma] \Rrightarrow Q}$$

An escrow  $[\sigma]$  is no longer ownership-dependent. It can be transformed into knowledge following the rule:  $[\sigma] \Leftrightarrow \Box[\sigma]$ . As shown in the second rule, the "key" P will be consumed once it is used to open the safe and retrieve the resource Q. Therefore P is preferred to be a *ghost assertion* instead some assertions relating to physical resources. A ghost assertion in the form  $[\gamma:t][\mu]$  indicates that  $\gamma$  is a ghost variable, and its value is a ghost permission t drawn from some *partial commutative monoid* (PCM) type  $\mu$ . With a fresh identity, a new ghost value t can be introduced out of thin air: true  $\Rightarrow \exists \gamma: [\gamma:t][\mu]$ .

#### C. WORKING WITH FENCES

As shown in Fig. 8b, synchronisations can also be established by using relaxed write and read operations but only with the help from C11 fences. In GPS+, this process is interpreted as that a relaxed write can only share the resource made *shareable* (denoted as  $\langle P \rangle$ ) by a prior release fence. On the other hand, when some resource is retrieved by a relaxed read, it cannot be used instantly. Instead, it is marked as *waiting-to-be-acquired*  $\boxtimes P$  and an acquire fence is needed to transform it back to its normal form.

The fence related rules are adopted by our new program logic. Detailed discussions will be provided in the next section to illustrate how we make them compatible with other more complicated features.

#### IV. REASONING ABOUT C11 RELEASE-SEQUENCES AND FRACTIONAL PERMISSIONS

The use of release-sequences provides C11 programs great flexibility to choose the best way to synchronise their threads. However, as discussed in previous sections no existing program logic supports the formal verification about the use of fully featured release-sequences due to its complexity. Also, there is no work in GPS family that supports fractional permissions. In this section, we introduce our new reasoning framework, GPS++, that support the aforementioned features with the aid from several novel techniques.

#### A. A NEW TYPE OF ASSERTION AND THE ENHANCED PROTOCOL SYSTEM

The key to reason about the C11 synchronisation process is to deal with the relaxed write operations involved. As that is discussed in §II-C2, unlike a release write, a relaxed write cannot form a synchronisation by itself. That is, no resource can be shared by a relaxed write to its readers unless (1) there is a release fence prior to it; or (2) it belongs to a release write's release-sequence. To reason about the behaviours of a relaxed write in the C11 synchronisation, its context must be taken under consideration. The first scenario is relatively easier, as we can adopt the *shareable* assertion introduced by GPS+ to indicate if there is a prior release fence that makes some resource available for the relaxed write operation to share. The second scenario is more complicated, as we need to know if there is a prior release write to the same memory location and if so, whether or not the release-sequence led by that release write is still valid at the point where the relaxed write takes place.

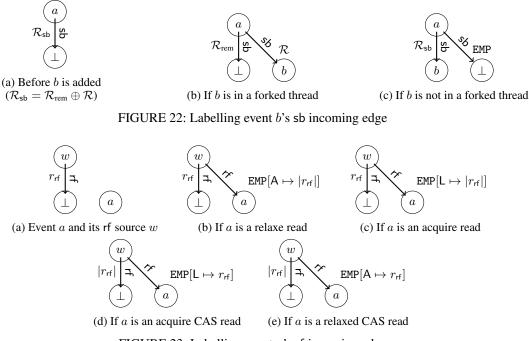

To tackle this problem, a naive solution is to introduce location-based restricted shareable assertions. That is, a release write operation on location  $\ell$  may create an assertion  $\langle P \rangle_{\ell}$ , which indicates P is shareable by following relaxed writes operation on  $\ell$  who are assumed to be the members of its release-sequence. However, as discussed in §II-C2 a release-sequence could be interrupted by non-update writes from other threads and this definition is not sufficient to be used to detect these potential interruptions. Therefore, we introduce state-based restricted shareable assertions (which we call restricted-shareable assertions for short) instead. Specifically, a release write that changes location  $\ell$  to state s may make some resource P shareable,  $\langle P \rangle_s$ , for the members of its release-sequence. To check if a following relaxed write belongs to the release-sequence and can use the restrictedshareable resource  $\langle P \rangle_s$ , we first check (1) whether they are operations on the same location; (2) whether they are in the same thread; and (3) whether the sequence is free from interruptions. The check for condition (1) can be done by simply examining whether the two writes follow the same protocol. To enable the checks for condition (2) and (3), we extend the state interpretation  $\tau(s, z)$  used in GPS+ to the form like  $\tau(s, z, tid, upd)$ , where tid indicates in which threads the target location can be transformed to the state s, and upd is 1 if the state s can only be reached by atomic update operations or 0 otherwise. With these preparations, we derive the following predicates:

$$\begin{split} \mathsf{sameThread}(s,s') &\triangleq \forall t,t',v,v',c,c'. \ (\tau(s,v,t,c) \not\Rightarrow \mathtt{false} \land \\ \tau(s',v',t',c') \not\Rightarrow \mathtt{false}) \Rightarrow t = t' \\ \mathsf{isCAS}(s) &\triangleq \forall v,t,u. \ (\tau(s,v,t,u) \not\Rightarrow \mathtt{false}) \Rightarrow u = 1 \end{split}$$

With these definitions, the thread and interruption checks can be formalised as:

$$\forall s''. s' \sqsupseteq_{\tau} s'' \sqsupseteq_{\tau} s \Rightarrow \mathsf{sameThread}(s'', s) \lor \mathsf{isCAS}(s'').$$

where s is the state established by the release head and s' is the target state of the relaxed write being checked. The following properties can be derived for our new restricted-shareable assertions based on our semantical model:

$$[\underline{\text{SEPARATION-R}}] \qquad [\underline{\text{UNSHARE-R}}] \\ \langle P_1 * P_2 \rangle_s \Leftrightarrow \langle P_1 \rangle_s * \langle P_2 \rangle_s \qquad \langle P \rangle_s \Rrightarrow P$$

The [SEPARATION-R] rule indicates that a restricted-shareable assertion can be split as while as several restricted-shareable assertions can be merged if they are restricted to the same state. The [UNSHARE-R] rule states that a restricted-shareable assertion can be transformed back into its normal form via a ghost move.

The new restricted-shareable assertion, the enhanced protocol system, and their properties are semantically supported by our upgraded resource model, which will be presented in later sections.

#### B. REASONING ABOUT C11 RELEASE-SEQUENCES

With our new restricted-shareable assertions and the enhanced protocol system introduced, new reasoning rule can be devised to handle the C11 programs with fully featured release-sequences. In this section, we first introduce the essential rules most related to C11 synchronisations in Fig. 10. Rules to deal with fractional permissions are presented in §IV-C, while other rules are discussed in §IV-D.

Unlike a release write in GPS+ which only needs to concern about what resource it can share to its readers, a release write in this work can also initiate a release-sequence, that is, it can make some resource shareable by the qualified relaxed writes followed. This idea is formalised in our [RELEASE-STORE] rule as that part of the resource P currently held in the release write's precondition can be transformed into a restricted shareable assertion  $\langle Q_1 \rangle_{s''}$ .

We require the P used in the rule must be *normal*, i.e., it can not contain any special forms of assertions (e.g., shareable assertions or waiting-to-be-acquired assertions). This ensures that  $Q_1$  is also free from special assertions and we do not create the problematic nesting of special assertions by putting  $Q_1$  into  $\langle \ldots \rangle_{s''}$ . The formal definition for the normality check is normal $(P) \triangleq P \Rightarrow \texttt{false} \lor \langle P \rangle \neq \texttt{false}$ . This is not the only occasion where the normality check is used. Allowing special assertions to be transmitted across threads also raises problems, therefore we require state assertions to be *normal* as well to prevent special assertions from being included.

The [<u>RELAXED-STORE-2</u>] rule illustrate how a release write works in a release write's release-sequence. With the

restricted-shareable assertion  $\langle P_2 \rangle_{s_o}$  created by a release write and passed down to the relaxed write, the relaxed write knows it may be in a release-sequence created at state  $s_o$ . The validity of the release-sequence needs to be checked using the second premise (recall §IV-A) then  $P_2$  can be used to imply the target state interpretation (the first premise).

Our reasoning framework is compatible with the rules developed in GPS+ for reasoning about the synchronisation initiated by a relaxed write with the help from a prior release fence. Therefore we inherit these rules as our [RELAXED-STORE-1] and [RELEASE-FENCE] rules. They state that a release fence can turn some resource into a (unrestricted) shareable resource and then being used by *any* relaxed write that follows. Intuitively, these tow rules are sound for C11 release-based synchronisation mechanism because every relaxed write after a release fence is a (hypothetical) release head and is allowed to share the observations established at point where the release fence took place (recall §II-C2).

On the other side, if the reader is an acquire read, the [<u>ACQUIRE-LOAD</u>] rule applies. It states that when observing the location l at a certain state s', some knowledge  $\Box Q$  can be learnt from the state interpretation. Similarly, as shown in the [<u>RELAXED-LOAD</u>] rule, a relaxed read can also retrieve some knowledge from the state interpretation, but this knowledge  $\Box Q$  is not instantly useable and is *waiting-to-be-acquired* by a following acquire fence that may transfer it to a normal knowledge according to the [<u>ACQUIRE-FENCE</u>] rule. These three rules are adopted from GPS+ with minor changes, as our extension with release-sequence is still compatible with the principles working on the reader's side.

Compare-and-swap (CAS) plays an important role in C11 concurrent programming. It is the foundation to the implementation of many locks and non-blocking algorithms. It can join in a release-sequence without being in the same thread as the release head. Therefore, sophisticated concurrent algorithms like the atomic reference counter [11] can use CAS operations to create synchronisations between many different threads. GPS+ provides some basic support to CASes without user specified memory orders. In this work, we devise a set of rules to cover CAS operations with all possible memory order specifications. We first take a close look at the [ACQ-REL-CAS] rule. The first premise corresponds to the case of success where  $\ell$ 's value is same  $v_o$  as expected. In this case, the acquire-release CAS performs as a release store However, unlike normal release write which can only use the resource *P* in its precondition to imply its target state's interpretation, a successful CAS can also use the resource from the state interpretation of  $\ell$ 's current state  $(\tau(s', v_o, -, -))$ . In this way, the CAS can retransmit the information passed down in its release-sequence. Moreover, a successful CAS can retrieve non-knowledge resources from the state interpretation of  $\ell$ 's current state. The second premise corresponds to the case of failure where  $\ell$  is found to have some value other than  $v_{\alpha}$ . In this case, the acquire-release CAS performs as an acquire read and some knowledge  $\Box R$  can be retrieved from the

| $[\underline{\text{RELEASE-STORE}}] \qquad [\underline{\text{RELAXED-STORE-1}}] \\ P \Rightarrow \tau(s'', v, -, 0) * Q_1 * Q_2 \qquad \text{normal}(P) \qquad P_2 \Rightarrow \tau(s'', v, -, 0) * Q$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\frac{P \Rightarrow \tau(s'', v, -, 0) * Q_1 * Q_2  \operatorname{normal}(P)}{\{\overline{ \ell:s \tau } * P\} [\ell]_{\operatorname{rel}} := v \{\overline{ \ell:s'' \tau } * \langle Q_1 \rangle_{s''} * Q_2\}}  \frac{P_2 \Rightarrow \tau(s'', v, -, 0) * Q}{\{\overline{ \ell:s \tau } * s. \tau(s', -, -, -) * P_1 * P_2 \Rightarrow s'' \sqsupseteq_\tau s'} \\ \frac{\forall s' \sqsupseteq_\tau s. \tau(s', -, -, -) * P_1 * P_2 \Rightarrow s'' \sqsupseteq_\tau s'}{\{\overline{ \ell:s \tau } * P_1 * Q_2\}}  \frac{\forall s' \sqsupseteq_\tau s. \tau(s', -, -, -) * P_1 * P_2 \Rightarrow s'' \sqsupseteq_\tau s'}{\{\overline{ \ell:s \tau } * P_1 * Q_2\}}$                                                     |

| $\left\{ [t \cdot S]^{\gamma} * F \right\} [t]_{rel} = v \left\{ [t \cdot S]^{\gamma} * \langle Q_1 \rangle_{S''} * Q_2 \right\} = \left\{ [t \cdot S]^{\gamma} * F_1 * \langle F_2 \rangle \right\} [t]_{rlx} = v \left\{ [t \cdot S]^{\gamma} * F_1 * Q \right\}$ [RELAXED-STORE-2]                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $P_2 \Rightarrow 	au(s'', v, -, 0) * Q$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $ \begin{array}{l} \forall s'. \ s'' \sqsupseteq_{\tau} \ s' \sqsupseteq_{\tau} \ s_o \Rightarrow sameThread(s', s_o) \lor isCAS(s') \\ \forall s' \sqsupseteq_{\tau} \ s. \ \tau(s', -, -, -) * P_1 * P_2 \Rightarrow s'' \sqsupseteq_{\tau} \ s' \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $\left\{ \begin{bmatrix} \ell : s \mid \tau \end{bmatrix} * P_1 * \langle P_2 \rangle_{s_o} \right\} [\ell]_{\mathtt{rlx}} := v \left\{ \begin{bmatrix} \ell : s'' \mid \tau \end{bmatrix} * P_1 * Q \right\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [ <u>RELEASE-FENCE</u> ] [ <u>ACQUIRE-FENCE</u> ]<br>normal(P)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\frac{1}{\{P\} \text{ fence}_{\text{rel}} \{\langle P \rangle\}} \qquad \overline{\{\boxtimes P\} \text{ fence}_{\text{acq}} \{\square P\}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\begin{bmatrix} ACQUIRE-LOAD \end{bmatrix} \qquad \begin{bmatrix} RELAXED-LOAD \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\frac{\forall s' \sqsupseteq_{\tau} s. \forall \overline{z. \tau(s', z, -, -)} * P \Rightarrow \Box Q}{\left\{ \left[ \ell: s \mid \overline{\tau} \right] * P \right\} \left[ \ell \right]_{acq} \left\{ z. \exists s'. \overline{\ell: s' \mid \overline{\tau}} * P * \Box Q \right\}}  \frac{\forall s' \sqsupseteq_{\tau} s. \forall z. \tau(s', z, -, -) * P \Rightarrow \Box Q}{\left\{ \left[ \ell: s \mid \overline{\tau} \right] * P \right\} \left[ \ell \right]_{rlx} \left\{ z. \exists s'. \overline{\ell: s' \mid \overline{\tau}} * P * \boxtimes Q \right\}}$                                                                                                                                                    |

| $\forall s' \sqsupseteq_{\tau} s. \tau(s', v_o, -, -) \underbrace{[ACQ-REL-CAS]}_{\forall s'' \sqsupseteq_{\tau} s. \forall y \neq v_o. \tau(s'', y, -, -) * P \Rightarrow \Box R$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\overline{\left\{ \boxed{\ell:s \tau} * P \right\}} \operatorname{CAS}_{\operatorname{acq,rel}}(\ell, v_o, v_n) \left\{ \boxed{z. \exists s''. \boxed{\ell:s'' \tau}} * \left( (z = 1 * Q) \lor (z = 0 * P * \Box R) \right) \right\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $ \begin{array}{c} [\underline{RLX-REL-CAS}] \\ \forall s' \sqsupseteq_{\tau} s. \tau(s', v_o, -, -) * P \Rrightarrow \exists s'' \sqsupseteq_{\tau} s'. \tau(s'', v_n, -, 1) * Q \\ \forall s'' \sqsupseteq_{\tau} s. \forall y \neq v_o. \tau(s'', y, -, -) * P \Longrightarrow \Box R \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\left\{ \boxed{\ell:s \tau} * P \right\} \operatorname{CAS}_{\mathtt{rlx},\mathtt{rel}}(\ell, v_o, v_n) \left\{ \begin{array}{l} z. \exists s''. \boxed{\ell:s'' \tau} \\ * ((z = 1 * \boxtimes Q) \lor \\ (z = 0 * P * \square R)) \end{array} \right\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $\begin{bmatrix} ACQ-RLX-CAS-1 \end{bmatrix} \\ \forall s' \sqsupseteq_{\tau} s. \tau(s', v_o, -, -) * P_2 \Rightarrow \qquad [ACQ-RLX-CAS-2]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\exists s'' \sqsupseteq_{\tau} s'. \tau(s'', v_n, -, 1) * Q \qquad \forall s' \sqsupseteq_{\tau} \overline{s. \tau(s', v_o, -, -)} * P_2 \Longrightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $ \begin{array}{ll} \forall s_i. \ s' \sqsupseteq_{\tau} \ s_i \sqsupseteq_{\tau} \ s_o \Rightarrow sameThread(s_i, s_o) \lor isCAS(s_i) \\ \forall s'' \sqsupseteq_{\tau} \ s. \ \forall y \neq v_o. \ \tau(s'', y, -, -) \ast P_1 \ast P_2 \Rightarrow \Box R \end{array} \\ \begin{array}{l} \exists s'' \sqsupseteq_{\tau} \ s. \ \forall y \neq v_o. \ \tau(s'', y, -, -) \ast P_1 \ast P_2 \Rightarrow \Box R \\ \forall s'' \sqsupseteq_{\tau} \ s. \ \forall y \neq v_o. \ \tau(s'', y, -, -) \ast P_1 \ast P_2 \Rightarrow \Box R \end{array} $                                                                                                                                                                          |

| $\overline{\left\{\frac{\left \left(l:s\mid\tau\right)*}{P_{1}*\langle P_{2}\rangle_{s_{o}}}\right\}} \operatorname{CAS}_{\operatorname{acq,rlx}}(\ell, v_{o}, v_{n}) \left\{\frac{z. \exists s''. \underbrace{\left(l:s''\mid\tau\right)}{*\left((z=1*Q)\vee\right)}}{(z=0*P*\Box R))}\right\}} \overline{\left\{\frac{\left \overline{l:s\mid\tau}\right *}{P_{1}*\langle P_{2}\rangle\right\}}} \operatorname{CAS}_{\operatorname{acq,rlx}}(\ell, v_{o}, v_{n}) \left\{\frac{z. \exists s''. \underbrace{\left(l:s''\mid\tau\right)}{*\left((z=1*Q)\vee\right)}}{(z=0*P*\Box R))}\right\}}$                                                                                                                                    |

| $[\underline{\text{RLX-RLX-CAS-1}}]$<br>$\forall s' \exists_{\tau} s. \tau(s', v_o, -, -) * P_2 \Rightarrow [\text{RLX-RLX-CAS-2}]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\exists s'' \sqsupseteq_{\tau} s'. \tau(s'', v_n, -, 1) * Q \qquad \forall s' \sqsupseteq_{\tau} \overline{s. \tau(s', v_o, -, -)} * P_2 \Rightarrow$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $ \begin{array}{ll} \forall s_i. \ s' \sqsupseteq_{\tau} \ s_i \sqsupseteq_{\tau} \ s_o \Rightarrow sameThread(s_i, s_o) \lor isCAS(s_i) \\ \forall s'' \sqsupseteq_{\tau} \ s. \ \forall y \neq v_o. \ \tau(s'', y, -, -) \ast P_1 \ast P_2 \Rightarrow \Box R \end{array} \\ \begin{array}{l} \exists s'' \sqsupseteq_{\tau} \ s. \ \forall y \neq v_o. \ \tau(s'', y, -, -) \ast P_1 \ast P_2 \Rightarrow \Box R \\ \forall s'' \sqsupseteq_{\tau} \ s. \ \forall y \neq v_o. \ \tau(s'', y, -, -) \ast P_1 \ast P_2 \Rightarrow \Box R \end{array} $                                                                                                                                                                          |

| $\overline{\left\{ \begin{array}{c} \boxed{\left[\ell:s\mid\tau\right]*}{P_{1}*\langle P_{2}\rangle_{s_{o}}} \right\}} \operatorname{CAS}_{\mathtt{rlx},\mathtt{rlx}}(\ell,v_{o},v_{n}) \left\{ \begin{array}{c} z. \exists s''. \boxed{\left[\ell:s''\mid\tau\right]}{*} \\ *\left((z=1*\boxtimes Q)\lor \\ (z=0*P*\Box R)\right) \end{array} \right\}} \overline{\left\{ \begin{array}{c} \boxed{\left[\ell:s\mid\tau\right]*}{P_{1}*\langle P_{2}\rangle} \right\}} \operatorname{CAS}_{\mathtt{rlx},\mathtt{rlx}}(\ell,v_{o},v_{n}) \left\{ \begin{array}{c} z. \exists s''. \boxed{\left[\ell:s''\mid\tau\right]}{*} \\ *\left((z=1*\boxtimes Q)\lor \\ (z=0*P*\Box R)\right) \end{array} \right\}} \\ \end{array} \right\}$ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

FIGURE 10: Synchronisation Related Verification Rules

actual state observed.

The ideas for the other CAS rules are similar. However, when a CAS has relaxed memory order for its reading component ([RLX-REL-CAS], [RLX-RLX-CAS-1], and [RLX-RLX-CAS-2]), it still can retrieve some information (Q) from the state it reads but this information needs to be marked as "waiting-to-be-acquired" in its post condition ( $\boxtimes Q$ ). When a CAS has relaxed memory order for its writing component ([<u>ACQ-RLX-CAS]</u>, [<u>RLX-RLX-CAS-1</u>], and [<u>RLX-RLX-CAS-2</u>]), it can only use the resources that are already sharable to derive its target state interpretation.

#### C. DEALING WITH FRACTIONAL PERMISSIONS

As discussed in §II-E, while atomic locations are designed for concurrent accesses, concurrent accesses (i.e., the accesses not ordered in hb) to a non-atomic location with at least one of them being a store operation lead to *data-races*. To ensure the verified programs are data-race-free, previous work in GPS family models each non-atomic location as a resource that could only be exclusively held by one thread at a time, which means these logics can not support the reasoning about programs with concurrent non-atomic reads (though they would not result in any race-condition). To verify real-world concurrent programs with concurrent non-atomic reads (e.g. the readers-writer-lock algorithm), we introduce fractional permissions for non-atomic locations.

Fractional permissions technique is an example of partial permissions [12], [13]. In our setting, a fraction in the interval [0, 1] is used to represent the portion of the ownership to a non-atomic location. The full permission  $\ell \stackrel{1}{\mapsto}$  – is needed for a thread to write to  $\ell$ ; while for a non-atomic read, only a fraction of the permission will be sufficient:

#### [NON-ATOMIC-STORE]

$$\begin{aligned} \overline{\{\mathsf{uninit}(\ell) \lor \ell \stackrel{1}{\mapsto} -\} \ [\ell]_{\mathtt{na}} := v \ \{\ell \stackrel{1}{\mapsto} v\}} \\ \frac{[\mathtt{NON-ATOMIC-LOAD]}}{p \in (0,1]} \\ \overline{\{\ell \stackrel{p}{\mapsto} v\} \ [\ell]_{\mathtt{na}} \ \{x. \ x = v \ast \ell \stackrel{p}{\mapsto} v\}} \end{aligned}$$

The empty permission  $\ell \stackrel{0}{\mapsto} -$  is semantically equivalent to emp. Permissions can also be combined or separated as defined below:

# $[\underline{\text{SEPARATION-F}}]$ $\ell \stackrel{p}{\mapsto} v * \ell \stackrel{q}{\mapsto} v \iff \begin{cases} \ell \stackrel{p \oplus q}{\mapsto} v & \text{if } p \oplus q \text{ is defined} \\ \texttt{false} & \text{otherwise} \end{cases}$ where $p \oplus q = \begin{cases} p+q & \text{if } p, q, p+q \in [0,1] \\ \texttt{undefined} & \text{otherwise} \end{cases}$

According to the composition rules, a full permission (writing permission) is not compatible with another full permission or any other non-zero permissions. As a result, a program verified by our logic would not have any race condition where a write goes in parallel with other accesses to the same non-atomic location.

#### D. OTHER RULES

Besides the rules highlighted in previous subsections, we also have the following rules that make our reasoning system complete. We gather them into groups for the convenience of discussion.

The following inference rules depict properties of knowledge assertions. That is, knowledge can be transformed back to its normal form; knowledge symbol can be safely nested; a piece of knowledge acts like pure information and thus the separation assertion is equivalent to the logical conjunction; a picked escrow, an assertion about atomic location and a pure term are all knowledge; and a duplicable ghost term is also a form of knowledge.

#### [KNOWLEDGE-MANIPULATION-1...7]

$$\begin{array}{ccc} \Box P \Rightarrow P & \Box P \Rightarrow \Box \Box P & \Box P \ast Q \Leftrightarrow \Box P \land Q \\ [\sigma] \Rightarrow \Box [\sigma] & \fbox{t:t'|\tau]} \Rightarrow \Box \fbox{t:t'|\tau} & t = t' \Rightarrow \Box t = t' \\ & \overbrace{ \overbrace{\gamma:t(\mu)} \Rightarrow \Box [\gamma:t(\mu)]}^{t \cdot \mu} \end{array}$$

The first inference rule below states that ghost terms can be composed or separated according to their PCM definitions. The second inference rule states that two atomic assertions about the same location only coherence if the protocols are same and the states are reachable from one to another or the other way around.

$$[\underline{\text{SEPARATION-1...2}}]$$

$$[\gamma:t|\mu]*[\gamma:t'|\mu] \Leftrightarrow [\gamma:t\cdot\mu t'|\mu]$$

$$\overline{\ell:s|\tau}*[\ell:s'|\tau'] \Rightarrow \tau = \tau' \land (s \sqsubseteq_{\tau} s' \lor s' \sqsubseteq_{\tau} s)$$

Following rules are about possible ghost moves. Particularly, similar to the [UNSHARE-R] rule we have discussed before, the fifth rule allows us to change an unrestricted shareable assertion to its normal form. The seventh rule states that a new ghost term can popup from thin air with a fresh identifier. The eighth rule states that a ghost variable can be updated to a new value as long as the new value is compatible with the environment. The last two rules are inherited from GPS/GPS+ to cope escrows.

$$\begin{bmatrix} \text{GHOST-MOVE-1...8} \end{bmatrix}$$

$$\frac{P \Rightarrow Q}{P \Rightarrow Q} \quad \frac{P \Rightarrow Q}{P \ast R \Rightarrow Q \ast R} \quad \frac{P \Rightarrow Q}{P \Rightarrow R} \quad \langle P \rangle \Rightarrow P$$

$$\text{true} \Rightarrow \exists \gamma . \begin{bmatrix} \gamma : t \mid \mu \end{bmatrix} \quad \frac{\forall t_F : \llbracket \mu \rrbracket . t_1 \#_\mu t_F \Rightarrow t_2 \#_\mu t_F}{[\gamma : t_1 \mid \mu] \Rightarrow \begin{bmatrix} \gamma : t_2 \mid \mu \end{bmatrix}}$$

$$\frac{\sigma : P \rightsquigarrow Q}{Q \Rightarrow [\sigma]} \quad \frac{\sigma : P \rightsquigarrow Q}{P \land [\sigma] \Rightarrow Q}$$

Note that, following the GPS/GPS+ logic for PCM terms with type  $\mu$  we use the shorthand notation  $t_1 \#_{\mu} t_2$  to indicate that  $t_1 \oplus t_2$  is defined. The type declaration can be omitted when it is obvious.

The following rule is for the memory allocation. Starting with any valid precondition, alloc(n) allocates n fresh and continuous locations, which are marked as uninitialised, and uses the leading location as its return value.

#### [ALLOCATION]

$\{\mathsf{true}\}\ \mathtt{alloc}(n)\ \{x.\ x \neq 0 * \mathsf{uninit}(x) * \cdots * \mathsf{uninit}(x+n-1)\}$

The following tow rules are for atomic initialisation. In the precondition P must hold as changing an atomic location to a particular state requires the state interpretation to be satisfied.

$$[INITIALISATION-1...2]$$

$$\frac{P \Rightarrow \tau(s, v)}{\{\text{uninit}(\ell) * P\} \ [\ell]_{rel} := v \ \{\overline{[\ell:s]\tau]}\}}$$

$$\frac{P \Rightarrow \tau(s, v)}{\{\text{uninit}(\ell) * \langle P \rangle\} \ [\ell]_{rlx} := v \ \{\overline{[\ell:s]\tau]}\}}$$

$$\frac{P' \Rightarrow P}{\{P\} \ e \ \{x. Q\}} \frac{[CONSEQUENCE-RULE]}{\{P\} \ e \ \{x. Q\}} \forall x. Q \Rightarrow Q'}{\{P'\} \ e \ \{x. Q\}}$$

$$\frac{[FRAME-RULE]}{\{P\} \ e \ \{x. Q\}}$$

$$\frac{[P' \Rightarrow R] \ e \ \{x. Q * R\}}{\{P * R\} \ e \ \{x. Q * R\}}$$

Essentially, the following rules states that the special assertions are not to be nested. Nesting special assertions is problematic as it may introduce things violate the exquisite design of the whole system. For instance, assuming we allow an assertion in the form of  $\boxtimes \langle P \rangle$ , it immediately becomes shareable,  $\langle P \rangle$ , after an acquire fence which does not have the releasing semantics. Therefore, we prevent such nesting from the resource model level and these inference rules are corollaries of our resource model design. Note that the annotation (e.g. *a*) used in these rules can be any valid label (for restricted shareable assertions) or nothing (for unrestricted shareable assertions).

#### [ASSERTION-PROPERTY-1...7]

$$\begin{split} & \Box \langle P \rangle_a \Rightarrow \texttt{false if EMP} \not\in \llbracket P \rrbracket^{\rho} \quad \boxtimes \langle P \rangle_a \Rightarrow \texttt{false if EMP} \not\in \llbracket P \rrbracket^{\rho} \\ & \boxtimes P \Rightarrow \texttt{false if EMP} \not\in \llbracket P \rrbracket^{\rho} \quad \langle \boxtimes P \rangle_a \Rightarrow \texttt{false if EMP} \not\in \llbracket P \rrbracket^{\rho} \\ & \Box \boxtimes P \Rightarrow \texttt{false if EMP} \not\in \llbracket P \rrbracket^{\rho} \quad \langle P \rangle_a * \langle Q \rangle_a \Leftrightarrow \langle P * Q \rangle_a \\ & \langle \langle P \rangle_{a_1} \rangle_{a_2} \Rightarrow \texttt{false if EMP} \not\in \llbracket P \rrbracket^{\rho} \end{split}$$

$$[\underline{\text{PURE-REDUCTION-AXIOM-1...2}}]$$

{true}  $v \{x. x = v\}$  {true}  $v = v' \{x. x = 1 \Leftrightarrow v = v'\}$

We also have the following rules for conditional statements, let-binding, fork expression, and the repeat loop. The fork rule states that given e can be safely executed from the precondition Q, we can fork a new thread with the precondition  $\{P * Q\}$  to execute e and leaving only P to the parent thread.

$$\begin{array}{c} [ \underline{\text{CONDITIONAL}} \\ \hline \{P \ast v \neq 0\} \ e_1 \ \{x.Q\} \ \ \{P \ast v = 0\} \ e_2 \ \{x.Q\} \\ \hline \{P\} \ \text{if } v \ \text{then } e_1 \ \text{else} \ e_2 \ \{x.Q\} \\ \hline \{P\} \ \text{if } v \ \text{then } e_1 \ \text{else} \ e_2 \ \{x.Q\} \\ \hline \{P\} \ e \ \{x.Q\} \ \ \forall x. \ \{Q\} \ e' \ \{y.R\} \\ \hline \{P\} \ \text{let } x = e \ \text{in } e' \ \{y.R\} \\ \hline \{P \ast Q\} \ \text{fork } e \ \{P\} \\ \hline \left\{P\} \ e \ \{x.(x = 0 \land P) \lor (x \neq 0 \land Q)\} \\ \hline \{P\} \ \text{repeat } e \ \text{end} \ \{x.Q\} \\ \hline \end{array} \right.$$

#### **V. CASE STUDIES**

In this section, we first demonstrate our logic with an illustrative example using a release-sequence to pass messages between three threads. Then, we further illustrate the power of our logic by using it to verify a readers-writer-lock implementation where both the release-sequence and concurrent reads are involved.

#### A. AN ILLUSTRATIVE EXAMPLE

In Fig. 11 we show a message passing program. In this example, the initial values for x and y are both 0. In the first thread, the message x is set to be 42 then y is set to be 1. As the write operation to y is a release write, it initiates a release-sequence that contains the following relaxed write and may contain the CAS in the second thread. In the third thread, y is repeatedly checked until a non-zero value is observed. Then the message x is examined. Note that, for readability we use  $x = e_1$ ;  $e_2$  as an equivalent expression for the command let  $x = e_1$  in  $e_2$  (or simply  $e_1$ ;  $e_2$  if the evaluation result of  $e_1$  is not used in  $e_2$ ). For the same reason, we use || to separate the threads forked.

$$\begin{array}{c|c} [x]_{rlx} := 42; \\ [y]_{rel} := 1; \\ [y]_{rlx} := 3; \end{array} \right\| \begin{array}{c} \mathsf{CAS}_{acq,rel}(y,1,2) \\ \mathsf{CAS}_{acq,rel}(y,1,2) \\ [x]_{req}(x) \\ [$$

FIGURE 11: Message passing using release-sequence