Citation for published version:

Xiang, X, Qiao, Y, Gu, Y, Zhang, X & Green, TC 2020, 'Analysis and Criterion for Inherent Balance Capability in Modular Multilevel DC–AC–DC Converters', *IEEE Transactions on Power Electronics*, vol. 35, no. 6, 8906076, pp. 5573-5580. https://doi.org/10.1109/TPEL.2019.2954304

*DOI:* 10.1109/TPEL.2019.2954304

Publication date: 2020

Document Version Peer reviewed version

Link to publication

© 2019 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other users, including reprinting/ republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works.

# **University of Bath**

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Analysis and Criterion for Inherent Balance Capability in Modular Multilevel DC-AC-DC Converters

Xin Xiang, Member, IEEE, Yang Qiao, Yunjie Gu, Member, IEEE, Xiaotian Zhang, Member, IEEE, Timothy C. Green, Fellow, IEEE

Abstract-Modular multilevel dc-ac-dc converters (MMDAC) have emerged recently for high step-ratio connections in medium voltage distribution systems. Extended phase-shift modulation has been proposed and was found to create the opportunity for inherent balance of SM capacitor voltages. This letter presents fundamental analysis leading to clear criterion for the inherent balance capability in MMDAC. A sufficient and necessary condition, with associated assumptions, to guarantee this capability is established. Using the mathematics of circulant matrices, this condition is simplified to a co-prime criterion which gives rise to practical guidance for the design of an MMDAC. Experiments on down-scaled prototypes and simulations on fullscale examples both provide verification of the analysis and criterion for the inherent balance capability of MMDAC.

*Index Terms*- Inherent voltage balance, modular multilevel dcac-dc converters, circulant matrix, MVDC, LVDC

#### I. INTRODUCTION

The rapid development of high voltage dc (HVDC) transmission and the promising prospect of low voltage dc (LVDC) distribution, as a means to integrate distributed renewable energy and electric vehicles, together provide an impetus to consider bridging the two with medium voltage dc (MVDC) interconnections [1], [2]. Such MVDC could provide controllable and flexible configurations to address growing power demand in urban areas and optimize operation of the distribution networks of the future within a smart grid [3]–[5].

An MVDC distribution system will need a new power electronic interface to connect the MVDC and LVDC networks [5]–[7]. Modular multilevel dc-ac-dc converters (MMDAC) based on dual-active-bridge (DAB) or *LLC* structure have emerged recently [8]–[11] as promising solutions for this application. On the MVDC side, they utilize sub-module (SM) stacks of the modular multilevel converter (MMC) structure to support the medium voltage stress with high modularity and high reliability. A single transformer is used in the internal ac stage to facilitate high step-ratio conversion, in contrast to other modular DAB and *LLC* converters with multiple transformers and associated insulation challenges [6], [12], [13]. The LVDC

Manuscript received September 17, 2019; revised October 26, 2019; accepted November 14, 2019. This work was supported by the Engineering and Physical Sciences Research Council of UK (EPSRC) under awards EP/S000909/1 and EP/T001623/1. (Corresponding author: Dr. Yujie Gu.)

Y. Qiao and X. Zhang is with Department of Electrical Engineering, Xi'an Jiaotong University, Xi'an, 710049, China. (e-mail: qiaoyang888@xjtu.edu.cn; xiaotian@xjtu.edu.cn).

side of MMDAC has the structure of classic DAB or *LLC* circuit and therefore retains the benefits of soft-switching operation leading to good efficiency.

Noting that the number of SMs in each stack of MMDAC is much less than that in a classic MMC for HVDC applications [14], an extended phase-shift modulation scheme [8], [15] was developed for MMDAC and was found to feature inherent balance of their SM capacitor voltages for some operating cases. Inherent balance is important for MMDAC because it can reduce the complexity of the complete control algorithm and thus ease the requirements placed on the controller hardware. It obviates the large computational burden of the real-time sorting and rotation needed in conventional MMC modulation schemes [14], which is usually conducted on expensive Field Programmable Gate Arrays (FPGAs), and it also avoids high speed communication between the controller and the SM. Further, the inherent balance capability allows the converter to revert to working in open-loop, with SM voltage balance maintained, if a sensor or feedback loop fails, and this increases the system reliability of MMDAC. Lastly, it can also benefit the hardware design since the switching frequency, voltage stress and current stress are equal for all SMs and tighter SM design limits can be specified, which could reduce the overall cost of the SM switches, SM capacitors and SM heat sink in MMDAC.

However, these benefits of inherent balance in MMDAC are comprised because its existence had only been demonstrated in some particular operating cases of specific MMDAC topologies [8], [11], [15] and was known to be absent in other cases [9], [16]. The mechanism and criterion for inherent balance have not been not fully understood and only empirical rules of thumb were given in [16]. This letter reformulates switching sequence of the phase-shift modulation [8], [15] as a circulant matrix to capture its feature of cyclically linking the state of the last SM in the stack back to the first. Based on this formulation, a sufficient and necessary condition, with associated assumptions, for inherent balance capability in MMDAC is established. Using the mathematics of circulant matrices [17]-[19], this condition is simplified to a co-prime criterion which gives rise to practical guidance for the design of an MMDAC. Based on these new discoveries, the phase-shift modulation is renamed circulant modulation in this letter to highlight its linkage with circulant matrices. A set of experiments and simulations verifies the analysis and criterion for the inherent balance capability.

## II. INHERENT BALANCE CAPABILITY

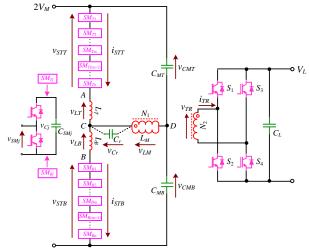

The schematic of the DAB-based MMDAC is shown in Fig.1. The MVDC side contains two stacks of half-bridge SMs, and each stack comprises n SMs. Together they form a single-

X. Xiang, Y. Gu and T. C. Green are with the Department of Electrical and Electronic Engineering, Imperial College London, London, SW7 2AZ, U.K. (e-mail: x.xiang14@imperial.ac.uk; yunjie.gu@imperial.ac.uk; t.green@imperial.ac.uk).

phase MMC arrangement with arm inductors  $L_T$  and  $L_B$ . The connection points for SM stacks and arm inductors are named as *A* for the top arm and *B* for the bottom. The primary winding  $N_1$  and magnetizing inductor  $L_M$  of the internal transformer  $(r_T = N_1/N_2)$  is connected between the phase midpoint *C* and a neutral point *D* created by two dc link capacitors  $C_{MT}$  and  $C_{MB}$ . The average voltages on these two capacitors are assumed to be equal at  $V_M$ . On the LVDC side, a full-bridge circuit connects the transformer secondary winding  $N_2$  to a smoothing capacitor  $C_L$  on the LVDC link. The topology of the *LLC*-based of MMDAC is almost the same but with an extra resonant capacitor  $C_r$  between the phase midpoint and transformer primary winding, as shown by the dashed connection in Fig. 1.

Fig. 1. Schematics of the DAB-based or LLC-based of MMDAC.

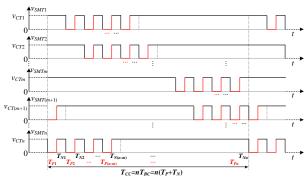

Fig. 2. Circulant modulation scheme for MMDAC (For each SM, red period means its capacitor bypassed, black period means its capacitor inserted).

For the DAB-based MMDAC, the top and bottom stacks generate a pair of complimentary square-wave voltages  $v_{STT}$ and  $v_{STB}$ , leading to identical low square-wave voltages  $v_{AD}$  and  $v_{BD}$  across the internal ac-stage passive network. The voltage  $v_{CD}$  imposed by the LVDC link  $V_L$  and set by the LVDC side full-bridge inverter has a phase shift angle  $\varphi$  with respect to  $v_{AD}$ and  $v_{BD}$ . The angle  $\varphi$  is used to control the current flow between MVDC and LVDC links as in the classic DAB converter, and the arm inductors  $L_T$  and  $L_B$  form a parallel connection and play the equivalent role as the phase-shift inductor in classic DAB converter [13]. For the *LLC*-based MMDAC, the top and bottom stacks also need to generate a pair of complimentary square-wave voltages and create identical low square-wave voltages  $v_{AD}$  and  $v_{BD}$  to excite the resonance between the arm inductor, magnetizing inductor, and resonant capacitor, which constitutes the resonant tank as in the classic *LLC* converter.

By switching either m or n SM capacitors into the circuit  $(1 \le m < n)$  for equal time durations, a SM stack can readily generate a square-wave voltage. Taking the top stack as the example, the positive stage is defined as m SMs switched in (the remainder, n - m, SMs are bypassed) for a period denoted as  $T_P$ . In this state, the top stack voltage  $v_{STT}$  is smaller than  $V_M$ and  $v_{AD}$  is positive. The negative stage is defined as all, i.e., n SMs switched in and its time period is set equal to the positive stage  $(T_N = T_P)$ . In this state, the top stack voltage  $v_{STT}$  is larger than  $V_M$  and  $v_{AD}$  is negative. With the circulant modulation [8], [15], the driving signal for each SM has a time shift of  $T_P + T_N$ with respect to the previous one and the signal of the last SM is the reference for the first. Each SM capacitor is inserted into and bypassed from the circuit in a preset circular sequence, and the SM output voltages,  $v_{SMTi}$  ( $j = 1, 2, \dots, n$ ), forms a sequence of voltage pulses with a circular shift of  $T_P + T_N$ , shown in Fig. 2.

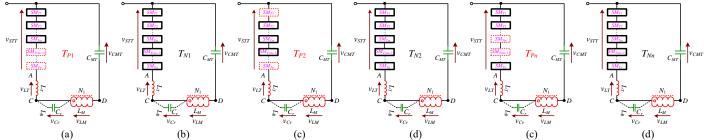

Considering the voltage loop of the top arm during the first positive stage  $T_{P1}$  yields (1), and the equivalent circuit is shown in Fig. 3(a).

$$v_{CMT} - v_{STT} = v_{CMT} - \sum_{j=1}^{n} v_{SMTj} = v_{CMT} - S_{P1T} \cdot v_{CT}^{T} = v_{AD} \quad (1)$$

where  $v_{CMT}$ ,  $v_{STT}$ , and  $v_{AD}$  are the instantaneous voltages for top link capacitor, top SM stack and internal ac-stage passive network. For the DAC-based MMDAC,  $v_{AD} = v_{LT} + v_{LM}$ . For the *LLC*-based MMDAC,  $v_{AD} = v_{LT} + v_{CT} + v_{LM}$ .  $v_{CT} = [v_{CT1} \quad v_{CT2} \cdots \quad v_{CTn}]$ , which is a *n* dimensional voltage vector for each instantaneous SM capacitor voltage.  $S_{P1T} = [\frac{m}{1 \quad 1 \quad \cdots \quad 1 \quad 1} \quad \frac{n-m}{0 \quad 0 \quad \cdots \quad 0 \quad 0}]$ , which is a *n* dimensional switching vector to indicate the on or off (1 or 0) state of each SM in top stack for  $T_{P1}$ . In other words, during the first positive stage, *m* capacitors from  $SM_{T1}$  to  $SM_{Tm}$  are inserted into the circuit while the remaining n - m capacitors from  $SM_{T(m+1)}$  to  $SM_{Tn}$  are bypassed.

The relationship in the following negative stage  $T_{N1}$  is shown in (2), where  $S_{N1T} = \begin{bmatrix} n \\ 1 \\ 1 \\ \cdots \\ 1 \end{bmatrix}$ . All *n* SM capacitors are inserted, and the equivalent circuit is given in Fig. 3(b).

$$v_{CMT} - S_{N1T} \cdot v_{CT}^{T} = v_{AD}$$

<sup>(2)</sup>

The second positive stage,  $T_{P2}$ , can still be expressed by (1) but with the switching vector  $S_{P2T}$  replacing  $S_{P1T}$ . The vector  $S_{P2T}$  for  $T_{P2}$  is generated from  $S_{P1T}$  with a circular shift of all the elements such that the state (1 or 0) of  $SM_{T1}$  is moved to  $SM_{T2}$ and so on plus the state of  $SM_{Tn}$  is moved to  $SM_{T1}$ , i.e.,  $S_{P2T} = \begin{bmatrix} \frac{m}{0 \ 1 \ \cdots \ 1 \ 1} & \frac{n-m}{1 \ 0 \ \cdots \ 0 \ 0} \end{bmatrix}$ . There are still *m* capacitors inserted in  $T_{P2}$  but they are now  $SM_{T2}$  to  $SM_{T(m+1)}$ . The remaining n-m capacitors from  $SM_{T(m+2)}$  to  $SM_{Tn}$  plus  $SM_{T1}$  are bypassed. The following negative stage,  $T_{N2}$ , is still described by (2) since all the SM capacitors are inserted again. The equivalent circuits for  $T_{P2}$  and  $T_{N2}$  are shown in Fig. 3(c) and Fig. 3(d) respectively.

This pattern continues such that the switching vector for *n*th positive stage,  $T_{Pn}$  (the last positive stage), is written as  $S_{PnT}$  =

Fig. 3. Equivalent circuits of the voltage loop of the top arm from  $T_{P1}$  to  $T_{Nn}$  within one circulant cycle. (a) During  $T_{P1}$ . (b) During  $T_{N1}$ . (c) During  $T_{P2}$ . (d) During  $T_{N2}$ . (e) During  $T_{Pn}$ . (f) During  $T_{Nn}$ . (For each SM, red dashed box means its capacitor bypassed, black bold box means its capacitor inserted).

$\begin{bmatrix} m & n-m \\ 1 & 1 & \cdots & 1 & 0 & 0 & 0 & \cdots & 0 & 1 \end{bmatrix}$  for the voltage relationship in (1). This means *m* capacitors from  $SM_{T1}$  to  $SM_{T(m-1)}$  plus  $SM_{Tn}$  are inserted into the circuit while the remaining n-mcapacitors from  $SM_{Tm}$  to  $SM_{T(n-1)}$  are bypassed. The corresponding equivalent circuit is given in Fig. 3(e). After the following negative stage  $T_{Nn}$ , shown in Fig. 3(f), which is still expressed by (2), the top stack operation returns to  $T_{P1}$  and the switching vector goes back to  $S_{P1T}$  for the relationship in (1).

A positive stage and the following common negative stage constitute one base cycle,  $T_{BC}$ , and  $T_{BC} = T_P + T_N$ . This is the operation cycle for dc link capacitor and internal ac-stage passive network. A full set of the base cycles taken together constitutes one circulant cycle,  $T_{CC}$ , and  $T_{CC} = nT_{BC}$ . This is the operation cycle for all the SM capacitors. The switching cycle  $T_{SC}$  for all the SM switches is equal to  $\frac{n}{n-m}T_{BC}$ , and this means the SM switching frequency is lower than the internal ac-stage fundamental frequency for all the operation cases.

In steady-state operation, the integral of  $v_{AD}$  over a base cycle is 0 for both DAB-based and *LLC*-based MMDAC. Combining (1) and (2) for a base cycle integral yields, the average values of each individual SM capacitor voltage as shown in (3).

$$S_{P1T} \cdot \overline{v}_{P1CT}^T + S_{N1T} \cdot \overline{v}_{N1CT}^T = 2V_M \tag{3}$$

where  $\overline{v}_{P1CT} = [\overline{v}_{P1CT_1} \quad \overline{v}_{P1CT_2} \quad \cdots \quad \overline{v}_{P1CT_n}]$  and  $\overline{v}_{N1CT} = [\overline{v}_{N1CT_1} \quad \overline{v}_{N1CT_2} \quad \cdots \quad \overline{v}_{N1CT_n}]$ , which are voltage vectors for the average value of each instantaneous SM capacitor voltage for  $T_{P1}$  and  $T_{N1}$ . Noting that the average voltage difference for each SM capacitor between the short positive stage and negative stage is very small and that the difference in average value between base cycles within one circulant cycle is negligible compared to the medium voltage  $2V_M$ , equation (3) can be written as (4).  $S_{P1T} \cdot \overline{v}_{P1CT}^T + S_{N1T} \cdot \overline{v}_{N1CT}^T$

$\approx \overline{v}_{P1T} \cdot \overline{v}_{1CT}^T + S_{N1T} \cdot \overline{v}_{1CT}^T \approx S_{P1T} \cdot \overline{v}_{CT}^T + S_{N1T} \cdot \overline{v}_{CT}^T = 2V_M \quad (4)$ where  $\overline{v}_{1CT} = [\overline{v}_{1CT1} \quad \overline{v}_{1CT2} \quad \cdots \quad \overline{v}_{1CTn}]$  and  $\overline{v}_{CT} = [\overline{v}_{CT1} \quad \overline{v}_{CT2} \quad \cdots \quad \cdots \quad \overline{v}_{CTn}]$ , which are voltage vectors for the average value of each instantaneous SM capacitor voltage for one  $T_{BC}$  and  $T_{CC}$ .

The circulant cycle  $T_{CC}$  is the voltage cycle for all SM capacitors, and so each of  $\bar{v}_{CT1}$ ,  $\bar{v}_{CT2}$ ,  $\cdots$ ,  $\bar{v}_{CTn}$  should be a constant (but not necessarily equal) in steady-state operation and their sum is designated as  $V_{CTS}(V_{CTS} = S_{N1T} \cdot \bar{v}_{CT}^T)$ .

Considering all the base cycles in relationship (4), the individual equations can be combined and expressed in (5).

$$S_{PT} \cdot \overline{v}_{CT}^{T} = \begin{bmatrix} S_{P1T} \\ S_{P2T} \\ \vdots \\ S_{PnT} \end{bmatrix} \cdot \begin{bmatrix} v_{CT1} \\ \overline{v}_{CT2} \\ \vdots \\ \overline{v}_{CTn} \end{bmatrix}$$

$$=\begin{bmatrix} \begin{matrix} m & & n-m \\ 1 & 1 & \cdots & 1 & 1 \\ 0 & 1 & \cdots & 1 & 1 & 1 \\ \vdots & & & \vdots & \\ 1 & 1 & \cdots & 1 & 0 & 0 & 0 \\ & \vdots & & & \vdots & \\ 1 & 1 & \cdots & 1 & 0 & 0 & 0 & \cdots & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} \bar{v}_{CT1} \\ \bar{v}_{CT2} \\ \vdots \\ \bar{v}_{CTn} \end{bmatrix} = \begin{bmatrix} 2V_M - V_{CTS} \\ 2V_M - V_{CTS} \\ \vdots \\ 2V_M - V_{CTS} \end{bmatrix}$$

(5)

Since  $S_{PT}$  is a  $n \times n$  matrix, the sufficient and necessary condition for a unique solution of *n* dimensional vector  $\overline{v}_{CT}$  in (5) is that the determinant of  $S_{PT}$  is not 0 [17], as written in (6).  $det(S_{PT}) \neq 0$  (6)

With this condition established, all the elements in voltage vector  $\overline{v}_{CT}$  are linearly independent in (5) which guarantees a unique solution for each of them. Furthermore, analyzing each switching vector,  $S_{P1T}$ ,  $S_{P2T}$ ,  $\cdots$ ,  $S_{PnT}$  in matrix  $S_{PT}$ , it is found that  $S_{PT}$  is a circulant matrix [18], which means each element of voltage vector  $\overline{v}_{CT}$  plays equivalent role in (5) when  $\overline{v}_{CT}$  has a unique solution. Therefore, so long as the voltage vector  $\overline{v}_{CT}$  has a shown in (7).

$$\bar{v}_{CT1} = \bar{v}_{CT2} = \dots = \bar{v}_{CTn} = \frac{2V_M}{m+n}$$

(7)

In other words, the sufficient and necessary condition for inherent balance of the average voltages of all SM capacitors in steady-state operation of MMDAC is that the determinant of its switching matrix  $S_{PT}$  is not 0. This guarantees that the modulation has a complete rotation for all the SMs within one circulant cycle and therefore energy is fully circulated and shared among all the SM capacitors such that their average voltages are inherently balanced at the value given by (7). In contrast, if  $det(S_{PT}) = 0$ , there exist linearly dependent elements in  $\overline{v}_{CT}$  and its solution is therefore not unique. This implies that the rotation is not complete and there exists redundant and ineffective rotation within one circulant cycle for SMs. Energy is only effectively circulated among subsets of SM capacitors, and so SM capacitor voltages will not be inherently balanced.

It is worth noting that this condition cannot guarantee equal ripple voltage for all the SMs within one circulant cycle because that depends also on individual values of the SM capacitances.

#### III. SIMPLIFIED CRITERION FOR PRACTICAL DESIGN

The condition in (6) ensures the inherent balance capability in steady-state operation of MMDAC, but the matrix  $S_{PT}$  is complex because the SM number in positive stage and negative stage can both be chosen flexibly  $(1 \le m < n)$  to create various step-ratios. The determinant of their consequent switching matrix is not straightforward enough to serve as a clear criterion for practical design and operation. Since  $S_{PT}$  is a  $n \times n$  circulant matrix, its determinant can be written as (8) using the circulant matrix theory [18], [19].

$$det(\mathbf{S}_{PT}) = \prod_{k=0}^{n-1} (1 + 1 \cdot \omega_k + \dots + 1 \cdot \omega_k^{m-1} + 0 \cdot \omega_k^m + 0 \cdot \omega_k^{m+1} + \dots + 0 \cdot \omega_k^{n-1})$$

(8)

where  $\omega_k = e^{i2\pi \frac{k}{n}}, k = 0, 1, \dots, n-1$ , which are the *n*th roots of

unity  $(\omega_k^n = 1)$  and *i* is the imaginary unit. Then, the expression (8) is simplified and expressed as (9).

$$det(S_{PT}) = \prod_{k=0}^{n-1} (1 + \omega_k + \omega_k^2 + \dots + \omega_k^{m-1}) = \prod_{k=1}^{n-1} \frac{1 - \omega_k^m}{1 - \omega_k} \cdot m$$

$$= \prod_{k=1}^{n-1} \frac{1 - e^{i2\pi \cdot \frac{mk}{n}}}{1 - e^{i2\pi \cdot \frac{mk}{n}}} \cdot m = \prod_{k=1}^{n-1} \frac{e^{i2\pi} - e^{i2\pi \cdot \frac{mk}{n}}}{e^{i2\pi} - e^{i2\pi \cdot \frac{k}{n}}} \cdot m$$

(9)

The value of  $\frac{mn}{n}$  cannot be an integer if the values of m and n are co-prime (i.e., their only common factor is 1) since k is an integer from 1 to n - 1 in the last product expression of (9) and thus the value of  $det(S_{PT})$  cannot equal 0. If, on the other hand, m and n have a common factor other than 1, i.e., they are not co-prime, there always exists a value of k between 1 and n-1which makes  $\frac{mk}{n}$  become an integer and therefore  $det(S_{PT})$  will equal 0. It follows that the sufficient and necessary condition (6) for inherent balance capability has been simplified to m and nbeing co-prime. In other words, so long as the number of SMs switched into positive stage and the number of SMs switched into negative stage are co-prime, the average voltages of all SM capacitor are inherently balanced in steady-state operation. In contrast, if the SM numbers for positive stage and negative stage have a common factor other than 1, the converter will lose this capability. This criterion of m and n being co-prime is much clearer and simper than the matrix condition (6) and provides more practical guidance for designing the circuit and modulation of an MMDAC.

As an example, if m = 3 and n = 4, the relationships of the average SM capacitor voltages are written in (10).

$$\begin{bmatrix} 1 & 1 & 1 & 0 \\ 0 & 1 & 1 & 1 \\ 1 & 0 & 1 & 1 \\ 1 & 1 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} \bar{v}_{CT1} \\ \bar{v}_{CT2} \\ \bar{v}_{CT3} \\ \bar{v}_{CTn} \end{bmatrix} = \begin{bmatrix} 2V_M - V_{CTS} \\ 2V_M - V_{CTS} \\ 2V_M - V_{CTS} \\ 2V_M - V_{CTS} \end{bmatrix}$$

(10)

Since m and n are co-prime, the determinant of this switching matrix is not 0. All the average SM capacitor voltages are linearly independent, and they are inherently balanced at the value in (11) derived from (10).

$$\bar{v}_{CT1} = \bar{v}_{CT2} = \bar{v}_{CT3} = \bar{v}_{CT4} = \frac{2}{7} V_M$$

(11)

As a contrasting example, with m = 2 and n = 4, the voltage relationships are given in (12).

$$\begin{bmatrix} 1 & 1 & 0 & 0 \\ 0 & 1 & 1 & 0 \\ 0 & 0 & 1 & 1 \\ 1 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} \vec{v}_{CT1} \\ \vec{v}_{CT2} \\ \vec{v}_{CT3} \\ \vec{v}_{CTn} \end{bmatrix} = \begin{bmatrix} 2V_M - V_{CTS} \\ 2V_M - V_{CTS} \\ 2V_M - V_{CTS} \\ 2V_M - V_{CTS} \end{bmatrix}$$

(12)

Because *m* and *n* have the common factor of 2, the determinant of this switching matrix is 0 and linearly dependent elements exist. The solution obtained from (12) is not unique for  $\bar{v}_{CT1}$ ,  $\bar{v}_{CT2}$ ,  $\bar{v}_{CT3}$ ,  $\bar{v}_{CT4}$ , as shown in (13), where *K* can be an arbitrary constant between 0 and  $\frac{2}{3}V_M$  and the solution that will exist in practice depends on the initial state of the circuit. Although there might exist a very specific initial state for the

circuit that leads to  $K = \frac{1}{3}V_M$  and  $\bar{v}_{CT1} = \bar{v}_{CT2} = \bar{v}_{CT3} = \bar{v}_{CT4} = \frac{1}{3}V_M$ , the converter in this operating case still needs to be seen as lacking inherent balance capability because it cannot rely, in general, on that specific initial state for the voltage balance of SM capacitors existing.

$$\begin{cases} v_{CT1} = v_{CT3} = K\\ \bar{v}_{CT2} = \bar{v}_{CT4} = \frac{2}{3}V_M - K \end{cases}$$

(13)

#### IV. DOWN-SCALED EXPERIMENTAL VERIFICATION

To validate the theoretical analysis, a down-scaled prototype of a DAB-based MMDAC was built first with the parameters listed in Table I. The ac-stage frequency is set at 3 kHz in this down-scaled prototype with consideration of the practical applications of MMDAC for high-power medium-voltage conversion [9], [20]. The SM capacitances have 10% variation from the nominal value due to the manufacturing tolerances.

TABLE I. DOWN-SCALED EXPERIMENTAL PARAMETERS

| Parameter                         | Description                        | Value                    |

|-----------------------------------|------------------------------------|--------------------------|

| Р                                 | Power Range                        | 0-±500 W                 |

| $2V_M$                            | Medium-side Terminal Voltage       | 700 V                    |

| $V_L$                             | Minimum Low-side Terminal Voltage  | 20 V                     |

| C <sub>SMT</sub> C <sub>SMB</sub> | DC Link Capacitance                | 550 µF                   |

| $L_T L_B$                         | Arm Inductance                     | 7.47 mH                  |

| $L_m$                             | Magnetizing Inductance             | 460 mH                   |

| $r_T$                             | Transformer Turns-ratio            | 55:22                    |

| f <sub>BC</sub>                   | Base Frequency, AC-stage Frequency | 3 kHz                    |

| n                                 | SM Number per stack                | 4                        |

| C <sub>SMj</sub>                  | SM Capacitance                     | 50 µF with 10% variation |

| S                                 | Power Switches                     | FF225R12ME4              |

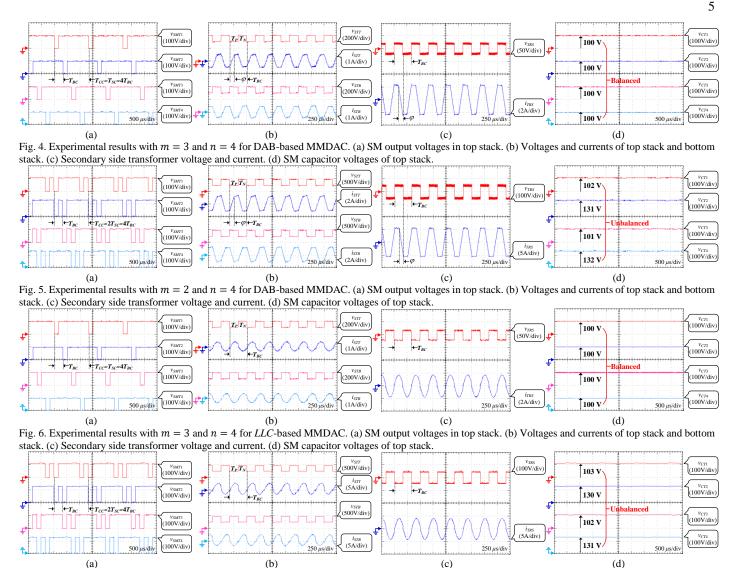

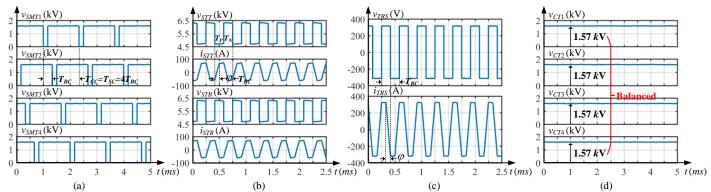

Experimental results for operation with m = 3 and n = 4 are recorded in Fig. 4. The SM output voltages in Fig. 4(a) show that one SM is bypassed in each positive stage and each SM is bypassed for one positive stage in each circulant cycle. The SMs are inserted into and bypassed from the circuit in a preset circular sequence and the switching frequency  $f_{sc}$  of all SMs is equal to a quarter of the base frequency  $f_{BC}$  for internal ac stage. This circular shift switching sequence generates the top stack voltage in Fig. 4(b), and the complimentary voltage from bottom stack as also presented. The transformer voltage  $v_{TRS}$ , shown in Fig. 4(c), is set an angle  $\varphi$  against the stack voltages to control the current as in the classic DAB. Because m and nare co-prime in this case, the average SM capacitor voltages should be inherently balanced. Here, they are within 2% of 100 V in Fig. 4(d), which is the value predicted from the theoretical analysis in (11). It is worth noting that the low-side terminal voltage and the angle  $\varphi$  can both be freely varied to adjust the power as in the classic DAB circuit and they are not constrained by the modulation pattern providing inherent balance.

Experimental results for operation with m = 2 and n = 4 are shown in Fig. 5. It can be seen in Fig. 5(a) that two SMs are bypassed in each positive stage and each SM is bypassed for two positive stages in each circulant cycle. The generated stack voltages in Fig. 5(b) still work at angle  $\varphi$  with respect to the

Fig. 7. Experimental results with m = 2 and n = 4 for *LLC*-based MMDAC. (a) SM output voltages in top stack. (b) Voltages and currents of top stack and bottom stack. (c) Secondary side transformer voltage and current. (d) SM capacitor voltages of top stack.

transformer voltage in Fig. 5(c) to control the current flow. However, the existence of common factor of 2 for m and n in this case removes the inherent balance capability between all SM capacitor voltages. The average SM capacitor voltages shown in the Fig. 5(d) validate the theoretical analysis in (13) and the voltage difference observed between SM capacitors is around 30% of their individual average voltage.

The prototype of DAB-based MMDAC can be readily modified to become an *LLC*-based MMDAC. All circuit parameters remain the same as in Table I but a resonant capacitor ( $C_r = 0.824 \ uF$ ) is inserted between the phase midpoint and transformer primary winding, as the connection in Fig. 1.

Experimental results for operation with m = 3 and n = 4 are shown in Fig. 6. The switching sequence and switching frequency, shown in Fig. 6(a), are the same with those in Fig. 4(a) for DAB-based MMDAC. The generated stack voltage in Fig. 6(b) excites the resonance between arm inductor and resonant capacitor, and the resonant current goes through transformer, shown in Fig. 6(c), before the rectification back to dc. Because m and n are co-prime, all the average SM capacitor voltages have been inherently balanced at 100 V in Fig. 6(d), which further validates the theoretical analysis in (11). The base frequency for internal ac stage can be freely adjusted around the resonant frequency to control the voltage as in the classic *LLC* circuit and it is not constrained by the inherent balance condition. In this case, the base frequency was 3 kHz and the resonant frequency was 2.87 kHz.

Experimental results for operation with m = 2 and n = 4 are recorded in Fig. 7. The switching sequence and switching frequency in Fig. 7(a) are also the same with those in Fig. 5(a). The generated stack voltage in Fig. 7(b) still excites the resonant operation, and the resonant current trough transformer in this operation case is shown in Fig. 7(c). Because *m* and *n* are not co-prime, this *LLC*-based MMDAC also loses the inherent voltage balance capability as expected, shown in Fig. 7(d).

### V. FULL-SCALE SIMULATION VERIFICATION

To verify that the analysis and the balance criterion remain

Fig. 8. Simulation results with m = 3 and n = 4 for DAB-based MMDAC. (a) SM output voltages in top stack. (b) Voltages and currents of top stack and bottom stack. (c) Secondary side transformer voltage and current. (d) SM capacitor voltages of top stack.

Fig. 9. Simulation results with m = 2 and n = 4 for DAB-based MMDAC. (a) SM output voltages in top stack. (b) Voltages and currents of top stack and bottom stack. (c) Secondary side transformer voltage and current. (d) SM capacitor voltages of top stack.

valid beyond the down-scaled prototype, a simulation model of DAB-based MMDAC was built for a full-scale medium voltage dc application with the parameters shown in Table II. The SM capacitances were set with 10% variation to reflect manufacturing tolerances.

| Parameter                         | Description                           | Value                         |

|-----------------------------------|---------------------------------------|-------------------------------|

| Р                                 | Power Range                           | 0-±300 kW                     |

| $2V_M$                            | Medium-side Terminal Voltage          | 11 kV                         |

| $V_L$                             | Minimum Low-side Terminal Voltage     | 310 V                         |

| C <sub>SMT</sub> C <sub>SMB</sub> | DC Link Capacitance                   | 550 µF                        |

| $L_T L_B$                         | Arm Inductance                        | 0.98 mH                       |

| $L_m$                             | Magnetizing Inductance                | 460 mH                        |

| $r_T$                             | Transformer Turns-ratio               | 5:2                           |

| $f_{BC}$                          | Base Frequency, AC-stage Frequency    | 3 kHz                         |

| n                                 | SM Number per stack                   | 4                             |

| C <sub>SM i</sub>                 | <i>C<sub>SMi</sub></i> SM Capacitance | 500 µF with                   |

| S                                 | Power Switches                        | 10% variation<br>FF450R33T3E3 |

TABLE II. FULL-SCALED SIMULATION PARAMETERS

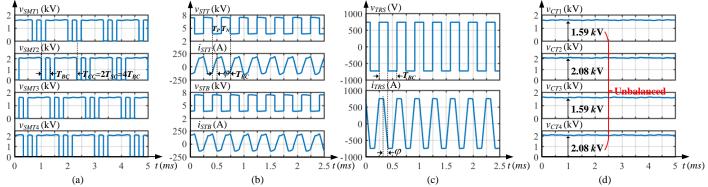

Simulation results for m = 3 and n = 4 are presented in Fig. 8. The switching sequence for each SM, shown in Fig. 8(a), is identical to that in Fig. 4(a). The generated stack voltages in Fig. 8(b) work with the transformer voltage in Fig. 8(c) and their phase-shift angle  $\varphi$  can be also utilized to control the power flow between MVDC side and LVDC side. Since *m* and *n* are co-prime, the average SM capacitor voltages are inherently balanced at 1.57 kV in Fig. 8(d), which also reaches good agreement with the results in (11).

Simulation results for the contrasting example with m = 2 and n = 4 are given in Fig. 9. The switching sequence in Fig. 9(a) is identical to that in Fig. 5(a), and the stack voltages in Fig. 9(b) still work with the transformer voltage in Fig. 9(c). Due to the existence of common factor for m and n in this case, the SM capacitor voltages cannot be inherently balanced at one common value, which verifies the results in (13) again.

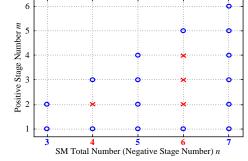

Fig. 10. Inherent balance results in various operation cases.

To further verify the criterion for inherent voltage balance, results for cases with the total number of SM, n, varying from 3 to 7 are summarized in Fig. 10. It can be seen that the SM capacitor voltages are inherently balanced when the total SM number (the negative stage number) n is set at 3, 5 and 7. All of these are prime numbers and cannot have a common factor other than 1 with any positive stage number m ( $1 \le m < n$ ). For n = 4 and n = 6, the inherent balance capability is lost when m and n are not co-prime (m = 2, n = 4; m = 2, n = 6; m = 3, n = 6; m = 4, n = 6). With this in mind, it is recommended that the

total number of SMs in each stack of an MMDAC is chosen to be prime thereby guaranteeing that inherent balance capability is present for all the operation cases.

The full-scale simulation results for the *LLC*-based MMDAC were also conducted by adding a resonant capacitor ( $C_r = 6.25 \ uF$ ) to the model of the DAB-based MMDAC. The results are very similar to Fig. 8 to Fig. 10, which also verify the theoretical analysis and criterion. The detailed waveforms are not repeated here to keep the letter concise.

#### VI. CONCLUSION

This letter has presented fundamental analysis leading to clear criterion for the inherent balance capability of SM capacitor voltages in modular multilevel dc-ac-dc converters (MMDAC). A sufficient and necessary condition, with associated assumptions, to guarantee this capability in steadystate operation was established. Using the mathematics of circulant matrices, this condition was equivalently simplified to a co-prime criterion which gives rise to practical guidance for the design of an MMDAC. It is recommended that a prime number is chosen for the total SM number in each stack because this guarantees that the inherent balance capability is present in all the operation cases. The experimental results on downscaled prototypes and simulation results on full-scale examples both verified the theoretical analysis and criterion for MMDAC.

#### REFERENCE

- S. Cui, J. Hu and R. W. De Doncker, "Control and Experiment of a TLC-MMC Hybrid DC-DC Converter for Interconnection of MVDC and HVDC Grids," in *IEEE Trans. on Power Electron.* Early Access.

- [2] Q. Song, B. Zhao, J. Li and W. Liu, "An Improved DC Solid State Transformer Based on Switched Capacitor and Multiple-Phase-Shift Shoot-Through Modulation for Integration of LVDC Energy Storage System and MVDC Distribution Grid," in *IEEE Trans. on Ind. Electronics*, vol. 65, no. 8, pp. 6719-6729, Aug. 2018.

- [3] S. Inoue and H. Akagi, "A Bidirectional Isolated DC–DC Converter as a Core Circuit of the Next-Generation Medium-Voltage Power Conversion System," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 535-542, March 2007.

- [4] S. P. Engel, M. Stieneker, N. Soltau, S. Rabiee, H. Stagge and R. W. De Doncker, "Comparison of the Modular Multilevel DC Converter and the Dual-Active Bridge Converter for Power Conversion in HVDC and MVDC Grids," in *IEEE Trans. on Power Electron.*, vol. 30, no. 1, pp. 124-137, Jan. 2015.

- [5] X. Zhang, M. Tian, X. Xiang, J. Pereda, T. C. Green and X. Yang, "Large Step Ratio Input-Series–Output-Parallel Chain-Link DC–DC Converter," in *IEEE Trans. on Power Electron.*, vol. 34, no. 5, pp. 4125-4136, May 2019.

- [6] J. Zhang, Z. Wang and S. Shao, "A Three-Phase Modular Multilevel DC– DC Converter for Power Electronic Transformer Applications," in *IEEE J. Emerg. Sel. Topics Power Electron*, vol. 5, no. 1, pp. 140-150, March 2017.

- [7] B. Zhao, Q. Song, J. Li, W. Liu, G. Liu and Y. Zhao, "High-Frequency-Link DC Transformer Based on Switched Capacitor for Medium-Voltage DC Power Distribution Application," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4766–4777, Jul. 2016.

- [8] X. Zhang, T. C. Green and A. Junyent-Ferré, "A New Resonant Modular Multilevel Step-Down DC–DC Converter with Inherent-Balancing," in *IEEE Trans. on Power Electron.*, vol. 30, no. 1, pp. 78-88, Jan. 2015.

- [9] Y. Qiao, X, Zhang, X. Xiang, X. Yang, T. C. Green, "Trapezoidal Current Modulation for Bidirectional High Step-ratio Modular DC-DC Converters," *IEEE Trans. Power Electron.*, Early Access.

- [10] S. Shao, M. Jiang, J. Zhang and X. Wu, "A Capacitor Voltage Balancing Method for a Modular Multilevel DC Transformer for DC Distribution System," in *IEEE Trans. on Power Electron.*, vol. 33, no. 4, pp. 3002-3011, April 2018.

- [11] Y. Li, X. Lyu and D. Cao, "A Zero-Current-Switching High Conversion Ratio Modular Multilevel DC–DC Converter," in *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 1, pp. 151-161, March 2017.

- [12] S. Cui, N. Soltau and R. W. De Doncker, "A High Step-Up Ratio Soft-Switching DC–DC Converter for Interconnection of MVDC and HVDC Grids," in *IEEE Trans. on Power Electron.*, vol. 33, no. 4, pp. 2986-3001, April 2018.

- [13] B. Zhao, Q. Song, W. Liu and Y. Sun, "Overview of Dual-Active-Bridge Isolated Bidirectional DC–DC Converter for High-Frequency-Link Power-Conversion System," in *IEEE Trans. on Power Electron.*, vol. 29, no. 8, pp. 4091-4106, Aug. 2014.

- [14] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard and P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review", *IEEE Trans. Power Electron*, vol. 30, no. 1, pp. 37-53, Jan. 2015.

- [15] S. Kenzelmann, A. Rufer, D. Dujic, F. Canales, and Y. R. de Novaes, "Isolated DC/DC Structure Based on Modular Multilevel Converter," *IEEE Trans. on Power Electron.*, vol. 30, no. 1, pp. 89-98, Jan. 2015.

- [16] X. Xiang, X. Zhang, G. P. Chaffey and T. C. Green, "An Isolated Resonant Mode Modular Converter With Flexible Modulation and Variety of Configurations for MVDC Application," in *IEEE Trans. on Power Del.*, vol. 33, no. 1, pp. 508-519, Feb. 2018.

- [17] G. Strang, Introduction to Linear Algebra, 5th edition, Wellesley-Cambridge, 2016.

- [18] P. Davis, *Circulant Matrices*, 2nd edition, American Mathematical Society, 2012.

- [19] G. Golub and C. Loan, *Matrix Computations*, 4th edition, Johns Hopkins University, 2013.

- [20] N. Soltau, H. Stagge, R. W. De Doncker and O. Apeldoorn, "Development and demonstration of a medium-voltage high-power DC-DC converter for DC distribution systems," 5th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Galway, 2014, pp. 1-8.