### Investigations of Perspective Materials for Aggressively Scaled Gate Stacks and Contact Structures of MOS devices

Von der Fakultät für Mathematik, Naturwissenschaften und Informatik der Brandenburgischen Technischen Universität Cottbus

zur Erlangung des akademischen Grades

Doktor der Naturwissenschaften (Dr. rer. nat.)

genehmigte Dissertation

vorgelegt von

# Dipl.-Phys. Andriy Goryachko

geboren am 2. November, 1974 in Kiew, Ukraine

Gutachter: Prof. Dr. rer. nat. habil. Dieter Schmeißer

Gutachter: Dr. rer. nat. habil. Hans-Joachim Müssig

Gutachter: Prof. Dr. rer. nat. habil. Karsten Horn

Tag der mündlichen Prüfung: 29. November 2002

#### **Contents**

| I. Introduction                                                                          | 1       |

|------------------------------------------------------------------------------------------|---------|

| II. Experimental techniques                                                              | 11      |

| II.1. Auger electron spectroscopy                                                        | 11      |

| II.1.a. Physical background of AES                                                       | 11      |

| II.1.b. Basic realisation of AES                                                         | 14      |

| II.1.c. Quantitative AES                                                                 | 17      |

| II.1.d. AES experimental setup.                                                          | 22      |

| II.1.e. Related technique: X-ray photoelectron spectroscopy                              | 23      |

| II.2. Scanning tunnelling microscopy                                                     | 24      |

| II.2.a. Physical background of STM                                                       | 25      |

| II.2.b. Principles of STM operation                                                      | 26      |

| II.2.c. STM experimental setup                                                           | 28      |

| III. New features in atomic structure of the Si(100)-c(4´4) reconstruction               | 29      |

| III.a. The c(4×4) reconstruction of the Si(100) surface                                  | 29      |

| III.b. Interaction of submonolayer Bi films with the Si(100) surface and formation       | tion of |

| the c(4×4) reconstruction.                                                               | 31      |

| III.c. Previously reported features of the Si(100)-c(4×4) structure                      | 37      |

| III.d. Novel features of the Si(100)-c(4×4) structure                                    | 39      |

| III.e. Semi-empirical modeling of the Si(100)-c(4×4) structure                           | 42      |

| III.f. Factors which stabilize the Si(100)-c(4×4) structure                              | 48      |

| III.g. Summary of the novel features of the Si(100)-c(4×4) reconstruction and to         | the     |

| issues relevant to epitaxy on the Si(100) surface                                        | 51      |

| IV. Thermal stability of Pr <sub>2</sub> O <sub>3</sub> films grown on Si(100) substrate | 55      |

| IV.a. High-K dielectrics and analysis of Pr <sub>2</sub> O <sub>3</sub>                  |         |

| IV.b. Uncapped film without annealing                                                    |         |

| IV.c. 600°C annealing of uncapped film                                                   | 59      |

| IV.d. 700°C annealing of uncapped film                                                   | 60      |

| IV.e. 900°C annealing of uncapped film in an N <sub>2</sub> atmosphere                 | 61           |

|----------------------------------------------------------------------------------------|--------------|

| IV.f. Annealing of Pr <sub>2</sub> O <sub>3</sub> film capped with Si                  | 62           |

| IV.g. Formation of PrSi <sub>x</sub> layer from capped Pr <sub>2</sub> O <sub>3</sub>  | 67           |

| IV.h. Source/Drain contacts based on PrSi <sub>x</sub>                                 | 70           |

| IV.i. Summary of Pr <sub>2</sub> O <sub>3</sub> thermal stability                      | 71           |

|                                                                                        |              |

| V. Improved AES sputter depth profiling of $W/WN_x$ and $WSi_x$                        | layers on Si |

| substrates                                                                             | 73           |

| V.a. W/WN <sub>x</sub> and WSi <sub>x</sub> layers on Si substrates and their analysis | 73           |

| V.b. W/WN <sub>x</sub> films                                                           | 74           |

| V.c. WSi <sub>x</sub> films                                                            | 82           |

| V.d. W/WN <sub>x</sub> and WSi <sub>x</sub> analysis specifics summary                 | 87           |

|                                                                                        |              |

| VI. Multitechnique control of the Co SALICIDE process                                  | 89           |

| VI.a. Self-aligned silicide (SALICIDE) process based on Co silicide                    | 89           |

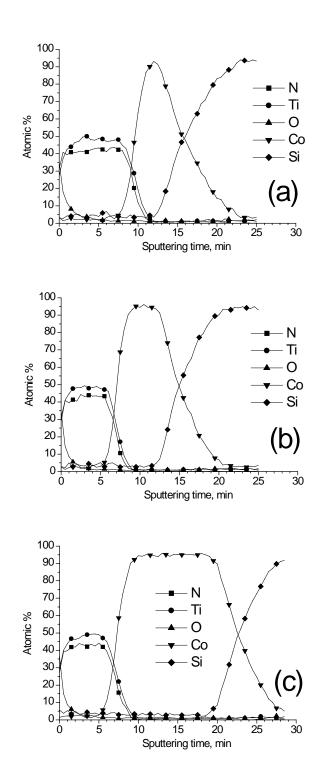

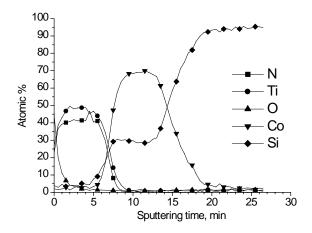

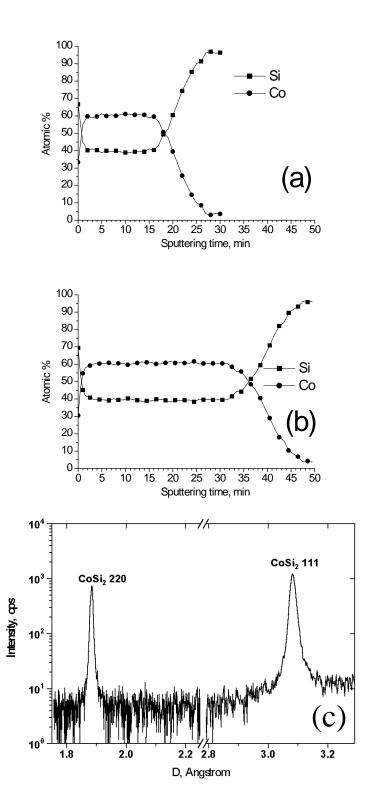

| VI.b. As-deposited structures (TiN/Co/Si)                                              | 91           |

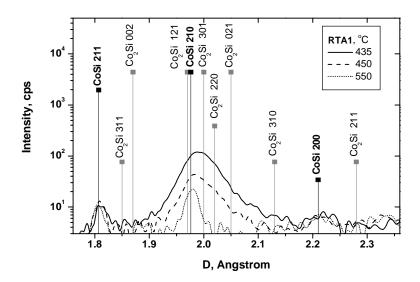

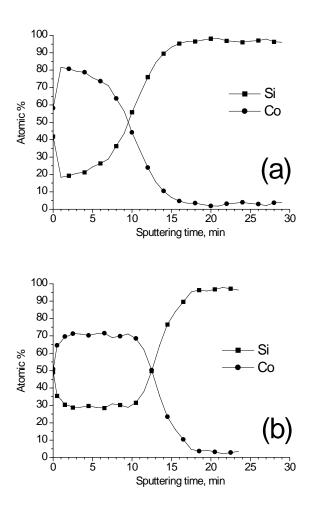

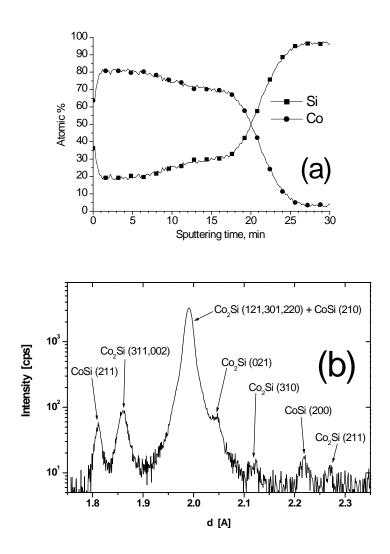

| VI.c. First silicidation step                                                          | 95           |

| VI.d. Second silicidation step                                                         | 102          |

| VI.e. Summary of Co SALICIDE process control for industrial wafer pro-                 | ocessing     |

| technology                                                                             | 103          |

|                                                                                        | 107          |

| VII. Conclusions                                                                       |              |

| VII.a. Outlook                                                                         |              |

| VII.b. Summary                                                                         | 109          |

| References                                                                             | 111          |

|                                                                                        |              |

| Acknowledgments                                                                        | 119          |

#### Chapter I

#### Introduction

Modern microelectronics is a rapidly developing field which is predominantly based on the complementary metal-oxide-semiconductor (CMOS) technology [1]. The fundamental element of all CMOS integrated circuits (ICs) is the metal-oxide-semiconductor (MOS) transistor [2]. Currently there is a market-driven trend of improving the ICs performance and functionality with a simultaneous decrease in cost. This trend dictates the necessity of further ICs miniaturisation, which in turn leads to shrinking sizes of the MOS transistors [3,4]. While the latter are scaled down, it is important to maintain or improve their gain, switching speed, power dissipation, reliability, operating voltage, etc. This turns out to be possible only if some of the materials traditionally used in the device structures (active and passive) are replaced by new ones with physical properties more suitable for achieving the targeted device parameters. The integration of new materials into the ICs is itself a complex task, since

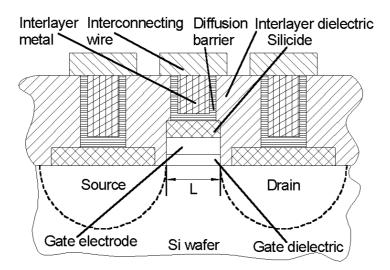

Fig. I.1. The basic structure of the MOS transistor inside of the IC. The transistor consists of source and drain areas in the Si substrate, the gate dielectric (usually  $SiO_2$ ), and the gate electrode (usually poly-Si). The circuit is formed by interconnecting wires (usually Al) going from one transistor to another. The wires are separated from the substrate by interlayer dielectric (usually  $SiO_2$ ). The contact between the wire and the transistor consists of silicide (usually  $WSi_2$ ,  $TiSi_2$ , or  $CoSi_2$ ), the diffusion barrier (usually TiN or Ti/TiN), and the interlayer metal (usually W).

it requires consideration of numerous issues: deposition procedures, thermal stability, physical properties degradation, etc. As a result a massive analytical effort is usually associated with introduction of new materials into the advanced ICs manufacturing technology.

In order to highlight the issues arising while scaling the MOS transistor it is helpful to consider the basic design of this device, some facts from the theory of its operation and how it is incorporated into the ICs [1-2]. The simplified structure of the transistor inside the IC is shown in fig. I.1. The ICs are manufactured on the Si substrate, which is usually a wafer in (100) orientation. At the front end of production sequence the basic parts of the MOS transistor are created: source and drain regions (the regions of doping opposite to that of a substrate), gate dielectric (traditionally SiO<sub>2</sub>) and gate electrode (traditionally poly-Si). Direct contacts to Si parts of the transistor (source, drain and gate) are usually done with silicides (traditionally WSi<sub>2</sub>, TiSi<sub>2</sub>, or CoSi<sub>2</sub>) in order to obtain contacts with low resistance [5]. The silicide is followed by the layer which serves as a diffusion barrier preventing any diffusion of metal into Si. One of the most widely used barriers is TiN, sometimes in combination with Ti layer [6]. The interconnecting wires are placed on top of the interlayer dielectric (SiO<sub>2</sub>) which serves as a "circuit board" inside of which the contact holes are produced. In the case of advanced ultra-large scale integrated (ULSI) circuits there are several layers of wiring and dielectric. The contact holes are filled with the interlayer metal (usually W) and it links the interconnecting wire with the diffusion barrier. Here the chemical vapour deposition (CVD) of W is used because of its high efficiency in filling high aspect ratio holes [6].

Inside of the CMOS digital circuit the sources and drains of transistors belonging to one logical element are connected to gates of transistors from other elements. During switching (from "off" to "on" states or vice versa), the saturated current of one transistor (flowing through the channel - a region of substrate between source and drain) recharges the gate capacitance of another transistor. This saturated value [2] is given by expression:

$$I_{DS} = -Z\mu C_G(V_{GS} - V_T)^2/2L$$

(I.1).

Here Z is the width of the channel (in the direction perpendicular to the plane of the drawing in fig. I.1,  $\mu$  is the carriers mobility inside the channel,  $C_G$  is the capacitance

per unit area of the gate electrode, V<sub>GS</sub> is the voltage between the gate and the source, V<sub>T</sub> is the threshold voltage and L is the length of the channel. As it was stated above, during switching between the logical states the saturation current recharges the capacitance C with the time constant  $\tau = RC$ , where R is the full resistance between the recharging and recharged transistors. The recharged capacitance has two principal contributions: the capacitance of the gate and the parasitic capacitance. It is very desirable to reduce the latter and this is being accomplished through introduction of low-K interlayer dielectrics [7]. The gate capacitance contribution is proportional to C<sub>G</sub>, which in its turn should not be reduced since it would lead to lower I<sub>DS</sub>. The maximum current needed in the process of recharging is V/R, where V is the voltage to/from which the gate is recharged. If I<sub>DS</sub><V/R, then it would take longer to switch between the logical states than it is expected from the given value of  $\tau$ , and the speed of circuit operation would be compromised. In practice it always appears that the parasitic capacitance is much larger than the gate capacitance, therefore it is actually better to increase C<sub>G</sub> in order to be able to drive larger loads by larger I<sub>DS</sub>. The classical scaling rule of the MOS transistor requires that all vertical and lateral sizes are decreased proportionally [8]. As miniaturisation of ICs proceeded, C<sub>G</sub> was increased by making the gate dielectric ever thinner. It helped to maintain the necessary value of Ls, which according to (I.1) would otherwise drop due to simultaneous decrease of operating voltage. The latter is required by the tendency of making low power consumption devices and to avoid electrical breakdown or excessive power dissipation in ever smaller devices. Up to recent time it was possible to decrease the gate dielectric thickness  $t = K/C_G$  (K is the dielectric constant of the given material and is normally small) as much as the value of Ls required. However already for 0.13 µm gate length CMOS technology t reaches 1.5 nm [3-4] and at this thickness the tunnelling through the oxide becomes noticeable [9]. It is still possible to produce functional devices under this condition but only if the tunnelling current is taken into account while designing the circuit [10]. However the power consumption associated with this current will be extremely undesirable for low-power mobile applications [11]. If t is further decreased, the tunnelling current will eventually become so large (it grows exponentially when t is reduced) that the MOS transistor will not function any longer, since there will be no effective insulation between the gate and the channel. It appears that the problem can be solved only if the SiO<sub>2</sub> gate dielectric is replaced with a material having a higher value

of K [12]. In this case the same C<sub>G</sub> can be achieved with the physical dielectric thickness K<sub>new material</sub>/K<sub>SiO2</sub> times larger than it had to be for SiO<sub>2</sub> [13]. Such new materials are called high-K dielectrics and their investigations are of vital importance for enabling further advances in microelectronics [14-18]. If the physical thickness of the gate dielectric can be kept above 2 nm, the tunnelling through it will be effectively eliminated and the gate isolation from the channel will be maintained. That is a desirable scenario of CMOS technology scaling, but it had yet to be realised in practice. There are a number of materials with K higher than  $K_{SiO2} \sim 4$ , but in order to be considered as gate dielectric candidates they must meet a number of stringent requirements. In particular, a good material must be thermally and chemically stable in contact with silicon and other materials forming the gate stack, have low leakage current, not substantially degrade with time, form a high-quality interface with silicon channel, etc. It turned out a formidable challenge to satisfy all these requirements simultaneously. A known solution, which is already applied for 0.1 micron CMOS technology is a SiO/SiN stacked gate dielectric [19]. In such a structure the tunnelling current is one order of magnitude smaller than in SiO<sub>2</sub> of equivalent electrical thickness. This is however only a temporary relief for the semiconductor industry, since no proven solutions exist for CMOS scaled beyond 0.09 µm gate length [4]. There are however a lot of promising materials which are intensively investigated [14-18]: metal oxides, rare earth oxides, titanates, silicates, aluminates, etc. In the current thesis an evaluation of one of such promising high-K candidates, Pr<sub>2</sub>O<sub>3</sub>, is described. This material is unique in terms of its fairly high K  $\sim$  30, ultra-low leakage current density of  $5\times10^{-9}$  A/cm<sup>2</sup> [20-21], and possibility of application in both n- or p-type MOS devices [22], but it was hardly at all investigated in comparison with other rare earth oxides. This prompted a thorough analytical investigation of Pr<sub>2</sub>O<sub>3</sub> and its compatibility with the CMOS technology.

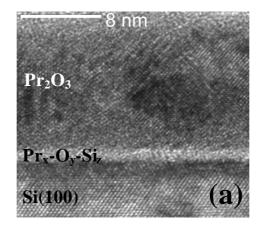

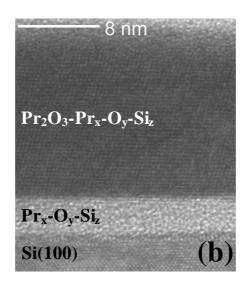

Due to the novelty of  $Pr_2O_3$ , the only readily available option to deposit it on the Si(100) substrate was by molecular beam epitaxy (MBE). In this way the qualitative difference between  $Pr_2O_3$  and  $SiO_2$  was that the first is crystalline [23-25], while the later is amorphous. In order to produce a crystalline  $Pr_2O_3$  one has to keep the temperature of the substrate in a certain range, giving the deposited molecules enough mobility, but simultaneously preventing their decomposition or chemical reaction with Si. It was possible to grow high quality  $Pr_2O_3$  films on the Si(100) substrate kept at

temperatures between 625°C and 725°C [20]. The crystalline condition of the substrate is an important factor influencing the growth process.

One of the most fundamental properties of any semiconductor surface is its reconstruction. The latter was intensively investigated for the case of the Si(100) surface already for several decades. The undying interest to this subject is fuelled by its ongoing dominant application in the microelectronics production and inability of alternative materials (e.g. III-V compounds) to become a viable replacement. The most widely investigated reconstruction of the Si(100) surface is a 2×1 dimer row structure [26]. This basic structure can have several modifications, namely a 2×n superstructure which arises due to ordering of dimer vacanices [27] and local  $c(4\times2)$  or  $p(2\times2)$  periodocities which arise due to dimer buckling [28]. The physical origins of these reconstructions are understood and their exact atomic models are developed, for which an excellent review with a historical perspective was given by Dabrowski and Müssig [29]. Surprisingly, the above-named cases have not exhausted all possible options despite many years of intensive research. It turned out, that some "exotic" (studied and understood to a lesser extent) reconstructions such as c(4×4) [30], c(4×8) [31], and c(8×8) [32] may exist on the Si(100) surface. The atomic models of their structures are not yet firmly agreed on and so are the factors which favour the formation of every particular one. This means that our knowledge of the physical properties of the Si(100) surface is still far from being complete. Understanding these properties in full is desired for further miniaturisation in Si(100)-based microelectronics technologies, thus warranting further studies. Concerning the deposition of high-K Pr<sub>2</sub>O<sub>3</sub> films, the Si(100)-c(4×4) reconstruction may be relevant in terms of forming the interface to the high-K dielectric. As thoroughly reviewed in [33], this reconstruction always appears at substrate temperatures between 550°C and 700°C independent of numerous reported preparation procedures, thus substantially overlapping with the temperature window of Pr<sub>2</sub>O<sub>3</sub> epitaxy. Obviously the properties of the c(4×4) reconstruction can strongly influence the quality of the epitaxial Pr<sub>2</sub>O<sub>3</sub> film, should the substrate find itself in this condition during growth. In particular, the substrate defects may be an aggravating circumstance, especially for ultra thin dielectric films applied in aggressively scaled MOS devices. These defects may lead to a low quality Si/high-K interface, causing all kinds of problems like reduced carriers mobility in the channel, high-K film subjected to electrical breakdown, and unsatisfactory MOS electrical characteristics, thus, making

a high quality interface an extremely important goal [14-15]. According to the previous works of other authors, it is exactly due to a large number of defects is the  $c(4\times4)$ reconstruction considered a metastable phase on the Si(100) surface (see references in [29,33]). In the meantime, it seemed strange that such kind of phase has a certain characteristic formation temperature and is insensitive to the types of adsorbates (if any) used in the preparation procedure. This controversy requires a revision of the Si(100)c(4×4) reconstruction models, for which the new insights can be gained from the scanning tunnelling microscopy (STM) investigations. The STM (although quickly approaching its 20th birthday) is still a relatively new and pioneering technique. It is capable of imaging the structure of solid surfaces with atomic resolution, thus being a front-end direct tool for studying the surface reconstructions [34]. The data presented in chapter III of this thesis give a strong hint that the c(4×4) reconstruction is a ground state of the Si(100) surface in the temperature range mentioned above. These data show how to reduce the number of defects on the Si(100)-c(4×4) surface, which may be important for obtaining high quality interfaces with Pr<sub>2</sub>O<sub>3</sub> deposited on top of it. The practical need for simulation of interfacial electronic or other properties, and also the fundamental interest in understanding semiconductor surfaces require creation of an adequate atomic model of the  $c(4\times4)$  reconstruction. As summarised in [33], the previously existed models of other authors contradicted each other, and also they could not account for the new STM images obtained in the present work and shown in chapter III. These images suggest that the  $c(4\times4)$  structure has a lower symmetry than was previously believed. This fact prompted a suggestion of the new atomic model for the Si(100)-c(4×4) reconstruction which was analysed by semi-empirical total energy calculations [33].

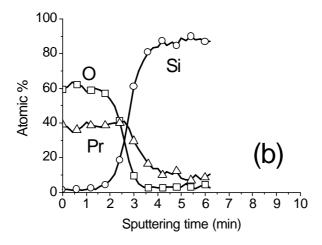

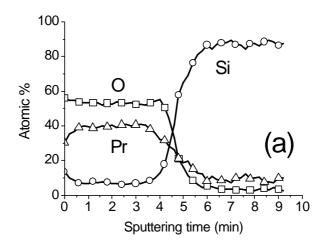

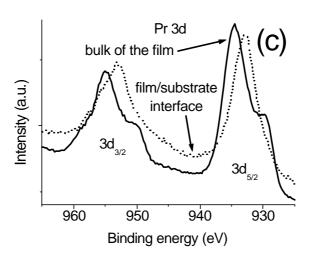

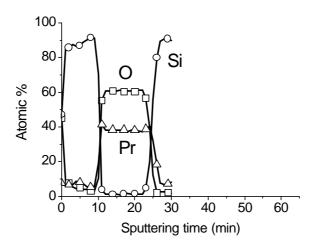

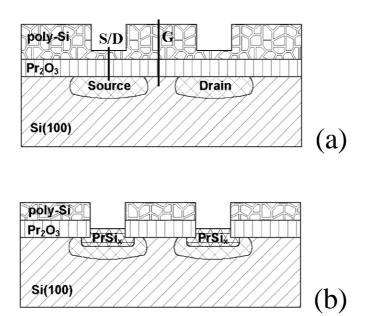

As long as a Pr<sub>2</sub>O<sub>3</sub> film is successfully deposited, one of the major concerns is its thermal stability in contact with Si. This corresponds to a traditional MOS transistor scheme (fig. I.1), where the gate dielectric is in contact with a Si(100) substrate underneath and a poly-Si gate electrode above. After transistors themselves are formed, they are inevitably subjected to several thermal treatments (silicidation anneal, dopants drive-in, etc.) belonging to the standard CMOS technology process sequence. A comprehensive study by Hubbard and Scholm [35] was aimed at estimating the thermal stability of all binary oxides in contact with Si on the basis of available thermodynamic data. These data are absent for possible reaction products in the case of Pr<sub>2</sub>O<sub>3</sub>/Si system,

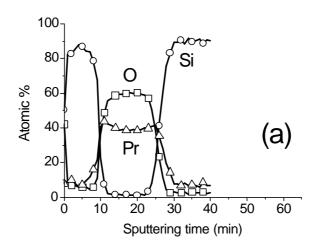

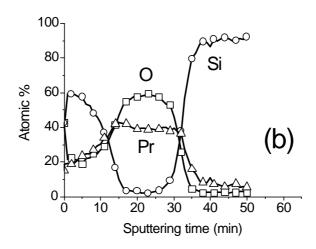

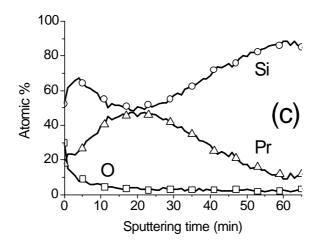

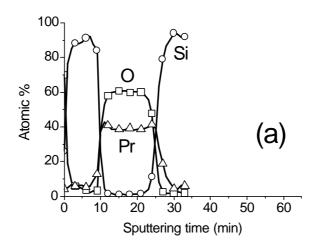

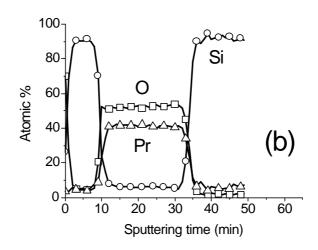

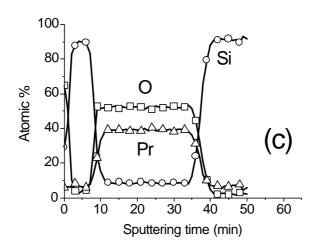

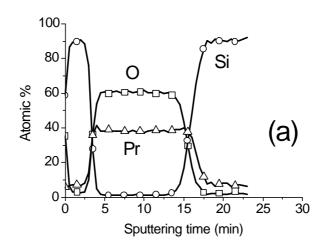

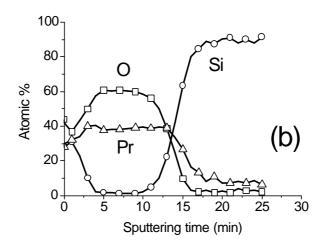

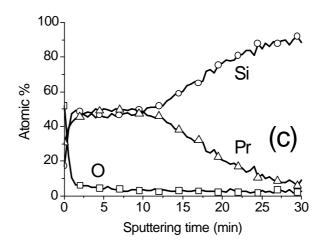

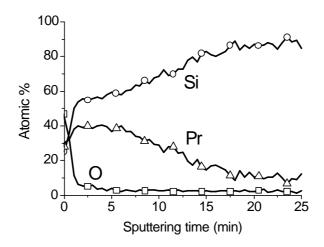

so the conclusion about thermal stability could not be reached. A more recent experimental infrared spectroscopy investigation by Ono and Katsumata [36] have detected the formation of Si-O-Pr bonds in this system at temperatures between 600°C and 800°C. The scarce information on thermal stability made obvious the need for a comprehensive research of this issue using some direct experimental technique. AES is a standard analytical tool allowing to detect chemical composition with a sensitivity of about 1% or less and lateral resolution about 100 nm or less [34,37]. When combined with ion sputtering it can reach arbitrarily deep layers inside the samples, thus being capable of producing three-dimensional elemental distribution maps. Therefore, AES depth profiling (obtaining elemental distribution as a function of depth) was used in this work to study intermixing of materials in Pr<sub>2</sub>O<sub>3</sub>/Si(100) and Si/Pr<sub>2</sub>O<sub>3</sub>/Si(100) structures. The first is of fundamental interest, while the latter is an application relevant model of the MOS capacitor or part of a MOS transistor's gate stack. Chapter IV of the thesis describes the investigations of these structures in the wide temperature range from 600°C to 1200°C both in vacuum and nitrogen environments [38]. It will be shown that the presence of nitrogen at ambient pressure leads to a much higher thermal stability, which is a positive sign because silicidation anneals (discussed in chapter VI) are usually done in this environment. Another interesting phenomenon, which will be demonstrated, is the dependency of the reaction's final product (Pr silicate or Pr silicide) on the initial geometric configuration of Pr<sub>2</sub>O<sub>3</sub> and Si. This dependency may be used for an elegant creation of source/drain contacts [39], should Pr silicide be chosen instead of traditional WSi<sub>2</sub>, TiSi<sub>2</sub>, or CoSi<sub>2</sub>.

The application of  $Pr_2O_3$  as a gate dielectric is targeted for future sub-100 nm MOS transistors. Building the ICs with such transistors will also require making other changes in the traditional set of materials applied in the modern CMOS technology. It is well known that ICs are getting not only smaller, but ever faster as well. This dictates designing logical circuits operating at ever higher frequencies, thus requiring the reduction of time constant  $\tau$  described above. Lower values of  $\tau$  can in particular be achieved by making the resistance R smaller all the way from the source or drain of the transistor in one logical element to the gate of transistor in the following logical element [40]. This goal can be achieved by using higher conductivity metal for interconnecting wires and designing lower resistance contacts between the wires and transistors. According to this trend, Cu is being actively introduced instead of Al for the

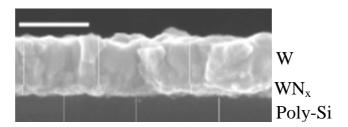

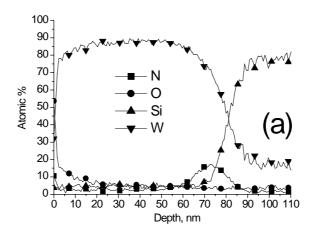

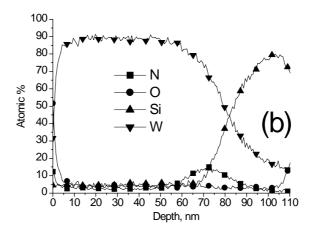

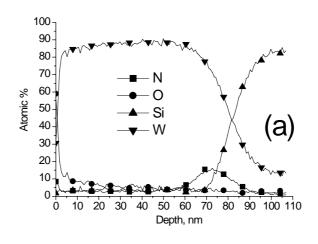

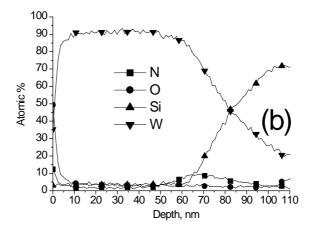

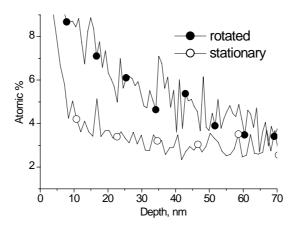

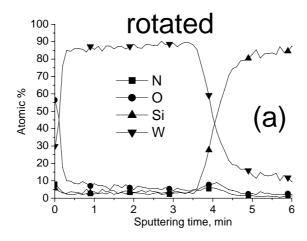

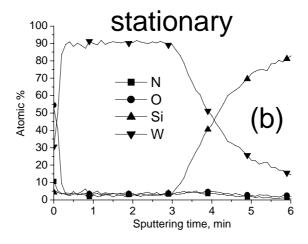

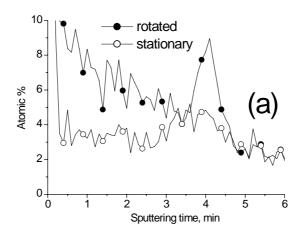

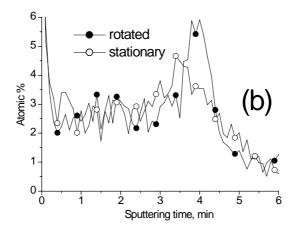

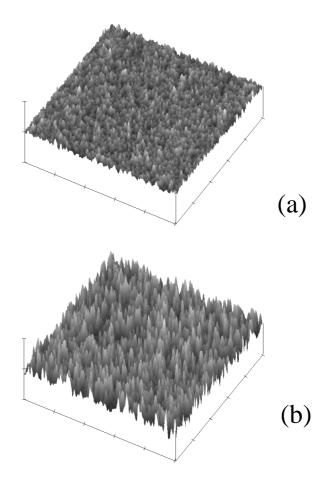

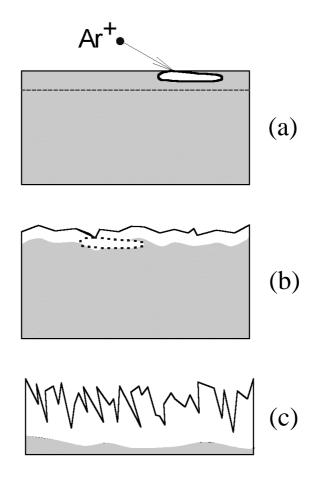

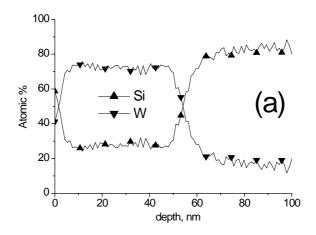

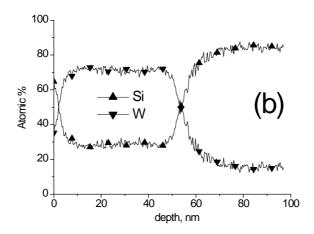

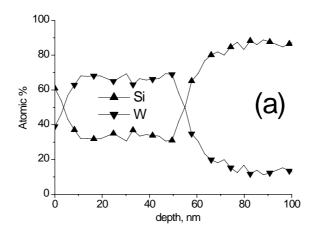

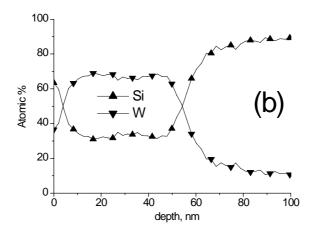

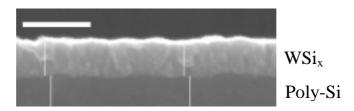

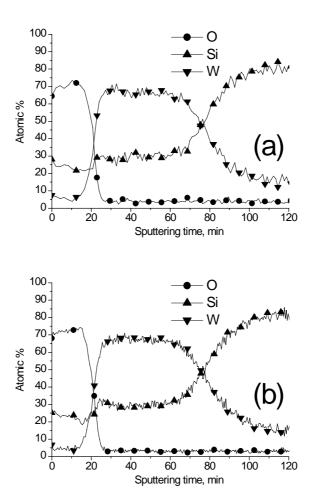

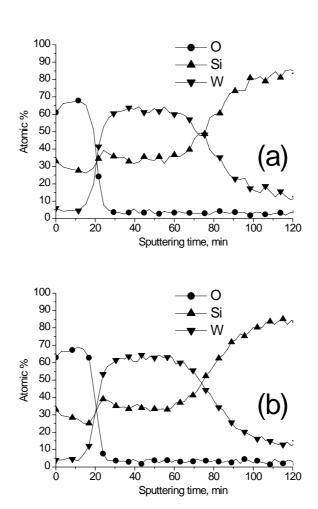

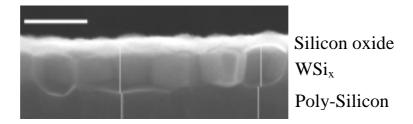

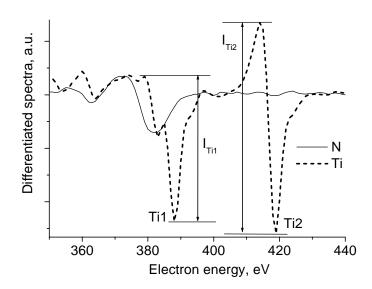

interconnecting wires [7]. An equally important task is ensuring the low resistance of contacts between wires and transistors under the conditions of shrinking sizes. Contact to the gate is a spatially most constrained location, where traditional WSi2 or TiSi2 suffer from a severe line width effect (resistivity increase at a size limitation in one or more dimensions). It was proposed to solve this problem by using W/WN<sub>x</sub>/poly-Si material combination for the gate stack [41]. This means that any silicide is completely removed from the gate and WN<sub>x</sub> barrier between W and Si actually serves to prevent silicidation [42-46]. The transistors with such gate stacks were used in particular for latest generations of dynamic random access memory ICs [47-48]. WN<sub>x</sub> was shown to be a good diffusion barrier also in cases when Cu was applied instead of Al for metallization [43-44,46] and when the higk-K material (Ta<sub>2</sub>O<sub>5</sub>) was applied as a gate dielectric [49]. The ability to grow WN<sub>x</sub> films by a CVD technique [43,46,50-51] puts it into a favourable position for application inside of very small contact holes. In the meantime, introducing this material into a real production requires its comprehensive analytic investigation. In particular, analysis of composition inside of the WN<sub>x</sub> layers and on the interfaces with W and Si is important for deposition process control and for verifying the effectiveness of WN<sub>x</sub> as a diffusion barrier. The results given in chapter V of this thesis are focused on AES depth profiling of the novel W/WN<sub>x</sub>/poly-Si and the older WSi<sub>2</sub>/poly-Si gate stacks [52]. Under the conditions of shrinking sizes of transistors, the barrier layers are getting ever thinner, thus raising an issue of adequate depth resolution in the Auger depth profiles (ADPs). Therefore, a goal was set to achieve the best possible resolution by using low energy sputtering ions and sample rotation during profiling. This worked perfectly for W/WN<sub>x</sub>/poly-Si structures, but preferential sputtering of Si did not allow to improve the depth resolution for WSi<sub>2</sub>/poly-Si samples when the latter were rotated. Also it turned out that preferential sputtering of O inside of W/WN<sub>x</sub> layers is a reason, why this element is detected better when the analysed sample is rotated during profiling than when it is stationary. Demonstration of these effects is a substantial contribution to the analysis methodology for advanced W/WN<sub>x</sub>/poly-Si gate stacks.

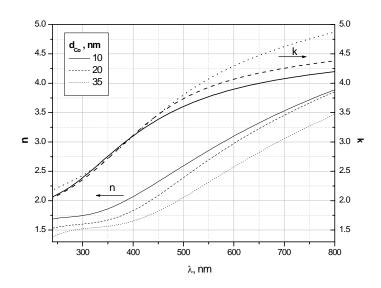

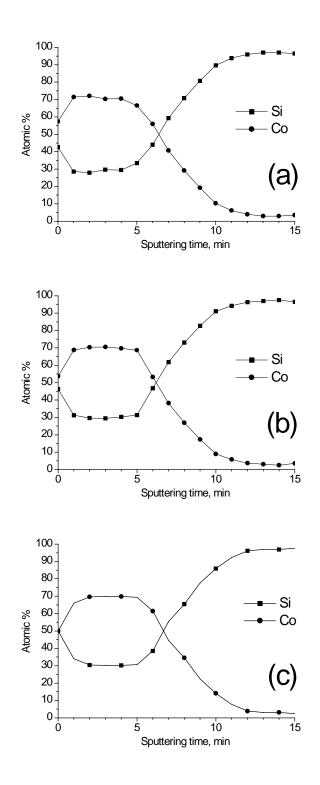

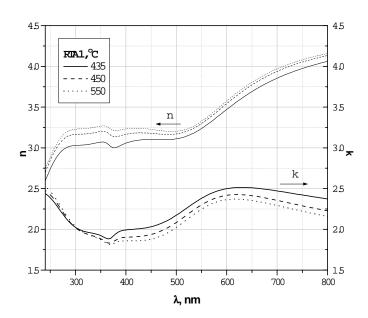

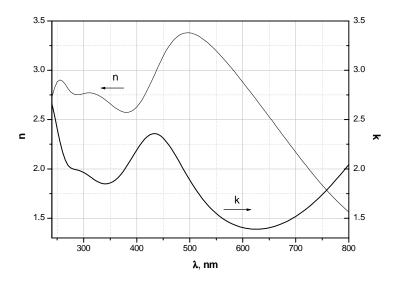

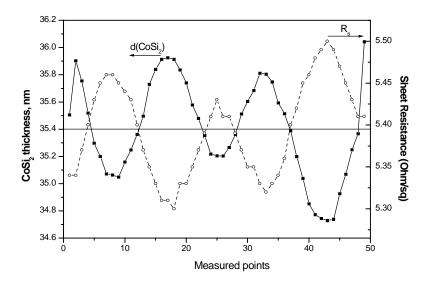

The novel sub-100 nm MOS transistors with high-K gate dielectric (e.g. Pr<sub>2</sub>O<sub>3</sub>) will also need low resistance contacts to source and drain areas [40]. Another very prospective material for making contacts between wires and transistors is CoSi<sub>2</sub>. It has a very low resistivity (18÷25 μOhm×cm) [5], which is not subject to feature size limitation [53]. CoSi<sub>2</sub> contacts can be formed through a convenient self-aligned silicide

(SALICIDE) process [1,54-55] on gate, source and drain of the MOS transistor. Such combination of desirable factors paves the way for universal CoSi<sub>2</sub> usage in the latest generations of ICs [7]. During the SALICIDE process an entire Si wafer is covered with SiO<sub>2</sub> which is removed only at contact locations. The layer of Co is blanket deposited over the entire wafer and annealed afterwards. CoSi2 formation proceeds only where Co is in direct contact with Si (where SiO<sub>2</sub> is absent), while no reaction takes place between Co and SiO<sub>2</sub>. After annealing, any unreacted Co is etched away selectively, leaving the silicide and SiO2 intact. Inside the contact holes, CoSi2 is followed by the TiN/Ti diffusion barrier, which separates the silicide from interlayer W. There arises an obvious need to control different stages of contact structure formation. In chapter VI of this thesis a multitechnique analytical investigation of the Co SALICIDE process on source/drain areas is presented. For this purpose, Co was deposited on the Si(100) substrate and annealed at different temperatures to yield three different phases (Co<sub>2</sub>Si, CoSi, and CoSi<sub>2</sub>), which were analysed by AES. Since preferential sputtering of Si during ion irradiation can distort the measured composition (as was shown for WSi2 in chapter V), it was quantitatively investigated for all three given phases [56]. After the extent of preferential sputtering was firmly established, AES depth profiling could give information about chemical uniformity and spatial distribution of different phases in thin silicide films. This allowed to identify the SALICIDE process parameters (annealing temperature and duration, film thickness, etc.) which are optimal for obtaining the targeted CoSi<sub>2</sub> layers. The obtained results were used to calibrate spectroscopic ellipsometry (SE) measurements and thus determine the optical parameters of all three silicide phases. SE [57] is a non-destructive technique for controlling the thickness and composition of thin films, which is preferred in production environment. After AES-assisted calibration, SE alone was able to identify the phases and thickness of corresponding silicide layers. It was then used as a non-destructive technique to control all stages of the SALICIDE process on the CMOS technology pilot line.

The text of the present thesis has the following structure. After the current introductory part, the details of experimental procedures are described in chapter II. All scientific work presented in this thesis is contained in chapters III-VI. The future outlook for the investigations described in chapters III-VI is given in chapter VII. The latter also gives an overview of emerging trends in CMOS technology and how the obtained results may fit into them. Further more, this part of the manuscript attempts to

create a perspective of how the surface science techniques will keep contributing into the continuous scaling of CMOS and once it is finished, how they will enter the realm of nanotechnology and nanoelectronics. The thesis is finalised with the summary of the key scientific results obtained by the author.

#### **Chapter II**

#### **Experimental techniques**

#### II.1. Auger electron spectroscopy

Auger electron spectroscopy (AES) is a powerful analytical technique, providing information about the chemical composition of near surface layers of solid bodies [34,37,58]. Physically, it is based on the Auger effect, discovered by P. Auger in 1923. When combined with ion sputtering, AES can obtain a complete three dimensional distribution of chemical elements in the sample of interest. This makes AES extremely valuable for both fundamental and applied research. Nowadays, AES had become a standard analytical tool in every industrial lab within semiconductor, chemical and other industries [59]. It is also a standard surface science technique universally used for basic research by countless groups world-wide.

#### II.1.a. Physical background of AES

The qualitative principles of AES are quite simple. The first thing, necessary for the Auger effect to occur, is the ionisation of some inner electron level A inside the atom. In practical analysis this is achieved through bombarding the sample by primary electrons, with kinetic energy  $E_p$  usually in the range from 3 to 10 keV. Another way of creating the inner vacancy is through the interaction of the atom with X-ray photon. While colliding with atoms, either electrons or photons transfer part of their energy to the electrons occupying inner levels, causing the latter to become ionised. After this, the primary particles become inelastically scattered and the ionisation electrons emerge. The ionised level A can be filled by the weaker bound electron from the occupied level B, freeing the relevant energy difference. The latter can be transferred to the third, yet weaker bound,

electron from level C. Thus, this third electron, called Auger electron, will leave the atom with kinetic energy equal to [60]:

$$E_{K(ABC)} = E_1(A) - E_2(B,C)$$

(II.1).

Here  $E_1(A)$  is the energy of a single charged isolated ion (the given atom with an electron at level A removed) and  $E_2(B,C)$  is the energy of double charged ion (the given atom with electrons at levels B and C removed). The above described process is referred to as Auger effect or Auger transition and is schematically depicted in fig. II.1. Such transitions are

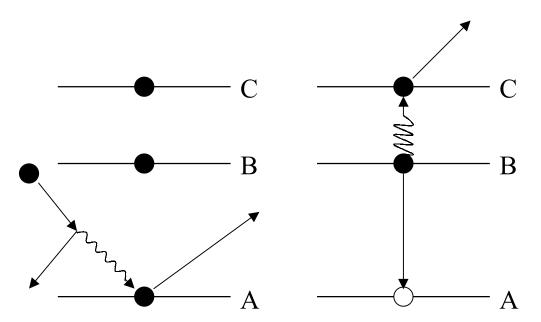

Fig. II.1. Schematic representation of Auger effect excited by collision between the electron and the atom. The primary electron ionises the level A, which is subsequently filled by electron from level B. The released energy is consumed to eject the Auger electron from level C. Filled circles depict electrons and empty circle is an electron vacancy. Straight arrows designate particle trajectories and wavy arrows - energy transfers.

denoted as ABC with actual letters designating the shells, to which involved electrons belong (such as K, L, M..., - in direct correspondence with the electron's principal quantum numbers n = 1, 2, 3...). For example, silicon can be identified by the LMM transition with  $E_{Si}(L, M, M) = 92eV$  and oxygen by KLL transition with  $E_O(K, L, L) = 503eV$ .

It is important to realise that the entire Auger electron emission is essentially a simultaneous quantum-mechanical process, which can only be approximately represented as sequential transitions of electrons between different states (including non-bound state) and energy exchange between them. If such approximation is performed one often uses the electron binding energies instead of ion energies [61]:

$$E_{K(ABC)} = E_{B(O)}(A) - [E_{B(O)}(B) + E_{B(O+1)}(C) + E_{B(O+1)}(B) + E_{B(O)}(C)]/2$$

(II.2).

Here  $E_{B(O)}(A)$  is the binding energy of the electron at level A in the atom with nuclear charge Q. The first two terms inside the square brackets in equation (II.2) are based on the following reasoning. The binding energy of the electron at level B is subtracted from that at level A, giving the energy released after the first vacancy is filled. This energy is then reduced by the binding energy of the electron at level C, in order to estimate the kinetic energy of Auger electron. Since the electron leaves from level C when there is a vacancy at level B, it is like leaving an atom with a nuclear charge larger by one. In reality one can not distinguish which electron fills the initial vacancy and which is emitted – B or C. That is why an arithmetic mean of energies corresponding to both possibilities is calculated through introducing the third and the fourth terms into the square brackets and dividing the latter by two. Expression (II.2) neglects the interaction between two vacancies left inside the atom after the Auger process has taken place and the difference between the single electron wave functions in the ion and in the neutral atom. There are also other sample specific factors like energy shifts of the electron levels inside the solid body comparative to the free atom or electron energy shifts due to chemical surrounding in compounds, mixtures and alloys comparative to pure chemical elements. Nevertheless it appears that Auger electrons' energies remain more or less constant and characteristic for every chemical element, except helium and hydrogen, always allowing for unambiguous determination of chemical species, which are present in the sample.

#### II.1.b. Basic realisation of AES

There are a number of ways to ionise the atoms and excite the Auger effect [34]. The most widely spread approach, which is also used in this work, relies on bombarding the sample with primary electrons of certain kinetic energy in the range from 3 to 20 keV. After the Auger electron has left the sample it is necessary to detect this electron and determine its kinetic energy. This is done by an electron energy analyser, which filters out all electrons except with kinetic energy it is tuned to, and by an electron current detector, which counts the electrons (measures their current) after they have passed the analyser. The tuned energy is scanned over a range where Auger energies (Auger spectral lines) are usually found from  $\sim$ 10 eV to  $\sim$ 2400 eV [62]. As a result, the electron current passing through the analyser is recorded as a function of electron energy I(E). When the analyser is tuned to an energy E, it actually lets the electrons having energies within a certain interval  $\Delta$ E to go through. The latter always has the finite value and determines the analyser's resolution as

$$r = \Delta E/E$$

(II.3).

The efficiency of collecting electrons with kinetic energy E is characterised by the analyser's transmission T(E). Further, as the electrons have passed the analyser they are registered by a detector, which in turn has its own sensitivity D(E). One may thus write the following relation between the raw signal I(E) and the energetic distribution N(E) of the electrons entering the analyser:

$$\begin{split} E+0.5\Delta E & E+0.5\Delta E \\ I(E) &= \int\!\! T(E)D(E)N(\epsilon)d\epsilon \approx T(E)D(E)\int\!\! N(\epsilon)d\epsilon \approx T(E)D(E)N(E)\Delta E = T(E)D(E)rEN(E) \\ E-0.5\Delta E & E-0.5\Delta E & (II.4). \end{split}$$

The values of T(E) and D(E) are in principle dependent on energy, however may be safely considered constant within the measured width of Auger spectral lines, thus being taken out of integration. Since in AES practically all of the information is extracted from narrow

spectral regions encompassing these lines, T(E) and D(E) may be considered as instrumental gain coefficients rather than real functions of energy. Also, the cylindrical mirror electron energy analyser (CMA) has constant r determined by its geometry. Therefore the energy distribution of electrons entering the analyser is measured in the form EN(E), since the measured signal is proportional to this product. Although it is not a problem to obtain a pure N(E) distribution via subsequent computer processing, it is traditionally accepted to use EN(E) for further spectroscopic analysis.

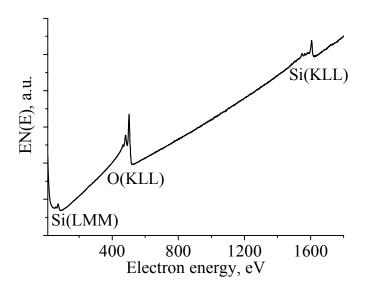

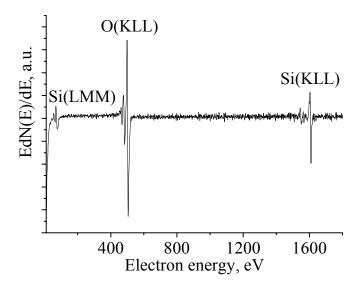

The EN(E) spectrum is a continuous distribution representing the electrons leaving the solid body as a result of irradiation by primary electrons. It has contributions from elastically scattered primary electrons, inelastically scattered primary electrons, secondary electrons and Auger electrons. The contribution from the latter is small comparative to others, so Auger spectral lines appear only as small peaks on the powerful background [63]. This is illustrated by fig. II.2, where the EN(E) spectrum of SiO<sub>2</sub> excited by 10 keV primary electrons is given. Three Auger transitions: Si(LMM), O(KLL) and Si(KLL) are visible together with their satellite structures. In order to eliminate the background and distinguish the Auger peaks better the I(E) raw data are differentiated:

$$dI(E)/dE = T(E)D(E)r[N(E) + EdN(E)/dE] \approx T(E)D(E)rEdN(E)/dE \quad (II.5).$$

The first term in square brackets is neglected, because it is much smaller than the second term in the spectral region approximately above 50 eV - where most of Auger peaks are found. The EdN(E)/dE distribution is called a differentiated spectrum and its example, obtained from data of fig. II.2, is given in fig. II.3.

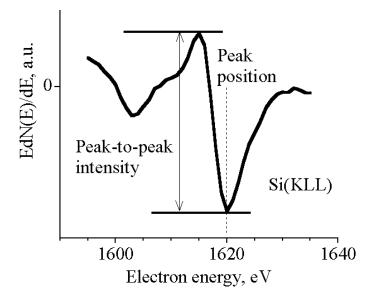

There are two major characteristics of the peak in the differentiated spectrum as exemplified in fig. II.4 by the Si(KLL) peak, measured on pure Si excited by 10 keV primary electrons. The peak position on the energy scale is assumed to correspond to its most negative value, as shown by the dotted line. This characteristic is used for assigning any particular peak to the corresponding chemical element by comparison with the published or measured peak energies from elemental standards. The intensity of the peak (designated by the double-sided arrow drawn between two horizontal bars) is assumed to be

Fig. II.2. An example of EN(E) AES spectrum of  $SiO_2$  excited by 10 keV primary electrons. Three Auger peaks are visible: Si(LMM), O(KLL), and Si(KLL).

Fig. II.3. A differentiated AES spectrum of  $SiO_2$  (obtained from data of fig. II.2). The background of non-Auger electrons is practically eliminated, leaving the Auger peaks nicely distinguishable.

Fig. II.4. Si (KLL) AES peak and its two major characteristics. The peak position is the energy of the lowest signal value in the differentiated spectrum. The intensity is the difference between its highest and lowest values.

a height difference between its most positive and most negative values. This difference is called the peak-to-peak intensity [64] and is used to calculate atomic concentration of the element in the sample, as described in the following section.

#### **II.1.c.** Quantitative AES

The principal task of quantitative AES is to determine the atomic concentrations of all elements found in the investigated sample [65]. This is achieved through establishing the correlation between the atomic concentration of some element and the current of Auger electrons corresponding to it. The probability that an atom of a certain sort will be ionised per unit time is a product of the ionising electrons current density  $\rho_i$  in the point of atom's location and the ionisation cross-section  $\sigma_A(E_p)$  for the core level A, giving rise to the Auger transition ABC. The number of atoms ionised per unit time and per unit depth of volume irradiated by primary electrons is  $\rho_i\sigma_A(E_p)C(z)S$ , where C(z) is an atomic concentration of the given atoms at a depth z below the surface and S is the surface area on which the primary electron beam is focused. When the primary electrons enter the analysed

sample and travel inside of it, some of them are reflected back, either elastically or inelastically but can still produce ionisation. These electrons are called backscattered electrons and cause the  $\rho_i$  to be larger than  $\rho_p$  - the current density associated with primary electrons. It is written in the form  $\rho_i = \rho_p[1+R(E_p,E_{iA},\alpha)]$ , where  $R(E_p,E_{iA},\alpha)$  is called the backscattering factor depending on primary electrons energy Ep, ionisation energy EiA of level A and the angle  $\alpha$  of primary electrons incidence relative to the surface normal. One can therefore write the number of ionised atoms per unit time and per unit depth as  $\rho_p[1+R(E_p,E_{iA},\alpha)]\sigma_A(E_p)C(z)S = I_p[1+R(E_p,E_{iA},\alpha)]\sigma_A(E_p)C(z)sec\alpha$ , where  $I_p$  is a primary beam current. The ionised atom will relax through Auger transition ABC and emit the Auger electron into the solid angle of the analyser's entrance aperture with probability P<sub>ABC</sub>. The electrons originating in the solid body are attenuated exponentially with distance due to various scattering processes as they travel towards the surface. That is why Auger electrons emitted at different depths contribute differently to the stream of electrons departing from the surface. This effect is characterised by the inelastic mean free path  $\lambda(E_{K(ABC)})$ , which is the average distance that the electron with kinetic energy  $E_{K(ABC)}$  will travel before being inelastically scattered. For most of Auger kinetic energies  $\lambda(E_{K(ABC)})$  does not exceed 3÷5 nm, thus making AES essentially a surface sensitive technique. In order to get the current N<sub>AES</sub>(E<sub>K(ABC)</sub>) of Auger electrons from a certain element one should integrate over its concentrations at all depths weighed by appropriate attenuation factor. If  $\beta$  is the angle at which electrons leave the solid body relative to the surface normal, one can write:

$$N_{AES}(E_{K(ABC)}) = I_p[1 + R(E_p, E_{iA}, \alpha)]\sigma_A(E_p)P_{ABC}sec\alpha \int\limits_0^\infty C(z)exp[-zsec\beta/\lambda(E_{K(ABC)})]dz \quad (II.6).$$

A very important case is the homogeneous sample with concentration C independent on depth. Then the integration can be performed analytically and (II.6) will be transformed into:

$$N_{AES}(E_{K(ABC)}) = I_p[1 + R(E_p, E_{iA}, \alpha)]\sigma_A(E_p)P_{ABC}sec\alpha Ccos\beta\lambda(E_{K(ABC)}) \quad (II.7).$$

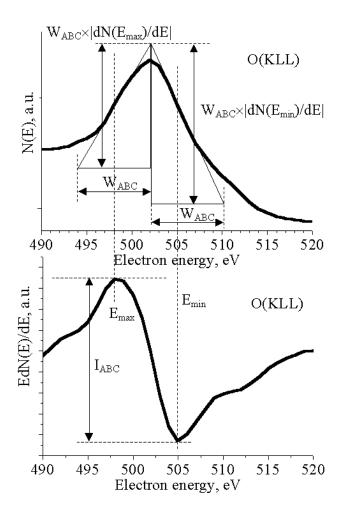

This expression was used for calibration of spectrometer's sensitivity to any particular element through elemental standards. The total amount of electrons  $N(E_{K(ABC)})$  entering the analyser with some particular energy  $E_{K(ABC)}$  consists of Auger electrons given by (II.6) and of background electrons  $N_{background}(E_{K(ABC)})$  originating from inelastic scattering processes. It has de facto proven impossible to remove the  $N_{background}(E_{K(ABC)})$  contribution completely in a well defined and consistent manner. In the simplest (and most widely used) approximation it is considered that the background is a very weak function of energy in comparison with a rapidly changing Auger signal. Thus the  $N_{AES}(E_{K(ABC)})$  will be a dominating contribution in the differentiated spectrum (II.5), where  $N_{background}(E_{K(ABC)})$  can be neglected. The peak-to-peak intensity  $I_{ABC}$  described in the previous section is essentially a peak's energy multiplied by the sum of absolute values of slope on both sides of the peak in N(E) representation. This is exemplified by the O(KLL) peak shown in fig. II.5 in N(E) and EdN(E)/dE representations.

The peak has an asymmetric shape due to characteristic low energy tail on the left side of the peak due to Auger electrons which have lost some of their energy through inelastic collisions. These electrons are not counted in  $N_{AES}(E_{K(ABC)})$ , since scattering was explicitly taken into account in (II.6) and (II.7) through the parameter  $\lambda(E_{K(ABC)})$ . The area of the peak can be approximated by two right angle triangles drawn with solid lines on the N(E) plot. The basis of every triangle is equal to  $W_{ABC}$ , which characterises the natural peak width (provided the analyser's resolution  $\Delta E$  is sufficient for not distorting the peak's shape). The hypotenuses are tangent lines to the N(E) curve in the maximum and minimum points of dN(E)/dE. In a simple approximation the area of such triangle (having the dimensionality of the number of electrons) is equal to  $N_{AES}(E_{K(ABC)})$  - showing the number of electrons introduced above the background by the peak's presence. This area can be written as  $0.5(W_{ABC})^2|dN(E_{max})/dE| + 0.5(W_{ABC})^2|dN(E_{min})/dE| = 0.5(W_{ABC})^2[dN(E_{max})/dE| - dN(E_{min})/dE|$ . Then using (II.5) one can write:

$$N_{AES}(E_{K(ABC)}) \approx 0.5 I_{ABC}(W_{ABC})^2 / T(E_{K(ABC)}) D(E_{K(ABC)}) r E_{K(ABC)}$$

(II.8).

Fig. II.5. Estimation of O(KLL) peak area in the N(E) spectrum and its connection to peak intensity in the EdN(E)/dE spectrum. The intensity is proportional to the number of Auger electrons, which have not lost their energy.

Finally using (II.7) and (II.8) the following relation between the measured peak-to-peak intensity and the elemental concentration in the homogeneous sample can be established:

$$\begin{split} I_{ABC} &= C[1 + R(E_p, E_{iA}, \alpha)] \times \\ &\times 2I_p \sigma_A(E_p) P_{ABC} sec \alpha cos \beta \lambda(E_{K(ABC)}) T(E_{K(ABC)}) D(E_{K(ABC)}) r E_{K(ABC)} / (W_{ABC})^2 \quad (II.9). \end{split}$$

The proportionality coefficient between  $I_{ABC}$  and C can be divided into two parts: the instrumental factor  $F_{ins} = 2I_{p}sec\alpha cos\beta T(E_{K(ABC)})D(E_{K(ABC)})r$  (containing the quantities which can be changed or vary as experimental parameters for different spectrometers) and

sensitivity factor  $S_{ABC}(element) = [1+R(E_p,E_{iA},\alpha)]\sigma_A(E_p)P_{ABC}\lambda(E_{K(ABC)})E_{K(ABC)}/(W_{ABC})^2$  (containing the quantities which can not be changed and characterise the effectiveness of detecting some particular element with Auger transition ABC). Thus (II.9) can be rewritten as:

$$I_{ABC} = CF_{ins}S_{ABC}(element)$$

(II.10).

It is important to note that expressions (II.9-10) are based on (II.7) and therefore valid only for the homogeneous sample. Expression (II.10) was used for quantitative AES analysis throughout the present work. First FinsSABC(element) products were determined for every element of interest, using homogeneous standards with known concentrations. Whenever possible, pure elemental standards were used (for example metals or silicon), but in the case of gases (oxygen, nitrogen) well defined compounds (like silicon dioxide or silicon nitride) were utilised. Every standard sample was measured together with the Si standard under identical conditions (with equal instrumental factors). Then, all elemental sensitivities were referenced to Si or in other words the ratio of products  $F_{ins}S_{ABC}(element)/F_{ins}S_{KLL}(Si) = S_{ABC}(element)/S_{KLL}(Si)$  were calculated and stored in the processing database. This had an advantage of removing the instrumental factor and extracting the sensitivity factors independent of experimental conditions or instrumental parameters. When the unknown sample was investigated, its chemical composition was represented through partial concentrations  $C_{\alpha}$  expressed in atomic percents - meaning the percentage of atoms of type  $\alpha$  among all other species occurring in the sample. According to (II.10) the partial concentration is equal to:

$$\begin{split} C_{\alpha} &= 100 \times I_{\alpha} / [F_{ins} S_{\alpha} (\Sigma I_{\beta} / F_{ins} S_{\beta})] = 100 \times [I_{\alpha} / S_{\alpha}] / [\Sigma I_{\beta} / S_{\beta}] \equiv \\ &\equiv 100 \times I_{\alpha} \times [S_{\alpha} / S_{KLL}(Si)]^{-1} \times [(\Sigma I_{\beta} / S_{\beta}) S_{KLL}(Si)]^{-1} \quad (II.11). \end{split}$$

The summation inside of the brackets is done over all elements which are found in the sample and included into the quantification calculation. In (II.11) the first transformation is possible because during measurement of every particular sample the experimental

conditions (and thus instrumental factor) are not changed and the second transformation is a trivial division of denominator and enumerator by  $S_{KLL}(Si)$  aimed to make use of the ratios recorded in the processing database. The final form of (II.11) establishes a direct relation between the peak-to-peak intensity  $I_{\alpha}$  of the given Auger transition of element  $\alpha$  and its partial concentration inside of the sample. This relation was universally used for quantification of AES data into chemical composition throughout this work.

#### II.1.d. AES experimental setup

A commercially available "PHI 670 Auger Nanoprobe" system from Perkin Elmer Physical Electronics was used in this work [66]. This system features the Auger spectrometer combined with the scanning electron microscope (SEM) housed in the ultrahigh vacuum (UHV) chamber with background pressure in the  $10^{-10} \div 10^{-11}$  mbar range. The sample exchange could be conducted via a loadlock without breaking the vacuum in the main chamber. The Schottky thermal field emitter was used as a source of primary electrons. It had a zirconiated single crystal tungsten tip operating at a temperature of 1800°K. The primary electrons were focused on the analysed sample by the electron optics column with the possibility of scanning over the sample's surface. This allowed to operate the column in the SEM mode, which was used for observation of sample's surface and selecting an appropriate part of it for analysis. The kinetic energy of primary electrons could be set anywhere between 0 eV and 20 keV. The AES analysis was performed using 10 keV primary beam at 30° angle of incidence, typically with a current of 100 nA rastered over the area 20×30 μm<sup>2</sup>. The analyser was of cylindrical mirror type (CMA) with the multichannel plate electron detector. The energy range accessible to the given CMA is from 0 eV to 3200 eV and the resolution is better than 0.6% (r = 0.006). AES depth profiling was performed in cycles of interchanged ion sputtering and recording preselected spectral regions, which contained Auger peaks of the elements of interest. During every cycle some layer of sample's material was sputtered away and elemental concentrations were determined on exposed surface. In this way the elemental distributions as a function of depth inside the

sample, or AES depth profiles (ADPs), were obtained. The sputtering was performed by a differentially pumped ion gun, which produced a beam of Ar<sup>+</sup> ions with kinetic energy up to 5 keV. If not stated otherwise, 1 keV energy and ~55° angle of incidence were used. The ion beam was focused and rastered in the sample surface plane over several mm<sup>2</sup> in order to eliminate the crater edge effects on the ADPs.

#### II.1.e. Related technique: X-ray photoelectron spectroscopy

The X-ray photoelectron spectroscopy (XPS) [63-65] is an analytic technique closely related to above described AES. Both share similar parts of instrumentation, employ similar data evaluation methods, and pursue a similar goal of elemental analysis on surfaces. The XPS is based on the photoeffect, namely a process of atom ionisation by means of photon absorption. The ejected electron is called photoelectron, and measuring its kinetic energy  $E_{\rm kin}$  allows for chemical identification of the atom of origin, provided the initial photon energy  $\omega$  is known. According to the law of energy conservation one can write:

$$\omega + E_A = E_{kin} + E_I$$

(II.12),

where  $E_A$  and  $E_I$  are the full energies of the atom and the ion respectively. Since the binding energy of the electron  $E_B = E_I - E_A$ , a well known photoeffect equation is obtained:

$$E_B = \omega - E_{kin}$$

(II.13).

The binding energy changes only slightly due to atom's surrounding, thus reflecting the specifics of chemical bonding. The chemical state of the atom (e.g. oxidised or not, etc) is more straightforward to interpret than in AES, since only one atomic level is involved, as compared with three in (II.1). Since binding energies are the "fingerprints" of chemical elements, both qualitative and quantitative elemental identification is possible. In this

respect XPS has approximately equal power as AES does. Due to the same reason as AES (see II.1.c), the XPS is also surface sensitive, being able to analyse only a few atomic layers under the specimen surface. An important difference between two techniques is the lateral resolution, or the smallest area which can be analysed. Due to a far better ability to focus electrons than X-rays, a sharply focused primary electron beam is easily produced. This brings a lateral resolution of modern AES spectrometers deep into sub-µm region, while XPS spectrometers reach several dozens of µm at best. Therefore, one can not use the XPS for analysis of chemical composition in device-size areas of modern ICs.

In the present work the XPS analysis was performed using the "PHI Model 5600 MultiTechnique System". In this system the X-ray source, the sample, and the electron energy analyser are housed in the UHV chamber, thus ensuring ultra-clean conditions for chemical analysis. A  $K_{\alpha}$  line of X-ray radiation originating from Al anode due to electron bombardment ( $\omega \sim 1486.5~\text{eV}$ ) is used to excite the photoelectron spectrum. The kinetic energy of photoelectrons is measured by spherical capacitor electron energy analyser. When it was necessary to investigate some layer inside the sample at a depth larger than the photoelectrons escape depth, an ion sputtering of sample material was used. This was done with  $Ar^+$  ions having 4 keV kinetic energy and bombarding the sample at an incidence angle of 45° to the surface normal. In this way the sample was gradually eroded, thus exposing deeper layers for chemical analysis.

#### II.2. Scanning tunnelling microscopy

A scanning tunnelling microscope (STM) is a tool which allows to investigate the surface topography of conducting and semiconducting samples [34,67]. It has an extremely high spatial resolution, namely on the order of 0.1 nm in the surface plane and on the order of 0.001 nm perpendicular to the surface. Due to these parameters it becomes possible to observe the arrangement of individual atoms. The STM was invented in 1982 by G. Binnig and H. Rohrer, for which they were awarded the 1986 Nobel Prize in physics [68]. Now almost 20 years since its creation, the STM is a standard analytical tool for every surface

science lab. Hundreds of both commercial and home-made instruments are used throughout the world for fundamental research, but the application of this technique in an industrial environment is nevertheless extremely limited.

#### II.2.a. Physical background of STM

The operation of STM is based on the tunnelling effect, which is a manifestation of the wave-particle duality. The tunnelling effect is a process when the quantum particle traverses the region of space where its full energy is smaller than its potential energy. This region of space is called the potential barrier, which is characterised by its shape (spatial configuration of the region) and height (the value of the potential energy). Fig. II.6 shows a one-dimensional barrier between two metal electrodes, separated by the distance d. In the STM terminology these two electrodes are called sample and tip, and are characterised by workfunctions  $\phi_s$  and  $\phi_t$ , and by the electronic densities of states  $\rho_s(E)$  and  $\rho_t(E)$ . The latter are functions of electron's full energy referenced to the Fermi level of each particular electrode. Fig. II.6a corresponds to the situation when no electrical potential difference is applied between the electrodes. In this case the Fermi level E<sub>f</sub> has equal positions in the sample and in the tip, therefore electrons do not tunnel between them. Fig. II.6b shows the case when a potential difference V is applied between the tip and the sample. Now the electrons can tunnel from the occupied states of the negatively biased electrode into the equienergetical vacant states of the positively biased electrode. As a result, an electric current, which is called the tunnelling current, is flowing between the tip and the sample. For barrier in fig. II.6 and when the voltage V is applied to the sample the tunneling current is expressed in the following way (m is electron's mass) [69]:

$$\begin{array}{c} eV \\ I_t \sim \int \!\! \rho_s(E) \rho_t(E - eV) exp(-2dm^{1/2}h^{-1}[\varphi_s + \varphi_t + eV - 2E]^{1/2}) dE \\ 0 \end{array} \ (II.14).$$

Fig. II.6. A one-dimensional tunnelling barrier between two metal electrodes. a) The case of zero potential difference between the electrodes. The electrons can not tunnel, because no occupied states (cross-hatched areas on the  $\rho(E)$  distributions) are energetically aligned with the empty states on the other side of the barrier. b) The case of potential difference V applied between the electrodes. The electrons from occupied states of the negative electrode can tunnel into empty states of the positive electrode.

#### II.2.b. Principles of STM operation

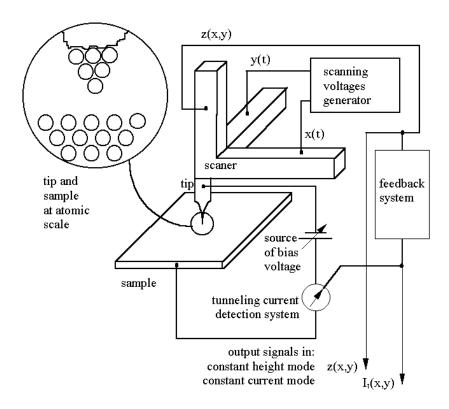

The schematic structure of STM is shown in fig. II.7 [70]. Usually, the sample (metal or semiconductor) has a relatively flat surface and the tip is an extremely sharp metallic needle (ideally atomically sharp). The tip is attached to a piezoelectric device, called scanner. It is built of piezoelectric crystals covered with metal electrodes, and it is possible to move the tip independently in three orthogonal directions by applying appropriate voltages to different electrodes. The tip is brought into sample's proximity, so that its apex is roughly 1 nm away from the surface. At this distance a measurable  $I_t$  will flow between the tip and the sample under a bias voltage of just a few Volts or even lower. When a desired value of  $I_t$  is obtained, the tip is moved parallel to the surface (x and y directions) in a raster-like manner by applying corresponding voltage sequences to the scanner. These x(t) and y(t) voltage sequences are supplied independently by the scanning voltage generator. The measured  $I_t$  value is fed into the feedback system, which compares it with the pre-set value  $I_0$ . According to (II.14),  $I_t$  depends exponentially on sample-tip separation d, and it changes very dramatically due to the slightest variations in sample's topography as a function of lateral coordinates z(x,y). When  $I_t > I_0$  the feedback system

Fig. II.7. Schematic structure of STM. The tip is attached to the piezoelectric scanner, which is being fed by the scanning voltages generator. The tunnelling current is measured in the circuit of the tip, sample, and the bias voltage source. The value of the current controls the response of the feedback system, which adjusts the tip-sample separation.

supplies such a voltage to the scanner, that it retracts the tip from the surface. On the contrary, when  $I_t < I_0$  - the tip is moved closer. As a result, the tip-surface separation is kept constant, and the tip's trajectory z(x,y) reflects the surface topography during scanning. When the tip is sharp enough, atomic resolution can be achieved when the surface image is constructed from the z(x,y) map. The described mode of STM operation is called the constant current mode. An alternative way to operate the STM is the so-called constant height mode. Then the tip is rastered along x and y co-ordinates, while its z co-ordinate is kept constant. The information about the surface topography can be obtained as  $z(x,y) \sim \ln[I_t(x,y)]$ , again due to exponential dependency of  $I_t$  on d. In this work all STM experiments were conducted in the constant current mode.

#### II.2.c. STM experimental setup

A homemade STM system with completely computerised electronic data acquisition was used in this work [71]. It had a maximum scanning range of ~1.5 μm along x and y axes and the same range of z movement. The STM head was mounted on a standard 6-inch conflat-type flange and placed in the UHV chamber with a base pressure of 2×10<sup>-10</sup> mbar. This chamber also contained the CMA type AES spectrometer, facilities for electron bombardment of samples and tips, and the metal evaporator with quartz microbalance. The tips and samples could be transferred through the load-lock, without breaking vacuum in the main chamber. The tips were formed by electrochemical etching in the NaOH solution using a W wire 0.2 mm in diameter. Such tips were annealed by electron bombardment, usually done with current of several mA and accelerating voltage of 2÷3 kV. Annealing was continued until all W oxide was desorbed and stable tunnelling could be achieved during scanning.

#### **Chapter III**

#### New features in atomic structure of the Si(100)-c(4×4) reconstruction

#### III.a. The $c(4\times4)$ reconstruction of the Si(100) surface

The  $c(4\times4)$  reconstruction of the Si(100) surface has become an object of intensive research in the recent years [30,33,72-106]. The attention is attracted to it because Si(100) is a technologically important surface in semiconductor industry, while for decades the (2×1) reconstruction seemed to be its lowest energy ground state. Since the early theoretical prediction by Pandey [76], the Si(100)-c(4×4) reconstruction was observed after various treatments of Si(100) samples in ultra-high vacuum (UHV) environment. Reported procedures of obtaining this structure always include annealing in the temperature range of 550°C÷700°C, but differ in species which are admitted to the surface if any. Namely, Wang et al [76], Lin et al [77], Nörenberg et al [78-79], and Miki et al [80] obtained the c(4×4) reconstruction by annealing the Si(100) surface in the UHV background atmosphere, while Ide et al [81], Uhrberg et al [82], and Kato et al [83] used interaction with hydrogen, Men et al [84] - oxygen, Zhang et al [85] - silicon homepitaxy, Goryachko et al [72-73], Miki et al [86], and Wasserfall et al [87] bismuth, Butz et al [88], Shek [89], and Leifeld et al [90-91] - carbon, Chen et al [92] fullerenes, Lin [93] - disilane, Shek [89], Kosugi et al [94], Takaoka et al [95], Ikeda et al [96], Stoffel et al [97], and Simon et al [98] - ethylene, Wang et al [99-100] diborane or decaborane, Moriarty et al [101] - sulphur, Hatayama et al [102] - DMGe, Saranin et al [105] - antimony, Wasserfall et al [III.18] – arsenic or antimony, Sakai et al [106] - carbon and germanium. The formation of the  $c(4\times4)$  structure in the temperature range mentioned above makes it noteworthy in the light of Pr<sub>2</sub>O<sub>3</sub> epitaxy prospects on the Si(100) surface. The latter proceeds in the 625°C÷725°C temperature range [20] and is aimed at achieving a high quality Pr<sub>2</sub>O<sub>3</sub>/Si(100) interface. Therefore it is desirable to establish an atomic model of the  $c(4\times4)$  reconstruction and determine whether it is better or not as a substrate for growth than the  $(2\times1)$  dimer row structure.

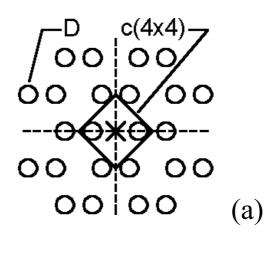

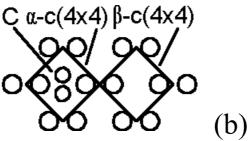

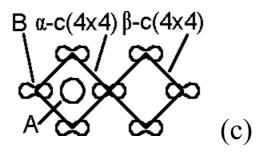

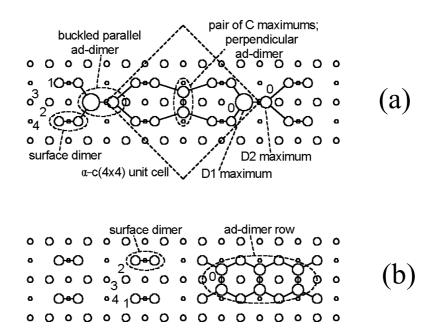

No matter of the widest preparation procedure variations, there exists universal agreement about the  $c(4\times4)$  patterns in STM, LEED or any other technique, whatever is used for surface characterization. This gives grounds to believe, that it is essentially the same Si(100)-c(4×4) structure observed after different sample treatments. No consensus is achieved about the atomic arrangement in this surface structure and what causes it to stabilize in favor of the more familiar Si(100)-2×1 dimer row structure, though carbon is most often recognized as such [78-80,88-92,94-98,103-104]. Consequently, five principally distinctive and competing models with [78,90,98] and without [76,82] carbon are most often used for interpretation of experimental data. The missing dimer model by Wang et al [76] considers the (2×1) dimer rows with dimer vacancies ordered in the c(4×4) manner. Nörenberg et al [78] had proposed a refined missing dimer model where the dimer vacancies are combined with carbon atoms in the 4<sup>th</sup> subsurface layer. Both models based on dimer vacancies stand in contradiction to the results of Ide et al [81] and Stoffel et al [97], who studied the interaction of the Si(100)-c(4×4) surface with hydrogen. These studies [81,97] strongly suggest that the Si(100)-c(4×4) structure is formed by surface dimers, which hydrogen can break. The mixed ad-dimer model by Uhrberg et al [82] deals with the parallel and perpendicular silicon ad-dimers on the defectless Si(100) surface and gives a good account of all the features observed in the STM images. Leifeld et al [90] had proposed a model of the defectless Si(100) surface, where silicon is substituted by carbon in some surface dimers and subsurface locations. Finally, the most recent model by Simon et al [98] suggests the presence of C in subsurface locations as well as on the surface in the form of Si-C heterodimers (in the ordered mixture with the same amount of Si-Si homodimers). The models by Leifeld et al [90] and Simon et al [98], however, account for only half of the features in STM images which are explained by the mixed ad-dimer model [82].

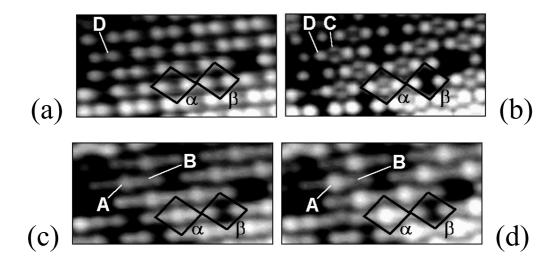

In the present work the Si(100)-c(4×4) reconstruction was encountered while studying the behavior of submonolayer Bi films on the Si(100) surface [72,73,107]. The interaction with Bi was chosen as the technically simplest technique to obtain the c(4×4) reconstruction, since very long annealing times are required to achieve it if no adsorbates are being used [77]. An observed c(4×4) structure turned out to be identical to what other researchers detected [76-102,105-106] and in particular to what Miki et al [86] and Wasserfall et al [87] had seen after the Si(100) surface interacted with Bi. In

the meantime, some evidence [33,74-75] about its behavior and features of STM appearance were not reported by other authors. Moreover, this evidence did not fit into the framework of the known c(4×4) reconstruction models [76,78,82,90,98]. Therefore, the purpose of the current investigation was to analyze possible atomic arrangements on the Si(100) surface, which could be compatible with all experimental data on the Si(100)-c(4×4) reconstruction. As a result, a new atomic model is suggested (named refined mixed ad-dimer model), which will be described below. This model will be discussed in connection with possible stabilization mechanisms of the Si(100)-c(4×4) reconstruction.

## III.b. Interaction of submonolayer Bi films with the Si(100) surface and formation of the $c(4\times4)$ reconstruction

The Si(100) samples used in the experiments were phosphor doped (4.5 Ohm×cm) and were prepared by ex-situ rinsing in acetone and hydrofluoric acid immediately before loading into the load lock of the UHV chamber. In-situ they were thermally treated by electron bombardment from the back side in the following stages: outgassing at 650°C for several hours, annealing at 1200°C for one minute, rapid quenching to 900°C and cooling down to room temperature over half of an hour. The base pressure in the chamber did not exceed 2×10<sup>-10</sup>mbar and it was always kept below 1×10<sup>-9</sup>mbar during annealing, quenching and cooling the sample. The above described preparation procedure always allowed to obtain the typical Si(100)-2×1 surface, like the one shown in fig. III.1a, and it was characterized by the ratio of peak-to-peak intensities in the differentiated AES spectrum Si(LMM, 92eV)/C(KLL, 272eV) equal to 800÷900. Bi was evaporated on this surface kept at room temperature and the deposited amount was controlled by a quartz micro-balance.

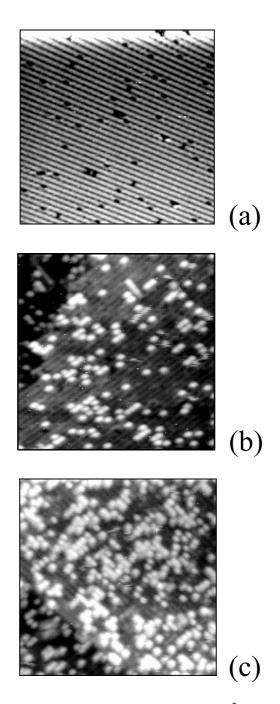

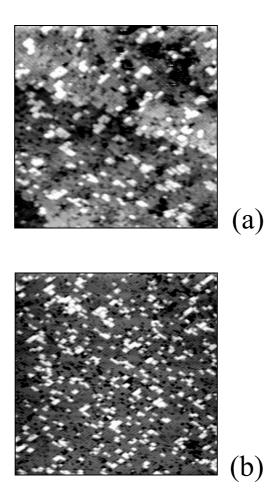

Fig. III.1 displays the images of two submonolayer bismuth coverages: b)  $\theta_{Bi}$ =0.06ML and c)  $\theta_{Bi}$ =0.15ML (1ML=6.8×10<sup>14</sup>atoms/cm<sup>2</sup> - surface atomic density on the Si(100) crystallographic plane). It is immediately seen that bright blobs appear on the background of Si(100)-2×1 reconstructed dimer rows structure. Counting the number of blobs yields half the number of atoms corresponding to the nominal

Fig. III.1. a) Clean Si(100)-2×1 surface,  $28\times28nm^2$ , U=-1.5V, I=56pA; b-c) Submonolayer Bi films deposited on Si(100)-2×1 at room temperature (bright blobs correspond to Bi dimers), b)  $28\times28nm^2$ , U=-1V, I=96pA,  $\theta_{Bi}$ =0.06ML; c)  $28\times28nm^2$ , U=-1.3V, I=96pA,  $\theta_{Bi}$ =0.15ML.

coverage, thus clearly indicating that each blob corresponds to a single bismuth dimer. Another important observation is that most of the dimers remain unordered [72,107]. There are no large islands (more than several dimers in size) of (2×1) or (2×2) ordered bismuth phases [108], which form when  $\theta_{Bi} \ge 0.2 ML$  is deposited at room temperature [109-110].

After taking the STM images of as deposited bismuth films, they were annealed at  $\approx$ 400  $^{0}$ C for several minutes. The resulting surface morphologies are shown in fig. III.2. One can judge, that bismuth dimers coalesce into squarely shaped islands, thus nucleating an ordered (2×1) phase. This result is in agreement with other works [110-112], where thermally activated ordering of larger Bi amounts into the (2×1) phase was also observed. One can also judge that a substantial amount of vacancy defects are formed in the course of annealing [72,107]. A small number of defects is already present on the initial clean surface (fig. III.1a), appearing as dark holes in the (2×1) reconstructed dimer rows structure. At fig. III.2 the number of defects is several times greater, they are unordered and some of them gather into clusters. Vacancy formation is attributed to the interaction between the Bi atom and the Si atom, which causes the latter to leave its lattice site with higher probability. It is noteworthy that very similar

Fig. III.2. The same submonolayer Bi films as in figs. III.1.b-c, but annealed at 400  $^{0}$ C after deposition. The Bi dimers coalesce into rectangular-shaped islands of the (2×1) adsorbate phase. a)  $55\times55$ nm<sup>2</sup>, U=-1.5V, I=236pA,  $\theta_{Bi}=0.06$ ML; b) $55\times55$ nm<sup>2</sup>, U=-1.5V, I=147pA,  $\theta_{Bi}=0.15$ ML.

defects were observed in the case of Sb on Si(100)-2×1 [113].

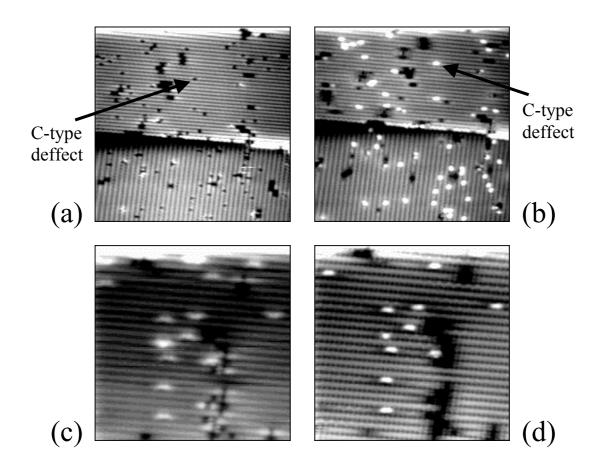

The next stage of investigation was to desorb bismuth from the surface, by heating the sample to  $\approx 600^{-0}$ C, and examine its subsequent condition. The overall topography of the silicon surface after this treatment is shown in figs. III.3a-b, where the same area is imaged in occupied and empty states correspondingly. One can see the reconstructed dimer rows structure with numerous vacancies grouped into clusters, not inherent to the starting surface [72,107]. The bright protrusions appearing in the empty states image are not the real adsorbates, since they look like slight depressions in the occupied states. Such objects are known as C-type defects [114] and they always appear on the Si(100)-2×1 surface. In order to investigate the vacancy clusters in more detail, we took the images of another smaller area, containing two large clusters. Its images in the occupied and empty states are given in figs. III.3c-d correspondingly. Because of

Fig. III.3. Vacancy clusters appear on the Si(100) surface after bismuth desorption (initial Bi coverage 0.09ML). a)  $31\times31$ nm<sup>2</sup>, U=-1.0V, I=644pA; b)  $31\times31$ nm<sup>2</sup>, U=1.0V, I=682pA; c)  $16\times16$ nm<sup>2</sup>, U=-0.8V, I=330pA; d)  $16\times16$ nm<sup>2</sup>, U=0.6V, I=1396pA.

using low sample bias voltage, C-type defects look like protrusions on both images, but the empty states image is more sharp. The most interesting feature is that vacancy clusters are "filling up", when the bias is switched from positive to negative one. They are characterized by a local density of electronic states, different from the surrounding surface areas, thus causing substantial change in appearance when the tunneling voltage is altered. It is possible that Si, C, or even residual Bi atoms (at coverage below the detection limit of AES) are filling up the vacancies - leading to the observed images.

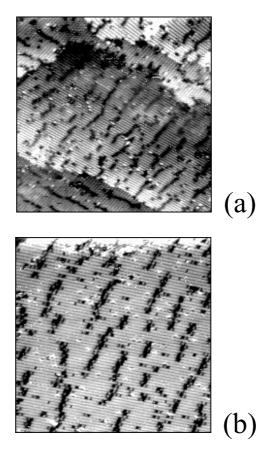

In contrast to ultra-low initial Bi amounts, thicker films ( $\theta_{Bi}>0.2ML$ ) interact with the Si(100) surface in a qualitatively different way. As an illustration, fig. III.4a shows an image of the sample after 0.69ML of Bi was deposited and desorbed. Now, instead of vacancy clusters, the vacancy lines are formed on the surface, giving rise to the local (2×n) reconstruction [72,107]. It is interesting to compare it with those on the Si(100) surface contaminated by a small amount of Ni, (fig. III.4b). Such contamination

Fig. III.4. a) Si(100) surface after deposition and thermal desorption of 0.69ML of Bi,  $54\times54$ nm<sup>2</sup>, U=1.0V, I=60pA. The vacancies are grouped into lines, thus forming a  $(2\times n)$  structure; b) Comparative image of the Ni-contaminated Si(100) surface;  $39\times39$ nm<sup>2</sup>, U=-2.0V, I=125pA.

resulted simply from handling the sample with stainless steel tweezers. While the vacancy lines show certain similarity, an important difference is that Ni contamination can not be eliminated by thermal annealing and the sample always displays the  $(2\times n)$  pattern. At the same time, the  $(2\times n)$  structure which resulted from Bi preadsorption is

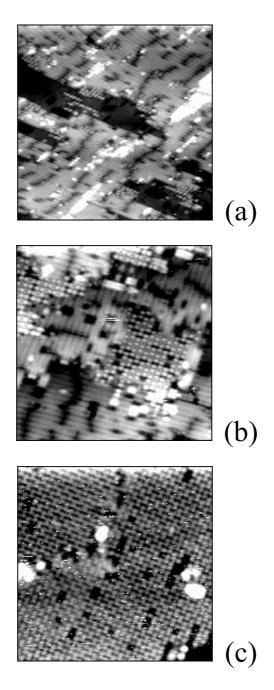

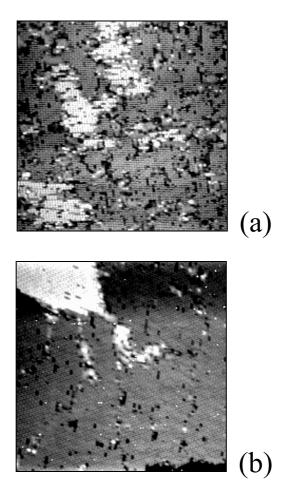

Fig. III.5. Subsequent stages of Si(100)- $2\times n \rightarrow Si(100)$ - $c(4\times 4)$  phase transition. The images were taken at  $20~^{0}$ C in between heating cycles at  $600\div700~^{0}$ C. a)  $40\times40$ nm<sup>2</sup>, U=1.5V, I=41pA, nucleation of  $c(4\times 4)$  islands; b)  $28\times28$ nm<sup>2</sup>, U=1.5V, I=90pA,  $c(4\times 4)$  patches grow in size; c)  $28\times28$ nm<sup>2</sup>, U=1.0V, I=50pA,  $c(4\times 4)$  reconstruction covers the entire surface.

completely removed after annealing at  $1200\,^{0}$ C, and the initial surface identical to those in fig. III.1a is completely restored.

Finally, if the initial amount of deposited Bi was ≥0.25÷0.3ML, then further annealing at 600÷750 °C, caused the phase transition between the Si(100)-2×n and the Si(100)-c(4×4) [72-73]. Three subsequent stages of this transition, starting from nucleation of the c(4×4) patches until it covers the entire surface, are shown in fig. III.5a-c. The total annealing time required to complete the transition was no more than half an hour. Comparing this with annealing of initially clean Si(100)-2×1 surface [77], one can judge, that preadsorbition of Bi reduces this time by one order of magnitude. The surface in fig. III.5c was stable to annealing at temperatures up to 750 °C, and did not show signs of reverse transition into the (2×1) or (2×n) states. However, if heated to 800 °C, the surface developed a large scale roughness and appeared to be disordered. Annealing the sample at 1200 °C restored the initial (2×1) structure, like shown in fig. III.1a. When the entire surface was covered with the c(4×4) phase the ratio of intensities Si(LMM, 92eV)/C(KLL, 272eV) was equal to 300. The threefold increase of carbon concentration could not be avoided and was attributed to contamination from the parts of sample holder and manipulator during annealing cycles.

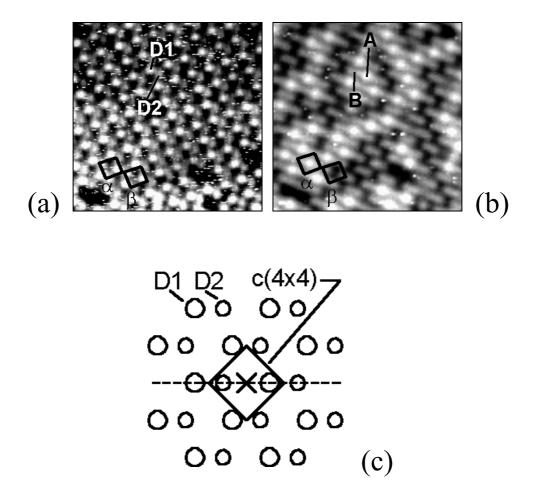

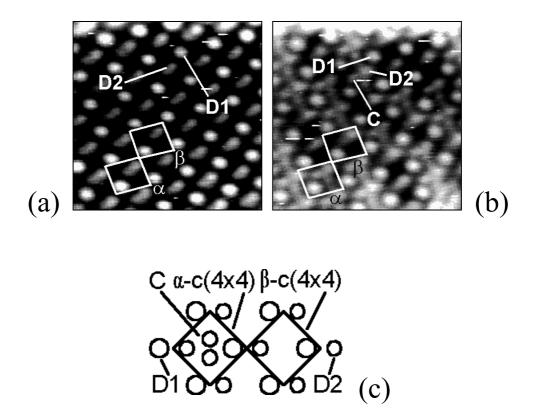

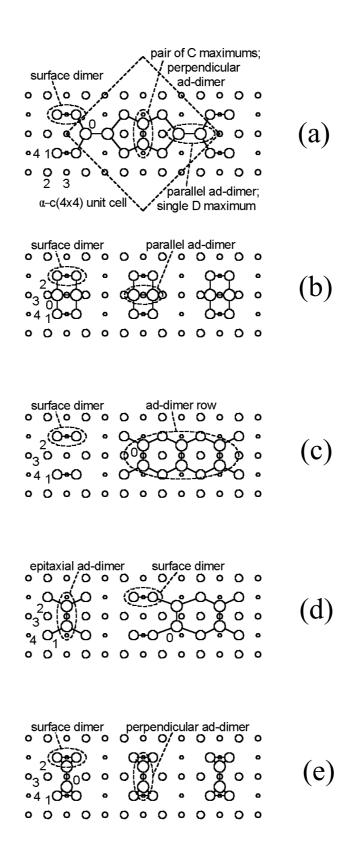

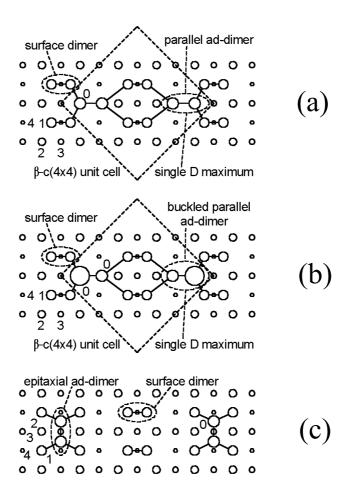

## III.c. Previously reported features of the Si(100)-c(4×4) structure